# The Investigation of Nano-Roughening Effect on the Reliability Enhancement of Adhesive Bond for NEMS Manufacture Application

Chia-Yeh Yang, Yu-Ting Cheng, and Wen-Syang Hsu

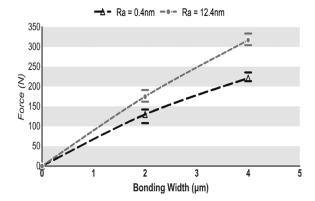

Abstract—The paper shows the importance of nano-roughening on the bonding interface to the reliability enhancement of adhesive bond for ensuring the continuation of packaging shrinkage from MEMS to NEMS. The roughening is realized via a nonuniformly etching characteristic of PR which is etched and then utilized as an etching mask for following silicon etching process. Ultraviolet adhesive for silicon-to-glass bonding is utilized for the verification of the nano-roughening effect on NEMS hermetic encapsulation. The average roughnesses of the silicon substrate before and after roughening are 0.4 nm and 12.4 nm, respectively. Experimental results show that the roughness increase of silicon substrate can effectively provide more than 30% bonding strength enhancement and 30% leakage reduction. In addition, stamp-and-stick test shows that nano-roughening indeed provides a better adhesive characteristic that can further ensure the success of the stamp-and-stick process for nano/microfabrication.

*Index Terms*—Hermetic encapsulation, nano-electromechanical systems (NEMS) manufacture, nano-roughening, scaling rule, ultraviolet (UV) adhesive bonding.

#### I. INTRODUCTION

AFER-LEVEL processing is a key principle that can ensure the success of nano/microelectromechanical Systems (N/MEMS) commercialization in terms of low manufacturing cost and high production throughput. However, similar to conventional microelectrommechanical systems (MEMS) fabrication, the mechanical structures in the systems would be susceptible to processing damage and contamination such as structural stiction, breakage, and debris deposition induced by wafer dicing operation [1]. The issue can be generally resolved via the incorporation of hermetic encapsulation into N/MEMS manufacture to protect device structure in wafer

Manuscript received January 14, 2009; revised October 02, 2009. First published February 02, 2010; current version published May 05, 2010. This work is supported by the National Science Council (Taiwan) under Grant NSC 97-2220-E-009-012, and in part by 98-EC-17-A-07-S1-001. This work was recommended for publication by Associate Editor A. Chiou upon evaluation of the reviewers comments.

C.-Y. Yang is with the Microsystems Integration Laboratory, Department of Electronics Engineering, and also with the Department of Mechanical Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: ytcheng@mail.nctu.edu.tw).

Y. T. Cheng is with the Microsystems Integration Laboratory, Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan. W.-S. Hsu is with the Department of Mechanical Engineering, National Chiao

Tung University, Hsinchu 300, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TADVP.2009.2038235

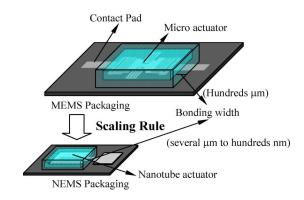

Fig. 1. The scaling rule for the packaging transition from MEMS to NEMS. The bonding width must shrink from hundreds micrometers to several micrometers or even smaller.

level. At present, utilizing microshells to encapsulate as-fabricated MEMS devices in wafer-level via an appropriate wafer bonding technique has been one of common approaches for low cost manufacture application, where the microshells simultaneously provide mechanical support, thermal and electrical path, and hermetic seal functions for the MEMS devices. In the approach, several adhesive bonding techniques have been developed and fascinated for MEMS hermetic encapsulation due to the characteristics of low-processing temperature and low-sealing cost [2]–[4].

Nevertheless, there should be a scaling rule for continuing the encapsulation development for NEMS (Nanomechanical Systems) fabrication. The shell size must be shrunk from sub-millimeter scale down to several micrometers as shown in Fig. 1 in terms of the reduction of parasitic effect and manufacturing cost of NEMS. The scaling would accompany with a reliability problem to the encapsulation which is the total bonding strength decrease resulted by the cap size shrinkage. For instance, tangential load applied to silicon wafer is around 0.2 N in a conventional dicing process with the conditions of 40 m/s blade speed, 7 mm/s workpiece feed rare, 0.5 mm depth of cut, and 50  $\mu m$  width of cut [5]. Meanwhile, the total bonding area of a microshell for NEMS encapsulation is only several thousand micrometer square since the bonding width of the encapsulation becomes only several micrometers or even smaller. In that case, the total bonding force of the shell to its substrate would become comparable with the tangential load and could evidently affect the reliability of encapsulation. Thus, this work shown in the paper is aimed to investigate the feasibility to employ

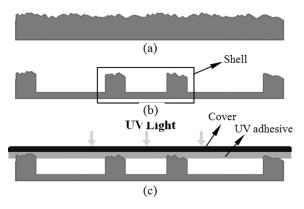

Fig. 2. The process flow of the hermetic encapsulation. (a) Surface roughening on a 4-in silicon substrate using the surface modification method which combines both spin-on photoresist and RIE etching [6]. (b) 9  $\mu$ m deep micro-concave structure fabrication using plasma etching. (c) Silicon-to-glass bonding with UV curable adhesive. (a) Surface roughness modification. (b) Shell is fabricated. (c) UV curable adhesive bonding.

a nano-roughening method for the strength and reliability improvement of adhesive bond for NEMS hermetic encapsulation application. Previously, we presented a room temperature wafer bonding technique using the UV curable adhesive, Loctite 3491, for wafer level MEMS hermetic encapsulation [2]. Since the spin-coated adhesive exhibits high bonding strength between glass and silicon substrates and good hermeticity to moisture adequate to sustain conventional water-jet dicing process and protect freestanding MEMS devices from stiction and damages, it is utilized as bonding medium for the investigation of the surface roughening scheme and the demonstration of its feasibility for NEMS packaging application abided by the aforementioned scaling idea.

#### II. EXPERIMENTAL PROCEDURE

In the experiment, a glass-to-silicon hermetic encapsulation scheme using UV curable adhesive is utilized as the demonstration vehicle for the investigation of nano-roughening effect. Two kinds of silicon surfaces, with and without nano-roughening treatments, are utilized for the comparison study. Fig. 2 illustrates the hermetic nano-encapsulation process. The nanoroughening is first accomplished on a 4-in silicon wafer using the previously developed surface modification method which combines both spin-on photoresist (PR) and RIE etching processes [6]. The modification starts with 0.5  $\mu m$  FH-6400 PR coating on a silicon substrate followed by 120 °C hot baking for 5 min. The PR coated surface is then reactive-ion-etched for 5 min using 100 W radio-frequency (RF) powered plasma with a 20 mtorr gas mixture of  $SF_6$  and  $O_2$  whose flows are maintained at 20 and 4 sccm, respectively. Due to the nonuniformly etching characteristic of PR in the condition, the PR can serve as a transferring template to make the silicon surface experience an uneven etch also under the same etching condition. Once the etching process is done, residual PR is then stripped in the solution of sulfuric acid and hydro peroxide, as shown in Fig. 2(a). The roughened silicon substrate is then spin-coated and patterned with 0.5  $\mu m$  Al layer as an etching mask for following silicon etch. The masked silicon is reactive-ion-etched to form 9  $\mu m$  deep micro concave structures, as shown in Fig. 2(b). Two

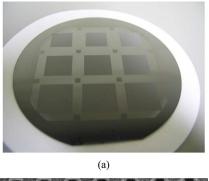

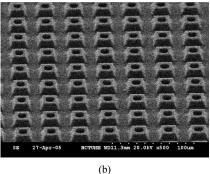

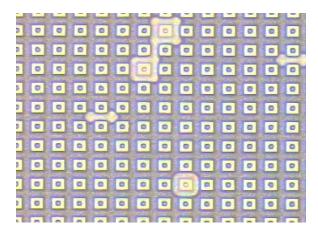

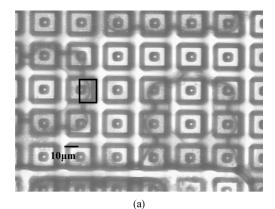

Fig. 3. (a) Optical micrograph of as-patterned silicon wafer where nine  $2\times 2\mathrm{cm}^2$  squares with dark color distribute. (b) Enlarged SEM view on each square where the microshells are distributed and designed with 4- $\mu\mathrm{m}$ -wide bonding width.

different bonding widths, 2 and 4  $\mu m$ , are chosen for bonding characterization with the nano-roughening effect. At final, the substrate is pressed to contact with a glass substrate, which is a Pyrex 7740 glass wafer coated with a layer of 3- $\mu$ m-thick UV curable adhesive. After a 40 mW/cm<sup>2</sup> flood exposure of UV light onto the bonded sample for 90 mins, hermetically encapsulated microcavitites are fabricated by the formation of adhesive bond as shown in Fig. 2(c) for following investigation of nano-roughening effect. Fig. 3 shows the as-patterned silicon wafer where nine  $2 \times 2 \text{ cm}^2$  squares with dark color distribute, as shown in Fig. 3(a). Fig. 3(b) shows an enlarged SEM view on each square where the microshells are distributed and designed with 4- $\mu$ m-wide bonding width. Once the silicon wafer is bonded with a glass wafer using the UV adhesive, the wafer will be diced into nine square pieces for following hermeticity and bonding strength characterizations. Fig. 4 shows an optical micrograph of the diced square. As shown in the figure, there is an area with different contrast indicating the occurrence of incomplete bond. The local bonding failure around the area could be due to air entrapment [2].

Two kinds of tests, optical inspection on the bonded sample with water immersion and bonding strength measurement, are used for studying the roughening effect on the hermeticity of encapsulation. The hermeticity of encapsulation is examined by immersing the bonded sample into water. These samples are immersed in a glass beaker long enough to ensure that water has filled inside the chips and has been effectively blocked by the sealing ring of each microcavity. The unbonded region in the sample could result in the leakage of water to the microcavities and would be left with water trace, which exhibits contrast

Fig. 4. Optical micrograph of silicon-to-glass bonding with UV curable adhesive. The microcavities is designed with a  $4-\mu$ m-wide bonding width. The local bonding failure around the area could be due to air entrapment [2].

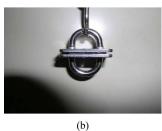

Fig. 5. The setup of bonding strength measurement. (a) Pull testing stage and (b) close view of the top and bottom sides of stainless plates which are glued to both sides of tested die, respectively.

difference caused by the refraction index difference between water and air. Thus, the failed encapsulation can be easily observed by the contrast difference once the sample is inspected under optical microscope. Bonding strength is measured using a homemade pull testing stage shown in Fig. 5. More than 10 samples for each case which is either 2 or 4  $\mu m$  bonding width with/without surface roughening treatments are measured in the bonding strength characterization. The top and bottom sides of tested die are glued to two stainless plates, respectively. Then, a pull gauge is connected to the plates and used for bonding force measurement. In order to prevent the misalignment of sample mounted on the stainless plate which would result in the redistribution of the strains/stresses and cause the error in the bonding strength characterization, we put the alignment marks on each stainless plate which can make most of the sample attach to the same position.

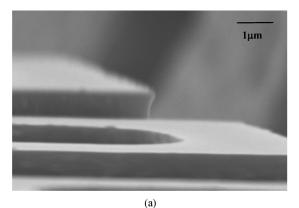

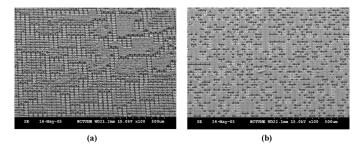

Fig. 6. SEM micrographs of silicon surfaces, (a) without and (b) with, nanoroughening treatments.

### III. RESULTS AND DISCUSSIONS

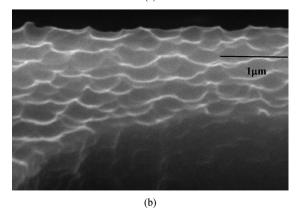

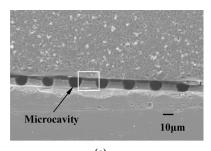

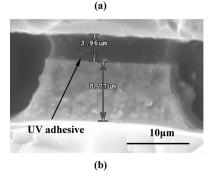

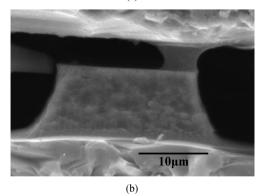

Fig. 6 shows the SEM micrographs of the surfaces before [Fig. 6(a)] and after [Fig. 6(b)] roughening whose average roughnesses characterized by optical surface profiler are 0.4 and 12.4 nm, respectively. Fig. 7 shows a uniform bond formed between two substrates while the adhesive is well UV-cured. The concave structures on the silicon substrate form hermetically sealed microcavities after bonding with the glass substrate, as shown in Fig. 7(a). Fig. 7(b), an enlarged cross-sectional SEM, shows a layer of about 4- $\mu$ m-thick cured adhesive exists between the silicon and glass substrates. Fig. 8 shows an optical micrograph of hermetic sealed microcavitites after leakage test. The darken region represents the leaky path with trapped moisture as shown in Fig. 8(a). Fig. 8(b) shows that the leakage is mainly caused by an incomplete bond formed in the bonding interface. Table I lists the leakage testing results. The leakage rate is defined as follows:

# Leakage Rate = $\frac{\text{the total number of failed microcavitites}}{\text{the total number of tested microcavities}} \times 100\%. \quad (1)$

The results show the addition of nano-roughening in the bonding interface can reduce the leakage rate about 30% in both cases whose bonding widths are 2 and 4  $\mu m$ , respectively. Besides, the result also shows the wider bonding width can exhibit lower leakage rate. Therefore, it indeed needs several process efforts,

Fig. 7. SEM cross-sectional micrographs of silicon-to-glass bonding with UV curable adhesive. (a) Overall view and (b) enlarged view.

Fig. 8. Hermeticity test results (a) optical micrograph of the hermetic encapsulations after leakage testing, and (b) enlarged SEM cross sectional view taken from the bonding interface of the failed package.

like the proposed surface nano-roughening, for the continuation of the scaling in terms of packaging size.

The bonding strength characterizations using the pull gauge are shown in Fig. 9 and summarized in Table II. The bonding strength is estimated based on the broken interface morphology,

TABLE I

LEAKAGE TEST RESULTS. SURFACE ROUGHNESS OF SILICON SURFACES WITH AND WITHOUT SURFACE ROUGHENING ARE 12.4 AND 0.4 NM, RESPECTIVELY

| Bonding Width | Surface Roughness (nm) | Leakage rate |

|---------------|------------------------|--------------|

| 2             | 0.4                    | 24.3%        |

| 4             | 0.4                    | 10.8%        |

| 2             | 12.4                   | 16.8%        |

| 4             | 12.4                   | 7.7%         |

|               |                        |              |

Fig. 9. Bonding strengths of the silicon-to-glass adhesive bonds designed with 2 and 4  $\mu$ m bonding width whose surfaces have been treated with and without non-roughening.

Fig. 10. SEM micrographs of the silicon substrate surfaces right after breaking the silicon-to-glass adhesive bonds (a) without and (b) with surface nano-roughening.

as shown in Fig. 10. Fig. 10(a) shows the silicon substrate surface after breaking the bonding interface with silicon surface roughening. The bonding ring covered by adhesive is identified as the bonded region since the adhesive is originally coated on the glass substrate. Based on the measured force from the load cell, the strength is then calculated by dividing the force by the estimated effective bonding area. The experimental results show that UV curable adhesive bond with larger surface roughness has larger bonding force. It can be attributed to the increase of effective bonding area due to the roughening. In comparison with the bonding strengths of Si-to-glass bond using UV adhesive without surface roughening, the bonding strengths of the bonding with surface roughening can be enhanced up to 34.6% and 43.2% for the case of the 2  $\mu m$  bonding width and that of  $4 \,\mu\mathrm{m}$  bonding width, respectively. In fact, Fig. 10(a) shows less silicon surface area covered with adhesive in comparison with Fig. 10(b) which is the silicon substrate surface after breaking

TABLE II

BONDING STRENGTH MEASUREMENT. SURFACE ROUGHNESS OF SILICON

SURFACES WITH AND WITHOUT SURFACE ROUGHENING ARE

12.4 AND 0.4 NM, RESPECTIVELY.

| Bonding Width (µm) | Surface Roughness (nm) | Bonding strength (MPa) |

|--------------------|------------------------|------------------------|

| 2                  | 0.4                    | 9.02±1.12              |

| 4                  | 0.4                    | 9.41±1.18              |

| 2                  | 12.4                   | 12.14±1.52             |

| 4                  | 12.4                   | 13.48±1.69             |

the bonding interface with the surface roughening treatment. It indicates that nano-roughening can provide better silicon to adhesive contact.

Although the experimental results have shown that nano-roughening can indeed enhance the reliability of adhesive bond for NEM hermetic encapsulation applications in terms of lower leakage rate and stronger bonding strength, the roughening process can only be applicable to the bonding material with self-reflowing characteristic. Reflowing can make the bonding media like the UV adhesive in this case well cover the rough surface, as shown in Fig. 7(b). Nevertheless, further investigation regarding the relation between the roughness and the reflow property of the adhesive is required in order to optimize the bonding process with the roughening concept. In addition, the scheme is not practical for the bonding techniques, such as anodic bonding and fusion bonding, which are very sensitive to the roughness of contact surfaces [7], [8]. Rough surface can result in partial bonding, increase the number of leak paths to moisture, and cause a reliability problem of hermetic encapsulation using the aforementioned bonding techniques. With such bonding techniques, a nano-roughening scheme would not enhance bonding as the bonding area reduces.

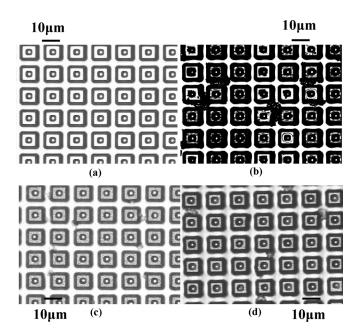

Previous experimental results have shown the nano-roughening can provide a better adhesive characteristic to the UV glue which could be applicable to the stamp-and-stick process, a common nano/microfabrication technique for various applications, such as microfluidic device fabrication and nanoimprinting [9], [10]. By stamping a mold on a layer of soft material, like PR, adhesive, and solvent, then onto another substrate surface, a layer of soft material with the mold pattern can be transferred via the stamp-and-stick process. Fig. 11 shows the optical micrographs of patterned silicon substrate surfaces. Fig. 11(a) and (b) shows the silicon substrate surfaces without surface roughening treatment before and after stamping onto UV adhesive, respectively. Fig. 11(c) and (d) shows the silicon substrate surfaces with surface roughening treatment before and after stamping onto UV adhesive, respectively. The darken region represents the surface covered with the adhesive after stamping. The contrast indicates the non-uniform distribution of UV adhesive on the patterned microstructures. The comparison indicates that the silicon substrate with surface roughening treatment can be uniformly coated with a layer of UV adhesive in comparison with the one without having the roughening. The utilization of nano-roughening can further ensure

Fig. 11. Stamping test results: (a) and (b) show the silicon bonding surface without nano-roughening before and after stamping to UV curable adhesive, respectively; (c) and (d) show the silicon surface with nano-roughening before and after stamping to UV curable adhesive, respectively.

the success of the stamp-and-stick process for nano/microfabrication. In addition, for most of MEMS hermetic encapsulation approaches using adhesive bonding scheme, the adhesive is usually put on the cap substrate instead of the device one to effectively avoid any possible process compatibility and manufacture yield issues. The cap substrate coated with adhesive is then bonded with the device substrate to form hermetic seal. Therefore, the stamp-and-stick testing result can further strengthen the concept implementation of nano-roughening to the NEMS packaging fabrication using adhesive bonding due to the reliability enhancement of adhesive bond resulted by the better contact characteristic between the adhesive on the glass cap to the silicon substrate with surface nano-roughening.

## IV. CONCLUSION

This paper reveals the importance of employing non-roughening for reliable hermetic encapsulation of N/MEMS manufacture. The surface roughening is realized via a nonuniform etch characteristic of PR which is etched then utilized as an etching mask for the following silicon etching process. The roughening can not only enhance adhesive bonding strength and hermetic encapsulation yield for N/MEMS manufacture, but also provide better sticky characteristic possible for nanoimprinting applications.

#### REFERENCES

- [1] Y. C. Lee, B. A. Parviz, J. A. Chiou, and S. Chen, "Packaging for microelectromechanical and nanoelectromechanical systems," *IEEE Trans. Adv. Pack.ag*, vol. 26, no. 3, pp. 217–226, Aug. 2003.

- [2] Z.-H. Liang, Y. T. Cheng, W. Hsu, and Y.-W. Lee, "A wafer-level hermetic encapsulation for MEMS manufacture application," *IEEE Trans. Adv. Packag.*, vol. 29, no. 3, pp. 513–519, Aug. 2006.

- [3] F. Sarvar, D. A. Hutt, and D. C. Whalley, "Application of adhesives in MEMS and MOEMS assembly: A review," in *Proc. Polymers 2nd Int. IEEE Conf. Adhesives Microelectron. Photonics (POLYTRONIC)*, 2002, pp. 22–28.

- [4] J. Oberhammer, F. Niklaus, and G. Stemme, "Selective wafer-level adhesive bonding with benzocyclobutene for fabrication of cavities," *Sens. Actuators A, Phys.*, vol. 105, pp. 297–304, 2003.

- [5] S. Y. Luo and Z. W. Wang, "Studies of chipping mechanisms for dicing silicon wafers," *Int. J. Adv. Manuf. Technol.*, vol. 35, pp. 1206–1218, 2008

- [6] C. C. Lee and W. S. Hsu, "Method on surface roughness modification to alleviate stiction of microstructures," *J. Vacuum Sci. Technol. B*, pp. 1505–1510, 2003.

- [7] Y. T. Cheng, L. Lin, and K. Najafi, "Localized silicon fusion and eutectic bonding for MEMS fabrication and packaging," *IEEE/ASME J. Microelectromechan. Syst.*, vol. 9, pp. 3–8, Mar. 2000.

- [8] C. Harendt, W. Appel, H. –G. Graf, B. Hofflinger, and E. Penteker, "Wafer fusion bonding and its application to silicon-on-Insulator fabrication," *J. Micromech. Microeng.*, vol. 1, pp. 145–151, 1991.

- [9] S. Satyanarayana, R. N. Karnik, and A. Majumdar, "Stamp-and-Stick room-temperature bonding technique for microdevices," *IEEE/ASME J. Microelectromechan. Syst.*, pp. 392–399, 2005.

- [10] J. -H. Jeong, Y. -S. Sim, H. Sohn, and E. -S. Lee, "UV nanoimprint lithograph using an elementwise embossed stamp," in *IEEE ICMEMS* '04, 2004, pp. 233–236.

Chia-Yeh Yang received the B.S. and M.S. degrees in mechanical engineering from National Chiao-Tung University, Hsinchu, Taiwan, in 2003 and 2005, respectively. His thesis work is about the development of hermetic nanopackaging technology.

Currently, he works for ASML about lithography technology development in The Netherlands.

Yu-Ting Cheng (SM'07) was born in Taiwan. He received the B.S. and M.S. degrees in materials science and engineering from National Tsing Hua University, Hsinchu, Taiwan, in 1991 and 1993, respectively. After his two-year army service in Taiwan, he went for Carnegie Mellon University, Pittsburgh, PA, and received the second M.S. degree in the same field in 1996. He received the Ph.D. degree in electrical engineering from the University of Michigan, Ann Arbor, in 2000. His Ph.D. dissertation is the development of novel vacuum packaging

technique for MEMS applications.

After his graduation, he worked for IBM Thomas J. Watson Research Center, Yorktown Heights, NY, as a research staff member and was involved in several system on package projects. In 2002, he came back to Taiwan as an Assistant Professor at the Department of Electronics Engineering in National Chiao Tung University. Since 2005, he has been promoted to be an Associate Professor. His research interests include the fundamental study of materials for microsystem integration and N/MEMS applications, SoP, and the design and fabrication of microsensors and microactuators.

Dr. Cheng is a member of the Institute of Physics and Phi Tau Phi.

**Wen-Syang Hsu** received the M.S. and Ph.D. degrees in mechanical engineering from the University of California, Berkeley, in 1990 and 1992, respectively.

He is the Professor in Mechanical Engineering Department of National Chiao Tung University, Hsinchu, Taiwan. His current interests include micro/nano fabrication technologies, design and fabrication of micro-transducers.