## 國立交通大學

## 工業工程與管理學系碩士班

## 碩士論文

球格陣列封裝製程之

主生產排程系統設計

The Design of Master Production Scheduling System for Ball Grid Array Packaging Process

研究生: 黃羑群

指導教授: 鍾淑馨 博士

中華民國九十三年七月

## 球格陣列封裝製程之主生產排程系統設計 The Design of Master Production Scheduling System for Ball Grid Array Packaging Process

研究生: 黃羑群

Student : Yu-Chun Huang

指導教授: 鍾淑馨 博士

Advisor : Dr. Shu-Hsing Chung

碩士論文

A SHILLER

A Thesis

Submitted to Department of Industrial Engineering and Management

College of Management National Chiao Tung University

ç .

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Engineering

July 2004

Hsinchu, Taiwan, Republic of China

中華民國九十三年七月

The Design of Master Production Scheduling System for Ball Grid Array Packaging Process

Student: Yu-Chun Huang

Advisor: Dr. Shu-Hsing Chung

Department of Industrial Engineering and Management National Chiao Tung University

### Abstract

Ball Grid Array (BGA) factories are characterized by long machine setup time, dynamical arrival of orders, and re-entrance of products. These three properties make a BGA factory difficult to maximize its capacity utilization while having all orders meeting their due dates. Therefore, this thesis designs a master production scheduling (MPS) system which aims for having high due date achievement as well as doing customer order promising. In order to achieve these goals, obtaining accurate cycle time estimation and good setup schedule is critical. The MPS system firstly adopts block-based cycle time estimation algorithm (BBCT) to estimate the cycle time. Then a mixed integer programming (MIP) model is applied to optimize the setup schedule so that the optimal MPS is planed. When a new order arrives, a forward scheduling algorithm basing on the optimal MPS is used to determine whether the new order can be accepted or not. The experimental results showed that both the accuracy of cycle time estimation and the performance of setup schedules were promised. With estimated cycle times and setup schedules, the master production scheduling system can plan master production schedules which are capable to meet the due date requirement and can handle the task of customer order promising.

Keywords: Master Production Scheduling, Ball Grid Array Packaging, Setup Time, Mixed Integer Programming 球格陣列封裝製程之主生產排程系統設計 研究生:黃麦群 指導教授:鍾淑馨 博士

國立交通大學工業工程與管理學系碩士班

#### 摘要

球格陣列封裝廠具有機台整備時間長、訂單動態來到以及產品會再回 流等三大特性。這三大特性使得球格陣列封裝廠難以在考慮最大化產能利 用的情況下同時維持高訂單達交率。本論文的目的即在設計一主生產排程 系統,用以規劃主生產排程使其滿足高訂單達交率的需求,且能作為新訂 單允收評估的參考依據。為了達成此研究目標,準確的生產週期時間估算 與良好的機台整備排程具有決定性的影響力,因此本主生產排程系統首先 採用區段基礎式生產週期時間估算法來估算生產週期時間,接著再使用混 合整數規劃模型來排出最佳的機台整備排程,進而求得主生產排程。當新 訂單到臨時,透過前推排程法與既定之主生產排程即可決定該訂單的允收 與否。實驗結果顯示,不論在生產週期時間的準確度或是機台整備排程的 績效上,本論文提出的方法都具有相當良好之成效。故本主生產排程系統 所規劃之主生產排程能有高訂單達交率,亦能作為新訂單允收評估之依 據。

關鍵字:主生產排程、球格陣列封裝、整備時間、混合整數規劃

ii

### Acknowledgement

這份論文得以完成,我首先必須感謝鍾淑馨老師一路不辭辛勞的指 導。在我的感覺裡,鍾老師的細心、專注和對論文品質的要求是無人能出 其右的。印象中,每次將稿子交給老師批閱,回來時總是密密麻麻的修正 與建議,看了雖然心情難免鬱卒,但經過此般千錘百鍊,其進步幅度是不 可同日而語的。我很明白,老師對我的付出乃是讓我往下紮根,向上成長 的力量。

此外,我也相當感激上天給我和實驗室這群朋友聚在一起的機會。我 永遠都會記得南庄之旅、八煙溫泉、觀霧之旅、熱鬧的慶生會、一起拼報 告的夜晚、噹噹噹系統模擬、拋物線理論實做…還有許許多多讓人回味無 窮的趣事。謝謝家馨、亞妮、涵琦、繼遠、簡城、育燐、清泓、益參、毓 淳、俊穎和許許多多學弟妹們的陪伴。

最後,我要感謝家人的支持與鼓勵,你們一直都是我心靈上最重要也 不可取代的寄託。

論文寫作是龐雜、漫長且艱辛的,

్

但在老師的引導下,我找到了明燈;

在朋友的陪同下,我發現了歡笑;

在家人的支持下,我知道我永不孤單。

黃羑群 敬上

中華民國九十三年八月十七日

| Abst | tract     |            |                                                  | i   |

|------|-----------|------------|--------------------------------------------------|-----|

| Ack  | nowledge  | ement      |                                                  | iii |

| Con  | tents     |            |                                                  | iv  |

| List | of Figure | es         |                                                  | vi  |

| List | of Tables | 5          |                                                  | vii |

| List | of Algor  | ithms      |                                                  | ix  |

| List | of Symb   | ols        |                                                  | X   |

| 1.   | Introduc  | tion       |                                                  | 15  |

|      | 1.1       | Researc    | h Background and Motivation                      | 15  |

|      | 1.2       | Researc    | h Goals                                          | 16  |

|      | 1.3       | Researc    | h Domain and Hypothesis                          | 16  |

|      | 1.4       | Researc    | h Process                                        | 17  |

| 2.   | Literatu  | re Review  | 7                                                | 18  |

|      | 2.1       | BGA Pa     | ackaging Technology                              | 18  |

|      | 2.1       | .1 Wa      | afer Bumping Process                             | 21  |

| 3.   | The Des   | ign of the | MPS system                                       | 26  |

|      | 3.1       | Problem    | n Analysis                                       | 26  |

|      | 3.2       |            | ction to the Design of the MPS system            |     |

|      | 3.3       | Product    | ion Planning Design                              |     |

|      | 3.3       | .1 VI      | PL Allocation and Rough Cycle Time Approximation | 31  |

|      |           | 3.3.1.1    | Select Bottleneck Machine Group                  | 32  |

|      |           | 3.3.1.2    | Rough Cycle Time Approximation                   | 34  |

|      |           | 3.3.1.3    | Dedicated and Mixed VPLs Allocation              |     |

|      |           | 3.3.1.4    | Non-bottleneck Machines Allocation               |     |

|      | 3.3       | .2 Ma      | aster Production Schedule Generation             | 40  |

|      |           | 3.3.2.1    | Mixed VPLs Setup Scheduling                      | 41  |

|      |           | 3.3.2.2    | Generate Master Production Schedule              | 54  |

|      | 3.3       | .3 Ne      | w Order Acceptability Evaluation                 | 56  |

|      | 3.3       | .4 Da      | ily Production Scheduling                        | 58  |

| 4.   | Experim   | nental Res | ults                                             | 59  |

|      | 4.1       | System     | Environment                                      | 59  |

|      | 4.1       | .1 Pla     | anning Horizon                                   | 59  |

|      | 4.1       | .2 Ma      | achines                                          | 59  |

|      | 4.1       | .3 Pro     | oduct Families and Production Routes             | 60  |

|      | 4.2       | Case St    | udy                                              | 62  |

|      | 4.2       | .1 Pro     | oduction Line Allocation Module                  | 63  |

## Contents

|    | 4.          | 2.1.1 Stage    | e 1: VPL Allocation and Rough Cycle Time           |        |

|----|-------------|----------------|----------------------------------------------------|--------|

|    | Aj          | oproximation   | 1                                                  | 63     |

|    |             | 4.2.1.1.1      | Select Bottleneck Machine Group                    | 63     |

|    |             | 4.2.1.1.2      | Rough Cycle time Approximation                     | 68     |

|    |             | 4.1.1.1.1      | Dedicated and Mixed VPLs Allocation                | 77     |

|    |             | 4.1.1.1.2      | Non-bottleneck Machines Allocation                 | 78     |

|    | 4.2         | 2.1.1. Stag    | e 2: Can the Capacity Demand under Current Pro     | duct   |

|    | М           | ix be Fulfille | ed?                                                | 80     |

|    | 4.2.2       | Capacity       | Planning and MPS Generation Module                 | 81     |

|    | 4.2         | 2.2.1 Stage    | e 3: Master Production Scheduling                  | 81     |

|    |             | 4.2.2.1.1      | Mixed VPLs Setup Scheduling                        | 81     |

|    |             | 4.2.2.1.2      | Generate Master Production Schedule                | 92     |

|    | 4.2         | 2.2.2 Stage    | e 4: Can the Capacity Demand under Current Prod    | duct   |

|    | М           | ix be Fulfille | ed?                                                | 94     |

|    | 4.2.3       | Order Pro      | omising and Shop Floor Control Module              | 94     |

|    | 4.2         | 2.3.1 Stage    | e 5: New Order Acceptability Evaluation            | 95     |

|    | 4.2         | 2.3.2 Stage    | e 6: Daily Production Scheduling                   | 97     |

|    | 4.3 Pe      | rformance A    | analysis                                           | 98     |

|    | 4.3.1       | Experime       | nt 1: Testing on the Approximated Cycle Times      | 98     |

|    | 4.3.2       | Experime       | ent 2: Testing on the Performance of the Setup Scl | hedule |

|    |             |                | IIP Model                                          |        |

| 5. | Conclusion  | and Future V   | Vorks                                              | 113    |

|    |             |                |                                                    |        |

|    | 5.2 Fu      | ture Works.    |                                                    | 114    |

| 6. | References. |                |                                                    | 115    |

# **List of Figures**

| Figure 1-1 2003 foundry package forecast [3]15                                                      |

|-----------------------------------------------------------------------------------------------------|

|                                                                                                     |

| Figure 1-2 Research Process                                                                         |

| Figure 2-1 Solder bumped on chip [6]                                                                |

| Figure 2-2 Wire bonding on chip [6]                                                                 |

| Figure 2-3 Tape automated bonding on chip [6]19                                                     |

| Figure 2-4 Quad flat pack [4]19                                                                     |

| Figure 2-5 Plastic ping grid array [4]20                                                            |

| Figure 2-6 Ball grid array [4]20                                                                    |

| Figure 2-7 IC device and packaging trends [6]21                                                     |

| Figure 2-8 A conceptual wafer bumping process [10]22                                                |

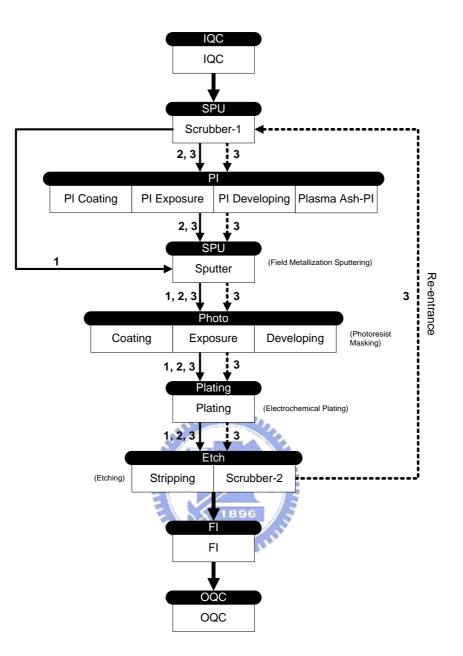

| Figure 2-9 Wafer bumping process flowchart                                                          |

| Figure 3-1 The hierarchy of production planning system27                                            |

| Figure 3-2 Flowchart of production planning procedure                                               |

| Figure 3-3 VPL allocation and rough cycle time approximation32                                      |

| Figure 3-4 Queue time cause by load and batch factors                                               |

| Figure 3-5 Non-bottleneck machines allocation                                                       |

| Figure 3-6 Master Production Schedule generation                                                    |

| Figure 3-7 An example of using concept of rolling schedule                                          |

| Figure 3-8 Total capacity that is allocated for a product family                                    |

| Figure 4-1 Product families and their routes                                                        |

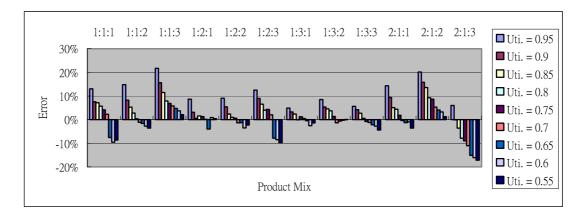

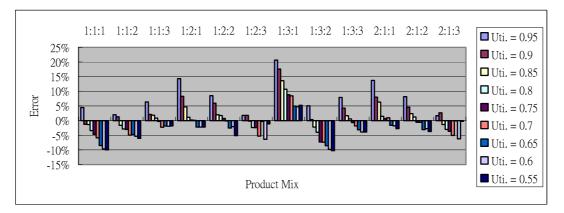

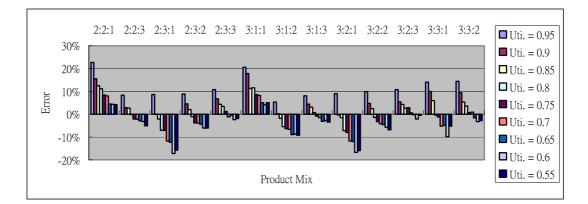

| Figure 4-2 Error of approximated cycle time of product family 1102                                  |

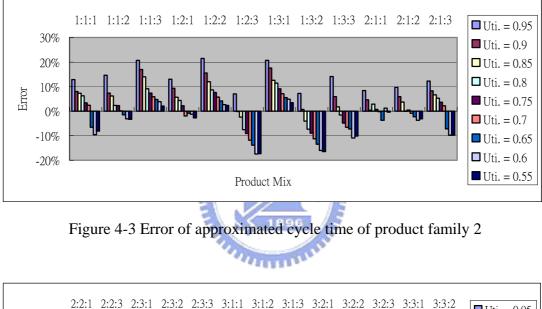

| Figure 4-3 Error of approximated cycle time of product family 2103                                  |

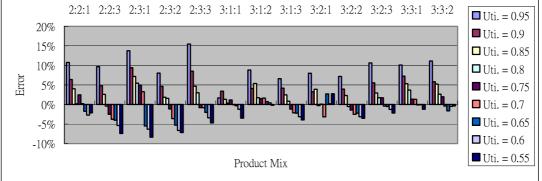

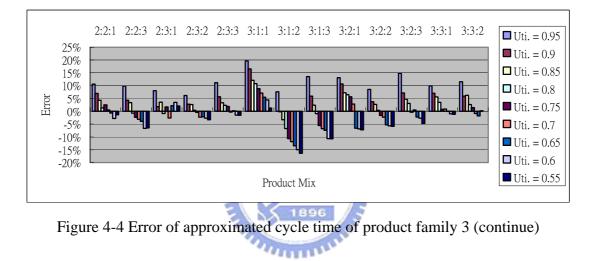

| Figure 4-4 Error of approximated cycle time of product family 3104                                  |

| Figure 4-5 Error of approximated cycle time of product family 4104                                  |

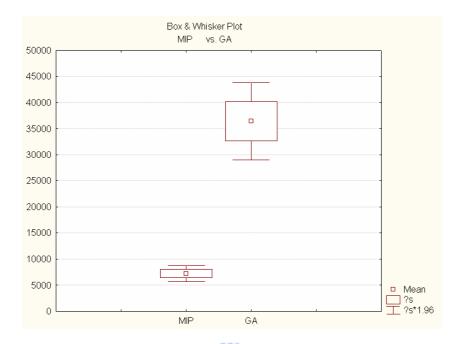

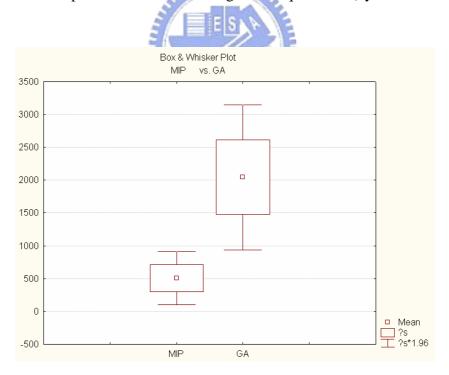

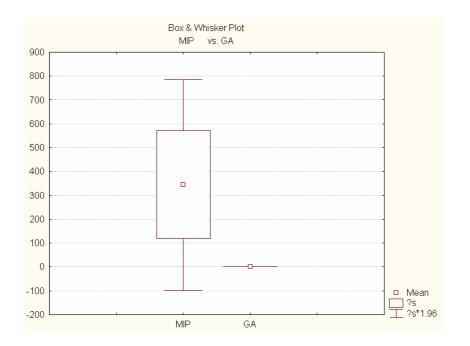

| Figure 4-6 Box plot of tardiness when tightness equals to 1 (by Statistica <sup>TM</sup> 6.0)111    |

| Figure 4-7 Box plot of tardiness when tightness equals to 0.85 (by Statistica <sup>TM</sup> 6.0)111 |

| Figure 4-8 Box plot of tardiness when tightness equals to 0.7 (by Statistica <sup>TM</sup> 6.0).112 |

| Figure 4-9 Box plot of tardiness when tightness equals to 0.55 (by Statistica <sup>TM</sup> $6.0$ ) |

|                                                                                                     |

## List of Tables

| Table 3-1 The possible combinations of the binary variables                    | 51     |

|--------------------------------------------------------------------------------|--------|

| Table 3-2 An example of searching for optimal setup schedule                   | 53     |

| Table 4-1 Machine information                                                  | 59     |

| Table 4-2 Number of visits of product families to machine groups               | 61     |

| Table 4-3 Order information                                                    | 62     |

| Table 4-4 Total capacity for all machine groups                                | 64     |

| Table 4-5 Total demand of product families during the planning horizon         | 65     |

| Table 4-6 Spare capacity of machine groups                                     | 65     |

| Table 4-7 The demand for product families on each machine group                | 66     |

| Table 4-8 Expected setup times for all machine groups                          | 67     |

| Table 4-9 Maximum setups for machine groups                                    | 68     |

| Table 4-10 The average number of dedicated machines                            | 69     |

| Table 4-11 Service rate of each machine group and product family               |        |

| Table 4-12 The arrival rates                                                   | 71     |

| Table 4-13 The utilizations                                                    | 72     |

| Table 4-14 The probability that there is no WIP in front of machine groups     |        |

| Table 4-15 The WIP levels                                                      |        |

| Table 4-16 The queue time caused by load factor                                | 75     |

| Table 4-17 Expected number of non-bottleneck machines                          | 79     |

| Table 4-18 The allocation of non-bottleneck machines                           | 79     |

| Table 4-19 Shifted due date of orders                                          | 81     |

| Table 4-20 Latest start time                                                   | 83     |

| Table 4-21 Sorted list according to latest start time                          | 84     |

| Table 4-22 Calculate the capacity that can not be fulfilled by dedicated VPLs  | 85     |

| Table 4-23 Assigning due date period                                           | 86     |

| Table 4-24 Variable values under the optimal solution                          | 88     |

| Table 4-25 Example of setting optimal sequence                                 | 91     |

| Table 4-26 Setup schedule                                                      | 91     |

| Table 4-27 Allocated capacity of mixed VPLs                                    | 92     |

| Table 4-28 allocated capacity for product families of each day                 | 93     |

| Table 4-29 Master production schedule                                          | 93     |

| Table 4-30 MPS of product family 1 with the new order that has a specified due | date   |

|                                                                                | 96     |

| Table 4-31 The latest start time of product family 1                           | 96     |

| Table 4-32 MPS of product family 1 with the new order that has no specified du | e date |

|                                                                                | 97     |

| Table 4-33 Error of approximated cycle time of product family 1                | 99         |

|--------------------------------------------------------------------------------|------------|

| Table 4-34 Error of approximated cycle time of product family 2                | 99         |

| Table 4-35 Error of approximated cycle time of product family 3                | 100        |

| Table 4-36 Error of approximated cycle time of product family 4                | 101        |

| Table 4-37 The settings of GA                                                  | 106        |

| Table 4-38 Tardiness when tightness equals to 1                                | 106        |

| Table 4-39 Tardiness when tightness equals to 0.85                             | 107        |

| Table 4-40 Tardiness when tightness equals to 0.7                              | 108        |

| Table 4-41 Tardiness when tightness equals to 0.55                             | 109        |

| Table 4-42 t-test for dependent samples on tardiness under MIP / GA generation | ated setup |

| schedules                                                                      | 110        |

# List of Algorithms

| Algorithm 3-1 Select bottleneck machine group     | 32 |

|---------------------------------------------------|----|

| Algorithm 3-2 Rough cycle time approximation      | 35 |

| Algorithm 3-3 Dedicated and mixed VPLs allocation | 38 |

| Algorithm 3-4 Non-bottleneck machines allocation  | 39 |

| Algorithm 3-5 Mixed VPLs setup scheduling         | 41 |

| Algorithm 3-6 Generate master production schedule | 55 |

| Algorithm 3-7 New order acceptability evaluation  | 56 |

| Algorithm 3-8 Daily production scheduling         | 58 |

|                                                   |    |

### **List of Symbols**

#### 1. Suffix Symbols

- *BM* : The batch type machine of the factory;

- *BMG*: The bottleneck machine group during the planning horizon;

- d: Serial number for days, d = 1, 2, ..., D;

- f: Serial number for product families, f = 1, 2, ..., F;

- g: Serial number for machine groups, g = 1, 2, ..., G;

- *j*: Serial number for orders, j = 1, 2, ..., J;

- *l*: Serial number for mixed VPLs, l = 1, 2, ..., L;

- *m*: Serial number for machines that are in the same machine group g, m = 1, 2, ..., M;

#### 2. Other Symbols

| $ANDM_{g,f}$ :  | The average number of dedicated machines for each product family               |

|-----------------|--------------------------------------------------------------------------------|

|                 | of each machine group during the planning horizon;                             |

| $AR_{g,f}$ :    | The lot arrival rate of each machine group $g$ for product family $f$          |

|                 | during the planning horizon;                                                   |

| $B_g$ :         | The batch size of machine group $g$ ;                                          |

| <i>BM</i> :     | Positive infinity;                                                             |

| BValue :        | A positive real number used to limit the difference of the allocated capacity; |

| $CMach_g$ :     | Total capacity of a machine in machine group $g$ during a day;                 |

| $CMPS_{f,d}$ :  | The capacity allocated for product family $f$ during day $d$ according         |

|                 | to the master production schedule;                                             |

| $CMPSM_{f,d}$ : | The capacity provided by mixed VPLs for product family $f$ during              |

|                 | day <i>d</i> according to the setup schedule;                                  |

| $CONWIP_f$ :    | Constant WIP level for product family <i>f</i> ;                               |

| $CSpare_{g}$ :  | Spare capacity of machine group $g$ during the planning horizon;               |

| $CT_{f}$ :         | Estimated cycle time of product family <i>f</i> ;                                                                |  |

|--------------------|------------------------------------------------------------------------------------------------------------------|--|

| $CTotal_{g}$ :     | Total capacity of machine group $g$ during the planning horizon;                                                 |  |

| $DDO_{j,f}$ :      | Due date of product family <i>f</i> of order <i>j</i> ;                                                          |  |

| $DDP_{ddsn}$ :     | The <i>ddsn</i> <sup>th</sup> due date period;                                                                   |  |

| ddsn:              | Due date period serial number;                                                                                   |  |

| $DOF_{ddsn,l,j}$ : | A binary variable. 0 denotes that the production of product family $f$                                           |  |

|                    | can not be joined with the production of the same product family during $DDP_{ddsn+1}$ to reduce setup.          |  |

| $DOQ_{j,f}$ :      | Demand of product family $f$ of order $j$ in quantity;                                                           |  |

| $DPP_{g,f}$ :      | Total demand of product family $f$ for machine group $g$ in                                                      |  |

|                    | percentage during the planning horizon;                                                                          |  |

| $DPQ_f$ :          | Total demand of product family $f$ in quantity during the planning                                               |  |

|                    | horizon;                                                                                                         |  |

| $DSCM_{j,f}$ :     | Shifted capacity demand of product family f of order j;                                                          |  |

| $DSCMD_{ddsn,f}$ : | Demand of product family $f$ of order $j$ that is during $DDP_{ddsn}$ ;                                          |  |

| $ISG_{ddsn,l,f}$ : | A binary variable. 0 denotes that the production of product family $f$                                           |  |

|                    | during $DDP_{ddsn}$ is impossible to join with the production of sameproductfamilyduring $DDP_{ddsn-1}$ .Thatis, |  |

|                    | $SUPP_{ddsn-1,l,f} \times SUPP_{ddsn,l,f} = 0;$                                                                  |  |

| $ISN_{ddsn,l,f}$ : | A binary variable. 0 denotes $NOPF_{ddsn,l,f} = 0$ . 1 denotes                                                   |  |

|                    | $NOPF_{ddsn,l,f} > 0;$                                                                                           |  |

| $ISP_{ddsn,l,f}$ : | A binary variable. 1 denotes $SUPP_{ddsn,l,f} > 0$ , 0 denotes                                                   |  |

|                    | $SUPP_{ddsn,l,f} = 0;$                                                                                           |  |

| $LQ_{g,f}$ :        | The WIP level of machine group $g$ for product family $f$ ;                                       |

|---------------------|---------------------------------------------------------------------------------------------------|

| $LST_{j,f}$ :       | Latest start time of product family $f$ of order $j$ ;                                            |

| $MINS_{ddsn,l}$ :   | Minimum number of setups of mixed VPL $l$ during $DDP_{ddsn}$ ;                                   |

| MWH:                | Maximum work hour during a day;                                                                   |

| $NAMS_g$ :          | Allowable maximum setups for machine group $g$ during the                                         |

| NBMV :              | planning horizon;<br>Total number of bottleneck machines which is allocated for mixed<br>VPLs;    |

| $NDBM_{f}$ :        | Number of bottleneck machines allocated for product family $f$                                    |

| NDDSN :             | during the planning horizon for a dedicated VPL;<br>The maximum number of due date serial number; |

| $NNM_{g,f}$ :       | Expected number of non-bottleneck machines in machine group $g$                                   |

|                     | that are allocated for product family $f$ during the planning horizon;                            |

| $NM_{g}$ :          | Number of machines in machine group $g$ ;                                                         |

| $NOPF_{ddsn,l,f}$ : | The number of other product families that have $SUPP_{ddsn,l,f} > 0$                              |

|                     | on mixed VPL <i>l</i> during $DDP_{ddsn}$ except the product family <i>f</i> itself;              |

| $NP_{g,f}$ :        | The times that product family $f$ passes machine group $g$ to finish                              |

|                     | the process;                                                                                      |

| $NSpare_{g,m}$ :    | Normalized spare capacity of machine $m$ in machine group $g$ .                                   |

| $NSS_{ddsn,l}$ :    | Number of saved setups from the start to <i>SDDO</i> <sub>ddsn</sub> ;                            |

| $NTM_g$ :           | Total number of machines in machine group $g$ ;                                                   |

| $P_{g,f}$ :         | Processing time on machine $m$ in machine group $g$ for product                                   |

|                     | family <i>f</i> ;                                                                                 |

| $PO_{g,f}$ :        | The planned output within the capacity limit of $ANDM_{g,f}$                                      |

machines;

| The probability that there is no WIP of product family $f$ before   |

|---------------------------------------------------------------------|

| machine group g;                                                    |

| The total queue time of each product family <i>f</i> ;              |

| The mean queue time of each product family $f$ before the batch     |

| machine group $g$ (namely, the Platers) caused by batch factor;     |

| The queue time of the product family $f$ before machine group $g$   |

| caused by load factors;                                             |

| The mean queue time of each product family $f$ caused by the peak   |

| load due to the batch process;                                      |

| Super small positive real number;                                   |

| Setup time of machines in machine group $g$ when switching setup    |

| from product family $f$ to $f'$ ;                                   |

| Shifted due date of product family <i>f</i> of order <i>j</i> ;     |

| Shifted due date of order with due date serial number <i>ddsn</i> ; |

| Expected setup time for machine group $g$ during the planning       |

| horizon;                                                            |

| The service rate of each machine group $g$ for product family $f$   |

| during the planning horizon;                                        |

| The capacity supply of mixed VPL $l$ for product family $f$         |

| during $DDP_{ddsn}$ ;                                               |

| The total processing time of each product family $f$ ;              |

| The utilization of each machine group $g$ for product family $f$ ;  |

| A set which contains all the machine groups that product family $f$ |

| should go through to complete its processes.                        |

|                                                                     |

$\tau_{g,m}$ : The set of product families that are assigned to machine *m* in the machine group *g* during the planning horizon, where  $g \notin BMG$ ;

### 1. Introduction

#### **1.1 Research Background and Motivation**

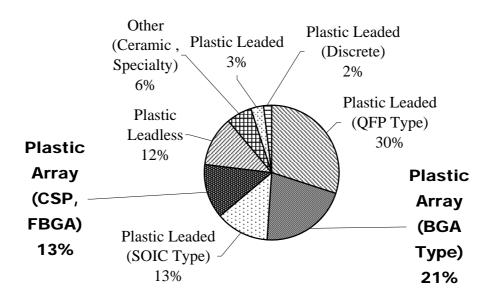

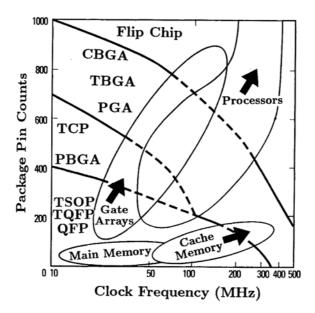

The need for small size, low cost and high performance is always the driving force of the electronic industry, and IC packaging is the key to achieve the goal for IC products. Among various packaging technologies, Ball Grid Array (BGA) packaging technology shows its superiority over others. For example, BGA packaging technology can support for higher package pin count and higher IC device clock frequency (high clock frequency usually means high speed). Figure 1-1 is the 2003 foundry package forecast; it shows that BGA packaging has became an important part of packaging factories. Consequently, packaging factories pay more and more attention to the BGA packaging manufacturing system.

Figure 1-1 2003 foundry package forecast [3]

For a BGA packaging factory, there are three typical properties that make it difficult to highly utilize the manufacturing system:

1. Customer orders come dynamically and can not be processed until wafers arrive. Packaging industry is characterized by its high customization because the specifications of ICs are different from customer to customer. It is not practical or even impossible to adapt make-to-stock production policy.

- 2. BGA packaging factories suffer from high machine setup time. Some machines take about 3 to 4 hours to setup for processing different product families. This property implies that the bottleneck machines can not setup too frequently or the capacity would be soon used up.

- 3. Products enter the same process for more than once (i.e., re-entrance). This property is similar to semiconductor foundries. Re-entrance often makes the system performance worse.

According to the discussion above, those three properties lead to the following results:

- 1. A BGA factory is almost totally make-to-order, and

- 2. Master production schedules should be finely tuned in order to minimize the time spent on setups.

Unfortunately, although there are many researches about packaging factories have been done, there are few researches that focus on BGA process. Most literatures discussed about traditional IC packaging technologies instead of BGA packaging technology [1][8][14][15]. Therefore this research is proposed to improve the efficiency of the production planning of a BGA factory.

#### **1.2 Research Goals**

1896 This research is aimed to make master production schedules (MPS) for a BGA factory. The MPS of this research is supposed to have high due date achievement as well as doing customer order promising.

#### **1.3 Research Domain and Hypothesis**

In order to simplify the problem, this research only focuses on the wafer bumping process (a critical "process section" of BGA packaging technology), and is built under an environment with the four hypotheses:

- 1. The factory adapts make-to-order production policy completely.

- 2. There is no raw material shortage.

- 3. Forecast orders, quoted capacity and confirmed orders are known, including their quantity, due dates and product mix.

- 4. Transportation time can be omitted.

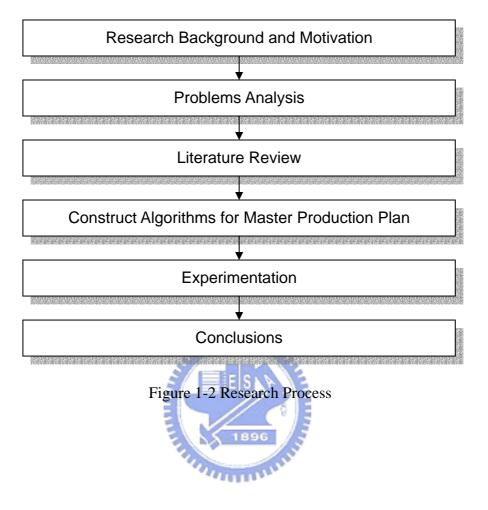

### **1.4 Research Process**

Figure 1-2 is the flowchart of this research.

### 2. Literature Review

As stated in section 1.2, this research is aimed to make master production schedules. Therefore, some related literatures are discussed in this chapter. Section 2.1 talks about the BGA packaging technology and its most critical process, wafer bumping process.

#### 2.1 BGA Packaging Technology

Packaging industry is always an indispensable part of electronic industry, and the packaging technology affect the performance of IC devices seriously [6][11]. Besides, IC packages are forced to be made smaller than before. Many devices nowadays need to integrate many ICs within limited space, for example, a mobile phone or a LCD monitor. For this reason, researchers continue developing new packaging technologies to minimize package size and package delay (the decrease in performance caused by packaging technologies) at the same time.

According to Dan Tracy [3], the packaging technology trend can be concluded as follows:

- 1. Proliferation of packaging type is moving from peripheral lead to area array, and shift from leaded to leadless.

- 2. Adopting 3-D or stacked packages.

- 3. Using wafer level packaging.

Following the trend stated above, BGA (Ball Grid Array) packaging technology is surely a winning solution for it can be applied on wafer level packaging, stacked packages, and leadless area array packages. Lau [6] lists a lot of popular packaging technologies, for instance, solder bumping (one of the BGA packaging technology, see Figure 2-1), wire bonding (see Figure 2-2), Tape Automated Bonding (see Figure 2-3), Quad Flat Pack (see Figure 2-4), Plastic Pin Grid Array (see Figure 2-5), and Ball Grid Array (see Figure 2-6). Among those packaging, BGA shows it superiority over others for three properties [4]:

- 1. Self alignment.

- 2. Small package area with high package pin count (pins/cm2).

- 3. Excellent electrical characteristics.

Figure 2-1 Solder bumped on chip [6]

Figure 2-3 Tape automated bonding on chip [6]

Figure 2-4 Quad flat pack [4]

Figure 2-5 Plastic ping grid array [4]

Figure 2-6 Ball grid array [4]

Moreover, Figure 2-7 shows that the high-speed devices (the arrows represent the trends) of the next generation require better packaging technology to support their high pin count or high clock frequency. Among the packaging technologies listed in Figure 2-7, BGA packaging technologies (CBGA, TBGA, and Flip Chip) undoubtedly best meet the requirements. Consequently BGA technology has become an important part of packaging factory.

Figure 2-7 IC device and packaging trends [6]

#### 2.1.1 Wafer Bumping Process

Although BGA packaging process has many steps, the most important and complicated part is the wafer bumping process. Therefore, for the reason of simplicity, this research only focuses on the wafer bumping process.

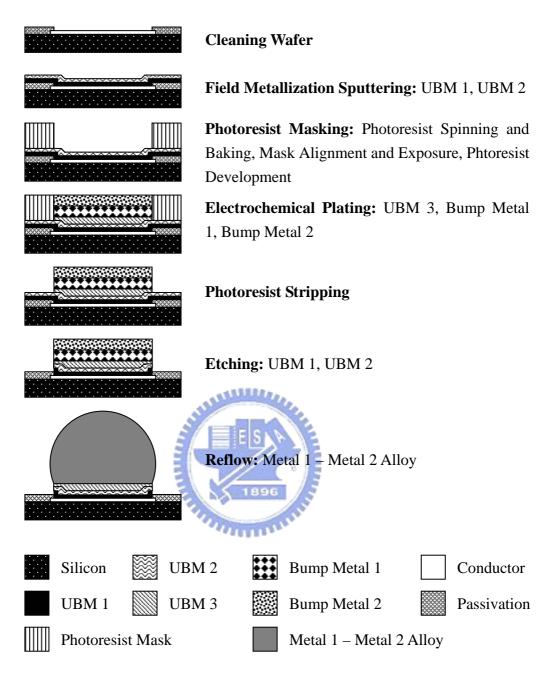

The goal of wafer bumping process is to "grow" metal bumps (could be solder ball, gold bump, etc.) on the bare wafer, and those bumps are then used as IC I/O pins. The bumping process starts with cleaning the wafer. Then Under Bump Metallization (UBM) is applied on the wafer. After UBM is done, use masking step to define the place for bumps to grow. Finally, remove photoresist and unnecessary UBM [7]. Figure 2-8 shows the conceptual bumping process, and the description of each step is briefly described below.

Figure 2-8 A conceptual wafer bumping process [10]

- 1. Cleaning wafer: When the wafer is sent to packaging factory, it is cleaned first in order to remove contaminants that may cause defect on the product.

- 2. Field metallization sputtering: This step grows two thin metal layers (Under Bump Metallization 1 (UBM 1) and Under Bump Metallization 2 (UBM 2)) on the wafer as the conductor between solder ball (it is formed in later steps) and the I/O port on the wafer.

- 3. Photoresist masking: Photoresist masking first coats a thick layer of photoresist. Then through baking, mask alignment, exposure, and photoresist

development to carve small holes on the photoresist so that the locations for solder balls to grow are defined.

- 4. Electrochemical plating: This step plates three layers of metals. They are Under Bump Metallization 3 (UBM 3), bump metal 1, and bump metal 2. UBM 3 is the metal pad for the solder ball to place on. Bump metal 1 and bump metal 2 are metals that will be used to form solder balls in later steps.

- 5. Photoresist stripping: This step simply removes all the photoresist.

- 6. Etching: The goal of etching is to remove the places of UBM 1 and UBM 2 that are not covered by UBM3, bump metal 1 and bump metal 2 so that each bump is isolated from others.

- 7. Reflow: The wafer is heated, hence bump metal 1 and bump metal 2 are melted and the metal 1-metal 2 alloy is formed. Because of surface tension, solder "balls" are formed after the metal 1-metal 2 ally cools down. This completes the wafer bumping process.

For the wafer bumping process there are some issues related to the manufacturing system should be addressed:

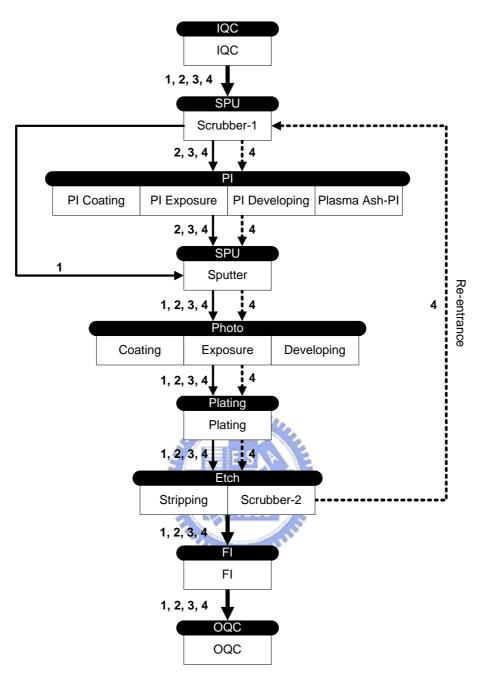

1. The routs of product families vary from one to another, and some of them have re-entrant routs. Figure 2-9 is the flowchart that shows some critical steps of wafer bumping process in the real world case. As it can be seen in Figure 2-9 (the descriptions in the parenthesis are the processes that map with Figure 2-8), there are several routs for different product families. The first one (indicated by number 1) does not have to go through the PI process (coat insulator on the wafer), and it does not have to pass the same machines for more than one time (i.e., no re-entrance), either. For the second one (indicated by number 2), it have to go through the PI process, but does not have to re-enter the same processes. The third one (indicated by number 3) has to go through the PI process, and it re-enters the same processes twice. This phenomenon makes the manufacturing system complex. If the master production schedule is not carefully tuned, the load balance of machines and the throughput of product families would be a big problem.

Figure 2-9 Wafer bumping process flowchart

- 2. Some machines have long setup times. The standard flow time of wafer bumping process ranges between 1.05 and 6.34 days. However, some processes, such as PI Coating, PI Exposure, PI Development, and Plasma Ash takes about 3 to 5 hours to setup for different product families. This is a great waste in capacity comparing to the standard flow time. Therefore frequent setup could soon use up the capacity and increase the cycle time dramatically.

- 3. Plating process has cup arrangement problem. The cup arrangement problem comes from that Platers (machines that are capable of running plating process) have different cup numbers. The cup number determines the batch size of the

Plater. Besides, the Plater can only process one product family each time. These properties lead to the problems that which Platers should setup for one specific product family so that the production flow is smooth (e.g., WIPs for a certain product family are not blocked seriously before Platers), and cycle time is reduced.

According to the discussion above, it is obvious that wafer bumping process has some critical problems that affect the manufacturing system seriously. Therefore how to make good master production schedules to boost the system performance is an important issue.

### 3. The Design of the MPS system

In this chapter, problem analysis is firstly discussed in Section 3.1. Section 3.2 then gives the introduction of the design of the MPS system. Finally, Section 3.3 shows the design of the MPS system.

#### **3.1 Problem Analysis**

This thesis focuses on the wafer bumping process of BGA packaging. According to the discussion in section 1.1 and section 2.1.1, the production characteristics of the wafer bumping process can be summarized as follows:

- 1. This is almost a totally make-to-order environment. Orders come dynamically, and the demands are customer-specific.

- 2. Wafer bumping process suffers from high machine setup time. Some process such as PI Coating, PI Exposure, PI Development, and Plasma Ash take about 3 to 5 hours to setup for different product families while the total flow time of wafer bumping process only ranges between 1.05 and 6.34 days. It is obvious that bad setup schedules will result in low machine utilization, low throughput, and long cycle time.

- 3. Some product families must go through the same processes twice. This property causes serious problem on machine load balance, and may result in low due date achievement.

In the rest of this chapter, a design of MPS system is proposed to cope with the second and third issues listed above so that a good MPS can be obtained. The MPS is supposed to have high due date achievement and do customer order promising.

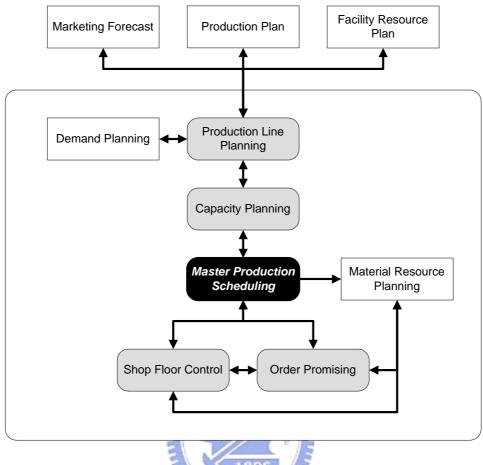

#### 3.2 Introduction to the Design of the MPS system

Figure 3-1 is the hierarchy of the production planning system. The modules in rectangles with white background colors are not discussed and are considered to be known all the time. On the contrary, the modules in gray and black rectangles are of interests. As stressed in Figure 3-1 (in black and gray background colors), this thesis mainly emphasizes on making master production schedules (black background color). However, to build a master production schedule, production line planning, capacity planning, shop floor control, and order promising are covered (gray background color). The general ideal of each modules are discussed below.

Figure 3-1 The hierarchy of production planning system

annun .

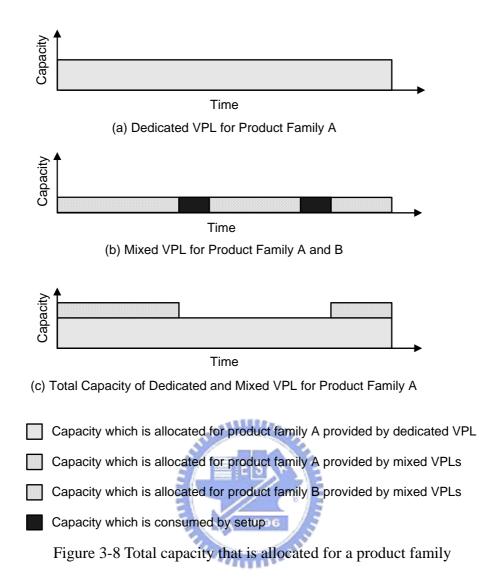

The production line planning is required in this MPS system because the key problem of wafer bumping process is its high setup time when switching from one product family to another. So the MPS system adopts the concept of Virtual Production Line (VPL) to do the production line planning and prevent the system from over setup. VPLs can be classified as dedicated VPLs and mixed VPLs. A dedicated VPL is a sequence of machines that is virtually organized as a flow production line, and is fully dedicated to a specific product family [8][12][15]. However, it is hard to divide up the machines among product families exactly according to the throughput target. Thus mixed VPLs are required to work on the jobs that can not be fulfilled by dedicated VPLs (A mixed VPL is a VPL that can produce several kinds of product families, and setups for different product families at demand). Although setup time can be dramatically reduced by dividing bottleneck machines into dedicated and mixed VPLs, there is still a problem. That is, mixed VPLs often suffer from low utilization due to frequent setup. Consequently, how to optimize the performance of mixed VPLs is a matter of concern, and this issue is solved in the MPS module.

After the VPLs are allocated, the capacity planning takes place to determine how many and which orders are assigned for a dedicated/mixed VPL as the input of the MPS module.

Under this research environment, the core of the MPS module is to reduce the setup frequency of mixed VPLs and to decide the production sequence of product families (it is called the setup schedule in this thesis) so as to minimize the time wasted on setup while the due dates of orders are still fulfilled. In order to accomplish the minimization task, when to setup and which product families share a mixed VPL should be taken into consideration at the same time. Therefore, a mixed integer programming (MIP) model is developed to solve this problem.

After the master production schedule is made, the acceptability of an incoming new order can be evaluated by the order promising module, and the dispatching of lots are handled by the shop floor control module. This completes the production planning.

In the following section, a complete and detailed production planning solution is presented.

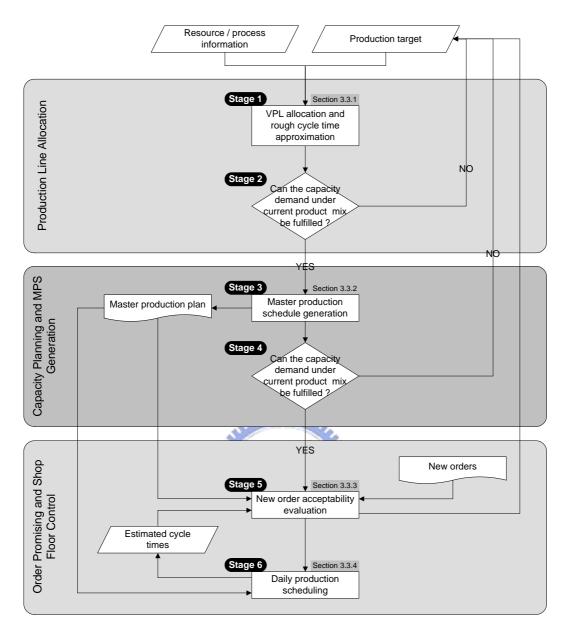

#### **3.3 Production Planning Design**

Figure 3-2 is the flowchart of production planning. It classifies the 5 modules mentioned in section 3.2 into 4 parts:

- 1. The inputs,

- 2. Production line allocation module,

- 3. Capacity planning and MPS generation module, and

- 4. Order promising and shop floor control module.

The concepts of the 4 parts are discussed in the following paragraphs.

Figure 3-2 Flowchart of production planning procedure

The production target and resource/process information shown in the Figure 3-2 are the inputs of this system, and they are supposed to be available and up to date all the time. The production target includes the due dates and quantity of each product family for confirmed orders, quoted orders, and forecast orders during the planning horizon. Resource/process information includes machine capability, machine setup times, and processing times for product families.

With the input data in hand, the MPS system starts with Virtual Production Line (VPL) allocation and rough cycle time estimation (see Section 3.3.1) In this stage, the approximated cycle time is calculated first so that the latest start times of orders can be obtained. According to the latest start times, the aggregate capacity demand of each

product family within the planning horizon can be computed by calculating the capacity demand for bottleneck resource. Then dedicated and mixed VPLs are determined according to the capacity demand of each product family.

Once the VPLs are decided, the manufacturing system is already simplified into dedicated VPLs and mixed VPLs. Because there is no setup on dedicated VPLs, the setup schedule of mixed VPLs is what should be emphasized on to elevate the system performance. Therefore, master production schedule generation (see Section 3.3.2) takes the capacity demand and mixed VPLs settings as the input for a mixed integer programming (MIP) model to determine the optimal setup time points and the production sequence of mixed VPLs so that the number of setups is minimized while the due date requirements are kept. After the optimal setup schedule is generated, the daily allocated capacity for each product family can be calculated simply. Till now, a "blank MPS" (a MPS that only has the information of allocated capacity but the order information) with optimal capacity allocation is obtained. Hence the next step of this procedure is to "fill out the blank" with orders according to their latest start time. By this way, the MPS is guaranteed to have high due date achievement.

When a new order is coming, new order acceptability evaluation (see Section 3.3.3) is required. New orders can be divided into two categories by whether their due dates are specified or not. If a new order has a specified due date, the new order and the confirmed orders are mixed and the production sequence is re-scheduled by forward scheduling technique to see if the new order can be completed in time. If a new order comes without a specified due date, a forward scheduling technique is also applied to calculate the earliest time that the new order can be completed without making confirmed orders late.

Finally this thesis presents a simple dispatching rule to schedule jobs so that the production flow is smooth and the load of machines is balanced. (see Section 3.3.4).

The following procedure lists all stages that are required to complete the production planning.

- Stage 1. Virtual Production Line (VPL) allocation and rough cycle time estimation. According to the production target, determine the bottleneck resource, and roughly approximate cycle time. Then decide how many bottleneck machines form a VPL for each product family, and which product families share a bottleneck machine (i.e. a mixed VPL).

- Stage 2. Check if the capacity demand for current product mix can be fulfilled or not. If yes, continue to Stage 3, else output the unfulfilled quantity as the feedback to adjust production target.

- Stage 3. Generate master production schedule. Use a MIP model to make setup

schedule and fill in orders to generate MPS.

- Stage 4. Check if the capacity demand under current product mix can be fulfilled. If yes, continue to Stage 5, else output the unfulfilled lots as the feedback to adjust production target.

- Stage 5. New order acceptability evaluation. When a new order arrives, use forward scheduling to check if the due date of the new order can be fulfilled or not according to the MPS generated in Stage 3 and the estimated cycle times. If yes, insert the new order into the confirmed order list, else reject the new order.

- Stage 6. Daily production scheduling. Use the master production schedule generated in Stage 3 to make daily production schedules. Stop this procedure.

In the following sections, all the building blocks, namely the VPL allocation and rough cycle time estimation, master production schedule generation, new order acceptability evaluation, and daily production scheduling, are discussed in detail.

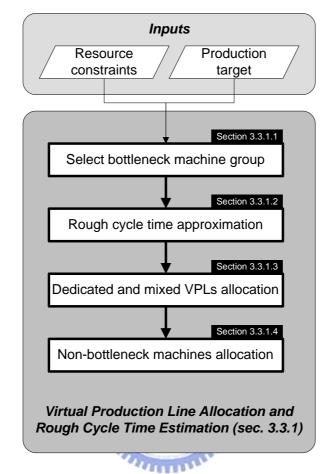

#### 3.3.1 VPL Allocation and Rough Cycle Time Approximation

Because the key problem of wafer bumping process is its high setup time when switching from one product family to another, the concept of Virtual Production Line (VPL) is adapted to prevent the system from frequent setup. VPLs can be classified as dedicated VPLs and mixed VPLs. A dedicated VPL is a sequence of machines that is virtually organized as a flow production line, and is fully dedicated to a specific product family [8][12][15]. Therefore a dedicated VPL will not setup for different product family so that the total setup time is decreased.

However, it is hard to divide up the machines among product families exactly according to the production target. Thus mixed VPLs are required to work on the jobs that can not be fulfilled by dedicated VPLs (A mixed VPL is a VPL that can produce several kinds of product families, and setups for different product families at demand).

Therefore this section lists five algorithms that are used to determine the allocation of dedicated VPLs, mixed VPLs, and non-bottleneck machines:

- 1. Select bottleneck machine group (Section 3.3.1.1).

- 2. Rough cycle time approximation (Section 3.3.1.2).

- 3. Dedicated and mixed VPLs allocation (Section 3.3.1.3).

- 4. Non-bottleneck machines allocation (Section 3.3.1.4).

Figure 3-3 shows the whole picture of VPL allocation and rough cycle time

approximation. Each algorithm is described in detail from section 3.3.1.1 through 3.3.1.4.

Figure 3-3 VPL allocation and rough cycle time approximation

#### 3.3.1.1 Select Bottleneck Machine Group

According to theory of constraints (Goldratt, 1988), the maximum performance of a system is defined by its weakest part [2][9][13]. Thus, finding out the system bottleneck is necessary to address the most important part of the manufacturing system. In the system of interest, setup time affects the system performance seriously, and the number of allowable setups is then taken as the index of selecting bottleneck. If a machine group can only afford the least number of setups, it would not be able to setup too many times or WIPs will build up quickly in front of it.

Hence the goal of this algorithm is to search for the machine group that can afford the least number of setups so that the system bottleneck is defined.

Algorithm 3-1 Select bottleneck machine group

Step 1. Calculate total capacity of machine group g during the planning horizon,

$CTotal_{g}$ .  $CTotal_{g}$  is the total available capacity of machine group g during the planning horizon with 5% capacity reserved as the protective capacity.

$$CTotal_{g} = CMach_{g} \times NM_{g} \times 95\% \times D \times B_{g}, \qquad (1)$$

for all machine group g.

**Step 2.** Calculate spare capacity of machine group g during the planning horizon,  $CSpare_{g}$ .

$$DPQ_f = \sum_j DOQ_{j,f} \tag{2}$$

$$CSpare_{g} = CTotal_{g} - \sum_{f} \left( P_{g,f} \times DPQ_{f} \times NP_{g,f} \right),$$

(3)

for each machine group g.

**Step 3.** Calculate expected setup time,  $SExp_g$ .  $SExp_g$  is the expected time spent on each setup for machine group g during the planning horizon.

$$DPP_{g,f} = \frac{DPQ_f \times NP_{g,f}}{\sum_{f} (DPQ_f \times NP_{g,f})}$$

(4)

$$SExp_g = \sum_{f} \left( DPP_{g,f} \times \frac{\sum_{f' \notin f} (DPP_{g,f'} \times S_{g,f,f'})}{\sum_{\delta \notin f} DPP_{g,\delta}} \right),$$

(5)

for each machine group g.

Equation (5) adopts the concept of conditional probability to compute the expected setup time.  $\frac{DPP_{g,f'}}{\sum_{\delta \notin f} DPP_{g,\delta}}$  is the probability that product family *f*'

appears when the other product family f definitely not appears. Hence

$$DPP_{g,f} \times \frac{\sum_{f' \notin f} (DPP_{g,f'} \times S_{g,f,f'})}{\sum_{\delta \notin f} DPP_{g,\delta}}$$

is the expected setup time.

**Step 4.** Calculate allowable maximum setups for machine group g during the planning horizon,  $NAMS_g$ .

$$NAMS_{g} = CSpare_{g} / SExp_{g} , \qquad (6)$$

for each machine group g whose  $SExp_g > 0$ .

**Step 5.** Sort  $NAMS_g$  in ascending order, and set the machine group which belongs the first one of the sorting list to be the bottleneck, BMG. **Stop** this algorithm.

#### 3.3.1.2 Rough Cycle Time Approximation

For approximating cycle times, the concept of block-based cycle time estimation algorithm (BBCT) [5] is adopted. BBCT classifies the factors that cause queue times before each machine as load factors and batch factors. The queue time caused by load factors is due to the demand of incoming lots, and can be estimated through queuing model. On the contrary, the queue time caused by batch factors is due to the need for accumulating lots until the quantity in front of the batch machine is larger than the minimum batch size, or due to the peak load caused by batch release.

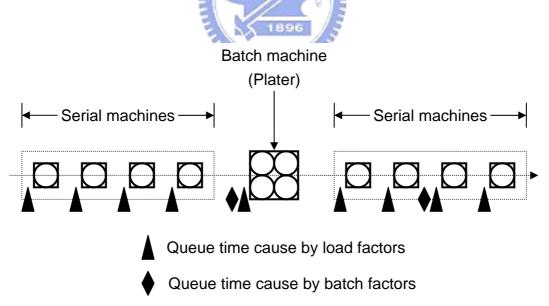

For wafer bumping process, the system can be generalized as Figure 3-4. As Figure 3-4 shows, the total queue time in front of each machine can be calculated by adding the load related (denoted by solid triangles) and batch related (denoted by solid rhombuses) queue times.

Figure 3-4 Queue time cause by load and batch factors

In the following algorithm, M/M/c queuing model<sup>\*</sup> is adopted to approximately estimate the load related queue time. Then, the batch related queue time is calculated by estimating the mean time for waiting  $B_g$  WIPs to arrive ( $B_g$  is the minimum batch size of machine group g), and the mean time for processing the peak load due to batch release. Finally, sum up queue times and the net flow time of processes to get the approximated cycle time.

## Algorithm 3-2 Rough cycle time approximation

Step 1. Calculate the average number of dedicated machines for each product family

of each machine group,  $ANDM_{g,f}$ .

$$ANDM_{g,f} = \left\lceil DPP_{g,f} \times NTM_{g} \right\rceil,\tag{7}$$

for each product family f and each machine group g which has to setup for different product families.

$$ANDM_{g,f} = NTM_g, \qquad (8)$$

for each product family f and each machine group g which does not have to setup for different product families.

**Step 2.** Calculate the service rate of each machine group g for product family f during the planning horizon,  $SR_{g,f}$ .

$$SR_{g,f} = \frac{B_g}{P_{g,f}} \times \frac{DPP_{g,f} \times NTM_g}{ANDM_{g,f}},$$

(9)

for each machine group g and product family f.

**Step 3.** Calculate the lot arrival rate of each machine group g for product family f during the planning horizon,  $AR_{g,f}$ . It can be obtained according to how many times a lot of product family f passes the machine group g.

<sup>&</sup>lt;sup>\*</sup> Note that, because this system has re-entrant processes, the arrival of lots in front of machines is complex, and can be treated as independent. Moreover, the processing times of the machines are not affected by the arrival sequence and the type of lots. Thus it is confident to say that the service time is independent.

$$AR_{g,f} = \frac{\sum_{f} \left( DPQ_f \times NP_{g,f} \right)}{24 \times D}, \tag{10}$$

for each machine group g which does not have to setup for different product families.

$$AR_{g,f} = \frac{DPQ_f \times NP_{g,f}}{24 \times D},\tag{11}$$

for each product family f and machine group  $g \notin \omega$  which has to setup for different product families.

Step 4. Calculate the utilization of each machine group g for product family f,

$$UTI_{g,f}$$

.

$$UTI_{g,f} = \frac{AR_{g,f}}{SR_{g,f} \times ANDM_{g,f}},$$

(12)

for each machine group g and product family f.

Step 5. Calculate the probability that there is no WIP of product family f before machine group g. PZ

$$PZ_{g,f} = \left\{ \begin{bmatrix} ANDM_{g,f}^{-1} \left( AR_{g,f}^{-1} SR_{g,f}^{-1} \right)^{T} \\ \sum_{r=0}^{r=0} r! \end{bmatrix}^{+} \\ \left[ \left( \frac{AR_{g,f}}{SR_{g,f}} \right)^{ANDM_{g,f}} \left( \frac{1}{ANDM_{g,f}!} \right)^{T} \\ \frac{1}{1 - \frac{AR_{g,f}}{ANDM_{g,f} \times SR_{g,f}}} \\ \end{bmatrix} \right]^{-1} , \quad (13)$$

for each machine group g and product family f.

**Step 6.** Calculate the WIP level of machine group g for product family f,  $\tau_{g,f}$ .

$$LQ_{g,f} = \frac{PZ_{g,f} \times \left(AR_{g,f} / SR_{g,f}\right)^{ANDM_{g,f}} \times UTI_{g,f}}{\left(ANDM_{g,f} ! \right) \left(1 - UTI_{g,f}\right)^{2}},$$

(14)

for each machine group g and product family f.

**Step 7.** Calculate the queue time of the product family *f* in front of machine group *g* caused by load factors,  $QTL_{g,f}$ .

$$QTL_{g,f} = \frac{LQ_{g,f}}{AR_{g,f}},\tag{15}$$

for each machine group g and product family f.

**Step 8.** Calculate the total processing time of each product family f,  $TPT_f$ .

$$TPT_f = \sum_{g \in \pi_f} P_{g,f} , \qquad (16)$$

where  $\pi_f$  is a set which contains all the machine groups that product family

f should go through to complete its processes.

**Step 9.** Calculate the mean queue time of each product family *f* before the batch machine (namely, the Platers) caused by batch factor,  $QTB_{g',f}$ .

$$QTB_{g,f} = \frac{\left(\frac{P_{g',f}}{ANDM_{g',f}}\right) + 2\left(\frac{P_{g',f}}{ANDM_{g',f}}\right) + \dots + \left(B_g - 1\right)\left(\frac{P_{g',f}}{ANDM_{g',f}}\right)}{B_g}, \quad (17)$$

$$= \frac{\left(B_g - 1\right) \times P_{g',f}}{2 \times ANDM_{g',f}}$$

for each product family *f*;

$g, QT_f$ .

where g is the batch machine group, and g' is the machine group with least spare capacity whose operation lies before g.

Step 10. Calculate the mean queue time of each product family f caused by the peak load due to the batch process,  $QTP_{g,f}$ .  $QTP_{g,f}$  is obtained by calculating the peak load related waiting time of WIPs in front of the critical serial machine group (the machine group whose  $UTI_{g,f}$  is the highest among the machine groups whose route is after the batch machine).

$$QTP_{g,f} = \left(\frac{B_{g'}}{ANDM_{g,f}} - 1\right) \times P_{g,f}, \text{ for each product family } f,$$

(18)

where g' is the batch machine group and g is the critical serial machine group whose route is after the batch machine group.

Step 11. Calculate the total queue time of each product family f before machine group

$$QT_{f} = \left(\sum_{g \notin \{g',g''\}} QTL_{g,f} \times NP_{g,f}\right) +$$

$$\max\left\{QTL_{g',f}, QTB_{g',f}\right\} \times NP_{g',f} + \max\left\{QTL_{g'',f}, QTP_{g'',f}\right\} \times NP_{g'',f}$$

(19)

for all product family *f*,

where g' is the batch machine group, and g'' is the critical machine group whose route is after the batch machine group.

**Step 12.** Calculate the approximated cycle time of product family f,  $CT_f$ .

$$CT_f = TPT_f + QT_f . ag{20}$$

## 3.3.1.3 Dedicated and Mixed VPLs Allocation

This algorithm uses the proportional perspective to allocate dedicated and mixed virtual production lines (VPLs) instead of allocating exact number of bottleneck machines according to the demand of each product family. The reason is that using the proportional perspective to allocate VPLs will assign more bottleneck machines for dedicated VPLs than actual need. This strategy will minimize the request for setup since dedicated VPLs do not setup at all. The following algorithm lists all the steps.

# Algorithm 3-3 Dedicated and mixed VPLs allocation

Step 1. Calculate the number of bottleneck machines which is allocated for dedicated VPLs,  $NDBM_f$ .

$$NDBM_{f} = \lfloor DPP_{BMG,f} \times NTM_{BMG} \rfloor$$

, for each product family f. (21)

Step 2. Calculate the number of bottleneck machines which is allocated for mixed VPLs.

$$NBMV = NTM_{BMG} - \sum_{f} NDBM_{f} , \qquad (22)$$

## 3.3.1.4 Non-bottleneck Machines Allocation

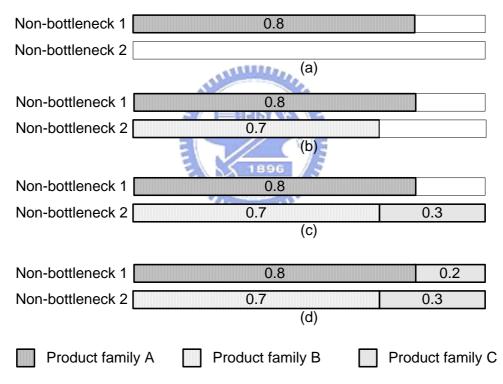

The non-bottleneck machines can be further divided into two categories: the ones that do not need setup, and the ones that requires setup when switching between different product families. The former does not need to be paid attention to because no matter how the product families changes, there is no waste on capacity. However, the later does need some strategy to avoid over setup although the problem is not as serious as bottleneck machines. Consequently, this algorithm follows the proportional perspective to allocate non-bottleneck machines but in a rough way. It first sorts the product families according to the proportion (i.e.,  $DPP_{s,f} \times NTM_{s,f}$ ) that should be

assigned to, and uses "the largest the first" rule to determine which product families share a non-bottleneck machine. For example, if there are three product families, say, product family A, B, and C, are going to be assigned to two non-bottleneck machines, and are expected to be assigned 0.8, 0.7, and 0.5 machines, respectively. Because product family A has the largest ratio, it is firstly assigned to the non-bottleneck machine 1 (see Figure 3-5 (a)). Then product family B is assigned to the non-bottleneck machine 2 because non-bottleneck machine 2 has the most capacity left (see Figure 3-5 (b)). However, when allocating product family C, there is not enough capacity left to fulfill the demand of product family C. Therefore 0.3 of product family C is assigned to the non-bottleneck machine 2 has the most capacity left. Then assign the rest 0.2 of product family C to the non-bottleneck machine 1 (see Figure 3-5 (d)). It completes the non-bottleneck machines allocation.

Figure 3-5 Non-bottleneck machines allocation

Algorithm 3-4 Non-bottleneck machines allocation

**Step 1.** Set the normalized spare capacity,  $NSpare_{g,m}$ , equal to 1 for all machine *m* in all machine group *g*.

Step 2. For each non-bottleneck machine group g that need to setup for different product families, do Step 3 through Step 8, else do nothing and start

allocating the next machine group. If all machine groups are assigned, **stop** this algorithm.

**Step 3.** Sort all product families according to  $NNM_{e,f}$  in descending order. Where

$NNM_{g,f}$  is given below.

$$NNM_{g,f} = DPP_{g,f} \times NTM_{g,f}, \text{ for each } f \text{ and } g.$$

(23)

- Step 4. Pick product families one by one according to the order obtained in Step 3, do Step 5 through Step 8 for each product family. If all product families are assigned, go back to Step 2 for the next machine group.

- **Step 5.** Search for the machine  $m^*$  in machine group g that has the most normalized spare capacity left.

- **Step 6.** If the normalized spare capacity of the machine  $m^*$  is larger or equal to  $NNM_{g,f}$ , go to **Step 7**, else go to **Step 8**.

- **Step 7.** Assign the capacity of machine  $m^*$  to the product family f, and substrate the capacity of the machine  $m^*$  by  $NNM_{g,f}$ . Put the product family f into  $\tau_{g,m^*}$ .  $\tau_{g,m^*}$  represents which product families are assigned for machine  $m^*$  in the

machine group g currently. Go back to Step 4 for the next product family.

**Step 8.** Assign all the spare capacity of the machine  $m^*$  to product family f, and set the normalized spare capacity of the machine  $m^*$  to 0. Put the product family f into  $\tau_{g,m^*}$ . Substrate  $NNM_{g,f}$  by the capacity assigned to it, and go to

**Step 5** to allocate the unassigned demand of product family *f*.  $\tau_{g,m^*}$  represents which product families are assigned for machine *m*\* in the machine group *g* currently.

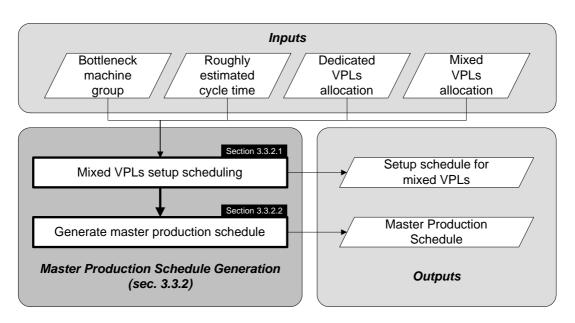

## 3.3.2 Master Production Schedule Generation

When making a master production schedule, it is important to consider the due dates of orders and the setup requirements at the same time to improve due date achievement and minimize total setup time. Hence a mixed integer programming (MIP) model is developed to derive the optimal setup schedules with the concern of due date and setup requirement. As Figure 3-6 shows, this module is completed by applying a MIP model on the mixed VPLs to derive the optimal setup schedule so that

the allocated capacity for each product family for each day is obtained to generate the MPS. Section 3.3.2.1, and 3.3.2.2 discuss them in detail.

Figure 3-6 Master Production Schedule generation

## 3.3.2.1 Mixed VPLs Setup Scheduling

This algorithm uses the due dates of orders and cycle time,  $CT_f$ , to derive the latest start time of product families of each order. Then basing on the latest start time, a forward scheduling procedure takes place to fill the unassigned capacity of dedicated VPLs and identifies how much work needs to be done on mixed VPLs. Finally, the setup schedule is generated by solving a mixed integer programming (MIP) model.

#### Algorithm 3-5 Mixed VPLs setup scheduling

**Step 1.** Shift the due date of the product families of orders earlier for  $CT_f$  according to the product family they belong to, so that the shifted due date of product family *f* of order *j*,  $SDDO_{i,f}$  is obtained.

$$SDDO_{j,f} = DDO_{j,f} - CT_f + \sum_{g \in \Theta} P_{g,f} , \qquad (24)$$

for each order j and product family f where  $\Theta$  is a set which contains the machine groups that products have to be processed on before the most utilized machine group.

Step 2. Calculate the latest start time of each product family of each order,  $LST_{j,f}$

$$LST_{j,f} = DDO_{j,f} - CT_f - \left(DOQ_{j,f} - 1\right) \times \left(\frac{P_{g,f}}{NTM_g \times DPP_{g,f}}\right) \times NP_{g,f}, \quad (25)$$

for each order *j* and product family *f*.

where g is the machine group such that  $UTI_{g,f}$  is the highest.

In this equation,  $\frac{P_{g,f}}{NTM_g \times DPP_{g,f}}$  is the average processing time of product

family f on the bottleneck machine group. Thus  $n \times \left(\frac{P_{g,f}}{NTM_g \times DPP_{g,f}}\right) \times NP_{g,f}$  denotes the time required to process all nlots of product family f of order j on the bottleneck machine. However when calculating  $LST_{j,f}$ ,  $\left(\frac{DOQ_{j,f}-1}{NTM_g \times DPP_{g,f}}\right) \times NP_{g,f}$  should be used instead of  $\frac{DOQ_{j,f} \times \left(\frac{P_{g,f}}{NTM_g \times DPP_{g,f}}\right) \times NP_{g,f}}{NTM_g \times DPP_{g,f}}$  Because  $DDO_{j,f} - CT_f$  already contains the processing time on the capacity

constrained machine.

**Step 3.** Sort  $LST_{j,f}$  in ascending order for each product family *f*.

- Step 4. According to the sorted list generated in Step 3, assign the capacity of the bottleneck machines of dedicated VPL to orders from the start of the planning horizon (note that the product family type of the order must be match the product family which the VPL dedicates for). If there is capacity of product family *f* of order *j* that can not be fulfilled by the dedicated VPL before  $SDDO_{j,f}$ , set the unfulfilled capacity as  $DSCM_{j,f}$  ( $DSCM_{j,f}$  is set to zero if there is no unfulfilled capacity).

- **Step 5.** List all job orders (*f* and *j*) with  $DSCM_{j,f} > 0$ . Then sort them in ascending

order according to their shifted due date,  $SDDO_{j,f}$  (note that if there are

two f and j pairs have the same shifted due date, assign the same due date serial number ddsn for them.). According to the sorted list, assign the numbering of ddsn, to each f and j pair from 1 on.

**Step 6.** Solve the MIP model below. The detailed description is placed after this algorithm. Here, only the formulas are listed.

Constants:

| NDDSN :             | The maximum number for sequencing due dates of all orders;                                                                                                                                        |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| F:                  | Total number of product families;                                                                                                                                                                 |  |  |  |  |  |  |

| NBMV:               | Total number of mixed VPLs;                                                                                                                                                                       |  |  |  |  |  |  |

| MWH:                | Maximum work hour during a day;                                                                                                                                                                   |  |  |  |  |  |  |

| $SExp_{BMG}$ :      | Expected setup time of bottleneck machine group BMG;                                                                                                                                              |  |  |  |  |  |  |

| $SDDOD_{ddsn}$ :    | Shifted due date for the order with due date serial number <i>ddsn</i> ;                                                                                                                          |  |  |  |  |  |  |

| $DSCMD_{ddsn,f}$ :  | Demand of product family $f$ of order $j$ that is during $DDP_{ddsn}$ ;                                                                                                                           |  |  |  |  |  |  |

| <i>BM</i> :         | Positive infinity;                                                                                                                                                                                |  |  |  |  |  |  |

| <i>ss</i> :         | Super small positive real number;                                                                                                                                                                 |  |  |  |  |  |  |

| BValue              | A positive real number used to limit the difference of the allocated capacity.                                                                                                                    |  |  |  |  |  |  |

| Variables:          | The Hust                                                                                                                                                                                          |  |  |  |  |  |  |

| $SUPP_{ddsn,l,f}$ : | The capacity supply of mixed VPL $l$ for product family $f$ during $DDP_{ddsn}$ ;                                                                                                                 |  |  |  |  |  |  |

| $ISP_{ddsn,l,f}$ :  | A binary variable. 1 denotes $SUPP_{ddsn,l,f} > 0$ , 0 denotes                                                                                                                                    |  |  |  |  |  |  |

|                     | $SUPP_{ddsn,l,f} = 0;$                                                                                                                                                                            |  |  |  |  |  |  |

| $MINS_{ddsn,l}$ :   | Minimum setups of mixed VPL $l$ during $DDP_{ddsn}$ ;                                                                                                                                             |  |  |  |  |  |  |

| $DOF_{ddsn,l,j}$ :  | A binary variable. 1 denotes the production of product family $f$ is not joined with the production of the same product family of the previous due date period, $DDP_{ddsn-1}$ , to reduce setup; |  |  |  |  |  |  |

| $ISG_{ddsn,l,f}$ :  | A binary variable. 0 denotes the production of product family $f$ of $DDP_{ddsn}$ is impossible to be used for reducing setup with the production of the same product family of                   |  |  |  |  |  |  |

$$DDP_{ddsn-1}$$

. That is,  $SUPP_{ddsn-1,l,f} \times SUPP_{ddsn,l,f} = 0$ ;

$NOPF_{ddsn,l,f}$ : The number of product families that  $SUPP_{ddsn,l,f} > 0$  on mixed VPL l during  $DDP_{ddsn}$  except the product family itself;

A binary variable. 0 denotes  $NOPF_{ddsn,l,f} = 0.1$  denotes  $ISN_{ddsn,l,f}$ :

$NOPF_{ddsn,l,f} > 0;$

Number of saved setups from the start of planning horizon  $NSS_{ddsn,l}$ : to  $SDDOD_{ddsn}$ .

Objective:

maximize

$$\sum_{ddsn=1}^{NDDSN} \sum_{l=1}^{NBMV} \sum_{f=1}^{F} SUPP_{ddsn,l,f}$$

Subject to:

Subject to:

$$\sum_{ddsn'=1}^{ddsn} \sum_{l=1}^{NBMV} SUPP_{ddsn',l,f} \ge \sum_{ddsn'=1}^{ddsn} DSCMD_{ddsn',f} \text{, for all } f \text{ and } ddsn ; \qquad (26)$$

$$\left(ISP_{ddsn,l,f} - 1\right) \times BM + ss \leq SUPP_{ddsn,l,f} \leq ISP_{ddsn,l,f} \times BM , \qquad (27)$$

for all ddsn, f, and l; where l = 1, 2, ..., NBMV;

$$MINS_{ddsn,l} = \sum_{f} ISP_{ddsn,l,f} - 1,$$

(28)

for all *ddsn* and *l*; where l = 1, 2, ..., NBMV;

$$ISP_{0,l,f} = 0$$

, for all *f*, and *l*; where  $l = 1, 2, ..., NBMV$ ; (29)

$$ISP_{ddsn,l,f} + ISP_{ddsn-1,l,f} - 1 \le ISG_{ddsn,l,f} \le \frac{\left(ISP_{ddsn,l,f} + ISP_{ddsn-1,l,f}\right)}{2}, \tag{30}$$

for all ddsn, f, and l; where l = 1, 2, ..., NBMV;

$$NOPF_{ddsn,l,f} = \left(\sum_{f'=1}^{F} ISP_{ddsn,l,f'}\right) - ISP_{ddsn,l,f}, \qquad (31)$$

for all ddsn, f, and l; where l = 1, 2, ..., NBMV;

$$(ISN_{ddsn,l,f} - 1) \times BM + ss \le NOPF_{ddsn,l,f} \le ISN_{ddsn,l,f} \times BM , \qquad (32)$$

for all ddsn, f, and l; where l = 1, 2, ..., NBMV;

$$DOF_{ddsn,l,f} \leq ISG_{ddsn,l,f},$$

(33)

for all ddsn, f, and l; where l = 1, 2, ..., NBMV;

$$\sum_{f} DOF_{ddsn,l,f} \ge \left(\sum_{f} ISG_{ddsn,l,f}\right) - 1,$$

(34)

for all ddsn, and l; where l = 1, 2, ..., NBMV;

$$DOF_{ddsn,l,f} \ge (ISG_{ddsn-1,l,f} - DOF_{ddsn-1,l,f}) + (ISG_{ddsn,l,f} - 1) + (ISN_{ddsn-1,l,f} - 1),$$

(35)

for all ddsn, f, and l; where l = 1, 2, ..., NBMV;

$$NSS_{ddsn,l} = \left(\sum_{ddsn'=1}^{ddsn} \sum_{f} ISG_{ddsn',l,f} - DOF_{ddsn',l,f}\right),\tag{36}$$

for all ddsn, and l; where l = 1, 2, ..., NBMV;

$$\left(\sum_{ddsn}^{ddsn}\sum_{f}SUPP_{ddsn',l,f}\right) + \left(ddsn-1\right) = NSS_{ddsn,d}\right) \times SExp_{BMG}$$

$$\leq MWH \times SDDOD_{ddsn}$$

for all  $ddsn$ , and  $l$ ; where  $l = 1, 2, ..., NBMV$ ;

$$\left(\sum_{ddsn}\sum_{l}SUPP_{ddsn,l,f} - \sum_{ddsn}DSCMD_{ddsn,f}\right) - \left(\sum_{ddsn}\sum_{l}SUPP_{ddsn,l,f'} - \sum_{ddsn}DSCMD_{ddsn,f'}\right) \leq BValue$$

(37)

$$(37)$$

For all product family *f* and *f*';

# Step 7. From the last due date period (i.e., *ddsn = NDDSN*) to the first one, do Step 8.

- **Step 8.** Mark the product family *f* whose  $DOF_{ddsn,l,j}$  is zero and  $ISG_{ddsn,l,f}$  is 1 as the first product family to be processed during  $DDP_{ddsn}$ . Mark the product family *f* of  $DDP_{ddsn-1}$  as the last product family to be processed. The sequence of other product families during  $DDP_{ddsn}$  is not important since it has no impact on the total setup time.

- Step 9. Record the sequence and allocated capacity of product families together with

the time points of setups to generate the setup schedule of mixed VPLs.

The main concept of the MIP model presented in **Step 6**, Algorithm 3-5 is discussed below.

$$\sum_{ddsn'=1}^{ddsn} \sum_{l=1}^{NBMV} SUPP_{ddsn',l,f} \ge \sum_{ddsn'=1}^{ddsn} DSCMD_{ddsn',f} \text{, for all } f \text{ and } ddsn ;$$

(26)

This inequality is used to satisfy the demand requirement. It uses the concept of "rolling schedule" to constrain that the total supply before  $SDDOD_{ddsn}$  must be larger or equal to the total demand before due date  $SDDOD_{ddsn}$ .

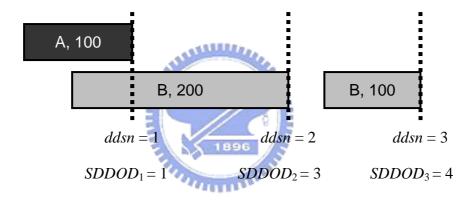

Take Figure 3-7 for example, there are three orders: 100 product A are due on day 1; 200 product B are due on day 3; 100 B product B are due on day 4.

Figure 3-7 An example of using concept of rolling schedule

For this case, inequality (26) generates the following inequalities:

$$SUPP_{1,A} \ge 100 \tag{39}$$

$$SUPP_{1,B} \ge 0 \tag{40}$$

$$SUPP_{1,A} + SUPP_{2,A} \ge 100 + 0$$

(41)

$$SUPP_{1,B} + SUPP_{2,B} \ge 0 + 200$$

(42)

$$SUPP_{1,A} + SUPP_{2,A} + SUPP_{3,A} \ge 100 + 0 + 0$$

(43)

$$SUPP_{1,B} + SUPP_{2,B} + SUPP_{3,B} \ge 0 + 200 + 100$$

(44)

Inequality (39) and (40) means that there must be at least 100 units capacity allocated for product family A and 0 unit for product family B before day 1 (ddsn = 1); Inequality (41) and (42) means that there must be at least 100 units capacity allocated for product family A and 200 units for product family B before day 3 (ddsn = 2); Inequality (43) and (44) means that there must be at least 100 units capacity allocated for product family A and 300 units for product family B before day 4 (ddsn = 3).

It is obvious that the inequalities gradually "roll" from the start to the end of the planning horizon. Therefore the orders are guaranteed not to be late for the due dates.

$$(ISP_{ddsn,l,f} - 1) \times BM + ss \leq SUPP_{ddsn,l,f} \leq ISP_{ddsn,l,f} \times BM , \qquad (27)$$

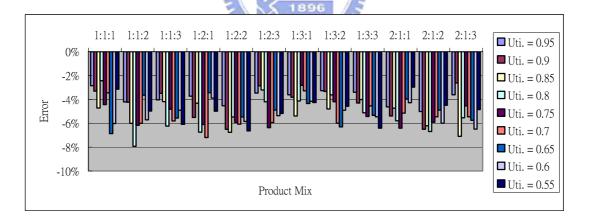

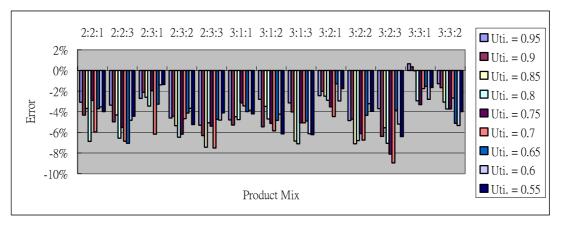

for each  $ddsn$ ,  $f$ , and  $l$ ; where  $l = 1, 2, ..., NBMV$ ;