Home Search Collections Journals About Contact us My IOPscience

Charge storage characteristics of high density Mo nanocrystal embedded in silicon oxide and silicon nitride

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2010 J. Phys. D: Appl. Phys. 43 075106

(http://iopscience.iop.org/0022-3727/43/7/075106)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/04/2014 at 04:32

Please note that terms and conditions apply.

J. Phys. D: Appl. Phys. 43 (2010) 075106 (4pp)

# Charge storage characteristics of high density Mo nanocrystal embedded in silicon oxide and silicon nitride

Chao-Cheng Lin<sup>1</sup>, Ting-Chang Chang<sup>2</sup>, Chun-Hao Tu<sup>1</sup>, Shih-Ching Chen<sup>2</sup>, Chih-Wei Hu<sup>1</sup>, Simon M Sze<sup>1</sup>, Tseung-Yuen Tseng<sup>1</sup>, Sheng-Chi Chen<sup>3</sup> and Jian-Yang Lin<sup>3</sup>

- <sup>1</sup> Institute of Electronics, National Chiao Tung University, Hsin-Chu 300, Taiwan, Republic of China

- <sup>2</sup> Department of Physics, Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, 70 Lien-hai Road, Kaohsiung 804, Taiwan, Republic of China

- <sup>3</sup> Graduate school of Opto-Electronic Engineering, National Yunlin University of Science and Technology, Yunlin 64002, Taiwan, Republic of China

E-mail: tcchang@mail.phys.nsysu.edu.tw

Received 16 July 2009, in final form 29 December 2009 Published 5 February 2010 Online at stacks.iop.org/JPhysD/43/075106

#### **Abstract**

We investigated the formation and charge storage characteristics of Mo nanocrystals in silicon oxide and in silicon nitride by rapid thermal annealing of oxygen- and nitrogen-incorporated Mo and Si mixed layers. A high density of Mo nanocrystal ( $6 \times 10^{12} \, \mathrm{cm}^{-2}$ ) was formed in the nitrogen-incorporated layer. Electrical analyses indicated that the memory window of the Mo nanocrystal embedded in the nitride is larger than that in the oxide. A reliability test showed that the Mo nanocrystal in the nitride has better reliability than the Mo nanocrystal in the oxide, which was explained by an electrical field simulation.

(Some figures in this article are in colour only in the electronic version)

#### 1. Introduction

Recently, metal nanocrystal memories have attracted considerable attention as promising candidates for next generation nonvolatile memories (NVMs) [1–3]. Compared with a semiconductor nanocrystal, metal nanocrystals have many advantages, such as higher density of states around the Fermi level and a wide range of available work functions [3]. However, when integrating the nanocrystal into the memory structure, there are still some issues regarding scaling. One of the main critical issues that limits device scaling is the variation of the electrical characteristics between cells, because the smaller the size of the device, the lower is the number of nanocrystals. Therefore, the formation of a high density nanocrystal which can alleviate the electrical variation between memory cells is important.

In this study, we investigate the formation of Mo nanocrystals by annealing oxygen- and nitrogen-incorporated Mo and Si mixed layers for nonvolatile memory application. Molybdenum is widely applied to VLSI due to its low cost, high work function and high thermal stability [4]. Furthermore, according to the literature, the size of a Mo nanocrystal can be as small as 2 nm without suffering from serious quantum effects, which is beneficial to retention characteristics [5]. In our experimental results, we found that the different ambience during sputtering can influence the density of the Mo nanocrystal. Furthermore, we study the memory characteristics and reliability of the Mo nanocrystal embedded in the oxide and in the nitride layer, and explain the difference in reliability between the Mo nanocrystal in the oxide and in the nitride through electrical field simulation.

### 2. Experiment

1

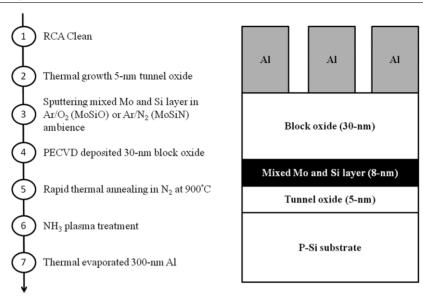

Figure 1 shows the process flow and memory structure. The memory cells were fabricated on a 6 inch p-type Si substrate. After the substrate was cleaned with the standard RCA process, a 5 nm-thick dry oxide was thermally grown at 950 °C on the substrate in a horizontal furnace as the tunnel oxide. An 8 nm-thick Mo silicate layer was subsequently deposited

Figure 1. Process flow and memory structure of this work.

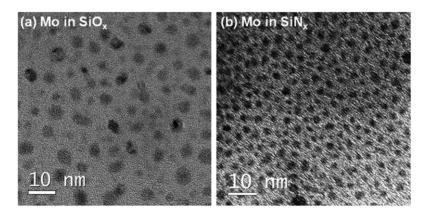

**Figure 2.** Plan-view TEM analyses for Mo nanocrystal (a) in oxide and (b) in nitride.

on the oxide layer by co-sputtering Mo and Si in Ar/O2 or Ar/N<sub>2</sub> ambience. 30 nm-thick Si oxide as the block oxide was deposited on the Mo silicate layer by plasma enhanced chemical vapour deposition at 300 °C. The thermal annealing process was performed in ambient N2 at 900 °C for 60 s to form Mo nanocrystals embedded in silicon oxide or nitride as the charge storage layer. Cells were then treated with NH<sub>3</sub> plasma to passivate the defects or traps in the oxide or nitride around the nanocrystals. To measure the electrical characteristics, 500 nm-thick Al was thermally evaporated through a shadow mask on the control oxide to form the metaloxide-semiconductor structure (MOS). Transmission electron microscopy (TEM) was used to investigate the nanostructure of the charge storage layer. Electrical characteristics including the capacitance-voltage (C-V) hysteresis and retention characteristics were measured using a Keithley4200 and HP4284 Precision LCR meter.

# 3. Results and discussion

Figures 2(a) and (b) are the plan-view TEM analysis for mixed Mo and Si layer deposited in Ar/O<sub>2</sub> (MoSiO) and in Ar/N<sub>2</sub>

(MoSiN) ambience after annealing at 900 °C, respectively. From the TEM analysis, the average size and density of the Mo nanocrystal formed in the oxygen-incorporated layer are about 5 nm and  $1\times 10^{12}\,\rm cm^{-2}$ , respectively. In contrast, the size of the Mo nanocrystal in the nitrogen-incorporated layer is about 2 nm, and the density is as high as  $6\times 10^{12}\,\rm cm^{-2}$ . The high density can prevent variation between cells while the size of the memory structure scales down. For the higher density of Mo nanocrystal in silicon nitride, we consider there is a higher density of dangling bonds in silicon nitride than in silicon oxide. According to the previous literature, nitridation of the silicon oxide layer increased the dangling bonds, which acted as nucleation centres in the layer. Therefore, the density of the nanocrystal can be increased.

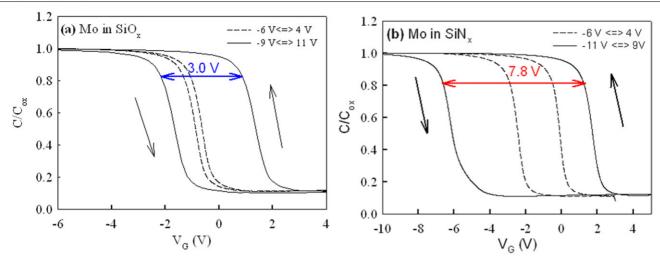

Figures 3(a) and (b) show the C-V curves of the Mo nanocrystal embedded in the oxide and in the nitride, respectively. The curves were obtained after the gate voltage swept from inversion to the accumulation region of the substrate (from 4 to -6 V and 9 to -11 V) and the reverse. The hysteresis loops of the sample are counterclockwise due to substrate injection through the tunnel oxide. It can be seen that the memory window (the width of the loop) for the Mo

Figure 3. C-V curves of the MOS for (a) Mo nanocrystal in the oxide and (b) Mo in the nitride as charge storage layer.

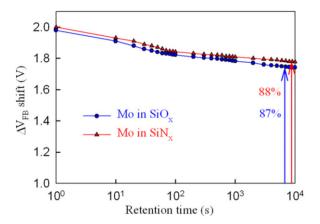

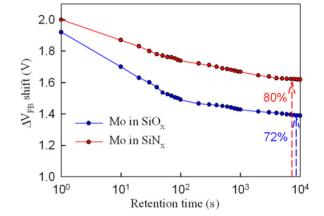

**Figure 4.** Retention behaviour of Mo nanocrystal in the oxide and in the nitride.

**Figure 5.** Retention behaviour of Mo nanocrystal in the oxide and in the nitride after 10<sup>6</sup> program/erase (P/E) cycles.

nanocrystal in the oxide is around  $3.0\,\mathrm{V}$  under  $9\,\mathrm{V}$  to  $-11\,\mathrm{V}$  sweeping voltage. In contrast, the memory window of the Mo nanocrystal in the nitride is around  $7.8\,\mathrm{V}$ . The larger memory window can be attributed to the high density of the nanocrystal. During the voltage sweeping, carriers can be injected from the substrate to the nanocrystals and then captured by the nanocrystals. The memory window is proportional to the total stored charges in the cell. If one nanocrystal captures one electron during the sweeping voltage, the total stored carriers for the higher density of the nanocrystal in the unit cell are larger than that for the lower density one. This results in a larger memory window for the Mo nanocrystal in the nitride than that for the Mo nanocrystal in the oxide.

Figure 4 is the retention characteristic for Mo embedded in the oxide and in the nitride. The retention was measured by the stress voltage on the Al gate electrode.  $\Delta V_{FB}$  was obtained by comparing the C-V curves for the sample before and after applying the programming voltage stress on the Al gate.  $V_{FB}$  is defined as the voltage at which the band bending in the substrate is flat. It can be seen that the remaining charge of the Mo nanocrystal in the oxide is 87% which is close to the remaining charge of the Mo nanocrystal in the nitride (88%). However, after programming and erasing (P/E)

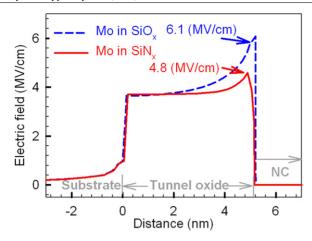

cycles at a pulse voltage of 15 V for 10 ms, the remaining charge is 72% for the Mo nanocrystal in the oxide (figure 5). The retention characteristic of Mo in the oxide has 15% degradation. In contrast, the retention of Mo nanocrystal in the nitride has only 8% degradation. These results indicated that the Mo nanocrystal embedded in the nitride layer as the charge storage layer has better reliability than the Mo nanocrystal in the oxide. The better retention characteristic of Mo in the nitride was explained by electrical field simulation for both structures. Figure 6 shows the electrical field distribution in the memory structure. The simulation conditions of the nanocrystal structures are according to TEM analyses and the gate voltage is settled at the programming voltage (15 V). Here, we use the ISE Integrated Systems Engineering TCAD software to build the nanocrystal (NC) structure and model. It can be seen that the maximum electrical field for the Mo embedded in oxide is 6.1 MV cm<sup>-1</sup>. However, the electrical field for the Mo embedded in nitride is 4.8 MV cm<sup>-1</sup>. Since the voltage drop on a metal nanocrystal is small and can be ignored, the larger the size of the nanocrystal in the dielectric, the higher the electrical field in the surrounding dielectric. For the same thickness of the gate dielectric and the same electrode bias, because the size of the nanocrystal in the oxide (5 nm) is

**Figure 6.** Simulation of electrical field for Mo nanocrystal in the oxide and in the nitride.

larger than that in the nitride (2 nm), the electrical field in the tunnel oxide of Mo embedded in the oxide should be larger than that in the nitride. During the P/E cycles, the larger electrical field indicates the larger amount of carrier transport between the nanocrystal and the substrate, resulting in a significant degradation in the tunnel oxide. Therefore, the retention of the Mo nanocrystal in the oxide is poorer than that of the Mo nanocrystal in the nitride.

## 4. Conclusion

In conclusion, memory characteristics of Mo nanocrystals embedded in silicon oxide and silicon nitride were investigated

in this study. The density of the Mo nanocrystal in the nitride is  $6\times10^{12}~\rm cm^{-2}$ . The memory window can be enhanced by the Mo nanocrystal embedded in the nitride. The larger memory (7.8 V) for the Mo nanocrystal in the nitride can be attributed to the higher density of the nanocrystal. The retention after  $10^6$  P/E cycles has 15% and 8% degradation for the Mo nanocrystal in the oxide and in the nitride, respectively. The large memory window and good reliability of high density Mo nanocrystals embedded in nitride can be applied in next generation NVMs.

# Acknowledgment

This work was performed at the National Science Council Core Facilities Laboratory for Nano-Science and Nano-Technology in Kaohsiung-Pingtung area and was supported by the National Science Council of the Republic of China under Contract Nos NSC-97-3114-M-110-001, NSC 97-2112-M-110-009-MY3 and NSC 98-2221-E-009-001-.

#### References

- [1] Tang S, Mao C, Liu Y, Kelly D Q and Banerjee S K 2007 *IEEE Electron Device Lett.* **54** 433

- [2] Dufourcqa J, Murb P, Gordonc M J, Minoretb S, Copparda R and Baron T 2007 Mater. Sci. Eng. C 27 1496

- [3] Liu Z, Lee C, Narayanan V, Pei G and Kan E C 2002 IEEE Electron Device 49 1606

- [4] Li T L, Ho W L, Chen H B, Wang H C H, Chang C Y and Hu C 2006 IEEE Trans. Electron Devices 53 1420

- [5] Guan W, Long S, Liu M, Liu Q, Hu Y, Li Z and Jia R 2007 Solid-State Electron. 51 806