The Characteristics of n- and p-Channel Poly-Si Thin-Film Transistors with Fully Ni-Salicided S/D and Gate Structure

Po-Yi Kuo,<sup>a,z</sup> Yan-Syue Huang,<sup>a</sup> Yi-Hsien Lue,<sup>a</sup> Tien-Sheng Chao,<sup>a</sup> and Tan-Fu Lei<sup>b</sup>

<sup>a</sup>Department of Electrophysics and <sup>b</sup>Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 30050, Taiwan

n- and p-channel poly-Si thin-film transistors with fully Ni-self-aligned silicided (fully Ni-salicided) source/drain (S/D) and gate structure (n- and p-channel FUSA-TFTs) have been successfully fabricated on a 40 nm thick channel layer. The conventional poly-Si gate is replaced by the fully Ni-silicided gate, and the parasitic S/D resistance of the FUSA-TFTs is significantly reduced by the fully Ni-silicided S/D structure. The fully Ni-salicidation process is executed at a low temperature of 500°C for a short rapid thermal annealing time. Experimental results show that the FUSA-TFTs give increased on/off current ratio, improved subtreshold characteristics, less threshold voltage roll-off, lower parasitic S/D resistance, higher gate capacitance, and larger field-effect mobility than conventional TFTs. The FUSA-TFTs are suitable for three-dimensional integration applications and high performance driver circuits in the active-matrix liquid crystal displays. © 2009 The Electrochemical Society. [DOI: 10.1149/1.3258283] All rights reserved.

Manuscript submitted April 17, 2009; revised manuscript received September 28, 2009. Published November 13, 2009.

Polycrystalline silicon thin-film transistors (poly-Si TFTs) have been widely used in many potential applications including threedimensional (3D) integration high density flash memories, pixel driving elements in active-matrix organic light emitting diodes and integrated peripheral driving circuits, and addressing elements of active-matrix liquid crystal displays (AMLCDs).<sup>1-4</sup> However, the output characteristics exhibit an anomalous increase in current in the saturation regime, often called the "kink" effect by analogy with silicon-on-insulator (SOI) devices.<sup>5-7</sup> This phenomenon can be attributed to the floating-body effect<sup>8</sup> and avalanche multiplication enhanced by grain boundary traps,<sup>6</sup> particularly in n-channel TFTs. With increasing drain voltage, the added drain current enhances impact ionization and the parasitic bipolar junction transistor (BJT) effect, which leads to a premature breakdown in return.<sup>8</sup> In the floating-body thin-film devices, the improved parasitic BJT effect can be achieved by using deep salicidation and a fully silicided source/drain (S/D) structure.<sup>9,1</sup>

Due to low hole field-effect mobility, p-channel TFTs have a lower on-state current than n-channel TFTs. Nevertheless, p-channel TFTs have advantages, such as a lower off-state leakage current, slighter floating-body and kink effects, a weaker drain impact ionization, and a higher hot carrier reliability. In addition, thin-channel poly-Si TFTs have better device characteristics such as a small leakage current and a suppressed floating-body effect than thick-channel poly-Si TFTs.<sup>11</sup> However, a thin-channel film also leads to increased parasitic S/D resistance. Parasitic S/D resistances become an increasingly serious issue for thin-channel poly-Si TFTs and SOI devices. Several methods such as self-aligned silicide, selective tungsten-clad and metal-replaced junction technology have been proposed to reduce parasitic S/D resistance in thin-channel SOI devices and poly-Si TFTs.<sup>12-15</sup>

Silicided and metal gates have a higher capacitance than poly-Si gates due to the elimination of poly-Si depletion.<sup>16-18</sup> Field-effect mobility and on-state current in such gates can be improved by reducing parasitic S/D resistance and increasing gate capacitance.<sup>14,15</sup> In this paper, n- and p-channel poly-Si thin-film transistors with fully Ni-self-aligned silicided (fully Ni-salicided) S/D and gate structure (n- and p-channel FUSA-TFTs), whose S/D and gate poly-Si layers are completely silicided with Ni, have been successfully fabricated on a 40 nm thick channel layer.<sup>19,20</sup> The low resistance fully Ni-salicided S/D and gate permits a significant re-

covery of the intrinsic characteristics of thin-channel TFTs. We also find that the floating-body and parasitic BJT effects can be significantly suppressed by FUSA-TFTs.

## Experimental

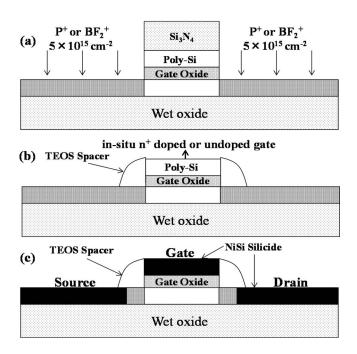

Figure 1 shows the main fabrication process steps of FUSA-TFTs. First, a 40 nm amorphous silicon (a-Si) layer was deposited by low pressure chemical vapor deposition (LPCVD) at 550°C on oxidized silicon wafers. The a-Si layer was then crystallized by solid-phase crystallization at 600°C for 24 h. After the patterning of the active region, a 50 nm tetraethoxysilane (TEOS) gate oxide layer was deposited by LPCVD. Next, a 50 nm a-Si gate layer, along with a 100 nm Si<sub>3</sub>N<sub>4</sub> layer as the hard mask, was deposited by LPCVD. Then, the a-Si gate layer was crystallized into poly-Si after the deposition of a Si<sub>3</sub>N<sub>4</sub> hard mask layer at 780°C for 1 h.

The a-Si gate layers were divided into in situ  $n^+$  phosphorusdoped or undoped gates in n-channel FUSA-TFTs. The a-Si gate layer was an undoped gate in p-channel FUSA-TFTs. Due to experimental equipment limitations, p-channel FUSA-TFTs with in situ p<sup>+</sup> boron-doped gates were not fabricated in our experiments.

After defining the gate electrode, self-aligned S/D implantation was used to form the n<sup>+</sup>/p<sup>+</sup> with P<sup>+</sup>/BF<sub>2</sub><sup>+</sup> to dose  $5 \times 10^{15}$  cm<sup>-2</sup> for n-/p-channel (Fig. 1a). Dopants were activated by rapid thermal annealing (RTA) at 600°C for 120 s for short channel FUSA-TFTs. A 150 nm TEOS oxide was deposited and etched to form the sidewall spacer. The Si<sub>3</sub>N<sub>4</sub> hard mask layer was then selectively etched in a hot phosphoric acid bath (Fig. 1b). A Ni film of about 40 nm was deposited by sputtering, and then a fully Ni-salicided process was carried out at 500°C for 60 s by a one-step RTA in the N<sub>2</sub> ambient. The fully Ni-silicided S/D and gate structure was formed by the fully Ni-salicided process (Fig. 1c). In addition, we used thin Ni film (about 15 nm) to form partially salicided n-channel TFTs with in situ doped gates. The V<sub>th</sub> differences between partially salicided n-channel TFTs and n-channel FUSA-TFTs with in situ doped gates are also studied in this paper.

Conventional devices with self-aligned n<sup>+</sup> S/D and without Nisalicidation were also fabricated to serve as controls. After the contact and metallization processes, NH<sub>3</sub> plasma treatments were implemented after sintering at 400°C for 30 min. Plasma treatment has long been used in TFT devices. A suitable plasma treatment can improve the electrical characteristics of TFT devices due to the generation of H atoms in NH<sub>3</sub> plasma, which effectively passivates defects in poly-Si TFTs.<sup>21,22</sup> The sintering process has also long been used in the fabrication of semiconductor devices for reducing the contact resistance between the metal and the semiconductor. Sintering was performed in atmospheric pressure N<sub>2</sub> ambient diluted

<sup>&</sup>lt;sup>z</sup> E-mail: kuopoyi.ee91g@gmail.com

Figure 1. Main process flow of FUSA-TFTs.

with 5%  $H_2$ . The H atoms generated during the sintering process passivate the defects in the metal/semiconductor interface.<sup>23</sup>

# **Results and Discussion**

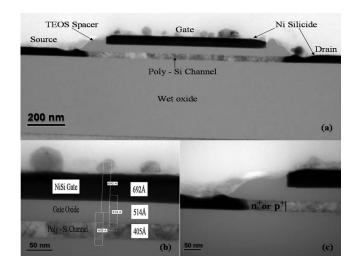

*FUSA process.*— Cross-sectional transmission electron microscopy (TEM) micrographs of FUSA-TFTs are shown in Fig. 2. The gate and S/D of FUSA-TFTs were fully Ni-salicided. In our study, we used a sufficiently thick Ni film (about 40 nm) to achieve fully Ni-salicided TFTs. According to the volume ratio of Ni-silicidation, a typical 30–40 nm thick Ni film can completely convert the 50 nm thick poly-Si to fully Ni-silicided. To ensure a fully Ni-salicided S/D and gate, we chose a 40 nm thick Ni film and a one-step RTA at 500°C for 60 s. To form fully Ni-salicided TFTs, the duration of RTA must be adequate. The key factor in the process is the balance between the TEOS spacer length and the RTA conditions. When the TEOS spacer length is longer than the lateral diffusion length of the Ni-silicidation, S/D n<sup>+</sup> or p<sup>+</sup> junction can be left to avoid the for-

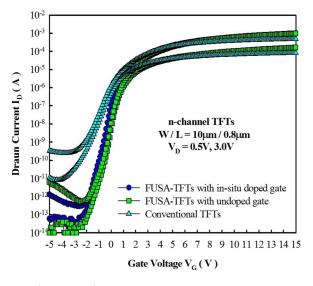

Figure 3. (Color online) Measured transfer characteristics of n-channel conventional and n-channel FUSA-TFTs with  $W/L = 10/0.8 \mu m$ .

mation of the Schottky barrier junction. When the Ni-silicided edge is too close to the S/D n<sup>+</sup> or p<sup>+</sup> junction edge, due to an inappropriate high temperature and an overly long RTA process, an abnormally high off-state leakage current ( $I_{off}$ ) and gate-induced-drain leakage (GIDL)-like current occur.<sup>24,25</sup>

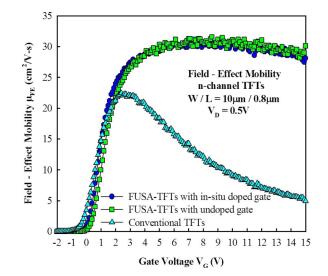

*n-Channel FUSA-TFTs.*— The measured transfer characteristics and field-effect mobility of the n-channel conventional and the n-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu$ m are shown in Fig. 3 and 4, respectively. The on-state currents and field-effect mobility in the FUSA-TFTs are higher than those of the conventional TFTs, while the off-state leakage currents of the FUSA-TFTs are lower than those of the conventional TFTs. The on-state currents are significantly degraded by the parasitic S/D resistance in short channel conventional TFTs. The field-effect mobility plotted in Fig. 4 is obtained from the channel conductance at  $V_D = 0.5 \ V$ . For conventional TFTs with a short gate length of 0.8  $\mu$ m, the field-effect mobility is seriously decreased when gate voltage  $V_G > 2.5 \ V$ , but this effect is not found in short channel FUSA-TFTs. The high fieldeffect mobility of FUSA-TFTs can be maintained with large gate

Figure 2. Cross-sectional TEM micrographs of FUSA-TFTs with gate length of 0.8  $\mu m$  and channel thickness of 40 nm.

**Figure 4.** (Color online) Field-effect mobility of n-channel conventional and n-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu m$ .

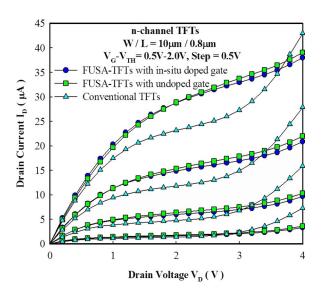

Figure 5. (Color online) Measured output characteristics of n-channel conventional and n-channel FUSA-TFTs with  $W/L = 10/0.8 \mu$ m.

voltages. This improvement is due to the fully Ni-salicided S/D and gate structure, which has a smaller parasitic S/D resistance, higher capacitance, and better scalability than conventional TFTs with poly-Si gates.<sup>15</sup> The superiority of the FUSA-TFTs may also be found in the subthreshold swing (SS). We believe that this is due to the higher gate capacitance in the FUSA-TFTs.

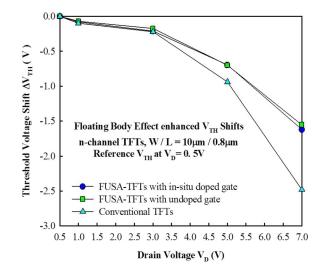

The measured output characteristics of the n-channel conventional and the n-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu\text{m}$  are shown in Fig. 5. Under a high drain voltage, the strong drain impact ionization causes a profound kink effect and induced parasitic BJT action, which results in decreased drain breakdown voltage due to the floating-body effect in conventional TFTs.<sup>26-29</sup> Silicidation is a well-known method for suppressing the floating-body effect because the silicide layer near the S/D junction works as a sink and an effective lifetime killer for holes.<sup>9,10</sup> Figure 6 illustrates the relationship between the  $V_{\rm th}$  shift ( $\Delta V_{\rm th}$ ) and  $V_{\rm D}$  for the n-channel conventional and the n-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu\text{m}$ . The reference voltage is  $V_{\rm th}$  at  $V_{\rm D} = 0.5$  V. The enhanced  $\Delta V_{\rm th}$  at high drain voltage is observed in conventional TFTs. The reduced kink

**Figure 6.** (Color online) Threshold voltage shift ( $\Delta V_{th}$ ) vs drain voltage  $V_D$  characteristics for the n-channel conventional and the n-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu$ m. The reference voltage is  $V_{th}$  at  $V_D = 0.5 \ V$ .

effect, increased drain breakdown voltage, and decreased  $\Delta V_{\rm th}$  of FUSA-TFTs clearly demonstrate that floating-body and parasitic BJT effects can be significantly suppressed by the fully silicided S/D structure.

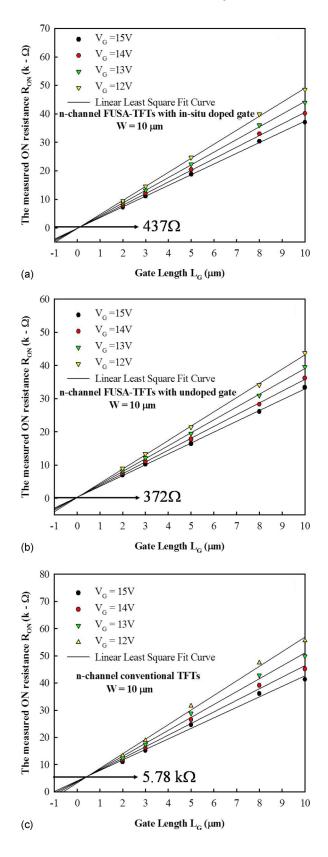

To demonstrate that parasitic S/D resistance can be greatly reduced by the fully Ni-salicided process, the parasitic resistance  $R_{\rm P}$  of (a) n-channel FUSA-TFTs with in situ doped gates, (b) n-channel FUSA-TFTs with undoped gates, and (c) n-channel conventional TFTs, in the linear region, is extracted by plotting the measured on-state resistance  $(R_{on})$  vs gate length  $(L_G)$ , as shown in Fig. 7. The relationship between  $R_{on}$  and L across different gate biases may be expressed by several straight lines that extend to merge at a characteristic length  $L_0$  representing the accumulation channel in the LDD (and S/D) area and having a residual value of gate-voltageindependent parasitic resistance  $R_{\rm P}$ .<sup>12</sup> The  $R_{\rm P}$  of FUSA-TFTs with an in situ doped gate and an undoped gate is roughly 437 and 372  $\Omega$ , respectively. The  $L_0$  of FUSA-TFTs with either in situ doped gate or undoped gate is close to 0  $\mu$ m. The  $R_{\rm P}$  of conventional TFTs is extracted by the same method and is about 5.78 k $\Omega$ . Therefore, the on-state currents and field-effect mobility are greatly improved by reducing  $R_{\rm P}$  in the n-channel FUSA-TFTs.

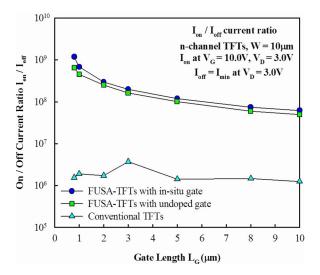

Figure 8 displays the on/off current ratio  $(I_{on}/I_{off})$  of the n-channel conventional and the n-channel FUSA-TFTs with W = 10  $\mu$ m. The on-state current is defined as the drain current ( $I_D$ ) at  $V_{\rm G}$  = 10.0 V,  $V_{\rm D}$  = 3.0 V, and the off-state current is defined as the minimum drain current  $(I_{min})$  at  $V_D = 3.0$  V. The  $I_{on}/I_{off}$   $(10^8-10^9)$ can be increased by scaling down the gate length in FUSA-TFTs. Because the  $V_{\rm th}$  of FUSA-TFTs with in situ doped gates is smaller than the  $V_{\rm th}$  of FUSA-TFTs with undoped gates, the  $I_{\rm on}/I_{\rm off}$  of FUSA-TFTs with in situ doped gates is larger than the  $I_{\rm on}/I_{\rm off}$  of FUSA-TFTs with undoped gates. The  $I_{\rm on}/I_{\rm off}$  (10<sup>6</sup>-10<sup>7</sup>) of conventional TFTs becomes limited as the gate length is scaled down. The enhancement of off-state leakage currents is observed in short channel conventional TFTs. The off-state leakage currents of the conventional TFTs increase as the gate length is scaled down. The enhanced off-state leakage current is due to the amplification of GIDL currents caused by floating-body and parasitic BJT effects in short channel devices. Because the FUSA-TFTs effectively suppress the floating-body effect, the enhancement of GIDL currents can be eliminated in short channel devices.

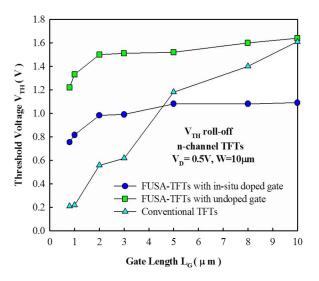

Figure 9 shows the extracted threshold voltage  $V_{\rm th}$  of the n-channel conventional and the n-channel FUSA-TFTs for different gate lengths (defined as  $I_{\rm D} = W/L \times 100$  nA at  $V_{\rm D} = 0.5$  V). The roll-off of  $V_{\rm th}$  is greatly improved in FUSA-TFTs. With this fully Ni-salicided structure, floating-body and parasitic BJT effects can be suppressed, resulting in a stable  $V_{\rm th}$  and a lower off-state leakage current in the FUSA-TFTs.<sup>31,32</sup> Figure 9 also shows the  $V_{\rm th}$  difference between the FUSA-TFTs with an in situ n<sup>+</sup> doped gate and the FUSA-TFTs with an undoped gate. The  $V_{\rm th}$  difference is observed with additional P<sup>+</sup> dopants in the FUSA-TFTs with an in situ n<sup>+</sup> doped gate. The fully Ni-silicided process induced segregation of the impurities from poly-Si to the silicide interface leads to a submonolayer segregation of the dopants, causing a change in the apparent NiSi work function shift.<sup>16,33</sup>

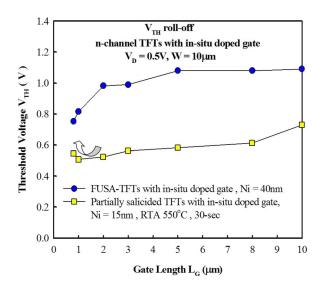

Further, we also used thin Ni film (about 15 nm) to form partially salicided TFTs with in situ doped gates. The partially salicided TFTs were formed by RTA at 550°C for 30 sec. Figure 10 displays the extracted  $V_{\rm th}$  roll-off of the n-channel FUSA-TFTs with in situ doped gates and n-channel partially salicided TFTs with in situ doped gates. The n-channel FUSA-TFTs with an in situ doped gate have a more positive  $V_{\rm th}$  than the partially salicided TFTs. We also found that short channel ( $L_{\rm G} = 1-0.8 \ \mu m$ ) partially salicided TFTs display a reverse  $V_{\rm th}$  change approximately equal to the  $V_{\rm th}$  of the short channel FUSA-TFTs. This result indicates that a shorter RTA time is required to achieve the fully Ni-silicided gate in short channel poly-Si TFTs, compared to long channel poly-Si TFTs. If we use a thinner Ni film to achieve the fully Ni-salicided TFTs, we need a

**Figure 7.** (Color online) The parasitic resistance  $R_{\rm P}$  of (a) n-channel FUSA-TFTs with in situ doped gate, (b) n-channel FUSA-TFTs with undoped gate, and (c) n-channel conventional TFTs, in the linear region, is extracted by plotting the measured on-state resistance ( $R_{\rm on}$ ) vs gate length ( $L_{\rm G}$ ).

**Figure 8.** (Color online) On/off current ratio  $(I_{on}/I_{off})$  of n-channel conventional and n-channel FUSA-TFTs with  $W = 10 \ \mu$ m. On-state current is defined as drain current ( $I_D$ ) at  $V_G = 10.0 \ V$ ,  $V_D = 3.0 \ V$ ; off-state current is defined as minimum drain current ( $I_{min}$ ) at  $V_D = 3.0 \ V$ .

higher RTA temperature or a longer RTA time to ensure that the S/D and gate are fully Ni-salicided across all gate lengths.

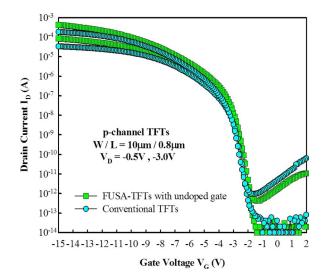

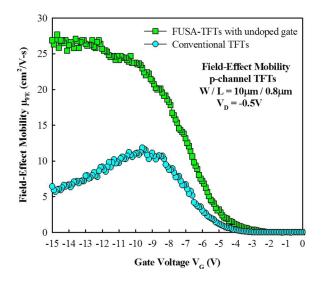

*p-Channel FUSA-TFTs.*— The measured transfer characteristics and field-effect mobility of the p-channel conventional and the p-channel FUSA-TFTs with  $W/L = 10/0.8 \mu$ m are shown in Fig. 11 and 12, respectively. In short channel p-channel TFTs, the on-state currents and field-effect mobility of the FUSA-TFTs are higher than in the conventional TFTs, while the off-state leakage currents of FUSA-TFTs are slightly lower than in the conventional TFTs. The improvement in the electrical characteristics of the p-channel FUSA-TFTs is similar to that seen in the n-channel FUSA-TFTs, except for the improvement in off-state leakage currents. The onstate currents are significantly limited by the parasitic S/D resistance in short channel conventional TFTs. For the conventional TFTs with a short gate length of 0.8  $\mu$ m, the field-effect mobility is seriously degraded when gate voltage  $V_G > -9.0$  V, but this effect is not seen in short channel FUSA-TFTs. The high field-effect mobility of p-channel FUSA-TFTs is due to the fully Ni-salicided S/D and gate

**Figure 9.** (Color online) Extracted  $V_{\rm th}$  roll-off of n-channel conventional and n-channel FUSA-TFTs with different gate lengths ( $V_{\rm th}$  is defined as  $I_{\rm D} = W/L \times 100$  nA at  $V_{\rm D} = 0.5$  V).

Figure 10. (Color online) Extracted  $V_{\rm th}$  roll-off of n-channel FUSA-TFTs with in situ doped gates and n-channel partially salicided TFTs with in situ doped gates. The partially salicided TFTs were formed by RTA at 550°C for 30 s.

structure, which offers a smaller parasitic S/D resistance, higher capacitance, and better scalability than the conventional TFTs with poly-Si gates.<sup>16</sup> The p-channel FUSA-TFTs also show improved subthreshold characteristics.

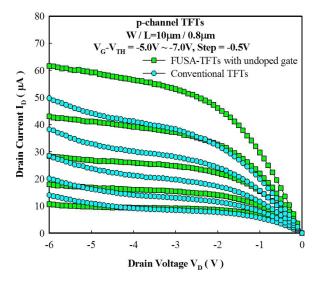

The measured output characteristics of the p-channel conventional and the p-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu\text{m}$  are shown in Fig. 13. Obviously FUSA-TFTs exhibit larger driving currents than conventional TFTs in short channel devices. The high driving currents of the FUSA-TFTs can be attributed to the fully Ni-salicided S/D and gate structure. The short channel FUSA-TFTs have more saturated output characteristics and increased drain breakdown voltage than the conventional TFTs. These findings provide strong evidence that parasitic BJT effects in p-channel TFTs are significantly suppressed by the fully silicided S/D structure.<sup>10</sup>

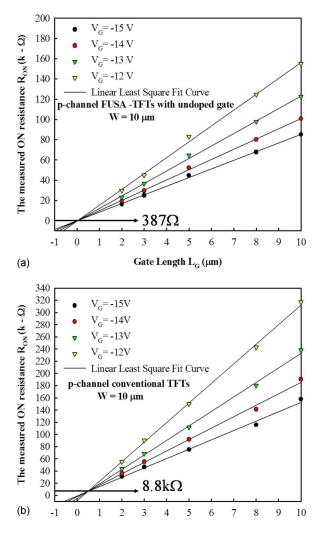

The parasitic resistance  $R_{\rm P}$  of (a) p-channel FUSA-TFTs with undoped gates and (b) p-channel conventional TFTs, in the linear region, is extracted by plotting the measured on-state resistance  $(R_{\rm on})$  vs gate length  $(L_{\rm G})$ , as shown in Fig. 14. The  $R_{\rm P}$  of FUSA-

Figure 11. (Color online) Measured transfer characteristics of p-channel conventional and p-channel FUSA-TFTs with  $W/L = 10/0.8 \mu m$ .

Figure 12. (Color online) Field-effect mobility of p-channel conventional and p-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu m$ .

TFTs with undoped gates is about 387  $\Omega$ , while their  $L_{\rm O}$  is close to 0  $\mu$ m. The  $R_{\rm P}$  of conventional TFTs is about 8.8 k $\Omega$ . Therefore, the on-state currents and field-effect mobility are significantly improved by reducing  $R_{\rm P}$  in the p-channel FUSA-TFTs.

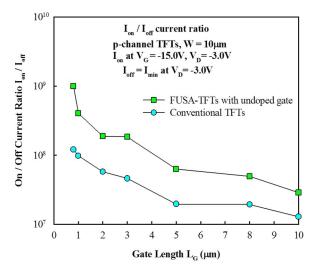

Figure 15 displays the on/off current ratio  $(I_{on}/I_{off})$  of the p-channel conventional and the p-channel FUSA-TFTs with  $W = 10 \ \mu\text{m}$ . The on-state current is defined as drain current  $(I_D)$  at  $V_G = -15.0 \ \text{V}$ ,  $V_D = -3.0 \ \text{V}$ , and the off-state current is defined as minimum drain current  $(I_{\min})$  at  $V_D = -3.0 \ \text{V}$ . The  $I_{on}/I_{off}$  ( $10^8-10^9$ ) can be increased when the gate length in FUSA-TFTs is reduced. Unlike n-channel conventional TFTs, the  $I_{on}/I_{off}$  ( $10^7-10^8$ ) of p-channel conventional TFTs increases as gate length is scaled down. The enhancement of off-state leakage currents is not observed in short channel p-channel conventional TFTs due to the weak drain impact ionization and a slight floating-body effect.

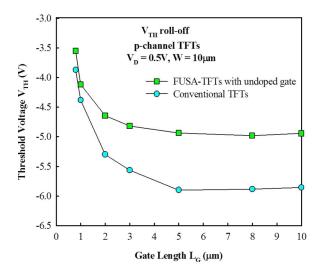

Figure 16 displays the extracted  $V_{\rm th}$  of the p-channel conventional and the p-channel FUSA-TFTs across different gate lengths (defined as  $I_{\rm D} = W/L \times 10$  nA at  $V_{\rm D} = -0.5$  V). The  $V_{\rm th}$  roll-off is greatly improved in the FUSA-TFTs. The threshold voltage absolute values  $|V_{\rm th}|$  of FUSA-TFTs are smaller than in conventional TFTs

Figure 13. (Color online) Measured output characteristics of p-channel conventional and p-channel FUSA-TFTs with  $W/L = 10/0.8 \ \mu m$ .

Figure 14. (Color online) The parasitic resistance  $R_{\rm P}$  of (a) p-channel FUSA-TFTs with undoped gates and (b) p-channel conventional TFTs, in the linear region, is extracted by plotting the measured on-state resistance  $(R_{on})$ vs gate length  $(L_G)$ .

due to the improved SS of the FUSA-TFTs. We believe that the stable  $V_{\rm th}$  and the improved SS of the p-channel FUSA-TFTs result from the fully Ni-salicided S/D and gate structure.

## Conclusions

We have developed n- and p-channel FUSA-TFTs. In n-channel TFTs, the FUSA-TFTs show reduced kink effect, increased drain breakdown voltage, stable  $V_{\rm th}$  roll-off, improved SS, lower parasitic S/D resistance, higher field-effect mobility, and increased on/off current ratio compared to conventional TFTs. The p-channel FUSA-TFTs were also fabricated with improved device performance. The parasitic resistance of S/D and gate is greatly reduced, making it possible to recover the intrinsic characteristics of thin-channel TFTs. In this paper, FUSA-TFTs with low thermal budget fully Nisalicided processes are shown to be a very promising structure with low parasitic S/D resistance and high gate capacitance ability, suitable for 3D integration applications and high-performance driver circuits in the AMLCDs.

## Acknowledgment

This work was supported by the National Science Council, Taiwan, under contract no. NSC-97-2221-E-009-152-MY3. The authors thank the Nano Facility Center (NFC) of National Chiao Tung Uni-

Figure 15. (Color online) On/off current ratio  $(I_{on}/I_{off})$  of p-channel conventional and p-channel FUSA-TFTs with  $W = 10 \ \mu m$ . On-state current is defined as drain current ( $I_D$ ) at  $V_G = -15.0$  V,  $V_D = -3.0$  V; off-state current is defined as minimum drain current  $(I_{min})$  at  $V_D = -3.0$  V.

Figure 16. (Color online) Extracted  $V_{\rm th}$  roll-off of p-channel conventional and p-channel FUSA-TFTs with different gate lengths ( $V_{\rm th}$  is defined as  $I_{\rm D}$  $= W/L \times 10$  nA at  $V_D = -0.5$  V).

versity and the National Nano Device Laboratory (NDL) for providing process equipment.

National Chiao Tung University assisted in meeting the publication costs of this article.

## References

- 1. A. J. Walker, S. Nallamothu, E. H. Chen, M. Mahajani, S. B. Herner, M. Clark, J. M. Cleeves, S. V. Dunton, V. L. Eckert, J. Gu, et al., in Symposium on VLSI Technology, Digest of Technical Papers, pp. 29–30 (2003). T. Shimoda, H. Ohshima, S. Miyashita, M. Kimura, T. Ozawa, I. Yudasaka, H.

- 2 Kobayashi, R. H. Friend, J. H. Burroughes, and C. R. Towns, in Proceedings of the

- Asian Symposium on Information Display, p. 217 (1998).

A. G. Lewis, I.-W. Wu, T. Y. Huang, A. Chiang, and R. H. Bruce, *Tech. Dig. Int.* Electron Devices Meet., 1990, 843.

- H. Oshima and S. Morozumi, *Tech. Dig. Int. Electron Devices Meet.*, **1989**, 157. M. Koyanagi, H. Kurino, T. Hashimoto, H. Mori, K. Hata, Y. Hiruma, T. Fujimori, 5.

- I.-W. Wu, and A. G. Lewis, Tech. Dig. Int. Electron Devices Meet., 1991, 571. M. Hack and A. G. Lewis, IEEE Electron Device Lett., 12, 203 (1990).

- J. P. Colinge, IEEE Electron Device Lett., 9, 97 (1988).

- M. Valdinoci, L. Colalongo, G. Baccarani, G. Fortunato, A. Pecora, and I. Policic-chio, *IEEE Trans. Electron Devices*, **44**, 2234 (1997). 8.

- F. Deng, R. A. Johnson, W. B. Dubbeldav, G. A. Garcia, P. M. Asbeck, and S. S. Lau, in Proceedings of the IEEE International SOI Conference, IEEE, p. 78 (1996).

- 10. T. Ichimori and N. Hirashita, IEEE Trans. Electron Devices, 49, 2296 (2002).

- 11. M. Miyasaka, T. Komatsu, W. Itoh, A. Yamaguchi, and H. Ohshima, Jpn. J. Appl.

- Phys., Part I, 35, 923 (1996).

H. W. Zen, T. C. Chang, P. S. Shih, D. Z. Peng, P. Y. Kuo, T. Y. Huang, C. Y. Chang, and P. T. Lin, *IEEE Electron Device Lett.*, 24, 509 (2003).

- 13. K. H. Lee, J. K. Park, and J. Jang, IEEE Trans. Electron Devices, 45, 2548 (1998).

- 14. D. Zhang and M. Wong, IEEE Electron Device Lett., 27, 269 (2006).

- 15. J. Chen, J. P. Colinge, D. Flandre, R. Gillon, J. P. Raskin, and D. Vanhoenacker, J. Electrochem. Soc., 144, 2437 (1997). 16. J. Kedzierski, D. Boyd, C. Cabral, Jr., P. Ronsheim, S. Zafar, P. M. Kozlowski, J.

- A. Ott, and M. Ieong, IEEE Trans. Electron Devices, 52, 39 (2005).

- 17. A. E. J. Lim, R. T. P. Lee, C. H. Tung, S. Tripathy, D. L. Kwong, and Y. C. Yeo,

- *J. Electrochem. Soc.*, **153**, G337 (2006). 18. M. Qin, V. M. C. Poon, and S. C. H. Ho, *J. Electrochem. Soc.*, **148**, G271 (2001). 19. P. Y. Kuo, T. S. Chao, R. J. Wang, and T. F. Lei, IEEE Electron Device Lett., 27,

- 258 (2006). 20. H. C. Wen, J. H. Sim, J. P. Lu, and D. L. Kwong, Electrochem. Solid-State Lett., 7,

- G258 (2004).

- C. W. Lin, M. Z. Yang, C. C. Yeh, L. J. Cheng, T. Y. Huang, H. C. Cheng, H. C. Lin, T. S. Chao, and C. Y. Chang, *Tech. Dig. Int. Electron Devices Meet.*, 1999, 305.

- 22. H. C. You, P. Y. Kuo, F. H. Ko, T. S. Chao, and T. F. Lei, IEEE Electron Device

Lett., 27, 799 (2006).

- 23. L. C. Hecht, J. Vac. Sci. Technol., 16, 328 (1979).

- 24. P. Y. Kuo, T. S. Chao, and T. F. Lei, IEEE Electron Device Lett., 25, 634 (2004).

- 25. Y. Zhang, J. Wan, K. L. Wang, and B. Y. Nguyen, IEEE Electron Device Lett., 23, 419 (2002).

- 26. S. Yamada, S. Yokoyama, and M. Koyanagi, Tech. Dig. Int. Electron Devices Meet., 1990, 859.

- 27. M. Yoshimi, M. Takahashi, T. Wada, K. Kato, S. Kambayashi, M. Kemmochi, and K. Natori, IEEE Trans. Electron Devices, 37, 2015 (1990).

- 28. A. G. Lewis, T. Y. Huang, R. H. Bruce, M. Koyanagi, A. Chiang, and I. W. Wu, Tech. Dig. - Int. Electron Devices Meet., 1988, 264.

- 29. K. P. Anish Kumar, J. K. O. Sin, C. T. Nguyen, and P. K. Ko, IEEE Trans. Electron Devices, 45, 2514 (1998).

- 30. J. Chen, F. Assaderaghi, P. K. Ko, and C. Hu, IEEE Electron Device Lett., 13, 572 (1992).

- 31. M. Chan, B. Yu, Z. J. Ma, C. T. Nguyen, C. Hu, and P. K. Ko, IEEE Trans. Electron Devices, 42, 1975 (1995). 32. H. F. Wei, J. E. Chung, N. M. Kalkhoran, and F. Namavar, IEEE Trans. Electron

- Devices, 42, 2096 (1995).

- 33. Y. Jiang, T. Y. Liow, N. Singh, L. H. Tan, G. Q. Lo, D. Chan, and D. L. Kwong, Tech. Dig. - Int. Electron Devices Meet., 2008, 869.