# CMOS voltage reference based on threshold voltage and thermal voltage

Tien-Yu Lo · Chung-Chih Hung · Mohammed Ismail

Received: 19 April 2007/Revised: 26 October 2007/Accepted: 22 May 2009/Published online: 11 June 2009 © Springer Science+Business Media, LLC 2009

**Abstract** A fully CMOS based voltage reference circuit is presented in this paper. The voltage reference circuit uses the difference between gate-to-source voltages of two MOSFETs operating in the weak-inversion region to generate the voltage with positive temperature coefficient. The reference voltage can be obtained by combining this voltage difference and the extracted threshold voltage of a saturated MOSFET which has a negative temperature coefficient. This circuit, implemented in a standard 0.35-µm CMOS process, provides a nominal reference voltage of 1.361 V at 2-V supply voltage. Experimental results show that the temperature coefficient is 36.7 ppm/°C in the range from – 20 to 100°C. It occupies 0.039 mm<sup>2</sup> of active area and dissipates 82 µW at room temperature. With a 0.5-µF load capacitor, the measured noise density at 100 Hz and 100 kHz is 3.6 and 25 nV/ $\sqrt{\text{Hz}}$ , respectively.

**Keywords** Voltage reference · Threshold voltage · Weak-inversion

T.-Y. Lo  $\cdot$  C.-C. Hung  $(\boxtimes)$

Analog Integrated Circuit Laboratory, Department of Communication Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, ROC e-mail: cchung@mail.nctu.edu.tw

T.-Y. Lo

e-mail: tienyu.lo@gmail.com

M. Ismail

Analog VLSI Laboratory, Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210, USA

e-mail: ismail@ece.osu.edu

### 1 Introduction

The high-precision voltage reference circuit is one of most important components in mixed-mode applications. A stable reference circuit provides a reliable reference voltage, and low supply voltage makes the integration with low voltage digital circuits possible. Such reference circuits should exhibit little dependence on supply voltage, process parameters, and temperature. Many previous researches used BJT devices to implement reference circuits [1–4]. However, the BJT devices implemented in standard CMOS process occupy large chip area. Moreover, some of the reported solutions using nonstandard CMOS processes require higher cost owing to extra process steps [5-9]. Thus, a novel voltage reference circuit that occupies small area in standard CMOS process would become very attractive. This paper discusses a voltage reference circuit by using MOSFETs. One part of the proposed circuit works in the weak-inversion region to provide the positive temperature coefficient current. The other part of the circuit, which works in the strong inversion region, is used to provide the negative temperature coefficient by extracting the threshold voltage. Thus, the positive and negative temperature coefficients would be summed to achieve a temperature independent reference parameter. The concept of the proposed voltage reference circuit will be illustrated and discussed in Sect. 2. Experimental results are presented in Sect. 3. Finally, Sect. 4 concludes the paper.

## 2 Proposed voltage reference circuit

2.1  $V_{\text{th}}$  versus temperature for MOS transistors in the saturation region

The concept of our circuit starts from the fact that the threshold voltage varies with temperature. According to the

literatures [10–12], the magnitude of the threshold voltage  $V_{\rm th}$  increases proportionally to the decrease of temperature. Therefore, we can model the relationship of the threshold voltage versus temperature as

$$|V_{th}(T)| = |V_{th}(T_0)| - \beta_{vth}(T - T_0) \tag{1}$$

where  $T_0$  is the reference temperature and  $\beta_{\nu th}$  is a positive constant, i.e., the absolute temperature coefficient of the threshold voltage.

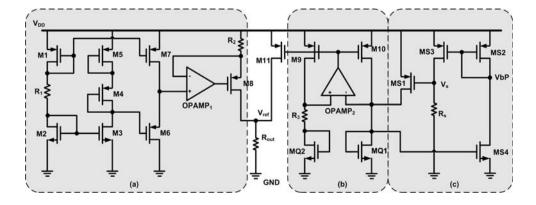

Figure 1(a) shows the negative temperature coefficient circuit, which extracts the threshold voltage of the MOS-FET working in the saturation region. In the circuit, the transistor sizes of PMOS M1, M6, and M7 are the same. The transistor sizes of PMOS M4 and M5 are also the same, and their aspect ratio is set four times larger than that of M1, M6, and M7. The transistor sizes of NMOS transistors M2 and M3 are also equal to each other. M1, M2, and  $R_1$  are used as the bias circuit to mirror the same drain current to M3, M4, M5, M6 and M7. The bulk and source terminals of transistors M4 and M6 are connected together to eliminate the body effect. From the square-law behavior of saturated MOSFETs,

$$V_{\text{SG.M4}} = V_{\text{SG.M5}} \tag{2}$$

In addition, when we neglect channel length modulation in a first approximation, we have:

$$V_{SG,M6} = 2V_{SG,M4} - |V_{th,p}| (3)$$

where  $|V_{\rm th,p}|$  is the threshold voltage of the PMOS transistor. Thus, we can obtain the output voltage  $V_{\rm outp}$  as

$$V_{\text{outp}} = V_{\text{DD}} - V_{\text{SG,M5}} - V_{\text{SG,M4}} + V_{\text{SG,M6}} \tag{4}$$

when we substitute (2) and (3) in (4), we obtain

$$V_{\text{outp}} = V_{\text{DD}} - \left| V_{\text{th,p}} \right| \tag{5}$$

Then, a unity gain buffer cascaded to the output node (source of M6) is used to provide the current with negative temperature coefficient. Thus, the output current of the circuit can be expressed as

$$I_{D8} = \frac{\left|V_{\text{th,p}}\right|}{R_2} \tag{6}$$

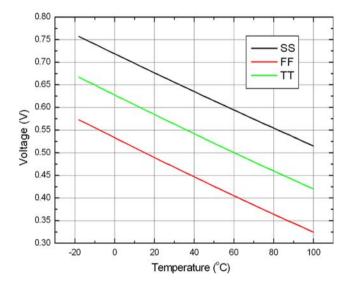

In practice, due to the temperature coefficient of  $R_2$ , the variation of  $I_{D8}$  deviates from the ideal equation. The temperature coefficient caused by resistors would be minimized and discussed in Sect. 2 D. Besides, channel length modulation would be an important issue and it would make  $I_{D8}$  a function of supply voltage, thus degrading PSRR performance of the circuit. Therefore, the device length of 6  $\mu$ m was used for transistors M1 to M7. The simulated threshold voltage  $V_{\rm th,p}$  as a function of temperature is shown in Fig. 2: the temperature coefficient of -1.87 mV/°C is obtained over the range from -20 to 100°C. We can find that the threshold voltage would have the same slope with respect to temperature as shown in (1) from slowest to fastest corner conditions. However, the variation of the threshold voltage from slowest to fastest corner condition

Fig. 2 Simulated PMOS threshold voltage versus temperature at different corner condition

Fig. 1 Proposed voltage reference circuit

is about 0.2 V, which indicates a 16% variation for typical corner condition at room temperature. This variation would affect the output reference voltage, and the solution to the variation is addressed in Sect. 2.4.

## 2.2 PTAT current generation circuit

In order to generate a current with positive temperature coefficient, the circuit shown in Fig. 1(b) has been designed. The circuit works in the weak-inversion region. The drain current in the weak-inversion region can be expressed by [13]

$$I_D = I_{D0} \left(\frac{W}{L}\right) \exp\left(\frac{V_{GS}}{nV_t}\right)$$

where  $V_t = \frac{kT}{q}$  (7)

where the term n is the subthreshold slope factor and  $I_{D0}$  is a process-dependent parameter [13]. Very large aspect ratios of MQ1 and MQ2 are chosen to guarantee weak-inversion operation by ensuring

$$\frac{W_{\rm Q1}}{L_{\rm Q1}} > \frac{\mu_p C_{\rm ox} W_{\rm 10}}{L_{\rm 10} I_{\rm D0}} e^{\frac{-V_{\rm th,n}}{nV_I}} (V_{\rm DD} - \left| V_{\rm th,p} \right|)^2 \tag{8}$$

where  $\mu_{\rm p}$  is the mobility of charge carriers of PMOS transistors,  $C_{\rm ox}$  is the gate oxide capacitance per unit area, and  $W_{10}/L_{10}$  is the aspect ratio of M10. An operational amplifier with PMOS input stage is used owing to the low input common mode voltage of the PTAT current generation circuit under weak-inversion operation. The feedback loop formed in the circuit will force the gate voltage of MQ1 to be equal to the sum of the gate voltage of MQ2 and the voltage across resistor  $R_3$ . Therefore, the PTAT current can be obtained as

$$I_{D9} = I_{D10} = \frac{nV_t(\ln k)}{R_2} \tag{9}$$

where k is the ratio between the aspect ratios of MQ1 and MQ2.

## 2.3 Startup circuit

The proposed voltage reference circuit requires a startup circuit. The start up circuit shown in Fig. 1(c) provides the initial current until the voltage reference circuit reaches a suitable operating condition [14]. When the supply voltage is turned on,  $V_{\rm S}$  voltage is equal to ground and thus turns MS1 on. The current provided by MS1 flows through MQ1 to start the operation of the voltage reference circuit and turn MS4 on, and then the current is mirrored by MS2 to MS3. The mirrored current will flow through  $R_4$  to provide voltage larger than  $V_{\rm DD}-|V_{\rm th,p}|$  to turn MS1 off. We should note that a weak startup current in the operational amplifier

would introduce significant systematic offset, and this condition will affect correct operation of the voltage reference circuit. In order to solve this problem, we need to control the operational amplifier with the same reference current used in the voltage reference circuit. Thus, this tracking mechanism of currents in the input stage of operational amplifier and the PTAT current can eliminate the systematic effect at all of the operation phase. Since the startup circuit still works under nominal operation and consumes extra power, so a larger resistance value of  $R_{\rm S}$  will be used. We should set the value of  $R_{\rm S}$  as

$$R_{S} > \frac{V_{\text{DD}} - |V_{\text{th,p}}|}{C \times D \times I_{\text{MOI}}} \tag{10}$$

where C is the current mirror ratio between the aspect ratios of MQ1 and MS4 and D is the current mirror ratio between the aspect ratios of MS2 to MS3. In addition,  $R_{\rm S}$  was built by N-WELL, which has the property of large sheet resistance so as to reduce silicon area.

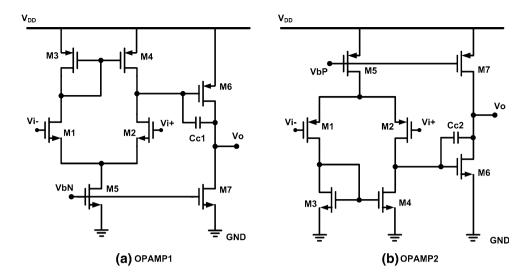

# 2.4 Circuit implementation

The complete schematic of the proposed voltage reference circuit is shown in Fig. 1, and the schematic of the OPAMPs is shown in Fig. 3. Currents proportional to positive and negative temperature coefficients are combined with current mirrors to obtain a temperature-insensitive voltage. From the circuit, the voltage reference is given by

$$V_{\text{ref}} = \left\lceil \frac{\left| V_{\text{th,p}} \right|}{R_2} + B \left( \frac{n V_t (\ln k)}{R_3} \right) \right\rceil R_{\text{out}}$$

(11)

where B is the current mirror ratio between the aspect ratios of M9 to M11. The reference voltage can be arbitrarily set to the desired value by choosing the value of Rout. The resistors  $R_2$ ,  $R_3$ ,  $R_{out}$  were fabricated by the same material, the N+ poly resistor, and thus the temperature coefficient caused by  $R_2$  and  $R_3$  could be minimized by dividing the temperature coefficient of  $R_{out}$ . Long channel devices are used for current mirrors to minimize channel length modulation. The temperature dependence of the voltage reference can be obtained by differentiating (11) with respect to temperature. Therefore, the proposed voltage reference circuit works at zero temperature coefficient operation under a first order approximation. The variation of threshold voltage under different corner conditions should be compensated. Since the output voltage is produced by combining the currents with positive and negative temperature coefficients, a simple trimming circuit composed by current mirror arrays can be used to solve this problem. Therefore, the number of the current mirrors can be designed by taking the 0.2 V voltage shift into consideration. The minimum supply voltage of the

**Fig. 3** The schematic of the OPAMPs

Table 1 Voltage reference component values

| Component    | Value        |  |

|--------------|--------------|--|

| MQ1          | 5/0.35       |  |

| MQ2          | 250/0.35     |  |

| MS1          | 1/1          |  |

| MS2          | 1/0.35       |  |

| MS3          | 50/0.35      |  |

| MS4          | 5/0.35       |  |

| M1           | 12/6         |  |

| M2           | 12/6         |  |

| M3           | 12/6         |  |

| M4           | 48/6         |  |

| M5           | 48/6         |  |

| M6           | 12/6         |  |

| M7           | 12/6         |  |

| M8           | 25/4         |  |

| M9           | 20/4         |  |

| M10          | 20/4         |  |

| M11          | 200/4        |  |

| $R_1$        | 350k         |  |

| $R_2$        | 150k         |  |

| $R_3$        | 114 <i>k</i> |  |

| $R_{\rm s}$  | 133 <i>k</i> |  |

| $R_{ m out}$ | 75k          |  |

circuit would be limited by the threshold voltage extraction circuit, which is based on the saturated MOS operation. The largest threshold voltage would be obtained under the lowest temperature, and the minimum supply voltage could be expressed as

$$V_{\rm DD,min} = 2V_{\rm th,p} + 3V_{\rm DS,Sat} \tag{12}$$

Thus, the supply voltage of the proposed voltage reference circuit can be down to 1.5 V with the considered

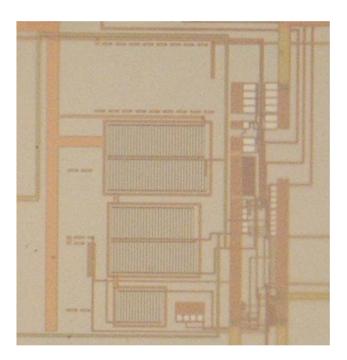

Fig. 4 Die microphotograph

0.35-µm CMOS technology. Moreover, a low-threshold-voltage process can be used to achieve a lower power supply voltage.

## 3 Experimental results

The proposed voltage reference circuit has been implemented in TSMC 0.35-µm CMOS technology. The transistor aspect ratios and resistor values are reported in Table 1. The chip micrograph, which occupies an active area of 0.039 mm<sup>2</sup>, is shown in Fig. 4. Careful layout is required to provide well matched circuits. Figure 5 shows

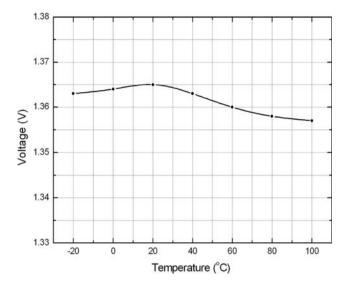

Fig. 5 Measured reference voltage versus temperature

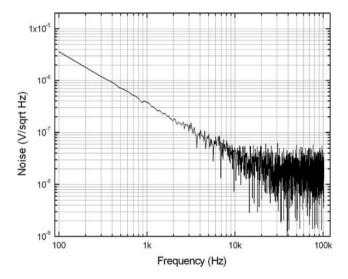

Fig. 6 Measured output noise spectral density of the proposed voltage reference circuit with 0.5  $\mu F$  loading capacitance

the measured output voltage of the proposed voltage reference circuit as a function of temperature at 2 V supply voltage. In the figure, the measured mean value of the reference voltage is 1.361 V and the measured temperature coefficient is 36.7 ppm/ $^{\circ}$ C in the range from -20 to  $100^{\circ}$ C. The current consumption of the circuit is 41 µA. The measured noise spectrum when connecting a 0.5-µF load capacitor is shown in Fig. 6. The measured noise density at 100 Hz and 100 kHz is  $3.6 \,\mu\text{V}/\sqrt{\text{Hz}}$  and  $25 \,\text{nV}/\sqrt{\text{Hz}}$ , respectively. The noise produced in the voltage reference circuit is composed by two OPAMPs, the threshold voltage circuit, and the thermal voltage circuit. The complicated circuit introduces a good temperature effect, but suffers the problem of higher noise. As loading a capacitor at the output node, the output noise features a low-pass fashion. Then, the noise corner frequency would be dependent on the output impedance and the loading capacitance. The noise can be reduced by larger loading capacitance with the drawback of longer startup time. The measured performances of the voltage reference circuit, which are composed only by MOSFETs and resistors, are summarized in Table 2.

#### 4 Conclusions

A voltage reference circuit based on CMOS technology has been presented. The threshold voltage of saturated MOS-FET devices, which exhibits a negative temperature coefficient, can be obtained from the threshold voltage extraction circuit. On the other hand, the voltage difference between two gate-to-source voltages of MOSFET devices, which exhibits a positive temperature coefficient in weak-inversion, can be obtained from the PTAT current generation circuit. Currents having opposite temperature coefficients are provided and combined to obtain a voltage reference independent of temperature variation. This is done at the minimum cost of area and power consumption. The proposed voltage reference circuit can be easily

**Table 2** Performance summary of the fabricated prototype

| Parameter                        | [11]     | [12]    | [15]  | [16]      | [17]     | [18]  | This work |

|----------------------------------|----------|---------|-------|-----------|----------|-------|-----------|

| Technology (μm CMOS)             | 0.6      | 1.2     | 0.5   | 2         | 1.5      | 0.18  | 0.35      |

| Supply voltage                   | 1.4 V    | 1.2 V   | 2.8 V | 5 V       | 3.3 V    | 0.85  | 2 V       |

| Supply current (μA)              | 9.6      | 3.6     | 8     | 36        | 89       | 2.8   | 41        |

| Reference voltage (V)            | 0.30931  | 0.2953  | 2.5   | 1.081     | 0.984    | 0.221 | 1.361     |

| Temperature coefficient (ppm/°C) | 36.9     | 119     | 360   | 92        | 57       | 271   | 36.7      |

| PSRR                             | -47 dB   | -40  dB | _     | -34.5  dB | -43.2 dB | _     | -43.5  dB |

|                                  | @ 100 Hz | @ 5 kHz |       | @ 1 kHz   | @ 1 kHz  |       | @ 10 kHz  |

| Active area (mm <sup>2</sup> )   | 0.055    | 0.23    | 0.25  | -         | 0.609    | 0.024 | 0.039     |

designed in CMOS technology and is suitable for many applications. The voltage reference circuit was fabricated in TSMC 0.35- $\mu$ m CMOS technology. Experimental results report an output voltage of 1.361 V at 2 V supply voltage. A temperature coefficient of 36.7 ppm/°C is achieved over the range of -20-100°C, with a power consumption of 82  $\mu$ W at room temperature.

**Acknowledgments** The authors would like to thank the National Chip Implementation Center of Taiwan for supporting the chip fabrication.

#### References

- Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design. New York: Oxford.

- Blauschild, R. A., Tucci, P. A., Muller, R. S., & Meyer, R. G. (1978). A new NMOS temperature-stable voltage reference. *IEEE Journal of Solid-State Circuits*, 13, 767–774.

- Giustolisi, G., Palumbo, G., Criscione, M., & Cutri, F. (2003). A low-voltage low-power voltage reference based on subthreshold MOSFETs. *IEEE Journal of Solid-State Circuits*, 38(1), 151–154.

- 4. Kuijk, L. E. (1973). A precision reference voltage source. *IEEE Journal of Solid-State Circuits*, 8, 222–226.

- Lee, I., Kim, G., & Kim, W. (1994). Exponential curvaturecompensated BiCMOS bandgap reference. *IEEE Journal of Solid-State Circuits*, 29, 1396–1403.

- Leung, K. N., & Mok, P. K. T. (2003). A CMOS voltage reference based on weighted △VGS for CMOS low-dropout linear regulators. *IEEE Journal of Solid-State Circuits*, 38(1), 146–150.

- 7. Lin, P. H., & Lin, Y. T. (2006). A simple subthreshold CMOS voltage reference circuit with channel—length modulation compensation. *IEEE Transactions on Circuits and Systems. II, Express Briefs*, 53(9), 882–885.

- Malcovati, P., Maloberti, F., Fiocchi, C., & Pruzzi, M. (2001).

Curvature—compensated BiCMOS bandgap with 1-V supply voltage. *IEEE Journal of Solid-State Circuits*, 36(7), 1076–1081.

- Meijer, G. C. M., Schmall, P. C., & van Zalinge, K. (1982). A new curvature-corrected bandgap reference. *IEEE Journal of Solid-State Circuits*, 17, 1139–1143.

- Ougey, H. J., & Gerber, B. (1980). MOS voltage reference based on polysilicon gate work function difference. *IEEE Journal of Solid-State Circuits*, 15, 264–269.

- Stair, R., Connelly, J. A., & Pulkin, M. (2000). A current mode CMOS voltage reference. In *Proceeding of Southwest Symposium* on *Mixed-Signal Design* (pp. 23–26).

- Harrison, W. T., Connelly, J. A., & Stair, R. (2001). An improved current-mode CMOS voltage reference. In *Proceeding of South*west Symposium on Mixed-Signal Design (pp. 25–27).

- 13. Razavi, B. (2001). Design of analog CMOS integrated circuit. New York: McGraw-Hill.

- Sanborn, K. E., Ma, D., & Ivanov, V.V. (2006). A sub-1 V low noise bandgap voltage reference. In *Proceeding of IEEE Custom Integrated Circuits Conference* (pp. 607–610).

- Tsividis, Y. P. (1987). Operation and modeling of the MOS transistor. New York: McGraw-Hill.

- Seo, Y. D., Nam, D., Yoon, B. J., Choi, I. H., & Kim, B. (1997).

Low-power CMOS on-chip voltage reference using MOS PTAT:

An EP approach. In Proceeding of Tenth Annual IEEE International ASIC Conference and Exhibit (pp. 316–320).

- Hoff, M. E. (1978). MOS voltage reference circuit. US Patent, 4(100), 437.

- Song, H. J., & Kim, C. K. (1993). A temperature-stabilized SOL voltage reference based on threshold voltage difference between enhancement and depletion NMOSFET's. *IEEE Journal of Solid-State Circuits*, 28, 671–677.

Tien-Yu Lo received the B.S., M.S., and Ph.D. degrees in Communication Engineering from National Chiao Tung University, Taiwan, in 2001, 2003 and 2007, respectively. Since 2008, he has been with the Analog Circuit Design Division, MediaTek Inc., Taiwan, as an analog IC designer. His research interests include analog and mixed-signal circuit design with particular focus on the topic of continuous-time filters and analog-to-digital converters.

Chung-Chih Hung was born in Tainan, Taiwan. He received the B.S. degree in Electrical Engineering from National Taiwan University, Taipei, Taiwan, in 1989, and the M.S. and Ph.D. degrees in Electrical Engineering from The Ohio State University, Columbus, Ohio in 1993 and 1997, respectively. From 1989 to 1991, he served in the Taiwan Marine Corps as a Communication officer. From 1997 to 2003, he worked for several IC design companies in

San Jose, CA and San Diego, CA, where he held analog circuit design manager and director positions. Since 2003, he has been an Assistant Professor of Communication Engineering at National Chiao Tung University, Hsinchu, Taiwan. His current interests include the design of analog and mixed-signal integrated circuits for communication and high-speed applications.

Mohammed Ismail has over 25 years experience of R&D in the fields of analog, RF and mixed-signal integrated circuits. He has held several positions in both industry and academia and has served as a corporate consultant to nearly 30 companies in the US, Europe and the Far East. He is Professor of Electrical and Computer Engineering and the Founding Director of the Analog VLSI Lab at The Ohio State University and of the

RaMSiS Group at KTH. His current interest lies in research involving digitally programmable/configurable integrated CMOS radios with focus on low voltage/low power "first-pass" solutions for cognitive radios, 3G and 4G wireless handhelds. He publishes intensively in this area and has been awarded 11 patents. He has co-edited and coauthored several books including a text on Analog VLSI Signal and Information Processing, (McGraw Hill). His last book (2007) is entitled Radio design in Nanometer Technologies, Springer. He advised the thesis work of 45 Ph.D. students and of over 85 MS students. He co-founded ANACAD-Egypt (now part of Mentor Graphics, Inc.) and First-pass Technologies Inc., a developer of CMOS radio and mixed-signal IPs for handheld wireless applications. Dr. Ismail has been the recipient of several awards including the US National Science Foundation Presidential Young Investigator Award,

the US Semiconductor Research Corp Inventor Recognition Awards in 1992 and 1993, The College of Engineering Lumley Research Award in 1992, 1997, 2002 and 2007 and a Fulbright/Nokia fellowship Award in 1995. He is the founder of the International Journal of Analog Integrated Circuits and Signal Processing, Springer and serves as the Journal's Editor-In-Chief. He has served as Associate Editor for many IEEE Transactions, is on the International Advisory Boards of several journals and was on the Board of Governors of the IEEE Circuits and Systems Society. He is the founder of ICECS, the CAS flagship Conference for Region 8. He obtained his BS and MS degrees in Electronics and communications from Cairo University, Egypt and the Ph.D. degree in Electrical Engineering from the University of Manitoba, Canada. He is a Fellow of IEEE.