## Flexible Fullerene Field-Effect Transistors Fabricated Through Solution Processing

By Chao-Feng Sung, Dhananjay Kekuda, Li Fen Chu, Yuh-Zheng Lee, Fang-Chung Chen, Meng-Chyi Wu, and Chih-Wei Chu\*

Recent research into organic semiconductors for organic thin-film transistors (OTFTs) - as alternatives to amorphous silicon-based systems - has yielded improved synthetic and fabrication techniques for devices with great potential for the use in consumable electronic applications. [1-3] To realize the advantages of organic semiconductors in practical applications, OTFTs fabricated through solution processing (spin-coating, casting, or printing) on flexible substrates are strongly desired. Although many groups have developed OTFTs incorporating soluble small-molecule or polymer semiconductors, the number of available hole-transporting materials overwhelms the number of electron-transporting materials. [4-6] Preparing efficient organic integrated circuits at low cost requires soluble hole- and electron-transporting materials that ideally exhibit comparable electrical performance. At present, the development of highperformance n-channel OTFTs remains a challenge, especially when using attractive fabrication processes (e.g., solution processing).

Since 1995, when  $C_{60}$  was first suggested as a promising material for n-channel thin-film transistors, <sup>[7]</sup> the electronic properties of these devices have improved dramatically, achieving field-effect mobilities of the order of  $1\,\mathrm{cm^2~V^{-1}\,s^{-1}}$ . Unfortunately,  $C_{60}$  thin films have been prepared most commonly using complicated and time-consuming thermal evaporation processes. Recently,  $C_{60}$  derivatives have gained much attention for the use in TFTs and bulk heterojunction solar cells because of their reasonable carrier mobilities and high solubilities in organic solvents,  $^{[11-13]}$  which makes device fabrication feasible through simple, low-cost spin-coating and printing processes. Despite these advantages, films prepared

from soluble  $C_{60}$  derivatives, such as the fullerene derivative [6,6]-phenyl- $C_{61}$ -butyric acid methyl ester (PCBM), have much lower mobilities than those obtained through thermal evaporation of  $C_{60}$  thin films. In addition, the complicated syntheses of soluble  $C_{60}$  derivatives are expensive.<sup>[14]</sup>

$C_{60}$  is reasonably soluble in some organic solvents. [15,16] Therefore, in addition to vacuum sublimation processing, it is likely that  $C_{60}$  films could be formed through solution processing. Moreover, serious electron trapping has been observed recently on hydroxyl gate-dielectric surfaces, resulting in an instability of the corresponding n-channel transistors, which leads to a poor device performance under ambient conditions. [17–19] Additionally, the relatively high electron affinity of  $C_{60}$  ( $\sim$ 4.5 eV) means that it readily forms low-resistance contacts with metals. [20] In this study, we present  $C_{60}$ -based TFTs on rigid and flexible substrates through solution processing. Although we obtained  $C_{60}$  in the amorphous phase after solution processing, the resulting transistors exhibit high performance, with field-effect mobilities as high as  $0.21\,\mathrm{cm}^2\,\mathrm{V}^{-1}\,\mathrm{s}^{-1}$  in the saturation regime.

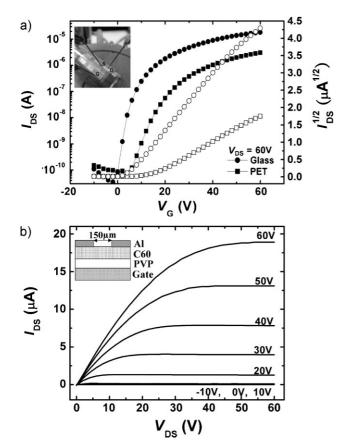

Figure 1a and b displays typical transfer- and output-curve characteristics, respectively, of the  $C_{60}$ -based TFTs on a rigid indium tin oxide (ITO) glass substrate with Al source/drain (S/D) electrodes. The devices exhibit typical n-channel characteristics with a good linear/saturation behavior. We have observed a strong field-effect modulation of the channel conductance, with ON/OFF current ratios ( $I_{\rm on}/I_{\rm off}$ ) as high as  $5\times 10^5$  (measured for gate voltages ( $V_{\rm G}$ ) from -10 to +60 V). The field-effect mobility ( $\mu$ ) and the threshold voltage ( $V_{\rm T}$ ) were extracted from the measured transfer curve by comparing it with the standard current–voltage equation for a transistor in the saturation regime:

$$I_{\rm DS} = (WC_{\rm i}/2L)\mu(V_{\rm G} - V_{\rm T})^2 \tag{1}$$

where  $I_{\rm DS}$  is the saturated drain current.<sup>[21]</sup> The transistors display mobilities as high as  $0.21\,{\rm cm^2\,V^{-1}\,s^{-1}}$  and a value of  $V_{\rm T}$  of 0.7 V. Although the mobilities in our devices are slightly lower than those of OTFTs prepared through vacuum deposition, our devices perform much better than those prepared through solution processing.<sup>[22–24]</sup> There are many factors that influence the value of  $V_{\rm T}$ , such as bulk traps (unintentional doping), interfacial states (organic/dielectric interfacial traps), and the crystallinity of the materials.  $C_{60}$  was purchased from Materials Technologies Research at >99.5% purity; however, because impurities (e.g., voids) are also formed during the fabrication process, unintentional doping is inevitable, leading to a lower

[\*] Dr. C.-W. Chu, C.-F. Sung, F.-C. Chen National Chao Tung University Hsinchu 30013 (Taiwan)

E-mail: gchu@gate.sinica.edu.tw

Dr. C.-W. Chu, Dr. D. Kekuda

Research Center for Applied Sciences

Academia Sinica, Nankang, Taipei 11529 (Taiwan)

Y.-Z. Lee

Display Technology Center

Industrial Technology Research Institute

Hsinchu 30013 (Taiwan)

Prof. M.-C. Wu, L. F. Chu

Department of Electrical Engineering

Nation Tsing Hua University

Hsinchu 30013 (Taiwan)

DOI: 10.1002/adma.200901215

**Figure 1.** a) Transfer curves of  $C_{60}$  devices (at a saturated drain voltage  $(V_{DS})$  of 60 V) prepared on flexible and rigid substrates obtained with real-time measurements; inset: photograph of a flexible device. b) Output characteristics of  $C_{60}$  devices grown on ITO glass; inset: device structure.

value of  $V_T$ , as had been observed by Dinelli et al. [25] The presence of organic-dielectric interfacial traps also plays an important role in affecting the value of  $V_T$ . SiO<sub>2</sub> is traditionally employed as the gate dielectric in OTFTs, even though protonation of the siloxyl groups on the SiO<sub>2</sub> surface can generate some OH groups at the interface between SiO2 and the organic semiconductor layer that can behave as electron traps. [17] Several approaches have been examined to overcome such issues, including the use of self-assembled monolayers<sup>[26]</sup> or polymers<sup>[19,27]</sup> at SiO<sub>2</sub>-organic semiconductor interfaces. In this study, we use crosslinked poly-4-vinylphenol (PVP), rather than SiO<sub>2</sub>, as the gate dielectric to reduce the number of interfacial traps. Therefore, in our system, the low value of  $V_T$  is most likely related to unintentional doping and a lower number of organic-dielectric interfacial traps. The subthreshold slope (SS) is also strongly dependent on the interfacial trap density - it increases upon increasing the interfacial trap density. From the transfer curve, an SS of 1.4 V decade<sup>-1</sup> is extracted, which is not close to the theoretical minimum of  $58 \,\mathrm{meV} \,\mathrm{decade}^{-1} \,[kT/q \,\ln(10)]$  (k is the Boltzmann constant, T the absolute temperature, and q the magnitude of electrical charge), presumably because of the presence of the OH

groups of PVP that were not utilized in the crosslinking process. Hence, we anticipate that the value of SS is reduced if we use an OH-free gate dielectric.

For comparison, Figure 1a presents the transfer curves of devices prepared on rigid and flexible substrates. The mobilities in the flexible devices are approximately one order of magnitude lower than those of the devices prepared on rigid glass substrates. For the flexible devices, the transfer curves provide values of  $\mu$ , SS, and  $V_{\rm T}$  of 0.057 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, 11 V, and 4.1 V decade<sup>-1</sup> respectively, thus, the threshold voltages of the flexible devices are higher than those of conventional devices formed on rigid substrates.<sup>[28]</sup> A greater substrate roughness is likely to cause a greater density of trap states in the gate dielectric and at the dielectric-semiconductor interface; such phenomena may explain the observed decrease in mobility and the increase in the threshold voltage. [29] The poorer characteristics of the flexible devices might also result from the high-temperature processing used to crosslink the polymer dielectrics, during which the flexible substrate may have undergone tensile/compressive stress. From a practical point of view, the need remains to prepare higher-performance organic transistors. Lowering the driving voltage and increasing the operating speed for solutionprocessable C<sub>60</sub> TFTs can be achieved by incorporating high-k dielectrics<sup>[30]</sup> or reducing the thickness of the dielectric.<sup>[31,32]</sup> These approaches open up further applications for such devices. Overall, the devices prepared on flexible substrates exhibited good field-effect modulation with an ON/OFF ratio greater than 104, sufficient for some practical applications.<sup>[33]</sup>

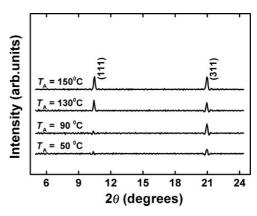

Field-effect mobility is the key device parameter affecting the performance of TFTs. We found that the characteristics of TFTs, fabricated using  $C_{60}$  semiconductors, are dependent on the annealing temperature for the conversion from amorphous to crystalline  $C_{60}$ . Figure 2 displays the extracted plot of the mobilities of the devices prepared on both conventional glass and flexible substrates as a function of the annealing temperature. The trends in the variation of the mobility with respect to the temperature are similar for the devices prepared on the rigid and flexible substrates, indicating the compatibility of the flexible devices. [34] In each case, the mobility reaches a maximum value at 90 °C. The decrease in mobility at annealing temperatures higher than 90 °C might be due to a change in the crystalline structure or an increase in grain size. The X-ray diffraction (XRD) pattern of a  $C_{60}$  thin film displays strong peaks that correspond to the (111)

Figure 2. Mobilities of OTFTs featuring  $C_{60}$  semiconductor films annealed at temperatures between 25 and 170  $^{\circ}$ C.

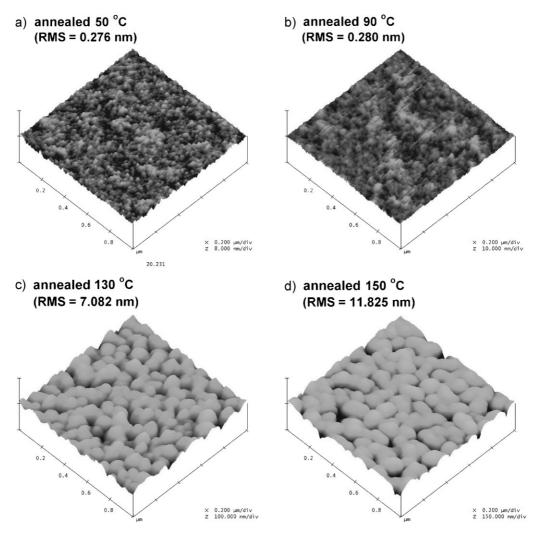

Figure 3. AFM images of C<sub>60</sub> thin films on ITO glass/PVP substrates annealed at a) 50, b) 90, c) 130, and d) 150 °C. RMS stands for root mean square.

and (311) reflections of the face-centered cubic (fcc) phase of C<sub>60</sub>, revealing the crystalline nature of the sample. Although crystallinity generally favors an enhancement in mobility, the opposite trend is observed in our case, presumably because of pronounced grain-boundary effects, which act as carrier scattering centers across the drain-source interface. Because such scattering seriously affects transport across the drain-source interface, the mobility decreases at high temperatures.

Figure 3a-d displays atomic force microscopy (AFM) images of the  $C_{60}$  films annealed at temperatures ranging from 50 to 150 °C. The surface morphologies of the films annealed at 50 and 90 °C are very smooth. In contrast, the faceted crystalline C<sub>60</sub> film obtained after annealing at 130 °C exhibits a very rough surface morphology. The average grain size increases upon increasing the annealing temperature but the mobility is not obviously related to the annealing temperature. The AFM images reveal that high temperatures support the crystallization of the C<sub>60</sub> molecules. Figure 4 presents XRD patterns of the C<sub>60</sub> thin films after thermal treatment at 50–150  $^{\circ}$ C. The C<sub>60</sub> films subjected to annealing at 50 and 90 °C possess amorphous features, whereas those annealed at 130 and 150 °C exhibit the strong diffraction

peaks of crystalline C<sub>60</sub>. Crystallization phenomena dominate the behavior of transistors at high temperatures and, thus, determine the performance of the devices. The correlation between the grain size and the mobility is an interesting phenomenon. For planar

Figure 4. XRD patterns of C<sub>60</sub> thin films grown on ITO/PVP substrates after annealing at 50, 90, 130, and 150  $^{\circ}$ C ( $T_{A}$ : annealing temperature).

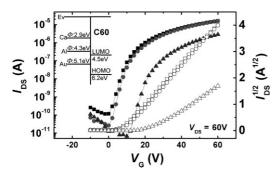

**Figure 5.** Typical transfer characteristics of  $C_{60}$  OTFTs featuring Au (triangles), Al (circles), and Ca (squares) as S/D electrodes at a constant drain voltage of  $60\,V$ .

molecules (e.g., pentacene) the mobility should increase with an increase in grain size. However, for spherical molecules (e.g.,  $C_{60}$ ), even when the grain size is small, nearest-neighbor hopping could lead to carrier transport, thus, our observed high mobility originates from the molecular assembly of the spherical molecules. When the annealing temperature is higher than 90 °C, pronounced grain-boundary effects become apparent (see the AFM images), thereby resulting in a marginal decrease in mobility. Grain-boundary effects in spherical molecules such as  $C_{60}$  are interesting phenomena that require further investigation. Our results suggest that the grain size has a less pronounced effect on the mobility of the device.

To study the effect of the work function of the metal electrodes on the performance of the C<sub>60</sub>-based OTFTs, three metals (Ca, Al, and Au), possessing different work functions (5.1, 4.3, and 2.9 eV, respectively), have been used as the S/D electrodes. The Ca electrodes were covered by an Al layer to protect them from oxidation. The energy level of the lowest occupied molecular orbital (LUMO) for C<sub>60</sub> is 4.5 eV. [35,36] Figure 5 displays the transfer characteristics of C60-based TFTs incorporating the various metals as the S/D electrodes. The values of  $\mu$  and  $V_{\rm T}$  are  $0.22\,{\rm cm}^2\,{\rm V}^{-1}\,{\rm s}^{-1}$  and  $-3\,{\rm V}$ , respectively, for the device incorporating Ca/Al S/D electrodes, 0.21 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and 0.7 V, respectively, for that featuring Al electrodes,  $0.035\,\text{cm}^2\,\dot{V}^{-1}\,\text{s}^{-1}$  and 22 V, respectively, for that featuring Au electrodes. The maximum currents increase as the work function of the metal electrodes decreases. For devices grown under similar conditions and having a top-contact structure, the variation in mobility should result mainly from the value of the contact resistance between the organic semiconductor and the metal electrodes. The expected Schottky-barrier height at the interface between Au electrodes and  $C_{60}$  is  $0.6\,\mathrm{eV}$ , with virtually no barrier for Ca and Al electrodes. We anticipated that the performance of C<sub>60</sub>-based TFTs would be affected by a large contact resistance between the electrodes and the C<sub>60</sub> channel, resulting in lower values of mobility in the case of highwork-function metals (e.g., Au). The mobility increases upon decreasing the work function of the electrode and we have observed a low-resistive ohmic characteristic of the Ca and Al contacts lacking a Schottky barrier. Because the work functions of Ca and Al are lower than the LUMO energy level of C<sub>60</sub>, no energy barrier exists for carrier injection across the metalsemiconductor contact. As a result, the mobility is more than five times higher than that obtained with the Au electrodes. To

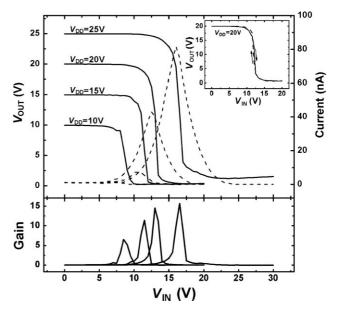

**Figure 6.** Output voltage (top, solid line), current (top, dashed line), and small-signal gain (bottom, solid line) plotted with respect to the input voltage for supply voltages between 10 and 25 V. The inverter featured a small-signal gain of 15. Inset: Transfer characteristics of the inverter in forward and back scans at a supply voltage of 20 V.

study the atmospheric stability of the devices, they were exposed to air for 30 min and then returned to the glove box. The mobility of these devices decreased by  $\sim$ 50%; however, when the devices are maintained either in vacuum or under an inert atmosphere, their mobilities are stable for several weeks. Surface passivation might be one way to minimize the degradation of the mobilities of devices in air.

When preparing high-performance organic complementary inverters with reasonable gain, it is highly desirable that both pand n-type transistors have high and comparable device performances. Figure 6 displays the voltage transfer characteristics of an organic complementary inverter incorporating pentacene and C<sub>60</sub> as p- and n-type semiconductors, respectively. The performance of the pentacene-based TFT was tested separately; its mobility is  $0.8 \, \text{cm}^2 \, \text{V}^{-1} \, \text{s}^{-1}$ . At a small input voltage ( $V_{IN}$ ), the p- and n-type transistors are in ON and OFF states, respectively, as a result, the device functions as an inverter. Consequently, the output voltage ( $V_{OUT}$ ) is almost equal to the supply voltage  $(V_{\rm DD})$  when the latter is varied between 10 and 25 V. When the value of  $V_{\rm IN}$  exceeds the threshold voltage of the inverters, the p-type transistor turns off and the n-type transistor turns on. As a result, the value of  $V_{OUT}$  switches to become almost equal to zero. The small-signal gain, defined as the maximum value of the slope of the transfer curve, is 15. The small-signal gain increases as the value of  $V_{\rm DD}$  augments. The corresponding increase in current, when the inverter is switched eventually, leads to power consumption, thus, when the inverter is switched, the power consumption deteriorates with an increase in  $V_{\rm DD}$ . Most importantly, the hysteresis effect in the inverter circuit is negligible for a supply voltage of 20 V (inset of Fig. 6). Further enhancement to the performance of our complementary circuits might be achieved by incorporating a high- $\bar{k}$  dielectric<sup>[37,38]</sup> or reducing the thickness of the dielectric. [20,39]

In summary, we have fabricated  $C_{60}$ -based TFTs through solution processing. XRD and AFM analyses have revealed that the solution-processed films possess an amorphous  $C_{60}$  phase. Crystalline  $C_{60}$  was not essential to achieve the highest field-effect mobility. We have also fabricated  $C_{60}$ -based TFTs incorporating S/D electrodes of three different materials (Ca, Al, and Au). The highest mobility  $(0.21\,\mathrm{cm^2\,V^{-1}\,s^{-1}})$  occurs in the  $C_{60}$  field-effect transistors featuring Ca and Al electrodes and is approximately one order of magnitude higher than that obtained using Au electrodes. Our results demonstrate that complementary circuits can be fabricated using solution-processed small-molecule organic semiconductors.

## Experimental

Devices were fabricated on ITO-coated glass substrates ( $< 10 \Omega \text{ sq}^{-1} \text{ sheet}$ resistance) and ITO-coated poly(ethylene terephthalate) (PEN) substrates  $(8-12 \Omega \text{ sq}^{-1} \text{ sheet resistance})$ . The ITO on the glass substrate was used as the gate electrode. After routine solvent cleaning, the substrates were treated with UV-ozone for 15 min. The cleaned ITO substrates were then covered with a 680-nm-thick polymer dielectric insulator, prepared by spin-coating a solution of PVP (11wt%) and poly(melamineco-formaldehyde) (4 wt%) in propyleneglycol monomethyl ether acetate (PGMEA). The substrate was then prebaked at 100  $^{\circ}\text{C}$  for 5 min, followed by baking at 200 °C for 20 min, to crosslink the polymer. The resulting capacitance per unit area of the film  $(C_i)$  is 5.47 nF cm<sup>-2</sup>. For deposition of the active layer, a 1 wt% C<sub>60</sub> solution was prepared in trichlorobenzene. The active layers of C<sub>60</sub> (Materials Technologies Research, >99.5%) thin films were spin-coated over the crosslinked PVP-covered ITO glass substrates under a N2 atmosphere inside a glove box. To induce crystallization in the films, prior to S/D electrode deposition, the devices were thermally annealed on a hot plate at various temperatures (50-150 °C) for 10 min. Finally, Al was thermally evaporated onto the C<sub>60</sub> film through a shadow mask to form the S/D electrodes. To study the effect of the electrode materials on the performance of the devices, other metal electrodes (Ca and Au) were also deposited. For the construction of complementary circuits, as p-type partners to the solution-processed C<sub>60</sub> devices, pentacene TFTs were fabricated through vacuum evaporation. A schematic cross section of the top-contact OTFTs is presented in the inset of Figure 1a; the channel length is  $150\,\mu m$  and the width is  $2\,mm$ . The electrical performance of the devices was measured under a N2 atmosphere inside a glove box using a Keithley 4200 semiconductor parameter analyzer and an HP 4980A Precision LCR meter.

## Acknowledgements

We thank the National Science Council, Taiwan (96-2221-E-001-017-MY2) and Academia Sinica, Taiwan for financial support.

Received: April 9, 2009 Published online: August 10, 2009

- [1] C. D. Dimitrakopoulos, P. R. L. Malenfant, Adv. Mater. 2002, 14, 99.

- [2] H. Sirringhaus, Adv. Mater. 2005, 17, 2411.

- [3] A. Facchetti, Mater. Today 2007, 10, 28.

- [4] B. Yoo, B. A. Jones, D. Basu, D. Fine, T. Jung, S. Mohapatra, A. Facchetti, K. Dimmler, M. R. Wasielewski, T. J. Marks, A. Dodabalapur, Adv. Mater. 2007, 19, 4028.

- [5] Y. L. Wu, P. Liu, B. S. Ong, Appl. Phys. Lett. 2006, 89, 013505.

- [6] P. T. Herwig, K. Mullen, Adv. Mater. 1999, 11, 480.

- [7] R. Haddon, A. Perel, R. Morris, T. Palstra, A. Hebard, R. Fleming, Appl. Phys. Lett. 1995, 67, 121.

- [8] T. D. Anthopoulos, B. Singh, N. Marjanovic, N. S. Sariciftci, A. M. Ramil, H. Sitter, M. Colle, D. M. de Leeuw, Appl. Phys. Lett. 2006, 89, 213504.

- [9] X. H. Zhang, B. Kippelen, J. Appl. Phys. 2008, 104, 104504.

- [10] X. H. Zhang, B. Kippelen, Appl. Phys. Lett. 2008, 93, 133305.

- [11] T. Morita, W. Takashima, K. Kaneto, Jpn. J. Appl. Phys. 2007, 46, L256.

- [12] C. Waldauf, P. Schilinsky, M. Perisutti, J. Hauch, C. J. Brabec, Adv. Mater. 2003, 15, 2084.

- [13] G. Yu, J. Gao, J. Hummelen, F. Wudl, A. Heeger, Science 1995, 270, 1789.

- [14] M. Chikamatsu, S. Nagamatsu, Y. Yoshida, K. Saito, K. Yase, K. Kikuchi, Appl. Phys. Lett. 2005, 87, 203504.

- [15] R. Ruoff, D. Tse, R. Malhotra, D. Lorents, J. Phys. Chem. 1993, 97, 3379.

- [16] N. Sivaraman, R. Dhamodaran, I. Kaliappan, T. Srinivasan, P. Rao, C. Mathews, J. Org. Chem. 1992, 57, 6077.

- [17] L. L. Chua, J. Zaumseil, J. F. Chang, E. C. W. Ou, P. K. H. Ho, H. Sirringhaus, R. H. Friend, *Nature* **2005**, *434*, 194.

- [18] J. Jang, J. W. Kim, N. Park, J. J. Kim, Org. Electron. 2008, 9, 481.

- [19] F. C. Chen, C. H. Liao, Appl. Phys. Lett. 2008, 93, 103310.

- [20] C. W. Chu, V. Shrotriya, G. Li, Y. Yang, Appl. Phys. Lett. 2006, 88, 153504.

- [21] S. M. Sze, Physics of Semiconductors, Wiley, New York 1981.

- [22] H. Yan, Y. Zheng, R. Blache, C. Newman, S. F. Lu, J. Woerle, A. Facchetti, Adv. Mater. 2008, 20, 3393.

- [23] Z. M. Wang, C. Kim, A. Facchetti, T. J. Marks, J. Am. Chem. Soc. 2007, 129, 13362

- [24] M. Chikamatsu, A. Itakura, Y. Yoshida, R. Azumi, K. Yase, Chem. Mater. 2008, 20, 7365.

- [25] F. Dinelli, M. Murgia, F. Biscarini, D. M. De Leeuw, Synth. Met. 2004, 146, 373.

- [26] M. M. Ling, P. Erk, M. Gomez, M. Koenemann, J. Locklin, Z. Bao, Adν. Mater. 2007, 19, 1123.

- [27] Th. B. Singh, S. Günes, N. Marjanovi, N. S. Sariciftci, J. Appl. Phys. 2005, 97, 14508.

- [28] J. Zhang, C. M. Li, M. B. Chan-Park, Q. Zhou, Y. Gan, F. Qin, B. Ong, T. Chen, Appl. Phys. Lett. 2007, 90, 243502.

- [29] H. Klauk, M. Halik, U. Zschieschang, F. Eder, G. Schmid, C. Dehm, Appl. Phys. Lett. 2003, 82, 4175.

- [30] L. Torsi, A. Dodabalapur, L. J. Rothberg, A. W. P. Fung, H. E. Katz, *Science* 1996, 272, 1462.

- [31] H. Klauk, U. Zschieschang, J. Pflaum, M. Halik, Nature 2007, 445, 745.

- [32] A. Facchetti, M. H. Yoon, T. J. Marks, Adv. Mater. 2005, 17, 1705.

- [33] J. Jang, Mater. Today 2006, 9, 46.

- [34] R. T. Weitz, K. Amsharov, U. Zschieschang, E. B. Villas, D. K. Goswami, M. Burghard, H. Dosch, M. Jansen, K. Kern, H. Klauk, J. Am. Chem. Soc. 2008. 130. 4637.

- [35] K. Kim, D. L. Carrolla, Appl. Phys. Lett. 2005, 87, 203113.

- [36] Z. R. Hong, Z. H. Huang, X. T. Zeng, Chem. Phys. Lett. 2006, 425, 62.

- [37] M. Kitamura, Y. Arakawa, Appl. Phys. Lett. 2007, 91, 053505.

- [38] X. H. Zhang, W. J. Potscavage, S. Choi, B. Kippelen, Appl. Phys. Lett. 2009, 94, 043312.

- [39] M. H. Yoon, H. Yan, A. Facchetti, T. J. Marks, J. Am. Chem. Soc. 2005, 127, 10388.