## Interfacial layer dependence on device property of high- TiLaO Ge/Si N -type metaloxide-semiconductor capacitors at small equivalent-oxide thickness

W. B. Chen and Albert Chin

Citation: Applied Physics Letters **95**, 212105 (2009); doi: 10.1063/1.3265947 View online: http://dx.doi.org/10.1063/1.3265947 View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/95/21?ver=pdfcov Published by the AIP Publishing

Articles you may be interested in Effects of fluorine incorporation and forming gas annealing on high- k gated germanium metal-oxidesemiconductor with Ge O 2 surface passivation Appl. Phys. Lett. **93**, 073504 (2008); 10.1063/1.2966367

Photocurrent measurements for oxide charge characterization of high- dielectric metal oxide semiconductor capacitors

J. Appl. Phys. 103, 054101 (2008); 10.1063/1.2841059

Reliability properties of metal-oxide-semiconductor capacitors using HfO 2 high- dielectric Appl. Phys. Lett. **91**, 123507 (2007); 10.1063/1.2786588

Molecular-beam epitaxy growth of device-compatible GaAs on silicon substrates with thin ( 80 nm ) Si 1 x Ge x step-graded buffer layers for high- III-V metal-oxide-semiconductor field effect transistor applications J. Vac. Sci. Technol. B **25**, 1098 (2007); 10.1116/1.2713119

Unpinned metal gate/high- GaAs capacitors: Fabrication and characterization Appl. Phys. Lett. **89**, 043501 (2006); 10.1063/1.2234837

This article is copyrighted as indicated in the article. Reuse of AIP content is subject to the terms at: http://scitation.aip.org/termsconditions. Downloaded to IP: 140.113.38.11 On: Wed, 30 Apr 2014 14:45:42

## Interfacial layer dependence on device property of high-κ TiLaO Ge/Si *N*-type metal-oxide-semiconductor capacitors at small equivalent-oxide thickness

W. B. Chen and Albert Chin<sup>a)</sup>

Department of Electronics Engineering, National Chiao-Tung University, Hsinchu 30010, Taiwan

(Received 14 October 2009; accepted 28 October 2009; published online 24 November 2009)

We have investigated the device property dependence of high dielectric-constant (high- $\kappa$ ) TiLaO epitaxial-Ge/Si *n*-type metal-oxide-semiconductor (*n*-MOS) capacitors on different GeO<sub>2</sub> and SiO<sub>2</sub> interfacial layers. Large capacitance density of 3.3  $\mu$ F/cm<sup>2</sup>, small equivalent-oxide thickness (EOT) of 0.81 nm and small *C*-*V* hysteresis of 19 mV are obtained simultaneously for MOS capacitor using ultrathin SiO<sub>2</sub> interfacial layer, while the device with ultrathin interfacial GeO<sub>2</sub> shows inferior performance of larger 1.1 nm EOT and poor *C*-*V* hysteresis of 93 mV. From cross-sectional transmission electron microscopy, secondary ion mass spectroscopy, and x-ray photoelectron spectroscopy analysis, the degraded device performance using GeO<sub>2</sub> interfacial layer is due to the severe Ge outdiffusion, thinned interfacial GeO<sub>2</sub> and thicker gate dielectric after 550 °C rapid-thermal anneal. © 2009 American Institute of Physics. [doi:10.1063/1.3265947]

Germanium (Ge) has attracted much attention for metaloxide-semiconductor field-effect transistor (MOSFET)<sup>1-14</sup> application due to both higher electron and hole mobility than Silicon (Si). However, the difficult challenges are the high leakage current of small energy band gap  $(E_G)$  Ge and the poor interface property with high dielectric-constant ( $\kappa$ ) material. To lower the leakage current, we pioneered the defect free Ge-on-insulator (GOI or GeOI) (Ref. 1) structure, and the leakage current decreases with decreasing the Ge body thickness.<sup>5</sup> Nevertheless, the degraded interface property is still a tough challenge especially for the Ge n-type MOSFET  $(n-MOSFET)^{6-12}$  at a small equivalent oxide thickness (EOT). The interface property is highly dependent on high- $\kappa$  dielectrics, where Al<sub>2</sub>O<sub>3</sub> (Ref. 1) and La<sub>2</sub>O<sub>3</sub> (Refs. 8 and 11) show lower interface trap density than  $HfO_2$ . This is related to the different metal-oxygen-Ge and defect formations<sup>11</sup> after a rapid-thermal anneal (RTA). To improve the interface, several passivation methods have been proposed such as plasma nitridation,<sup>4,8</sup> NH<sub>3</sub> treatment, SiH<sub>4</sub> annealing, and interfacial GeO<sub>2</sub> layer<sup>8–10,12–14</sup> at larger EOT, but small EOT less than 1 nm is needed for 32 nm node and beyond.

In this letter, we have applied the ultrathin GeO<sub>2</sub> and SiO<sub>2</sub> interfacial layers<sup>15</sup> into high- $\kappa$  TiLaO (Ref. 16) epitaxial-Ge/Si *n*-type MOS (*n*-MOS) capacitors, where the ultrathin body Ge of 5 nm is directly grown on Si to reach low leakage current. The TiLaO gate dielectric has the merits of unique negative flatband voltage ( $V_{\rm fb}$ ) from La<sub>2</sub>O<sub>3</sub> (Ref. 17) and the much higher  $\kappa$  by adding TiO<sub>2</sub>.<sup>16</sup> Such negative  $V_{\rm fb}$  is needed for low threshold voltage ( $V_t$ ) MOSFET. The control TaN/TiLaO/Ge/Si *n*-MOS capacitor without the ultrathin GeO<sub>2</sub> or SiO<sub>2</sub> interfacial layer showed poor EOT and large  $V_{\rm fb}$  degradation after a 550 °C RTA, which is required to activate ion-implanted source-drain in the MOSFET. Such degradations are related to interface reaction and oxygen vacancy formation<sup>18,19</sup>

ultrathin GeO<sub>2</sub> or SiO<sub>2</sub> (Ref. 15) interfacial layer. However, the high- $\kappa$  TiLaO Ge/Si *n*-MOS capacitor with interfacial GeO<sub>2</sub> showed much poorer capacitance-voltage (*C*-*V*) hysteresis than that using SiO<sub>2</sub> at a smaller EOT less than 1 nm. This is due to the Ge outdiffusion and intermixing of high- $\kappa$ TiLaO/GeO<sub>2</sub> as observed by cross-sectional transmission electron microscopy (TEM) and secondary ion mass spectroscopy (SIMS).

After standard cleaning, a 200 nm undoped Si buffer, 5 nm Ge, and 1.5 nm Si capping layer were epitaxial grown on 6 in. p-type Si substrate (10  $\Omega$  cm) by ultrahigh-vacuum chemical-vapor deposition. After removing the native oxide of Si-capping layer, various thick GeO<sub>2</sub> or SiO<sub>2</sub> and 5 nm high- $\kappa$  TiLaO (Ref. 16) were deposited by physical vapor deposition and followed by postdeposition annealing at 400 °C in oxygen ambient to improve gate dielectric quality. Here the ultrathin Si capping is used to prevent Ge oxidation and process loss, where no interfacial Si was found by crosssectional TEM after device process. Then a 50 nm TaN was deposited and patterned to form the metal gate. The formed gate stack was applied by a 550 °C RTA that is needed for Ge n-MOSFET fabrication. Finally, Aluminum was deposited on wafer backside to form the MOS capacitors. For comparison, control device without GeO<sub>2</sub> or SiO<sub>2</sub> interfacial layer was also made. The fabricated gate stack was examined by SIMS, TEM, x-ray photoelectron spectroscopy (XPS), and C-V measurements to investigate the physical, chemical bonding, and electrical properties, respectively.

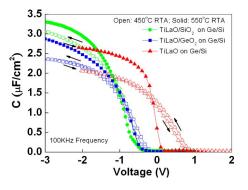

Figure 1 shows the measured *C-V* characteristics of high- $\kappa$  TiLaO Ge/Si *n*-MOS capacitors with or without the interfacial GeO<sub>2</sub> or SiO<sub>2</sub> layer. For device without the inserted GeO<sub>2</sub> or SiO<sub>2</sub> layer, both the capacitance density and  $V_{\rm fb}$  were severely degraded. Such  $V_{\rm fb}$  roll-off at high temperature was previously reported due to the interface reaction between high- $\kappa$  and semiconductor.<sup>19</sup> In contrast, the capacitor with GeO<sub>2</sub> or SiO<sub>2</sub> layer shows much improved  $V_{\rm fb}$  rolloff even after a 550 °C RTA. Besides, the needed negative  $V_{\rm fb}$  of -0.48 V is obtained and important for low  $V_t$  Ge *n*-MOSFET. However, the device with GeO<sub>2</sub> interfacial layer

<sup>&</sup>lt;sup>a)</sup>Also at Nano-Electronics Consortium of Taiwan, Taiwan, R.O.C. Electronic mail: albert\_achin@hotmail.com.

FIG. 1. (Color online) C-V characteristics of TaN/TiLaO Ge/Si n-MOS capacitors with or without the inserted GeO<sub>2</sub> and SiO<sub>2</sub> interfacial layer and after 450 or 550 °C RTA. The device size is  $100 \times 100 \ \mu m^2$ .

shows poorer C-V hysteresis of 93 mV at 1.1 nm EOT than the much improved 19 mV hysteresis at smaller 0.81 nm EOT for device using SiO<sub>2</sub> interfacial layer, by taking account of quantum-mechanical effect with parameters of Ge.' The C-V hysteresis and negative  $V_{\rm fb}$  value are among the best reported data for Ge *n*-MOS capacitors at the smallest EOT and after a 550 °C RTA,  $^{1-14}$  to our best knowledge.

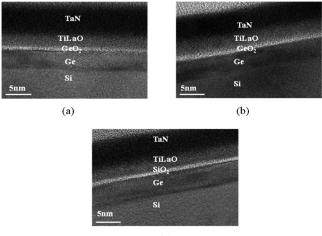

We have used TEM to study the better electrical performance for device using interfacial  $SiO_2$  layer. Figures 2(a) and 2(b) show the TEM images of TaN/TiLaO/GeO<sub>2</sub>/Ge/Si n-MOS structure before and after a 550 °C RTA. Sharp GeO<sub>2</sub> interfacial layer of 0.76 nm thickness was found for as-deposited sample but becomes blurred after the 550 °C RTA. The high- $\kappa$  layer is also thicker after the 550 °C RTA, where intermixing of high- $\kappa$  TiLaO and GeO<sub>2</sub> is observed. The thicker high- $\kappa$  layer explains the lower capacitance density after a 550 °C RTA. In strong contrast, sharp SiO<sub>2</sub> interface shown in Fig. 2(c) is still preserved even after the 550  $^\circ C$  RTA.

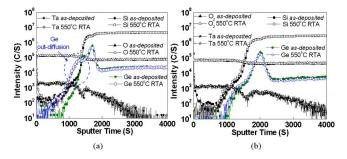

We have further used SIMS to study the large difference for devices with different interfacial GeO<sub>2</sub> and SiO<sub>2</sub>. Figures 3(a) and 3(b) show the measured SIMS profiles of TaN/ TiLaO on Ge/Si structure with interfacial GeO<sub>2</sub> and SiO<sub>2</sub> layers, respectively. Severe Ge outdiffusion was found for device structure with interfacial GeO<sub>2</sub> layer after a 550 °C RTA, while much improved Ge outdiffusion was achieved

FIG. 3. (Color online) SIMS profile of TaN/TiLaO Ge/Si n-MOS structure with inserted (a) GeO2 and (b) SiO2 interfacial layer before and after 550 °C RTA.

using ultrathin SiO<sub>2</sub> interfacial layer even at a smaller 0.81 nm EOT.

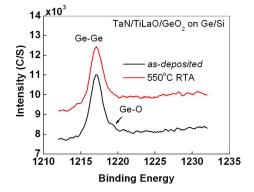

The degraded interface property with ultrathin interfacial  $GeO_2$  was also examined by XPS. Figure 4 shows the Ge  $2p^3$ XPS spectra of TiLaO/GeO<sub>2</sub>/Ge/Si n-MOS structure before and after the 550 °C RTA. The as-deposited sample shows a strong Ge peak at 1217.4 eV, and a small higher energy side peak is attributed to Ge–O bonds of  $\text{GeO}_2$ .<sup>20</sup> However, this Ge-O peak becomes much weaker for the sample after the 550 °C RTA. This is consistent with the largely thinned GeO<sub>2</sub> and intermixed TiLaO/GeO<sub>2</sub> interface found from cross-sectional TEM and the large Ge outdiffusion measured by SIMS. The thinner interfacial GeO<sub>2</sub> after the high temperature 550 °C RTA may be related to the measured reaction at 758–589 K,<sup>21</sup>

$$GeO_{2(s)} + Ge_{(s)} \rightarrow 2GeO_{(g)}.$$

(1)

In contrast, the interface reaction between ultrathin  $SiO_2$ layer and Ge is unfavorable due to the much higher bond enthalpy of SiO<sub>2</sub> (800 kJ/mol) than GeO<sub>2</sub> (659 kJ/mol).<sup>22</sup>

In conclusion, we have studied the high- $\kappa$  TiLaO on Ge/Si MOS structure with GeO<sub>2</sub> and SiO<sub>2</sub> interfacial layers. Low EOT of 0.81 nm, small C-V hysteresis of 19 mV and needed negative  $V_{\rm fb}$  are obtained using ultrathin SiO<sub>2</sub> interfacial layer. The device with ultrathin interfacial GeO2 shows inferior device performance of larger EOT and poor C-Vhysteresis, which is due to the severe Ge outdiffusion through GeO<sub>2</sub> from SIMS profile, thicker gate dielectric from TEM observation and thinned interfacial GeO2 after a 550 °C RTA from TEM and XPS analysis.

(c)

FIG. 2. Cross-sectional TEM images of TaN/TiLaO/GeO2/Ge/Si n-MOS capacitors (a) before and (b) after 550 °C RTA. (c) This a TaN/TiLaO/SiO2/Ge/Si n-MOS capacitors after 550 CRTAD content is subjectructure before and after 550 CRTAD org/terms conditions. Downloaded to IP:

This work was supported in part by National Nano Project NSC of Taiwan under Contract No. 97-2120-M-009-008.

- <sup>1</sup>C. H. Huang, M. Y. Yang, A. Chin, W. J. Chen, C. X. Zhu, B. J. Cho, M.-F. Li, and D. L. Kwong, *Symposium on VLSI Technology Digest* (IEEE, New York, 2003), p. 119.

- <sup>2</sup>W. P. Bai, N. Lu, J. Liu, A. Ramirez, D. L. Kwong, D. Wristers, A. Ritenour, L. Lee, and D. Antoniadis, *Symposium on VLSI Technology Digest* (IEEE, New York, 2003), p.121.

- <sup>3</sup>K. Kita, K. Kyuno, and A. Toriumi, Appl. Phys. Lett. 85, 52 (2004).

- <sup>4</sup>T. Maeda, T. Yasuda, M. Nishizawa, N. Miyata, Y. Morita, and S. Takagi, Appl. Phys. Lett. 85, 3181 (2004).

- <sup>5</sup>A. Chin, H. L. Kao, Y. Y. Tseng, D. S. Yu, C. C. Chen, S. P. McAlister, and C. C. Chi, *Proceedings of the ESSDERC* (IEEE, France, 2005), p. 285.

<sup>6</sup>V. V. Afanas'ev, Y. G. Fedorenko, and A. Stesmans, Appl. Phys. Lett. 87, 032107 (2005).

- <sup>7</sup>Q. Zhang, J. Huang, N. Wu, G. Chen, M. H. Hong, L. K. Bera, and C. X. Zhu, IEEE Electron Device Lett. **27**, 728 (2006).

- <sup>8</sup>T. Takahashi, T. Nishimura, L. Chen, S. Sakata, K. Kita, and A. Toriumi Tech. Dig. - Int. Electron Devices Meet. **2007**, 697.

- <sup>9</sup>D. Kuzum, A. J. Pethe, T. Krishnamohan, Y. Oshima, Y. Sun, P. Jim McVittie, P. A. Pianetta, P. C. McIntyre, and K. C. Saraswat, Tech. Dig. Int. Electron Devices Meet. **2007**, 723.

- <sup>10</sup>A. Delabie, F. Bellenger, M. Houssa, T. Conard, P. C. McIntyre, S. Van Elshocht, M. Caymax, M. Heyns, and M. Meuris, Appl. Phys. Lett. **91**,

082904 (2007).

- <sup>11</sup>G. Mavrou, P. Tsipas, A. Sotiropoulos, S. Galata, Y. Panayiotatos, A. Dimoulas, C. Marchior, and J. Fompeyrine, Appl. Phys. Lett. **93**, 212904 (2008).

- <sup>12</sup>J. H. Park, M. Tada, D. Kuzum, P. Kapur, H. Y. Yu, H.-S. P. Wong, and K. C. Saraswat, Tech. Dig. Int. Electron Devices Meet. **2008**, 389.

- <sup>13</sup>Y. Nakakita, R. Nakane, T. Sasada, H. Matsubara, M. Takenaka, and S. Takagi Tech. Dig. Int. Electron Devices Meet. **2008**, 877.

- <sup>14</sup>S. Swaminathan, Y. Oshima, M. A. Kelly, and P. C. McIntyre, Appl. Phys. Lett. **95**, 032907 (2009).

- <sup>15</sup>M. F. Chang, P. T. Lee, and A. Chin, IEEE Electron Device Lett. **30**, 861 (2009).

- <sup>16</sup>C. H. Cheng, H. C. Pan, H. J. Yang, C. N. Hsiao, C. P. Chou, S. P. McAlister, and A. Chin, IEEE Electron Device Lett. 28, 1095 (2007).

- <sup>17</sup>Y. H. Wu, M. Y. Yang, A. Chin, and W. J. Chen, IEEE Electron Device Lett. **21**, 341 (2000).

- <sup>18</sup>J. Robertson, O. Sharia, and A. A. Demkov, Appl. Phys. Lett. **91**, 132912 (2007).

- <sup>19</sup>C. F. Cheng, C. H. Wu, N. C. Su, S. J. Wang, S. P. McAlister, and A. Chin, Tech. Dig. - Int. Electron Devices Meet. **2007**, 333.

- <sup>20</sup>NIST x-ray photoelectron spectroscopy database, NIST standard reference database 20, version 3.5 (web version), http://srdata.nist.gov/xps.

- <sup>21</sup>W. L. Jolly and W. M. Latimer, J. Am. Chem. Soc. 74, 5757 (1952).

- <sup>22</sup>D. S. Yu, A. Chin, C. H. Wu, M.-F. Li, C. Zhu, S. J. Wang, W. J. Yoo, B. F. Hung, and S. P. McAlister, Tech. Dig. Int. Electron Devices Meet. **2005**, 649.