# 第一章 緒論

## 1-1 研究動機

台灣之半導體代工在全球居於領先地位，但也吸引如美、日、韓與中國大陸半導體業者的激烈競爭，晶圓廠要有高良率與低成本的競爭優勢，方能在產業中保持領先地位，如何以現有設備滿足多樣之客戶製程變化，也考驗晶圓廠的經營實力，本文中以半導體製程薄膜化學氣相沉積中之電漿輔助化學氣相沉積(Plasma Enhance Chemical Vapor Deposition)為研究對象，討論隨著製程演進而發生之新問題，如何能在不花錢更新設備，找出新方法去克服製程瓶頸。

論文之主題是 PECVD 沉積薄膜因 Wafer Arcing 造成沉積薄膜厚度不均而導致 IC 良率下降。CVD 製程中會遇到許多問題如微粒 Particle，薄膜厚度之一致性，沉積薄膜應力 Stress 等問題，會選定 Wafer Arcing 為主題是因為電漿中之 Arcing 無法預知何時發生，無法 real time 監控，以製程流程為例說明，當 PECVD 沉積之二氧化矽薄膜  $\text{SiO}_2$ ，正常應該沉積  $19000\text{\AA}$  之厚度( $1\text{\AA}=10^{-4}\mu\text{m}=10^{-10}\text{m}$ )但因 wafer Arcing 造成沉積厚度局部只有  $9000\text{\AA}$ ，而 PECVD 後接著 CMP (Chemical Mechanical Polishing)平坦化製程，因局部厚度不均，造成 CMP 研磨過拋，將底層之 Metal line 研磨造成金屬污染引起晶圓報廢。

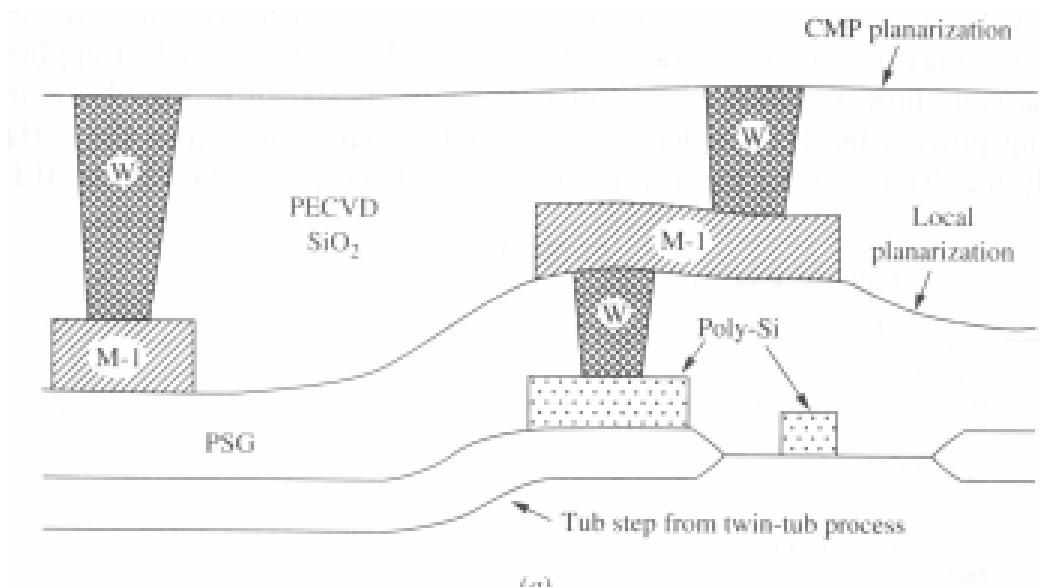

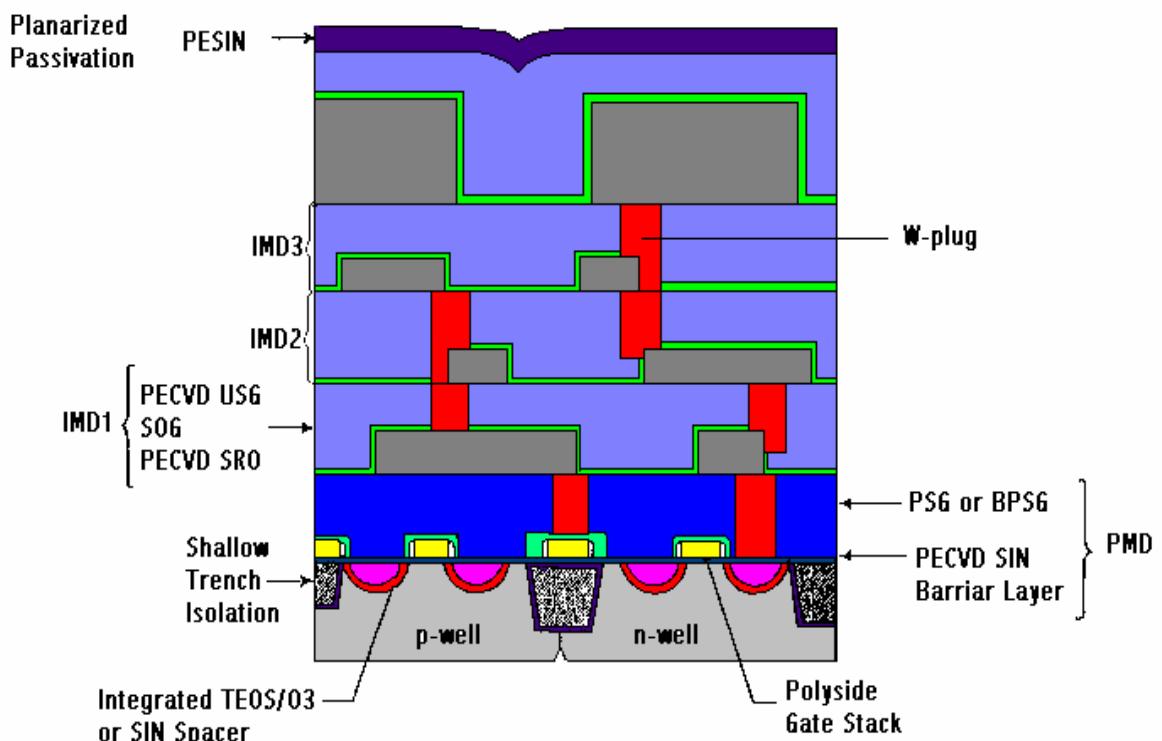

圖 1.1 晶片製程剖面圖

晶圓廠一天對 PECVD 機台執行一~二次測機動作，藉以驗證機台所沉積出之薄膜品質合乎製程規範要求，Particle 、 Stress 、薄膜厚度均勻性、阻抗值等特性條件一般來說較穩定，藉由固定時間之測機動作可發現異常之變化，但 wafer Arcing 發生之頻率不固定，一個 Lot 25 片晶圓也許只有三片晶圓發生 Arcing 異常，下個 Lot 未發生，隔了 3 個 Lot 又發生，如此不穩定的條件造成報廢難以預防，能夠找出改善方法，對提升良率及降低成本都有很大之幫助。

## 1-2. 研究目的

隨著科技發展，IC 運用在生活中的範圍也愈來愈廣，晶圓代工之客戶及製程種類也變多，隨著製程技術進步，原本購置昂貴之半導體生產設備，也面臨多樣式生產變化的挑戰，以本文中的 Wafer Arcing 為例，此種設備原廠設計主要用來生產沉積薄膜厚度小於  $3000\text{\AA}$  之製程，但因應製程改變，晶圓沉積二氧化矽厚度之變化已從小於  $3000\text{\AA}$  變成  $19000\text{\AA}$ ，沉積時間愈長，clean 時間也須愈長，電漿中離子撞擊作用對腔體中之零件傷害也隨時間成正比，原本在較薄之薄膜不會發生之問題，改變製程後，wafer Arcing 造成產品報廢的問題就出現了，但昂貴之設備也不能因此就不生產，因此有了各種實驗之改變，目的就是找出最有效及成本最低的方法，改善 wafer Arcing 之問題。

## 1-3. 本文架構

本論文主旨研究 wafer Arcing 之成因，及實驗找出 wafer Arcing 之方法，主要架構分為五章，第一章緒論 介紹研究動機及目的。第二章 研究背景介紹 PECVD 製程原理，電漿原理、CVD Clean endpoint 介紹、電漿中 RF Vdc Vpp 代表意義及 Vdc 可應用在預知 Wafer Arcing 發生的方法，Wafer Arcing 簡介。

第三章討論實驗方法，介紹 ASM PECVD 實驗設備，厚度量測設備及實驗方法。第四章討論實驗結果，提出各項實驗條件改變對 Arcing 發生頻率的影響及找出對應的解決方法。第五章為 結論與未來之改善方向。

## 第二章 研究背景

### 2-1 PECVD 原理

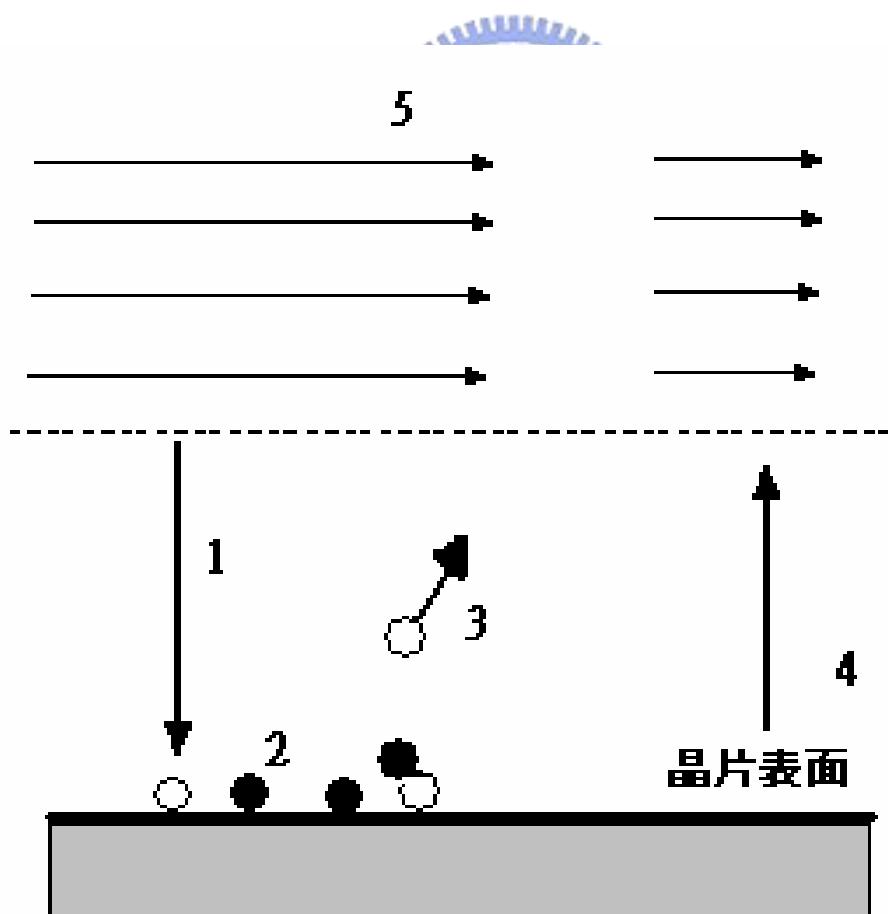

CVD 反應通常分為五個主要步驟，(1)反應氣體擴散通過介面邊界層，主要是藉著主氣流(Main Stream )與晶片表面間的濃度差，以擴散(Diffusion)的方式，由主氣流經過介面層，到達晶片的表面。.(2)反應物到達晶片表面，失去部分動能而被晶片表面所吸附進而沉積於晶片表面。(3)反應物在晶片表面獲得晶片表面提供的能量化學反應產生，在沉積過程中，反應生成物會在晶片表面移動，最後沉積完成。(4)當沉積反應發生後，未反應之反應物及部分生成物會從 wafer 表面獲得能量而脫離晶片表面，並通過介面邊界層。(5)部分生成物與未反應物回到主氣流裡，藉由 Pump 抽走 [1]。

圖 2.1 化學氣相沉積 CVD 簡圖

本篇論文所討論之 CVD 為電漿加強式 CVD (Plasma Enhanced CVD) PECVD，主要沉積 Film 為  $\text{SiO}_2$ , 反應材料有  $\text{SiH}_4$  及 TEOS(Tetra Ethyl-Ortho-Silicate) [ 2 ]

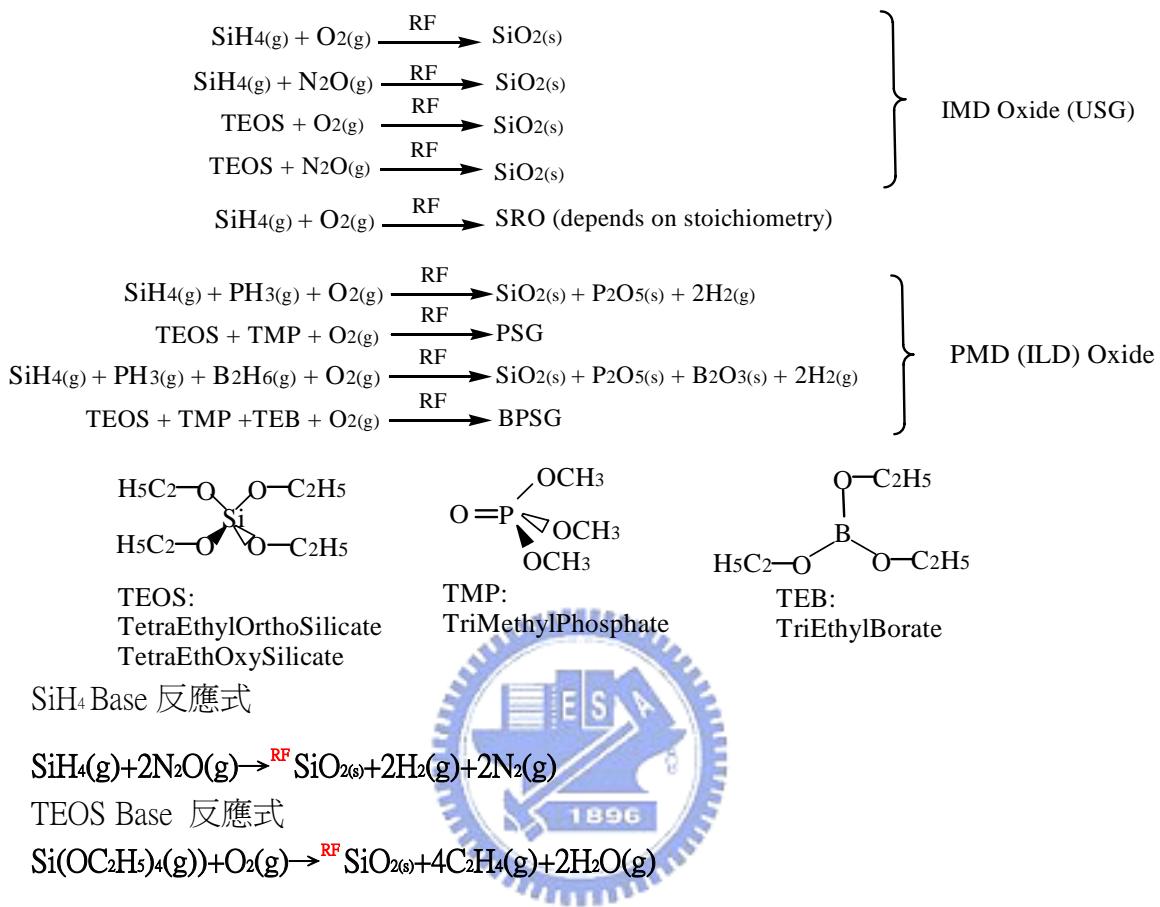

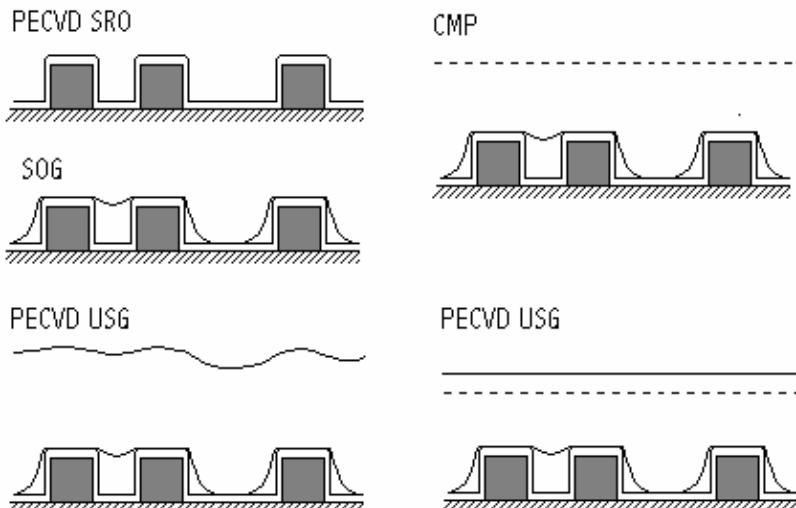

### Process of Dielectric Film in IMD

PECVD/SOG(O3-TEOS)/PECVD/CMP/PECVD

圖 2.2 PECVD 製程流程

## Cross section Map

圖 2.3 製程剖面圖

## PECVD 電漿系統

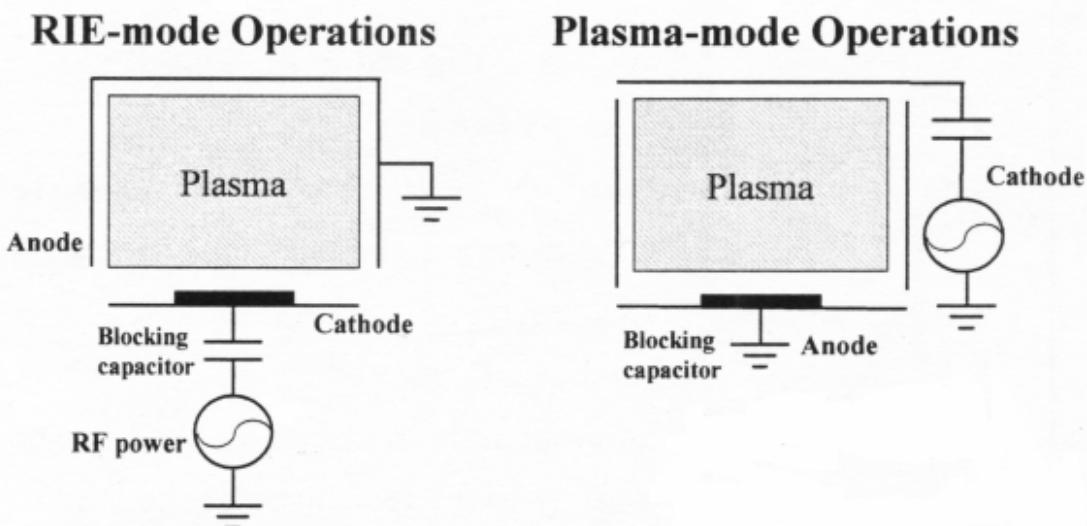

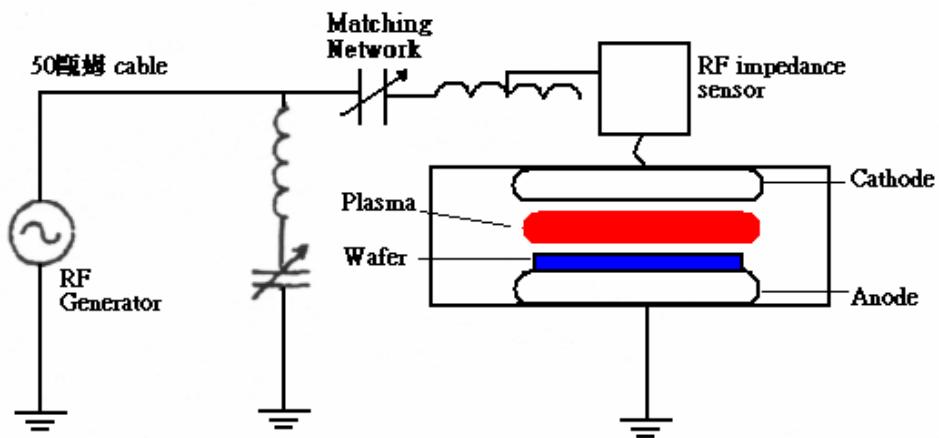

以 Capacitive Discharges mode plasma 使用在 PECVD Plasma 最常見, 13.56MHZ RF 在 Cathode 端輸入 Power 建立電漿, 晶圓擺放在 Anode 端, 若將蝕刻 Etch 之 RIE 相比如下圖。

圖 2.4 RIE 與 PECVD 腔體比較

表 2.1 不同製程之二氧化矽薄膜特性比較圖〔3〕

| Deposition                  | Plasma                                                                | Plasma                                      | APCVD                            | LPCVD                             | LPCVD                         | Thermal                                                                  |

|-----------------------------|-----------------------------------------------------------------------|---------------------------------------------|----------------------------------|-----------------------------------|-------------------------------|--------------------------------------------------------------------------|

|                             | SiH <sub>4</sub> + O <sub>2</sub>                                     | TEOS + O <sub>2</sub>                       | TEOS + O <sub>3</sub>            | SiH <sub>4</sub> + O <sub>2</sub> | TEOS + O <sub>2</sub>         |                                                                          |

| Temperature(℃)              | 250                                                                   | 400                                         | 400                              | 450                               | 700                           | 1000                                                                     |

| Step coverage               | Nonconformal                                                          | conformal                                   | Isotropic Flow                   | Nonconformal                      | conformal                     | conformal                                                                |

| Dielectric constant         | 4.9                                                                   | —                                           | 4.3                              | 4                                 | —                             | 3.9                                                                      |

| Refractive Index            | 1.45                                                                  | 1.45                                        | —                                | 1.44                              | 1.46                          | 1.46                                                                     |

| Density(g/cm <sup>3</sup> ) | 2.3                                                                   | —                                           | 1.2                              | 2.1                               | 2.2                           | 2                                                                        |

| Etch rate nm/min            |                                                                       |                                             | —                                |                                   |                               |                                                                          |

| (100:1 H <sub>2</sub> O:HF) | 40                                                                    | 164                                         |                                  | 6                                 | 3                             | 2.5                                                                      |

| Comments                    | High density<br>Cusp problem<br>and<br>microparticle<br>contamination | High density<br>Limited surface<br>coverage | Excellent<br>surface<br>coverage | High density<br>Low density       | High density<br>High moisture | Excellent quality<br>High<br>temperature<br>High<br>moisture<br>affinity |

## 2-2 電漿在半導體上的應用

電漿製程被廣泛的使用在半導體製程上，在 IC 製造上圖案化蝕刻電漿蝕刻，電漿增強式化學氣相沉積(PECVD)和高密度電漿化學氣相沉積(HDP-CVD)廣泛的用於介電質的沉積上。物理氣相沉積(PVD)製程中也會使用電漿，在製程中利用離子轟擊金屬靶的表面，使之濺鍍沉積在晶片表面上，腔體清潔(Chamber clean) 使用電漿解離蝕刻氣體，如 C<sub>2</sub>F<sub>6</sub>, C<sub>3</sub>F<sub>8</sub> or NF<sub>3</sub> 對腔體作化學反應蝕刻及離子撞擊(Ion Bombardment)之物理性蝕刻，達到清潔腔體之目的。

半導體製程大量使用電漿製程，因為電漿可以提供易於控制之能量型式，以符合半導體製程趨於微小化的需求。

- 一. 電漿並不是經由加熱提供所需的能量，可以在較低溫下(>400°C)進行反應。

- 二. 電場方向受到精確的控制，受電場加速的離子或自由基在撞擊晶片時的方向與能量也可以被控制。

- 三. 電漿蝕刻相對於濕蝕刻，可以提供較少的反應材料來獲取較高的能量。

在 CVD 製程中使用電漿有下列的優點：

- 一. 在較低的溫度下可達到高沉積速率

- 二. 利用離子轟擊來控制沉積薄膜的應力

- 三. 利用以氟離子為主的電漿對腔體作清潔

- 四. 高密度電漿源具有優異的間隙填充能力

## 2-2-1 高密度電漿的發展與原理

電漿是由中性原子或分子，負電(電子)和正電(離子)所構成，且是一種區域性的電解氣體粒子(Local ionized gas)，可以用直流或交流電源產生.交流式的 RF 電漿，電容耦合型(Capacitively couple plasma)電漿，以 RF 高頻電源兩端輸出端加諸於兩金屬電極.RF 的頻率是產生在 MHZ 之範圍，置於低壓狀態下，粒子中的電子與質子，得到同步且相反方向的加速作用而產生電離子，這種加諸於氣體分子的高頻能量，使得電離子帶有相當高的化學能，可產生化學的分解或合成反應。

電漿中有兩種碰撞，彈性碰撞和非彈性碰撞，彈性碰撞較常發生，但由於在彈性碰撞過程中，碰撞分子間並沒有能量交換，因此並不重要，許多非彈性碰撞的種類會同時在電漿中發生電子和中性分子間、中性分子和離子、離子和離子、電子和離子等之間的碰撞，電漿中任何想像得到的碰撞都有可能發生。

### The chemistry of PECVD

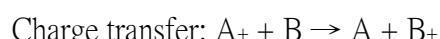

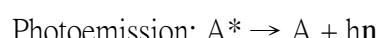

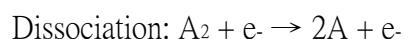

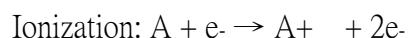

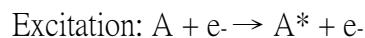

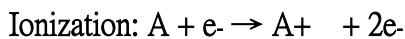

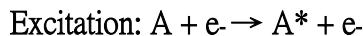

where A,  $A_2$  and B are reactants,  $e^-$  is an electron,  $A^*$  is reactant A in an excited state, and  $A^+$ ,  $A^-$ , and  $B^+$  are ions of A and B [ 4 ]

半導體的電漿而言，有三種碰撞是最重要的：

### 離子化碰撞

### 激發碰撞

### 分解碰撞

**離子化碰撞 Ionization:** 當電子與一個原子或分子相碰撞時，它會將部份的能量傳遞至受到原子核或分子核所束縛的軌道電子上，如果軌道電子獲的能量足以脫離原子核的束縛，它就會變成自由電子。

### 激發碰撞 Excitation:

有時軌道電子無法從撞擊電子中獲得足夠的能量來逃離原子核的束縛，然而如果碰撞能夠傳遞足夠的能量而使軌道電子躍升到能量更高的軌道層時，這個過程就稱之為激發 Excitation。激發狀態既不穩定而且短暫，在激發態軌道的電子無法在此能量較高的軌道中層中停留太久，它會調回最低的能階或基態，這個過程叫做 relaxation，激發原子或分子會迅速的鬆弛到原來的基態，並且以光子的型態把它從電子撞擊中所獲得的多餘能量釋放出來，造成電漿特有的輝光放電(glow discharge)現象。

### 分解碰撞 Dissociation:

當電子和分子碰撞時，如果因撞擊而傳遞到分子的能量會比分子的鍵結能量要高時，那就能打破化學鍵並且產生自由基(Free radicals)，自由基是至少帶有一個不成對電子的一種分子碎片，因此並不穩定。自由基在化學上是非常活潑的，因為它們有一種很強的傾向去搶奪其他原子或分子的電子以形成穩定的分子，自由基能夠促進蝕刻和 CVD 反應室的化學反應，在電漿中經由分解碰撞過程所產生的自由基能有效的提高化學反應速率，增進沉積速率。

## AR 電漿之物理特性表

| 化學反應                                                | 反應速率( $m^3/s$ )                                                                      | Energy shield<br>(eV) |

|-----------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------|

| 解離反應<br>$Ar + e^- \rightarrow Ar^+ + 2e^-$          | $K_{iz} = 1.23 * 10^{-13} * e^{-18.68/T_e}$                                          | $i_z = 15.76$         |

| 激發反應<br>$Ar + e^- \rightarrow Ar^* + 2e^-$          | $K_{ex} = 2.2 * 10^{-14} * e^{-12.4/T_e}$                                            | $i_z = 11.55$         |

| 彈性碰撞<br>$Ar + e^- \rightarrow Ar + e^- + 6 * T_e^4$ | $K_{el} = 10^{-15} * (0.514 + 5.51 * T_e + 22.9 * T_e^2 - 6.42 * T_e^3 + 6 * T_e^4)$ | $eI = 3m_e/m_i * T_e$ |

| 名稱                     | 物理量                           |

|------------------------|-------------------------------|

| 波茲曼常數( $K_B$ )         | $1.38 * 10^{-23}$ (焦耳/K)      |

| 磁導率( $\mu_0$ )         | $4 * 10^{-7}$ (H/m)           |

| 真空介電常數( $\epsilon_0$ ) | $8.8542 * 10^{-12}$           |

| 電子重量( $m_e$ )          | $9.1 * 10^{-31}$ (Kg)         |

| Ar 級子重量( $m_i$ )       | $6.64451 * 10^{-26}$ (Kg)     |

| 電子伏特(e)                | $1.622 * 10^{-19}$ (焦耳)       |

| 電子平均自由徑( $\lambda_e$ ) | $0.01 / (330 * P) (m)$ P:腔體壓力 |

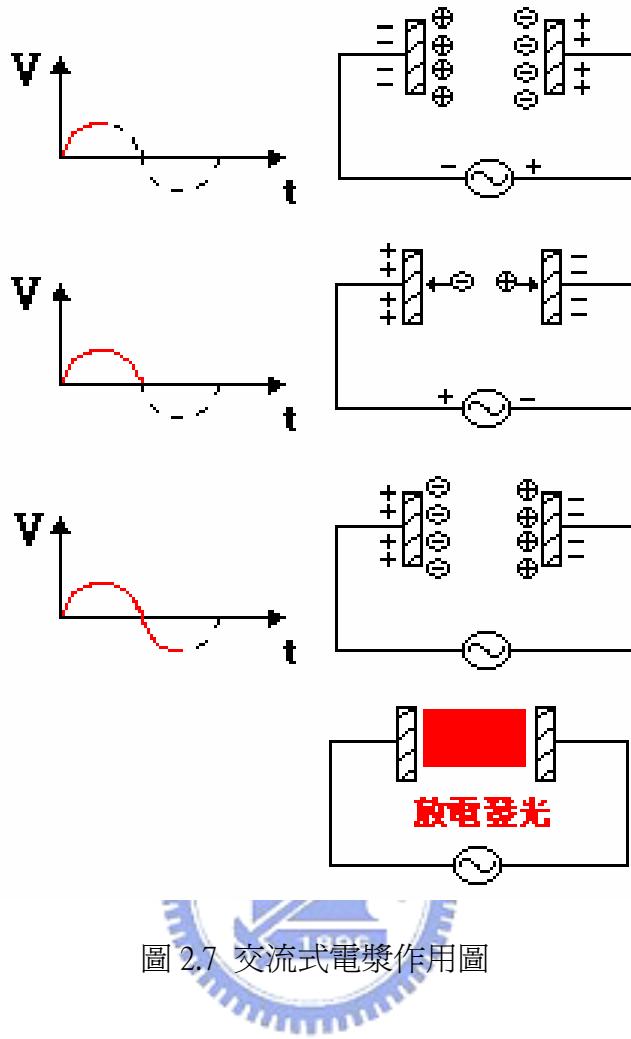

## 2-2-2 交流式電漿

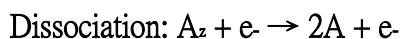

DC 電漿的應用範圍受限於電極的材料，如果電極的材質是非導體時，電極板上所吸收的電荷將無法被排除，當所累積的電荷達飽和時，帶電荷粒子往電極移動的淨流動便終止。

圖 2.5 直流式電漿簡圖

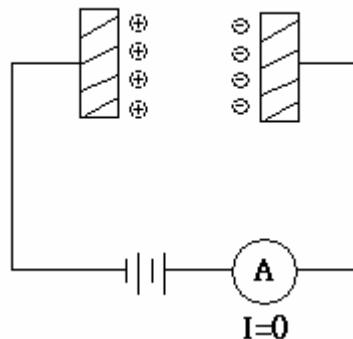

交流式電漿(AC Plasma)，利用交流式電極的切換，來避免電荷在電極板上累積，在 AC 電壓加之於電漿產生器的兩個電極的瞬間，陰極在左邊且陽極在右邊，反應室內帶正電荷的離子便開始往左邊的電極移動，直到板面的電荷密度達飽和為止。

當所施加的 AC 電壓轉相(Phase)，使左邊的電極成為陽極且右邊為陰極時，帶負電荷的電子往左邊移動。

圖 2.6 交流式電漿簡圖

假如我們開始增加 AC 切換的頻率，而且頻率大到切換的間隔時間，不足以讓帶電荷粒子將各電極板板面所能承受的電荷容量加以飽和時，雖然電極板的材質為非導體，在較高的 AC 頻率下，電漿裏的電極將隨時處於非飽和的狀態，使主要的粒子撞擊反應得以進行，電漿得以產生並維持。

圖 2.7 交流式電漿作用圖

維持 AC 電漿所需要的最低頻率，約在 100MHz，因為離子的質量遠高於電子，AC 頻率對離子的影響也就比電子還來得大。頻率愈高，離子在電場所獲至的能量或其運動速度，也就愈少且愈慢。

假如再增加 AC 電漿的切換頻率，離子的運動將受到影響，假如所使用的頻率夠高，且高到電場的轉換已無法有效的對離子作加速度時，離子便不再因陽陰極左右的切換而改變其運動的方向和動能，此時的 AC 頻率，稱之為離子過度頻率(Ion Transition Frequency)這個頻率約在 1~3MHz，目前最常使用為 13.56MHz。

當電漿的切換頻率到達這個水準時，電漿內電子獲得能量的來源是利用電子在 RF 切換下的振盪(Oscillation)，來獲得進行各種電子撞擊(Electron Impact Reaction)所需的能量。〔5〕

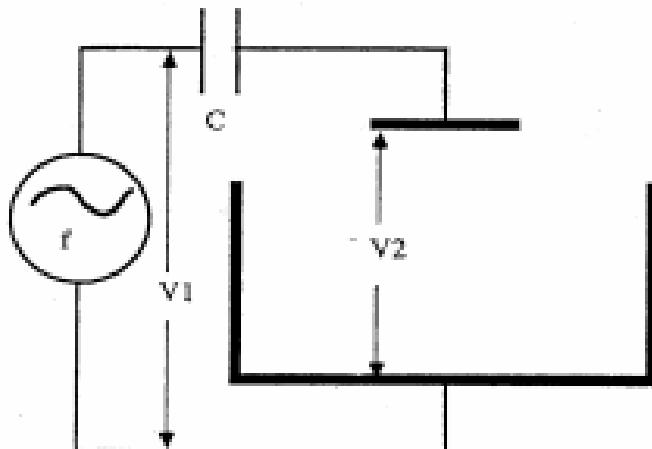

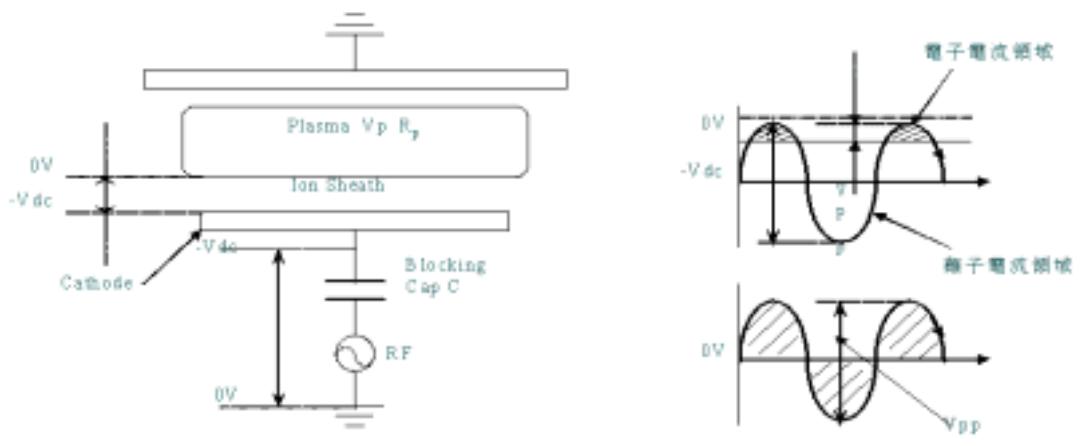

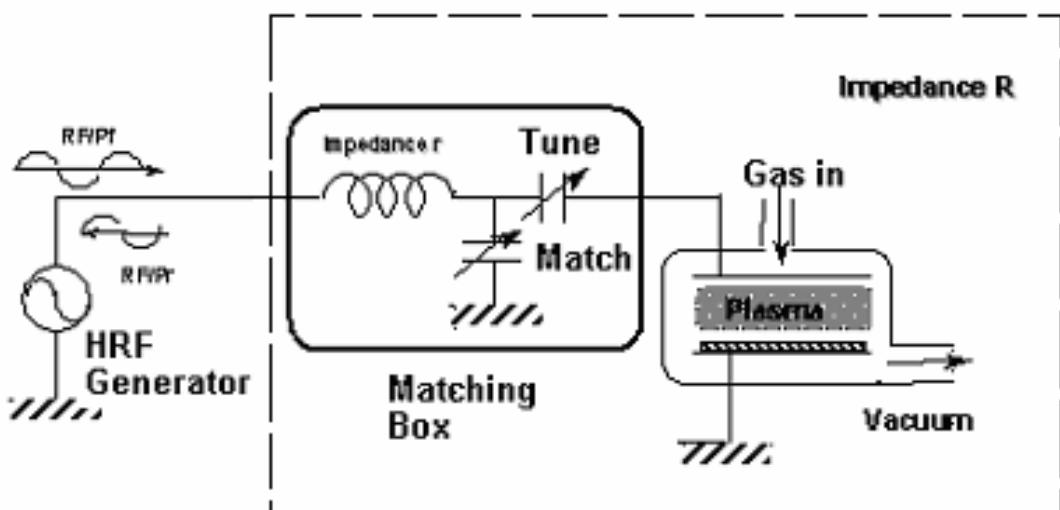

## 2-2-3 簡介 RF Vdc 與 Vpp

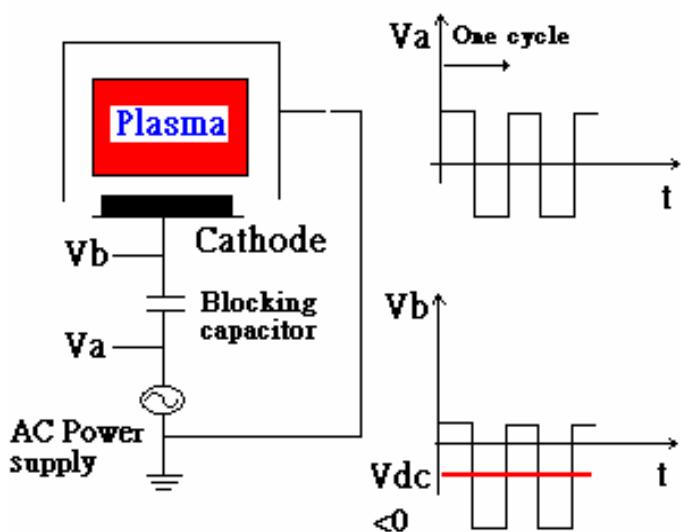

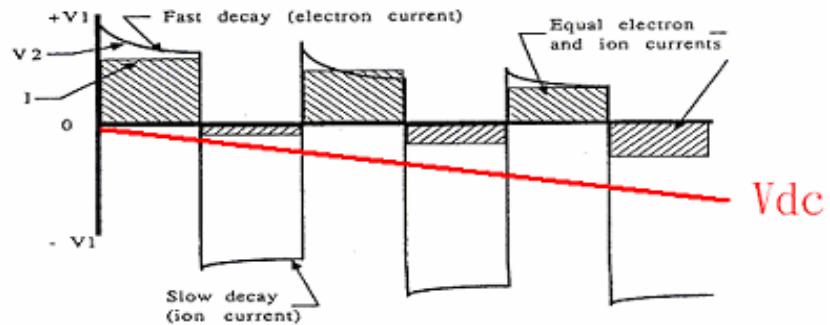

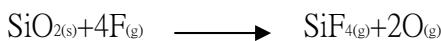

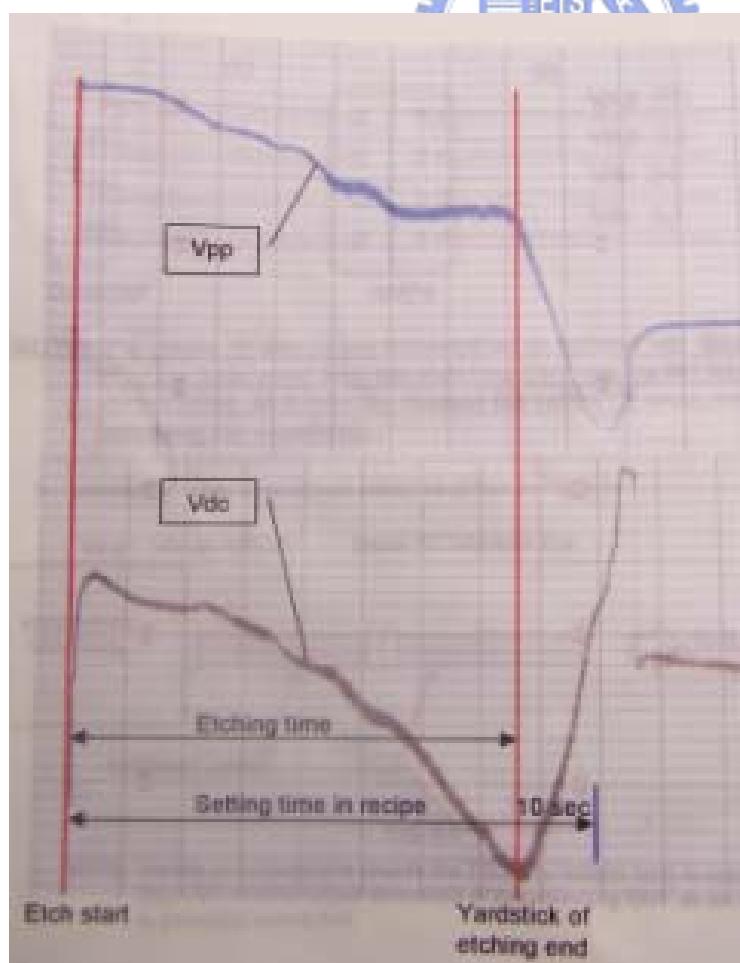

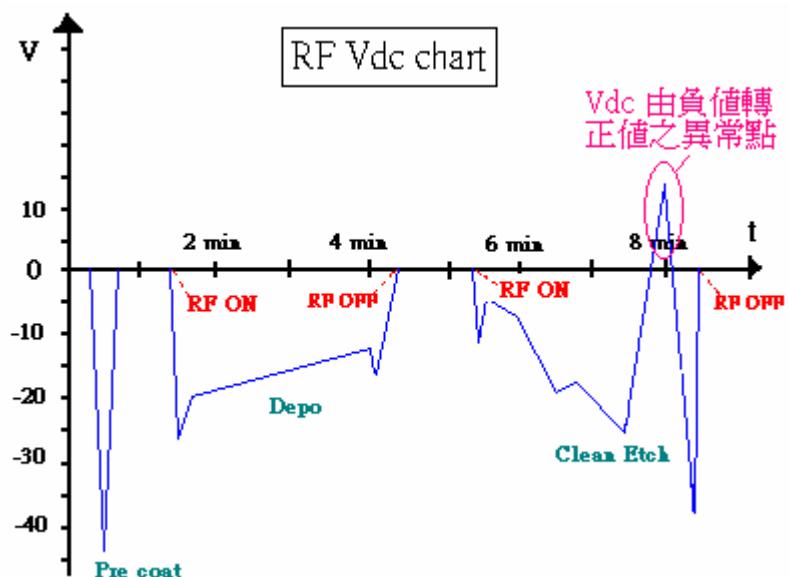

ASM PECVD 電漿屬於電容耦合型電漿(Capacitively couple plasma )，可監控 RF Vdc 及 Vpp，當 Arcing 發生時由實驗得知 Vdc 變化會由負值轉正值，所以可藉由 Vdc 之 chart 預知 Arcing 發生。

圖 2.8 電容耦合型電漿簡圖

- Vpp:Peak to Peak voltage**

- Vdc:self-bias voltage**

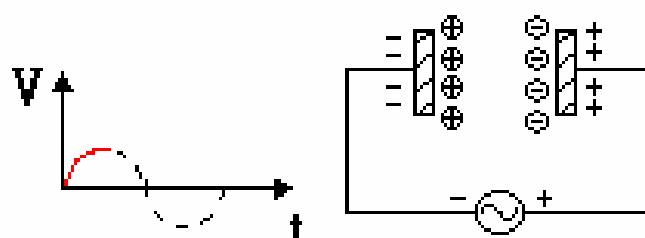

### Vdc ,Vpp 代表意義

電漿中有帶正電的正離子與帶負電的電子在交流電位正半周時，可吸引負電子至基板表面。在交流負半週期時，可吸引正離子至基板表面，由於電子質量遠較離子質量輕，移動速率也比快，故相互比較下，在交流電位正半週期時，可吸引較多的電子至基板表面上，在交流電位負半週時，相對有較少的正離子被吸引至基板表面，經過幾個週期後，基板表面就累積相當數目的電子，於是就在基板表面上建立一個直流負電位(Vdc) 。

由於這個區域中的正離子密度比較低，因此這個區域負電子和正離子的結合率比較低由於基板帶負電位，當電漿內正離子進入此區域時，就會被吸引加速而撞擊基板形成離子轟擊效應。〔6〕

## V<sub>pp</sub>

V<sub>pp</sub> 乃指 RF 正弦波的 Peak to Peak，通常是 Route Means Square(RMS)有效值的  $2\sqrt{2}$  倍。

當 RF 在正的半週期時，V<sub>n</sub> 電位在電漿形成，吸引負電子電荷往 Cathode 上的 Wafer 移動。此時電荷能量為  $-q \times V_n$

當 RF 在負的半週期時，將提供正離子電荷  $+q \times (V_p + V_{dc})$  的能量，使正離子電荷往 Cathode 上的 Wafer 加速移動。負電子電荷與正離子電荷的移動數量是相同的。

## V<sub>dc</sub>

V<sub>dc</sub> 乃經由 RF 電源的供給，在電漿內的電子和離子，因質量差所產生的加速度不同而形成。但有其形成條件

- Anode 面積要大於 Cathode 面積

- Cathode 要與 GND 絶緣

V<sub>dc</sub> 相當於 Cathode 電極上的 RF 電壓的平均值，即所謂的直流成份。

V<sub>dc</sub> 亦可視為 Ion Sheath 的直流電位差，亦即是 Ion Sheath 的厚度 D<sub>s</sub> 乘以 Ion Sheath 對 Cathode 的平均電場強度 E 之值 ( $V_{dc} = E \times D_s$ )。通常自我偏壓所形成的 V<sub>dc</sub> 值可大約為 V<sub>pp</sub> 的一半。此值不同於機台所示的 V<sub>dc</sub> 值，機台所示的 V<sub>dc</sub> 值為整合器內部旁路阻抗電路上的  $5M\Omega$  阻抗的直流電壓壓降值。

## V<sub>dc</sub> 的效果

V<sub>dc</sub> 可促使電漿內的離子以垂直方向入射 Wafer 表面，達成異方向性蝕刻的效果。

-V<sub>dc</sub> 的形成將可避免電子侵入 Ion Sheath

## V<sub>dc</sub> 和 RF 頻率關係

RF 頻率越高則 V<sub>dc</sub> 降低，反之 RF 頻率越低則 V<sub>dc</sub> 越高。

## V<sub>dc</sub> 和電漿密度

壓力越高(低真空)時，離子密度降低，Ion Sheath 厚度變薄，相對的 Sheath 電位差變小，V<sub>dc</sub> 變小。

壓力越低(高真空)時，離子密度增高，Ion Sheath 厚度變厚，相對的 Sheath 電位差變大，V<sub>dc</sub> 變大。

電漿密度除了壓力以外，對於 RF 頻率及其電源亦有影響。

RF 頻率越高時離子密度增高，越低時離子密度降低

RF 電源越大時離子密度增高，越小時離子密度降低

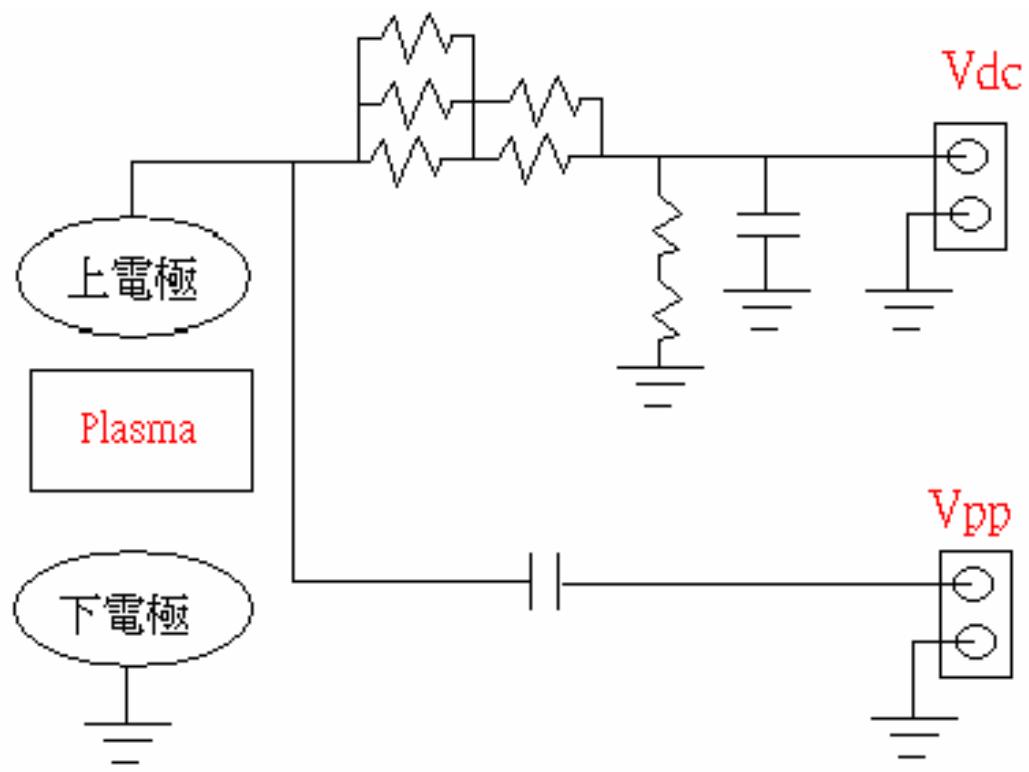

圖 2.9  $V_{dc}$  與  $V_{pp}$

圖 2.10  $V_{dc}$  與  $V_{pp}$

.Vdc Vpp 量測

圖 2.11 實驗設備 A S M P E C V D  $V_{pp}$  與  $V_{dc}$  之量測

## 2-2-4 利用 RF Vd 變化獲知 chamber clean 蝕刻終點

PECVD 腔體，當晶圓沉積完成，下一片晶圓要進入腔體執行沉積動作前，必須先執行一次電漿腔體清潔(Chamber clean)，否則在 chamber wall 上將覆著一層沉積物，成為污染微粒來源，也影響沉積薄膜之品質，但要如何決定 chamber clean 時間的長短，就是一個問題，Clean 時間不足，Chamber wall 覆著物將慢慢累積，然後剝落；成為腔體污染來源，但 clean 時間過久(Over clean)，電漿 中離子撞擊作用將加速腔體零件之損傷，縮短腔體零件壽命。

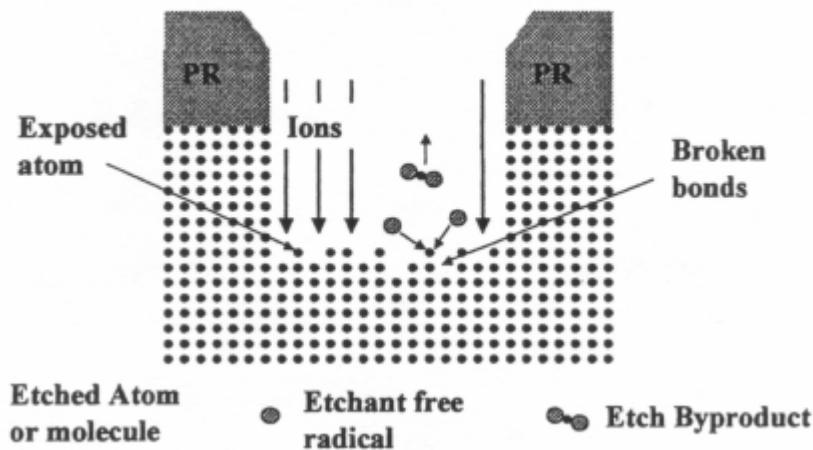

Chamber Etch clean 主要可分為 物理性蝕刻與化學性蝕刻

物理性蝕刻(Physical sputtering by ion bombardment )

- 主要 Factor：離子撞擊與能量

- 能量控制由 Self bias Vdc control

- Anisotropic 非等向性蝕刻

- Low selectivity

### Ion-induced Etching

圖 2.12 電漿蝕刻作用圖

化學性蝕刻(Chemical Etching by reactive radicals)

- Major factor: Radical species and density

- Isotropic 等向性蝕刻

- High selectivity

下表中列出目前使用幾種蝕刻終點( Clean Endpoint) 之方法 [ 7 ]

表 2.2 偵測蝕刻終點之方法

| Methods                       | Measuring                                 | Monitoring                     |

|-------------------------------|-------------------------------------------|--------------------------------|

| Impedance Monitoring          | Impedance mismatch                        | Voltage change                 |

| Optical Emission spectroscopy | Intensity of light emitted from discharge | Emission from reactive species |

| Pressure                      | Total pressure                            | Changes in total pressure      |

| Langmiur Probe                | change in electron density                | Current from probe             |

表 2.3 蝕刻終點波長特性表

Etch Endpoint Wavelengths

| Film                    | Etchant                          | Wavelength (Å) | Emitter       |

|-------------------------|----------------------------------|----------------|---------------|

| AL                      | $\text{Cl}_2$ BCL <sub>3</sub>   | 2614           | $\text{AlCl}$ |

|                         |                                  | 3962           | $\text{AlCl}$ |

| Poly Si                 | $\text{Cl}_2$                    | 2882           | Si            |

|                         |                                  | 6156           | O             |

| $\text{Si}_3\text{N}_4$ | $\text{CF}_4/\text{O}_2$         | 3370           | $\text{N}_2$  |

|                         |                                  | 3862           | CN            |

|                         |                                  | 7037           | F             |

|                         |                                  | 6740           | $\text{N}_2$  |

|                         |                                  | 7037           | F             |

|                         |                                  | 4835           | CO            |

| $\text{SiO}_2$          | $\text{CF}_4$                    | 6156           | O             |

|                         |                                  | 2535           | P             |

|                         |                                  | 7037           | F             |

| PSG ,BPSG               | $\text{CF}_4$ and $\text{CHF}_3$ |                |               |

| W                       | $\text{SF}_6$                    |                |               |

本實驗設備沉積二氧化矽，Clean Endpoint 方式採用 RF impedance monitor。

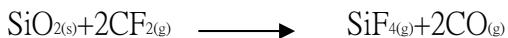

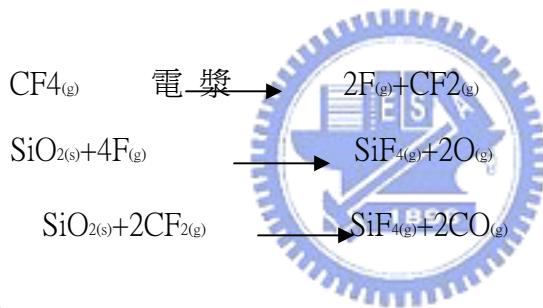

腔體內因沉積二氧化矽( $\text{SiO}_2$ )或氮化矽( $\text{SiN}$ )，會使用蝕刻反應氣體  $\text{CF}_4$  與  $\text{SiO}_2$  反應產生  $\text{SiF}_4$ ，隨真空 pump 抽除，以達到腔體清潔效果。

下圖為一個以 RF impedance 感應器來監控 Endpoint 蝕刻終點之簡圖，RF impedance 感應器位於 Matching network 與 cathode RF 陰極版之間，提供之資料經過處理計算，快速解決 clean Endpoint 之相關問題。.

圖 2.13 利用 RF 阻抗來偵測蝕刻終點

當到達蝕刻終點時，因腔體內反應氣體組成改變，將導致  $V_{dc}$  曲線呈現一不連續或反轉變化，此即清潔蝕刻終點(Clean etch endpoint)。

圖 2.14  $V_{dc}$ & $V_{pp}$  chart

## 2-3 Wafer Arcing 簡介

### 問題描述:

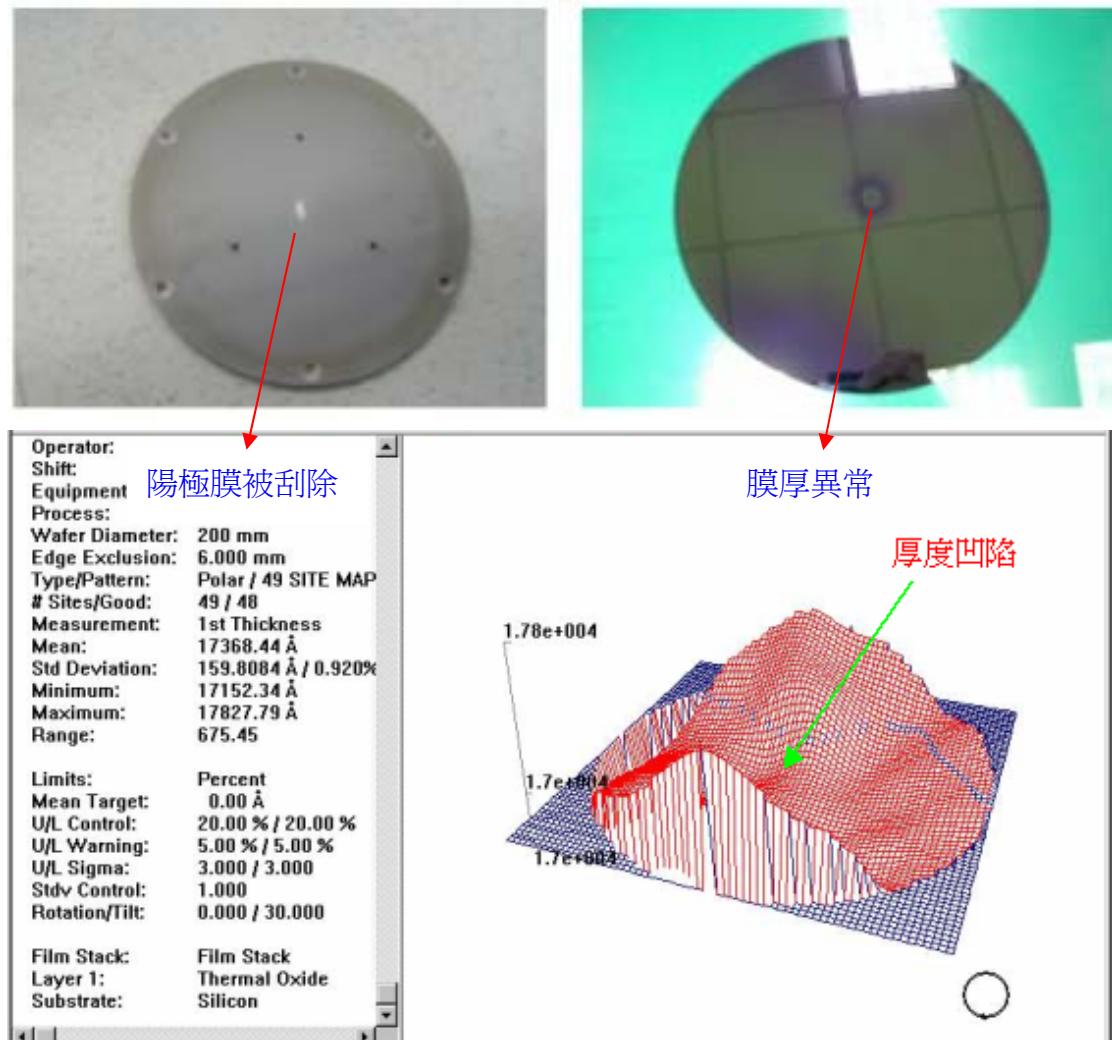

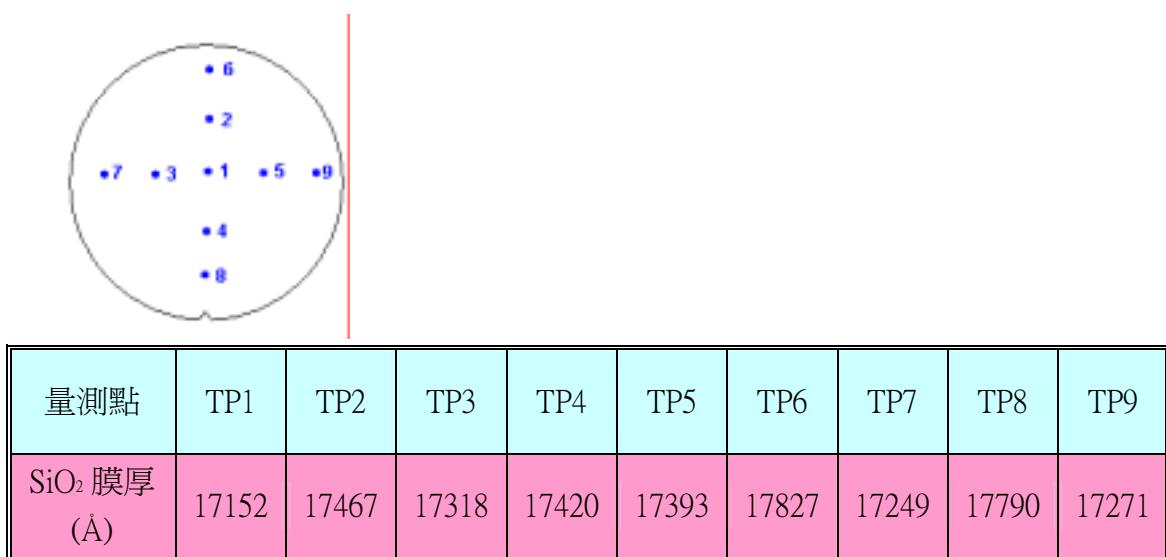

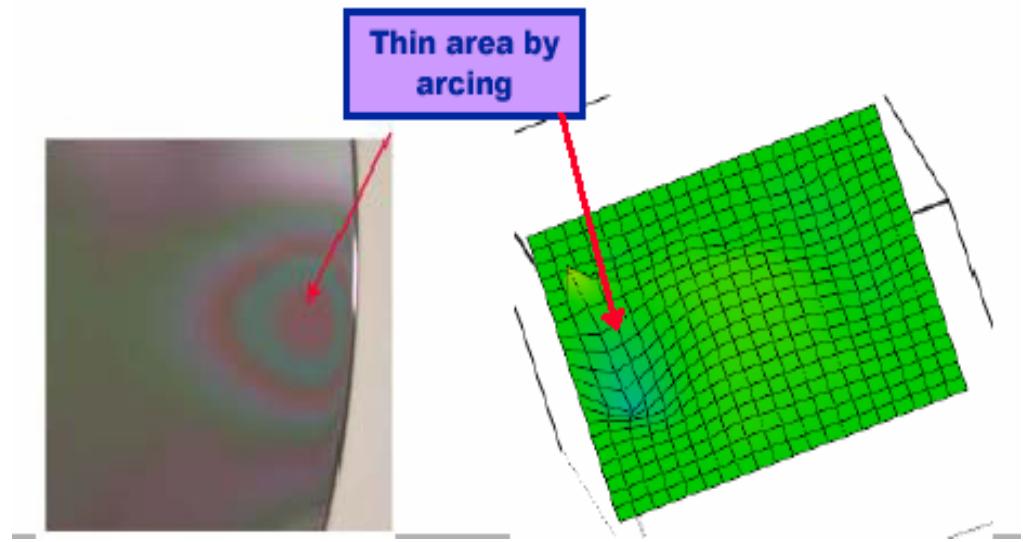

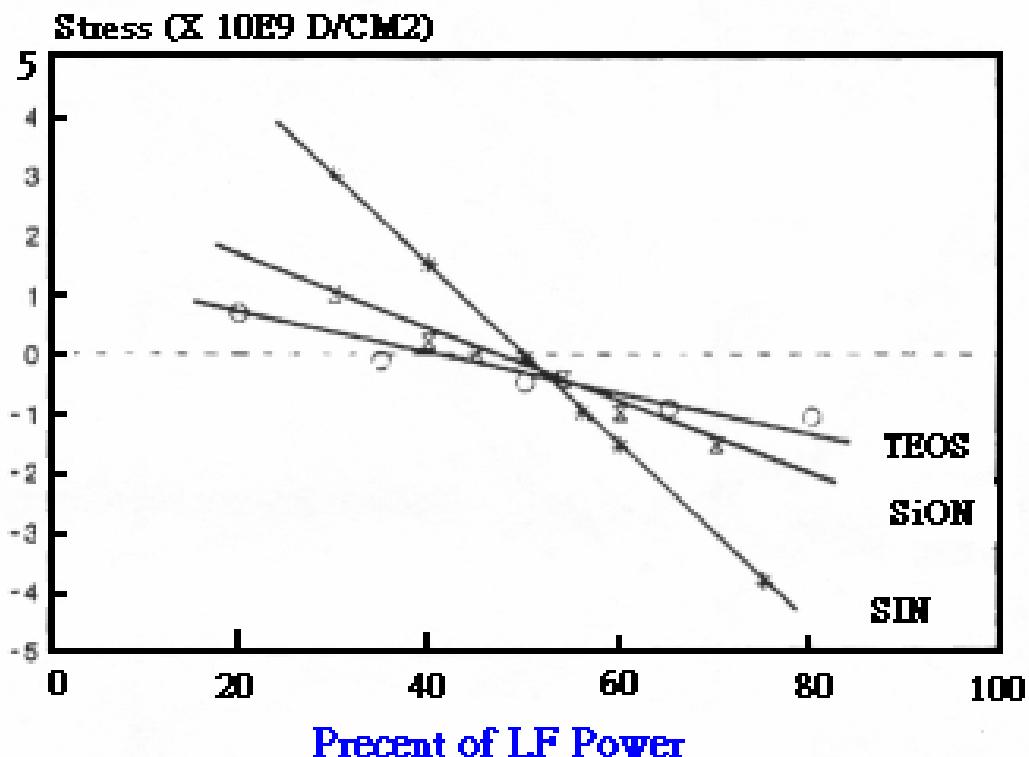

在 ASM PECVD 發生之 Wafer Arcing，主要現象為沉積在晶圓 上之二氧化矽薄膜，發生膜厚不均之異常現象，量測薄膜厚度之工具為 美商 KLA 公司之 UV-1280 厚度測量儀，主要發生厚度不均勻之製程發生在 PECVD TEOS 薄膜厚度  $>3000 \text{ \AA}$  厚度之製程。

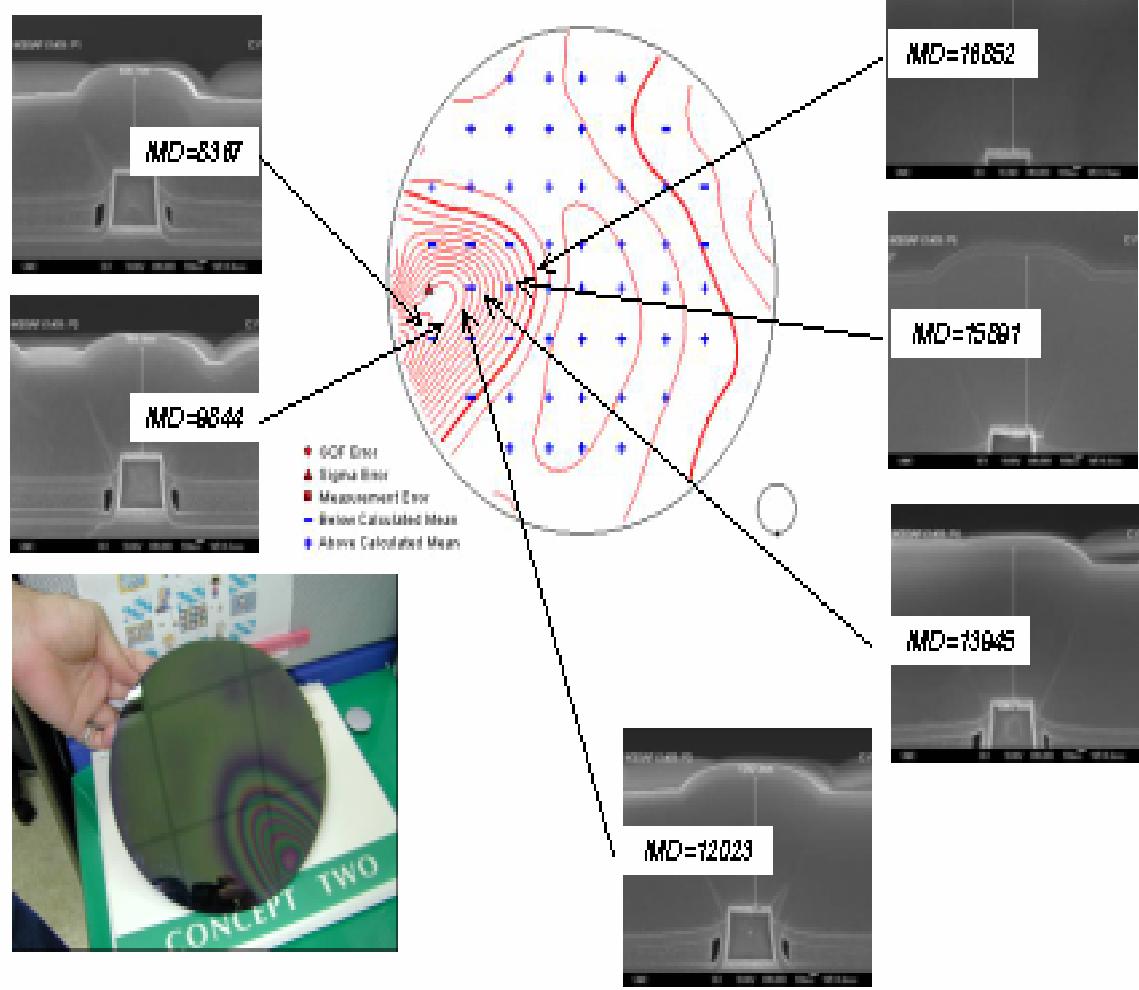

## Arcing Wafer Map and SEM

圖 2.15 Arcing 晶片厚度分布圖

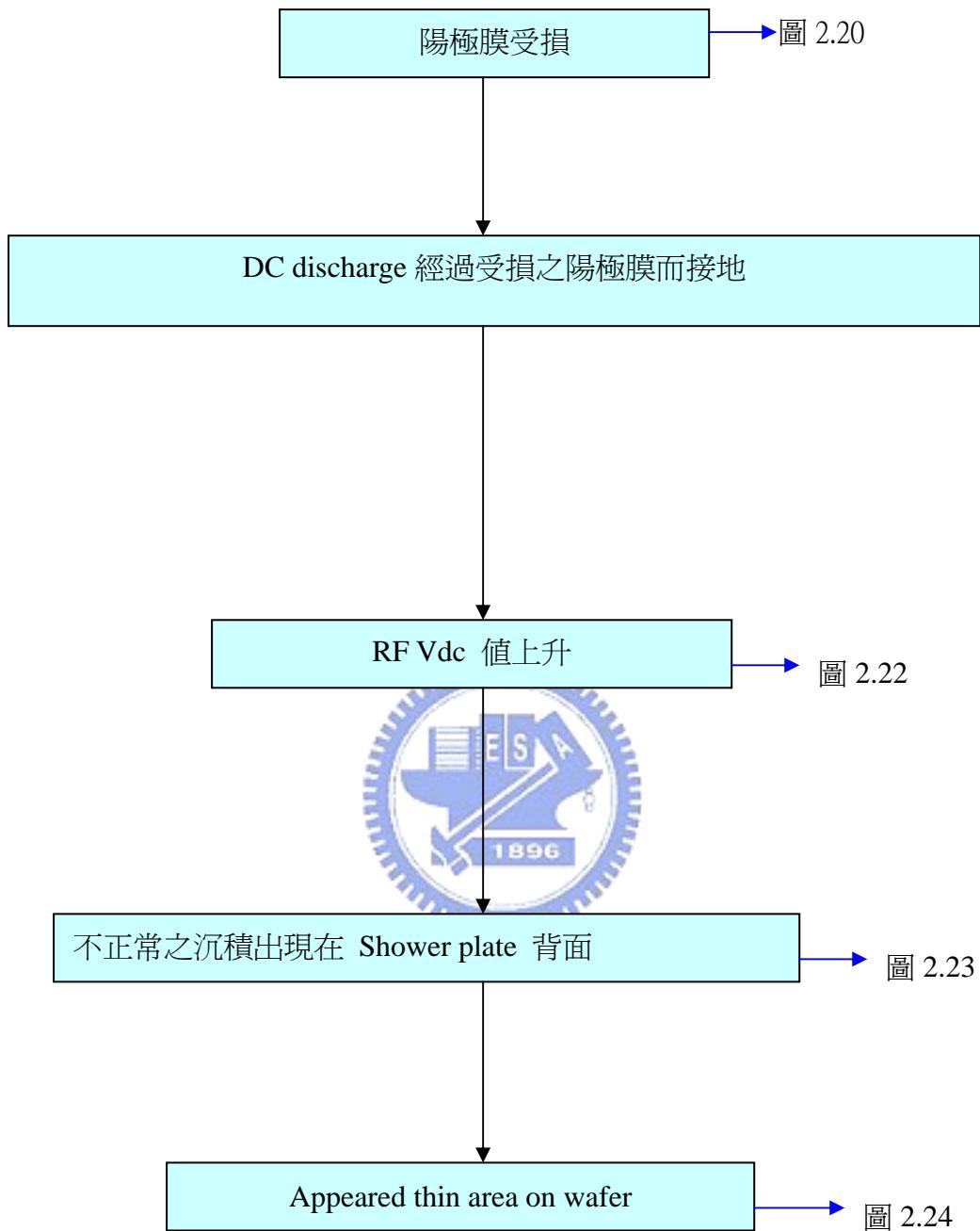

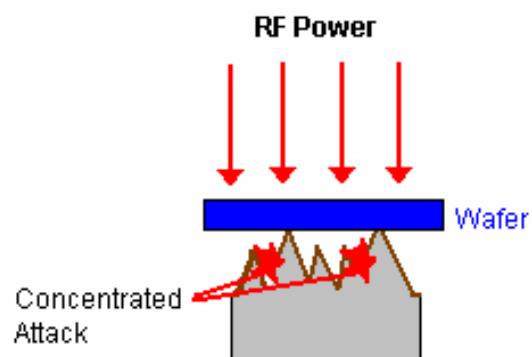

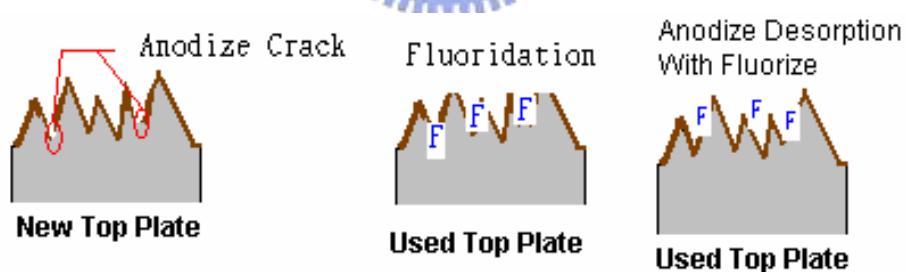

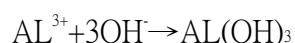

### 2-3-1 Wafer Arcing 成因與異常現象

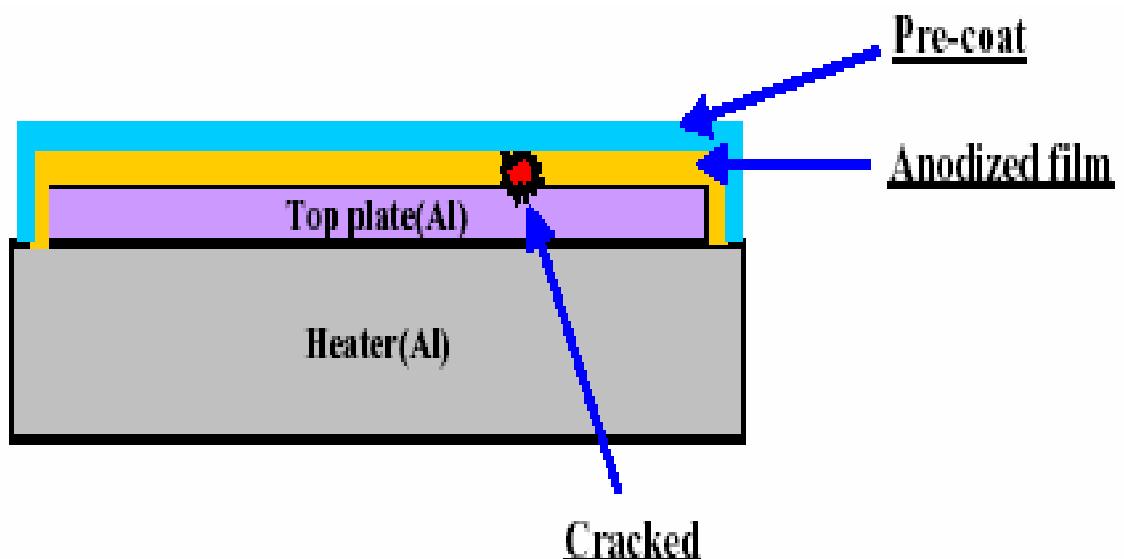

1. Top Plate(下電極)陽極膜缺陷。

2. 長時間的電漿(Plasma)作用，所造成的高溫與 RF 使 Top Plate 陽極膜損傷擴大。

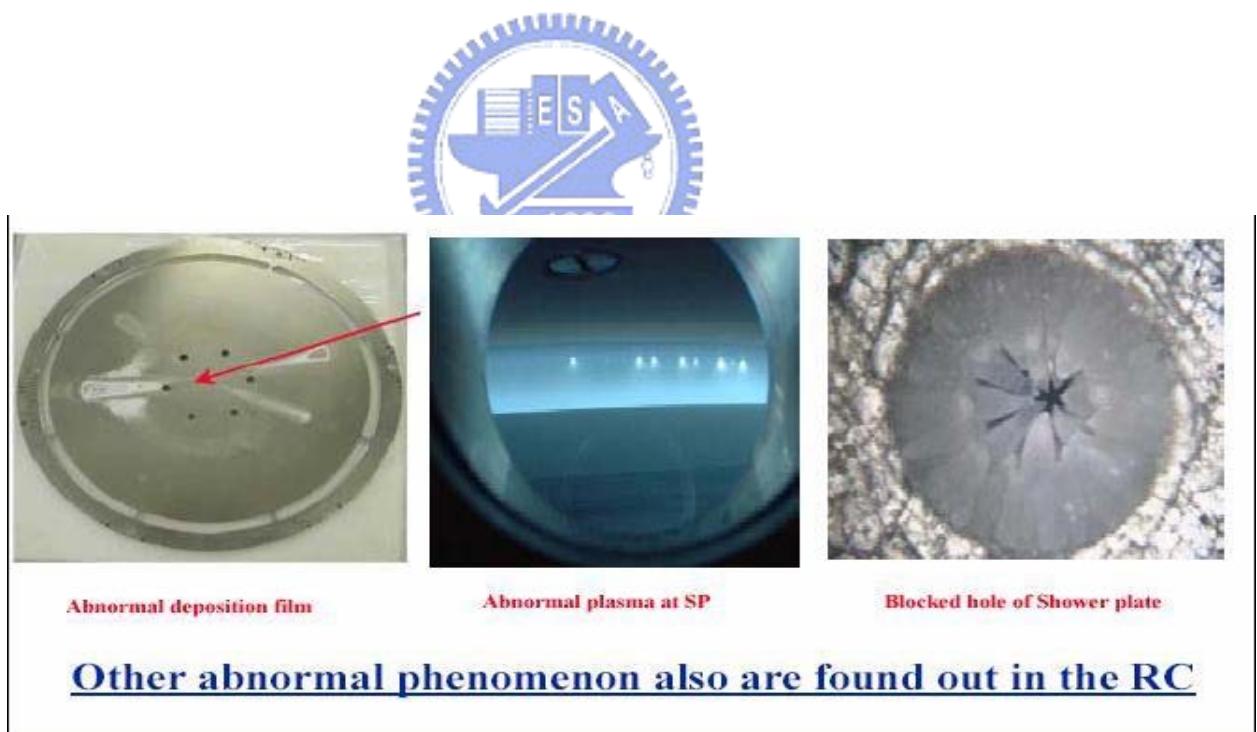

3. 腔體由 Top Plate 陽極膜破壞處不正常放電(Arcing)，所形成之高溫讓反應氣體 TEOS 提前在 Shower Plate(下電極)與 Buffer Plate 間反應，並使 Shower Plate 陽極膜損傷。

4. TEOS 提前在 Shower Plate 與 Buffer Plate 間反應形成白粉，累積後掉落於晶圓(wafer)上，而 Wafer Arcing 處因無沉積而形成彩紋。

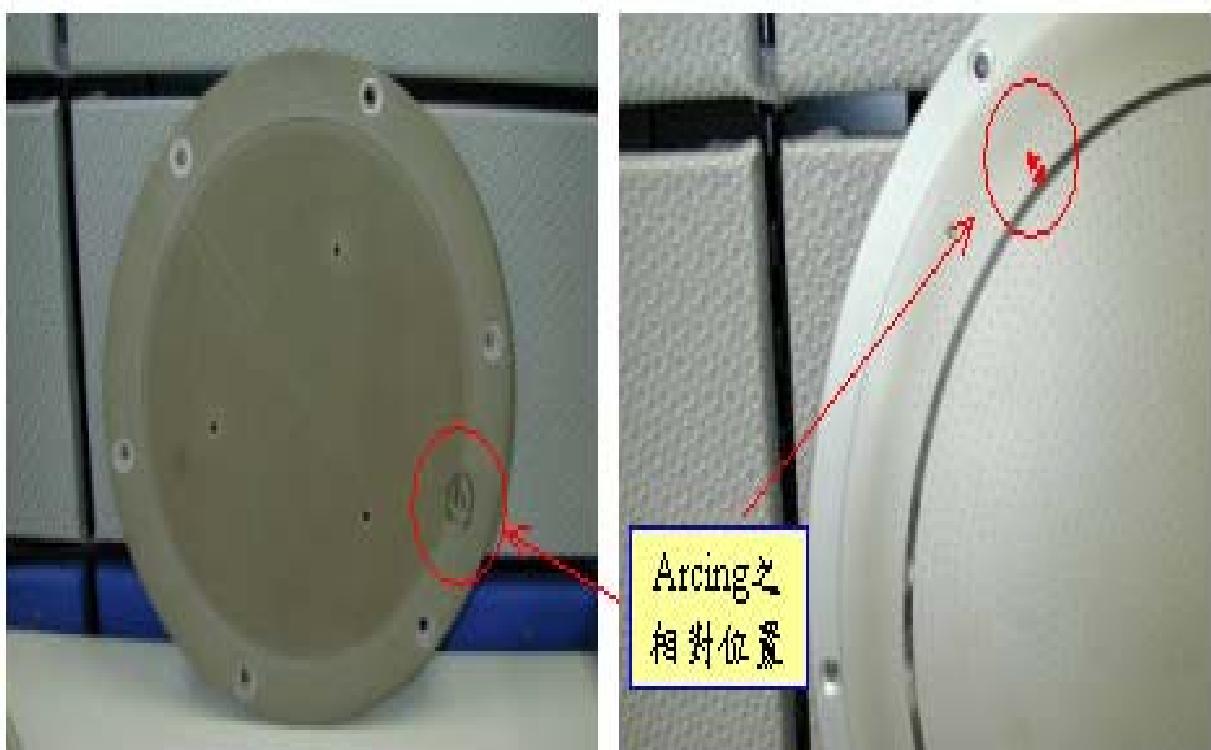

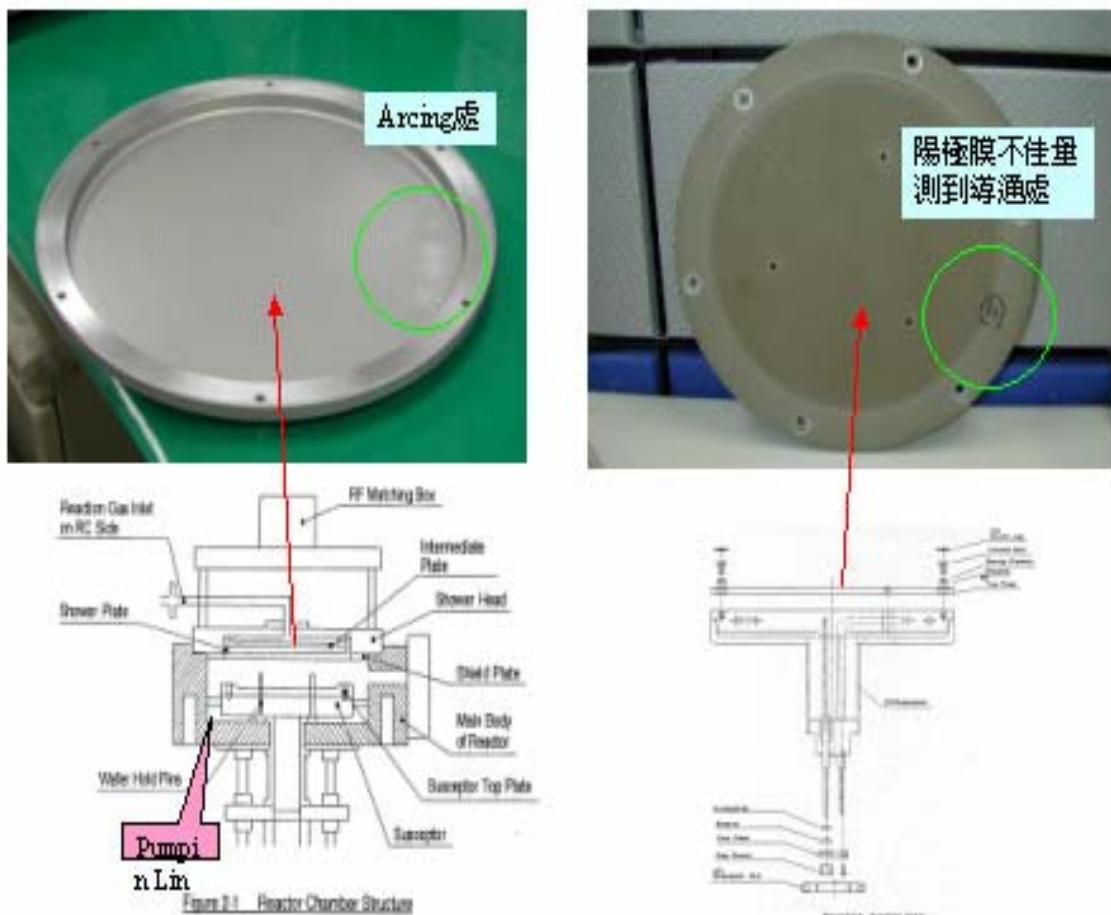

Arcing Chamber Parts 之異常現象：

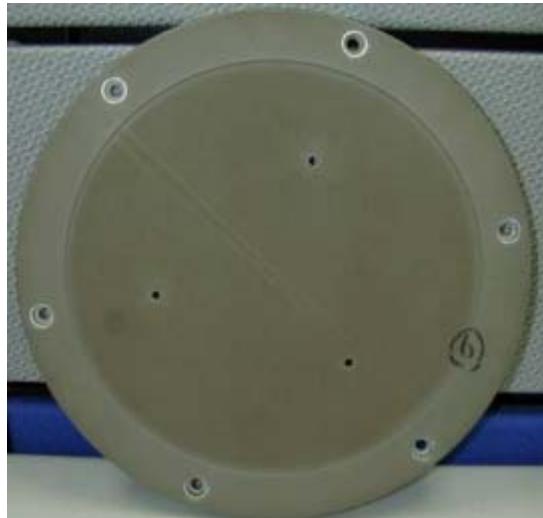

發生 Arcing 之 Top plate 放置

Wafer Position 邊緣用電表測試

阻值有些點有幾乎導通現象

發生 Arcing Shower Plate 邊緣氣孔

用電表測試阻值有幾乎導通現象，

靠近中間的氣孔則無此現象

圖 2.16 Arcing Chamber Parts 之異常

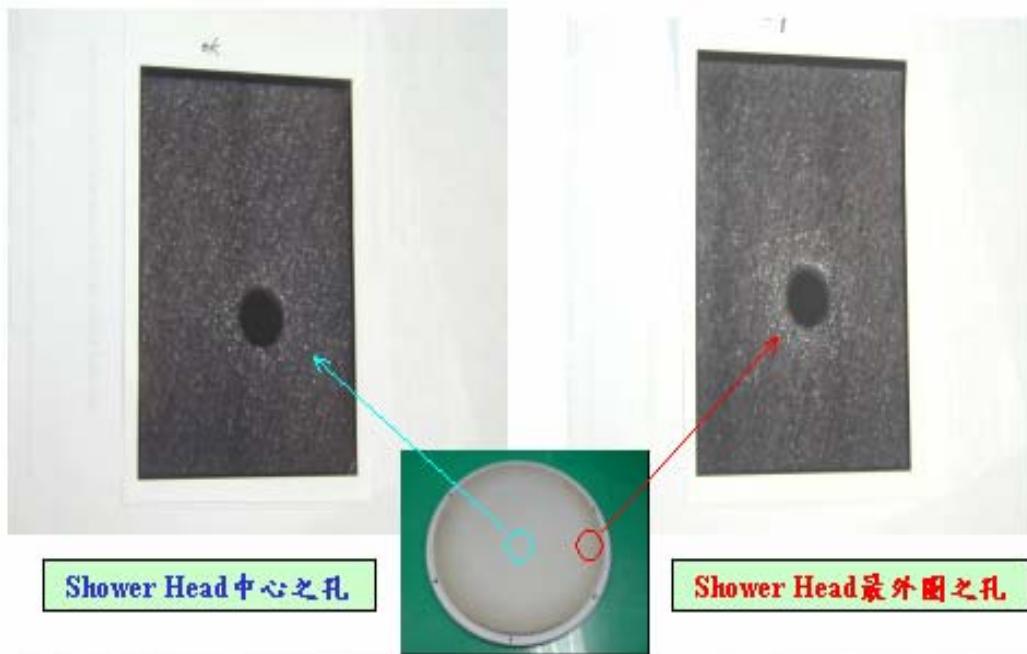

Shower Plate 在發生 Arcing 後，用顯微鏡觀察發現，外圍氣孔的陽極膜已有嚴重被蝕刻露出底材鋁合金的現象。

圖 2.17 Shower Head 氣孔顯微圖

## Wafer Arcing 的複製實驗

將 Top Plate 中央陽極膜絕緣膜刮除一小塊，沉積後在相對應位置即有膜厚異常的現象。

圖 2.18 異常晶片厚度立體圖

## Wafer Arcing 流程圖

圖 2.19 Wafer Arcing 流程圖

## 腔體內示意圖

圖 2.20 腔體內式意圖〔8〕

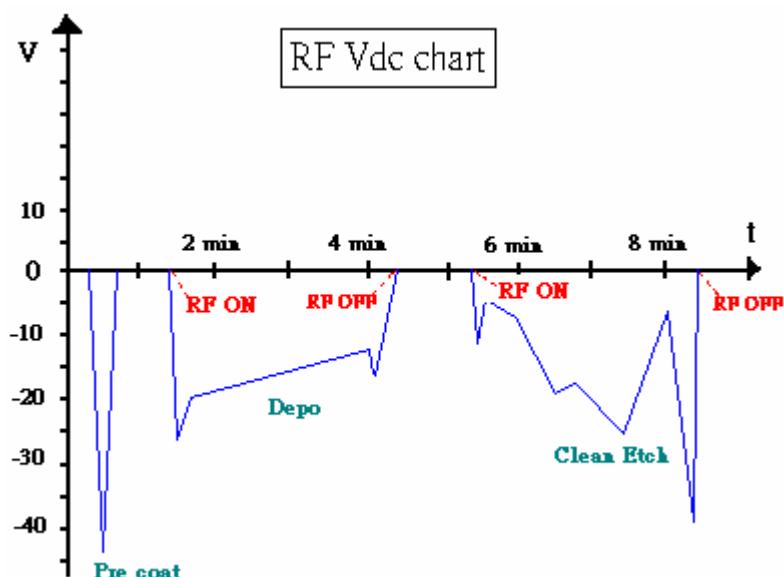

正常 Vdc chart

圖 2.21 正常 Vdc chart

異常 Vdc chart

圖 2.22 異常 Vdc chart

圖 2.23 Showerhead 後出現白粉

圖 2.24 晶片 Arcing 處膜厚度凹陷

圖 2.25 Arcing 腔體內不正常現象

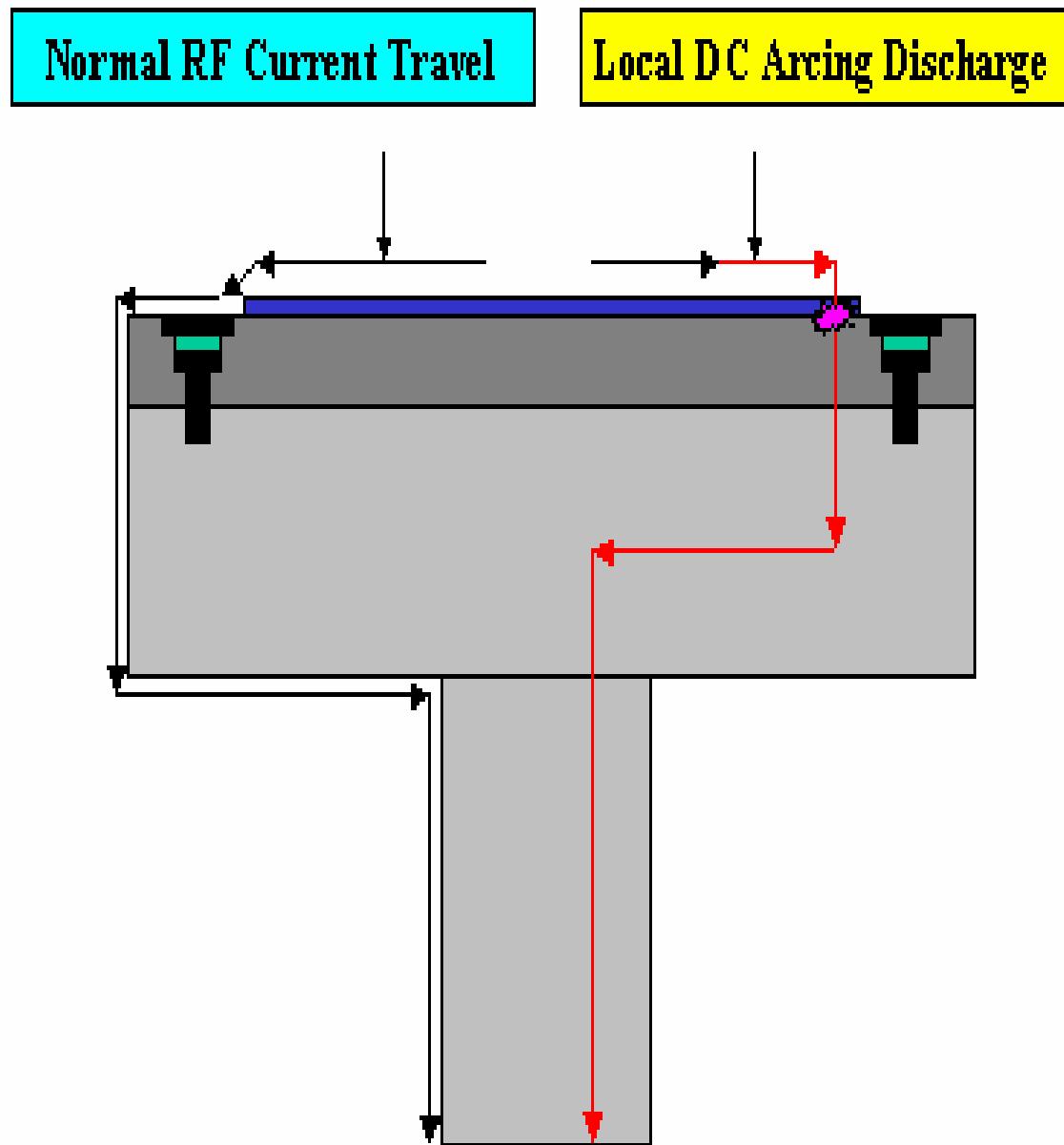

## ASM機台 Chamber Arcing 的路徑

圖 2.26 Chamber arcing 的路徑

## 第三章 實驗方法

### 3-1 實驗設備 ASM Eagle-10 PECVD Equipment

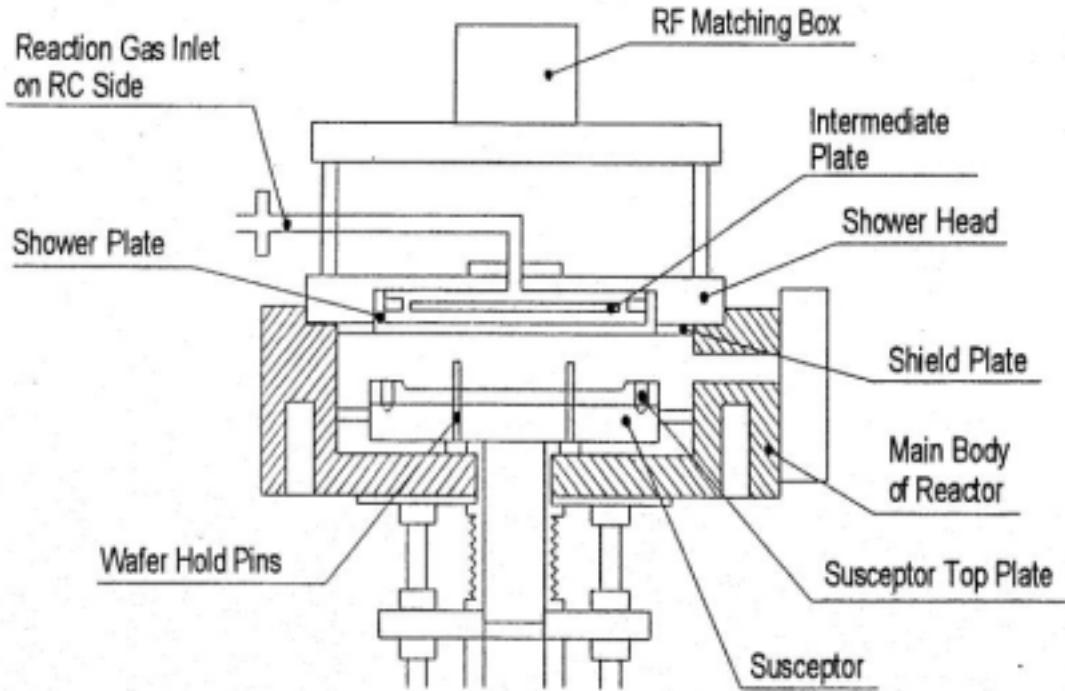

#### ASM PECVD Chamber 介紹

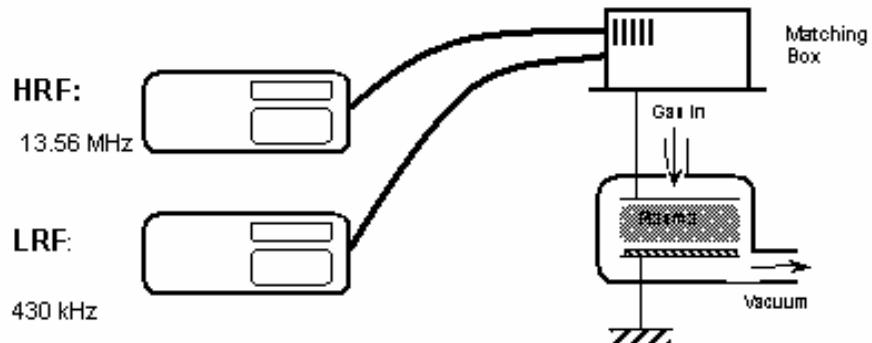

ASM PECVD 是設計為包含了高頻(13.56MHZ)與低頻 (430KHZ )之電漿輔助化學氣相沉積(Plasma Enhanced Chemical Vapor Deposition)系統藉由電漿輔助，可使傳統上需溫度 700~900 度 C 之 thermal CVD 氮化矽(Silicon Nitride) ，溫度降低至 300~450 度 C，便可沉積出相同之薄膜，因為有了電漿輔助，能夠沉積出多種類之薄膜。

ASM PECVD 是設計為一次沉積一片晶圓，並且在一次沉積之後跟隨進行一次電漿 etch clean，此 clean 可使沉積在腔體週邊之生成物，藉由電漿及 clean gas  $\text{CF}_4$  之物理及化學反應，讓生成物反應成氣體隨 PUMP 抽走。

#### 腔體(Chamber)

腔體主要是由鋁合金為主要材料製作而成內容積約 7 公升，主要之加熱系統包含了加熱器(Susceptor Heater)及 warm wall system (80~120 度 C) ，藉由氣體為介質傳導，使腔體之溫度能夠分布均勻，加熱器上有三支 Lift PIN，主要作為傳送時承接機器手臂(Robot)晶片之用。

加熱器主要材質為鋁，內含一組加熱線圈及一組偵測溫度之 Thermal Couple，一支加熱器日本原廠報價約新台幣 20 萬元，在晶圓廠內可沉積約 20 萬片晶圓，當 Heater 使用一定程度將會因變形或是熱傳效率變差，導致沉積出之薄膜品質發生變異，而必須汰換。.

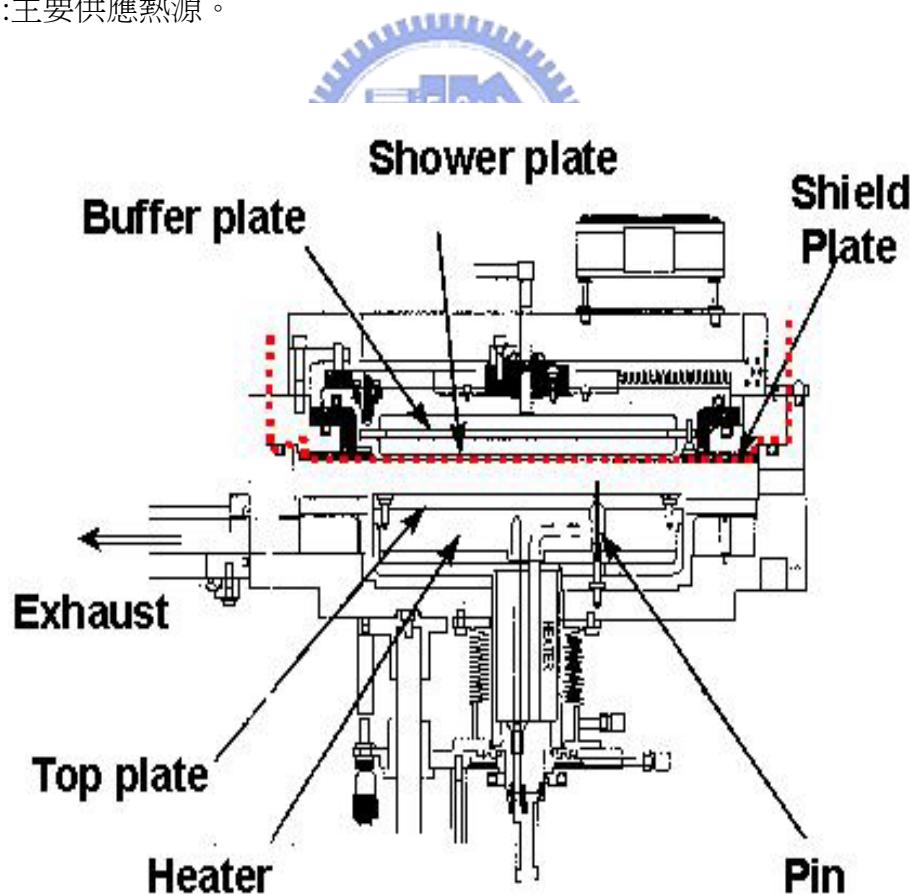

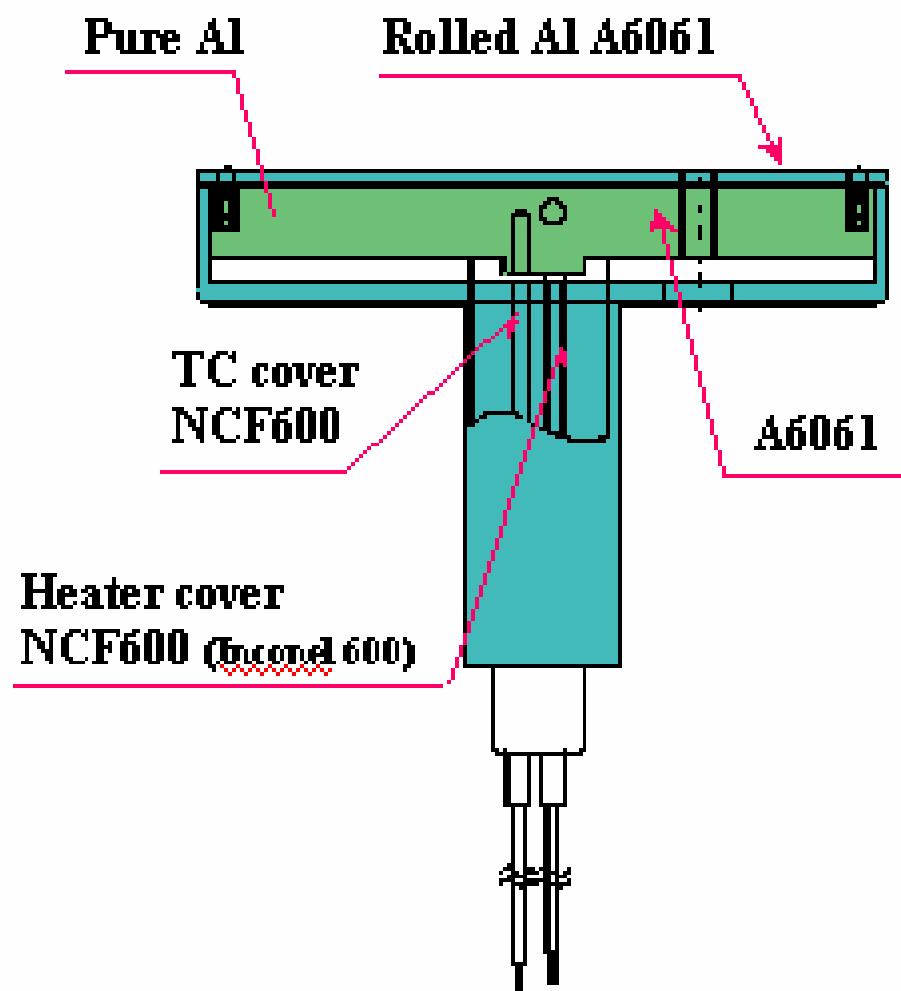

Figure 2-1 Reactor Chamber Structure

圖 3.1 腔體結構圖

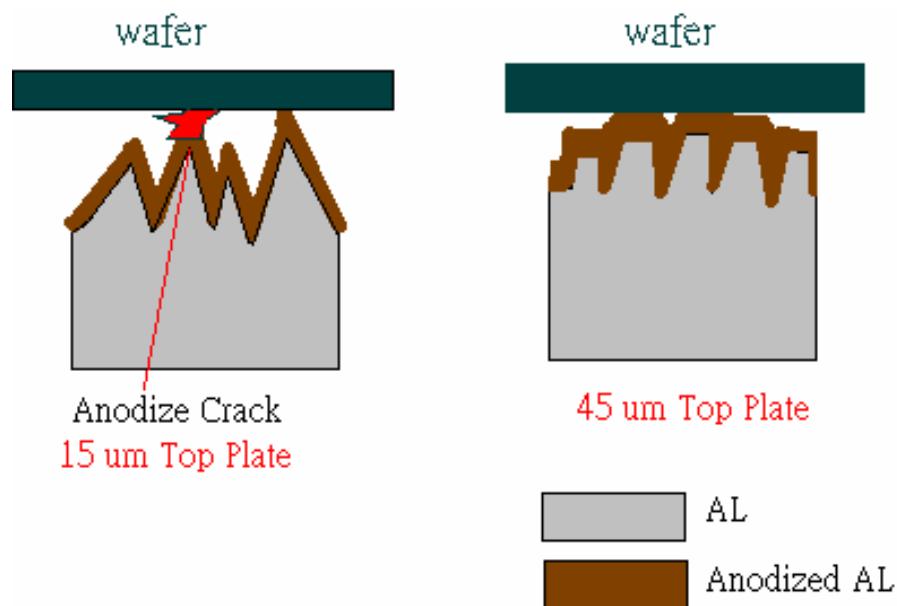

在加熱器上有一 Top plate，為了容易保養(Maintenance)，利用六支螺絲將 Top plate 以 16 in-lb 磅之力量鎖緊於加熱器上，TOP Plate 每片成本約新台幣 2 萬元，可使用沉積約 1 萬片晶圓，Top plate 之材質主要為鋁合金，但正面表面以陽極處理技術覆蓋上一層厚度約  $15 \mu m$ ，之陽極膜，此層陽極膜為絕緣，Top plate 之背面為導電性良好之鋁合金表面。〔9〕

圖 3.2 腔體

圖 3.3 Top plate

沉積時晶片置於 TOP Plate 之上，加熱器之熱量藉由 Top plate 傳導至晶圓，使用壽命到只需更換 Top plate 而不需更換加熱器，節省成本及降低更換複雜度。

腔體內另一個主要用來使反應氣體分布均勻的零件 Shower plate，成本約 10 萬元，其有許多孔洞，能夠使反應氣體以最佳分布沉積於晶圓上，與 Top plate 相同，Shower plate 正面覆蓋一層不導電之陽極膜，背面為導電性良好之鋁合金表面。

圖 3.4 Shower Plate

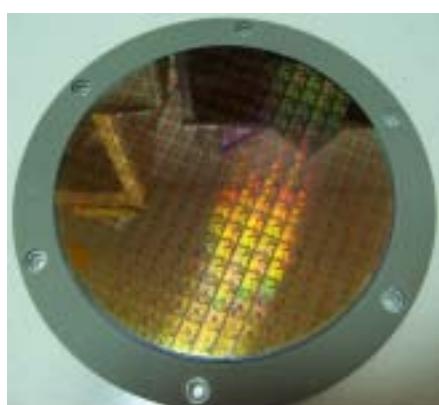

主要腔體結構可分成上下兩個部份:

Shower head 上電極 (Upper electrode):

如下圖，上電極部份主要有三個重要零件

1. Buffer plate :主要材質為鋁，位於 Shower plate 背面，使反應氣體能夠均勻的流入 Shower plate 。

2. Shower plate :主要的上電極，使反應氣體流向更均勻。

3. Shield plate :主要材質為陶瓷(ceramic)作為上電極與下電極之間的絕緣層。

Susceptor 下電極 (Down electrode) :

1. Top plate:主要與晶圓接觸不同種類之製程，對應不同使用類型之 Top plate 。

2. Heater :主要供應熱源。

圖 3.5 ASM PECVD 上電極圖

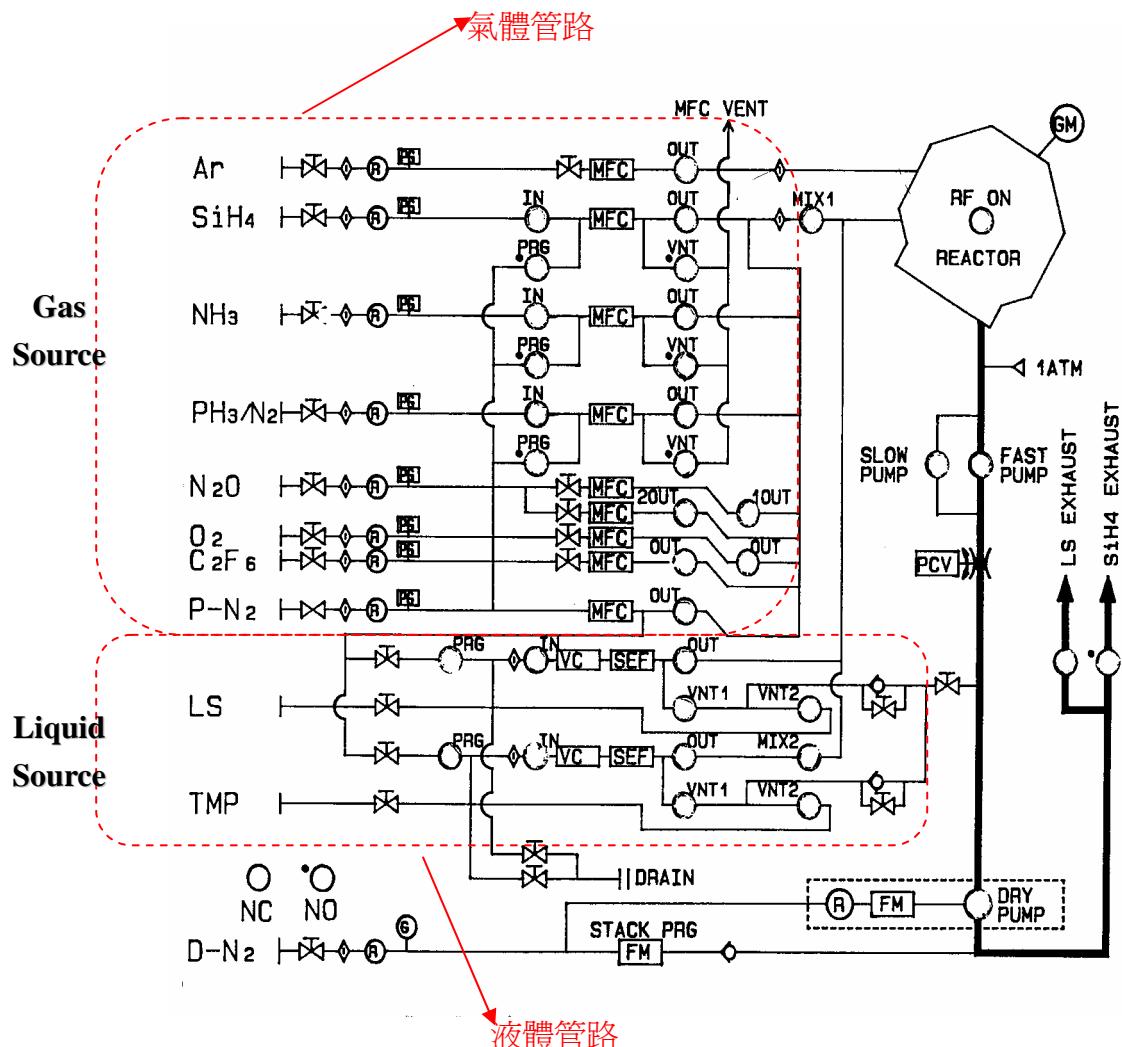

## 氣體管路

氣體管路主要包含兩個部份，氣體(gas) 與液體( Liquid)

### 1. 氣體管路:

如下圖，主要有包含 Ar 、SiH<sub>4</sub> 、NH<sub>3</sub> 、C<sub>2</sub>F<sub>6</sub> 、N<sub>2</sub> 及 N<sub>2</sub>O 。

### 2. 液體管路

Liquid 管路主要用來輸送 TEOS 及 TMP，管路系統包含了加熱溫度控制，使化學液體經加熱而揮發成氣體，再經由質流控制器(Mass Flow Controller)控制流量，並且防止因溫度過低，而造成管路中發生凝結(Condensed) 。

圖 3.6 ASM PECVD 氣體管路圖

## RF 系統

ASM PECVD 之 RF 系統包含了高頻(HRF)13..56MHZ，及低頻(LRF)430KHZ 之 RF 能量，RF 能量由 RF Generator 產生，經由導線傳輸至 RF Matching box，Matching box 與上電極相通，RF 能量藉由 Shower plate 進入腔體內，解離反應氣體，產生電漿。

圖 3.7 RF 系統圖

### RF System Net Work and Matching Box

Matching box 內包含了兩個由馬達控制之可變電容及一個固定電感，如下圖所示，可變電容可分為 Tune 與 Match，Tune 電容為串聯，Match 電容為並聯，當 RF 能量由 Generator 產生，Tune 與 Match 將由馬達控制自動調變，改變整個 Matching Box 阻抗，使輸入 腔體內之 RF 能量為最大值。

圖 3.8 RF Matching Network

### 加熱器(Heater)

加熱器主要材質為鋁合金，溫度感應器 (Thermal Couple) 位於加熱器之中心部位。

圖 3.9 ASM Heater 加熱器

## 3-2 實驗條件與材料

操作條件，8 英吋晶圓

表 3.1 實驗條件表

| 晶圓沉積 SiO <sub>2</sub> |            |

|-----------------------|------------|

| 製程參數                  | 操作條件       |

| 沉積厚度                  | 19000 Å    |

| TEOS 流量               | 100 sccm   |

| O <sub>2</sub> 流量     | 1000 sccm  |

| Ar 流量                 | 100 sccm   |

| 13.56 MHZ RF power    | 480 W      |

| 430 KHZ RF power      | 180W       |

| 腔體壓力                  | 3500 mTorr |

| Heater 溫度             | 400°C      |

| 沉積時間                  | 約 3分鐘      |

| 腔體清潔(Clean Etch)                 |            |

|----------------------------------|------------|

| C <sub>2</sub> F <sub>6</sub> 流量 | 300 sccm   |

| O <sub>2</sub> 流量                | 900 sccm   |

| Ar 流量                            | 100 sccm   |

| 13.56 MHZ RF power               | 850 W      |

| 430 KHZ RF power                 | 0 W        |

| 腔體壓力                             | 4000 mTorr |

| 清潔時間                             | 約 4分鐘      |

- (1) TEOS: 主要 SiO<sub>2</sub> 反應氣體

- (2) AR: 參與電漿反應

- (3) O<sub>2</sub>: Clean/Depo 反應氣體

- (4) C<sub>2</sub>F<sub>6</sub>:Clean 反應氣體

### 3-3 量測原理與儀器

#### 厚度量測設備

量測晶圓長成膜厚及膜厚均勻度之設備是美商 KLA 公司之， TENCOR PROMETRIX UV1280。〔10〕

量測膜厚共取樣九點。

The measurement points and uniformity calculation equation

圖 3.10 晶片膜厚量測取樣點分布圖

Measurement points t<sub>6</sub>, t<sub>7</sub>, t<sub>8</sub> and t<sub>9</sub> are located 6 mm form the edge

Measurement point t<sub>2</sub>, t<sub>3</sub>, t<sub>4</sub> and t<sub>5</sub> are located 47 mm form the center

Average =Average thickness =

$$\bar{t} = \frac{1}{9} \sum_{i=1}^9 t_i$$

Sigma within wafer uniformity

$$U\% = \frac{\sqrt{\frac{1}{8} \sum_{i=1}^9 (t_i - \bar{t})^2}}{\bar{t}} * 100\%$$

### 薄膜應力 Stress 量測

薄膜應力量測採用 KLA TENCOR 公司之 FLX-5400 平均量測結果介於 -5E08~3E09(dyne/cm<sup>2</sup>)

### 薄膜微粒量測

薄膜微粒量測採用 KLA TENCOR 公司之 SurfScan 6420 ,平均量測結果 0.5~0.25um 大小之微粒數量小於 30 顆

### RF Power 量測

圖 3.11 ADTEC RF Generator

|                            |                                                        |

|----------------------------|--------------------------------------------------------|

| Model                      | AX-1000III                                             |

| Output power               | 1000W                                                  |

| Output settable range      | (1W increments) at 50Ω                                 |

| Output deviation           | ± 0.5% of Set Value or 2W(whichever is larger) at 25°C |

| Output frequency           | 13.56MHz                                               |

| Frequency stability        | ± 0.01% (10°C - 40°C)                                  |

| Output impedance           | 50Ω ± 2Ω                                               |

| Output harmonic distortion | Less than -50dB of fundamental wave                    |

| Remote control connection  | Analog control<br>RS-232C Control(D-sub 9pin)          |

| Output connector           | N-type Receptacle                                      |

| Cooling method             | Forced Air                                             |

| Power supply               | 3Φ,3wire 50/60Hz, 200/220V, 2.0kVA                     |

[http://www.adtec-rf.com/en/product/ax\\_series/AX1000III.html](http://www.adtec-rf.com/en/product/ax_series/AX1000III.html)

RF power 是經由機台下指令給 RF Generator 再由 generator 輸出 power 至 腔體.

## 腔體壓力量測

圖 3.12 MKS 622A Baratron gauge

壓力量測採用 MKS 622A Baratron Absolute Capacitance Manometer ,量測範圍 0~1000 Torr

<http://www.mksinst.com/cgi-bin/product.exe>

### 加熱器溫度量測

腔體溫度主要以加熱器內之 E-type 溫度感應 TC 為量測 Meter,配合 SSR (Solid State Relay )及溫度控制器,作 400°C 之溫度控制.

## 3-4 實驗改善方法

- a. 更換不同厚度陽極膜之 Top plate , 比較其 Arcing 發生之機率 。

- b. 修改程式加入 Pre-coat 一層二氧化矽在 Top Plate 上 , 並比較 Pre coat 不同厚度二氧化矽之 Top plate , 其 Arcing 發生機率之比較 。

- c. 針對程式中主要之製程參數條件 , TEOS 流量、氧氣流量、沉積壓力、高頻 RF 能量、低頻 RF 能量、等條件 , 做不同之改變 , 並分析個別條件對晶圓 Arcing 之影響 。

- d. 實驗設計不同種類之 Top Plate, 並比較其差異 。

## 第四章 實驗結果與分析

### 引發晶片 Arcing 因素

由實驗得知 Top plate 上陽極膜破損使底材鋁金屬露出，喪失陽極膜之絕緣保護作用，引發電漿中不正常局部放電反應，是造成晶片 Arcing 之主因，造成 Top plate 損傷之主要原因可分

- 電漿作用

- 高能量之 RF Power

- 晶片傳輸過程所造成之機械摩耗

-

### 防止 Arcing 發生之改善方法

#### 實驗方法一

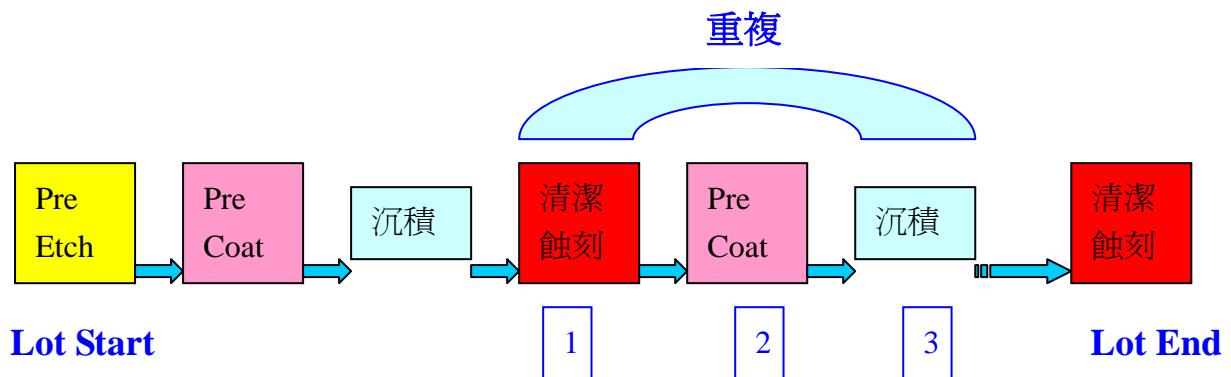

##### 4-1 預先沉積(Pre-coat)二氧化矽薄膜在 Top Plate 上

實驗中 PECVD 之製程流程是一片晶圓沉積完畢後跟隨進行一次腔體清潔，改善方法一是在腔體清潔(chamber clean)後，晶圓尚未進入腔體進行沉積前，先反應沉積一層二氧化矽薄膜在 Top plate 上，利用二氧化矽當作絕緣層保護 Top plate。

改善效益→防止局部放電(DC discharge)發生。

圖 4.1 Pre coat 二氧化矽預防 Arcing

## 製程流程圖

圖 4.2 ASM PECVD 製程流程圖

※ Pre Coat 步驟加入在原有之沉積步驟前

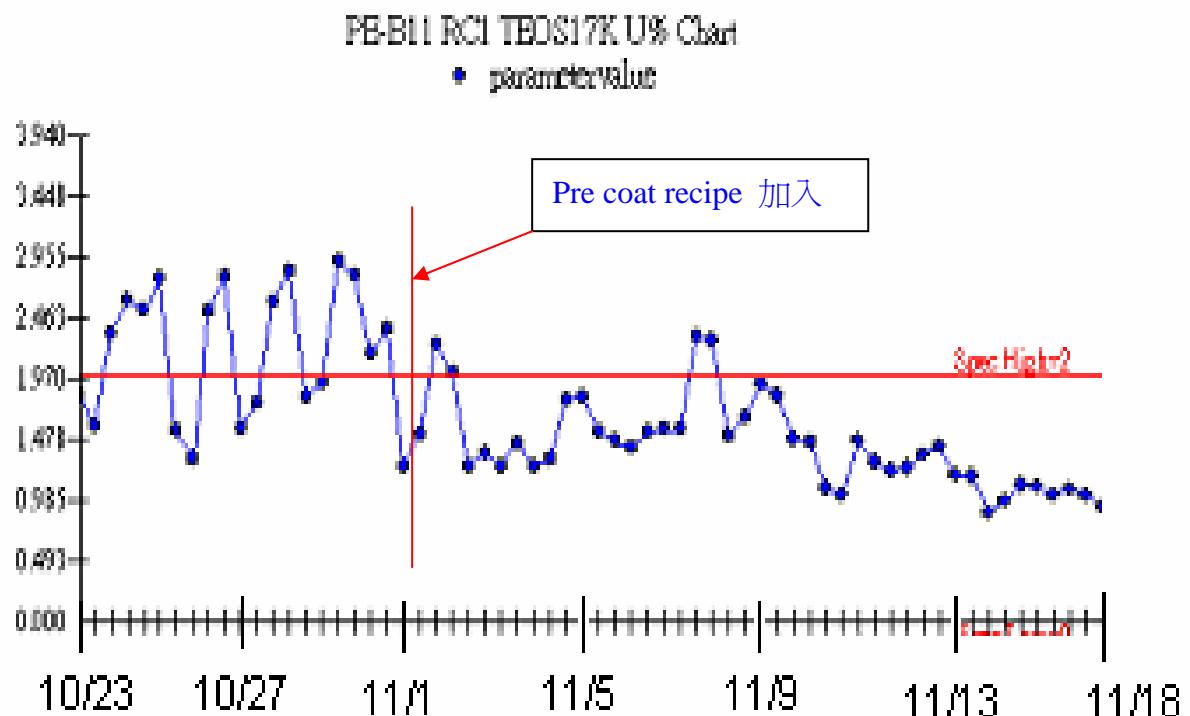

### ★Pre-coat 實驗結果

| Pre coat 厚度 | 晶圓計算         |           |

|-------------|--------------|-----------|

|             | Vdc unstable | Arcing 發生 |

| 0nm         | 49 wafers    | 1 wafer   |

| 100nm       | 12 wafers    | None      |

| 200nm       | 2 wafers     | None      |

| 300nm       | None         | None      |

50 wafers/Each run

Pre coat 對沉積在晶圓上薄膜特性影響比較

|                      | 沉積速率<br>(Depo rate)<br>(nm/min) | 均勻度<br>(Uniformity)<br>(%) | 應力(Stress)<br>(Mpa) | 微粒數目<br>(Particle<br>counts) >0.2um |

|----------------------|---------------------------------|----------------------------|---------------------|-------------------------------------|

| 標準<br>(Not Pre Coat) | 976                             | 1.82                       | -203                | 8                                   |

| Pre Coat<br>100nm    | 985                             | 1.63                       | -203                | 6                                   |

| Pre Coat<br>300nm    | 990                             | 1.80                       | -199                | 7                                   |

由累積之測機資料來看，Pre coat 能夠改善晶圓厚度之均勻度。

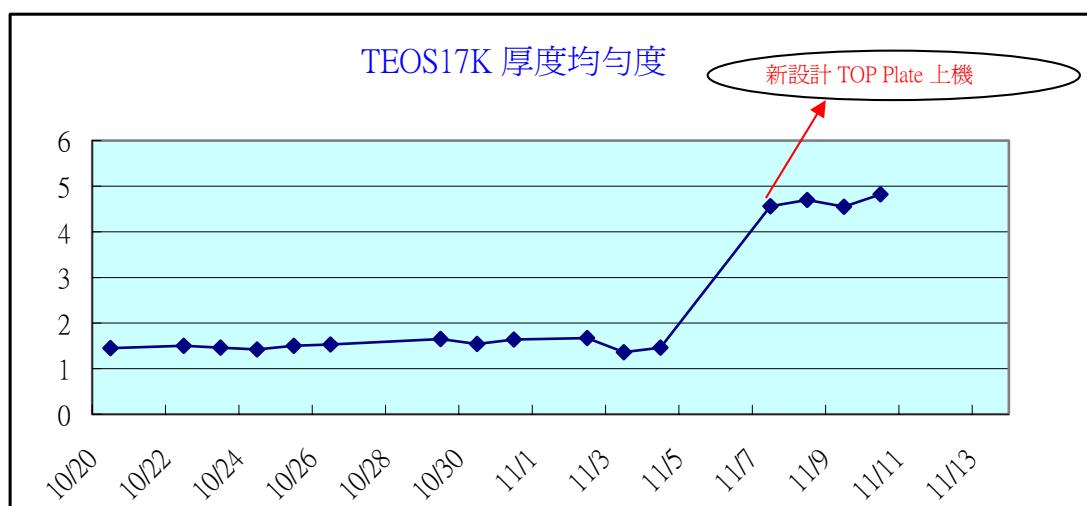

圖 4.3 Pre coat 加入後測機厚度均勻性

## 4-2 實驗方法二 使用不同厚度陽極膜之 Top Plate 比較

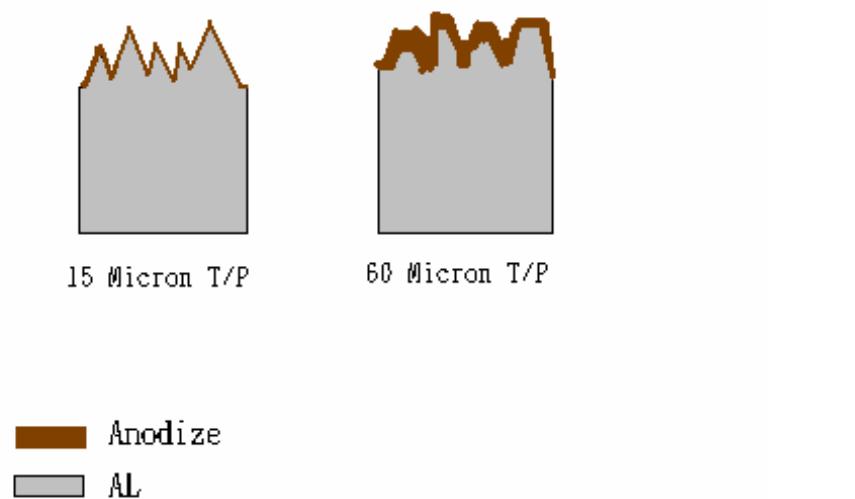

### 4-2-1. 陽極膜厚度與晶圓 Arcing 之關係

陽極膜(Anodize film)厚度愈薄，愈容易引起晶圓 Arcing，但愈厚之陽極膜或表面粗糙度愈小在製程應用上愈容易引起 wafer 黏片(Sticking)。

圖 4.4 陽極膜厚度

陽極膜之表面愈粗糙，F 級離子愈容易侵蝕

圖 4.5 電漿及氟離子侵蝕陽極膜

使用陽極膜(anodize film)厚度較厚之 Top plate 降低晶圓 Arcing 發生機率

改善效益→增加 Top plate 使用壽命,延長陽極膜使用時間

### ★ 不同陽極膜厚度 Top plate 實驗結果

| 陽極膜厚度 (um) | 表面粗度( $\mu$ ) | 晶圓 Arcing 發生之頻率 |

|------------|---------------|-----------------|

| 15         | 0.8           | 未發生             |

| 15         | 5.0           | 64%             |

| 0          | 0.8           | 100%            |

| 7          | 0.8           | 24%             |

| 30         | 0.8           | 未發生             |

| 45         | 5.0           | 未發生             |

25 wafers/Each run

總結陽極膜厚度及表面粗糙度對晶圓 Arcing 發生的影響

- 較厚的陽極膜較能夠預防晶圓 Arcing 之發生

- 完全無陽極膜保護之 Top plate, 會造成 100% 晶圓 Arcing 之發生

- 表面粗糙度較高之陽極膜比表面較平整之陽極膜更容易發生晶圓 Arcing

表 4.1 ASM 日本原廠 Top Plate 種類表〔11〕

### 1.3.1. Top plate

For different process, different types of top plate need to be installed. Usually, the non-blast, GB300, E-60 and N-type E-60 would be used.

| Top plate type                  | Non-blast | GB300        | GB300 C/P | E-60    | N-type E-60 | E-60 C/P |

|---------------------------------|-----------|--------------|-----------|---------|-------------|----------|

| Character                       | Two Rings | One Ring     | One ring  | No ring | No ring     | No ring  |

| Roughness(μm)                   | Smooth    | 1~2          | 1~2       | 3~5     | 3~5         | 3~5      |

| Roughness shape                 | ——        | VVVVV        | VVVVV     | VVV     | VVV         | VVV      |

| Process function                | SiSi      | TEOS or SiSi | TEOS      | TEOS    | TEOS        | TEOS     |

| USG pattern                     |           |              |           |         |             |          |

| Stress (compressive, dynes/cm²) |           | higher       | Normal    | Normal  | Normal      | lower    |

| Life time                       | =         | ○            | ○         | ○       | ○           | ○        |

| Wafer sticky                    | =         | ○            | ○         | ○       | ○           | ○        |

表 4.2 ASM 日本 Top Plate 出廠檢測單

受入検査成績表

執行部門:品質保証部門 品質係証G

作成日: 2005 年 7 月 15 日

| 品名      | TOP PLT  | 品番 | 70055-00889B | 承認 | 作成 |

|---------|----------|----|--------------|----|----|

| シリアルNo. | 50603H49 |    |              |    |    |

| 特記項目    |          |    |              |    |    |

#### 1. 外觀検査

測定方法: 目視

判定基準: 有害なバリ、傷、色むらまたは変色のないこと

測定結果: OK

#### 2. 寸法検査

##### 2-1. 平面度

測定方法: 検査用エハを表面に置き、指圧にてがたつきを見る

判定基準: がたつきのないこと

測定結果: OK

##### 2-2. 階極酸化膜厚および表面粗さ

###### 【階極酸化膜厚】

| 測定位置 | A    | B    | C    | D    | E    | ave.                |

|------|------|------|------|------|------|---------------------|

| 測定結果 | 14.0 | 17.0 | 15.0 | 15.0 | 17.0 | 15.60 $\mu\text{m}$ |

###### 【表面粗さ】

| 測定位置 | A-Eの測定値の平均値にて Ra 3~5 $\mu\text{m}$ |

|------|------------------------------------|

| 測定位置 | A                                  |

| 測定結果 | 3.80                               |

###### 参考

|      |

|------|

| 否認判定 |

|      |

帳票2#-1/JN:

QA-FM12-2000.2

日本エー・エス・エム株式会社

### 4-3 實驗方法三

改變製程參數條件之比較

評估條件

TEOS 流量(sccm)/ O<sub>2</sub>流量(sccm)/ 腔體壓力(Torr)/ 13.56 MHZ RF Power/ 430KHZ RF

標準條件 100 sccm/ 1000 sccm/ 3.5Torr / 480 kw/ 180 kw

| HRF            | 480  | 450  | 400 |

|----------------|------|------|-----|

| (W)            | ★    | ◇    | ○   |

| LRF            | 180  | 150  | 100 |

| (W)            | ★    | ★    | ◇   |

| Pressure       | 4.0  | 3.75 | 3.5 |

| Torr           | ○    | ★    | ★   |

| TEOS           | 120  | 100  | 80  |

| (sccm)         | ★    | ★    | ◇   |

| O <sub>2</sub> | 1200 | 1000 | 800 |

| (sccm)         | ★    | ★    | ★   |

○ 表示晶圓沉積正常

◇ 表示輕微 Discharge 發生

★ 表示不正常 Discharge 發生

由實驗得知當 RF power 變大時，Arcing 發生機率變大，直接原因是 RF power 強，離子轟擊效應對 Top plate 陽極膜所造成之破壞有放大效應，降低 RF Power 可降低 Arcing 發生機率，但由實驗得知改變 RF 功率將對沉積薄膜特性產生改變。

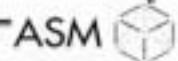

- RF power 對二氧化矽薄膜應力(Stress)之影響

增加低頻(LF 430 KHZ) RF 功率，可增加離子轟擊效應，降低薄膜 stress 應力，並且可改善薄膜之致密性〔12〕

### CONTROL OF FILM STRESS

圖 4.6 PECVD RF Power 與沉積薄膜應力特性圖

#### 4-4 實驗方法四.

試驗新設計之 Top Plate ,並比較其測機差異值.

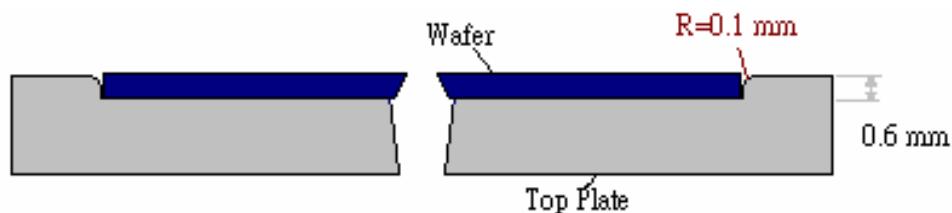

因為大部分之 Arcing 皆發生在 Top plate 凸起邊緣導角處，此邊緣導角之設計是為了防止晶片滑動，限制晶片移動，我們新設計了一種 Top plate，其邊緣以一片薄的不導電陶瓷(Ceramics) ring ，代替原廠 Top Plate 之導角設計，如下圖所示。

新設計之 Top Plate

原廠 Top plate

Ceramic edge ring 正面

Ceramic edge ring 反面

圖 4.6 新設計 Top Plate 圖形

圖 4.7 新設計 Top Plate edge ring

此新設計之 Top Plate，經上機實驗發現可能是因此種設計之 Top plate 包含了金屬鋁(AL)與 陶瓷 (Ceramic)兩種不同之材料，兩種材料之若熱傳導係數之差異造成晶片沉積時，二氧化矽薄膜厚度之均勻性變的很差，超出我們所需之規格上限，而無法使用。

|                                   | 導熱係數(watts/mm <sup>2</sup> )/(°C/mm) | 密度 Mg/m <sup>3</sup> |

|-----------------------------------|--------------------------------------|----------------------|

| 陶瓷 Al <sub>2</sub> O <sub>3</sub> | 0.029                                | 3.8                  |

| 鋁 AL                              | 0.22                                 | 2.7                  |

圖 4.8 新設計 Top Plate 測機膜厚均勻性

#### 4-5 實驗方法五.

修改 Top plate 導角，並比較其測機測機差異值

因為大部分之 Arcing 皆發生在 Top plate 凸起邊緣導角處，我們嘗試改良 Top plate 之突起導角弧度，避免尖端放電效應之產生。

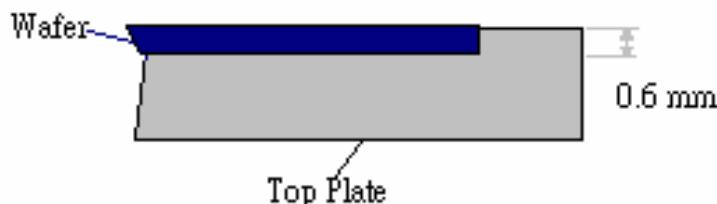

8 吋晶圓厚度約 0.8mm，Top plate 導角高度約 0.6mm

圖 4.9 原廠無修圓弧導角 Top plate 示意圖

圖 4.10 圓弧導角 Top plate 示意圖

| Data                                    | Arcig frequency<br>(Vdc unstable) | 均勻度<br>(Uniformity)<br>(%) | 應力(Stress)<br>(Mpa) | 微粒數目<br>(Particle counts)<br>>0.2um |

|-----------------------------------------|-----------------------------------|----------------------------|---------------------|-------------------------------------|

| Top plate                               |                                   |                            |                     |                                     |

| 0nm pre coat<br>15um anodize<br>無圓弧導角   | 1 wafer                           | 1.80                       | -205                | 5                                   |

| 300nm pre coat<br>15um anodize<br>無圓弧導角 | None                              | 1.65                       | -203                | 6                                   |

| 0nm pre coat<br>15um anodize<br>有圓弧導角   | None                              | 2.20                       | -200                | 48                                  |

50 wafers/Each run

由實驗測機資料可得知有圓弧導角之 Top plate，在 Particle 微粒增量及厚度之均勻度兩項測機值表現較差，尤其是微粒增量部份遠超出平均值。

## 第五章 結論與未來展望

### 5-1.結論

晶圓 Arcing 為晶圓廠內因製程條件改變而發生之問題，實驗結果得知，Arcing 發生頻率與 Top Plate 陽極膜特性有很大之關係，在尚未克服陽極處理技術之前，可利用 Pre coat、改用較厚之陽極膜、或是修改製程參數、改變 chamber 特性等來避免 wafer Arcing 之發生，利用 RF Vdc 趨勢也可預知 Arcing 的發生，提前將機台停機，作預防保養更換必要之零件，以預防生產線上昂貴之生產晶圓半產品大量報廢。

目前實驗方法得知，在晶圓沉積前將二氧化矽 pre coat 在 腔體及 Top Plate 上，可藉由二氧化矽之絕緣特性及 CVD Film 之填洞能力，修補 Anodize 陽極膜之缺損，是最有效也最經濟之預防方法，且 Pre Coat 長期來看可改善晶圓沉積厚度之均勻性，對機台生產時效的降低也屬可接受之影響範圍。

### 5-2.未來研究改善方向

- 1.利用 RF Vdc 在腔體蝕刻清潔(Etch clean ) 時偵測 Vdc 反轉現象來預防晶圓 Arcing，在使用上仍有誤偵測之現象發生，需經驗收集以降低誤判動作而造成機台停機及晶圓生產中斷而造成之損失。

- 2.利用 Pre coat 程式 + Vdc 反轉偵測是最有效之解決方案，但監控軟體以程式化開發仍有待發展。

- 3.利用增加 Vdc monitor board 即時(Real time) 監測 Vdc voltage 為未來發展趨勢。

- 4.由現有數據顯示，Arcing 發生在晶圓上的點對應在 Top plate 之位置，為 Top plate 為預防晶圓於沉積過程發生滑動而設計之突起狀，此突起設計易造成尖端放電效應，當電漿蝕刻長期作用下，陽極膜的破損也於此處發生，未來是否可以有更佳之設計能夠同時預防晶圓滑動又能兼顧陽極膜長成之品質也是值得研究之方向。

## 參考文獻

- [1] 張俊彥教授，積體電路製程及設備技術手冊， 經濟部技術處發行 1997.

- [2] ASM .Japan ,E-10 System documentation.

- [3] S. Wernick, R. Piner and P. G. Sheasby, The Surface Treatment and Finishing of Aluminum and its Alloys, vol.1, 4<sup>th</sup> edn, ASM International, 1987.

- [4] G. King, Surface Treatment and Finishing of Aluminum, Pergamon Press,1988.

- [5] Michael A.Liberman Allan J. Lichtenberg , Principles of Plasma Discharges and Materials Processing

- [6] 國立台北科技大學， 光電科技系 高立書局，UNIVERSITY Physics.

- [7] 詹國禎 朱建國 新文京開發出版社 電子與光電材料 .

- [8] Hong Xiao 著,羅正忠,張鼎張譯,Introduction to semiconductor manufacturing Technology , Person Education Taiwan P.376-378(2002)

- [9] 黃百炫，Geometrical Effects of the Ring Duct on the Uniformity of Thin-film Deposition in a 8" -PECVD Chamber，交通大學，2003.

- [10] KLA Tencor UV12X0 USER Manual , 1998

- [11] 莊達仁書局， VLSI 製造技術 高立書局 2000

- [12] 簡鈺人，Deposition and Etching of Silicon Nitride Thin Films by High Density Plasma Chemical Vapor Deposition system ，逢甲大學 2003.

- [13] 林佳玟 Effect of heat treatment of the microstructure and electrochemical characteristics of the anodized aluminum oxide ， 成功大學 2003.

- [14]林信安，Effect of anodizing on the properties of Aluminum Arc-sprayed Magnesium Alloys ， 大同大學 2002

- [15]游順源, Growth of SiC Thin Films by Inductively-Coupled plasma Chemical Vapor Deposition ，逢甲大學 2003.

- [16] Evert P. van de Ven, I-Wen Connick, Alain S. Harris Novellus Systems

- [17]李介民，變壓耦合式電漿二維流體模型與批次電漿蝕刻設備控制，交通大學，2004.

## 附錄 A 陽極處理技術簡介

### 鋁合金陽極處理(Anodizing):

陽極處理是化成皮膜 (Conversion Coating) 技術的一種，化成皮膜指的是利用化學或電化學處理，使金屬表面生成一種含有該金屬成份的皮膜層，例如鋅的鉻酸鹽皮膜處理，鋼鐵的磷酸鹽皮膜處理，鋁合金的陽極處理等，欲施行化成皮膜處理的金屬，其形成的化合物或氧化物必須不具水溶性，同時也不是粉狀物，亦即必須是連續皮膜。

一般鋁合金很容易氧化，氧化層雖有一定鈍化作用，但長期曝露之結果，氧化層仍會剝落，喪失保護作用，因此陽極處理的目的即利用其易氧化之特性，藉電化學方法控制氧化層之生成，以防止鋁材進一步氧化，同時增加表面的機械性質

#### .製程

於電解槽中，將金屬（如鋁或鋁合金）工件置於陽極，施加一定電壓與電流，促使工件表面形成附著良好的氧化層。簡要而言，發生下述反應：

一般而言，陽極處理工程流程例如下：

工件 → 脫脂 (I) → 水洗 → 化學光澤 (II) → 水洗 → 脫漬 (III) → 水洗 → 陽極處理 (IV) → 水洗 → 封孔 (V) → 水洗 → 乾燥

上述流程中，主要步驟的化學溶液如下：

(I) 有抑制劑之熱鹼洗液，60~70°C

(II)  $\text{H}_3\text{PO}_4 + \text{HNO}_3$  溶液，88~110°C

(III) 25~35%  $\text{HNO}_3$ ，常溫

(IV) 15%  $\text{H}_2\text{SO}_4$ ，21~25°C

(V) 100°C  $\text{H}_2\text{O}$

## 陽極處理電解液

鋁合金陽極處理使用的電解液有很多種，每一種電解液的主要化學成份不同，經其處理後的皮膜組織不同，性質也因之有所差異；有些場合即以電解液歸類製程。文獻資料有很多不同的配方例，以下每一種僅舉一例，但並非僅有此種配方。

### i) 硫酸液

如 Alumilite 製程含 15~20% 硫酸，電壓是 14~22 伏特，電流密度是  $1\sim2A/dm^2$ ，操作溫度  $18\sim25^\circ C$ ，處理時間 10~60 分鐘，皮膜厚度  $3\sim35\mu m$ ，皮膜呈無色透明。

硫酸液製程所得皮膜抗蝕性良好，而且抗磨耗性佳，此製程若將操作溫度降至  $5^\circ C$  以下，硫酸濃度降至 7% 左右，處理電壓提高至 23~120 伏特，可以長時間處理以獲得厚至  $200\mu m$  以上的硬質陽極皮膜，應用於需耐磨耗的場合。

### ii) 鉻酸液

如含 5~10% 鉻酸，電壓是 40 伏特，電流密度是  $0.15\sim0.30A/dm^2$ ，操作溫度  $35^\circ C$ ，處理時間 30 分鐘，所得皮膜約  $2\sim3\mu m$ ，皮膜呈灰色或灰綠色，具有良好的抗蝕性，但耐磨耗性較差，在應用上方能不需封孔。

### iii) 草酸液

如 Eloxit GX 製程含 3~5% 草酸，電壓是 40~60 伏特，電流密度是  $1\sim2A/dm^2$ ，操作溫度  $18\sim20^\circ C$ ，處理時間 40~60 分鐘，皮膜呈黃色，厚度  $10\sim65\mu m$ ，此製程成本高於硫酸液製程。操作溫度可以降至  $3\sim5^\circ C$ ，經長時間處理以獲得厚達  $625\mu m$  的皮膜。草酸液的色澤較多樣化。

#### iv) 磷酸液

如含 10% 磷酸，電壓是 10~12 伏特，電流密度較不定，操作溫度 23~25°C，處理時間 20~30 分鐘，皮膜呈無色，厚度 1~2 μm；磷酸液處理之皮膜孔隙較大，適於後續電鍍。

以上四種電鍍液較常用，其原因是，這四種電解液中形成皮膜時，實際上有一定的孔隙，允許鋁持續溶出以形成皮膜，同時其皮膜具有一定的溶解度，因此皮膜可以持續成長至其溶解速度與成長速度相等為止，但是，它種電解液如硼酸液，酒石酸液等，其生成的皮膜很緻密，不易再允許鋁經由電解溶出，因之僅能形成很薄的皮膜。

鋁合金陽極處理，可產生陽極氧化膜，提升防蝕能力，利用陽極處理外加電流，使的表面產生陽極膜，若能在後續封孔處理得當，可產生細緻氧化層，提高表面硬度及抗蝕性。多孔鋁陽極處理膜的氧化包含下列幾個反應:

##### (a) 離子反應

##### (b) 化學反應

##### (C) 時效過程

Anodizing 陽極處理的種類與程序

##### (d) 溶解反應

反應生成的產物不易溶於電解中，在皮膜乾燥時無法導電的一種強附著性皮膜，這種皮膜的生長主要是藉表面的溶解生成細孔以使電流繼續流通，皮膜一直增厚到有足夠的電阻阻止電流，使的生長速率等於溶解速率，而達到一定的極限，這種皮膜的最大厚度受到電解液種類和操作條件不同而有很大的差別。

封孔的目的是为了避免经阳极处理后的氧化膜受到污染及腐蚀，可用於封孔的方式有很多種，最簡單及方便的方式即是用熱水來封孔，下列為熱水封孔所產生的反應

當水溫低於 80°C 時為

當水溫高於 80°C 時為

未經封孔的陽極氧化膜在空氣中也會自動封孔，但是封孔效果不佳。

#### Anodizing 陽極處理的表面顏色與電解液

| 材料   | 電解液 | 膜厚        | 顏色  |

|------|-----|-----------|-----|

| 6061 | 硫酸  | 10~30 μm  | 灰色  |

| 6061 | 硫酸  | 30~50 μm  | 灰黑色 |

| 6061 | 硫酸  | 50~100 μm | 黑色  |

| 6061 | 草酸  | 10~30 μm  | 灰白色 |

| 6061 | 草酸  | 30~50 μm  | 灰色  |

| 6061 | 草酸  | 50~100 μm | 金黃色 |

| 5052 | 硫酸  | 10~30 μm  | 灰色  |

| 5052 | 硫酸  | 30~50 μm  | 黃黑色 |

| 5052 | 硫酸  | 50~100 μm | 黑色  |

| 5052 | 草酸  | 10~30 μm  | 淡黃色 |

| 5052 | 草酸  | 30~50 μm  | 黃色  |

| 5052 | 草酸  | 50~100 μm | 黃色  |

**陽極皮膜檢測** 膜厚:渦電流接觸式檢測、抗電壓測試、微硬度測試、鹽霧試驗、熱龜裂試驗 硝酸滴定試驗、表面粗度量測、外觀顏色檢查。

**影響陽極處理皮膜品質的因素(缺陷)** 鋁合金雜質的含量、機械加工、陽極處理時電流的大小、陽極處理所配合的電解液、其他。

陽極處理皮膜成長示意圖