# The Dependence of the Performance of Strained NMOSFETs on Channel Width

Lingyen Yeh, *Member, IEEE*, Ming Han Liao, *Student Member, IEEE*, Chun Heng Chen, Jun Wu, Joseph Ya-min Lee, Chee Wee Liu, *Senior Member, IEEE*, T. L. Lee, and M. S. Liang

Abstract—The dependence of the performance of strained NMOSFETs on channel width was investigated. When the channel width was varied, the stress in the channel varied accordingly. This changed the electron effective mass and, consequently, the ON-state current  $I_{\rm on}$ . By shrinking the channel width of a strained NMOSFET from 1 to 0.1  $\mu$ m and by keeping the channel length at 55 nm, the ON-state drain current per unit channel width was enhanced by 22%. The gate leakage current was also affected by the stress in the channel, which can be explained by the increase in hole barrier height at the Si/SiO<sub>2</sub> interface. Furthermore, when the film stress was increased by 1 GPa, the gate leakage current density  $J_g$  of a strained NMOSFET with a channel width of 0.1  $\mu$ m and a length of 55 nm under a negative bias -3 V was reduced by 63%.

*Index Terms*—Contact etch stop layer (CESL), high-stress silicon nitride, MOSFET, strained silicon.

## I. Introduction

THE USE OF a contact etch stop layer (CESL) is one of the key methods to boost the performance of nanometer-scale MOSFETs [1]–[3]. The stress in the channel of a CESL-strained MOSFET can be enhanced by increasing the CESL film stress and the CESL thickness and by optimizing the device structure [1], [2]. The stress in the channel is also observed to depend on the layout of a MOS transistor [3]. However, few studies have been carried out to increase the stress in the channel by properly choosing the channel width. The optimal channel width to reach an  $I_{\rm on}$  gain for a CESL-strained NMOSFET with a channel length of 55 nm has already been reported [4]. The stress in the channel is also found to affect the gate leakage current density  $J_g$ . However, the dependence of  $J_g$  on the channel width has not been fully investigated. This brief examined the dependence of  $I_{\rm on}$  and  $J_g$  on the channel width,

Manuscript received January 22, 2009; revised July 22, 2009. Current version published October 21, 2009. The review of this brief was arranged by Editor J. Woo.

- L. Yeh is with the Institute of Electronics Engineering, National Tsing Hua University, Hsinchu City 300, Taiwan, and also with Taiwan Semiconductor Manufacturing Company, Hsinchu City 300, Taiwan (e-mail: lyyeh. jcsu@msa.hinet.net).

- M. H. Liao, T. L. Lee, and M. S. Liang are with Taiwan Semiconductor Manufacturing Company, Hsinchu City 300, Taiwan.

- C. H. Chen and J. Y. Lee are with the Institute of Electronics Engineering, National Tsing Hua University, Hsinchu City 300, Taiwan.

- J. Wu is with Taiwan Semiconductor Manufacturing Company, Hsinchu City 300, Taiwan, and also with the Graduate Institute of Materials Science and Engineering, National Chiao Tung University, Hsinchu City 300, Taiwan.

- C. W. Liu is with the Department of Electrical Engineering, National Taiwan University, Taipei 106, Taiwan, and also with the National Nano Device Laboratories, Hsinchu City 300, Taiwan.

Digital Object Identifier 10.1109/TED.2009.2030542

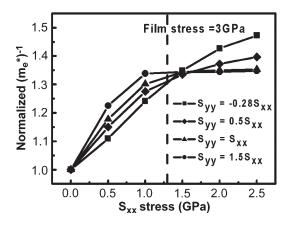

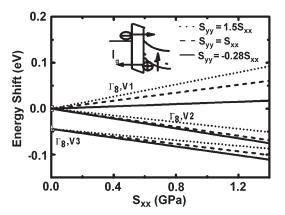

Fig. 1. Calculated inverse of the electron effective mass plotted as a function of  $S_{xx}$  in the channel. Various  $S_{yy}/S_{xx}$  ratios  $-0.28,\,0.5,\,1$  (biaxial stress), and 1.5 are depicted.

and its scope has been extended to the channel width for CESL-strained NMOSFETs with channel lengths ranging from 1  $\mu$ m to 55 nm.

## II. EXPERIMENT

In this brief, NMOSFETs were processed using shallow trench isolation (STI), nitrided-SiO<sub>2</sub> gate dielectric, n+ polycrystalline silicon gate, and tensile silicon nitride CESL [5]. The filling material of the STI was silicon oxide that was deposited by a high-density-plasma chemical-vapor-deposition (CVD) process. The STI process followed the conventional STI process reported in [6]. The effective oxide thickness was about 1.9 nm, which was measured on a large gate square and operated at 1.1 V. The CESL was deposited by a CVD process. The 3-D stress distribution with different device geometric structures was simulated by a 3-D finite element mechanical stress simulation program, ANSYS. In the simulation, the elastic analysis was restricted to the effect of the nitride layer on the channel [7]. The change in the effective mass under the stress was calculated by the  $k \cdot p$  model [8], [9].

# III. RESULTS AND DISCUSSION

Fig. 1 shows the calculated inverse electron effective mass  $m_e^*$  as a function of the simulated  $S_{xx}$ . Various  $S_{yy}/S_{xx}$  ratios of -0.28, 0.5, 1 (biaxial stress), and 1.5 are depicted.  $S_{xx}$  and  $S_{yy}$  represent the stresses in the channel, which are in parallel and transverse to the direction of the current flow. The inverse  $m_e^*$  is observed to increase with an increase in  $S_{xx}$  when the

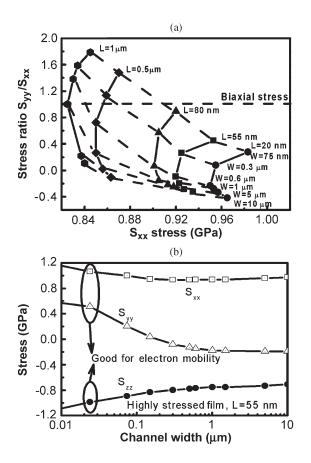

Fig. 2. (a) Calculated  $S_{yy}/S_{xx}$  plotted as a function of  $S_{xx}$  with various combinations of channel length and channel width. (b) Stress components plotted as a function of channel width for NMOSFETs with  $L=55\,\mathrm{nm}$ .

value of  $S_{xx}$  is smaller than about 1.5 GPa. Furthermore, the film stress after annealing must be greater than 3 GPa to give an  $S_{xx}$  of 1.5 GPa in the simulation. It is unlikely that silicon nitride would ever reach such a high tensile film stress [10]. Thus,  $S_{xx}$  that is below approximately 1.5 GPa has been the focus of this study. Moreover,  $m_e^*$  is observed to further reduce with an increasing ratio of  $S_{yy}/S_{xx}$  from -0.28 to 1.5.

Fig. 2(a) shows the ways to reach a high  $S_{yy}/S_{xx}$  (small  $m_e^*$ ) by optimizing the dimensions of the NMOSFETs. The calculated  $S_{yy}/S_{xx}$  was plotted as a function of  $S_{xx}$  with various combinations of channel length L and channel width W. For example, consider the curve with L = 55 nm in Fig. 2(a). It can be observed that, when W decreases from 10 to 0.6  $\mu$ m,  $S_{uu}/S_{xx}$  increases; however,  $S_{xx}$  decreases with the reduction in W. When W decreases further from 0.6  $\mu m$  to 75 nm,  $S_{yy}/S_{xx}$  keeps increasing with the reduction in W, but  $S_{xx}$ changes from a decreasing to an increasing value with the reduction in W. Fig. 2(b) (in our previous work, Fig. 1(b)[4]) provides an explanation for this phenomenon. When W is greater than 0.6  $\mu$ m,  $S_{yy}$  increases, whereas  $S_{xx}$  decreases, and, therefore,  $S_{yy}/S_{xx}$  increases with a reduction in W. Both  $S_{yy}$  and  $S_{xx}$  increase with a reduction in W when W is lesser than 0.6  $\mu$ m. The rate of increase in  $S_{yy}$  with decreasing W is observed to be about eight times of that for  $S_{xx}$ . As a result,  $S_{yy}$ is found to dominate the width dependence of  $S_{yy}/S_{xx}$ , and the  $S_{yy}/S_{xx}$  ratio is observed to increase with a reduction in W. In

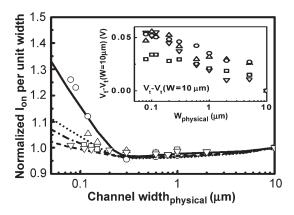

Fig. 3. Experimental  $I_{\rm on}$  per unit width compared to the theoretical calculation is plotted as a function of channel width. (—) Theoretical  $I_{\rm on}$ ,  $L_{\rm physical}=55\,{\rm nm}$  (quasi-ballistic model). (···) Theoretical  $I_{\rm on}$ ,  $L_{\rm physical}=80\,{\rm nm}$  (quasi-ballistic model). (···) Theoretical  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, \mu m}$  (drift-diffusion model). (o) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=55\,{\rm \, nm}$ . ( $\triangle$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=55\,{\rm \, nm}$ . ( $\triangle$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, \mu m}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, \mu m}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm physical}=0.5\,{\rm \, mm}$ . ( $\square$ ) Measured  $I_{\rm on}$ ,  $L_{\rm on}$

addition,  $S_{xx}$  is found to take up a minimum value when W is about 0.6  $\mu$ m, which gives rise to the turnaround in the curve with L=55 nm [Fig. 2(a)]. A similar analysis can be applied to other L values.

As shown in Fig. 2(a), to reduce  $m_e^*$  by a large  $S_{yy}/S_{xx}$  ratio, the smallest W should be used. Furthermore,  $S_{xx}$  and  $S_{yy}$  became more tensile, and  $S_{zz}$  became more compressive with a decrease in W, and this trend was preferred to increase the electron mobility [2], [4]. Thus, the preferred  $S_{xx}$ ,  $S_{yy}$ , and  $S_{zz}$  stresses and  $S_{yy}/S_{xx}$  ratio could be reached by adopting the smallest W value.

To prove the mechanism mentioned earlier, the measured  $I_{\mathrm{on}}$  per unit width of the strained NMOSFETs with various W and L values is presented in Fig. 3. By reducing the value of W from 1 to 0.1  $\mu$ m, the  $I_{\rm on}$  per unit width was observed to increase to about 1%, 2%, 7%, and 22% for L of 1  $\mu$ m,  $0.5 \mu m$ , 80 nm, and 55 nm, respectively. Furthermore, the magnitude of the increase in the  $I_{\rm on}$  per unit width increased with decreasing channel length mainly because of the smaller separation distance between the center of the channel and the sources of the applied stress with decreasing L. Thus, the film stress became more effective to affect the stress in the channel and reduce the electron effective mass. Furthermore, the film stress was also more effective in increasing  $I_{\rm on}$ . The stressinduced enhancement of the electron mobility was applied to the theoretical calculation of NMOSFETs with an L of 1 and  $0.5~\mu m$ , based on the drift-diffusion model [11]. However, ballistic transport was observed in nano-MOSFETs [12]. To resolve this problem, a quasi-ballistic transport model was used for nano-NMOSFETs with an L of 80 and 55 nm (Fig. 3). The details of the calculation using quasi-ballistic transport were reported in [8] and [12]-[14].

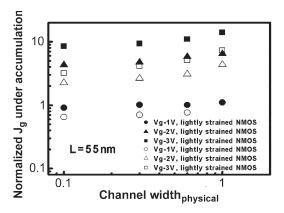

To further validate the stress mechanism discussed earlier,  $J_g$  under the stress described in Fig. 2(a) was also studied. Fig. 4 shows the measured  $J_g$  as a function of W under

Fig. 4.  $I_g$  of the highly and lightly strained NMOS devices is plotted as a function of channel width. The CESL stress for the highly strained devices is 1 GPa higher than that for the lightly strained ones.  $V_{

m substrate}=0~{

m V}$  in this measurement.

accumulation. Both the highly and lightly strained NMOSFETs were measured, and the CESL stress for the highly strained devices was 1 GPa higher than the lightly strained ones. The  $J_q$ of the highly strained NMOSFET with a W/L of 0.1  $\mu$ m/55 nm was reduced by 63% compared that of the lightly strained one under a negative bias of -3 V. Furthermore, the  $J_a$  of the lightly strained devices was reduced by about 17%, 33%, and 39% by decreasing W from 1 to 0.1  $\mu$ m under  $V_q$  biases of -1, -2, and -3 V, respectively, and that of the highly strained devices by about 40%, 48%, and 56%, respectively. Thus,  $J_q$  could be reduced by decreasing W from 1 to 0.1  $\mu$ m, and this effect was more obvious for the highly strained devices. Generally, the  $J_a$ of NMOSFETs with a smaller W was higher than those with a higher W because  $J_q$  near the STI edge was higher [15]–[17]. Hence, the  $J_q$  reduction in Fig. 4 may not have been caused by the STI process. Furthermore, the energy bands of the strained silicon and carrier distribution were altered by stress [2]. The influence of stress on the electron barrier height was relatively insignificant because the work functions of conductors and heavily doped polycrystalline silicon changed relatively little by stress [18]. Thus, the effect was mainly on holes. The calculation of the splitting of the sixfold degenerate valence band was reported in [19]. It involved linear splitting and spinorbit splitting, expressed in terms of deformation potentials. The spin-orbit splitting for silicon was very small ( $\sim 0.04 \text{ eV}$ ), and, hence, this term was neglected in the calculation. The required parameters to calculate the deformation potential can be obtained from [19]-[21]. The calculated result is shown in Fig. 5. A higher  $S_{yy}/S_{xx}$  value was observed to cause a greater shift of the valence band edge. Thus, the barrier height for light holes increased, and the probability of the hole injecting into the gate was reduced, which explains the reduction in  $J_q$ in Fig. 4. This  $J_q$  reduction was found to be more effective with decreasing channel length. This can be explained by the fact that the separation distance between the center of the channel and the sources of the applied stress became closer with decreasing channel length. As a result, for an NMOSFET with smaller channel length, the CESL film stress may become more effective to affect the stress in the channel and to increase the barrier height for light holes. Thus, the CESL film stress may be more effective in reducing  $J_q$ .

Fig. 5. Calculated valence band splitting of light holes (V1), heavy holes (V2), and split-off holes (V3) are plotted as a function of stress  $S_{xx}$ . Various  $S_{yy}/S_{xx}$  ratios from -0.28 to 1.5 are depicted.

#### IV. CONCLUSION

Thus, in this study, the dependence of the performance of silicon-nitride-strained NMOSFETs on channel width was investigated. When the value of W was varied, the stress in the channel varied accordingly. This changed  $m_e^*$  and, consequently,  $I_{\text{on}}$ . By reducing the value of W,  $S_{xx}$  and  $S_{yy}$  became more tensile,  $S_{zz}$  became more compressive, and the  $S_{yy}/S_{xx}$ ratio became higher. All these changes aided in the reduction in  $m_e^*$  and increased the value of  $I_{\rm on}$ . By decreasing the value of W from 1 to 0.1  $\mu$ m, the  $I_{\rm on}$  per unit width was observed to increase by about 1%, 2%, 7%, and 22% for an L of 1  $\mu$ m,  $0.5~\mu m$ , 80~nm, and 55~nm, respectively. The stress in the channel also reduced the value of  $J_q$ . This was explained by an increase in the barrier height for light holes. When the film stress was increased by 1 GPa, the  $J_q$  of an NMOSFET with a W/L of 0.1  $\mu$ m/55 nm was reduced by 63% under a negative bias of -3 V.

### REFERENCES

- S. Pidin, T. Mori, R. Nakamura, T. Saiki, R. Tanabe, S. Satoh, M. Kase, K. Hashimoto, and T. Sugii, "MOSFET current drive optimization using silicon nitride capping layer for 65-nm technology node," in *VLSI Symp. Tech. Dig.*, 2004, pp. 54–55.

- [2] S. E. Thompson, M. Armstrong, C. Auth, M. Alavi, M. Buehler, R. Chau, S. Cea, T. Ghani, G. Glass, T. Hoffman, C.-H. Jan, C. Kenyon, J. Klaus, K. Kuhn, Z. Ma, B. Mcintyre, K. Mistry, A. Murthy, B. Obradovic, R. Nagisetty, P. Nguyen, S. Sivakumar, R. Shaheed, L. Shifren, B. Tufts, S. Tyagi, M. Bohr, and Y. El-Mansy, "A 90-nm logic technology featuring strained silicon," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1790–1797, Nov. 2004.

- [3] A. Oishi, O. Fujii, T. Yokoyama, K. Ota, T. Sanuki, H. Inokuma, K. Eda, T. Idaka, H. Miyajima, S. Iwasa, H. Yamasaki, K. Oouchi, K. Matsuo, H. Nagano, T. Komoda, Y. Okayama, T. Matsumoto, K. Fukasaku, T. Shimizu, K. Miyano, T. Suzuki, K. Yahashi, A. Horiuchi, Y. Takegawa, K. Saki, S. Mori, K. Ohno, I. Mizushima, M. Saito, M. Iwai, S. Yamada, N. Nagashima, and F. Matsuoka, "High performance CMOSFET technology for 45 nm generation and scalability of stress-induced mobility enhancement technique," in *IEDM Tech. Dig.*, 2005, pp. 229–232.

- [4] M. H. Liao, L. Yeh, T.-L. Lee, C. W. Liu, and M.-S. Liang, "Superior nMOSFET performance by optimal stress design," *IEEE Electron Device Lett.*, vol. 29, no. 4, pp. 402–404, Apr. 2008.

[5] C. C. Wu, Y. K. Leung, C. S. Chang, M. H. Tsai, H. T. Huang,

- [5] C. C. Wu, Y. K. Leung, C. S. Chang, M. H. Tsai, H. T. Huang, D. W. Lin, Y. M. Sheu, C. H. Hsieh, W. J. Liang, L. K. Han, W. M. Chen, S. Z. Chang, S. Y. Wu, S. S. Lin, H. C. Lin, C. H. Wang, P. W. Wang, T. L. Lee, C. Y. Fu, C. W. Chang, S. C. Chen, S. M. Jang, S. L. Shue, H. T. Lin, Y. C. See, Y. J. Mii, C. H. Diaz, B. J. Lin, M. S. Liang, and Y. C. Sun, "A 90-nm CMOS device technology with high-speed, general-purpose, and low-leakage transistors for system on chip applications," in *IEDM Tech. Dig.*, 2002, pp. 65–68.

- [6] C. H. Yu, M. H. Chi, Y. H. Liou, Y. L. Tu, C. S. Wu, Y. S. Chen, C. Y. Pai, and C. S. Tsai, "Plasma charging defect characterization, inspection, and monitors in poly-buffered STI," *IEEE Trans. Semicond. Manuf.*, vol. 15, no. 4, pp. 478–485, Nov. 2002.

- [7] ANSYS Complete User's Manual, ANSYS Incorporation, Canonsburg, PA, 2004, p. 22, ver., 9.0.

- [8] M. H. Liao, C. W. Liu, L. Yeh, T.-L. Lee, and M.-S. Liang, "Gate width dependence on backscattering characteristics in the nanoscale strained complementary metal—oxide—semiconductor field-effect transistor," *Appl. Phys. Lett.*, vol. 92, no. 6, p. 063 506, Feb. 2008.

- [9] K. Uchida, T. Krishnamohan, K. C. Saraswat, and Y. Nishi, "Physical mechanisms of electron mobility enhancement in uniaxial stressed NMOSFETs and impact of uniaxial stress engineering in ballistic regime," in *IEDM Tech. Dig.*, 2007, pp. 129–132.

- [10] P. R. Chidambaram, C. Bowen, S. Chakravarthi, C. Machala, and R. Wise, "Fundamentals of silicon material properties for successful exploitation of strain engineering in modern CMOS manufacturing," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 944–964, May 2006.

- [11] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. Cambridge, U.K.: Cambridge Univ. Press, 2002, p. 423.

- [12] M. Lundstrom, "Elementary scattering theory of the Si MOSFET," *IEEE Electron Device Lett.*, vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [13] M. Lundstrom, "On the mobility versus drain current relation for a nanoscale MOSFET," *IEEE Electron Device Lett.*, vol. 22, no. 6, pp. 293– 295, Jun. 2001.

- [14] M.-J. Chen, H.-T. Huang, K.-C. Huang, P.-N. Chen, C.-S. Chang, and C. H. Diaz, "Temperature dependent channel backscattering coefficients in nanoscale MOSFETs," in *IEDM Tech. Dig.*, 2002, pp. 39–42.

- [15] T. Ohashi, T. Kubota, and A. Nakajima, "Ar annealing for suppression of gate oxide thinning at shallow trench isolation edge," *IEEE Electron Device Lett.*, vol. 28, no. 7, pp. 562–564, Jul. 2007.

- [16] A. H. Perera, J.-H. Lin, Y.-C. Ku, M. Azrak, B. Taylor, J. Hayden, M. Thompson, and M. Blackwell, "Trench isolation for 0.45 μm active pitch and below," in *IEDM Tech. Dig.*, 1995, pp. 679–682.

- pitch and below," in *IEDM Tech. Dig.*, 1995, pp. 679–682.

[17] W. Tonti, R. Bolam, and W. Hansch, "Impact of shallow trench isolation on reliability of buried- and surface-channel sub-μm PFET," in *Proc. IRPS*, 1995, pp. 24–29.

- [18] M. L. Lee and E. A. Fitzgerald, "Hole mobility enhancements in nanometer-scale strained-silicon heterostructures grown on Ge-rich relaxed Si<sub>1-x</sub>Ge<sub>x</sub>," *J. Appl. Phys.*, vol. 94, no. 4, pp. 2590–2596, Aug. 2003.

- [19] C. G. V. de Walle and R. M. Martin, "Band line ups and deformation potentials in the model-solid theory," *Phys. Rev. B, Condens. Matter*, vol. 39, no. 3, pp. 1871–1883, 1989.

- [20] C. Ohler, C. Daniels, A. Foster, and H. Luth, "Heterojunction band offsets and Schottky-barrier heights: Tersoff's theory in the presence of strain," *Phys. Rev. B, Condens. Matter*, vol. 58, no. 12, pp. 7864–7871, 1998.

- [21] R. Hull, *Properties of Crystalline Silicon*. London, U.K.: INSPEC, 1999, ser. EMIS Data Reviews Series, p. 404.

**Ming Han Liao** (S'07) received the B.S. degree in mechanical engineering and the Ph.D. degree in electric engineering from National Taiwan University, Taipei, Taiwan, in 2003 and 2007, respectively.

Since 2008, he has been with the R&D, Taiwan Semiconductor Manufacturing Company, Hsinchu City, Taiwan, where he is involved in strained Si technology and ultrashallow junction development. He has authored or coauthored more than 30 publications/conference proceeding papers/presentations.

Dr. Liao was the recipient of the Zhuo Zhang-Zong Scholarship Award in 2005 for his outstanding research work.

Chun Heng Chen was born in Taipei, Taiwan, in 1982. He received the B.S. degree in electrical engineering from National Chung Hsing University, Taichung, Taiwan, in 2005 and the M.S. degree in electronics engineering from National Tsing Hua University, Hsinchu City, Taiwan, in 2007, working on the electrical characterization and reliability of high-k dielectrics, where he is currently working toward the Ph.D. degree in silicon solar cells.

processing.

**Jun Wu** received the B.S. and M.S. degrees in materials sciences and engineering in National Tsing Hua University, Hsinchu City, Taiwan, in 1993 and 1997, respectively.

He is currently with the Graduate Institute of Materials Science and Engineering, National Chiao Tung University, Hsinchu City. He is currently with the R&D, Taiwan Semiconductor Manufacturing Company, Hsinchu City, where his work involves thin-film processing and strained silicon technology. His research interests include semiconductor

**Lingyen Yeh** (M'04) received the M.S. degree in materials science and engineering from National Tsing Hua University, Hsinchu City, Taiwan, in 1994.

Since 1994, he has been worked in the semiconductor industry in Taiwan. From 1994 to 1995, he was with the R&D, Holtek Semiconductor Incorporation. From 1995 to 2000, he was with the R&D, Winbond Electronics Corporation, and its subsidiary company Worldwide Semiconductor Manufacturing Company. Since 2000, he has been with the R&D, Taiwan Semiconductor Manufacturing Com-

pany, Hsinchu City. He is currently with the Institute of Electronics Engineering, National Tsing Hua University, Hsinchu City. He has done research work in CMOS devices, including shallow trench isolation, strained silicon, ultrashallow junction, thin dielectric film, and CMOS process integration. He has authored and coauthored more than ten papers and received more than ten U.S. patents.

**Joseph Ya-min Lee** received the B.S. degree from the Department of Physics, National Taiwan University, Taipei, Taiwan, in 1965 and the Ph.D. degree from the Department of Physics, University of Maryland, College Park, in 1972. His Ph.D. thesis work was done in the area of experimental solid-state physics.

From 1972 to 1975, he was an Associate Professor with the Department of Physics and the Department of Materials Science, National Tsing Hua University, Hsinchu City, Taiwan. From 1976 to 1987, he

worked in the U.S. semiconductor industry. From 1977 to 1981, he was with Carlsbad Research Center, Hughes Aircraft Company, Carlsbad, CA, and, from 1981 to 1987, with Hughes Research Laboratories, Malibu, CA. From 1987 to 1989, he was a Full Professor with the Department of Electrical Engineering and Applied Physics, Case Western Reserve University, Cleveland, OH. Since 1989, he has been a Full Professor with the Department of Electrical Engineering, National Tsing Hua University. He has done research work in experimental solid-state physics, semiconductor photodetectors, CMOS and CMOS/SOS devices, GaAs/AlGaAs real space transfer devices, high dielectric constant, and ferroelectric thin films for VLSI memory devices. He has published more than 115 scientific journal papers and authored seven books.

Chee Wee Liu (M'99–SM'00) received the B.S. and M.S. degrees in electrical engineering from National Taiwan University (NTU), Taipei, Taiwan, in 1985 and 1987, respectively, and the Ph.D. degree in electrical engineering from Princeton University, Princeton, NJ, in 1994.

He is currently a Professor with the Department of Electrical Engineering, NTU, where he is also with the Graduate Institute of Electronics Engineering. He is also with the National Nano Device Laboratories, Hsinchu City, Taiwan. His current research interests

include strained-Si/Ge FETs, SiGe photonics, Ge/Si on anything, high-k, metal gate, and bulk/thin-film solar cells. He invented the first MOS tunneling LEDs and photodetectors.

T. L. Lee, photograph and biography not available at the time of publication.

M. S. Liang, photograph and biography not available at the time of publication.