## Nonvolatile memory with switching interfacial polar structures of nano Si-inmesoporous silica

Jia-Min Shieh, Jung Y. Huang, Wen-Chien Yu, Jian-Da Huang, Yi-Chao Wang, Ching-Wei Chen, Chao-Kei Wang, Wen-Hsien Huang, An-Thung Cho, Hao-Chung Kuo, Bau-Tong Dai, Fu-Liang Yang, and Ci-Ling Pan

Citation: Applied Physics Letters 95, 143501 (2009); doi: 10.1063/1.3240888

View online: http://dx.doi.org/10.1063/1.3240888

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/95/14?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Controlled fabrication of Si nanocrystal delta-layers in thin SiO2 layers by plasma immersion ion implantation for nonvolatile memories

Appl. Phys. Lett. 103, 253118 (2013); 10.1063/1.4848780

Formation of iridium nanocrystals with highly thermal stability for the applications of nonvolatile memory device with excellent trapping ability

Appl. Phys. Lett. 97, 143507 (2010); 10.1063/1.3498049

Retention in nonvolatile silicon transistors with an organic ferroelectric gate

Appl. Phys. Lett. 94, 263507 (2009); 10.1063/1.3158959

Improved memory window for Ge nanocrystals embedded in SiON layer

Appl. Phys. Lett. 89, 162105 (2006); 10.1063/1.2362972

Polycrystalline silicon/CoSi 2 Schottky diode with integrated SiO 2 antifuse: a nonvolatile memory cell

Appl. Phys. Lett. 82, 4163 (2003); 10.1063/1.1581364

## Nonvolatile memory with switching interfacial polar structures of nano Si-in-mesoporous silica

Jia-Min Shieh, <sup>1,2,a)</sup> Jung Y. Huang, <sup>2</sup> Wen-Chien Yu, <sup>1</sup> Jian-Da Huang, <sup>2</sup> Yi-Chao Wang, <sup>2</sup> Ching-Wei Chen, <sup>2</sup> Chao-Kei Wang, <sup>1</sup> Wen-Hsien Huang, <sup>1</sup> An-Thung Cho, <sup>2</sup> Hao-Chung Kuo, <sup>2</sup> Bau-Tong Dai, <sup>1</sup> Fu-Liang Yang, <sup>1</sup> and Ci-Ling Pan<sup>2,3</sup>

<sup>1</sup>National Nano Device Laboratories, No. 26, Prosperity Road 1, Hsinchu 30078, Taiwan

(Received 28 September 2008; accepted 19 August 2009; published online 5 October 2009)

We show an artificially engineered electret with Si nanocrystals embedded in mesoporous silica for nonvolatile memory. We attribute the polarization to from polar layers lying at the interfaces between one-side bonded Si nanocrystals and mesoporous silica matrix. Under external field, the Si nanocrystals could be displaced in the porechannels causing displaced charge distributions and therefore a field-controllable electric polarization. Nonvolatile memory is demonstrated with a metal-oxide-semiconductor field-effect transistor. © 2009 American Institute of Physics. [doi:10.1063/1.3240888]

To satisfy the ever-increasing need for information flow and storage, the industry of semiconductor integrated circuits (ICs) has eagerly hunted for an ideal semiconductor memory technology with the high speed of static random access memory (RAM), the nonvolatility of flash, and the density of dynamic RAM. Nonvolatile memories (NVMs) can retain the data even when power is interrupted and are becoming a crucial component for the society of efficient energy utilization. In this regard, NVM based on the concept of storing information into the states of electric polarization had attracted much interest. In a ferroelectric field effect transistor with the gate dielectric layer being replaced by a ferroelectric thin film,<sup>2–4</sup> the electric polarization of the gate can be sensed by monitoring the magnitude of the source-drain current,<sup>2–4</sup> offering high speed random access,<sup>5</sup> low power consumption,<sup>2,4,5</sup> and nonvolatility.

The spontaneous polarization of a ferroelectric crystal with a noncentrosymmetric structure is mainly due to permanent dipoles that can switch directions under an action of electric field. Bulk silicon does not possess ferroelectric properties due to the diamond structure with centrosymmetry. To realize ferroelectric RAMs (FeRAM), tremendous efforts have been made to integrate nonsilicon-based ferroelectric films, such as lead zirconate titanate (PZT) and strontium bismuth tantalite (SBT), with the mature silicon memory technology. However, the interface reactions between PZT (SBT) and the Si substrate often generate mobile ions and lead to low data retention time. 2.3,7

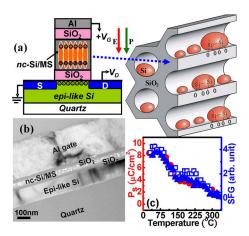

Recently, we had shown that interfacial properties could be employed to yield multifunctionality with polar Si–O nanostructures formed by asymmetrically embedding Si nanocrystals (nc-Si) in mesoporous silica (MS). In this letter, a full silicon-based metal-oxide-semiconductor field-effect transistor (MOSFET) NVM was demonstrated by using the artificially engineered electret. Figure 1(a) presents the

schematic of the NVM cell, where the electret film is sandwiched between two oxide buffer layers to serve as the gate dielectrics.

We prepared the test samples of nc-Si/MS by first depositing a 10-nm-thick SiO<sub>2</sub> buffer layer and then spin coating a 90-nm-thick MS nanotemplate layer on *n*- or *p*-type silicon. We thereafter synthesized Si nanocrystals in the MS templates with the high-density inductively coupled plasma method. By invoking an enhancement effect with an electrically biased substrate similar to the gap-filling/etching process used in IC manufacturing, we can create one-side bonded silicon nanocrystals with polar layer structures at the interfaces of nc-Si and MS as illustrated in Fig. 1(a). The biased growth condition can be prepared by applying an electrical power of 300 W at 300 kHz on the substrate during the synthesis of Si nanocrystals. Finally a 10-nm-thick SiO<sub>2</sub>

FIG. 1. (Color online) (a) Schematic diagram showing the one-side bonding geometry of Si nanocrystals in porechannels (right plot). A field-effect transistor structure with an Al/SiO<sub>2</sub>/nc-Si-in-MS/SiO<sub>2</sub> gate stack on an epilike Si layer was depicted in the left plot of (a) and its cross-sectional TEM image in (b). (c) The SFG signal is presented as the film temperature is increased (open squares) or decreased (filled triangles). For comparison, the temperature dependence of electric polarization is shown with filled circles.

<sup>&</sup>lt;sup>2</sup>Department of Photonics and Institute of Electro-Optical Engineering, National Chiao Tung University, 1001 Ta Hsueh Road, Hsinchu 30010, Taiwan

<sup>&</sup>lt;sup>3</sup>Department of Physics and Institute of Photonics Technologies, National Tsing Hua University, 101 Section 2, Kuang-Fu Road, Hsinchu 30013, Taiwan

<sup>&</sup>lt;sup>a)</sup>Author to whom correspondence should be addressed. Electronic addresses: jmshieh@ndl.org.tw and jmshieh@faculty.nctu.edu.tw.

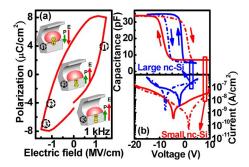

FIG. 2. (Color online) (a) The P-E hysteresis characteristics of the 90-nmthick Si-O polar layers sandwiched with 10-nm-thick SiO2 buffer layers in a MIM structure. Schematic drawings are presented in the inset to illustrate the switching process. The centers of gravity of the positive and negative charge distributions are labeled by  $\oplus$  and  $\Theta$ , respectively. (b) C-V hysteresis (top) and I-V characteristic curves (bottom) of a MOS capacitor containing an oxide stack identical to that in (a). For comparison, the C-V hysteresis of a MOS capacitor containing larger nc-Si contacting with the porechannels of MS (solid and dashed curves in blue) is also presented. Solid and dashed curves indicate the characteristics with a voltage sweep from positive to negative and from negative to positive, respectively. The top electrode pad of the device was made of aluminum film and 400- $\mu$ m in diameter.

layer was deposited on the MS films and an electrode was then formed to complete MOS and metal-insulator-metal (MIM) structures for capacitance-voltage (C-V) and polarization-electric field (P-E) measurements, respectively.

Optical sum-frequency generation (SFG) is sensitive to surface and polar structure of a material<sup>8,10</sup> and hereby was applied to verify the existence of the polar bonding layers in nc-Si/MS. The generated SFG signal<sup>8</sup> is presented in Fig. 1(c) as the open squares when the film temperature was raised from room temperature to 350 °C. Above this temperature, the SFG signal disappears. The curve with filled triangles displays the SFG signal as the film temperature was decreased from 350 °C to room temperature. The two curves are similar to each other, revealing the highly reversible nature of the SFG susceptibility.<sup>11</sup>

To verify that a nonvanishing electric polarization can be yielded from the polar bonding structure in nc-Si/MS with direction switchable with an external electric field, we probed the electrical polarization in the insulation layer of SiO<sub>2</sub> (10 nm)/nc-Si-in-MS (90 nm)/SiO<sub>2</sub> (10 nm) with P-E measurements. 11 The results are presented in Fig. 2(a). The polarization of the sample at E=0 V was found to be 5  $\mu$ C/cm<sup>2</sup>, which is much larger than the reported values for iron-passivated porous silicon. <sup>12</sup> The temperature dependence of saturated polarization  $P_s$  from the P-E measurements is presented in Fig. 1(c) with filled circles. Striking similarity between the temperature-dependent behaviors of electric polarization and SFG was observed, suggesting the SFG susceptibility and the electric polarization of the oneside bonded nc-Si-in-MS to have the same origin. Under the dipole approximation, SFG is necessarily allowed on surface/at an interface or in a film with polar structure. We therefore attribute the results shown in Figs. 1(c) and 2(a) to originate from the polar structure existing in the artificially engineered electret.

Typical C-V characteristics of a MOS structure with a similar oxide stack of SiO<sub>2</sub>/nc-Si-in-MS/SiO<sub>2</sub> on a p-type silicon substrate are presented in Fig. 2(b). A clockwise hysteresis loop with a positive-to-negative-to-positive voltage This a sweep was observed [see ithe red-colored curve in Fig.

2(b)],<sup>4,7</sup> yielding a memory window of 10 V. We had also verified that the C-V hysteresis loop changes from clockwise for samples prepared on p-type silicon to counterclockwise on *n*-type silicon substrate.  $^{2,4,7}$  Note that charging (discharging) of quantum dots (QDs) by electrons (holes) via a tunneling process can shift the flatband voltage to a more (less) positive value. 13 This leads to a counterclockwise 14 hysteresis loop on p-type silicon when a positive-tonegative-to-positive voltage sweep is carried out, which contradicts with what we had observed. Although a clockwise C-V hysteresis loop can also be yielded with charged QDs, the clockwise C-V hysteresis can only be generated as the sweep range of applied voltage is sufficiently large to enable the charged QDs to be neutralized by injected carriers.<sup>13</sup> We found that our clockwise C-V hysteresis loop on p-type silicon substrates is essentially independent of the sweep range. Furthermore, the leakage current through the  $SiO_2/nc$ -Si-in-MS/SiO<sub>2</sub> stack is below  $1 \times 10^{-7}$  A/cm<sup>2</sup> in the entire sweep range [see Fig. 2(b)], suggesting that the charging/discharging effect via a tunneling process in our sample is fairly minor. 15

The polar nature of the one-side bonded nc-Si/MS MOS capacitor is expected to disappear as the Si nanodots grow up to sufficiently large, making the circumferences of each Si nanodots to touch on the wall of the pore channels. In this case, we observed a counterclockwise C-V hysteresis, revealing the charge localization effect as shown by the bluecolored curves in Fig. 2(b). Assuming both of the C-V characteristics of nc-Si/MS capacitors to be produced completely by charge localization, we are expecting to find that a nc-Si/MS layer with larger nc-Si shall result in an increased gate current [see Fig. 2(b)], and therefore a wider memory window<sup>16</sup> (due to a higher charge density in the QDs). However, as shown in Fig. 2(b), an opposite result was observed. By summarizing these discoveries, we therefore attribute the clockwise C-V hysteresis of the MOS capacitor with oneside bonded nc-Si/MS on p-type silicon to originate from electric dipole layers.<sup>17</sup> In this case, the built-in dipole field from an electrical polarization in the MOS capacitor would either enhance or screen the external field depending on the direction of the applied field.

The quasipermanent interfacial polarization in our oneside bonded nc-Si/MS is switchable with an external field [Fig. 2(a)]. This is understandable by noting that the Si nanocrystals in porechannels can displace under an action of electric field, causing a displacement of the center of gravity of the negative charge distribution [labeled by  $\Theta$  in the inset of Fig. 2(a)] relative to that of the positive charge distribution (labeled by  $\oplus$  in the inset of Fig. 2(a)). We calculated that a relative displacement of the charge distributions across the interfacial layers of nc-Si/MS, which have a thickness of about 3-4 Å, can readily produce an electric polarization as large as 5  $\mu$ C/cm<sup>2</sup>. Schematic drawings are presented in the inset of Fig. 2(a) to facilitate the illustration of the switching process.

To test the feasibility of nc-Si/MS as a NVM, a MOSFET with a 55-nm-thick nc-Si/MS electret layer was fabricated. A 20-nm-thick oxide buffer layer underneath and above the nc-Si/MS film was introduced to inhibit charge transportation through the gate structure. The MOSFET with a channel length of 6  $\mu m$  and a channel width of 25  $\mu m$ was fabricated with a 120-nm-thick epilike silicon layer 18 on

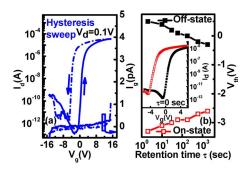

FIG. 3. (Color online) (a) A hysteretic switching  $I_{d}$ - $V_{\rho}$  curve for a MOSFET device with a gate structure of Al/SiO<sub>2</sub>/nc-Si-in-MS/SiO<sub>2</sub> with a fairly low gate current  $I_g$  was shown. (b) Data retention of the MOSFET is shown as the decaying behavior of threshold voltages  $V_{\rm th,on}$  (open squares) and  $V_{\rm th,off}$ (filled squares) with time  $(\tau)$  in the on state and off state. The inset shows that the transfer characteristics of the MOSFET at  $\tau$ =0 after the MOSFET was programmed to the on and off state with 20 ms duration  $V_g$  pulse of 15 and -15 V, respectively.

mission electron microscopy (TEM) image of the device around the gate region. The drain currents  $I_d$  as a function of gate voltage  $V_g$  are presented in Fig. 3(a). By keeping the drain voltage  $V_d$  at 0.1 V while increasing  $V_g$  from -15 to +15 with an increment of 0.1 V, we can switch the device from the "off" state to the "on" state with an off-state threshold voltage  $V_{\text{th,off}}$ =0.7 V. On the contrary, as the  $V_g$  sweeps from +15 to -15, the device can be switched off with an on-state threshold voltage  $V_{\text{th,on}} = -4.3 \text{ V}$  and yields a memory window of  $\Delta V = V_{\text{th,off}} - V_{\text{th,on}} = 5$  V.<sup>3,7</sup> The memory window saturates at 5 V as long as maximum sweeping voltage  $|V_g|$  is greater than 12 V. The drain current  $I_d$  of the MOSFET in the off state is about  $1 \times 10^{-12}$  A with  $V_g$ =0 V. In the on state,  $I_d$  can reach the level of  $1 \times 10^{-5}$  Å with  $V_{o}=0$  V. Thus, a contrast ratio of the on to the off state larger than 7 orders of magnitude is achieved [see the inset of Fig. 3(b)].

Note that the major causes of the short data retention time in a typical FeRAM can be (1) depolarization field effect and (2) finite gate leakage current.<sup>3,5</sup> Since our nc-Si/MS is intrinsically a low permittivity material, the depolarization field shall not cause a problem. The data retention time in a FeRAM device with a remnant polarization  $P_r$ , gate leakage current density I, and a trapping probability of  $\alpha$  can be estimated with  $\tau = P_r/I\alpha$ . In our MOSFET with nc-Si/MS electret, the measured remnant polarization  $P_r = 5 \mu \text{C/cm}^2$ and gate leakage current density  $3 \times 10^{-7}$  A/cm<sup>2</sup> implies a data retention time of  $T=10^5$  s to be achievable. The estimated retention time<sup>5</sup> with  $I_g \sim 0.5\,$  pA, the gate area and a trapping probability of 10<sup>-4</sup> agrees well with the measured result shown in Fig. 3(b), where the variation of threshold voltages  $V_{\text{th,on}}$  (open squares) and  $V_{\text{th,off}}$  (filled squares) as a function of lasting time in the on state and off state is pre-

In conclusion, we report an artificially engineered NVM electret material synthesized by embedding nc-Si in mesoporous silica. Material characterizations indicated that the nanocrystals form noncentrosymmetric bonding with the host silica matrix, yielding highly stable interfacial polar structures. We fabricated a MOSFET by using a nc-Si/MS layer in place of the gate dielectrics. The device exhibits a polarization-induced memory window of 5 V, a very low gate leakage and high ratio of the on state to the off state, promising for a fully silicon-based NVM technology with the potential of low cost and scalable to nanometer dimensions.

The authors would like to thank the National Science Council of the Republic of China, Taiwan for partially supporting this research.

<sup>1</sup>M. H. R. Lankhorst, B. W. S. M. M. Ketelaars, and R. A. M. Wolters, Nature Mater. 4, 347 (2005).

<sup>2</sup>T. P. Juan, C. Y. Chang, and J. Y. Lee, IEEE Electron Device Lett. **27**, 217

<sup>3</sup>T. Li, S. T. Hsu, B. D. Ulrich, and D. R. Evans, Appl. Phys. Lett. 86, 123513 (2005).

<sup>4</sup>C. Y. Chang, P. C. J. Trevor, and Y. M. L. Joseph, Appl. Phys. Lett. 88, 072917 (2006).

<sup>5</sup>T. P. Ma and J. P. Han, IEEE Electron Device Lett. 23, 386 (2002).

<sup>6</sup>S. Sakaia, M. Takahashia, K. Takeuchib, Q. H. Lia, T. Horiuchia, S. Wang, K. Y. Yuna, M. Takamiyac, and T. Sakuraic, Non-Volatile Semiconductor Memory Workshop and International Conference on Memory Technology and Design, Monterey, CA, 2008 (unpublished), pp.103-105

<sup>7</sup>T. Li, S. T. Hsu, B. D. Ulrich, L. Stecker, D. R. Evans, and J. J. Lee, IEEE Electron Device Lett. 23, 339 (2002).

<sup>8</sup>J. Y. Huang, J. M. Shieh, H. C. Kuo, and C. L. Pan, Adv. Funct. Mater. 19, 2089 (2009).

<sup>9</sup>G. M. Sessler, *Electrets* (Laplacian, Morgan Hill, 1999).

<sup>10</sup>X. Su, L. Lianos, Y. R. Shen, and G. A. Somorjai, Phys. Rev. Lett. 80, 1533 (1998).

<sup>11</sup>K. J. Choi, M. Biegalski, Y. L. Li, A. Sharan, J. Schubert, R. Uecker, P. Reiche, Y. B. Chen, X. Q. Pan, V. Gopalan, L. Q. Chen, D. G. Schlom, and C. B. Eom, Science 306, 1005 (2004).

<sup>12</sup>Q. Chen, X. Li, Y. Zhang, and Y. Qian, Adv. Mater. **14**, 134 (2002).

<sup>13</sup>S. Tiwari, F. Rana, H. Hanafi, A. Hartstein, E. F. Crabbe', and K. Chan, Appl. Phys. Lett. 68, 1377 (1996).

<sup>14</sup>D. N. Kouvatsos, V. L. Sougleridis, and A. G. Nassiopoulou, Appl. Phys. Lett. 82, 397 (2003).

<sup>15</sup>N.-M. Park, S.-H. Choi, and S.-J. Park, Appl. Phys. Lett. **81**, 1092 (2002). <sup>16</sup>N.-M. Park, S.-H. Jeon, H.-D. Yang, H. Hwang, S.-J. Park, and S.-H. Choi, Appl. Phys. Lett. 83, 1014 (2003).

<sup>17</sup>J. P. Han, S. M. Koo, C. A. Richter, and M. V. Eric, Appl. Phys. Lett. 85,

<sup>18</sup>J. M. Shieh, W. C. Yu, J. Y. Huang, C. K. Wang, B. T. Dai, H. Y. Jhan, C. W. Hsu, H. C. Kuo, F. L. Yang, and C. L. Pan, Appl. Phys. Lett. 94, 241108 (2009).