# On the Experimental Determination of Channel Backscattering Characteristics—Limitation and Application for the Process Monitoring Purpose

Wei Lee, Student Member, IEEE, and Pin Su, Member, IEEE

Abstract—This paper reports a generalized temperaturedependent channel backscattering extraction method that can selfconsistently determine the temperature sensitivity of the low-field mobility and the critical length in nanoscale MOSFETs. Through comparing the gate voltage and temperature dependence, we have shown that assuming constant temperature sensitivity of the low-field mobility and the critical length will result in unphysical backscattering characteristics. We have also investigated the limitation in this self-consistent method and proposed guidelines for experimental extraction. Our results show that channel backscattering is increased for NMOSFETs with higher body doping and HfO<sub>2</sub> dielectric and can be reduced for PMOSFETs when the process-induced uniaxial compressive strain technology is employed. This paper indicates that the self-consistent temperaturedependent method is competent to be routinely used in technology development for the process monitoring purpose.

*Index Terms*—Ballistic transport, channel backscattering, CMOSFET, process monitoring.

#### I. INTRODUCTION

$\mathbf{S}$  INCE the introduction of channel backscattering theory [1], [2], there has been great interest in determining how close to the ballistic limit the CMOS device can be operated. Indeed, the 2007 edition of the International Technology Roadmap of Semiconductors has reported that, to attain adequate drive current for the highly scaled MOSFETs, quasiballistic operation with enhanced thermal velocity and injection at the source end appears to be needed [3]. In addition, the continued aggressive scaling of CMOS is driving the industry toward a number of major technological innovations such as high-k dielectrics and uniaxial-strain technologies. Therefore, there is a strong motivation on developing techniques to experimentally estimate backscattering coefficient  $(r_{\rm sat})$  for providing guidelines in CMOS processes and determining impacts of modern technologies on the ballistic efficiency.

To this purpose, Lochtefeld and Antoniadis [4] have proposed a technique to determine the thermal limit (the ballistic limit) by comparing the measured effective velocity to the

Manuscript received December 5, 2008; revised May 27, 2009. First published August 25, 2009; current version published September 23, 2009. This work was supported in part by the National Science Council of Taiwan under Contract NSC 98-2221-E-009-178 and in part by the Ministry of Education in Taiwan under ATU Program. The review of this paper was arranged by Editor C. McAndrew.

The authors are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: jarjar.ee92g@nctu.edu.tw; pinsu@faculty.nctu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2028376

simulated injection velocity. Moreover, Barral et al. [5], [6] presented an experimental  $r_{\mathrm{sat}}$  extraction methodology with consideration of multisubband population based on the simulated corrective factor. Although both studies have originally presented determination of the ballistic efficiency, relying on simulation in extraction procedures is inconvenient to be routinely used in technology development. So far, to the best of our knowledge, the method in [7] and [8] evaluating  $r_{\rm sat}$  based on the temperature-dependent characteristics of drain current is the only fully experimental method and has been used for process-monitoring purposes [9]-[15]. However, this method assumes that the low-field mobility  $(\mu_0)$  is phonon limited and proportional to  $T^{-1.5}$ , which is questionable for state-of-the-art nanoscale MOSFETs [18]-[20]. For example, Ren et al. [19] have shown that the electron mobility in high-k (HfO<sub>2</sub>) devices is relatively insensitive to temperature ( $\sim T^{-1}$ ). Moreover, the temperature dependence of the critical length l may change with devices [20] and has not been considered. Therefore, a correct backscattering extraction method considering accurate temperature dependence of  $\mu_0$  and l is needed.

In this paper, we report a generalized temperature-dependent channel backscattering extraction that can self-consistently determine the temperature sensitivity of  $\mu_0$  and l in nanoscale MOSFETs. The validity of our method for the process monitoring purpose is assessed based on various types of devices: high versus low body doping, HfO<sub>2</sub> versus SiO<sub>2</sub> dielectric, and unstrained versus uniaxially strained. The organization of this paper is as follows. In Section II, we present the generalized temperature-dependent method and possible error sources. Then, we present several experimental guidelines in utilizing the generalized self-consistent method in Section III. In Section IV, the extracted coefficients on different kinds of devices are discussed. Finally, the conclusion will be drawn in Section V.

## II. SELF-CONSISTENT TEMPERATURE-DEPENDENCE METHOD

According to the channel backscattering theory [1], [2], the transistor drain current per channel width W in saturation region can be expressed as [21]

$$\frac{I_{d,\text{sat}}}{W} = Q_{\text{inv}} \left( \frac{1 - r_{\text{sat}}}{1 + r_{\text{sat}}} \right) \left\{ \sqrt{\frac{2k_B T}{\pi m^*}} \left( \frac{\Im_{\frac{1}{2}}(\eta_F)}{\Im_0(\eta_F)} \right) \right\}. \quad (1)$$

The first factor on the right-hand side (RHS) of (1) is the inversion layer charge at the top of the source-to-channel barrier

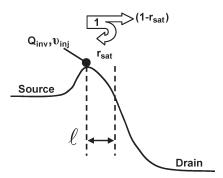

Fig. 1. Schematic diagram illustrating the backscattering theory [1]. Carrier in the critical length l has a backscattering ratio  $r_{\rm sat}$ . The average injection velocity  $v_{\rm inj}$  is determined by the equilibrium thermal velocity  $v_{\rm therm}$  and  $r_{\rm sat}$  as  $v_{\rm inj} = v_{\rm therm} (1-r_{\rm sat})/(1+r_{\rm sat})$ .

(Fig. 1), which is normally determined by the MOS electrostatics [2], i.e.,  $C_{\rm ox}(V_{\rm gs}-V_{T,\rm sat})$ , where  $C_{\rm ox}$  is the gate capacitance and  $V_{T,\rm sat}$  is the saturation threshold voltage. The second factor is defined as the ballistic efficiency  $B_{\rm sat}$  and describes the reduction of injection carriers due to channel backscattering  $r_{\rm sat}$ . The  $r_{\rm sat}$  depends on the mean-free path  $\lambda$  and the critical length l as  $r_{\rm sat}=1/(1+\lambda/l)$ . The third factor is the degenerate thermal velocity  $v_{\rm therm}$ , which is a function of the Fermi level  $E_F$  normalized to  $k_BT$ , i.e.,  $\eta_F=(E_F-E_i)/k_BT$  [21]. The temperature-dependent analytic model derived from (1) can be employed to extract the  $\lambda/l$  as well as  $r_{\rm sat}$  [10]

$$\frac{\partial I_{d,\text{sat}}}{I_{d,\text{sat}}\partial T} = \left[ -\frac{\partial V_{T,\text{sat}}}{(V_{\text{gs}} - V_{T,\text{sat}})\partial T} - \left( \frac{1}{1 + r_{\text{sat}}} + \frac{1}{1 - r_{\text{sat}}} \right) \frac{\partial r_{\text{sat}}}{\partial T} + \frac{1}{v_{\text{therm}}} \frac{\partial v_{\text{therm}}}{\partial T} \right]. \quad (2)$$

Note that we can obtain  $\partial r_{\rm sat}/\partial T = -[(1+\alpha+(\beta_{\mu}-\beta_{l})-\gamma)r_{\rm sat}(1-r_{\rm sat})]/T$  and  $\partial v_{\rm therm}/\partial T = (v_{\rm therm}\gamma)/T$  from the temperature dependence of  $\lambda/l$  and  $v_{\rm therm}$  [21], [22]

$$v_{\rm therm} = \sqrt{\frac{2k_B T}{\pi m^*}} \left( \frac{\Im_{1/2}(\eta_F)}{\Im_0(\eta_F)} \right) \propto T^{\gamma}$$

(3a)

$$\frac{\lambda}{\ell} \approx \frac{2k_B T \mu_0}{v_{\text{therm}} q L} \left( \frac{\Im_0(\eta_F)}{\Im_{-1}(\eta_F)} \right) \left( \frac{q V_{\text{DS}}}{k_B T} \right)^{\beta_l} \propto T^{1+\alpha+(\beta_\mu - \beta_l) - \gamma}$$

(3b)

where  $\alpha$ ,  $\beta_{\mu}$ ,  $\beta_{l}$ , and  $\gamma$  are defined as the temperature sensitivities of the degenerate factor [21], the low-field mobility  $\mu_{0}$ , the  $k_{B}T$  layer's width [32], and the thermal velocity  $\upsilon_{\rm therm}$ , respectively. L is the metallurgical channel length [32]. In [7]–[15], the nondegenerate limit  $\alpha=0$  [21],  $\beta_{\mu}=-1.5$ , and  $\beta_{l}=1$  were assumed. To generalize (3b), we propose using

$$\frac{\lambda}{\ell} \propto T^{\beta - \gamma} \tag{3c}$$

where  $(\beta - \gamma)$  accounts for the temperature sensitivity of  $\lambda/l$ . Then, we can obtain  $\partial r_{\rm sat}/\partial T = -[(\beta - \gamma)r_{\rm sat}(1 - r_{\rm sat})]/T$ . Finally, (2) can be expressed as follows [7], [8], [10], [16]:

$$\frac{\lambda}{\ell} = \frac{-2(\beta - \gamma)}{\gamma - \left(\frac{\partial I_{d,\text{sat}}}{I_{d,\text{sat}}\partial T} + \frac{\partial V_{T,\text{sat}}}{(V_{\text{gs}} - V_{T,\text{sat}})\partial T}\right)T} - 2. \tag{4}$$

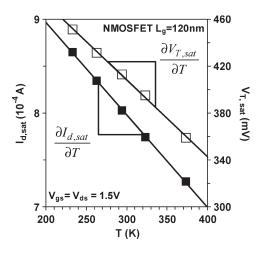

Fig. 2. Measured  $I_{d,\mathrm{sat}}$  and  $V_{T,\mathrm{sat}}$  versus T characteristics for the NMOSFET with  $L_g=120\,$  nm. Linear dependence of  $I_{d,\mathrm{sat}}$  and  $V_{T,\mathrm{sat}}$  on T is shown for  $T=233\sim373\,$  K.  $V_{T,\mathrm{sat}}$  is determined by maximum transconductance method with DIBL considered, i.e.,  $V_{T,\mathrm{sat}}=V_{T,\mathrm{lin}}-DIBL$ . DIBL is the gate-voltage difference between gate voltages at  $I_d=100\,$  nA/ $\mu$ m for  $V_{\mathrm{ds}}=0.05\,$  and 1.5 V.

Note that (4) is derived without the following assumptions:  $v_{\rm therm} = (2k_BT/\pi m^*)^{0.5}, \lambda = (2k_BT\mu_0/qv_{\rm therm}), l \propto (k_BT)^{\beta l}, \, \mu_0 \propto T^{\beta \mu}$ , and the nondegenerate limit. When  $\alpha = 0, \, \beta_\mu = -1.5, \, \beta_l = 1$ , and  $\gamma = 0.5, \, \beta = -1.5$  and (4) reduces to the original model used in [7]–[15]. Although (4) can be used to experimentally extract  $\lambda/l$  as well as  $r_{\rm sat}$  from the measured  $I_{d,{\rm sat}} - T$  and  $V_{T,{\rm sat}} - T$  characteristics, the validity of the extracted  $\lambda/l$  relies on the accuracy of  $I_{d,{\rm sat}}, V_{T,{\rm sat}}, \beta$ , and  $\gamma$ . In the following sections, we will examine each of the parameters separately.

Fig. 2 shows measured  $I_{d,sat}$  and  $V_{T,sat}$  versus temperature characteristics for the NMOSFET with  $L_g=120\,$  nm. Linear temperature dependence of  $I_{d,sat}$  and  $V_{T,sat}$  can be observed for  $T=233\sim373$  K. From the slope,  $\partial I_{d,\mathrm{sat}}/\partial T$ and  $\partial V_{T,\text{sat}}/\partial T$  can then be determined.  $V_{T,\text{sat}}$  was calculated from the linear threshold voltage  $V_{T,\mathrm{lin}}$ , which was determined by the maximum transconductance method at  $V_{\rm ds} = 0.05~{

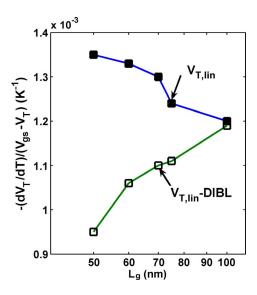

m V},$ with drain-induced barrier lowering (DIBL) consideration, i.e.,  $V_{T,\text{sat}} = V_{T,\text{lin}} - DIBL$ . DIBL was characterized from the subthreshold characteristics as in [7] and [10]. Using  $V_{T,\mathrm{sat}}$ instead of  $V_{T,\text{lin}}$  in estimating  $Q_{\text{inv}}$  is important to accurately account for the DIBL effect on the reduction of threshold voltage. Fig. 3 shows the calculated  $-(\partial V_T/\partial T)/(V_{\rm gs}-V_T)$ with and without DIBL consideration. Significant discrepancy can be seen as  $\mathcal{L}_g$  reduces. We have noted that the estimated  $-(\partial V_T/\partial T)/(V_{\rm gs}-V_T)$  with DIBL consideration shows the same  $L_q$  dependence as the simulated  $(\partial Q_{\rm inv}/\partial T)/Q_{\rm inv}$  in [20]. Moreover, to exclude the doping effect [20] and the nonequilibrium effect [28] on the validity of  $Q_{\rm inv} = C_{\rm ox}(V_{\rm gs} V_T$ ) for ultrashort channel devices, one can directly obtain  $(\partial Q_{\rm inv}/\partial T)/Q_{\rm inv}$  from the C-V measurement instead of using  $-(\partial V_T/\partial T)/(V_{\rm gs}-V_T)$  in (4). Note that the validity of  $Q_{\rm inv}\sim C_{\rm ox}(V_{\rm gs}-V_T)$  has been confirmed by the C-Vmeasurement in this paper.

From (3b) and (3c), we know that the physical meaning of  $\beta$  is related to the mean-free path  $\lambda$ , the low-field mobility  $\mu_0$ , and the critical length l. However, the backscattering extraction in [7]–[15] involves constant  $\beta$  (i.e.,  $\beta=-1.5$ ) that is not necessarily correct in state-of-the-art MOSFETs with technology

Fig. 3. Different estimations of  $-(\partial V_T/\partial T)/(V_{\rm gs}-V_T)$ .  $V_{T,\rm lin}$  is extrapolated from the maximum transconductance. DIBL was characterized from the subthreshold characteristics.

innovations (such as halo implantation, high-k dielectric, and strain technologies). There is evidence in plenty to show that carrier scattering mechanisms may change from phonon scattering  $(\beta_{\mu} = -1.5 \text{ [25]})$  to Coulomb scattering  $(\beta_{\mu} > 0)$  for devices with different size and technologies [17]-[19]. Moreover, one cannot consider  $\lambda$  independent of the carrier energy [30]. In addition, it has been suggested that the entire channel or a more significant part of the channel may participate in the backscattering [29], [30]. While the concept of the  $k_BT$ layer [2] can correctly explain MOSFET operation (at least in saturation), the temperature exponent of the critical length l may not necessarily be equal to one [18], [20], [32]. In other words, it is difficult to predict an accurate value of  $\beta$ for nanoscale state-of-the-art MOSFETs in the backscattering extraction. Therefore, we propose to use (3c) and (4) to determine  $\beta$  and  $\lambda/l$  self-consistently. The procedure starts with the first guess of  $\beta = -1.5$  and  $\gamma = 0.5$ . From (4), one can obtain  $\lambda/l$  at different T and, thus, the temperature power exponent of  $\lambda/l$ . Then, a new guess of  $\beta$  is made for a new  $\lambda/l$  versus T characteristics. This procedure is repeated until the constraint of (3c) is satisfied. Fig. 4 shows  $\lambda/l-T$  characteristics for the first guess of  $\beta = -1.5$  and the final self-consistently determined  $\beta = -1.185$ . It can be seen that the calculated  $\lambda/l$  with  $\beta=-1.5$  is proportional to  $T^{-1.3193}$ . From (3c), we obtain a value of  $\beta = -0.8193$ . It is worth noting that the selfconsistently determined  $\beta = -1.185$  lies in between  $\beta = -1.5$ and  $\beta = -0.8193$ . Moreover, the temperature dependent of  $\lambda/l$  can satisfy the constraint of (3c) for self-consistent  $\beta$ , but not for  $\beta = -1.5$ . Although the difference between the selfconsistently determined  $\beta$  and -1.5 is only 0.315, significant discrepancy in  $\lambda/l$  can be seen.

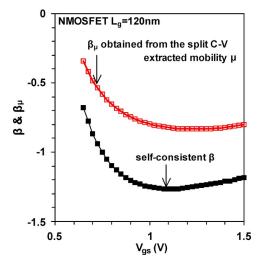

To further verify the extracted self-consistent  $\beta$ , we have directly extracted  $\beta_{\mu}$  based on the effective mobility  $\mu$ , measured by the split C-V method at  $V_{\rm ds}=5$  mV with the  $R_{\rm sd}$  correction as in [31]. Fig. 5 shows the comparison of self-consistent  $\beta$  and  $\beta_{\mu}$  for the device with  $L_g=120$  nm. Although the effective mobility  $\mu$  may not be identical to the low-field mobility  $\mu_0$  (as defined by  $\lambda$  [2], [21]), similar  $V_{\rm gs}$  dependence can be seen. The increased  $\beta_{\mu}$ , as well as  $\beta$  with decreasing  $V_{\rm gs}$ , manifests the

Fig. 4.  $\lambda/l$  versus T characteristics show the need of self-consistent  $\beta$  for the backscattering coefficient extraction. In [7]–[15],  $\beta=-1.5$  from  $\beta\sim 1+(\beta\mu-\beta_l),\,\beta\mu=-1.5$ , and  $\beta_l=1$ . Note that different values of  $I_{d,\mathrm{sat}}$  and  $V_{T,\mathrm{sat}}$  are considered in (4) at the corresponding temperature.

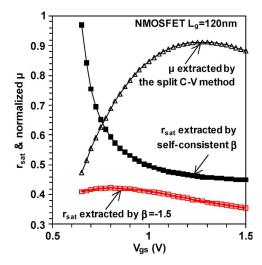

Fig. 5. Extracted  $\beta$  and  $\beta_{\mu}$  versus  $V_{\rm gs}$  characteristics for the NMOSFET with  $L_g=120$  nm.  $\beta_{\mu}$  ( $-\!\!\!\!\!-\!\!\!\!\!-\!\!\!\!\!-$ ) is observed based on the effective mobility  $\mu$ , which is extracted at different temperature by the split  $C\!-\!V$  method with  $R_{\rm sd}$  correction.

importance of Coulomb scattering in the weak inversion region [31]. Fig. 6 shows the extracted  $r_{\rm sat}$  and  $\mu$  for the NMOSFET with  $L_g=120$  nm. It can be seen that the assumption of  $\beta=-1.5$  results in insensitive  $r_{\rm sat}-V_{\rm gs}$  dependence. On the other hand, the  $r_{\rm sat}$  value extracted by the self-consistent  $\beta$  shows significant  $V_{\rm gs}$  dependence. The increased  $r_{\rm sat}$  with decreasing  $V_{\rm gs}$  results from the decreased  $\mu$  (through  $\lambda$ ) and manifests the importance of Coulomb scattering in the weak inversion region [31]. Moreover, the decreased potential gradient of the source-channel junction barrier (i.e., increased l) with decreasing  $V_{\rm gs}$  may also account for such  $V_{\rm gs}$  dependence of the  $r_{\rm sat}$  [8].

#### III. LIMITATION AND GUIDELINES

This self-consistent temperature-dependent method still has limitations because of the uncertainty in  $\gamma$ . From (3a), we know that  $\gamma$  decreases from 0.5 (nondegenerate limit:  $\eta_F \to 0$ ) to 0 (degenerate limit:  $\eta_F \to \infty$ ) with increasing  $V_{\rm gs}$ . Therefore,

Fig. 6. Extracted  $r_{\rm sat}$  and the effective mobility  $\mu$  versus  $V_{\rm gs}$  characteristics for the NMOSFET with  $L_q=120$  nm.

we propose using  $\gamma=0.5$  as a first approximation and then estimating the impact of the  $\gamma=0.5$  assumption on the extracted  $r_{\rm sat}$ . From  $r_{\rm sat}=1/(1+\lambda/l)$  and (4),  $\partial r_{\rm sat}/\partial \gamma$  can be expressed as

$$\frac{\partial r_{\text{sat}}}{\partial \gamma} = \frac{r_{\text{sat}} (1 - r_{\text{sat}})}{\gamma - \left(\frac{\partial I_{d,\text{sat}}}{I_{d,\text{sat}} \partial T} + \frac{\partial V_{T,\text{sat}}}{(V_{\text{gs}} - V_{T,\text{sat}}) \partial T}\right) T}.$$

(5)

We know from (4) and (5) that the RHS value of (5) is positive, which implies that an overestimated  $\gamma$  ( $\Delta\gamma$ ) may result in an overrated  $r_{\rm sat}$  ( $\Delta r_{\rm sat}$ ). Based on (5), we propose several experimental guidelines to increase accuracy of  $r_{\rm sat}$  extraction.

- 1) To reduce the impact of  $\Delta \gamma$ , one can reduce the RHS value of (5) by increasing the measurement temperature.

- 2)  $\Delta \gamma$  can also be reduced when temperature increases because the degenerate effect is reduced and  $\eta_F \to 0$  (i.e.,  $\gamma \to 0.5$ ).

- 3) Comparison under the same effective electrical field  $(E_{\rm eff})$  is needed to minimize  $\Delta r_{\rm sat}$  due to different  $\eta_F$ .  $E_{\rm eff} = (V_{\rm gs} + (n-1)V_T nV_{\rm FB} 2n\Phi_B)/3nT_{\rm OX}$ , where n is an empirical factor with the values  $\sim 2$  and  $\sim 3$  commonly used for electrons and holes, respectively [34].  $V_{\rm FB}$  is the flatband voltage, and  $\Phi_B$  is the potential difference between the Fermi level and the intrinsic Fermi level.

- 4) On the other hand,  $\Delta\gamma$  may be similar under the same  $E_{\rm eff}$  and can be neglected for the purpose of qualitative comparison.

- 5) Since  $\Delta \gamma$ , as well as  $\Delta r_{\rm sat}$ , varies with  $V_{\rm gs}$ , a comparison from weak inversion to strong inversion is suggested.

- 6) Once  $\gamma$  can be determined by other methods such as Monte Carlo simulations [20], one can use (5) to estimate  $\Delta r_{\rm sat}$  and correct the extracted  $r_{\rm sat}$ .

- 7) In case the  $Q_{\rm inv}$  is different from  $C_{\rm ox}(V_{\rm gs}-V_T)$ , one can directly obtain  $(\partial Q_{\rm inv}/\partial T)/Q_{\rm inv}$  from the C-V measurement [33] instead of using  $-(\partial V_T/\partial T)/(V_{\rm gs}-V_T)$  in (4).

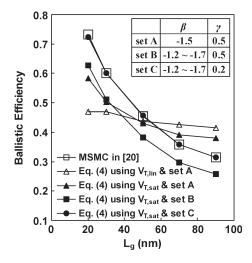

To further assess the impact of  $\Delta\gamma$  on  $r_{\rm sat}$ , the results of multisubband Monte Carlo (MSMC) simulation in [20] are investigated. Fig. 7 shows the calculated ballistic efficiency

Fig. 7. Calculated ballistic efficiency  $(1 - r_{\rm sat})/(1 + r_{\rm sat})$  versus  $L_g$  based on the MSMC results in [20]. In [20],  $\gamma \approx 0.2$  was extracted for different  $L_g$ .

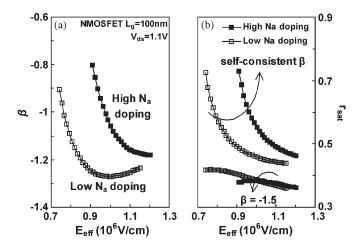

Fig. 8. (a) Extracted  $\beta$  and (b)  $r_{\rm sat}$  versus  $E_{\rm eff}$  characteristics for 100-nm  $L_g$  NMOSFETs with high and low body doping  $N_a$ .

$B_{\rm sat}$  versus  $L_g$  based on the results in [20]. It can be seen that after considering the  $V_{T,\rm sat}$  and  $L_g$  dependence of  $\beta$  in (4), the observed  $B_{\rm sat}$  for  $\gamma=0.5$  (set B) and 0.2 (set C) present almost the same  $L_g$  dependence as predicted by the MSMC simulation. Note that  $\gamma\approx0.2$  for different  $L_g$  was extracted in [20]. Moreover, Fig. 7 reveals the importance of  $L_g$  dependence of  $\beta$ . Since  $\beta$  can be physically determined, the self-consistent temperature-dependent method is competent to be routinely used in technology development for the process monitoring purpose. Three examples of technology comparison (including high versus low body doping, HfO<sub>2</sub> versus SiO<sub>2</sub> dielectric, and the impact of uniaxial strain) for the process monitoring purpose are presented in the next section.

#### IV. RESULT AND DISCUSSION

### A. High Versus Low Body Doping

Fig. 8 shows the extracted  $\beta$  and  $r_{\rm sat}$  versus  $E_{\rm eff}$  characteristics for the 100-nm  $L_g$  NMOSFETs with high and low body doping  $N_a$ . It is clear that the self-consistently determined  $\beta$  really presents the increased  $\beta_\mu$  due to increased Coulomb scattering for the high  $N_a$  device. Moreover, the impact of

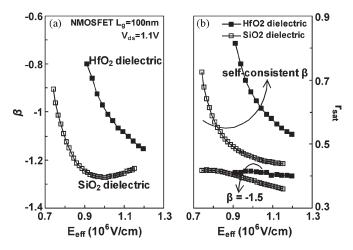

Fig. 9. (a) Extracted  $\beta$  and (b)  $r_{\rm sat}$  versus  $E_{\rm eff}$  characteristics for 100-nm  $L_g$  NMOSFETs with HfO $_2$  and SiO $_2$  gate dielectrics.

increasing  $N_a$  on  $r_{\rm sat}$  can be observed through comparing the extracted  $r_{\rm sat}$  in the whole  $V_{\rm gs}$  region. In contrast to the result for  $\beta=-1.5$ , the  $r_{\rm sat}$  extracted by the self-consistent  $\beta$  is increased for the high  $N_a$  device. The increased  $r_{\rm sat}$  is consistent with the prediction in [26] and may result from the reduced carrier mobility [24] due to increased Coulomb scattering.

### B. HfO2 Versus SiO2 Dielectric

Coprocessed NMOSFETs with HfO $_2$  and SiO $_2$  dielectrics were implanted by the same  $N_a$  condition and showed similar DIBL characteristics. Fig. 9 shows the extracted  $\beta$  and  $r_{\rm sat}$  versus  $E_{\rm eff}$  characteristics for the 100-nm  $L_g$  NMOSFETs with HfO $_2$  and SiO $_2$  dielectrics. It is worth noting that the self-consistently determined  $\beta$  is increased for the HfO $_2$  dielectric. The result is consistent with the simulation predictions in [19] and can be explained by the active low-energy interfacial phonons [19] and excess Coulomb scattering [27]. Moreover, reduced carrier mobility has been reported for high-k devices [19] and was expected to reduce  $\lambda$  as well as increase  $r_{\rm sat}$ . However, as shown in Fig. 9(b), the extracted  $r_{\rm sat}$  cannot respond to the reduced mobility unless the self-consistent  $\beta$  is applied.

#### C. Impact of Uniaxial Strain

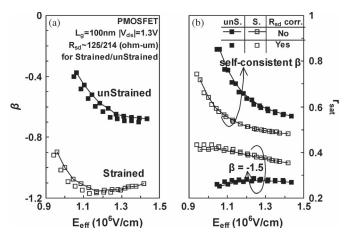

Process-induced uniaxially strained silicon technologies featuring compressive SiGe source/drain and compressive contact etch stop layer were employed for the strained device. Related strain characteristics of these devices have been reported in our previous studies [16], [23], [24]. Fig. 10 shows the extracted  $\beta$  and  $r_{\rm sat}$  versus  $E_{\rm eff}$  characteristics for the unstrained and strained PMOSFETs with  $L_g = 100$  nm, respectively. It can be seen that the self-consistently determined  $\beta$  is far from -1.5, particularly for the unstrained device. Similar behavior also shows in the measured  $I_{d,sat}-V_{gs}$  characteristics [16], in which the  $I_{d,\mathrm{sat}}$  of the strained device shows more phononlimited behavior (i.e.,  $I_{d,sat}$  decreases as temperature increases) and thus  $\beta$  decreases. Moreover,  $r_{\rm sat}$  is actually reduced in the compressive-strained PFET, which is contrary to previous studies [9], [10] using  $\beta = -1.5$ . Note that the  $\gamma = 0.5$ assumption may result in underestimation for the impact of

Fig. 10. (a) Extracted  $\beta$  and (b)  $r_{\rm sat}$  versus  $E_{\rm eff}$  characteristics for 100-nm  $L_g$  PMOSFETs with and without uniaxially compressive strain [23], [24]. The  $R_{\rm sd}$  effect has been corrected ( $R_{\rm sd}\sim 125~\Omega\cdot\mu{\rm m}$  for the strained device and 214  $\Omega\cdot\mu{\rm m}$  for the unstrained device).

compressive strain on the reduction of  $r_{\rm sat}$  because the degenerate effect is more significant for the strained PMOSFET, resulting in more overestimated  $\gamma$  as well as  $r_{\rm sat}$ . In addition, we have carefully extracted the source/drain resistance  $R_{\rm sd}$  (per one side) for strained ( $\sim$ 125  $\Omega \cdot \mu \rm m$ ) and unstrained devices ( $\sim$ 214  $\Omega \cdot \mu \rm m$ ), respectively [35]. The effect of  $R_{\rm sd}$  can then be considered by replacing  $V_{\rm gs}$  in (4) with ( $V_{\rm gs} - I_{d,\rm sat} R_{\rm sd}$ ) [7]. It is clear in Fig. 10(b) that  $r_{\rm sat}$  with the  $R_{\rm sd}$  correction is still reduced in the compressive-strained PFET.

#### V. CONCLUSION

We have reported a generalized temperature-dependent channel backscattering extraction method that can self-consistently determine  $\beta$  in nanoscale MOSFETs. Through comparing the  $V_{\rm gs}$  and temperature dependence, we have shown that assuming  $\beta_{\mu}$  and  $\beta_{l}$  constants will result in unphysical backscattering characteristics. We have also investigated the limitation in this self-consistent method and proposed guidelines for experimental extraction. Our results indicate that  $r_{\rm sat}$  is increased for NMOSFETs with higher  $N_a$  and HfO2 dielectric and can be reduced for PMOSFETs when the process-induced uniaxial compressive strain technology is employed. Since  $\beta$  and  $r_{\rm sat}$  can be physically determined by our developed program, the self-consistent temperature-dependent method is competent to be routinely used in technology development for the process monitoring purpose.

#### REFERENCES

- K. Natori, "Ballistic metal-oxide-semiconductor field effect transistor," J. Appl. Phys., vol. 76, no. 8, pp. 4879–4890, Oct. 1994.

- [2] M. S. Lundstrom, "Elementary scattering theory of the Si MOSFET," IEEE Electron Device Lett., vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [3] International Technology Roadmap for Semiconductors. [Online]. Available: http://www.itrs.net

- [4] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of carrier velocity in deeply scaled NMOS: How close to the thermal limit?" *IEEE Electron Device Lett.*, vol. 22, no. 2, pp. 95–97, Feb. 2001.

- [5] V. Barral, T. Poiroux, F. Rochette, M. Vinet, S. Barraud, O. Faynot, L. Tosti, F. Andrieu, M. Casse, B. Previtali, R. Ritzenthaler, P. Grosgeorges, E. Bernard, G. LeCarval, D. Munteanu, J. L. Autran, and S. Deleonibus, "Will strain be useful for 10 nm quasi-ballistic FDSOI devices? An experimental study," in VLSI Symp. Tech. Dig., 2007, pp. 128–129.

- [6] E. Bernard, T. Ernst, B. Guillaumot, N. Vulliet, V. Barral, V. Maffini-Alvaro, F. Andrieu, C. Vizioz, Y. Campidelli, P. Gautier, J. M. Hartmann, R. Kies, V. Delaye, F. Aussenac, T. Poiroux, P. Coronel, A. Souifi, T. Skotnicki, and S. Deleonibus, "Novel integration process and performances analysis of low standby power (LSTP) 3D multi-channel CMOSFET (MCFET) on SOI with metal/high-K gate stack," in VLSI Symp. Tech. Dig., 2008, pp. 17–19.

- [7] M.-J. Chen, H.-T. Huang, K.-C. Huang, P.-N. Chen, C.-S. Chang, and C. H. Diaz, "Temperature dependent channel backscattering coefficients in nanoscale MOSFETs," in *IEDM Tech. Dig.*, Dec. 2002, pp. 39–42.

- [8] M.-J. Chen, H.-T. Huang, Y.-C. Chou, R.-T. Chen, Y.-T. Tseng, P.-N. Chen, and C.-H. Diaz, "Separation of channel backscattering coefficients in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 9, pp. 1409–1415, Sep. 2004.

- [9] H.-N. Lin, H.-W. Chen, C.-H. Ko, C.-H. Ge, H.-C. Lin, T.-Y. Huang, and W.-C. Lee, "Channel backscattering characteristics of strained PMOSFETs with embedded SiGe source/drain," in *IEDM Tech. Dig.*, Dec. 2005, pp. 141–144.

- [10] H.-N. Lin, H.-W. Chen, C.-H. Ko, C.-H. Ge, H.-C. Lin, T.-Y. Huang, and W.-C. Lee, "Channel backscattering characteristics of uniaxially strained nanoscale CMOSFETs," *IEEE Electron Device Lett.*, vol. 26, no. 9, pp. 676–678, Sep. 2005.

- [11] K.-W. Ang, K.-J. Chui, H.-C. Chin, Y.-L. Foo, A. Du, W. Deng, M.-F. Li, G. Samudra, N. Balasubramanian, and Y.-C. Yeo, "50 nm silicon-on-insulator N-MOSFET featuring multiple stressors: Silicon-carbon source/drain regions and tensile stress silicon nitride liner," in VLSI Symp. Tech. Dig., 2006, pp. 66–67.

- [12] K.-W. Ang, H.-C. Chin, K.-J. Chui, M.-F. Li, G. Samudra, and Y.-C. Yeo, "Carrier backscattering characteristics of strained N-MOSFET featuring silicon-carbon source/drain regions," in *Proc. ESSDERC*, 2006, pp. 89–92.

- [13] M. H. Liao, C. W. Liu, L. Yeh, T.-L. Lee, and M.-S. Liang, "Gate width dependence on backscattering characteristics in the nanoscale strained complementary metal-oxide-semiconductor field-effect transistor," *Appl. Phys. Lett.*, vol. 92, no. 6, p. 063 506, Feb. 2008.

- [14] V. Barral, T. Poiroux, M. Vinet, J. Widiez, B. Previtali, P. Grosgeorges, G. Le Carval, S. Barraud, J. L. Autran, D. Munteanu, and S. Deleonibus, "Experimental determination of the channel backscattering coefficient on 10–70 nm-metal-gate double-gate transistors," *Solid State Electron.*, vol. 51, no. 4, pp. 537–542, Apr. 2007.

- [15] S. S. Chung, Y. J. Tsai, P. W. Liu, C. H. Tsai, Y. H. Lin, C. T. Tsai, G. H. Ma, S. C. Chien, and S. W. Sun, "A roadmap of backscattering for the strained CMOS devices in the ballistic regime," in *Proc. Silicon Nanoelectron. Workshop*, Kyoto, Japan, Jun. 2007, pp. 19–20.

- [16] W. Lee, J. Kuo, W. Chen, P. Su, and M. Jeng, "Impact of uniaxial strain on channel backscattering characteristics and drain current variation for nanoscale PMOSFETs," in VLSI Symp. Tech. Dig., Jun. 2009, pp. 112–113.

- [17] A. Cros, K. Romanjek, D. Fleury, S. Harrison, R. Cerutti, P. Coronel, B. Dumont, A. Pouydebasque, R. Wacquez, B. Duriez, R. Gwoziecki, F. Boeuf, H. Brut, G. Ghibaudo, and T. Skotnicki, "Unexpected mobility degradation for very short devices: A new challenge for CMOS scaling," in *IEDM Tech. Dig.*, Dec. 2006, pp. 1–4.

- [18] A. Khakifirooz and D. A. Antoniadis, "MOSFET performance scaling—Part I: Historical trends," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1391–1400, Jun. 2008.

- [19] Z. Ren, M. V. Fischetti, E. P. Gusev, E. A. Cartier, and M. Chudzik, "Inversion channel mobility in high-k high performance MOSFETs," in *IEDM Tech. Dig.*, Dec. 2003, pp. 33.2.1–33.2.4.

- [20] M. Zilli, P. Palestri, D. Esseni, and L. Selmi, "On the experimental determination of channel back-scattering in nanoMOSFETs," in *IEDM Tech. Dig.*, Dec. 2007, pp. 105–108.

- [21] A. Rahman and M. S. Lundstrom, "A compact scattering model for the nanoscale double-gate MOSFET," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 481–489, Mar. 2002.

- [22] E. Pop, C. O. Chui, S. Sinha, R. Dutton, and K. Goodson, "Electron-thermal comparison and performance optimization of thin-body SOI and GOI MOSFETs," in *IEDM Tech. Dig.*, Dec. 2004, pp. 411–414.

- [23] P. Su and J. J.-Y. Kuo, "On the enhanced impact ionization in uniaxial strained p-MOSFETs," *IEEE Electron Device Lett.*, vol. 28, no. 7, pp. 649–651, Jul. 2007.

- [24] W. P.-N. Chen, P. Su, and K.-I. Goto, "Investigation of Coulomb mobility in nanoscale strained PMOSFETs," *IEEE Trans. Nanotechnol.*, vol. 7, no. 5, pp. 538–543, Sep. 2008.

- [25] D. S. Jeon and D. E. Burk, "MOSFET electron inversion layer mobilities—A physically based semi-empirical model for a wide tempera-

- ture range," *IEEE Trans. Electron Devices*, vol. 36, no. 8, pp. 1456–1463, Aug. 1989.

- [26] T. Škotnicki, C. Fenouillet-Beranger, C. Gallon, F. Boeuf, S. Monfray, F. Payet, A. Pouydebasque, M. Szczap, A. Farcy, F. Arnaud, S. Clerc, M. Sellier, A. Cathignol, J.-P. Schoellkopf, E. Perea, R. Ferrant, and H. Mingam, "Innovative materials, devices, and CMOS technologies for low-power mobile multimedia," *IEEE Trans. Electron Devices*, vol. 55, no. 1, pp. 96–130, Jan. 2008.

- [27] T. Yamaguchi, R. Iijima, T. Ino, A. Nishiyama, H. Satake, and N. Fukushima, "Additional scattering effects for mobility degradation in Hf-silicate gate MISFETs," in *IEDM Tech. Dig.*, Dec. 2002, pp. 621–624.

- [28] M. V. Fischetti, L. Wang, B. Yu, C. Sachs, P. M. Asbeck, Y. Taur, and M. Rodwell, "Simulation of electron transport in high-mobility MOSFETs: Density of states bottleneck and source starvation," in *IEDM Tech. Dig.*, Dec. 2007, pp. 109–112.

- [29] A. Svizhenko and M. P. Anantram, "Role of scattering in nanotransistors," *IEEE Trans. Electron Devices*, vol. 50, no. 6, pp. 1459–1466, Jun. 2003.

- [30] E. Fuchs, P. Dollfus, G. Le Carval, S. Barraud, D. Villanueva, F. Salvetti, H. Jaouen, and T. Skotnicki, "A new backscattering model giving a description of the quasi-ballistic transport in nano-MOSFET," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2280–2289, Oct. 2005.

- [31] W. P.-N. Chen, P. Su, and K.-I. Goto, "Impact of process-induced strain on Coulomb scattering mobility in short-channel n-MOSFETs," *IEEE Electron Device Lett.*, vol. 29, no. 7, pp. 768–770, Jul. 2008.

- [32] M.-J. Chen and L.-F. Lu, "A parabolic potential barrier-oriented compact model for the  $k_BT$  layer's width in nano-MOSFETs," *IEEE Trans. Electron Devices*, vol. 55, no. 5, pp. 1265–1268, May 2008.

- [33] W. Lee, P. Su, K. Su, C. Chiang, and S. Liu, "Investigation of anomalous inversion C-V characteristics for long-channel MOSFETs with leaky dielectrics: Mechanisms and reconstruction," *IEEE Trans. Semicond. Manuf.*, vol. 21, no. 1, pp. 104–109, Feb. 2008.

- [34] K. Chen, H.-C. Wann, J. Dunster, P.-K. Ko, and C. Hu, "MOSFET carrier mobility model based on gate oxide thickness, threshold and gate voltages," *Solid State Electron.*, vol. 39, no. 10, pp. 1515–1518, Oct. 1996.

[35] D.-W. Lin, M.-L. Cheng, S.-W. Wang, C.-C. Wu, and M.-J. Chen, "A

- [35] D.-W. Lin, M.-L. Cheng, S.-W. Wang, C.-C. Wu, and M.-J. Chen, "A constant-mobility method to enable MOSFET series-resistance extraction," *IEEE Electron Device Lett.*, vol. 28, no. 12, pp. 1132–1134, Dec. 2007.

Wei Lee (S'03) was born in Taipei, Taiwan, in 1979. He received the B.S. degree from the Department of Engineering and System Science, National Tsing Hua University, Hsinchu, Taiwan, in 2001 and the M.S. degree from the Department of Electrical Engineering, National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 2003. He is currently working toward the Ph.D. degree in the Institute of Electronics, NCTU.

From 2003 to 2009, he conducted his doctoral research in physics and characterization of advanced

CMOS devices in the NCTU. He has also been an intern student with the Taiwan Semiconductor Manufacturing Company, Hsinchu. His research interests include mesophysics, carrier transport, single-electron transistors, channel backscattering characteristics, and silicon-based nanoelectronics.

**Pin Su** (S'98–M'02) received the B.S. and M.S. degrees in electronics engineering from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, and the Ph.D. degree from the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley.

From 1997 to 2003, he conducted his doctoral and postdoctoral research in silicon-on-insulator (SOI) devices at Berkeley. He was also one of the major contributors to the unified BSIMSOI model, the first industrial standard SOI MOSFET model for circuit

design. Since August 2003, he has been with the Department of Electronics Engineering, NCTU, where he is currently an Associate Professor. He has authored or coauthored over 85 research papers in international journals and conference proceedings. His research interests include silicon-based nanoelectronics, modeling and design for advanced CMOS devices, and device/circuit interactions in ultrascaled CMOS.