# A Wide Tuning Range G<sub>m</sub>–C Filter for Multi-Mode CMOS Direct-Conversion Wireless Receivers

Tien-Yu Lo, Chung-Chih Hung, Senior Member, IEEE, and Mohammed Ismail, Fellow, IEEE

Abstract—A third-order channel selection filter for multi-mode direct-conversion receivers is presented. The filter is designed with a Butterworth prototype and with the target wireless applications of Bluetooth, cdma2000, Wideband CDMA, and IEEE 802.11a/b/g/n wireless LANs. Linear-region MOS transistors are used to perform voltage-to-current conversion. The wide tuning range is achieved by the current multipliers and linear voltage-to-current converters. Implemented in the TSMC 0.18  $\mu m$  CMOS process, the measurement results show that the filter can operate successfully over a cutoff frequency range of 500 kHz to 20 MHz, and is compliant with the requirements of different wireless applications. The power consumption is 4.1 mW to 11.1 mW for minimum and maximum cutoff frequencies respectively from a 1.2 V supply voltage. The circuit performance compares favorably with previously reported works.

Index Terms—Current multiplier, direct-conversion receiver, multi-mode, transconductor, wide tuning range.

#### I. INTRODUCTION

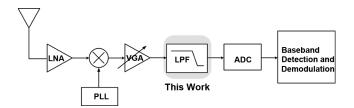

S THE LEVEL of integration in RF transceivers increases, CMOS emerges as the technology with the greatest potential for cost effectiveness where RF, mixed-signal and digital circuits are integrated in a single system-on-chip (SoC). This is particularly true when multi-mode wireless chip sets are embedded into mobile computing or multimedia systems. When designing a wireless receiver, one of the most important tasks is to design the channel filtering to separate the desired signal from the unwanted ones. Recent demand for multi-standard transceivers calls for adopting direct-conversion architectures to achieve the highest level of integration and for ease of system design. Fig. 1 shows a block diagram of a direct-conversion receiver. It converts the RF signal with both desired and unwanted signals, directly to baseband. Since the unwanted signals are still left at adjacent channel, the received signal is selected by the channel selection filter for further demodulation. However, an array or a stack of channel selection filters in a multi-standard radio design may not be power-efficient and would need large chip areas. Therefore,

Manuscript received November 27, 2007; revised April 11, 2009. Current version published August 26, 2009.

T.-Y. Lo is with MediaTek Inc., Hsinchu, Taiwan (e-mail: tienyu.lo@gmail. com)

C.-C. Hung is with the Department of Communication Engineering, National Chiao Tung University, Hsinchu, Taiwan (e-mail: cchung@mail.nctu.edu.tw).

M. Ismail is with the Department of Electrical and Computer Engineering, The Ohio State University, Columbus, OH 43210 USA (e-mail: ismail@ece.osu.edu).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2009.2023154

Fig. 1. Simplified block diagram of a direct-conversion receiver.

there is a strong motivation to realize a single baseband channel select filter such that it meets the requirements of multi-mode applications.

This work focuses on the design of such a multi-mode channel selection filter and is targeting direct-conversion radio architectures. The filter is designed based on a  $G_m$ –C filter topology, and has a wide continuous tuning range. The large tuning range is designed to meet the wireless specifications of Bluetooth (650 kHz), cdma2000 (700 kHz), Wideband CDMA (2.2 MHz), IEEE 802.11a/g (10 MHz), IEEE 802.11b (12 MHz), IEEE 802.11n (20 MHz) wireless LANs applications. These specifications cover the frequency range from 650 kHz to 20 MHz.

Most G<sub>m</sub>-C filters encounter noise and linearity tradeoff when they are utilized for large tuning-range application. They usually suffer from either low linearity or high noise. From system level analysis, the input-referred noise within the specified bandwidth can be determined by giving the RF front-end gain. The noise level defines the sensitivity of a receiver where the minimum acceptable level can be detected, and the gain of the RF front-end section should be chosen so that the output stage would not saturate under system specification. From the Friis equation, the noise figure (NF) of the receiver is given by

$$NF_{Total} = NF_{RF} + \frac{NF_{BB} - 1}{A_{RF}^2}$$

(1)

where NF<sub>Total</sub>, NF<sub>RF</sub> and NF<sub>BB</sub> are the noise figure of receiver, RF front-end, and analog baseband. The analog baseband includes the analog filter and the programmable gain amplifier. When the output impedance of the RF front-end is given by  $Rs_{\rm RF}$ , the input-referred noise of analog baseband section can be expressed as

$$NF_{BB} = 1 + \frac{v_{n,out}^2}{4kTRs_{RF}A_{BB}^2} = 1 + \frac{v_{n,in}^2}{4kTRs_{RF}}$$

(2)

where k is the Boltzmann coefficient and  $v_{n,in}^2$  is the input-referred noise power specified for 1 Hz bandwidth. Therefore, we can relax required noise specification by giving a larger RF

front-end gain. However, we should note that the linearity performance is defined by

$$\frac{1}{A_{\text{IP3,Total}}^2} = \frac{1}{A_{\text{IP3,RF}}^2} + \frac{A_{\text{RF}}^2}{A_{\text{IP3,BB}}^2}$$

(3)

where  $A_{\text{IP3,Total}}$ ,  $A_{\text{IP3,RF}}$  and  $A_{\text{IP3,BB}}$  are the input third-order intercept point (IIP3) of the system, RF front-end, and analog baseband sections. It is clearly shown that larger RF front-end gain will amplifier blockers and relax the noise performance of the baseband section. To define the noise specification in the system design, the RF front-end gain can be obtained by giving largest blocker in RF front-end stage, and can be enlarged by pushing the linearity requirement to the baseband stage. Then, the noise specification of the baseband stage can be relaxed. The analysis for a multi-mode receiver front-end requires a range of input signal magnitude specifications that cover all the operation modes. Assuming that the receiver provides a NF of 9 dB, an overall IIP3 of -9 dBm, and a gain requirement between 10 and 100 dB, the range of all the requirements for the baseband section is the result of an optimal tradeoff among gain, noise, and linearity throughout the receiver blocks. By giving the system analysis and the scenario simulated over the receiver, the acceptable levels of the filter IIP3 for GSM/cdam2000, Wideband CDMA, and IEEE 802.11 mode are 19.2 Bm, 21.1 dBm, and 19.6 dBm, respectively.

For the  $G_{\rm m}$ –C topology, a transconductor is used as a basic building block [1]–[5], and the transconductance value is proportional to the -3 dB cutoff frequency of the filter. The application mode is selected by changing the transconductance, and a tuning ratio of 30 is required. However, when process and temperature variations are taken into account, a tuning ratio of more than 50 should be achieved and the linearity performance should be still maintained at acceptable levels.

In this paper, Section II develops the proposed high linearity transconductor with a wide transconductance tuning range. The third-order Butterworth  $G_{\rm m}$ –C filter which meets the required specification is presented in Section III. Section IV presents the measurement results and compares the proposed design with the state of the art. Finally, conclusions are addressed in Section V.

### II. PROPOSED TRANSCONDUCTOR CIRCUIT

The main function of a transconductor is to convert the input voltage into the output current with a linear transformation factor, and the transconductor employed in filters must be linear over the input signal swing range. On the other hand, the transconductance should be tuned to compensate for process and temperature variations, and we can model it as a voltage controlled current source. In the circuit implementation, bipolar transistors offer wide transconductance tunable range because the collector current can be varied with little change in the base-emitter voltage. In contrast, the bias of the MOS transistors should be varied significantly and the supply voltage would then limit the tuning range, which implies the requirement of a higher supply voltage. Thus, a high linearity and wide tuning range transconductor in a low voltage CMOS technology would not only be needed for multi-mode wireless applications but also be helpful to combine with digital circuits for a system on a chip design.

# A. The Voltage-to-Current Conversion in CMOS Technology

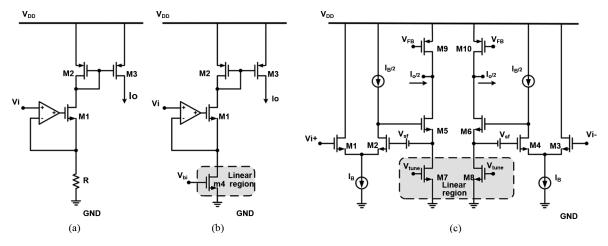

Fig. 2(a) shows a conventional transconductor, where the voltage-to-current conversion is obtained by using an operational amplifier through a passive resistor. The current is then sensed and mirrored to the output node. In this circuit, an array of resistors should be used to make the transconductance tunable. This method will increase the chip area and the precision of the transconductance would be limited by the choice of the programmable resistors. To achieve transconductance tuning, a single linear region transistor, shown in Fig. 2(b), is used to replace the passive resistor. This circuit is a MOSFET-only configuration. When the NMOS operates in the linear region, a linear drain current is obtained, and a linear voltage-to-current relationship for the circuit in Fig. 2(b) is presumably obtained. From a simplified BISM Level 3 model, the drain current is given by

$$I_{\rm D,lin} = K_{\rm lin}(V_{\rm GS} - V_{\rm thn})V_{\rm DS} - \frac{1}{2}\alpha K_{\rm lin}V_{\rm DS}^2$$

where  $\alpha = 1 + \frac{1}{2}\gamma \left(2\Phi_f + V_{\rm BS}\right)^{-1/2}$  (4)

where  $\gamma$  is the body effect factor and  $\Phi_f$  is the surface inversion potential.  $K_{\rm lin} = \mu_n C_{\rm ox}(W/L)$ , W and L are the width and length of the device, respectively,  $C_{\rm ox}$  is the oxide capacitance per unit channel area,  $\mu_n$  is the low-field mobility, and  $V_{\rm thn}$  is the NMOS threshold voltage.  $V_{\rm GS}$  and  $V_{\rm DS}$  are the gate-to-source and drain-to-source voltages, respectively. By taking the process and temperature variation into consideration,  $\alpha$  can be chosen to be a value of 1.2.

We can now see that the output current would not really hold a linear relationship to the input voltage owing to the additional second term in (4), which thus degrades the linearity of the transconductor. We can find that the second term in (4) forms a square-law equation. Previous research [6] reports that another transistor could be added to cancel out the second term in (4) based on the large signal square-law equation in the saturation region. Thus, the output current would be proportional to the input voltage, and the transconductance can be tuned by adjusting the bias voltage at the gate terminal. In the circuit, the -40 dB total harmonic distortion (THD) was reported. There are several disadvantages of this linearization technique. First, extra complex circuit should be included for current cancellation, and this technique needs an extra operational amplifier, which implies more power consumption. Second, the constraint of linear region operation,  $V_{\rm GS} - V_{\rm t} > V_{\rm DS}$ , should be held and this condition is hard to sustain under wide tuning requirement. Finally, it would not work well in modern nanoscale CMOS technologies owing to the fact that short channel effects would alter the square-law behavior and then degrades nonlinearity cancellation.

Since the compensation technique reported in [6] is based on a single-ended structure and is not suitable to provide the required high linearity and low power for transconductor design in modern CMOS process, a differential structure can be simply used to cancel out the second term in (4). Therefore, we can take the single-ended circuit of Fig. 2(b) and use it in a fully differential mode as shown in Fig. 2(c). To obtain the voltage-to-current

Fig. 2. (a) Conventional transconductor. (b) MOSFET-only transconductor. (c) Differential transconductor.

characteristics of the circuit, the input differential voltages at the gate of transistors M1 and M2, are given by

$$V_{i+} = V_{\rm cm} + \frac{v_d}{2}$$

(5)

$V_{i-} = V_{\rm cm} - \frac{v_d}{2}$  (6)

$$V_{i-} = V_{\rm cm} - \frac{v_d}{2} \tag{6}$$

where  $V_{\rm cm}$  is the input common-mode voltage and  $v_d$  is the input differential voltage. The gate terminals of the linear-region transistors M7 and M8 will be biased at an appropriate voltage,  $V_{\text{tune}}$ , to make sure the linear region operation is achieved. The second term in (4) can be cancelled out by the inherent differential structure, and thus the output current would be given by

$$i_{\text{out}} = K_{\text{lin}}(V_b - V_{\text{thn}} - \alpha V_{\text{cm}})v_d. \tag{7}$$

The equation shows that a linear voltage-to-current conversion is obtained, and that the output current is dependent on the bias voltage and the input common-mode voltage.

## B. The Proposed Transconductor With Tuning Scheme

Followed the basic concept of the differential structure in Fig. 2(c), wide range transconductance tuning is hard to achieve by adjusting  $V_{\mathrm{tune}}$  and  $V_{\mathrm{cm}}$  . In general,  $V_{\mathrm{tune}}$  should be biased at a higher voltage, such as the supply rail, and then the transistor would always work in deep linear region and perform a highly linear operation. Thus, a high linearity current multiplier would be required following the voltage-to-current conversion.

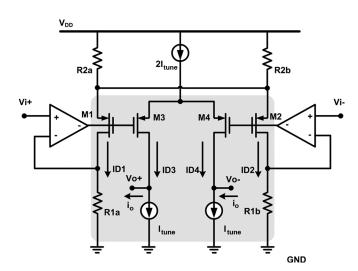

Fig. 3 shows the concept of the transconductor, which has a wide transconductance range. In the proposed transconductor, the linear voltage-to-current conversion is performed first, and then the transconductance is tuned over a wide range using the translinear loop that follows. The translinear loop is to provide the function of current multiplier. Through the use of the feedback loop, linear voltage-to-current conversion can be obtained owing to the fact that the input voltage would be equal to the drain voltage of transistors M1 and M2. Thus, the current flowing through resistors  $R_{1a}$  and  $R_{1b}$  would have a very high linearity relationship with the input voltage. The current multiplier is composed by transistors M1 to M4, resistors  $R_{1a}$  and

Fig. 3. Concept of a wide tuning range transconductor.

$R_{1b}$ , and current source  $I_{\text{tune}}$ . Transistors M1 to M4 are biased to operate in the weak inversion region while suitable device sizes are used. A single expression of the transistor model useful in weak, moderate, and strong inversion regions with  $V_{\rm DS}$  larger than a few times of the thermal voltage  $U_{\rm T}$ , is employed [7]

$$I_{\rm D} = I_{\rm S} \ln^2 \left[ 1 + e^{(V_{\rm GS} - V_{\rm TH})/2nU_{\rm T}} \right]$$

(8)

where  $I_{\rm S}$  is the fitting parameter, n is the subthreshold slope factor,  $V_{\rm th}$  is the transistor threshold voltage, and  $U_{\rm T}$  is the thermal voltage. The inversion factor defined by  $F = I_D/I_S$  is often used to define the boundaries between the MOS inversion regions. When  $F \gg 1$ , the operation region is corresponding to the strong inversion. On the opposite, the operation region is corresponding to the weak inversion when  $F \ll 1$ . The expression can fit the case of the general weak to strong inversion equations. For a MOSFET operating in the weak inversion region, its current exhibits an exponential dependence on  $V_{\rm GS}$ , and can be expressed from (8) to obtain

$$I_{\rm D} = I_{\rm D0} \frac{W}{L} \exp\left(\frac{V_{\rm GS} - V_{\rm th}}{nU_{\rm T}}\right) \tag{9}$$

where W and L are the width and the length of the transistor, respectively, and  $I_{\rm D0}$  is the reverse saturation current. From the above equation, we can find that

$$V_{\rm SG1} - V_{\rm th} = nU_{\rm T} \left( \frac{I_{\rm D1}}{I_{\rm D0}} \frac{L_1}{W_1} \right)$$

(10)

$$V_{\rm SG2} - V_{\rm th} = nU_{\rm T} \left( \frac{I_{\rm D2}}{I_{\rm D0}} \frac{L_2}{W_2} \right).$$

(11)

The device sizes of transistors M1 and M2 are set to be the same, and so are transistors M3 and M4. We can obtain from the linear conversion,  $I_{\rm D1} = I_1 + i_i$  and  $I_{\rm D2} = I_1 - i_i$ , where  $I_1 = V_{\rm cm}/R_{1(a,b)}$ . We can have

$$\Delta V = V_{\text{SG1}} - V_{\text{SG2}} = V_{\text{SG3}} - V_{\text{SG4}} = nU_{\text{T}} \ln \left( \frac{I_1 + i_i}{I_1 - i_i} \right). \tag{12}$$

The current output from the differential pair of transistors M3 and M4 can be expressed by

$$I_{\rm D3} = \frac{2I_{\rm tune}}{1 + e^{-\Delta V/nU_{\rm T}}} = \frac{2I_{\rm tune}}{1 + \left(\frac{I_{1} - i_{i}}{I_{1} + i_{i}}\right)}$$

$$= I_{\rm tune} + \frac{I_{\rm tune}}{I_{1}}i_{i} \qquad (13)$$

$$I_{\rm D4} = \frac{2I_{\rm tune}}{1 + e^{\Delta V/nU_{\rm T}}} = \frac{2I_{\rm tune}}{1 + \left(\frac{I_{1} + i_{i}}{I_{1} - i_{i}}\right)}$$

$$= I_{\rm tune} - \frac{I_{\rm tune}}{I_{1}}i_{i}. \qquad (14)$$

Finally, the output current  $i_o$  is given by

$$i_o = I_{\rm D3} - I_{\rm tune} = I_{\rm tune} - I_{\rm D4} = \frac{I_{\rm tune}}{I_1} i_i.$$

(15)

Thus, the output current is equal to a scaled value of the input current. The transconductance tuning can be achieved and the scaling can be determined by the bias current  $I_{\rm tune}$ . In the circuit, the transconductance in the weak inversion region can be expressed as

$$G_{\text{m,weak}} = \frac{I_{\text{tune}}}{V_{\text{cm}}}.$$

(16)

In case of a large  $I_{\rm tune}$  current, transistors M3 and M4 will enter into the saturation region while transistors M1 and M2 are still in the weak inversion region. From the equation of a differential amplifier in the saturation region, the output current  $i_{\rm O}$  can be expressed as

$$i_o = \frac{I_{\rm D3} - I_{\rm D4}}{2} = \frac{K_{3,4}}{4} (\Delta V) \sqrt{\frac{4I_{\rm tune}}{K_{3,4}} - \Delta V^2}$$

(17)

where  $\Delta V$  is the gate differential voltage expressed in (12), and the value can be simplified by neglecting high order terms from a Taylor series expansion. Therefore, we can have

$$\Delta V = nU_{\rm T} \ln \left( \frac{I_1 + i_i}{I_1 - i_i} \right) \approx nU_{\rm T} \frac{2i_i}{I_1}. \tag{18}$$

We can substitute (18) into (17) to obtain the output current. For a small  $\Delta V^2$  compared to  $4I_{\rm tune}/K_{3.4}$

$$i_o \approx \frac{K_{3,4}}{4} (\Delta V) \sqrt{\frac{4I_{\text{tune}}}{K_{3,4}}} = nU_{\text{T}} \frac{i_i}{2I_1} \sqrt{K_{3,4}I_{\text{tune}}}.$$

(19)

Then, the transconductance becomes

$$G_{m,sat} = nU_{T} \frac{\sqrt{K_{3,4}I_{tune}}}{V_{cm}}.$$

(20)

From the above equation, the transconductance can be adjusted by current  $I_{\rm tune}$ . We should note that the transconductance is dependent on the square value of  $I_{\rm tune}$  at this condition, rather than the linear scaled fashion in (16).

When the tuning current  $I_{\rm tune}$  becomes larger, transistors M3 and M4 will enter into the moderate inversion region. We can use (8) and F is defined between 0.1 and 10 to express moderate inversion operation. By using the expression for moderate inversion region, it is hard to have a simple general form for transconductance in the transconductor. Thus, the numerical behavior is applied to simulation, and the behavior shows that the tranconductance is in proportional to the function of current  $I_{\rm tune}$ , and has an inverse proportion to input common-mode voltage. The analysis also predicts the THD of less than -55 dB for the current multiplier in moderate inversion region where the worst case occurs at F=10. The scaled output current can be combined with the highly linear voltage-to-current conversion, and then the proposed wide tuning range linear transconductor can be achieved.

# C. The Final Circuit Implementation

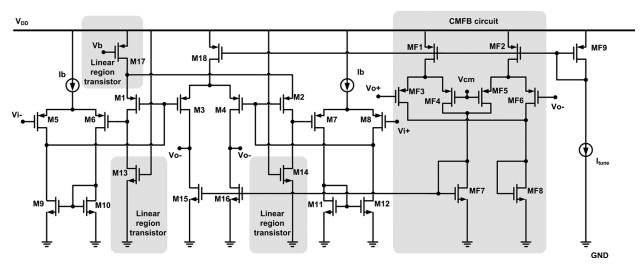

Fig. 4 shows the final circuit implementation of the proposed transconductor. The linear region transistors are used as the resistor  $R_1$  and  $R_{1b}$  in Fig. 3. Unfortunately, short channel effects still occur and high order nonlinearity components degrade the linearity of the V-I conversion, especially for nanoscale technologies because (4) is a simplified approximate model. Thus, any distortion components should be analyzed and a new design methodology should be applied to perform a high linearity conversion. For a linear region transistor, the transistor model which takes the mobility effect into consideration is expressed as [8]

$$I_{\rm D,lin} = K_{\rm lin} \left[ \frac{(V_{\rm GS} - V_{\rm thn}) V_{\rm DS} - \frac{1}{2} \alpha V_{\rm DS}^2}{1 + \theta (V_{\rm GS} - V_{\rm thn})} \right] \cdot \left\{ 1 + \frac{R_{\rm eq} K_{\rm lin}}{V_{\rm DS}} \left[ \frac{(V_{\rm GS} - V_{\rm thn}) V_{\rm DS} - \frac{1}{2} \alpha V_{\rm DS}^2}{1 + \theta (V_{\rm GS} - V_{\rm thn})} \right] \right\}^{-1}$$

(21)

where  $\theta$  is the mobility reduction coefficient and  $R_{\rm eq}$  is the default device equivalent resistance in the linear region. In the equation, the value of  $\alpha$  would be set to one for simplification. By giving  $V_{\rm GS,13}=V_{\rm GS,14}=V_{\rm DD},\,V_{\rm DS,14}=V_{\rm cm}+v_d/2,$  and  $V_{\rm DS,13}=V_{\rm cm}-v_d/2,$  we can derive the voltage-to-current characteristic of MOS transistors M13 and M14. To analyze the linearity of the  $V_{\rm DS}$  voltage against the drain current, a Taylor

Fig. 4. Final implementation of the proposed transconductor with the CMFB circuit.

series expansion is used and then the relationship would be expressed by

$$I_{D,lin} = I_{D14} - I_{D13}$$

$$= a_{1,lin}v_d + a_{2,lin}v_d^2 + a_{3,lin}v_d^3$$

$$+ a_{4,lin}v_d^4 + \dots$$

(22)

where  $a_{1,lin}$  and  $a_{3,lin}$  are as given in the equation at the bottom of the page.

Therefore, the third-order harmonic distortion term can be approximated to (23), shown at the bottom of the page.

Owing to the non-ideal characteristic of the linear region MOS transistor, the linearity performance would be degraded. In the equation, the first-order term defines the transconductance of the MOS resistor. The even-order harmonic terms can be cancelled out by the differential structure and thus the third-order harmonic distortion would become the dominant component. We can find that to minimize the third-order distortion term of the circuit, a small  $V_{\rm cm}$  should be taken. In the theoretical analysis, a 20 dB increase can be achieved for a 3 dB decrease of the input common-mode voltage. However,

compared with the calculated value, an 18.8 dB increase of linearity performance is obtained in simulation, and a value of smaller than -60 dB can be achieved for an optimized input common-mode voltage. In addition, since resistors  $R_{2a}$  and  $R_{2b}$  shown in Fig. 3 are used to provide a suitable bias point when tuning the transconductance, the resistance would be small in our circuit and can be replaced by a transistor in the linear region. Therefore, the transistor M17 with large aspect ratio in Fig. 4 is introduced.

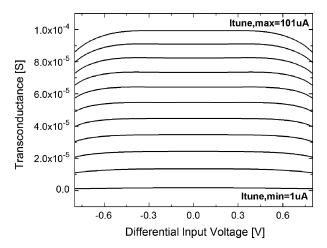

Fig. 5 shows the large signal simulation with respect to the function of the differential input voltage. The tuning range of 2  $\mu$ S to 110  $\mu$ S corresponding to the scaled value of current  $I_{\rm tune}$  can be obtained. The tuning ratio of more than 55 can be achieved, and it is suitable for our applications. We can find that transistors M3 and M4 would operate from weak inversion region to saturation region at large bias current, and the scaled function would become a radical expression.

The CMFB circuit, which is composed by transistors MF1 to MF8, is used for the differential structure. The aspect ratio of the transistor M18 would be twice the value of the transistors MF1 and MF2 for suitable operation. The purpose of the CMFB circuit is to balance the voltage over the entire range

$$a_{1,\text{lin}} = \frac{K_{\text{lin}} \left\{ R_{\text{eq}} K_{\text{lin}} V_{\text{cm}}^2 + 4 \left( V_{\text{DD}} - V_{\text{th}} - V_{\text{cm}} \right) \left[ 1 + \left( R_{\text{eq}} K_{\text{lin}} + \theta \right) \left( V_{\text{DD}} - V_{\text{th}} \right) \right] \right\}}{\left\{ 2 + R_{\text{eq}} K_{\text{lin}} \left[ 2 \left( V_{\text{DD}} - V_{\text{th}} \right) - V_{\text{cm}} \right] + 2 \left( V_{\text{DD}} - V_{\text{th}} \right) \theta \right\}^2}$$

$$a_{3,\text{lin}} = \frac{-4 R_{\text{eq}} K_{\text{lin}}^2 \left[ 1 + \theta \left( V_{\text{DD}} - V_{\text{th}} \right) \right] \left[ 1 + \left( R_{\text{eq}} K_{\text{lin}} + \theta \right) \left( V_{\text{DD}} - V_{\text{th}} \right) \right]}{\left\{ 2 + R_{\text{eq}} K_{\text{lin}} \left[ 2 \left( V_{\text{DD}} - V_{\text{th}} \right) - V_{\text{cm}} \right] + 2 \left( V_{\text{DD}} - V_{\text{th}} \right) \theta \right\}^4}$$

$$HD_{3} \cong \frac{R_{\text{eq}}K_{\text{lin}} \left[1 + \theta \left(V_{\text{DD}} - V_{\text{th}}\right)\right] v_{d}^{2}}{16 \left[1 + \left(\theta + R_{\text{eq}}K_{\text{lin}}\right) \left(V_{\text{DD}} - V_{\text{th}}\right) - V_{\text{cm}}\right]^{2} \left(V_{\text{DD}} - V_{\text{th}} - V_{\text{cm}}\right)}$$

(23)

Fig. 5. Simulated G<sub>m</sub> range of the proposed transconductor.

of the transconductor output nodes. The feedback loop forces the output common-mode voltage to the desired value, and then the linearity of the input transistors in the following transconductor circuit would be maintained. In our circuit, the maximum output swing range is defined by the maximum input signal, and the correct swing operation is confirmed by simulation. To obtain higher gain at low supply voltage, large sizes of transistors MF3 to MF6 are selected and these transistors operate in the weak inversion region. However, the CMFB gain would be reduced at large input swing. When the gain of the CMFB circuit is reduced, it will lead to an offset voltage to the input node of next stage and then affect the linearity of voltage-to-current conversion. Thus, the distortion would become a little worse than expected when large signal appears within the filter cutoff frequency. This effect can be recovered by using extra resistors to replace differential pair for averaging differential signals.

#### D. Nonidealities in the Proposed Circuit

The thermal noise is a combination of the noise generated by the voltage-to-current conversion core and the current multiplier. In order to obtain the noise performance, a noise model validated in the weak to strong inversion region is required. As the model in [9] is introduced, the input-referred thermal noise is as shown in (24) at the bottom of the page, where k is the Boltzmann constant and  $\delta$  is the noise parameter at saturation, subthreshold, and linear regions. From the equation, the noise contribution can be divided into two parts. One is contributed by the feedback amplifier, which is composed by transistors M5 to M12, and the other is the devices in the nega-

tive feedback network. To reduce the noise of the feedback amplifier, we can increase the transconductance of input transistors M5 to M8. For the differential input stage with a biased current source, the transconductance is proportional to the current and thus it results in a tradeoff between the noise performance and the power consumption. In this design, larger aspect ratio would be used by taking the gate overdrive voltage and the voltage headroom of the current source into consideration. To reduce the noise contributed in the negative feedback network, we need to maintain large amplifier gain and increase transconductance of transistors M13 and M14. Usually, the amplifier gain is large enough, so the transconductance of transistors M13 and M14 dominates the noise contribution. Transistors M13 and M14 are operated in the linear region, and the transconductance can be increased by giving a large transistor aspect ratio and gate overdrive voltage. We should note that to achieve a larger transconductance, the bias current would become larger to consume more power. Thus, a small input common-mode voltage can be used to maintain the bias current while the overall transconductance derived from (16) and (20) tends to increase. In this circuit, even the high linearity current multiplier would contribute extra noise in the wide tuning transconductor, it is fortunate that half of the multiplier is combined with the voltage-to-current core, and thus only transistors M1 to M4 are added for current scaling. This condition reduces the contributed noise from the current multiplier. In our simulation, a 3 dB increase of the aspect ratio could result in about 3 dB increase of the noise performance.

The impact of flicker noise should also be taken into consideration. In this design, the device sizes of the transistors which determine the flicker noise are increased to reduce the flicker noise, and the transistor length is designed to ten times of the minimal size used in the process. The larger size of the device also decreases the effect of channel length modulation and increase the output impedance. We should note that the large device size would induce more parasitic capacitance, and thus not only the unity-gain frequency is decreased but also the voltage-to-current conversion linearity at high speed is degraded. Since the flicker noise contributes only part of the noise in our design, the tradeoff between the noise and speed should be taken into consideration.

The mismatch is caused by the random variation of the process in physical quantities of identically designed devices. The random mismatch comes from the fabrication tolerances, and it produces the even-order distortion terms in differential structure. In the circuit, the linearity of the voltage-to-current conversion core is not sensitive to the mismatch owing to

$$\overline{V_{\text{n,in}}^{2}} = \frac{4kT}{gm_{13,14}^{2}} \left( \frac{\delta_{3,4}gm_{1,2}^{2}}{gm_{3,4}} + \delta_{1,2}gm_{1,2} + \delta_{13,14}gm_{13,14} \right) \left[ \frac{gm_{13,14} + gm_{5,6,7,8} \left( ro_{5,6,7,8} || ro_{9,10,11,12} \right) gm_{1,2}}{gm_{5,6,7,8} \left( ro_{5,6,7,8} || ro_{9,10,11,12} \right) gm_{1,2}} \right]^{2} + \frac{8kT}{gm_{5,6,7,8}^{2}} \left( \delta_{5,6,7,8}gm_{5,6,7,8} + \delta_{9,10,11,12}gm_{9,10,11,12} \right) \tag{24}$$

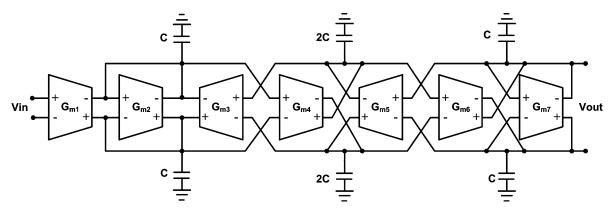

Fig. 6. Block diagram of the third-order Butterworth filter.

the feedback topology. The mismatch of the input transistor dimensions and threshold voltage will just produce a DC offset voltage at the resistor terminals. Thus, the converted output current would behave only first-order fashion to the input voltage. When the linear region transistors are introduced, the offset voltage will induce a slight variation of transconductance as the short channel effect is simply neglected, and then the linearity performance can be hold. However, when the mismatch between linear region transistors M13 and M14 occurs, the voltage-to-current conversion would provide second-order distortion and degrade the linearity performance. In addition to the voltage-to-current conversion core, mismatch problem would get a higher nonlinear effect on the current multiplier. Simulation results show an increase of 3 dB in the second harmonic distortion term for a 2% mismatch of transistors M1 and M2. Thus, large transistor length is suitable for the multiplier in our design. This condition also helps the multiplier to achieve a higher linearity operation since it tends to work under the weak inversion operation.

#### III. FILTER ARCHITECTURE

From the demonstration of the passive ladder prototype, the third-order Butterworth low-pass  $G_{\rm m}$ –C filter, consisting of seven identical transconductors, is used as shown in Fig. 6.

In this low-pass filter design, the time constant of the filter is determined only by the G<sub>m</sub>/C ratio, where G<sub>m</sub> is the transconductance and C is the loading capacitance. The loading capacitor is realized from metal-insulator-metal structure. The transconductance would be programmable and has a nominal value of 50  $\mu$ S. The -6 dB gain loss of the passive prototype has been compensated at the input of the filter by increasing the transconductance by a factor of two. The other transconductors would be set to the same value so that frequency tuning can be achieved from a single source. Dynamic range scaling was applied, and we have made sure the output swing of each transconductor is equal to the maximum range. Since the filter is synthesized by Butterworth ladder prototype, which behaves all-pole characteristic, the quality factor is equal to 1. Therefore, no peaking will appear near the cutoff frequency. The cutoff frequency of the  $G_m$ -C filter is tuned by changing the bias current  $I_{tune}$  in our proposed transconductor. The automatic frequency tuning circuitry has not been investigated for this filter. However, the

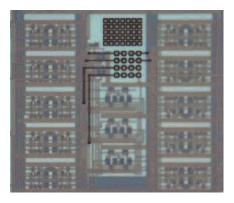

Fig. 7. Chip micrograph.

tuning circuitry can be developed with digitally controlled circuits in a system on chip solution by choosing a number of current sources for multi-mode selection. In addition, Q tuning circuits are not considered here with the intrinsic quality of the low Q structure.

The output common-mode voltage of each block would be fixed by three CMFB circuits in the filter. The CMFB circuit is shown in Fig. 4. The bias current of the CMFB circuit should be changed according to the  $I_{\rm tune}$  value, and then the performance of the common-mode control topology can be maintained.

#### IV. MEASUREMENT RESULTS

The transconductor and the filter were designed in the TSMC 0.18  $\mu$ m CMOS process. The chip micrograph is shown in Fig. 7 with the active area less than 0.23 mm<sup>2</sup>.

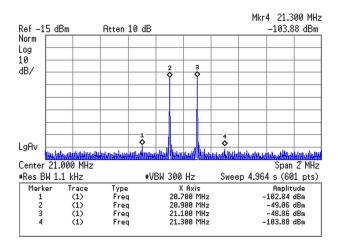

The transconductor has been examined in the frequency domain to obtain its linearity performance. Fig. 8 shows the spectrum of the transconductor through inter-modulation characterization by applying two-tone signals near 20 MHz with the amplitude of 0.6  $V_{\rm pp}$  voltage. In this measurement, the transconductance is 100  $\mu$ S and the loading resistor is 50 ohm. The result shows the third-order inter-modulation distortion (IM3) is around -54 dB. The measured performance is smaller than the expected value from simulation. This is owing to the deviation of the feedback amplifier gain and the effect of parasitic capacitance at high frequency.

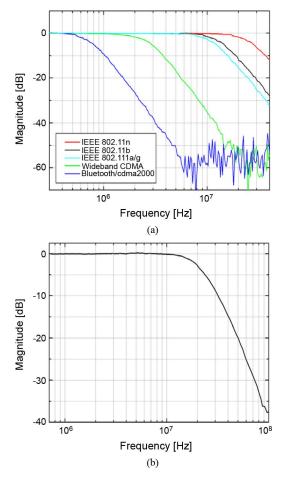

Fig. 9 illustrates the filter frequency response at 1.2 V supply voltage. We should note that the magnitude is normalized owing

Fig. 8. Two-tone test of the proposed transconductor.

Fig. 9. (a) Measured frequency responses of the proposed multi-mode filter. (b) Frequency response of IEEE 802.11 mode with an extension to 100 MHz.

to the use of the output buffer. The cutoff frequency can be tuned from 500 kHz to 20 MHz, and the range covers the specifications of Bluetooth, cdma2000, Wideband CDMA, and IEEE 802.11a/b/g/n wireless LANs. The IM3 test yield the IIP3 results of 22.3 dBm, 21.8 dBm, 20.5 dBm, 20.2 dBm, and 19 dBm for each wireless specification, respectively.

The measured input-referred noise spectrum density at  $70\,^{\circ}$ C is summarized in Table I. Since the cutoff frequency of the

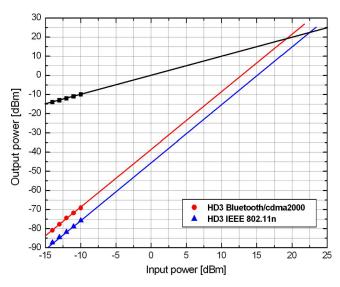

Fig. 10. In-band IIP3 between Bluetooth/cdma2000 and IEEE 802.11n setting.

$G_{\rm m}$ –C filter is programmed by adjusting the transconductance, the filter can be considered as a constant-capacitance network. In [10], the integrated output thermal noise is shown to be independent to the frequency scaling factor from analysis, and the dynamic range is almost the same over the tuning range. We can find that the measured input-referred noise density value in Table I has an inverse proportion factor rather than a square-rooted inverse proportion factor to the scaled frequency. The deviation of the expected value is owing to the circuit flicker noise at low frequency and extra circuit on PCB board at high frequency. The measured noise gives an 80 dB dynamic range at IEEE 802.11 mode for -40 dB IM3.

The DC offset decreases the dynamic signal swing, and then reduce the gain and linearity performance of the receiver. The offset cancellation loop/algorithm is usually used to compensate DC values while still maintaining the well performance of the system. The measured input second-order intercept point (IIP2), which can stand for the second-order distortion performance for every wireless mode, is also shown. Moreover, the linearity performance of out-of-band blocking interferences is measured. The value is described by out-of-band IIP3 in Table I. The IIP3 plot for highest and lowest cutoff frequency setting is shown in Fig. 10.

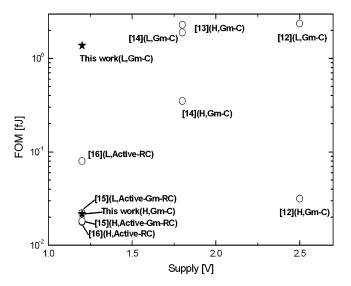

Table II summarizes the filter type and detailed information for several filters reported in recent years. A figure of merit (FOM), which is independent to the tuning ratio, is used to evaluate the filter performance [11]

$$FOM = \frac{(P_{\text{tot}}/N)}{f_c \times SFDR \times N^{4/3}}$$

(25)

where  $P_{\rm tot}$  is the total power of the filter, N is the number of poles,  $f_c$  is the cutoff-frequency,  ${\rm SFDR}(N)^{4/3}$  is the normalized spurious-free dynamic range, with

$$SFDR = \left(\frac{IIP3}{P_n}\right)^{2/3} \tag{26}$$

where  $P_n$  is the input-referred noise power. In this paper, the FOM of this filter is plotted versus the supply in Fig. 11 and

| Technology                   | 0.18-μm CMOS                          |                  |                    |                  |                  |  |  |  |  |  |

|------------------------------|---------------------------------------|------------------|--------------------|------------------|------------------|--|--|--|--|--|

| Supply                       | 1.2-V                                 |                  |                    |                  |                  |  |  |  |  |  |

| Filter<br>Prototype          | 3-rd order Buttorworth Lowpass Filter |                  |                    |                  |                  |  |  |  |  |  |

| Tuning<br>Range              | 500 kHz – 20 MHz                      |                  |                    |                  |                  |  |  |  |  |  |

| Application                  | Bluetooth/<br>cdma2000                | Wideband<br>CDMA | IEEE<br>802.11 a/g | IEEE<br>802.11 b | IEEE<br>802.11 n |  |  |  |  |  |

| IIP3                         | 22.3 dBm                              | 21.8 dBm         | 20.5 dBm           | 20.2 dBm         | 19 dBm           |  |  |  |  |  |

| IIP2                         | 40 dBm                                | 39.3 dBm         | -                  | -                | 30.8 dBm         |  |  |  |  |  |

| Out-of-band<br>IIP3          | 17.5 dBm                              | 17.3 dBm         | -                  | -                | 13 dBm           |  |  |  |  |  |

| Power                        | 4.1 mW                                | 4.7 mW           | 7.1 mW             | 8.2 mW           | 11.1 mW          |  |  |  |  |  |

| Input-referred noise density | 425nV/√Hz                             | 128nV/√Hz        | 29nV/√Hz           | 24nV/√Hz         | 12nV/√Hz         |  |  |  |  |  |

TABLE I

PERFORMANCE SUMMARY OF THIS WORK

TABLE II

COMPARISON WITH PREVIOUSLY REPORTED WORKS

| Reference      |         | [12]                           | [13]                                          | [14]                                      | [15]                      | [11]                         |                                                          |

|----------------|---------|--------------------------------|-----------------------------------------------|-------------------------------------------|---------------------------|------------------------------|----------------------------------------------------------|

|                | ESSCIRC | ESSCIRC                        | JSSC                                          | JSSC                                      | JSSC                      | This Work                    |                                                          |

|                |         | 2003                           | 2004                                          | 2005                                      | 2006                      | 2007                         |                                                          |

| Technology     |         | 0.18μ CMOS                     | 0.18μ CMOS                                    | 0.25μ<br>BiCMOS                           | 0.13μ CMOS                | 0.13μ CMOS                   | 0.18μ CMOS                                               |

| Are            | ea      | 0.83mm <sup>2</sup>            | 0.125mm <sup>2</sup>                          | $0.25 \text{ mm}^2$                       | 0.45mm <sup>2</sup>       | $0.52 \text{ mm}^2$          | 0.23mm <sup>2</sup>                                      |

| Туре           |         | $G_m$ - $C$                    | $G_m$ - $C$                                   | $G_m$ - $C$                               | Active- $G_m$ -R          | Active-RC                    | $G_m$ - $C$                                              |

| Supply         | voltage | 1.8                            | 1.8                                           | 2.5                                       | 1.2                       | 1.2                          | 1.2                                                      |

| Filter order   |         | 6                              | 4                                             | 3                                         | 4                         | 2-6                          | 3                                                        |

| -3dB frequency |         | 1.5MHz-                        | 0.5MHz-                                       | 50kHz-                                    | 2.11MHz-11                | 350kHz-                      | 500kHz-                                                  |

|                |         | 12MHz                          | 12MHz                                         | 2.2MHz                                    | MHz                       | 23.5MHz                      | 20MHz                                                    |

| Tuning ratio   |         | 8                              | 24                                            | 40                                        | 5.5                       | 67                           | 40                                                       |

| Application    |         | W-CDMA/<br>IEEE<br>802.11a/b/g | BlueTooth<br>/W-CDMA/<br>IEEE<br>802.11a/b/g/ | GSM<br>/BlueTooth<br>/W-CDMA/<br>CDMA2000 | UMTS/ IEEE<br>802.11a/b/g | Software<br>defined<br>radio | BlueTooth/<br>cdma2000/W-<br>CDMA /IEEE<br>802.11a/b/g/n |

| IIP3           | Min     | 7.2dBm                         | 9.4dBm                                        | 22dBm                                     | 21dBm                     | 20dbm                        | 19 dBm                                                   |

|                | Max     | 9.3dBm                         | 11.1 <b>d</b> Bm                              | 28dBm                                     | 21dBm                     | -                            | 22.3 dBm                                                 |

| Power          | Min     | 10mW                           | 1.1mW                                         | 2.5mW                                     | 3.4mW                     | 0.72mW                       | 4.1mW                                                    |

|                | Max     | 15mW                           | 4.5mW                                         | 7.3mW                                     | 14.2mW                    | 21.6mW                       | 11.1mW                                                   |

Fig. 11. FOM versus supply comparison with previously published works.

favorably compared to other published works, where some of them are not  $G_{\rm m}\text{--}C$  prototypes. In this figure, symbols L

and H denote the lowest and highest frequency for each filter, respectively.

# V. CONCLUSION

The CMOS implementation of a third-order Butterworth low-pass  $G_{\rm m}$ –C filter for multi-mode applications is presented. The transconductor is designed by the combination of a voltage-to-current circuit and a current multiplier to achieve both the high linearity and wide tuning range simultaneously. Through the use of the wide tuning range linear transconductor as a building block, the cutoff frequency of the channel selection filter can be widely tuned from 500 kHz to 20 MHz, which meets the specifications of Bluetooth, cdma2000, Wideband CDMA, and IEEE 802.11a/b/g/n wireless LANs under direct-conversion architecture. The theoretical analysis of the operation and the measurement results are provided to demonstrate the validity of the filter.

# ACKNOWLEDGMENT

The authors would like to thank the National Chip Implementation Center of Taiwan for supporting the chip fabrication.

#### REFERENCES

- [1] M. Ismail and T. Fiez, Analog VLSI Signal and Information Processing. New York: McGraw-Hill, 1994.

- [2] S. R. Zarabadi, M. Ismail, and C.-C. Hung, "High performance analog VLSI computational circuits," *IEEE J. Solid-State Circuits*, vol. 33, pp. 644–649, Apr. 1998.

- [3] T. Y. Lo and C. C. Hung, "A 1-V 50 MHz pseudo-differential OTA with compensation of the mobility reduction," *IEEE Trans. Circuits Syst. II, Expr. Briefs*, vol. 54, no. 12, pp. 1047–1051, Dec. 2007.

- [4] T. Y. Lo and C. C. Hung, "A 40-MHz double differential-pair CMOS OTA with -60-dB IM3," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 1, pp. 258–265, Feb. 2008.

- [5] C. C. Hung, K. A. Halonen, M. Ismail, V. Porra, and A. Hyogo, "A low-voltage, low-power CMOS fifth-order elliptic G<sub>m</sub>—C filter for baseband mobile, wireless communication," *IEEE Trans. Circuits Syst. Video Technol.*, vol. 7, pp. 584–593, Aug. 1997.

- [6] B. Fotouhi, "All-MOS voltage-to-current convereter," *IEEE J. Solid-State Circuits*, vol. 36, no. 1, pp. 147–151, Jan. 2001.

- [7] Y. Tsividis, K. Suyama, and K. Vavelidis, "Simple "reconciliation" MOSFET model valid in all regions," *Electron. Lett.*, vol. 31, pp. 506–508, Mar. 1995.

- [8] The BSIM Model. BSIM Research Group, Univ. California, Berkeley [Online]. Available: http://www-device.eecs.berkeley.edu/~bsim3/ bsim4.html

- [9] U. Yodprasit and C. C. Enz, "A 1.5-V 75-dB dyamic range third-order G<sub>m</sub>-C filter integrated in a 0.18-\(\mu\)m standard digital CMOS process," *IEEE J. Solid-State Circuits*, vol. 38, no. 7, pp. 1189–1197, Jul. 2003.

- [10] S. Pavan and Y. Tsividis, "Time-scaled electrical networks. Properties and applications in the design of programmable analog filters," *IEEE Trans. Circuits Syst. II*, vol. 47, pp. 161–165, Feb. 2000.

- [11] V. Giannini, J. Craninckx, S. D'Amico, and A. Baschirotto, "Flexible baseband analog circuits for software-defined radio front-ends," *IEEE J. Solid-State Circuits*, vol. 42, no. 7, pp. 1501–1512, Jul. 2007.

- [12] A. Cathelin, L. Fabre, L. Baud, and D. Belot, "A multiple-shape channel selection filter for multimode zero-IF receiver using capacitor over active device implementation," in *Proc. ESSCIRC*, 2002, pp. 651–654.

- [13] S. Hori, T. Maeda, H. Yano, N. Matsuno, K. Numata, N. Yoshida, Y. Takahashi, T. Yamase, R. Walkington, and H. Hida, "A widely tunable CMOS  $G_m$ –C filter with a negative source degeneration resistor transconductor," in  $Proc.\ ESSCIRC,\ 2003,\ pp.\ 449–452.$

- [14] S. Hori, T. Maeda, N. Matsuno, and H. Hida, "Low-power widely tunable G<sub>m</sub>-C filter with an adaptive Dc-blocking, triode-biased MOSFET transconductor," in *Proc. ESSCIRC*, 2004, pp. 99–102.

- [15] D. Chamla, A. Kaiser, A. Cathelin, and D. Belot, "A G<sub>m</sub>-C low-pass filter for zero-IF mobile applications with a very wide tuning range," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1143–1450, Jul. 2005.

- [16] S. D'Amico, V. Giannini, and A. Baschirotto, "A 4th-order active-Gm-RC reconfigurable (UMTS/WLAN) filter," *IEEE J. Solid-State Circuits*, vol. 40, no. 7, pp. 1143–1450, Jul. 2006.

**Tien-Yu Lo** received the B.S., M.S., and Ph.D. degrees in communication engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2001, 2003 and 2007, respectively.

Since 2008, he has been with the Analog Circuit Design Division, MediaTek Inc., Hsinchu, Taiwan, as an Analog IC Designer. His research interests include analog and mixed-signal circuit design with particular focus on the topic of continuous-time filters and analog-to-digital converters.

Chung-Chih Hung (M'98–SM'07) received the B.S. degree in electrical engineering from National Taiwan University, Taipei, Taiwan, in 1989, and the M.S. and Ph.D. degrees in electrical engineering from The Ohio State University, Columbus, in 1993 and 1997, respectively.

From 1989 to 1991, he served in the Taiwan Marine Corps as a Communication officer. From 1997 to 2003, he worked for several IC design companies in San Jose, CA, and San Diego, CA, where he held Analog Circuit Design Manager

and Director positions. Since 2003, he has been with National Chiao Tung University, Hsinchu, Taiwan, where he is currently an Associate Professor in the Department of Electrical Engineering. His research interests include the design of analog and mixed-signal integrated circuits for communication and high-speed applications.

**Mohammed Ismail** (F'97) received the B.S. and M.S. degrees in electronics and communications from Cairo University, Cairo, Egypt, and the Ph.D. degree in electrical engineering from the University of Manitoba, Canada.

He has over 25 years experience of R&D in the fields of analog, RF and mixed-signal integrated circuits. He has held several positions in both industry and academia and has served as a corporate consultant to nearly 30 companies in the US, Europe, and the Far East. He is Professor of electrical and com-

puter engineering and the Founding Director of the Analog VLSI Lab at The Ohio State University, Columbus, and of the RaMSiS Group at KTH–Royal Institute of Technology, Stockholm, Sweden. His current interest lies in research involving digitally programmable/configurable integrated CMOS radios with focus on low voltage/low power "first-pass" solutions for cognitive radios, 3 G and 4 G wireless handhelds. He publishes intensively in this area and has been awarded 11 patents. He has co-edited and coauthored several books, including Analog VLSI Signal and Information Processing (McGraw Hill). His most recent book is Radio Design in Nanometer Technologies, (Springer, 2007). He advised the thesis work of 45 Ph.D. students and of over 85 M.S. students. He co-founded ANACAD-Egypt (now part of Mentor Graphics, Inc.) and Firstpass Technologies Inc., a developer of CMOS radio and mixed-signal IPs for handheld wireless applications.

Dr. Ismail has been the recipient of several awards, including the US National Science Foundation Presidential Young Investigator Award, the US Semiconductor Research Corp Inventor Recognition Awards in 1992 and 1993, The College of Engineering Lumley Research Award in 1992,1997, 2002 and 2007 and a Fulbright/Nokia fellowship Award in 1995. He is the founder of the International Journal of Analog Integrated Circuits and Signal Processing (Springer) and serves as the Journal's Editor-In-Chief. He has served as Associate Editor for many IEEE transactions, is on the International Advisory Boards of several journals, and was on the Board of Governors of the IEEE Circuits and Systems Society. He is the founder of ICECS, the CAS flagship Conference for Region 8.