# 國立交通大學

電子工程研究所

碩士論文

應用於 Serial ATA 6Gbps 之可程式化展頻時脈產生器

A Programmable Spread Spectrum Clock Generator for Serial ATA 6Gbps

1896

指導教授:周世傑博士

研究生:莊誌華

中華民國 95 年7月

#### 應用於 Serial ATA 6Gbps 之可程式化展頻時脈產生器

# A Programmable Spread Spectrum Clock Generator for Serial ATA 6Gbps

指導教授:周世傑 Advisor: Prof. Shyh-Jye Jou

研究生:莊誌華 Student: Chih-Hua Chuang

國立交通大學電子工程研究所碩士論文

Submitted to Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

In

**Electronics Engineering**

July 2006

Hsinchu, Taiwan, Republic of China

中華民國九十五年七月

#### 應用於 Serial ATA 6Gbps 之可程式化展頻時脈產生器

學生:莊誌華 指導教授:周世傑

#### 國立交通大學電子工程研究所碩士班

#### 摘 要

現代的電路系統操作速度越來越快,其所控制時間的電路也越來越重要。 因此,鎖相迴路在所有高速的系統中扮演一個非常重要的角色。例如:頻率合成器、倍頻器、資料回復電路等等。因為這些系統需要一個準確的時脈,一個低抖動的鎖相迴路是我們所設計的一個重點。

且隨著晶片操作速度越來越快,時脈信號所造成的高頻電磁雜訊干擾 (Electro-Magnetic Interference, EMI)通常會影響到其他電路的操作。且當操作速度越快時,這種問題就越嚴重。傳統的解決方法是將電磁雜訊干擾加以屏蔽,或是控制時脈信號的上升速度,但是缺點是昂貴的成本與龐大的體積。較先進的解決方法是直接在晶片上降低電磁雜訊干擾,以達到低成本與高彈性空間。改變時脈信號的中心頻率是最常被採用的方法。這種方法被稱為展頻時脈技術 (Spread Spectrum Clocking),因為時脈信號的頻譜被展開成較寬的頻帶。

在本論文中,我們先簡單的介紹了鎖相迴路及展頻時脈產生器的基本觀念。並在第五章提出了如何降低電壓抖動的方法以及可程式化展頻時脈產生器的架構。我們的展頻時脈產生器是以調變多重相位的方法來達到展頻的效果並

且符合 Serial-ATA 6Gbps 的規格。可程式化展頻時脈產生器可依系統的需求,選擇對 10 個輸出相位或是 20 個輸出相位作展頻。各有各的優缺點,接下來會詳細的討論並驗證之。

本論文包含了鎖相迴路及展頻時脈產生器的設計、模擬、和製作,並且附上鎖相迴路在 0.18 毫米互補式金氧半的製程實現後的量測結果,證明我們所提出的設計在實現與應用上是可行,並且符合 Serial-ATA 6Gbps 的規格。

# A Programmable Spread Spectrum Clock Generator for Serial ATA 6Gbps

student: Chih-Hua Chuang Advisors: Dr. Shyh-Jye Jou

#### Department of Electronics Engineering National Chiao Tung University

As chips work at faster operation speed, the timing issue becomes more and more important. So the PLL plays an important role in all high-speed systems, such as: frequency synthesizer, clock multiplier, Clock and Data Recovery (CDR) circuit, and clock de-skew application. Consequently, a low-jitter PLL is important because these systems require a stringent timing specification.

Due to the operation speed is becoming faster and faster, many higher order harmonics of the signal are generated. These signals often generate Electric-Magnetic Interference (EMI) that affects the operation of other equipments. When the operation speed is higher, the EMI problem is more severe.

The conventional techniques to reduce EMI tend to enclose or reduce the amount of the generated radiation, such as shield cables and coaxial wires, but they are usually costly and bulky. Modern EMI reduction is done on-chip without using

heavy shielding materials to the goal of low-cost and flexibility.

Altering the center frequency of internal clocks is a widely adopted EMI reduction technique. The technique is called Spread Spectrum Clocking (SSC) because the spectrum of the clock is spread over a broader range. It also offers the best immunity with respect to manufacturing process variation. Serial-ATA (SATA) specification defines an EMI reduction method using SSC.

A low-jitter programmable spread-spectrum clock generator using switching phases and the modified  $\Delta\Sigma$  modulator is presented in this thesis. The circuits are proposed, simulated, and implemented in a standard 0.18um CMOS technology. Our low jitter PLL is achieved through VCO with low  $K_{VCO}$  by using medium-threshold voltage PMOS and passive resistance. The spectrum in the clock generator with modulation on phases can be spread by 10 phases or 20 phases depending on the system's requirement, such as power saving or low jitter in time domain. Besides, the programmable spread spectrum generator is also fit with the specification of Serial-ATA 6Gbps. Finally, the experiment results show that the architecture achieves spread spectrum function as expectations.

#### 誌謝

真的很開心,終於到了論文完成的這一天。同樣不免俗的我必須抒發我心裡的感激。我必須承認,我要感謝的人太多了。首先要感謝的是引領我碩士生涯入門的李崇仁教授,教導我研究的態度。接下來要感謝的是我的論文指導教授周世傑老師,在這段時間不斷的鞭策我們,並且為我們定下每一時期的短程目標與終極目標,才能使我們能準時畢業。

我也要謝謝我的同學們:阿呆、威憲、小明、劉坪、世平、明學、阿發、志杰,因為你們,讓我的課外生活多采多姿。也要謝謝 TOTORO 學長,在我的研究當中給了我不少的建議與指導。接下來當然還有小朱、小胖、一哥,有了你們,研究的日子很快就在歡樂聲度過了。

當然還要感謝我的女友惠雅,由於她的陪伴,我更有動力盡快完成我的論文。也因為她,我的碩士生涯變的不只有做研究,還有更豐富的心靈生活。接下來我會繼續努力的把我的空頭支票慢慢兌現,不會讓妳失望的。

最後,最重要的一定要謝謝我的父母、我的阿媽,有他們一路上的支持我 與栽培我,我最終才能完成這個學位與論文,我要說聲謝謝你們大家。過不久, 我即將踏入社會,我會以加倍的愛,來回報你們這些年來對我付出的辛勞。祝 你們大家身體健康,萬事如意。

這麼長的歲月,要感謝的人當然不只這些。所有的授課老師、學長姐、同學、學弟妹們,我也要在這裡說聲謝謝你們大家,因為你們大家的牽成,才有今天的我,謝謝你們。

莊誌華

國立交通大學

## **Table of Contents**

| Chapter  | 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1      | Introduction of Timing Module for Serial Link                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1  |

| 1.2      | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

| 1.3      | Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4  |

| Chapter  | 2 Principles of Phase-Locked Loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6  |

| 2.1      | Introduction to PLL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6  |

| 2.2      | Brief History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8  |

| 2.3      | Basic Operations in PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9  |

| 2.3.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 |

| 2.3.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 2.3.3    | B Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16 |

| 2.3.4    | A STATE OF THE PARTY OF THE PAR | 20 |

| 2.4      | Analysis of PLL Linear Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20 |

| 2.4.1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 2.4.2    | Analysis of Closed Loop Transfer Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23 |

| Chapter: | Basic of Spread Spectrum Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26 |

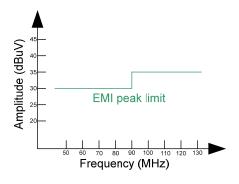

| 3.1      | Background: EMI Problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26 |

| 3.2      | Concept of Spread Spectrum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 28 |

| 3.3      | Spread Spectrum parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 30 |

| 3.3.1    | Modulation Frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

| 3.3.2    | 2 Modulation Profiles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 33 |

| 3.3.3    | 3 Timing Impacts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 36 |

| Chapter  | 4 Principles of Spread Spectrum Clock Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39 |

| 4.1      | Concept of SSCG Using Switching Phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

| 4.2   | The  | e Switch Phase Mechanism                   | 40 |

|-------|------|--------------------------------------------|----|

| 4.3   | Pri  | nciples of ΣΔ Modulator                    | 44 |

| Chapt | er 5 | Spread Spectrum Clock Generator            | 55 |

| 5.1   | Inti | roduction                                  | 55 |

| 5.2   | Sys  | stem architecture                          | 55 |

| 5.3   | Bel  | navior Simulation                          | 58 |

| 5.4   | Cir  | cuit Implementation                        | 62 |

| 5.    | 4.1  | Phase / Frequency Detector                 | 62 |

| 5.    | 4.2  | Charge Pump                                | 64 |

| 5.    | 4.3  | Loop Filter                                | 67 |

| 5.    | 4.4  | Programmable Voltage-Controlled Oscillator | 68 |

| 5.    | 4.5  | Divider                                    | 76 |

| 5.    | 4.6  | Programmable Modulation Profile Generator  |    |

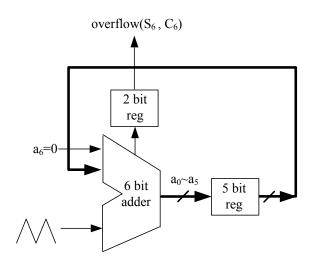

| 5.    | 4.7  | Modified Delta-Sigma Modulator             | 78 |

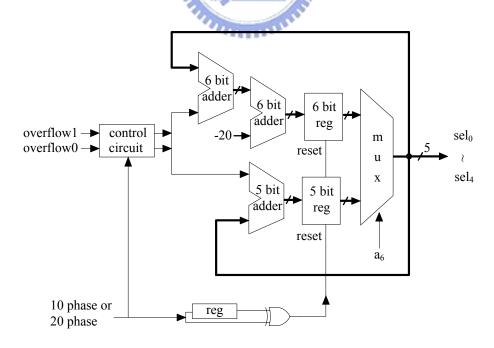

| 5.    | 4.8  | Programmable MUX Control Circuit           | 80 |

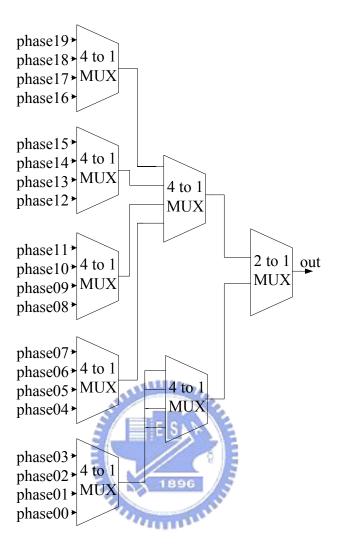

| 5.    | 4.9  | Multiplexer                                | 81 |

| 5.    | 4.10 | SSCG System                                | 82 |

| 5.5   | Exp  | perimental Results                         | 90 |

| 5.    | 5.1  | Measurement Setup                          | 92 |

| 5.    | 5.2  | Measured Waveform and Spectrum of PLL      | 94 |

| Chapt | er 6 | Conclusions and Future Work                | 98 |

# **List of Figures**

| Fig. 1.1 Architecture of Serial-ATA transmitter with PLL                        | 2      |

|---------------------------------------------------------------------------------|--------|

| Fig. 2.1 The block diagram of PLL.                                              | 9      |

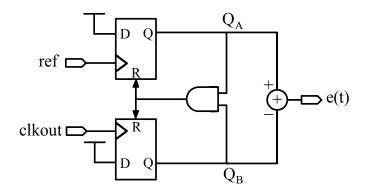

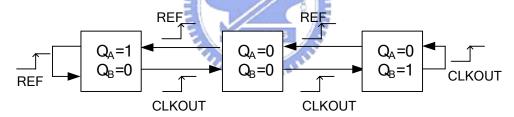

| Fig. 2.2 Architecture of tri-state PFD.                                         | 11     |

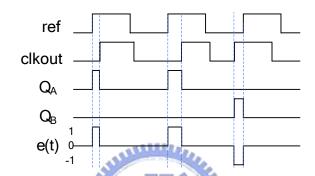

| Fig. 2.3 Timing diagram of tri-state PFD.                                       | 11     |

| Fig. 2.4 State diagram for PFD                                                  | 11     |

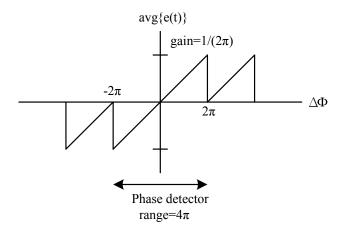

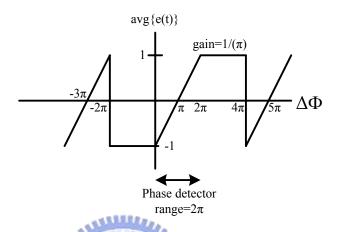

| Fig. 2.5 Tri-state PFD characteristic                                           | 12     |

| Fig. 2.6 Architecture of tri-state PFD.                                         | 12     |

| Fig. 2.7 Timing diagram of XOR-based PFD                                        | 12     |

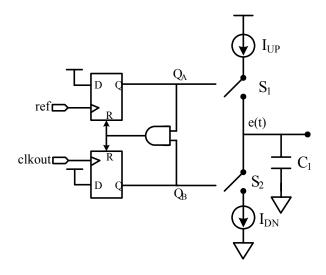

| Fig. 2.8 XOR-based PFD characteristic                                           | 13     |

| Fig. 2.9 PFD with charge pump                                                   |        |

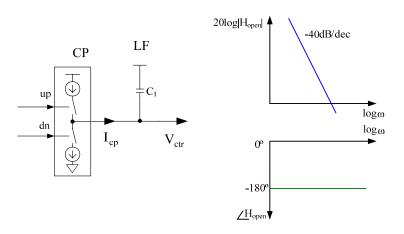

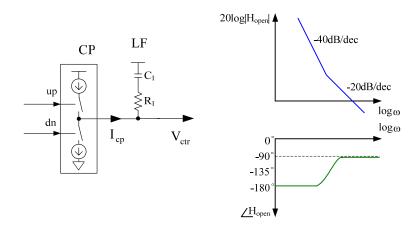

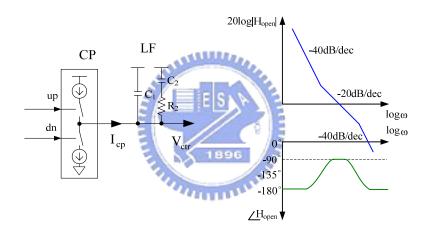

| Fig. 2.10 Stability of 2-pole PLL                                               |        |

| Fig. 2.11 Stability of 2-pole 1-zero PLL                                        | 18     |

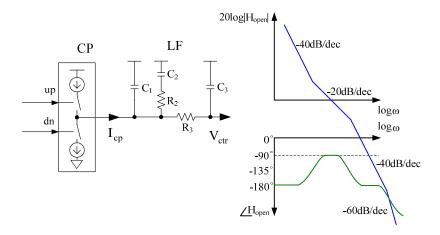

| Fig. 2.12 Stability of 3-pole 1-zero PLL.                                       | 18     |

| Fig. 2.13 Stability of 4-pole 1-zero PLL                                        |        |

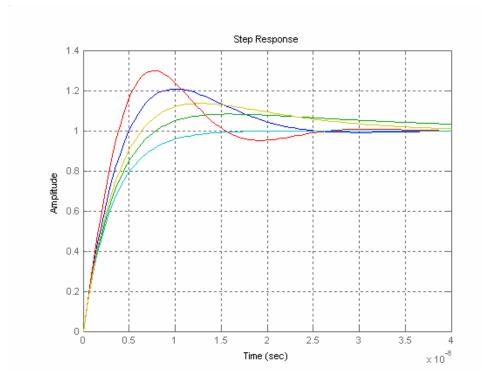

| Fig. 2.14 Step response under various $\zeta$                                   |        |

| Fig. 3.1 FFC EMI peak limit.                                                    | 26     |

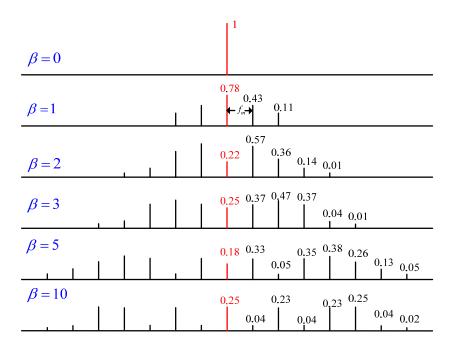

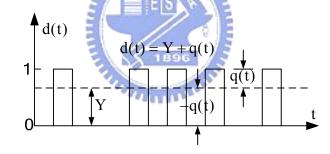

| Fig. 3.2 Spectra of sinewave FM under various modulations                       | 30     |

| Fig. 3.3 Modulation profiles and spectrums of                                   | 31     |

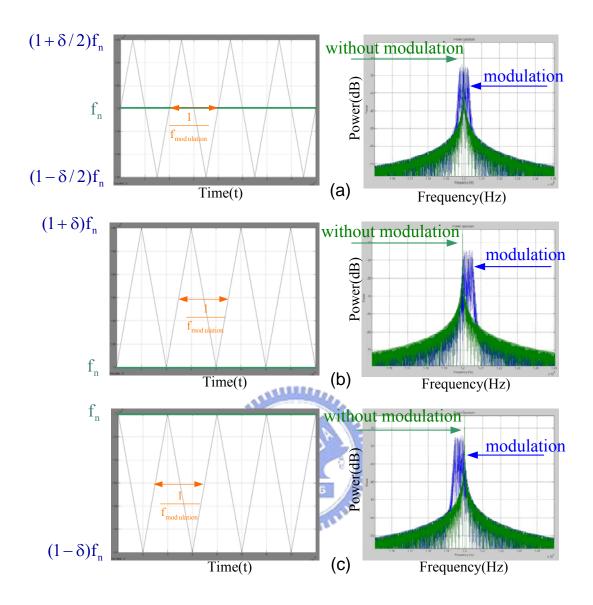

| Fig. 3.4 Comparing between modulation frequency and peak attenuation            | 33     |

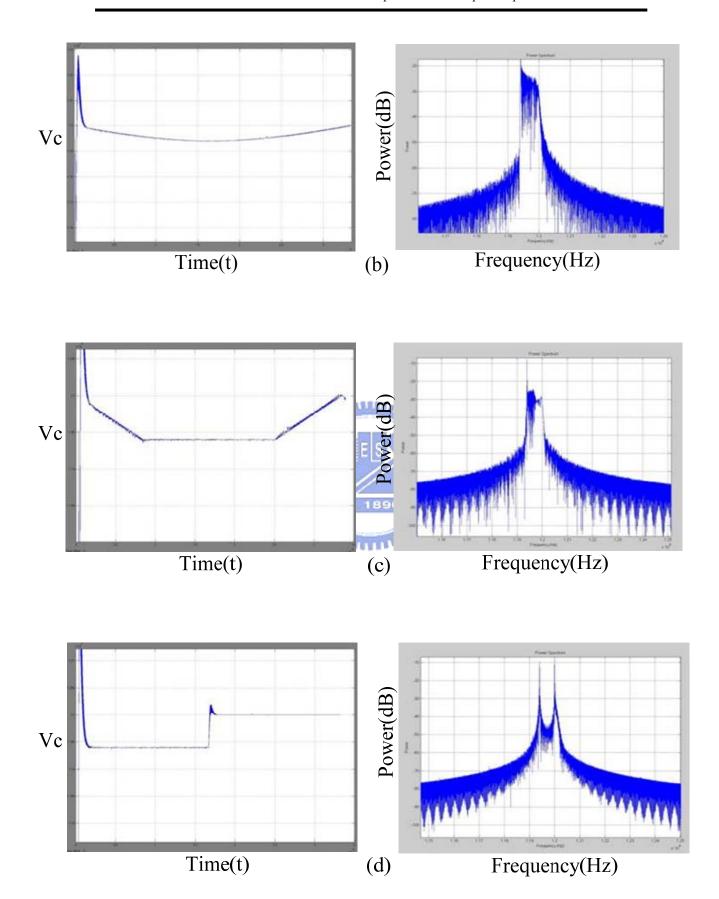

| Fig. 3.5 Vc profiles and their corresponding spectrums (a) without modulation s | signal |

| (b) sinusoidal modulation signal (c) trapezoid modulation signal (d) step modu  | lation |

| signal (e) triangular modulation signal                                         | 36     |

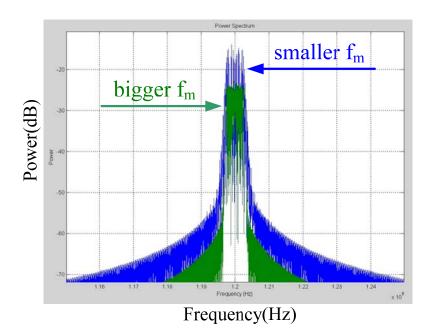

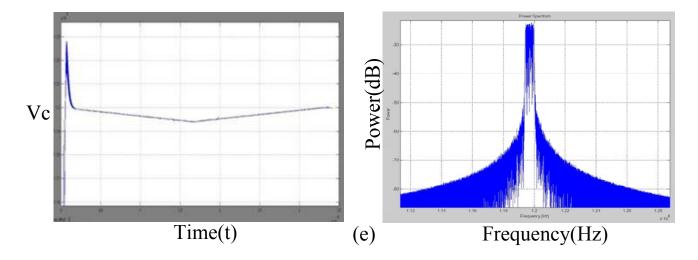

| Fig. 3.6 Time domain behaviors (a) without modulating (b) with modulating       | 36     |

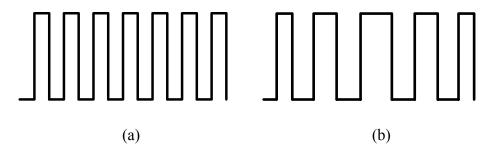

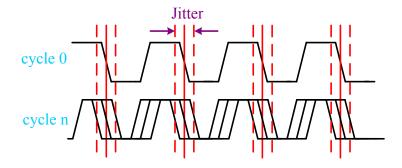

| Fig. 3.7 Diagram of cycle to cycle jitter                                       | 37     |

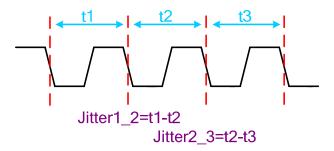

| Fig. 3.8 Diagram of peak to peak jitter                                                               | 38   |

|-------------------------------------------------------------------------------------------------------|------|

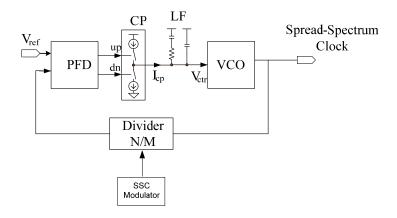

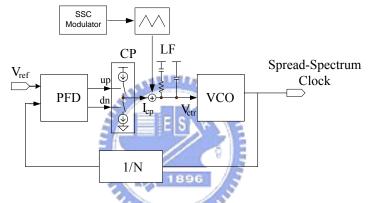

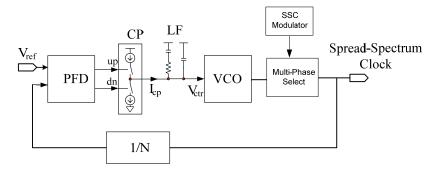

| Fig. 4.1 Type II of SSCG.                                                                             | 40   |

| Fig. 4.2 Type III of SSCG                                                                             | 40   |

| Fig. 4.3 Type IV of SSCG                                                                              | 40   |

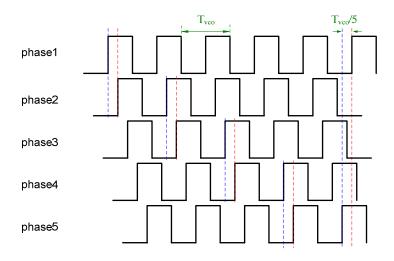

| Fig. 4.4 Timing diagram of 5 phases from VCO                                                          | 41   |

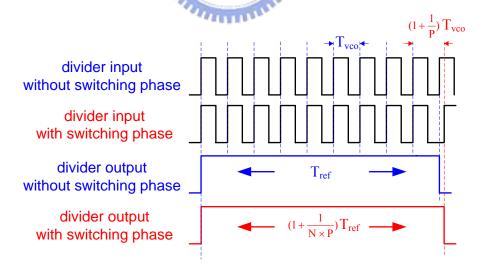

| Fig. 4.5 Timing diagram of switching phase.                                                           | 41   |

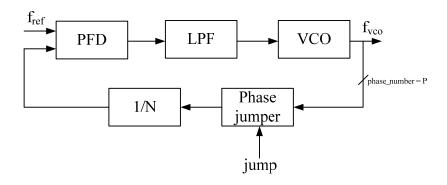

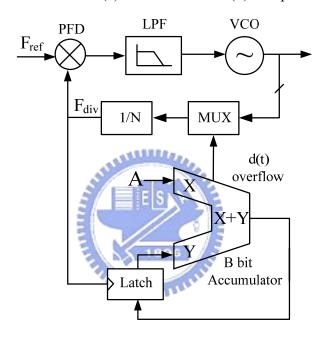

| Fig. 4.6 Simple jumping phase PLL                                                                     | 42   |

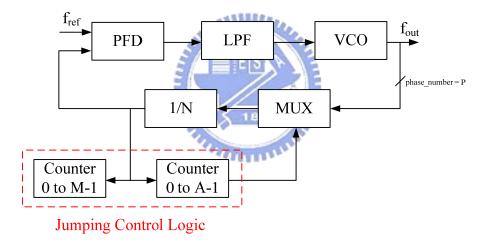

| Fig. 4.7 Switching phase PLL using Boolean logic                                                      | 42   |

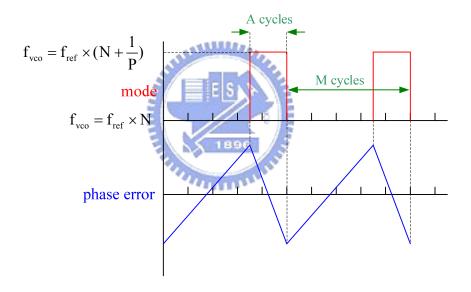

| Fig. 4.8 Periodic accumulation error phenomenon                                                       | 43   |

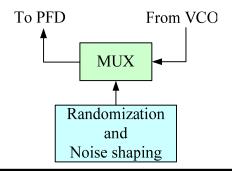

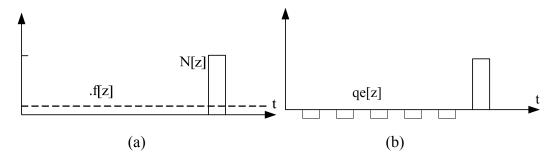

| Fig. 4.9 Randomization and Noise shaping to eliminate unwanted spurs                                  | 45   |

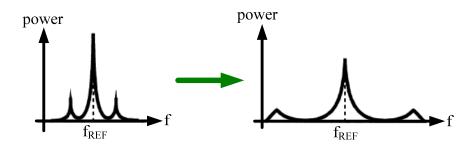

| Fig. 4.10 Noise shaping by means of a $\Sigma\Delta$ modulator                                        | 45   |

| Fig. 4.11 Output waveform of decimal(t)                                                               | 45   |

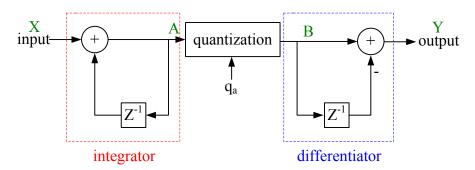

| Fig. 4.12 Original $\Sigma\Delta$ modulator block diagram                                             | 45   |

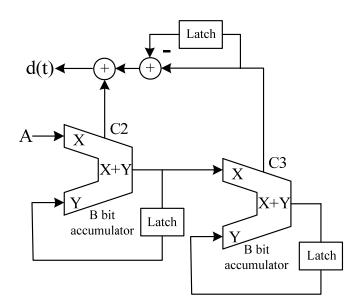

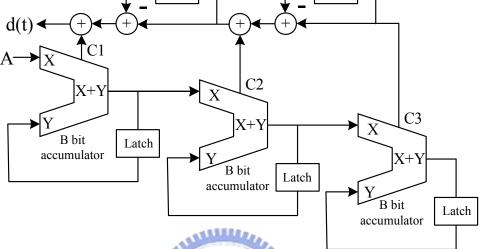

| Fig. 4.13 Improved $\Sigma\Delta$ modulator block diagram                                             | 46   |

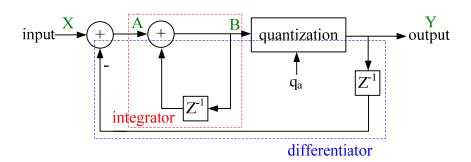

| Fig. 4.14(a) $\Sigma\Delta$ modulator using accumulator (b) Block diagram of $\Sigma\Delta$ modulator | 47   |

| Fig. 4.15 Output waveform of (a) the accumulator (b) the quantization error                           | 48   |

| Fig. 4.16 Realization of $\Sigma\Delta$ modulator                                                     | 48   |

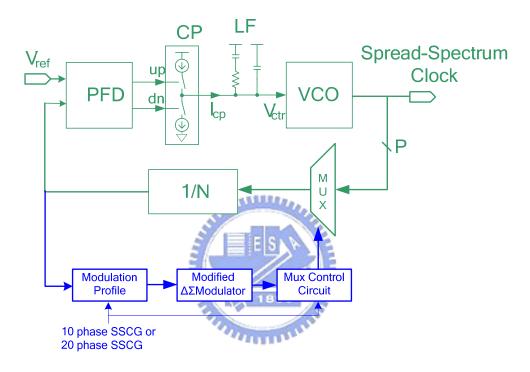

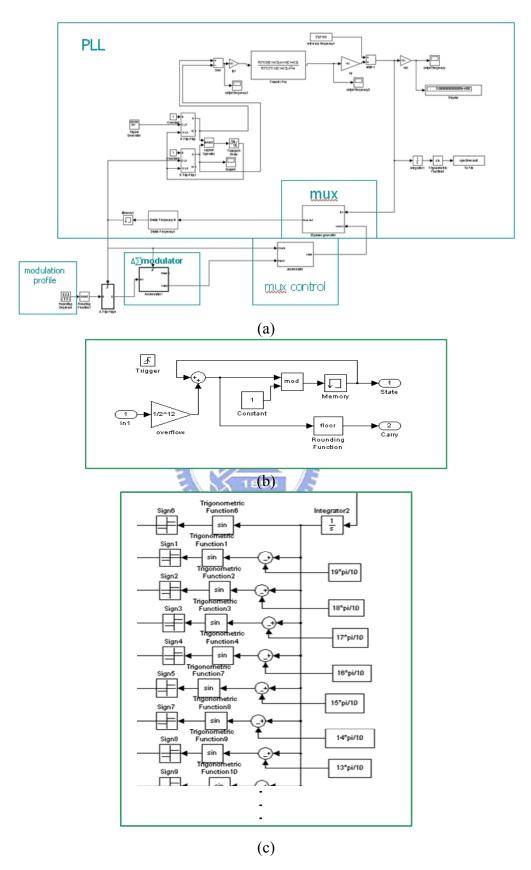

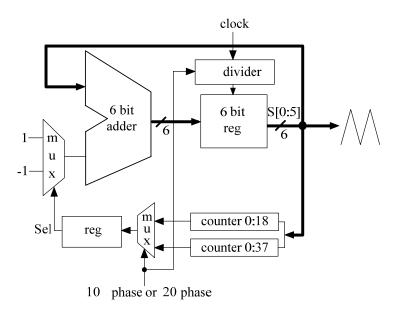

| Fig. 5.1 The architecture of SSCG based on switching phase                                            | 56   |

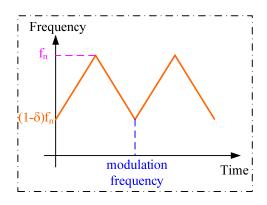

| Fig. 5.2 The variation of frequency in spread spectrum                                                | 57   |

| Fig. 5.3 SIMULINK model of the SSCG (a) SSCG based on the PLL                                         | 59   |

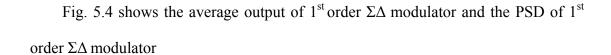

| Fig. 5.4 (a) Average output (b) PSD of $1^{st}$ order $\Sigma\Delta$ modulator                        | 60   |

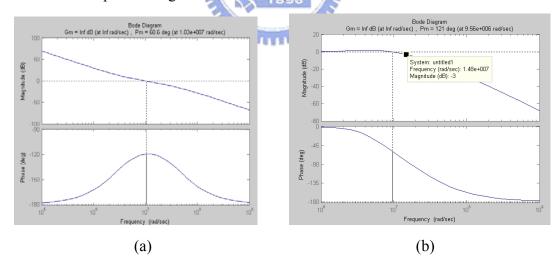

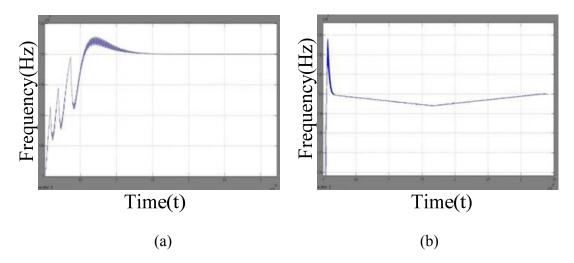

| Fig. 5.5 Frequency response of (a) Open Loop Bode Plot (b) Close Loop Bode Plot                       | t 60 |

| Fig. 5.6 (a) Frequency of VCO without SSCG (b) Frequency of VCO with SSCG                             | 61   |

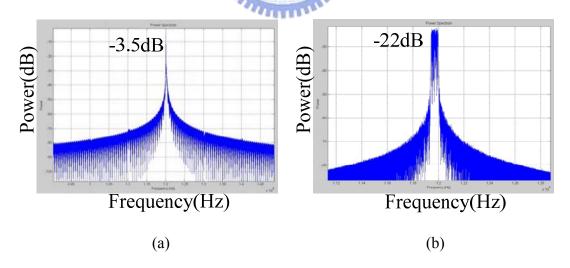

| Fig. 5.7 (a) Spectrum of VCO without SSCG (b) Spectrum of VCO with SSCG                               | 61   |

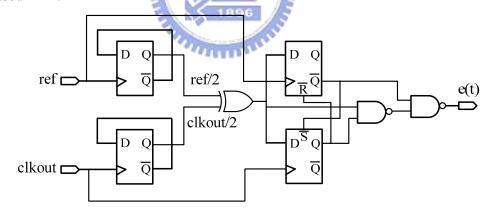

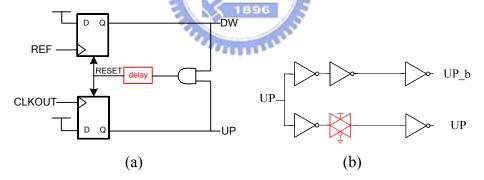

| Fig. 5.8 Schematic of (a) PFD (b) Single to Different circuit                                         | 62   |

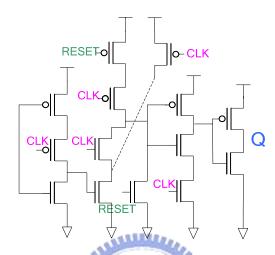

| Fig. 5.9 Circuit of dynamic DFF.                                               | 63 |

|--------------------------------------------------------------------------------|----|

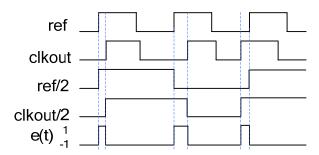

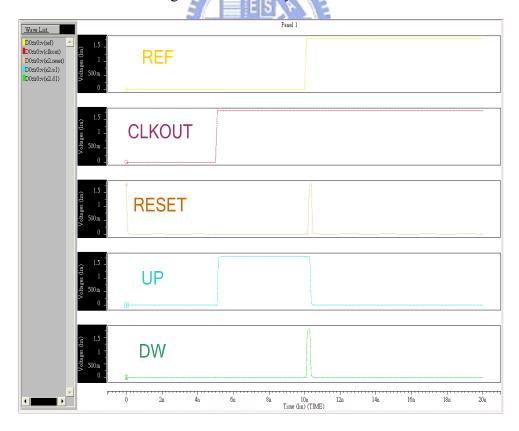

| Fig. 5.10 Timing diagram of PFD                                                | 63 |

| Fig. 5.11 Timing diagram of Zero dead zone                                     | 64 |

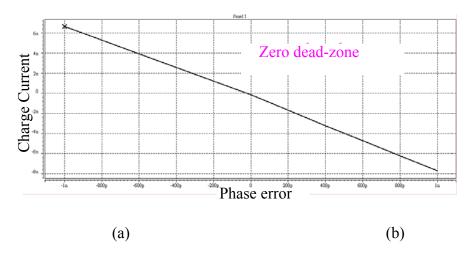

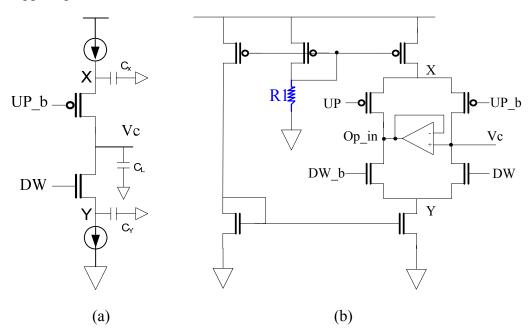

| Fig. 5.12 (a) traditional charge pump (b) charge pump with active amplifier    | 65 |

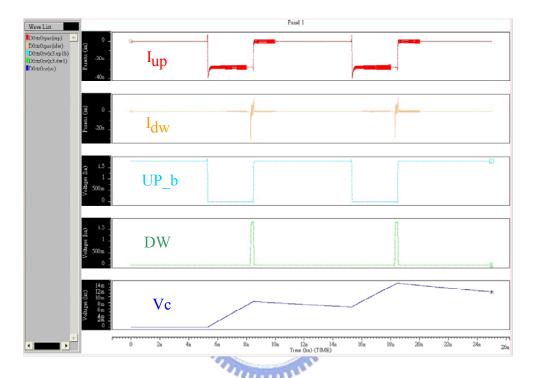

| Fig. 5.13 Timing diagram of charge pump (with SSN)                             | 66 |

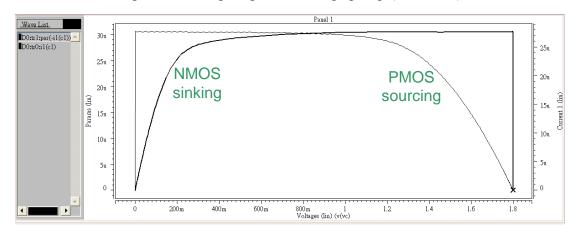

| Fig. 5.14 Charge pump current matching characteristic                          | 66 |

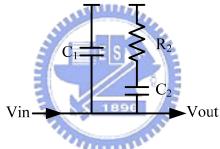

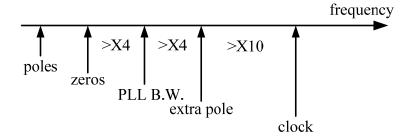

| Fig. 5.15 2 <sup>nd</sup> order loop filter                                    | 67 |

| Fig. 5.16 Relationship between zero, poles, reference clock and loop bandwidth | 67 |

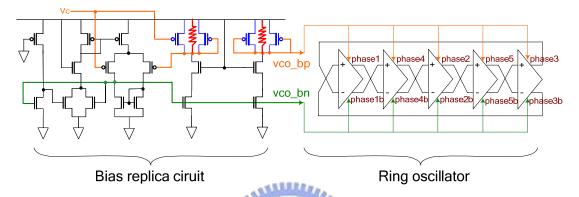

| Fig. 5.17 Scheme of voltage control oscillator                                 | 68 |

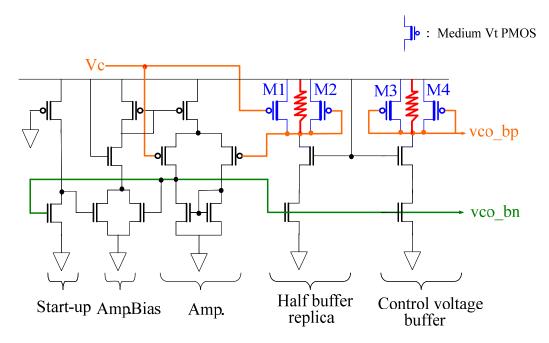

| Fig. 5.18 Bias replica circuit                                                 | 69 |

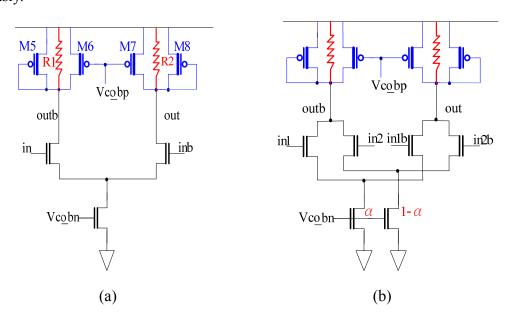

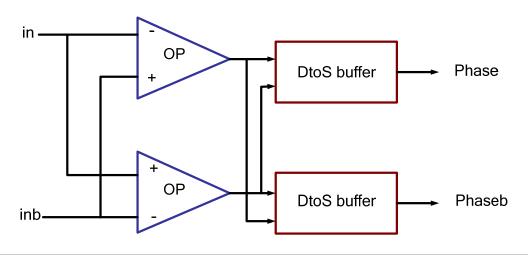

| Fig. 5.19 (a)Delay cell (b)Interpolator                                        | 69 |

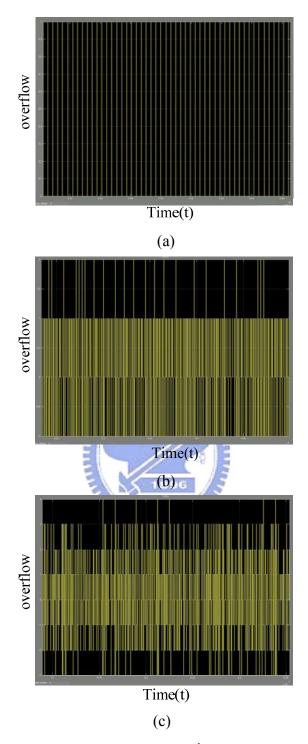

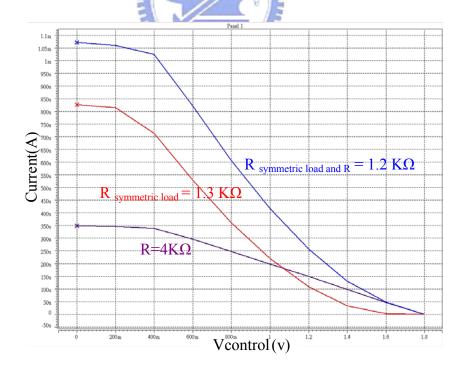

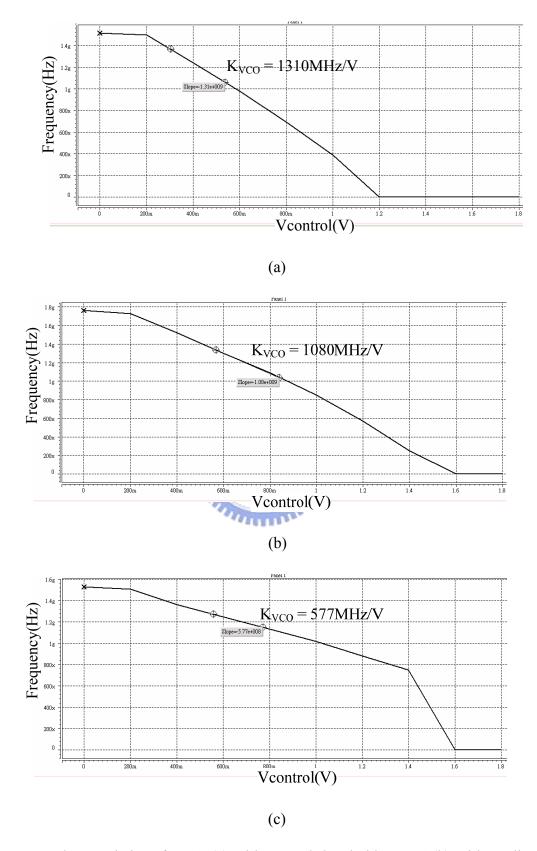

| Fig. 5.20 Characteristics of VCO (a) with normal threshold PMOS (b) with media | ım |

| threshold PMOS(c) with medium threshold PMOS and passive resistance in t       |    |

| symmetric load                                                                 | 72 |

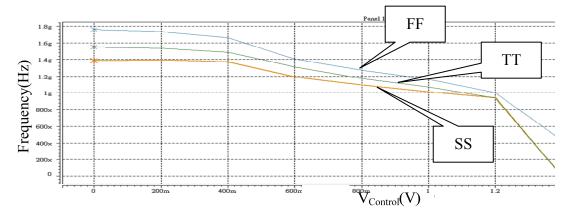

| Fig. 5.21 Simulation results of the voltage-controlled oscillator              | 73 |

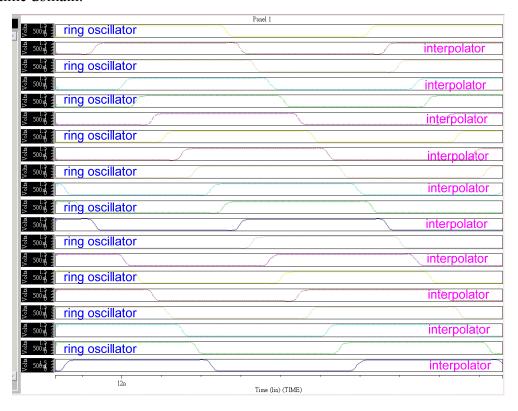

| Fig. 5.22 Diagram of ring oscillators and interpolators                        | 74 |

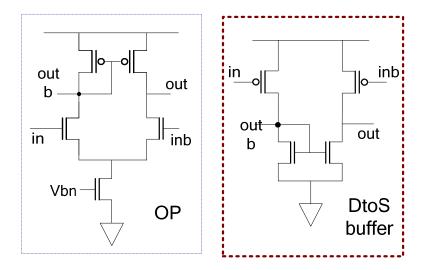

| Fig. 5.23 VCO output buffer                                                    | 75 |

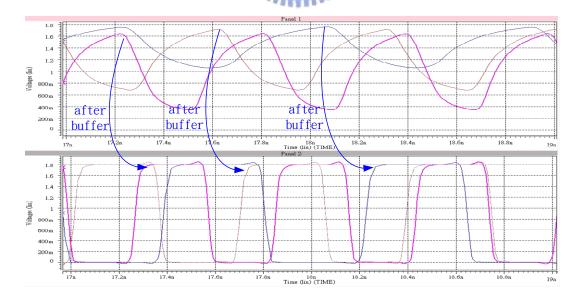

| Fig. 5.24 Diagram of delay cell output and buffer output                       | 75 |

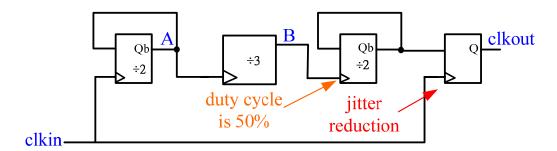

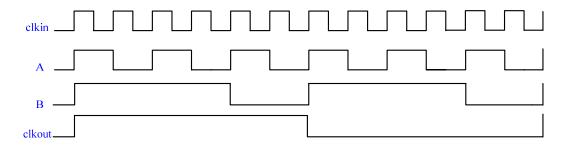

| Fig. 5.25 Schematic of divider                                                 | 76 |

| Fig. 5.26 Time diagram of divider                                              | 76 |

| Fig. 5.27 Schematic of programmable profile generator                          | 78 |

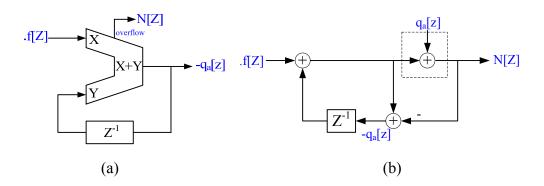

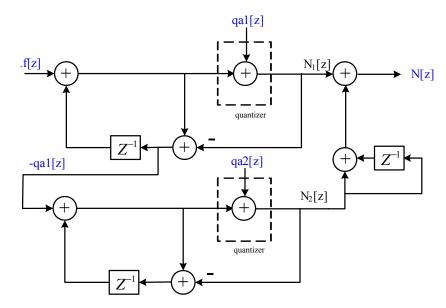

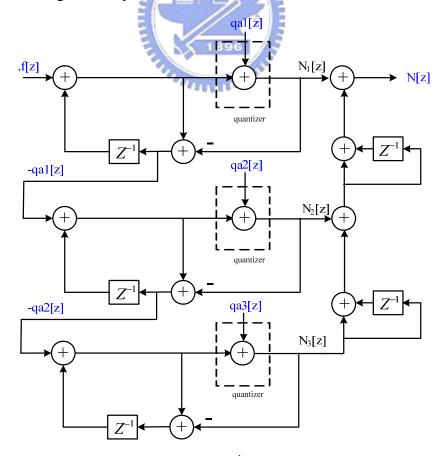

| Fig. 5.28 Modified 1 <sup>st</sup> order $\Sigma\Delta$ modulator              | 79 |

| Fig. 5.29 Programmable MUX control circuit                                     | 80 |

| Fig. 5.30 20 to 1 Multiplexer                                                  | 82 |

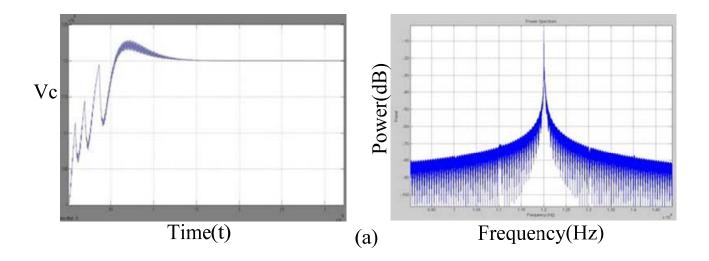

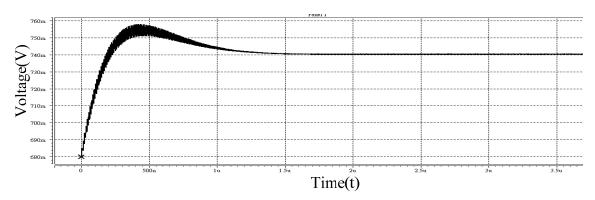

| Fig. 5.31 Post-simulation of V <sub>C</sub> acquisition of PLL                 | 83 |

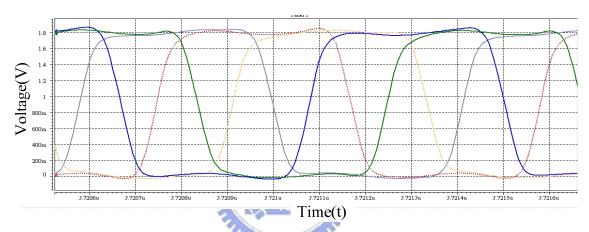

| Fig. 5.32 Post-simulation of 5 phases in VCO.                                    | 83 |

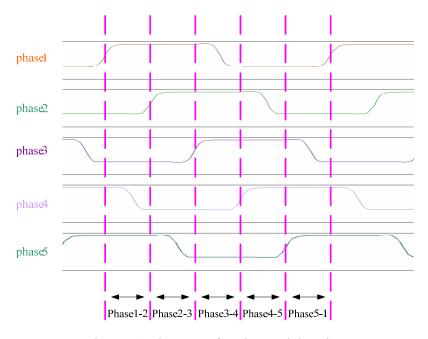

|----------------------------------------------------------------------------------|----|

| Fig. 5.33 Diagram of 5 phases delay time                                         | 83 |

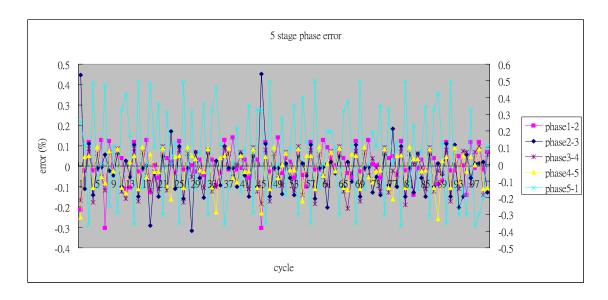

| Fig. 5.34 Difference in 5 phases delay time (Post-Simulation)                    | 84 |

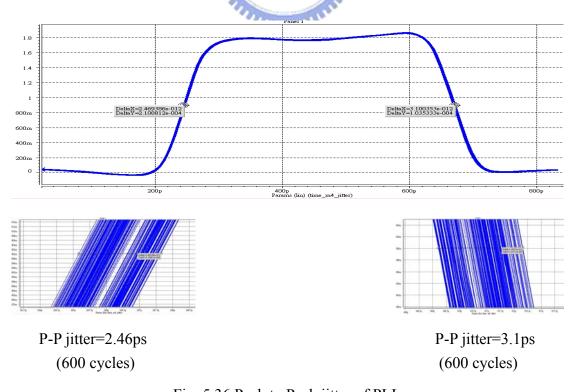

| Fig. 5.35 Peak to Peak jitter of PLL.                                            | 84 |

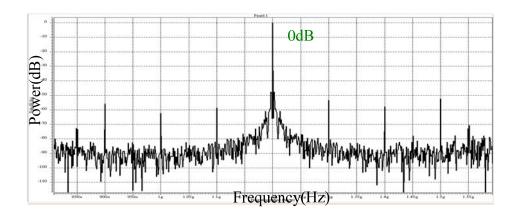

| Fig. 5.36 Carrier Spectra without spread spectrum (0dBV @ 1.2GHz)                | 85 |

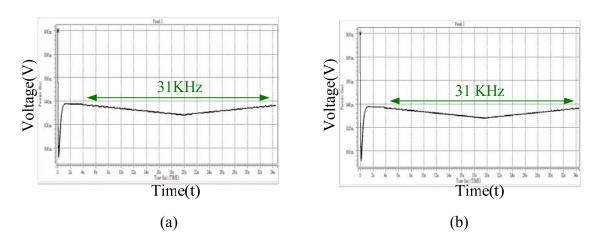

| Fig. 5.37 VCO control voltage in (a) 10 and (b) 20 phases SSCG                   | 86 |

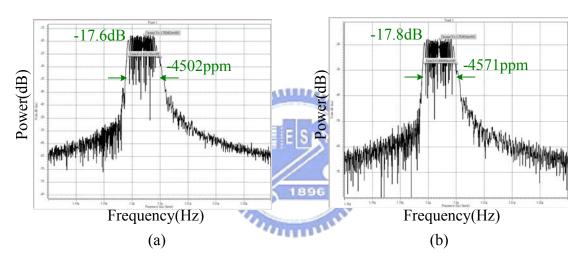

| Fig. 5.38 Carrier Spectra with spread spectrum in (a) 10 and (b) 20 phases SSCG. | 86 |

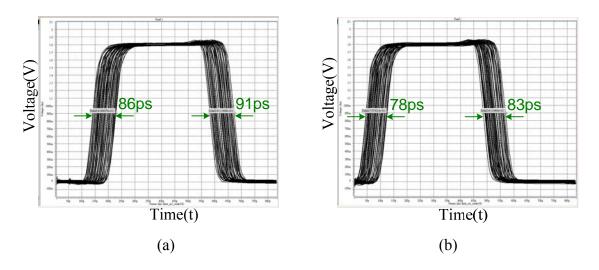

| Fig. 5.39 P-P jitter in (a) 10 and (b) 20 phases SSCG                            | 86 |

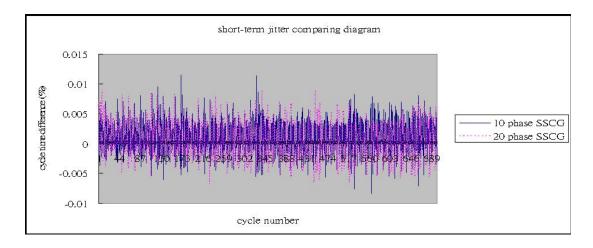

| Fig. 5.40 Cycle to Cycle jitter in 10 and 20 phases SSCG                         | 87 |

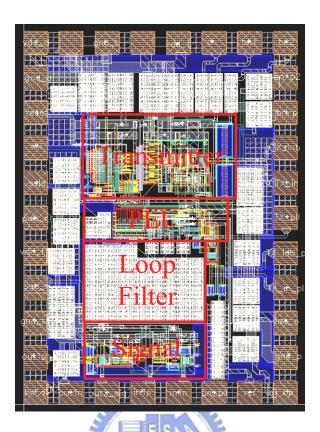

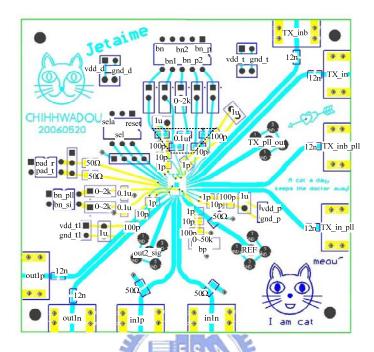

| Fig. 5.41 Chip layout of SSCG                                                    | 90 |

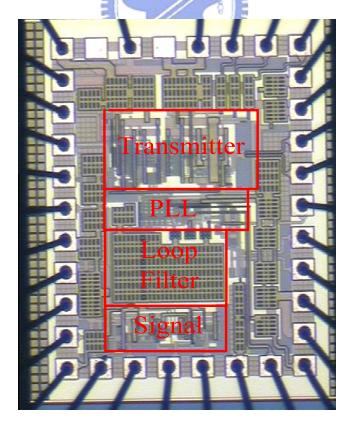

| Fig. 5.42 Chip layout of low jitter-PLL                                          | 91 |

| Fig. 5.43 Die microphotograph of low-jitter PLL                                  | 91 |

| Fig. 5.44 PCB of low-jitter PLL                                                  |    |

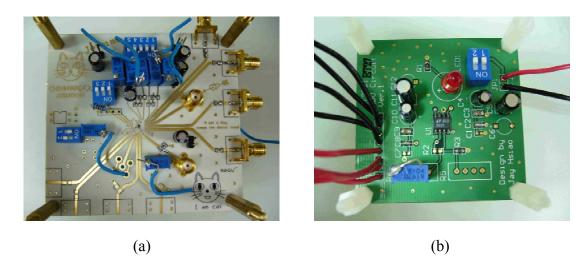

| Fig. 5.45(a) PCB (b) Regulator                                                   | 93 |

| Fig. 5.46 Photograph of PCB and voltage regulator                                | 93 |

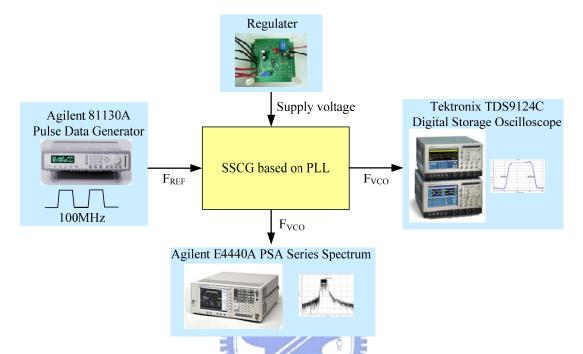

| Fig. 5.47 Measurement setup of the programmable SSCG                             | 94 |

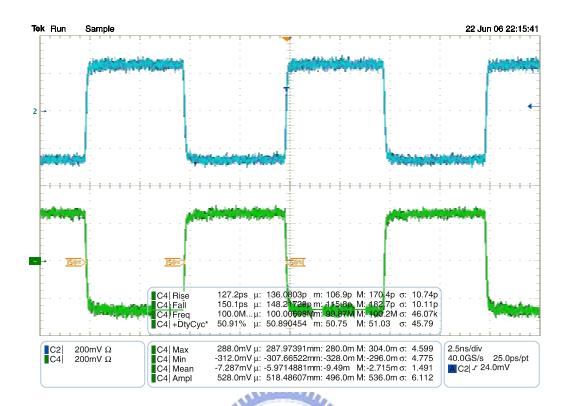

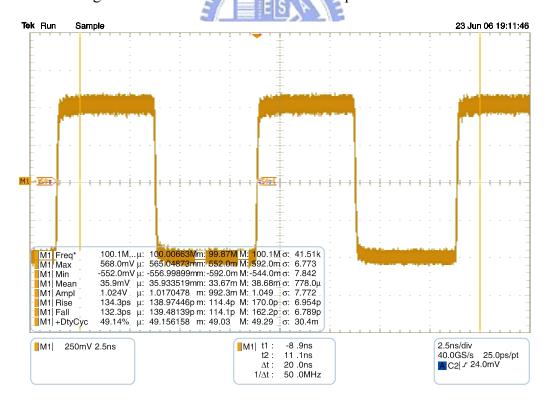

| Fig. 5.48 Measurement of differential output from DIVIDER                        | 95 |

| Fig. 5.49 Measurement waveform of DIVIDER                                        | 95 |

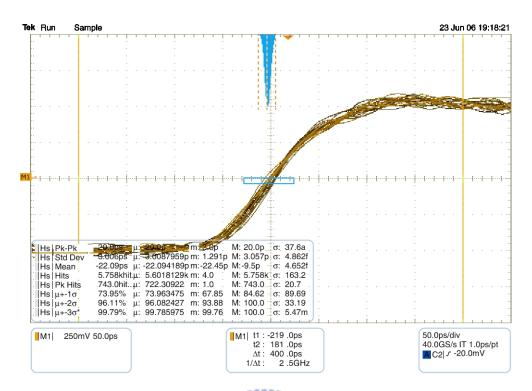

| Fig. 5.50 Peak to Peak Jitter of DIVIDER.                                        | 96 |

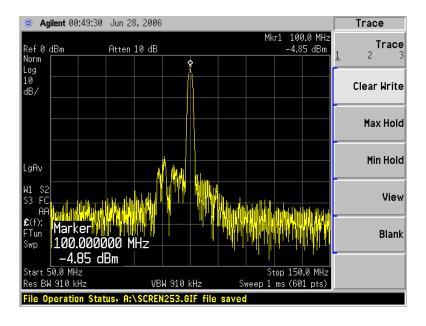

| Fig. 5.51 Carrier Spectra when PLL locked.                                       | 96 |

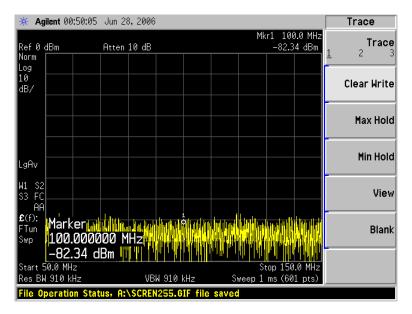

| Fig. 5.52 Carrier Spectra in no signal                                           | 97 |

# **List of Tables**

| Table 2.1 Phase margin under various $K/\omega_2$                | 25 |

|------------------------------------------------------------------|----|

| Table 5.1 SSCG in Serial-ATA specifications                      | 58 |

| Table 5.2 PMOS and NMOS in 0.18um CMOS                           | 71 |

| Table 5.3 Parameter in programmable modulation profile generator | 78 |

| Table 5.4 Transform equation of the control circuit              | 80 |

| Table 5.5 PLL performance summary                                | 87 |

| Table 5.6 PLL performance in corner cases                        | 88 |

| Table 5.7 Programmable SSCG performance comparison               | 88 |

| Table 5.8 Comparison of SSCG performance                         | 89 |

## Chapter 1

### Introduction

#### 1.1 Introduction of Timing Module for Serial Link

Recently, the advance in IC fabrication technology along with aggressive circuit design have led to an exponential growth of the speed and integration levels of digital IC's. However, these advancements have led to some chips being limited by the chip-to-chip data communication bandwidth. This limitation has motivated research in the area of high-speed link that interconnect systems. So that the increasing demands for the data bandwidth in network has driven the development of high-speed and low-cost serial link technology. The serial link technology can lower the numbers of transmission lines to decrease volumes and cost, and decrease the EMI effect. The population applications are such as USB2.0, IEEE-1394b, RAM Bus, Serial ATA, and PCI express.

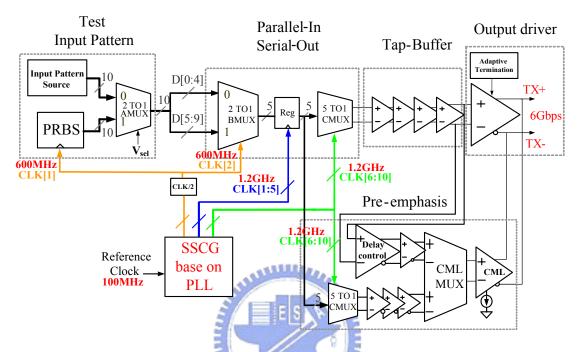

Fig. 1.1 shows the transmitter architecture of 6Gbps for Serial ATA [1]. The transmitter is composed of a phase-locked loop, PISO, buffer, driver and pre-emphasis. High speed parallel to serial data conversion is achieved by means of time-division 5 to 1 multiplexer controlled by a multi-phases PLL which oscillates in 1.2GHz. Finally, the serial data of 6Gbps is sent to the receiver through the channel. The REG and CMUX need 5 phases of the 1.2GHz clock respectively. We use the different 5 phases

to control the REG and CMUX in order to prevent influencing each other. As a result, our goal is to design a low-jitter 5-stages ring oscillators and 10-phases clocking for a 6Gbps serial link transmitter.

Fig. 1.1 Architecture of Serial-ATA transmitter with PLL

#### 1.2 Motivation

As chips work at faster operation speed, the timing issue becomes more and more important. PLL (phase-locked loop) can generate a clean and stable clock to work as timing source, so the PLL plays an important role in all high-speed systems, because these systems require a stringent timing specification.

PLL is already widely used in SoC designs. It is often applied to communication applications, such as: frequency synthesizer, clock multiplier, Clock and Data Recovery (CDR) circuit, and clock de-skew application. The design of PLL is a trade-off among jitter performance, frequency / phase resolution, lock-in time, area cost, power consumption, circuit complexity and design time. So how to design a suitable PLL for system requirement is the most important issue in the system timing.

There are two of VCO: LC tank and ring oscillator. The things we are concerned in choosing the VCO structure are the low phase noise, sufficient tuning range and acceptable power consumption. LC tank oscillators are widely used in the wireless communication applications due to their ease of achieving high frequency with power consumption [2], but its disadvantage is difficult to implement a good inductor and frequency running range small. So the performance of the frequency synthesizer is sensitive to the process variations. However, ring oscillators are much easier implementing high quality IC. It also has wider tuning range and occupies smaller area than a LC tank. It can also easily provide multiple phases and this is the main reason we choose the ring oscillator in our VCO.

Besides, due to the operation speed is becoming faster and faster, many higher order harmonics of the signal are generated. These signals often generate Electric-Magnetic Interference (EMI) that affects the operation of other equipments. In a portable device, the high-speed interfaces between peripheral storages and the other signal processing units are the main noise sources. When the operation speed is higher, the EMI problem is more severe.

There are many methods to diminish EMI; and all have positive and negative effects on the products. Among these methods, spread spectrum is the simplest and the most efficient one. It also offers the best immunity with respect to manufacturing process variation.

Spread spectrum scheme is to slightly modulate a narrowband clock's signal frequency, and spread it over a wider bandwidth: In this way, energy peaks at specific frequencies are diminished. This approach reduces the EMI of fundamental clock frequency, as well as the higher order harmonic components. Therefore the EMI radiation of the whole system is reduced.

As external storage devices are widely used, high-speed serial links connecting hosts and external devices are becoming popular. Serial AT Attachment (SATA) is one of the most promising technologies providing large bandwidth up to 6Gbps (in SATAIII). SATA specification defines an EMI reduction method using spread-spectrum clocking (SSC), which reduces the peak EMI emission by spreading carrier frequency. EMI reduction using SSC has been studied and explored in several papers. However, it is more important to consider the time-domain impact of SSC in addition to the EMI peak reduction since the major concern in serial data transmission is signal integrity in the time domain. A low-jitter programmable spread-spectrum clock generator using switching phases and the  $\Delta\Sigma$  modulator is presented in this thesis.

Low jitter PLL is achieved through VCO with low K<sub>VCO</sub> by using medium-threshold voltage PMOS and passive resistance. The spectrum in the clock generator can be spread by 10 phases or 20 phases depending on the requirement, such as power saving or low jitter in time domain. Our SSCG for Serial ATA Specification is down spread 5000 ppm with a triangular waveform of modulation frequency 30~33KHz. The proposed circuit is fabricated in a 0.18-um CMOS process. The non-spread spectrum clocking has a peak to peak jitter of 3.1ps and the maximum EMI reduction is -17.8dB in 20 phases spread spectrum mode which the power dissipation is only 28mw.

#### 1.3 Thesis Organization

This thesis will introduce the basic theorem of the low jitter PLL and programmable spread spectrum clocking. Besides, the circuit implementation in PLL and SSCG is also explained in detail. The thesis is organized as follows:

Chapter 2 begins with the brief introduction of the charge-pump PLL. We describe the way to analyze PLL in the linear model. Then we discuss the open loop transfer function as well as closed loop transfer function.

In Chapter 3, we describe the principle of SSCG using switching phase scheme. The most important design is to let the  $\Sigma\Delta$  modulator control the jumping phases and make a spreading spectrum clock.

Chapter 4 begins with the introduction to EMI problem and several solutions used for the EMI reduction. The most significant part explains the concept of spread spectrum using frequency modulation technology. Other parameters, like modulation profile and modulation frequency and timing impacts, are also discussed.

In Chapter 5, a low jitter programmable spread spectrum clock generator using switching phase is presented. The SSCG is fabricated in 0.18µm CMOS 1P6M process. We first introduce the architecture of the proposed programmable spread spectrum clock generator and the behavior simulation in MATLAB. The following sections describe the implementations and simulations in Hspice of each building block. Finally, we show the measurement setup and the measurement results.

Chapter 6 gives conclusions to our work. Suggestions for future works are recommended at the ending of this thesis

## Chapter 2

## **Principles of Phase-Locked Loop**

#### 2.1 Introduction to PLL

Due to the demand for higher performance and lower cost in electronic systems, and the advance of integrated-circuit (IC) technologies in terms of speed and complexity, Phase-locked loop (PLL) become more and more popular in the last twenty years. PLL plays an important role in radio, telecommunications, wireless systems, and computers, especially for the serial link transceiver. Because whether parallel-to-serial data conversion in the transmitter or serial-to-parallel data conversion in the receiver, the generating phases of PLL are needed.

A PLL is a feedback circuit that causes a particular system to track with another reference signal. In other words, a PLL is a circuit synchronizing an output signal with a reference in frequency as well as in phase. In the locked state, the phase error between the oscillator's output signal and the reference signal is zero, or remains constant.

If a phase error builds up, the feedback system of PLL will act on the oscillator such that the phase error will be reduced to a minimum. Finally, the phase of the output signal is again locked to the phase of the input signal. That is why we call it as phase-locked loop.

The main applications of PLL are as follows:

- 1. Clock recovery: Some data streams, especially high-speed serial data streams, (such as the raw stream of data from the magnetic head of a disk drive) are sent without an accompanying clock. The receiver generates a clock from an approximate frequency reference, and then phase-aligns to the transitions in the data stream with a PLL. In order for this scheme to work, the data stream must have a transition frequently enough to correct any drift in the PLL's oscillator. Typically, some sort of redundant encoding is used; 8B10B is very common.

- 2. **Deskewing**: If a clock is sent in parallel with data, that clock can be used to sample the data. Because the clock must be received and amplified before it can drive the flip-flops which sample the data, there will be a finite, and process-, temperature-, and voltage-dependent delay between the detected clock edge and the received data window. This delay limits the frequency at which data can be sent. One way of eliminating this delay is to include a de-skew PLL on the receive side, so that the clock at each data flip-flop is phase-matched to the received clock.

- **3. Clock generation**: Most electronic systems include processors of various sorts that operate at hundreds of megahertz. Typically, the clocks supplied to these processors come from clock generator PLLs, which multiply a lower-frequency reference clock (usually 50 or 100 MHz) up to the operating frequency of the processor. The multiplication factor can be quite large in cases where the operating frequency is multiple gigahertz and the reference crystal is just tens or hundreds of megahertz.

- **4. Spread spectrum**: All electronic systems emit some unwanted radio frequency energy. Various regulatory agencies (such as the FCC in the United States) put limits on this emitted energy and any interference caused by it. The emitted noise

generally appears at sharp spectral peaks (usually at the operating frequency of the device, and a few harmonics). A system designer can use a spread-spectrum PLL to reduce interference with high-Q receivers by spreading the energy over a larger portion of the spectrum. For example, by changing the operating frequency up and down by a small amount (about 1%), a device running at hundreds of megahertz can spread its interference evenly over a few megahertz of spectrum, which drastically reduces the amount of noise seen by FM receivers which have a bandwidth of tens of kilohertz.

#### 2.2 Brief History

The very first phase-locked loops were implemented as early as 1932 by Bellescize; this French engineer is considered the inventor of "coherent communication." However, The PLL found industrial applications only when it became available as an IC. The first PLL ICs appeared around 1965 and were called linear PLL (LPLL)[3], because each block is analog device. An analog multiplier was used as the phase detector and the loop filter was built from a passive or active RC filter. In the following years the first digital PLL (DPLL) was invented in 1970. It is in effect a hybrid device. The only digital circuit is phase detector, e.g., made from an EXOR gate or a JK-flipflop. But the remaining blocks were still analog. A few years latter, the "all-digital" PLL (ADPLL) was invented. Each block is digital. The loop filter is from Up/Down counter. The VCO is from DCO. Finally, software PLL was presented. The PLL functions are performed by a computer program rather than a piece of specialized hardware.

#### 2.3 Basic Operations in PLL

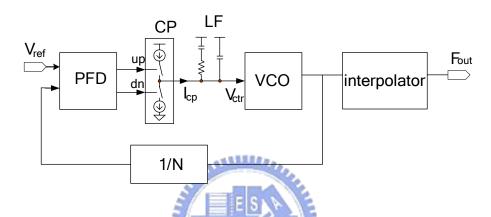

A basic PLL consist of five parts (Fig. 2.1): phase/frequency detector (PFD), charge pump (CP), loop filter (LF), voltage-controlled oscillator (VCO) and frequency divider. The interpolator is not always needed unless you want to create more phases.

Fig. 2.1 The block diagram of PLL

The operation principle of the PLL is as follows: the PFD compares the frequency and phase errors between the reference signal and the feedback signal from the output of the divider, thus producing digital up or down signals to control the CP.