# 國立交通大學

電子工程學系 電子研究所碩士班 碩 士 論 文

2Gbps 低擺幅差動訊號傳輸之傳送器 A 2Gbps Reduced Swing Differential Signaling (RSDS) Transmitter

研究生: 鄭鍵樺

指導教授 : 吳錦川 教授

中華民國九十四年八月

## 2Gbps 低擺幅差動訊號傳輸之傳送器

#### A 2Gbps Reduced Swing Differential Signaling (RSDS)

#### **Transmitter**

研究生: 鄭鍵樺 Student: Chien-Hua Cheng

指導教授: 吳錦川 教授 Adviser: Prof. Jiin-Chuan Wu

國立交通大學 電子工程學系 電子研究所碩士班 碩士論文

A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

for the Degree of

Master of Science

In

**Electronic Engineering**

Aug 2005

Hsin-Chu, Taiwan, Republic of China

中華民國九十四年八月

## 2Gbps 低擺幅差動訊號傳輸之傳送器

學生:鄭鍵樺 指導教授:吳錦川 博士

國立交通大學電子工程學系 電子研究所碩士班

#### 摘要

隨著積體電路製程技術的日新月異,處理器的運算速度愈來愈快,單位時間內處理的資料量也日益增多,通常,傳輸介面的電路所能達到的單位時間最大傳輸量往往是整體系統速度的關鍵限制,因此,本篇論文是描述一個應用於高速串列數位影像傳輸介面,使用低擺幅差動訊號傳輸之傳送器的設計,並致力於設計此傳送器之資料傳輸速度操作在 2Gbps 。

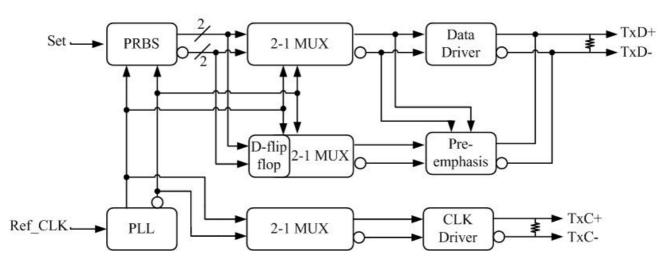

傳送器由一個四相位鎖相迴路、虛擬隨機位元串列產生器、二對一多工器和一擁有預先加強電路設計之輸出驅動器所組成,其中,四相位鎖相迴路的輸入頻率為125MHz,輸出為四個相位 平均分佈且頻率同為1GHz的時脈訊號,所包含的電路有相位/頻率偵測器、電荷幫浦、迴路濾波器、兩級差動壓控振盪器和一個除八的除頻器。此鎖相迴路所產生的平均分佈時脈提供給虛擬隨機位元串列產生器和二對一多工器,並將一組並列資料轉為串列輸出,再經由輸出驅動器並搭配預先加強電路,來增加傳送資料位元轉變期間所需的電流量,最後,將此串列資料傳送至傳輸線上,即完成整個傳送器的設計。

此傳送器採用 TSMC 0.35μm 2P4M CMOS 製程技術實現,當鎖相迴路輸入時脈為 66.67MHz 時,傳送器能正常傳送出 1066.67Mbps 的串列資料。

A 2Gbps Reduced Swing Differential Signaling (RSDS) Transmitter

Student: Chien-Hua Cheng Adviser: Prof. Jiin-Chuan Wu

Department of Electronics Engineering & Institute of Electronics

National Chiao-Tung University

**Abstract**

As the advancement of IC fabrication technology, the operation of processors has sped

up. The amounts of data processed in each unit time become larger and larger as time goes

by. For most of time, the key limitation of a whole system is the maximum data amounts of

the transmission interface circuit transmitted in each unit time. Therefore, the thesis

describes the design of a transmitter for a high-speed serial digital display interface by

RSDS technique. We have devoted to design the data rate of the transmitter at 2Gbps.

The transmitter is composed of a four-phase PLL, PRBS circuits, 2-1 multiplexers and

an output data driver with a pre-emphasis circuit. Among these devices, the input frequency

of the four-phase PLL is 125MHz; it outputs four uniformly distributed clocks with 1 GHz

frequency. The PLL comprises a Phase/Frequency Detector, a Charge Pump, a Loop Filter, a

two-stage differential VCO and a divided-by-eight divider. It offers the PRBS and the 2-1

multiplexer with four uniformly distributed clocks to convert parallel pseudo-data into serial

stream. Then, the serial data is transmitted by an output data driver with the pre-emphasis

circuit. The pre-emphasis circuit is designed to increase the current during the data

transition. In the end, the transmitter drives the serial data onto the transmission bus.

The transmitter is implemented in the TSMC 0.35µm 2P4M CMOS process. When the

input reference frequency is 66.67MHz, the transmitter can transmit serial data at

1066.67Mbps successfully.

iii

#### 致謝

首先,我要感謝我的指導老師吳錦川教授,在碩士班兩年的研究生涯中,不厭其 煩地指導我,不論是專業知識的培養,或是做研究的態度和處理問題的方法,都讓我 獲益良多。其次,也要感謝陳巍仁教授、藍正豐學長、張恆祥學長撥冗擔任我的口試 委員,並且提供我不少寶貴的意見。

接下來我要感謝我的父母,在金錢、精神等各方面全力的支援我,也由於沒有後顧之憂,才能夠專心一志的在研究所的這兩年實現我的短程目標和理想。這本論文能夠順利完成,還得要感謝口譯界的明日之星頌衍和心理界的未來之光舒聿,在英語文法上的幫助及教學。

論文研究能夠完成,要感謝在 307實驗室的諸多學長,謝謝你們這兩年的指導, 另外,還要感謝一同在 527 奮鬥的夥伴,諭哥、建樺、紅毛、弼嘉、阿信、煒銘、polo、 志朋、傑忠、巴嘿、粘哥、岱原、台祐、小西西、建文、進元等好多好多人,有了你 們,平淡的研究生活多了許多樂趣,還有其他的學長、同學,要感謝的人還有很多, 在此一併感謝。

最後還要感謝我的大學同期,陪我一起熬夜爆肝的玩,在我研究學習之於,回復 我的戰鬥力和增加我的肝功能指數,還有要感謝我的女朋友舒聿,總是給予我最大的 支持和鼓勵,妳的每一個笑容是我繼續努力下去的原動力。

謹以此篇論文獻給所有關心我的人。

鄭鍵樺

國立交通大學

中華民國九十四年八月

## **CONTENTS**

| ABSTRACT (CHINESE)                                  | i   |

|-----------------------------------------------------|-----|

| ABSTRACT (ENGLISH)                                  | iii |

| ACKNOLEDGMENTS                                      | V   |

| CONTENTS                                            | vii |

| LIST OF TABLES                                      | X   |

| LIST OF FIGURES                                     | xii |

|                                                     |     |

|                                                     |     |

| CHAPTER 1 INTRODUCTION                              |     |

| 1.1 Motivation                                      | 1   |

| 1.2 What is RSDS?                                   | 2   |

| 1.2 What is RSDS?                                   | 3   |

|                                                     |     |

| CHAPTER 2 BACKGROUND                                |     |

| 2.1 RSDS <sup>TM</sup> Specification                | 5   |

| 2.1.1 Scope                                         | 5   |

| 2.1.2 Introduction of RSDS                          | 5   |

| 2.1.3 System Diagram                                | 6   |

| 2.1.4 Electrical Specification                      | 7   |

| 2.1.5 RSDS <sup>TM</sup> Transmitter Characteristic | 7   |

| 2.1.6 Bus Configuration                             | 8   |

| 2.2 Basic Link Design                               | 10  |

| 2.3 Interface Consideration                         | 11  |

| 2.4 Eye Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| CHAPTER 3 PHASE- LOCKED LOOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15 |

| 3.2 Architecture of Phase-Locked Loop (PLL)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 16 |

| 3.3 Circuit Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

| 3.3.1 Phase/Frequency Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17 |

| 3.3.2 Charge Pump                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 20 |

| 3.3.3 Loop Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

| 3.3.4 Voltage Controlled Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22 |

| 3.3.5 Divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 27 |

| 3.4 PLL Liner Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29 |

| 3.4 PLL Liner Model  3.5 Noise Analysis and Stability  3.6 Loop Parameter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 31 |

| 3.6 Loop Parameter Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33 |

| 3.7 Specification and Simulation of Transmitter PLL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 35 |

| To the state of th |    |

| CHAPTER 4 TRANSMITTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

| 4.1 Architecture of Transmitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 38 |

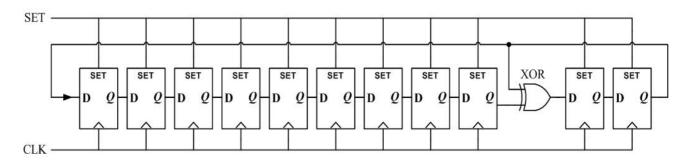

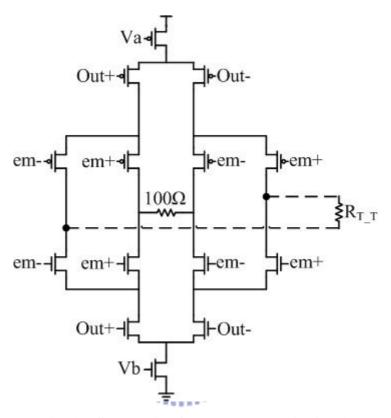

| 4.2 Pseudo Random Bit Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39 |

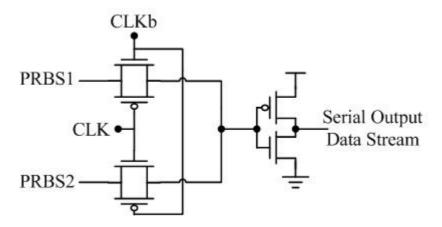

| 4.3 2-1 Multiplexer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 40 |

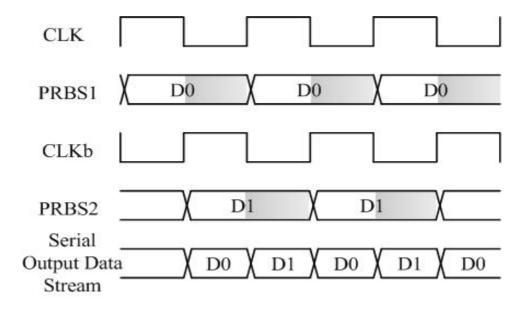

| 4.4 Data Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41 |

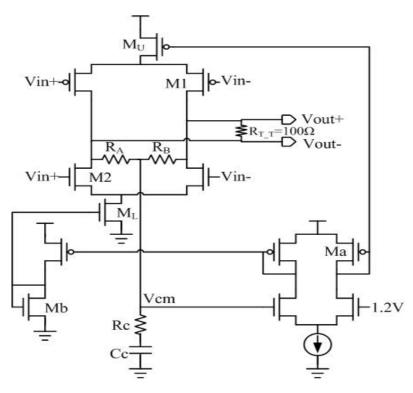

| 4.5 Pre-emphasis Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43 |

| 4.6 Transmitter Simulation Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

| CHAPTER     | 5 EXPERIMENTAL RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.1 Experir | mental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46   |

| 5.2 Layout  | and PCB Consideration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 47   |

| 5.3 Transm  | nitter Experimental Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48   |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| CHAPTER     | 6 CONCLUSIONS AND FUTURE V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WORK |

| 6.1 Conclu  | usion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55   |

| 6.2 Future  | work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56   |

| REFERENC    | CES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 57   |

| VITA        | ES I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59   |

|             | THE PERSON NAMED IN COLUMN TWO IS NOT THE PARTY OF THE PA |      |

## LIST OF TABLES

| Table 1-1 RSDS and LVDS                                                | 3  |

|------------------------------------------------------------------------|----|

| Table 2-1 Electrical Specifications of RSDS <sup>TM</sup> transmitters | 8  |

| Table 3-1 Parameters of the PLL                                        | 35 |

| Table 4-1 the operation of the pre-emphasis circuit                    | 45 |

## LIST OF FIGURES

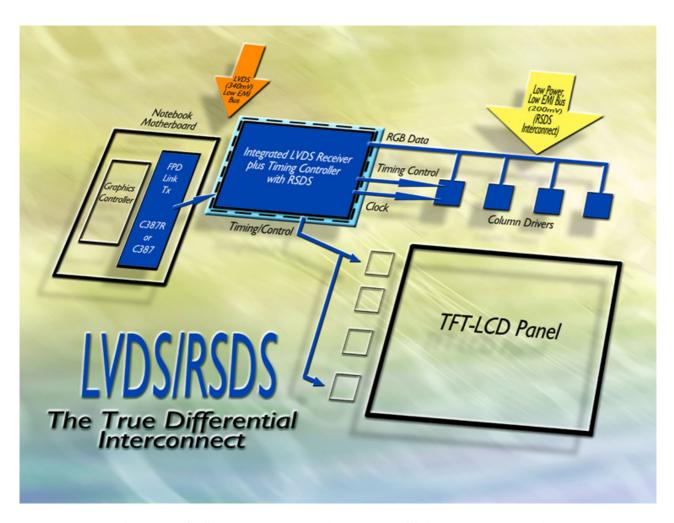

| Fig. 1-1 RSDS technology used in energy-efficient Flat Panel Displays    | 2  |

|--------------------------------------------------------------------------|----|

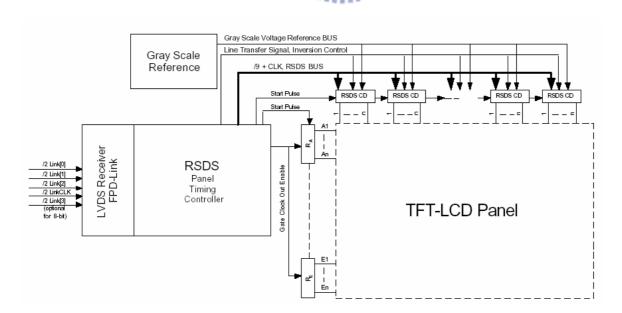

| Fig. 2-1 Block Diagram of the LCD Module with Discrete Timing Controller | 6  |

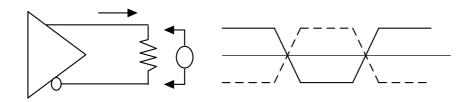

| Fig. 2-2 RSDS <sup>TM</sup> Interface                                    | 7  |

| Fig. 2-3 RSDS <sup>TM</sup> reference circuit and transmitter output     | 7  |

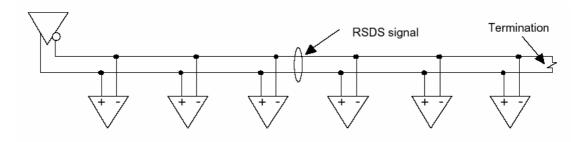

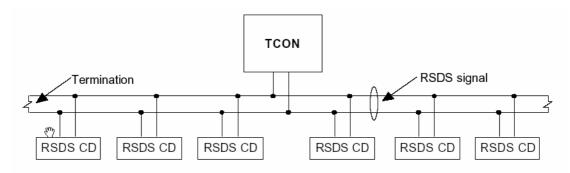

| Fig. 2-4 Type 1 Bus Configuration                                        | 9  |

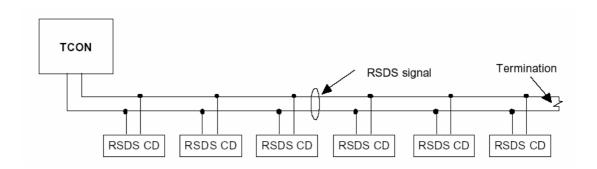

| Fig. 2-5 Type 2 Bus Configuration                                        | 9  |

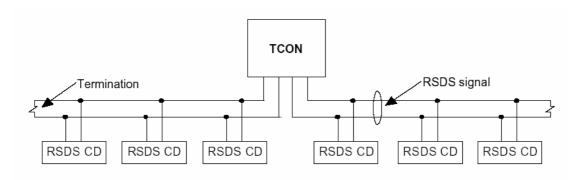

| Fig. 2-6 Type 3 Bus Configuration                                        | 10 |

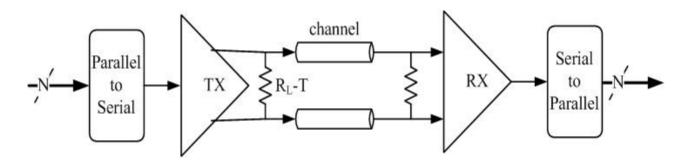

| Fig. 2-7 Block diagram of the basic serial link                          | 11 |

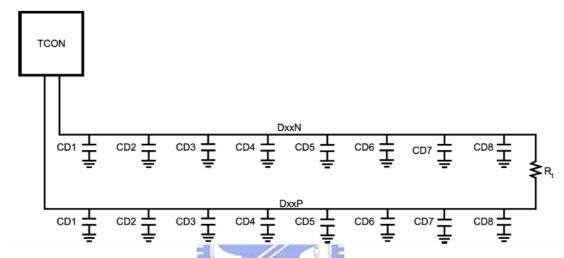

| Fig. 2-8 Loading of RSDS Bus                                             | 13 |

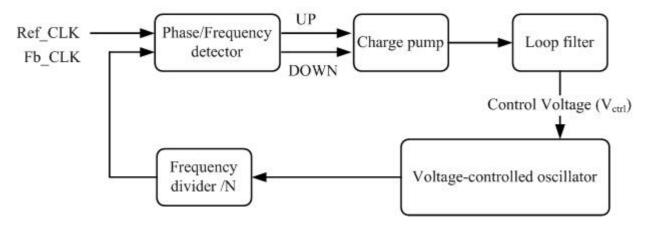

| Fig. 3-1 Functional block diagram of charge pump PLL.                    | 16 |

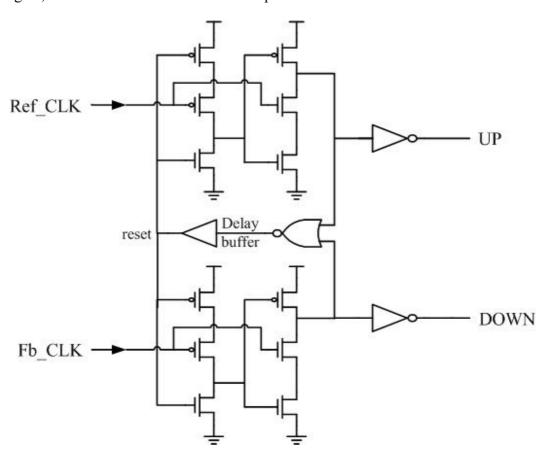

| Fig. 3-2 Phase/Frequency detector with TSPC D-flip flops                 | 17 |

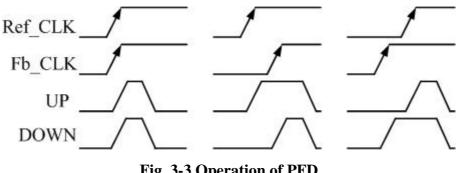

| Fig. 3-3 Operation of PFD                                                | 18 |

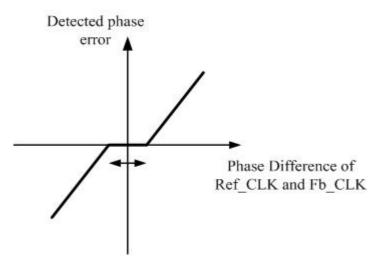

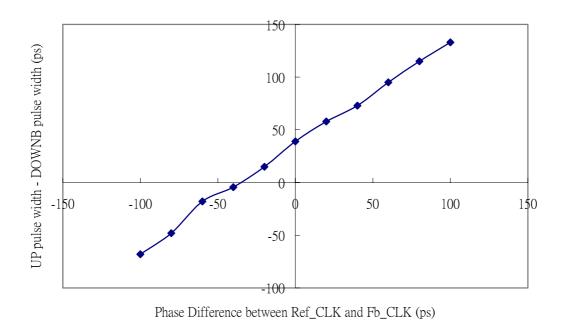

| Fig. 3-4 The PFD dead zone                                               | 19 |

| Fig. 3-5 simulation result of PFD without dead zone                      |    |

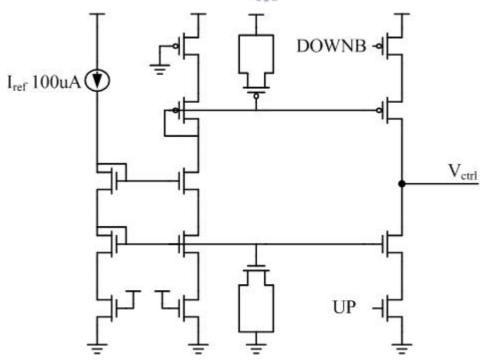

| Fig. 3-6 Schematic of the charge pump                                    | 20 |

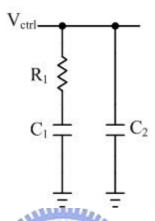

| Fig. 3-7 Schematic of the loop filter                                    | 21 |

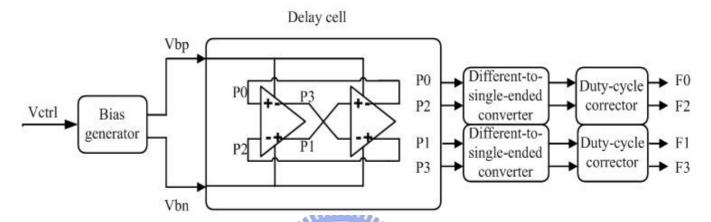

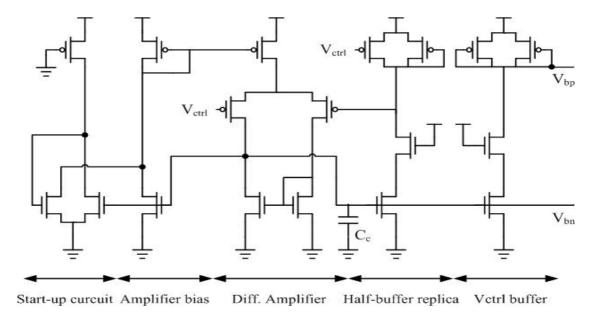

| Fig. 3-8 Architecture of the VCO.                                        | 22 |

| Fig. 3-9 the replica-feedback current source bias circuit                | 23 |

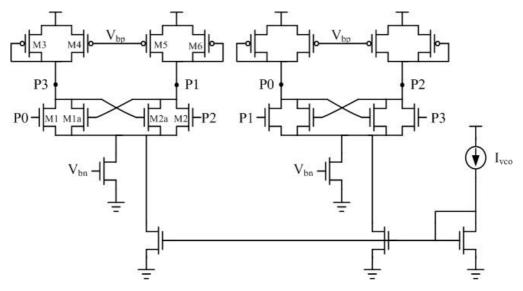

| Fig. 3-10 Differential delay cells with partial positive feedback        | 23 |

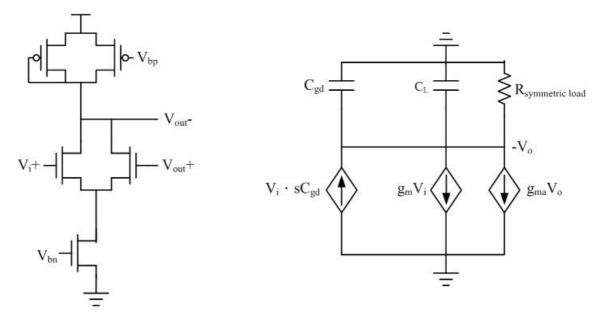

| Fig. 3-11 Half-circuit and small signal model of a delay cell            | 24 |

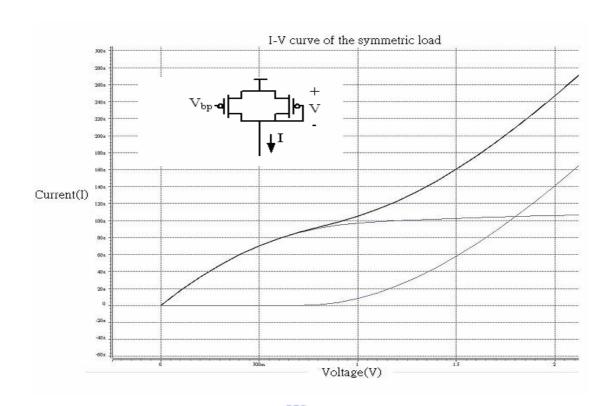

| Fig. 3-12 Typical symmetric load and I-V characteristic                  | 25 |

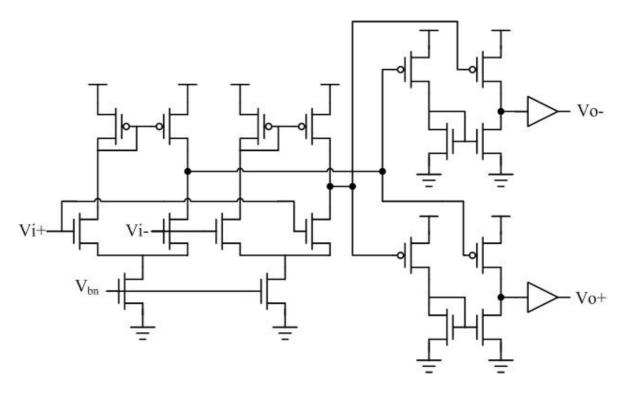

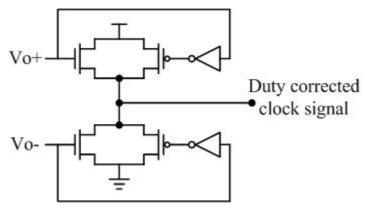

| Fig. 3-13 Schematic of differential-to-single-ended converter            | 26 |

| Fig. 3-14 Feed forward-type duty-cycle corrector schematic               | 26 |

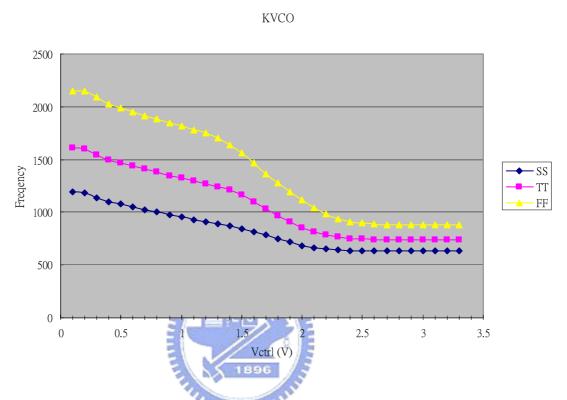

| Fig. 3-15 Transfer curve of the VCO                                      | 27 |

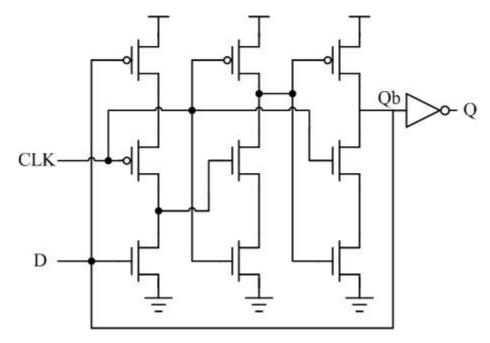

| Fig. 3-16 Schematic of TSPC asynchronous divided-by-two circuit                  | 28 |

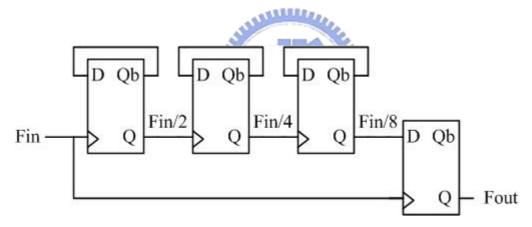

|----------------------------------------------------------------------------------|----|

| Fig. 3-17 Divided-by-eight circuit with asynchronous and synchronous counters    | 28 |

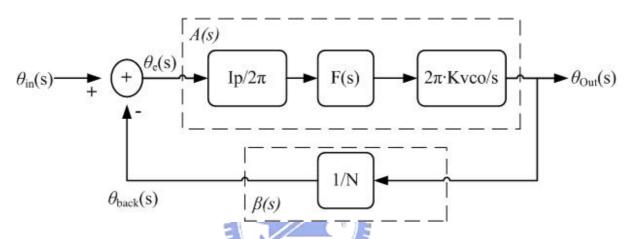

| Fig. 3-18 Linear model of the PLL                                                | 29 |

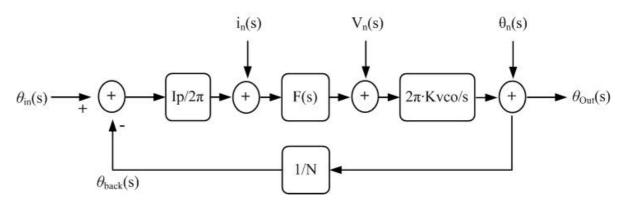

| Fig. 3-19 The PLL linear model with different noise sources                      | 31 |

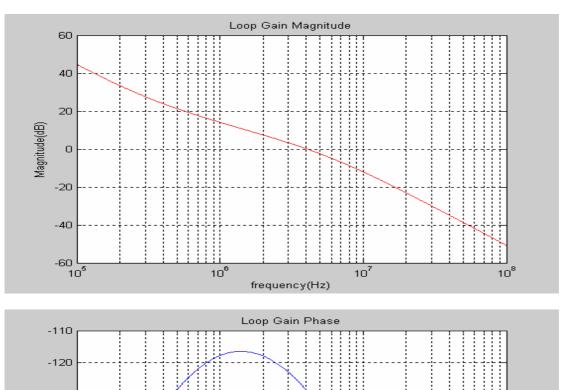

| Fig. 3-20 Loop gain simulation of the PLL using parameters in Table 3-1          | 36 |

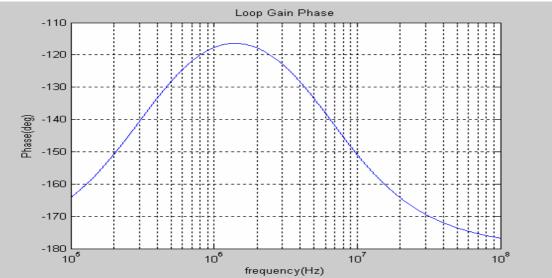

| Fig. 3-21 Closed Loop Gain simulation of the PLL                                 | 36 |

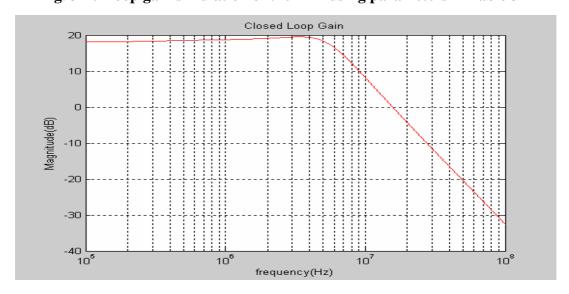

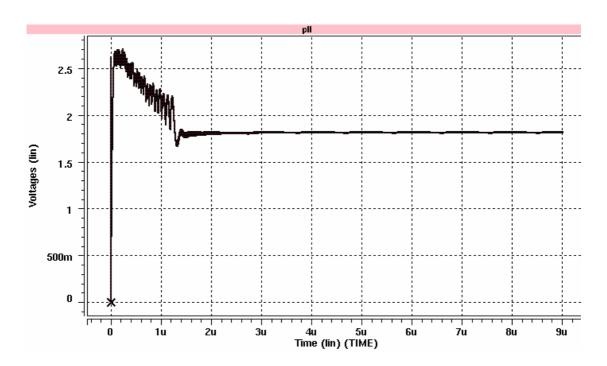

| Fig. 3-22 Control voltage simulation of the VCO                                  | 37 |

| Fig. 3-23 Simulation of the four output clock signals of the PLL.                | 37 |

| Fig. 4-1 Architecture of the transmitter                                         | 39 |

| Fig. 4-2 Block diagram of the PRBS circuit.                                      | 40 |

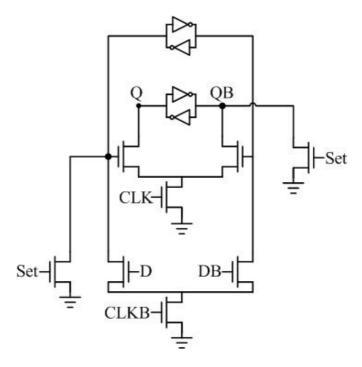

| Fig. 4-3 D-flip flop delay cell of the PRBS circuit.                             | 41 |

| Fig. 4-4 Schematic of the 2-1 transmission-gate multiplexer                      | 41 |

| Fig. 4-5 Timing Diagram of the serial output data stream                         | 42 |

| Fig. 4-6 Schematic of the transmitter driver and the closed-loop control circuit | 43 |

| Fig. 4-7 Schematic of the pre-emphasis circuit                                   | 44 |

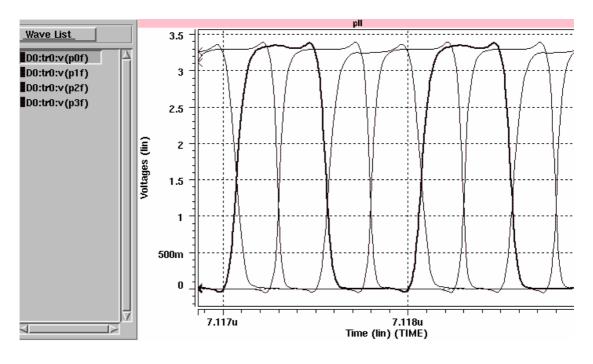

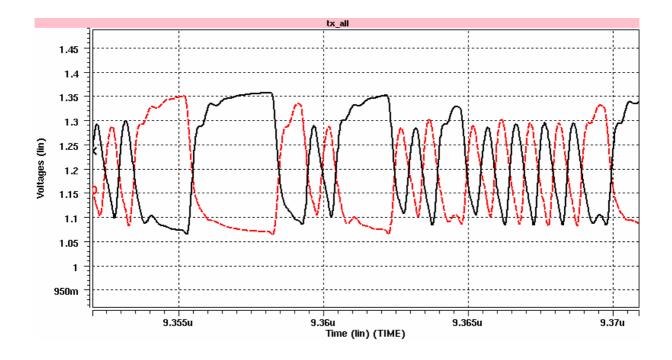

| Fig. 4-8 Simulation result of the transmitter output waveform                    | 45 |

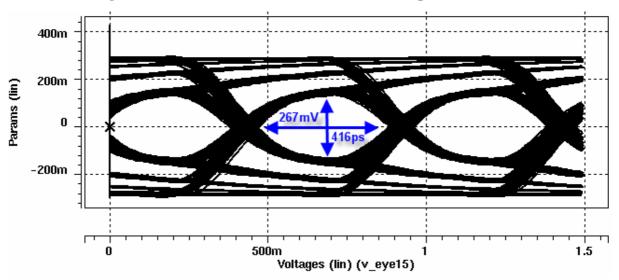

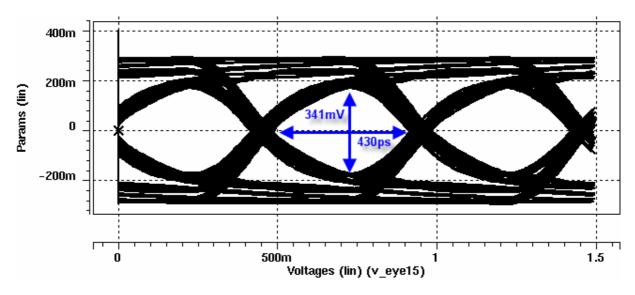

| Fig. 4-9 Eye diagram of the signal at transmitting side without pre-emphasis     | 46 |

| Fig. 4-10 Eye diagram of the signal at transmitting side with pre-emphasis       | 46 |

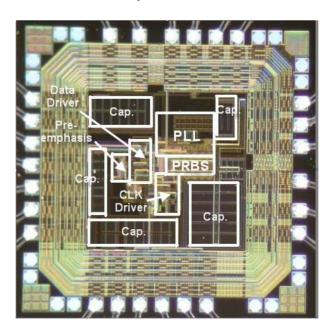

| Fig. 5-1 Chip layout micrograph of the transmitter                               | 47 |

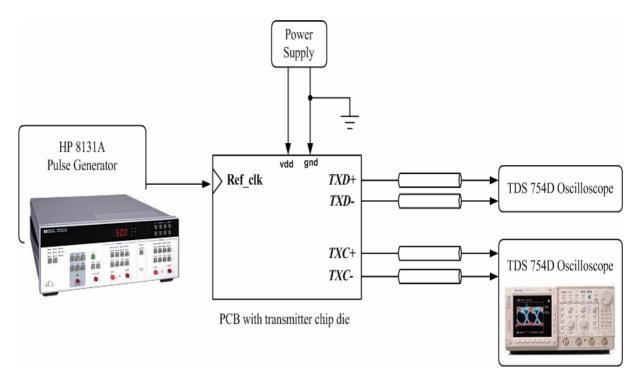

| Fig. 5-2 the experimental setup of the transmitter                               | 48 |

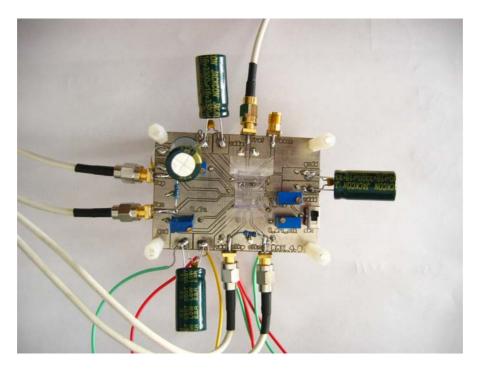

| Fig. 5-3 the print circuit board layout                                          | 49 |

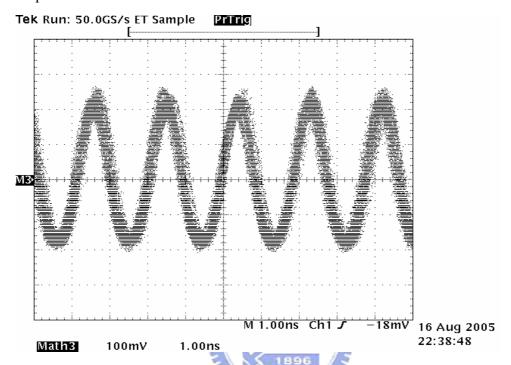

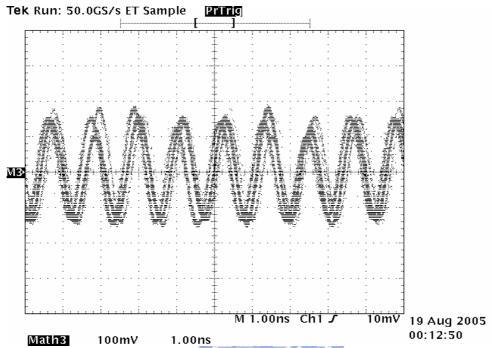

| Fig. 5-4 the differential output of the transmitter clock driver                 |    |

| at VCO's free running frequency 270MHz.                                          | 50 |

| Fig. 5-5 the eye diagram of the transmitter data driver differential output      |    |

| at 540 Mbps (according to the Fig. 5-4)                                          | 50 |

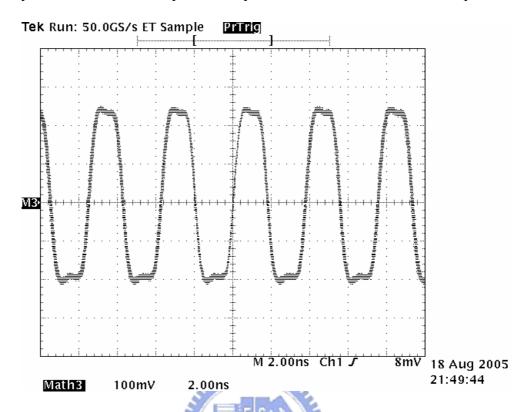

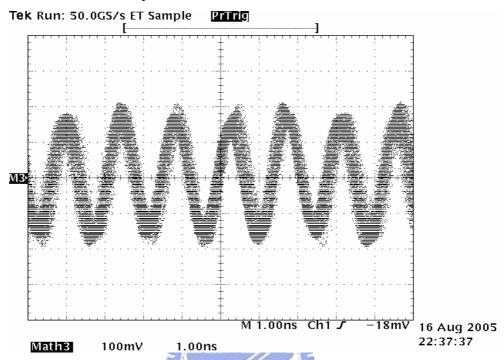

| Fig. 5-6 the differential output of the transmitter clock driver at 533 MHz                                 | 51  |

|-------------------------------------------------------------------------------------------------------------|-----|

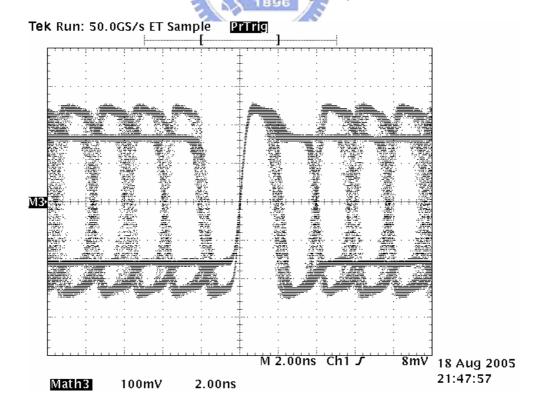

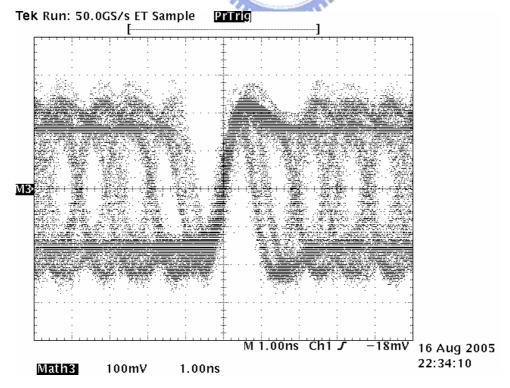

| Fig. 5-7 the eye diagram of the transmitter data driver differential output at 1066 Mbps                    | 51  |

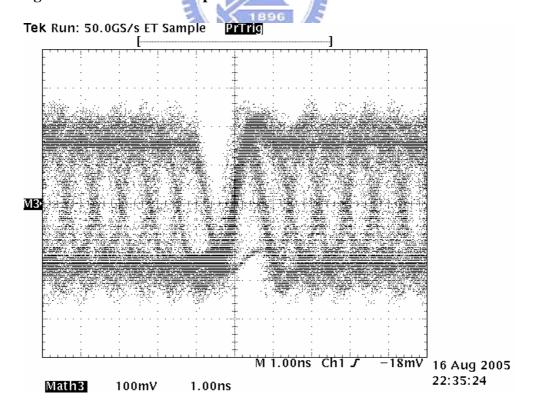

| Fig. 5-8 the differential output of the transmitter clock driver at 727 MHz                                 | 52  |

| Fig. 5-9 the eye diagram of the transmitter data driver differential output at 1454 Mbps                    | 52  |

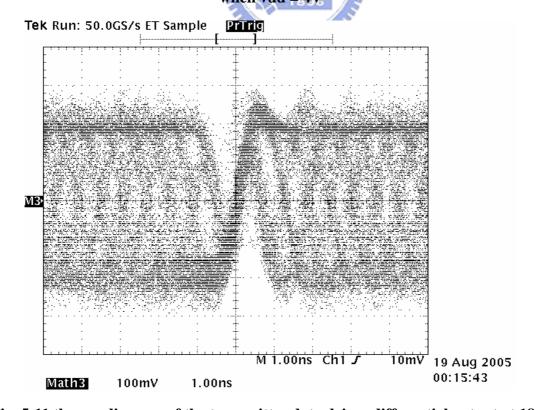

| Fig. 5-10 the differential outpus of the transmitter clock driver at 930 MHz when vdd = 4V.                 | .53 |

| Fig. 5-11 the eye diagram of the transmitter data driver differential output at 1860 Mbps when $vdd = 4V$ . | .53 |

# **Chapter 1**

## Introduction

## 1.1 Motivation