# 國立交通大學

電子工程學系 電子研究所碩士班 碩 士 論 文

1. 2Gbps 更小擺幅差動訊號傳輸模式收發器 A 1.2Gbps RSDS Serial-link transceiver

1896

研究生: 邱啟祐

指導教授 : 吳錦川 教授

中華民國九十四年八月

# 1. 2Gbps 更小擺幅差動訊號傳輸模式收發器 A 1.2Gbps RSDS Serial-link transceiver

研究生: 邱啟祐 Student: Chi-Yu Chiu

指導教授: 吳錦川 教授 Advisor: Prof. Jiin-Chuan Wu

國立交通大學 電子工程學系 電子研究所碩士班 碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering & Institute of

Electronics

College of Electrical Engineering and Computer Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

for the Degree of

Master of Science

In

**Electronic Engineering**

Aug 2005

Hsin-Chu, Taiwan, Republic of China

中華民國九十四年八月

## 1. 2Gbps 更小擺幅差動訊號傳輸模式收發器

學生:邱啟祐 指導教授:吳錦川博士

國立交通大學電子工程學系 電子研究所碩士班

#### 摘要

由於積體電路製程上技術的進展,在晶片間的資料傳輸所要求的速度與傳輸 資料量也因應的提升,但如何在達到高速傳輸的目的下卻不造成空間與功率的浪 費,而在現今以高速序列傳輸方式為主流中,具有高速、低功率、低雜訊干擾特 性的(RSDS)更小擺幅差動訊號傳輸方式的技術是頗受歡迎的。

本篇論文在研究 RSDS 傳輸模式下以 1.2Gbps 的傳輸速度運作的收發器架構,當中分為傳輸與接收兩個部份,並以 tsmc 0.352P4M CMOS 的製程技術在電壓電源為 3.3V 的情況下進行模擬。

傳輸器利用一個鎖相迴路來提供時脈和多工器將資料由並列轉為序列輸出。鎖相迴路的輸入頻率為 75MHz,輸出頻率鎖在 150MHz 並提供八個相位的時脈給多工器使用,並在時脈與資料間先進行預先位準調整,再經由八對一多工器輸出可得 1.2Gbs 的資料頻率輸出,該接收器的消耗功率為 134mW。

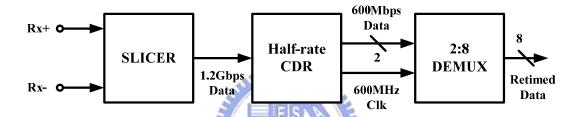

接收器使用一具磁滯現象比較器將接收訊號放大為數位訊號。再利用一操作在輸入資料一半頻率、且具有頻率、相位雙向追蹤的時脈資料回復電路來將資料與時脈對準,最後由一對八解多工器將資料轉回並列。該接收器的功率消耗為164mW。

A 1.2Gbps RSDS Serial-link transceiver

Student: Chi-Yu Chiu Advi

Advisor: Prof. Jiin-Chuan Wu

Department of Electronics & Institute of Electronics

National Chiao-Tung University

**Abstract**

Due to the improvement of IC fabrication technology, the speed and amount of

inter-chip data transmission has also been required more. The problem is how to make

high speed transmission without wasting space and power. Among the main stream,

high speed serial ports, RSDS technology with high speed, low power and low EMI

character is popular now.

This thesis describes the design of a high-speed RSDS transmission interface

with 1.2Gbps rate. The transceiver includes transmitter and receiver and is simulated

in a TSMC 0.35µm 2P4M process and at 3.3V supply voltage.

The transmitter makes use of a PLL to provide the 8-phase, 150MHz clock for

the multiplexer and translate the parallel data to be serial and the input frequency of

PLL is 75MHz. The data and clock is pre-skewed to adjust the accuracy. Then with the

8-phase clock and 8 to 1 multiplexer, the output data can be transmitted at 1.2Gbps

data rate. And the total power of the transmitter is 134mW.

The receiver uses the comparator with hysteresis to amplify the incoming data

to full swing, and uses (CDR) clock and data recovery with phase and frequency

III

detectors to lock the clock with better jitter performance. Finally, the 1 to 8 de-multiplexer converts the CDR output to 8 parallel data channels. The total power of receiver is 164mW.

#### 誌謝

首先,我要感謝我的指導老師吳錦川教授,在碩士班兩年的研究生涯中,悉心地指導我,不論是專業知識的培養,或是做研究的態度和處理問題的方法,都讓我獲益良多。其次,也要感謝陳巍仁教授、藍正豐學長、張恆祥學長撥冗擔任我的口試委員,並且提供我不少寶貴的意見。

論文研究能夠完成,要感謝在 307 實驗室的諸多學長,謝謝你們這兩年的指導,並要感謝阿瑞、周政賢、權哲等學長的教導,讓我獲益良多,在此衷心的感謝你們。還要感謝一同在 527 奮鬥的夥伴,鍵樺、志朋、傑忠、峻帆、靖驊、弼嘉、建樺、阿信、瑋銘、岱原,特別感謝同屬吳錦川老師旗下的各位伙伴們,在平時一起研究討論而在研究之餘能夠互相打氣並一同歡樂,使的課業繁重的研究生生活增添了許多的樂趣與活力,

另外要感謝我的父母與我的家人,謝謝父母從小以來栽培我所花的勞心與勞力,並在我繁忙與失意的時候給我最大的支持與鼓勵,並給予我許多的人生方向上的建議,最後要感謝我的女朋友福真,感謝你陪我度過這求學階段最艱辛也最重要的一刻,因為有妳的相陪,使我能夠一路堅持到底的努力。

謹以此篇論文獻給所有關心我的人與我所關心的朋友。

邱啟祐

國立交通大學

中華民國九十四年八月

# **Contents**

| Abstract (Chinese)           | j    |

|------------------------------|------|

| Abstract (English)           | ii   |

| Contents                     | iv   |

| List of Tables               | viii |

| List of Figures              | ix   |

| Chapter 1                    |      |

| Introduction                 |      |

| 1.1 Motivation               | 1    |

| 1.2 Introduction of RSDS     |      |

| 1.2.1 RSDS/LVDS              |      |

| 1.2.2 Applications RSDS/LVDS | 3    |

| 1.2.3 The Trend of RSDS      | 3    |

| 1.3 Thesis Organization      | 4    |

| Chapter 2                    |      |

| Background                   |      |

| 2.1 RSDS Specification       | 7    |

| 2.2 Basic Serial Link        | 9    |

| 2.3 Noise Issue              | 10   |

| 2.3.1 Cross-talk             | 11   |

| 2.3.2 Reflection             | 13   |

| 2.3.3 Power Supply Noise                      | 13 |

|-----------------------------------------------|----|

| 2.4 Signaling Circuits                        | 15 |

| 2.5 Timing Recovery Architecture              | 17 |

| 2.5.1 PLL-based Architecture                  | 17 |

| 2.5.2 Oversampling Phase-picking Architecture | 20 |

| Chapter 3                                     |    |

| Phase-Locked-Loop                             |    |

| 3.1 Introduction                              | 23 |

| 3.2 Phase-Locked Loop Architecture            | 23 |

| 3.3 Circuit Implementation                    | 24 |

| 3.3.1 Phase Frequency Detector (PFD)          | 24 |

| 3.3.2 Charge Pump                             | 28 |

| 3.3.3 Voltage Control Oscillator (VCO)        | 30 |

| 3.3.4 Loop Filter                             | 35 |

| 3.3.5 Divider                                 | 36 |

| 3.4 Fundamentals of PLL                       | 37 |

| 3.4.1 PLL Linear Model                        | 37 |

| 3.4.2 PLL Noise Analysis and Stability        | 39 |

| 3.5 Loop Parameters Consideration             | 40 |

| Chapter 4                                     |    |

| Transmitter                                   |    |

| 4.1 Architecture of Transmitter               | 45 |

| 4.2 Pseudo Random Bit Sequence (PRBS)         | 46 |

| 4.3 Multiplexer (8 to 1)                      | 47 |

| 4.3.1 The Algorithm for Parallel to Serial | 47        |

|--------------------------------------------|-----------|

| 4.3.2 MUX Architecture                     | 49        |

| 4.3.3 The 8:1MUX with pre-skew circuit     | 52        |

| 4.4 Data driver                            | 55        |

| 4.5 Simulation Result of Transmitter       | 56        |

| 4.5.1 Simulation Result of PLL             | 57        |

| 4.5.2 Architecture Comparison              | 58        |

| 4.5.3 Layout of transmitter                | 60        |

| Chapter 5                                  |           |

| Receiver                                   |           |

| 5.1 Architecture of Receiver               | 63        |

| 5.2 Slicer                                 | 63        |

| 5.3 Clock and Data Recovery                | 66        |

| 5.3.1 Introduction                         | 66        |

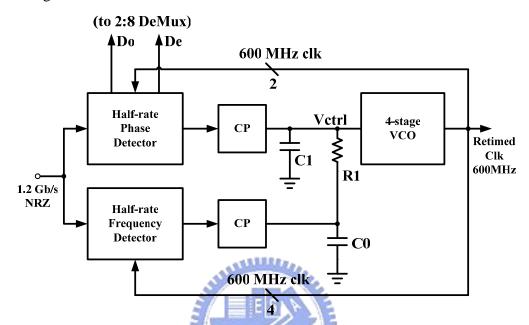

| 5.3.2 Architecture of CDR                  | 66        |

| 5.3.3 Half-rate Phase Detector             | 67        |

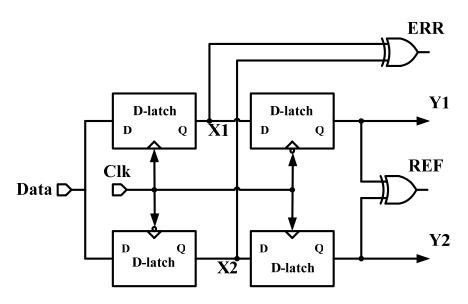

| 5.3.4 Half-rate Frequency Detector         | 70        |

| 5.4 Linearization Circuit                  | 73        |

| 5.5 Parameters of CDR                      | 75        |

| 5.6 De-Multiplexer                         | 76        |

| 5.7 Receiver Simulation Result             | <b>79</b> |

| Chapter 6                                  |           |

| Conclusion and Future work                 |           |

| 6.1 Conclusion                             | 83        |

| 6.2 Future Work | 84 |

|-----------------|----|

|                 |    |

| Reference       | 85 |

# LIST OF TABLES

| Table 1-1 RSDS/LVDS comparison [1]                                   | 2  |

|----------------------------------------------------------------------|----|

| Table 1-2 RSDS/LVDS applications                                     | 3  |

| Table 2-1 Electrical specification of RSDS transmitters and receiver | 8  |

| Table 2-2 Comparison between full-rate and half-rate timing recovery |    |

| architectures                                                        | 19 |

| Table 3-1 Noise transfer function                                    | 39 |

| Table 3-2 Parameter of the transmitter PLL                           | 43 |

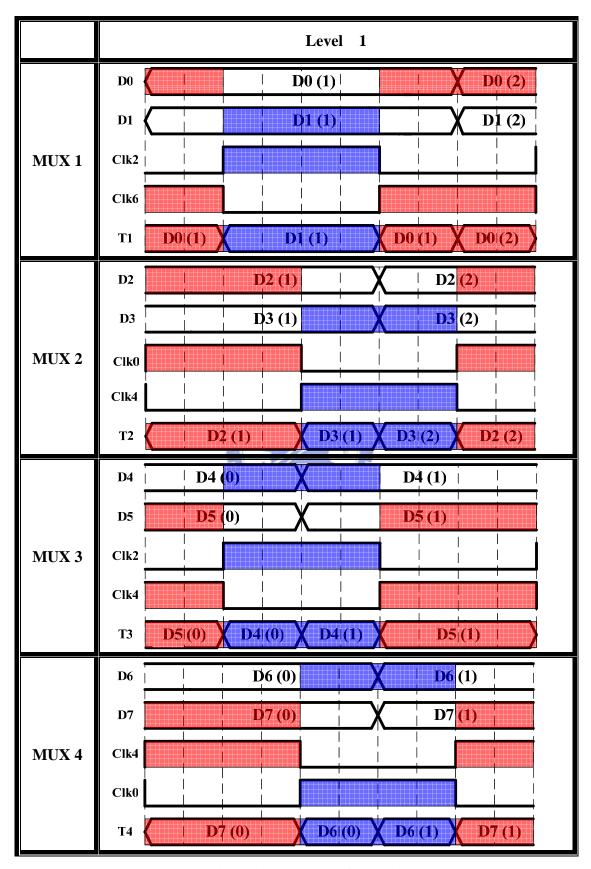

| Table 4-1 the deductive logic of 3-levels multiplexer                | 48 |

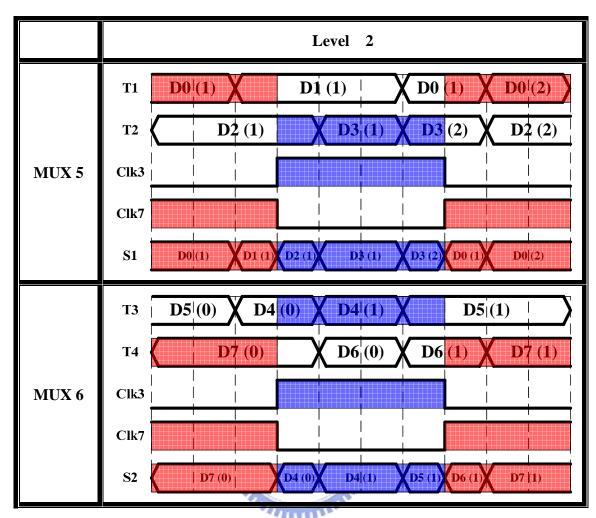

| Table 4-2 Algorithm Result of the First Level                        | 53 |

| Table 4-3 Algorithm Result of the Second Level                       | 54 |

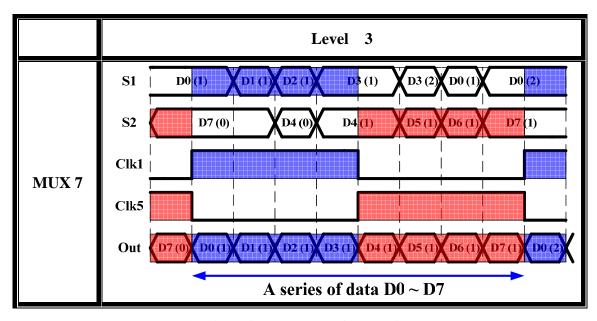

| Table 4-3 Algorithm Result of the Third Level                        | 54 |

| Table 5-1 Parameters of CDR                                          | 75 |

# LIST OF FIGURES

| Figure 1-1 Block diagram of the LCD nodule [2]                                  | . 4 |

|---------------------------------------------------------------------------------|-----|

| Figure 2-1 RSDS swing level                                                     | . 8 |

| Figure 2-2 Block diagram of the basic serial link                               | . 9 |

| Figure 2-3 Cross-talk                                                           | 12  |

| Figure 2-4 Transmitter timing diagram with different transmitter architectures: |     |

| (a) voltage-mode, (b) current mode, and (c) differential                        | 16  |

| Figure 2-5 Timing recovery architecture                                         |     |

| (a) PLL-based (b) oversampling phase-picking                                    | 17  |

| Figure 2-6 (a) Full-rate data and clock (b) Half-rate data and clock            | 19  |

| Figure 3-1 Block diagram of a phase locked loop                                 | 24  |

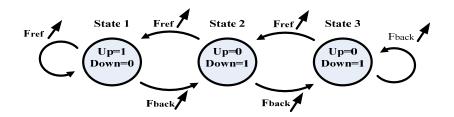

| Figure 3-2 tri-state diagram of the phase detector                              | 25  |

| Figure 3-3 reference signal comes after feed back signal                        | 25  |

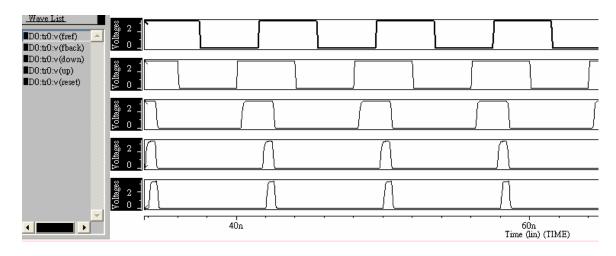

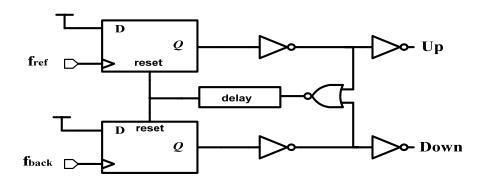

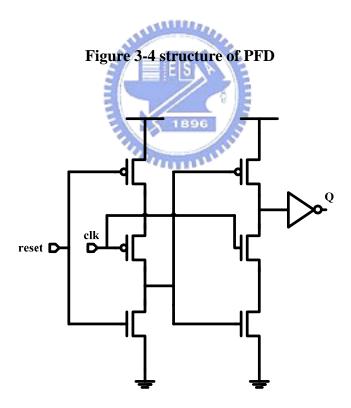

| Figure 3-4 structure of PFD                                                     | 26  |

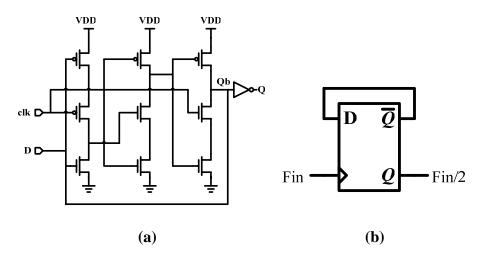

| Figure 3-5 Dynamic D Flip-Flop TSPC                                             | 26  |

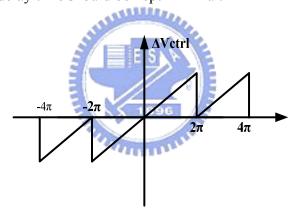

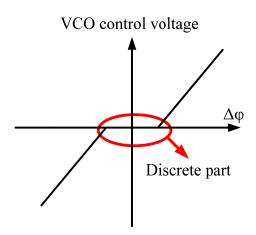

| Figure 3-6 PFD transfer characteristic curve                                    | 27  |

| Figure 3-7 PFD transfer character curve with dead zone                          | 27  |

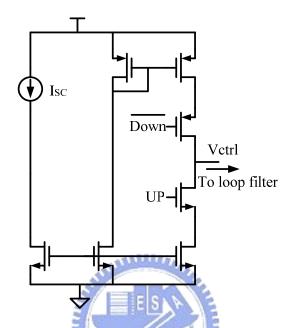

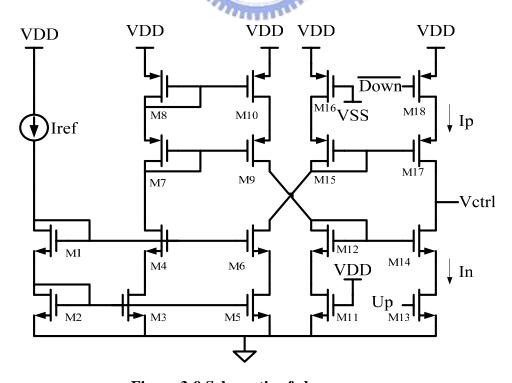

| Figure 3-8 Charge pump with charge injection effect                             | 29  |

| Figure 3-9 Schematic of charge pump                                             | 29  |

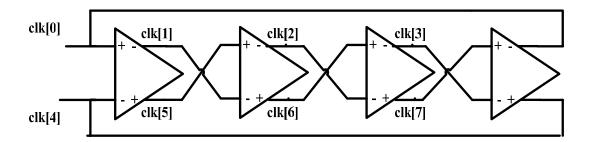

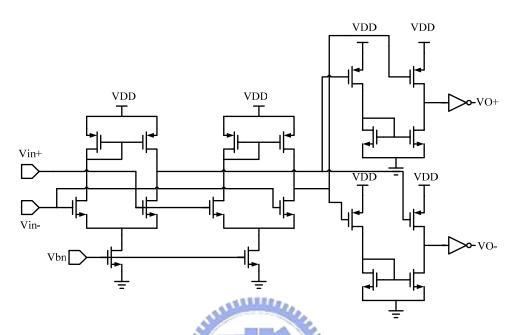

| Figure 3-10 Schematic of the four stages VCO                                    | 30  |

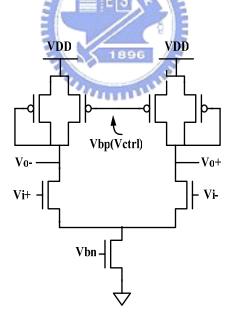

| Figure 3-11 Schematic of VCO delay cell with symmetric load elements            | 30  |

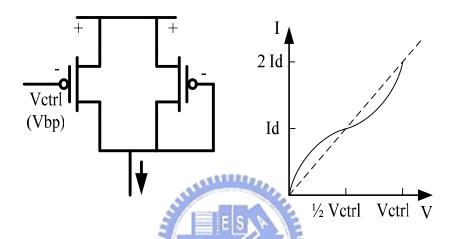

| Figure 3-12 The symmetric load I-V curve                                        | 31  |

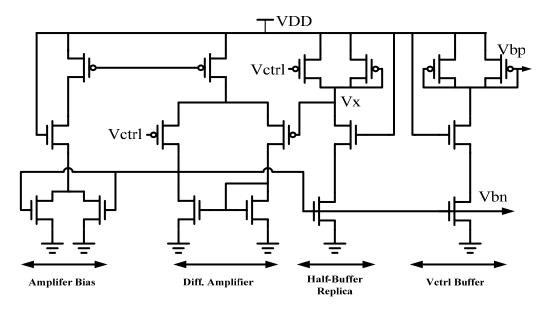

| Figure 3-12 Replica-feedback current source bias circuit                        | 33  |

| Figure 3-13 Schematic of differential-to-single-ended converter                 | 34  |

| Figure 3-14 Schematic of duty-cycle corrector and its timing diagram        | 35 |

|-----------------------------------------------------------------------------|----|

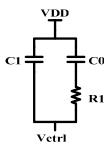

| Figure 3-15 2 <sup>nd</sup> order passive loop filter                       | 36 |

| Figure 3-16 (a) TSPC asynchronous divided-by-two circuit (b) divider scheme | 36 |

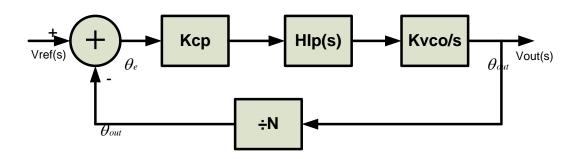

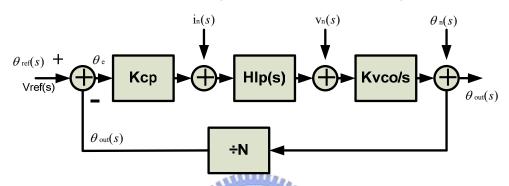

| Figure 3-17 PLL linear model                                                | 37 |

| Figure 3-18 PLL linear model with various equivalent noise sources          | 39 |

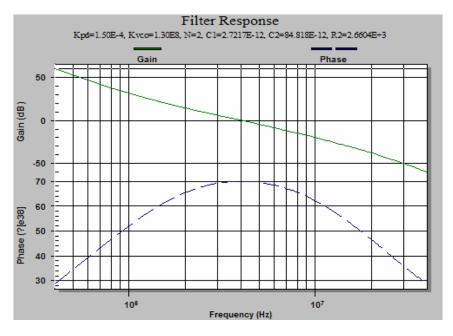

| Figure 3-19 open loop PLL frequency response                                | 41 |

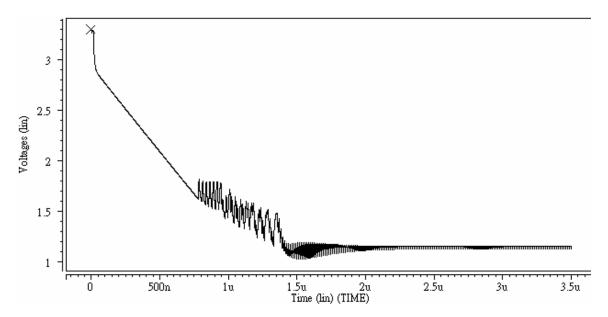

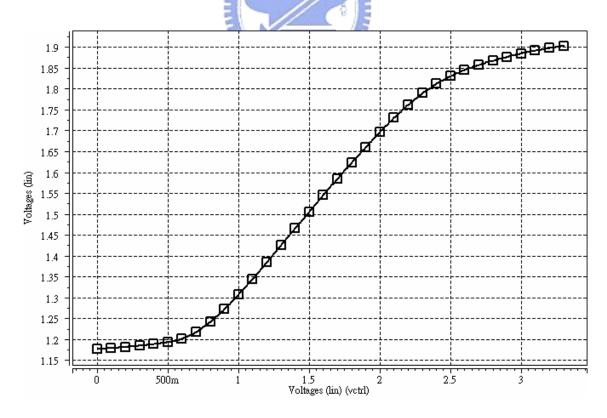

| Figure 3-20 Vctrl timing diagram                                            | 42 |

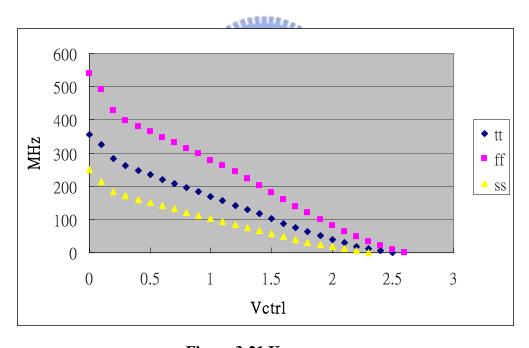

| Figure 3-21 Kvco curve                                                      | 42 |

| Figure 4-1 Block diagram of the transmitter                                 | 45 |

| Figure 4-2 PRBS delay cell circuit                                          | 46 |

| Figure 4-3 Scheme of Pseudo Random Bit Sequence (PRBS)                      | 47 |

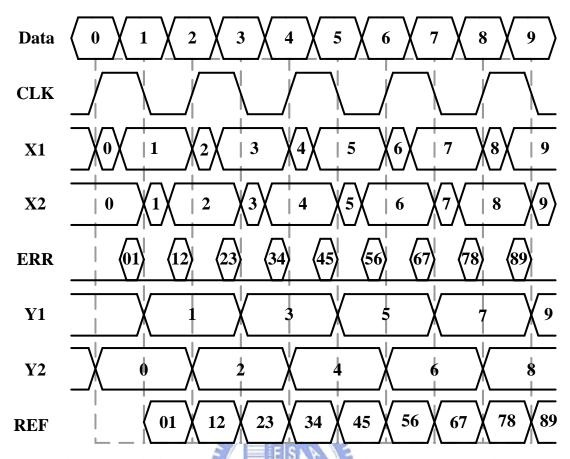

| Figure 4-4 Timing diagram of 8:1 multiplexer                                | 47 |

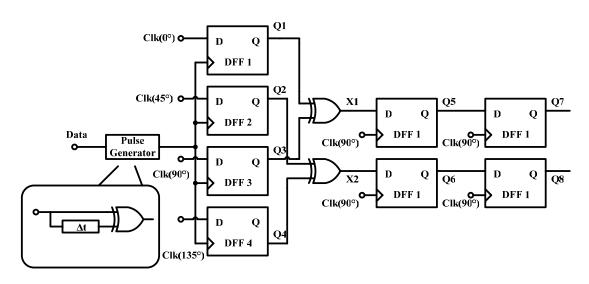

| Figure 4-5 Multi-phase Type MUX                                             | 49 |

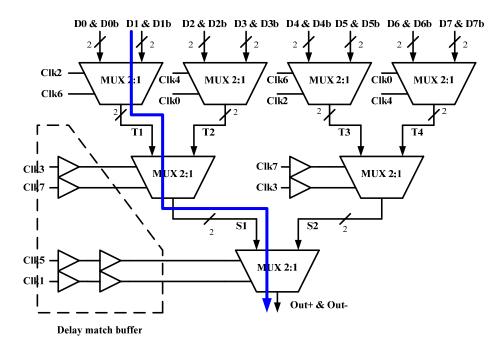

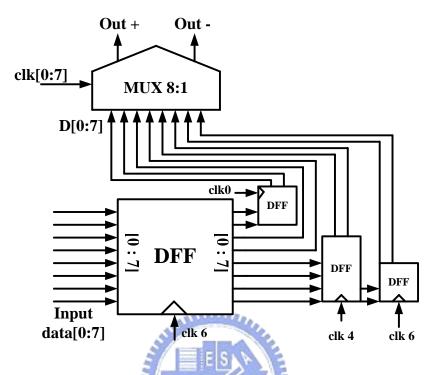

| Figure 4-6 Architecture of the 3-levels multiplexer                         | 49 |

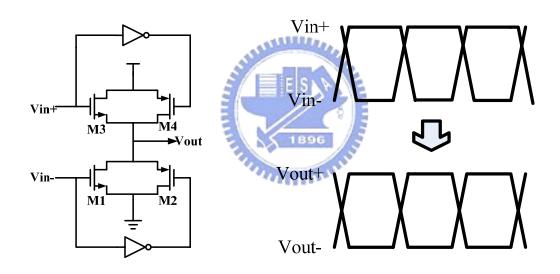

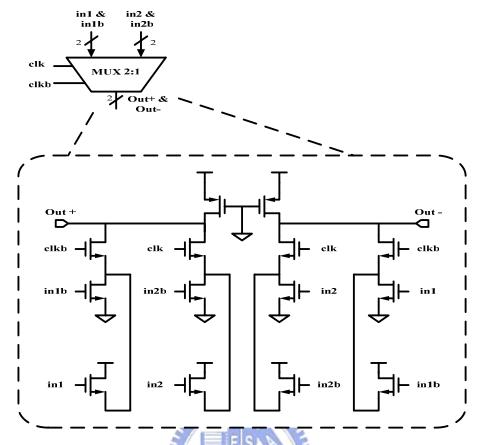

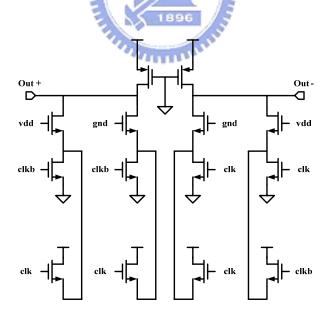

| Figure 4-7 Scheme of 2:1MUX Cell                                            | 51 |

| Figure 4-8 Delay Match Buffer                                               | 51 |

| Figure 4-9 Pre-skew Circuit                                                 | 52 |

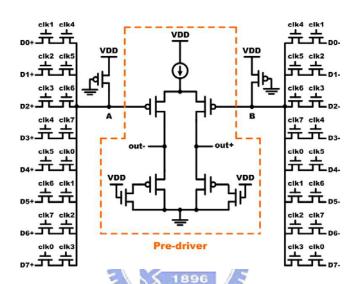

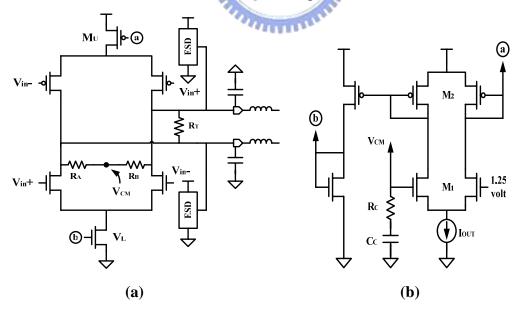

| Figure 4-10 (a) RSDS transmitter data driver (b) Common mode feedback       |    |

| circuit                                                                     | 55 |

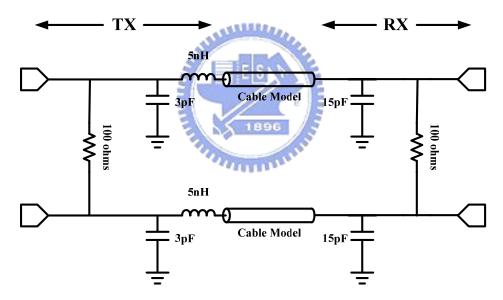

| Figure 4-11 Simulation Environment                                          | 56 |

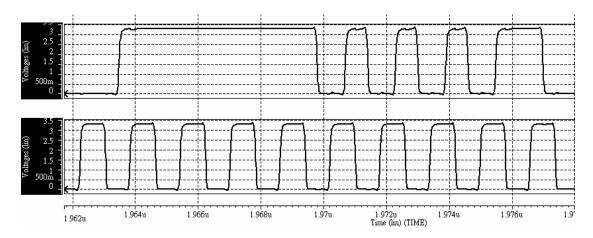

| Figure 4-12 Eight-phase VCO clock                                           | 57 |

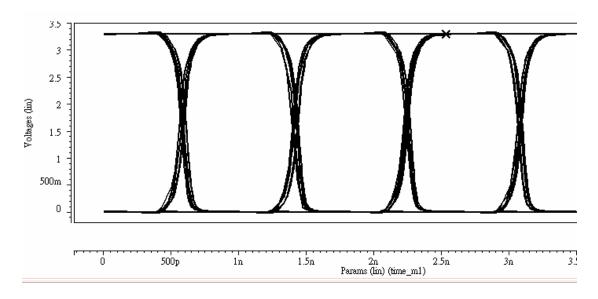

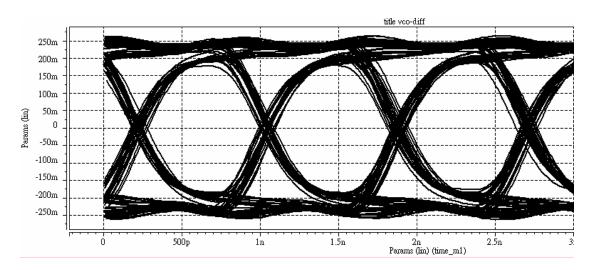

| Figure 4-13 eye-diagram of VCO clock                                        | 57 |

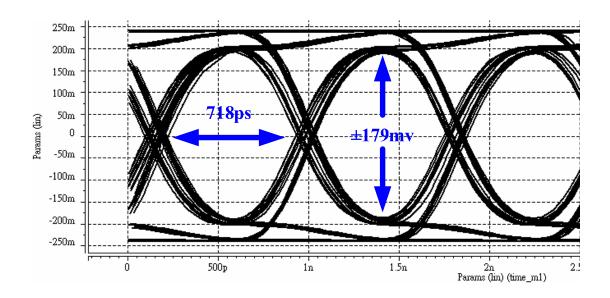

| Figure 4-14 eye-diagram of output (Multi-phase Type MUX)                    | 58 |

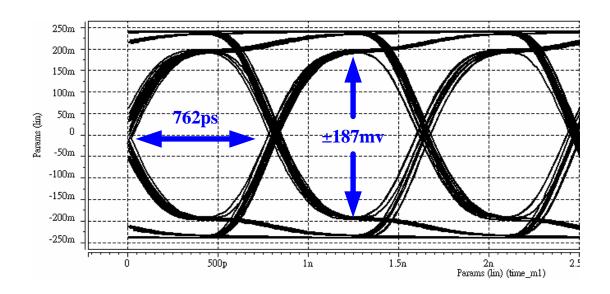

| Figure 4-15 eye-diagram of output (3-levels MUX without pre-skew)           | 59 |

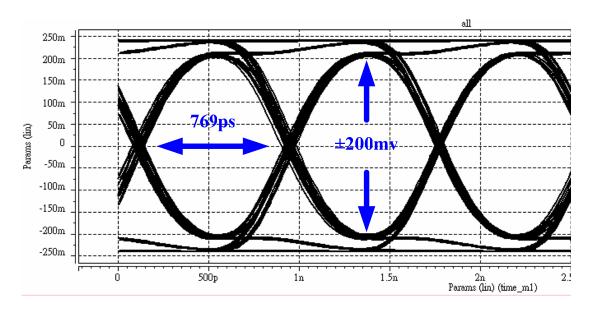

| Figure 4-16 eye-diagram of output (3-levels MUX with pre-skew)              | 60 |

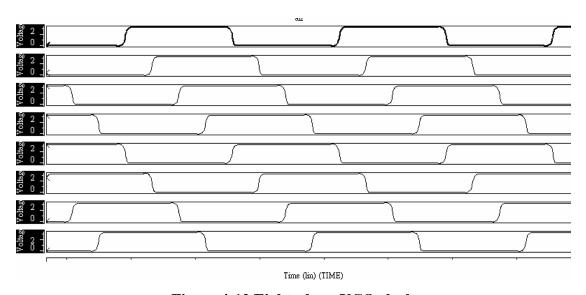

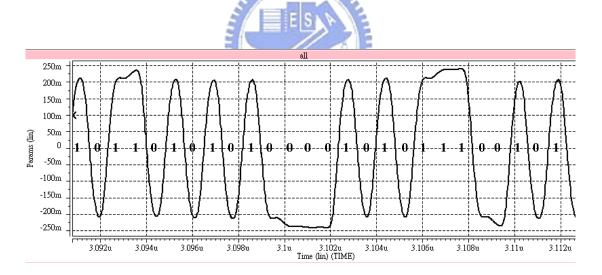

| Figure 4-17 output waveform of TX                                           | 60 |

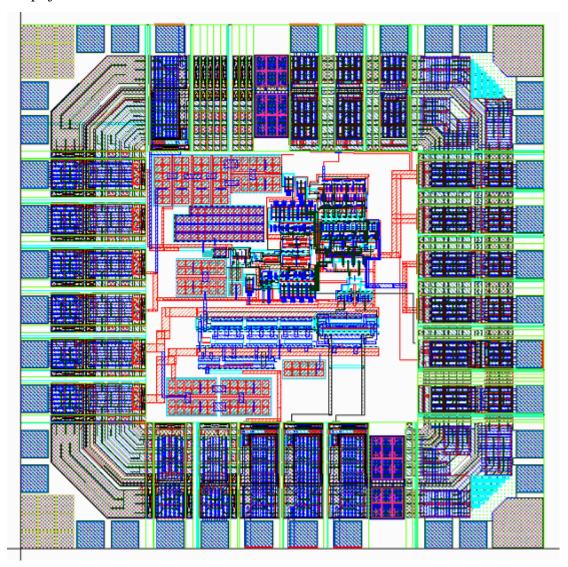

| Figure 4-18 Layout of transmitter                                              | 61         |

|--------------------------------------------------------------------------------|------------|

| Figure 4-19 post simulation of transmitter                                     | 61         |

| Figure 5-1 Block diagram of the receiver                                       | 63         |

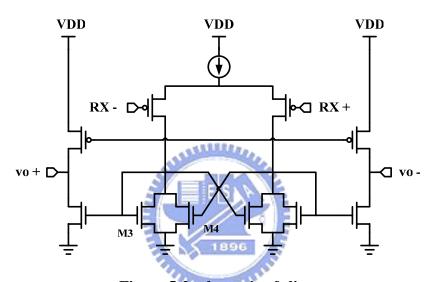

| Figure 5-2 schematic of slicer                                                 | 64         |

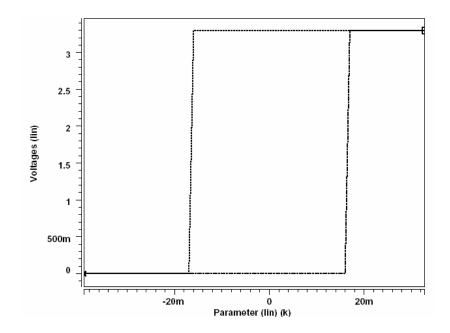

| Figure 5-3 Simulation of Hysteresis comparator                                 | 65         |

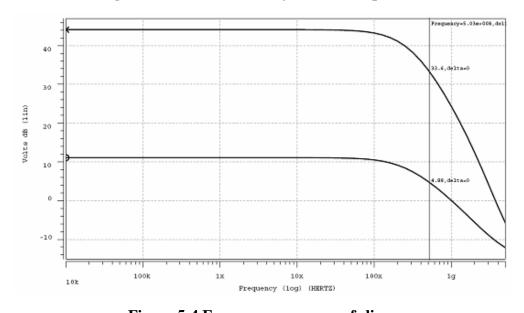

| Figure 5-4 Frequency response of slicer                                        | 65         |

| Figure 5-5 Half-rate CDR architecture                                          | 67         |

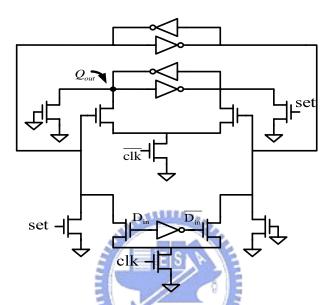

| Figure 5-6 Half-rate phase detector                                            | 67         |

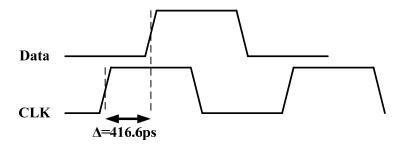

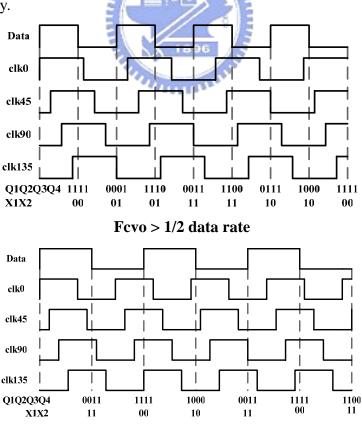

| Figure 5-7 Timing scheme of the half-rate phase detector operation             | 69         |

| Figure 5-8 perfect locked condition                                            | 70         |

| Figure 5-9 Transfer characteristic of phase detector                           | <b>7</b> 0 |

| Figure 5-10 Half-rate frequency detector                                       | <b>7</b> 0 |

| Figure 5-11 timing diagram of FD                                               | 71         |

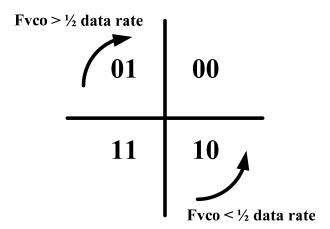

| Figure 5-12 Circular phase diagram                                             | 72         |

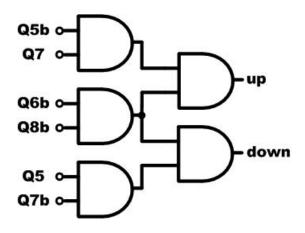

| Figure 5-13 Up and down generator                                              | 72         |

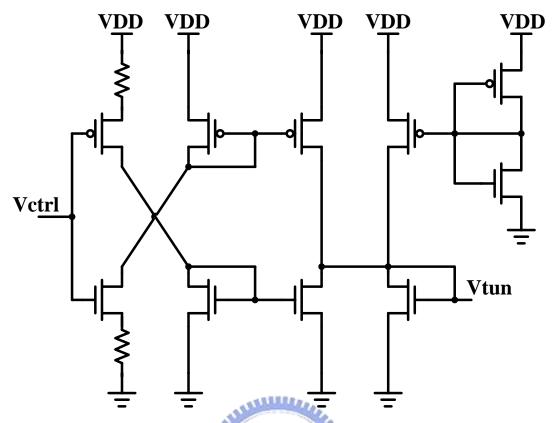

| Figure 5-14 Schematic of the linearization circuit                             | 74         |

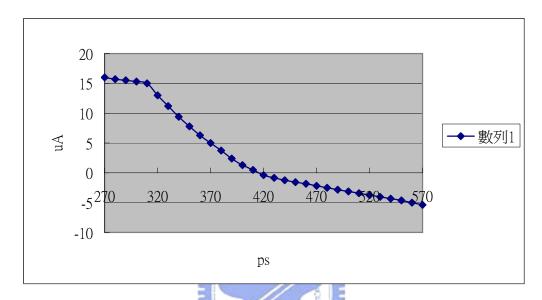

| Figure 5-15 Transfer curve of the linear circuit                               | 74         |

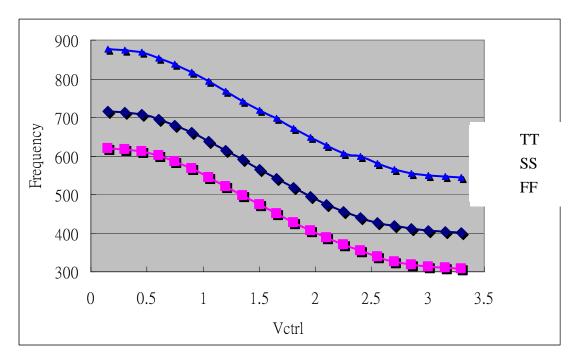

| Figure 5-16 Transfer curve of VCO (Kvco=160MHZ/V - TT)                         | 75         |

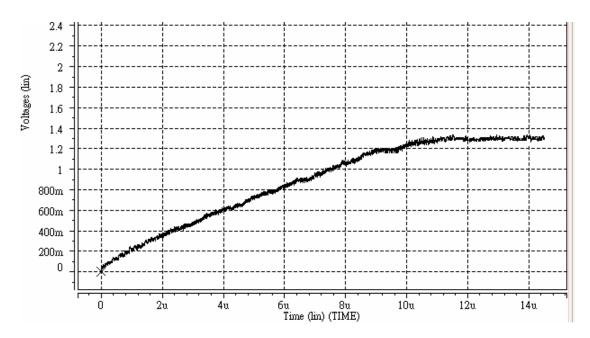

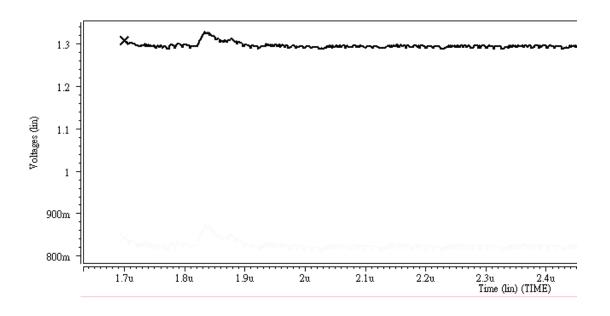

| Figure 5-17 Control voltage of VCO                                             | <b>7</b> 6 |

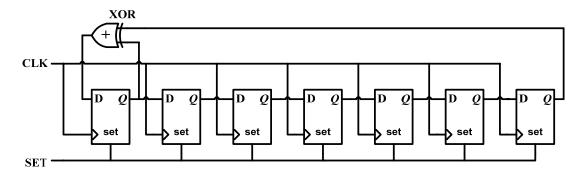

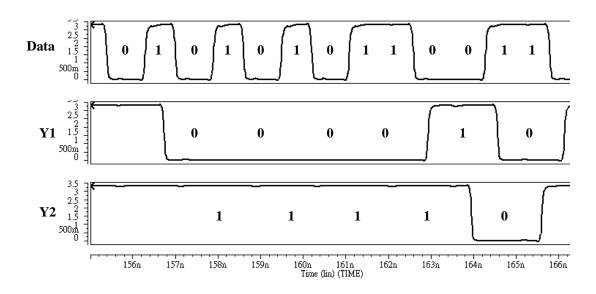

| Figure 5-18 Asynchronous tree-type 2:8 de-multiplexer                          | 77         |

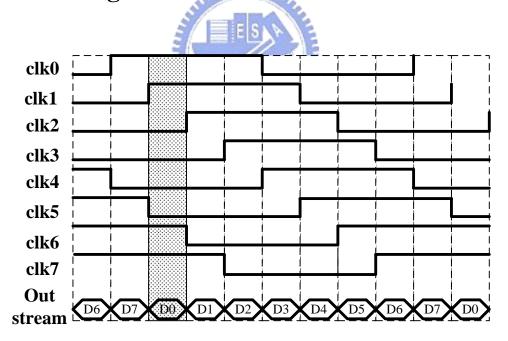

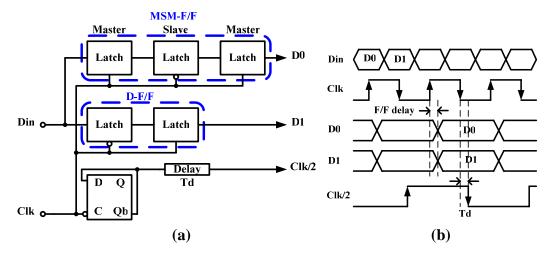

| Figure 5-19 (a) 1:2 DEMUX (b) timing diagram                                   | 77         |

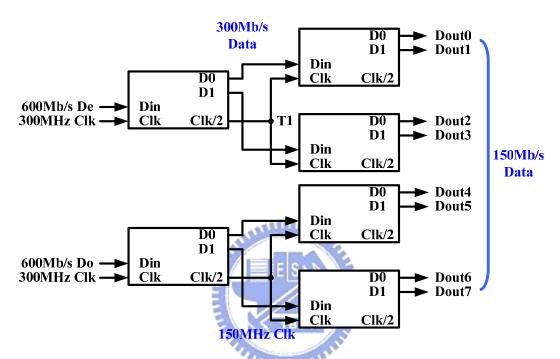

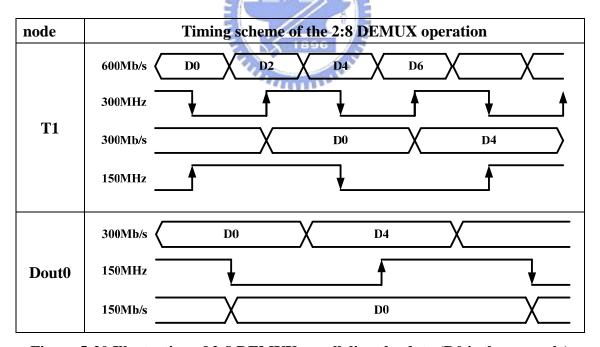

| Figure 5-20 Illustration of 2:8 DEMUX paralleling the data (D0 is the example) | <b>78</b>  |

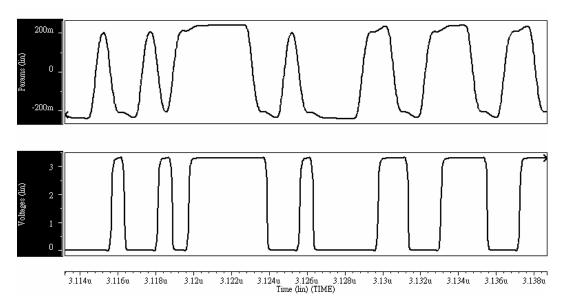

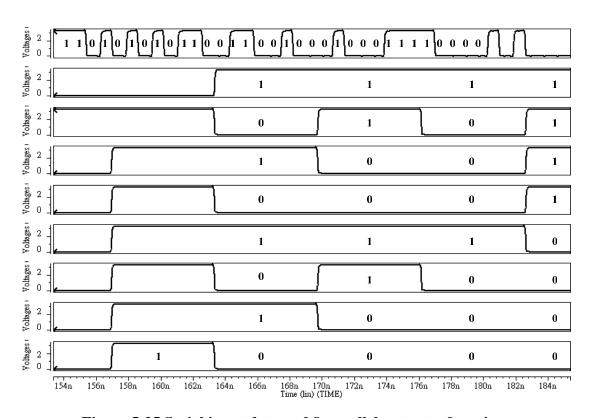

| Figure 5-21 Waveforms of received data and output of the slicer                | 80         |

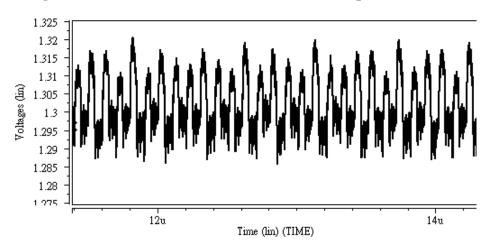

| Figure 5-22 Control voltage of VCO when CDR is in lock state                   | 80         |

| Figure 5-23 Input data and retimed clock while CDR in the lock state           | 80         |

| Figure 5-24 Retimed even and odd data and Retimed clock                        | 81         |

| Figure 5-25 Serial input data and 8-parallel outputs of receiver             | 81 |

|------------------------------------------------------------------------------|----|

| Figure 5-26 The variation of control voltage when the phase of input data is |    |

| changed by 90°                                                               | 82 |

# **Chapter 1**

# Introduction

#### 1.1 Motivation

Recently, the advances of IC fabrication technology have led to an great growth of the integration levels of digital IC's. For perfect performance, all high-speed components of a system should be integrated into a signal die. However, some technological obstacles forbid the implementation of System-On-a-Chip (SOC). Therefore, high speed links will be the key of the connection between different modules and chips. While improving the I/O speed, we also need to keep the circuit are a small and power consumption low so that we can make sure that integrating transmitter, receiver, and protocol control into a single chip will have the good performance[1].

The basic data link consists of the components such as transmitter, receiver, and channel. The transmitter translates the incoming digital data to analog level and converts the data into a serial data stream on the channel to receiver. A high-level and a low-level are the logical value in the analog system as 0 and 1 are the logical value to the digital system. In order to detect the logic level of analog waveform from the channel, the analog waveform needs to be amplified in the front of receiver. The timing recovery circuit is additional part in receiver to resolve the input into the needed clock. Finally, the receiver converts the serial data to the parallel data.

In this thesis, the achievement is to design a CMOS serial link transceiver based on the RSDS interface and meet the specification for delay, cost, data mapping, power consumption and logic threshold variation. RSDS means Reduced Swing Differential Signaling. It's a way to transmit data with very low differential swing (200mv) over two printed circuit board (PCB) traces or a balance cable. The following section will show RSDS in more detail.

#### 1.2 Introduction of RSDS

#### **1.2.1 RSDS/LVDS**

Reduced Swing Differential Signaling, like it's predecessor LVDS (Low Voltage Differential Signal), originated from the LCD Manufacture's unique need for on glass interface with high speed, reduced interconnection, lower power, and a lower EMI.

The following figure indicates the difference between RSDS/LVDS

| Characteristic            | RSDS         | LVDS          |  |  |  |

|---------------------------|--------------|---------------|--|--|--|

| Vod, output voltage swing | +/- 200mV    | +/- 350mV     |  |  |  |

| Rterm, Termination        | 100 Ω        | 100Ω          |  |  |  |

| Iod, output drive current | 2mA          | 3.5mA         |  |  |  |

| Data MUX                  | 2:1          | 7:1           |  |  |  |

| Content                   | RGB Data     | RGB Data and  |  |  |  |

|                           |              | control       |  |  |  |

| Application               | Intra-system | System-system |  |  |  |

|                           | interface    | interface     |  |  |  |

Table 1-1 RSDS/LVDS comparison [2]

# 1.2.2 Applications RSDS/LVDS

Because of the benefits of the RSDS and LVDS low signal swing, the RSDS and LVDS are widely used standards of flat panel interfaces. The chart below shows some applications based on RSDS/LVDS interface.

| PC/Computing               | Telecom/Datacom       | Consumer                |  |  |

|----------------------------|-----------------------|-------------------------|--|--|

| Flat panel displays        | Switches              | Home/office             |  |  |

| Monitor link               | Add/drop multiplexers | Set op boxes            |  |  |

| Printer engine link        | Box-to-Box            |                         |  |  |

| System clustering          | Routers               | Game displays/controls  |  |  |

| SCI processor interconnect | Hubs                  | In-flight entertainment |  |  |

Table 1-2 RSDS/LVDS applications

## 1.2.3 The Trend of RSDS

The tendency of the TFT industry toward higher resolution displays requires a new low noise digital interface. The open RSDS technology offers us an industry leading technology platform. Combining the TFT display-related technology with a low power consumption, low noise interface like RSDS will accelerate developing new TFT driver families to achieve next-generation, high-performance TFT LCD modules.

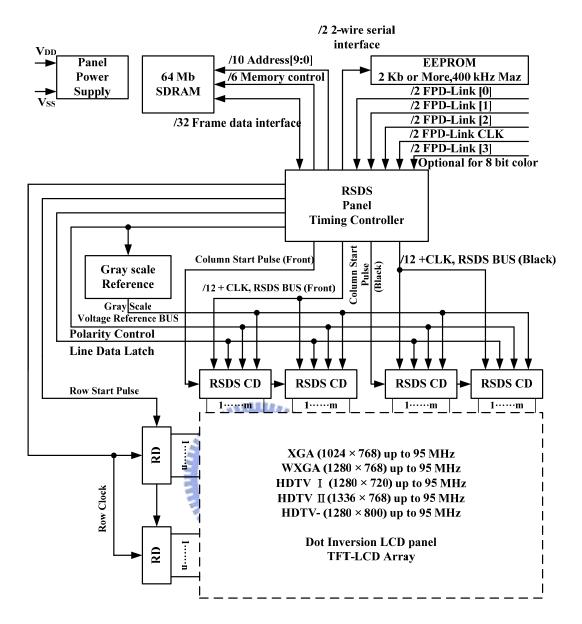

**Fig 1-1** illustrates a typical application block diagram of the LCD module. The RSDS bus is located between the Panel timing Controller (TCON) and the Colum Drivers. This bus is typical nine pair wide plus clock and is a multidrop bus configuration.

Figure 1-1 Block diagram of the LCD nodule [3]

## 1.2.4 The Benefits of RSDS

With RSDS technology, designers are able to reduce the size of circuit boards and the bus interconnect, and eliminate discrete components typically used in TFT LCD modules. The XGA (eXtended Graphics Adapter) panel timing controller combined with a partner's RSDS-enabled XGA column driver form a powerful solution to reduce size, weight and cost.

The use of RSDS Technology also enables several other key features and benefits in these new display designs. Substantial power savings, critical in battery-operated and mobile applications can be realized without sacrificing performance and resolution. Significantly reduced EMI-radiated (electro-magnetic interference) noise can be achieved, lowering production costs by eliminating EMI shielding.[3]

## 1.3 Thesis Organization

This thesis is organized into six chapters and the first one is the introduction of the RSDS interface. Chapter 2 introduces more specification and background of RSDS interface transmission and shows the basic design of serial link. In Chapter3, the conception and architecture of Phase-Locked Loop (PLL) will be described. Chapter 4 shows the discussion of the transmitter architecture. High speed parallel to serial data conversion is achieved by means of time-division multiplexer toggled by a low jitter and 8-phases phase-locked loop. The transmitter simulation result is shown in the end. Chapter5 presents the building block of receiver. The clock and data recovery circuit will be introduced and the architecture with improved jitter performance is proposed. The frequency acquisition part design is also introduced. The whole simulation performance (including transmitter, cable and receiver) will be shown in the end of this Chapter. Chapter 6 is the conclusion of this thesis and shows the future work.

# Chapter 2

# **Background**

Chapter 2 describes the detail of RSDS specification, some terminologies and conceptions for transmission environment, some basic design architectures and some opinions for performance enhancement.

## 2.1 RSDS Specification [5]

Reduced Swing Differential Signaling (RSDS) is a signaling standard that defines the output characteristics of a transmitter and inputs of a receiver along with the protocol for a chip-to-chip interface between Flat Panel timing Controllers and Column Drivers. RSDS which is a differential interface with a nominal signal swing tend to be used in display applications. It retains the many benefits of the LVDS interface commonly used between host and the panel for high bandwidth, robust digital interface. The RSDS provides many benefits to the applications which include:

- Reduced bus width enables smaller thinner column driver boards

- Low power dissipation extends system run time

- Low EMI generation eliminates EMI suppression components and shielding

- High noise rejection maintains signal image

- High throughput enables high resolution displays

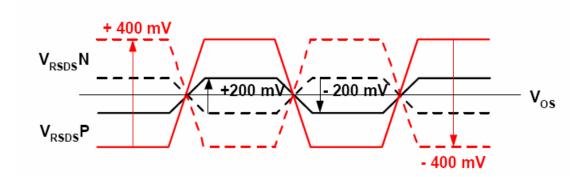

The **Fig 2-1** below show the RSDS transmitter output swing level in single end and differential end. The RSDS has the waveform with low signal swing of 200mV. And the **Table 2-1** below presents the electrical specification for a transmitter (TX) and receiver (RX).

Figure 2-1 RSDS swing level

athlife.

|       |                   | 4 6 7 1 1      | The state of the s |     |     |        |         |

|-------|-------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------|---------|

| Tx/Rx | Parameter         | Definition     | Condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | MIN | TYP | MAX    | Units   |

| Tx    | $V_{\mathrm{OD}}$ | Differential   | $RL=100\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100 | 200 | 600    | lmvl    |

|       |                   | output voltage | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |     |        |         |

| Tx    | Vos               | Offset voltage | 1896                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0.5 | 1.2 | 1.5    | V       |

| Tx    | Irsds             | RSDS driver    | Trib.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1   | 2   | 6      | ma      |

|       |                   | current        | THE STATE OF THE S |     |     |        |         |

| Tx    | Tr/Tf             | Transition     | 20%to80%,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | 500 |        | ps      |

|       |                   |                | Vod=200m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |     |        |         |

|       |                   |                | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |     |        |         |

|       |                   |                | CL=5pf                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |     |        |         |

| Tx    |                   | RSDS clock     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 45  | 50  | 55     | %       |

|       |                   | duty cycle     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |        |         |

| Rx    | V <sub>TH</sub>   | Differential   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     | +/-100 | mV      |

|       |                   | threshold      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |        |         |

| Rx    | Vcm               | Input common   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0.3 |     | 1.5    | V       |

|       |                   | mode voltage   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |        |         |

| Rx    | IL                | RSDS Rx input  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -10 |     | 10     | $\mu$ A |

|       |                   | leakage        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |     |        |         |

Table 2-1 Electrical specification of RSDS transmitters and receiver

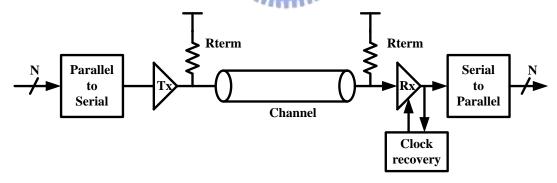

#### 2.2 Basic Serial Link

As shown in the below **Fig 2-2**, the common components of the basic serial link are transmitter, channel and receiver. In order to increase the bandwidth of the link, the data are usually parallel before being sent by the transmitter. The transmitter converts the digital information to analog level on the transmission medium. The driver makes the analog signal be differential. The medium on which the signal travels, e.g. coaxial cable or twisted pair, are commonly called the communication channel. The receiver in the end of channel recovers the incoming signal to the original digital information by amplifying and sampling the signal. The termination resistor which matches the impedance of the channel could minimize the signal reflection. The circuit at receiver, the clock and data recovery adjusts the receiver clock based on the received data to let the sampling point fix the center of the data eye. Finally, the serial to parallel interface converts the serial data back to N parallel bits data.

Figure 2-2 Block diagram of the basic serial link

The performance of a link is mainly characterized by the data bandwidth. The another important parameter of link performance is the bit error rate (BER), a measure of how many bit errors are made per second. A link's maximum data rate is specified at the specific BER to guarantee the robustness of the overall system. BER

is important not only because it reduces the effectiveness of a system's bandwidth, but also because in many systems, applications of error correction techniques can prohibitively increase the system cost. The errors are caused by the noise from each part of the system. The intrinsic sources of noise are the random fluctuation due to the thermal vibration and shot noise of the positive and active system components. In VLSI applications, other non-fundamental sources of noise also limit the performance of link. The noise sources include coupling effect from other channel, the mutual inductance, switching activity from other circuits integrated with the link circuit, and the reflections induced from the link imperfections. These types of noise typically have non-white frequency spectrum, and exhibit with the strong data correction. Moreover, the overall power is often proportional to the power of the signals. Therefore, there are two main issues in designing high-speed serial link interface circuit: signaling and clock.[6]

#### 2.3 Noise Issue

When selecting a particular signaling or a clocking scheme, the primary goal is to transmit data between system components with the maximum bandwidth, while keeping the low associated cost low. These costs include the power consumption and the area occupied by the signaling and synchronization circuits, as well as the cost of the required external component. Unfortunately, the noises in the digital system make it difficult to achieve the objective. The noises influence the amplitude and timing of transmitted signal, thus the impact impels the correct reception. These noises are either relative to, or independent of the original transmitted signal amplitude. The problem of independent noise can be easily overcome by reinforce the amplitude of

the transmitted signals. But it is more arduous to solve the problem of the proportional noise source. This type noise only can be minimized or erased by designing the signaling circuit and transmitting environment carefully. The most critical proportional noise sources are cross-talk, reflection and self-induced power supply noise. In this section, these types of noise sources and the methods commonly used to deal with them will be discussed.

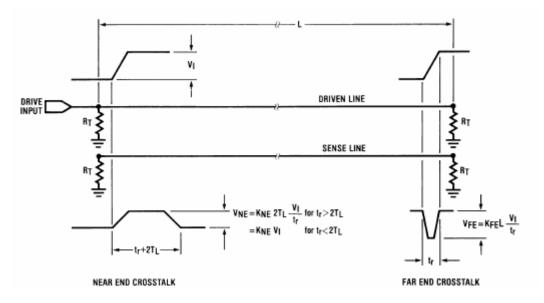

#### 2.3.1 Cross-talk [7]

The problem of cross-talk and how to deal with it is becoming more important as system performance and board densities increase. Our discussion on cable-to-cable coupling described cross-talk as appearing due to the distributed capacitive coupling and the distributed inductive coupling between two signal lines. When the cross-talk is measured on an undriven senses line to a driven line (both terminated at their characteristic impedance), the near end cross-talk and far end cross-talk have quite distinct features, as shown in the **Fig 2-3**. It should be noted that the near end component reduces to zero at the far end and vice versa. At any point in between, the cross-talk is a fractional sum of the near and far end cross-talk waveforms as shown in the figure. It also can be noted that the far end cross-talk can have either polarity whereas the near end cross-talk always has the same polarity as the signal causing it.

The amplitude of the noise generated on the undriven senses line is directly related to the edge rates of the signal on the driven line. The amplitude is also directly related to proximity of the two lines. This is factored into the coupling constants KNE and KFE by terms that include the distributed capacitance per unit length, and the length of the line. The lead to lead capacitance and mutual inductance thus created

causes "noise" voltages to appear when adjacent signal paths switch.

Figure 2-3 Cross-talk

Several useful observations that apply to a general case can be made:

- The cross-talk always scales with the signal amplitude VI.

- Absolute cross-talk amplitude is proportional to skew rate V<sub>I</sub> / t<sub>r</sub>, not just 1/ t<sub>r</sub>.

- Far end cross-talk width is always tr.

- For tr < 2TL, when tr is the transition time of the signal on the driven line and

TL is the propagation or bus delay down the line, the near end cross-talk

amplitude VNE expressed as a fraction of signal VI is KNE which is a function

of physical layout only.</li>

- The higher the value of "tr" (slower transition times) the lower percentage of cross-talk (relative to signal amplitude).

From these above points, the goal of serial link, high-speed transmission, makes the effect of cross-talk worse and more significant. The methods to reduce the amplitude of the cross-talk include: diminishing the amplitude of transmission data, arranging the layout carefully to reduce the coefficient K<sub>NE</sub> (the value of mutual capacitance and

mutual inductance), lessening the times of the signal transition by coding the data and techniques like slew-rate control of driver output signals.

#### 2.3.2 Reflection

Reflection-induced inter-symbol interference is the most common type of proportional noise on the serial link. Like the Fig 2-2, signal lines must be terminated. This can be accomplished by setting termination circuits on either the transmitter or the receiver end of line. The use of the termination circuit is to absorb the transmitted signal energy, and avoid it reflected back into transmission medium.

The reflection of signal is given by [8]

$$V_{reflected} = \rho V_{incident}$$

(2-1)

$$V_{reflected} = \rho V_{incident}$$

$$\rho_L = \frac{Z_L - Z_0}{Z_L + Z_0}$$

$$\rho_S = \frac{Z_S - Z_0}{Z_S + Z_0}$$

(2-2)

Where:  $\rho_L$ =load reflection coefficient,  $\rho_S$ =source reflection coefficient,  $Z_L$ =load resistance, Zs=source driving-point resistance, Zo=transmission line impedance

Terminating both at source and destination ends of the transmission medium can be used to alleviate this problem at the expense of increased power dissipation. Automatic impedance control can also be used to reduce reflection noise by dynamically adjusting the termination resistor to match the interconnection characteristic impedance [9].

## 2.3.3 Power Supply Noise

Self-induced power supply noise is a result of the finite supply pin impedances in the semiconductor package. Power supply noise is perhaps the most important contributor to system noise. When any element switches logic state, the current drawn from the external supply of the chip changes at a rate equal to dI/dt. The inductance L of the supply voltage bonding wire will then cause the on-chip power supply voltage drop by a voltage  $\Delta V = L \frac{di}{dx}$ . If the drop becomes too large; it can cause the internal logic error. Even a supply spike on one circuit's output could feed an extraneous noise voltage into the next device's input. It is a problem in almost every digital system. However, power supply noise is generally not a dominant voltage noise in the differential links. Sending complementary signals allow the total current draw from (and discharged to) each power supply to be constant, eliminating large current spikes across the power pin inductors or power distribution inductance. Moreover, since the differential pairs are nicely balanced, to the first order, any power supply noise coupled to the signal pair at both the transmitter and the receiver are common-mode.

Although power supply noise affects different systems by different degree, its presence in digital systems has stimulated enormous research efforts in techniques to reduce the dI/dt noise. Such techniques include minimizing the inductance of power distribution networks, employing constant-current drivers or more generally keeping the total current drawn from each supply constant, increasing the bypass capacitance both on the chip and on the board, using separate power supplies for noise-sensitive circuit, generating on-chip supplies using voltage regulators, slowing down signal transition using slew rate control [10], and using coding schemes that reduce switching frequency of signals [11].

## 2.4 Signaling Circuits

The noise sources mentioned in Section 2.2 all are proportional to transmitted signal amplitude and hence cannot be overcome by simply increasing the signal swing. Therefore, these noise sources are the primary types of noise that the transmitter and receiver must deal with.

The transmitter drives a HIGH or LOW analog voltage onto the channel and is designed for a particular output-voltage swing based on the system specification. The design issues are to maintain small voltage noise and timing noise on the signal. There are two types of output drivers to drive the output: voltage-mode drivers and current-mode drivers. Voltage-mode drivers, as shown in Fig 2-4 (a), are switches that switch the line voltage. Because the switches are implemented with transistors, the driver appears as a switched resistance. To switch the voltage fully, a small resistance is needed which typically requires a large switching device. In contrast, current-mode drivers, as illustrated in Fig 2-4 (b), are switching current sources. The output impedance of the driver is much higher than the line impedance. It is also called high impedance signaling. Therefore, the transmitter bandwidth is typically not an issue even with significant output capacitance. The voltage to be transmitted on the line is determined by the switched current and the line impedance or an explicit load resistor. The driver can be simply implemented by biasing the MOS transistor in its saturation region. Current-mode drivers are slightly better in terms of insensitivity to supply-power noise because they have high output impedance and hence the signal is tightly coupled only to V<sub>OH</sub>, the signal return path. The output current does not vary with ground noise as long as the current source bias signal is tightly coupled to the

ground signal. The disadvantage with current-mode drivers is that, in order to keep the current sources in saturation, the transmitted voltage range must be well above ground that increases power dissipation.

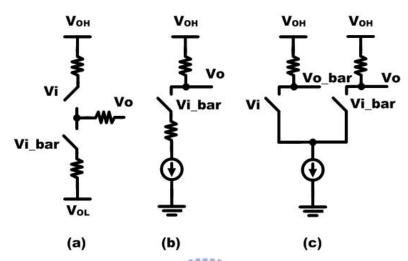

Figure 2-4 Transmitter timing diagram with different transmitter architectures:

(a) voltage-mode, (b) current mode, and (c) differential.

For better supply-noise rejection, the differential mode can be adopted, as shown in Fig 2-4 (c), because the supply noise is now common-mode. Since the current remains roughly constant, the transmitter induces less switching noise on the supply voltage that could benefit other transmitted or received signals on the same die. To reduce reflections at the end of the transmission line, the transmitter needs to be terminated. An off-chip termination resistor could introduce significant impedance mismatches because of the package parasitic components. To incorporate the resistor, with current-mode drivers, an explicit on-chip resistor at the driver can act as the termination resistor. If a resistive layer is not available, a transistor in its linear region can be used as the resistor. With voltage-mode drivers, the design is slightly more complex because the switch resistance should match the line impedance Z<sub>0</sub>. This may be done either through proper sizing of the driver or by over-sizing the driver and

compensating with an external series resistor, as shown in the Fig 2-4 (a).

## 2.5 Timing Recovery Architecture

#### 2.5.1 PLL-based Architecture

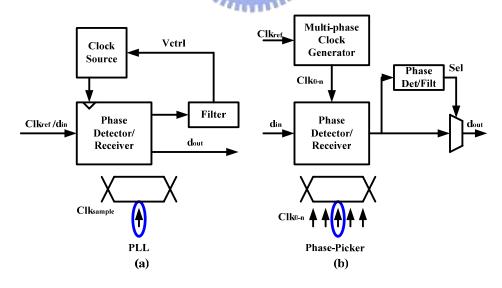

The task of the timing recovery circuit is to recover the phase and frequency information from the transition in the received data stream. The optimal sample point is midway between the possible data-transition times. Noise and mismatches inherent to the timing recovery circuit produce jitter in the sampling clocks, which degrade the timing margin. Moreover, the transmitter jitter causes uncertainty in the transition points makes clock extraction more difficult. As shown in **Fig 2-5**, two types of timing recovery architectures have been used in links. One is the PLL-based (data-recovery PLL) [12] and the other is the oversampling phase-picking [13].

Figure 2-5 Timing recovery architecture

#### (a) PLL-based (b) oversampling phase-picking

In PLL-based architecture, as shown in Fig 2-5(a), the negative feedback loop

controls the internal phase by adjusting the frequency of the voltage controlled oscillator (VCO) with Vctrl signal until the frequency matches that of an external reference. A phase detector detects the phase difference between the sampling clock and the external input data signal, and adjusts the VCO control voltage. A phase detector generally drives a charge pump that converts the phase difference into a charge. A filtered version of this charge becomes the VCO control voltage. Based on the phase information of the data, the best sample is chosen as the data bit by some decision logic. To maintain good phase relationship between the sampling clock and the data transitions, the PLL should detect the input phase accurately and track any input jitter with a high loop bandwidth. Unfortunately, the stability limits the loop bandwidth of the system. Because the timing information is embedded in the data system, coding of the data is used to ensure a minimum and maximum transition density. High data transition density in the data stream is preferred since it could maintain the stability of the system.

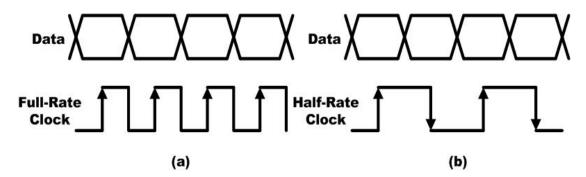

PLL-based timing recovery architectures can be categorized into full-rate and half-rate architectures. In a full-rate circuit the position of the data transition is compared to the falling edge or rising edge of the clock and clock frequency is equal to the data rate as shown in **Fig 2-6 (a)**. Single edge triggered flip flop can be used to retime the data. On the other hand, the location of the data transition is compared to both rising and falling edges of the clock in a half-rate circuit and the clock frequency is equal to one half of the data rate as shown in **Fig 2-6(b)**. Due to the one half of the clock frequency, double edge triggered flip flop is needed to perform the data retiming.

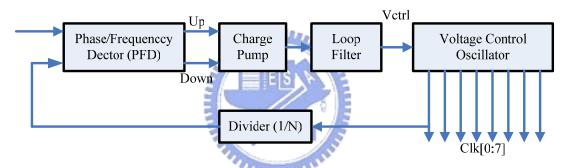

The most important advantage of half-rate architectures is the reduction of the circuit speed by a factor of two. This often means the reduction of the total power dissipation. In fact, as the operation speed of circuits approaches the maximum

operating frequency of a particular technology, the required power consumption grows exponentially. In addition, the de-multiplexing performed simultaneously by half-rate architecture is another attractive feature that makes them suitable for serial link architecture. It can reduce the complexity, hardware, and power dissipation of the deserializer.

Figure 2-6 (a) Full-rate data and clock (b) Half-rate data and clock