## 國立交通大學

電子工程學系 電子研究所碩士班

碩 士 論 文

IEEE 802.16a 分時雙工正交分頻多重進接下行導引訊號輔助式 通道估測之技術與數位訊號處理器軟體實現

IEEE 802.16a TDD OFDMA Downlink Pilot-Symbol-Aided Channel Estimation: Techniques and DSP Software Implementation

研究生: 陳汝芩

指導教授:林大衛 博士

中華民國九十四年六月

## IEEE 802.16a 分時雙工正交分頻多重進接下行導引訊號輔助式通道估測之技術與數位訊號處理器軟體實現

# IEEE 802.16a TDD OFDMA Downlink Pilot-Symbol-Aided Channel Estimation: Techniques and DSP Software Implementation

研究生: 陳汝芩 Student: Ruu-Ching Chen

指導教授: 林大衛 博士 Advisor: Dr. David W. Lin

國立交通大學

電子工程學系 電子研究所碩士班

碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics College of Electrical Engineering and Computer Science

National Chiao Tung University in Partial Fulfillment of Requirements

for the Degree of Master of Science

in

Electronics Engineering

June 2005

Hsinchu, Taiwan, Republic of China

中華民國九十四年六月

## IEEE 802.16a 分時雙工正交分頻多重進接下行導引訊號輔助式 通道估測之技術與數位訊號處理器軟體實現

研究生: 陳汝芩 指導教授: 林大衛 博士

#### 國立交通大學

電子工程學系 電子研究所碩士班

#### 摘要

正交分頻技術近來因為能在行動環境中穩定高速傳輸而廣受注目,IEEE 802.16a即是一個基於正交分頻多重進接技術用於無線區域網路和大都會網路的標準。

本論文主要在討論 IEEE 802.16a 下行通道估測的方法以及數位訊號處理器軟體實現。

我們使用最小平方差的估測器來估計在導訊上的通道頻率響應,因為硬體的計算方便。而內插的方法我們則研究了線性內插、二次式內插。而在用時域的資料改善的方法有下列兩種:二維內插法、以及最小平均平方差適應 (LMS adaptation)。我們的在靜態以及瑞雷通道上模擬。結合線性內插和二維內插法,我們得到較好的表現,而且運算複雜度也比較低,所以決定在數位訊號處理器軟體上實現。

我們將通道估測的技術以軟體實現在 Texas Instruments (TI) 公司製造型號為 TMS320C6416 的數位訊號處理器上 (DSP)。此處理器的操作平台為 Innovative Integration 公司製名為 Quixote 的 cPCI 卡。因為我們所使用的 DSP 是專為定點運算所設計的,所以浮點數運算是很費時的。有三種方法可以加速運算速度:改變資料型態、程式語法的改良及使用 intrinsic 程式。所謂的改變資料型態就是把一開始的浮點數運算先改成 32-bit 的定點運算,再改成 16-bit 的定點運算。程式語法的改良則是把許多耗時的指令做修正,如 if-else 的指令。Intrinsic 程式是一種直接對應到 C64x 指令集的程式,可以改善我們 C 程式的表現。在依照上述步驟對原本浮點數運算的程式做改良後,我們得到了很大的進步,雖然與理論上運算的複雜度相比,成效最高只到 49%。不過在線性內插程式方面,我們至少達到了只需 0.52 個 symbol time 就能完成的速度。

## IEEE 802.16a TDD OFDMA Downlink Pilot-Symbol-Aided Channel Estimation: Techniques and DSP Software Implementation

Student: Ruu-Ching Chen Advisor: Dr. David W. Lin

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

#### **Abstract**

OFDM (orthogonal frequency division multiplexing) technique has drawn much interest recently for its robustness in the mobile transmission environment and its high transmission data rate. IEEE 802.16a is a wireless local and metropolitan area networks standard which is based on OFDMA (orthogonal frequency division multiple access) technique.

This work considers two main subjects of the downlink channel estimation under the specifications of IEEE 802.16a, the interpolation schemes and the DSP implementation.

We use LS estimator for estimations of pilot carriers because of its low computational complexity. We study the linear, the second-order interpolations in frequency domain and the LMS adaptation algorithm, the two-D interpolation in time domain. We did the simulation on both static and Rayleigh fading channels. Combination of linear interpolation and 2-D interpolation are chosen to be implemented on DSP board for its low computational complexity.

Our implementation is software-based, employing Texas Instruments' TMS320C6416 digital signal processor (DSP) housed on Innovative Integration's Quixote cPCI card. For the fixed-point DSP operation environment, floating-point operation is absolutely time-consuming. There are three ways to accelerate the DSP execution speed: changing data type, code style optimization, and using intrinsic functions. Changing data type means we replace the original floating-point operation with 32-bit fixed-point operation and then 16-bit fixed-point operation at last. Code style optimization is to modify the time-wasting parts of code, such as spared if-else instruction. Intrinsic functions are special functions that map directly to C64x instructions, to optimize our C code performance. The execution cycles of each function is improved a lot after optimized although compared with the theoretical execution cycles, the efficiency is 49% at most. At least, we reach the 0.52 multiples of real time needed per symbol in linear interpolation.

#### 誌謝

要感謝的人太多,尤其是林老師,感謝他兩年多來對我的指導與包容,能當老師的學生是我前世修來的福氣。

此外,感謝通訊電子與訊號處理實驗室所有的成員,包含各位師長、同學、 學長姐與學弟妹們。我要感謝吳俊榮學長、洪崑健學長指導與建議,還有昱昇、 志凱、景中、鎮宇、、等同學,謝謝他們在這兩年來對我的幫助及帶給我歡樂。

家人對我的支持、鼓勵是我研究路上一股強大的動力,對他們的感謝,是筆 墨難以形容的。

最後由衷感謝所有幫助關懷過我的人。

陳汝芩

民國九十四年七月 於新竹

## Contents

| 1        | Intr                   | roducti | ion                                               | 1  |

|----------|------------------------|---------|---------------------------------------------------|----|

|          | 1.1                    | Brief 1 | Introduction to IEEE 802.16a [1], [2]             | 1  |

|          | 1.2                    | Motiv   | ration of This Thesis                             | 4  |

|          | 1.3                    | Organ   | nization of This Thesis                           | 5  |

| <b>2</b> | $\mathbf{C}\mathbf{h}$ | annel   | Estimation for IEEE 802.16a OFDMA Downlink Trans- |    |

|          | mis                    | sion    | 1896                                              | 6  |

|          | 2.1                    | Introd  | duction to the IEEE 802.16a TDD OFDMA System      | 6  |

|          |                        | 2.1.1   | Generic OFDMA Symbol Description                  | 7  |

|          |                        |         | 2.1.1.1 Time Domain Description                   | 7  |

|          |                        |         | 2.1.1.2 Frequency Domain Description              | 7  |

|          |                        | 2.1.2   | Primitive Parameters                              | 8  |

|          |                        | 2.1.3   | Derived Parameters                                | 8  |

|          |                        | 2.1.4   | Downlink Carrier Allocation                       | 9  |

|          |                        |         | 2.1.4.1 Pilot Allocation                          | 9  |

|          |                        |         | 2.1.4.2 Data Carrier Allocation                   | 11 |

|          |                        | 2.1.5   | Data Modulation and Pilot Modulation              | 12 |

|          |                        |         | 2.1.5.1 Data Modulation                           | 12 |

|   |     |         | 2.1.5.2 Pilot Modulation                                       | 13 |

|---|-----|---------|----------------------------------------------------------------|----|

|   | 2.2 | DL Ch   | annel Estimation Methods                                       | 14 |

|   |     | 2.2.1   | Pilot-Symbol-Aided Channel Estimation                          | 14 |

|   |     | 2.2.2   | Frequency Domain Interpolation Methods                         | 16 |

|   |     |         | 2.2.2.1 Linear Interpolation                                   | 16 |

|   |     |         | 2.2.2.2 Second-Order Interpolation                             | 17 |

|   |     | 2.2.3   | Time Domain Improvement Methods                                | 18 |

|   |     |         | 2.2.3.1 Two-Dimensional Interpolation [11]                     | 18 |

|   |     |         | 2.2.3.2 Least Mean Square (LMS) Adaptation [12], [14] $^{2}$   | 21 |

| 3 | DSI | P Intro | duction 2                                                      | 23 |

|   | 3.1 | Introd  | uction to TMS320C6416 DSP [16]                                 | 23 |

|   |     | 3.1.1   | TMS320C6416 Features                                           | 23 |

|   |     | 3.1.2   | Central Processing Unit                                        | 25 |

|   |     |         | 3.1.2.1 Pipeline                                               | 26 |

|   |     |         | 3.1.2.2 Functional Units                                       | 29 |

|   |     | 3.1.3   | Memory Architecture                                            | 29 |

|   | 3.2 | Introd  | uction to the Quixote cPCI Board [15]                          | 32 |

|   | 3.3 | Introd  | uction to the Code Composer Studio Development Tools[17], [18] | 36 |

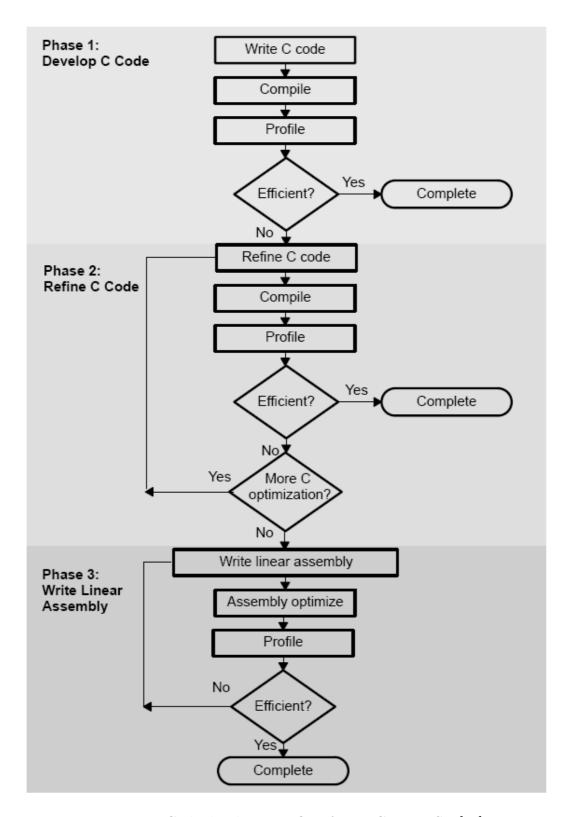

|   | 3.4 | Code (  | Optimization Methods [21]                                      | 38 |

|   |     | 3.4.1   | Compiler Optimization Options [17], [18]                       | 40 |

|   |     | 3.4.2   | Using Intrinsics                                               | 42 |

| 4 | Sim | ulatior | and DSP Implementation 4                                       | 13 |

|                           | 4.1    | Compa   | arison Be | tween 2-D Interpolation and LMS Adaptive Methods. | 43  |

|---------------------------|--------|---------|-----------|---------------------------------------------------|-----|

|                           |        | 4.1.1   | Simulati  | on Results for AWGN Channel                       | 44  |

|                           |        | 4.1.2   | Simulati  | on Results for Static Multipath Channel           | 45  |

|                           |        |         | 4.1.2.1   | Two-Dimensional Interpolation                     | 48  |

|                           |        |         | 4.1.2.2   | LMS Adaptive Algorithm                            | 57  |

|                           |        | 4.1.3   | Multipat  | th Rayleigh Fading Channel Simulations            | 57  |

|                           | 4.2    | DSP I   | mplement  | cation                                            | 63  |

|                           |        | 4.2.1   | Introduc  | etion to Program Structure                        | 65  |

|                           |        | 4.2.2   | Performa  | ance of the Original Program                      | 69  |

|                           |        | 4.2.3   | Choice o  | of the Fixed-Point Data Formats                   | 71  |

|                           |        |         | 4.2.3.1   | 32-bit Fixed-Point Operation                      | 71  |

|                           |        |         | 4.2.3.2   | 16-Bit Fixed-Point Operation                      |     |

|                           |        | 4.2.4   | Code Im   | provement                                         | 76  |

|                           |        |         | 4.2.4.1   | Coding Style Improvement                          |     |

|                           |        |         | 4.2.4.2   | Optimization by Using Intrinsic Functions [21]    | 78  |

|                           |        | 4.2.5   | Final Ve  | ersion of Fixed-Point 16-Bit Operation            | 80  |

|                           |        |         | 4.2.5.1   | Execution Efficiency                              | 81  |

|                           |        | 4.2.6   | Summar    | у                                                 | 87  |

| 5                         | Cor    | nclusio | n and Fu  | iture Work                                        | 90  |

|                           | 5.1    | Concli  | ision     |                                                   | 90  |

|                           | 5.2    |         |           |                                                   | 91  |

|                           | 0.2    | I dould | , 1101K   |                                                   | O I |

| $\mathbf{B}^{\mathbf{i}}$ | ibliog | graphy  |           |                                                   | 92  |

## List of Figures

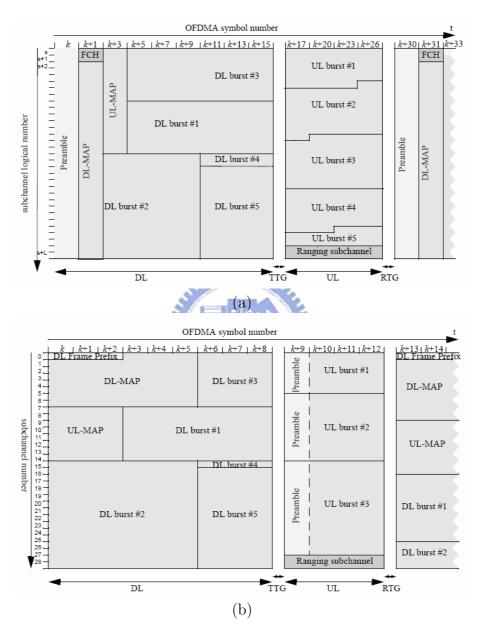

| 1.1 | (a) Frame structure in IEEE 802.16-2004 [1]. (b) Frame structure in |    |

|-----|---------------------------------------------------------------------|----|

|     | IEEE 802.16a-2003 [2]                                               | 3  |

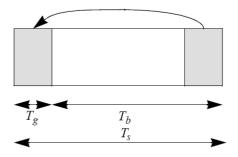

| 2.1 | Time structure of OFDMA symbol (from [2])                           | 7  |

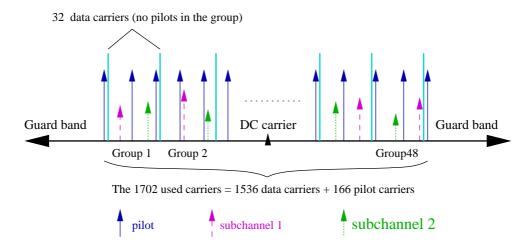

| 2.2 | Illustration of carrier usage in OFDMA DL (from [3])                | 9  |

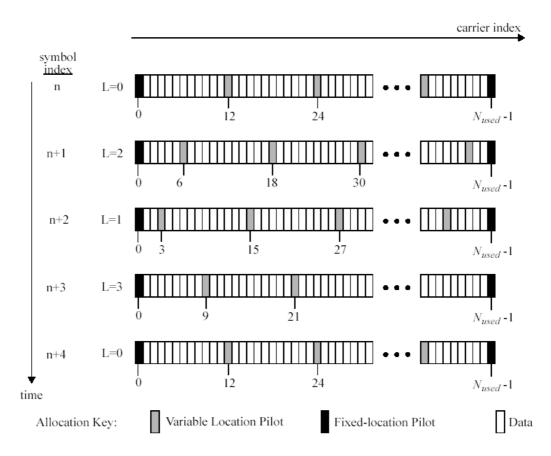

| 2.3 | Pilot allocation in the OFDMA DL (from [2])                         | 10 |

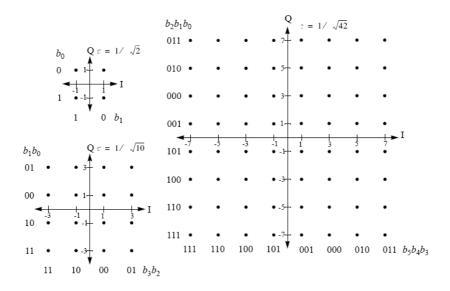

| 2.4 | QPSK, 16-QAM and 64-QAM constellations (from [2])                   | 13 |

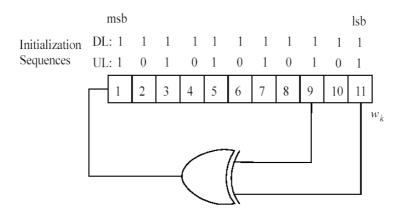

| 2.5 | Pseudo random binary sequence (PRBS) generator for pilot modula-    |    |

|     | tion (from [2])                                                     | 14 |

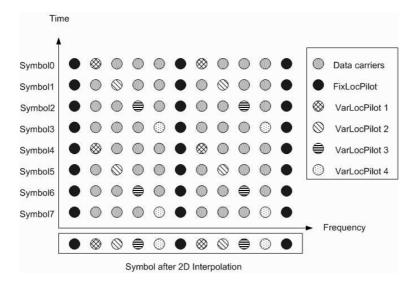

| 2.6 | Illustration of 2D interpolation                                    | 18 |

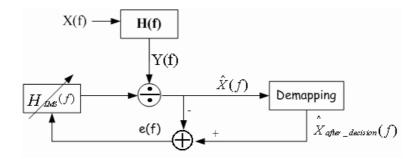

| 2.7 | Adaptive channel estimation using the LMS algorithm                 | 21 |

| 3.1 | Block diagram of the TMS320C6416 DSP [16]                           | 26 |

| 3.2 | Pipeline phases of TMS320C6416 DSP [16]                             | 27 |

| 3.3 | TMS320C64x CPU data path [16]                                       | 31 |

| 3.4 | Block diagram of Quixote [15]                                       | 33 |

| 3.5 | Block diagram of DSP streaming mode [15]                            | 34 |

| 3.6 | Code development flow for TI C6000 DSP [21]                         | 39 |

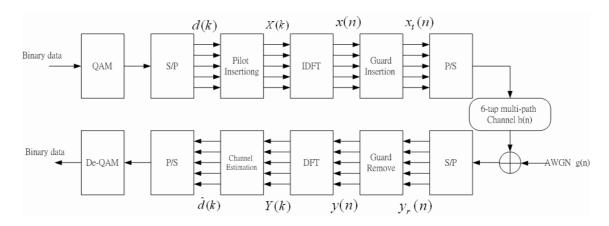

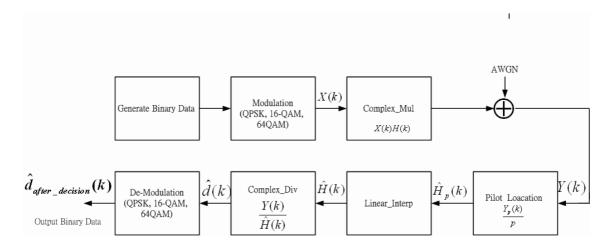

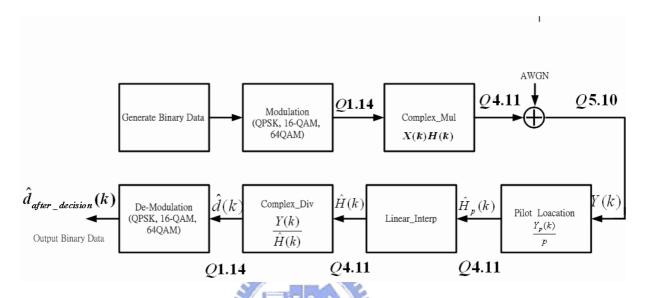

| 4.1 | Block diagram of the simulated system                               | 44 |

| 4.2  | Channel estimation steps                                                 | 44 |

|------|--------------------------------------------------------------------------|----|

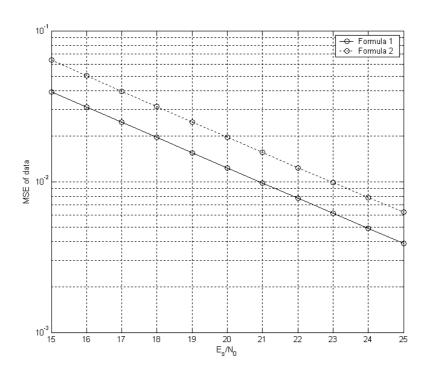

| 4.3  | MSE of $ \hat{X}_i - X_i $ for AWGN channel                              | 45 |

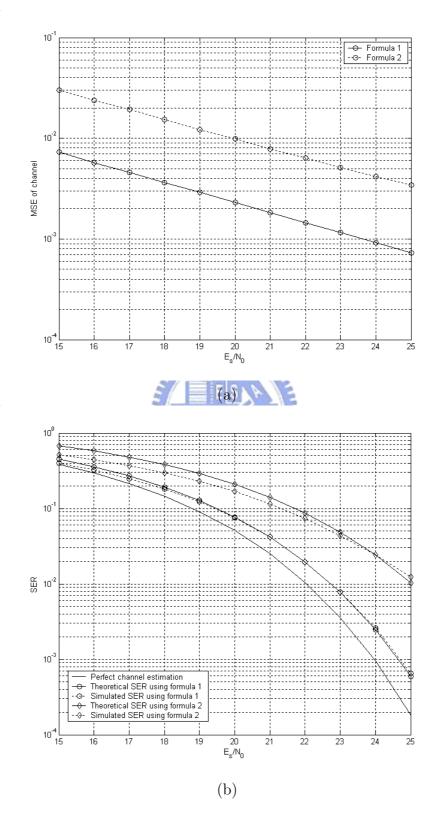

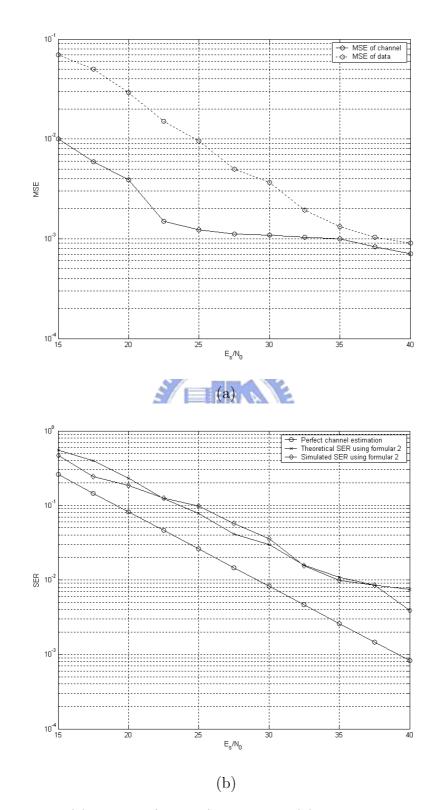

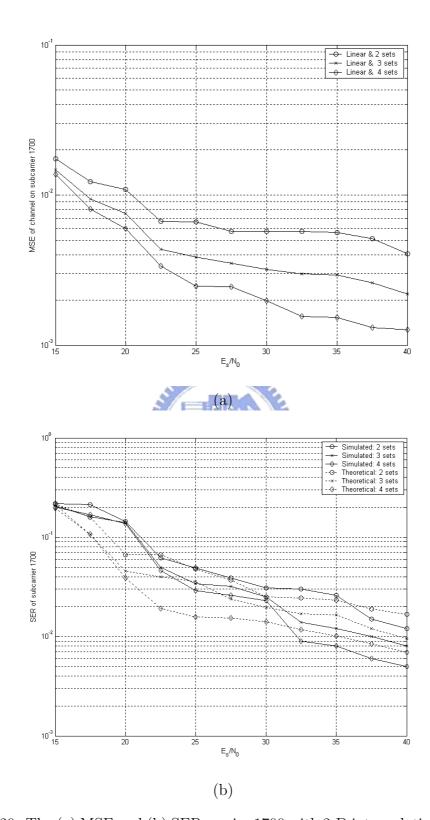

| 4.4  | The (a) MSE and (b) SER for AWGN channel simulation                      | 46 |

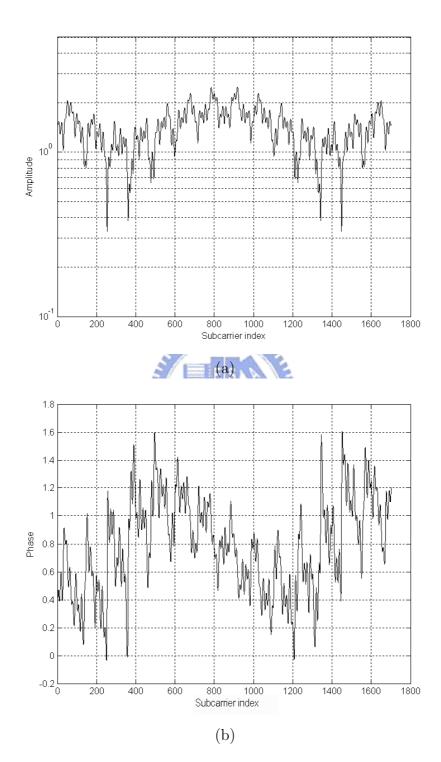

| 4.5  | (a)Amplitude response and (b) phase response of the channel given        |    |

|      | in Table 4.2                                                             | 47 |

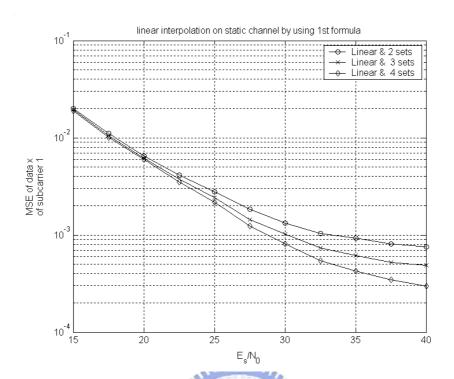

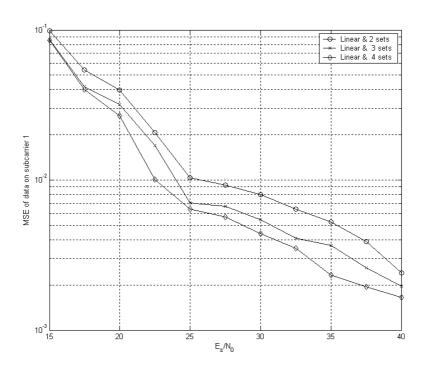

| 4.6  | MSE of $ \hat{X}_i - X_i $ on subcarrier 1                               | 49 |

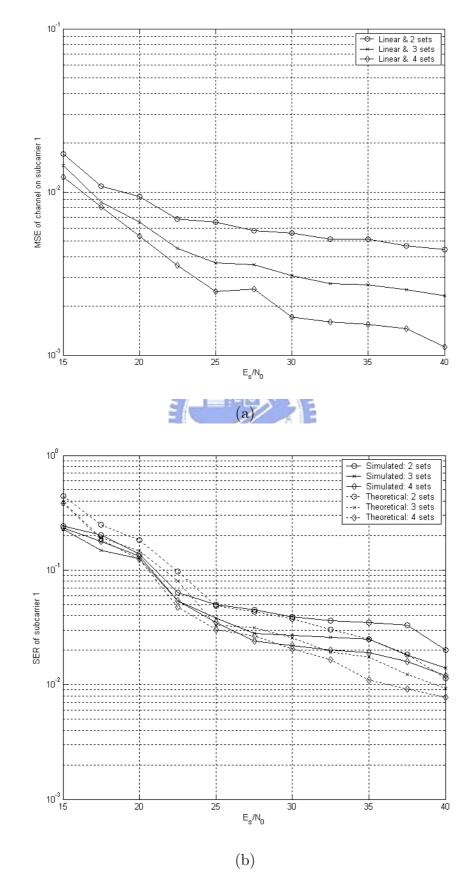

| 4.7  | The (a) MSE and (b) SER on the subcarrier 1 of the 2-D interpolation     |    |

|      | using formula 1 with linear interpolation in the frequency domain        |    |

|      | respectively                                                             | 50 |

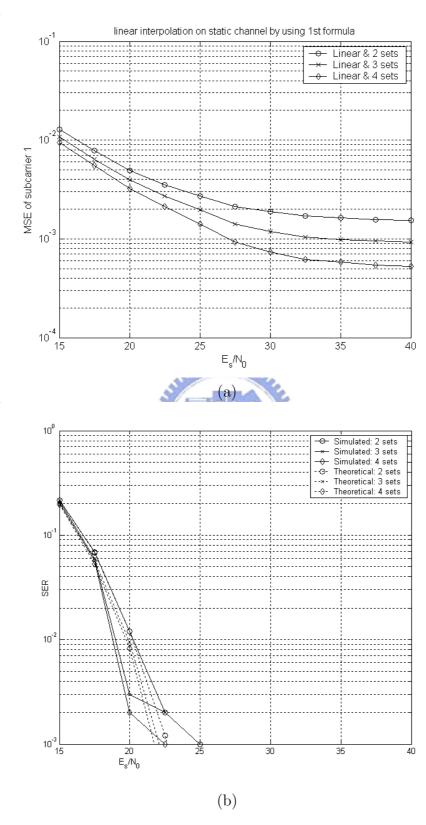

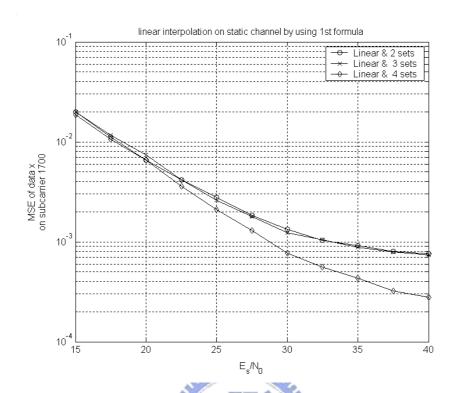

| 4.8  | MSE of $ \hat{X}_i - X_i $ on subcarrier 1700                            | 51 |

| 4.9  | The (a) MSE and (b) SER on the subcarrier 1700 of the 2-D inter-         |    |

|      | polation using formula 1 with linear interpolation in the frequency      |    |

|      | domain respectively.                                                     | 52 |

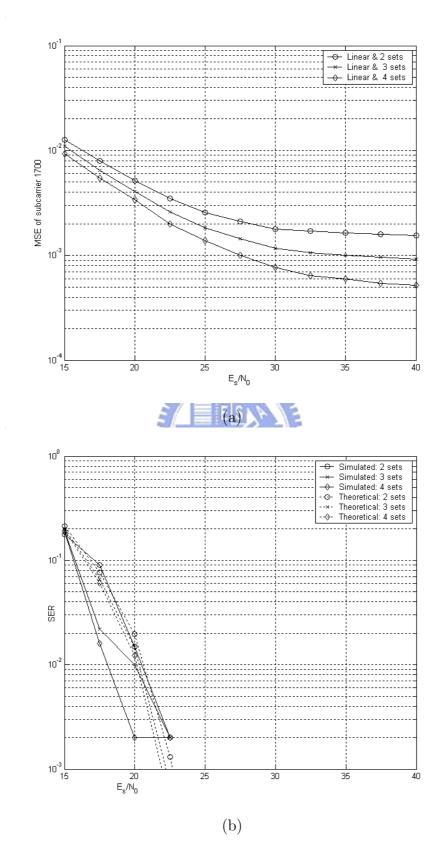

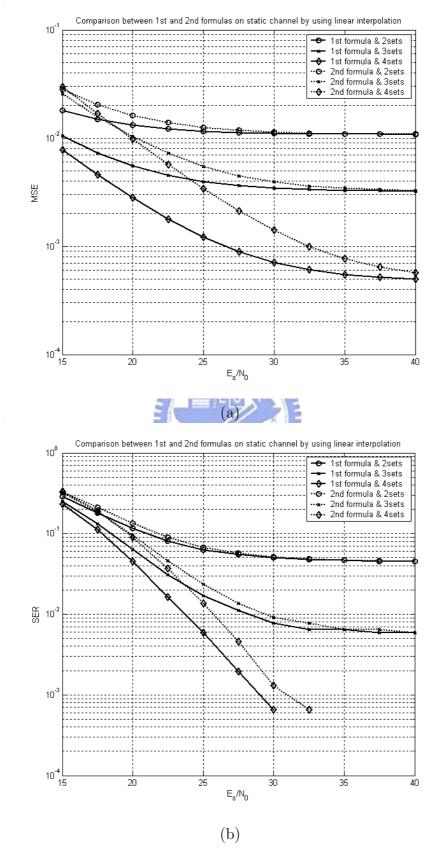

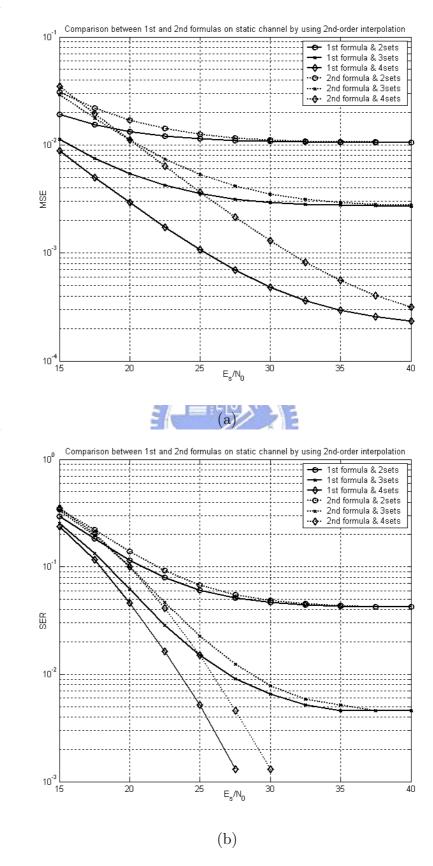

| 4.10 | The (a) MSE and (b) SER of the 2-D interpolation using formula           |    |

|      | 1 with linear and 2nd-order interpolation in the frequency domain        |    |

|      | respectively                                                             | 53 |

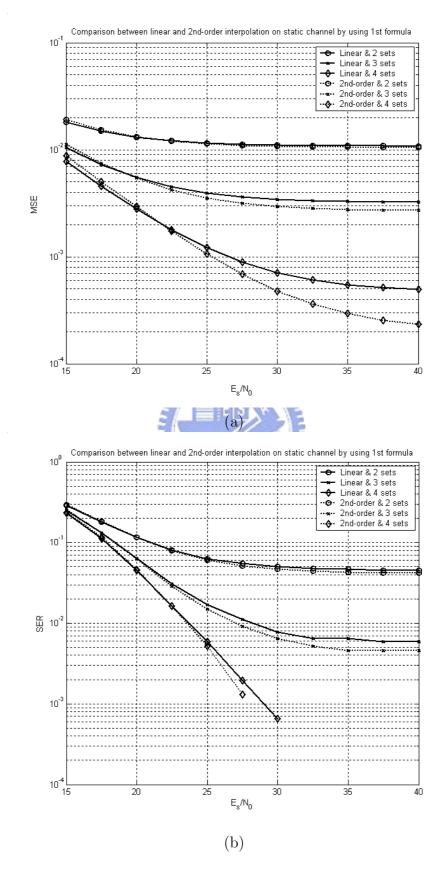

| 4.11 | The (a) MSE and (b) SER of the 2-D interpolation using formula           |    |

|      | 2 with linear and 2nd-order interpolation in the frequency domain        |    |

|      | respectively                                                             | 54 |

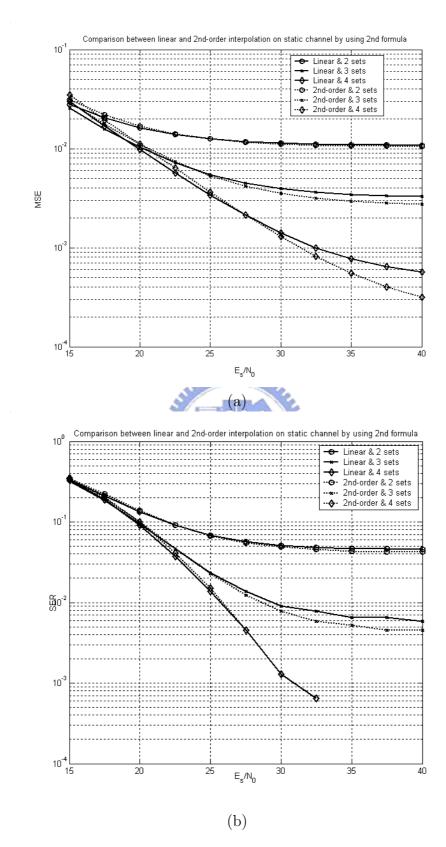

| 4.12 | The (a) MSE and (b) SER of using formula 1 and 2 in the 2-D inter-       |    |

|      | polation respectively with linear interpolation in the frequency domain. | 55 |

| 4.13 | The (a) MSE and (b) SER of using formula 1 and 2 in the 2-D in-          |    |

|      | terpolation respectively with 2nd-order interpolation in the frequency   |    |

|      | domain                                                                   | 56 |

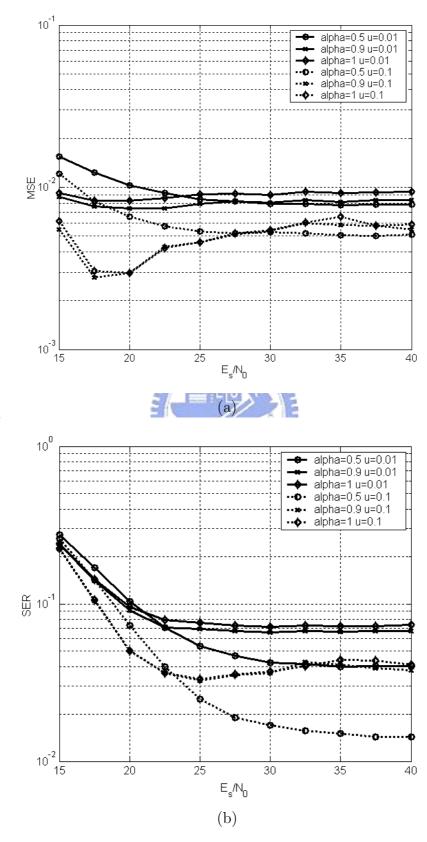

| 4.14 | The (a) MSE and (b) SER for different weighting and different step-                         |    |

|------|---------------------------------------------------------------------------------------------|----|

|      | size parameters in LMS adaptive method                                                      | 58 |

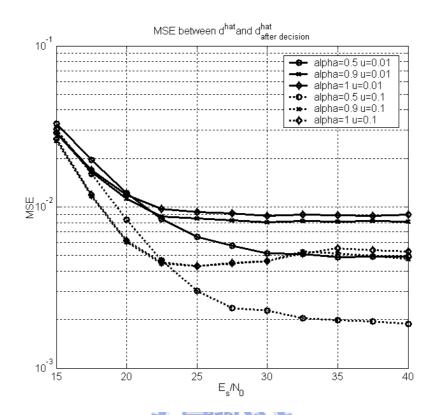

| 4.15 | MSE between $\hat{X}$ and $\hat{X}_{after\_decision}$ for different weighting and different |    |

|      | step-size parameters in LMS adaptive method                                                 | 59 |

| 4.16 | The (a) MSE of $ \hat{x}_i - x_i $ , MSE and (b) SER for one-path Rayleigh                  |    |

|      | fading channel, where $V=27$ km/h, $fdT=0.01.$                                              | 62 |

| 4.17 | MSE of $ \hat{X}_i - X_i $ on subcarrier 1 for multipath Rayleigh fading channel.           | 63 |

| 4.18 | The (a) MSE and (b) SER of carrier 1 with 2-D interpolation using                           |    |

|      | formula 2 with linear interpolation in the frequency domain respec-                         |    |

|      | tively. $V = 27 \text{ km/h}, f dT = 0.01$                                                  | 64 |

| 4.19 | MSE of $ \hat{X}_i - X_i $ on subcarrier 1700 for multipath Rayleigh fading                 |    |

|      | channel                                                                                     | 65 |

| 4.20 | The (a) MSE and (b) SER carrier 1700 with 2-D interpolation using                           |    |

|      | formula 2 with linear and 2nd-order interpolation in the frequency                          |    |

|      | domain respectively. $V=27$ km/h, $fdT=0.01.$                                               | 66 |

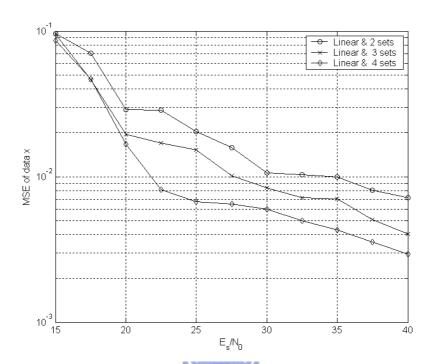

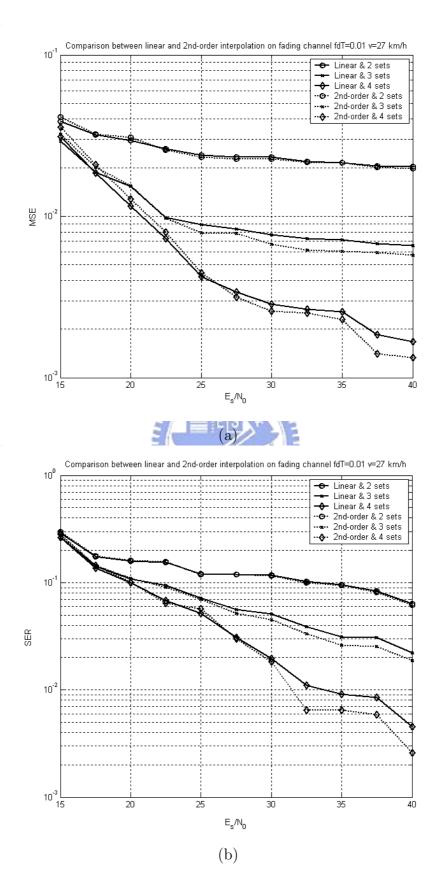

| 4.21 | The (a) MSE and (b) SER of the 2-D interpolation using formula                              |    |

|      | 2 with linear and 2nd-order interpolation in the frequency domain                           |    |

|      | respectively. $V=27$ km/h, $fdT=0.01$                                                       | 67 |

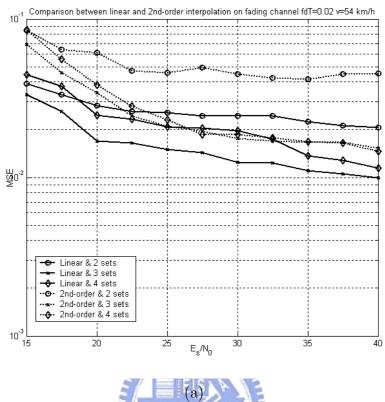

| 4.22 | The (a) MSE and (b) SER of the 2-D interpolation using formula                              |    |

|      | 2 with linear and 2nd-order interpolation in the frequency domain                           |    |

|      | respectively. $V = 54$ km/h, $f_d T = 0.02$                                                 | 68 |

| 4.23 | Program structure for channel estimation                                                    | 69 |

| 4.24 | Function Modulation (QPSK)                                                                  | 70 |

| 4.25 | Function Complex_Mul                                                                        | 70 |

| 4.26 | Function Linear_Interp                                                                      | 71 |

| 4.27 | Function Complex_Div                                                                | 72 |

|------|-------------------------------------------------------------------------------------|----|

| 4.28 | Function $De\text{-}modulation(QPSK)$                                               | 72 |

| 4.29 | Function $Modulation(QPSK)$ of 32-bit fixed-point operation                         | 74 |

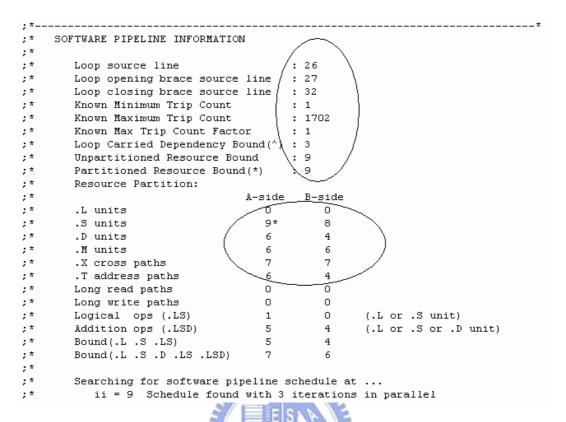

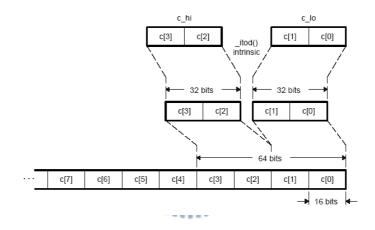

| 4.30 | Software pipelining information of 32-bit fixed-point $Complex\_Mul.$ .             | 75 |

| 4.31 | The loop kernel of $Complex\_Mul$                                                   | 76 |

| 4.32 | Fixed-point data formats used in DSP implementation                                 | 77 |

| 4.33 | Example of different coding styles in C code                                        | 78 |

| 4.34 | Result of different coding styles in complied assembly code                         | 79 |

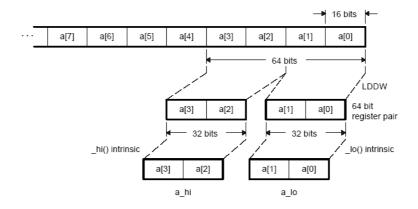

| 4.35 | Array access in vector sum by LDDW [21]                                             | 80 |

| 4.36 | Array access in vector sum by STDW [21]                                             | 80 |

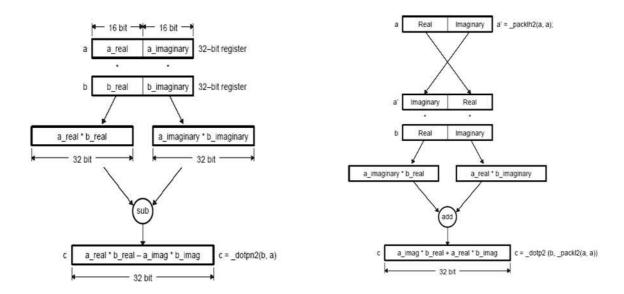

| 4.37 | Illustration of the _dotp2 and the _dotpn2 intrinsics [21]                          | 81 |

|      | Function vec_Complex_Mul                                                            |    |

| 4.39 | Function $vec\_Complex\_Div$                                                        | 83 |

|      | Original interpolation loop                                                         |    |

| 4.41 | Final version of the interpolation loop                                             | 84 |

| 4.42 | Loop kernel of modified assembly code in <i>Linear_Interp</i>                       | 85 |

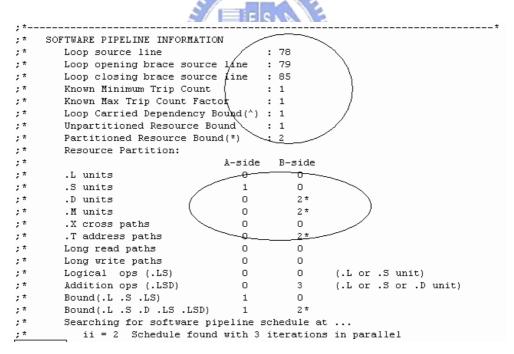

| 4.43 | Software pipelining information of the modified loop in $\mathit{Linear\_Interp}$ . | 85 |

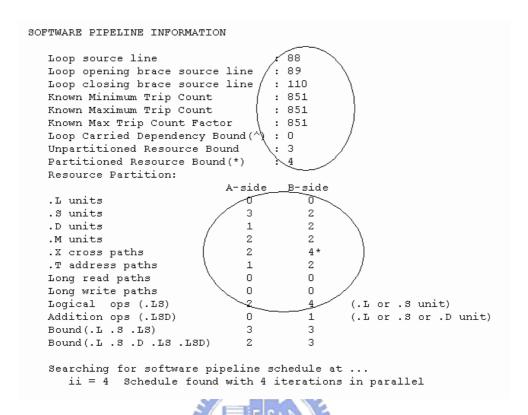

| 4.44 | Software pipelining information of 16-bits fixed-point of $Complex\_Mul$ .          | 87 |

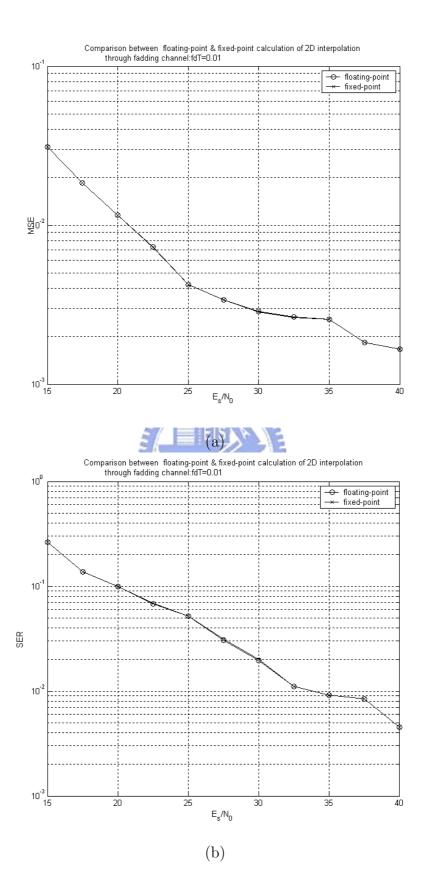

| 4.45 | (a) MSE and (b) SER comparison between floating-point and 16-bit                    |    |

|      | fixed-point operations with 2-D interpolation using formula 2 (4 sets)              |    |

|      | with linear interpolation in the frequency domain. $V=27~\mathrm{km/h},$            |    |

|      | $fdT = 0.01. \dots \dots \dots \dots \dots \dots \dots \dots$                       | 89 |

## List of Tables

| 1.1 | Carrier Allocation in the OFDMA DL (from [1])                        | 4  |

|-----|----------------------------------------------------------------------|----|

| 2.1 | Carrier Allocation in the OFDMA DL (from [2])                        | 12 |

| 3.1 | Execution Stage Length Description for Each Instruction Type [16] .  | 28 |

| 3.2 | Functional Units and Operations Performed [16]                       | 30 |

| 4.1 | MSE Ratio Between Formula 1 and Formula 2 for AWGN Channel .         | 48 |

| 4.2 | Channel Impulse Response                                             | 48 |

| 4.3 | MSE Ratio Between Formula 1 and Formula 2 for Multipath Channel      | 57 |

| 4.4 | Relation Between Speed and Maximum Doppler Shift                     | 61 |

| 4.5 | Floating-Point Profile of 802.16a DL Channel Estimation Function     |    |

|     | Blocks                                                               | 73 |

| 4.6 | Q16.15 Bit Fields                                                    | 73 |

| 4.7 | Fixed-Point 32-Bit Operation Profile of 802.16a DL Channel Estima-   |    |

|     | tion Function Blocks                                                 | 73 |

| 4.8 | Q1.14 Bit Fields                                                     | 77 |

| 4.9 | Different Ways of Variable Declaration, Where r Stands for Real Part |    |

|     | and i Stands for Imaginary Part                                      | 77 |

| 4.10 | Fixed-Point 16-bit Operation with Coding Style Modified Profile of      |

|------|-------------------------------------------------------------------------|

|      | 802.16a DL Channel Estimation Function Blocks                           |

| 4.11 | Performance Comparison Between Different Data Types of $Complex\_Mul$   |

|      | 86                                                                      |

| 4.12 | Performance Comparison Between Different Data Types of $Complex\_Div$   |

|      | 86                                                                      |

| 4.13 | Performance Comparison Between Different Data Types of $Linear\_Interp$ |

|      | 87                                                                      |

#### Chapter 1

#### Introduction

#### 1.1 Brief Introduction to IEEE 802.16a [1], [2]

In recent years, orthogonal frequency division multiplexing (OFDM) modulation technique has drawn much attention for its ability to deal with frequency-selective fading in high-speed wireless communication. The IEEE 802.16 standard committee has developed a group of standards for wireless metropolitan area networks (MANs). Project 802.16a is one of them. The object of this present study is the OFDMA-based interface option of this project, namely WirelessMAN-OFDMA.

The IEEE 802.16-2001 specifies the air interface of fixed (stationary) point-to-multipoint broadband wireless access systems providing multiple services. The medium access control layer is capable of supporting multiple physical layer specifications optimized for the frequency bands of application. This standard includes a particular physical layer specification applicable to systems operating between 10 and 66 GHz.

The IEEE 802.16a amends IEEE 802.16-2001 by enhancing the medium access control layer and providing additional physical layer specifications in support of broadband wireless access at frequencies from 2 to 11 GHz.

For the reason that our project started in year 2002, we have followed the specifi-

cation of these two standards above. However, the IEEE 802.16 standard committee has completed a new version of the standard in year 2004, namely IEEE 802.16-2004. This standard specifies the air interface of fixed broadband wireless access (BWA) systems supporting multimedia services. The medium access control layer (MAC) supports a primarily point-to-multipoint architecture, with an optional mesh topology. The MAC is structured to support multiple physical layer (PHY) specifications, each suited to a particular operational environment. For operational frequencies of 10–66 GHz, the PHY is based on single-carrier modulation. For frequencies below 11 GHz, where propagation without a direct line of sight must be accommodated, three alternatives are provided, using OFDM, OFDMA, and single carrier modulation techniques.

Since pilot allocations are key to the study reported in this thesis, we summarize the difference between these two versions about the carrier allocations. Table 1.1 shows the pilot allocation of IEEE 802.16-2004. The variable set of pilots embedded within the symbol of each segment obeys the following rule:

THE PERSON NAMED IN

$$PilotsLocation = VariableSet \#x + 6 \cdot (FUSC\_SymbolNumber mod 2)$$

(1.1)

where FUSC\_SymbolNumber counts the FUSC (full uasage of subchannels) symbols used in the transmission starting from 0. The arrangement is slightly different from the specification in the IEEE 802.16a-2003 (see also Fig.2.3). We have four kinds of variable location pilot arrangements in 802.16a but there are only two kinds in IEEE 802.16-2004.

As to the frame structure, the IEEE 802.16-2004 also made modification to it. From Fig. 1.1(a) we can see that in IEEE 802.16-2004, each frame begins with a preamble followed by a downlink transmission period and an uplink transmission period. This is quite different from the frame structure in IEEE 802.16a-2003, shown in Fig. 1.1(b), where preamble is used only in the uplink subframe.

Figure 1.1: (a) Frame structure in IEEE 802.16-2004 [1]. (b) Frame structure in IEEE 802.16a-2003 [2].

Table 1.1: Carrier Allocation in the OFDMA DL (from [1])

| Parameter                                 | Value | Comments                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of DC Subcarriers                  | 1     | Index 1024                                                                                                                                                                                                                                                                                                                                 |

| Number of Guard Subcarriers, Left         | 173   |                                                                                                                                                                                                                                                                                                                                            |

| Number of Guard Subcarriers, Right        | 172   |                                                                                                                                                                                                                                                                                                                                            |

| Number of Used Subcarriers ( $N_{uzed}$ ) | 1703  | Number of all subcarriers used within a symbol, including all possible allocated pilots and the DC carrier.                                                                                                                                                                                                                                |

| Pilots                                    |       |                                                                                                                                                                                                                                                                                                                                            |

| VariableSet #0                            | 24    | 0,72,144,216,288,360,432,504,576,648,720,792,864,<br>936,1008,1080,1152,1224,1296,1368,1440,1512,1584,<br>1656,48,120,192,264,336,408,480,552,624,696,768,<br>840,912,984,1056,1128,1200,1272,1344,1416,1488,<br>1560,1632,24,96,168,240,312,384,456,528,600,672,<br>744,816,888,960,1032,1104,1176,1248,1320,1392,<br>1464,1536,1608,1680 |

| ConstantSet #0                            | 4     | 39,645,1017,1407,330,726,1155,1461,351,855,1185,<br>1545                                                                                                                                                                                                                                                                                   |

| VariableSet #1                            | 24    | 36,108,180,252,324,396,468,540,612,684,756,828, 900,972,1044,1116,1188,1260,1332,1404,1476,1548, 1620,1692,12,84,156,228,300,372,444,516,588,660, 732,804,876,948,1020,1092,1164,1236,1308,1380, 1452,1524,1596,1668,60,132,204,276,348,420,492, 564,636,,708,780,852,924,996,1068,1140,1212,1284, 1356,1428,1500,1572,1644                |

| ConstantSet #1                            | 4     | 261,651,1143,1419,342,849,1158,1530,522,918,1206, 1701                                                                                                                                                                                                                                                                                     |

| Number of data subcarriers                | 1536  |                                                                                                                                                                                                                                                                                                                                            |

| Number of data subcarriers per subchannel | 48    |                                                                                                                                                                                                                                                                                                                                            |

| Number of Subchannels                     | 32    |                                                                                                                                                                                                                                                                                                                                            |

| PermutationBase                           |       | 3, 18, 2, 8, 16, 10, 11, 15, 26, 22, 6, 9, 27, 20, 25, 1, 29, 7, 21, 5, 28, 31, 23, 17, 4, 24, 0, 13, 12, 19, 14, 30                                                                                                                                                                                                                       |

#### 1.2 Motivation of This Thesis

In high data rate transmission, the imperfectness of channels, e.g., multipaths, causes more severe trouble than in low-rate transmission in demodulation. The result of data transmission over such a channel is that each received symbol is affected somewhat by adjacent symbols, thereby bringing about a common form of interference referred to as inter-symbol-interference (ISI). Inter-symbol-interference is a major source which degrades performance in the reconstructed data at receiver. In single carrier transmission, we usually employ an time domain adaptive equalizer to solve this problem. If the channel has very long impulse response compared with symbol

duration, time domain equalizer may fail to handle ISI. However, in OFDM system, ISI can be easily eliminated by inserting cyclic prefix which is longer than the maximum delay spread, at the expense of some loss in capacity.

In uncoded OFDM, we only need a frequency domain equalizer with one tap at the receiver for each subcarrier. The purpose of channel estimation is to obtain the channel response at each subcarrier. Then, we can easily obtain the equalizer coefficient, the inverse of the channel gain. In channel coded OFDM, such as that in IEEE 802.16a OFDMA, equalization is not needed, but the estimated channel response is directly useful in channel decoding. Hence in this thesis, we will investigate channel estimation methods that can be employed to the IEEE 802.16a downlink transmission.

#### 1.3 Organization of This Thesis

The contents of this thesis are as follows. In chapter 2, we give some specifications of the IEEE 802.16a OFDMA downlink system and introduce the channel estimation approaches. In chapter 3, we describe the implementation platform, which consists of Texas Instruments' TMS320C6416 digital signal processor(DSP) on a cPCI board Quixote made by Innovative Integration. Then, in chapter 4, we discuss the performance of the proposed channel estimation method as well as its DSP implementation. At last, we will give the conclusion and potential future work in chapter 5.

#### Chapter 2

## Channel Estimation for IEEE 802.16a OFDMA Downlink Transmission

For wideband mobile communication systems, the radio channel is usually frequency selective and time variant. Therefore, our estimation schemes combine frequency domain estimation with time domain processing. In this thesis, our algorithms for channel estimation in OFDM system are intimately related to pilot sub-carrier arrangement.

## 2.1 Introduction to the IEEE 802.16a TDD OFDMA System

The IEEE standard 802.16a specifies the WirelessMAN air interface for wireless metropolitan area networks. There are several system modes in 802.16a: SCa (single-carrier modulation), OFDM (orthogonal frequency-division multiplexing) and OFDMA (orthogonal frequency-division multiple access). It also supports two duplex types: TDD (time division duplex) and FDD (frequency division duplex). We consider the TDD OFDMA option. Most contents in this section are taken from [2].

Figure 2.1: Time structure of OFDMA symbol (from [2]).

#### 2.1.1 Generic OFDMA Symbol Description

#### 2.1.1.1 Time Domain Description

An OFDM symbol contains the useful symbol part and the cyclic prefix (CP) part. The useful symbol time is referred to as  $T_b$ . The CP is a copy of the last  $T_g$   $\mu$ s of the useful symbol period. The two together are referred to as the symbol time  $T_s$ . The ratio of CP time to useful time  $(T_g/T_b)$  that should be supported includes 1/32, 1/16, 1/8 and 1/4. In this thesis, the CP time to useful time ratio is set to 1/8. The time domain OFDMA symbol structure is shown in Fig. 2.1.

#### 2.1.1.2 Frequency Domain Description

In frequency domain, we have 3 carrier types:

- Data carriers for data transmission.

- Pilot carriers for various estimation purposes.

- Null carriers no transmission at all, for guard bands and DC carrier. (The purpose of the guard bands is to enable the signal to naturally decay and create the FFT "brick wall" shaping.)

In the OFDMA mode, active carriers are devided into subsets of carriers, and each subset is termed a subchannel. In the downlink (DL), a subchannel may be intended for different groups of receivers; similarly, a transmitter may be assigned one or more subchannels in the uplink (UL), so serveral transmitters may transmit in parallel. The symbol structure in frequency domain will be shown in detail in the following section.

#### 2.1.2 Primitive Parameters

Four primitive parameters characterize the OFDMA symbol:

- BW. This is the nominal channel bandwidth. And it equals 10 MHz in our system simulation.

- $(F_s/BW)$ . This is the ratio of "sampling frequency" to the nominal channel bandwidth. This value is set to 8/7.

- $(T_g/T_b)$ . This is the ratio of CP time to "useful" time. We use 1/8 in our system.

- $N_{FFT}$ . This is the number of points in the FFT. The OFDMA PHY defines this value to be 2048.

#### 2.1.3 Derived Parameters

The following parameters are defined in terms of the primitive parameters.

- $F_s = (F_s/BW) \cdot BW = \text{sampling frequency}$ . The value equals  $10 \times 8/7 = 11.42$  MHz.

- $\triangle f = F_s/N_{FFT} = \text{carrier spacing} = 5.57617 \text{ KHz}.$

- $T_b = 1/\Delta f = \text{useful time} = 179.33 \ \mu \text{s}.$

- $T_g = (T_g/T_b) \cdot T_b = \text{CP time} = 22.4 \ \mu\text{s}.$

- $T_s = T_b + T_g = \text{OFDM symbol time} = 201.9 \ \mu \text{s}.$

- $1/F_s$ = sample time = 87.5657 ns.

#### 2.1.4 Downlink Carrier Allocation

Since we focus on downlink pilot-symbol-aided channel estimation in this thesis, it is necessary to understand what the allocation of carriers is.

#### 2.1.4.1 Pilot Allocation

The carriers allocation in a DL OFDM symbol is shown in Fig. 2.2. Null carriers are allocated in the left and right sides as well as at DC. The pilot and data carriers are termed useful carriers since they transmit useful information. The pilot tones are allocated first, and the remainder of the used carriers are divided into 32 subchannels, and then the data carriers are allocated within each subchannel.

Figure 2.2: Illustration of carrier usage in OFDMA DL (from [3]).

The pilot carriers include fixed-location pilots and variable-location pilots. The carrier indices of fixed-location pilots never change. The carrier indices of the variable-location pilots vary according to the formula  $varLocPilot_k = 3L + 12P_k$ , where  $varLocPilot_k$  is the carrier index of a variable-location pilot, L is the symbol index that cycles through the values 0,2,1,3 periodically every 4-symbol period, and  $P_k = \{0, 1, 2, ...., 141\}$ . The pilot carriers allocation map is shown in Fig. 2.3.

Figure 2.3: Pilot allocation in the OFDMA DL (from [2]).

#### 2.1.4.2 Data Carrier Allocation

After inserting the pilots, the remaining space is for the useful carriers from the data subchannels. To allocate data subchannels, we partition the remaining carriers into groups of contiguous carriers. Each subchannel consists of one carrier from each of these groups respectively. The number of carriers in a subchannel is therefore equal to the number of groups, and it is denoted  $N_{subcarriers}$ . The number of carrier groups is equal to the number of channels, and it is denoted  $N_{subchannels}$ . The total number of data carriers is thus equal to  $N_{subcarriers} \times N_{subchannels}$ .

The exact partitioning into subchannels is according to the following equation called a permutation formula:

$$carrier(n,s) = (N_{subchannels}) \cdot n + \{p_s[n_{mod(N_{subchannels})}] + ID_{cell} \cdot ceil[(n+1)/N_{subchannels}]\}_{(mod(N_{subchannels}))}$$

(2.1)

where:

- 1896

- carrier(n, s) = carrier index of carrier n in subchannel s.

- $s = \text{index number of a subchannel, from the set } [0, \dots, N_{subchannels} 1].$

- $n = \text{carrier-in-subchannel index from the set } [0, \dots, N_{subcarriers} 1].$

- $N_{subchannels} = \text{number of subchannels}$ .

- $p_s[j]$  = the series obtained by rotating { $PermutationBase_0$ }, which is given in the Table 2.1, cyclically to the left s times.

- ceil[] = ceiling function which rounds its argument up to the next integer.

- $ID_{cell}$  = a positive integer assigned by the MAC to identify this particular base-station cell.

- $X_{mod(k)}$  = the remainder of the quotient X/k, which is at most k-1.

Table 2.1: Carrier Allocation in the OFDMA DL (from [2])

| Parameter                                                                    | Value                                                                                                                                                                     |

|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of de carriers                                                        | 1                                                                                                                                                                         |

| Number of guard carriers, left                                               | 173                                                                                                                                                                       |

| Number of guard carriers, right                                              | 172                                                                                                                                                                       |

| $N_{used}$ , Number of used carriers                                         | 1702                                                                                                                                                                      |

| Total number of carriers                                                     | 2048                                                                                                                                                                      |

| $N_{varLocPilots}$                                                           | 142                                                                                                                                                                       |

| Number of fixed-location pilots                                              | 32                                                                                                                                                                        |

| Number of variable-location pilots which coincide with fixed-location pilots | 8                                                                                                                                                                         |

| Total number of pilots <sup>a</sup>                                          | 166                                                                                                                                                                       |

| Number of data carriers                                                      | 1536                                                                                                                                                                      |

| $N_{\it subchannels}$                                                        | 32                                                                                                                                                                        |

| $N_{subcarriers}$                                                            | 48                                                                                                                                                                        |

| Number of data carriers per subchannel                                       | 48                                                                                                                                                                        |

| BasicFixedLocationPilots                                                     | {0,39, 261, 330, 342, 351, 522, 636, 645, 651, 708, 726, 756, 792, 849, 855, 918, 1017, 1143, 1155, 1158, 1185, 1206, 1260, 1407, 1419,1428, 1461, 1530,1545, 1572, 1701} |

| $\{PermutationBase_0\}$                                                      | {3, 18, 2, 8, 16, 10, 11, 15, 26, 22, 6, 9, 27, 20, 25, 1, 29, 7, 21, 5, 28, 31, 23, 17, 4, 24, 0, 13, 12, 19, 14, 30}                                                    |

<sup>&</sup>lt;sup>a</sup>Variable Location Pilots which coincide with Fixed-location Pilots are counted only once in this value.

The numerical parameters are given in Table 2.1.

#### 2.1.5 Data Modulation and Pilot Modulation

#### 2.1.5.1 Data Modulation

The data modulation schemes in 802.16a are shown in Fig. 2.4. The data bits are entered serially to the constellation mapper. Gray-mapped QPSK and 16-QAM must be supported, whereas the support of 64-QAM is optional.

Figure 2.4: QPSK, 16-QAM and 64-QAM constellations (from [2]).

#### 2.1.5.2 Pilot Modulation

Pilot carriers are inserted into each data burst in order to constitute the symbol and they are modulated according to their carrier locations within the OFDMA symbol. A PRBS (pseudo-random binary sequence) generator is used to produce a sequence  $w_k$  where k corresponds to the carrier index. The value of the pilot modulation on carrier k is then derived from  $w_k$ . The polynomial for the PRBS generator is  $X^{11} + X^9 + 1$ , as shown in Fig. 2.5.

Symbols in the TDD OFDMA system DL transmission can be separated into two different types. The first three symbols are preamble symbols, and other symbols are normal symbols. The initialization vector of the PRBS in the DL normal symbols is [1111111111], while the initialization vector of the PRBS in the DL preamble symbol is [01010101010]. The PRBS shall be initialized so that its first output bit coincides with the first usable carrier. A new value shall be generated by the PRBS on every usable carrier. Each pilot shall be transmitted with a boosting of 2.5 dB

Figure 2.5: Pseudo random binary sequence (PRBS) generator for pilot modulation (from [2]).

over the average power of each data tone. The pilot carriers shall be modulated as

$$Re\{c_k\} = \frac{8}{3}(\frac{1}{2} - w_k), Im\{c_k\} = 0.$$

(2.2)

#### 2.2 DL Channel Estimation Methods

Interpolation plays an significant role in pilot-symbol-aided channel estimation. Our interpolation schemes work in both frequency and the time domains. Linear and second-order interpolation are applied in the frequency domain, while 2-D interpolation and LMS (least mean square adaptation) optimize their performance in the time domain.

#### 2.2.1 Pilot-Symbol-Aided Channel Estimation

Channel estimators usually need some kind of pilot information as a point of reference. A fading channel requires constant tracking, so pilot information has to be transmitted more or less continuously. Decision-directed channel estimation can also be used. But even in these types of schemes, pilot information has to be transmitted regularly to mitigate error propagation [4].

In general, the fading channel can be viewed as a two-dimensional (2-D) signal

(time and frequency), which is sampled at pilot positions and the channel coefficients between pilots may be estimated by interpolation.

Based on a priori known data, we can estimate the channel information on pilot carriers roughly by the least-square (LS) or the minimum mean square error (MMSE) estimator. An LS estimator minimizes the following squared error [5]:

$$||\mathbf{Y} - \hat{\mathbf{H}}_{LS}\mathbf{X}||^2 \tag{2.3}$$

where  $\mathbf{Y}$  is the received signal and  $\mathbf{X}$  is a priori known pilots, both in the frequency domain and both being  $N \times 1$  vectors where N is the OFDM FFT size.  $\hat{\mathbf{H}}_{LS}$  is an  $N \times N$  matrix whose values are 0 except at pilot locations  $m_i$  where  $i = 0, \dots, N_p-1$ :

$$\hat{\mathbf{H}}_{LS} = \begin{bmatrix} H_{m_0,m_0} & \cdots & 0 & \cdots & 0 & \cdots & 0 \\ 0 & \cdots & H_{m_1,m_1} & \cdots & 0 & \cdots & 0 \\ 0 & \cdots & 0 & \cdots & H_{m_2,m_2} & \cdots & 0 \\ 0 & \cdots & 0 & \cdots & 0 & \cdots & 0 \\ 0 & \cdots & 0 & \cdots & 0 & \cdots & H_{m_{N_p-1},H_{m_{N_p-1}}} \end{bmatrix}. \tag{2.4}$$

Therefore, (2.3) can be rewritten as

be rewritten as

$$[Y(m) - \hat{H}_{LS}(m)X(m)]^2, \text{ for all } m = m_i. \tag{2.5}$$

Then the estimate of pilot signals, based on one observed OFDM symbol, is given by

$$\hat{H}_{LS}(m) = \frac{Y(m)}{X(m)} = \frac{X(m)H(m) + N(m)}{X(m)} = H(m) + \frac{N(m)}{X(m)}$$

(2.6)

where N(m) is the complex white Gaussian noise on subcarrier m. We collect  $H_{LS}(m)$  into  $\hat{\mathbf{H}}_{\mathbf{p},\mathbf{LS}}$ , an  $N_p \times 1$  vector where  $N_p$  is the total number of pilots, as

$$\mathbf{\hat{H}}_{p,LS} = [H_{p,LS}(0) \ H_{p,LS}(1) \ \cdots H_{p,LS}(N_p - 1)]^T

= \mathbf{X}_p^{-1} \mathbf{Y}_p$$

$$= [\frac{Y_p(0)}{X_p(0)}, \frac{Y_p(1)}{X_p(1)}, \dots, \frac{Y_p(N_p - 1)}{X_p(N_p - 1)}]^T,$$

(2.7)

where  $\mathbf{X}_p$  and  $\mathbf{Y}_p$  are the collections of the transmitted and the received signal on the pilot subcarriers respectively. The LS estimate of  $\mathbf{H}_p$  based on one OFDM symbol only is susceptible to Gaussian noise, and thus an estimator better than the LS estimator is preferable.

The minimum mean-square error (MMSE) estimate has been shown to be better than the LS estimate for channel estimation in OFDM systems, but the major drawback of the MMSE estimate is its high complexity. A low-rank approximation results in a linear minimum mean squared error (LMMSE) estimator that uses the frequency-domain correlation of the channel [6]. The mathematical representation for the LMMSE estimator of pilot signals is

$$\hat{\mathbf{H}}_{p,lmmse} = \mathbf{R}_{H_pH_{p,LS}}\mathbf{R}_{H_{p,LS}H_{p,LS}}^{-1}\hat{\mathbf{H}}_{p,LS}$$

$$= \mathbf{R}_{H_pH_p}(\mathbf{R}_{H_pH_p} + \sigma_n^2(\mathbf{X}_p\mathbf{X}_p^H)^{-1})^{-1}\hat{\mathbf{H}}_{p,LS} \tag{2.8}$$

where  $\hat{\mathbf{H}}_{p,LS}$  is the least-square estimate of  $\mathbf{H}_p$  in (2.7),  $\sigma_n^2$  is the variance of the Gaussian white noise, and the covariance matrices are defined by

$$\mathbf{R}_{H_p H_{p,LS}} = E\{\mathbf{H}_p \mathbf{H}_{p,LS}^H\}, \tag{2.9}$$

$$\mathbf{R}_{H_{p}H_{p,LS}} = E\{\mathbf{H}_{p}\mathbf{H}_{p,LS}^{H}\}, \qquad (2.9)$$

$$\mathbf{R}_{H_{p,LS}H_{p,LS}} = E\{\mathbf{H}_{p,LS}\mathbf{H}_{p,LS}^{H}\}, \qquad (2.10)$$

$$\mathbf{R}_{H_p H_p} = E\{\mathbf{H}_p \mathbf{H}_p^H\}. \tag{2.11}$$

Note that there is a matrix inverse involved in the MMSE estimator, which must be calculated every time, and the computation of matrix inversion requires  $O(N_n^3)$ arithmetic operations [7]. We also need to use the statistical properties of the unknown channel. Therefore, we use the LS estimator which requires only  $O(N_p)$ operations instead of the LMMSE due to the concerns of complexity and unknown information.

#### 2.2.2Frequency Domain Interpolation Methods

#### 2.2.2.1Linear Interpolation

Linear interpolation is a commonly used method of interpolation. It does the interpolation simply with two known data, and interpolates those unknown data between them. It is given by [8]

$$H_e(k) = H_e(m+l) = (H_p(m+1) - H_p(m))\frac{l}{L} + H_p(m)$$

(2.12)

where  $H_p(k)$ ,  $k = 0, 1, \dots, N_p$ , are the channel frequency responses at pilot subcarriers, L is the distance between the two given data, that is, the pilot sub-carriers spacing, and  $0 \le l < L$ .

#### 2.2.2.2 Second-Order Interpolation

Theoretically, using higher-order polynomial interpolation may fit the channel response better than linear interpolation [9]. However, the computational complexity grows as the order is increased. Here we consider the second order polynomial interpolation, and it has also been called Gaussian second order estimation. It is given as a solution to the second order polynomial with respect to l/L by using three reference signal points. The interpolation is obtained using three successive pilot subcarriers signal as follows [10]:

$$H_e(k) = H_e(m+l)$$

=  $c_1 H_p(m-1) + c_0 H_p(m) + c_{-1} H_p(m+1)$  (2.13)

where

$$\begin{cases}

c_1 = \frac{\alpha(\alpha - 1)}{2}, \\

c_0 = -(\alpha - 1)(\alpha + 1), \\

c_{-1} = \frac{\alpha(\alpha + 1)}{2}, \\

\alpha = \frac{l}{l}.

\end{cases}$$

The notations are the same as they are in linear interpolation.

Figure 2.6: Illustration of 2D interpolation.

#### 2.2.3 Time Domain Improvement Methods

As Table 2.1 shows, we can only use 166 pilots in one symbol to interpolate the channel in the frequency domain. It is not sufficient because the pilot spacings are too wide in our system. Since the channel does not change abruptly over time, here we propose two methods to improve the performance.

#### 2.2.3.1 Two-Dimensional Interpolation [11]

Recall the downlink variable pilot allocation in IEEE 802.16a in Fig. 2.3. The equation of the allocation formula is

$$varLocPilot_k = 3L + 12P_k (2.14)$$

where:

- $varLocPilot_k = carrier index of a variable-location pilot.$

- $L \in {0, \dots, 3}$  is a function of the symbol index, modulo 4.

- $P_k \in \{0, 1, 2, \cdots, N_{varLocPilots} 1\}.$

Because the positions of the variable location pilots vary with a period of four symbols, we could make use of the four sets of pilot locations to help channel estimation. The maximum number of pilot locations that we can use is

$$(N_{varLocPilots} - N_{CoincidentPilots}) \times 4 + N_{fixLocPilots} = (142 - 8) \times 4 + 32 = 568$$

(2.15)

where  $N_{ConincidentPilots}$  is the number of the variable location pilots which are coincident with the fixed location pilots. For example, we can use extrapolation in the time domain to estimate the channel frequency response at the pilot locations of other symbols. It should work the best when transmitting through a static channel. The method is illustrated in Fig. 2.6.

One possible way of interpolation (extrapolation) is

$$\tilde{h}_{4sets}^{2D-extrap-p}(f) = \frac{1}{2}\tilde{h}_{0}^{p}(f) + \frac{1}{2}\tilde{h}_{-4}^{p}(f)

+ \frac{1}{2}\tilde{h}_{-1}^{p}(f) + \frac{1}{2}\tilde{h}_{-5}^{p}(f)

+ \frac{1}{2}\tilde{h}_{-2}^{p}(f) + \frac{1}{2}\tilde{h}_{-6}^{p}(f)

+ \frac{1}{2}\tilde{h}_{-3}^{p}(f) + \frac{1}{2}\tilde{h}_{-7}^{p}(f)$$

(2.16)

where  $\tilde{h}_{-n}^p(f)$ ,  $n=0,1,\cdots,7$ , are the channel frequency responses at pilot carriers in the *n*th previous symbol. We can use interpolations again in the frequency domain after obtaining  $\tilde{h}^{2D-extrap-p}(f)$ . Since the equivalent number of pilots becomes 568/166 = 3.421 times that of the original case, better estimation is expected.

However, there are seven extra registers needed to store the channel frequency response at pilot carriers. Except for the hardware concern, a fast fading channel might seriously affect the accuracy of the extrapolations in the time domain, because we need to use the information from the seven previous symbols. Thus, an alternative is use less previous symbols, say only 3 or 2. Then the extrapolation

formula becomes

$$\tilde{h}_{3sets}^{2D-extrap-p}(f) = \frac{1}{2}\tilde{h}_{0}^{p}(f) + \frac{1}{2}\tilde{h}_{-4}^{p}(f)

+ \frac{1}{2}\tilde{h}_{-1}^{p}(f) + \frac{1}{2}\tilde{h}_{-5}^{p}(f)

+ \frac{1}{2}\tilde{h}_{-2}^{p}(f) + \frac{1}{2}\tilde{h}_{-6}^{p}(f)$$

(2.17)

and

$$\tilde{h}_{2sets}^{2D-extrap-p}(f) = \frac{1}{2}\tilde{h}_{0}^{p}(f) + \frac{1}{2}\tilde{h}_{-4}^{p}(f)

+ \frac{1}{2}\tilde{h}_{-1}^{p}(f) + \frac{1}{2}\tilde{h}_{-5}^{p}(f),$$

(2.18)

respectively.

When dealing with fading channels, we consider replacing the formulas above with

$$\tilde{h}_{4sets}^{2D-extrap-p}(f) = \tilde{h}_{0}^{p}(f)

+ \frac{5}{4}\tilde{h}_{-1}^{p}(f) - \frac{1}{4}\tilde{h}_{-5}^{p}(f)

+ \frac{3}{2}\tilde{h}_{-2}^{p}(f) - \frac{1}{2}\tilde{h}_{-6}^{p}(f)

+ \frac{7}{4}\tilde{h}_{-3}^{p}(f) - \frac{3}{4}\tilde{h}_{-7}^{p}(f),$$

(2.19)

$$\tilde{h}_{3sets}^{2D-extrap-p}(f) = \tilde{h}_{0}^{p}(f)

+ \frac{5}{4}\tilde{h}_{-1}^{p}(f) - \frac{1}{4}\tilde{h}_{-5}^{p}(f)

+ \frac{3}{2}\tilde{h}_{-2}^{p}(f) - \frac{1}{2}\tilde{h}_{-6}^{p}(f),$$

(2.20)

and

$$\tilde{h}_{2sets}^{2D-extrap-p}(f) = \tilde{h}_{0}^{p}(f)

+ \frac{5}{4}\tilde{h}_{-1}^{p}(f) - \frac{1}{4}\tilde{h}_{-5}^{p}(f),$$

(2.21)

where we emphasize the weighting of  $\tilde{h}_n^p(f)$  n=-1,-2,-3 nearier to  $\tilde{h}_0^p(f)$  in a linear fashion, because when time variation of the channel is not overly fast, the channel coefficients can be modelled to a first-order approximation as varying linearly with time in a short-enough time span.

Figure 2.7: Adaptive channel estimation using the LMS algorithm

#### 2.2.3.2 Least Mean Square (LMS) Adaptation [12], [14]

The LMS algorithm is the most widely used adaptive filtering algorithm in practice for its simplicity. Meanwhile, it is stable and robust against different channel conditions.

The LMS channel estimation process is illustrated in Fig. 2.7, where X(f) is the input signal sent into the channel, H(f) is channel frequency response, and Y(f) is the channel output. The following equations apply to our work where  $\mathbf{H}_{LMS}^n(f)$  is the estimated channel response at the *n*th symbol.

• Filtering by channel:

$$y(n) = h(n) * x(n), \tag{2.22}$$

$$\mathbf{Y}(f) = \mathbf{H}(f) \cdot \mathbf{X}(f). \tag{2.23}$$

• Estimated error:

$$\mathbf{e}(f) = \hat{\mathbf{X}}_{after\_decision}(f) - \hat{\mathbf{X}}(f), \tag{2.24}$$

$$\hat{\mathbf{X}}(f) = \frac{\mathbf{Y}(f)}{\mathbf{H}_{LMS}^{n}(f)}.$$

(2.25)

• Cost function:

$$\hat{\xi}(f) = \mathbf{e}^2(f) = |\hat{\mathbf{X}}_{after\_decision}(f) - \hat{\mathbf{X}}(f)|^2.$$

(2.26)

• Channel frequency response adaptation:

$$\mathbf{H}_{LMS}^{n+1}(f) = \mathbf{H}_{LMS}^{n}(f) + \mu \mathbf{e}^{*}(f)\hat{\mathbf{X}}(f), \tag{2.27}$$

where  $\mu$  is the step size which affects the speed of convergence. With a larger step size, the estimated channel converges more quickly to the real channel response. However, if it is too big, then it may lead to a unstable condition.

To minimize the error shown in (2.24), we try to minimize the expected value of (2.26). For this, we can tune the estimated channel weights adaptively. In our simulation, we use the interpolated channel estimation  $\tilde{H}_{interp}^0(f)$  as  $\mathbf{H}_{LMS}^0(f)$  and  $\mathbf{H}_{LMS}^n(f)$  is obtained by (2.27) when n > 0. Following the algorithm, only the first symbol's pilot information is used in the whole flow, thus the pilot information in other symbols is wasted. So we try to combine the interpolated channel and the  $\mathbf{H}_{LMS}^n(n)$  which is the estimated channel by using LMS algorithm when n > 0. The combination is given by

$$\tilde{H}_{modified\ LMS}^{n}(f) = \begin{cases} \alpha \cdot \mathbf{H}_{LMS}^{n}(f) + (1 - \alpha) \cdot \tilde{H}_{interp}^{n}(f), & n > 0, \\ \tilde{H}_{interp}^{n}(f), & n = 0, \end{cases}$$

(2.28)

where  $\mathbf{H}_{LMS}^n(f)$  is the channel estimated by the LMS adaptation algorithm and  $\tilde{H}_{interp}^n(f)$  is the channel estimated by interpolation. The  $\alpha$  and the  $(1-\alpha)$  are the weighting factors for  $\mathbf{H}_{LMS}^n(f)$  and  $\tilde{H}_{interp}^n(f)$ , respectively. Therefore,  $\tilde{H}_{modified\ LMS}^n(f)$  is the combination of these two kinds of estimation outcomes and may be more correct. Then, we use  $\tilde{H}_{modified\ LMS}^n(f)$  in place of  $\mathbf{H}_{LMS}^n(f)$  in the right-hand side of (2.27) to calculate the estimated channel response for the next symbol.

# Chapter 3

# **DSP** Introduction

DSP implementation is the final goal of our work. The DSP platform that we use is the Quixote board produced by Innovation Integration. The DSP on the board is TMS320C6416 made by Texas Instruments. In this chapter, we introduce the architectures of the Quixote board and the DSP chip.

# 3.1 Introduction to TMS320C6416 DSP [16]

# 3.1.1 TMS320C6416 Features

The TMS320C64x DSPs are the highest-performance fixed-point DSP generation of the TMS320C6000 DSP devices with a performance of up to 6000 million instructions per second (MIPS) and an efficient C compiler. The TMS320C64x device is based on the second-generation high-performance, very-long-instruction-word (VLIW) architecture developed by Texas Instruments (TI). The C6416 device has two high-performance embedded coprocessors, Viterbi Decoder Coprocessor (VCP) and Turbo Decoder Coprocessor (TCP) that significantly speed up channel-decoding operations on-chip. But they do not apply to the work reported in this thesis.

The C64x core CPU consists of 64 general-purpose 32-bits registers and 8 function units. These 8 function units contain:

- Two multipliers.

- Six ALUs.

#### Features of C6000 devices include:

- Advanced VLIW CPU with eight functional units, including two multipliers and six arithmetic units:

- Executes up to eight instructions per cycle.

- Allows designers to develop highly effective RISC-like code for fast development time.

- Instruction packing:

- Gives code size equivalence for eight instructions executed serially or in parallel.

- Reduces code size, program fetches, and power consumption.

- Conditional execution of all instructions:

- Reduces costly branching.

- Increases parallelism for higher sustained performance.

- Efficient code execution on independent functional units:

- Efficient C compiler on DSP benchmark suite.

- Assembly optimizer for fast development and improved parallelization.

- 8/16/32-bit data support, providing efficient memory support for a variety of applications.

- 40-bit arithmetic options add extra precision for applications requiring it.

- Saturation and normalization provide support for key arithmetic operations.

- Field manipulation and instruction extract, set, clear, and bit counting support common operation found in control and data manipulation applications.

The additional features of C64x include:

- Each multiplier can perform two 16×16 bits or four 8×8 bits multiplies every clock cycle.

- Quad 8-bit and dual 16-bit instruction set extensions with data flow support.

- Support for non-aligned 32-bit (word) and 64-bit (double word) memory accesses.

- Special communication-specific instructions have been added to address common operations in error-correcting codes.

- Bit count and rotate hardware extends support for bit-level algorithms.

# 3.1.2 Central Processing Unit

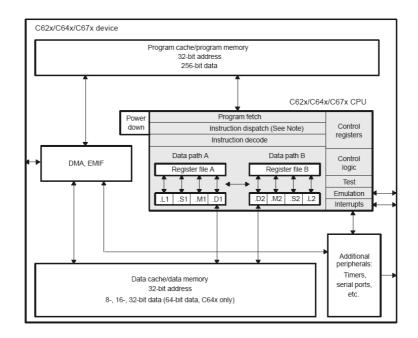

The block diagram of the C6416 DSP is shown in Fig. 3.1. The DSP contains:

- Program fetch unit.

- Instruction dispatch unit.

- Instruction decode unit.

- Two data paths, each with four functional units.

- 64 32-bit registers.

- Control registers.

Figure 3.1: Block diagram of the TMS320C6416 DSP [16].

- Control logic.

- Test, emulation, and interrupt logic.

The TMS320C64x DSP pipeline provides flexibility to simplify programming and improve performance. The pipeline can dispatch eight parallel instructions every cycle. These two factors provide this flexibility:

- Control of the pipeline is simplified by eliminating pipeline interlocks.

- Increased pipelining eliminates traditional architectural bottlenecks in program fetch, data access, and multiply operations. This provides single cycle throughput.

#### **3.1.2.1** Pipeline

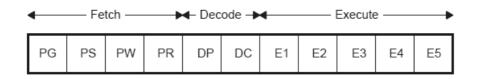

The pipeline phases are divided into three stages as shown in Fig. 3.2:

• Fetch has 4 phases:

Figure 3.2: Pipeline phases of TMS320C6416 DSP [16].

- PG (program address generate): The address of the fetch packet is determined.

- PS (program address send): The address of the fetch packet is sent to memory.

- PW (program access ready wait): A program memory access is performed.

- PR (program fetch packet receive): The fatch packet is at the CPU boundary.

### • Decode has two phases:

- DP (instruction dispatch): The next execute packet in the fetch packet is determined and sent to the appropriate functional units to be decoded.

- DC (instruction decode): Instructions are decoded in functional units.

#### • Execute has five phases:

- E1: Execute 1.

- E2: Execute 2.

- E3: Execute 3.

- E4: Execute 4.

- E5: Execute 5.

The pipeline operation of the C62x/C64x instructions can be categorized into seven instruction types. Six of these are shown in Table 3.1, which gives a mapping of operations occurring in each execution phase for the different instruction types. The delay slots associated with each instruction type are listed in the bottom row.

The execution of instructions can be defined in terms of delay slots. A delay slot is a CPU cycle that occurs after the first execution phase (E1) of an instruction. Results from instructions with delay slots are not available until the end of the last delay slot. For example, a multiply instruction has one delay slot, which means that one CPU cycle elapses before the results of the multiply are available for use by a subsequent instruction. However, results are available from other instructions finishing execution during the same CPU cycle in which the multiply is in a delay slot.

Table 3.1: Execution Stage Length Description for Each Instruction Type [16]

|                  |    | Instruction Type                              |                                                             |                                            |                                                    |                                |                           |  |  |  |  |  |

|------------------|----|-----------------------------------------------|-------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|--------------------------------|---------------------------|--|--|--|--|--|

|                  | 3  | Single Cycle                                  | 16 X 16 Single<br>Multiply/<br>C64x .M Unit<br>Non-Multiply | Store                                      | C64x<br>Multiply<br>Extensions                     | Load                           | Branch                    |  |  |  |  |  |

| Execution phases | E1 | Compute<br>result<br>and write to<br>register | Read operands<br>and start<br>computations                  | Compute address                            | Reads oper-<br>ands and<br>start com-<br>putations | Compute address                | Target-<br>code<br>in PG‡ |  |  |  |  |  |

|                  | E2 |                                               | Compute result<br>and write to<br>register                  | Send ad-<br>dress and<br>data to<br>memory |                                                    | Send ad-<br>dress to<br>memory |                           |  |  |  |  |  |

|                  | E3 |                                               |                                                             | Access<br>memory                           |                                                    | Access<br>memory               |                           |  |  |  |  |  |

|                  | E4 |                                               |                                                             |                                            | Write results to register                          | Send data back to CPU          |                           |  |  |  |  |  |

|                  | E5 |                                               |                                                             |                                            |                                                    | Write data into register       |                           |  |  |  |  |  |

| Delay<br>slots   |    | 0                                             | 1                                                           | 0†                                         | 3                                                  | 4†                             | 5‡                        |  |  |  |  |  |

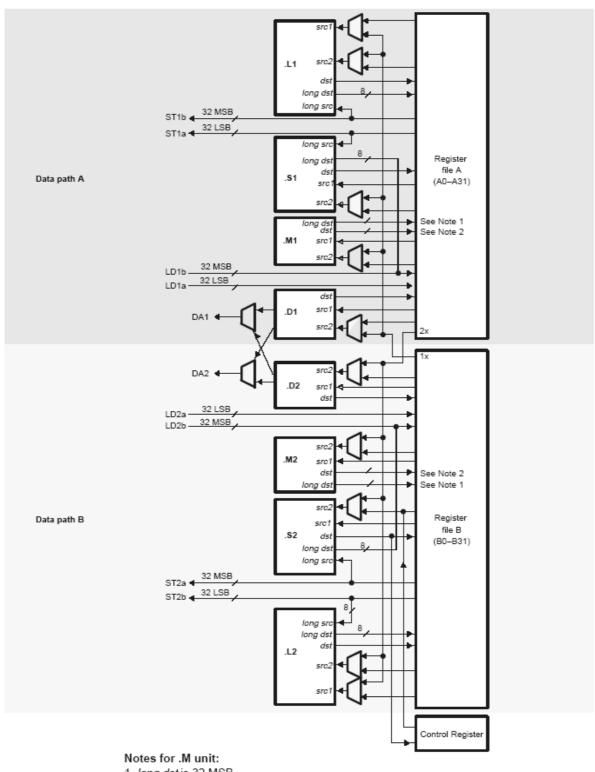

#### 3.1.2.2 Functional Units

The eight functional units in the C6000 data paths can be divided into two groups of four; each functional unit in one data path is almost identical to the corresponding unit in the other data path. The functional units are described in Table 3.2. Besides being able to perform 32-bit operations, the C64x also contains many 8-bit to 16-bit extensions to the instruction set. For example, the MPYU4 instruction performs four 8×8 unsigned multiplies with a single instruction on an .M unit. The ADD4 instruction performs four 8-bit additions with a single instruction on an .L unit.

The data line in the CPU supports 32-bit operands, long (40-bit) and double word (64-bit) operands. Each functional unit has its own 32-bit write port into a general-purpose register file (listed in Fig. 3.3). All units ending in 1 (for example, L1) write to register file A, and all units ending in 2 write to register file B. Each functional unit has two 32-bit read ports for source operands src1 and src2. Four units (L1, L2, S1, and S2) have an extra 8-bit-wide port for 40-bit long writes, as well as an 8-bit input for 40-bit long reads. Because each unit has its own 32-bit write port, when performing 32-bit operations all eight units can be used in parallel every cycle.

# 3.1.3 Memory Architecture

The C64x has a 32-bit, byte-addressable address space. Internal (on-chip) memory is organized in separate data and program spaces. When off-chip memory is used, these spaces are unified on most devices to a single memory space via the external memory interface (EMIF). The C64x has two 64-bit internal ports to access internal data memory have and a single internal port to access internal program memory, with an instruction-fetch width of 256 bits.

A variety of memory options are available for the C6000 platform. In our system,

Table 3.2: Functional Units and Operations Performed [16]

| Function Unit      | Operations                                                    |  |  |  |  |  |  |

|--------------------|---------------------------------------------------------------|--|--|--|--|--|--|

| L unit (.L1, .L2)  | 32/40-bit arithmetic and compare operations                   |  |  |  |  |  |  |

|                    | 32-bit logical operations                                     |  |  |  |  |  |  |

|                    | Leftmost 1 or 0 counting for 32 bits                          |  |  |  |  |  |  |

|                    | Normalization count for 32 and 40 bits                        |  |  |  |  |  |  |

|                    | Byte shifts                                                   |  |  |  |  |  |  |

|                    | Data packing/unpacking                                        |  |  |  |  |  |  |

|                    | 5-bit constant generation                                     |  |  |  |  |  |  |

|                    | Dual 16-bit arithmetic operations                             |  |  |  |  |  |  |

|                    | Quad 8-bit arithmetic operations                              |  |  |  |  |  |  |

|                    | Dual 16-bit min/max operations                                |  |  |  |  |  |  |

|                    | Quad 8-bit min/max operations                                 |  |  |  |  |  |  |

| .S unit (.S1, .S2) | 32-bit arithmetic operations                                  |  |  |  |  |  |  |

|                    | 32/40-bit shifts and 32-bit bit-field operations              |  |  |  |  |  |  |

|                    | 32-bit logical operations                                     |  |  |  |  |  |  |

|                    | Branches                                                      |  |  |  |  |  |  |

|                    | Constant generation                                           |  |  |  |  |  |  |

|                    | Register transfers to/from control register file (.S2 only)   |  |  |  |  |  |  |

|                    | Byte shifts                                                   |  |  |  |  |  |  |

|                    | Data packing/unpacking                                        |  |  |  |  |  |  |

|                    | Dual 16-bit compare operations                                |  |  |  |  |  |  |

|                    | Quad 8-bit compare operations                                 |  |  |  |  |  |  |

|                    | Dual 16-bit shift operations                                  |  |  |  |  |  |  |

|                    | Dual 16-bit saturated arithmetic operations                   |  |  |  |  |  |  |

|                    | Quad 8-bit saturated arithmetic operations                    |  |  |  |  |  |  |

| .M unit (.M1, .M2) | 16 x 16 multiply operations                                   |  |  |  |  |  |  |

|                    | 16 x 32 multiply operations                                   |  |  |  |  |  |  |

|                    | Quad 8 x 8 multiply operations                                |  |  |  |  |  |  |

|                    | Dual 16 x 16 multiply operations                              |  |  |  |  |  |  |

|                    | Dual 16 x 16 multiply with add/subtract operations            |  |  |  |  |  |  |

|                    | Quad 8 x 8 multiply with add operation                        |  |  |  |  |  |  |

|                    | Bit expansion                                                 |  |  |  |  |  |  |

|                    | Bit interleaving/de-interleaving                              |  |  |  |  |  |  |

|                    | Variable shift operations                                     |  |  |  |  |  |  |

|                    | Rotation                                                      |  |  |  |  |  |  |

| D (D1 D2)          | Galois Field Multiply                                         |  |  |  |  |  |  |

| .D unit (.D1, .D2) | 32-bit add, subtract, linear and circular address calculation |  |  |  |  |  |  |

|                    | Loads and stores with 5-bit constant offset                   |  |  |  |  |  |  |

|                    | Loads and stores with 15-bit constant offset (.D2 only)       |  |  |  |  |  |  |

|                    | Load and store double words with 5-bit constant               |  |  |  |  |  |  |

|                    | Load and store non-aligned words and double words             |  |  |  |  |  |  |

|                    | 5-bit constant generation                                     |  |  |  |  |  |  |

|                    | 32-bit logical operations                                     |  |  |  |  |  |  |

1. long dst is 32 MSB 2. dst is 32 LSB

Figure 3.3: TMS320C64x CPU data path [16].

the memory types we can use are:

- On-chip RAM, up to 875 MB.

- Program cache.

- 32-bit external memory interface supports SDRAM, SBSRAM, SRAM, and other asynchronous memories.

- Two-level caches [20]. Level 1 cache is split into program (L1P) and data (L1D) cache. Each L1 cache is 16 KB. Level 2 memory is configurable and can be split into L2 SRAM (addressable on-chip memory) and L2 cache for caching external memory locations. The size of L2 is 1 MB. External memory can be several MB large. The access time depends on the memory technology used but is typically around 100 to 133 MHz. In our system, the external memory usable by DSP is a 32 MB SDRAM.

# 3.2 Introduction to the Quixote cPCI Board [15]

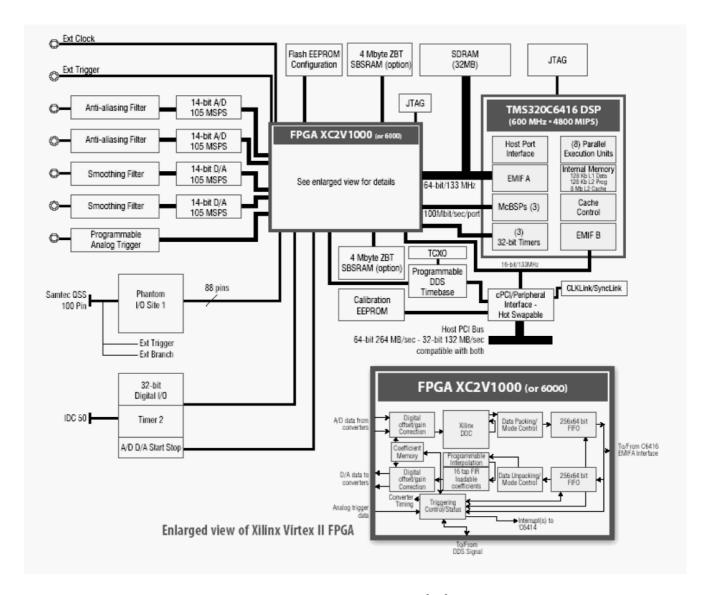

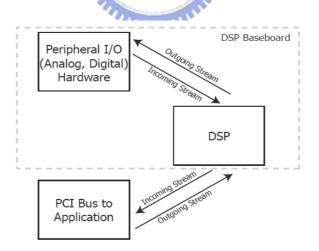

The Quixote is one of Innovative Integration's Velocia-family baseboard for applications requiring speed and processing power. Quixote features a processing core built around Texas Instruments' fixed-point TMS320C6416 and Xilinx Virtex2 with 32 MB of DSP RAM and 2 MB of FPGA computation RAM (optional). The TI C6416 DSP operating at 600 MHz offers a processing power of 4800 MIPS. The analog IO features of the board include dual channels of 105 MHz A/D and D/A (2 in, 2 out). A block diagram of Quixote board is shown in Fig. 3.4.

The Quixote card has a 32 MB SDRAM for use by the DSP. When used with the advanced cache controller on the 'C6416, the SDRAM provides a large, fast external memory pool for DSP data and code. The Quixote has a serial EEPROM for storing data such as board identification, calibration coefficients, and other data that needs

Figure 3.4: Block diagram of Quixote [15].

to be stored permanently on the card. This memory is 16K bits in size. Functions for using the serial EEPROM are included in the Pismo Toolset that allow the software application programmer to easily write and read from the memory without controlling the low-level interface.

The Caliente subsystem handles the details of interacting with the baseboard in streaming mode. There are 3 ways for data transmission between host PC and DSP: data streaming, block mode data streams and message packet I/O.