# 國立交通大學

# 電子工程學系 電子研究所

博士論文

先進材料應用於低溫複晶矽薄膜電晶體之研究

1896

A Study of Low-Temperature Polycrystalline Silicon Thin Film

Transistors Using Advanced Materials

研 究 生:楊明瑞

指導教授:簡昭欣 博士

黄調元 博士

中華民國 九十七 年 十二 月

## 先進材料應用於低溫複晶矽薄膜電晶體之研究

# A Study of Low-Temperature Polycrystalline Silicon Thin Film Transistors Using Advanced Materials

研究生:楊明瑞 Student: Ming-Jui Yang

指導教授: 簡昭欣 博士 Advisors: Dr. Chao-Hsin Chien

Dr. Tiao-Yuan Huang

黄調元 博士

#### A Dissertation

Submitted to Department of Electronics Engineering and

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy

in

**Electronics Engineering**

December 2008 Hsinchu, Taiwan, Republic of China

中華民國 九十七 年 十二 月

## 先進材料應用於低溫複晶矽薄膜電晶體之研究

研究生: 楊明瑞 指導教授: 簡昭欣 博士

黄調元 博士

### 國立交通大學

#### 電子工程學系暨電子研究所

### 摘要

在本論文中,我們利用了先進的高介電常數材料來製造高效能的低溫複晶矽 薄膜電晶體。研究成果著重於探討利用新穎的分子氣相沉積(AVD)系統所成長出高 介電薄膜的特性,並且利用此種新研發的薄膜來改善複晶矽薄膜電晶體的運作性 能,最後並探討了這些高介電薄膜電晶體的可靠度。

首先,我們利用了一種新的分子氣相沉積系統來成長先進的高介電薄膜。在文章中,我們有系統地研究討論有關於各種參數對沉積薄膜的影響,其中包含了沉積溫度、腔體壓力、氧氣流量、注射頻率、以及薄膜成分調整等。而高溫的退火處理也被用來測試此高介電薄膜的熱穩定性。我們發現,要利用此種分子氣相沉積系統獲得高品質和化學當量比的高介電薄膜,較高的沉積溫度和充足的氧氣流量乃是必要的條件。在研究中,我們也發現擁有多晶結構的二氧化给(HfO2)薄膜會導致較大的漏電流;相對地,矽酸给(HfSiOx)薄膜則表現出比較優異的熱穩定度,在高溫退火處理後仍維持其非晶狀態的結構。當然,較二氧化給薄膜低的介電常數,則為矽酸給薄膜的缺點。另外,具有較低介電常數的介面層自然形成於高介電薄膜和矽基板之間,將會導致等效氧化層厚度降低的問題。

接著,我們嘗試將此新開發的高介電薄膜應用在低溫複晶矽薄膜電晶體上。在這個部份,我們首先探討較厚高介電薄膜的結構和電性;接著,我們針對使用二氧化鉿和矽酸鉿薄膜當作閘極介電層的低溫 P 型通道複晶矽電晶體作一系列的研究和探討。我們發現因為高介電薄膜具有較大的閘極電容密度,因此以其作為閘極介電層的薄膜電晶體都展現出比使用傳統沉積氧化層的元件較佳的特性,例如較高的開闢電流比、較低的次臨界擺幅、和較低的臨界電壓,除了稍高的關閉狀態的漏電流。其中,使用矽酸鉿薄膜當作閘極介電層的薄膜電晶體,其場效遷移率是使用沉積氧化層的電晶體的 1.76 倍;但是,使用二氧化鉿當作閘極介電層的元件卻表現出劣化的遷移率。最後,針對通道長度、通道寬度和元件特性的相關性也會在此被討論。

此外,我們更深入地研究有關二氧化給薄膜電晶體遷移率劣化的機制。我們討論了其他發生散射的原因,其中可能是存在於二氧化給薄膜中和二氧化給薄膜與多晶矽通道介面間的缺陷電荷、固定電荷、微弱聲子(soft Phonon)、和薄膜結晶化所造成的。我們也研討了有關使用高介電薄膜當作問極介電層的複晶矽薄膜電晶體所引起的嚴重漏電流現象。我們認為高介電薄膜所產生的較高電場是引發嚴重的開極誘發汲集漏電流(GIDL)的原因,而場發射電流為其主要的漏電流機制。緊接著,我們利用了變溫量測和負電壓溫度不穩定(NBTI)的應力量測方法來測試使用各種不同間極介電層的薄膜電晶體的可靠度;很明顯地,高介電薄膜電晶體展現了相較於傳統使用沉積氧化矽的薄膜電晶體優異的溫度免疫能力。而在這些使用不同高介電薄膜的元件中,使用矽酸給薄膜的電晶體更展現出在負電壓溫度不穩定應力測試下較二氧化給薄膜電晶體優異的容忍度,其中包含了臨界電壓飄移、次臨界擺幅劣化、場效遷移率劣化、以及驅動電流衰退等測試項目。因此我們相信,相較於二氧化給薄膜,矽酸給薄膜將會是較佳的未來高性能複晶矽薄膜電晶體間極介電層材料。

# A Study of Low-Temperature Polycrystalline Silicon Thin Film Transistors Using Advanced Materials

Student: Ming-Jui Yang Advisors: Dr. Chao-Hsin Chien

Dr. Tiao-Yuan Huang

Department of Electronics Engineering and Institute of Electronics

National Chiao-Tung University

### **ABSTRACT**

In this thesis, advanced high- $\kappa$  materials were employed to fabricate high-performance low-temperature polycrystalline silicon thin film transistors (TFTs). Most of the efforts were focused on exploring the deposition of high- $\kappa$  films by the new atomic-vapor deposition (AVD) system, improving the performance of the poly-Si TFTs with newly-developed high- $\kappa$  films, and studying the reliability of these high- $\kappa$  TFTs.

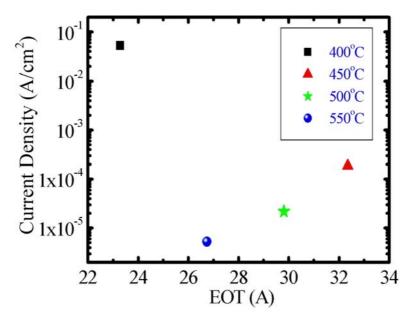

First of all, a new AVD system was employed for the deposition of the advanced high- $\kappa$  materials. The impacts of deposition parameters, including the deposition temperature, chamber pressure, oxygen gas flow, injection frequency, and composition adjustment, were investigated systematically. The thermal stability of high- $\kappa$  films was also tested by high temperature post-deposition annealing (PDA). It was found that higher deposition temperature and sufficient oxygen gas flow are essential to obtain the good quality and stoichiometric high- $\kappa$  films by the AVD system. However, the large leakage current would be caused by the polycrystalline structure of HfO<sub>2</sub> films. In

contrast,  $HfSiO_x$  films exhibit better thermal stability and retain the amorphous structure even after high temperature annealing. Certainly, the lower  $\kappa$  compared with  $HfO_2$  film is the disadvantage of the  $HfSiO_x$  films. Besides, the native interfacial layer with lower  $\kappa$  value always exists between the thin high- $\kappa$  gate dielectric and Si substrate, which defeats the purpose of EOT lowering.

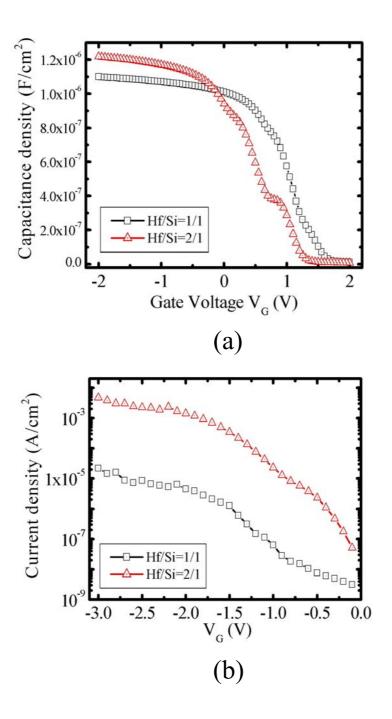

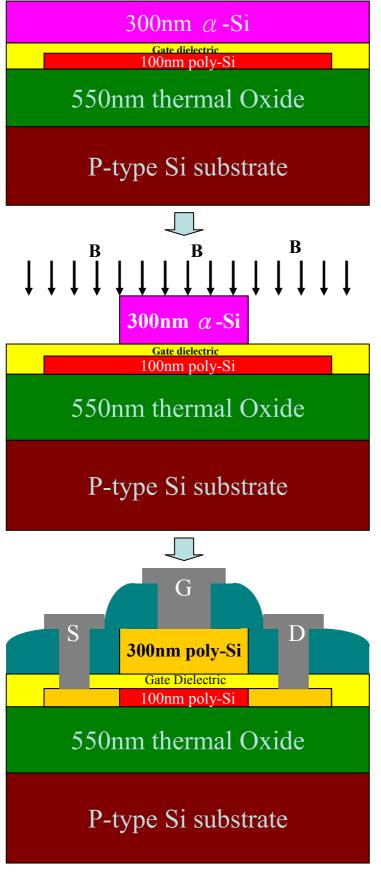

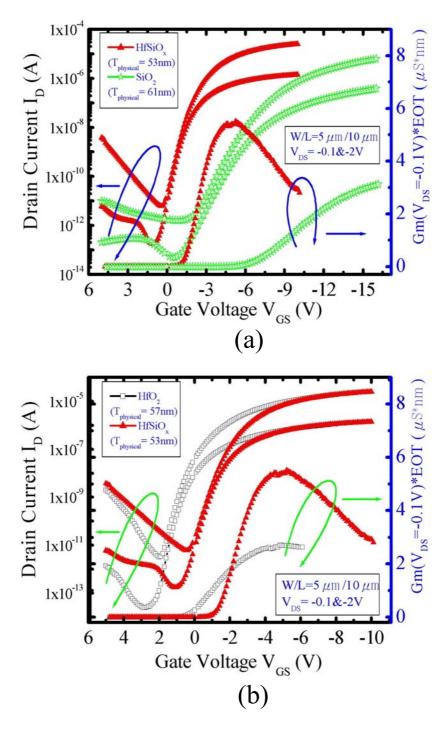

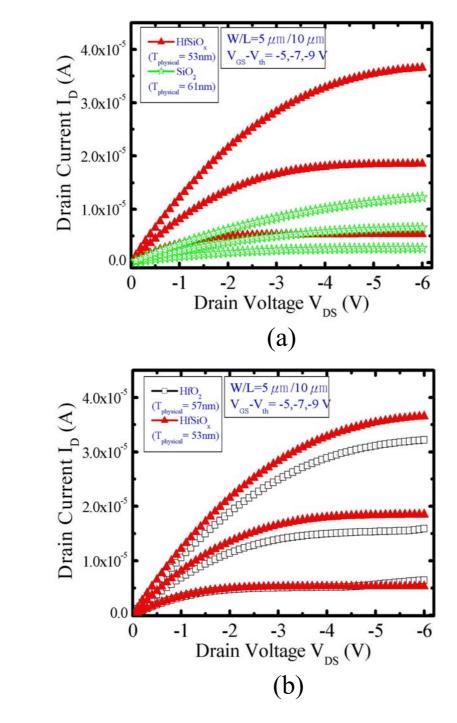

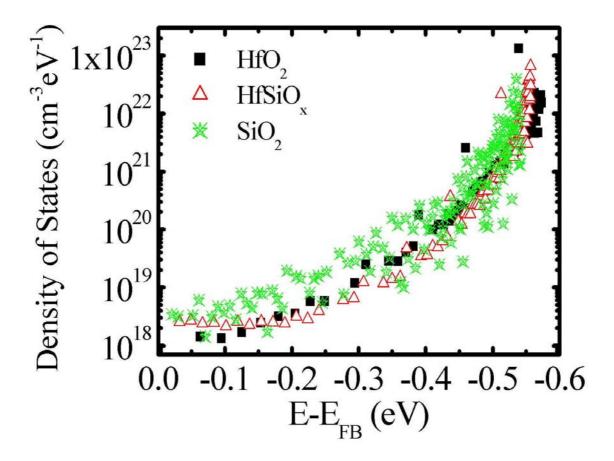

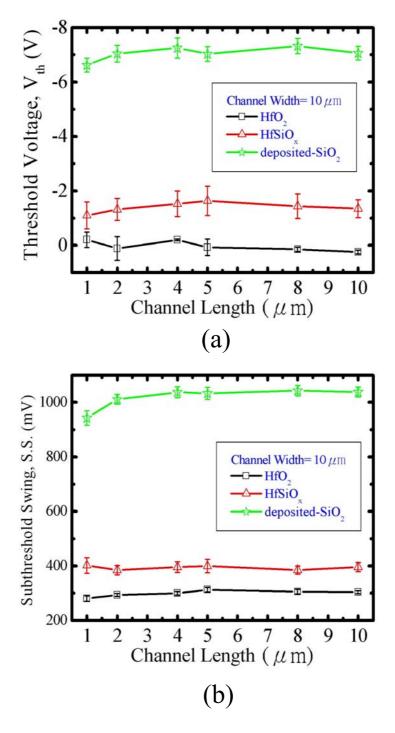

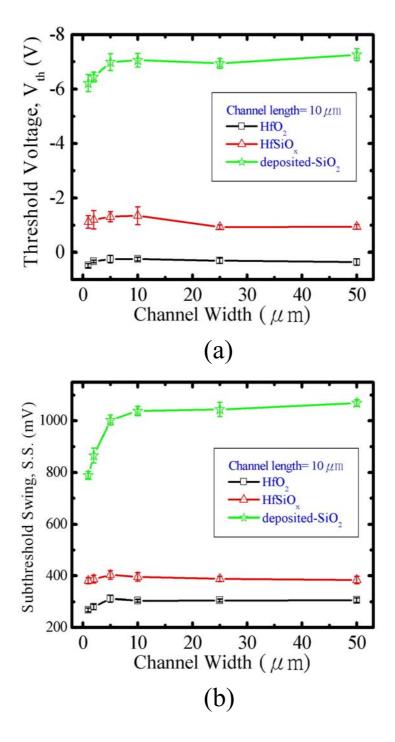

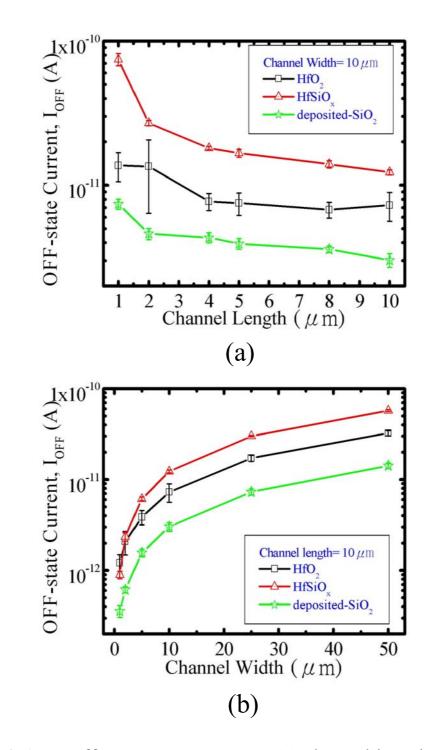

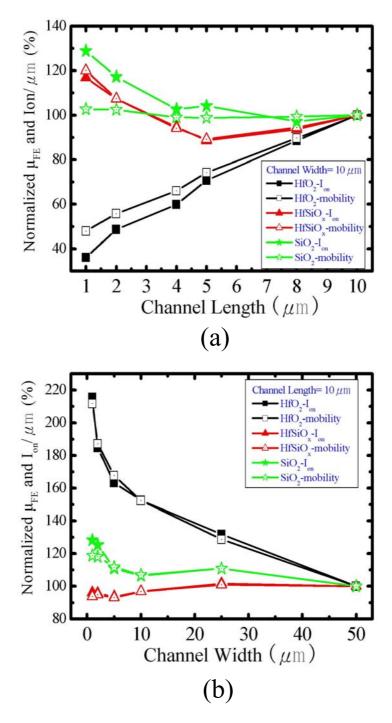

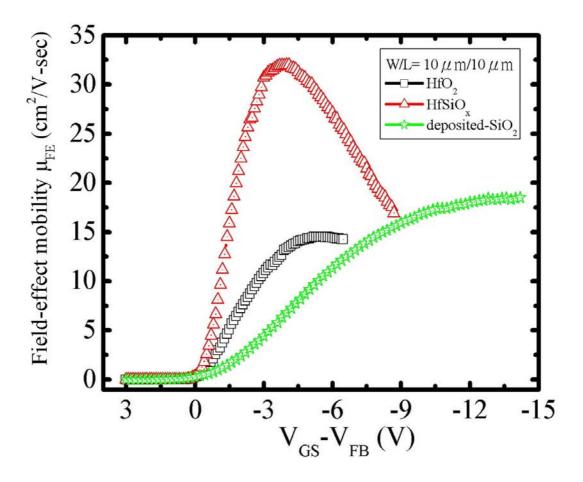

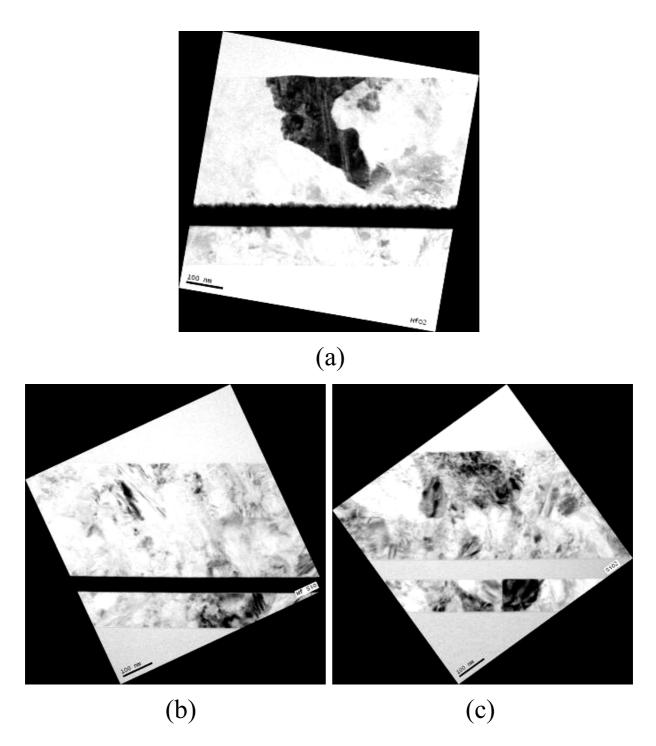

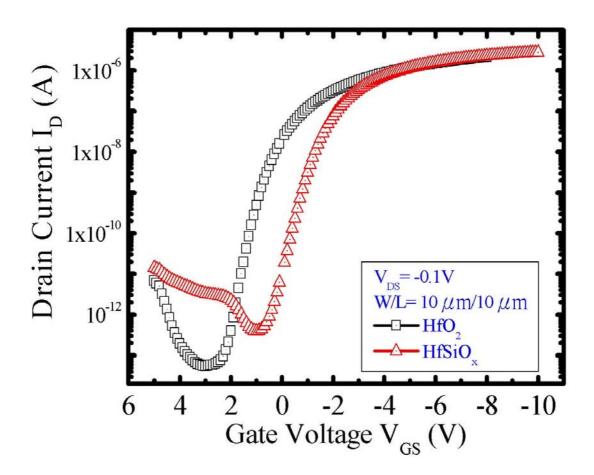

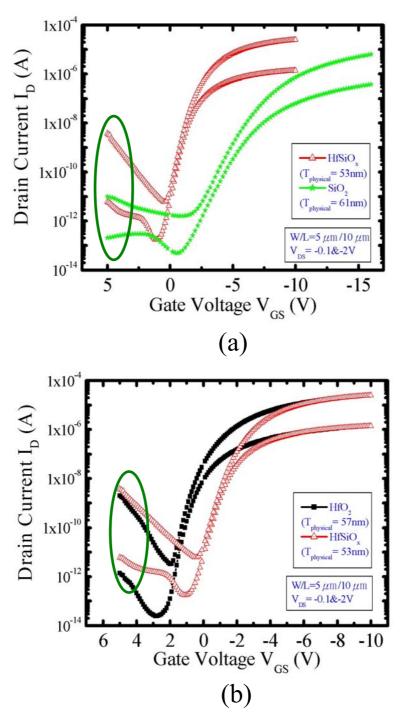

Next, we also tried to apply the newly-developed high- $\kappa$  films to the low-temperature polycrystalline silicon (LTPS) TFTs. In this part, the structural and electrical properties of the thicker high- $\kappa$  films were characterized first. Then, we performed a systematic study on the electrical properties of low-temperature-compatible p-channel poly-Si thin-film transistors (TFTs) using HfO<sub>2</sub> or HfSiO<sub> $\kappa$ </sub> high- $\kappa$  gate dielectric. Because of their higher gate capacitance density, TFTs containing the high- $\kappa$  gate dielectric exhibit superior device performance in terms of higher  $I_{on}/I_{off}$  current ratio, lower subthreshold swing (S.S.), and lower threshold voltage ( $V_{th}$ ), relative to the conventional deposited-SiO<sub>2</sub> counterparts, albeit with slightly higher OFF-state current. TFTs incorporating HfSiO<sub> $\kappa$ </sub> as the gate dielectric has 1.76 times the field-effect mobility ( $\mu_{FE}$ ) relative to that of the deposited-SiO<sub>2</sub> TFTs. In contrast, the HfO<sub>2</sub>-TFTs exhibit inferior mobility. The device performance dependence on the channel length and width of poly-Si TFTs was also discussed.

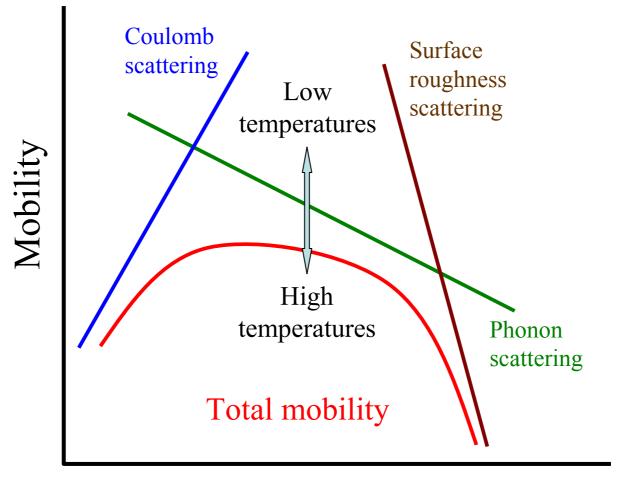

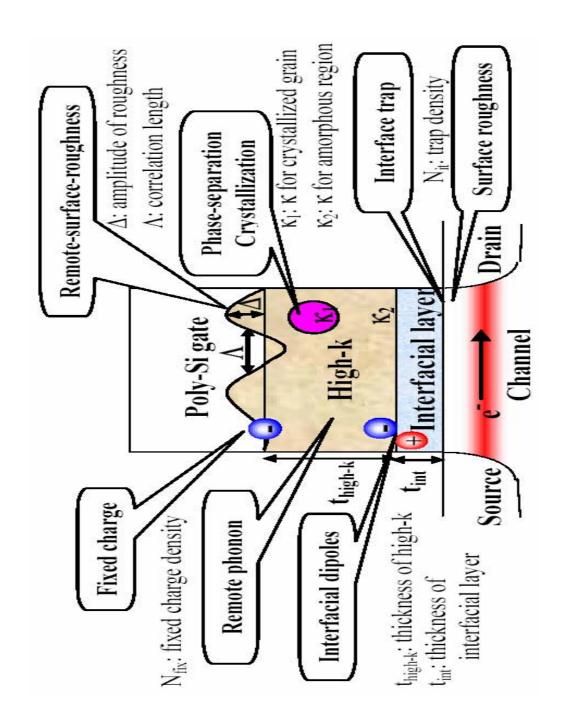

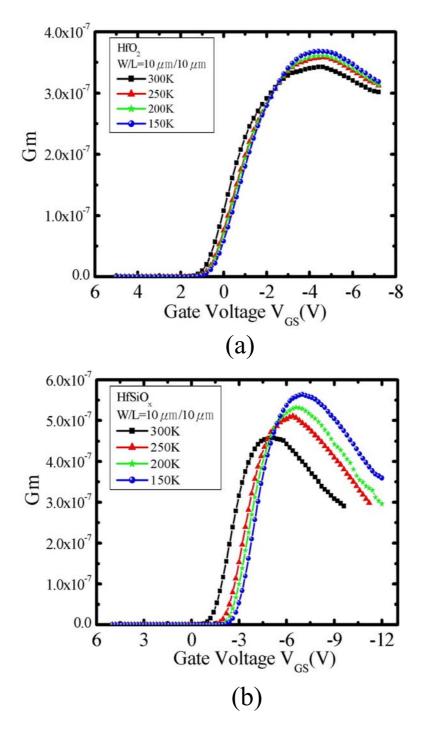

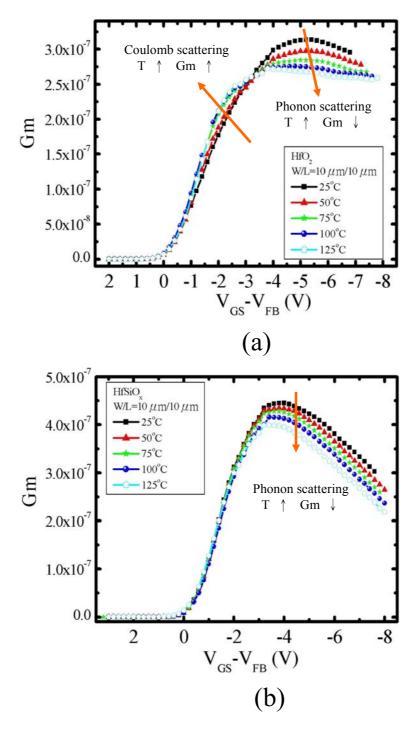

Furthermore, we also carefully investigated the mobility degradation mechanisms in these HfO<sub>2</sub>-TFTs. We discussed possible origins of the additional scatterings, which might be attributed to the trapped charges, fixed charges, soft phonons, and crystallization in the HfO<sub>2</sub> films and HfO<sub>2</sub>/poly-Si channel interface. Moreover, the higher leakage current of poly-Si TFTs using high-κ gate dielectrics was also studied. Aggravated gate-induced drain leakage (GIDL) current was thought to arise from the higher induced electric field by the introduction of high-κ films, and field-emission current would be the dominant leakage mechanism. In addition, the reliabilities of these

TFTs with different gate dielectrics were tested by the varying-temperature measurements and negative bias temperature instability (NBTI) stress. Obviously, the high- $\kappa$  TFTs exhibit better temperature immunity over the conventional TFTs containing the deposited-SiO<sub>2</sub> film. In comparison with the devices using different high- $\kappa$  gate dielectrics, the immunity of HfSiO<sub>x</sub>-TFTs was better than that of HfO<sub>2</sub>-TFTs—in terms of V<sub>th</sub> shift, SS degradation,  $\mu_{FE}$  degradation, and drive current deterioration—against NBTI stressing. Thus, we believe that HfSiO<sub>x</sub>, rather than HfO<sub>2</sub>, is a better candidate as the gate dielectric material for the future high-performance poly-Si TFTs.

## 誌謝

走過五個多年頭,我終於順利畢業了!此時心中五味雜陳,但是最想說出口的就是心中滿滿的感謝。

首先要感謝我的指導教授簡昭欣老師和黃調元老師,兩位老師的叮嚀和不厭其 煩的指導,讓我得以在這深奧的研究領域中,一步一步地向前邁進。黃老師博學 多聞和淡泊名利的學者風範,一直深植在我心中,是我學習的典範。簡博更是我 讀取博士學位路程上的良師益友,沒有他的鼓勵和引導,我不可能進入博士班就 讀,更遑論今日順利拿到博士學位了。

辛苦的一路上,除了要感謝簡博實驗室同學和學長學弟的互相砥礪和幫忙,更要感謝的是國家奈米元件實驗室(NDL)的大力支持,提供我在職進修的機會;在優良的研究環境下,加上同事們的互相討論和大力幫忙,讓我能夠順利地進行實驗而完成本論文。那些在身旁支持鼓勵我的同事們,志彥、阿國、侯哥、綉芝、李姐、鳳姐、宋爺、小鄧、柏源、君惠、棟煥、財哥、俊淇、旭君、巫 Sir、龍哥、信良、阿貴、張茂男博士、黃國威博士等等,還有好多好多沒有列出而遺漏名字的同事們,我在此由衷向你們說聲謝謝!

最後,僅以此論文獻給我的父母和家人,感謝你們的關心與鼓勵,讓我一路上 能夠無後顧之憂的完成學業。老婆雪華的支持和陪伴是我一直向前的動力!

## Contents

| Abstract ( | Chinese)i                                                                    |

|------------|------------------------------------------------------------------------------|

| Abstract ( | English)iii                                                                  |

| Acknowle   | edgements (Chinese)vi                                                        |

| Contents . | vii                                                                          |

| Table List | sxi                                                                          |

| Figure Ca  | ptionsxii                                                                    |

| Chapter 1  | Introduction1                                                                |

|            | n Overview of Low-Temperature-Polycrystalline-Silicon (LTPS) Thin Film       |

| Tı         | ransistors (TFTs)                                                            |

| 1-2 M      | otivation for improving Low-Temperature-Deposited Gate Dielectrics Used      |

|            | LTPS TFTs                                                                    |

| 1-3 O      | rganization of the Thesis                                                    |

| Chapter 2  | Characterizations of the High-к Films Deposited by Atomic-Vapor              |

|            | Deposition9                                                                  |

| 2-1 In     | troduction9                                                                  |

| 2-2 O      | verview of Atomic-Vapor Deposition (AVD) System10                            |

| 2-3 St     | ructural and Electrical Characterizations of HfO <sub>2</sub> Films11        |

| 2-3.       | 1 Experimental                                                               |

| 2-3.       | 2 Thickness Dependence of HfO <sub>2</sub> films on Deposition Temperature12 |

| 2-3.       | 3 Structural Characterizations of HfO <sub>2</sub> Thin Films by XRD         |

|            | Analysis13                                                                   |

| 2-3        | 4 Chemical Bonding and Composition of HfO. Thin Films by XPS                 |

|             | Analysis                                                               | 15         |

|-------------|------------------------------------------------------------------------|------------|

| 2-3.5       | Structural Images of HfO <sub>2</sub> Thin Films by TEM Analysis       | 16         |

| 2-3.6       | Structure Changes of HfO <sub>2</sub> Thin Films by Conductive AFM     |            |

|             | Analysis                                                               | 19         |

| 2-3.7       | Electrical Properties of HfO <sub>2</sub> Thin Films                   | 19         |

| 2-3.8       | Characteristics of MOSFETs Using HfO <sub>2</sub> Gate Dielectrics     | 21         |

| 2-3.9       | Summaries of Characteristics of HfO <sub>2</sub> Films                 | 23         |

| 2-4 Struc   | ctural and Electrical Characterizations of HfSiO <sub>x</sub> Films    | 23         |

| 2-4.1       | Experimental                                                           | 23         |

| 2-4.2       | Thickness Dependence of Different Parameters (Deposition Ten           | nperature, |

|             | Injection Frequency, Film Composition) on HfSiO <sub>x</sub> Films     | 24         |

| 2-4.3       | Chemical Bonding and Composition of HfSiO <sub>x</sub> Thin Films by X |            |

|             | Analysis ES                                                            | 25         |

| 2-4.4       | Depth Profiles of HfSiO <sub>x</sub> Films by AES Analysis             | 27         |

| 2-4.5       | Structural Characterizations of HfSiO <sub>x</sub> Thin Films by XRD   |            |

|             | Analysis                                                               | 28         |

| 2-4.6       | Structural Images of HfSiO <sub>x</sub> Thin Films by TEM Analysis     | 28         |

| 2-4.7       | Electrical Properties of HfSiO <sub>x</sub> Thin Films                 | 28         |

| 2-4.8       | Summaries of Characteristics of HfSiO <sub>x</sub> Films               | 31         |

| 2-5 Sum     | mary                                                                   | 31         |

| Chapter 3 I | High-Performance and Low-Temperature-Compatible P-Char                 | inel       |

| ]           | Polycrystalline-Silicon TFTs Using Hafnium Silicate Gate               |            |

| ]           | Dielectric                                                             | 67         |

| 3-1 Intro   | oduction                                                               | 67         |

| 3-2 High    | n-к Film Depositions and Device Fabrications                           | 68         |

| 3-4     | Electrical Properties of High-κ Thick Films71                          |

|---------|------------------------------------------------------------------------|

| 3-5     | Characteristics of Low-Temperature-Polycrystalline-Silicon (LTPS) TFTs |

|         | Using High-κ Gate Dielectrics71                                        |

| 3-6     | Dependence of Electrical characteristics on Channel Length and Channel |

|         | Width                                                                  |

| 3-7     | Summary                                                                |

| Chapte  | r 4 Mobility, Off-State Current, and Reliability Study of the          |

|         | Newly-Developed TFTs99                                                 |

| 4-1     | Introduction                                                           |

| 4-2     | Device Fabrications                                                    |

| 4-3     | Possible Mobility Degradation Mechanisms of High-κ TFTs102             |

| 4-4     | Origins of Off-State Current among Poly-Si TFTs with Different Gate    |

|         | Dielectrics                                                            |

| 4-5     | Temperature Instability of Poly-Si TFTs with Different Gate            |

|         | Dielectrics                                                            |

| 4-6     | Negative-Bias-Temperature-Instability (NBTI) of Poly-Si TFTs with      |

|         | Different Gate Dielectrics                                             |

| 4-7     | Summary                                                                |

| Chapte  | r 5 Conclusions and Future Prospects137                                |

| 5-1     | Conclusions                                                            |

| 5-2     | Future Prospects                                                       |

|         |                                                                        |

| Doforon | 141                                                                    |

|         | Coupled Plasma Chemical Vapor Deposition at Low Tempo                       | erature on |

|---------|-----------------------------------------------------------------------------|------------|

|         | SiO <sub>2</sub> Substrates                                                 | 155        |

| A-1 Int | roduction                                                                   | 155        |

| A-2 Ch  | aracterizations of the Polycrystalline Ge Films on SiO <sub>2</sub> Substra | ate by     |

| IC      | P-CVD at 400°C                                                              | 157        |

| A-2.1   | Experimental                                                                | 157        |

| A-2.2   | 2 Structural Characterization of Deposited-Ge Films by XPS,                 | AES, XRD,  |

|         | And TEM Analysis                                                            | 157        |

| A-3 Ph  | ysical and Electrical Properties of Ge Films Deposited at 300°C             | C by       |

| IC      | P-CVD System                                                                |            |

| A-3.    | 1 Experimental                                                              | 160        |

| A-3.    |                                                                             |            |

|         | Films                                                                       | 163        |

| A-3.3   |                                                                             |            |

| A-3.4   | Characterizations of the Re-Crystallization Ge Films                        | 164        |

| A-3.5   | Electrical Characteristics of Doped Ge Films                                | 166        |

| A-4 Ur  | afinished Low-Temperature Poly-Ge TFTs                                      | 167        |

| A-5 Su  | mmary                                                                       | 167        |

| A-6 Re  | ference                                                                     | 169        |

# Table Lists

| Cha | apter | 2 |

|-----|-------|---|

|     |       |   |

| Table 2-1  | Relative contents of Hf, C and O elements of as-deposited HfO <sub>2</sub> films. The  |

|------------|----------------------------------------------------------------------------------------|

|            | deposition temperature, chamber pressure and oxygen flow are 400°C, 1.5                |

|            | mbar, and 300sccm, respectively                                                        |

| Table 2-2  | Compositions of HfO <sub>2</sub> films inside and outside the grain region34           |

| Table 2-3  | Summary of thickness, dielectric constant, EOT for the sample deposited at             |

|            | 400°C with and without post annealing                                                  |

| Table 2-4  | Parameters of topographic AFM and conductive AFM for as-deposited HfO <sub>2</sub>     |

|            | film and those subjected to post-deposition annealing at 600°C -1000°C in              |

|            | $N_2$ ambient for 30sec. The deposition temperature, chamber pressure and              |

|            | oxygen flow are 400°C, 1.5mbar, and 300sccm, respectively                              |

| Chapte     | r 3                                                                                    |

| Table 3-1  | Device parameters of Low-Temperature P-Channel Poly-silicon TFTs                       |

|            | (W/L= $5\mu m/10\mu m$ ) incorporating various gate dielectrics at a value of $V_{DS}$ |

|            | of -0.1V                                                                               |

| Table 3-2. | Etching rates of various gate dielectrics                                              |

|            |                                                                                        |

| Append     | lix                                                                                    |

| Table A-1  | The grain sizes of the as-deposited Ge film capped with a $SiN_x$ layer and            |

|            | after re-crystallization with various re-crystallization methods, annealing            |

|            | temperatures, and durations. The thicknesses of Ge films are around                    |

|            | 160nm                                                                                  |

# **Figure Captions**

# **Chapter 2**

| Fig. 2-1  | Schematic diagram of atomic-vapor deposition (AVD) system                                  |

|-----------|--------------------------------------------------------------------------------------------|

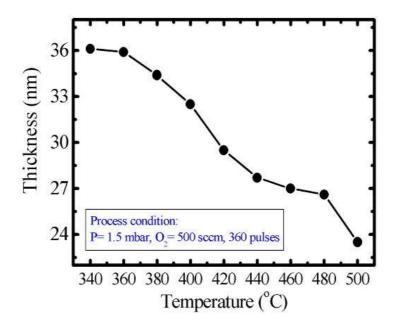

| Fig. 2-2  | Temperature dependence of the thickness of HfO <sub>2</sub> films                          |

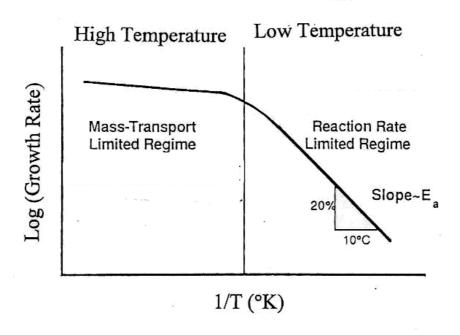

| Fig. 2-3  | Temperature dependence of the growth rate of the CVD films38                               |

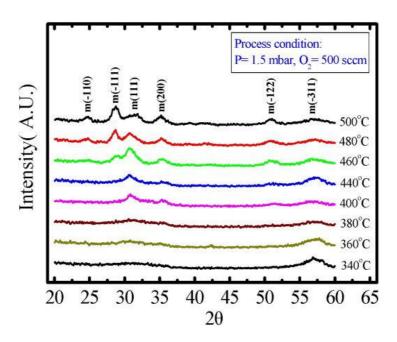

| Fig. 2-4  | XRD spectra of as-deposited HfO <sub>2</sub> films at various process temperatures. The    |

|           | chamber pressure is 1.5mbar and oxygen gas flow is 500sccm39                               |

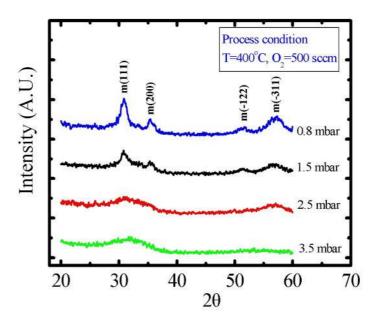

| Fig. 2-5  | XRD spectra of as-deposited HfO <sub>2</sub> films at various chamber pressures. The       |

|           | temperature is 400°C and oxygen gas flow is 500sccm39                                      |

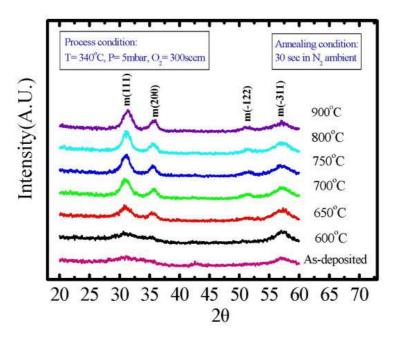

| Fig. 2-6  | XRD spectra of HfO <sub>2</sub> films deposited at 340°C with different post-deposition    |

|           | annealing temperatures, in N <sub>2</sub> ambient, 30seconds. The chamber pressure is      |

|           | 5mbar and oxygen gas flow is 300sccm                                                       |

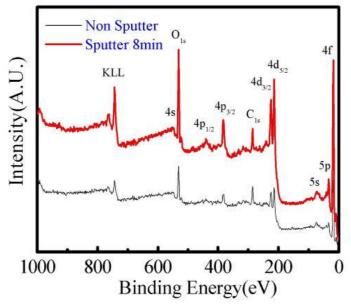

| Fig. 2-7  | XPS spectra of as-deposited HfO <sub>2</sub> thin films. The deposition temperature,       |

|           | chamber pressure and oxygen flow are 400°C, 1.5mbar, and 500sccm,                          |

|           | respectively                                                                               |

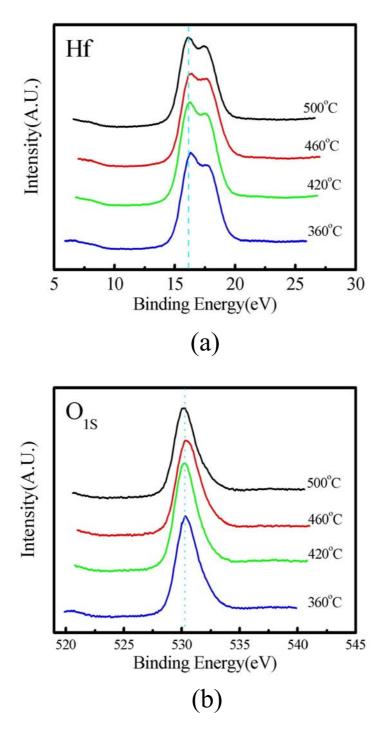

| Fig. 2-8  | XPS data of (a) $Hf_{4f}$ spectra, and (b) $O_{1s}$ spectra for $HfO_2$ films deposited at |

|           | various temperatures. The thickness is around 30nm                                         |

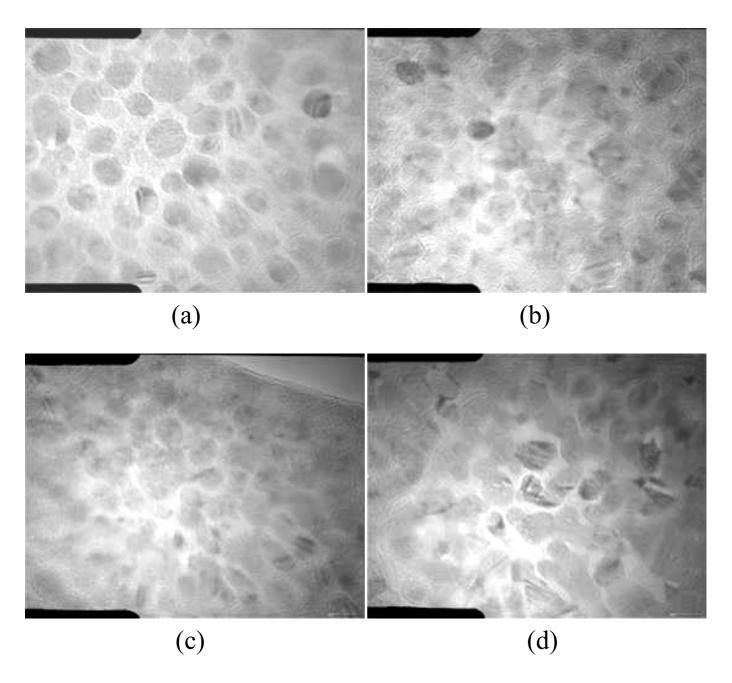

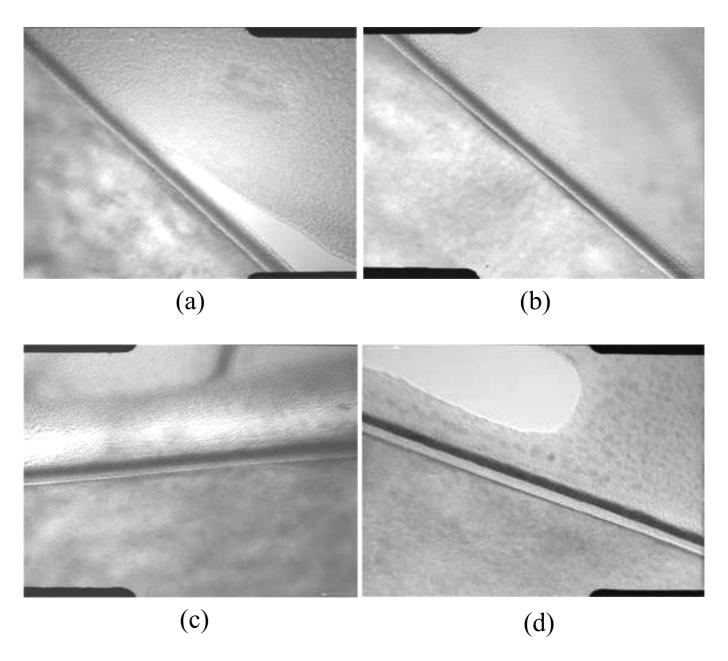

| Fig. 2-9  | Plane-view TEM images of (a) as-deposited thin film and those subjected to                 |

|           | (b) 600°C, (c) 800°C, (d) 1000°C post-deposition annealing in N <sub>2</sub> ambient       |

|           | for 30sec. The deposition temperature, chamber pressure and oxygen gas                     |

|           | flow are 400°C, 1.5mbar, and 300sccm, respectively                                         |

| Fig. 2-10 | Cross-sectional TEM images of (a) as-deposited thin film and those                         |

|           | subjected to (b) 600°C, (c) 800°C, (d) 1000°C post-deposition annealing                    |

|           | in $N_2$ ambient for 30sec. The deposition temperature, chamber pressure                   |

|           | and oxygen flow are 400°C, 1.5mbar, and 300sccm, respectively43                            |

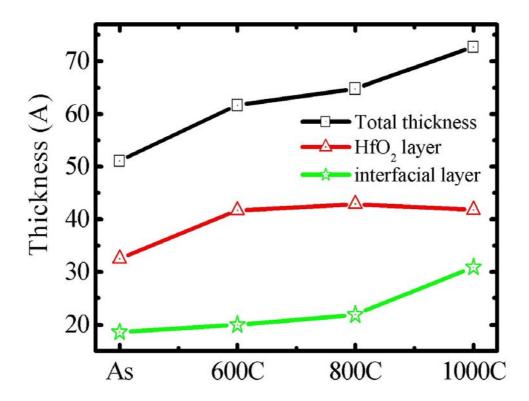

| F1g. 2-11 | Inickness versus PDA temperature of individual layers44                                        |

|-----------|------------------------------------------------------------------------------------------------|

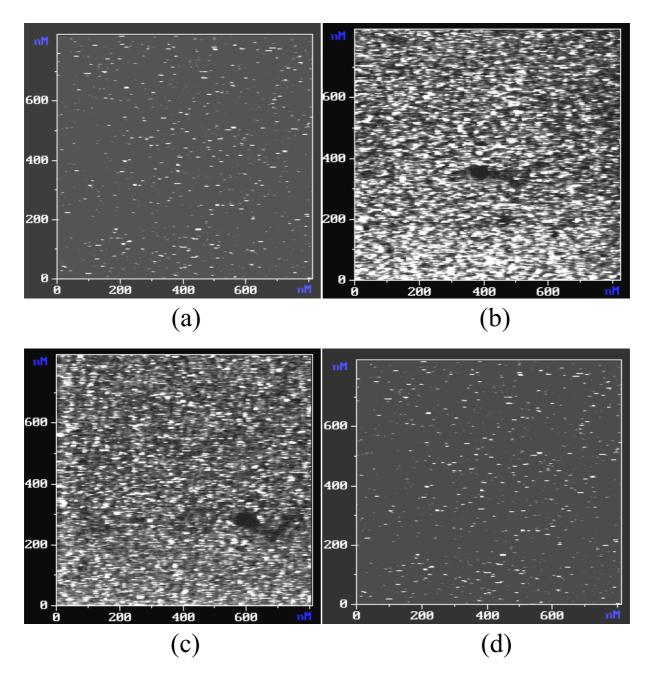

| Fig. 2-12 | The images of conductive-AFM of (a) as-deposited thin film and those                           |

|           | subjected to (b) 600°C, (c) 800°C, (d) 1000°C post-deposition annealing in                     |

|           | N <sub>2</sub> ambient for 30sec. The deposition temperature, chamber pressure and             |

|           | oxygen flow are 400°C, 1.5mbar, and 300sccm, respectively45                                    |

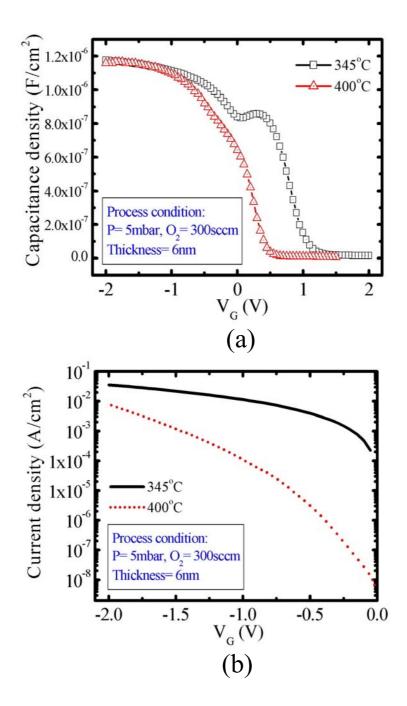

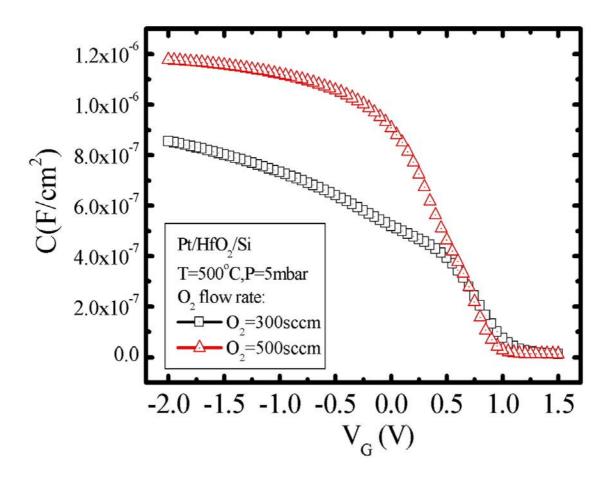

| Fig. 2-13 | (a) C-V and (b) J-V characteristics of the HfO <sub>2</sub> films deposited at different       |

|           | substrate temperature on HF-treated wafers. The chamber pressure is 5mbar                      |

|           | and the oxygen gas flow is 300sccm. The thickness is around 6nm46                              |

| Fig. 2-14 | C-V characteristics of the HfO <sub>2</sub> films deposited with different oxygen gas          |

|           | flows on HF-treated wafers. The substrate temperature is 500°C and the                         |

|           | chamber pressure is 5mbar. The thickness is around 6nm                                         |

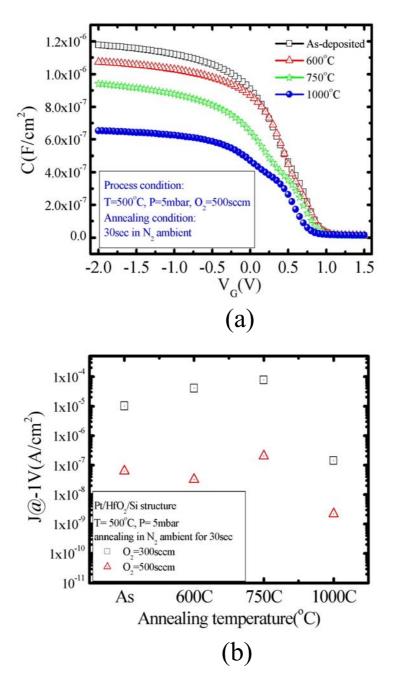

| Fig. 2-15 | (a) C-V characteristics and (b) leakage current density at -1V versus PDA                      |

|           | temperature of the HfO <sub>2</sub> films deposited at 500°C with different O <sub>2</sub> gas |

|           | flow on HF-treated wafers                                                                      |

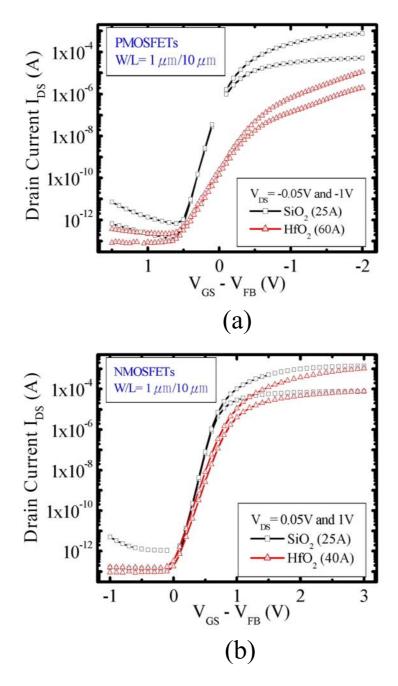

| Fig. 2-16 | Transfer characteristics of (a) PMOSFETs, and (b) NMOSFETs with HfO <sub>2</sub>               |

|           | gate dielectrics. The deposition temperature and oxygen flow of the HfO <sub>2</sub>           |

|           | film are 400°C, 300sccm for PMOSFETs and 500°C, 1700sccm for                                   |

|           | NMOSFETs, respectively                                                                         |

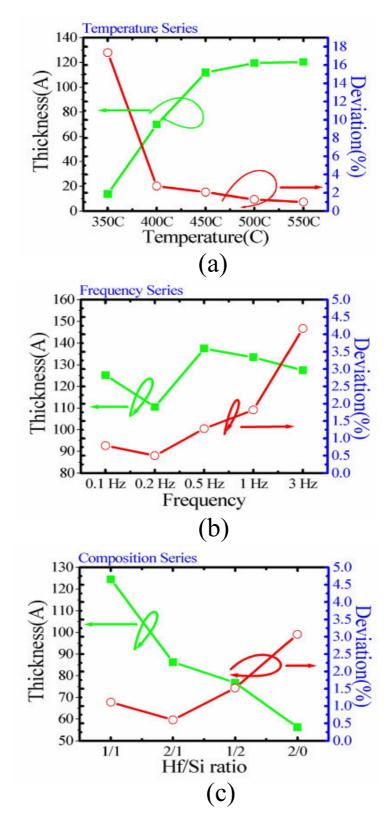

| Fig. 2-17 | Thickness and deviation variations of (a) Temperature series, (b) Frequency                    |

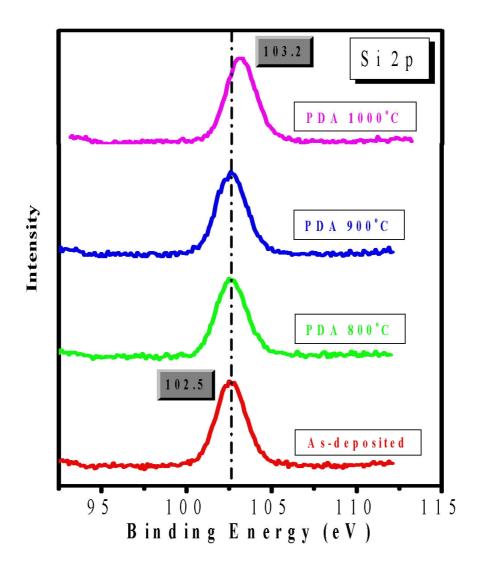

|           | series, (c) Composition series                                                                 |

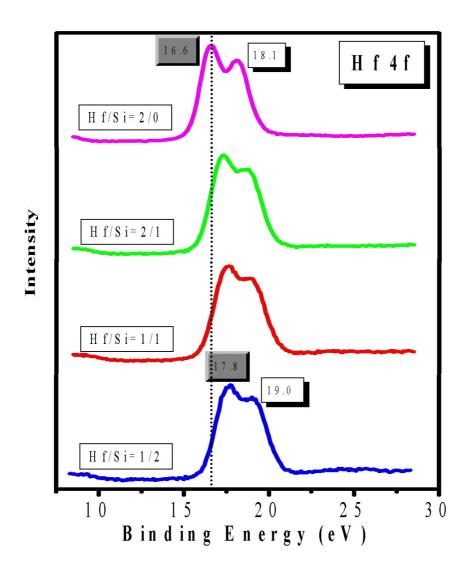

| Fig. 2-18 | XPS Spectra of Hf <sub>4f</sub> for HfSiO <sub>x</sub> films deposited by AVD at various Hf/Si |

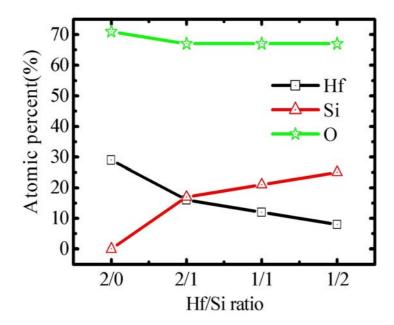

|           | composition ratios on Si (100)                                                                 |

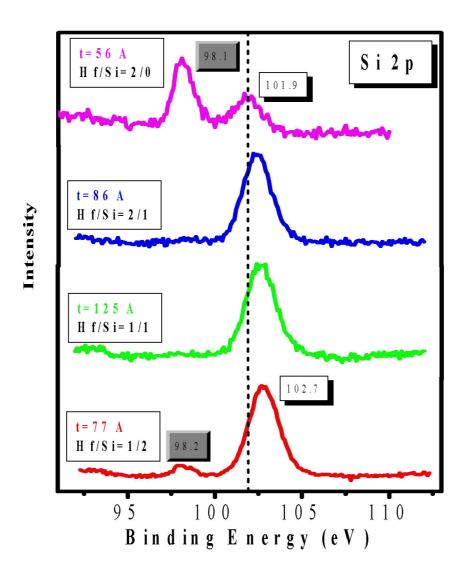

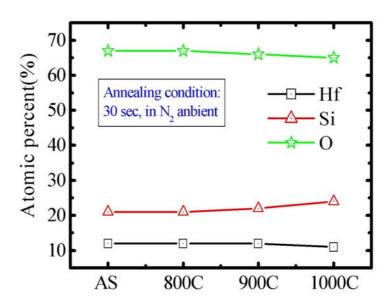

| Fig. 2-19 | XPS Spectra of Si <sub>2p</sub> for HfSiO <sub>x</sub> films deposited by AVD at various Hf/Si |

|           | composition ratios on Si (100)                                                                 |

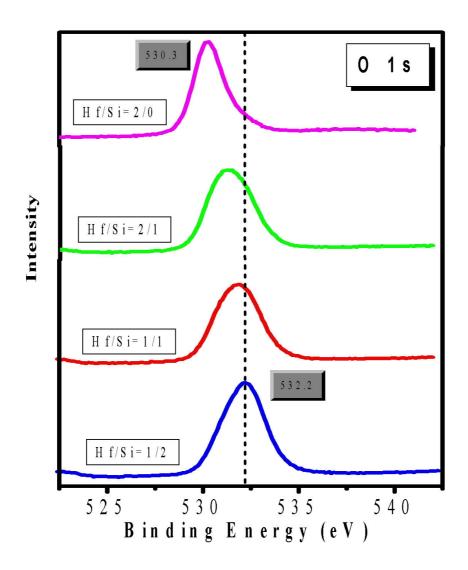

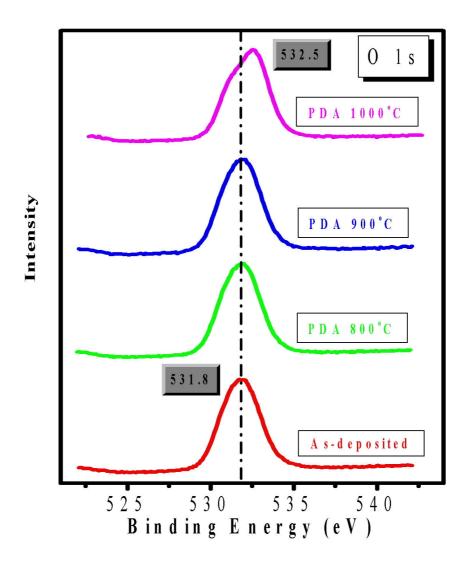

| Fig. 2-20 | XPS Spectra of O <sub>1s</sub> for HfSiO <sub>x</sub> films deposited by AVD at various Hf/Si  |

|           | composition ratios on Si (100)                                                                 |

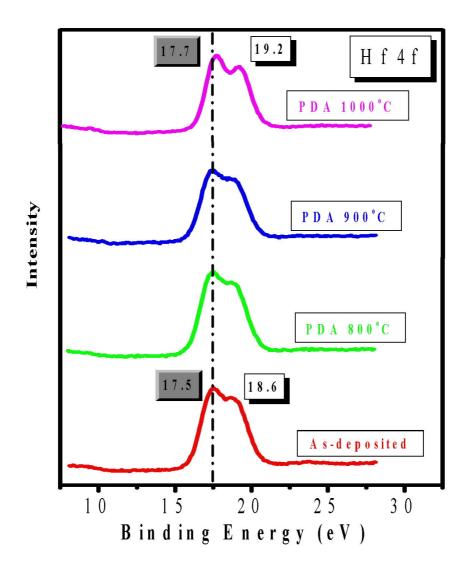

| F1g. 2-21 | XPS Spectra of $HI_{4f}$ for $HISIO_x$ films with $HI/SI$ ratio of $I/I$ deposited by                 |

|-----------|-------------------------------------------------------------------------------------------------------|

|           | AVD on Si (100) after different PDA treatments. The thickness is around                               |

|           | 26nm                                                                                                  |

| Fig. 2-22 | XPS Spectra of Si <sub>2p</sub> for HfSiO <sub>x</sub> films with Hf/Si ratio of 1/1 deposited by     |

|           | AVD on Si (100) after different PDA treatments. The thickness is around                               |

|           | 26nm                                                                                                  |

| Fig. 2-23 | XPS Spectra of O <sub>1s</sub> for HfSiO <sub>x</sub> films with Hf/Si ratio of 1/1 deposited by      |

|           | AVD on Si (100) after different PDA treatments. The thickness is around                               |

|           | 26nm                                                                                                  |

| Fig. 2-24 | Variations of different atomic percent for HfSiO <sub>x</sub> films deposited by AVD at               |

|           | various Hf/Si composition ratios on Si (100)                                                          |

| Fig. 2-25 | Variations of different atomic percent for HfSiO <sub>x</sub> films with Hf/Si ratio of               |

|           | 1/1 deposited by AVD on Si (100) after different PDA treatments. The                                  |

|           | thickness is around 26nm                                                                              |

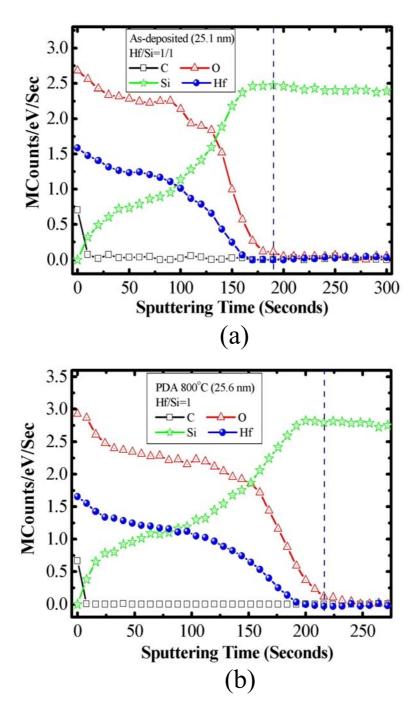

| Fig. 2-26 | AES depth profiles of (a) the as-deposited HfSiO <sub>x</sub> film with Hf/Si ratio of                |

|           | 1/1 deposited at 500°C by AVD on Si (100) and the samples with (b) 800°C                              |

|           | (c) 900°C (d) 1000°C PDA treatments                                                                   |

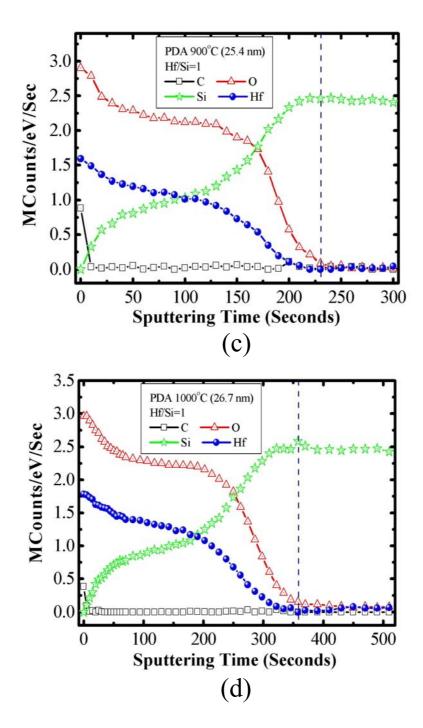

| Fig. 2-27 | XRD Spectra of HfSiO <sub>x</sub> film with Hf/Si ratio of 1/1 deposited at 500°C by                  |

|           | AVD on Si (100) with various PDA temperature, $T=800^{\circ}\text{C} \sim 1000^{\circ}\text{C}$ . The |

|           | thickness is around 26nm                                                                              |

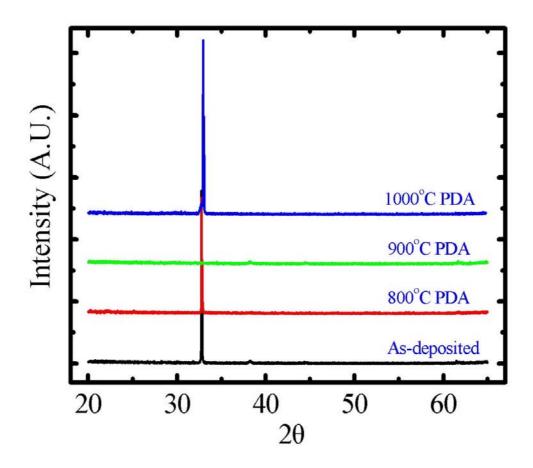

| Fig. 2-28 | Images of cross-sectional TEM for as-deposited HfSiO <sub>x</sub> film with Hf/Si                     |

|           | ratio of 1/1 deposited at 500°C by AVD on native-oxide-based Si-substrate.                            |

|           | The thicknesses of HfSiO <sub>x</sub> thin film is around 11nm61                                      |

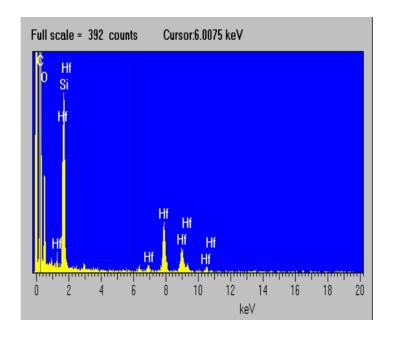

| Fig. 2-29 | TEM-EDX for as-deposited HfSiO <sub>x</sub> film with Hf/Si ratio of 1/1 deposited at                 |

|           | 500°C by AVD on native-oxide-based Si-substrate. The thicknesses of thin                              |

|           | films are around 11nm.                                                                                |

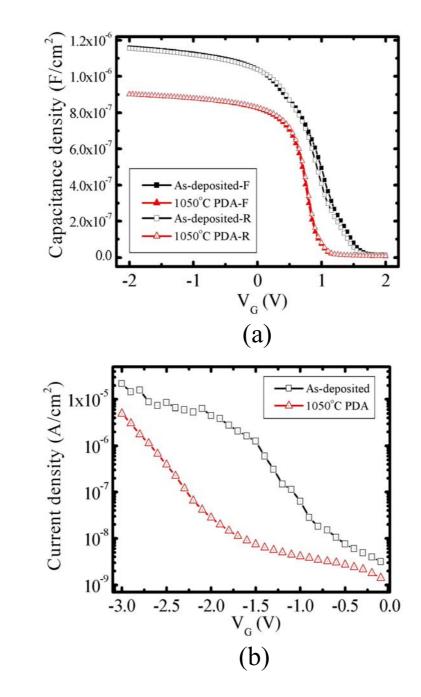

| Fig. 2-30 | (a) C-V and (b) J-V characteristics of $HtSiO_x$ films deposited at 500°C and                    |

|-----------|--------------------------------------------------------------------------------------------------|

|           | 1050°C PDA treatment for 10sec in N <sub>2</sub> ambient. The oxygen gas flow is                 |

|           | 1700sccm and the thickness is 5nm                                                                |

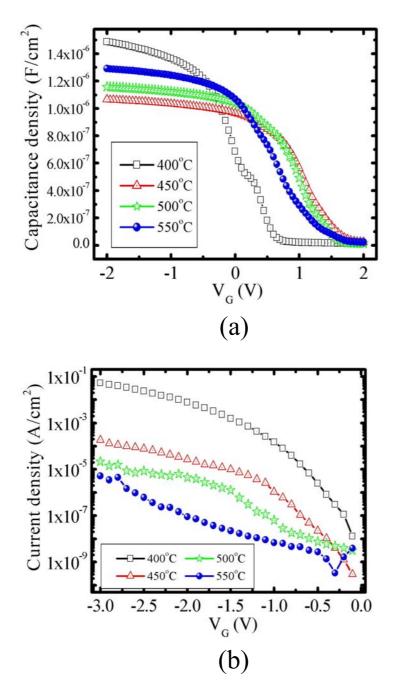

| Fig. 2-31 | (a) C-V and (b) J-V characteristics of HfSiO <sub>x</sub> films deposited at different           |

|           | substrate temperatures. The oxygen gas flow is 1700sccm and the thickness                        |

|           | is 5nm63                                                                                         |

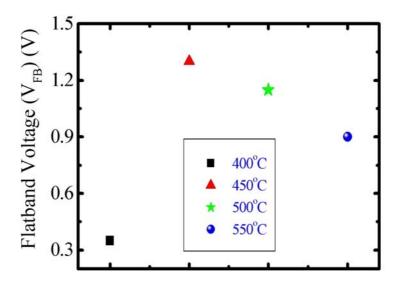

| Fig. 2-32 | Flatband voltage of HfSiO <sub>x</sub> films deposited at different substrate                    |

|           | temperatures. The oxygen gas flow is 1700sccm and the thickness is around                        |

|           | 5nm                                                                                              |

| Fig. 2-33 | Leakage current density versus EOT of HfSiO <sub>x</sub> films deposited at different            |

|           | substrate temperatures. The oxygen gas flow is 1700sccm and the thickness                        |

|           | is around 5nm                                                                                    |

| Fig. 2-34 | (a) C-V and (b) J-V characteristics of HfSiO <sub>x</sub> films deposited at 500°C with          |

|           | different Hf/Si ratios. The oxygen gas flow is 1700sccm and the thickness                        |

|           | is around 5nm65                                                                                  |

|           |                                                                                                  |

| Chapte    | er 3                                                                                             |

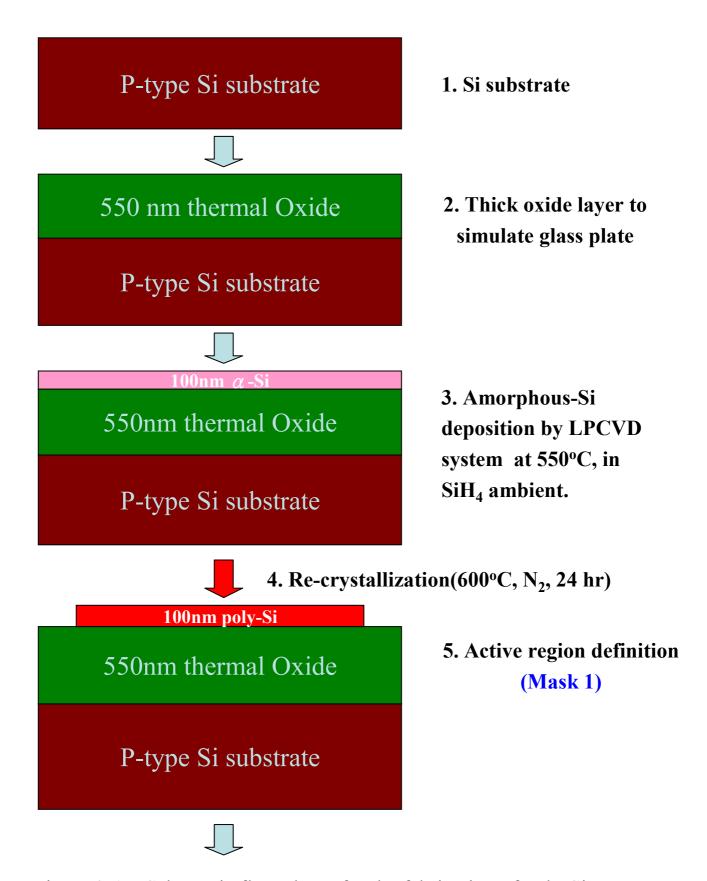

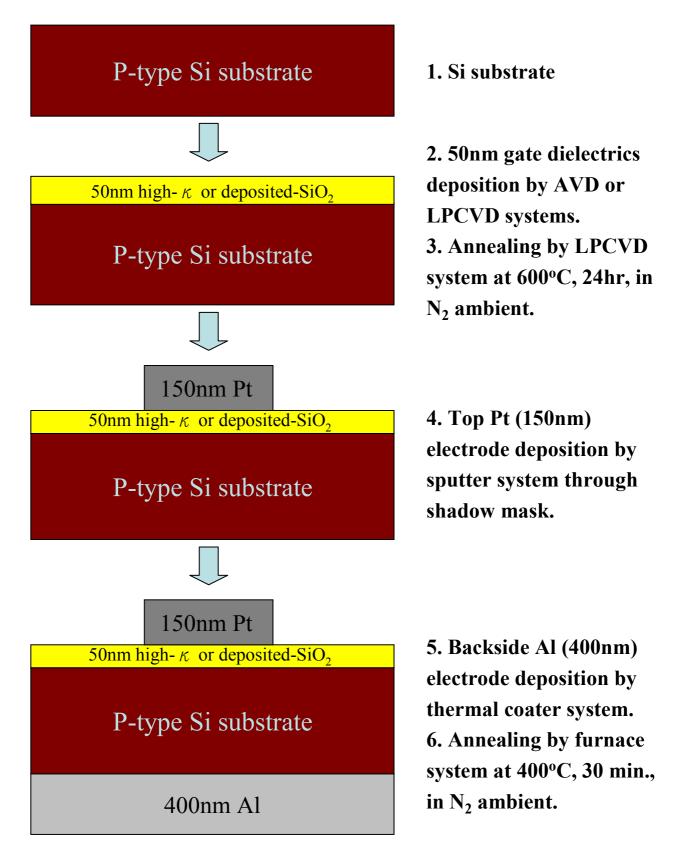

| Fig. 3-1  | Schematic flow charts for the fabrication of the poly-Si TFTs79                                  |

| Fig. 3-2  | Schematic flow charts for the fabrication of the capacitors                                      |

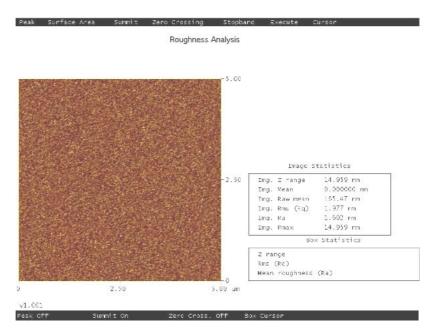

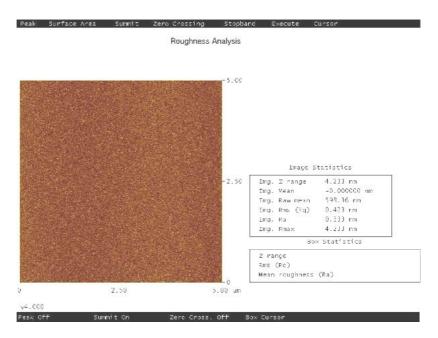

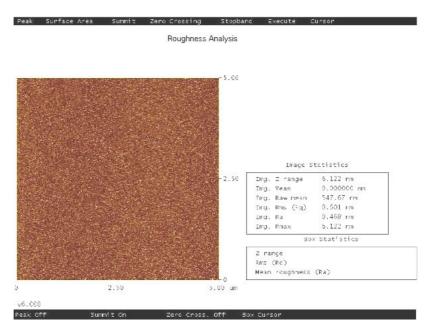

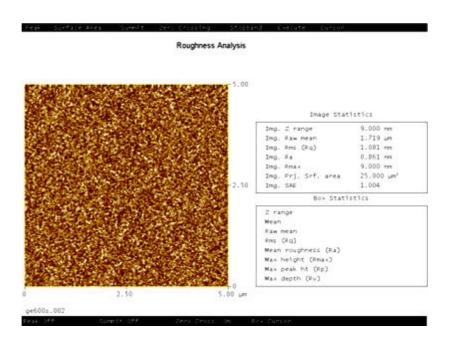

| Fig. 3-3  | Atomic force microscope (AFM) images of (a) the HfO <sub>2</sub> film (b) the HfSiO <sub>3</sub> |

|           | film (c) the deposited-SiO <sub>2</sub> film. All samples were annealed in furnace at            |

|           | 600°C in N <sub>2</sub> ambient for 24 hr. The thicknesses of all samples are around             |

|           | 50nm82                                                                                           |

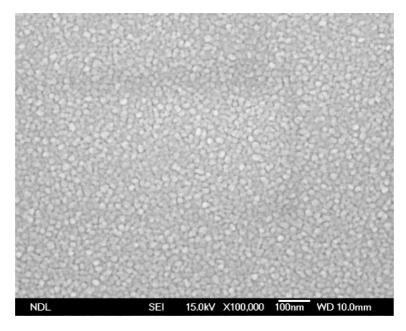

| Fig. 3-4  | Scan Electron Microscope (SEM) image of the HfO <sub>2</sub> film after annealing for            |

|           | 24 h at 600 °C in a N <sub>2</sub> ambient. The thickness is around 50nm83                       |

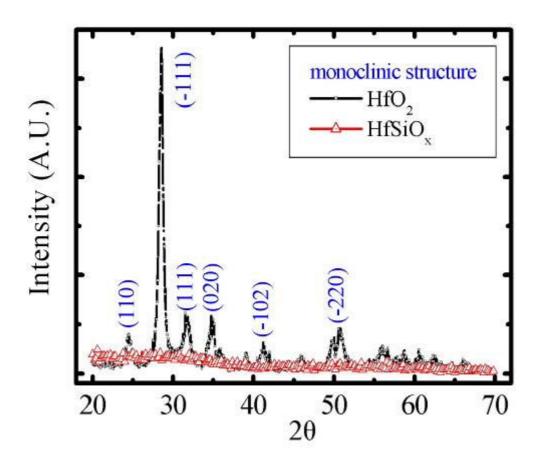

| Fig. 3-5  | X-ray diffraction patterns of HfO <sub>2</sub> and HfSiO <sub>x</sub> films after annealing for 24 h                  |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

|           | at $600\ ^{\circ}\text{C}$ in a $N_2$ ambient. The thicknesses of all samples are around                              |

|           | 50nm                                                                                                                  |

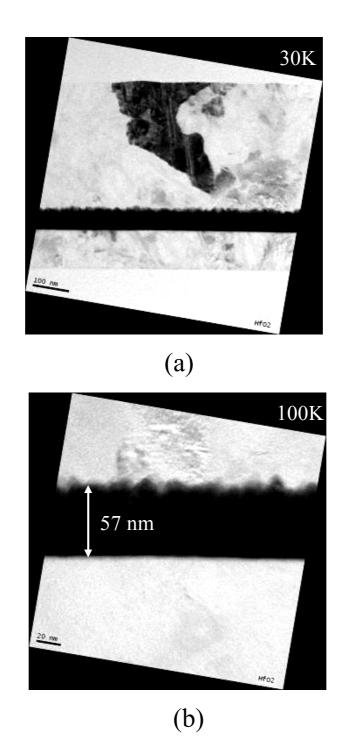

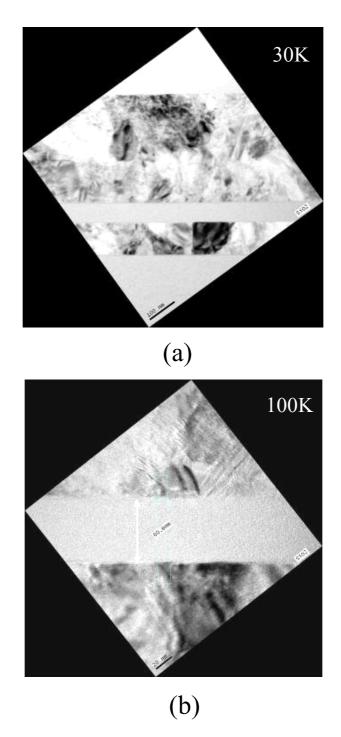

| Fig. 3-6  | Cross-sectional TEM images of TFTs incorporating HfO <sub>2</sub> gate dielectrics.                                   |

|           | The magnifications of TEM images are (a) 30K and (b) 100K,                                                            |

|           | respectively                                                                                                          |

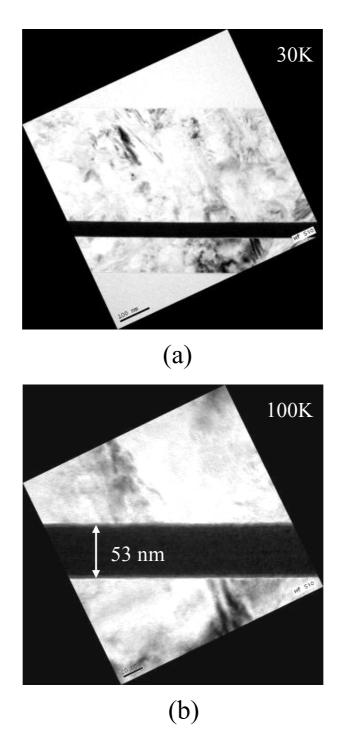

| Fig. 3-7  | Cross-sectional TEM images of TFTs incorporating HfSiO <sub>x</sub> gate dielectrics.                                 |

|           | The magnifications of TEM images are (a) 30K and (b) 100K                                                             |

|           | respectively. 86                                                                                                      |

| Fig. 3-8  | Cross-sectional TEM images of TFTs incorporating deposited-SiO <sub>2</sub> gate                                      |

|           | dielectrics. The magnifications of TEM images are (a) 30K and (b) 100K,                                               |

|           | respectively                                                                                                          |

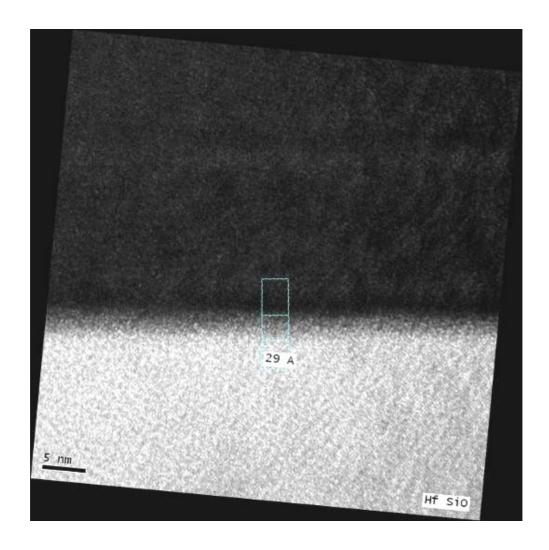

| Fig. 3-9  | Cross-sectional TEM image of the interfacial layer between the HfSiO <sub>x</sub> gate                                |

|           | dielectric and poly-Si channel                                                                                        |

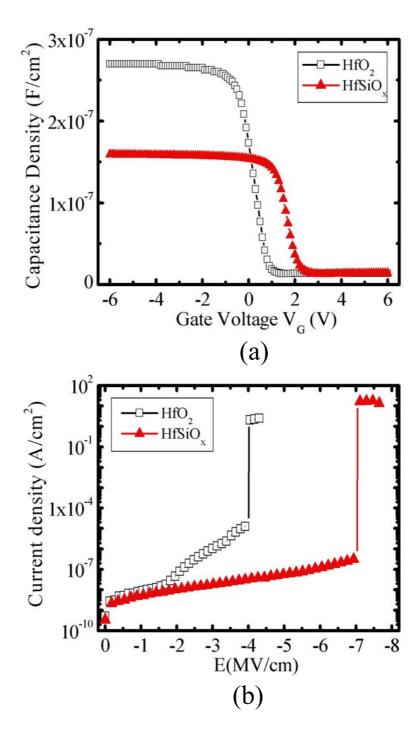

| Fig. 3-10 | Plots of (a) capacitance density versus gate voltage and (b) leakage current                                          |

|           | density versus electrical field for the HfO2 and HfSiOx films obtained after                                          |

|           | annealing for 24h at 600 °C in a N <sub>2</sub> ambient                                                               |

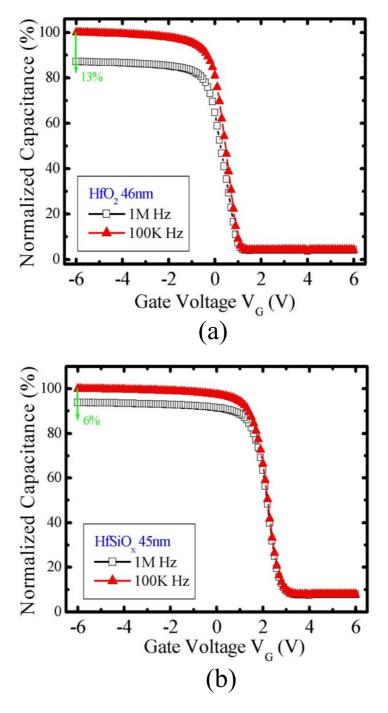

| Fig. 3-11 | Frequency dispersions of normalized capacitance versus gate voltage for (a)                                           |

|           | HfO <sub>2</sub> and (b) HfSiO <sub>x</sub> films obtained after annealing for 24h at 600 °C in a                     |

|           | N <sub>2</sub> ambient90                                                                                              |

| Fig. 3-12 | Comparisons of transfer characteristics at $V_{DS}$ of -0.1 and -2 V between                                          |

|           | TFTs containing (a) HfSiO <sub>x</sub> and deposited-SiO <sub>2</sub> and (b) HfSiO <sub>x</sub> and HfO <sub>2</sub> |

|           | as gate dielectrics                                                                                                   |

| Fig. 3-13 | Comparisons of output characteristics at $V_{DS}$ of -0.1 and -2 V between the                                        |

|           | TFTs containing (a) HfSiO <sub>x</sub> and deposited-SiO <sub>2</sub> and (b) HfSiO <sub>x</sub> and HfO <sub>2</sub> |

|           | as gata dialactrias                                                                                                   |

| Fig. 3-14 | Densities of states extracted from transfer characteristics ( $V_{DS} = -0.1 \text{ V}$ ) of         |

|-----------|------------------------------------------------------------------------------------------------------|

|           | poly-Si TFTs incorporating various gate dielectrics93                                                |

| Fig. 3-15 | (a) Threshold voltage and (b) subthreshold swing versus channel length for                           |

|           | devices with different gate dielectrics                                                              |

| Fig. 3-16 | (a) Threshold voltage and (b) subthreshold swing versus channel width for                            |

|           | devices with different gate dielectrics                                                              |

| Fig. 3-17 | Off-state current versus (a) channel length and (b) channel width for devices                        |

|           | with different gate dielectrics96                                                                    |

| Fig. 3-18 | Normalized field-effect mobility and drive current versus (a) channel length                         |

|           | and (b) channel width for devices with different gate dielectrics97                                  |

|           | 4411172                                                                                              |

| Chapte    | er 4                                                                                                 |

| Fig. 4-1  | Schematic for carrier mobility as a function of vertical electric field for                          |

|           | MOSFETs in the universal mobility model                                                              |

| Fig. 4-2  | Possible sources for reduced mobility in high-κ gate stacks. (Ref. [4.21] S.                         |

|           | Saito, D. Hisamoto, S. Kimura, and M. Hiratani, "Unified Mobility Model                              |

|           | for High-κ Gate Stacks", IEDM Technical Digest, 33.3.1-4, 2003.)114                                  |

| Fig. 4-3  | Comparisons of field-effect mobility versus gate voltage between TFTs                                |

|           | containing different gate dielectrics                                                                |

| Fig. 4-4  | Cross-sectional TEM images of TFTs incorporating (a) HfO <sub>2</sub> , (b) HfSiO <sub>x</sub> , and |

|           | (c) deposited-SiO <sub>2</sub> gate dielectrics                                                      |

| Fig. 4-5  | Transconductance (Gm) versus gate voltage at different measured                                      |

|           | temperatures (150°K to 300°K) for devices using (a) HfO <sub>2</sub> and (b) HfSiO <sub>x</sub> as   |

|           | gate dielectrics                                                                                     |

| Fig. 4-6  | Comparisons of transfer characteristics at $V_{DS}$ of -0.1 V between TFTs                           |

| containing $HIO_2$ and $HISIO_x$ as gate dielectrics                                      |

|-------------------------------------------------------------------------------------------|

| Fig. 4-7 Transconductance (Gm) versus gate voltage at different measure                   |

| temperatures (25°C to 125°C) for devices using (a) $HfO_2$ and (b) $HfSiO_x$ and          |

| gate dielectrics                                                                          |

| Fig. 4-8 Schematic illustrations of electron mobility degradation observed in MISFE       |

| with partially crystallized Hf-silicate. (Ref. [4.15] T. Yamaguchi, R. Iijim              |

| T. Ino, A. Nishiyama, and H. Satake, "Additional Scattering Effects for                   |

| Mobility Degradation in Hf-silicate Gate MISFETs", IEDM Technica                          |

| Digest, 26.3.1-4, 2002.)                                                                  |

| Fig. 4-9 Comparisons of transfer characteristics at $V_{DS}$ of -0.1 and -2 V between TFT |

| containing (a) $HfSiO_x$ and deposited- $SiO_2$ and (b) $HfSiO_x$ and $HfO_2$ as ga       |

| dielectrics                                                                               |

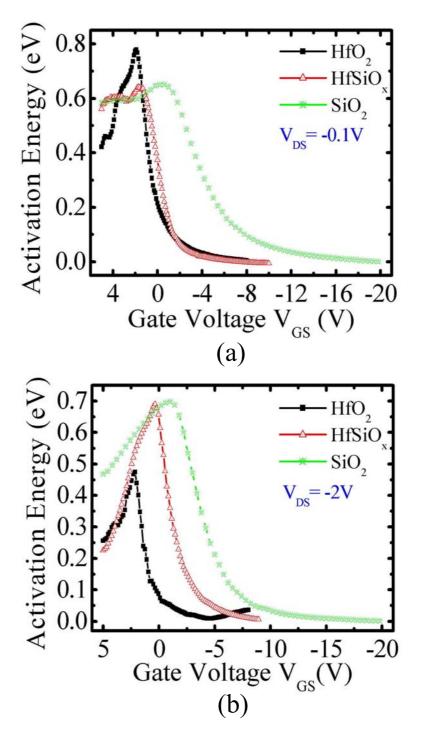

| Fig. 4-10 Channel activation energies obtained from the temperature dependence of         |

| transfer characteristics of poly-Si TFTs incorporating various ga                         |

| dielectrics at V <sub>DS</sub> of (a) -0.1 and (b) -2 V                                   |

| Fig. 4-11 Comparisons of transfer characteristics at $V_{DS}$ of (a) -0.1 and (b) -2 $V$  |

| different measured temperatures for the TFT containing deposited-SiG                      |

| gate dielectrics. 123                                                                     |

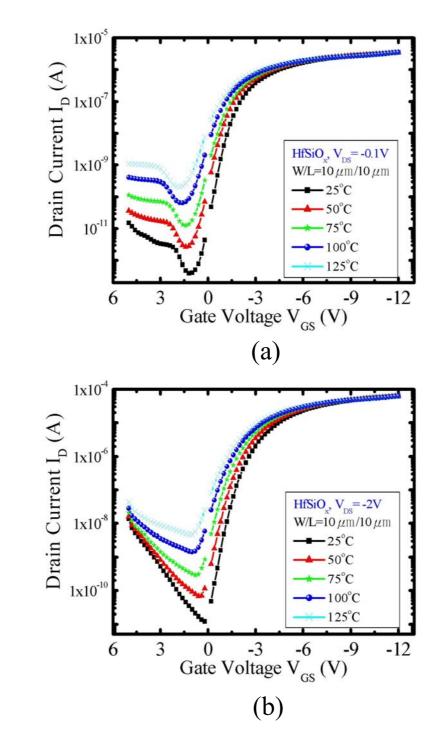

| Fig. 4-12 Comparisons of transfer characteristics at $V_{DS}$ of (a) -0.1 and (b) -2 $V$  |

| different measured temperatures for the TFT containing HfSiO <sub>x</sub> ga              |

| dielectrics. 124                                                                          |

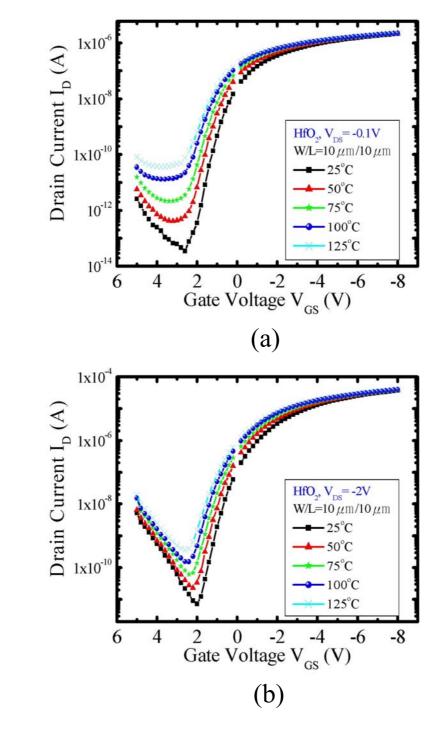

| Fig. 4-13 Comparisons of transfer characteristics at $V_{DS}$ of (a) -0.1 and (b) -2 $V$  |

| different measured temperatures for the TFT containing HfO2 ga                            |

| dielectrics. 12:                                                                          |

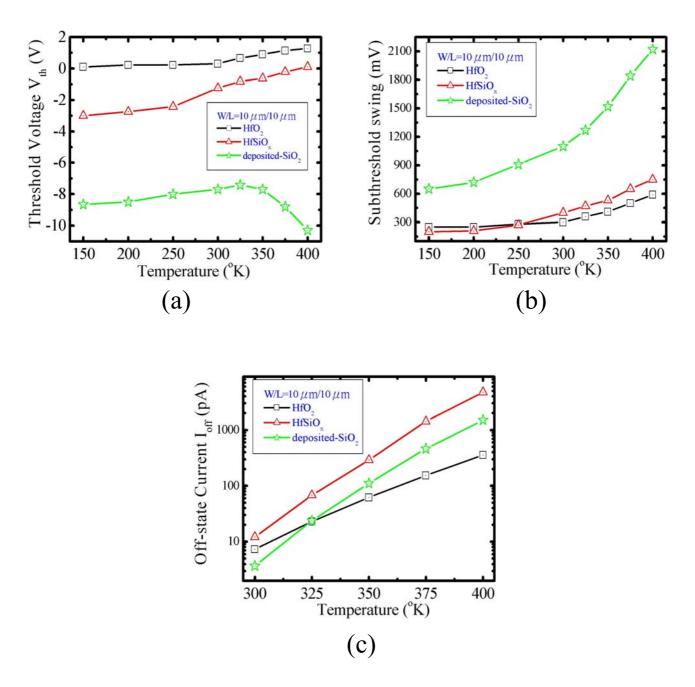

| Fig. 4-14 Comparisons of (a) threshold voltage, (b) subthreshold swing, (c) off-star      |

| current. (d) field-effect mobility, and (e) drive current versus measure                  |

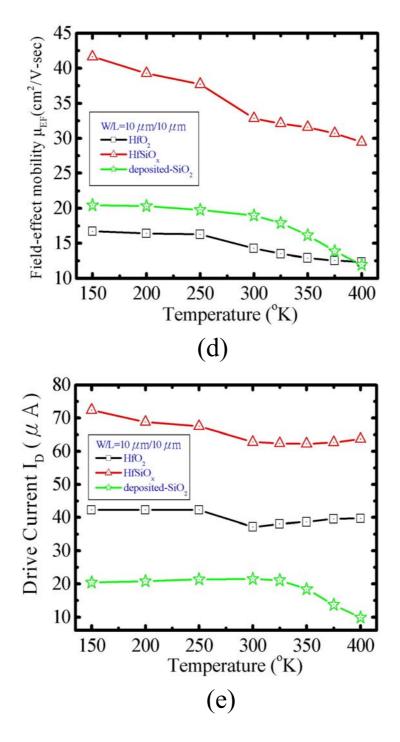

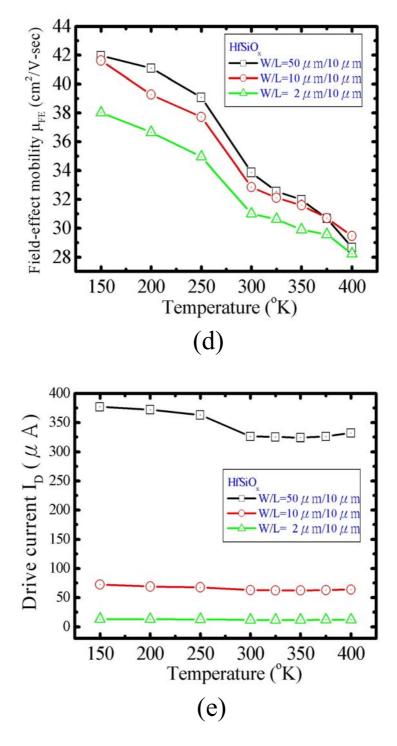

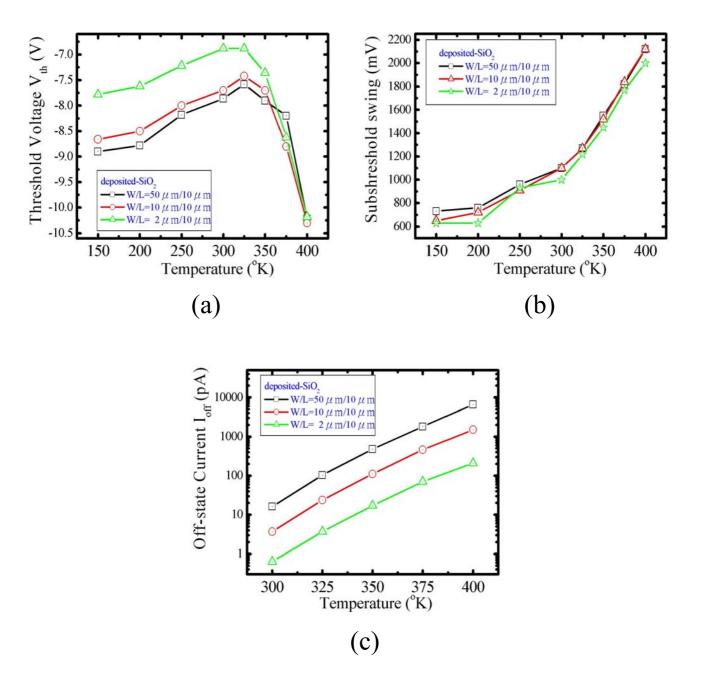

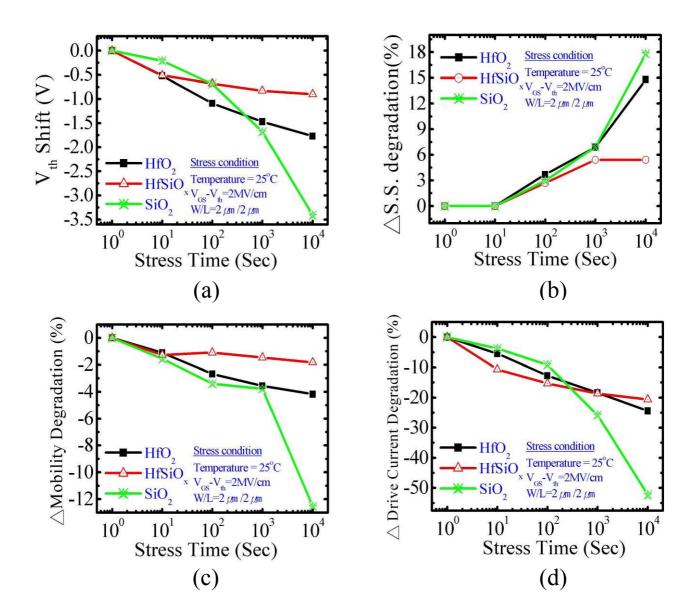

|           | temperatures among TFTs using different gate dielectrics                                                       |  |

|-----------|----------------------------------------------------------------------------------------------------------------|--|

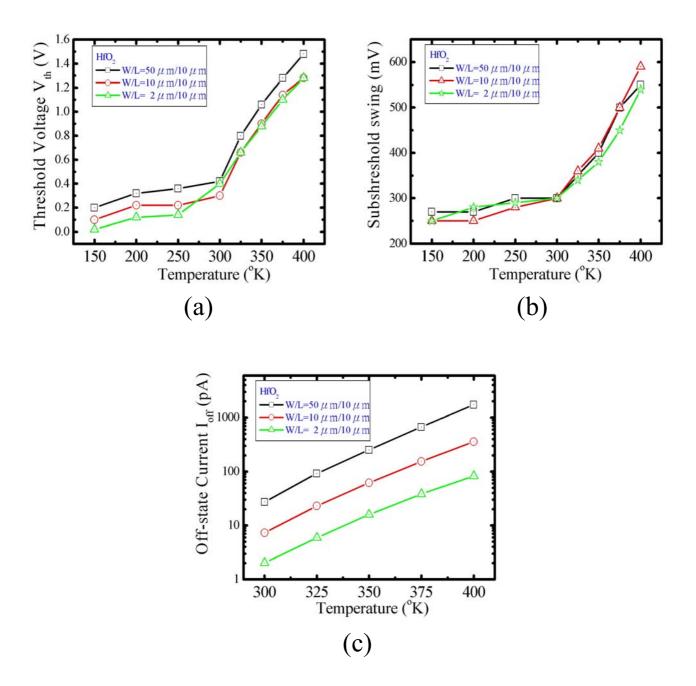

| Fig. 4-15 | Comparisons of (a) threshold voltage, (b) subthreshold swing, (c) off-state                                    |  |

|           | current, (d) field-effect mobility, and (e) drive current versus measured                                      |  |

|           | temperatures among HfO <sub>2</sub> -TFTs with different device dimensions128                                  |  |

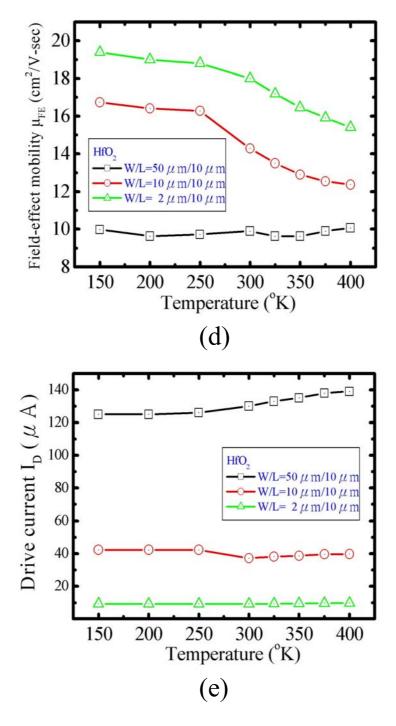

| Fig. 4-16 | Comparisons of (a) threshold voltage, (b) subthreshold swing, (c) off-state                                    |  |

|           | current, (d) field-effect mobility, and (e) drive current versus measured                                      |  |

|           | temperatures among HfSiO <sub>x</sub> -TFTs with different device dimensions130                                |  |

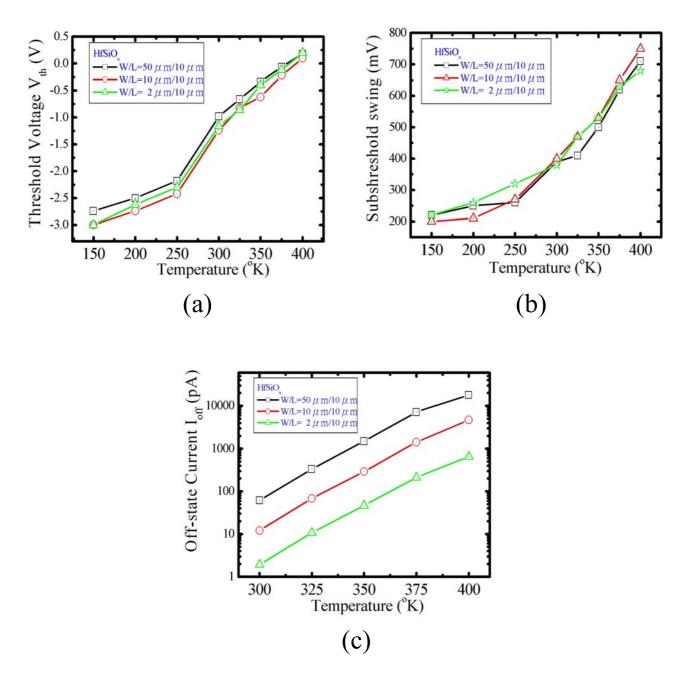

| Fig. 4-17 | Comparisons of (a) threshold voltage, (b) subthreshold swing, (c) off-state                                    |  |

|           | current, (d) field-effect mobility, and (e) drive current versus measured                                      |  |

|           | temperatures among deposited-SiO <sub>2</sub> TFTs with different device                                       |  |

|           | dimensions                                                                                                     |  |

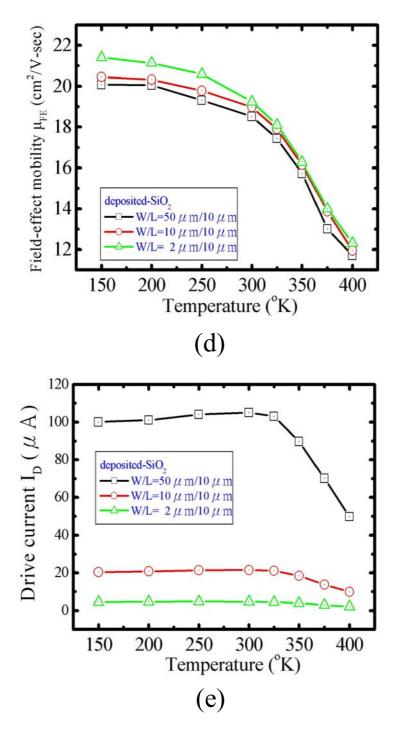

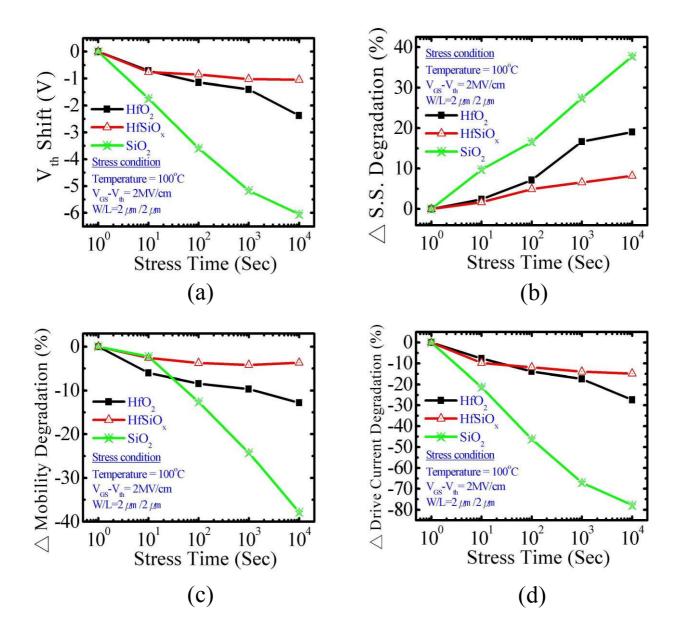

| Fig. 4-18 | (a) $V_{th}$ , (b) SS, (c) $\mu_{FE}$ , and (d) drive current as a function of stress time at 25               |  |

|           | °C for poly-Si TFTs incorporating various gate dielectrics                                                     |  |

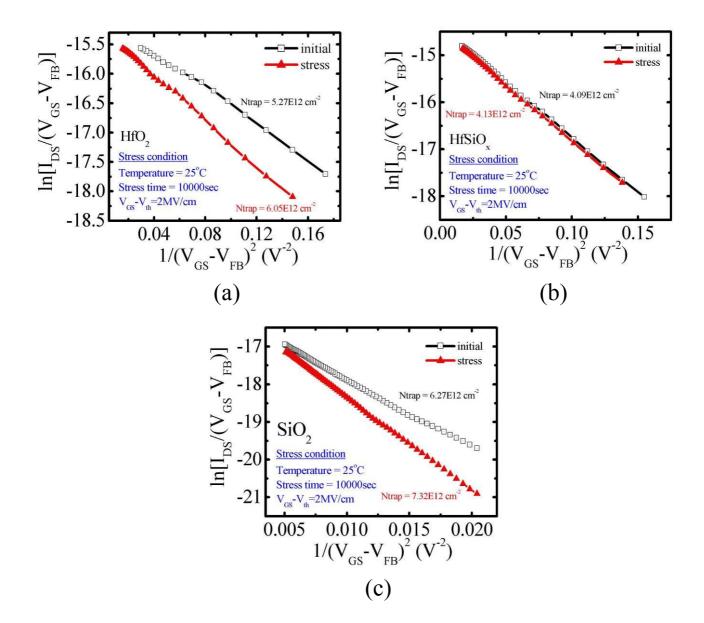

| Fig. 4-19 | Grain-boundary trap-state density extraction of poly-Si TFTs incorporating                                     |  |

|           | (a) HfO <sub>2</sub> , (b) HfSiO <sub>x</sub> , and (c) deposited-SiO <sub>2</sub> gate dielectrics before and |  |

|           | after NBTI stressing for 10,000 s at 25 °C; stress bias: $V_{GS} - V_{th} = 2$                                 |  |

|           | MV/cm                                                                                                          |  |

| Fig. 4-20 | (a) $V_{\text{th}},$ (b) SS, (c) $\mu_{\text{FE}},$ and (d) drive current as a function of stress time at      |  |

|           | 100 °C for poly-Si TFTs incorporating various gate dielectrics                                                 |  |

|           |                                                                                                                |  |

| Appendix  |                                                                                                                |  |

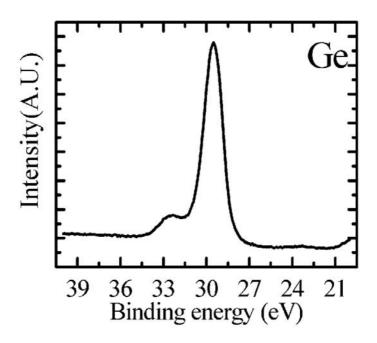

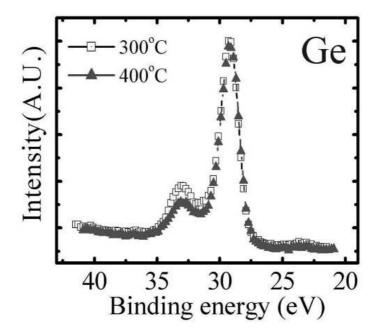

| Fig. A-1  | The spectrum of Ge 3d level by XPS measurement, which revealed the                                             |  |

|           | surface conditions of the as-grown Ge films deposited onto SiO <sub>2</sub> substrate at                       |  |

|           | 400°C                                                                                                          |  |

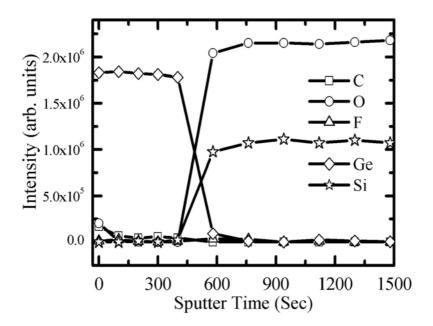

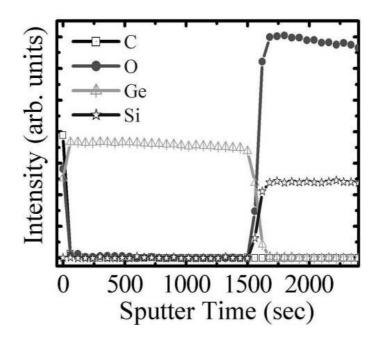

| Fig. A-2  | AES depth profiles of Ge film deposited onto SiO <sub>2</sub> substrate at 400°C175                            |  |

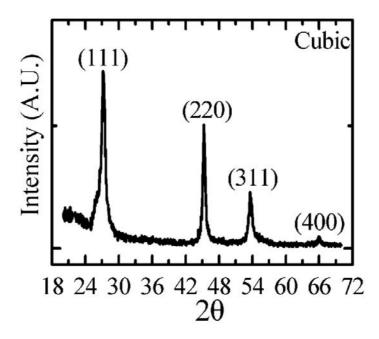

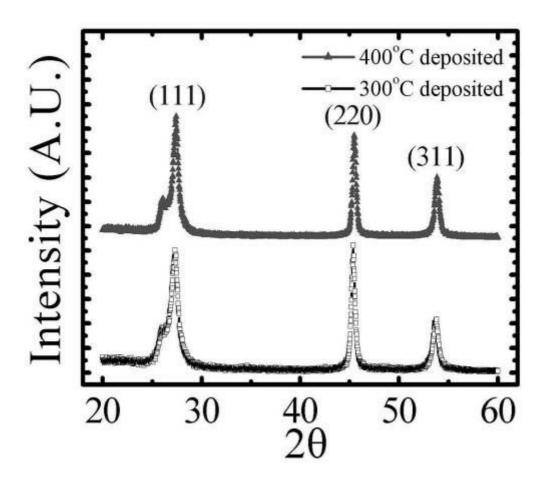

| F1g. A-3  | X-ray diffraction patterns of Ge film deposited at $400^{\circ}$ C on $810_2$ substrate.     |

|-----------|----------------------------------------------------------------------------------------------|

|           | The thickness of the Ge film is around 100nm                                                 |

| Fig. A-4  | Atomic force microscope (AFM) image of Ge film deposited at 400°C. The                       |

|           | thicknesses of the sample is around 100nm                                                    |

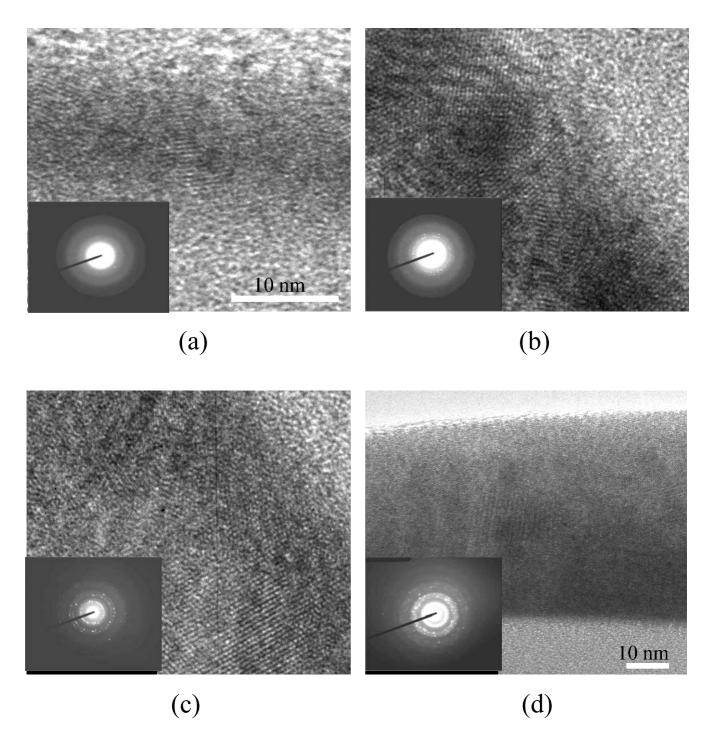

| Fig. A-5  | TEM images and diffraction patterns (insets) of the deposited Ge thin films                  |

|           | for (a) 30s, (b) 60s, (c) 180s, and (d) 600s deposition time,                                |

|           | respectively                                                                                 |

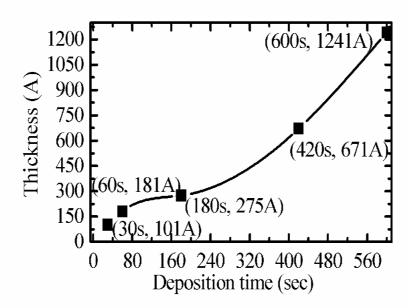

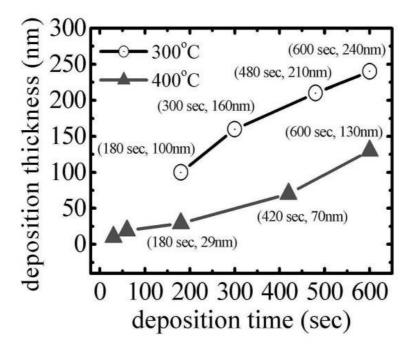

| Fig. A-6  | Ge film thicknesses (by SEM and TEM measurements) plotted as a function                      |

|           | of the deposition time at 400°C                                                              |

| Fig. A-7  | The spectrum of Ge 3d level by XPS measurement, which revealed the                           |

|           | surface conditions of the as-grown Ge films deposited onto $\mathrm{SiO}_2$ substrate at     |

|           | 300 and 400°C                                                                                |

| Fig. A-8  | AES depth profiles of Ge film deposited onto SiO <sub>2</sub> substrate at 300°C179          |

| Fig. A-9  | Ge film thicknesses (by SEM and TEM measurements) plotted as a function                      |

|           | of the deposition time at 300 and 400°C                                                      |

| Fig. A-10 | X-ray diffraction patterns of the as-grown Ge films of about 150nm in                        |

|           | thickness, deposited onto SiO <sub>2</sub> substrates at 300 and 400°C180                    |

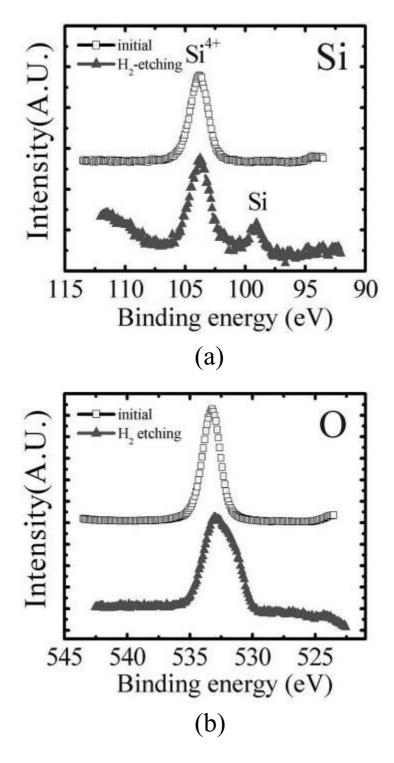

| Fig. A-11 | XPS spectra revealing the status of (a) Si and (b) O atoms of an oxidized                    |

|           | wafer before and after etching with H <sub>2</sub> plasma                                    |

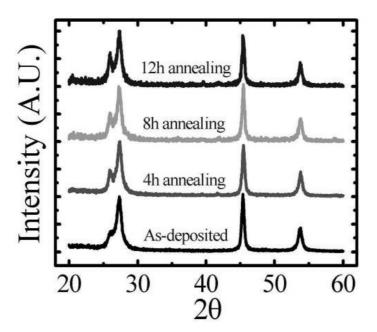

| Fig. A-12 | X-ray diffraction patterns of the as-deposited Ge film without capping $\text{SiN}_{x}$      |

|           | layer and after re-crystallization in a furnace at 400°C for various duration.               |

|           | The thickness of Ge films is around 160nm                                                    |

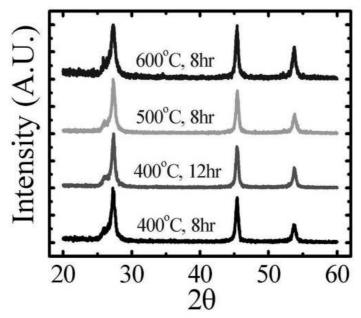

| Fig. A-13 | X-ray diffraction patterns of the as-deposited Ge film capped with a $\text{SiN}_{\text{x}}$ |

|           | layer and after re-crystallization in a furnace for various duration. The                    |

|           | thickness of Ge films is around 160nm                                                        |

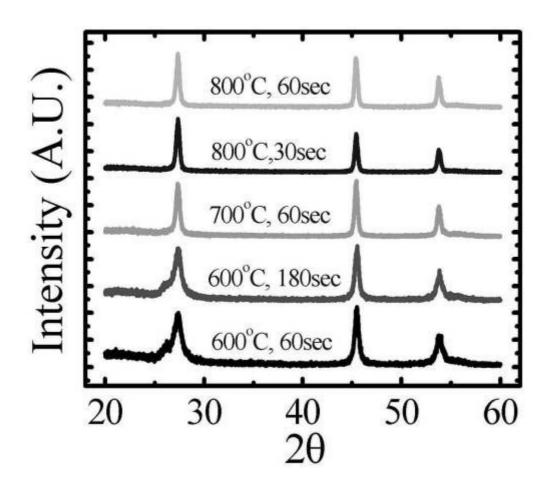

| Fig. A-14 | X-ray diffraction patterns of the as-deposited Ge film capped with a SiN <sub>x</sub>        |

|           | layer and after re-crystallization in a RTA system for various duration. The             |

|-----------|------------------------------------------------------------------------------------------|

|           | thickness of Ge films is around 160nm                                                    |

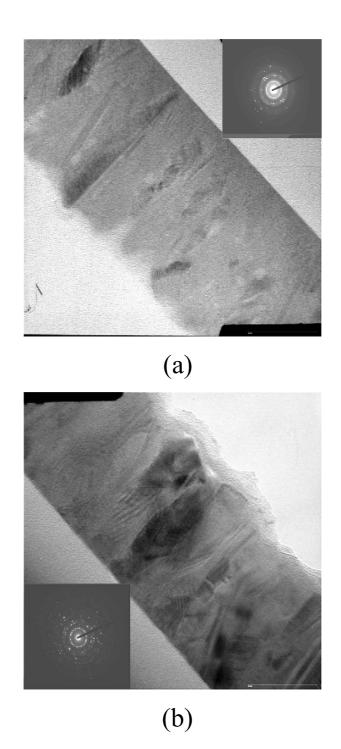

| Fig. A-15 | TEM images and diffraction patterns (insets) of (a) the Ge film deposited at             |

|           | 300°C and (b) the sample after 700°C, 60s, RTA treatment                                 |

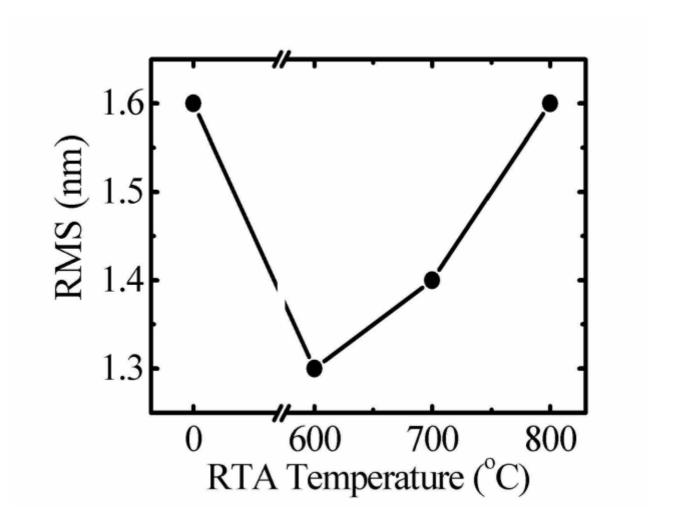

| Fig. A-16 | Surface roughness of the re-crystallized Ge films, all with thickness of                 |

|           | about 160nm, as a function of RTA temperature. The RTA process time is                   |

|           | 60 seconds                                                                               |

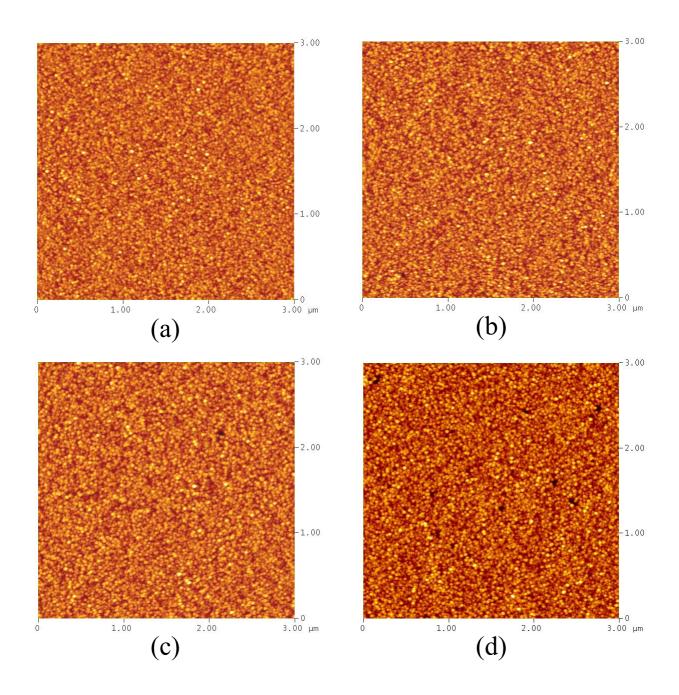

| Fig. A-17 | AFM images of Ge films obtained after RTA treatment: (a) 600 °C, 60 s; (b)               |

|           | 700 °C, 60 s; (c) 800 °C, 30 s; (d) 800 °C, 60 s                                         |

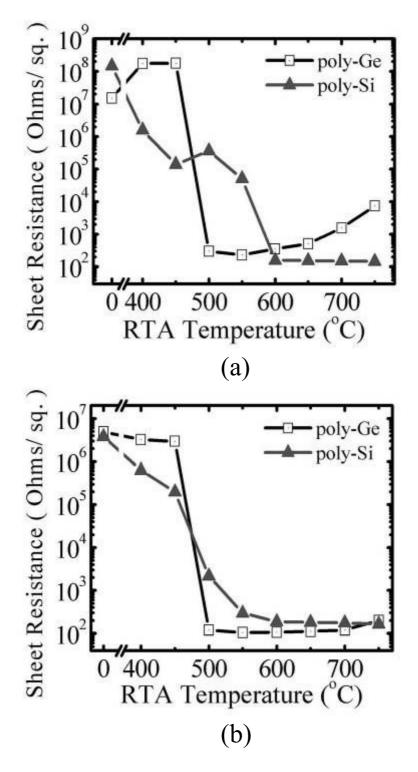

| Fig. A-18 | Sheet resistance as a function of the RTA temperature for implanted poly-Ge              |

|           | and poly-Si films incorporating (a) phosphorus and (b) boron                             |

|           | dopants                                                                                  |

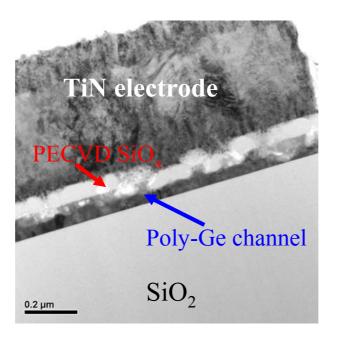

| Fig. A-19 | Cross-sectional TEM images of poly-Ge TFTs. The device structure is TiN                  |

|           | electrode / PECVD SiO <sub>2</sub> / poly-Ge channel / thick SiO <sub>2</sub> layer / Si |

|           | Substrate                                                                                |

| Fig. A-20 | Cross-sectional TEM images of poly-Ge TFTs. The device structure is TaN                  |

|           | electrode / PECVD SiN <sub>x</sub> / poly-Ge channel / thick SiO <sub>2</sub> layer / Si |

|           | Substrate. 188                                                                           |

# Chapter 1 Introduction

Low-temperature-polycrystalline-silicon (LTPS) thin-film-transistors (TFTs) have received much attention in recent years because of their increasing applications in active matrix displays (AMLCDs) [1.1]-[1.5], active matrix organic light emitting displays (AMOLEDs) [1.6]-[1.7], and memory devices [1.8]. Because of their better grain crystallinity, compared with the amorphous counterparts, higher carrier mobility and drive current can be achieved in poly-Si TFTs. The ability of fabricating high-performance LTPS TFTs enables their use in a wide range of new applications. Therefore, further improving the performance of LTPS TFTs is an interesting and important topic.

# 1-1 An Overview of Low-Temperature-Polycrystalline-Silicon (LTPS) Thin Film Transistors (TFTs)

The study of polycrystalline silicon (poly-Si) thin film transistors (TFTs) fabricated below a maximum temperature of 600°C commenced in the 1980s. The original motivation was to replace quartz substrate with low-cost glass for active matrix display applications. In the beginning, the a-Si:H (hydrogenated amorphous silicon) TFTs were applied as the pixel switching device in the first-generation active matrix liquid crystal displays (AMLCDs). The major advantages of a-Si:H TFT technology are low processing temperature compatible with large-area glass substrate and low leakage current due to the high off-state impedance. However, because of the lack of short range order, the low carrier field-effect mobility (typically below 1 cm²/(V-Sec)) of a-Si:H TFTs limited their application to the switching elements only. Integration of driver

circuits with display panel on the same substrate is very desirable because of the cost reduction in the module and reliability improvement of the system. More recently, poly-Si TFTs are employed extensively in active-matrix liquid crystal displays because of their superior performance. The effective carrier mobility in poly-Si is significantly higher than that in a-Si, so the devices with reasonably high drive currents can be achieved in poly-Si TFTs [1.9]. The higher drive-current allows smaller TFTs to be used as the pixel-switching elements, resulting in higher aperture ratio and lower parasitic gate-line capacitance for improved display performance [1.10]. Previously, poly-Si TFT technology was primarily applied on small, high-definition LCD panels for projection display systems, however, the high processing temperature made it incompatible with commercial large-area glass substrates. With the rapid development of fabrication processes which are compatible with glass substrates in recent years, the manufacture of LTPS TFTs in AMLCDs on large-are substrates attracts more attentions. Modification of process procedure for enhancing TFT performance and reducing fabrication cost become an important issue in the fabrication of LTPS TFTs on large-area glass substrates.

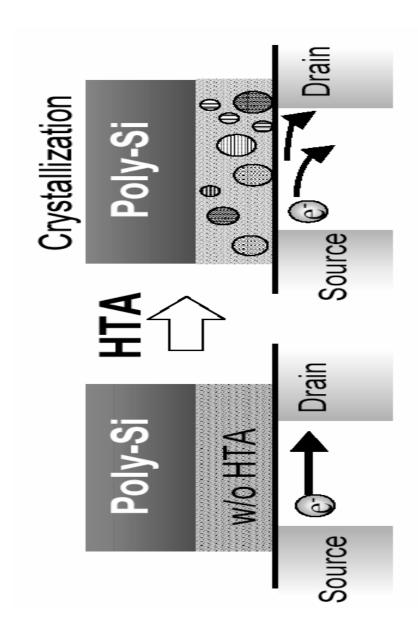

Compared to the ultra-large scale integration (ULSI) process technology, the processes and device structures ofLTPS **TFTs** are similar with metal-oxide-semiconductor field-effect-transistors (MOSFETs). The noticeable difference between LTPS TFTs and MOSFETs is that the former has to be performed at relatively low temperatures in order to be compatible with glass substrates. Due to this feature, only a-Si or poly-Si channels can be achieved on the glass substrate and the mobilities of a-Si and poly-Si are both much lower than that of c-Si (single-crystal silicon), which is widely used in conventional MOSFETs. Therefore, how to further increase the mobility of the low-temperature TFTs is one of the most important challenges. Among various process issues, the crystallization of a-Si thin films has been considered to be the most important process for fabricating high-performance LTPS TFTs. The crystallized poly-Si thin films always serve as active layer (i.e., channel) in the poly-Si TFTs. As a result, the quality of crystallized poly-Si films profoundly affects the performance of the poly-Si TFTs. In polycrystalline materials, most of defects are present in the grain boundaries. Enlarging grain size by various crystallization methods, such as solid phase crystallization (SPC) [1.11], laser crystallization [1.12-1.13], and metal-induced crystallization (MILC) [1.14-1.16], can reduce the grain boundaries and effectively promote the quality of poly-Si. The performance of devices can be improved through the high-quality poly-Si formed by crystallization technologies.

Furthermore, other low-temperature process technologies of fabricating LTPS TFTs, such as gate dielectric formation, dopant activation, defect passivation, and device structures, are also essential for producing high-performance LTPS TFTs. Although many maturely developed fabrication processes in ULSI technology can be applied to LTPS TFTs technology, some high-temperature technologies, such as thermal oxidation and dopant activation, are not suitable for LTPS TFTs. Because of the thermal budget issue, the low-temperature oxide deposited by plasma-enhanced chemical vapor deposition (PECVD) system is widely applied in LTPS TFTs as the gate dielectric. The quality of the low-temperature deposited oxide is much worse than that of the thermal oxide used in MOSFETs. Therefore, a thicker low-temperature deposited-oxide is required to keep tight rein on the leakage current, which compromises the performance of LTPS TFTs. What kind of novel gate dielectric is appropriate for the next-generation LTPS TFTs is therefore a critical challenge.

# 1-2 Motivations for Improving Low-Temperature-Deposited Gate Dielectrics Used in LTPS TFTs

Although trap states in the poly-Si thin film serving as the device channel tend to

dominate electrical behavior of the poly-Si TFTs, the quality gate dielectric is also a critical issue for the performance and reliability of TFTs. Thin oxide films can be formed using physical vapor deposition (PVD) or chemical vapor deposition (CVD), and the latter is preferred due to its better step coverage and uniformity over large area substrate. Among various CVD methods, PECVD (plasma-enhanced chemical vapor deposition) has been the "de facto" choice for the gate oxide deposition in LTPS-TFT technology due to its low-temperature process and compatibility with large-area glass substrates. However, the low-temperature-deposited oxide used in LTPS TFTs always exhibits poorer physical and electrical quality, such as high interface trap density, high gate leakage and low breakdown field, compared with high-temperature thermal grown oxide used in VLSI MOSFETs. Consequently, thicker gate oxide has to be used to prevent the high gate leakage current.

Recently, the practicability of integrating the entire system on the panel (SOP) has been vigorously investigated [1.17]. In addition to cost reduction, integration of peripheral circuits can also reduce the weight of display module and increase panel reliability. This requires that the display driving circuits contain high-performance TFTs capable of operating at lower voltages while delivering higher drive currents. For the next-generation active-matrix displays with smaller size and higher resolution, scaling down of the gate oxide in poly-Si TFTs would be an essential issue to obtain the superior device performance. Although scaling down the gate oxide can increase the drive current of TFTs, it leads inevitably to a higher gate leakage current because of the decreased quality of the low-temperature-deposited gate dielectrics [1.18].

High-κ materials have attracted a lot of attentions in scaling MOSFETs technology in recent years. With the continuous scaling of CMOS technology for device performance improvement, the large gate leakage current due to the direct tunneling mechanism exceeds the specifications (i.e., 1 A/cm<sup>2</sup>). To circumvent this critical

problem, high- $\kappa$  materials such as hafnium-based, zirconium-based, and aluminum oxide have been introduced. The introduction of high- $\kappa$  gate dielectrics can effectively reduce the tunneling leakage current due to its larger physical thickness under the same electrical thickness.

Other than the applications in MOSFETs, the high- $\kappa$  materials also have been applied to LTPS TFTs. To maintain the physical dielectric thickness while increasing the gate capacitance, several new high- $\kappa$  materials have been proposed, including Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, and HfO<sub>2</sub> [1.19–1.21]. Because Al<sub>2</sub>O<sub>3</sub> films exhibit relatively low value of  $\kappa$  (around 7) and excess fixed charge, the TFT performance enhancement is only marginal [1.22]. The narrow band-gap of Ta<sub>2</sub>O<sub>5</sub> means that a thicker film is necessary to reduce the gate leakage current of TFTs [1.23], which limits the increase in gate capacitance. Recently, hafnium dioxide (HfO<sub>2</sub>) has been applied to TFTs because of its high value of  $\kappa$  (14–20) and sufficiently wide band-gap [1.24]. Although poly-Si TFTs incorporating HfO<sub>2</sub> as the gate dielectric exhibit superior performance in many respects, several issues remain problematic: e.g., the higher gate leakage current arising from poly-crystalline HfO<sub>2</sub> films and the degraded mobility arising from additional scattering. Therefore, the pursuit of an ideal high- $\kappa$  material remains an important challenge for LTPS TFTs.

### 1-3 Organization of the Thesis

In this thesis, the advanced high-κ materials were employed to fabricate the high-performance low-temperature polycrystalline silicon thin film transistors.

In Chapter 2, a new AVD system, dedicated to the deposition of the advanced high- $\kappa$  films, was introduced briefly. Afterwards, we focused on the study in which  $HfO_2$  and  $HfSiO_x$  films were deposited under different conditions using AVD system. Both structural and electrical characterizations of the high- $\kappa$  films were presented. The effects of important deposition parameters, including the deposition temperature, the

chamber pressure, oxygen gas flow, deposition frequency, and the composition adjustment, on the physical properties of as-deposited thin films were examined. Then the thermal stability of the high- $\kappa$  films was studied with the help of post-deposition annealing (PDA) at high temperature.

the scaling limit of the thickness of the conventional low-temperature-deposited SiO<sub>2</sub> film, we tried to employ these newly-developed high-κ films to replace the conventional deposited-SiO<sub>2</sub> gate dielectric in the LTPS TFTs, as discussed in Chapter 3. Similar to the previous chapter, we presented both structural and electrical characterizations of the thick high-κ films prepared by AVD system, and employed HfO<sub>2</sub> HfSiO<sub>x</sub> films dielectrics fabricate and as gate low-temperature-compatible p-channel poly-Si thin-film transistors. The systematic study of the electrical properties of these devices was then performed. Besides, the dependence of the electrical properties of high-k TFTs on the channel length and width of the TFTs was also discussed.

Furthermore, the mechanisms of the mobility degradation, leakage current, and the reliability issues in these TFTs using different gate dielectrics were investigated in Chapter 4. The lower field-effect mobility caused by additional scatterings was found in the HfO<sub>2</sub>-TFTs. In order to clarify the degradation mechanism of the poly-Si TFTs using HfO<sub>2</sub> gate dielectric, various possible origins of the mobility scatterings were analyzed and discussed in detail. Afterwards, the leakage current behaviors among the devices with different gate dielectrics were investigated. Although TFTs incorporating high-κ gate dielectrics exhibit better on-state electrical properties than conventional TFTs containing deposited-SiO<sub>2</sub>, aggravated gate-induced drain leakage (GIDL) current was found clearly in TFTs using high-κ gate dielectrics. So, the leakage mechanism of poly-Si TFTs using high-κ gate dielectrics was addressed. Moreover, the reliability issues of these TFTs with different gate dielectrics were characterized by

varying-temperature tests and negative bias temperature instability (NBTI) stress. In the poly-Si TFTs, due to the poor thermal conductively of the glass substrate and high operation voltage, the NBTI effect was more important in the reliability issues. Due to the grain boundary in the channel regions and much severe gate induced drain leakage (GIDL) effect of poly-Si TFTs, the NBTI degradation mechanism in poly-Si TFTs could be different from that in MOSFETs. By measuring and analyzing the transfer characteristics before and after stressing for various stress times and temperatures, we determined the effects of NBTI on the poly-Si TFTs incorporating high-κ dielectrics.

Finally, conclusions as well as future prospects for further research were given in Chapter 5.

## Chapter 2

# Characterizations of High-κ Films Deposited by Atomic-Vapor deposition

#### 2-1 Introduction

As the dimensions of complementary metal oxide semiconductor (CMOS) devices are scaled into the nanometer regime, the equivalent oxide thickness (EOT) of the gate dielectric decreases steadily to thinner than 1nm. Its leakage current under normal operation bias falls into the direct tunneling regime. For future generations of metal-oxide-semiconductor field-effect transistors (MOSFET), the current gate oxide layer  $(SiO_2 \text{ or } SiO_xN_y)$  will need to be replaced with a new material possessing a higher dielectric constant ( $\kappa > 3.9$ ). High- $\kappa$  materials are employed to increase the physical thickness of the gate insulator while maintaining the same EOT and gate capacitance, thus reduces significantly the tunneling leakage current. Although many high-k materials are proposed to replace silicon dioxide as gate insulator, HfO2 is the most promising candidate for its excellent advantages, such as a suitable dielectric constant (~25) [2.1], high band-gap energy (~ 5.9eV), and suitable tunneling barrier height for both electron and hole (>1eV). However, HfO<sub>2</sub> is easily crystallized during deposition or following annealing processes, and crystallization increases the leakage current via grain boundaries. In order to improve the relatively low crystallization temperature of around 600°C of pure HfO<sub>2</sub>, alloying HfO<sub>2</sub> with Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub> has been proposed[2.2]-[2.3]. Since their silicon or aluminum binary oxides, such as HfSiO<sub>x</sub> and HfAlO<sub>x</sub>, retain an amorphous structure after high-temperature treatment, these binary oxides are now the most promising candidates to become the gate dielectric for

next-generation MOSFETs [2.4]-[2.8].

Recently, high-κ materials have been investigated using several deposition techniques including physical vapor deposition (PVD) [2.4], atomic layer deposition (ALD) [2.9], and pulsed laser deposition [2.10]. Although PVD is a simple technique for depositing new materials for evaluation in an academic organization, it may cause severe plasma damage to the electrical devices and is not preferred by industries because of poor step coverage and thickness uniformity. Chemical vapor deposition has the advantages of uniform thickness over large substrate areas and good conformal step coverage. In contrast to ALD, it is relatively easy to dope the HfO<sub>2</sub> using CVD, which may be necessary for future gate dielectrics.

In this chapter, we employed the new atomic-vapor deposition (AVD) system to deposit the high-κ films. The AVD system would be introduced briefly in section 2-2. Afterward, we focused on a study in which HfO<sub>2</sub> and HfSiO<sub>x</sub> films were deposited under different conditions using AVD system. We present both structural and electrical characterizations of the high-κ films. First of all, the deposition and evaluation of HfO<sub>2</sub> thin films have been performed in section 2-3. The effects of important deposition parameters, including the growth temperature, the chamber pressure and the gas flow of oxygen on the physical properties of as-deposited thin films have been examined. And then, the thermal stability of HfO<sub>2</sub> films would be tested by high temperature post-deposition annealing (PDA). In the second part, the Si incorporation into HfO<sub>2</sub> films was investigated and the results of HfSiO<sub>x</sub> films were discussed in section 2-4. The effects of the growth temperatures, the deposition frequencies and the composition adjustments on the physical and electrical properties of as-deposited thin films have been examined.

### 2-2 Overview of Atomic-Vapor Deposition (AVD) System

Figure 2-1 illustrates the schematic diagram of the AVD system. The main parts of the AVD system contain an AIXTRON horizontal reactor and a liquid-delivery TRIJET-TM vaporizer. Metal-organic precursors are used as the source of the high-k film and kept at room temperature in liquid phase in a stainless tank. The precursor would be injected into the vaporizer via high-speed electro-mechanical valves and the injector plays the important role to control the injection amounts of the precursors. The injected amounts of the precursors can be controlled exactly by adjusting the injection numbers and opening time of individual injectors. In our experiment, the opening times of the injectors were all fixed at 0.8 msec. The injection periods and pulses can be adjusted to control the thickness and composition of the deposited films. The liquid precursor was injected to the vertical vaporizer and transferred from liquid type to gas type immediately. The temperature of vaporizer (160°C and 170°C in our experiment) could be adjusted according to the kind of precursors. Argon gas would be used as carrier gas to carry the vaporized precursor into the reactor through the showerhead. The process gas, oxygen in our experiment, would be heated first in gas-box and then mixed with vaporized precursors in the showerhead. Finally, the mixed gases flowed to the process reactor and film deposition would take place on the hot substrate. The deposition parameters, including deposition temperature, chamber pressure, oxygen gas flow, injection frequency and pulse numbers, could be fine-tuned to obtain the adaptable films in different device applications. Among all process parameters, the substrate temperature is the key issue to affect the quality of the as-deposited films.

## 2-3 Structural and Electrical Characterizations of HfO<sub>2</sub> Films

#### 2-3.1 Experimental

$HfO_2$  films were deposited by liquid-injection atomic-vapor deposition (AVD) system and the liquid precursor was tetrakis(diethylamido)hafnium,  $Hf[N(C_2H_5)_2]$ ,

which was dissolved in octane to make a 0.05 M solution. The evaporation temperature of vaporizer was 170°C. Argon was used as the carrier gas, with a flow rate of 200 sccm, and oxygen as the oxidant, with a flow rate of 100 to 500 sccm. Substrate temperatures were in the range from 340°C to 500°C, and the chamber pressures were varied from 1.5 to 5mbar. Prior to the deposition, the 6-inch silicon substrates were treated with standard RCA clean. After the cleaning process, the HF-treatment was to immerse wafers into a 100:1 diluted HF solution and then spun dry without rinse in DI water. Subsequently, wafers were put immediately into AVD system for HfO<sub>2</sub> deposition to prevent the native oxide formation. The thickness of HfO2 was controlled by the injection pulse numbers. The deposition rate was extracted by measuring the thickness of thick HfO<sub>2</sub> films with N&K analyzer. Because the system was designed for 200 mm wafers, the 150 mm wafers would be placed on a quartz adaptor and transferred to the process reactor. After film deposition, post-deposition annealing (PDA) was performed on all samples to investigate its impact on material properties and electrical characteristics of HfO<sub>2</sub> films. The fundamental physical properties of these films were analyzed by many techniques, such as grazing incidence x-ray diffraction spectrum (GI-XRD), x-ray photoelectron spectrum (XPS), transmission electron microscopy (TEM) and conductive atomic force microscopy (C-AFM). In addition, the electrical characteristics of the HfO<sub>2</sub> films were extracted from the capacitors and MOSFET devices. For electrical analysis, a precision impedance meter (Agilent 4284) was used for C-V measurements and a semiconductor parameter analyzer (Agilent 4156C) was used for I-V measurements.

### 2-3.2 Thickness Dependence of HfO<sub>2</sub> Films on Deposition Temperature

As mentioned above, the substrate temperature is the most important process parameter of as-deposited films by AVD system. The thickness of as-deposited HfO<sub>2</sub>

films versus substrate temperature is shown in Figure 2-2. It can be seen clearly that the film thickness decreases monotonously as the substrate temperature increases. For conventional CVD systems, the deposition mechanisms could be divided into two regimes: Reaction-rate-limited regime at low temperature and mass-transport-limited regime at high temperature (Figure 2-3). The CVD mechanism, in which the growth rate decreases as the deposition temperature increases, is contrary to our experimental data. Possible reasons are described as follow: Firstly, although the liquid precursor was evaporated at the vaporizer, the vaporized precursor still contained a lot of organic elements. When the substrate temperature was higher, the precursor would be decomposed more quickly and completely during film deposition step. And then, the large amount of decomposed organic elements could not be pumped out immediately and retarded subsequent precursors to go to the surface. So the thinner films obtained at higher deposition temperature could be attributed to the reduced surface chemical reaction. Secondly, the supply of the precursor was discrete and limited in AVD system. The desorption and flow rate would increase at higher temperature due to the higher thermal energy. For this reason, the surface reaction time became shorter and the thinner deposited film would be obtained.

# 2-3.3 Structural Characterizations of HfO<sub>2</sub> Thin Films by XRD Analysis

Figure 2-4 shows the GI-XRD spectra of the HfO<sub>2</sub> films, which were deposited at various temperatures ranging from 340°C to 500°C. The chamber pressure and oxygen flow were fixed to 1.5 mbar and 500 sccm, respectively. For the samples deposited below 400°C, the intensities of the signals are extremely low. However, a bump at the position of around 57° has been clearly observed. We speculate that thin films deposited at the temperature below 400°C consist of diverse-oriented small granules, and the

bump is the convolution of these discrete signals of the granules. As a result, it is unlikely to exactly identify the structure of HfO<sub>2</sub> thin films with this broad and weak x-ray signal peak. The only thing can be confirmed is that films deposited at such low temperature range have poor crystallinity. This trend may imply that lower temperature will lead to the formation of amorphous structure. Concomitant with increasing temperature, more sharp peaks, which are identified to come from monoclinic crystal structure, become more visible. It means that thin film will undergo structural phase change and start to form monoclinic polycrystalline structures as the deposition temperature is higher than 460°C. The corresponding orientations in monoclinic structure are identified and shown by the labeled indices.

The effect of chamber pressure on the structure of thin films is demonstrated in Fig. 2-5. It is found that the crystallinity of the deposited film also strongly depends on the pressure conditions. Obviously, lower pressure results in better crystallinity for the samples grown at the same temperature. This is related to longer mean free path of reactive species in lower pressure ambient.

Figure 2-6 shows the XRD spectra of HfO<sub>2</sub> thin films deposited at 340°C with various post-annealing conditions. The initial aim of depositing thin film at such low temperature of 340°C is to see if HfO<sub>2</sub> can retain its amorphous phase even after subjecting to higher thermal cycles in subsequent processes, for example, during annealing for activation of dopant impurities in S/D region. The advantages of amorphous thin films in the device applications are the lower leakage current, superior heterogeneous interface quality, blocking capability against impurity diffusion from poly-electrode. Rapid thermal annealing in N<sub>2</sub> ambient for 30s was employed to test the thermal stability of the deposited HfO<sub>2</sub> films. However, the HfO<sub>2</sub> film is not a good diffusion barrier for O atoms, HfO<sub>2</sub> film starts to crystallize as annealing temperature is above 650°C and the crystallinity of deposited films is enhanced by increasing RTA

temperature, as shown by increasing signal intensity. These results show that the HfO<sub>2</sub> film will depict polycrystalline structure above 600°C, no matter at film deposition or subsequent high-temperature annealing.

## 2-3.4 Chemical Bonding and Composition of HfO<sub>2</sub> Thin Films by XPS Analysis

Chemical characterizations of HfO<sub>2</sub> films were accomplished by x-ray photoelectron spectroscopy (XPS) utilizing monochromatic and standard Al x-ray source. The results are shown in figure 2-7. Detected elements in thin films are hafnium (Hf), oxygen (O), and carbon (C). In order to avoid the undesirable carbon contamination on the sample surfaces, XPS analyses were also performed with ion milling. The low energy ion sputtering time is 15 sec, 3 min, and 8 min, respectively. Negligible damage by low energy ions during depth profiling could be assumed since no significant shift of the binding energies is observed. The relative contents of Hf, C, and O elements, which were determined by the spectra of the non-sputtering and 8min sputtering samples, are summarized in Table 2-1. It is found that the relative intensity of C<sub>1s</sub> signals decreases drastically after sputtering. This result is reasonable due to the fact that all air-exposed materials will have a thin film deposition, composed primarily of hydroxide (i.e., alcohol-type, C-OH units). After removing this thin layer, the signals originating from purer HfO<sub>2</sub> can be obtained. Estimating from the data of 8-min sputtered samples, the content of C elements incorporated in the bulk of HfO<sub>2</sub> thin films during deposition process is only at the level of approximately 2.56%. This result strongly suggests that the decomposition of the employed Hf-precursor is very effective at 400°C. Therefore, the carbon atoms contained in the ligand can easily be evacuated. As a consequence, the concern of high level C incorporation using other Hf-precursors, such as alkoxdes and β-diketonates, doesn't apply to the use of the

tetrakis(diethylamido)-hafnium precursor. With such low C concentration level, thin films are be expected to have lower defect density, resulting in more robust thin films from the viewpoint of reliability.

Figure 2-8 shows Hf<sub>4f</sub> and O<sub>1S</sub> XPS spectra as a function of deposition temperature. The binding energy of Hf-O bond is nearly the same among all samples deposited at different temperatures. This result also means that the Hf precursor, Hf[N(C<sub>2</sub>H<sub>5</sub>)<sub>2</sub>], is easily decomposed above 360°C to form the HfO<sub>2</sub> films. Nevertheless, it can be seen clearly that the separation of the two peaks of Hf spectra, Hf 4f<sub>7/2</sub> and Hf 4f <sub>5/2</sub>, becomes more apparent at higher deposition temperature. This phenomenon shows that the composition of HfO<sub>2</sub> becomes more stoichiometric at higher deposition temperature; in contrast, the impurities of the organic precursor are more easily incorporated into HfO<sub>2</sub> system at lower deposition temperature. The proof that the binding energy of Hf-O bond in a silicate film is about 1eV higher than that of Hf-O bond in a pure HfO<sub>2</sub> system will be given in section 2-4.

### 2-3.5 Structural Images of HfO<sub>2</sub> Thin Films by TEM Analysis

Figure 2-9 shows the images of plane-view TEM for (a) the HfO<sub>2</sub> sample deposited at 400°C and the samples with subsequent (b) 600°C, (c) 800°C, (d) 1000°C post-deposition annealing for 30sec in N<sub>2</sub> ambient, respectively. There are obviously two contrast regions in all the samples: dark and bright regions; with the dark areas embedded in the bright regions. At first glance, the spherical-shaped dark regions would be easily recognized as polycrystalline grains. However, only a few of them in as-deposited sample show crystalline diffraction patterns. This poor crystallinity has been evidenced by broad x-ray peaks, which become sharper concomitant with enhancing growth temperature. The contrast is supposed to be caused by the different compositions. Dark region is more likely to be produced by Hf-rich composition while