# 國立交通大學電子工程學系電子研究所博士論文

高性能低溫多晶矽薄膜電晶體 之製程技術與特性研究

1896

Study on the Process Technologies and Characteristics of High-Performance Low Temperature Polycrystalline Silicon Thin-Film Transistors

研究生:蔡春乾

指導教授: 鄭晃忠博士

中華民國 九十七 年 一 月

#### 高性能低溫多晶矽薄膜電晶體之製程技術與特性研究

#### Study on the Process Technologies and Characteristics of High-Performance Low Temperature Polycrystalline Silicon Thin-Film Transistors

研究生: 蔡春乾 Student: Chun-Chien Tsai

指導教授: 鄭晃忠 博士 Advisor: Dr. Huang-Chung Cheng

#### **A Dissertation**

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao Tung University

National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

in

**Electronics Engineering**

January 2008 Hsinchu, Taiwan, Republic of China

中華民國 九十七 年 一 月

#### 高性能低溫多晶矽薄膜電晶體 之製程技術與特性研究

研究生:蔡春乾 指導教授:鄭晃忠 博士

國立交通大學電子工程學系暨電子研究所

#### 摘要

多晶矽薄膜電晶體因為具有較高的載子移動率,及可將周邊驅動電路與液晶面板積體化至玻璃基板上來降低液晶顯示器之生產成本的優勢,使得它成為液晶顯示技術應用中的關鍵元件,並且在高附加價值與多功能整合的系統面板(System-on-Panel)的應用及三維積體電路(3-D ICs)的實現上具有很大的潛力。在現階段,採用準分子雷射退火法對非晶矽薄膜進行再結晶是最有潛力的量產結晶技術,藉由達到快速熔融與固化再結晶的方法,可得到一高品質的多晶矽薄膜並且可以保持玻璃基板不受到高溫的影響。雖然透過準分子雷射可有效的提升多晶矽層的結晶性,但此方法仍有些許缺點,如隨機的晶粒邊界及晶粒分佈、大晶粒的製程窗口較窄小、主動層和介電層之間造成大的粗糙界面等等。在本篇論文裡,我們將提出多項雷射結晶方法及元件結構來增進低溫多晶矽薄膜電晶體的特性。

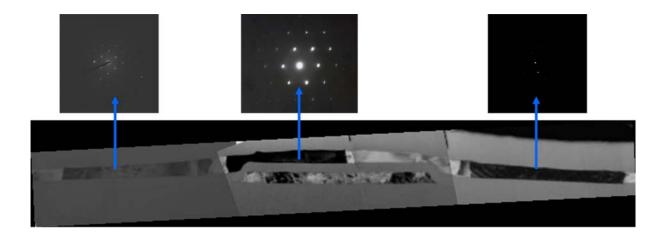

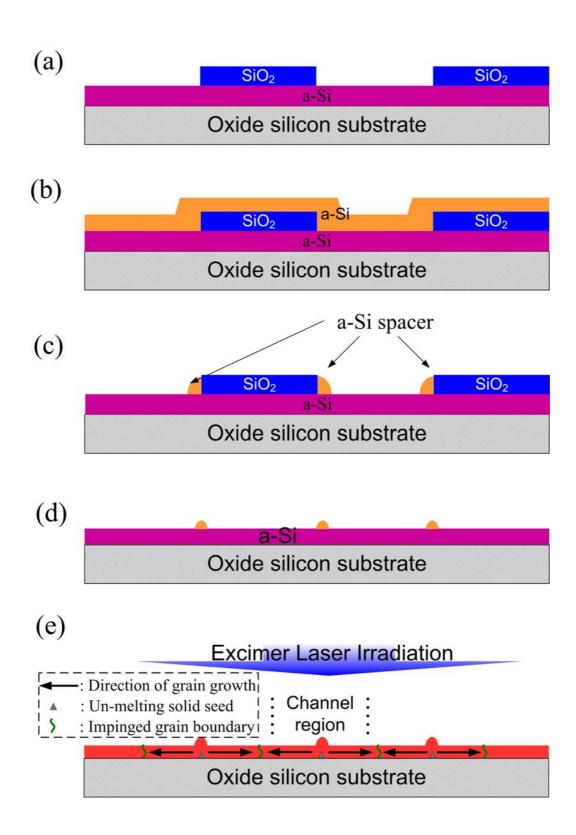

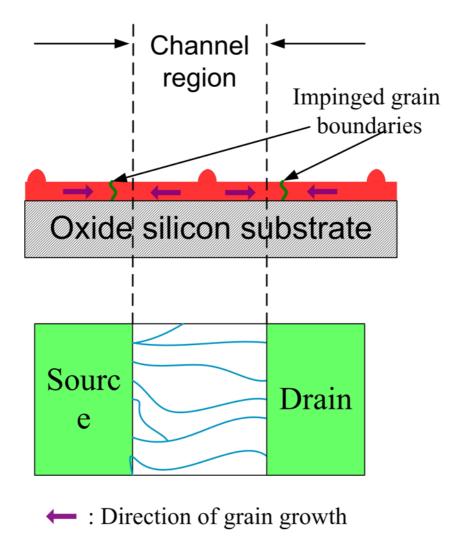

首先,為了改善低溫多晶矽薄膜電晶體的電特性,我們先針對元件通道的多晶矽薄膜結晶性進行改善。一種我們具有晶粒邊界位置控制的底閘極低溫多晶矽薄膜電晶體方法將被提出而加以探討。其結晶機制敘述如下,因為底閘極結構邊緣台階區提供了較厚非晶矽層,在準分子雷射退火時,我們只需將雷射能量控制在可以使薄區的非晶矽薄膜

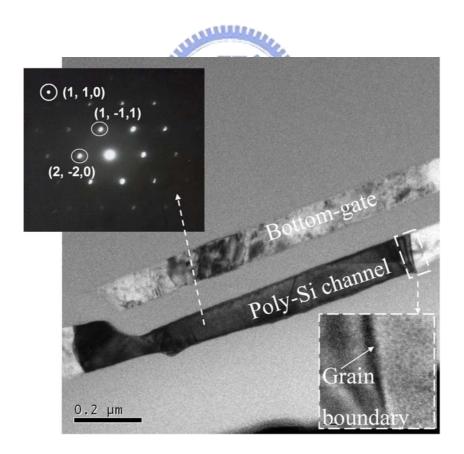

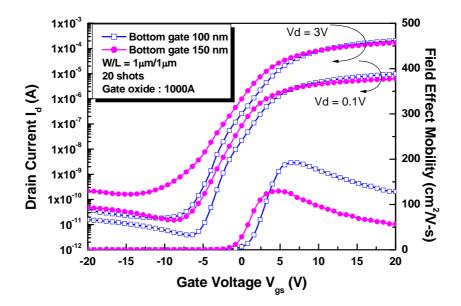

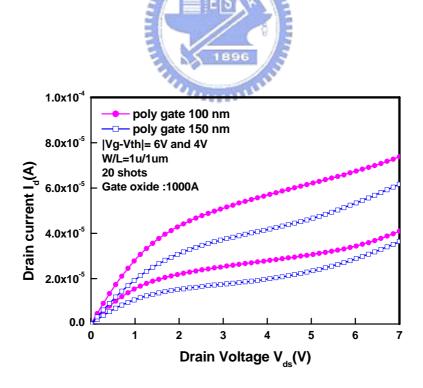

完全熔解的能量密度以上,同時讓厚區的非晶矽薄膜部分熔解而確保留下部分微晶矽作為晶種,就可以得到一致分佈的大型晶粒成長,因此可以提升薄膜的均勻性及元件的效能。由實驗的結果分析可知,我們可以得到最大長度約為  $0.85\,\mu$ m 長的人為控制晶粒。我們也製作出單一晶粒邊界的低溫多晶矽薄膜電晶體,其載子移動率可達到  $330\,\mathrm{cm}^2$  / V-S,同時閘極引起的汲極漏電和紐結效應也減少了,而且元件的均勻性也大幅提升。而且在閘極偏壓的可靠度量測之下,我們發現單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體有較小的起始電壓漂移量及較高的崩潰電場,因此更適用於元件的微小化。

雖然單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體表現出良好的電特性,由於偏離的黃光微影製程,造成源極(汲極)相對於閘極的離子佈植不對稱,使的元件的電特性不對稱。因此我們結合背後曝光方法與單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體製作出新穎之自我對準的單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體的良好特性,自我對準的單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體的良好特性,自我對準的單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體也表現出良好的電對稱性。如此一來我們更能將自我對準的單一晶粒邊界的底閘極低溫多晶矽薄膜電晶體應用於畫素電路中的開關元件。

將元件縮小,雖然可以進一步的提升多晶矽薄膜電晶體的電特性,但是也遭遇到嚴重的短通道效應,尤其是薄膜電晶體因為本身通道較多的缺陷及低溫製程,短通道效應更是較傳統金氧半場效電晶體明顯嚴重,因此雙閘極結構結合通道晶粒成長的技術也在本論文提出,藉由該底閘極的準分子雷射結晶法,通道中的晶粒成長控制來得到較好的結晶性,與上下雙閘極對通道的耦合來改善閘極對通道的控制能力,其 N 型元件以單通道長度換算之等效載子移動率可超過 1000 cm²/V-s,而 P 型元件則超過 400 cm²/V-s。此元件有高驅動電流,高開關電流比,優異的短通道抵抗力,較陡峭之次臨界擺幅,較小的汲極誘導能障下降(DIBL),同時均勻性也得到改善。

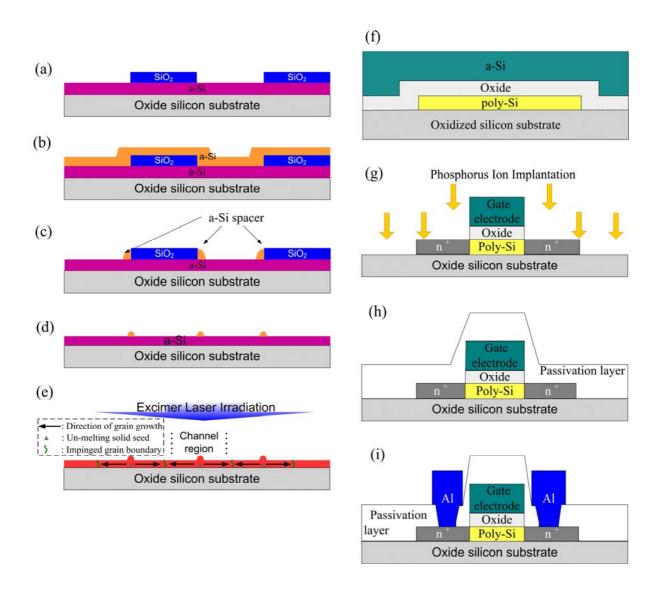

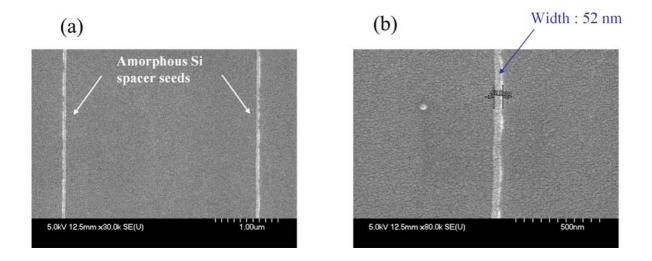

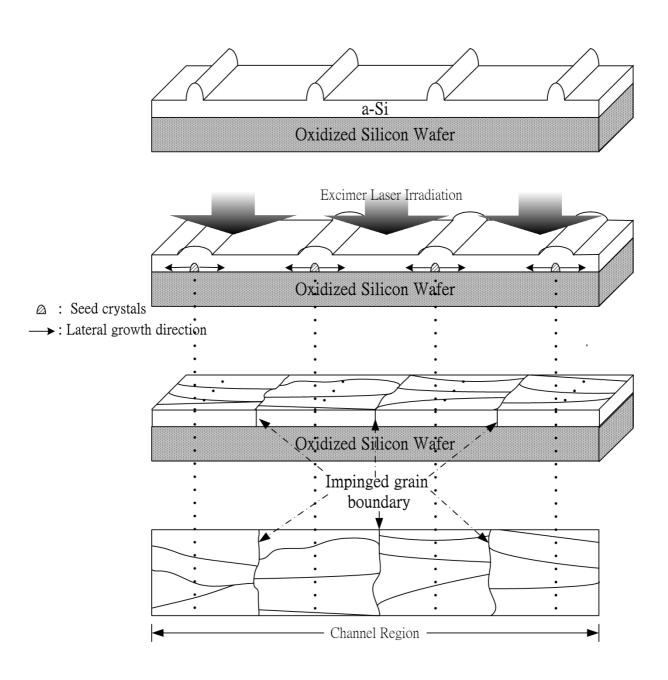

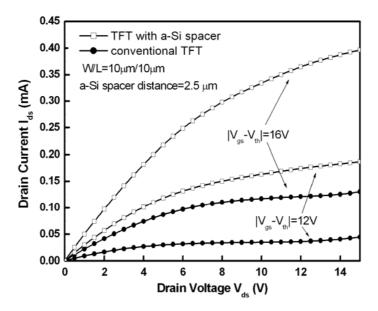

雖然利用底閘極的準分子雷射結晶技術可以有效的改善多晶矽薄膜結晶性,但是不可避免的,在低溫多晶矽薄膜電晶體的通道中存在一高角度的晶粒邊界,進而對於元件電特性造成劣化及耐用度上的問題。因此我們提出了一個新穎的側向雷射結晶方式-間際壁式結晶法-來消彌通道中的高角度的晶粒邊界,其結晶機制是利用空間上的熱傳機

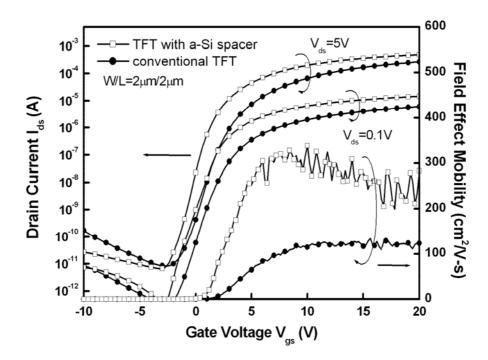

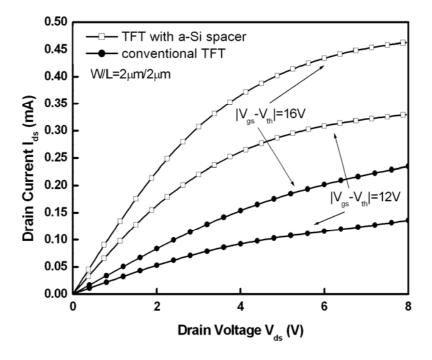

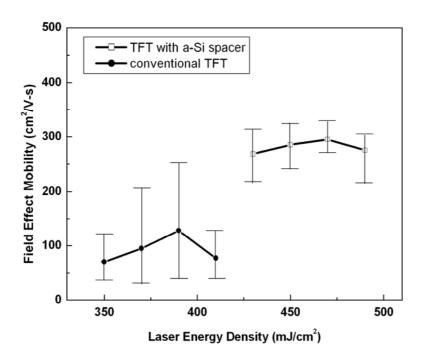

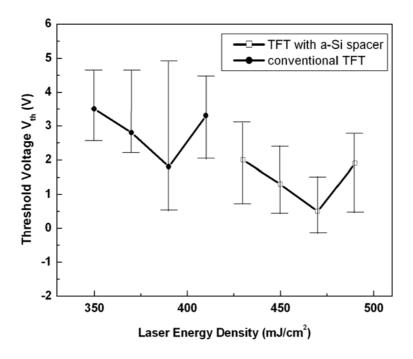

制來達成晶粒橫向成長的目的,首先利用傳統間隙壁法製作出 50 奈米大小的晶種,並在局部微小區域產生兩種厚度不同的非晶矽薄膜,當準分子雷射照射在此一結構上,使較薄的區域完全熔融時,而間隙壁較厚的區域部分熔解,晶粒便會以這些非晶矽間隙壁為結晶起始點,做橫向成長,再藉由適當的安排間隙壁與元件通道的相關位置,我們將可以消除通道中所有垂直電流方向的晶粒邊界,更進一步的改善元件的載子移動率與均勻性。以通道長度為 2 μm 的元件為例,以此結晶方法做出的低溫多晶矽薄膜電晶體其載子移動率可以到達 288 cm²/V-s,而傳統的元件的載子移動率只有 129 cm²/V-s.。

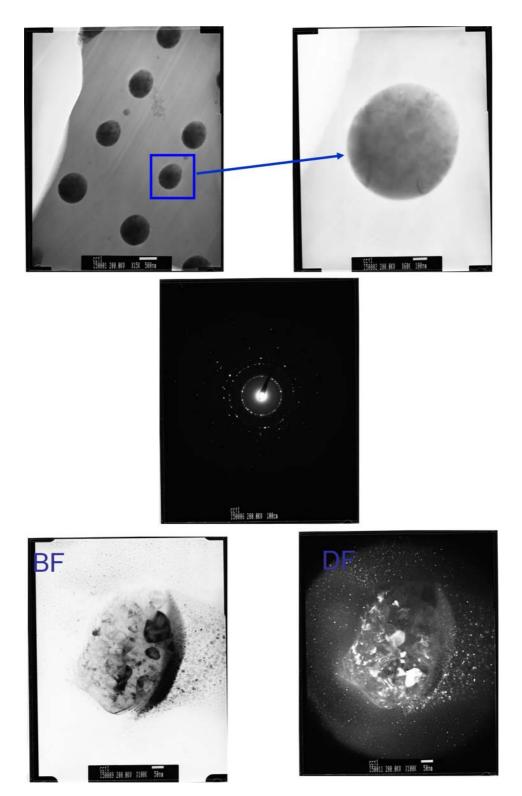

為了更進一步的提升多晶矽薄膜電晶體的驅動能力,達到一類似絕緣層上覆晶矽(Silicon-On-Insulator-like)金氧半場效電晶體的效能,進而實現 SOP 或 3D ICs 的夢想,無晶粒邊界的單晶矽電晶體(Single-grain TFT)是最終目標的元件,因此我們提出了一個新穎的二維晶粒控制側向成長的雷射結晶方式,結合上述之非晶矽間隙壁及先定義矽薄膜之結晶法來分別達成 X 軸及 Y 軸的熱梯度,進而完成單晶粒之側向晶粒成長。從實驗分析結果發現,我們可以得到一直徑為 1.8 μm 大的圓型週期性單晶粒矽薄膜。以通道長度為 1.5 μm 的元件為例,以此結晶方法做出的低溫多晶矽薄膜電晶體其載子移動率可以到達 308 cm²/V-s,開關電流比則高於 108,且具高度的均勻性。

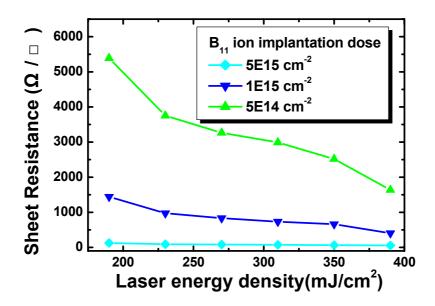

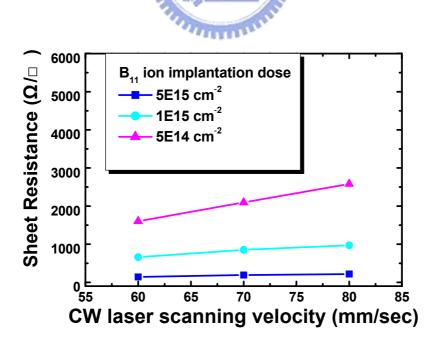

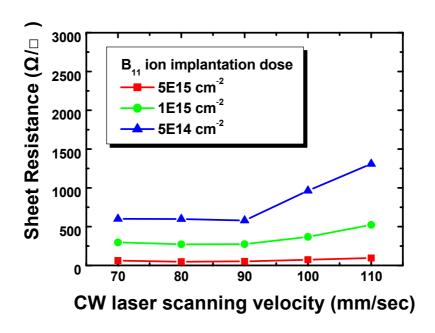

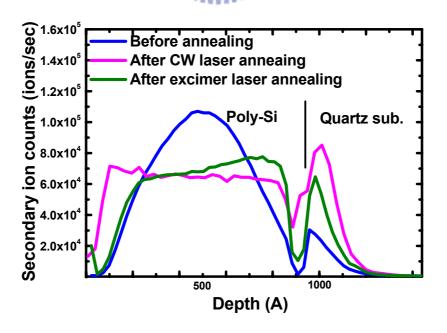

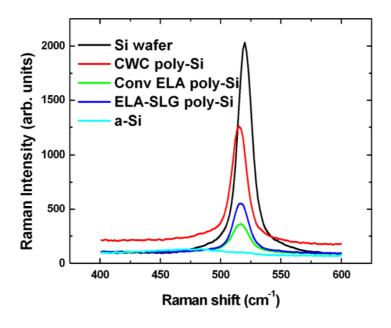

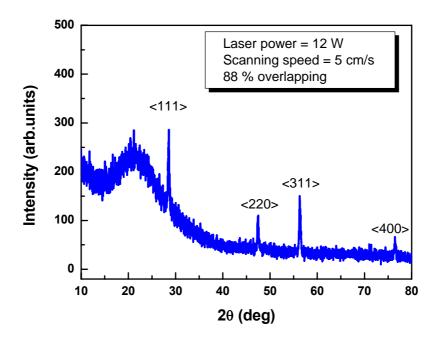

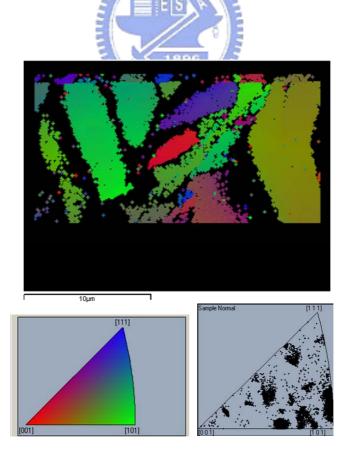

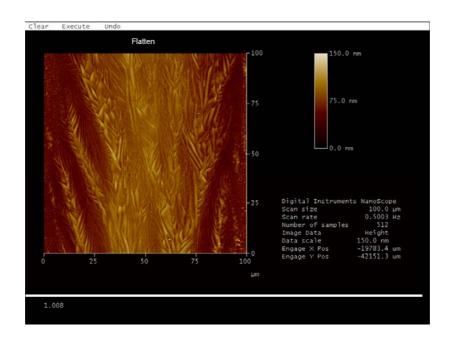

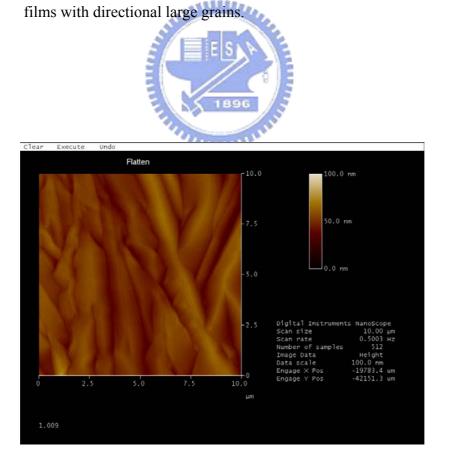

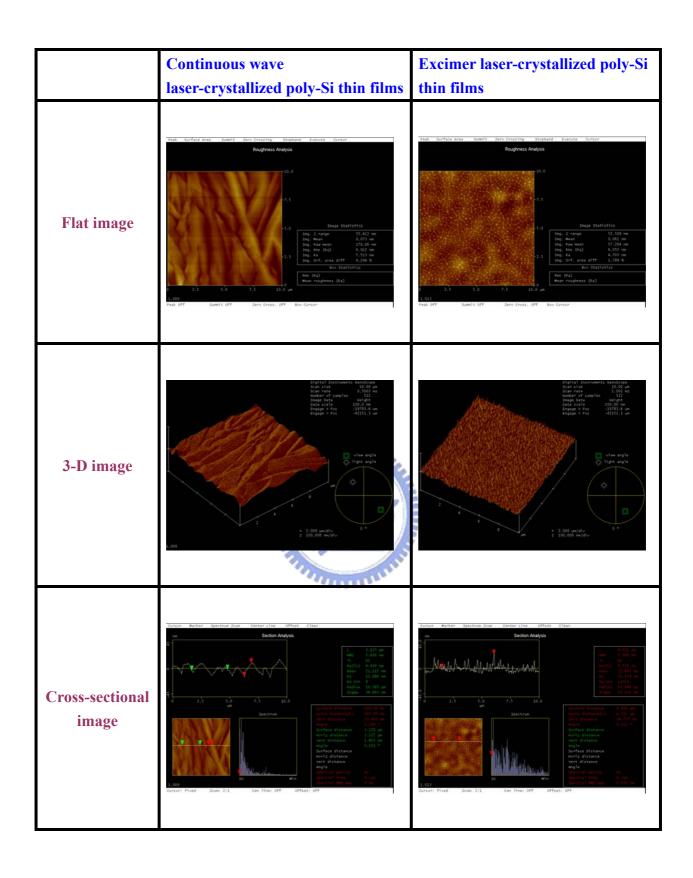

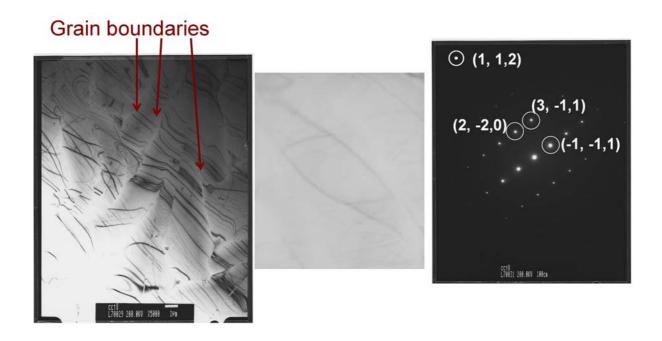

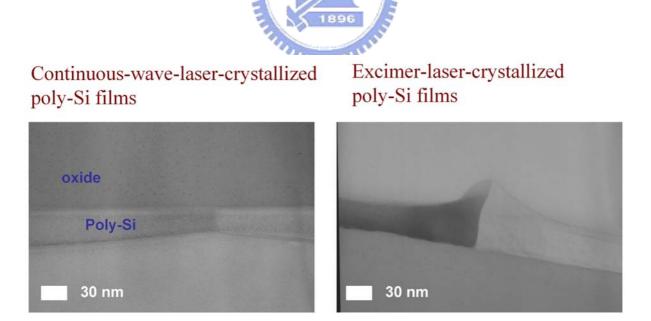

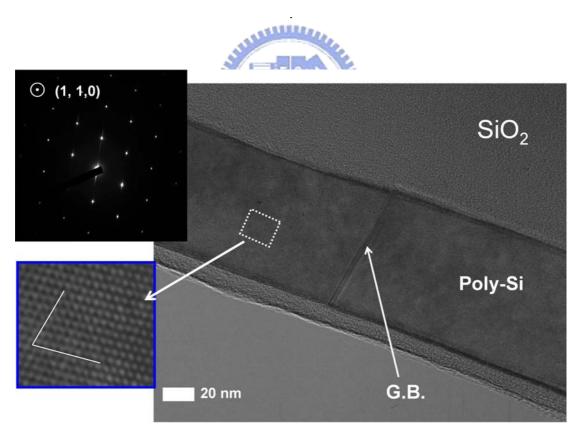

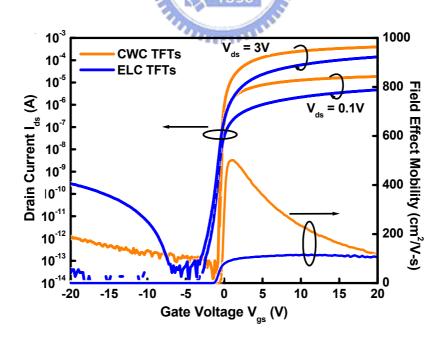

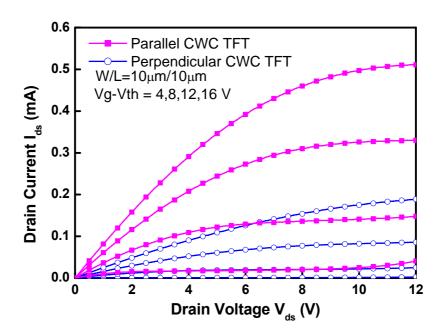

上述的結晶法雖然可以達成大晶粒成長及高性能薄膜電晶體的目的,而本論文亦提出一新式的固態連續波雷射(Continuous-wave Laser)退火技術,直接利用控制掃瞄速度及掃瞄功率來達成晶粒橫向成長。一長度達  $15~\mu m$  的多晶矽薄膜晶粒可以製作出來而不損傷到玻璃基板,而實驗結果亦顯示矽薄膜具有極佳的結晶性,同時其晶粒邊界位置的表面粗糙度極為平順。利用連續波雷射結晶法製作的低溫多晶矽薄膜電晶體擁有優異的電特性,例如較高的電子移動率(n 通道的其載子移動率可達  $500 cm^2/V$ -s,而 p 通道的為  $200 cm^2/V$ -s)及較高的開關電流比。另外,我們也探討了利用連續波雷射在掺雜活化的退火特性,其由四點探針分析可得一片電阻低於  $50~\Omega/\Box$ ,同時由二次離子質譜分析儀得到一均勻分佈的掺雜雜質,因此連續波雷射退火法是一個低熱預算和高效率的活化方法。由於連續波雷射結晶法製作大晶粒流程十分簡單,因此使用連續波結晶法製作的低溫多晶矽薄膜電晶體的亦極適合於未來系統面板的應用。

## Study on the Process Technologies and Characteristics of High-Performance Low Temperature Polycrystalline Silicon Thin-Film Transistors

Student: Chun-Chien Tsai Advisor: Dr. Huang-Chung Cheng

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

#### **ABSTRACT**

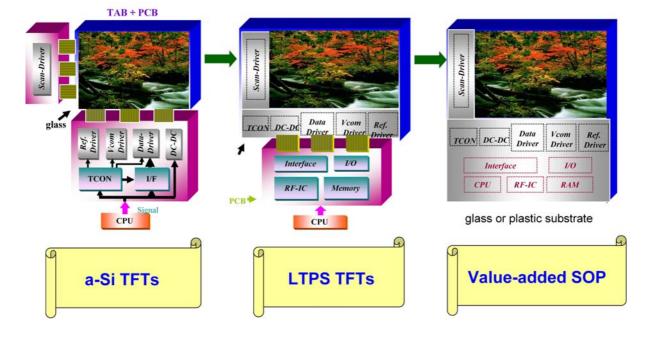

Low-temperature polycrystalline silicon (LTPS) thin film transistors (TFTs) have been extensively studied for active matrix flat panel displays (AMFPDs), full-function system-on-panel (SOP), and potential for the 3-dimensional integrated circuits (3D-ICs) applications owing to their high field-effect mobility, low power consumption, high reliability, high resolution, and low fabrication cost by the integration of driver and controller ICs. At this moment, excimer laser crystallization (ELC) of amorphous silicon (a-Si) thin films seems to be the most promising method for its great advantages in mass production and high quality silicon grains without damage to the glass/plastic substrates. Although large grains can be attained in the super lateral growth (SLG) regime by ELC, many fine grains still spread between these large grains due to the narrow process window for producing large-grain poly-Si and highly rough interface. Consequently, non-uniform and randomly distributed poly-Si grains will result in the large variation of TFT performance when the laser energy density is controlled in the SLG regime, especially for the small-dimensional TFTs. In this

thesis, many approaches, including techniques of excimer-laser-crystallized poly-Si thin films, advanced device structures, and diode-pumped solid-state (DPSS) continuous-wave (CW) laser annealing, have been proposed to further enhance the performance of LTPS TFTs.

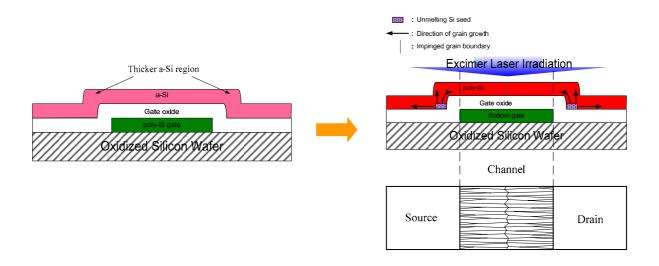

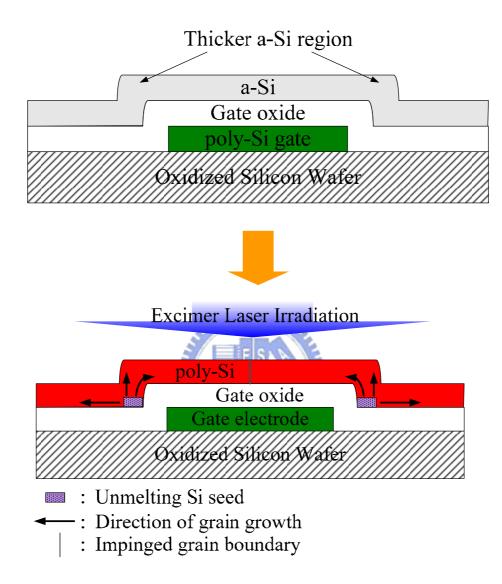

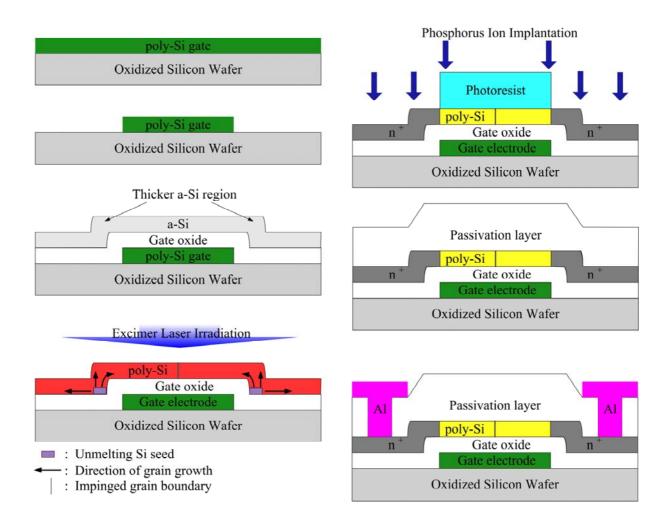

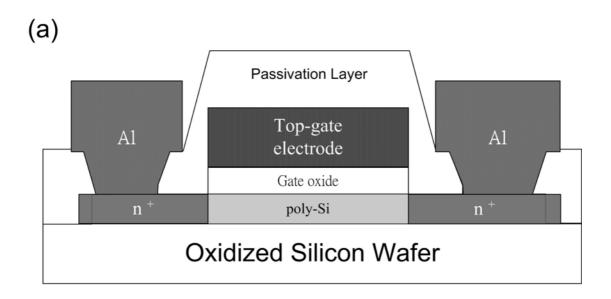

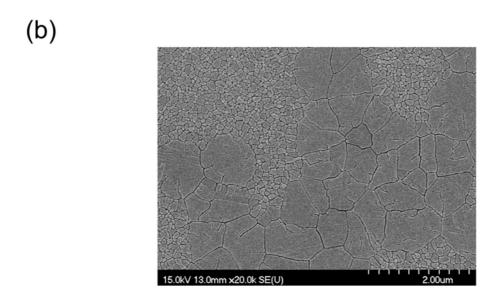

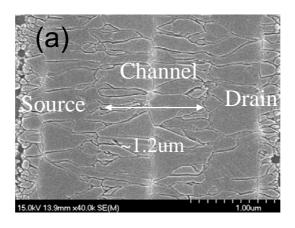

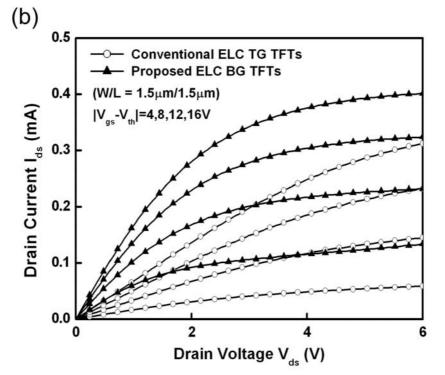

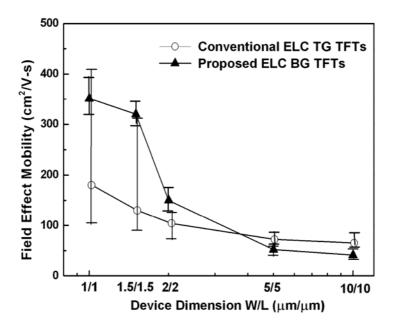

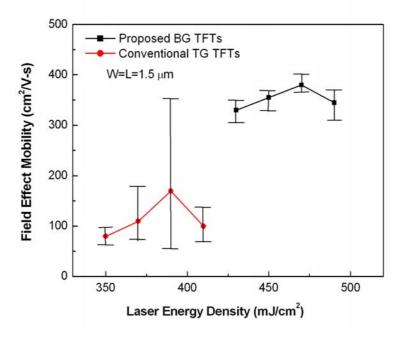

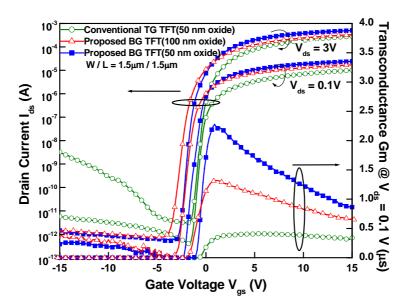

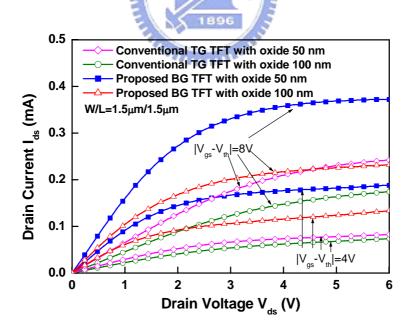

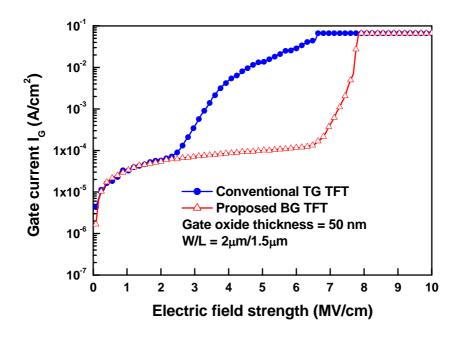

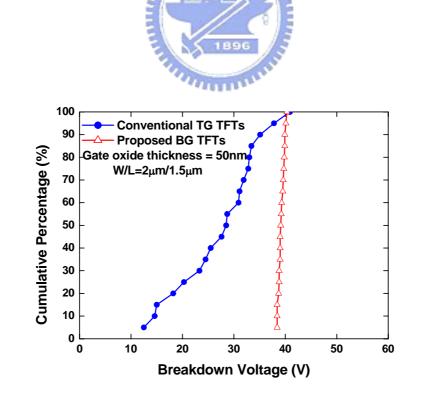

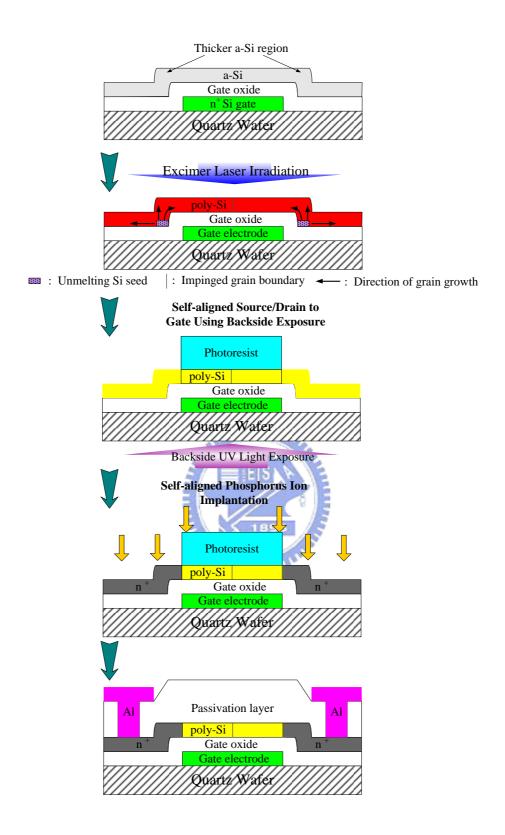

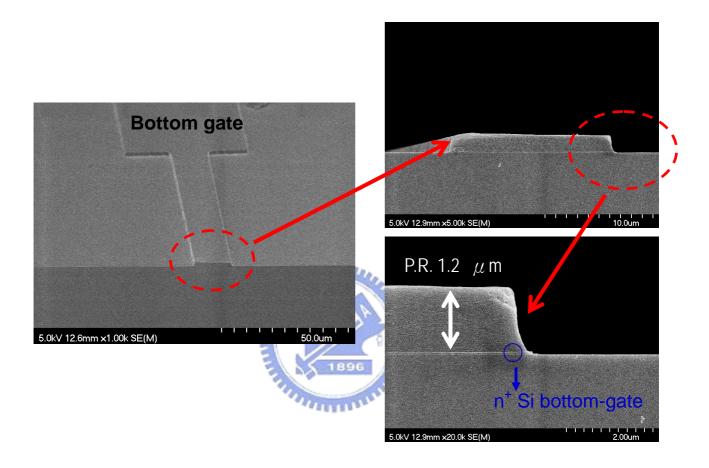

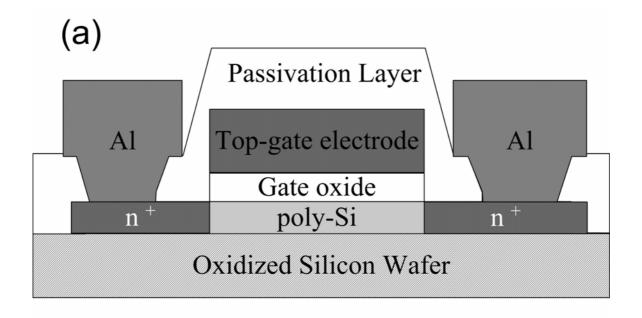

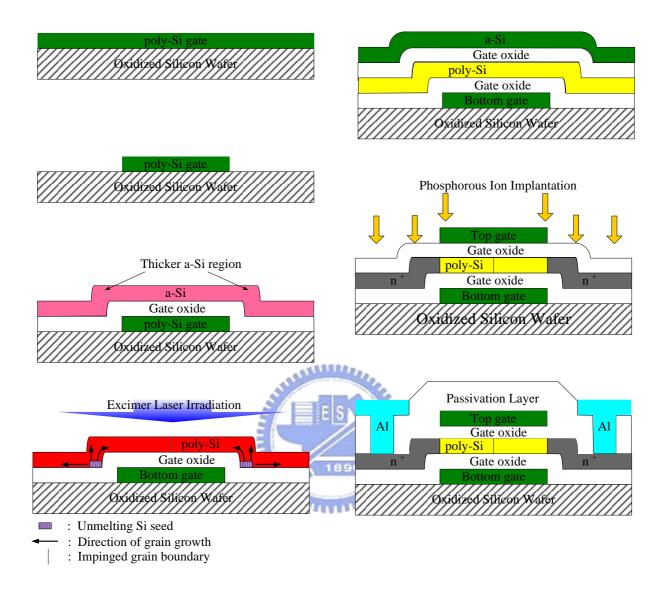

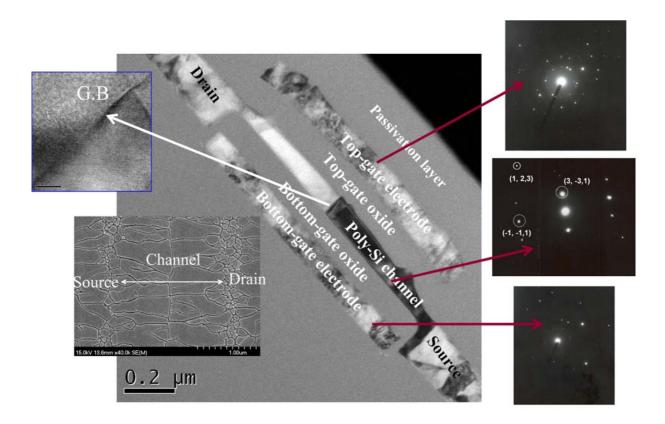

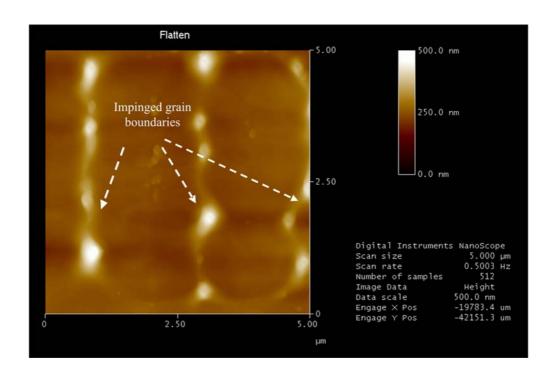

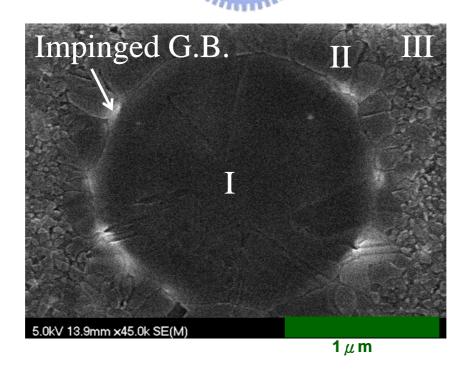

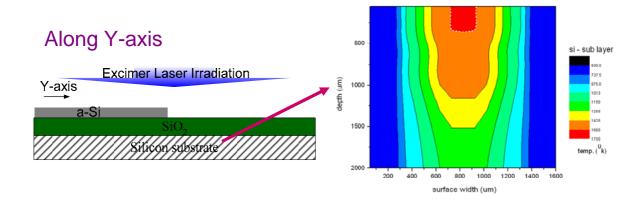

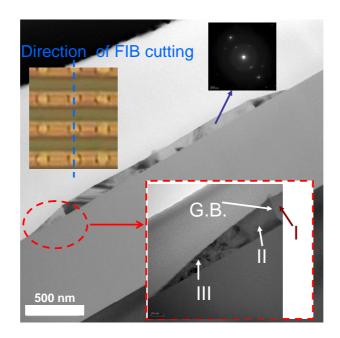

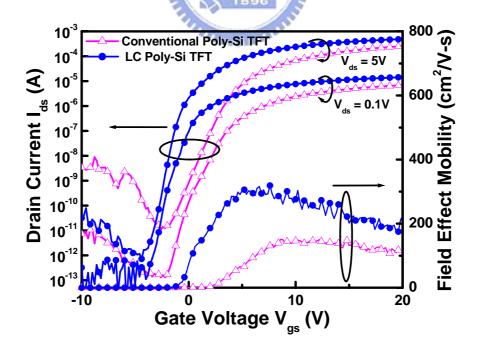

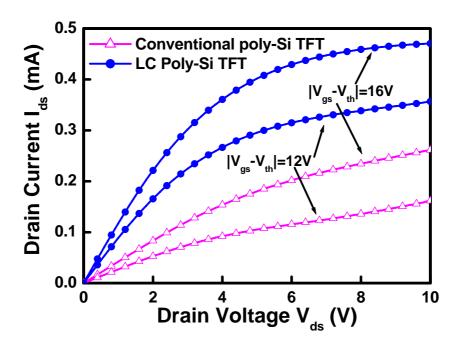

At first, from the perspective of improving channel material quality, LTPS TFTs with bottom gates (BG) have been demonstrated to achieve large silicon grains due to the lateral grain growth. In this method, a-Si thin film with two kinds of thicknesses in a local region was formed by the deposition of a-Si films on the plateau structure. When the excimer laser irradiation is applied on the a-Si thin film, the applied laser energy density is controlled to completely melt the thin region of a-Si film in the channel region but partially melted the thick region of a-Si film near the edges of bottom gate. Therefore, a lateral temperature gradient can be produced between the local thin and thick regions of a-Si film, and the lateral grain growth started from the un-melted silicon solid seed at the base neighbor to the bottom-gate corner, and extended toward the completely melted region until the solid-melt interface from opposite direction impinges. From material analyses, it can be observed that the large longitudinal grains artificially grown of about 0.85 µm in size were observed in the device channel region. Therefore, high-performance BG LTPS-TFTs have been demonstrated with the field-effect mobility exceeding 330cm<sup>2</sup>/V-s, low GIDL effect, suppressed kink current, and improved device uniformity due to the large silicon grains. Moreover, the BG TFTs reveal higher breakdown voltage and better reliability due to the smooth interface between gate dielectric and poly-Si channel films as thinner gate oxide were employed without additional processes or materials. The improved breakdown and driving characteristics imply that the proposed BG-TFT structure is more suitable for the device-scaled-down applications.

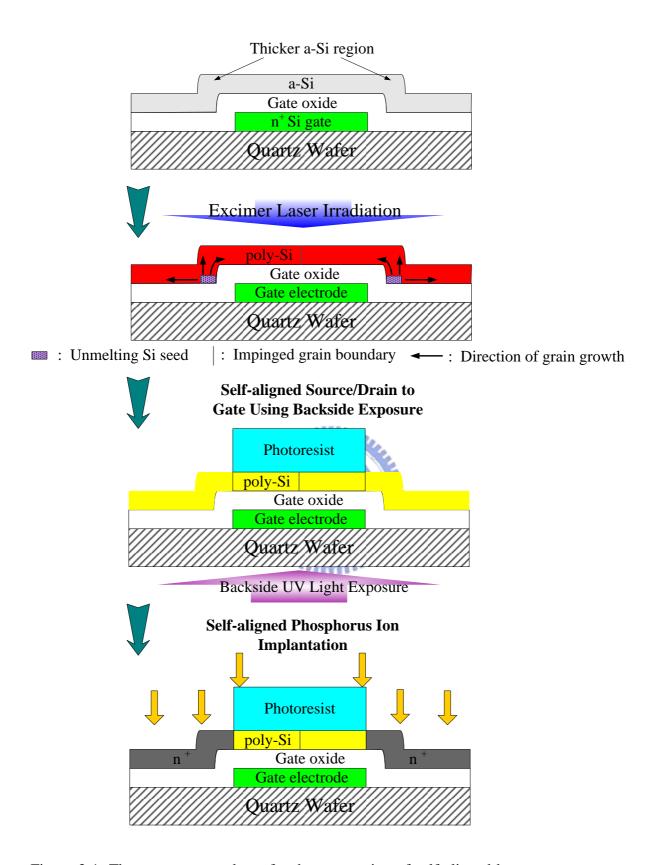

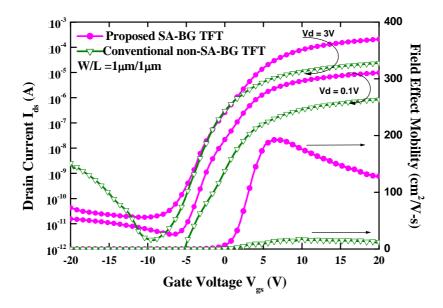

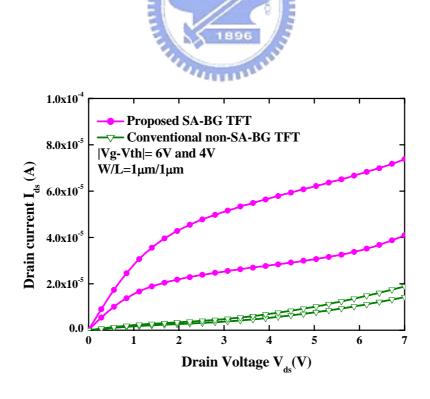

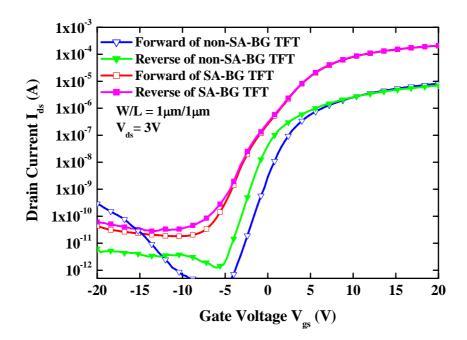

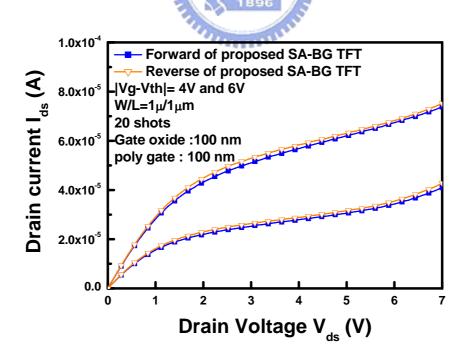

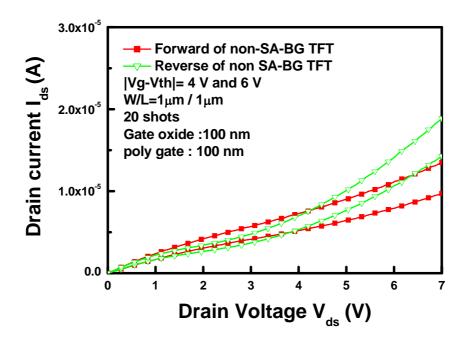

Although BG LTPS-TFTs exhibit superior electrical characteristics, asymmetrical electrical characteristics are also observed due to the misaligned process effect. Therefore, a self-aligned (SA) bottom-gate TFT with appropriate channel length has been fabricated by

the simple ELC and backside exposure. As a result, not only all the advantages of BG LTPS-TFTs with lateral silicon grains, but also the symmetrical electrical characteristics can be also observed in SA BG LTPS-TFTs. Consequently, SA-BG TFTs with the channel length of 1  $\mu$ m exhibited field-effect-mobility reaching 193 cm²/Vs without hydrogenation, while the mobility of the conventional non-SA-BG TFTs and conventional SA top-gate ones were about 17.8 cm²/Vs and 103 cm²/Vs, respectively.

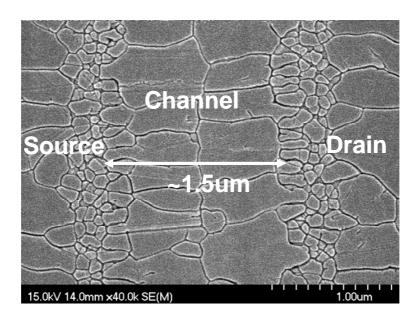

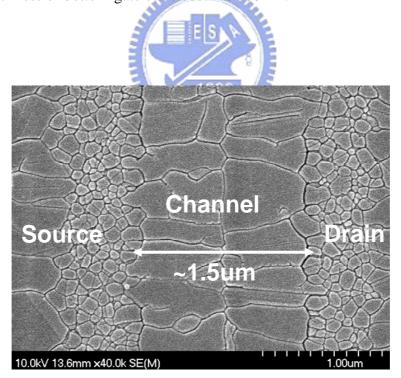

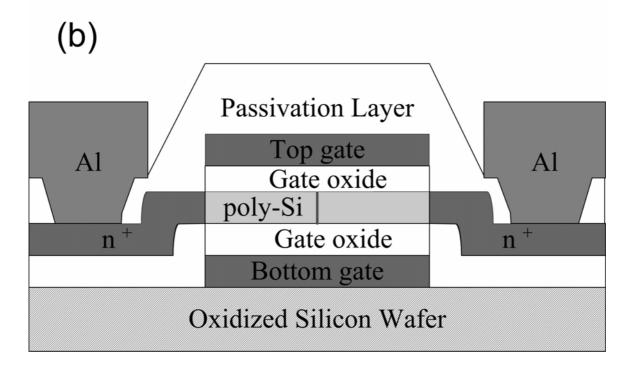

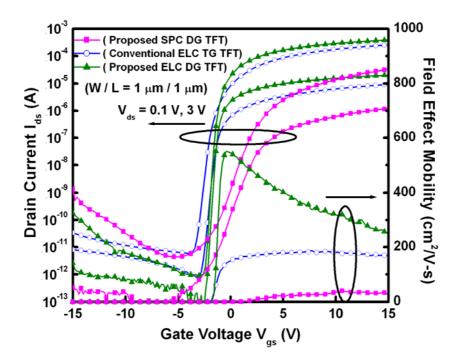

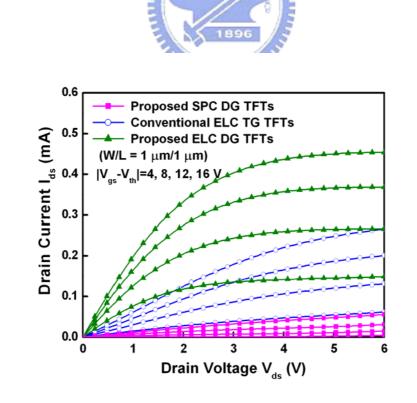

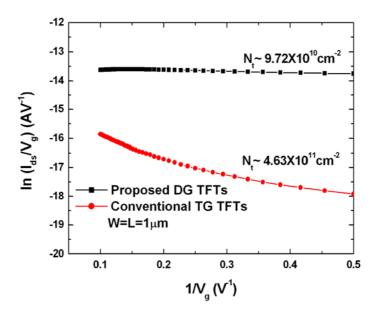

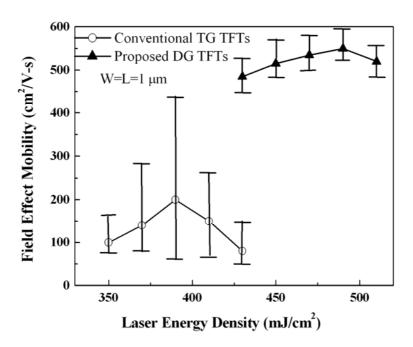

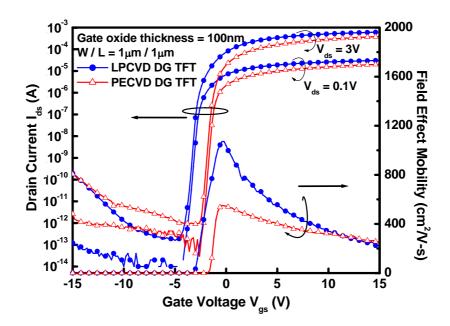

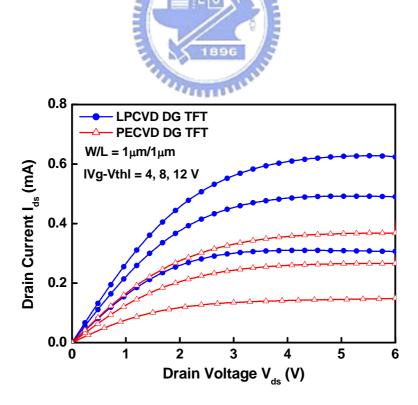

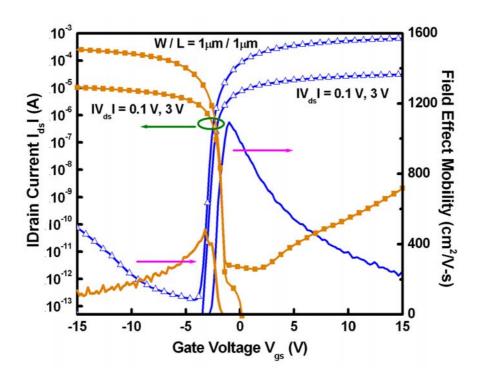

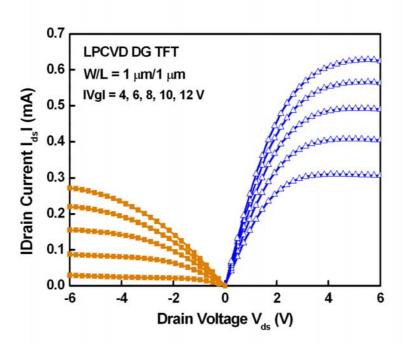

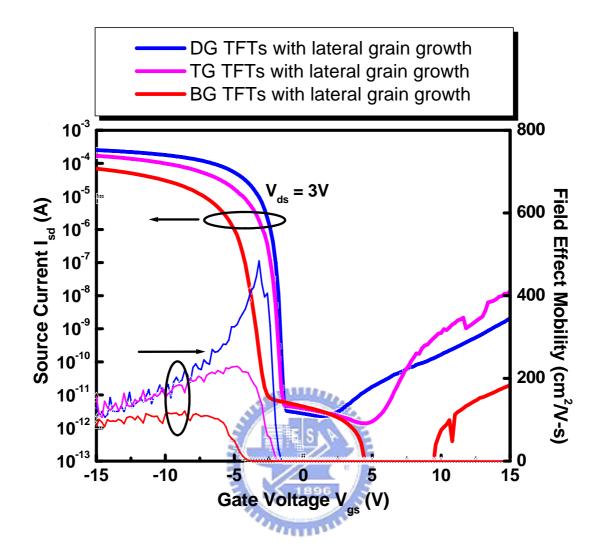

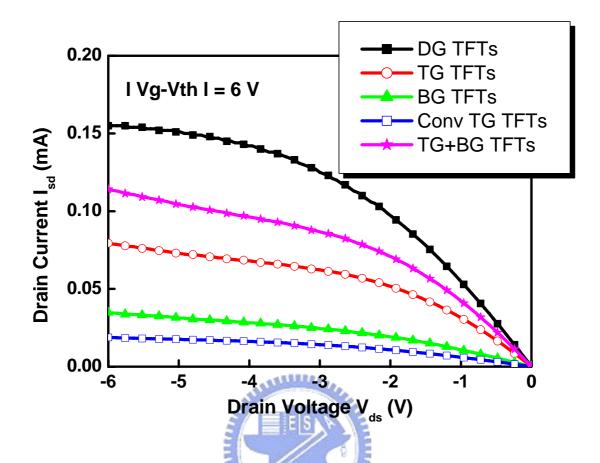

Shrinking the device size is an effective way to improving the device performance, but poor short-channel effects (SCE) is encountered owing to the insufficient gate controllability. Novel high-performance LTPS TFTs with double-gate (DG) structure and controlled lateral grain growth have been demonstrated by excimer laser crystallization. Because of the double gate operation mode and lateral silicon grains formed in the channel region, the devices have a higher driving current, steeper subthreshold slope, superior short-channel effect immunity, and suppression of the floating-body effect. The proposed DG TFTs (W/L =  $1/1 \mu m$ ) have the equivalent field-effect-mobility exceeding 1050 cm<sup>2</sup>/Vs for the N-channel device, 403 cm<sup>2</sup>/Vs for the P-channel device, on/off current ratio higher than  $10^9$ , smaller DIBL, and excellent device uniformity.

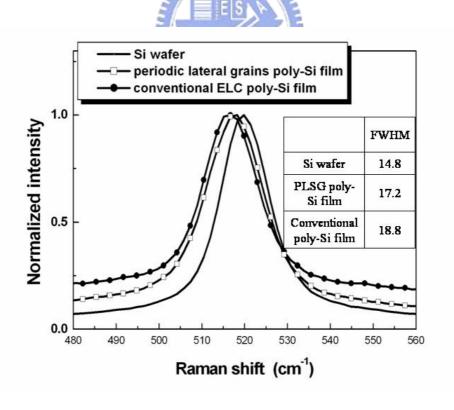

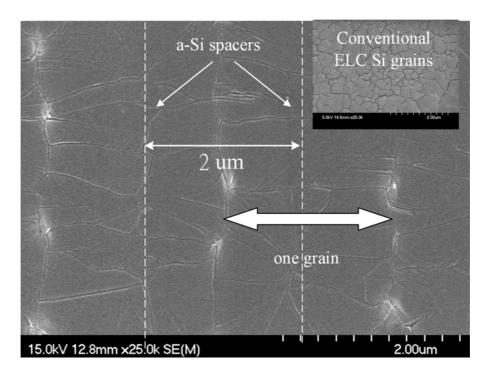

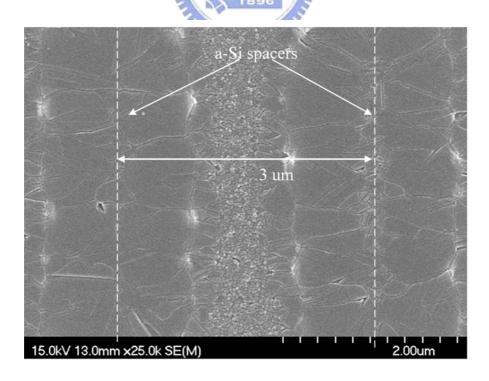

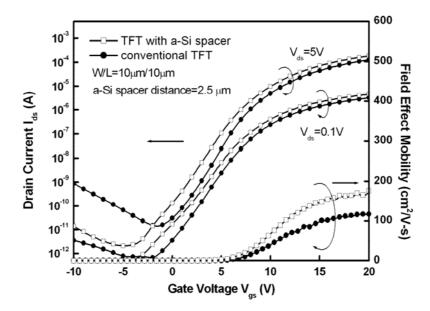

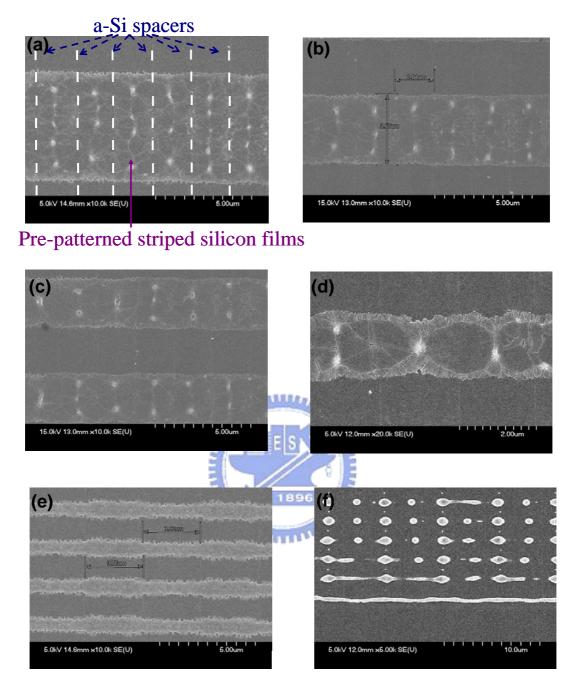

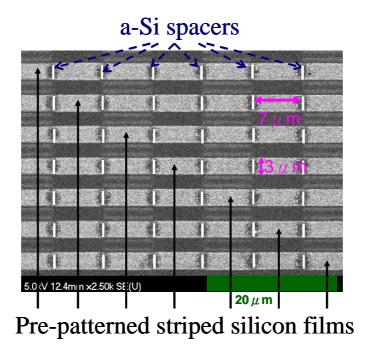

Although the crystallinity of poly-Si thin film can be effectively enhanced via ELC with bottom-gate structure, it is inevitable that there is a high angle grain boundary in the middle of channel region, which degrades the TFT performance and reliability. A novel laser crystallization method which can remove the high angle grain boundary and produce the large and uniform grains in the desired local region is proposed to improve the field-effect mobility as well as the device uniformity. Periodically lateral silicon grains with 2 µm in length can be artificially grown in the channel regions via the amorphous silicon spacer structure with excimer laser irradiation. By the way, such periodically large and lateral grains in the TFTs would achieve high field-effect mobility of 298 cm²/Vs, as compared with the conventional ones of 128 cm²/Vs. In addition, the device-to-device uniformity could be improved due to

this location-manipulated lateral silicon grains.

In order to further improve the performance of LTPS TFTs, single-grain TFT in which the channel is grain-boundary-free will exhibit SOI-like performance to satisfy the requirements of system on panel. A new crystallization technology for producing two-dimensional lateral grain growth, aiming at single-grain TFT, has been developed by excimer laser irradiation relying on the spatially temperature distribution at the artificially sites. The high quality silicon grains are controlled via manipulating super lateral growth phenomenon by spatially two kinds of silicon films and pre-patterned structure. An array of 1.8-µm-sized disklike silicon grains is formed periodically. Not only high-performance poly-Si TFTs with field-effect-mobility reaching 308 cm²/Vs but also excellent device uniformity are demonstrated owing to the artificially-controlled lateral grain growth. Proposed poly-Si TFTs, therefore, have great potential for the future SOP and 3D-ICs applications.

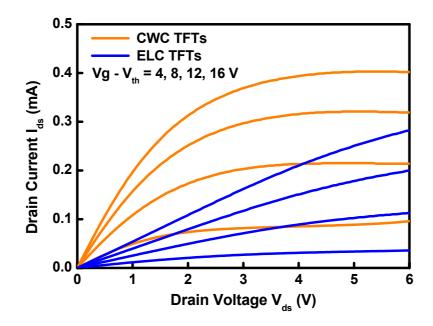

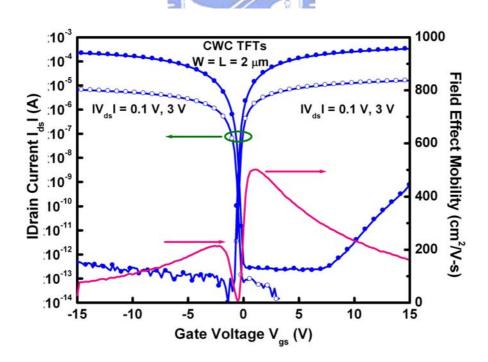

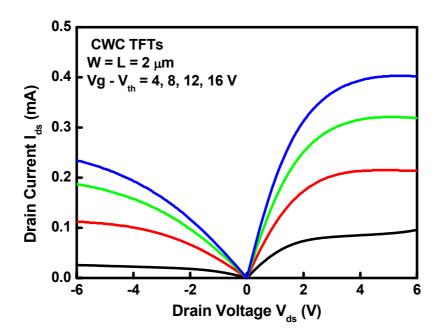

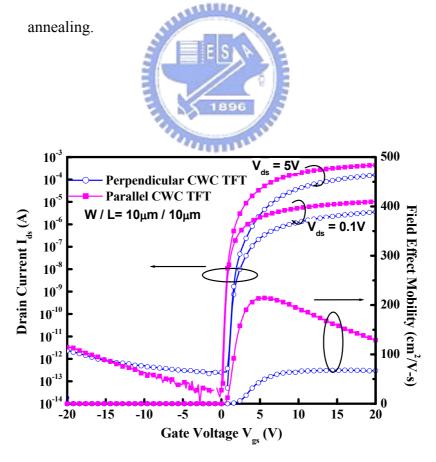

Although the aforementioned laser crystallization methods can fabricate large homogeneous silicon grains and high-performance LTPS TFTs, another crystallization approach, a new and simple CW laser crystallization, is also proposed to produce lateral grain growth via controlling the laser scanning speed and laser power. According to the experimental results, a directional river-like lateral Si grain growth with tens of micron, flat surface morphology, and excellent crystallinity are achieved without damage to the glass substrates. As a result, ultra-high performance CW laser-annealed LTPS-TFTs have been fabricated on the oxidized silicon wafer for the first time with field-effect mobility exceeding 504 cm<sup>2</sup>/V-s for n-channel devices and 220 cm<sup>2</sup>/V-s for p-channel devices. It is also found that CW laser annealing is a low-thermal-budget and high-efficiency dopant activation method attributed to the low sheet resistance and uniformly redistributed dopant profiles after CW laser annealing. Because of the simple process, continuous-wave laser-annealed LTPS TFTs are very promising for the future SOP, 3D-ICs, and solar cell applications.

#### 誌謝

感謝我的論文指導教授 鄭晃忠博士在實驗、研究與論文上的熱心且詳實的指導, 老師嚴謹認真的研究態度以及謙恭溫和的待人處事,都讓學生獲益良多,老師耐心的教 誨與鼓勵,也使我能順利完成博士學位。

感謝常鼎國學長與林敬偉學長帶領我進入低溫多晶矽薄膜電晶體的研究領域,給予充分熱心的實驗訓練幫助及研究觀念上的指導,也由衷的感謝陳旭信學弟、韋凱方學弟、曾煥均學弟、陳彥佑學弟、張為鈞學弟在實驗及計畫上的幫忙及支援,同時感謝李逸哲同學、李序恆學弟、楊柏宇學弟、李耀仁學長、林家彬學長在行政及生活上的幫忙與協助;使得本論文研究得以順利的完成。

感謝實驗室的學長、同學、學弟妹及助理們,謝謝你們在實驗或是生活上都能夠給予我支持與關心,使得我的研究能夠順利完成,其中包含了王志良學長、阮全平學長、陳國基學長、張芳龍學長、張國瑞學長、曾章和學長、張原熏學長、朱芳村學長、林高照同學、陳柏廷學弟、賴瑞霖學弟、呂健豪學弟、江可玉學妹、郭育如學妹、魏瑛君學妹、廖大傳學弟、許鈞凱學弟、林君翰學弟、王祐圻學弟、陳俠威學弟、高翠敏助理、簡秀芳助理、李瑩姿助理、凌碧蓮助理、張依婷助理、楊宜樺助理以及其他學長、同學、學弟妹們,有了你們在生活上的相伴和打氣,此論文才能順利完成。

感謝國立交通大學奈米中心及國家奈米元件實驗室提供優良的設備與研究環境,尤 其要感謝彭兆光先生、吳政三先生、徐秀鑾小姐、陳明麗小姐、黄月美小姐、陳聯珠小 姐、陳悅婷小姐、彭馨誼小姐、倪月珍小姐、范秀蘭小姐、林素珠小姐、徐台鳳小姐、 劉曉玲小姐及何惟梅小姐等,在製程、設備及分析上的大力協助。也感謝諸位口試委員 的指導與建議。

感謝我敬愛的父母 蔡神祐先生與陳蓮枝女士,謝謝你們多年來辛苦的培育我,教育我,有了你們持續的支持與默默的付出,才能讓我得以全心投入學業,完成博士學位,同時也要感謝我的妹妹 蔡月霜以及弟弟 蔡育修,在家中生活上的幫忙扶持。

感謝我的太太 辜郁雯在我研究生生涯中無悔的支持我,不論晴雨,一路相隨;也 感謝太太娘家家人的對我的鼓勵與信任,由衷的感謝你們。

最後感謝所有曾經幫助過我的朋友們,謝謝你們一路上給我的支持與關心。

#### **Contents**

|               | with Bottom-Gate Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25      |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|               | Thin-Film Transistors Crystallized by Excimer Laser Irra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | diation |

| Chapter 2     | High-Performance Low Temperature Polycrystalline Silice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | on      |

| 1.6           | Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18      |

| 1.5           | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15      |

| 1.4           | Ion Doping and Activation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 13      |

| 1.3.          | .3 Laser Crystallization for Poly-Si Thin Films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8       |

| 1.3.          | 2 Metal Induced Crystallization for Poly-Si Thin Films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6       |

| 1.3.          | .1 Solid Phase Crystallization for Poly-Si Thin Films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5       |

| 1.3           | Approaches to the Preparation of Polycrystalline Silicon Thin Films                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5       |

| 1.2           | TFT Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3       |

| 1.1           | The Evolution of Silicon-Based Thin-Film Transistors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1       |

|               | WILLIAM TO THE PARTY OF THE PAR |         |

| Chapter 1     | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1       |

| Tigure Capi   | ions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | AVII    |

| Figure Capt   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xvii    |

| Table Caption | ons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | xiv     |

| Contents      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ix      |

| Acknowled     | gments (in Chinese)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | viii    |

| Abstract (in  | English)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iv      |

| Abstract (in  | Chinese)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1       |

| 2.1    | Introd           | duction                                                          | 25        |

|--------|------------------|------------------------------------------------------------------|-----------|

| 2.2    | The C            | Concept of Controlled Lateral Grain Growth with Bottom-Gate stru | ucture30  |

| 2.3    | Expe             | eriments                                                         | 31        |

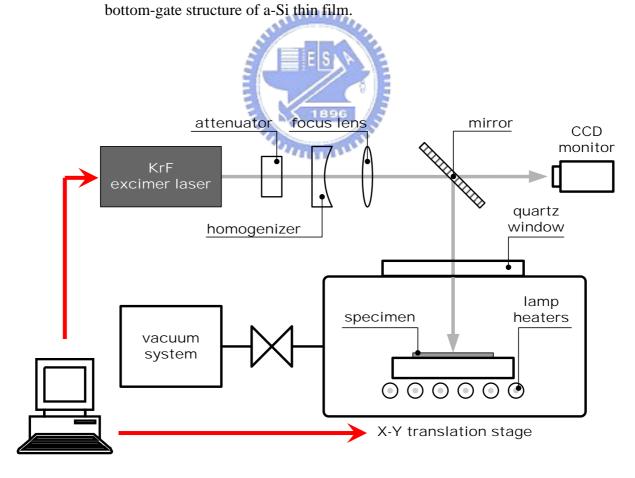

|        | 2.3.1            | The Setup of Excimer Laser Crystallization System                | 31        |

|        | 2.3.2            | Sample Preparation for Material Analysis                         | 32        |

|        | 2.3.3            | Fabrication of Bottom-Gate LTPS TFTs using ELC                   | 33        |

| 2.4    | Resul            | lts and Discussion                                               | 35        |

|        | 2.4.1            | Material Characterization of ELC Poly-Si Thin Films with Botto   | m-Gate    |

|        |                  | Structure                                                        | 35        |

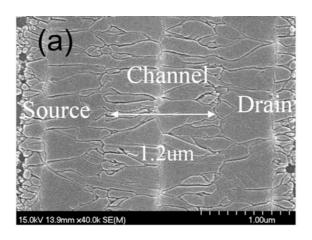

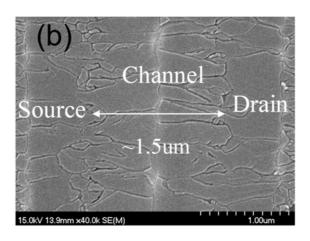

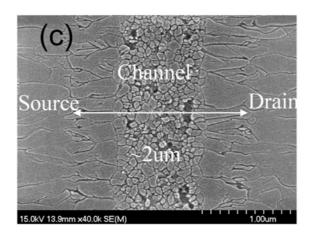

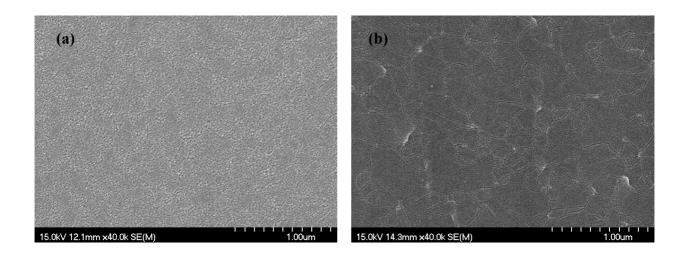

|        | 2.4              | 4.1.1 Scanning Electron Microscopy (SEM) Analysis                | 36        |

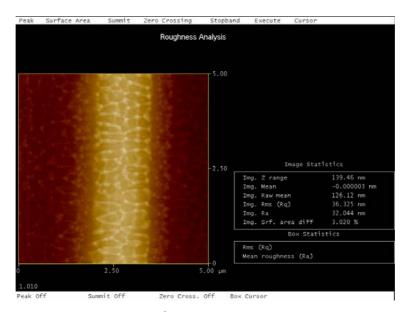

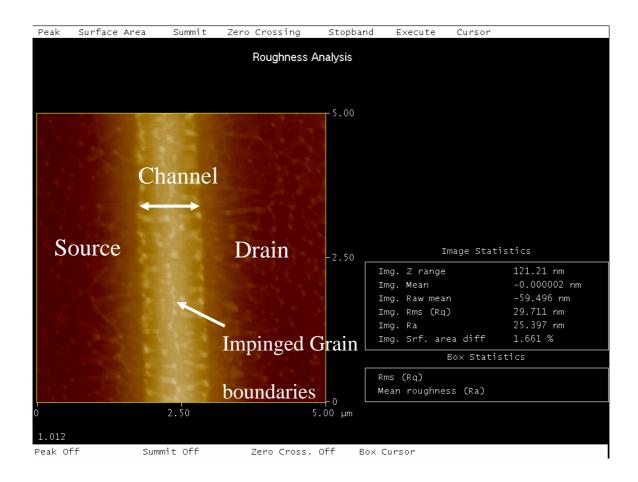

|        | 2.4              | 4.1.2 Atomic Force Microscopy (AFM) Analysis                     | 40        |

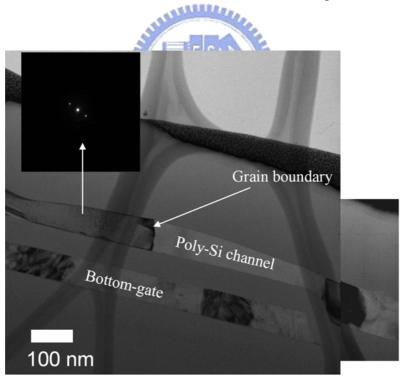

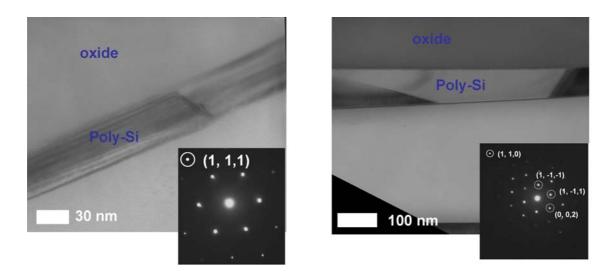

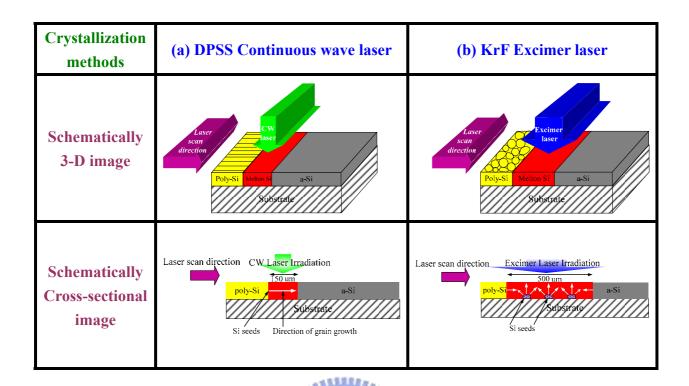

|        | 2.4              | 4.1.3 Transmission Electron Microscopy (TEM) Analysis            | 40        |

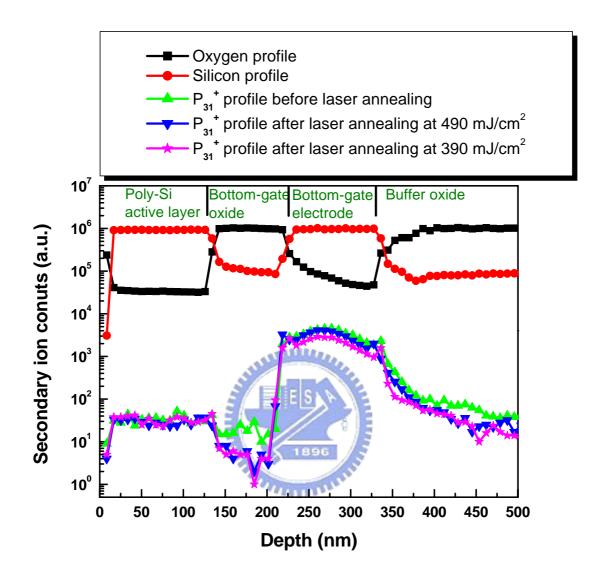

|        | 2.4              | 4.1.4 Secondary Ion Mass Spectroscopy (SIMS) Analysis            | 41        |

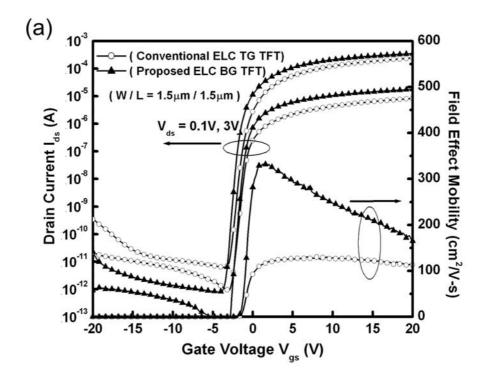

|        | 2.4.2            | Electrical Characteristics of LTPS TFTs Fabricated Using Excim   | er Laser  |

|        |                  | Irradiation with Bottom-Gate Structure                           | 42        |

| 2.5    | Sumr             | mary                                                             | 46        |

|        |                  |                                                                  |           |

| Chapte | r3 H             | ligh-Performance Self-Aligned Bottom-Gate Low Tempe              | erature   |

|        | P                | Polycrystalline Silicon Thin-Film Transistors with Excin         | ıer Laser |

|        | $\boldsymbol{C}$ | Erystallization                                                  | 64        |

|        |                  |                                                                  |           |

| 3.1    | Introd           | duction                                                          | 64        |

| 3.2    | Expe             | eriments                                                         | 66        |

|        | 3.2.1            | Sample Preparation for Material Analysis                         | 66        |

|        | 3.2.2            | Fabrication of Self-Aligned (SA) BG LTPS TFTs using ELC          | 67        |

| 3.3    | Resul            | ılts and Discussion                                              | 69        |

|         | 3.3.1 | Material Characterization of SA-BG LTPS Thin Films           | 69                |

|---------|-------|--------------------------------------------------------------|-------------------|

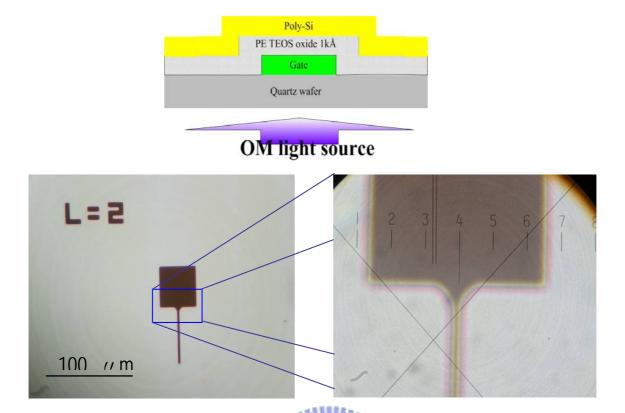

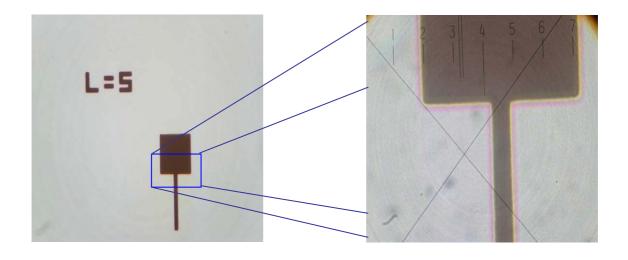

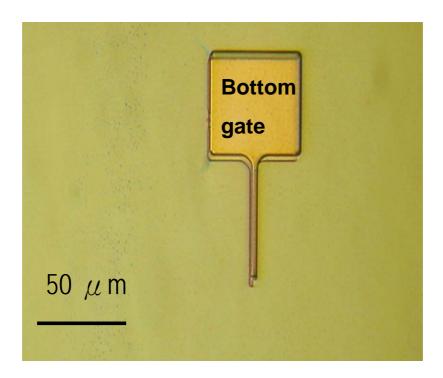

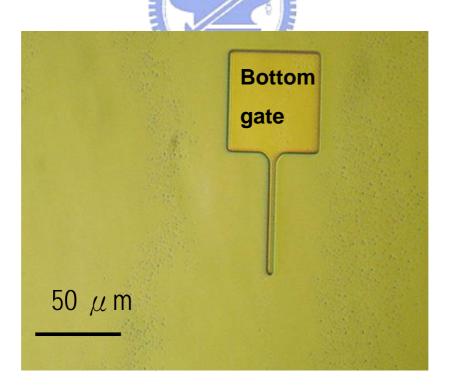

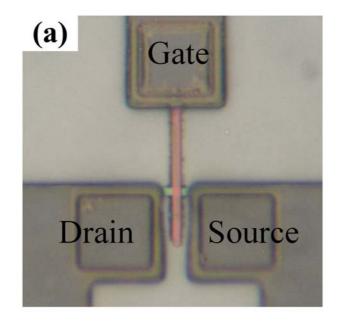

|         | 3.    | 3.3.1.1 Optical Microscopy (OM) Analysis                     | 69                |

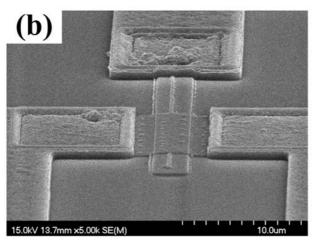

|         | 3.    | S.3.1.2 Scanning Electron Microscopy (SEM) Analysis          | 70                |

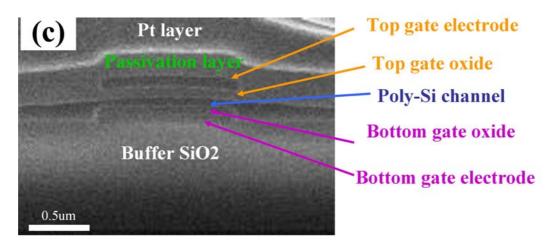

|         | 3.    | 3.3.1.3 Transmission Electron Microscopy (TEM) Analysis      | 71                |

|         | 3.3.2 | Electrical Characteristics of SA-BG LTPS TFTs using ELC      | 73                |

| 3.4     | Sum   | nmary                                                        | 75                |

|         |       |                                                              |                   |

| Chapter | r4 H  | High-Performance Short-Channel Double-Gate Low T             | <i>Emperature</i> |

|         | P     | Polycrystalline Silicon Thin-Film Transistors Using E.       | xcimer            |

|         | L     | Laser Crystallization                                        | 89                |

|         |       | 4.555.0                                                      |                   |

| 4.1     |       | oduction                                                     | 89                |

| 4.2     | Expe  | eriments                                                     | 91                |

| 4.3     |       | ults and Discussion                                          | 93                |

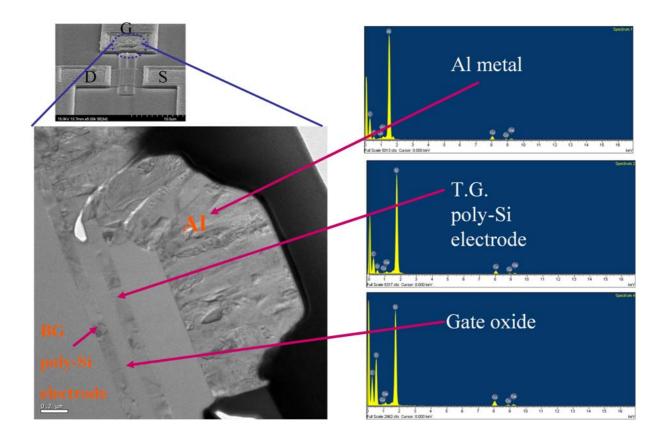

|         | 4.3.1 | Material Characterization of Excimer Laser-Crystallized Dou  | ble-Gate          |

|         |       | Low-temperature Poly-Si Thin Films Transistors               | 93                |

|         | 4.3.2 | Electrical Characterization of Excimer Laser-Crystallized Do | uble-Gate         |

|         |       | Low-temperature Poly-Si Thin Films Transistors               | 95                |

| 4.4     | Sum   | nmary                                                        | 101               |

| Chapter | r 5 P | Periodically Lateral Silicon Grains Fabricated by Exci       | mer Laser         |

| •       |       | Trradiation with Amorphous Silicon Spacers and Its A         |                   |

|         |       | to High-Performance Low Temperature Polycrystallin           |                   |

|         |       | Thin Film Transistors                                        |                   |

|         | _     |                                                              |                   |

| 5.1     | Intro | oduction                                                     | 119               |

| 5.2    | The I | Basic Concept of Periodically Lateral Silicon Grain | s Employing Excimer     |

|--------|-------|-----------------------------------------------------|-------------------------|

|        | Lase  | er Crystallization with a-Si Spcaer Structures      | 120                     |

| 5.3    | Expe  | eriments                                            | 122                     |

| 5.4    | Resu  | lts and Discussion                                  | 123                     |

|        | 5.4.1 | Material Characterization of ELC Poly-Si Thin Fi    | lms with a-Si Spacer    |

|        |       | Structure                                           | 123                     |

|        | 5.4.2 | Electrical Characteristics of LTPS TFTs Fabricate   | d Using Excimer Laser   |

|        |       | Irradiation with a-Si Spacer Structure              | 125                     |

| 5.5    | Sumr  | mary                                                | 127                     |

|        |       |                                                     |                         |

|        | L     | aser Irradiation                                    | 141                     |

| 6.1    | Intro | duction                                             | 141                     |

| 6.2    | Expe  | eriments                                            | 142                     |

| 6.3    | Resul | lts and Discussion                                  | 145                     |

| 6.4    | Sumr  | mary                                                | 150                     |

| Chapte | r 7 U | ltra High-Performance Low Temperature I             | Polycrystalline Silicon |

|        | T     | hin-Film Transistors Fabricated via Diode           | -Pumped Solid-State     |

|        | C     | Continuous Wave Laser Annealing                     | 159                     |

| 7.1    | Intro | duction                                             | 159                     |

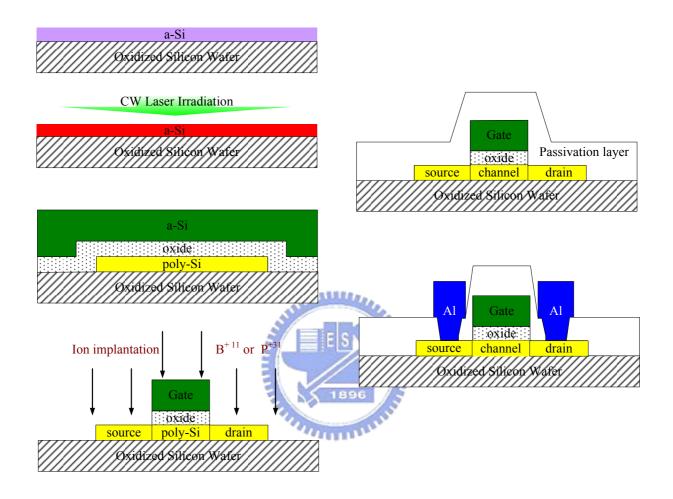

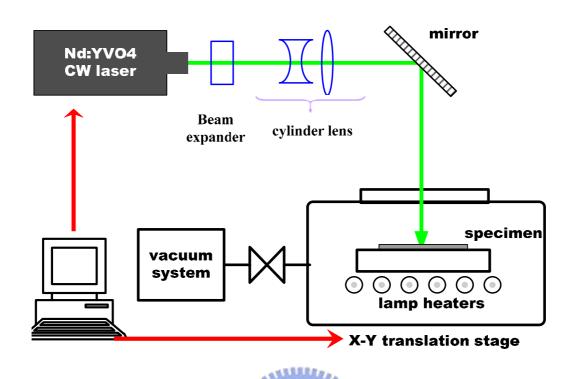

| 7.2    | Expe  | eriments                                            | 162                     |

| 73     | Resul | Its and Discussion                                  | 164                     |

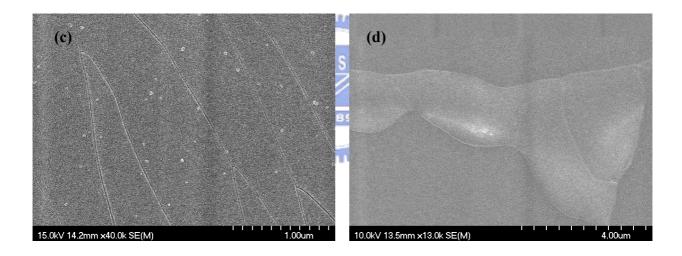

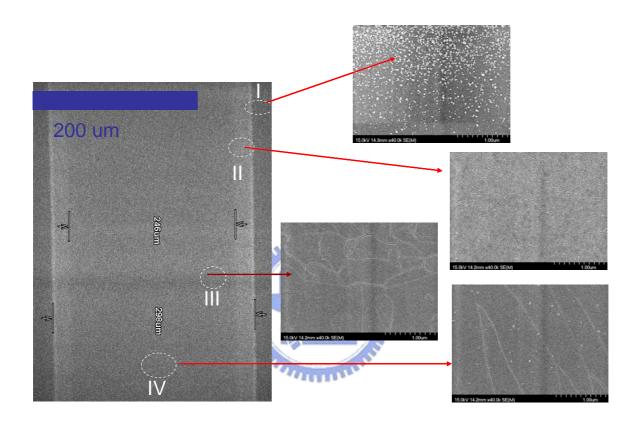

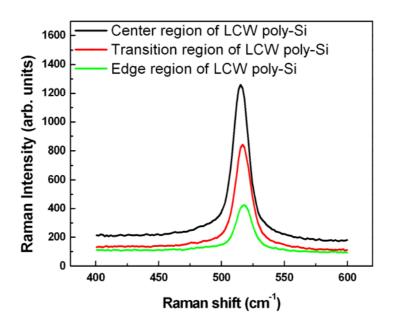

| 7.3.1  | Material Characterization of Poly-Si Thin Films Crystallized by      |                                                |

|--------|----------------------------------------------------------------------|------------------------------------------------|

|        | Diode-Pumped Solid-State Continuous Wave Laser                       | 164                                            |

| 7.3.2  | Crystallization Mechanism of Diode-Pumped Solid-State Continuous W   | <sup>7</sup> ave                               |

|        | Laser-Crystallized Poly-Si Thin Films                                | 171                                            |

| 7.3.3  | Electrical Characteristics of LTPS TFTs Fabricated Using Diode-Pumpe | ed                                             |

|        | Solid-State Continuous Wave Laser Annealing                          | 172                                            |

| Sumr   | nary                                                                 | 175                                            |

|        |                                                                      |                                                |

| r 8 Su | ummary and Conclusions1                                              | 195                                            |

|        |                                                                      |                                                |

| r9 Fi  | uture Prospects2                                                     | 01                                             |

| ıces   | ZI Z                             | 04                                             |

|        | 1896                                                                 |                                                |

|        | 7.3.2 7.3.3 Sumr                                                     | Diode-Pumped Solid-State Continuous Wave Laser |

Vita

#### **Table Captions**

#### **Chapter 1**

| Table 1-1 | The system-on-panel (SOP) technology roadmap where LTPS TFT performances                                                                                    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | and related processes are going on in the features21                                                                                                        |

| Chapter   | 2                                                                                                                                                           |

| Table 2-1 | Measured electrical characteristics of bottom-gate LTPS TFTs and conventional                                                                               |

|           | top-gate ones                                                                                                                                               |

| Table 2-2 | Measured electrical characteristics of bottom-gate LTPS TFTs and conventional top-gate ones. (W = L = $1.5 \mu m$ and gate oxide thickness of 500 Å or 1000 |

|           | Å48                                                                                                                                                         |

| Chapter   | 3                                                                                                                                                           |

| Table 3-1 | Measured electrical characteristics of SA-BG LTPS TFTs with lateral grain growth and conventional non-SA BG ones                                            |

| Chapter   | 4                                                                                                                                                           |

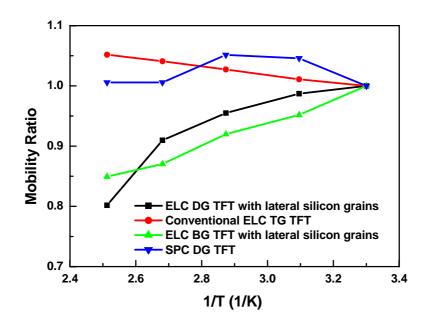

| Table 4-1 | Measured electrical characteristics of ELC DG TFTs with lateral grain growth, SPC DG TFTs, and conventional ELC TG TFTs                                     |

| Table 4-2 |                                                                                                                                                             |

|           |                                                                                                                                                             |

|           | LPCVD gate oxide and ELC DG TFTs with low-temperature PECVD gate                  |

|-----------|-----------------------------------------------------------------------------------|

| Table 4-3 | oxide                                                                             |

| 14010 4-2 | and p-channel ELC DG TFTs with lateral grain growth                               |

| Table 4-4 |                                                                                   |

|           | ELC TG TFTs with lateral grain growth, and ELC BG TFTs with lateral grain         |

|           | growth104                                                                         |

| Chapter   | 5                                                                                 |

| Table 5-1 | Measured electrical characteristics of LTPS TFTs crystallized with a-Si spacer    |

|           | and conventional structures                                                       |

| Table 5-2 | Measured optimal electrical characteristics of LTPS TFTs crystallized with        |

| Chapter   | conventional and a-Si spacer structures, respectively                             |

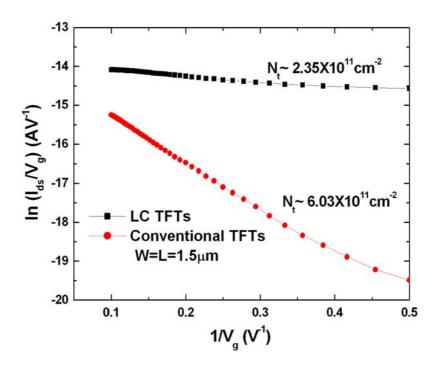

| Table 6-1 | Measured electrical characteristics of poly-Si TFTs with location-controlled (LC) |

|           | silicon grains and conventional TFTs with random grain structure151               |

| Chapter   | 7                                                                                 |

| Table 7-1 | The comparisons of excimer laser and DPSS continuous wave laser177                |

| Table 7-2 | Measured sheet resistance of samples after various activation methods177          |

| Table 7-3 | Measured electrical characteristics of LTPS TFTs crystallized by DPSS CW laser    |

|           | and excimer laser                                                                 |

| Table 7-4 | Comparisons of CWC TFTs channel length structurally parallel and |

|-----------|------------------------------------------------------------------|

|           | perpendicular to the direction of laser scanning                 |

#### **Figure Captions**

#### Chapter 1

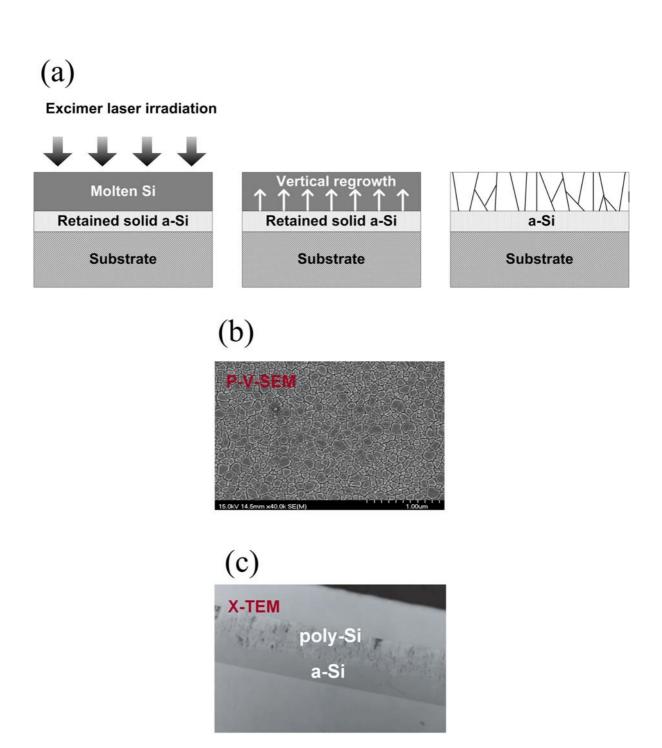

| Fig. 1-1. | (a) The schematic illustration of the low-energy density regime corresponding to     |

|-----------|--------------------------------------------------------------------------------------|

|           | energy densities that partially melt the a-Si thin film. (b) The plane-view scanning |

|           | electron micrograph (SEM) and (c) cross-sectional transmission electron              |

|           | micrograph (TEM) of excimer-laser- crystallized poly-Si thin films in the            |

|           | partial-melting regime, respectively                                                 |

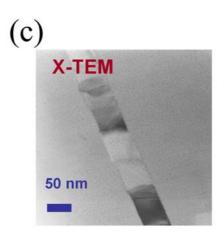

| Fig. 1-2. | (a) The schematic illustration of the high-energy density regime corresponding to    |

|           | energy densities that completely melt the a-Si thin film. (b) The plane-view         |

|           | scanning electron micrograph (SEM) and (c) cross-sectional transmission electron     |

|           | micrograph (TEM) of excimer-laser- crystallized poly-Si thin films in the            |

|           | complete-melting regime, respectively                                                |

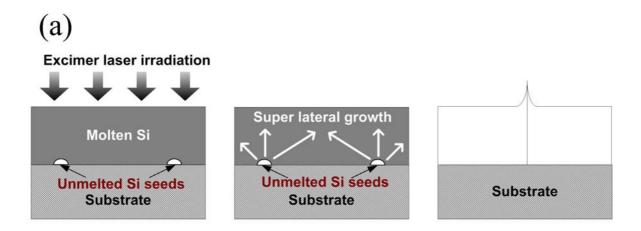

| Fig. 1-3. | (a) The schematic illustration of the near-complete-melting regime corresponding     |

|           | to energy densities that near completely melt the a-Si thin film. (b) The plane-view |

|           | scanning electron micrograph (SEM) and (c) cross-sectional transmission electron     |

|           | micrograph (TEM) of excimer-laser- crystallized poly-Si thin films in the            |

|           | near-complete-melting regime, respectively24                                         |

#### **Chapter 2**

Fig. 2-1. The schematic illustration of the mechanism of lateral grain growth using

|           | bottom-gate structure of a-Si thin film                                                           |

|-----------|---------------------------------------------------------------------------------------------------|

| Fig. 2-2. | The schematic illustration of excimer laser crystallization system49                              |

| Fig. 2-3. | The process procedures for the preparation of poly-Si thin films with bottom-gate                 |

|           | structure crystallized by ELC                                                                     |

| Fig. 2-4. | The key processes for fabricating short channel bottom-gate LTPS TFTs with                        |

|           | excimer laser annealing                                                                           |

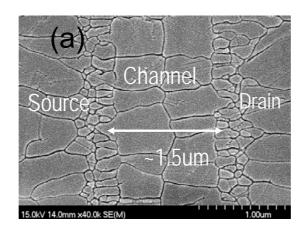

| Fig. 2-5. | (a) The schematic cross-sectional drawing of conventional top- gate LTPS TFTs                     |

|           | using the super lateral growth (SLG) excimer laser annealing condition. (b)                       |

|           | Plane-view SEM micrograph of excimer laser crystallized poly-Si thin film with                    |

|           | SLG laser annealing condition after Secco-etch                                                    |

| Fig. 2-6. | The SEM micrographs of excimer laser crystallized poly-Si thin films with                         |

|           | bottom-gate structure after Secco etching, in which the device channel length was                 |

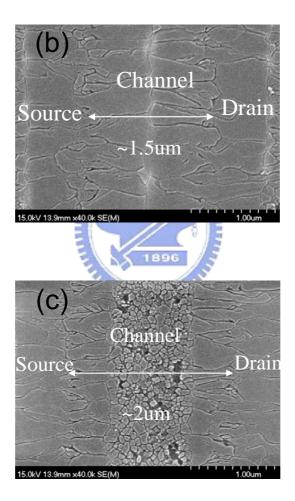

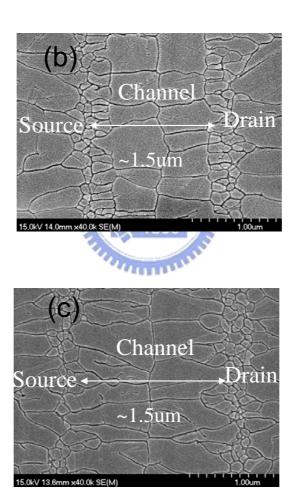

|           | (a) 1.2 $\mu$ m, (b) 1.5 $\mu$ m, and (c) 2.0 $\mu$ m, respectively. In this case, the laser shot |

|           | number is single pulse and the poly gate thickness was 1000 Å. The laser energy                   |

|           | density is 450 mJ/cm <sup>2</sup> 53                                                              |

| Fig. 2-7. | Scanning electron microscope micrographs of excimer laser crystallized poly-Si                    |

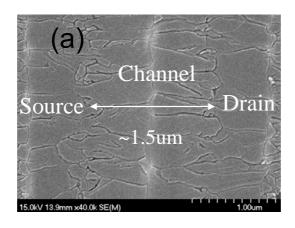

|           | thin film with bottom-gate structure after Secco-etch, in which the device                        |

|           | channel length was $1.5\mu m$ , and the laser shot number was (a) 1shot, (b) 20 shots,            |

|           | and (c) 100 shots, respectively54                                                                 |

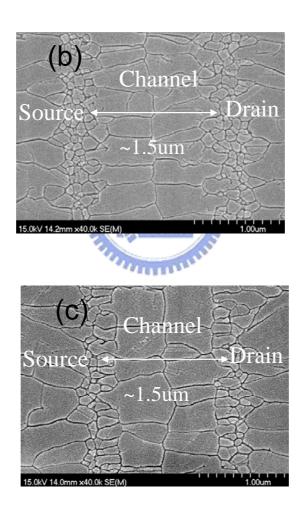

| Fig. 2-8. | Scanning electron microscope micrographs of excimer laser crystallized poly-Si                    |

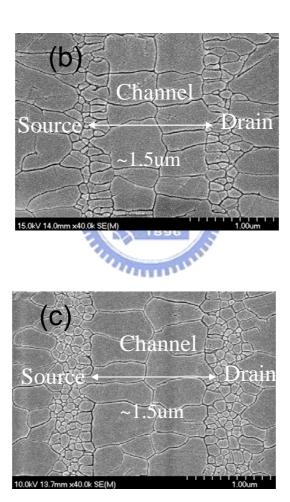

|           | thin film with bottom-gate structure after Secco-etch, in which the device                        |

|           | channel length was $1.5\mu m$ , and the laser energy density was (a) 430, (b) 450, and            |

|           | (c) 490 mJ/cm <sup>2</sup> , respectively55                                                       |

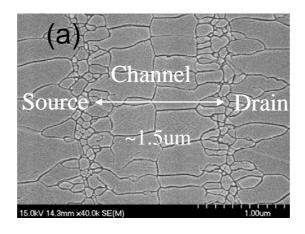

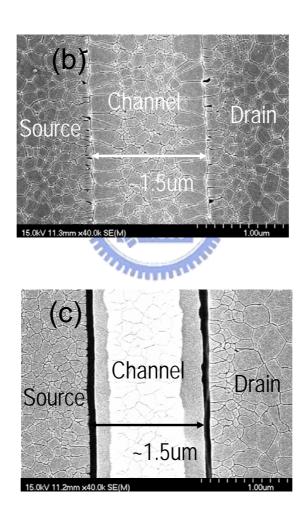

| Fig. 2-9. | The SEM micrographs of poly-Si thin films irradiated by excimer laser shot                        |

|           | number of 20 shots and the gate oxide thickness of (a) 30, (b) 50, and (c) 100 nm,                |

|           | respectively, in which the device channel length was 1.5 µm. The laser energy                     |

|            | density is 450 mJ/cm <sup>2</sup> 56                                                    |

|------------|-----------------------------------------------------------------------------------------|

| Fig. 2-10. | The SEM micrographs of poly-Si thin films irradiated by excimer laser shot              |

|            | number of 20 shots and the bottom-gate thickness of (a) 100, (b) 200, and (c)           |

|            | 300 nm, respectively, in which the device channel length was 1.5 $\mu$ m57              |

| Fig. 2-11. | The AFM image of 1000 Å-thick poly-Si thin films with bottom-gate structure             |

|            | after laser crystallization, in which the device channel length is 1.5 $\mu m.$ In this |

|            | case, the laser shot number is 20 shots and the bottom-gate thickness is 1000           |

|            | Å58                                                                                     |

| Fig. 2-12. | The cross-sectional TEM image of 1000 Å-thick poly-Si thin films with                   |

|            | bottom-gate structure after laser crystallization, in which the device channel          |

|            | length is 1.5 μm58                                                                      |

| Fig. 2-13. | The element SIMS depth profiles of the excimer laser-crystallized bottom-gate           |

|            | TFTs59                                                                                  |

| Fig. 2-14. | Comparisons of (a) Transfer characteristics and (b) Output characteristics for          |

|            | ELC BG LTPS TFT with lateral silicon grains and conventional ELC TG                     |

|            | TFT60                                                                                   |

| Fig. 2-15. | Dependence of field-effect-mobility on the device dimension for ELC BG LTPS             |

|            | TFTs with lateral silicon grins and conventional ELC TG ones. The field effect          |

|            | mobility was evaluated at $V_{ds} = 0.1 \ V$ 61                                         |

| Fig. 2-16. | Dependence of field-effect-mobility on applied laser energy density for ELC BG          |

|            | TFTs with lateral silicon grins and conventional ELC TG ones with random                |

|            | grain structures61                                                                      |

| Fig. 2-17. | (a) Comparison of the transfer characteristics of the n-channel LTPS BG-TFTs            |

|            | with lateral silicon grains and conventional TG ones with $W=L=1.5\ \mu m$ and          |

|            | gate oxide thickness of 500 Å or 1000 Å. (b) Comparison of the output                   |

|            | characteristics of the n-channel LTPS RG-TFTs with lateral silicon grains and           |