# Statistical Metrology of Metal Nanocrystal Memories With 3-D Finite-Element Analysis

Jonathan Shaw, Tuo-Hung Hou, Hassan Raza, Member, IEEE, and Edwin Chihchuan Kan, Senior Member, IEEE

Abstract—We study the parametrical yield of memory windows for the metal nanocrystal (NC) Flash memories with consideration of the 3-D electrostatics and channel percolation effects. Monte Carlo parametrical variation that accounts for the number and size fluctuations in NCs as well as channel length is used to determine the threshold voltage distribution and bit error rate for gate length scaling to 20 nm. Devices with nanowire-based channels are compared with planar devices having the same gate stack structure. Scalability prediction by 1-D analysis is found to be very different from 3-D modeling due to underestimation of effective NC coverage and failure to consider the 3-D nature of the channel percolation effect.

*Index Terms*—Nanocrystal (NC), nonvolatile memories, programming window distribution, 3-D electrostatics.

#### I. INTRODUCTION

UE to the scaling limit of gate length and tunneling oxide thickness, it is difficult for conventional floating gate memories to achieve required retention and interference characteristics while maintaining low-voltage program/erase (P/E) operations [1]. To overcome this inherent design limitation, nanocrystal (NC) [2] memory is considered as one of the promising candidates that enable reduced intercell floating gate coupling, tolerance to local dielectric defect, low P/E voltage, fast P/E speed, and compatibility with current CMOS technology [3]-[7]. In particular, metal NC memories can potentially push further scaling due to large density of states, inherent field enhancement, selectable work function, and tunneling asymmetry between P/E and retention [5], [7]. Furthermore, Coulomb blockade energy can be reduced by replacing the insulating layer in the gate stack by a high- $\kappa$  dielectric, which also leads to an increase in channel-NC coupling due to the field enhancement effect [6], [8].

Manuscript received September 18, 2008; revised May 18, 2009. Current version published July 22, 2009. This work was supported by the National Science Foundation through the Cornell Center of Materials Research and the Center of Nanoscale Systems. The review of this paper was arranged by Editor G.-T. Jeong.

- J. Shaw and E. C. Kan are with the School of Electrical and Computer Engineering, Cornell University, Ithaca, NY 14853 USA (e-mail: jts57@cornell.edu).

- $\hbox{T.-H. Hou is with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan.}$

- H. Raza is with the School of Electrical and Computer Engineering, University of Iowa, Iowa City, IA 52242 USA.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2024108

Fluctuation in memory window due to NC size/density/ registry variations and gate length is one of the main concerns for scalability [9], [10]. The goal of this paper is to illustrate the importance of the 3-D electrostatics and channel percolation effects that are not considered in previous Monte Carlo (MC) statistical metrology of NC memories [9]–[15]. The new model can be used for more accurate scaling prediction. We perform the MC parametrical analysis, with inner loops by the finiteelement (FE) solver in COMSOL to predict the threshold voltage  $(V_{\rm th})$  variations and corresponding bit error rate (BER). Furthermore, nanowire (NW)-based memories with sub-10-nm Si-channel widths have been proposed to obtain large  $V_{\rm th}$ shifts and longer charge retention times by the bottleneck and quantum confinement effects [16]. Metal NC memory with NW [17] channel is studied in comparison with the planar device for  $\Delta V_{\rm th}$  variation analysis. Simulation results indicate that the high percentage of erratic bits will still be one of the main concerns for NW devices with sub-30-nm gate lengths due to NC number density variation. Previously, it has been shown that preferential self-alignment (SA) of NC to the carbon nanotube (CNT) can be achieved [18]. Preferential growth of NC near the channel can offer an effective solution to NC density variation.

# II. DEVICE MODELING AND ASSUMPTIONS

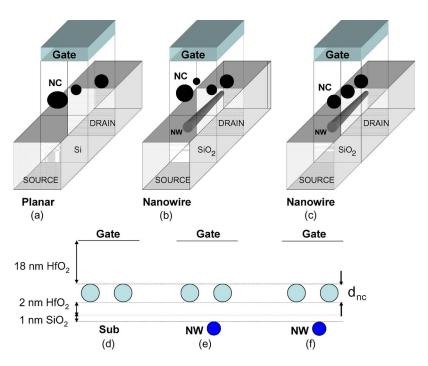

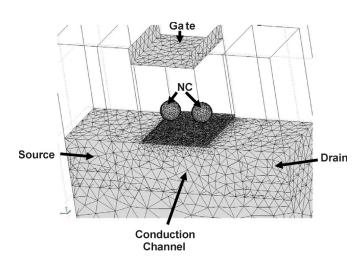

Schematics and a sample mesh of the simulated planar and NW devices [17] are shown in Figs. 1 and 2, respectively. Our model assumes a p-type silicon substrate with  $10^{17}$  cm<sup>-3</sup> doping. For planar devices, a halo-doping profile is added to control short-channel effects (SCEs), and the channel width is fixed at 20 nm. Spherical NCs are embedded in a gate stack with 18 nm HfO<sub>2</sub> control oxide and a heterogeneous tunnel dielectric of 2 nm HfO<sub>2</sub> and 1 nm SiO<sub>2</sub> [8]. The NC diameter is 6.1  $\pm$ 1.2 nm, and the average number density is  $5.0 \times 10^{11}$  cm<sup>-2</sup> with percentage fluctuations of 51% and 34% for 20 and 30 nm channel lengths, respectively, following the experimental distribution from unconstrained self assembly in a gate-first process [19]. Gaussian variations of NC size and channel length, Poisson variations of NC number density, and uniform variation on NC registry have been included in the MC simulation, with statistics extracted from the experiments [17]-[20]. The NW device is 3 nm in diameter [17] and has the same gate stack structure, doping level (but without halo), and source/drain structures as the planar device for direct comparison. All simulation cases assume an electrostatic environment, where the NCs either remain charged with five electrons or uncharged,

Fig. 1. Schematic of metal NC Flash memory with (a) a planar channel, (b) an NW channel, and (c) an NW channel with self-aligned NCs. For the SA case, each NC is centered at locations on top of the channel region. The corresponding cross-sectional views are shown in (d), (e), and (f), respectively. Simulation parameters of the structure: NC diameter  $d_{\rm nc}$ : 6.1 nm; NW diameter: 3 nm; average NC density:  $5.0 \times 10^{11}$  cm<sup>-2</sup>; tunneling oxide: 2 nm HfO<sub>2</sub> on top of 1 nm SiO<sub>2</sub>; and control oxide: 18 nm HfO<sub>2</sub>.

Fig. 2. Sample mesh of the planar device with 20 nm gate length in the COMSOL FE solver.

for calculating the control gate characteristics, unless stated otherwise. Our FE model consists of 3-D Poisson and modified drift-diffusion formalisms, implemented by COMSOL [21]. It does not include detailed quantum transport effects that can enhance the accuracy for sub-90-nm above- $V_{\rm th}$  currents [22]. We also ignore quantum confinement and band-splitting effects, which may be important in NW devices [23], [24]. The classical transport is used to maintain acceptable computational efficiency in the statistical metrology of 3-D geometrical design, where total computation can be accomplished in several weeks on a 64-bit central processing unit 8-GB memory platform. For  $\Delta V_{\rm th}$  fluctuation prediction, our simulation model should be acceptable since 3-D electrostatics and channel percolation below  $V_{\rm th}$  are self-consistently considered. We define BER as

the probability of a programmed bit with an offset in  $V_{\rm th}$  that falls below the nominal "0" state plus a fixed voltage  $V_{\rm tol}$ , which is determined by the sense amplifier tolerance. Table I shows the simulated Gaussian fitted mean threshold voltage shift  $\mu(\Delta V_{\rm th})$  and standard deviation  $\sigma(\Delta V_{\rm th})$  for various device structures.

# III. RESULTS AND DISCUSSION

# A. Fringing Field Effect and Comparison With 1-D Analytical Model

To have a qualitative understanding on  $V_{\rm th}$  fluctuation to account for 3-D electrostatics, we can describe the nominal memory window  $\Delta V_{\rm th}$  in a semiempirical model as [9], [20]

$$\Delta V_{\rm th} = R \cdot \frac{e \cdot N}{C} \tag{1}$$

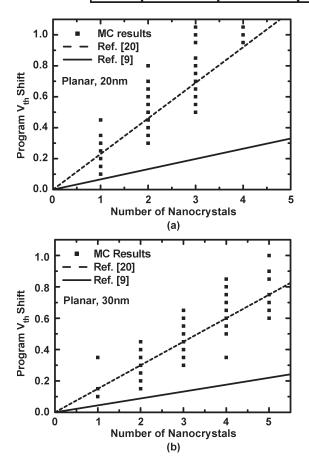

where e is the elemental charge, R is a constant representing the relative strength of channel–NC coupling, C is the 3-D NC-to-control-gate coupling capacitance, and N is the number of electrons stored in each NC. The nominal memory window  $\Delta V_{\rm th}$  as well as  $V_{\rm th}$  fluctuations increases with increasing R through effective NC coverage over the channel. Clearly, the charge in an NC perturbs the channel potential on a larger coverage area than the NC cross-sectional area due to the fringing effect [20]. As shown in Fig. 3,  $\Delta V_{\rm th}$  estimated by the 3-D MC FE solver is significantly greater than the cases where the coverage area is assumed to be the NC cross-sectional area in semi-1-D models. Good agreement can be obtained between the 3-D model [20] and the MC FE solver for  $\Delta V_{\rm th}$  versus the number charges stored in each NC. Due to the discrete nature

#### TABLE I

Gaussian-Fitted Mean Threshold Voltage Shift  $\mu(\Delta V_{\rm th})$ , Standard Deviation  $\sigma(\Delta V_{\rm th})$ , and BER With  $V_{\rm tol}=0.1$  V. FC Cases Refer to the Cases Where All NCs Have Five Electrons Stored. PC Cases Refer to the Cases Where Only NCs Centered on Top of the Channel Region Are Charged. SA Cases Refer to the Cases Where the NCs Are Self-Aligned on the CNT by Surface Energy Preference

| Device | Channel<br>Type | Gate Length<br>(nm) | Diameter/<br>Width (nm) | μ(ΔVth)<br>(V) | $\sigma(\Delta V th)$ | $BER$ $V_{tol} = 0.1 \text{ V}$ |

|--------|-----------------|---------------------|-------------------------|----------------|-----------------------|---------------------------------|

| A      | Planar          | 20                  | 20                      | 0.50           | 0.27                  | $3.85 \times 10^{-2}$           |

| В      | Planar          | 30                  | 20                      | 0.47           | 0.19                  | 1.92 x 10 <sup>-2</sup>         |

| С      | Nanowire, FC    | 20                  | 3                       | 0.53           | 0.28                  | 3.41 x 10 <sup>-2</sup>         |

| D      | Nanowire, FC    | 20                  | 7                       | 0.41           | 0.26                  | 6.65 x 10 <sup>-2</sup>         |

| Е      | Nanowire, FC    | 30                  | 3                       | 0.65           | 0.21                  | 3.4 x 10 <sup>-3</sup>          |

| F      | Nanowire, FC    | 30                  | 7                       | 0.53           | 0.23                  | 3.15 x 10 <sup>-2</sup>         |

| G      | Nanowire, PC    | 20                  | 3                       | 0.16           | 0.29                  | 1.87 x 10 <sup>-1</sup>         |

| Н      | Nanowire, PC    | 20                  | 7                       | 0.17           | 0.33                  | 1.64 x 10 <sup>-1</sup>         |

| I      | Nanowire, PC    | 30                  | 3                       | 0.24           | 0.26                  | 1.42 x 10 <sup>-1</sup>         |

| J      | Nanowire, PC    | 30                  | 7                       | 0.34           | 0.21                  | 7.54 x 10 <sup>-2</sup>         |

| K      | Nanowire, SA    | 20                  | 3                       | 0.32           | 0.11                  | 2.27 x 10 <sup>-2</sup>         |

| L      | Nanowire, SA    | 30                  | 3                       | 0.53           | 0.10                  | 1.52 x 10 <sup>-6</sup>         |

Fig. 3. Threshold voltage shift after programming versus the number of NCs within each planar device with (a) 20 nm and (b) 30 nm gate lengths. Five electrons are stored in each NC. Semi-1-D analytical model assumes that the coverage area is equal to the NC's cross-sectional area, whereas 3-D model incorporates the fringing field enhancement effect on channel–NC coupling. One hundred cases were simulated for each scenario.

of NC array and the spherical shape of NC,  $\Delta V_{\rm th}$  and  $V_{\rm th}$  fluctuation prediction must be calculated rigorously considering the entire 3-D potential profile in the channel.

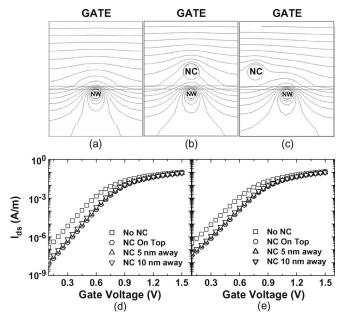

Fig. 4. Cross-sectional view of the 3-D electrostatic potential contours of the NW devices with (a) no NC, (b) one NC centered on top of the NW, and (c) one NC centered 10 nm away from the NW. Five electrons are stored in each NC.  $V_G=2$  V, and the contour spacing is 90 mV. Also shown are the corresponding I-V curves of (d) 3-nm-diameter and (e) 7-nm-diameter NW devices with no NC, one NC centered directly on top of the NW, and one NC centered either 5 or 10 nm away from the NW.

Fig. 4 shows the potential contours of an NW device with NC located directly on top and away from the channel, where the channel potentials are affected by the NC fringing fields and the corresponding I-V curves for NW devices with diameters of 3 and 7 nm. We have found minute fluctuation in  $\Delta V_{\rm th}$  from NC registry variation in planar or NW devices, which suggests an enhanced channel–NC coupling dominated by the fringing field effect. However, the NC registry can affect the charging state during the P/E operations in the NW device since the tunneling length, and hence, the program current can be very different. We consider two asymptotic scenarios: 1) full coverage (FC),

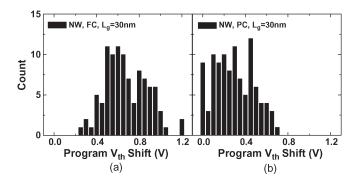

Fig. 5. MC simulation results showing the  $\Delta V_{th}$  distribution of the scenarios where (a) all the NCs within the gate area are charged (FC) or (b) only the NCs that overlap with the channel region are charged (PC). The NW is 3 nm in diameter and 30 nm in gate length. Five electrons are stored in each NC. One hundred cases were simulated for each scenario.

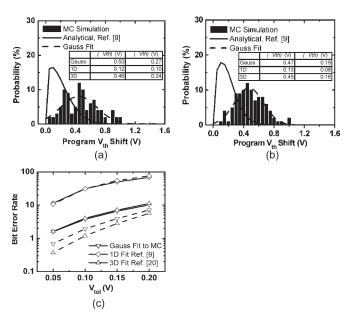

Fig. 6.  $\Delta V_{\rm th}$  distribution probability density curves for planar devices with (a) 20 nm and (b) 30 nm gate lengths. Gaussian-fitted and semi-1-D analytical models are also shown. The inset is a table comparing  $\mu(\Delta V_{\rm th})$  and  $\sigma(\Delta V_{\rm th})$  estimated by semi-1-D, full 3-D electrostatic, and Gaussian-fitted models. Plot (c) compares the corresponding BERs calculated from the three models versus  $V_{\rm tol}$ . The solid lines represent the 20-nm device, and the dashed lines represent the 30-nm device.

where every NC in the gate stack is uniformly charged, and 2) partial coverage (PC), where only NCs overlapping the NW channel are charged. Fig. 5 compares  $\Delta V_{\rm th}$  distribution plots for the PC and FC configurations. The design combination of planar and NW devices is summarized in Table I. Due to the fringing fields coming from NCs that do not overlap with the NW, devices A and D show larger  $\Delta V_{\rm th}$  and slightly tighter distribution than devices G and I.

In either the 1-D [9] or 3-D [20] analytical models, the mean threshold voltage shift  $\mu(\Delta V_{\rm th})$  and the standard deviation  $\sigma(\Delta V_{\rm th})$  can be approximated by

$$\mu(\Delta V_{\rm th}) = R \cdot \frac{e \cdot N}{C} \cdot \overline{N_{\rm td}} \tag{2}$$

$$\sigma(\Delta V_{\rm th}) = \mu \Delta V_{\rm th} \cdot \sqrt{\frac{\sigma^2 N_{\rm td}}{\overline{N_{\rm td}}^2} + \frac{1}{\overline{N_{\rm td}}} \cdot \frac{(\sigma(R))^2}{\overline{R^2}^2}}$$

(3)

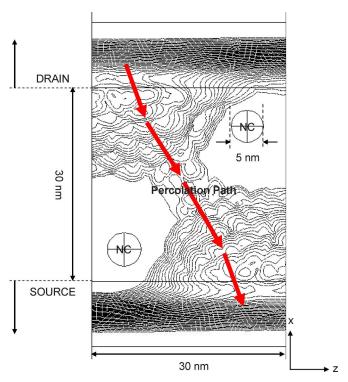

Fig. 7. Contour plot of electron density for a  $30 \times 30$  nm planar device. Each NC is charged with one electron. Electrons in the channel are screened by the NC, and the dominant percolation path of the channel leakage current is highlighted.

where  $\overline{N_{\rm td}}$  is the average number of NCs, and  $\sigma(R)$  is the standard deviation of substrate–NC coupling factor. Fig. 6 compares  $\mu(\Delta V_{\rm th})$ ,  $\mu(\Delta V_{\rm th})$ , and BER as a function of gate length for the analytical models by (2) and (3) [9], [20] and Gaussian-fitted MC simulation. It has been shown that R is a relative weak function of NC diameter when the channel coupling is adequate [20]. Since Gaussian-fitted parameters agree well with the 3-D analytical model, the variation in  $\Delta V_{\rm th}$  is mainly determined by density fluctuation according to (3). However, previous semi-1-D models [9]–[15] excluding 3-D fringing and channel percolation underestimated NC coverage, resulting in severe parametric distribution distortion.

#### B. Impact of Gate Length and NW Diameter

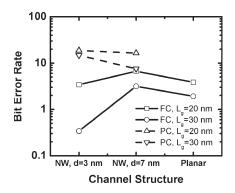

The channel percolation effect of the planar structure is illustrated in Fig. 7. Typically, the percolation effect is enhanced with increasing channel W/L ratio, resulting in more severe  $\Delta V_{\rm th}$  fluctuations [11]. Fig. 8 shows the percentage increase in BER for various device structures by scaling down the effective gate length from 30 to 20 nm. For gate length scaling with a fixed channel width, the number of percolation paths available increases, and a higher BER is observed. As the diameter of NCs becomes larger than the diameter of NW devices, channel–NC coupling is enhanced, and the number of percolation path vanishes in comparison with planar devices. Devices with a larger NW diameter (B and E) have a BER larger than those of the smaller ones (A and D) in FC charging as shown in Table I, dominated by the fringing field effect. In

Fig. 8. BER comparison between planar and NW channels with 20 and 30 nm gate lengths. BER calculated with the following two additional constraints are also shown for illustration: 1) all NCs within the gate region (FC) or 2) only NCs that are centered within the channel area (PC) have five electrons stored.

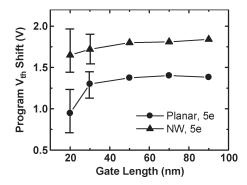

Fig. 9.  $V_{\rm th}$  roll-off behavior with statistical error bars for the 3-nm-diameter NW and planar devices. Each NC is charged with five electrons. NCs are orthogonally aligned with a fixed inter-NC distance of 10 nm and an NC diameter of 5 nm.

contrast, devices I and J with PC charging show a decreasing BER with increasing NW diameter due to  $\Delta V_{\rm th}$  sensitivity to NC density variation when NCs away from the channel are not charged and do not exert additional fringing fields.

# C. Templated Assembly of NC

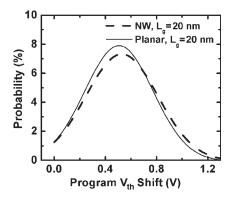

NC placement can be regulated by polymer [25] or protein [26] lattice, and hence, the NC size and position variation becomes negligible. However, the number density and vertical alignment with NW devices will still contribute to  $\Delta V_{\rm th}$  variations. Fig. 9 shows the  $V_{\rm th}$  roll-off behavior and statistical error bars for an array of NCs orthogonally aligned with a fixed inter-NC distance of 10 nm and an NC diameter of 5 nm. NW devices have superior control on the SCE, even in sub-30-nm devices and larger  $\Delta V_{\rm th}$  for the same number of electrons stored in each NC, but we observe NW devices having similar  $\Delta V_{\mathrm{th}}$  fluctuations as the planar devices. Originally, the bottleneck effect [16] with decreasing channel width in the NW device is expected to eliminate the percolation leakage effect and increase mean memory window as well as standard deviation. However, if we consider 3-D fringing,  $\Delta V_{\rm th}$  fluctuation should be less severe in the NW device in comparison with previous semi-1-D models [9], [16]. As illustrated in Fig. 10, planar and 3-nm NW devices can have similar  $\Delta V_{\rm th}$  fluctuation. Although planar devices

Fig. 10. Gaussian-fitted curves to the  $\Delta V_{\rm th}$  distribution estimated by the MC method for the (solid lines) planar and (dash lines) 3-nm NW devices. Gate length is 20 nm, and all NCs within the gate area have five electrons stored.

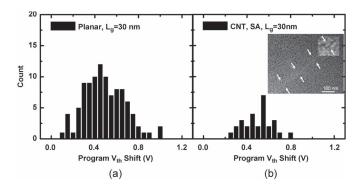

Fig. 11. MC simulation results of (a) planar (100 cases) and (b) 3-nm-diameter self-aligned NW devices (25 cases). Gate length is set at 30 nm. Inset shows an SEM image of self-aligned NC to carbon nanotubes, where NCs are concentrated near the channel area.

are less sensitive to NC number density variation, it lacks the channel-NC coupling enhancement effect in the NW devices.

# D. SA of NC to NW or Nanotube Channels

Previous work has demonstrated that CNT devices can achieve SA of NC to the CNT [18] by surface energy preference. Fig. 11 compares planar to self-aligned NW devices with an average number density of  $10^{12}~\rm cm^{-2}$  near the channel area. With the NC diameter larger than that of the NW, NC–channel coupling is dominant due to the fringing field enhancement. Number density variation on  $\Delta V_{\rm th}$  becomes less severe with increased density near the channel surface area. Thus, we observe higher  $\mu(\Delta V_{\rm th})$  and smaller  $\sigma(\Delta V_{\rm th})$ , which suggests that self-aligned NW devices can be the device candidate to achieve a small BER.

### IV. CONCLUSION

We have demonstrated the importance of including 3-D electrostatics and channel percolation in metal NC memory statistical metrology and examined BER in various channel structures for scaling prediction. Contrary to previous semi-1-D models,  $\Delta V_{\rm th}$  fluctuation is mainly due to number density variation and is less sensitive to NC diameter variation within the range of 6.1  $\pm$  1.2 nm. In addition, the field enhancement

effect from NCs away from the channel has noticeable effects on devices with small width/length ratios. NW devices benefit from the field enhancement and the bottleneck effect to achieve a higher threshold voltage shift, but with diminishing return as the gate area is scaled down even with templated NC placement. SA of NC to NW shows strong promise in both increasing memory windows and controlling  $\Delta V_{\rm th}$  fluctuation.

#### REFERENCES

- G. Atwood, "Future directions and challenges of ETox Flash memory scaling," *IEEE Trans. Device Mater. Rel.*, vol. 4, no. 3, pp. 301–305, Sep. 2004.

- [2] S. Tiwari, F. Rana, K. Chan, H. Hanafi, W. Chan, and D. Buchanan, "Volatile and non-volatile memories in silicon with nano-crystal storage," in *IEDM Tech. Dig.*, 1995, pp. 521–524.

- [3] Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, "Metal nanocrystal memories—Part 1: Device design and fabrication," *IEEE Trans. Electron Devices*, vol. 49, no. 9, pp. 1606–1613, Sep. 2002.

- [4] C. Lee, A. Gorur-Seetharam, and E. C. Kan, "Operational and reliability comparison of discrete-storage nonvolatile memories: Advantages of single- and double-layer metal nanocrystals," in *IEDM Tech. Dig.*, 2003, pp. 557–560.

- [5] M. Takata, S. Kondoh, T. Sakaguchi, H. Choi, J.-C. Shim, H. Kurino, and M. Koyanagi, "New non-volatile memory with extremely high density metal nano-dots," in *IEDM Tech. Dig.*, 2003, pp. 553–556.

- [6] J. J. Lee and D. L. Kwong, "Metal nanocrystal memory with high- $\kappa$  tunneling barrier for improved data retention," *IEEE Trans. Electron Devices*, vol. 52, no. 4, pp. 507–511, Apr. 2005.

- [7] C. Lee, U. Ganguly, V. Narayanan, T. H. Hou, and E. C. Kan, "Asymmetric electric field enhancement in nanocrystal memories," *IEEE Electron Device Lett.*, vol. 52, no. 12, pp. 879–881, Dec. 2005.

- [8] T. H. Hou, C. Lee, V. Narayanan, U. Ganguly, and E. C. Kan, "Design optimization of metal nanocrystal memory—Part 2: Gate-stack engineering," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 3103–3109, Dec. 2006.

- [9] L. Perniola, B. D. Salvo, G. Ghibaudo, A. F. Para, G. Pananakakis, V. Vidal, T. Baron, and S. A. Lombardo, "Modeling of the programming window distribution in multinanocrystals memory," *IEEE Trans. Nan-otechnol.*, vol. 2, no. 4, pp. 277–284, Dec. 2003.

- [10] D. Ielmini, C. M. Compagnoni, A. S. Spinelli, A. L. Lacaita, and C. Geradi, "A new channel percolation model for V<sub>T</sub> shift in discrete-trap memories," in *Proc. IEEE Annu. Int. Rel. Phys. Symp.*, 2004, pp. 515–521.

- [11] R. Gusmeroli, A. S. Spinelli, C. M. Compagnoni, D. Ielmini, F. Morelli, and A. L. Lacaita, "Program and SILC constraints on NC memories scaling: A Monte Carlo approach," in *IEDM Tech. Dig.*, Dec. 5 2005, pp. 1038–1041.

- [12] C. M. Compagnoni, D. Ielmini, A. S. Spinelli, and A. L. Lacaita, "Modeling of tunneling P/E for nanocrystal memories," *IEEE Trans. Electron Devices*, vol. 52, no. 4, pp. 569–576, Apr. 2005.

- [13] C. M. Compagnoni, D. Ielmini, A. S. Spinelli, A. L. Lacaita, C. Gerardi, L. Perniola, B. De Salvo, and S. Lombardo, "Program/erase dynamics and channel conduction in nanocrystal memories," in *IEDM Tech. Dig.*, 2003, pp. 549–552.

- [14] B. D. Salvo, G. Ghibaudo, G. Pananakakis, P. Masson, T. Baron, N. Buffet, A. Fernandes, and B. Guillaumot, "Experimental and theoretical investigation of nano-crystal and nitride-trap memory devices," *IEEE Trans. Electron Devices*, vol. 48, no. 8, pp. 1789–1799, Aug. 2001.

- [15] T. Ishii, T. Osabe, T. Mine, F. Murai, and K. Yano, "Engineering variations: Towards practical single-electron (few-electron) memory," in *IEDM Tech. Dig.*, 2000, pp. 305–308.

- [16] M. Saitoh, E. Nagata, and T. Hiramoto, "Large memory window and long charge-retention time in ultranarrow-channel silicon floating-dot memory," *Appl. Phys. Lett.*, vol. 82, no. 11, pp. 1787–1789, Mar. 2003.

- [17] J. Fu, K. D. Buddharaju, S. H. G. Teo, C. Zhu, M. B. Yu, N. Singh, G. Q. Lo, N. Balasubramanian, and D. I. Kwong, "Trap layer engineered gate-all-around vertically stacked twin Si-nanowire nonvolatile memory," in *IEDM Tech. Dig.*, 2007, pp. 79–82.

- [18] U. Ganguly, E. C. Kan, and Y. Zhang, "Carbon nanotube-based non-volatile memory with charge storage in metal nanocrystals," *Appl. Phys. Lett.*, vol. 87, no. 4, p. 043 108, Jul. 2005.

- [19] C. Lee, U. Ganguly, and E. C. Kan, "Characterization of number fluctuations in gate-last metal nanocrystal nonvolatile memory array beyond

- 90 nm CMOS technology," in *Proc. MRS*, Boston, MA, Nov. 29–Dec. 3 2004, pp. 223–228.

- [20] T.-H. Hou, C. Lee, V. Narayanan, U. Ganguly, and E. C. Kan, "Design optimization of metal nanocrystal memory—Part 1: Nanocrystal array engineering," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 3095– 3102, Dec. 2006.

- [21] Comsol Multiphysics 3.4, Comsol Inc., Burlington, MA, 2005.

[CD-ROM].

- [22] Z. Ren, R. Venugopal, S. Datta, M. Lundstorm, D. Jovanovic, and J. G. Fossum, "The ballistic nanotransistor: A simulation study," in *IEDM Tech. Dig.*, 2000, pp. 715–718.

- [23] Y. Zheng, C. Rivas, R. Lake, K. Alam, T. B. Boykin, and G. Klimeck, "Electronic properties of silicon nanowires," *IEEE Trans. Electron Devices*, vol. 52, no. 6, pp. 1097–1103, Jun. 2005.

- [24] D. D. D. Ma, C. S. Lee, F. C. K. Au, S. Y. Tong, and S. T. Lee, "Small-diameter silicon nanowire surfaces," *Science*, vol. 299, no. 5614, pp. 1874–1877, Mar. 2003.

- [25] K. W. Guarini, C. T. Black, Y. Zhang, I. V. Babich, E. M. Sikorski, and L. M. Gignac, "Low voltage, scalable nanocrystal FLASH memory fabricated by templated self assembly," in *IEDM Tech. Dig.*, 2003, pp. 541–544.

- [26] S. Tang, C. Mao, Y. Liu, D. Q. Kelly, and S. K. Banerjee, "Nanocrystal Flash memory fabricated with protein-mediated assembly," in *IEDM Tech. Dig.*, 2005, pp. 174–177.

**Jonathan Shaw** received the B.S. degree in electrical engineering from the University of California, San Diego, CA, in 2006. He is currently working toward the Ph.D. degree at the School of Electrical and Computer Engineering, Cornell University, Ithaca. NY.

His current research interests include nanocrystal memories and molecular-based memory devices.

**Tuo-Hung Hou** was born in Chia-Yi, Taiwan, in 1975. He received the B.S. and M.S. in electronic engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1996 and 1998, respectively, and the Ph.D. degree in electrical and computer engineering from Cornell University, Ithaca, NY, in 2008.

From 1998 to 2000, he served as a Second Lieutenant in the Army, Taiwan. In 2000, he joined Taiwan Semiconductor Manufacturing Company (TSMC). From 2001 to 2003, he was also a TSMC

assignee at International SEMATECH, Austin, TX. During his tenure with TSMC, he has contributed to several key front-end processes such as spike annealing, high-k/metal-gate stack through atomic layer chemical deposition, and reliability improvement of ultrathin gate oxide. Since August 2008, he has been an Assistant Professor with the Department of Electronics Engineering, National Chiao Tung University. He is the author or a coauthor of more than 30 technical papers. He is the holder of seven U.S. patents.

Dr. Hou received an IEEE Electron Devices Society Ph.D. student fellowship in 2007.

Hassan Raza (M'07) received the B.S. degree (with honors) in electrical engineering from the University of Engineering and Technology, Lahore, Pakistan, in July 2001 and the M.S. and Ph.D. degrees in electrical engineering from Purdue University, West Lafayette, IN, in December 2002 and May 2007, respectively.

In May 2007, he joined the Center for Nanoscale Systems, Cornell University, Ithaca, NY, as a Post-doctoral Associate. Since May 2009, he has been an Assistant Professor with the School of Electrical and

Computer Engineering, University of Iowa, Iowa City. His research interests include the experimental, theoretical, and computational aspects of quantum transport for novel logic and memory devices in various material systems, e.g., graphene, carbon nanotubes, molecules, and quantum dots.

Dr. Raza received the Magoon Award for Excellence in Teaching from the School of Engineering, Purdue University, in 2004.

Edwin Chihchuan Kan (S'86–M'91–SM'05) received the B.S. degree in electrical engineering from the National Taiwan University, Taipei, Taiwan, in 1984 and the M.S. and Ph.D. degrees in electrical engineering from the University of Illinois, Urbana, in 1988 and 1992, respectively.

From 1984 to 1986, he served as a Second Lieutenant in the Air Force, Taiwan. In January 1992, he joined Dawn Technologies as a Principal CAD Engineer, where he developed advanced electronic and optical device simulators and technology CAD

framework. From 1994 to 1997, he was a Research Associate with Stanford University, Stanford, CA, where he led projects such as TCAD 1-2-3-D tool development, software architecture definition, model hierarchy, and MEMS modeling. From 1997 to 2002, he was an Assistant Professor with the School of Electrical and Computer Engineering, Cornell University, Ithaca, NY, where he is currently an Associate Professor. He has spent the summers of 2000 and 2001 at IBM Microelectronics, Yorktown Heights and Fishkill, NY, in the IBM Faculty Partner Program. In 2004 and 2005, he was a Visiting Researcher at Intel Research, Santa Clara, CA, and a Visiting Professor at Stanford University during his sabbatical leave. His main research areas include CMOS technology, semiconductor device physics, systems-on-a-chip, composite CAD development, and numerical methods for PDE and ODE.

Dr. Kan received the Presidential Early Career Award for Scientists and Engineer (PECASE) in October 2000 from the White House. He also received several teaching awards from Cornell Engineering College for his CMOS and MEMS courses.