# Impact of Gate Leakage on Performances of Phase-Locked Loop Circuit in Nanoscale CMOS Technology

Jung-Sheng Chen and Ming-Dou Ker, Fellow, IEEE

Abstract—In the nanoscale CMOS technology, the thin gate oxide causes large gate-tunneling leakage. In this brief, the influence of gate-tunneling leakage in the MOS capacitor (used in the loop filter) on the circuit performance of the phase-locked loop (PLL) in the nanoscale CMOS technology has been investigated and analyzed. The basic PLL with a second-order loop filter is used to observe the impact of gate-tunneling leakage on the performance degradation of the PLL in a 90-nm CMOS process. The MOS capacitors with different oxide thicknesses are used to investigate their impact on the PLL performance. The locked time, static phase error, and jitter of the second-order PLL are found to be degraded by the gate-tunneling leakage of the MOS capacitor used in the loop filter.

Index Terms—Gate-tunneling leakage, loop filter, MOS capacitor, phase-locked loop (PLL).

## I. INTRODUCTION

THE REDUCTION of power consumption is very important to the portable microelectronic products. In general, the most common and efficient way to reduce the power consumption in CMOS very large scale integrated circuits is to reduce the power-supply voltage. The standard supply voltage has been scaled down from 2.5 V to 1 V or even lower. The gate-oxide thickness of the MOS transistor becomes thinner to reduce its normal operation voltage (power-supply voltage). The thinner gate-oxide thickness causes large gate-tunneling leakage (gate leakage current) in the nanoscale CMOS technology. In digital circuits, the gate-tunneling leakage results in the high standby power consumption [1]. Therefore, to suppress the impact of gate-tunneling leakage is a very important circuit-design issue in the nanoscale CMOS processes [2], [3].

Recently, clock synthesizers have been widely used in the high-speed data-processing devices such as microprocessors, DSPs, and communication systems. A clock synthesizer generates several sets of clock signals with different frequencies or phases from a reference clock signal. Clock synthesizers

Manuscript received December 10, 2008; revised April 19, 2009. First published June 19, 2009; current version published July 22, 2009. This work was supported in part by the National Science Council (NSC), Taiwan, under Contract NSC 97-2221-E-009-170 and by "Aim for the Top University Plan" of the National Chiao Tung University and Ministry of Education, Hsinchu, Taiwan. The review of this brief was arranged by Editor C.-Y. Lu.

J.-S. Chen is with the Power Conversion Taiwan, Fairchild Semiconductor Corporation, Hsinchu 300, Taiwan.

M.-D. Ker is with the Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, and also with the Department of Electronic Engineering, I-Shou University, Kaohsiung, Taiwan (e-mail: mdker@ieee.org). Digital Object Identifier 10.1109/TED.2009.2022696

are usually implemented with the phase-locked loop (PLL). The demand on low-jitter PLL has become strong to avoid the time-skew problem between the clock and the data signals. To improve the PLL performance, the loop filter is added into the PLL to make it stable and to filter out the noise. The loop filter was usually formed with resistor and capacitor. The capacitor of the loop filter needs a large capacitance to make the PLL stable, which is often realized with MOSFET (MOS capacitor) to reduce the occupied silicon area. However, the MOS capacitor with thinner gate-oxide thickness in the loop filter will also have a larger gate-tunneling leakage in the advanced CMOS technology, which will influence the PLL performance. Recently, some compensation techniques, such as the modified capacitor structure [4], [5], opamp-based compensation [6]–[8], nonopamp-based compensation [9], capacitor multiplier [10]-[12], and digital filter techniques [13], have been developed to compensate the gate-tunneling current of the MOS capacitor used in the loop filter of the PLL. However, the impact from the gate-tunneling leakage of the MOS capacitor in the loop filter on the PLL performance was not clearly investigated and reported in the literature.

In this brief, the influence of the gate-tunneling leakage on the performance of the PLL is investigated and analyzed in a 90-nm CMOS process [14]. The normal operating voltage of the MOSFET device is only 1 V in such a 90-nm CMOS process. The gate-tunneling leakage of the MOS capacitor is simulated by SPICE with BSIM4 model. The BSIM4 model was included with the gate-tunneling leakage [15]–[17]. The MOS capacitors realized with thick or thin gate oxides in the loop filter are used to investigate the impact of gate-tunneling leakage on the PLL performance.

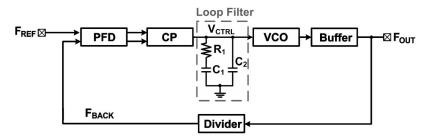

## II. PLL

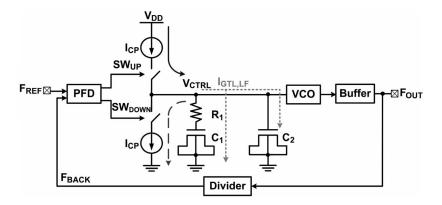

A PLL is basically an oscillator whose frequency is locked onto some frequency component of an input signal. Fig. 1 shows the basic PLL with a second-order low-pass loop filter [18]. PLL is a second-order negative-feedback system similar to the *RLC* circuit. PLL may be stable or unstable, depending on its phase margin. Stability affects PLL performance, such as settling time, static phase error, and jitter. The capacitor of the loop filter is used to integrate the charge-pump (CP) current and to generate an averaged control voltage, which ensures the proper output frequency for the PLL. The loop filter is also used to generate the pole and zero to adjust the bandwidth and the phase margin of the PLL. In general, the bandwidth of

PFD: Phase-Frequency Detector

**CP: Charge Pump**

**VCO: Voltage Control Oscillator**

**Buffer: Differential Input to Single Output Converter**

Divider: Frequency Divider (divided by N)

Fig. 1. Basic PLL with a second-order low-pass loop filter.

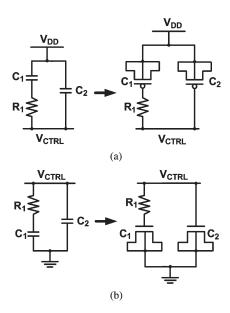

the PLL is usually designed about only 1/10–1/20 of the input reference frequency for system stability. A PLL consists of a phase/frequency detector (PFD), a CP, a loop filter, a voltagecontrolled oscillator (VCO), and a frequency divider (divided by an integer N). The negative feedback synchronizes the internal signal  $(F_{\text{BACK}})$ , which is from the frequency divider, to the external reference signal  $(F_{REF})$  by comparing their phases. The PFD develops two output signals, which are proportional to the phase errors. The CP is used to convert the logic states of PFD into analog signals for controlling the VCO, where the frequency of the output signal will be changed by charging or discharging the loop filter. In the loop filter, extra poles and zeros should be introduced to filter out high-frequency signals from the PFD and the CP. The PLL will be "locked" when the phase difference between  $F_{\rm REF}$  and  $F_{\rm BACK}$  is kept constant. Therefore, the phases of  $F_{REF}$  and  $F_{BACK}$  are aligned, and the frequency of the output signal  $(F_{OUT})$  is N-times of the input reference signal  $(F_{REF})$ . The loop filter realized with a secondorder low-pass filter has been widely used in the PLL design to improve the stability and to suppress the high-frequency noise. The on-chip capacitor in the second-order loop filter can be realized by PMOS and NMOS transistors, respectively, as shown in Fig. 2(a) and (b). In general, the filter capacitor  $C_1$  has a typical range from 50 to 400 pF. The capacitor  $C_2$  smoothes the large IR ripple on the signal of  $V_{\text{CTRL}}$ . The resistor  $R_1$ provides the instantaneous phase correction without affecting the averaged frequency of the VCO.

The capacitor of the loop filter needs a large capacitance to make the PLL stable, but it also has a large gate-tunneling leakage through the MOS capacitor in the loop filter to degrade the PLL performance in the nanoscale CMOS technology. The gate-tunneling leakage of the MOSFET has been modeled as [15]–[17]

$$J_g = A \left[ \frac{T_{\text{oxref}}}{t_{\text{ox}}} \right]^{\text{ntox}} \frac{V_g V_{\text{aux}}}{T_{\text{ox}}^2} e^{-B(\alpha - \beta |V_{\text{ox}}|)(1 + \gamma |V_{\text{ox}}|)t_{\text{ox}}}$$

(1)

where  $A=q^2/8\pi h\phi_B$ ,  $B=8\pi\sqrt{2qm_{\rm ox}}\phi_B^{3/2}/3h$ ,  $m_{\rm ox}$  is the effective carrier mass in oxide,  $\phi_B$  is the tunneling barrier height,  $t_{\rm ox}$  is the oxide thickness,  $T_{\rm oxref}$  is the reference oxide thickness, and  $V_{\rm aux}$  is an auxiliary function which approximates the density of the tunneling carriers.  $\alpha$ ,  $\beta$ , and  $\gamma$  are the physical

Fig. 2. Second-order loop filter realized with (a) PMOS and (b) NMOS capacitors.

parameters defined by device technology.  $V_g$  is the gate voltage of the MOSFET device, ntox is a fitting parameter, and  $V_{\rm ox}$  is the voltage across the oxide of the MOSFET device.

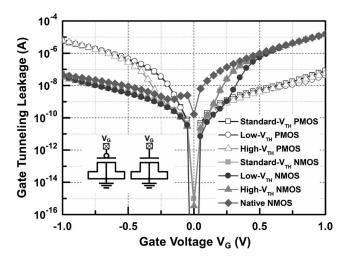

The MOS capacitor of the loop filter is operated in the stronginversion region in the PLL. In (1), the gate-tunneling-leakage density strongly depends on the oxide thickness, device size, and voltage across the oxide of the MOSFET. Fig. 3 shows the dependence of the gate-tunneling leakage on the NMOS and PMOS capacitors with different threshold voltages under different gate voltages in a 90-nm 1-V CMOS technology. The normal operating voltage of the MOSFET device is only 1 V, and the typical oxide thickness of the MOSFET device is 2.33 nm in the given 90-nm CMOS process. The NMOS capacitor has larger gate-tunneling leakage than that of the PMOS capacitor. The electron conduction-band (ECB) tunneling is the dominant component of the gate-tunneling leakage in the NMOS device, whereas it is the hole valance-band (HVB) tunneling in the PMOS device. Because the barrier height for HVB (4.5 eV) is significantly greater than that of ECB (3.1 eV), this results in the much lower gate-tunneling leakage in the PMOS device [15]. The summary of gate-tunneling leakage per unit area of the

Fig. 3. Simulated gate-tunneling leakage on the different threshold-voltage NMOS and PMOS capacitors under the different gate voltages in a 90-nm 1-V CMOS technology.

TABLE I

GATE-TUNNELING LEAKAGE PER UNIT AREA OF NMOS AND

PMOS CAPACITORS WITH DIFFERENT THRESHOLD

VOLTAGES IN A 90-NM CMOS PROCESS

| MOS Capacitor            |                                  |                          |                                  |  |  |

|--------------------------|----------------------------------|--------------------------|----------------------------------|--|--|

| NMOS                     |                                  | PMOS                     |                                  |  |  |

| Structure                | Gate Tunneling Leakage           | Structure                | Gate Tunneling Leakage           |  |  |

| Standard-V <sub>TH</sub> | 1.11 nA/μm <sup>2</sup>          | Standard-V <sub>TH</sub> | $0.654 \text{ nA/}\mu\text{m}^2$ |  |  |

| High-V <sub>TH</sub>     | $0.764 \text{ nA/}\mu\text{m}^2$ | High-V <sub>TH</sub>     | $0.401 \text{ nA/}\mu\text{m}^2$ |  |  |

| Low-V <sub>TH</sub>      | 1.161 nA/μm <sup>2</sup>         | Low-V <sub>TH</sub>      | $0.701 \text{ nA/}\mu\text{m}^2$ |  |  |

| Native NMOS              | 1.571 nA/μm <sup>2</sup>         |                          |                                  |  |  |

NMOS and PMOS capacitors with different threshold voltages in the given 90-nm CMOS process is shown in Table I. The gate voltage  $V_G$  is set to 0.492 V in the loop filter of the PLL in this study. The thin-oxide NMOS device with the low threshold voltage has larger gate-tunneling leakage than the other devices in the same 90-nm CMOS process.

# III. EFFECT OF GATE-TUNNELING LEAKAGE IN MOS CAPACITOR ON THE PERFORMANCE OF THE PLL CIRCUIT

The static phase error, settling time, and jitter are the key factors in the PLL design and application, which will cause the time-skew problem to induce system malfunction. In this work, the PLL with a second-order low-pass loop filter is used to investigate the impact from gate-tunneling leakage of the MOS capacitor on the PLL performance. The design parameters and simulated results of the second-order PLL in a 90-nm CMOS process are shown in Table II. To compare the impact of gatetunneling leakage in the MOS capacitor on the PLL performance, the loop filter  $(C_1, C_2, \text{ and } R_1)$  in the second-order PLL is simulated with ideal capacitor and resistor in Table II as a reference. The  $C_1$  and  $C_2$  capacitors of the low-pass loop filter in the PLL, as shown in Fig. 2, are replaced by the MOS capacitors with different oxide thickness to investigate the impact of gate-tunneling leakage on the PLL performance. The capacitances of the different MOS capacitors  $C_1$  and  $C_2$ are 85.172 and 8.782 pF, respectively, under the gate voltage of

TABLE II

DESIGN PARAMETERS AND SIMULATED RESULTS OF THE

SECOND-ORDER PLL IN A 90-NM CMOS PROCESS

| Design Parameters of PLL in a Standard 90-nm CMOS Process |          |                             |           |  |  |

|-----------------------------------------------------------|----------|-----------------------------|-----------|--|--|

| Operating Voltage                                         | 1 V      | C1                          | 85.172 pF |  |  |

| Input Frequency                                           | 25 MHz   | C2                          | 8.782 pF  |  |  |

| Output Frequency                                          | 200 MHz  | R1                          | 3.2168 kΩ |  |  |

| Charge Pump Current                                       | 50 μΑ    | Phase Margin                | 57°       |  |  |

| Divided by N                                              | 8        | Loop Bandwidth              | 1.8 MHz   |  |  |

| VCO Gain                                                  | 625 MHz  | Damping Factor              | ≈ 1.1     |  |  |

| Simulated Results of PLL in a Standard 90-nm CMOS Process |          |                             |           |  |  |

| Locked Time                                               | 1.3 μsec | Output Jitter<br>at 200 MHz | 2.7 psec  |  |  |

| Static Phase Error                                        | 45 psec  | Total Power<br>Consumption  | 4.8647 mW |  |  |

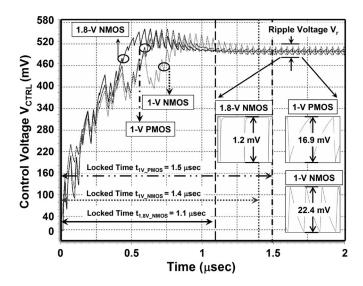

Fig. 4. Simulated transition waveforms of control voltage  $(V_{\rm CTRL})$  to find the locked time under the MOS capacitors with different oxide thickness in the second-order PLL.

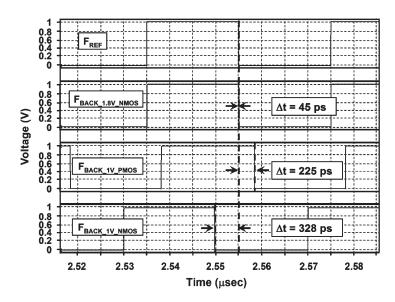

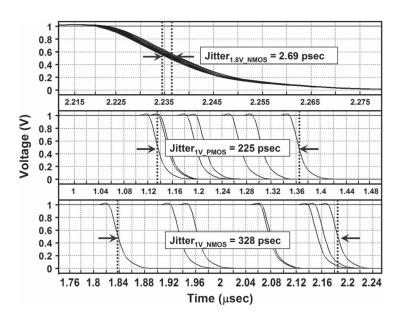

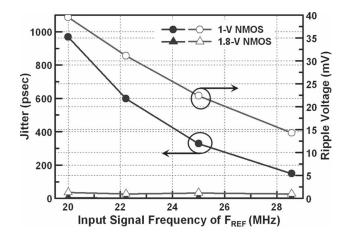

0.492 V. Fig. 4 shows the simulated transition waveforms of the control voltage  $(V_{CTRL})$  to find the locked time under the MOS capacitors with different oxide thickness in the second-order PLL. The PLL design with thin-oxide MOS capacitors (1-V NMOS and PMOS) has longer locked time and larger ripple voltage  $V_r$  than that with thick-oxide MOS capacitor (1.8-V NMOS). The simulated static phase error  $\Delta t$  under the MOS capacitors with different oxide thickness in the second-order PLL is shown in Fig. 5. The thin-oxide MOS capacitors (1-V NMOS and PMOS) cause larger static phase error  $\Delta t$  than that with thick-oxide MOS capacitor (1.8-V NMOS) in the secondorder PLL. The simulated voltage waveforms to find the jitter under the MOS capacitors with different oxide thicknesses in the second-order PLL is shown in Fig. 6. The thin-oxide MOS capacitors (1-V NMOS and PMOS) cause larger jitter than that with thick-oxide MOS capacitor (1.8-V NMOS) in the secondorder PLL, due to the large ripple voltage at the  $V_{\rm CTRL}$  node. The dependence of the different input-signal frequencies on the jitter and ripple voltage under the MOS capacitor with different oxide thickness in the second-order PLL is shown in Fig. 7.

Fig. 5. Simulated static phase error  $\Delta t$  under the MOS capacitors with different oxide thickness in the second-order PLL.

Fig. 6. Simulated voltage waveforms to find the jitter under the MOS capacitors with different oxide thicknesses in the second-order PLL.

Fig. 7. Dependence of different input-signal frequencies on the jitter and ripple voltage under the MOS capacitors with different oxide thickness in the second-order PLL.

The higher input-signal frequency  $F_{\rm REF}$  has a smaller jitter in the second-order PLL due to the gate-tunneling leakage.

# IV. DISCUSSION

In general, the capacitance of the MOS capacitor  $C_1$  is larger than that of the MOS capacitor  $C_2$  in the second-order PLL design, as shown in Fig. 1. Because the capacitance of the MOS capacitor is proportional to the device size and oxide thickness, the gate-tunneling leakage of the MOS capacitor  $C_1$  is larger than that of the capacitor  $C_2$ . The circuit schematic of Fig. 1 can be simplified to that of Fig. 8, where the current  $I_{\rm CP}$  is the CP current, and the current  $I_{\rm GTL,LF}$  is the total gate-tunneling leakage of the MOS capacitors  $C_1$  and  $C_2$ . The CP current  $I_{\rm CP}$ , which is controlled by the phase difference between  $F_{\rm REF}$  and  $F_{\rm BACK}$  signals through the PFD, is working as a constant current source. The effective charge current  $I_C$  through

Fig. 8. Schematic of the second-order PLL including the gate-tunneling leakage in the loop filter.

MOS capacitors  $\mathcal{C}_1$  and  $\mathcal{C}_2$  in the second-order PLL can be expressed as

$$I_C = I_{\rm CP} - I_{\rm GTL, LF}. (2)$$

To reach the locked state (phase difference between  $F_{\rm REF}$  and  $F_{\rm BACK}$  is constant), the second-order PLL needs a setting time for system stability. The gate-tunneling leakage reduces the effective charge current  $I_C$ , therefore, the PLL needs more charge time to make the control voltage  $V_{\rm CTRL}$  into the static state for controlling the VCO oscillation at the correct frequency. The locked time of the second-order PLL is increased due to the gate-tunneling leakage of the MOS capacitor.

In the locked state, the dependence of gate-tunneling leakage on the ripple voltage  $V_r$  in the second-order PLL can be written as

$$\Delta V_r = \frac{I_{\rm GTL, LF} \times T_{\rm REF}}{C_1} \tag{3}$$

where  $T_{\rm REF}$  is the period of input signal  $F_{\rm REF}$ . The amount of ripple voltage  $V_r$  is proportional to the gate-tunneling leakage. The large gate-tunneling current of the MOS capacitor will cause a large ripple voltage at the  $V_{\rm CTRL}$  node in the second-order PLL. In (3), the ripple voltage  $V_r$  is also proportional to the period of input signal  $F_{\rm REF}$ , Therefore, the higher input-signal frequency causes a smaller ripple voltage in the second-order PLL, as shown in Fig. 7. According to (3), the dependence of gate-tunneling leakage on the jitter of the second-order PLL can be expressed as

$$\text{Jitter} \propto \Delta V_r \times K_{\text{VCO}} = \frac{I_{\text{GTL,LF}} \times K_{\text{VCO}}}{f_{\text{REF}} \times C_1} \tag{4}$$

where the  $K_{\rm VCO}$  (Hz/V) is the gain of the VCO, and  $f_{\rm REF}$  is the input frequency of input signal  $F_{\rm REF}$ . The large ripple voltage  $\Delta V_r$  and the low input frequency of  $F_{\rm REF}$  cause large jitter in the second-order PLL. Therefore, the gate-tunneling leakage of the MOS capacitor in the loop filter has serious impact on the PLL performance. To reduce the impact from the gate-tunneling leakage of the MOS capacitor in the loop filter on the PLL performance, the PLL should be designed with small  $K_{\rm VCO}$  gain in the VCO.

When the PLL is operating in the locked state, the feedback clock signal  $(F_{\rm BACK})$  compares with the reference clock signal  $(F_{\rm REF})$  via the CP to generate loop voltage  $(V_{\rm CTRL})$  for

controlling the VCO frequency. The CP has always supplied the current pulses to compensate the gate-tunneling leakage of the MOS capacitor. The dependence of gate-tunneling leakage on the static phase error  $\Delta t$  of the second-order PLL can be expressed as

$$\Delta t \propto \frac{I_{\rm GTL,TL}}{I_{\rm CP}} \times T_{\rm REF}.$$

(5)

To reduce the static phase error in the second-order PLL, the CP should be designed with a large constant current.

The different layout structures will also influence the gate-tunneling leakage of the MOS transistor in the nanoscale CMOS process. When the equivalent gate-oxide resistance is also reduced due to the oxide thickness scaling down, the gate resistor (poly resistance) may lead to an effective gate-bias drop resulting in the decrease of drain current and tunneling leakage. As a result, the threshold voltage of a thin-oxide device is apparently increased by the voltage drop on gate poly resistor and fluctuates due to the gate-tunneling leakage [19]. Because the gate-tunneling leakage of the MOSFET is proportional to the voltage drop through the gate oxide, the MOS capacitor should be drawn in the layout with fewer gate fingers to reduce the negative impact of gate-tunneling leakage on the PLL performance.

# V. CONCLUSION

The influence from the gate-tunneling leakage of the MOS capacitor on the circuit performance in the second-order PLL has been analyzed and investigated in a 90-nm 1-V CMOS process. The locked time, static phase error, and jitter of the second-order PLL were degraded by the gate-tunneling leakage of the MOS capacitor in the loop filter. The higher input-signal frequency can be used to reduce the negative impact of gate-tunneling leakage on the performance of the second-order PLL in nanoscale CMOS technology. The PMOS device with high threshold voltage and thick oxide thickness can be used to realize the MOS capacitor in the loop filter for achieving the second-order PLL with low-jitter performance.

# ACKNOWLEDGMENT

The authors would like to thank Editor C.-Y. Lu and his reviewers for their valuable suggestions to improve this manuscript.

#### REFERENCES

- [1] W. K. Henson, N. Yang, S. Kubicek, E. M. Vogel, J. J. Wortman, K. De Meyer, and A. Maem, "Analysis of leakage currents and impact on off-state power consumption for CMOS technology in the 100-nm regime," *IEEE Trans. Electron Devices*, vol. 47, no. 7, pp. 1393–1400, Jul. 2000.

- [2] M. Drazdziulis and P. Larsson-Edefors, "A gate leakage reduction strategy for future CMOS circuits," in *Proc. IEEE Eur. Solid-State Circuits Conf.*, 2003, pp. 317–320.

- [3] C.-H. Choi, K.-Y. Nam, Z. Yu, and R. W. Dutton, "Impact of gate direct tunneling current on circuit performance: A simulation study," *IEEE Trans. Electron Devices*, vol. 48, no. 12, pp. 2823–2829, Dec. 2001.

- [4] K. Minami, M. Fukaishi, M. Mizuno, H. Onishi, K. Noda, K. Imai, T. Horiuchi, H. Yamaguchi, T. Sato, K. Nakamura, and M. Yamashina, "A 0.10 μm CMOS, 1.2 V, 2 GHz phase-locked loop with gain compensation VCO," in *Proc. IEEE Custom Integr. Circuits Conf.*, 2001, pp. 213–216.

- [5] R. Holzer, "A 1 V CMOS PLL designed in high-leakage CMOS process operating at 10–700 MHz," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2002, pp. 272–274.

- [6] R. Maley, "Method and apparatus for tunneling leakage current compensation," U.S. Patent 6 744 303, Jun. 1, 2004.

- [7] K. Ho, "Method and apparatus for gate current compensation," U.S. Patent 6 696 881, Feb. 24, 2004.

- [8] C.-N. Chuang and S.-I. Liu, "A 1 V phase locked loop with leakage compensation in 0.13 μm CMOS technology," *IEICE Trans. Electron.*, vol. E89-C, no. 3, pp. 295–299, Mar. 2006.

- [9] Y. Frans, N. Nguyen, B. Daly, Y. Wang, D. Kim, T. Bystrom, D. Olarte, and K. Donnelly, "A 1–4 Gbps quad transceiver cell using PLL with gate current leakage compensator in 90 nm CMOS," in *Proc. IEEE Int. Symp. VLSI Circuits Dig. Tech. Papers*, 2004, pp. 134–137.

- [10] Y. Tang, M. Ismail, and S. Bibyk, "Adaptive Miller capacitor multiplier for compact on-chip PLL filter," *Electron. Lett.*, vol. 39, no. 1, pp. 43–45, Jan. 2003.

- [11] G. Yan, C. Ren, Z. Guo, Q. Ouyang, and Z. Chang, "A self-biased PLL with current-mode filter for clock generation," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2005, pp. 420–421.

- [12] J. Yan, H. Zheng, X. Zeng, and T. Tang, "Compact current-mode loop filter for PLL applications," *Electron. Lett.*, vol. 41, no. 23, pp. 1257– 1258, Nov. 2005.

- [13] H.-C. Lin, B. Haroun, T. Foo, J.-S. Wang, B. Helmick, T. Mayhugh, C. Barr, and J. Kirkpatrick, "A PVT tolerant 0.18 MHz to 600 MHz selfcalibrated digital PLL in 90 nm CMOS process," in *IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers*, 2004, pp. 488–541.

- [14] J.-S. Chen and M.-D. Ker, "Impact of gate tunneling leakage on performances of phase locked loop circuit in nanoscale CMOS technology," in *Proc. IEEE Int. Rel. Phys. Symp.*, 2007, pp. 664–665.

- [15] W.-C. Lee and C. Hu, "Modeling gate and substrate currents due to conduction- and valence-band electron and hole tunneling," in *Proc. IEEE Int. Symp. VLSI Technol. Dig. Tech. Papers*, 2000, pp. 198–199.

- [16] K. M. Cao, W.-C. Lee, W. Liu, X. Jin, P. Su, S. K. H. Fung, J. X. An, B. Yu, and C. Hu, "BSIM4 gate leakage model including source-drain partition," in *IEDM Tech. Dig.*, 2000, pp. 815–818.

- [17] C.-H. Choi, K.-H. Oh, J.-S. Goo, Z. Yu, and R. W. Dutton, "Direct tunneling current model for circuit simulation," in *IEDM Tech. Dig.*, 1999, pp. 735–738.

- [18] D. H. Wolaver, *Phase-Locked Loop Circuit Design*. Englewood Cliffs, NJ: Prentice-Hall, 1991.

- [19] M. Koh, K. Iwamoto, W. Mizubayashi, H. Murakami, T. Ono, M. Tsuno, T. Mihara, K. Shibahara, S. Yokoyama, S. Miyazaki, M. M. Miura, and M. Hirose, "Threshold voltage fluctuation induced by direct tunnel leakage current through 1.2–2.8 nm thick gate oxides for scaled MOSFETs," in *IEDM Tech. Dig.*, 1998, pp. 919–922.

Jung-Sheng Chen received the B.S. degree from the Department of Electronics Engineering, National Taiwan University of Science and Technology, Taipei, Taiwan, in 2000, the M.S. degree in engineering and system science from National Tsing-Hua University, Hsinchu, Taiwan, in 2002, and the Ph.D. degree from the Institute of Electronics, National Chiao-Tung University, Hsinchu, in 2007.

He is currently a Circuit Design Engineer with Power Conversion Taiwan, Fairchild Semiconductor Corporation, Hsinchu. His research interests include

reliability design of analog circuits as well as power management integrated circuits and systems.

Ming-Dou Ker (S'92–M'94–SM'97–F'08) received the Ph.D. degree from the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan, in 1993

He was a Department Manager with the VLSI Design Division, Computer and Communication Research Laboratories, Industrial Technology Research Institute, Hsinchu. Since 2004, he has been a Full Professor with the Department of Electronics Engineering, National Chiao-Tung University, where from 2006 to 2008, he served as the Director of the

master's degree program of the College of Electrical Engineering and Computer Science, as well as the Associate Executive Director of National Science and Technology Program on System-on-Chip in Taiwan. Since 2008, he has been the Chair Professor and Vice-President of I-Shou University, Kaohsiung, Taiwan. In the field of reliability and quality design for circuits and systems in CMOS technology, he has published over 360 technical papers in international journals and conferences. He is the inventor/co-inventor of 144 U.S. and 144 Taiwan patents after his many proposed inventions to improve the reliability and quality of integrated circuits (ICs). He had been invited to teach and/or to consult on the reliability and quality design for IC products by hundreds of design houses and semiconductor companies in the worldwide IC industry. His current research interests include reliability and quality design for nanoelectronics and gigascale systems, high-speed and mixed-voltage I/O interface circuits, onglass circuits for system-on-panel applications, and biomimetic circuits and systems for intelligent prosthesis.

Prof. Ker has served as a member of the Technical Program Committee and the session chair of numerous international conferences. He has served as Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS. He was selected as distinguished lecturer in the IEEE Circuits and Systems Society (2006–2007) and in the IEEE Electron Devices Society (2008–2009). He was the president of Foundation in Taiwan ESD Association. In 2008, he was elevated to IEEE Fellow with the citation of "for contributions to electrostatic protection in integrated circuits and performance optimization of VLSI microsystems." In 2009, he was awarded as one of the top ten Distinguished Inventors in Taiwan, and he is one of the top hundred Distinguished Inventors in China.