國立交通大學

電機與控制工程學系

碩士論文

應用於 Power IC 之 700 伏特 LIGBT 元件研發

Design and Implementation of 700V LIGBT for Power

IC Application

研究 生：洪嘉偉

指 導 教 授：張 隆 國 博 士

中華民國九十四年七月

以高線性度 Gm-C 為架構的

可程式化類比陣列

Based on high linearity Gm-C structure for

application of Field Programmable Analog Array

學 生：陳鵬宇

Student : Peng-Yu Chen

指導教授：張隆國 博士

Advisor : Dr. Lon-Kou Chang

A Thesis

Submitted to Institute of Electrical and Control Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Electrical and Control Engineering

July 2005

Hsinchu, Taiwan, Republic of China

中華民國九十二年六月

# 應用於 Power IC 之 700 伏特 LIGBT 元件研發

## Design and Implementation of 700V LIGBT for Power IC Application

學 生：洪嘉偉

Student : chia-wei hung

指導教授：張隆國 博士

Advisor : Dr. Lon-Kou Chang

A Thesis

Submitted to Institute of Electrical and Control Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Electrical and Control Engineering

June 2005

Hsinchu, Taiwan, Republic of China

中華民國九十四年六月

# 應用於 Power IC 之 700 伏特 LIGBT 元件研發

研究生：洪嘉偉

指導教授：張隆國博士

國立交通大學電機與控制工程學系

## 摘要

近年來，由於平面顯示器和通訊產品的推陳出新，使得功率元件的需求大幅增加。而為了順應電路積體化的潮流，將功率元件與低壓電路整合在同一晶片上，傳統垂直式的元件結構也必須改善為橫向式設計，因此本文針對橫向絕緣閘雙極性電晶體（LIGBT）做一研究與發展。

應用 RESURF（Reduced Surface Field，簡稱 RESURF）的原理，可以將功率元件做在矽晶片的薄磊晶層上。本文根據空乏區電荷分享理論為基礎並加以計算，接著利用計算的結果進行 Tsuprem4 與 Medici 等電腦輔助設計軟體工具，對 LIGBT 元件進行各種特性模擬分析，包括靜態崩潰電壓、導通電流等。最後運用園區某半導體製程公司裡的 100V/0.5um 高壓製程，實作出耐壓達 700V 的 LIGBT 元件。實驗中，做了許多製程的參數對照組。量測結果，在某些預定的參數的實驗組中，其 LIGBT 元件的耐壓皆可達 700V 以上，並且在實作上與模擬做一比較，說明各種模擬方式與實作上的異同與可行性。

# **Design and Implementation of 700V LIGBT for application of Power IC**

Student: Chia-Wei hung      Advisor: Dr. Lon-Kou Chang

National Chiao-Tung University

## **Abstract**

In recent years, following the rapid progress of the flat panel displays and communication products, the demands for power devices have increased substantially. To approach the target of circuit integration, the traditional discrete vertical power devices needs to be changed to lateral structures so that they can be integrated with the low voltage components on the same chip. Therefore, in this thesis concentrates on the development of the lateral insulated gate bipolar transistor (LIGBT).

The power devices have been successfully built on a thin epi-layer in this thesis by employing the principles of Reduced Surface Field (RESURF) on a silicon chip. The charge sharing theory in the depletion layer of the power device has been studied through the theoretical computation as the design assistance. Furthermore, through the aid of Tsuprem4 and Medici computer aided design tool, the physical and electrical characteristics of LIGBT devices have been simulated and studied including the static breakdown voltage, conductive current and so on. The LIGBT devices have finally fabricated successfully under the environment of semiconductor corporation's 100V/0.5um-high-voltage-process. Many process parameters have been arranged in the experiments. The breakdown voltages of the devices fabricated with some specific parameters are over 700V in all. All the simulation results and measurement results have been compared and analyzed to demonstrate the implementation possibility of our designs.

## 誌謝

首先感謝指導教授張隆國 博士在這兩年內對學生在專業學理的啟發及為人處事的建議，在此表示最誠摯的敬意。

感謝口試委員廖德誠 教授、鄭木火 教授、林君明教授及張隆國 教授對本論文內容的斧正與建議，使本論文更加完善，於此致上由衷的感謝。

感謝銘信學長在論文的撰寫以及專業知識的討論方面，給予學弟我相當大的幫助，使得本實驗研究進行順利與完成，另外致暉學長平時熱心的幫助，在論文研究方面給予不少助益。而宴銘學長、建仁學長以及實驗室 815 各學長在其他方面的指導，幫助良多。

感謝吾所深愛的父母、妹妹及女友佳蓉對我的支持、關懷與鼓勵，使我無後顧之憂，得以專心求學完成學業。僅將本論文獻給我所敬愛的家人。

在同窗同學啊彭、劉志偉及如璇與各死黨小為、小弟、小姐、龜米、肥全、綠茶、大姐及蘇柏等的支持下，完成本論文，僅以此文之研究成果表達吾人無盡的感激。

洪嘉偉

謹誌於交通大學 815 實驗室

中華民國九十四年六月

# 目錄

|                              |     |

|------------------------------|-----|

| 中文摘要                         | i   |

| 英文摘要                         | ii  |

| 誌謝                           | iii |

| 目錄                           | iv  |

| 圖例                           | vi  |

| 表格                           | x   |

| 第一章 緒論 .....                 | 1   |

| 1.1 前言 .....                 | 1   |

| 1.2 研究目的與動機 .....            | 2   |

| 1.3 論文架構 .....               | 3   |

| 第二章 IGBT理論與特性 .....          | 4   |

| 2.1 前言 .....                 | 4   |

| 2.2 IGBT與LIGBT元件分析 .....     | 9   |

| 2.2 IGBT與LIGBT比較 .....       | 22  |

| 2.3 回顧LIGBT元件在結構上效能的改善 ..... | 24  |

| 第三章 LIGBT電信分析與研究方法 .....     | 29  |

| 3.1 參數符號定義與結構規劃 .....        | 29  |

| 3.2 參數分析與定義 .....            | 30  |

| 3.3 製程規劃 .....               | 46  |

| 第四章 LIGBT模擬與理論驗證 .....       | 49  |

| 4.1 模擬結果（實驗室輸入檔） .....       | 52  |

| 4.2 模擬結果（公司輸入檔） .....        | 58  |

| 4.3 下線規劃模擬 .....             | 64  |

|                       |    |

|-----------------------|----|

| 4.4 公司製程流程.....       | 67 |

| 第五章 實作與量測.....        | 69 |

| 5.1 元件定義.....         | 69 |

| 5.2 量測儀器說明與波形圖.....   | 73 |

| 5.3 LIGBT量測結果與討論..... | 76 |

| 5.4 良好元件說明.....       | 89 |

| 第六章 結論與建議.....        | 90 |

| 參考文獻.....             | 91 |

## 圖例

|                                      |    |

|--------------------------------------|----|

| 圖 1.1 功率元件應用範圍及其所需耐壓需求圖.....         | 1  |

| 圖 1.2 高低壓電路整合圖.....                  | 2  |

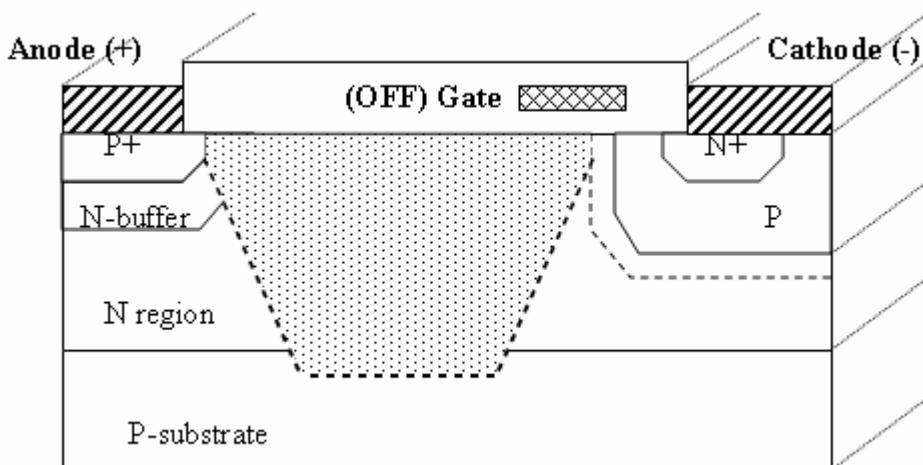

| 圖 2.1 IGBT功率元件結構圖 .....              | 4  |

| 圖 2.2 基納崩潰示意圖.....                   | 6  |

| 圖 2.3 空乏區載子受到加速衝擊的游離現象圖.....         | 7  |

| 圖 2.4 垂直與橫向IGBT結構圖 .....             | 9  |

| 圖 2.5 IGBT元件結構等效電路圖 .....            | 10 |

| 圖 2.6 LIGBT元件結構等效電路圖 .....           | 10 |

| 圖 2.7 IGBT縱向電場示意圖 .....              | 11 |

| 圖 2.8 LIGBT橫向電場示意圖 .....             | 12 |

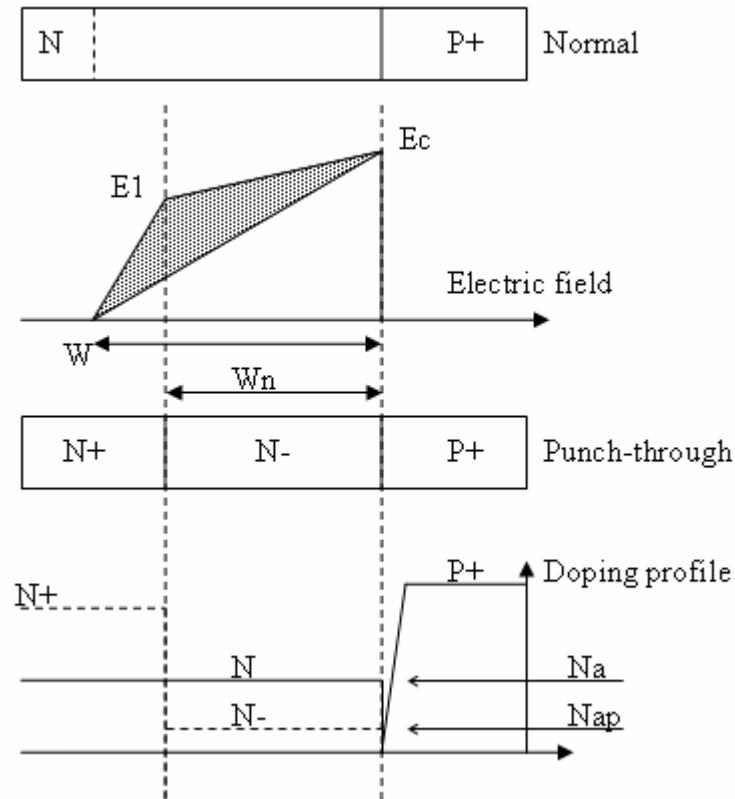

| 圖 2.9 punch-through diode示意圖 .....   | 13 |

| 圖 2.10 動態示意圖 .....                   | 13 |

| 圖 2.11 IGBT縱向電場示意圖 .....             | 14 |

| 圖 2.12 LIGBT橫向電場示意圖 .....            | 14 |

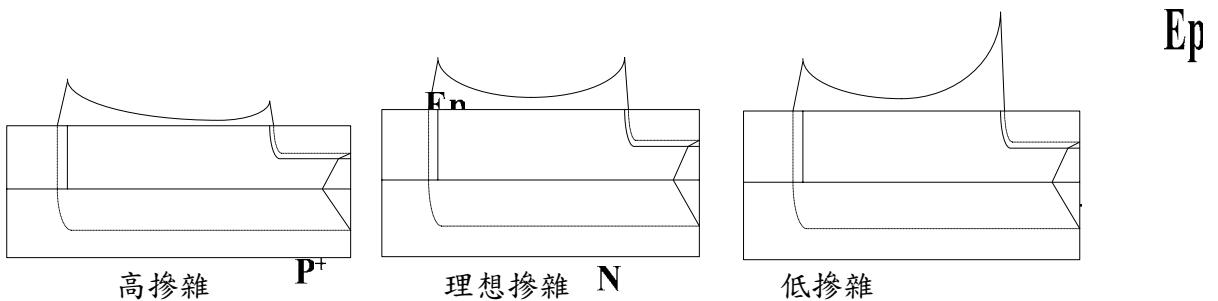

| 圖 2.13 (a) 淺摻雜 (b) 身摻雜接面空乏區示意圖 ..... | 15 |

| 圖 2.14 浮接場環結構示意圖 .....               | 15 |

| 圖 2.15 浮接場環放置示意圖 .....               | 16 |

| 圖 2.16 場板結構示意圖 .....                 | 16 |

| 圖 2.17 場板覆蓋結構說明圖 .....               | 17 |

| 圖 2.18 電阻係數示意圖 .....                 | 17 |

| 圖 2.19 IGBT結構電阻分佈圖 .....             | 18 |

| 圖 2.20 $R_{on,sp}$ 電阻說明圖 .....       | 19 |

| 圖 2.21 LIGBT導通電流行進範圍圖 .....          | 21 |

|                                                |    |

|------------------------------------------------|----|

| 圖 2.22 p型井與P埋藏層結構圖 .....                       | 24 |

| 圖 2.23 自行對準溝朝式結構圖 .....                        | 25 |

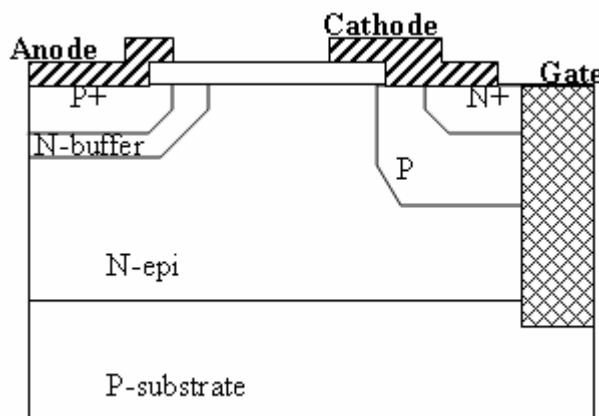

| 圖 2.24 溝朝式閘極結構圖 .....                          | 25 |

| 圖 2.25 陽極短路結構圖 .....                           | 26 |

| 圖 2.26 RESURF示意圖 .....                         | 27 |

| 圖 2.27 不同摻雜濃度下電場分佈圖 .....                      | 27 |

| 圖 3.1 初步計算結構定義圖 .....                          | 29 |

| 圖 3.2 橫向結構圖 .....                              | 31 |

| 圖 3.3 將圖 3.1 結構拆解成兩個接面示意圖 .....                | 31 |

| 圖 3.4 橫向接面電場表示圖 .....                          | 32 |

| 圖 3.5 resurf理論結構圖 .....                        | 34 |

| 圖 3.6 $\eta$ 值與Nepi濃度相關圖形 .....                | 38 |

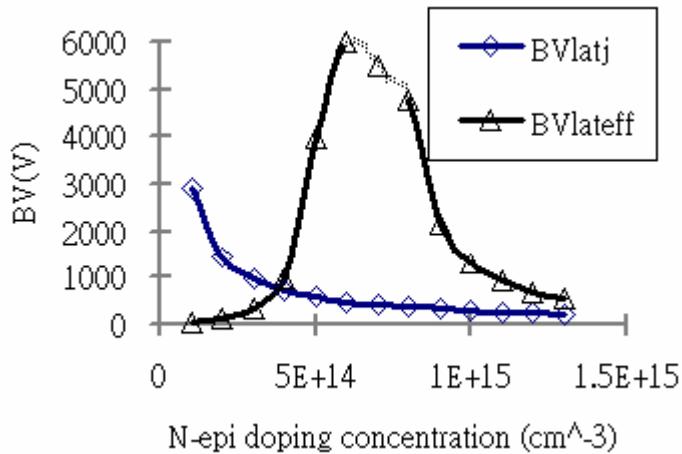

| 圖 3.7 BVlatj與BVlateff電壓分佈圖 .....               | 39 |

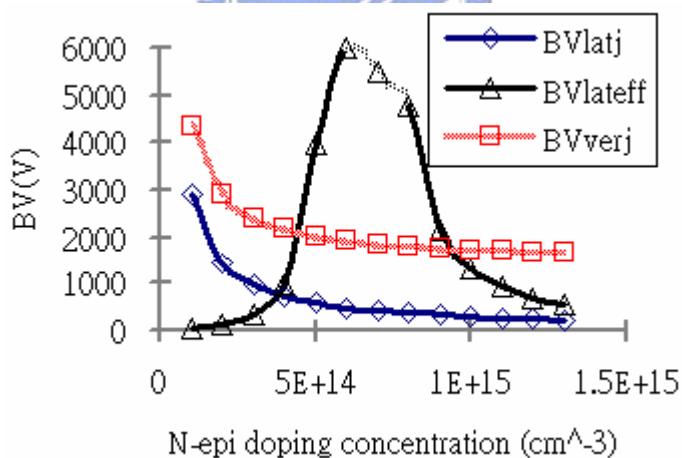

| 圖 3.8 各接面電壓分佈圖 .....                           | 39 |

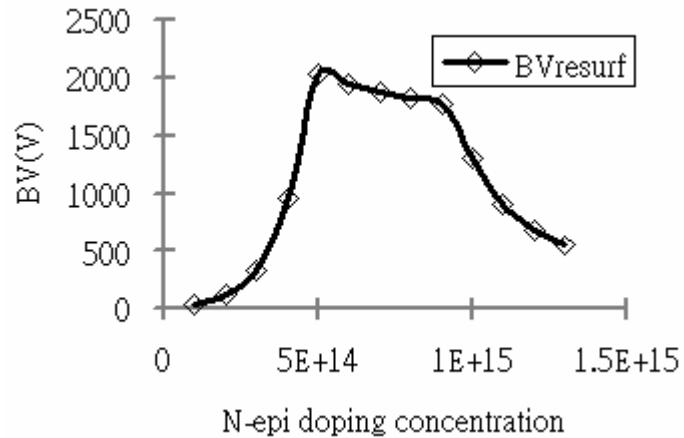

| 圖 3.9 RESURF現象電壓圖 .....                        | 40 |

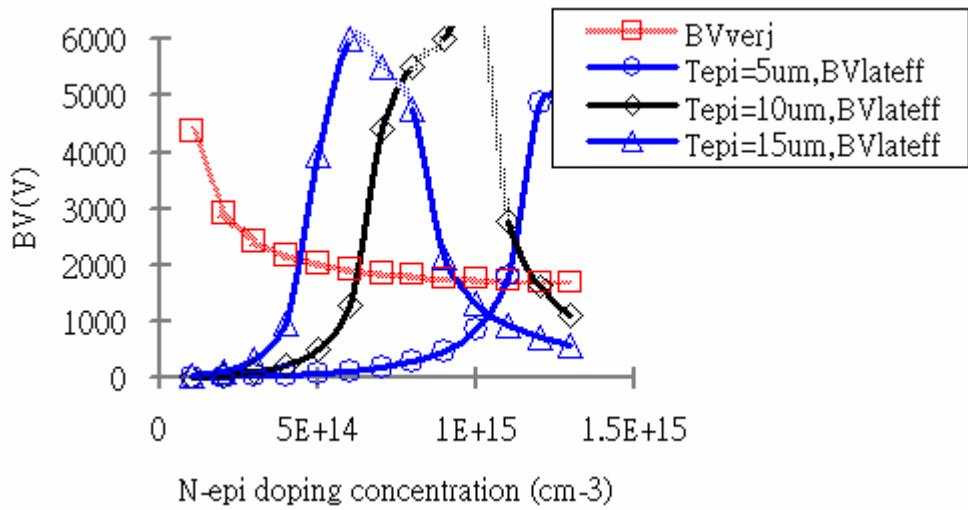

| 圖 3.10 不同N-epi厚度RESURF電壓分佈圖 .....              | 40 |

| 圖 3.11 Tepi=10um所計算出來的電壓關係圖 .....              | 41 |

| 圖 3.12 厚度與崩潰電壓關係圖 .....                        | 41 |

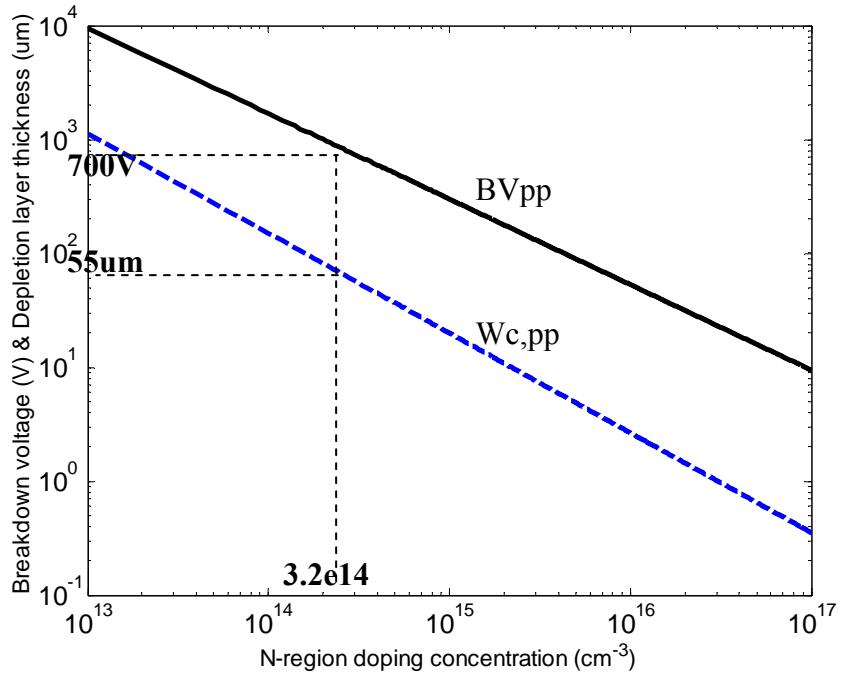

| 圖 3.13 BVpp、Wc,pp與N-epi層摻雜濃度綜合計算結果圖 .....      | 43 |

| 圖 3.14 穿透二極體電壓分佈圖 .....                        | 44 |

| 圖 3.15 各參數範圍示意圖 .....                          | 45 |

| 圖 4.1 模擬基本結構圖 .....                            | 50 |

| 圖 4.2 Poly overlap length耐壓關係圖 .....           | 52 |

| 圖 4.3 Anode overlap length耐壓關係圖 (Po=2um) ..... | 53 |

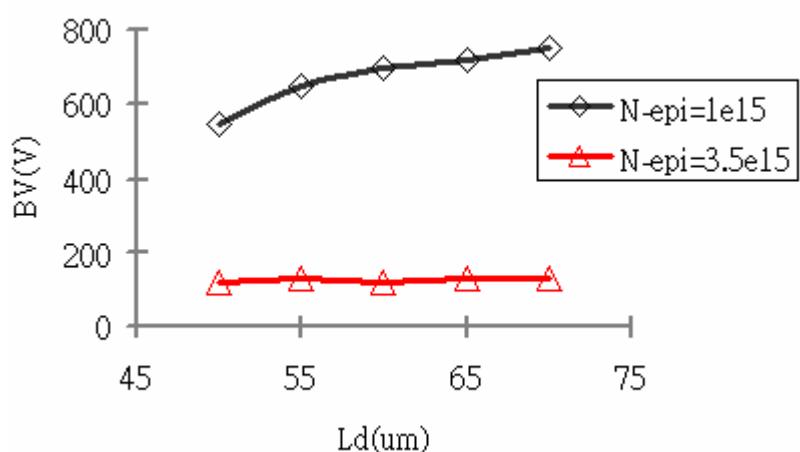

| 圖 4.4 Ld與耐壓關係圖 (LAB input file) .....          | 53 |

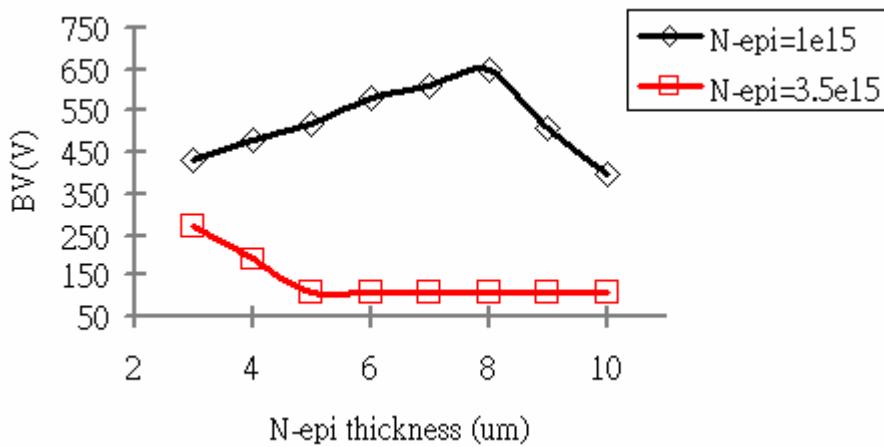

| 圖 4.5 N-epi層厚度與耐壓關係圖 (LAB input file) .....    | 54 |

|                                               |    |

|-----------------------------------------------|----|

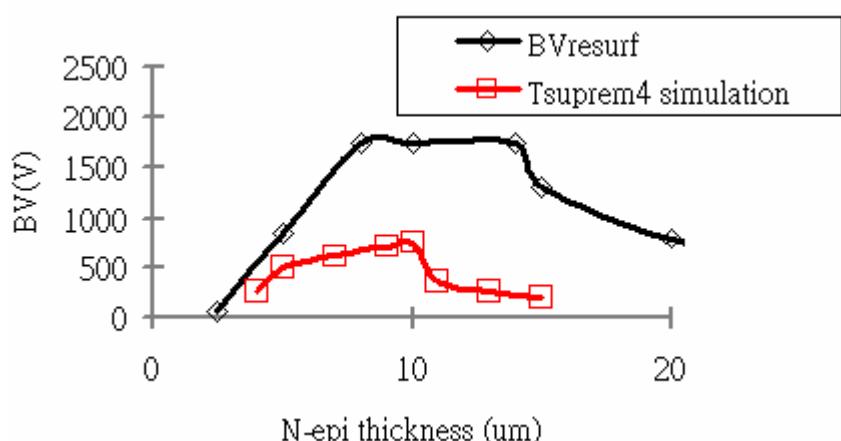

| 圖 4.6 計算與模擬比較圖 .....                          | 55 |

| 圖 4.7 基底摻雜濃度與耐壓關係圖 .....                      | 55 |

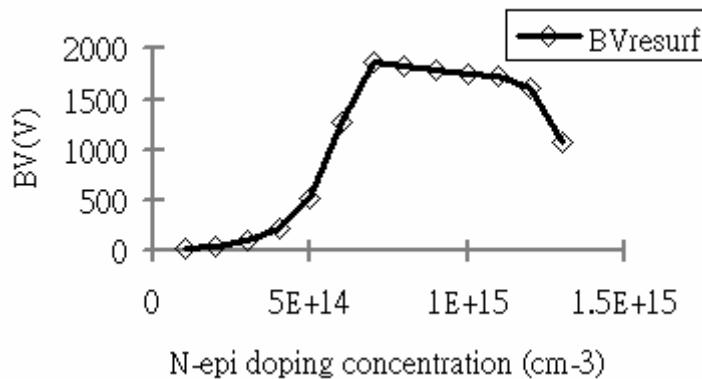

| 圖 4.8 N-epi摻雜濃度與耐壓關係圖 (LAB input file) .....  | 56 |

| 圖 4.9 計算與模擬比較圖 .....                          | 57 |

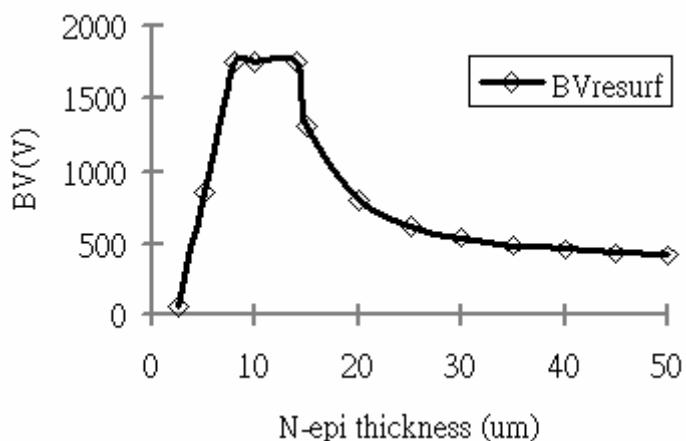

| 圖 4.10 N-epi層厚度與耐壓關係圖 (VIS input file) .....  | 58 |

| 圖 4.11 Ld與耐壓關係圖 (VIS input file) .....        | 59 |

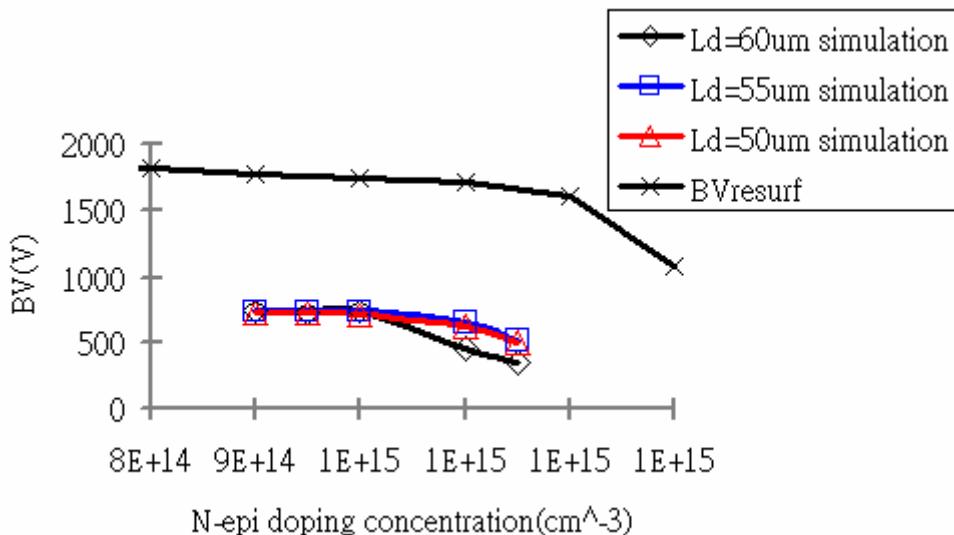

| 圖 4.12 計算與模擬比較圖 (VIS input file) .....        | 59 |

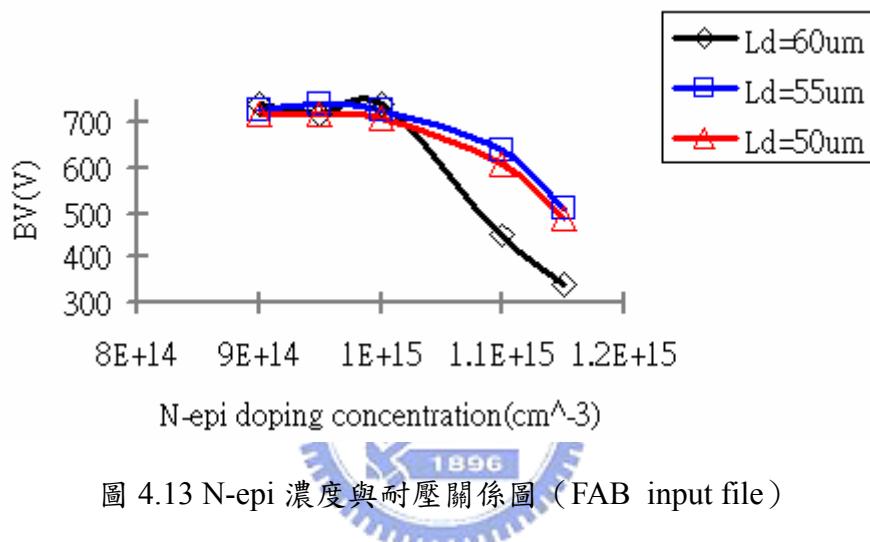

| 圖 4.13 N-epi濃度與耐壓關係圖 (VIS input file) .....   | 60 |

| 圖 4.14 計算與模擬比較圖 (VIS input file) .....        | 61 |

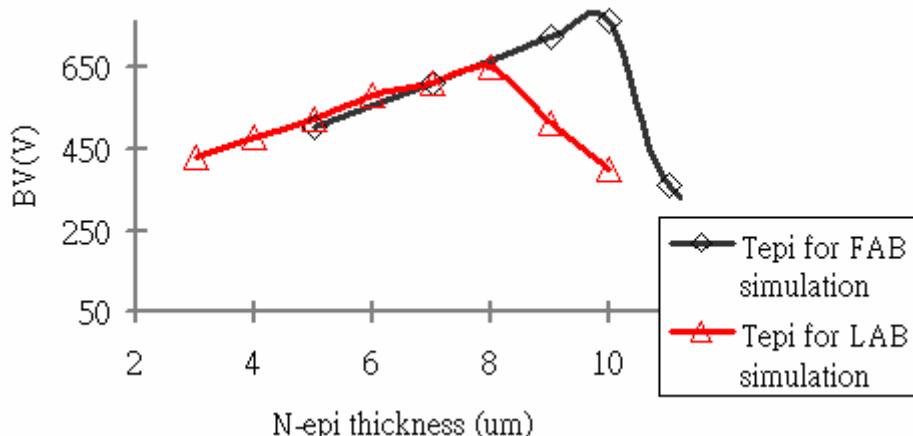

| 圖 4.15 N-epi厚度與耐壓比較圖 .....                    | 61 |

| 圖 4.16 LAB與VIS輸入檔製程結構比較圖 .....                | 62 |

| 圖 4.17 Ld與耐壓的比較圖 .....                        | 62 |

| 圖 4.18 N-epi摻雜濃度與耐壓比較圖 .....                  | 63 |

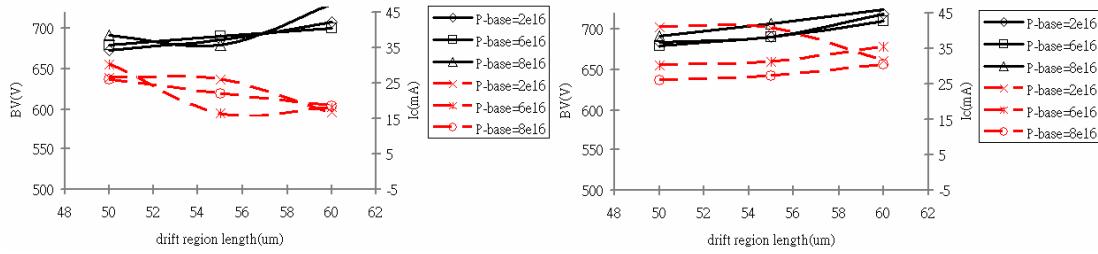

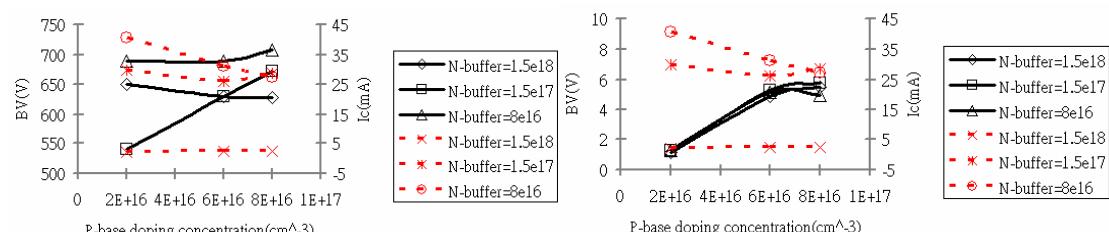

| 圖 4.19 實作前之模擬BV值與Ic結果圖 .....                  | 66 |

| 圖 5.1 光罩結構示意圖 .....                           | 69 |

| 圖 5.2 光罩圖形示意圖 (無顏色為閘極端) .....                 | 71 |

| 圖 5.3 BV值量測波形圖 .....                          | 73 |

| 圖 5.4 Ic電流量測圖 .....                           | 74 |

| 圖 5.5 (a) LDMOS與 (b) LIGBT電流比較圖 .....         | 75 |

| 圖 5.6 Vth量測圖 .....                            | 75 |

| 圖 5.7 各P-iso橫向擴散比率與P-base摻雜濃度電壓關係圖 .....      | 76 |

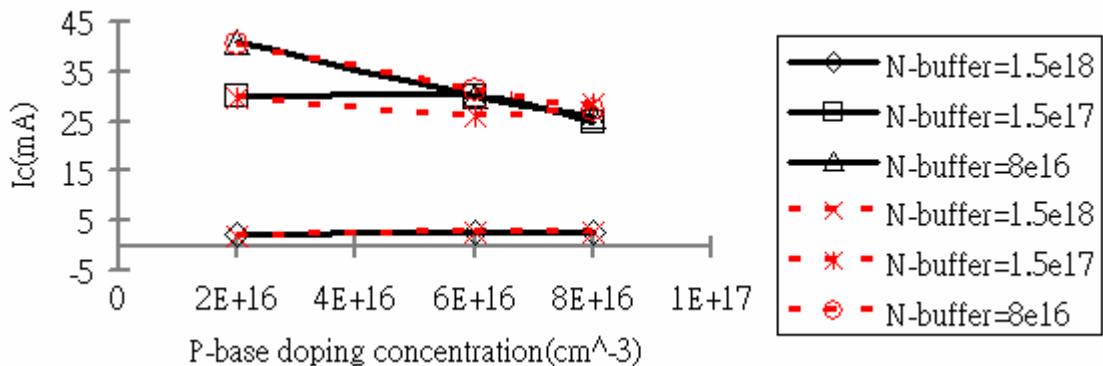

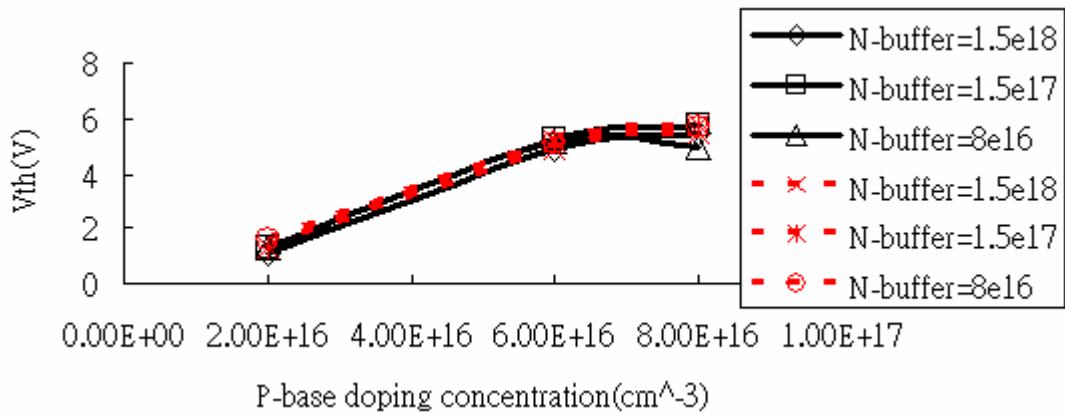

| 圖 5.8 各P-iso橫向擴散比率與P-base摻雜濃度電流關係圖 .....      | 77 |

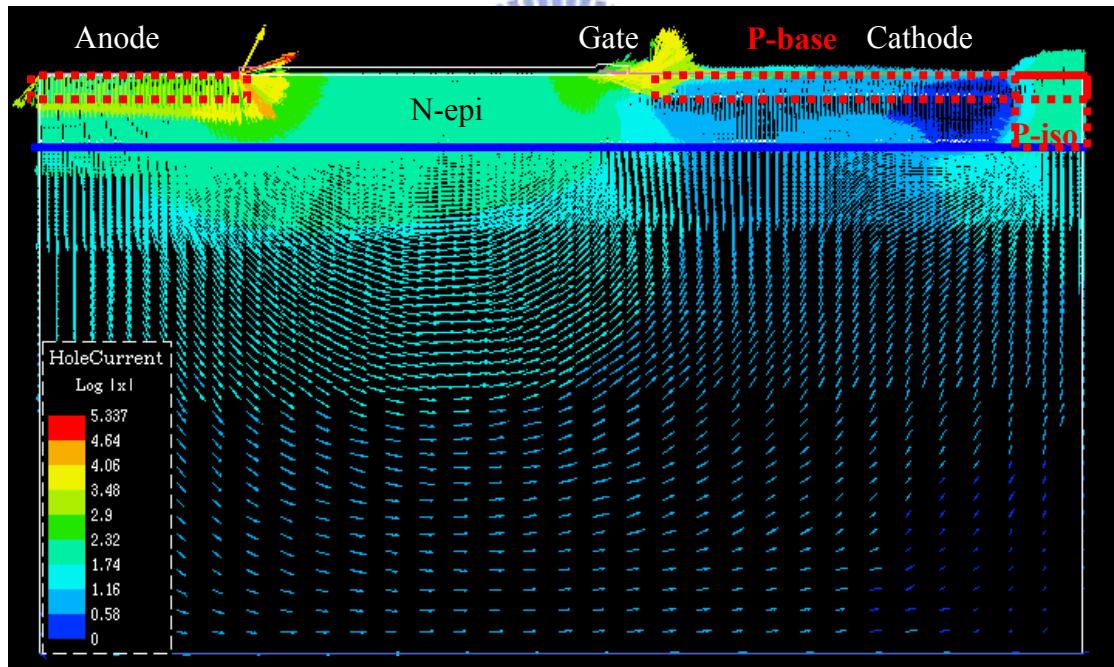

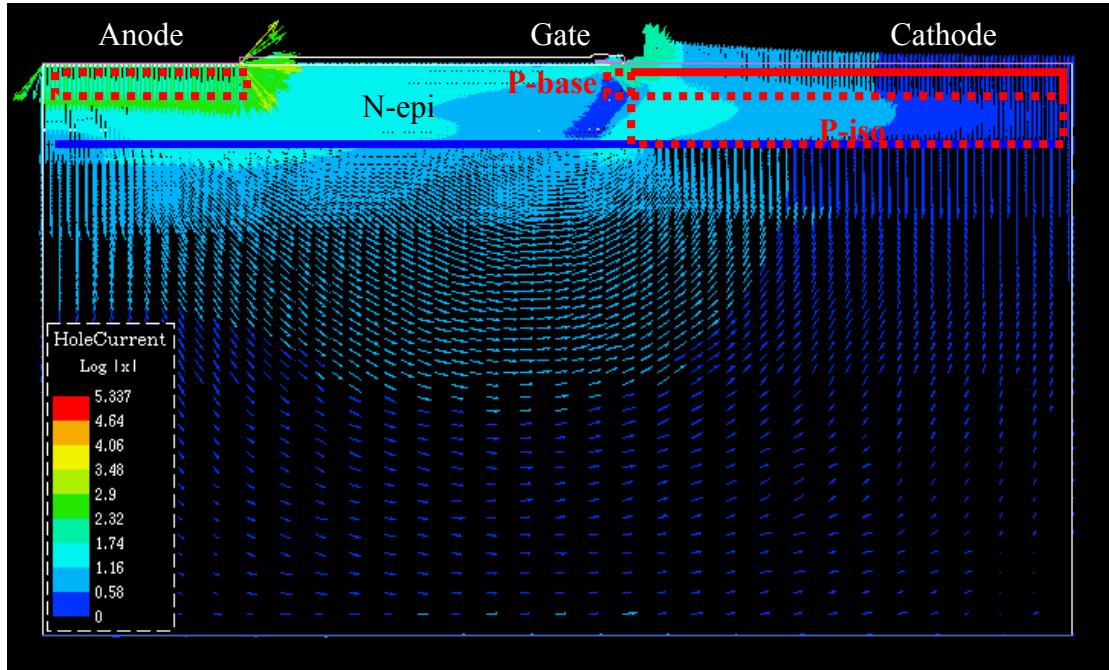

| 圖 5.9 P-iso橫向擴散比率為 1 : 6 電洞流圖 .....           | 78 |

| 圖 5.10 P-iso橫向擴散比率為 1 : 11 電洞流圖 .....         | 78 |

| 圖 5.11 P-iso橫向擴散比率為 1 : 0.75 電洞流圖 .....       | 79 |

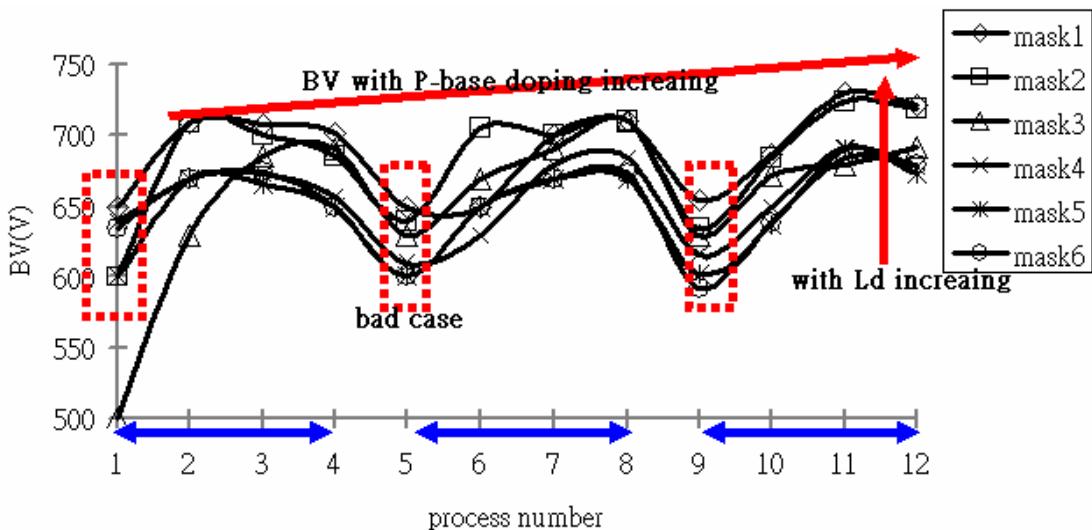

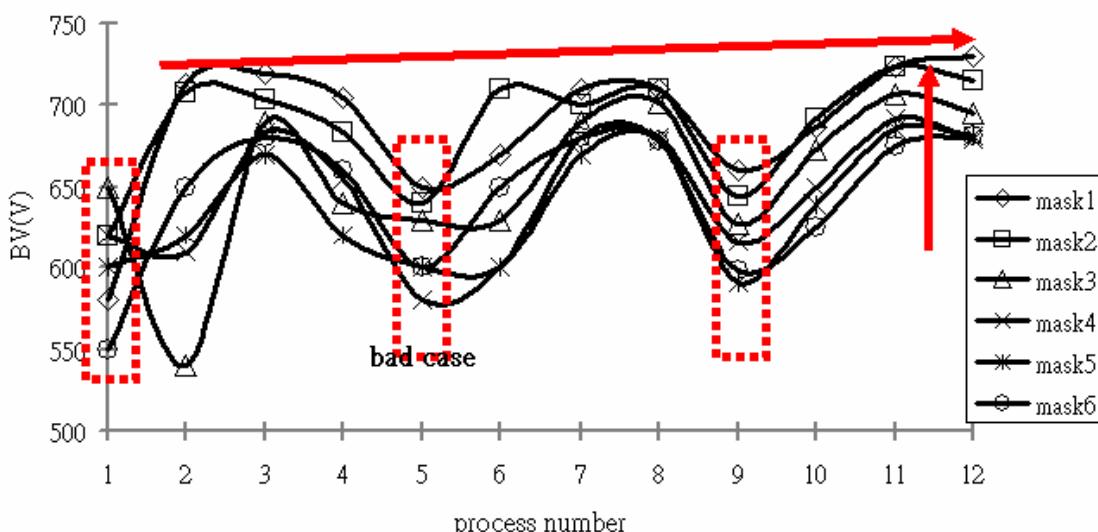

| 圖 5.12 P-iso橫向擴散比率為 1 : 0.75 耐壓與製程順序關係圖 ..... | 80 |

|                                                            |    |

|------------------------------------------------------------|----|

| 圖 5.13 P-iso橫向擴散比率為 1：6 耐壓與製程順序關係圖 .....                   | 80 |

| 圖 5.14 P-iso橫向擴散比率為 1：1 之導通電流、Vth與製程順序關係圖（其中虛線為Vth） .....  | 81 |

| 圖 5.15 P-iso橫向擴散比率為 1：6 之導通電流、Vth與製程順序關係圖 .....            | 81 |

| 圖 5.16 P-iso=1：1 P-iso=1：6（虛線為Ic） .....                    | 82 |

| 圖 5.17 P-iso=1：1 P-iso=1：6（虛線為Ic） .....                    | 82 |

| 圖 5.18 P-iso=1：1 P-iso=1：6（虛線為Ic） .....                    | 83 |

| 圖 5.19 N-buffer=1.5e17 N-buffer=8e16 Vth與Ld關係（虛線為Ic） ..... | 83 |

| 圖 5.20 BV值、Ic與Vth關係圖（虛線為Ic） .....                          | 84 |

| 圖 5.21 BV值、Ic與Vth關係圖（虛線為Ic） .....                          | 84 |

| 圖 5.22 BV值、Ic與Vth關係圖（虛線為Ic） .....                          | 84 |

| 圖 5.23 BV值、Ic與Vth關係圖（虛線為Ic） .....                          | 85 |

| 圖 5.24 BV值、Ic與Vth關係圖（虛線為Ic） .....                          | 85 |

| 圖 5.25 BV值、Ic與Vth關係圖（虛線為Ic） .....                          | 85 |

| 圖 5.26 通道長度為 3um與 1.5um BV值關係圖（虛線為 1.5um） .....            | 86 |

| 圖 5.27 通道長度 3um與 1.5um電流關係圖（虛線為 1.5um） .....               | 86 |

| 圖 5.28 通道長度為 3um與 1.5umVth關係圖（虛線為 1.5um） .....             | 87 |

| 圖 5.29 通道長度為 3um與 1.5um BV值關係圖（虛線為 1.5um） .....            | 87 |

| 圖 5.30 通道長度為 3um與 1.5um 電流關係圖（虛線為 1.5um） .....             | 87 |

| 圖 5.31 通道長度為 3um與 1.5um Vth關係圖（虛線為 1.5um） .....            | 88 |

## 表格

|                                       |    |

|---------------------------------------|----|

| 表 1.1 LDMOS 與 LIGBT 元件比較表 .....       | 3  |

| 表 2.1 IBGT 與 LIGBT 元件比較表 .....        | 23 |

| 表 3.1 初始元件計算表格 .....                  | 38 |

| 表 3.2 定義各層參數圖表 .....                  | 45 |

| 表 3.3 實驗室製程流程表 .....                  | 46 |

| 表 4.1 參數定義表格 .....                    | 51 |

| 表 4.2 實驗室輸入檔模擬參數取得表 .....             | 57 |

| 表 4.3 實驗室與公司輸入檔比較表格 .....             | 64 |

| 表 4.4 各層實作摻雜與厚度 .....                 | 64 |

| 表 4.5 下線光罩規劃 .....                    | 65 |

| 表 4.6 下線製程規劃 .....                    | 65 |

| 表 4.7 公司製程流程表 .....                   | 67 |

| 表 5.1 實作光罩檔參數表 .....                  | 70 |

| 表 5.2 下線製程規劃表 .....                   | 72 |

| 表 5.3 模擬結果參考表 .....                   | 73 |

| 表 5.4 實作參數表 (BV>710V 及 Ic>20mA) ..... | 90 |

# 第一章 緒論

## 1.1 前言

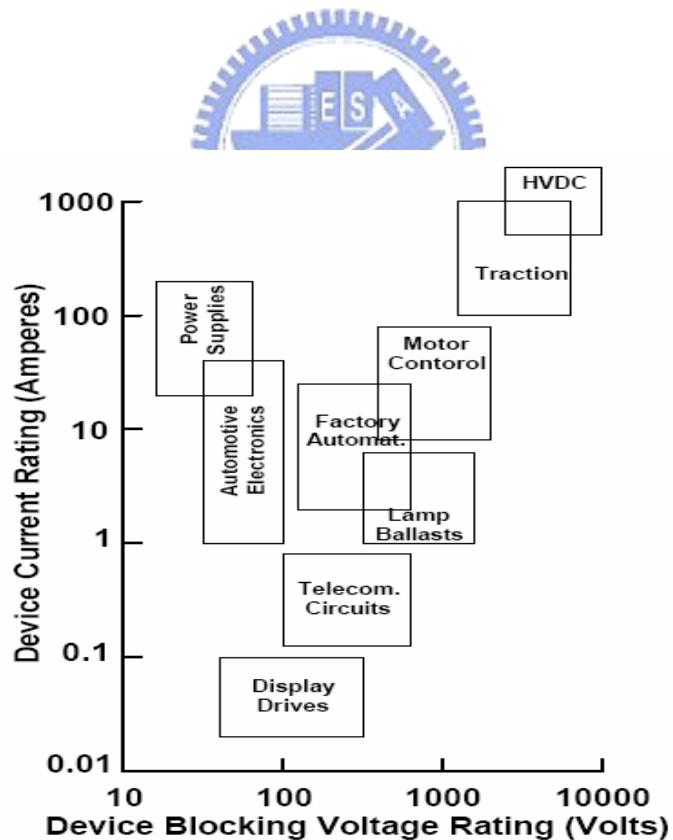

功率元件在電力電子方面的應用極為廣泛，舉凡馬達控制、汽車、照明設備以及家電用品等等，均息息相關。圖 1.1 顯示出功率元件的應用範圍，以及所需耐壓要求[1]。從 60 年代的 SCR，到目前的 LDMOSFET 與 LIGBT 功率元件，每一個世代在電子產品上均扮演舉足輕重的角色，近年來由於顯示器與通訊產品的大量需求，更使得功率元件的研發大幅上升，在投入這方面的人才亦有成長的趨勢，倘若能配合國內成熟的半導體產業基礎，順應國際科技發展潮流，將功率元件整合成智慧型功率積體電路（Smart power IC）[2]，這個領域的發展將有長足的進步。

圖 1.1 功率元件應用範圍及其所需耐壓需求圖

## 1.2 研究目的與動機

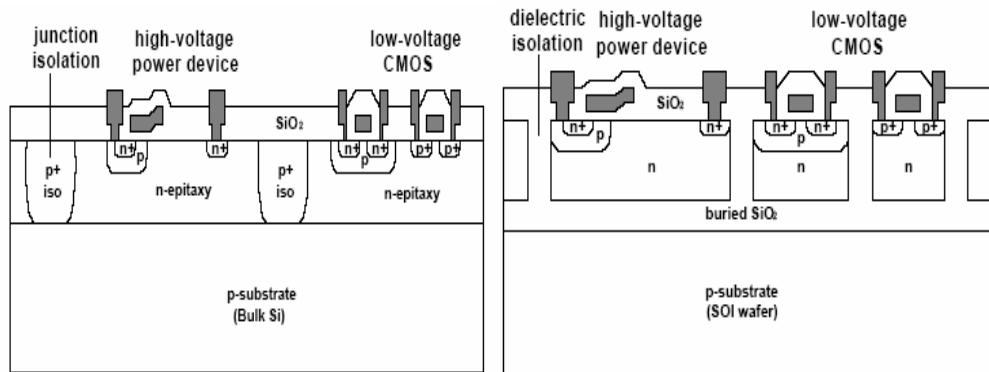

在功率元件與控制電路整合於同一晶片上，主要優點有：第一、電路積體化後，各個分立的元件集中在同一晶片上，少掉許多額外的包裝與線路連接，就體積上比分立元件來得小。第二、在工廠大量生產下，一個晶片生產成本勢必比分立元件來得低。而在達到電路積體化的前提下，傳統垂直式的功率元件必然改成橫向式結構，如此才能將高低壓整合於同一個晶片上。

圖 1.2 高低壓電路整合圖

圖 1.2 為目前最常使用積體電路結構，分別由磊晶 Si (Epitaxy layer-Si) 與 SOI 晶片 (Silicon on insulator) 所製成[3]，其皆可結合高壓元件與 CMOS 電路，並且使用接面隔離(junction isolation)[4][5]或介電質隔離(dielectric isolation)[6][7]技術來隔離高低壓元件。一般而言，良好的功率元件必須包含以下幾點：

- (1) 在功率方面：需有耐高壓與承載大電流的能力，其安全操作區域 (Safe Operating Area 簡稱 SOA) 要大。

- (2) 在速度方面：可操作頻率要高，切換速度快。

- (3) 在損耗方面：需有低漏電功率消耗、低導通功率消耗以及低切換功率消耗特性。

- (4) 在驅動方面：具備低電壓驅動與簡單的驅動電路。

於 LDMOS 與 LIGBT 分別具有上述優點，而在結構上兩者的不同，亦導致操作特性：

表 1.1 LDMOS 與 LIGBT 元件比較表

| LDMOS                                      | LIGBT                                   |

|--------------------------------------------|-----------------------------------------|

| Gate 端控制電路，驅動簡單無輸入電流                       | Gate 端控制電路，驅動簡單無輸入電流                    |

| 利用多數載子來傳導電流，元件關閉時沒有少數載子囤積現象，操作頻率在幾十 MHz 以上 | 混和多數載子與少數載子傳導電流，元件有少數載子囤積現象，操作頻率在幾十 KHz |

| 沒有傳導調變效應，導通電阻大，限制電流的大小                     | 有傳導調變效應，導通電阻小，但有順向跨壓現象                  |

| 沒有門鎖效應問題                                   | 有寄生閘流體存在，有門鎖效應存在                        |

| 負溫度效應，沒有熱跑脫問題                              | 由負溫度係數 MOSFET 與正溫度係數 BJT 結合結構，需注意熱跑脫問題  |

在比較兩者因為操作特性不同，不難發現，LDMOS 雖然擁有高速切換速度的優點，但是在元件導通電流方面，卻不足 LIGBT，於兩者比較下，本文以元件耐壓 700V 為目標下，選用導通電流較佳的 LIGBT 為主要研究元件，希望在基本結構上，取得最佳參數。

### 1.3 論文架構

其中第二章我們將回顧 IGBT 與 LIGBT 的發展，藉以瞭解元件改良的目標，確定研究方向。第三章則就研究方法為主軸，探討理論推導與研究過程，如何設計模擬方向和方法，以達到最佳化設計。第四章為模擬結果與討論，在定下方向與方法之下所模擬出來的結果，更進一步驗證理論基礎。第五章為量測結果，在製程方面所測得結果，再與之前模擬做一比較與核對，其中包含製程流程與光罩規劃。最後第六章為結論與未來展望。

## 第二章 IGBT 理論與特性

### 2.1 前言

60 年代功率元件的設計主要以雙極性功率電晶體元件 (Power Bipolar device) 為主，其功率承載的表現上亦相當卓越，但由於雙極性功率電晶體為電流控制元件，工作時需額外的驅動電級導致控制電路設計複雜及切換頻率稍低而限制了功率電晶體的發展空間。70 年代後，功率場效應電晶體 (Power MOSFET) 開始商業化量產，Power MOSFET 具有高輸入阻抗及電壓驅動電流的特性，大為簡化了控制電路及控制系統的功率消耗，至今 Power MOSFET 仍是中低功率、高頻切換系統中的主流功率元件。然在承載功率的提昇上仍受到元件本身特性的限制。因此在 1988 年由 Baliga 等人開發出第一顆絕緣閘控電晶體 (Insulated Gate Bipolar Transistor)，整合了 Power MOSFET 及 Power Bipolar 的特性，擴展了功率元件在應用上的範圍。

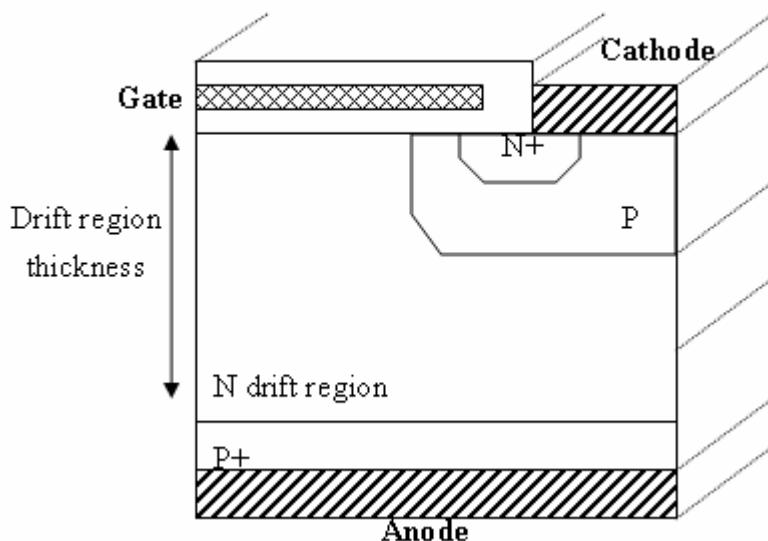

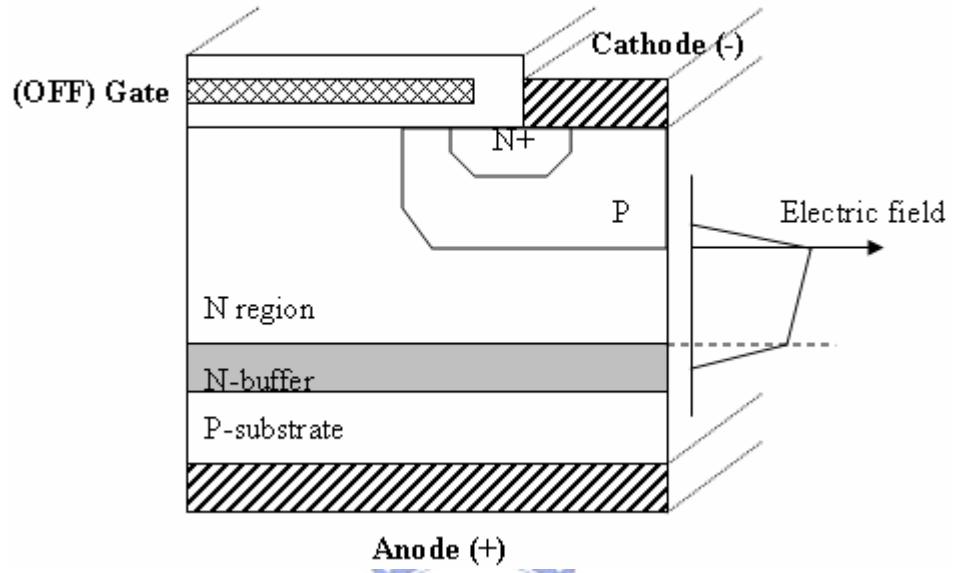

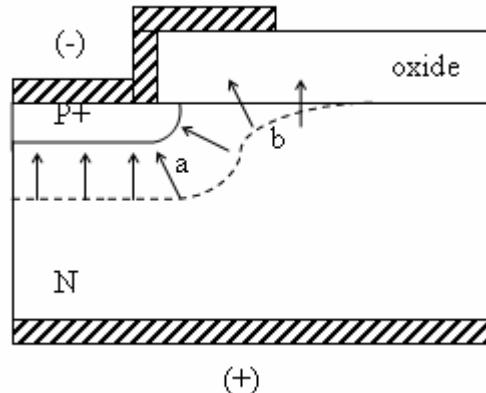

圖 2.1 IGBT 功率元件結構圖

功率元件的設計，運用了半導體空乏區適當延伸來分散電場加諸於 P/N 接面上的電場應力 (electric field stress)。以垂直功率元件 (Vertical Power Device) 為例，

在陽極 (Anode) 與陰極 (Cathode) 中加入了一層低摻雜的漂移區 (drift region)，如圖 2.1 所示結構。當功率元件關閉時 Anode 對 Cathode 兩端產生高電位差，藉由漂移區中的空乏效應，使得原本加於 P/N 接面的電場應力分散在漂移區上，降低了 Anode 端的電場強度而達到高耐壓效果。垂直功率元件因漂移區厚度與其最大操作電壓 (崩潰電壓) 呈正比關係，這往往需要幾十、幾百  $\mu\text{m}$  的長度，才能達到百伏特、甚至幾千伏特的耐壓規格，因此在設計上都直接使用高阻值晶圓 (High resistance wafer) 作為漂移區，在 wafer 磨薄至所需厚度後，將 Anode 摻雜在 wafer 背面。這樣的結構使得垂直功率元件與低電壓的控制電路的晶片整合技術開發上不容易，因此垂直功率元件仍是以分立式元件 (discrete device) 為主。

本章重點在於垂直式 IGBT 與橫向式 IGBT 做一比較，就元件結構上分析，包括耐壓、導通特性以及元件電阻等，由於本文主要重點在於 LIGBT 實驗，在最後，也就 LIGBT 在結構上的改善，說明其優缺點。首先在進入主題之前，將就運用理論分析與公式做一說明。

在功率元件的設計裡，耐高電壓為主要重點之一，其耐壓能力無非來自於 P/N 接面逆向偏壓的耐壓能力，當逆向偏壓過高時，P/N 接面空乏區會產生崩潰現象，就半導體物理言之，崩潰機制大可分類為三種接面崩潰 [8]: 基納崩潰 (Zener breakdown)、穿透崩潰 (punch-through breakdown) 以及累增崩潰 (avalanche breakdown)。

### A. 基納崩潰 (Zener breakdown) :

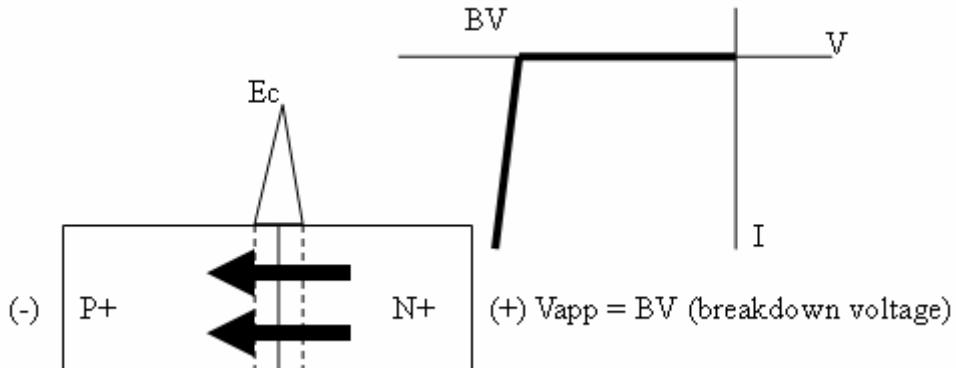

圖 2.2 基納崩潰示意圖

當一半導體 P、N 兩邊為重摻雜時，當給予一逆向偏壓，P/N 接面所產生的空乏區，會由於摻雜量過重，而使空乏區接面處產生極大的電場，而使電場強度達臨界值 ( $E_c$ )，此時，大量的電子脫離共價鍵而形成導電的電子-電洞對，接面隨即崩潰，而產生大電流，這時定義臨界電壓即為崩潰電壓 (Breakdown Voltage)，簡稱為 BV 值。所以在基納崩潰中，其 BV 值勢必不高，一般在於六伏特以內，大多用於低壓穩壓電路裡，在功率元件設計方面，應盡量避免此種崩潰現象的發生。

### B. 穿透崩潰 (punch-through breakdown) :

如同基納崩潰機制一樣，當半導體 P、N 兩邊給予逆向偏壓時，P/N 接面會因為形成空乏區而產生接面電場，這時倘若元件的尺寸過小，不夠空乏區的長度來延伸，將會導致空乏區會因無法再擴張而撞到另一個接面，空乏區就會彼此相連形成連續接面，此時電流就會毫無阻礙的通過，稱之為穿透崩潰，如要避免這種崩潰機制的發生，只要增大元件的尺寸，提供足夠空乏區延伸的距離即可，而在功率元件的設計上，也會有用到穿透崩潰效應的地方，將在後面章節做討論。

### C. 累增崩潰 (avalanche breakdown) :

在半導體 P、N 兩邊均為輕摻雜或一邊為輕摻雜的清況下，此時給予 P/N 接面逆向偏壓，其空乏區內的載子會由熱游離 (thermal-generation) 或從準中性區

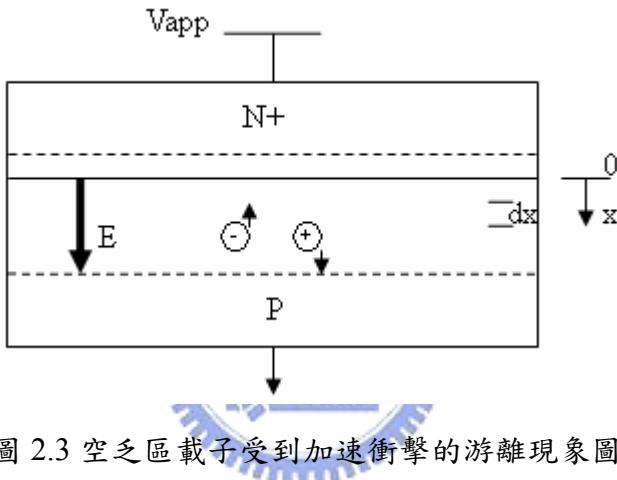

(quasi-neutral region) 漂移而至，再受到因逆向偏壓產生的空乏區電場而加速，當電場大到可以提供載子足夠的動能，使得原子內的電子由共價帶 (valence band) 躍升到導電帶 (conduction band)，在這樣的過程中，稱之為衝擊游離[9]。在空乏區內載子衝擊的過程中，會產生電子-電洞對，這些新產生的電子電洞對會因為強大電場作用下，往相反方向移動，造成逆向偏壓電流增加，在此，如果產生的電子-電洞對又獲得足夠的能量來解離其他的原子，便會引發雪崩般的效應，所以累增崩潰也稱為雪崩崩潰，這也是一般功率元件之所以能夠承受高耐壓的主要機制。那該如何定義崩潰電壓，以下圖 2.3 說明：

圖 2.3 空乏區載子受到加速衝擊的游離現象圖

在空乏區游離的過程中，會有產生電子-電洞對的程度，定義為游離係數 (ionization coefficients)，其中  $\alpha_n$  與  $\alpha_p$  分別代表電子與電洞的游離係數， $\alpha_n$  表示電子在空乏區內沿著電場負方向進行一公分所產生的電子電洞對數量，同理  $\alpha_p$  亦為這樣定義。圖 2.3 中考慮在位置  $x$  處產生了一個電子-電洞對，由於元件兩端逆向偏壓所存在的接面電場，電子-電洞對會受到此電場的加速，電子往  $N+$  區域移動，電洞往  $P$  區域移動，當經過一段距離後，此時假設為  $dx$ ，電子衝擊晶格產生了  $(\alpha_n, dx)$  組電子-電洞對，相同情況下，電洞衝擊也產生  $(\alpha_p, dx)$  組電子-電洞對，經過一連串連鎖反應後，會產生多組的電子-電洞對，因此假設經過了  $dx$  距離後，可以產生  $M(x)$  組電子-電洞對，得[9]

$$M(x) = 1 + \int_0^x \alpha_n M(x) dx + \int_x^w \alpha_p M(x) dx$$

其中，w 為空乏區的寬度，對其等號兩邊微分，得

$$\frac{dM(x)}{dx} = (\alpha_n - \alpha_p)M(x)$$

解此微分方程式，得

$$M(x) = M(0) \exp \left[ \int_0^x (\alpha_n - \alpha_p) dx \right]$$

代回原式，得  $x=0$  的解為

$$M(0) = \left\{ 1 - \int_0^w \alpha_p \exp \left[ \int_0^w (\alpha_n - \alpha_p) dx \right] dx \right\}^{-1}$$

故

$$M(x) = \frac{\exp \left[ \int_0^x (\alpha_n - \alpha_p) dx \right]}{1 - \int_0^w \alpha_p \exp \left[ \int_0^w (\alpha_n - \alpha_p) dx \right] dx} \quad (2.1)$$

從(2.1)式中，觀察式子分母的部分，當分母為零時，也就是說全部的電子-電洞對  $M(x)$  或通稱為增值係數 (multiplication) 趨近於無限大的時候，發生崩潰現象，即

$$\int_0^w \alpha_p \exp \left[ \int_0^w (\alpha_n - \alpha_p) dx \right] dx = 1 \quad (2.2)$$

(2.2)式又稱為游離積分 (ionization integral)，在模擬與接面崩潰理論公式的推導，為一重要公式。而一般在用這樣的公式時，會簡化其式子，以方便日後運算。

令

$$\alpha_n = \alpha_p = \alpha$$

得其

$$\int_0^w \alpha \cdot dx = 1$$

查閱  $\alpha = 1.8 \times 10^{-35} \cdot E^7$  [ref]

$$\int_0^w 1.8 \times 10^{-35} \cdot E^7 \cdot dx = 1 \quad (2.3)$$

公式(2.3)為一般常用公式，未來在穿透二極體裡，將會用到這一式子，主要用於計算未來 LIGBT 漂移區長度的依據，在往後章節再做說明。

## 2.2 IGBT 與 LIGBT 元件分析

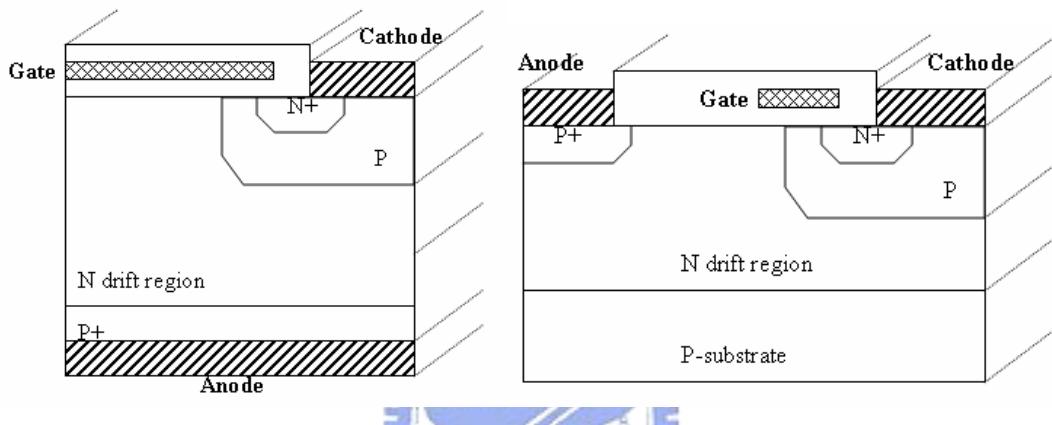

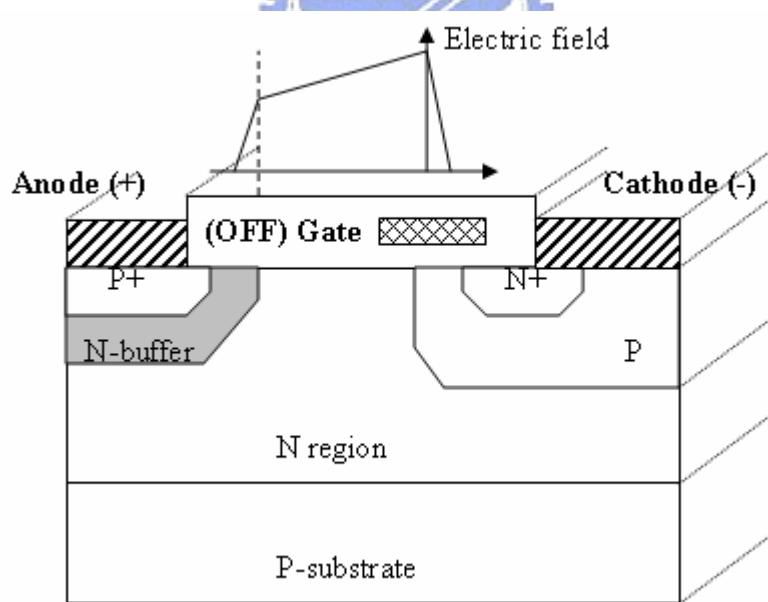

圖 2.4 垂直與橫向 IGBT 結構圖

在圖 2.4 中，分別圖示出 IGBT 與 LIGBT 結構上不同的地方，在分析上，IGBT 主要以縱向結構，不管是在耐壓、寄生效應或導通電阻等，均以縱向分析。而在 LIGBT 方面，則以橫向結構為主，分析上則以橫向分析。由於這兩種結構本由相同，在以下討論中，會先就 IGBT 先分析後，再說明 LIGBT 不同之處，最後在總結對兩者做一比較，以方便在後面的章節上給予適當的理論背景。

### A. 導通機制：

#### A.1 Trun-on

在 IGBT 與 LIGBT 兩種元件中，當閘極 (Gate) 純予驅動電壓訊號時，元件會做一開的動作 (turn-on)，此時在 NMOS 結構部分會因為閘極電壓關係，在 P 區域上產生一反轉層，形成電子通道 (N-channel)，而當陽極 (anode) 與陰極 (cathode) 兩端有壓降時，通道將會流經電子流促使 PNP 電晶體的基極 (base) 端有通道電子的注入，最後會因為 PNP 電晶體使得電子流被倍數增加，形成元

件間大電流，這樣機制發生在 IGBT 與 LIGBT 裡，兩者主要差別是在於前者主要為縱向電流，後者為橫向電流，以圖 2.5 與圖 2.6 所示。

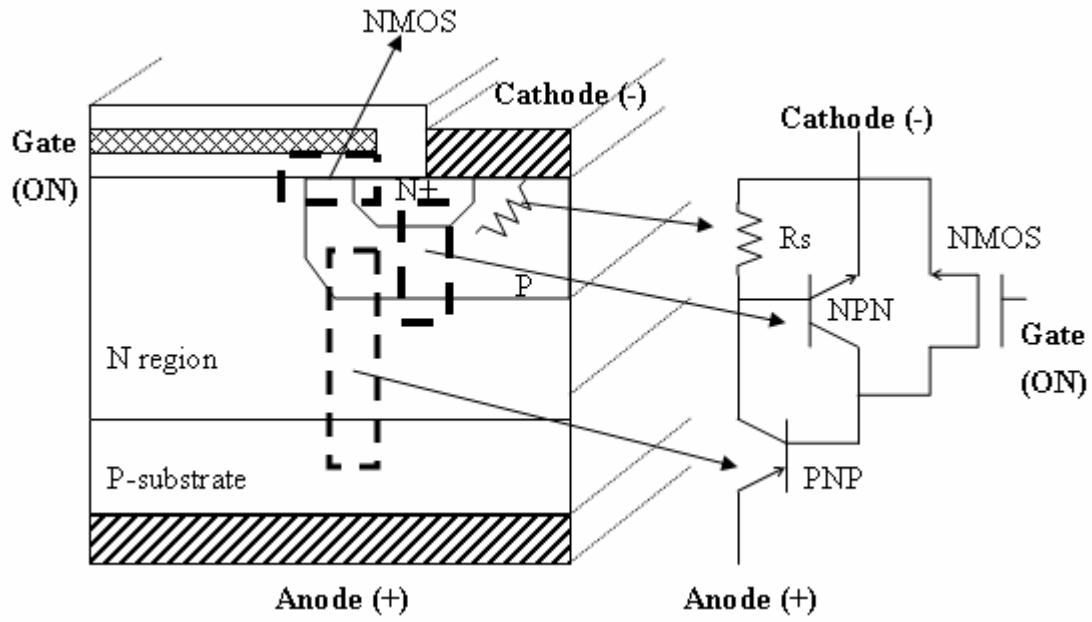

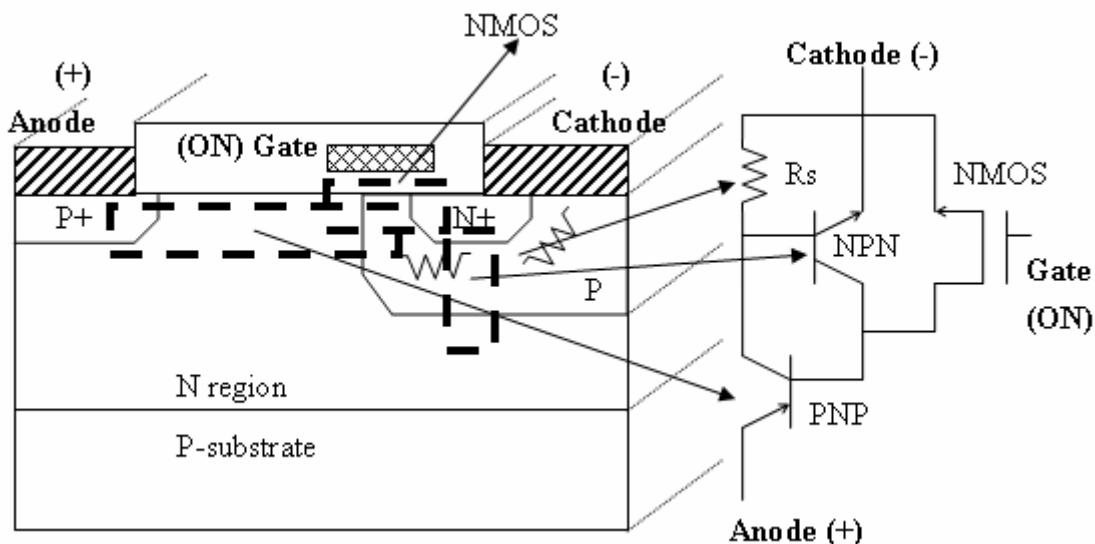

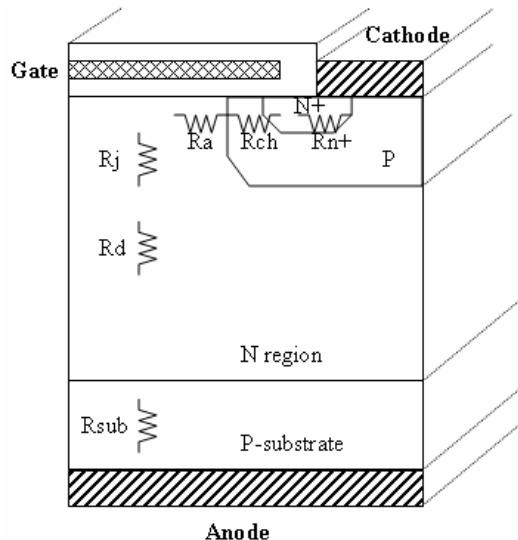

圖 2.5 IGBT 元件結構等效電路圖

圖 2.6 LIGBT 元件結構等效電路圖

在圖 2.5 與圖 2.6 中，IGBT 與 LIGBT 元件結構大致可以等效出圖中右側的電路圖，而在結構上除了本身需要的 NMOS 與 PNP 電晶體外，亦寄生了電阻(Rs)與 NPN 電晶體，在正常工作情況下，流經 Rs 上的電流會形成電壓，如果當壓降過大以至於導通 NPN 電晶體，則元件將流經更大電流，且此電流將不再受 NMOS

閘極控制，失去原本元件功用，稱之為門鎖效應（latch-up）[9]。此效應不單造成電流不受控制，也會由於電流過大，足以損毀本身元件以及周遭控制電路等，在一般電路工作上，應盡量避免，改善方面大多分成兩部分，就摻雜而言，對陰極附近 P 區域做重摻雜，及降低  $R_s$  電阻值，就結構上則改變電流方向或陰極深入，一樣為降低  $R_s$  電阻值，以保護元件不被門鎖，此部分於後面章節會詳細介紹。

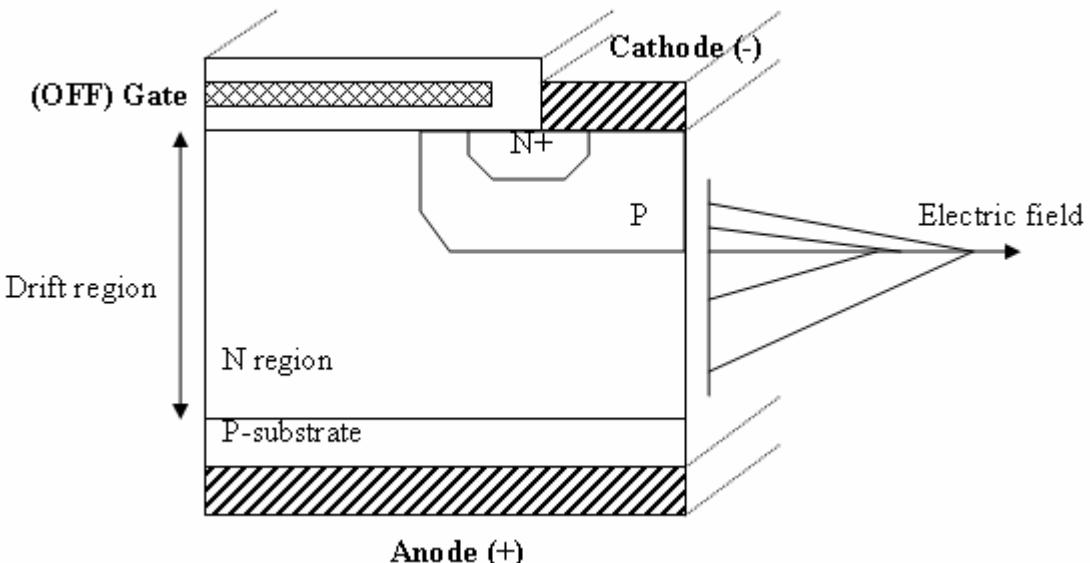

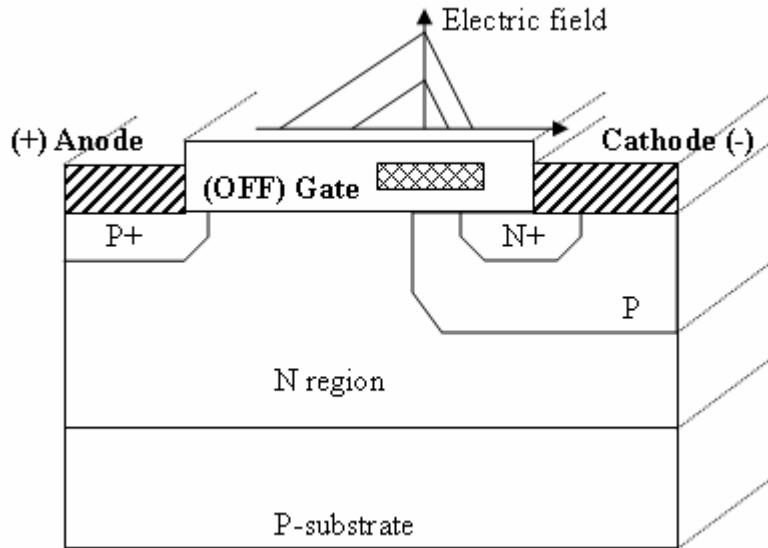

### A.2 Turn-off

當閘極給予零偏壓，甚至逆偏壓時，反轉層通道並未形成，則元件做一關（turn-off）的動作，元件兩端即使有電位差，電子依舊無法經由通道流至 PNP 電晶體的基極（base）端，定義為靜態特性（static blocking characteristic），此時若於陽極與陰極兩端持續提供電位差，在接面尚未崩潰前，元件便無大電流，而元件壓降主要乃接面電場撐起，此時所能承受之最大電壓定義為元件崩潰電壓（breakdown voltage），簡稱為 BV 值。相同機制結構，IGBT 以縱向電場為主，而 LIGBT 則以橫向電場，以圖 2.7 與 2.8 所示。

圖 2.7 IGBT 縱向電場示意圖

圖 2.8 LIGBT 橫向電場示意圖

由圖 2.7 與圖 2.8 可以清楚看到，電場分佈於 P/N 接面逆偏空乏部分，考慮 Poisson's equation[8]：

$$\frac{d^2V}{d^2x} = -\frac{dE}{dx} = -\frac{Q(x)}{\epsilon_s} = \frac{qNa}{\epsilon_s}$$

其中  $Na$  為重摻雜濃度的一端， $Q(x)$  為空乏區電荷。觀察一次微分與二次微分項，可得知在一般 P/N 接面逆向偏壓裡，可承受的壓降即為電場積分，以上圖 2.7 與圖 2.8 而言，元件可承受的耐壓可近似為圖中的三角形面積，然而必須符合接面電場未達臨界電場 ( $E_c$ )， $P/N$  接面  $E_c \cong 3 \times 10^5 V/cm$ 。在接面電場部分，在電場  $E$  值未達  $E_c$  時，三角形面積有限，以功率元件動輒數百伏效能來看，元件長度必須提高，以相同長度下，提供改變電場形狀理論，即為穿透二極體 (punch-through diode) 理論[9]。以圖 2.9 為例，利用穿透崩潰機制，將更低摻雜區域至於原本 P、N 區域中間，並利用逆向偏壓使其更低摻雜區域完全空乏，導致 N+/N-接面形成電場，則電場形狀可由原本三角形變成近似梯形，以提升電場積分面積。

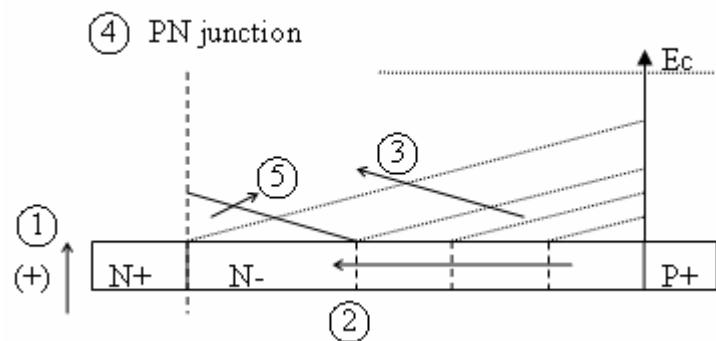

於圖 2.10 做一動態說明，當 ① 電壓逐漸上升，② 空乏區開始往低摻雜濃度延伸，③ 相對下，電場也逐漸依一定斜率上升，直到碰到 N-/N+接面，此時 N-區域已完全被空乏，若電壓繼續上升，由於 N-區域已完全空乏形成

正離子區域，此時 N-區域被近似為 P 型態，也就是說在 N+/N-接面產生一近似 PN 接面④，隨之新 P/N 接面便會衍生電場⑤，且隨著電壓上生電場繼續延伸，最後，形成一近似梯形電場。

圖 2.9 punch-through diode 示意圖

圖 2.10 動態示意圖

本實驗 LIGBT 元件在設計上，也充分運用穿透二極體理論，不光是在 RESURF 技術上提升電壓(之後章節將會介紹)，更可有效縮短元件尺寸，在 IGBT 與 LIGBT 等功率元件上，在 N 型態區域 (N-region) 中加入一重摻雜，定義為

N-buffer 層，與穿透二極體理論相同，將空乏區電場形狀改變為一近似梯形，以提升電場積分面積，在圖 2.11 與 2.12 分別表示 IGBT 和 LIGBT 接面空乏區電場分佈。

圖 2.11 IGBT 縱向電場示意圖

圖 2.12 LIGBT 橫向電場示意圖

在 N 區域靠近陽極附近，佈植更重摻雜 N-buffer 層[9]，在 N-buffer/N/P 形成一穿透二極體，當陽極陰極兩端電位差逐漸升高，N 區域完全被空乏時，N-buffer/N 接面形成電場，將原本三角形電場變成近似梯形，其理論近似 RESURF

現象，不過由於 N 區域長度過長（大於 50um），因為空乏區的曲率和氧化層上電極等影響，電場形狀會近似為雙峰，不利 RESURF 的效應（之後章節做討論），不過可將電場不利形狀降至最低，以提升元件最高耐壓。

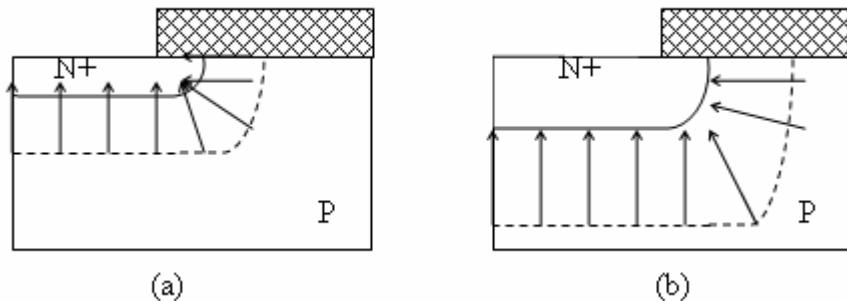

## B. 耐壓提升

IGBT 與 LIGBT 在最高耐壓能力方面，皆以半導體 P/N 接面空乏區為主，以下以空乏區形狀或邊緣效應為討論重點[9]。在摻雜深度方面，考慮圖 2.13。

圖 2.13 (a) 淺摻雜 (b) 深摻雜接面空乏區示意圖

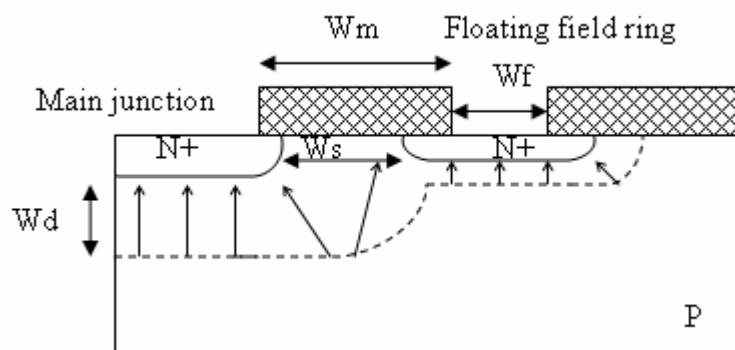

雖同為半導體異質摻雜，因其摻雜深度的深淺，空乏形狀有所區別，以圖 2.13 (a) 而言，在接面邊緣部分，由於深度淺，電力線形成擁擠現象，如此一來在接面尚未達臨界電場值 ( $E_c$ ) 時，便會提早崩潰，則耐壓效果不彰。同樣機制在圖 2.13 (b)，由於深摻雜，空乏形狀較不易形成電力線擁擠，崩潰電壓比較接近理論值。然而這方面在製程上控制不易，此時提供浮接場環 (floating field ring) 技術，以緩和空乏形狀，主要使用在實作元件邊緣。

圖 2.14 浮接場環結構示意圖

在主要接面邊緣的附近，因為空乏形狀容易導致電場提早崩潰，加入浮接

摻雜 (floating field ring)，在接面空乏區連續效應下，降低電力線擁擠問題，相對下也提升了崩潰電壓，在元件實作上，浮接場環會放置於主元件最外一層，由於並無須多加光罩，在實作方面經常被使用，以圖 2.15 示意。

圖 2.15 浮接場環放置示意圖

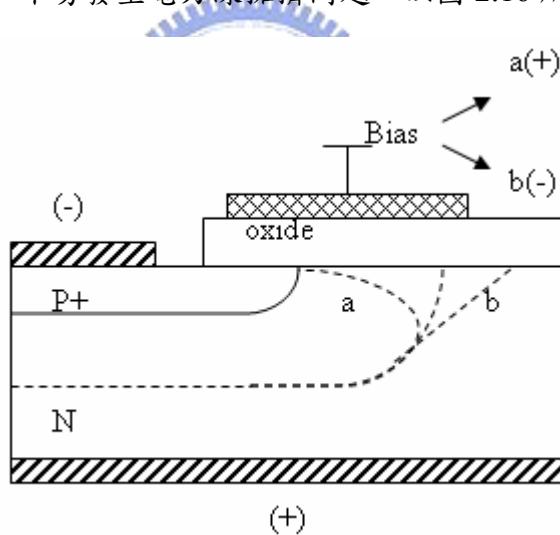

另一項要介紹的耐壓提昇技術為場板 (field plates)，利用偏壓方式，使得空乏區形狀得以緩和，不易發生電力線擁擠問題，以圖 2.16 所示

圖 2.16 場板結構示意圖

在 P/N 接面給予逆向偏壓，隨之空乏區形成，而在場板端加入正偏壓，在 N 區域因其空乏區電荷為正離子，與偏壓在排斥力作用下，造成 a 空乏區域形狀，如此電力線會更加擁擠，崩潰電壓也將隨之下降。若偏壓給予負電壓，會因正離子與偏壓有吸引力關係，延伸了空乏區的形狀，將電力線分散在空乏區內，相對下耐壓也就可以提升，屬於元件設計上需要注意的技術。另外值得注意地方在於偏壓與 P 區域偏壓極性相同，於本實驗 LIGBT 元件設計上，大可將兩電極相連，

製程上不但不需要多加光罩，原場板偏壓也無須多加偏壓電路，只要在電極做一覆蓋動作（overlap），即可提升電壓。以圖 2.17 說明場板覆蓋效果。

圖 2.17 場板覆蓋結構說明圖

圖 2.17 清楚說明了覆蓋式場板可以舒緩區域 b 電力線分佈，避免因為電力線擁擠而讓元件提早崩潰，以提升耐壓，以 IGBT 與 LIGBT 言之，在三端電極端，包括閘極、陰極和陽極附近，都會使用到場板技術，這將會在第四章模擬上做一說明。

### C. 特性導通電阻

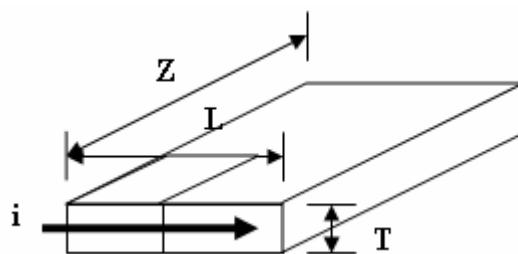

在討論元件電阻元素前，就電阻係數作一說明。一般電阻係數上，大多用到兩種，分別為  $\rho_{square}$  與  $\rho$  [8]，主要在於前者不需考慮電流流經厚度，厚度的考慮併於係數裡，用於薄摻雜層，後者則是用於厚摻雜，需要考慮電流流經厚度。

圖 2.18 電阻係數示意圖

就圖 2.18 中電流方向，以兩種不同電阻係數，求解整塊電阻 (R<sub>total</sub>)

$$R_{total} = \rho_{square} \cdot \frac{L}{Z} = \rho \cdot \frac{L}{T \cdot Z}$$

之後於導通電阻計算時，會用到這兩種係數。

### C.1 定義 $R_{on,sp}$

功率元件中，於順向導通特性 (forward conduction characteristic)，元件工作操作在線性區，利用導通電流與輸入壓降關係，可計算出一電阻值，稱之為導通電阻 ( $R_{on}$ )，其大小影響著導通電流的大小。首先就功率損耗而言，其

$$P_D = I_D \cdot V_D = I_D^2 \cdot R_{on}$$

在考慮一晶片面積下

$$\frac{P_D}{A} = J_D^2 \cdot R_{on,sp}$$

其中

$$R_{on,sp} = R_{on} \cdot A$$

$\frac{P_D}{A}$  定義為晶片上每單位面積的功率損耗， $J_D$  為導通電流密度與  $R_{on,sp}$  定義為特性導通電阻 ( $R_{on,specific}$ ) [9]，為每平方單位上分佈的導通電阻，單位  $\Omega \cdot \text{cm}^2$ 。在一般封裝方面，受到最大允許接面溫度與熱撞擊效應，最大功率損耗為  $100W / \text{cm}^2$  [9]，所以最大可操作電流密度的平方與  $R_{on,sp}$  成反比，就設計上，將  $R_{on}$  降低或是元件面積縮小均可提升操作電流。

在推導  $R_{on,sp}$  之前，先考慮一垂直 IGBT 各各電阻元素。

圖 2.19 IGBT 結構電阻分佈圖

圖 2.19 標示出元件裡各電阻位置圖，此為一縱向 IGBT 元件，取其半元件，就分析而言，日後只要考慮兩邊即可。在忽略電極電阻的情況下，可以寫出以下

$$R_{on} = R_{n+} + R_{ch} + R_a + R_j + R_d + R_{sub}$$

圖 2.20 Ron,sp 電阻說明圖

以圖 2.20 說明 IGBT 內各分佈電阻。

### C.2 R-substrate resistance

$$R_{on,sp} = \left( \rho_{substrate} \frac{l}{A} \right) \cdot (A) = \rho_{substrate} \cdot t_s$$

其中  $A = Z(m + Lg/2)$  為元件面積， $\rho_{substrate}$  為電阻係數， $t_s$  為基底厚度。

### C.3 Source resistance

$$R_{N+} = \rho_{SN+} \frac{L_{n+}}{Z}$$

一般  $N+$  層的摻雜淺，在電阻係數多半用  $\rho_{square}$ ，其  $\rho_{SN+}$  為  $\rho_{square}$  係數。接著加入面積計算

$$R_{N+,sp} = \rho_{SN+} \frac{L_{n+}}{Z} \cdot Z \left( \frac{L_g}{2} + m \right) = \frac{1}{2} \rho_{SN+} \cdot L_{N+} (L_g + 2m)$$

#### C.4 Channel resistance

在通道電阻方面，主要利用電流公式推導，其

$$I_d = \frac{u_n C_{ox} Z}{L} \cdot (V_g - V_t) \cdot V_d$$

則

$$R_{ch} = \frac{V_d}{I_d} = \frac{L}{u_n C_{ox} Z (V_g - V_t)}$$

考慮面積，求解  $R_{on,sp}$

$$R_{ch,sp} = \frac{L}{u_n C_{ox} Z (V_g - V_t)} \cdot Z \left( \frac{L_g}{2} + m \right) = \frac{L_{ch} (L_g + 2m)}{2 \cdot u_n C_{ox} (V_g - V_t)}$$

主要在通道短、閘極驅動電壓大以及臨界電壓 (Vt) 小時，特性電阻小。

#### C.5 Accumulation layer resistance

累增電阻的成因，因電子從通道到 JFET 區域產生電子流擁擠情形，其值大約可用通道電阻來表示，再加上實驗誤差 K，大約等於 0.6，得

$$R_a = K \cdot \frac{(L_g - 2X_p)(L_g + 2m)}{2 \cdot u_{na} C_{ox} (V_g - V_t)}$$

#### C.6 JFET region resistance

縱向結構中，為了加元件大電流量，通常以閘極為中心，兩邊摻雜 P-base 區域，所以在接面產生空乏區的情況下，會有一寄生 JFET 產生，而電阻值也根據 JFET 做一推導。以 JFET 區域考量面積

$$A_{JFET} = a \cdot Z = \left( \frac{L_g}{2} - X_p \right) \cdot Z$$

在代入電阻係數

$$R_J = \frac{\rho_D \cdot (W_o + X_p)}{a \cdot Z} \cdot Z \cdot \left( \frac{L_g}{2} + m \right) = \frac{\rho_D \cdot (W_o + X_p)}{(L_g - 2X_p - 2W_o)} (L_g + 2m)$$

其中

$$a = \frac{L_g}{2} - X_p - W_o$$

### C.7 Drift region resistance

以圖 2.20 所示，當電流離開 JFET 區域，進入漂移區域（drift region）時，行進方面會往外近似 45 度角，在 P-base 正下方並無電流流經，所以電阻需要做一積分動作

$$R_D = \int_0^t \frac{\rho_D}{A} \cdot dx = \int_0^t \frac{\rho_D}{(a+x) \cdot Z} \cdot dx = \frac{\rho_D}{Z} \cdot \ln\left(\frac{a+t}{a}\right)$$

其中  $A = (a+x) \cdot Z$  和  $y = x$ 。則

$$R_{D,sp} = \frac{\rho_D \cdot (L_g + 2m)}{2} \ln\left(\frac{a+t}{a}\right)$$

然而在高壓元件裡，漂移區厚度以及空乏區寬度均與推導公式理想上有所出入，所以做一修正

$$R_{D,sp} = \frac{\rho_D \cdot (L_g + 2m)}{2} \ln\left(\frac{L_g + 2m}{L_g - 2X_p - 2W_o}\right) + \rho_D (t - m - X_p - W_o)$$

最後，在 LIGBT 方面，元件結構乃為橫向，電阻則以橫向為主，電阻分佈可參考 IGBT，然而在電流行進部分，以圖 2.21 所示，其中陰影地方為電流分佈。

圖 2.21 LIGBT 導通電流行進範圍圖

IGBT 與 LIGBT 在組成電阻成分多，低壓上或許各佔有一席之地，然高壓上，絕大部分卻取決於漂移區電阻，以本文 700V 為例，漂移區動輒 60um，電阻值勢必遠大於各各元素電阻，在考慮元件導通電阻方面，需對漂移區多進行研究，效能改善才有可能。而在  $R_{on,sp}$  本定義在 IGBT 上是有其物理意義，但其後也有人用在 LIGBT 上，其物理意義並不明顯，所以在日後文章的研究與討論上，主要針對 LIGBT 的導通電流，而非  $R_{on,sp}$ 。

## 2.2 IGBT 與 LIGBT 比較

IGBT 元件主要用於高耐壓、高電流承載以及頻率較低的電路上，而近來整合晶片發展下，IGBT 却有著無法突破的缺點，以致於 LIGBT 陸續研發中，可望在日後可完成高低壓隔離整合，實現功率 IC (power IC) 的時代，因此，以下介紹 IGBT 與 LIGBT 的各特性比較，以表 2.1 所示。

表 2.1 IGBT 與 LIGBT 元件比較表

|                        | IGBT                                         | LIGBT                             |

|------------------------|----------------------------------------------|-----------------------------------|

|                        | 機制：空乏電場積分                                    | 機制：空乏電場積分                         |

|                        | 技術：厚漂移區、N-buffer layer 摻雜                    | 技術：RESURF 理論、N-buffer layer 摻雜    |

| 耐壓 (BV)                | 利用元件的厚度與形狀，可將其最大耐壓至幾千伏，屬於良好的耐壓元件。            | RESURF 技術誤差大，於製程不易而且有最大耐壓一千多伏的限制。 |

| 導通電流 (I <sub>c</sub> ) | 機制：閘極驅動、電晶體電流放大                              | 機制：閘極驅動、電晶體電流放大                   |

|                        | 縱向結構因素，導通電流大。                                | 橫向結構限制，導通電流較小。                    |

| 隔離                     | 縱向結構關係，元件大多用於分立式結構 (discrete device) 並無隔離問題。 | 需要額外設計隔離結構或電路，漏電流控制不易。            |

| 整合                     | 基底接電極關係，整合不易。                                | 加入良好隔離技術，可進行高低壓整合。                |

所以在綜合表 2.1 兩種元件上的比較，雖然 IGBT 各方面均優於 LIGBT，包括最高耐壓、導通電流等，不過在未來 IC 時代裡，並不適合與低壓控制電路做一整合，所以本實驗選用 LIGBT，利用 RESURF 技術來實現高耐壓元件，並且希望實作出最高耐壓達 700V 的 LIGBT 功率元件。

## 2.3 回顧 LIGBT 元件在結構上效能的改善

由於本實驗元件以 LIGBT 為主，在回顧以往元件結構上的變化，以改善元件效能，便不再討論縱向結構的 IGBT。

### A. 門鎖效應的防治

在圖 2.6 結構等效電路圖中，就如之前討論過元件會因為  $R_s$  電阻過大，導致 NPN 電晶體導通，形成無法關閉的電流，造成門鎖效應，在防治方面，就以降低  $R_s$  電阻為主要目標。

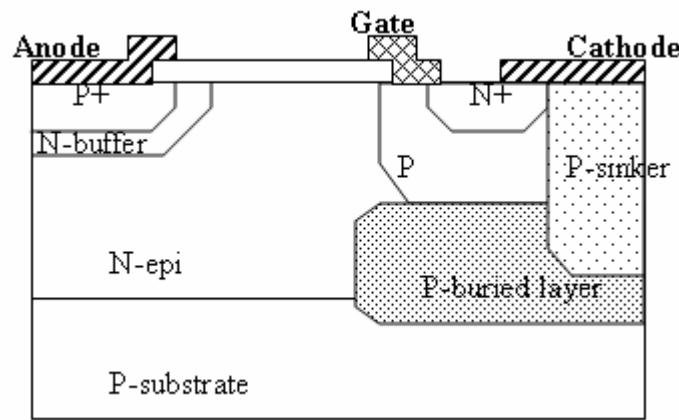

#### A.1 p 型井和埋藏層結構 (p-sinker and p-buried layer structure)

圖 2.22 p 型井與 P 埋藏層結構圖

在圖 2.22[10]中，元件利用加入 P+sinker 層的重摻雜濃度，以降低  $R_s$  電阻，而其 P-buried layer 為較低摻雜濃度，主要用來吸引電洞流經此處，導向 P+sinker 層，防止電流流經 P-base 層，避免門鎖效應。然而這樣結構會多增加兩道光罩，增加成本是需要考量的地方。

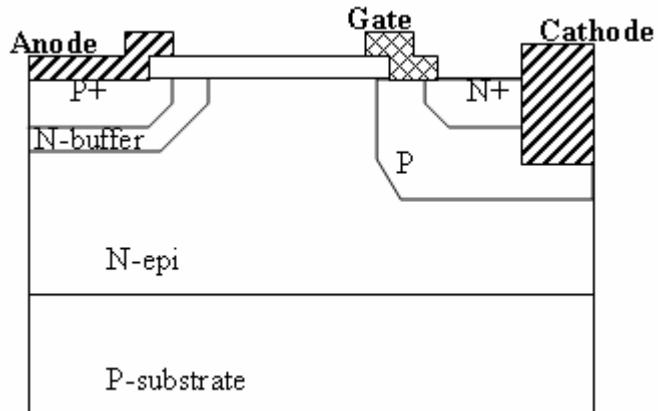

## A.2 自行對準溝朝式結構 (self-aligned trench structure)

圖 2.23 自行對準溝朝式結構圖

在圖 2.23[11]中，元件在陰極端 N+形成氧化層後，利用蝕刻 (etching) 的方式，做一垂直凹朝，使得陰極金屬端可以同時接觸到 N+與 P-base 層，縮短了電洞流經 P-base 層的距離，也降低  $R_b$  的電阻，此結構使用自我對準，並不需要再多開一道光罩。

## A.3 溝朝式閘極結構 (trench gate structure)

圖 2.24 溝朝式閘極結構圖

在圖 2.24[12]中，元件於結構上，利用改變電流路徑的方法，將陰極端與閘極端交換位置，使其電流並不需要經由 P-base 而是直接到達陰極，如此一來便可將寄生電阻  $R_s$  去除。其製程技術需要很準確，其閘極才可以控制得宜，是在這樣元件下需要克服的方向。

## B. 操作頻率提升

LIGBT 雖有其閘極壓控電流、高輸入阻抗的優點，又有電晶體放大電流效應以提高承載電流，然而卻也必須承受電晶體少數載子殘留的問題，導致 LIGBT 無法在高頻操作，以下就頻率作一說明。

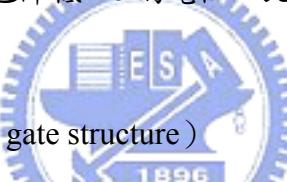

### B.1 陽極短路結構 (shorted anode structure)

圖 2.25 陽極短路結構圖

圖 2.25[13]的元件結構在於加速移除少數載子的殘留，在 PNP 橫向電晶體中，元件開與關之間，少數載子會殘留於 N-epi 區域，此時並無一順向 P/N 接面路徑，提供少數載子移除，只靠複合電流，所以速度慢，在此，提供一路徑，由  $N_{epi} > N_{buffer} > N^+$ ，少數載子經由此路徑，在速度上有所改進，其製程亦方便，不需要在額外加入光罩，所以在一般 LIGBT 元件設計上，都會用來作為與一般元件的比較。

### B.2 蕭基陽極結構 (Schottky Injection FET, 簡稱 SINFET)

利用蕭基二極體 (schottky diode) 取代陽極 PN 接面，此元件又稱為 SINFET[14]。導通時，SINFET 利用蕭基介面注入適量的少數載子，達到導通調變的作用，在元件關閉時，由於沒有累積太多的少數載子，其移除的時間相對減少，增快元件操作速度，另一方面，蕭基接面因順偏跨壓較 PN 接面小，所以在 SINFET 其元件在順向跨壓也比傳統元件來的小，可以減少導通時額外的功率損耗。

### C. 耐壓提升

LIGBT 為一橫向結構元件，在耐壓方面並非一味使用厚的漂移區來提升電壓，主要乃利用 RESURF 技術 (Reduced surface field) [15]，降低表面電場效應，以改變接面電場的形狀，使其近似雙三角形面積以增大電場積分面積，理論上有點像先前介紹的穿透二極體，然而由於漂移區過長，電場於中間部分會有下降現象。

圖 2.26 RESURF 示意圖

如圖 2.26 所示，P/N 接面因逆向偏壓產生空乏區的延伸，導致 N 區域全部被空乏時，電場出現雙峰，此時元件耐壓即為電場積分面積，只要雙峰電場任一個不到臨界電場 ( $E_c$ ) 值，接面便不會崩潰，元件就可以承受這樣的耐壓。

圖 2.27 不同摻雜濃度下電場分佈圖

在圖 2.27 中可以發現，於 RESURF 技術中，N 區域扮演最重要角色一環，不管在厚度與摻雜濃度上，足以影響整個元件耐壓程度，詳細部分將於後面章節加以說明，不過最主要目的均為利用不同參數調整，以得相同峰值電場，如此電場積分面積才會大，以提升元件耐壓。

另一方面，在模擬與實作元件中，會加入場板 (field plate) [9]於閘極和陽

極端，目的為了讓 N 區域在空乏區延伸中，空乏區曲率不置於過小，導致電場提早崩潰，至於應覆蓋多少長度，日後於第四章模擬部分將會加以討論，在實作元件部分，有關元件形狀也盡量不以尖角出現為第一考量，不然也是會有電場崩潰於尖角問題存在。

## 第三章 LIGBT 電信分析與研究方法

經由第二章 LIGBT 元件結構上的討論後，經由橫向思考，來導通高電流與承受高耐壓，而在各參數的調整上，卻是讓人有不知該如何定義，以及如何取其數值加以進行模擬，更而實作元件。所以在本章節主要在於研究方法的進行，利用文獻理論基礎，加以數值運算，計算出所需之參數，在本文結構中，屬於核心章節，以未來模擬上的參數給予一個切入點。

### 3.1 參數符號定義與結構規劃

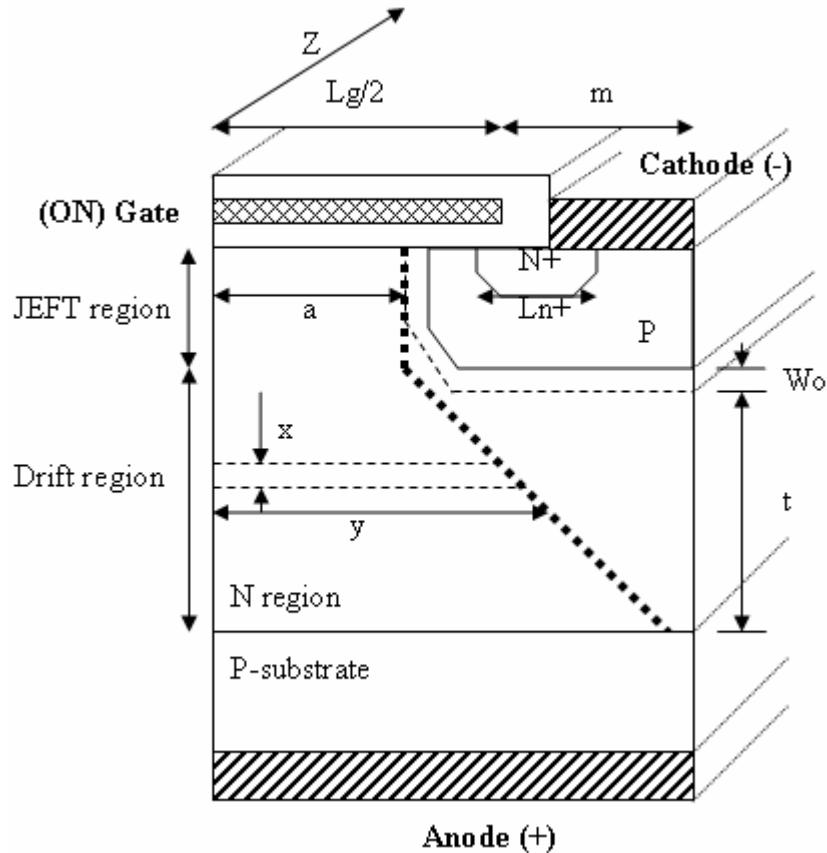

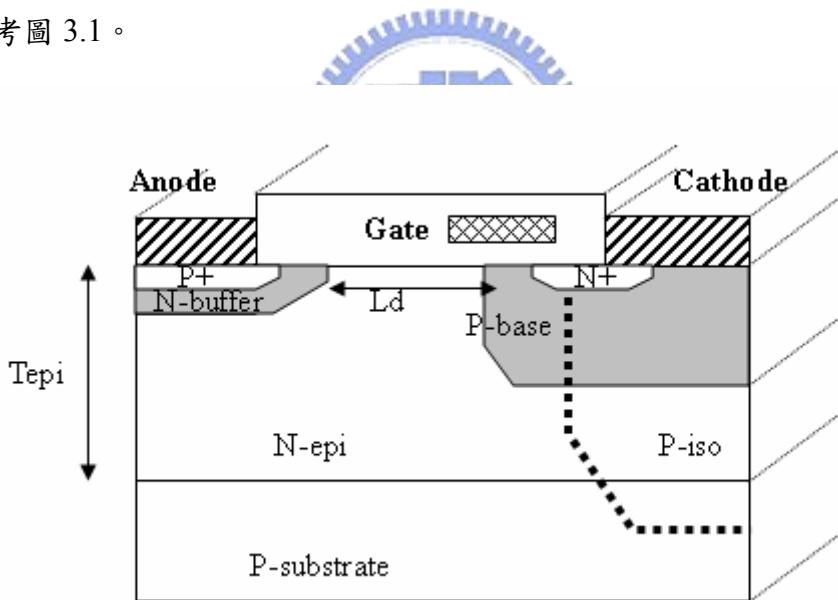

在推導公式分析之前，初步定義出元件的計算模型，輔助日後模擬，元件結構參考圖 3.1。

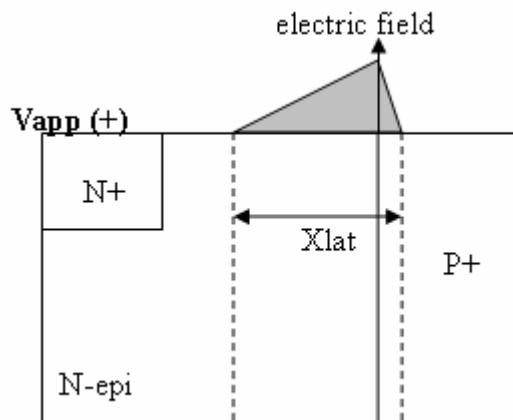

圖 3.1 初步計算結構定義圖

在圖 3.1 中，元件基本的結構就像第二章所描述，在文獻中得知橫向耐壓需要 N 區域(此時定義為 N-epi)完全被空乏，已降低表面電場效應，簡稱為 RESURF 現象，所以在此加入 P-iso 層，於這層的摻雜濃度會比 P-base 來的重，主要除了讓 N-epi 空乏區延伸容易外，更是可以確保與基底短路，形成空乏區電荷分享效應 (charge sharing)，這個理論的相關部分將於本章第二節做詳細說明。另外，

加入 P-iso 層亦方便日後此 LIGBT 功率元件與低壓控制電路在整合時，發揮隔離效果，阻止漏電流燒毀低壓電路。就之前所討論的，LIGBT 元件之所以能撐起高耐壓全靠 RESURF 理論，簡言之，運用改變表面電場形狀來提升電場積分，獲得更大的電位差，在 RESURF 形成下，其 N-epi 層需要完全被空乏 (fully depletion)，因此 N-epi 層一直為眾所注意的地方，也有不少文獻探討與實作其各參數，在此，利用以下推導理論公式，分別定義出 N-epi 層之厚度 (Tepi)、長度 (Ld) 與摻雜濃度，以便日後模擬分析。

## 3.2 參數分析與定義

### A. RESURF 理論

RESURF (reduce surface field) 定義為降低表面電場效應，利用低摻雜區域空乏區寬度的延伸，降低表面電場以防止接面提早達到臨界電場 ( $E_c$ )，而導致崩潰，而在電場形狀改變方面如同先前介紹過的最大好處在於出現雙峰，增大電場積分，回顧圖 2.10 與圖 2.27。然而在設計上，N-epi 層在濃度與厚度上的敏感度 (sensitivity) 大，不易達到最佳化值，於模擬上添增不少困難，而在 RESURF 各式理論中，本文選用空乏區電荷分享 (depletion charge sharing) [16] 做為計算依據，其因在於其 P 區域與本實驗 P-iso 擁有共同目的，適合初步計算。

於 1979 年，J.A. Appeals 和 H.M.J Vaes 提出 RESURF (REduced SURface Field) 原理，高壓元件始被製作於較薄的磊晶層上 (N-epi 或 P-epi 層)，這項技術不但提供了薄磊晶層與高耐壓的可能，更是在高低壓製程整合上大大提升機會，以迎接功率 IC 的時代。由於高壓功率元件 (此主要指 LIGBT 與 LDMOS) 大多有著三個接面：P+/N-epi、P-sub/N-epi 與 N-epi/N+，則考慮一個橫向結構，以圖 3.1 結構圖所示。

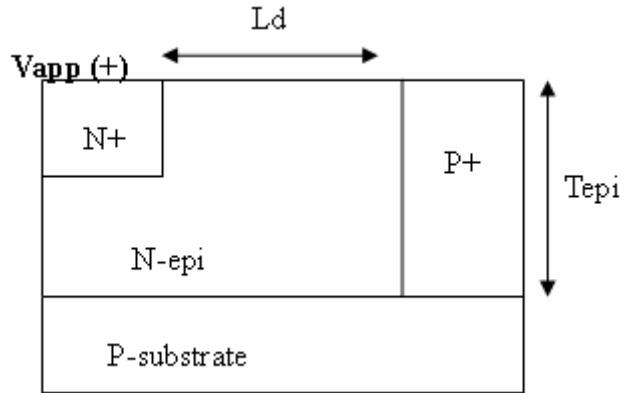

圖 3.2 橫向結構圖

當  $V_{app}$  電壓逐漸增加，於  $P+/N$ -epi 與  $P$ -substrate/N-epi 接面會因為空乏區而產生接面電場，在偏壓均為逆偏情況下，電場尚未崩潰之前，元件僅流漏電流，高壓元件在此稱之為靜態特性 (static blocking characteristics)，為一般功率開關元件此時的電流應為零，而元件兩端承受一高耐壓。當  $V_{app}$  電壓大至一值，導致前述三種接面電場之一崩潰，其元件便流通大量電流，此電流不僅使電路工作不正常，更是可能毀損元件接面結構，造成永久性傷害，當其  $V_{app}$  電壓昇至最大值，定義為元件之崩潰電壓 (breakdown voltage)，簡稱為  $BV$  值。就圖 3.1 結構，在考慮  $V_{app}$  電壓增加時，將其結構拆解成圖 3.2 所示，其中虛線即為空乏區域的形成。

圖 3.3 將圖 3.1 結構拆解成兩個接面示意圖

此時假設  $P+$  摻雜濃度大於  $N$ -epi 濃度，則

$$w = \sqrt{\frac{2\epsilon_s V_{app}}{qN_a}} \equiv X_{lat}$$

在這個接面空乏區的形成主要與重摻雜區域有關。另外，由於 P-sub 層濃度與 N-epi 層的濃度比較接近，所以在空乏區寬度方面則與兩者摻雜濃度有關，得

$$X_{ver}(Vapp) = \sqrt{\frac{2\epsilon_s \cdot Vapp \cdot Psub}{q \cdot Nepi \cdot (Psub + Nepi)}}$$

在得知空乏區寬度後，可以推得空乏區電荷 Q

$$Q_{lat}(Vapp) = q \cdot Nepi \cdot X_{lat}(Vapp)$$

利用 Poisson's equation

$$\frac{d^2V}{d^2x} = -\frac{dE}{dx} = -\frac{\rho(x)}{\epsilon_s}$$

等號兩邊做積分

$$E = \int \frac{\rho(x)}{\epsilon_s} dx = - \int \frac{qNepi}{\epsilon_s} dx = \frac{-qNepi}{\epsilon_s} x + C1$$

令常數為零，且 x 以 Xlat(Vapp) 代入

$$E_{lat}(Vapp) = \frac{Q_{lat}(Vapp)}{\epsilon_s} = \frac{2 \cdot Vapp}{X_{lat}(Vapp)}$$

得知電場對 x 積分的面積即為電位，此處假設 P+ 區域濃度大於 N-epi 濃度，即空乏區寬度主要延伸為 N-epi 層區域，得電位大約為圖 3.3 之三角形面積。

圖 3.4 橫向接面電場表示圖

電場積分面積大約為

$$V(triangular\_area) = \frac{1}{2} E_{lat}(Vapp) \cdot X_{lat}(Vapp)$$

而由於  $V(triangular area) = Vapp$ ，得

$$\frac{1}{2} Elat(Vapp) \cdot \sqrt{\frac{2\epsilon_s Vapp}{qNepi}} = Vapp$$

得

$$Vapp = \frac{\epsilon_s Elat(Vapp)^2}{2qNepi}$$

於功率元件裡，定義當  $Vapp = BV$  時，其接面電場崩潰，得一臨界電場  $Ec$  值，

得

$$BVlatj = \frac{\epsilon_s \cdot Eclat^2}{2qNepi}$$

其中 P/N 接面臨界電場  $Ec \approx 3 \times 10^5 V/cm$ ， $Ec$  為橫向接面最大崩潰電場。

同理，在考慮縱向結構時 (N-epi 與 P-substrate 接面)，其  $Xver$  如下：

$$Xver(Vapp) = \sqrt{\frac{2\epsilon_s \cdot Vapp \cdot Psub}{q \cdot Nepi \cdot (Psub + Nepi)}} \quad (3.1)$$

由式子(3.1)不難發現，當 N-epi 與 P-substrate 濃度較接近時，兩邊區域都有空乏區的延伸，如此一來可以加大三角形電場的底邊，增大電場積分的電壓，之後會證明，於 N-epi 層在某些值時， $BVverj$  為主要耐壓。接著利用 Poisson's equation，得

$$BVverj = \frac{\epsilon_s \cdot Ecver^2}{2q} \cdot \left( \frac{1}{Nepi} + \frac{1}{Psub} \right)$$

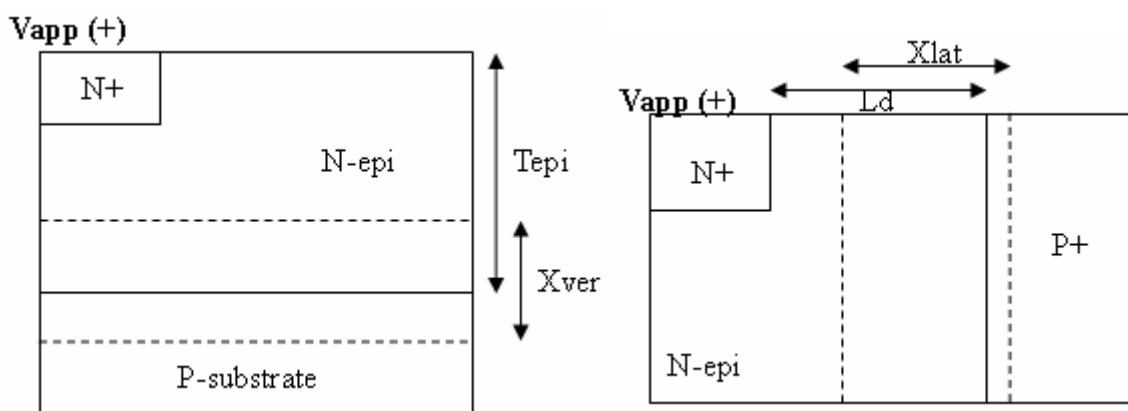

分別考慮完縱向與橫向的接面電場與崩潰電壓後，將兩大結構綜合考慮，可以得到以下圖 3.4 元件結構：

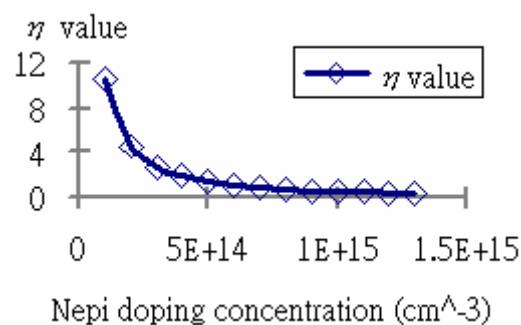

圖 3.5 resurf 理論結構圖

在圖 3.4 中，空乏區長度的延伸以考慮低摻雜區域為主，清楚看到，在 N-epi 層區域，因為 P+與 P-substrate 關係，兩邊接面空乏區共同往 N-epi 層延伸，導致出現一共同空乏區域 (depletion charge sharing)，為圖 3.4 陰影部分，在以下推導我們以橫向為主，提出一假設參數：

$$\Delta Q(Vapp) = q \cdot Nepi \cdot Xlat(Vapp) \cdot \eta(Vapp)$$

其中

$$\eta(Vapp) = \frac{Xver(Vapp)}{Tepi} \geq 0$$

可以清楚看到其  $\Delta Q(Vapp)$  為陰影部分電荷面積，而實際有效橫向空乏區即

$$Qlateff(Vapp) = Qlat(Vapp) - \Delta Q(Vapp) = [1 - \eta(Vapp)] \cdot Qlat(Vapp)$$

換言之，對橫向接面來說， $Qlat(Vapp)$  並非為加入 P-sub 結構時的空乏電荷，而是需要改寫，使其扣除有關縱向接面所提供的空乏電荷。接著，假設其等效電場  $Elateff$ ，則

$$Elateff(Vapp) = \frac{Qlateff(Vapp)}{\epsilon_s}$$

由之前公式

$$Qlat(Vapp) = q \cdot Nepi \cdot Xlat(Vapp)$$

且

$$Qlateff(Vapp) = [1 - \eta(Vapp)] \cdot Qlat(Vapp)$$

得

$$Qlateff(Vapp) = [1 - \eta(Vapp)] \cdot q \cdot Nepi \cdot Xlat$$

假設

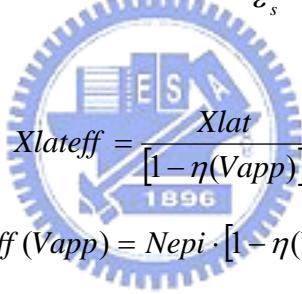

$$Xlateff = \frac{Xlat}{[1 - \eta(Vapp)]}$$

所以改寫

$$Qlateff(Vapp) = [1 - \eta(Vapp)] \cdot q \cdot Nepi \cdot Xlat = [1 - \eta(Vapp)]^2 \cdot q \cdot Nepi \cdot Xlateff$$

方便日後計算，令  $Nepieff(Vapp) = Nepi \cdot [1 - \eta(Vapp)]^2$

得

$$Qlateff(Vapp) = q \cdot Nepieff \cdot Xlateff$$

代回公式，得

$$Elateff(Vapp) = \frac{q \cdot Nepieff(Vapp) \cdot Xlateff(Vapp)}{\varepsilon_s}$$

其中

$$Xlateff = \frac{Xlat}{[1 - \eta(Vapp)]}$$

$$Nepieff(Vapp) = Nepi \cdot [1 - \eta(Vapp)]^2$$

由於

$$BVlatj = \frac{\varepsilon_s \cdot Eclat^2}{2qNepi}$$

其中 N-epi 由於空乏區電荷分享 (charge sharing) 的關係，改寫成 Nlateff，而在未來模擬中，我們將會調整 N-epi 濃度至 Nresurf 時，產生 RESURF 現象，而其對應崩潰電壓為 BVresurf。

因此代入  $Nepieff(Vapp) = Nepi \cdot [1 - \eta(Vapp)]^2$  於上式中

得

$$BVlateff = \frac{\varepsilon_s \cdot Eclat^2}{2q \cdot Nresurf} = \frac{\varepsilon_s \cdot Eclat^2}{2q \cdot Nepi \cdot [1 - \eta(Vapp)]^2} = \frac{BVlatj}{[1 - \eta(Vapp)]^2}$$

由於此時  $Vapp = BVlatj$ ，改寫

$$BVlateff = \frac{BVlatj}{[1 - \eta(BVlatj)]^2}$$

可得

$$BVresurf = \text{Min}[BVlat, BVver]。$$

## B. $\eta$ 值討論與物理意義

上述公式中，以求解  $\eta$  值，作為 RESURF 現象公式說明。一般而言，由於崩潰區域大都為濃度梯度較大的橫向接面，所以在此討論時仍以橫向 BV 值為主。首先

$$BVlateff = \frac{BVlatj}{[1 - \eta(BVlatj)]^2} \quad (3.2)$$

可知當橫向接面崩潰時，其耐壓最大為  $BVlatj$ ，其影響固然決定於濃度關係，但是在式子(3.2)裡， $\eta$  值卻是扮演著提升耐壓的效果，只要適當調整各參數值，便可得到想要的 RESURF 電壓。而在調整  $\eta$  值之前，先就其物理意義作為討論。

$$\text{令 } \eta(Vapp) = \frac{Xver(Vapp)}{Tepi}$$

$$B.1 \quad \eta(BVlatj) = 0$$

當  $\eta$  值等於零，代表  $Xver(Vapp) = 0$ ，所以並沒有 P-substrate 區域，所有的崩潰電壓由橫向接面來決定， $BVlateff = BVlatj$ 。

$$B.2 \quad 0 < \eta(BVlatj) < 1$$

得知  $Tepi > Xver(Vapp)$ ，在尺寸結構上來說，表示  $Tepi$  過大，導致 N-epi 層根本無法被完全空乏，就摻雜濃度而言，其 N-epi 層濃度過大或是 P-sub 濃度過小，均導致空乏區寬度的延伸不夠，其 N-epi 層亦無法完全被空乏，所以公式需改寫  $BVlateff = BVlatj$ ，此時元件並無法有 RESURF 現象，然後

$$BV = \text{Min}[BVlateff, BVver]。$$

在以上討論的兩個情況下，RESURF 現象均並未沒有出現，耐壓也會過低，不過卻是有一個值得我們去注意的地方，在日後，可以將 N-epi 層的摻雜濃度與厚度做一調整，便可達到具有 RESURF 現象的元件。

### B.3 $\eta(BV_{latj}) = 1$

由公式(3.2)可得知，當  $\eta$  值等於一時，其  $BV_{lateff} = \infty$ ，然而受限於物理結構上，這是不可能的，因為  $Nepieff(Vapp) = Nepi \cdot [1 - \eta(Vapp)]^2$ ，得  $Nepieff(Vapp) = 0$ ，半導體物理上沒有一個濃度摻雜可以為零，因此必須做一修正

$$Nepieff(Vapp) = Nepi \cdot [1 - \eta(Vapp)]^2 + Ni = 1.45 \times 10^{10} \text{ cm}^{-3}$$

也就是說當 N-epi 層為本質半導體時，可以得到最大耐壓，不過如此一來，並沒有任何半導體物理意義，元件也非原本構思，這一情況並非所要討論之 RESURF 現象。

### B.4 $2 > \eta(BV_{latj}) > 1$

這個情況發生在薄 Tepi 與低 N-epi 層摻雜，Xver 與 Xlat 形成的空乏區可以輕易延伸至整個 N-epi 層區域，形成 RESURF 的現象，增大電場積分，也提升了原本的耐壓，就一橫向高耐壓的元件而言，在 N-epi 層的厚度與摻雜濃度上加以調整，分別取得兩者參數值，進而實現元件 RESURF 現象的產生，增大耐壓。

然而濃度會影響導通電阻，造成電流過小的問題，所以在設計的時候，應該找一個耐壓符合規格以及 N-epi 濃度最大的最佳化設計，相關部分在於第四章模擬做更詳細的討論。

### B.5 $\eta(BV_{latj}) = 2$

在實現 RESURF 現象中，橫向耐壓提升條件下， $\eta$  值為最大可能值，若其值大於二，橫向崩潰電壓 ( $BV_{latj}$ ) 便沒有放大的效果，所得到的耐壓相對成二次方程式下降。

### B.6 $\eta(BV_{latj}) > 2$

可以發現其 N-epi 層厚度過小，或是摻雜過低，其橫向 PN 接面電場由於摻雜梯度過大而容易崩潰，耐壓相對低。

綜合以上 RESURF 數學式，利用 EXCEL 計算這些數質，並畫成圖形，以方便日後模擬的參數取樣。

### C. N-epi 層摻雜濃度定義

表 3.1 初始元件計算表格

|               |                        |

|---------------|------------------------|

| P-sub         | 1.78e14                |

| N-epi         | Split                  |

| Q             | 1.6e-19                |

| Es            | $11.7 \times 8.85e-14$ |

| Eclat = Ecver | 3e5                    |

| Tepi          | 15 and split           |

在計算理論公式過程中，以橫向耐壓為主要重點，並畫出計算得到的圖形，以方便分析，其中參數初始定義為以上所示，過程中，最重要為  $\eta$  參數取得，其影響 RESURF 現象最為顯著。首先計算與圖示出以下式子：

$$Xver(Vapp) = \frac{2\varepsilon_s \cdot Vapp \cdot Psub}{\sqrt{q \cdot Nepi \cdot (Psub + Nepi)}}$$

與

$$\eta(Vapp) = \frac{Xver(Vapp)}{Tepi} \geq 0$$

得

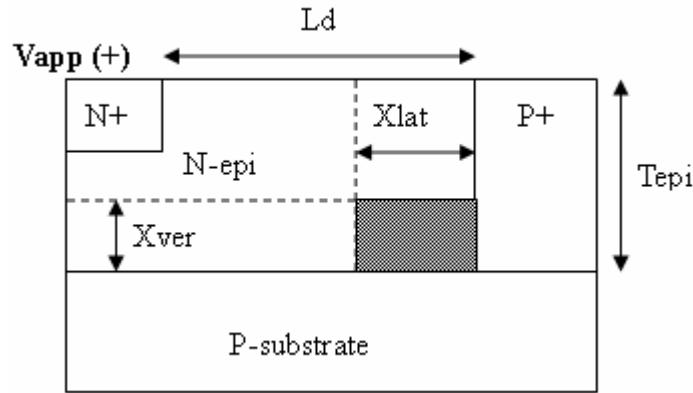

圖 3.6  $\eta$  值與 Nepi 濃度相關圖形

再將其  $\eta$  值代入以下式子：

$$BVlateff = \frac{BVlatj}{[1 - \eta(BVlatj)]^2} \quad BVlatj = \frac{\varepsilon_s \cdot Eclat^2}{2qNepi}$$

以得實際上 BVlateff 的值：

圖 3.7 BVlatj 與 BVlateff 電壓分佈圖

由圖 3.6 中，不難發現，原本 BVlatj 的耐壓會與 N-epi 層摻雜濃度成負相關，而這與兩個接面的濃度差異有關，然而今卻會因為 RESUFR 的現象，將其耐壓提升，為一近似二次函數，主要為  $\eta$  參數本身就是一個二次函數關係，有一最高值，在計算這結果後，再加入 BVverj 關係，進而瞭解各電壓的分佈。

圖 3.8 各接面電壓分佈圖

在圖 3.7 中，可以看到縱向接面的崩潰電壓明顯大於橫向接電崩潰電壓，其因在於濃度梯度小與空乏長度大，而在橫向出現 RESURF 現象後，取其兩取線最小值，及

$$BV_{resurf} = \min[BV_{lateff}, BV_{ver}]$$

可以得到 BVresurf 圖形：

圖 3.9 RESURF 現象電壓圖

接著加入另一變數  $T_{epi}$ ，分別為 5um、10um 以及 15um，再做一次上述計算，以圖 3.9 所示。

圖 3.10 不同 N-epi 厚度 RESURF 電壓分佈圖

圖 3.9 顯示出在不同 N-epi 厚度下，RESURF 電壓與摻雜濃度關係，其中以厚度為 10um 為本實驗所取樣參數，主要原因在於不但實作上可配合，而其 N-epi 摻雜濃度在製程上比較可能，濃度太輕導通電阻過大，太重則製程成本過高。綜合以上各圖，取樣出所要模擬圖形。

圖 3.11  $T_{epi}=10\mu m$  所計算出來的電壓關係圖

#### D. N-epi 層厚度定義

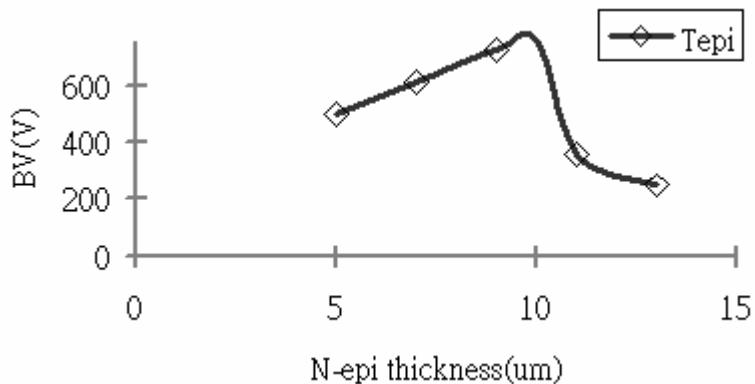

接著利用各層摻雜濃度  $P$ -substrate =  $1.78e15$ 、 $N_{epi}=1e15$  等，以  $T_{epi}$  作為變數，計算出數值，並畫出圖形：

圖 3.12 厚度與崩潰電壓關係圖

從圖 3.10 觀察，崩潰電壓前段為線性上升，與厚度成正比，之後到達一固定值，最後，超出 RESURF 現象則成二次函數遞減，其遞減速度相當快，在元件設計也盡量不要接近後段區間，防止元件耐壓過低。

#### E. 漂移區 (drift region) 長度定義

在第二章裡，曾討論過穿透二極體效應，元件上加入 N-buffer 層區域，以改變電場形狀，提升元件耐壓能力，在此以圖 2.9 圖為例，將 P/N 接面做一逆向偏壓，此時摻雜濃度 P+ 區域大於 N 區域，所以空乏區域會向 P 區域延伸，以下推導只考慮延伸較多的區域。接著考慮 Poisson's equation

$$\frac{d^2V}{d^2x} = -\frac{dE}{dx} = -\frac{Q(x)}{\epsilon_s} = \frac{qNa}{\epsilon_s}$$

利用積分求解 E 和 V，得

$$E(x) = \frac{qNa}{\epsilon_s}(w-x) , V(x) = \frac{qNa}{\epsilon_s}(wx - \frac{x^2}{2})$$

在電壓 V 方面，代入邊界條件， $V = Va$  時  $x = w$ ，得

$$w = \sqrt{\frac{2\epsilon_s Va}{qNa}}$$

再將 W 代回電場公式，得

$$Em = \sqrt{\frac{2qNaVa}{\epsilon_s}}$$

此時  $Em$  可令之為 P/N 接面電場的最大值，也就是說，當逆偏電壓到達一定值，可得到最大電場  $Em$ ，若在增加偏壓，電場便會過大，導致 P/N 接面崩潰，這時元件便會流經大電流，一般稱為崩潰電壓 (BV)，其電場稱為臨界電場 ( $Ec$ )。

最後，將所得電場  $Em$  公式代入原本游離因子公式，得

$$\int_0^w 1.8 \times 10^{-35} E^7 dx = \int_0^w 1.8 \times 10^{-35} \left[ \frac{qNa}{\epsilon_s} (w-x) \right]^7 dx = 1$$

解其方程式，得 W 值

$$w = 2.67 \times 10^{10} Na^{-7/8} \equiv W_{c,pp}$$

代回電壓公式，得 V 值

$$V = 5.34 \times 10^{13} Na^{-3/4} \equiv BV_{pp}$$

再綜合這兩個方程式，利用 MATLAB 做圖，以下所示：

圖 3.13 BVpp、Wc,pp 與 N-epi 層摻雜濃度綜合計算結果圖

在圖 3.11 中，在崩潰電壓（BVpp）與空乏區寬度（Wc,pp）裡，將其座標轉成指數座標以方便我們觀察，不難發現，當低摻雜濃度指數下降，其空乏區寬度與崩潰電壓隨之上升，如此一來，若今日設計元件在於 700V 以上，N 區域摻雜濃度便要比 3.2e14 更低，而其空乏區寬度也要大於 55um 以上，這樣的話，元件於順向偏壓，也就是當操作在線性區時，造成導通電阻過大，其電流會明顯的下降，失去高壓元件的另一項考量，因此，根據前節 RESURF 計算結果與日後模擬、下線製程方面，必須將其 N 區域濃度調整至 1e15 左右，換言之，希望在崩潰電壓符合規格條件下，加上漂移區摻雜濃度影響導通電阻，將其摻雜濃度可調之最大值以降低導通電阻，此時加入 N-buffer 層，利用圖 2.9 穿透二極體示意圖，推導以下理論公式。首先，利用電場公式，將 Wc,pp 以及 BVpp 代入，得

$$Ec, pp = 4010Na^{-1/8}$$

接著觀察穿透二極體的電場積分面積，大約等於其梯形面積，即

$$V_{NT} = \frac{1}{2}(Ec + E_1)W_N$$

代入電場公式，得

$$E_1 = Ec - \frac{qN_{aN}}{\epsilon_s} W_N$$

綜合兩式，得

$$V_{NT} = Ec \cdot W_N - \frac{q \cdot N_{aN} W_N^2}{2\epsilon_s}$$

再結合

$$Ec, pp = 4010Na^{-1/8}$$

利用 MATLAB 做圖

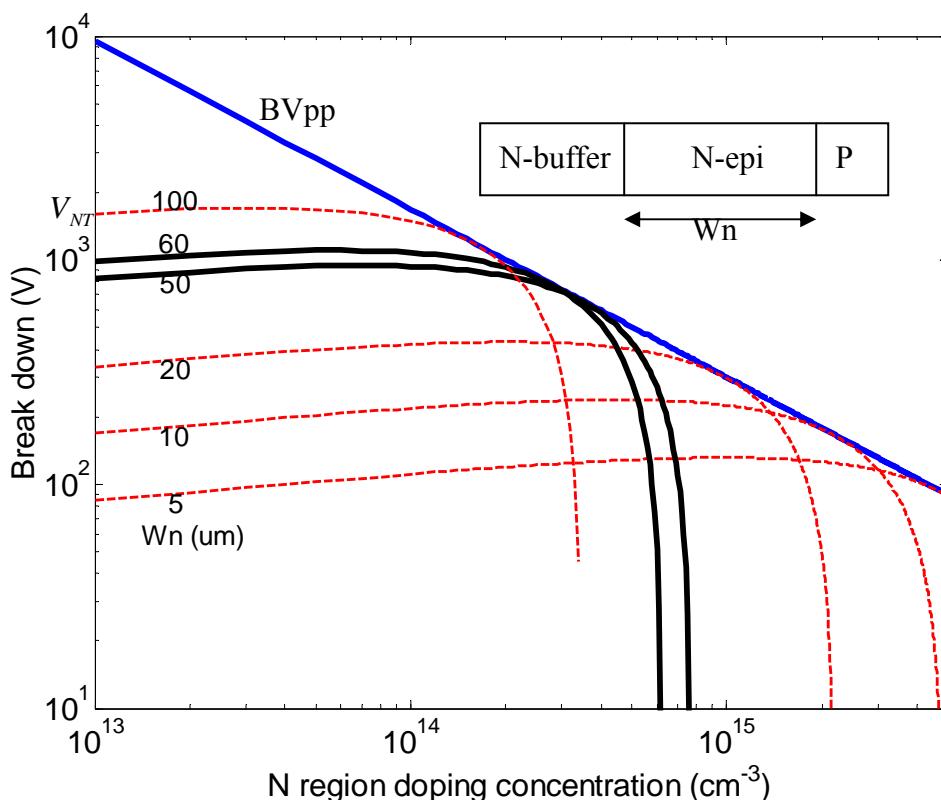

圖 3.14 穿透二極體電壓分佈圖

圖 3.12 中可以清楚看到，當要設計一利用穿透二極體的元件時（加入 N-buffer 層），若其耐壓要超過 700V 以及 N-epi 摻雜濃度要高時，其 Wn 分佈需要大於 50um 以上。

綜合以上四點，討論 RESURF 理論分析、N-epi 的摻雜濃度與厚度以及漂移區長度的計算，可以規劃出未來模擬初步參數定義範圍，給予一切入點，以圖

3.13 與表 3.2 所示。

圖 3.15 各參數範圍示意圖

表 3.2 定義各層參數圖表

|                   | 摻雜濃度                                  | 厚度    |

|-------------------|---------------------------------------|-------|

| P-substrate layer | $1.78 \times 10^{15} \text{ cm}^{-3}$ | 90um  |

| PISO layer        | $1 \times 10^{18} \text{ cm}^{-3}$    | 12 um |

| N-epi layer       | Split                                 | Split |

| P-base layer      | Split                                 | 1um   |

| N-buffer          | Split                                 | 2um   |

| N+ layer          | $1 \times 10^{20}$                    | 0.5um |

| P+ layer          | $1 \times 10^{20}$                    | 0.5um |

### 3.3 製程規劃

在有了前兩節的計算基礎後，本節對於製程流程上著手進行初步規劃，以便第四章模擬分析。

表 3.3 實驗室製程流程表

| 流程                   | 備註                                                                | 厚度    |

|----------------------|-------------------------------------------------------------------|-------|

| 1. Wafer start       | p-sub = 81ohm-cm                                                  | 90um  |

| 2. SAC               | Dry O <sub>2</sub> 1050°C/10min                                   | 250A  |

| Mask #PISO           |                                                                   |       |

| 3. PISO implant      | B: 6E14/80keV/ titl=7                                             |       |

| 4. N-epi             | P: 5e14 ~ 5e15<br>1100 °C/ 180min                                 | 10um  |

| 5. SAC               | Dry O <sub>2</sub> 1050°C/10min                                   | 250A  |

| Mask #PISO           |                                                                   |       |

| 6. PISO implant      | B: 6E14/80keV/ titl=7                                             |       |

| 7. SAC               | Dry O <sub>2</sub> 1050°C/10min                                   | 250A  |

| 8. Well drive-in     | INERT: 1150 °C/120min                                             |       |

| Mask #P-base         |                                                                   |       |

| 9. PBASE implant     | B: split                                                          | 1um   |

| Mask #N-buffer       |                                                                   |       |

| 10. N-buffer implant | P: 9e13/100keV                                                    | 2um   |

| 11. Well drive-in    | INERT: 1150 °C/120min                                             |       |

| 12. FOX              | DRYO2: 1050 °C/20min<br>WETO2: 1100 °C/50min<br>DRYO2: 1050 °C/20 | 5000A |

| 13. Gate Oxide       | DRYO2: 1050 °C/35min                                              | 420A  |

| 14. POLY             |                                                                   | 1000A |

|                   |                                            |       |

|-------------------|--------------------------------------------|-------|

| Mask #N+          |                                            |       |

| 15. N+ implant    | ARSENIC:<br>3E15/50keV/titl=7              | 0.5um |

| Mask #P+          |                                            |       |

| 16. PPLUS implant | BF2: 5E15/50keV/TILT=7                     | 0.5um |

| 17. BPSG          | Deposit OXIDE 1um<br>DRY O2: 900 °C /10min | 1um   |

| 18. METAL         | Al                                         | 2um   |

經由以上製程流程規劃，在各層方面做一說明與討論，以方便日後研究用。

#### A. Wafer 層：

本實驗主要以高阻值晶圓作為實驗基底，一般在高壓元件生產上，絕大部分會用這樣的晶圓，屬於特殊晶圓。

#### B. PISO 層：

此層在磊晶層尚未成長時，便會打入想要的區域，之後磊晶層長好後，可以利用退火（drive-in）製程步驟，以達成 PISO 層，所以在 PISO 層裡會有分兩次離子佈植的步驟。

#### C. N-epi 層：

高壓元件通常會長一厚度達數十 um 的磊晶層，製程過程長，以達此層濃度均勻，比起離子佈植較不會有濃度擴散不均的問題。

#### D. P-base 層：

此層在於調整元件  $V_{th}$  以及橫向電場分佈，在效能上影響極為重要，由於決定通道大小，所以在  $BV$  值與導通電阻上會 trade-off 的現象。

#### E. N-buffer 層：

在 N-buffer 製程上，一般高壓元件並不會多加一道光罩來製作，主要共用低壓 N-well 光罩即可，以減低成本。

#### F. Gate oxide 層：

在閘極方面，仍以多晶矽為主，厚度一般 700V 最好大於 400A，本文以 420A 為主，以防止電場崩潰於 oxide，其崩潰原因在於 P/N 接面靠近 oxide 層容易被其電場應力給打穿。

## 第四章 LIGBT 模擬與理論驗證

在新元件的開發中，由於實作製程上時間冗長，一般都是運用計算初步估計值，接著加以模擬分析，最後規劃製程與光罩，才會下線製作晶片。本文使用計算機輔助軟體 (TCAD) 裡的 2D 模擬，以 Tsuprem4 模擬製程步驟而完成元件製造，之後再將完成的元件以另一套軟體 Medici 作電信分析，包括耐壓 (BV 值)、導通電流 (Ic) 與元件臨界電壓 (Vth) 等，以得欲實作元件的特性，本文以開發初期 LIGBT 元件為主，目標在於耐壓可達 700V，再調整其他參數以得最佳化的元件。在元件耐壓 (BV 值) 方面，本章除了可以驗證之前第三章推導的公式外，還為日後在實作製程元件上作為依據，模擬出可能實作出的元件，進而比較出模擬與實作上的差異。在 Tsuprem4 的模擬製程中，本實驗共使用了兩套輸入檔 (input file)，一為實驗室版本，簡稱為 LAB input file，主要依據第三章第三節的製程規劃流程而撰寫，另一為園區某半導體製程公司提供之輸入檔，簡稱為 FAB input file，為符合實際實作而撰寫，不過卻基於機密文件與公司硬體設備，需要在公司內部完成，模擬時間較長也較難以管理，然而不管何種輸入檔，在模擬過程中均以調整尺寸為先，調整後再做各層摻雜濃度模擬，而在參數初步猜測值方面，以第三章計算的結果為主。首先就元件模擬結構上做一說明，以圖 4.1 所示。

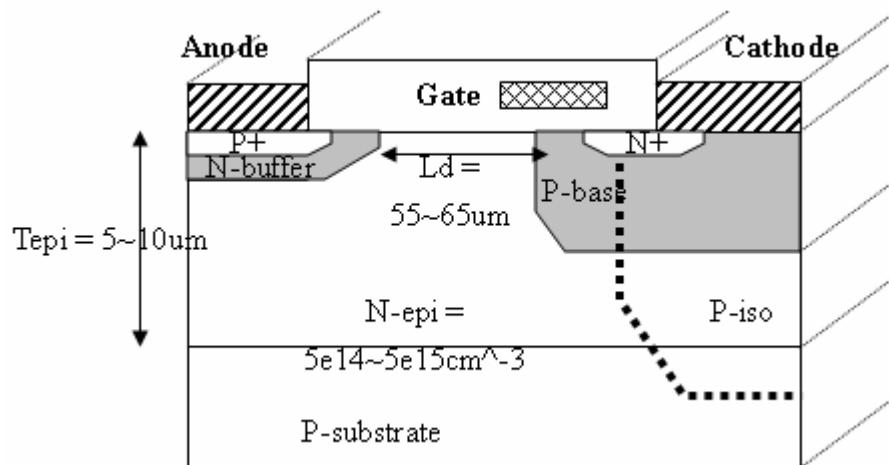

圖 4.1 模擬基本結構圖

在圖 4.1 裡，主要定義出元件尺寸參數，其中由於模擬軟體為 2D 模擬，所以截面積深度以 1um 為基本單位。接著以表 4.1 簡介各參數定義。

表 4.1 參數定義表格

| 名稱          | 說明                              | 參數模擬                              | 備註                                                                         |

|-------------|---------------------------------|-----------------------------------|----------------------------------------------------------------------------|

| Ao          | Anode overlap length            | 1um~5um                           | 在陽極端電極做一延伸，主要功用讓空乏區邊緣得以延伸，防止接面因為空乏區形狀而提早崩潰。                                |

| Po          | Poly gate overlap length        | 0um~5um                           | 模擬時，由於 N-epi/P-base 接面最容易崩潰，除了半導體摻雜的關係外，其 Poly oxide 為薄氧化層，容易被打穿，所以需要場板技術。 |

| Tepi        | N-epi layer thickness           | 3um~12um                          | 影響 RESURF 現象形成與否，過薄與過厚均不好，找出適當參數值。                                         |

| Ld          | Drift region length             | 50um~70um                         | 主要影響元件耐壓與導通電阻，於模擬時需要做變數模擬。                                                 |

| N-epi       | N-epi layer concentration       | 7e14~<br>1.5e15cm <sup>-3</sup>   | 與第三章計算做一比較，主要找出耐壓可以大於 700V 與此層摻雜濃度最高的參數值。                                  |

| P-substrate | P-substrate layer concentration | 1.5e14~<br>1.8e14cm <sup>-3</sup> | 雖然晶圓為 1.78e14cm <sup>-3</sup> 摻雜濃度，仍然可以模擬觀察耐壓趨勢圖。                          |

綜合以上各參數表，著手進行模擬工作，以便實作時參數給定，然而 Tsuprem4 模擬軟體模擬時間很長，以一個元件為例，需要一至兩天時間，所以這時在第三章所計算的 RESURF 耐壓結果便顯著重要。

#### 4.1 模擬結果（實驗室輸入檔）

根據第三章第三節，規劃出製程流程後，撰寫模擬軟體 Tsuprem4 的輸入檔 (input file)，本節定義為實驗室輸入檔 (LAB input file)，除了找出實作時所需要的資料，更而進一步比較與第三章計算結果，驗證公式的正確性。以下就尺寸模擬與摻雜濃度模擬兩方面做一說明。

##### A. 尺寸模擬

在規劃本實驗的模擬步驟方面，以尺寸模擬為先，然後進入各層半導體摻雜濃度模擬，當然元件除了這些尺寸參數外，另有一些影響較不大的區域，模擬過程中，先是取其適當值，日後如有要更進一步探討變化，再予以加入參數做一討論。首先討論在 Ao 與 Po 長度的影響，其理論主要利用場板 (field plate) 技術，來防止電場提早崩潰。

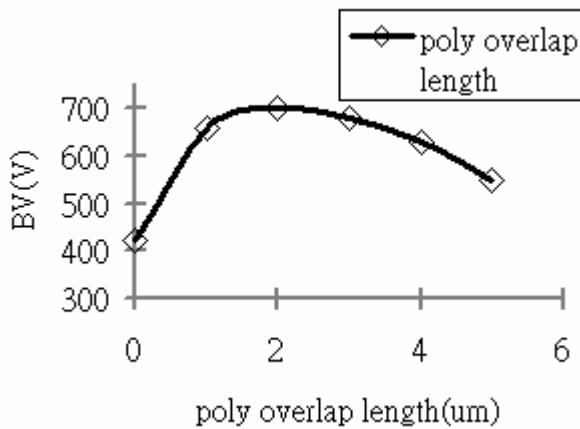

圖 4.2 Poly overlap length 耐壓關係圖

圖 4.3 Anode overlap length 耐壓關係圖 (Po=2um)

以圖 4.2 與圖 4.3 中可以看出場板效應裡，在沒有電極延伸的範例時候，其 BV 值均較低。然而在 Ao 與 Po 兩者對元件的影響中，由於 N-epi/P-base 接面，也就是 Po 的影響，為空乏區先形成處，若沒加場板的話，空乏區電場容易因為電力線擁擠而崩空，所以場板的影響便很大，在圖 4.2 中，Po 長度不夠長的話，電壓會下降的非常快，因為 N-epi 層空乏區的延伸形狀不夠平坦，造成電力線擁擠，電場過大導致接面提早崩潰，其 BV 值嚴重下降。接著在陽極與陰極電極覆蓋部分，由於空乏區形狀影響並非閘極那樣大，所以可以發現在圖 4.3 裡，Ao 幾乎沒影響到耐壓。因此在陽極電極覆蓋與閘極電極覆蓋方面，取其 Ao=3um 與 Po=2.5um。

圖 4.4 Ld 與耐壓關係圖 (LAB input file)

在圖 4.4 中，取其實驗室輸入檔模擬兩種 N-epi 層摻雜濃度時 Ld 變化情況，

明顯的在  $N\text{-epi}=1\text{e}15$  時，LIGBT 元件才會有 RESURF 的現象產生，另外耐壓（BV 值）會隨漂移區長度變大而提升，而在  $L_d=65\text{um}$  的情況下，耐壓可以高於 700V，而在  $N\text{-epi}=3.5\text{e}15$  時，理論上  $N\text{-epi}/P\text{-base}$  接面會因為濃度梯度過大得關係，在  $N\text{-epi}$  層尚未完全被空乏時就已崩潰了，所以不管漂移區長度如何改變，其 BV 值依舊取決於  $N\text{-epi}/P\text{-base}$  接面的崩潰電壓，也因為沒有 RESURF 現象的產生，所以 BV 值大約只在 100V 左右。

圖 4.5 N-epi 層厚度與耐壓關係圖 (LAB input file)

在圖 4.5 中，在  $N\text{-epi}=1\text{e}15$  的範例中，當  $T_{epi}$  小於 8um 時，元件會有 RESURF 現象的產生，所以 BV 值會因為空乏區長度的變大而跟隨著電場積分面積變大而提升，當  $T_{epi}$  約大於 8um 時， $N\text{-epi}$  層便無法完全被空乏，RESURF 現象也就消失，則電壓下降，另外  $N\text{-epi}=3.5\text{e}15$  裡，由於沒 RESURF 現象，耐壓並未隨  $T_{epi}$  有所改變，幾乎為一常數。

#### A.1 比較

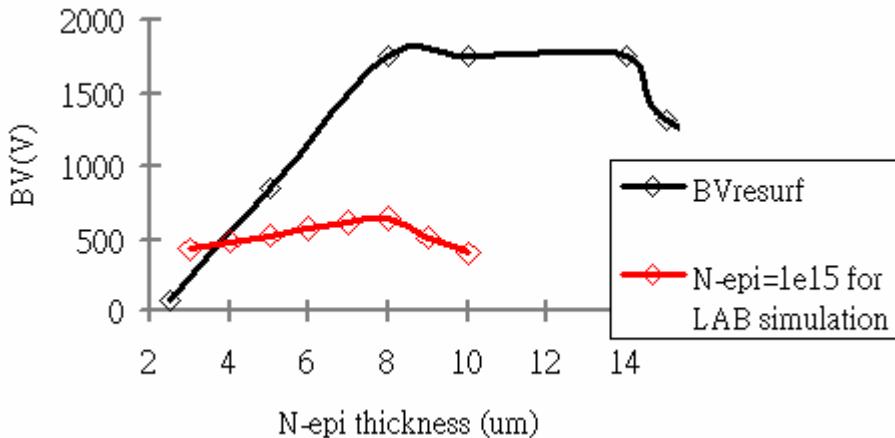

於第三章時，RESURF 原理方面，可以運用推導公式而計算出結果，以得  $N\text{-epi}$  摻雜濃度分佈，所以針對第三章計算結果與模擬做一比較，觀察模擬與計算曲線的趨勢，以圖 4.6 所示。

圖 4.6 計算與模擬比較圖

圖 4.6 中，可以發現 BVresurf 電壓分佈曲線相對於模擬曲線明顯大很多，主要在於崩潰接面的不同，由於 RESURF 計算主要均已接面崩潰為主，沒有考慮到閘極氧化層被打穿而崩潰的問題，所以當  $T_{epi}$  介於 8 到 14um 之間，最高耐壓取決於 N-epi/P-substrate 接面的崩潰電壓，而 BV 值在  $N-epi=1e15$  情況下可以達上千伏，然而以模擬與實際實作而言並無法達到如此理論值，主要由於崩潰點幾乎位於閘極附近不然就是陽極接面，所以大約為 700V 左右，所以在數值上仍需要進一步考量，而在曲線的趨勢方面，在  $T_{epi}=8um$  時，為模擬 BV 值時最佳參考值。

#### B. 掺雜濃度模擬

根據以上尺寸的模擬後，取其耐壓有達到 700V 的範例，其  $Ao=2.5um$ 、 $Po=2um$ 、 $Ld$  分別為 68um 與 88um，最後取  $T_{epi}=8um$  做濃度上的調變與模擬。

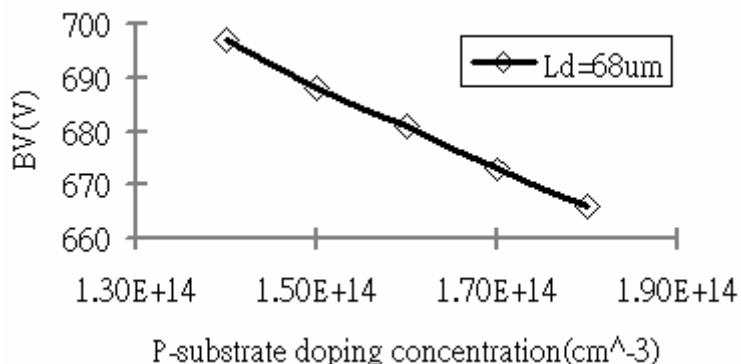

圖 4.7 基底掺雜濃度與耐壓關係圖

在圖 4.7 中，當基底摻雜濃度越高時，BV 值也會下降，主要在於低摻雜濃度時，對於 Psubstrate 區域逆偏空乏區的延伸較大，相對下電場面積積分也會較大，耐壓也就提升，不過由於這次實作上主要以摻雜為  $1.78e14$  的晶圓為主，所以在日後模擬還是主要以  $P\text{-substrate} = 1.78e14$  為主，不再加以討論。

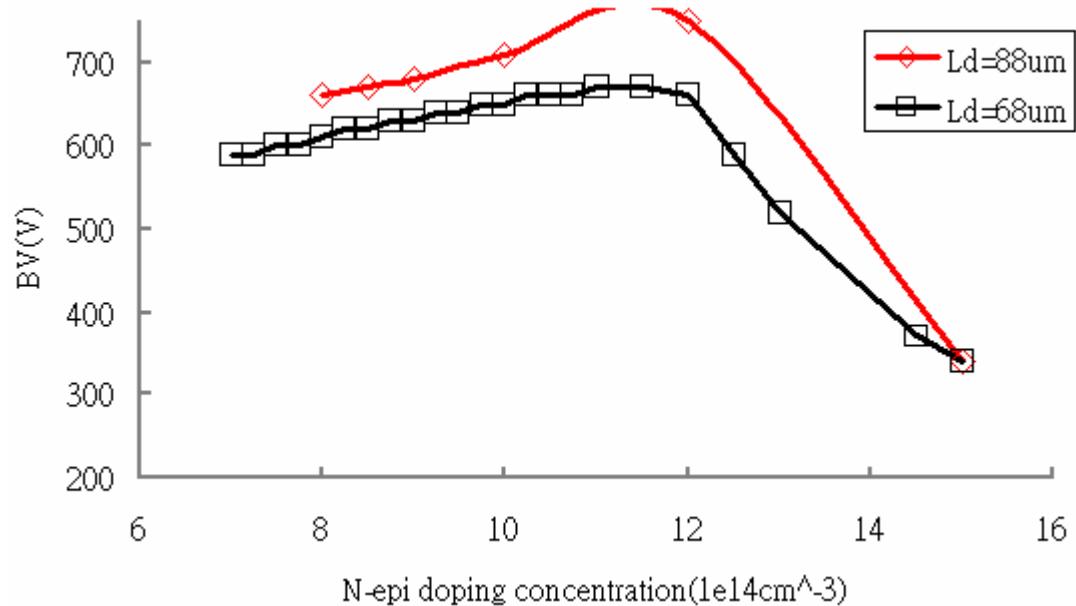

圖 4.8 N-epi 摻雜濃度與耐壓關係圖 (LAB input file)

在圖 4.8 中，以 N-epi 層摻雜濃度作為變數觀察 BV 值曲線關係，在  $Ld=68\text{um}$  時，N-epi 濃度為  $8e14\sim12e14$  時，BV 值為最高點，不過大約卻只有  $600\text{V}$  左右，就元件形成 RESURF 現象而言，增加  $Ld$  長度，加大電場積分，可以得到更高的耐壓，所以在  $Ld=88\text{um}$  時，摻雜濃度為  $10e14\sim12e14$  時可以大於  $700\text{V}$ ，不過在這樣的清況下，除了漂移區長度過大外，在耐壓曲線方面，變化率過大，於製程上的變動也會添增許多變異，是需要多注意與改善的地方。

### B.1 比較

相同情況下，針對第三章 N-epi 層摻雜濃度計算結果，與模擬圖形做一比較，觀察理論與模擬趨勢是否有相異之處。以圖 4.9 所示。

圖 4.9 計算與模擬比較圖

在圖 4.9 中，RESURF 計算耐壓結果在最高點仍為 N-epi/P-substrate 接面崩潰電壓，所以其值較高，而對於趨勢而言，在 N-epi 濃度大於  $1.2\text{e}15$  時，N-epi 層空乏區的延伸較為困難，所以 RESURF 現象難以形成，導致電壓下降，這點在計算結果與模擬 BV 值都是相同的趨勢，代表理論公式有符合模擬的地方。

綜合以上討論，在使用實驗室輸入檔 (LAB input file) 部分，得到耐壓大於 700V 的情形，以表 4.2 所示。

表 4.2 實驗室輸入檔模擬參數取得表

|                   |         |

|-------------------|---------|

| P-substrate layer | 1.78e14 |

| N-pei layer       | 1e15    |

| Tepi              | 8um     |

| Ao                | 3um     |

| Po                | 2um     |

| Ld                | 88um    |

## 4.2 模擬結果 (FAB 輸入檔)

沿用園區某家半導體製程公司的 100V/0.5um 製程流程，模擬 LIGBT 元件製程，作為實作上參考資料，其中在 Tsuprem4 的輸入檔部分，由 FAB 廠商提供，元件模擬亦於公司內部完成，此為更確定實作的可行與成功性，需要進行更接近製程的模擬，而在公司內也有本身模擬的程式，將運用於本實驗，以比較出不同製程輸入檔上元件的差異。

### A. 尺寸模擬

在 Ao 與 Po 的選擇上仍與實驗室輸入檔模擬一樣，分別選擇 2.5um 與 2um，給予空乏區邊緣的延伸，不會因為空乏形成邊緣曲率過小，導致電力線擁擠而接面電場提早崩潰。

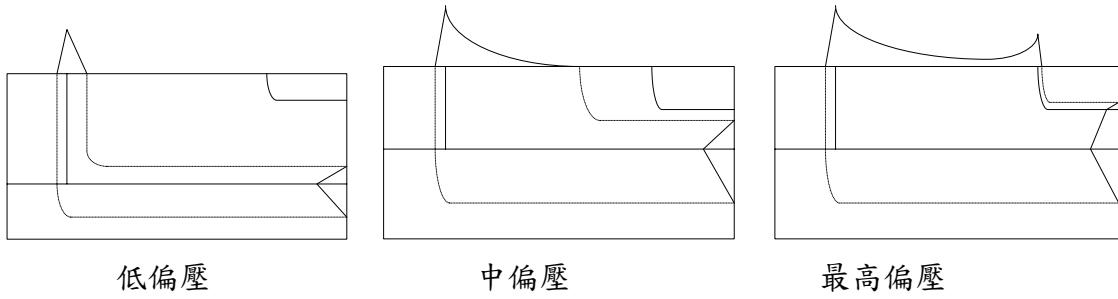

圖 4.10 N-epi 層厚度與耐壓關係圖 (FAB input file)

在圖 4.10 中，耐壓幾乎以  $Tepi=10\text{um}$  為分水嶺，前半區段  $BV$  值與  $Tepi$  近似線性正比，屬於 RESRUF 現象表現，耐壓會隨著空乏區內電場面積積分變大而  $BV$  值變大，曲線為近似線性，而後半段耐壓幾乎以二次函數下降，乃因 N-epi 厚度過大，不易被空乏，其 RESURF 隨著 N-epi 厚度變大而更難以形成，所以耐壓急速下降。而在當  $Tepi=10\text{um}$  時，其  $BV$  值可以大於 700V，為日後模擬與實作時重要參數，不過仍要注意的地方在於當  $Tepi$  大於 10um 時，耐壓會快速下降，設計時應當避免位於這一區間。

圖 4.11 Ld 與耐壓關係圖 (FAB input file)

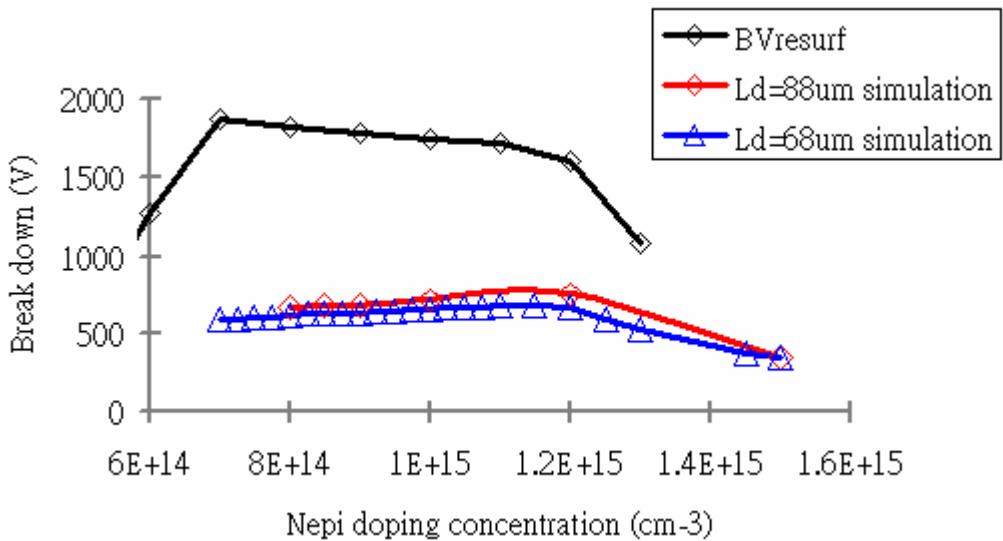

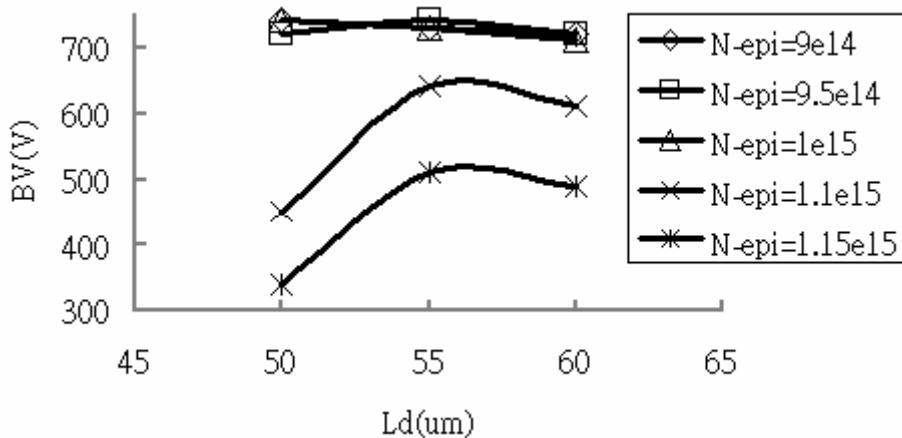

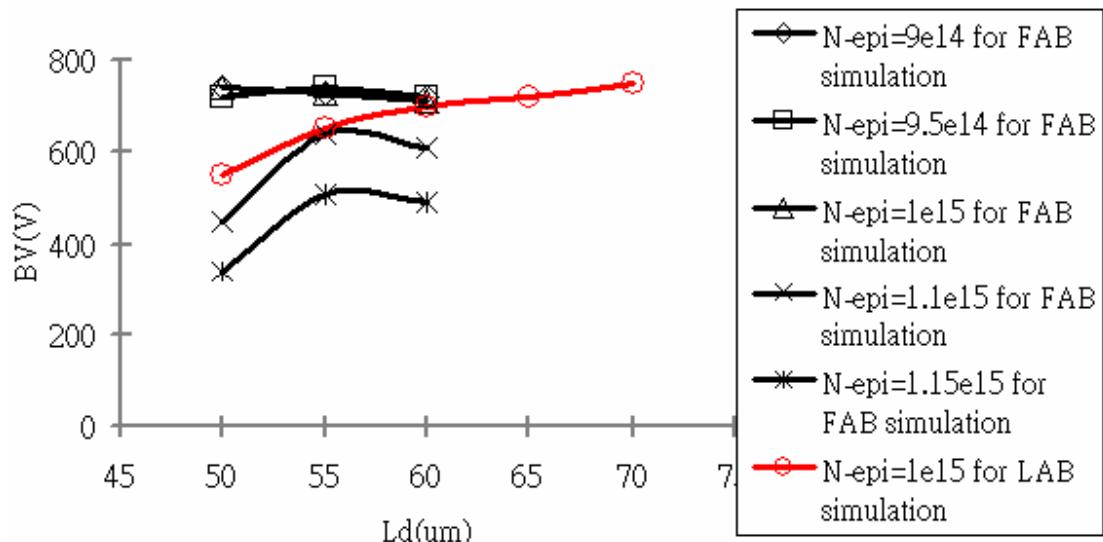

在圖 4.11 中，除了以  $L_d$  為變數外，另外取樣五種  $N$ -epi 摻雜濃度，作為觀察重點，首先可以發現，當  $N$ -epi 層摻雜濃度大於  $1e15$  時，雖有 RESURF 現象的發生，卻會因為接面摻雜濃度梯度過大，導致電場過大，而接面提早崩潰，所以  $BV$  值均偏低，而在  $BV$  值可以大於  $700V$  的範例中，其  $N$ -epi 摻雜濃度介於  $9e14$  與  $10e14$  之間，而且在  $L_d$  的影響並不大，這些可以作為日後模擬與實作的重要參考數值。

#### A.1 比較

在 FAB 輸入檔的模擬結果上，依舊比對之前理論公式計算結果，觀察其  $BV$  值曲線趨勢圖。

圖 4.12 計算與模擬比較圖 (FAB input file)

在圖 4.12 中，擷取第三章厚度與耐壓計算的結果圖，加入模擬  $BV$  值曲線，

可以發現，耐壓依舊沒有理論計算上來的高，不過在趨勢方面，在計算與模擬的 BV 值幾乎為一近似曲線，當 N-epi 厚度小於 10um 時，元件會有 RESURF 現象，所以耐壓以近似線性上升，BV 值與空乏區面積大小成正比，而當 N-epi 厚度到達大於 10um 之後，N-epi 區不易被完全空乏，RESURF 現象不易產生，耐壓也成近似二次函數下降，所以在模擬上，可以證明公式的正確性，也說明了公式裡二次函數的曲線趨勢。

## B. 掺雜濃度模擬

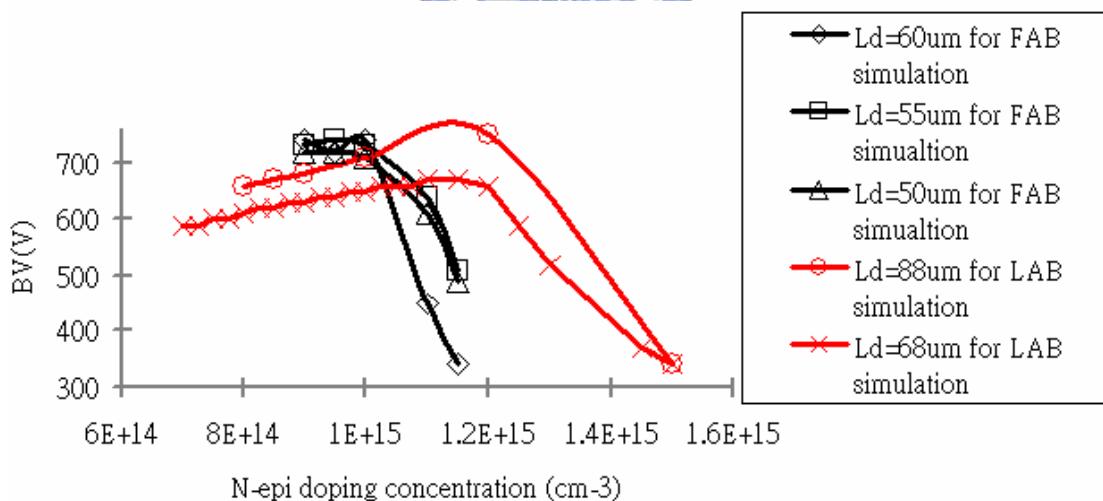

圖 4.13 N-epi 濃度與耐壓關係圖 (FAB input file)

在圖 4.13 中，可以發現在  $L_d$  介於 50um 與 60um 之間，以及 N-epi 掺雜濃度介於  $9e14$  與  $10e14$  之間，其 BV 值大於均可以 700V，這段區間可作為日後模擬與實作上重要參考數據。

### B.1 比較

圖 4.14 計算與模擬比較圖 (FAB input file)

於第三章理論計算結果裡，N-epi層會有一段區間摻雜濃度維持一定的耐壓，然後分別在濃度大與濃度小的時後，BV 值會下降，在圖 4.14 模擬與計算比較圖裡，可以發現模擬結果也是有這樣的趨勢，不過由於模擬時間有限，在此不討論濃度過小時的趨勢，卻是可以推測其耐壓也會下降，所以在未來的模擬與實作上只需要取濃度較高，BV 值又可大於 700V 的區間即可。

綜合以上模擬結果討論，可以得到未來在實作上可以參考數據，接著只需要做兩套輸入檔的比較，規劃出最佳化數值。

## B.2 比較 LAB input file 與 FAB input file

圖 4.15 N-epi 厚度與耐壓比較圖

在圖 4.15 中，當  $\text{Tepi}$  小於 8um 時，於兩套輸入檔製程所模擬出來的耐壓對

應厚度的曲線幾乎相同，然而在實驗室輸入檔模擬耐壓方面卻無法大於 700V 就開始下降，主要原因在於場氧化層的形成形狀問題，在 FAB 輸入檔模擬裡，可以形成鳥嘴形狀，以分散電場分佈，降低接面提早崩潰，而在實驗室的輸入檔模擬裡，場氧化層由於撰寫的問題，無法完全符合實際製程過程而形成鳥嘴形狀，接面也就提早崩潰，在此就場氧化層做一圖形說明，以圖 4.16 所示。

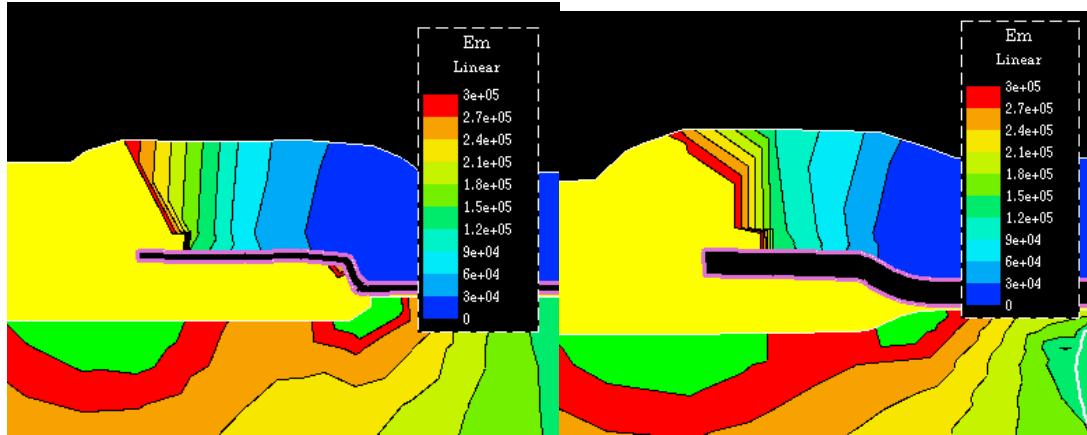

圖 4.16 LAB 與 FAB 輸入檔製程結構比較圖

由圖 4.16 中，可以發現兩個輸入檔所製程的氧化層截然不同，左邊為實驗室輸入檔，右邊為 FAB 輸入檔，以實驗室輸入檔而言，於閘極附近氧化層形狀並非電場擁擠效應較小的鳥嘴形狀，而在 FAB 輸入檔所製程的元件結構上，有鳥嘴效應，對於電場分佈有分散的效果，所以在耐壓呈現較高。因此在程式撰寫方面，應與實際製程設備相對，在爐管溫度、退火時間等，都應與模擬程式有所相同。

圖 4.17 Ld 與耐壓的比較圖

在圖 4.17 中，LAB 輸入檔模擬需要更大的漂移區長度才能到達 700V，除了面積損失不少外，對於導通電阻的增加亦是一大缺點，所以在實作上仍以長度較短的漂移區為主。

圖 4.18 N-epi 摻雜濃度與耐壓比較圖

在圖 4.18 裡，以 BV 值的分佈曲線而言，實驗室輸入檔模擬結果依舊需要較長的漂移區才能到達 700V，而且曲線變異過大，所以如果以此輸入檔作為實際製程的話，由於製程溫度變異或是其他變異因素影響，實作較為不理想。綜合以上兩套模擬比較，主要取其較為接近實際的 FAB 輸入檔為主。

### B.3 表格比較

在這兩套輸入檔討論與模擬結果後，主要以 BV 值大於 700V 條件下，取其參數作為未來實作的規劃，並建一表格做一比較，以表 4.3 所示

表 4.3 實驗室與公司輸入檔比較表格

| 名稱          | VIS input file 實作參數     | LAB input file 實作參數     |

|-------------|-------------------------|-------------------------|

| Ao          | 3um                     | 3um                     |

| Po          | 2um                     | 2um                     |

| Tepi        | 10um                    | 8um                     |

| Ld          | 50~60um                 | 大於 88um                 |

| N-epi       | 1e15cm <sup>-3</sup>    | 1e12cm <sup>-3</sup>    |

| P-substrate | 1.78e14cm <sup>-3</sup> | 1.78e14cm <sup>-3</sup> |

### 4.3 下線規劃模擬

在下線規劃過程中，主要以 LIGBT 耐壓達 700V 為前提，在利用 P-base、P-iso 以及 N-buffer 層做參數調變，希望可以得到一個導通電流高以及耐壓達 700V 以上的 LIGBT 元件。以表 4.4 做一說明，其中陰影地方為新加入摻雜層。

表 4.4 各層實作摻雜與厚度

| 各層名稱              | 摻雜濃度        | 厚度    |

|-------------------|-------------|-------|

| P-substrate layer | 1.78e14     | 90um  |

| P-iso layer       | 6e17~1e18   | 12um  |

| P-base layer      | 2e16~8e16   | 3um   |

| N-epi layer       | 1e15        | 10um  |

| N-buffer layer    | 8e16~1.5e18 | 3um   |

| N+/P+ layer       | 1.5e18      | 0.5um |

綜合前兩節模擬結果後，固定其 P-substrate、N-epi 與 N+/P+層，再加入可以增加電流與維持耐壓的 P-iso、P-base 以及 N-buffer 層，表格數值範圍為實作想要的摻雜濃度範圍。接著定義這次下線的光罩檔以表 4.5 所示

表 4.5 下線光罩規劃

| 編號    | 漂移區長度<br>(Ld) | 通道長度<br>(L-channel) | 閘極覆蓋長度<br>(Po) | 陽極覆蓋長度<br>(Ao) |

|-------|---------------|---------------------|----------------|----------------|

| MASK1 | 60um          | 3um                 | 2um            | 3um            |

| MASK2 | 60um          | 1.5um               | 2um            | 3um            |

| MASK3 | 55um          | 3um                 | 2um            | 3um            |

| MASK4 | 50um          | 3um                 | 2um            | 3um            |

| MASK5 | 50um          | 1.5um               | 2um            | 3um            |

| MASK6 | 50um          | 1.5um               | 2um            | 2um            |

在光罩規劃方面，主要仍以漂移區長度 (Ld) 為變數，另外加入通道長度調變，用於觀察導通電流 (Ic) 與臨界電壓 (Vth) 變化。

表 4.6 下線製程規劃

|          |        | #1 | #2 | #3 | #4 | #5 | #6 | #7 | #8 | #9 | #10 | #11 | #12 |

|----------|--------|----|----|----|----|----|----|----|----|----|-----|-----|-----|

| P-iso    | 6e17   | v  | v  | v  |    |    |    | v  | v  |    | v   | v   |     |

|          | 1e18   |    |    |    | v  | v  | v  |    |    | v  | v   |     |     |

| N-buffer | 1.5e18 | v  |    |    | v  |    |    | v  |    |    |     |     |     |

|          | 1.5e17 |    | v  |    |    | v  |    | v  | v  | v  | v   | v   |     |

|          | 8e16   |    |    | v  | v  |    | v  |    |    | v  |     | v   |     |

| P-base   | 2e16   | v  | v  | v  | v  |    |    |    |    |    |     |     |     |

|          | 6e16   |    |    |    | v  | v  | v  | v  |    |    |     |     |     |

|          | 8e16   |    |    |    |    |    |    | v  | v  | v  | v   |     |     |

根據表 4.5 與表 4.6，作為下線前的光罩與製程規劃，其中在表 4.6 中，規劃出 12 道製程，以調變 P-iso、N-buffer 以及 P-base 摻雜濃度。接著根據所規劃光罩與製程，模擬出 BV 值、Ic 與 Vth。

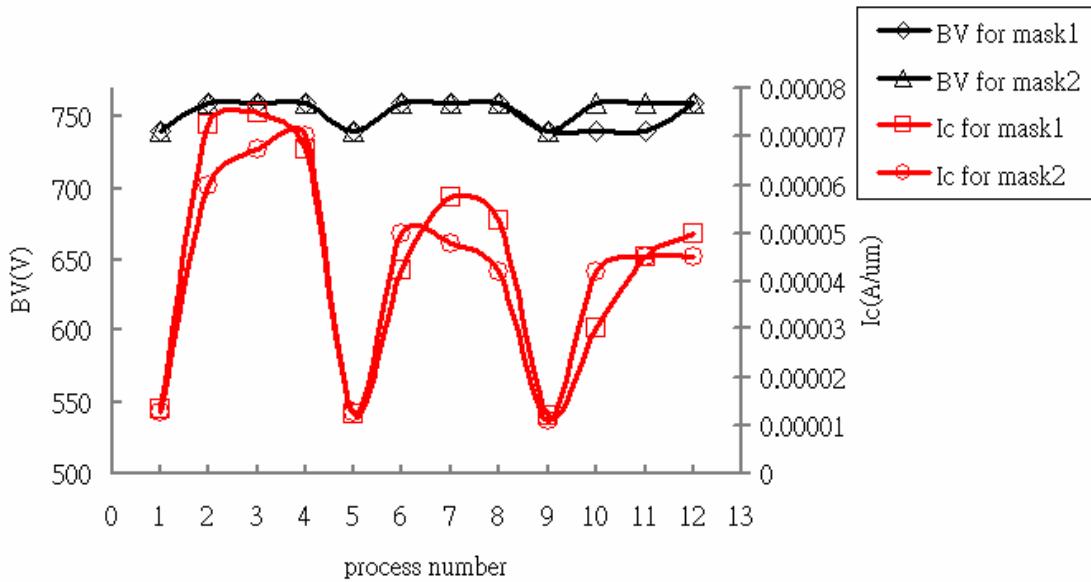

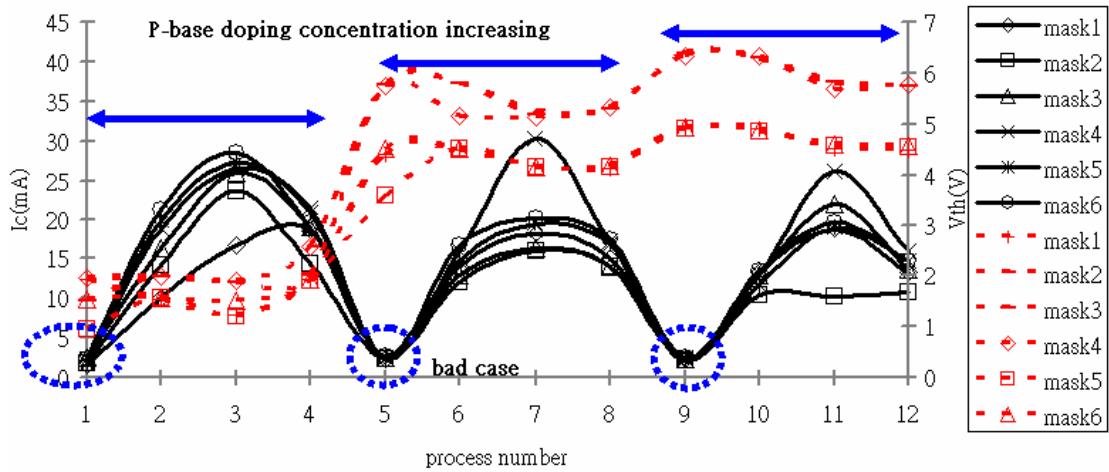

圖 4.19 實作前之模擬 BV 值與 Ic 結果圖

圖 4.19 是由表 4.6 所規劃的製程參數模擬出來波形圖，這兩個光罩耐壓均可以大於 700V，而電流以製程數為 1 到 4 的電流為最高。接著利用世界先進公司提供晶片下線，實作出 LIGBT 元件後，再與模擬結果做一比較，以便日後研發功率 LIGBT 元件。

## 4.4 FAB 製程流程

表 4.7 FAB 製程流程表

| 各層流程                  | 摻雜參數調整              | 厚度   |

|-----------------------|---------------------|------|

| Wafer start           | P-substrate:1.78e14 | 90um |

| Sac                   |                     |      |

| MASK# P-iso           |                     |      |

| Piso layer            | P-type:6e17~1e18    | 12um |

| MASK # NBL            |                     |      |

| NBL layer             |                     |      |

| Well drive in for NBL |                     |      |

| MASK# P-iso           |                     |      |

| Piso layer            | P-type:6e17~1e18    | 12um |

| Nepi layer            | N-type:1e15         | 10um |

| Sac                   |                     |      |

| MASK# Sinker          |                     |      |

| Sinker layer          |                     |      |

| MASK# P-iso           |                     |      |

| Piso layer            | P-type:6e17~1e18    | 12um |

| Well drive part1      |                     |      |

| Well drive part2      |                     |      |

| MASK# P-base          |                     |      |

| P-base layer          | P-type:2e16~8e16    | 3um  |

| Sac                   |                     |      |

| MASK# N-buffer        |                     |      |

| Nwell layer           | N-type:8e16~1.5e18  | 3um  |

|                     |                                                                                    |       |

|---------------------|------------------------------------------------------------------------------------|-------|

| Pbase drive in      |                                                                                    |       |

| Pad oxide 200A      |                                                                                    |       |

| Field oxide 5000A   |                                                                                    |       |

| Sac                 |                                                                                    |       |

| MASK# HVOX          |                                                                                    |       |

| HVOX layer          |                                                                                    |       |

| MASK# poly oxide    |                                                                                    |       |

| Gate oxide          |                                                                                    | 420A  |

| MASK# N+/P+         |                                                                                    |       |

| LDDN and LDDP layer |                                                                                    |       |

| S/D layer           | P-type and N-type:1.5e18                                                           | 0.5um |

| BPSG flow           |  | 2um   |

| MASK# contact       |  | 2um   |

| Contact etch        |  |       |

| MASK# metal         |  |       |

| METAL layer         |                                                                                    |       |

## 第五章實作與量測

本章就 LIGBT 在實作上的量測，以各項參數做討論，包括元件崩潰電壓(BV 值)、導通電流(I<sub>c</sub>)與元件臨界電壓(V<sub>th</sub>)。另外也綜合了第二章的元件定義，第三章基本尺寸與 N-epi 層摻雜濃度計算以及第四章元件各參數模擬後，利用 Cadence 製作光罩軟體，規劃元件光罩，配合半導體公司高壓製程技術，開發 LIGBT 功率元件。

### 5.1 元件定義

有關這次實作製程，運用 FAB 原本的 100V/0.5umVDMOS (vertical DMOS) 製程，在不影響原本光罩數與製程流程下，研發出 LIGBT 結構，於本節討論中，就 LIGBT 下線規劃談起，而在實作方面可分為兩大分面，分別為光罩規劃與製程流程。

#### A. 就光罩而言

以圖 5.1 與表 5.1 顯示本次實驗所用光罩與元件結構圖：

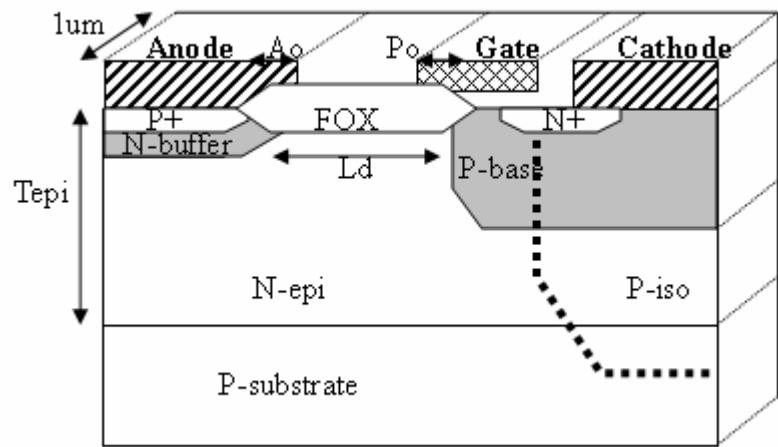

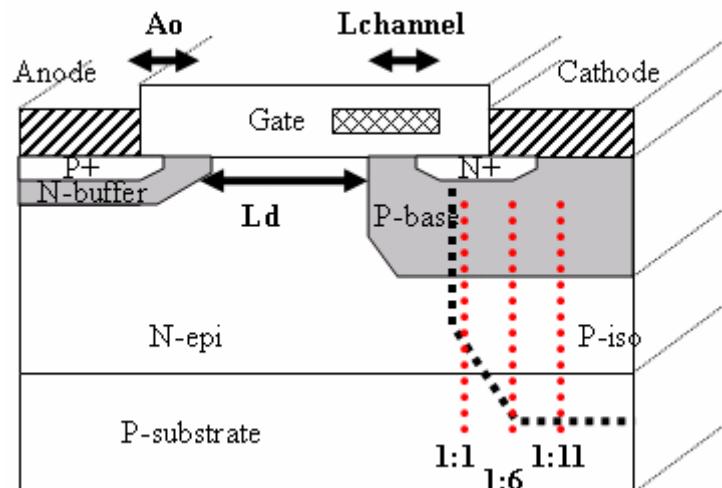

圖 5.1 光罩結構示意圖

表 5.1 實作光罩檔參數表

| 編號    | P-iso 層橫向擴散比率 | 漂移區長度 (Ld) | 通道長度 (L-channel) | 陽極覆蓋長度 (Ao) |

|-------|---------------|------------|------------------|-------------|

| Mask1 | 1:1           | 60um       | 3um              | 3um         |

|       | 1:6           |            |                  |             |

|       | 1:11          |            |                  |             |

| Mask2 | 1:1           | 60um       | 1.5um            | 3um         |

|       | 1:6           |            |                  |             |

|       | 1:11          |            |                  |             |

| Mask3 | 1:1           | 55um       | 3um              | 3um         |

|       | 1:6           |            |                  |             |

|       | 1:11          |            |                  |             |

| Mask4 | 1:1           | 50um       | 3um              | 3um         |

|       | 1:6           |            |                  |             |

|       | 1:11          |            |                  |             |

| Mask5 | 1:1           | 50um       | 1.5um            | 3um         |

|       | 1:6           |            |                  |             |

|       | 1:11          |            |                  |             |

| Mask6 | 1:1           | 50um       | 1.5um            | 2um         |

|       | 1:6           |            |                  |             |

|       | 1:11          |            |                  |             |

在圖 5.1 與表 5.1 裡，實作光罩主要規劃出  $6 \times 3$  道，其中除了六道為第四章所提之長度變異外，額外再加入 P-iso 層橫向擴散長度變數，其因在於本實驗運用了原本 100V 的高壓製程，在 P-iso 層的原製程裡主要作為隔離 (isolation) 層

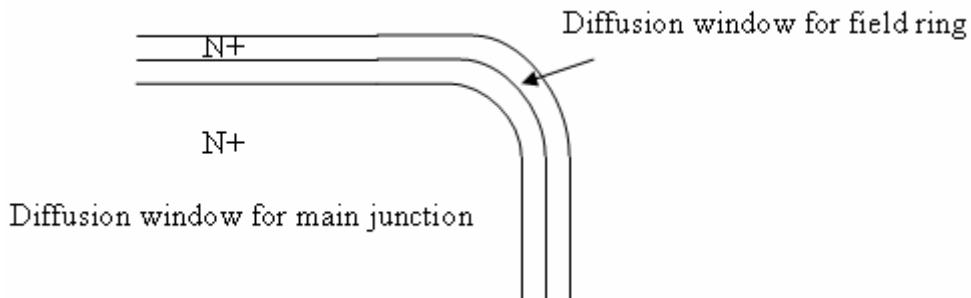

用，而今要運用此層與基底導通，形成空乏區電荷分享 (depletion charge sharing) 效應，所以在製程上，橫向擴散長度方面需要做一調整，以免因為 P-iso 層橫向擴散過長，導致 P-base 層摻雜濃度受到影響，而影響了通道的形成。此時根據公司給予資料，做了初步規劃，橫向擴散比率，以利日後研發依據。另外在光罩形狀方面，規劃出三種形狀，為方形、圓形以及原方形，以圖 5.2 所示

圖 5.2 光罩圖形示意圖（無顏色為開極端）

所以在本次下線總共規劃出  $3 \times 3 \times 6$  道有效光罩，還外加入測試用 LDMOS 光罩有三道，其中，根據邊緣電場擁擠的效應理論下，以圓形光罩在高功率元件在耐壓效能方面呈現較佳，在這次初步開發中，也以此形狀為主，而考慮在後期發展裡，會因為圓形不利於高低壓電路上面積的整合，所以另外規劃方形與圓方形，以利後期研究。

## B. 就製程而言

本次實驗在製程上，基為成本與市場供應問題，晶圓只能固定一批，為 P 區域摻雜且濃度為  $1.78 \times 10^{14} \text{ cm}^{-3}$  的晶圓，之前在第三章計算與第四章模擬也均以此濃度為重點。另外在磊晶層 (N-epi 層) 方面，根據第四章最後總結，以 N-epi 層為  $10\text{ }\mu\text{m}$  且摻雜濃度  $1 \times 10^{15} \text{ cm}^{-3}$  為主，其他濃度部分只能靠模擬來得知各濃度上不同所呈現的結果。所以在 P-iso、N-buffer 以及 P-base 層裡，為這次下線的主要重點，給予各摻雜濃度參數，規劃出十二道製程，以下表 5.2 為此次下線製程規劃表。

表 5.2 下線製程規劃表

|          |        | #1       | #2       | #3       | #4       | #5       | #6       | #7       | #8       | #9       | #10      | #11      | #12      |

|----------|--------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| P-iso    | 6e17   |          | <b>V</b> | <b>V</b> | <b>V</b> |          |          |          | <b>V</b> | <b>V</b> |          | <b>V</b> | <b>V</b> |

|          | 1e18   |          |          |          |          | <b>V</b> | <b>V</b> | <b>V</b> |          |          | <b>V</b> | <b>V</b> |          |

| N-buffer | 1.5e18 | <b>V</b> |          |          |          | <b>V</b> |          |          |          | <b>V</b> |          |          |          |

|          | 1.5e17 |          | <b>V</b> |          |          |          | <b>V</b> |          |          | <b>V</b> | <b>V</b> | <b>V</b> | <b>V</b> |

|          | 8e16   |          |          | <b>V</b> | <b>V</b> |          |          | <b>V</b> |          |          |          |          | <b>V</b> |

| P-base   | 2e16   | <b>V</b> | <b>V</b> | <b>V</b> | <b>V</b> |          |          |          |          |          |          |          |          |

|          | 6e16   |          |          |          |          | <b>V</b> | <b>V</b> | <b>V</b> | <b>V</b> |          |          |          |          |

|          | 8e16   |          |          |          |          |          |          |          |          | <b>V</b> | <b>V</b> | <b>V</b> | <b>V</b> |

為了使表 5.2 看起來更簡潔，在單位方面以文字說明，最上一列為製程流程編號，號碼越大也代表在 P-base 摻雜濃度上給予更重摻雜，而在數值上，並非可以利用第三章有理論公式計算，主要在於模擬上的揣摩與公司資料給予參考，才訂出以上濃度的圖表。而除了以上製程流程外，其餘各層參數直以下表 5.3 所示，主要利用第三章與第四章模擬資料所得。

表 5.3 模擬結果參考表

| 名稱          | 摻雜濃度    | 厚度    |

|-------------|---------|-------|

| N-epi 層     | 1e15    | 10um  |

| P+/N+       | 5e18    | 0.5um |

| P-substrate | 1.78e14 | 90um  |

綜合以上光罩與製程，實作出 LIGBT 元件，在量測方面在以下第二節與第三節做一說明與討論。

## 5.2 量測儀器說明與波形圖

在本次開發元件裡，主要針對 LIGBT 三個規格來做一量測，包括：崩潰電壓 (BV)、導通電流 (Ic) 與臨界電壓 (Vth)。量測儀器主要有兩台：波形追蹤器 (cure tracer) 其最高功率為 2000W，與 HP4156 多端元件量測器，其最大限流為 100mA。在耐壓量測以波形追蹤器作為量測，另外在導通電流與臨界電壓則以 HP4156 作為量測。

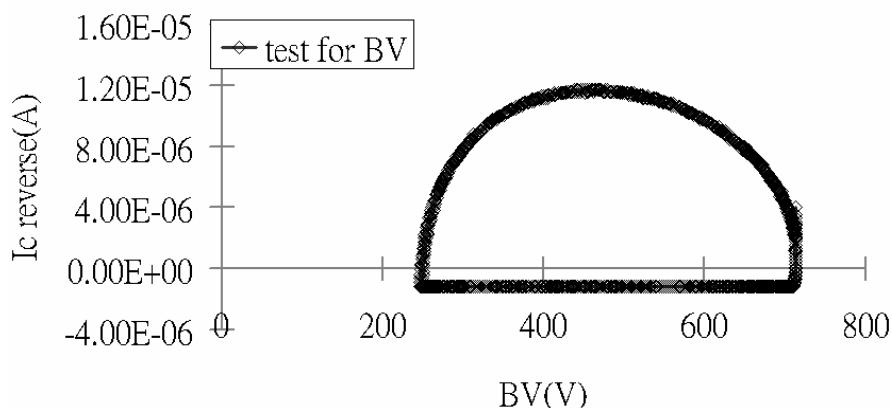

本實驗在量測規格方面，崩潰電壓 (BV) 以元件逆向偏壓在漏電流大於 10uA 時，量測出來定義為崩潰電壓 (BV 值)，在 Ic 電流量測方面則以驅動電壓為 18V，即閘極端電位為 18V，Vac 端電壓以 50mV 漸增做一掃瞄，描繪出電壓與電流波形圖，並取 Vac=3V 作為導通電流量測參考點，最後在 Vth 方面，Vac 紿予 2V，在逐漸加入閘極電壓，做一電壓掃瞄，在此取得計算 GM 程式，定義本實驗之 Vth 為 GM 圖形微分為零之處。以下做圖解說明。

### A. BV 量測圖

就崩潰電壓上，使用波形追蹤器 (cure tracer)，將儀器功率調至最大 (2000W)，量測其輸出波形，以圖 5.3 所示

圖 5.3 BV 值量測波形圖

圖 5.3 表示利用波形追蹤器在量測 BV 值的結果圖，其中為元件電壓與漏電流關係，此範例元件的耐壓可以到 710V，其量測工作為電壓不斷掃瞄，測出漏電流量，當量測電壓大於 710V 時，元件電壓不在隨輸入的測試電壓上升而上升，

到達電壓飽和，此時，漏電流會飆升，若儀器電壓持續上升，龐大的漏電流將使元件接面處燒毀，形成永久性損毀。另外在元件量測與模擬  $BV$  值上截然不同，模擬可以精確算至  $BV$  值有多少伏，然而實際量測時，當測試電壓達到  $BV$  值附近，則元件 P/N 接面容易被穿透，所以在量測上應當注意，不可一次給予過大電壓，以防止元件損毀。

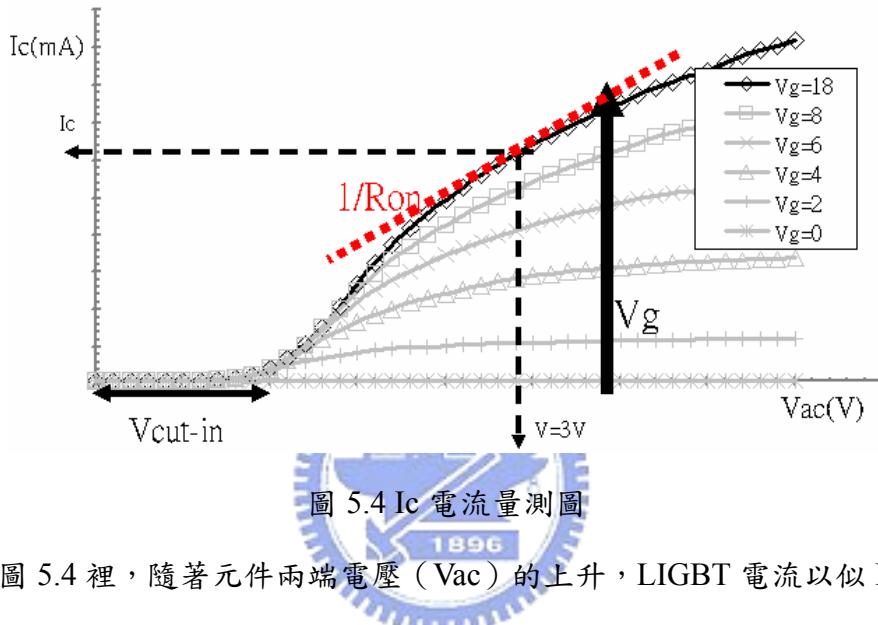

## B. 導通電流 $I_c$ 量測

在圖 5.4 裡，隨著元件兩端電壓 ( $V_{ac}$ ) 的上升，LIGBT 電流以似 BJT 電晶體導通電流，且與閘極電壓成正比，所以為了節省量測時間，在之後的元件量測  $I_c$  方面，皆取其閘極電壓為 18V，而一般功率元件對於電路工作方面，閘極電壓會用低壓電路作昇壓動作來驅動，以提升 LIGBT 抗雜訊的能力，所以在量測的規格上，本實驗定義閘極為 18V 與  $V_{ac}=3V$  時所測得的  $I_c$  值，為本實驗 LIGBT 導通電流規格。而在  $V_{ac}=3V$  處取其電流微分，本實驗定義為 LIGBT 導通電阻倒數，此為特性導通電阻 ( $R_{on,sp}$ ) 計算依據之一，另外可以發現在導通電壓方面，LIGBT 元件必須先承受一個  $V_{cut-in}$  電壓，此為陽極 P+/N-buffer 接面導通之壓降，一般在結構改善上可以使用蕭基二極體代替，以降地此電壓，減少 LIGBT 功率損耗，本實驗並不在結構上多做模擬與討論，有待日研發與改善。

在這次實驗的對照方面，由於 LIGBT 與 LDMOS 功率元件結構上只差在陽極摻雜不一樣，光罩並未有所改變，所以這次下線也加入 LDMOS 對照元件，主

要用於觀察各種元件不同的特性，以便日後研究。

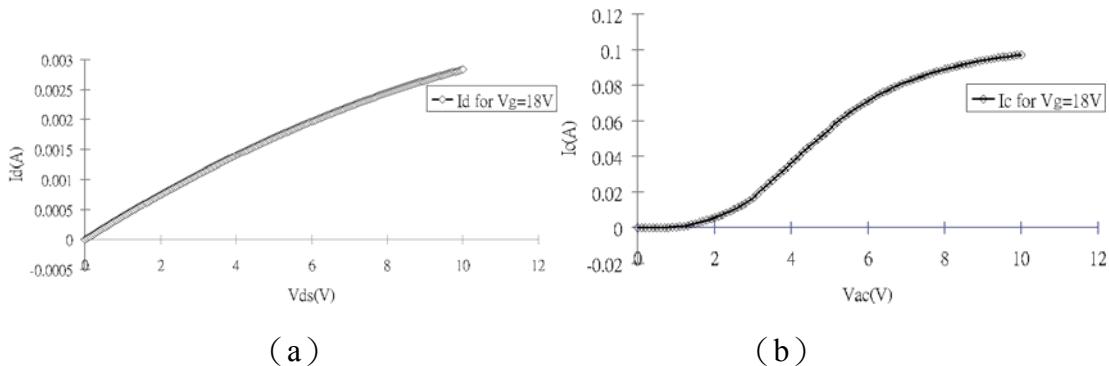

圖 5.5 (a) LDMOS 與 (b) LIGBT 電流比較圖

在圖 5.5 裡，觀察 LIGBT 與 LDMOS 兩種元件上電流曲線的不同，其中最大的差別在於，第一，LIGBT 電流明顯大於 LDMOS，其因在於 LDMOS 並沒有 BJT 電流放大問題，第二，LDMOS 並無  $V_{cut-in}$  電壓功率損耗較小。然而兩者除了在電流與  $V_{cut-in}$  上，因為 LIGBT 有少數載上殘留問題，所以導致頻率下降，這兩者元件應用於產品上也是有所不同，此處在於第一章有粗略的比較。

### C. 臨界電壓 $V_{th}$ 量測

圖 5.6  $V_{th}$  量測圖

在圖 5.6 裡，臨界電壓 ( $V_{th}$ ) 量測方面，運用 GM 電導計算，在電流微分方面取其等於零之處，此定義為本實驗之  $V_{th}$  值，以圖 5.5 所示。一般功率元件臨界電壓不可太低，不過在高  $V_{th}$  值的情況下，通道變小，導致導通電子流量也縮小，所以在電流表現方面便下降不少，因此在抗雜訊與導通電流量方面，需要做一考量，而一般  $V_{th}$  的值最好介於 3~5V 內。

### 5.3 LIGBT 量測結果與討論

本節分別就這次下線所給予變數做一討論，由於元件量測點相當多，如果一一列出的話顯著複雜，因此以有系統挑選量測點，與依序步驟作以下討論。

#### A. P-iso 層横向擴散比率

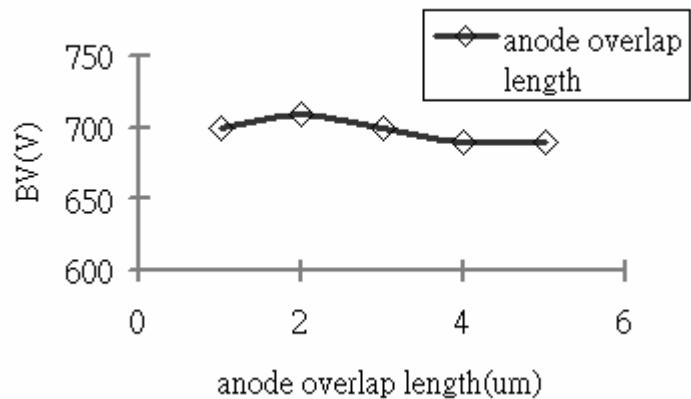

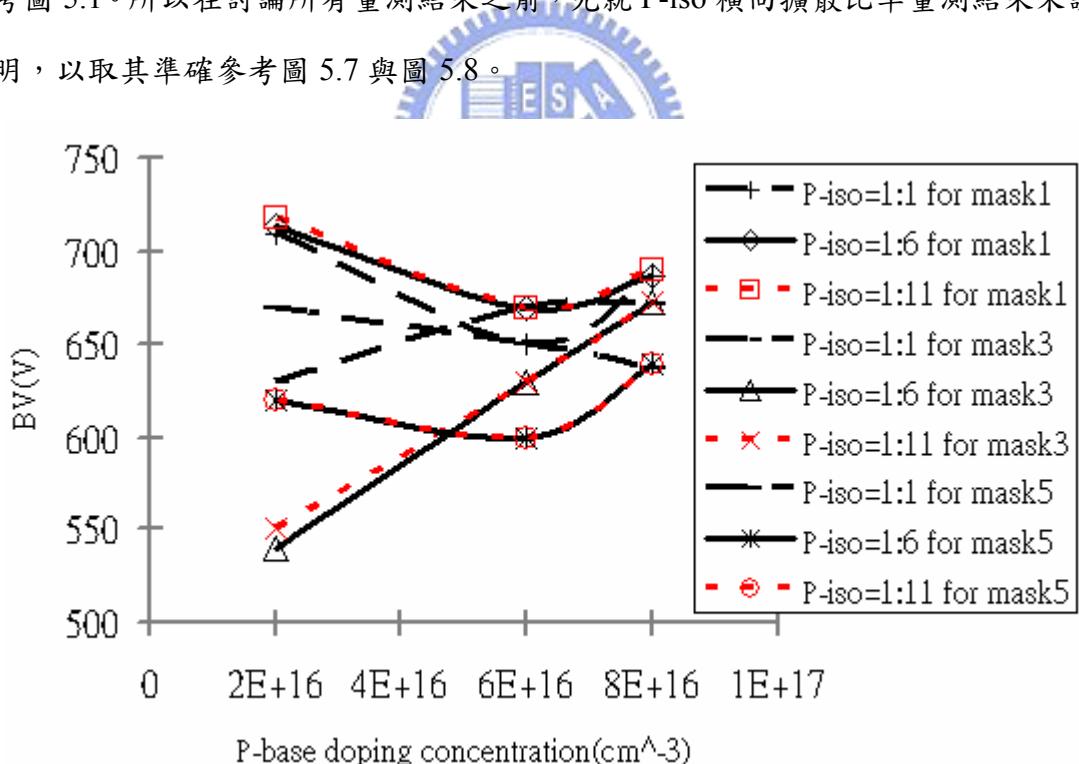

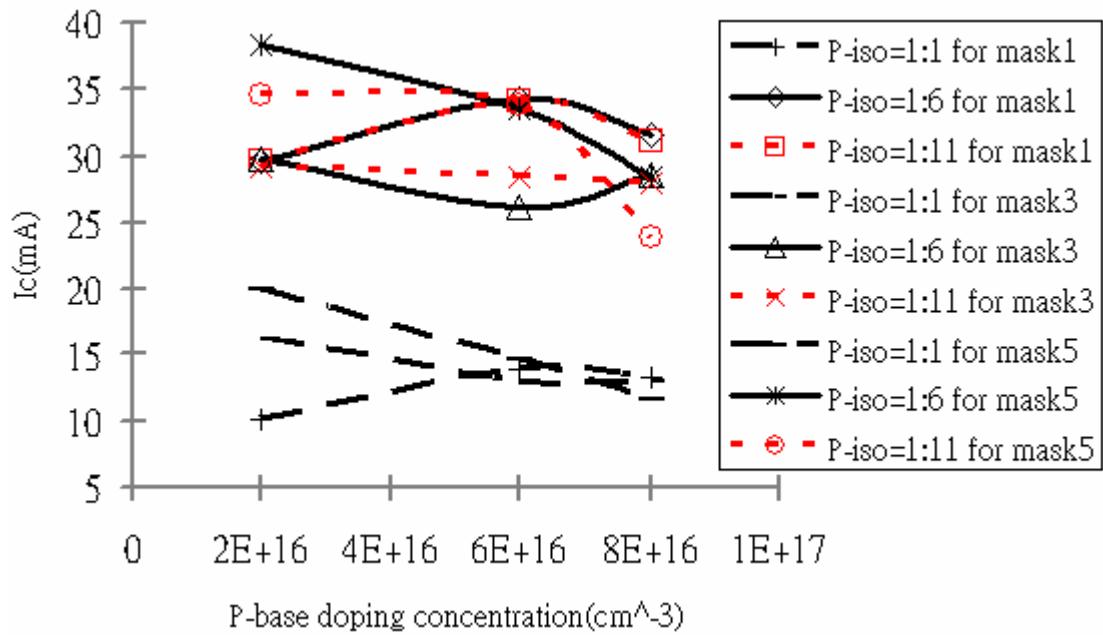

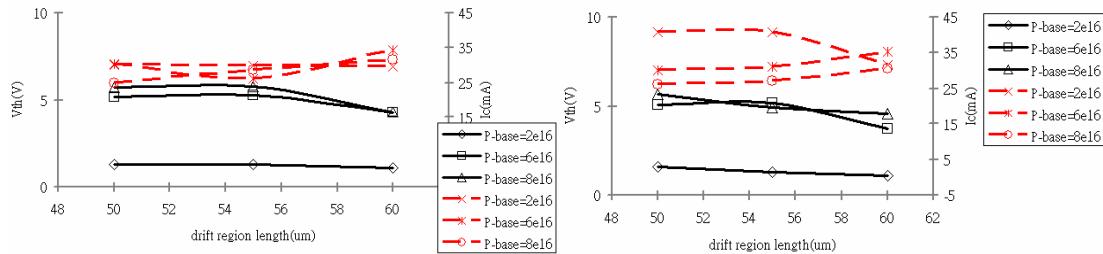

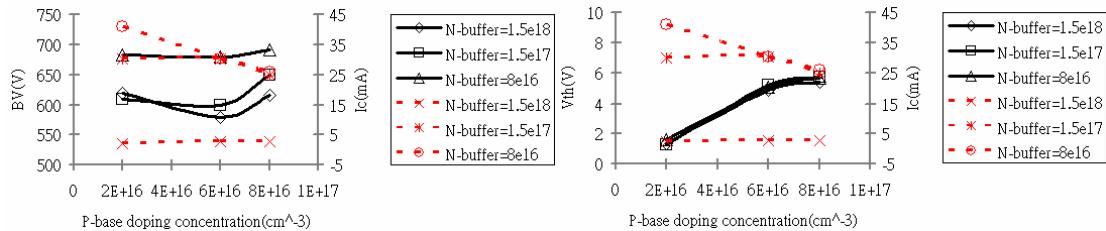

在討論各量測參數之前，首先討論 P-iso 光罩長度變化，在製程裡，由於爐管溫度變異、或是製程上變異的誤差影響，在横向長度擴散方面影響極大，此次實驗由於運用 FAB 公司原本的 100V 製程，在 P-iso 長度取得方面資料有限，於模擬上，擴散長度為其 1：1，為了顧及設計完整性，P-iso 層除了原本的 1：1 的比率外，另外加入 1：6 與 1：11 等比率，除了對於日後 LIGBT 研發製程上比較有參考的價值外，也提高了模擬與實作的準確性，相關這層的結構圖，可以參考圖 5.1。所以在討論所有量測結果之前，先就 P-iso 橫向擴散比率量測結果來說明，以取其準確參考圖 5.7 與圖 5.8。

圖 5.7 各 P-iso 橫向擴散比率與 P-base 摻雜濃度電壓關係圖

圖 5.8 各 P-iso 橫向擴散比率與 P-base 摻雜濃度電流關係圖

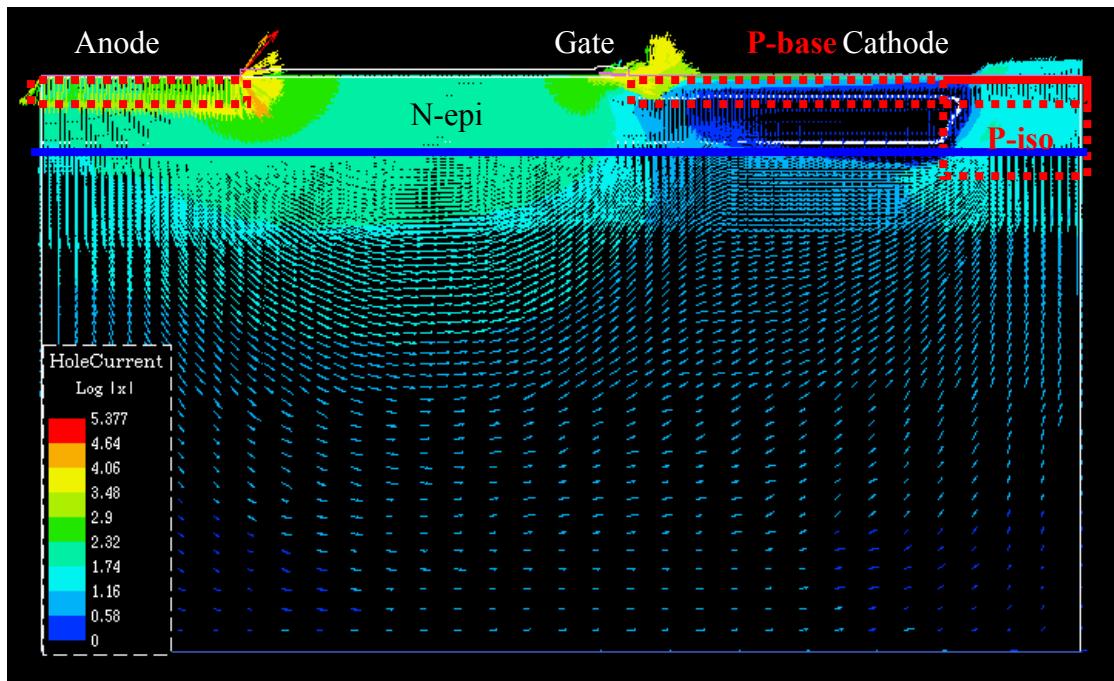

在圖 5.7 與圖 5.8 裡，取樣三種光罩於 BV 值與 Ic 分佈，發現 P-iso 比率為 1:6 與 1:11 的 BV 值分佈曲線幾乎一樣，而在比率為 1:1 方面，則與另兩段曲線有所出入，主要乃因 P-iso 層橫向擴散過多，影響了形成通道的 P-base 層，相對也影響到了  $V_{th}$ ，使其臨界電壓變大，導致導通通道變小，如此一來，不只在耐壓上有影響外，於電流方面也降低不少，換言之在 P-iso 層橫向擴散比率為 1:1 的導通電流與其他兩種比率的要小很多，因此以 100V/0.5um 高壓製程而言，日後在實作 P-iso 橫向擴散長度比率最好介於 1:6 與 1:0.75 之間，這點為模擬上有所誤差的地方，往後需要多加注意，另外，在電流關係圖中，其比率為 1:11 比 1:6 的電流大致要小一點，有關這方面說明主要在於電流路徑上的改變。以下圖 5.9 與 5.10 做說明。

圖 5.9 P-iso 橫向擴散比率為 1:6 電洞流圖

圖 5.10 P-iso 橫向擴散比率為 1:11 電洞流圖

在圖 5.9 與圖 5.10 裡，由於 N-epi/P-iso 接面有位障關係，N-epi 層內的電流並不會直接流經此接面，而是經由電子通道流經電子於 N-epi 層內做復合電流，然而在縱向 PNP 電晶體仍有一小部分放大電流，經由 P-substrate 層流至 P-iso，此時由於 P-iso 橫向擴散比率為 1:6 的電阻較小，導通電流會比比率為 1:11

來的大，其  $I_c$  電流才會比較大一點點，不過按照這樣推理，應該是 P-iso 橫向擴散比率為  $1:1$  較大，不過因為其 P-iso 橫向擴散過渡，導致 P-base 通道難以形成，通道電子電流過小，整體導通電流嚴重下降。以圖 5.11 所示。

圖 5.11 P-iso 橫向擴散比率為  $1:0.75$  電洞流圖

在圖 5.11 清楚發現，雖然陰極端擁有一大片重摻雜的 P-iso 層，卻因通道導通過小，電子流經不易，造成整體元件電流下降。經由以上討論，對於以下量測關係圖，均已較為 Piso 較為精確的橫向擴散比率  $1:6$  做說明，對於日後研究其量測數據也較為準確。

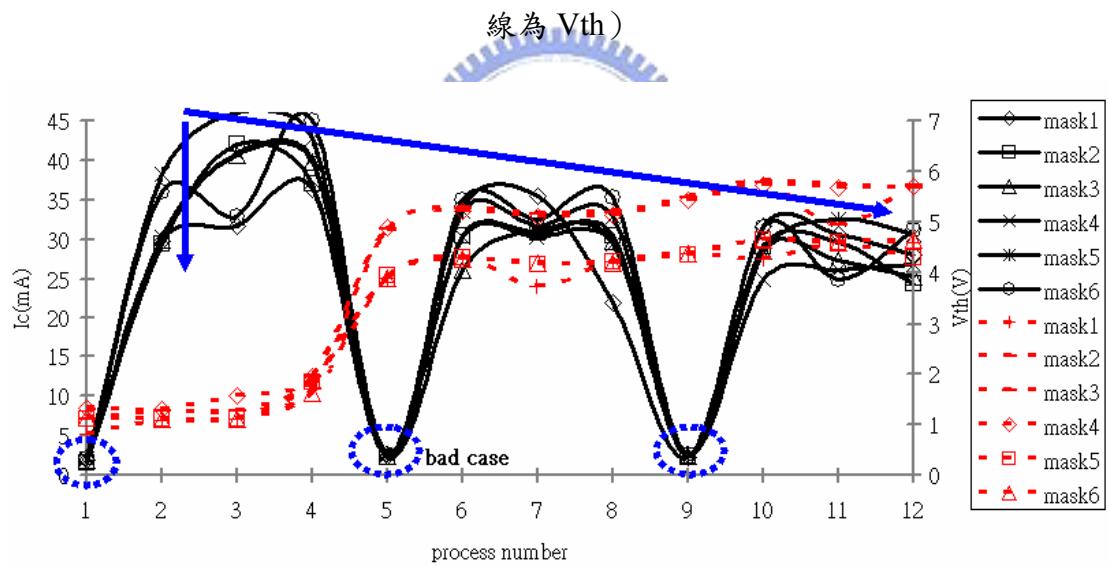

## B. 各製程數量測

首先，以製程順序為橫軸，BV 值為縱軸，根據六個光罩，描繪出圖 5.12 耐壓關係圖。分別討論 P-iso 橫向擴散比率為  $1:1$  與  $1:6$ 。

圖 5.12 P-iso 橫向擴散比率為 1 : 0.75 耐壓與製程順序關係圖

由於製程順序主要關係到 P-base 摻雜濃度大小，可以參考製程規劃表 5.2，所以在圖 5.12 橫軸以製程順序為主，摒除不好的範例，也就是圖中的 bad case，製程數為 1、5、9 的不考慮，其電壓隨著 P-base 摻雜濃度往上升，主要因為其 P-base 層濃度在 P-iso 橫向擴散比率為 1:1 中，影響了原本摻雜濃度，與模擬有所不同，至於有關 bad case 主要因為是由於 N-buffer 層的濃度過大，造成接面濃度梯度過大，電場容易崩潰，BV 值表現相當不理想。

圖 5.13 P-iso 橫向擴散比率為 1 : 6 耐壓與製程順序關係圖

在圖 5.13 中，BV 值與模擬大致符合，呈現近似水平的曲線，而綜合以上二圖，不管 P-iso 橫向擴散比率為 1:1 或是 1:6，其 N-buffer 層的摻雜濃度均

不可過大，此 bad case 在模擬上就可以觀察到了，在此更是運用實作上來驗證。

接著就  $I_c$  與  $V_{th}$  關係圖來做討論。

圖 5.14 P-iso 橫向擴散比率為 1:1 之導通電流、 $V_{th}$  與製程順序關係圖（其中虛

圖 5.15 P-iso 橫向擴散比率為 1:6 之導通電流、 $V_{th}$  與製程順序關係圖

比較圖 5.13 與圖 5.14，如同之前所討論過，P-iso 層橫向擴散比率為 1:1 在導通電流的表現方面，略顯不足，摒除 bad case 不談，明顯圖 5.14 的導通電流均大於圖 5.13，而且在  $V_{th}$  的表現上，圖 5.14 較為平穩，不像圖 5.13 變動那麼大，造成電流不穩定，除此之外，由於 P-iso 橫向擴散比率為 1:1 的範例裡，在通道與 N-epi 層接觸地方，會有電流擁擠問題，也是圖 5.14 電流大於圖 5.13 電流的主要原因之一。

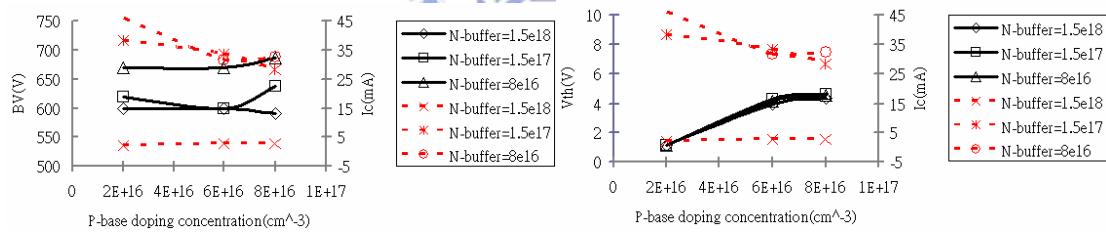

### C. 漂移區長度 (Ld) 討論

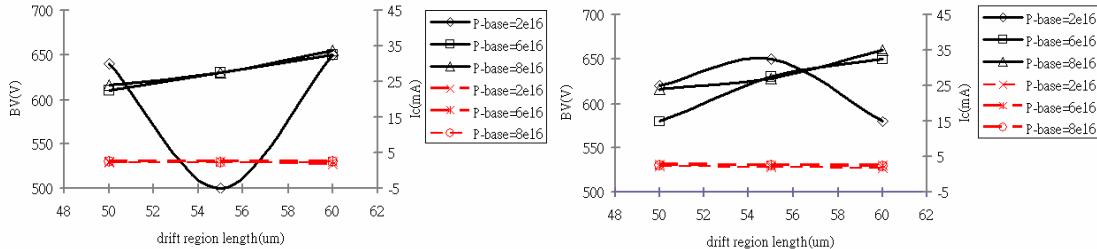

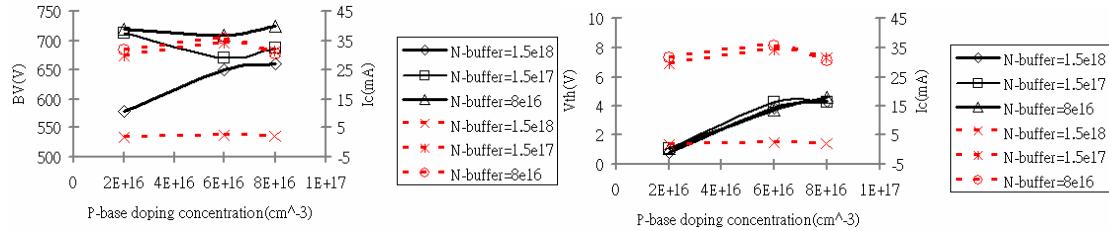

接下來針對不同的 N-buffer 層摻雜濃度下，以漂移區長度作為橫軸變數，做詳細討論。

#### C.1 N-buffer=1.5e18

圖 5.16 P-iso=1:1

P-iso=1:6 (虛線為 Ic)

在圖 5.15 裡，除了  $P\text{-base}=2\text{e}16$  這樣摻雜濃度外，其 BV 值與  $Ld$  大致上成正比，然而由於 N-buffer 層摻雜的濃度過大，導致  $P+/N\text{-epi}$  接面的少數載子擴散電流過小，換言之在 PNP 電晶體的  $\beta$  過低，幾乎沒有 BJT 電流放大的效果，所以在這樣的 N-buffer 層摻雜濃度是未來設計上需要避免的地方。

#### C.2 N-buffer=1.5e17

圖 5.17 P-iso=1:1

P-iso=1:6 (虛線為 Ic)

在圖 5.16 中， $P\text{-iso}$  層橫向擴散比率為 1:6 的導通電流，明顯大於比率為 1:1 的，與之前範例相同地方，除了  $P\text{-base}=2\text{e}16$  的摻雜濃度  $BV$  值與  $Ld$  並非成正比外，其餘兩種  $P\text{-base}$  摻雜濃度均與  $Ld$  大致成正比，另外需要觀察的地放在於導通電流  $Ic$ ，其導通電流似乎並沒有因為  $Ld$  長度的上升而減小，此乃電流主要與通道大小以及 PNP 電晶體的增益相關，與  $Ld$  較無關係。

### C.3 N-buffer=8e16

圖 5.18 P-iso=1:1

P-iso=1:6 (虛線為 Ic)

在圖 5.17 中，討論最後一種 N-buffer 層摻雜情況下，在 BV 值的表現方面，不管 P-base 層的摻雜濃度為何，均與 Ld 大致上成正比，而且在兩種不同 P-iso 層橫向擴散比率下，其 BV 值也可以達到 700V 以上，所以以本實驗目標而言，屬於成功範例。不過就以上三張圖而言，在 BV 值達規格之後，觀察其導通電流 (Ic) 與 Ld 的變化情形，以圖 5.17 為例，在 P-iso 層比率為 1:6 的圖形裡，Ic 與 Ld 似乎也成正比，就之前元件上的設計有所出入，這是因為沒有考慮到 Vth 的變化，由 Vth 的大小亦影響到 Ic 值的大小，所以以下就 Vth 做一討論。另外，在 N-buffer=1.5e18 摻雜濃度下，對於橫向 PNP 電晶體電流增益無用，換言之，在這樣濃度下，幾乎無 PNP 電晶體存在，其電流表現出來與 LDMOS 一樣，在之後討論亦可發現，這樣濃度下的元件並不好，往後設計上為應避免之地方。

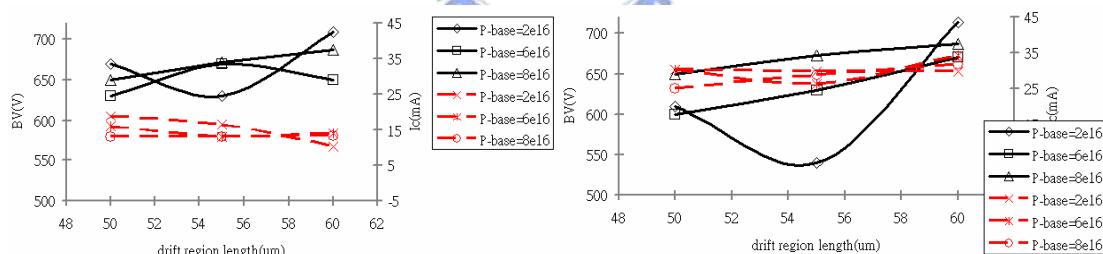

### D. Vth 討論

圖 5.19 N-buffer=1.5e17

N-buffer=8e16 Vth 與 Ld 關係(虛

線為 Ic)

在圖 5.18 中，在 P-base=6e16 與 8e16 兩種摻雜濃度下，其 Vth 值的變動不應該隨著漂移區的增長而有所變動，所以在 Ld 的變動上，卻影響了通道的形成，這點在往後模擬與實作方面，需要更加，因此之前所提導通電流所以會變動的原

因，還包括了  $L_d$  與  $V_{th}$  值等兩個變數影響，而綜合起來，電流與  $L_d$  關係曲線大致以圖 5.18 所示。接著在不同光罩，就 P-base 層摻雜濃度與 N-buffer 層摻雜濃度來作比較。接著就各光罩以 P-iso 層橫向擴散比率為 1:6 做一綜合整理與討論。

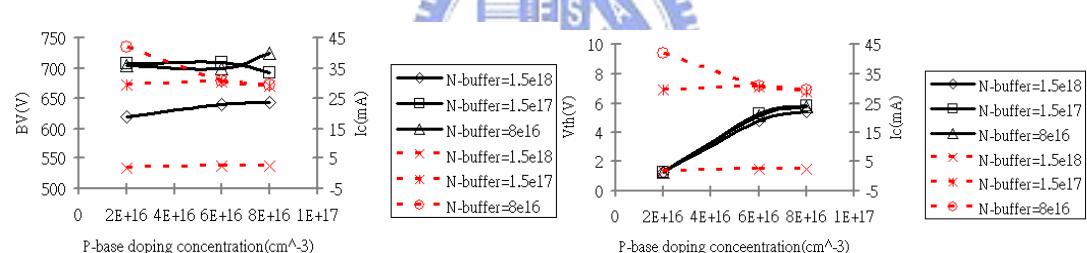

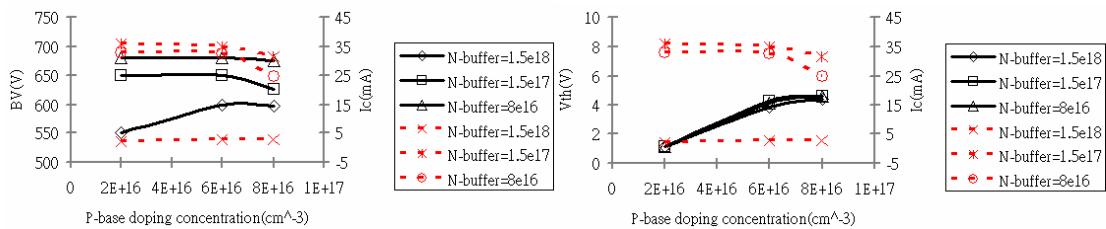

#### E. $L_d=60\mu m$ L-channel=3um Ao=3um

圖 5.20 BV 值、 $I_c$  與  $V_{th}$  關係圖（虛線為  $I_c$ ）

在圖 5.19 中，這個光罩裡，在 N-buffer 層摻雜濃度為  $1.5e18$  為為一低導通電流狀況，而且耐壓表現亦無其他濃度來的高，往後為設計避免地方。

#### F. $L_d=60\mu m$ L-channel=1.5um Ao=3um

圖 5.21 BV 值、 $I_c$  與  $V_{th}$  關係圖（虛線為  $I_c$ ）

在圖 5.20 中，以  $N\text{-buffer}=8e16$  與  $P\text{-base}=2e16$ ，為最好表現，然而發現在  $V_{th}$  上，其值可能過低，不足兩伏，這將來在整合部分，會有抗雜訊問題存在，為需要發展地方。

#### G. $L_d=55\mu m$ L-channel=3um Ao=3um

圖 5.22 BV 值、 $I_c$  與  $V_{th}$  關係圖（虛線為  $I_c$ ）

在圖 5.21 中，在漂移區較短的範例裡，其耐壓有些許下降，電流並未明顯

提升，主要為  $V_{th}$  有所變異，需要漂移區長度與  $V_{th}$  值兩者變數綜合，不過在此可以發現，當導通電流大時，相對下  $V_{th}$  也會下降，所以在日後改善導通電流方面可能需要重 N-buffer 與元件形狀著手。

#### H. $L_d=50\mu m$ L-channel=3um Ao=3um

圖 5.23 BV 值、 $I_c$  與  $V_{th}$  關係圖（虛線為  $I_c$ ）

圖 5.22 中，當漂移區縮至本實驗最短時，整體耐壓也降至最地處，在各層摻雜中，幾乎沒有一個範例是大於 700V 的，電流方面卻也沒有因為漂移區縮減而提升，主要仍受到  $V_{th}$  值影響，導通電流在本實驗中依舊根據導通通道圍住要影響。

#### I. $L_d=50\mu m$ L-channel=1.5um Ao=3um

圖 5.24 BV 值、 $I_c$  與  $V_{th}$  關係圖（虛線為  $I_c$ ）

圖 5.23 中，將通道降低至 1.5um，其耐壓並未有影響，依舊沒有大於 700V，此範例會在之後針對通道長度在作為一討論。

#### J. $L_d=50\mu m$ L-channel=3um Ao=2um

圖 5.25 BV 值、 $I_c$  與  $V_{th}$  關係圖（虛線為  $I_c$ ）

圖 5.24 中，耐壓普遍下降，電流依舊維持一定水平。

綜合以上各光罩討論，可以發現在這次的實驗中，P-base 扮演重要角色，除了在耐壓接面上影響，其  $V_{th}$  值更是決定電流的依據，在此，通道形成除了通道摻雜濃度之外，其通道長度有時亦為決定電流大小之變數，所以以下就通道長度作為討論。

## K. 通道長度

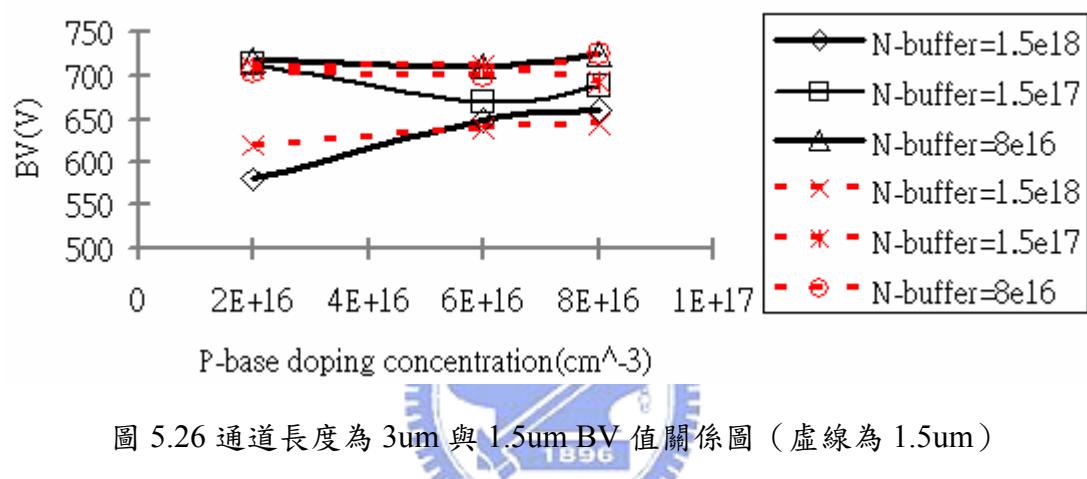

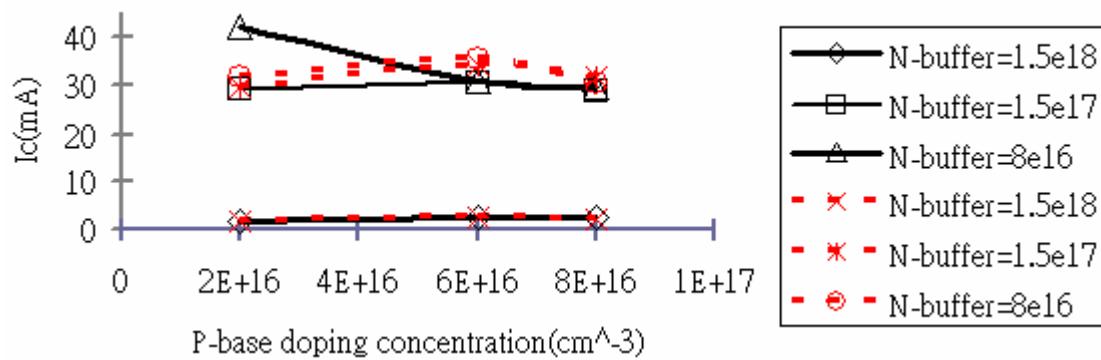

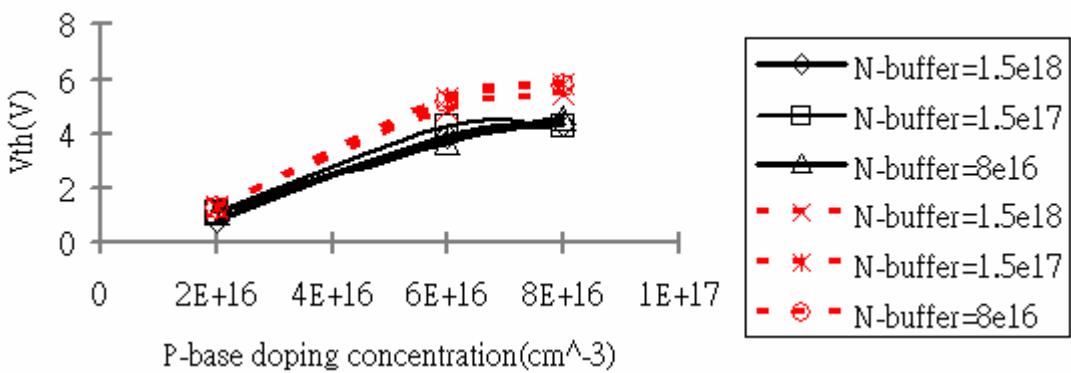

K.1  $L_d=60\mu m$

其通道長度比較圖形以圖 5.25 至圖 5.27 所示

圖 5.26 通道長度為 3um 與 1.5um BV 值關係圖（虛線為 1.5um）

圖 5.27 通道長度 3um 與 1.5um 電流關係圖（虛線為 1.5um）

圖 5.28 通道長度為 3um 與 1.5um Vth 關係圖 (虛線為 1.5um)

圖 5.25 中，有關通道影響耐壓不大，幾乎一樣，不過依舊在 P-base 摻雜濃度上，越重耐壓有提升效果。圖 5.26 中，通道長度大一點，電流有些微高一些，而其電流亦隨 P-base 摻雜濃度越重而下降。圖 5.27 中，各 Vth 與通道並無太大關係。

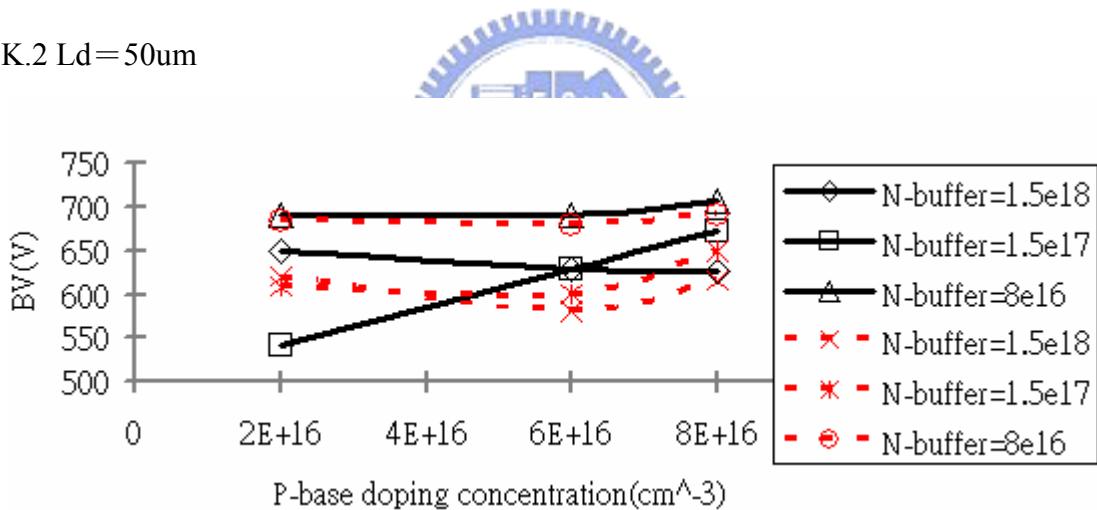

K.2 Ld=50um

圖 5.29 通道長度為 3um 與 1.5um BV 值關係圖 (虛線為 1.5um)

圖 5.30 通道長度為 3um 與 1.5um 電流關係圖 (虛線為 1.5um)

圖 5.31 通道長度為 3um 與 1.5um Vth 關係圖（虛線為 1.5um）

在圖 5.28 至圖 5.30 中，顯示出  $L_d=50\mu m$  下，不同通道長度的各各量測值，其中除了 BV 值有些許不同外，在導通電流與 Vth 幾乎為同一曲線，而由於在 BV 值量測上的誤差會較大，因此在通道長度的變化下，對元件的影響是有限的，甚至可以假設毫無影響。

#### 5.4 良好元件說明

經由以上三節量測點所討論，基於研究而言，需要將好與不好的範例做一比較，給予日後研發上的方向，在本節以本下線良好結果為主，其規格訂於 BV 值大於 710V 與當  $V_{ac}=3V$  時， $I_c$  值大於 20mA，以表 5.4 所示，不難發現，以本實驗元件 LIGBT 耐壓達 700V 以上而言，其漂移區長度 ( $L_d$ ) 至少要大於 60um，在小於 60um 的範例下，雖然  $I_c$  值較高，但耐壓並沒有可達 700V 以上的，另外在表 5.4 的陰影範例中，其 Vth 過低，只有 1V 左右，在耐壓與導通電流雖符合規格情況下，屬於較不良的元件，主要在於抗雜訊能力過差。

表 5.4 實作參數表 (BV>710V 及 Ic>20mA)

|                                      | BV<br>(V) | Ic(mA)<br>當 Vac<br>=3V | Vth(V) | 相關參數        |                 |                 |

|--------------------------------------|-----------|------------------------|--------|-------------|-----------------|-----------------|

| Ld=60um<br>L-channel=3um<br>Ao=3um   | 713       | 29.7                   | 1.09   | P-base=2e16 | P-iso=6e17      | N-buffer=1.5e17 |

|                                      | 719       | 31.68                  | 1.1    |             |                 | N-buffer=8e16   |

|                                      | 710       | 35.46                  | 3.73   |             |                 | N-buffer=8e16   |

|                                      | 710       | 22                     | 4.23   | P-base=6e16 |                 | N-buffer=1.5e17 |

|                                      | 724       | 30.55                  | 4.6    | P-iso=1e18  | N-buffer=1.5e17 |                 |

|                                      | 730       | 28.07                  | 4.61   |             | N-buffer=8e16   |                 |

| Ld=60um<br>L-channel=1.5um<br>Ao=3um | 710       | 30.46                  | 5.21   | P-base=2e16 | P-iso=1e18      | N-buffer=8e16   |

|                                      | 710       | 30.49                  | 5.29   |             |                 | N-buffer=1.5e17 |

|                                      | 715       | 24.41                  | 5.68   | P-base=6e16 | P-iso=6e17      | N-buffer=1.5e17 |

|                                      | 724       | 29.58                  | 5.74   |             |                 | N-buffer=8e16   |

## 第六章 結論與建議

本文主要在於研發耐壓達 700V 的 LIGBT 元件，綜合前五章與模擬結果的討論，成功實作出耐壓達 700V 的 LIGBT 元件，且在  $V_{ac}=3V$  情況中，其導通電流約為 30mA，除此之外，本實驗所使用之模擬軟體亦可以符合實際製程，主要在於模擬輸入檔選寫的詳細，與環境參數設定，為日後提供一條可以節省時間與準確製程的研究環境，至於在改進與研究方面而言，有以下幾點。

### A. $R_{on,sp}$ 的降低

在以耐壓達 700V 的情況下，本實驗最低的  $R_{on,sp}$  大約為  $20m\Omega \cdot cm^2$ ，其值主要與元件面積成正比關係，所以在特徵電阻的降低方法主要在於縮減元件面積，以下提供兩種結構：1. 運用第三層金屬層，如此可以縮減陽極電極面積。2. 採取多個元件並聯元件，如此可以共用陰極部分，大幅縮減元件面積。

### B. 操作頻率的提升

本實驗在操作頻率上並未做一量測與討論，日後如果在頻率上可以量測外，在改善方面也可以利用第二章文獻回顧的陽極短路結構，這方面有待日後的研究與發展。

### C. 高低壓隔離技術

未來功率 IC 時代裡，其高壓功率元件與低壓控制電壓的隔離整合仍為重要課題之一，在功率元件不失其高耐壓與高導通電流下，不影響低壓電路效能，因此對於 Power IC 時代中，以上幾點均為需要注意地方。

## 參考文獻

- [1] S. P. Robb, and J. L. Sutor, "Recent advances in Power Integrated Circuits with High Level Integration," in Proc. IEEE International Symposium on Power semiconductor Devices and IC's, 1994, pp.343-348.

- [2] J. Tihanyi, "Smart Power technologies," in Proc. IEEE International Symposium on VLSI and Computer Peripherals, May 1989, pp.5099-5104.

- [3] A. O. Adan, T. Naka, A. Kagisawa, and H. Shimizu, "SOI as a Mainstream IC Technology," IEEE International Symposium on SOI, Oct. 1998, pp.9-12.

- [4] P. A. Mawby, T. K. Starke, P. M. Holland, S. Hussain, W. M. Jamal, and P. M. Igic, "Advanced junction isolation structures for Power Integrated Circuit technology," IEEE International Symposium on Microelectronics'2004, May 2004, vol. 1, pp.17-22.

- [5] D. W. Green, S. Hardikar, R. Tadikonda, M. Sweet, K. V. Vershinin, and E. M. S. Narayanan, "Design and Analysis of Multichannel LIGBT's in Junction Isolation Technology", IEEE J. Electron Devices IEEE Transactions, vol.52, no.7, July.2005, pp.1672-1676.

- [6] N. Nolhier, G. Charitat, D. Zerrrouk, and P. Rossel, "Self-Shielded High Voltage SOI Structure for HVIC's," in Proc. IEEE Semiconductor Conference, Sept.1996, pp.317-270.

- [7] F. Vogt, H. Vogt, M. Radecker, and H. Fiedler, "Smart Power with 1200V DMOS," in Proc. IEEE International Symposium on Power Semiconductor Devices and IC's, May 1997, pp.317-320.

- [8] F. R. Pierret, Semiconductor Device Fundamentals, Addison-Welsley publishing Company, 1996.

- [9] B. J. Baliga, Power Semiconductor Devices, PWS. Publishing Company, 1995.

- [10] L. A. Robinson, D. N. Pattanayak, M. S. Adler, B. J. Baliga, and E. J. Wildi, "Lateral insulated gate transistors with improved latching characteristics," IEEE Electron Device Letters, 1996, vol.EDL-7, no.2, pp.61-63.

- [11] A. Nezar, K. T. P. Mok, and C. A. T. Salama, "Latch-up prevention in insulated gate bipolar transistors," ISPSD'93, pp.236-239.

- [12] J. Cai, and K. F. Lo, "A latch-up immunized lateral trench-gate conductivity modulated power transistor," in Proc. IPFA'99, 1999, Singapore, pp.168-172.

- [13] T. P. Chow, B. J. Baliga, D. N. Pattanayak, and M. S. Adler, "Comparison of p-channel lateral insulated-gate bipolar transistors with and without collector shorts," IEEE Electron Device Letters, 1990, vol.11, pp.184-186.

- [14] J. K. O. Sin, C. A. T. Salama, and L. Z. Hou, "Analysis and characterization of

- the hybrid Schottky injection field effect transistor," IEDM Tech. Dig, 1986, pp.222-224.