## 國立交通大學

# 電機工程學系 電信工程研究所

#### Intrinsic Parameter Fluctuation in Nanoscale MOSFET with Vertical Silicon Channels

#### 研究生:黄至鴻

指導教授:李義明 教授

中華民國九十八年十一月

## 立體通道之矽奈米級金氧半場效應電晶體本質參 數擾動之研究

## Intrinsic Parameter Fluctuation in Nanoscale MOSFET with Vertical Silicon Channels

研究生:黄至鴻 Student: Chih-Hong Hwang 博士 指導教授:李義明 Advisor: Dr. Yiming Li 國立交通大學 電機工程學 電信工程研究所 博士論文 **A** Dissertation Submitted to Institute of Communication Engineering Department of Electrical Engineering College of Electrical and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in **Electrical Engineering** Hsinchu, Taiwan

2009年11月

摘 要

延續摩爾定律而獲得高性能矽晶片以及高密度元件之觀點,新材料、新製程與 新結構的開發是半導體製造上繼續微縮元件的尺寸最有效的策略方案;其中,16 奈 米之後電晶體結構的改變儼然已成為非常前瞻與重要的趨勢,因此研究隨機掺雜問 題與製程變異在多重開極場效電晶體特性之影響已為重要且急迫之課題之一。因此 本論文發展了三維度元件電路模擬技術使用等效原子層級離散掺雜暨量子傳輸方程 的大尺度統計運算方法,並成功地分析 16 奈米立體矽場效應電晶體特性之擾動由 單開極、雙開極、三開極至全開極電晶體。此研究方法之準確度已成功地以次 20 奈 米矽場效應電晶體特性之實驗驗證。相較於單閒極電晶體,臨界電壓擾動在雙閉極、 三閒極至全閒極分別被壓抑 2.2、3.3 與 4 倍,壓抑的原理及物理特性均有探討。此 外,近來金屬閒極與高介電係數材料的使用已成為奈米電晶體元件開發之重要課 題,但金屬閒極與高介電係數材料的使用已成為奈米電晶體元件開發之重要課 題,但金屬閒極與高介電係數材料的使用已成為奈米電晶體元件開發之重要課 題,但金屬閒極與高介電係數材料的使用已成為奈米電晶體元件開發之重要課 題,但金屬閒極與高介電係數材料的使用已成為奈米電晶體元件開發之重要課 題,但金屬閒極與高介電係數材料的使用已成為奈米電晶體元件開發之重要課 題,但金屬閒極與電介電係數材料的使用已成為奈米電晶體元件開發之重要課

iv

#### Abstract

Gate-length scaling is still the most effective way to continue Moore's Law for transistor density increase and chip performance enhancement. Accompanied with complementary metal-oxide-semiconductor (CMOS) technology advanced to 32-nm node in production, further scaling down to sub-20 nm and even beyond has been widely noticed encountering much more challenges at short channel control than previous generations. The worsened short channel control of nanoscale transistor not only increases standby power dissipation, but also enlarges electrical characteristic fluctuations, such as the deviation of threshold voltage, drive current, mismatch, and so on. The fluctuation budget has to be controlled even tighter due to doubly increased transistor number along with technology node moving ahead. Moreover, the fluctuation is intrinsically increased with the scaling of transistor feature size, even not considering worsened short channel control. This thesis describes the intrinsic parameter fluctuations in vertical-channel devices from planar transistor to

double gate, tri-gate, omega fin-type field effect transistors (FinFETs) and nanowire Fin-FETs through experimental validated three-dimension device simulation and characterization. The implication of device variability in nanoscale transistor circuits are advanced. The extensive study assesses the fluctuations on device and circuit reliability, which can in turn be used to optimize nanoscale MOSFET and circuits. Full realization of the benefit of nanoscale transistor therefore requires development and optimization of new device materials, structures, and technologies to keep transistor performance and reliability.

謝

六年前的夏天,回憶的片段像口試時撥放的投影片,一頁頁略過我的腦海。當初那個羞澀 中帶有點稚氣的年輕人又映入我的眼簾,背景的圖案從工程四館、電資大樓、校門口的土地公 廟到交大的校園的每一處不停的變換,中間閃過了日本、希臘、法國、美國等充滿異國風情的 背景,最後回到了一張多人的大合照。曾幾何時,那笨拙稚氣的年輕人已穿上了西裝露出微笑, 眼角泛著淚光,曾幾何時,那本來瘦弱的臂膀已變得強壯而結實,這一切的一切都要感謝照片 中所有人的陪伴、支持與鼓勵。

年輕人右手邊的是他的指導教授 李義明老師,他是帶給照片那位年輕人影響最多的人。 多年的悉心指導、專業知識的傳授、研究方法的推敲、用字遣辭之斟酌以及為學處世待人接物 謹慎積極的態度,讓那位年輕人在治學方法及處世態度上受益良多,尤其是在論文發表時常退 居幕後,讓學生站在國際的舞台上發光發熱,更是年輕一輩學子日後之表率。值得一提的是李 老師右手邊的 周復芳老師與 李育民老師,兩位老師在修業期間提供的教誨與最大的自由度 與支持讓學生得以進行感興趣的研究。在幾位老師身旁的是論文口試期間提供寶貴意見與殷切 指正讓論文更臻完備的成大電機工程學系 王水進老師、清華大學電機工程學系 白田里一郎老 師、清華大學工程與系統科學系 張廖貴術老師與交通大學電子工程學系 陳明哲老師。師恩細 長,深切銘心,學生在此謹獻上最誠摯的感謝與敬意。

年輕人的左手邊是他平行科學計算實驗室的好伙伴:正凱、紹銘、素雲、惠文、益廷、大 慶、宣銘、典燁、毓翔、英傑、國輔、銘鴻、紀寰、忠誠及俊諺,正凱學長神人般留傳的程式 庫、紹銘學長的熱情教學與呵呵微笑、同窗好友的互相砥礪,如繞樑之音盤旋在腦海。年輕人 身後還有他一群共患難的朋友:金玲、逸宏、闡哥、酷桑、阿琅、小宇、培育、哲宇、獻哲, 謝謝你們,尤其是金玲,與妳在一起的六個年頭,有苦有笑點滴在心頭,謝謝妳一路的陪伴。 感謝這群陪伴我渡過許多困難的好友,學業的路上沒有你們,再美好的風景都覺得索然無味。 畫面轉回到身後的家人,感謝之詞溢於言表,謝謝你們在背後默默的支持與忍耐,你們是我最 大的力量來源,讓我在疲憊的時候給我最大的鼓勵與支持,請讓我用行動表達心中的感謝。

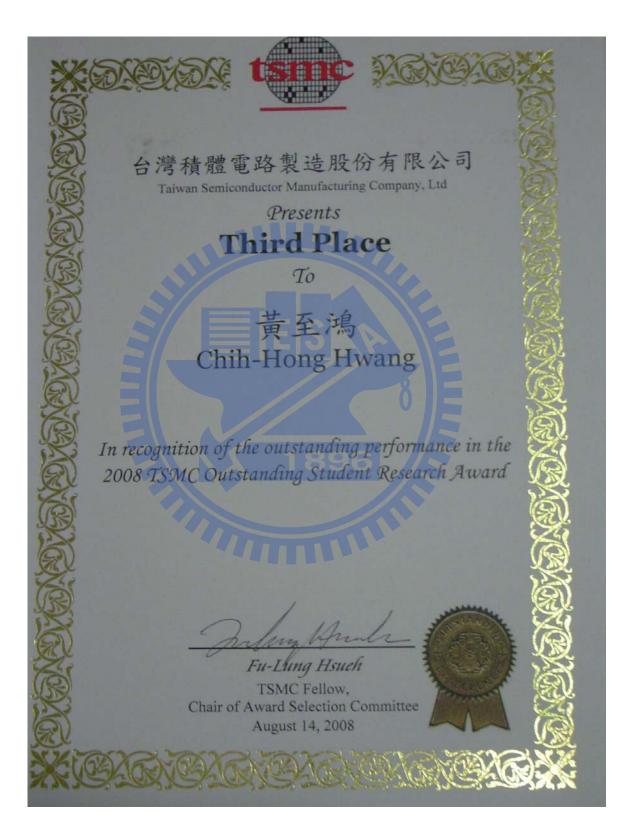

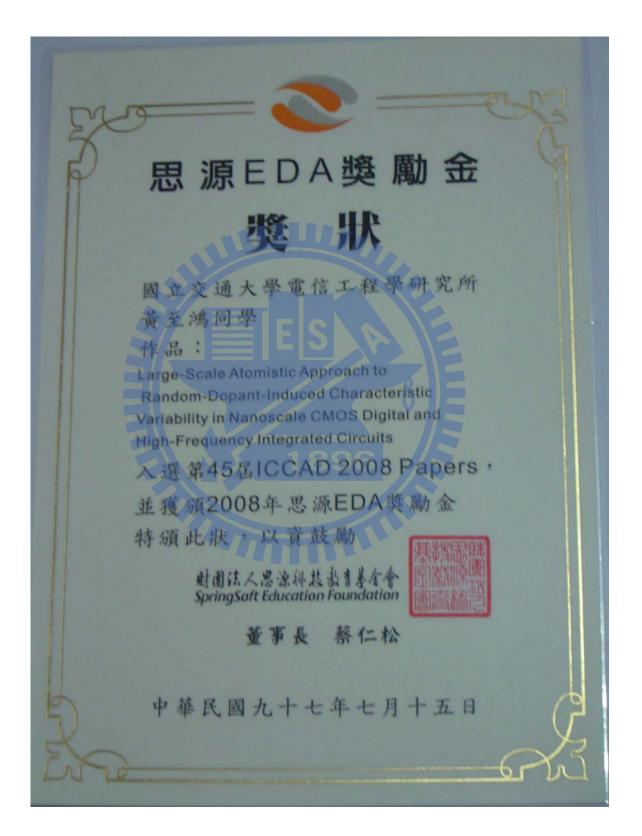

投影片到了最後的一頁,感謝行政院國家科學委員(計畫編號:NSC-96-2221-E-009-210、 NSC-95-2221-E-009-336、NSC-95-2752-E-009-003-PAE、 NSC-97-2221-E-009-154- MY2)、卓 越延續計畫(計畫編號:NSC-95-2752-E-009-003-PAE、NSC-96-2752-E-009-003-PAE)、五年五 百億計畫、群創光電股份有限公司、台灣積體電路製造股份有限公司產學研究計畫之經費補 助。感謝台積電楊副處長富量博士(現國家奈米元件實驗室主任)與黃經理俊仁博士提供研究 上的協助。能順利完成博士學業,全靠父母、家人及諸位朋友、同學的支持與忍耐,對此由衷 感謝,謹在此將本論文獻給關心我的人。

黃至鴻 謹誌

中華民國九十八年十月 于交通大學

### Contents

| Abs  | stract                                       | v    |

|------|----------------------------------------------|------|

| Ack  | knowledgments                                | vii  |

| List | t of Tables                                  | xiii |

| List | t of Figures                                 | XV   |

| 1    | Introduction                                 | 1    |

|      | 1.1   Toward Nanoscale Transistor Era        | 1    |

|      | 1.2 Vertical Channel Transistor Architecture | 5    |

|      | 1.2.1 FinFET Process Steps                   | 7    |

|      | 1.2.2 Process Simulation Using TCAD          | 8    |

|      | 1.3 Current Research Status and Motivation   | 10   |

|      | 1.4 Outline                                  | 15   |

| 2    | Device Model and Numerical Methods           | 17   |

|   | 2.1                                           | The Quantum-Mechanical Corrected Transport Equations                                                                                       | 17                               |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |                                               | 2.1.1 The Density-Gradient Equations                                                                                                       | 17                               |

|   |                                               | 2.1.2 The Mobility Model                                                                                                                   | 21                               |

|   | 2.2                                           | The Numerical Simulation Methods                                                                                                           | 22                               |

|   |                                               | 2.2.1 The Gummel Decoupling Method                                                                                                         | 22                               |

|   |                                               | 2.2.2 The Adaptive Finite Volume Method                                                                                                    | 25                               |

|   |                                               | 2.2.3 The Monotone Iterative Method                                                                                                        | 28                               |

|   | 2.3                                           | A 25-nm FinFET Simulation and Calibration                                                                                                  | 30                               |

|   | 2.4                                           | Summary                                                                                                                                    | 45                               |

|   |                                               |                                                                                                                                            |                                  |

| 3 | Sim                                           | ulation of Intrinsic Parameter Fluctuation                                                                                                 | 47                               |

| 3 | <b>Sim</b><br>3.1                             | ulation of Intrinsic Parameter Fluctuation Process Variation Effect                                                                        | <b>47</b><br>48                  |

| 3 |                                               |                                                                                                                                            |                                  |

| 3 | 3.1                                           | Process Variation Effect                                                                                                                   | 48                               |

| 3 | 3.1                                           | Process Variation Effect                                                                                                                   | 48<br>50                         |

| 3 | 3.1                                           | Process Variation Effect          Random-Dopant-Induced Characteristics Fluctuation          3.2.1       Discrete Dopant Generation Method | 48<br>50<br>52                   |

| 3 | <ul><li>3.1</li><li>3.2</li></ul>             | Process Variation Effect                                                                                                                   | 48<br>50<br>52<br>56<br>59       |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Process Variation Effect                                                                                                                   | 48<br>50<br>52<br>56<br>59<br>67 |

| 4 | Random-Dopant-Induced Characteristics Fluctuation in Vertical-Channel De- |    |

|---|---------------------------------------------------------------------------|----|

|   | vices                                                                     | 77 |

|   | 4.1  | Bulk Fin-Type Field Effect Transistors                               | 78  |

|---|------|----------------------------------------------------------------------|-----|

|   |      | 4.1.1 Roll-Off Characteristics                                       | 79  |

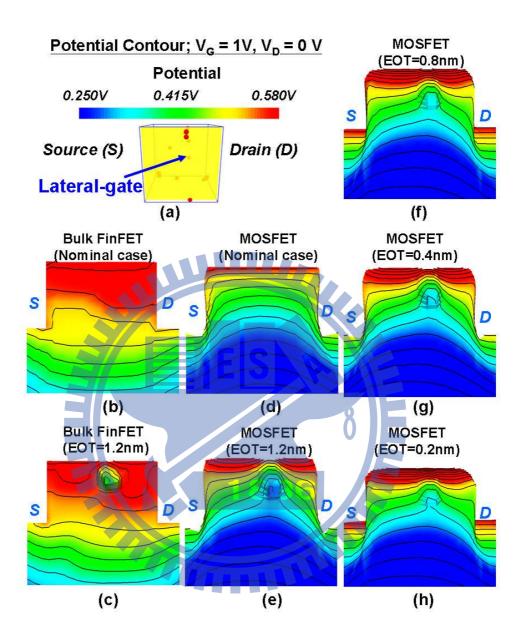

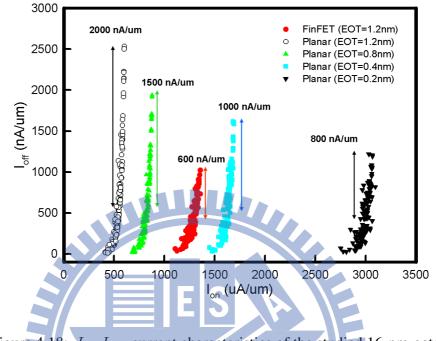

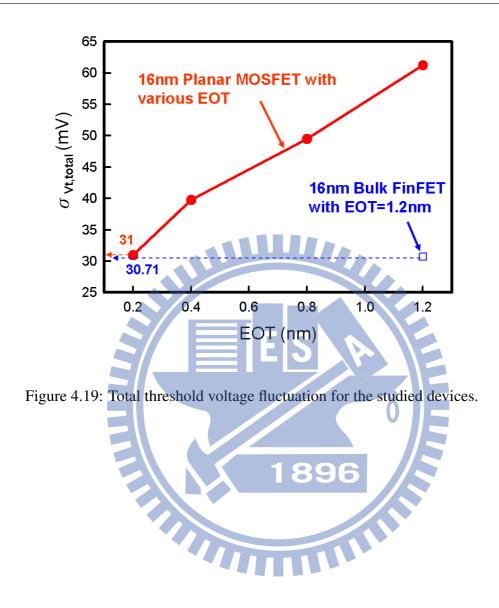

|   |      | 4.1.2 Comparison with Planar MOSFETs with High- $\kappa$ Dielectrics | 93  |

|   | 4.2  | Silicon-on-Insulator Transistors                                     | 105 |

|   | 4.3  | Summary                                                              | 126 |

| 5 | Intr | insic Parameter Fluctuation in Fin-Typed Field Effect Transistors    | 128 |

|   | 5.1  | DC Characteristic Fluctuation                                        | 129 |

|   | 5.2  | AC Characteristic Fluctuation                                        | 134 |

|   | 5.3  | Summary                                                              | 143 |

| 6 | Imp  | lication of Device Variability in Circuits                           | 145 |

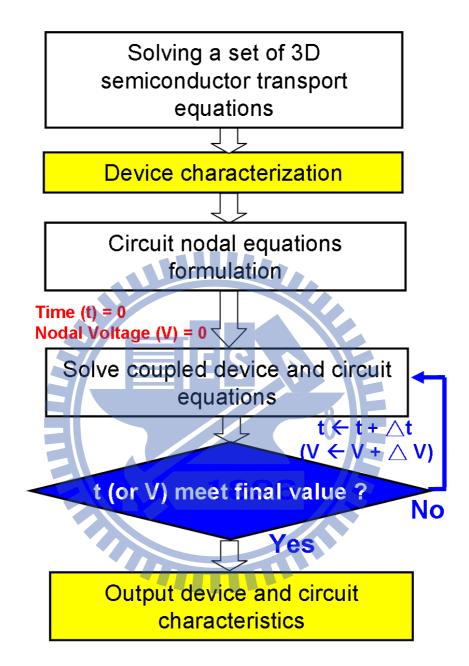

|   | 6.1  | The Coupled Device-Circuit Simulation Technique                      | 146 |

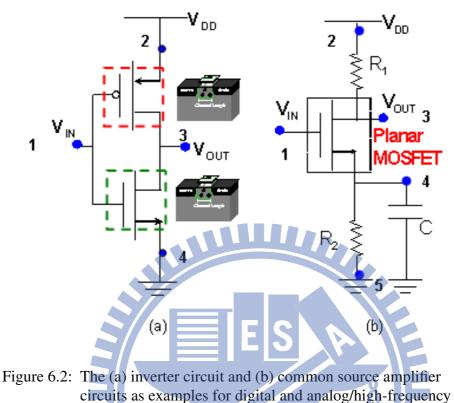

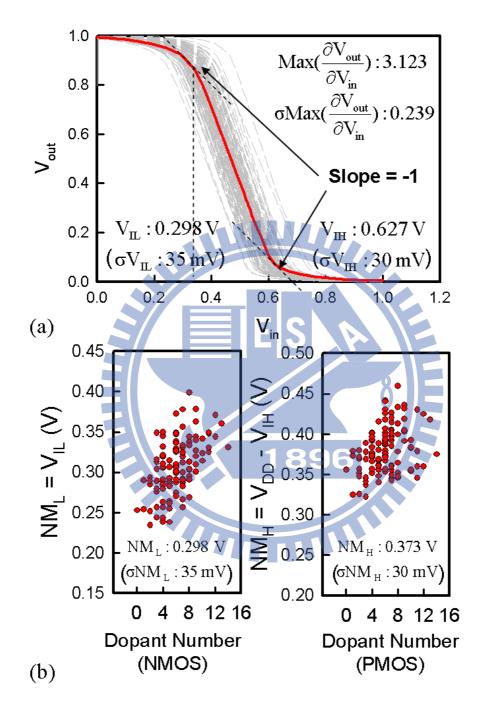

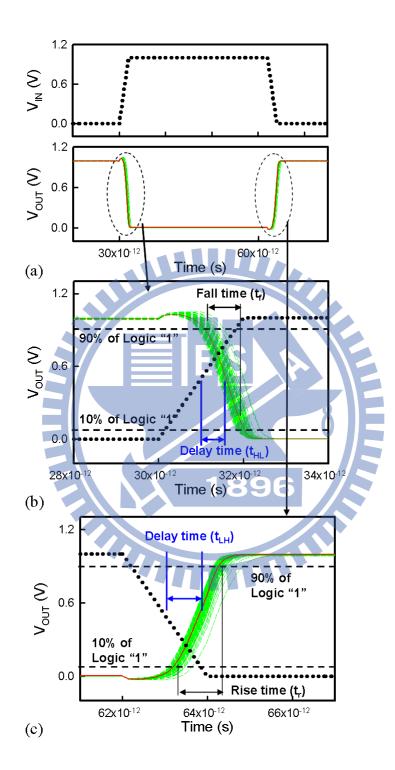

|   | 6.2  | Digital Circuits                                                     | 151 |

|   | 6.3  | Analog/High-Frequency Circuits                                       | 168 |

|   | 6.4  | Summary                                                              | 179 |

| 7 | Con  | clusions and Future Work                                             | 181 |

|   | 7.1  | Conclusion of This Study                                             | 181 |

|   | 7.2  | Suggestions on the Suppression Approaches                            | 182 |

|   |      | 7.2.1 Vertical Doping Profile Engineering                            | 182 |

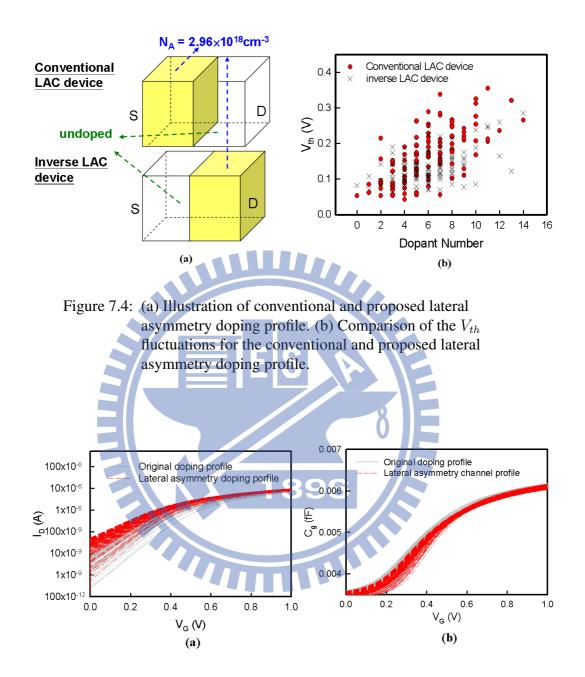

|      | 7.2.2    | Inverse Lateral Asymmetry Doping Profile | 88 |

|------|----------|------------------------------------------|----|

| 7.3  | Sugges   | stions on the Future Work                | 91 |

| Refe | rences . |                                          | 94 |

#### Appendix A

| VITA |

|------|

|------|

#### **List of Tables**

| 2.1 | Material parameters setting for silicon, poly-silicon, $SiO_2$ and $Si_3N_4$ . The |     |

|-----|------------------------------------------------------------------------------------|-----|

| 2.1 | epsilon is the ratio of the permittivities of material and vacuum                  | 40  |

| 3.1 | The trend of $V_{th}$ for technology scaling. The nominal $L_g$ cases in table are |     |

| 3.2 | nominal gate lengths for each technology node respectively                         | 73  |

| 0.2 | ated 20-nm-gate planar CMOS transistors                                            | 73  |

| 4.1 | The the threshold voltage fluctuation induced by S/D dopants only, channel         |     |

|     | dopants only, and fully discrete schemes and the simulation time for one           |     |

|     | transistor.                                                                        | 79  |

| 4.2 | Threshold voltage of the studied devices with nominal continuous channel           |     |

|     | doping                                                                             | 82  |

| 4.3 | Summary of the threshold voltage fluctuation of the explored planar MOS-           |     |

|     | FETs and bulk FinFETs                                                              | 105 |

| 6.1 | Transition time variation for the 16-nm-gate planar inverter circuits. (*  |

|-----|----------------------------------------------------------------------------|

|     | normalized by the nominal value)                                           |

| 6.2 | Summarized high-frequency characteristic fluctuations of the nano-MOSFETs  |

|     | circuit                                                                    |

| 7.1 | Effectiveness of vertical doping profile engineering and lateral asymmetry |

## **List of Figures**

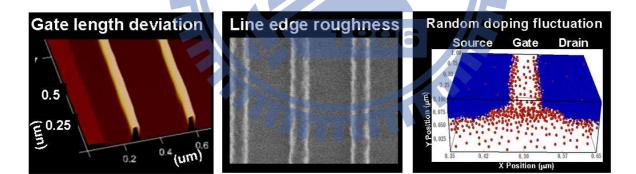

| 1.1 | The major sources of intrinsic parameter fluctuations: the gate length devi-           |   |

|-----|----------------------------------------------------------------------------------------|---|

|     | ation, line edge roughness, and random dopant fluctuation [15]                         | 2 |

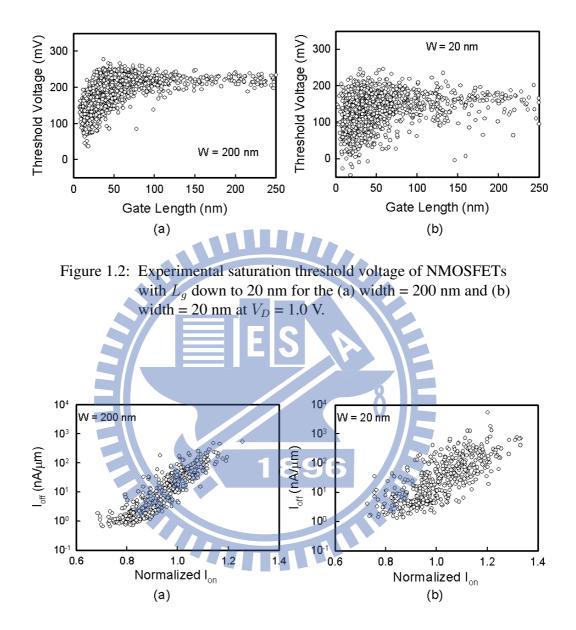

| 1.2 | Experimental saturation threshold voltage of NMOSFETs with $L_g$ down to               |   |

|     | 20 nm for the (a) width = 200 nm and (b) width = 20 nm at $V_D$ = 1.0 V<br><b>1896</b> | 3 |

| 1.3 | Experimental $I_{on}$ - $I_{off}$ characteristics of NMOSFETs with $L_g$ down to 20    |   |

|     | nm for the (a) width = 200 nm and (b) width = 20 nm at $V_D$ = 1.0 V. The              |   |

|     | $I_{on}$ was normalized against the on-current of nominal $L_g$ case, i.e. the 20      |   |

|     | nm $L_g$ case                                                                          | 3 |

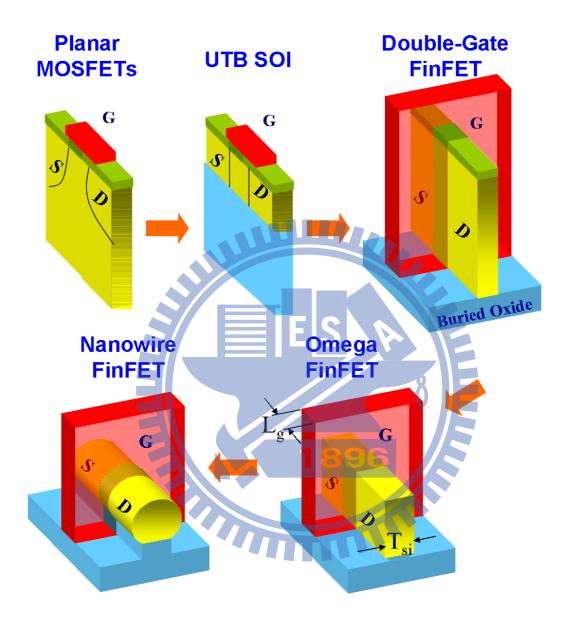

| 1.4 | The evolution of transistor architecture from planar MOSFETs to ultra-                 |   |

|     | thin-body silicon-on-insulator, double-gate, omega gate, and nanowire Fin-             |   |

|     | FETs                                                                                   | 6 |

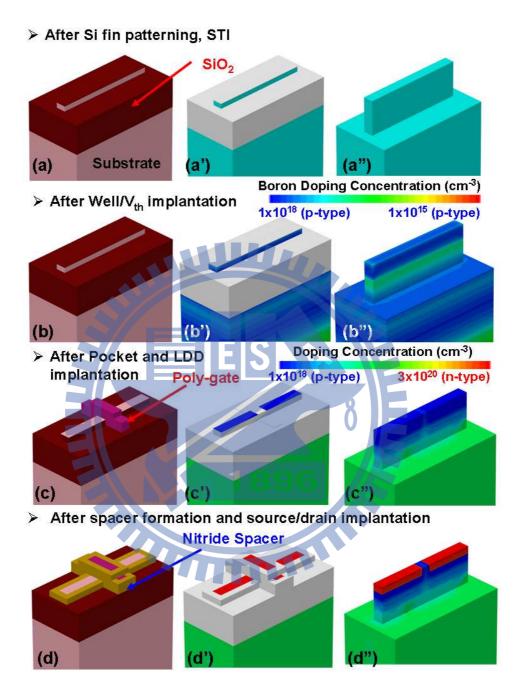

The process simulation result for FinFETs. ((a)-(a"))The device structure 1.5 after Si fin patterning, STI. The doping concentration in this step is background doping with  $1.0 \times 10^{15}$  cm<sup>-3</sup> boron concentration.((b)-(b"))After Well/V<sub>th</sub> implantation and annealing, the dopants are activated after thermal annealing. The fabrication process then goes to gate formulation, pocket and LDD implantation. The gate oxide is formulated after the gate oxide growth ((c)-(c")). ((d)-(d"))After spacer formation and source/drain implantation, the final device structure is shown. 9 The gate length deviation, line edge roughness, and random dopant fluctu-1.6 ation induced  $V_{th}$  fluctuation versus equivalent oxide thickness (EOT). . . . 11 The threshold voltage fluctuation versus technology node. . 1.7 . . . . 13 The plot of FV method. (a) One-Irregular mesh, and (b) the difference 2.1 between finite element mesh and finite volume mesh 26 The mesh used for the solution process. 2.2 27 2.3 (a) An illustration of the simulated fin-type field effect transistors. The top of the fin is formed to a round shape naturally and the fin bottom is not actually rectangular for the lithography and silicon etching processes. (b) The  $I_D$ - $V_G$  curves for the FinFETs. The red and black lines are the 31

| 2.5 | (a) The device dimension and parameter setting of the simulated fin-type       |

|-----|--------------------------------------------------------------------------------|

|     | field effect transistors, in which the device workfunction is 4.28 eV. (b) The |

|     | characteristics of the $I_D$ - $V_G$ curves for the FinFETs. The red and black |

|     | lines are the simulated and measured data, respectively. The simulation        |

|     | shows a good agreement with measurement data, which represents the ac-         |

|     | curacy of the calibrated 3D device simulation                                  |

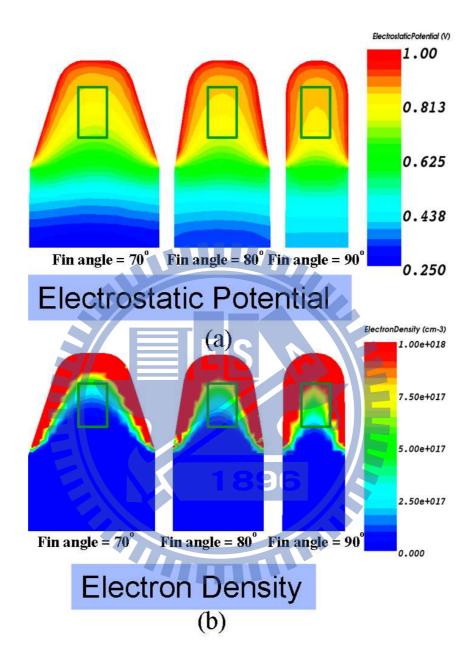

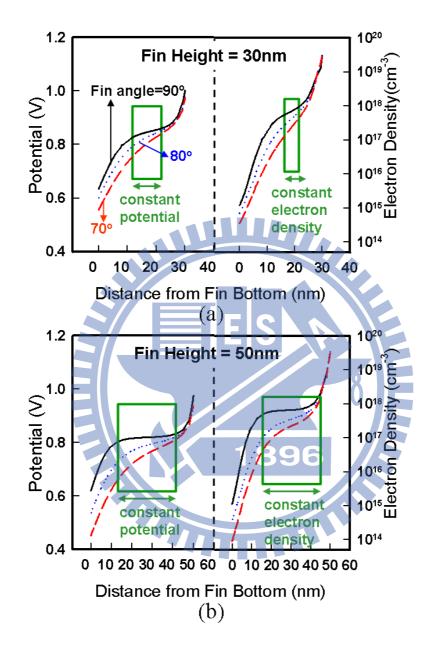

2.8 Plots of the 2D cutting plane of the simulated on-state ( $V_D = 1.0$  V and  $V_G = 1.0$  V) (a) potential and (b) electron density at the center of channel of the 30 nm-height bulk FinFET. The fin angles are the 90°, 80°, and 70°, respectively.

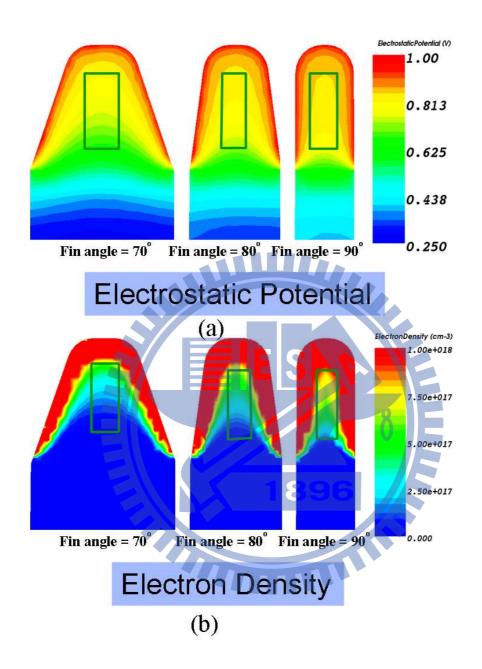

- 2.9 Plots of the 2D cutting plane of the on-state (a) potential and (b) electron density at the center of channel of the 40 nm-height bulk FinFET. The fin angles are the 90°, 80°, and 70°, respectively.

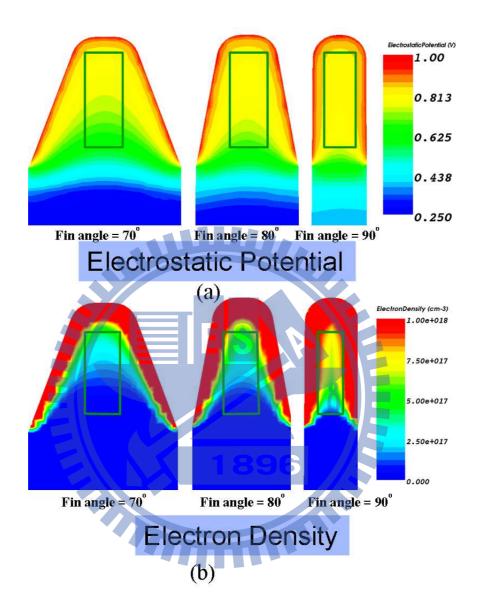

- 2.10 Plots of the 2D cutting plane of the on-state ((a) potential and (b) electron density at the center of channel of the 50 nm-height bulk FinFET. The fin angles are the 90°, 80°, and 70°, respectively.

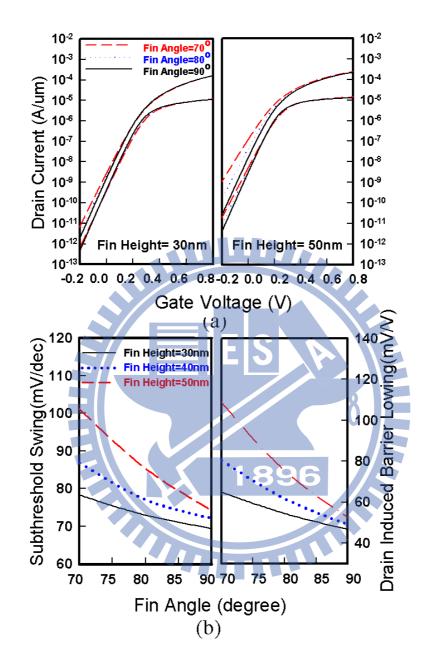

- 2.12 (a) The  $I_D$ - $V_G$  curves for the device for different fin angles and heights. The solid lines are the result of 90°, the dotted lines are for the 80°, and the dashed lines are for the 70°. (b) Results of SS (the left plot) and DIBL (the right one) versus the fin angle, where the solid lines are the result of 30 nm, the dotted lines are for the 40 nm, and the dashed lines are for the 50 nm. 44

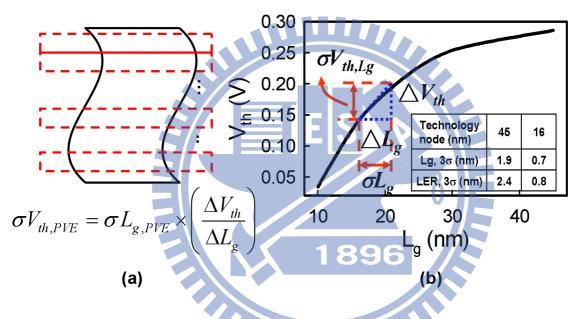

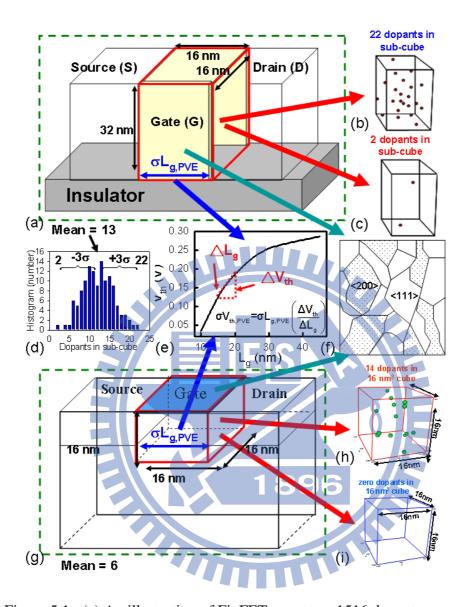

| 3.1 | (a) An illustrates for the result of generated profile. The process-variation-                                                                                                                                                                                                                                                                                                                                                   |    |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | effect induce gate length variation, $\sigma L_{g,PVE}$ , are obtained. The inset shows                                                                                                                                                                                                                                                                                                                                          |    |

|     | the equation for the estimation of $\sigma V_{th,PVE}$ . (b)A look-up table of the                                                                                                                                                                                                                                                                                                                                               |    |

|     | threshold voltage versus gate length. Using the $V_{th}$ roll-off relation, the                                                                                                                                                                                                                                                                                                                                                  |    |

|     | $\sigma V_{th,PVE}$ can be obtained.                                                                                                                                                                                                                                                                                                                                                                                             | 48 |

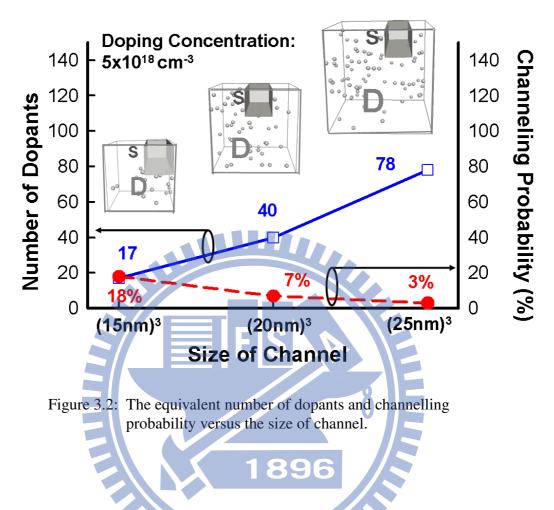

| 3.2 | The equivalent number of dopants and channelling probability versus the size of channel.                                                                                                                                                                                                                                                                                                                                         | 51 |

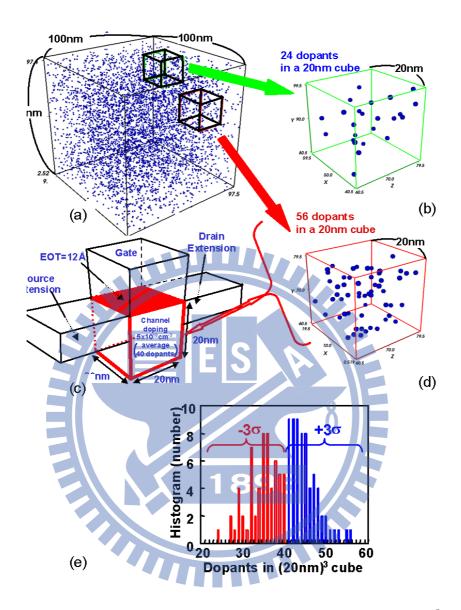

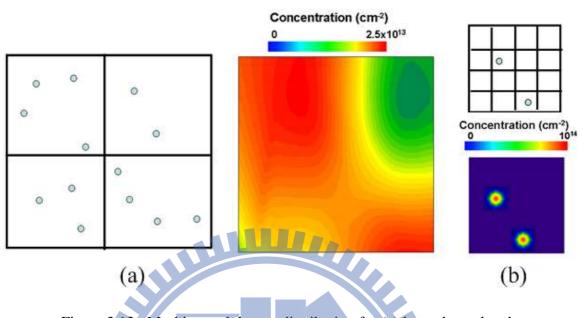

| 3.3 | (a) Discrete dopants randomly distributed in $(100 \text{ nm})^3$ cube with an average concentration of $5 \times 10^{18} \text{ cm}^{-3}$ . 5000 dopants are in the $(100 \text{ nm})^3$ cube, but dopants vary from 24 to 56 (the average number is 40 and the standard deviation is 6.3) within its sub-cubes of $(20 \text{ nm})^3$ , (the (b), (c), and (e)). These sub-cubes are then equivalently mapped into channel re- |    |

|     | gion for RDF simulation, as shown in the (d)                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

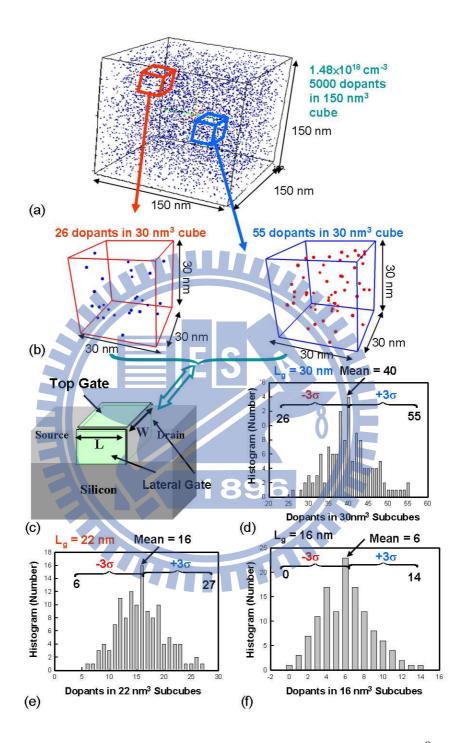

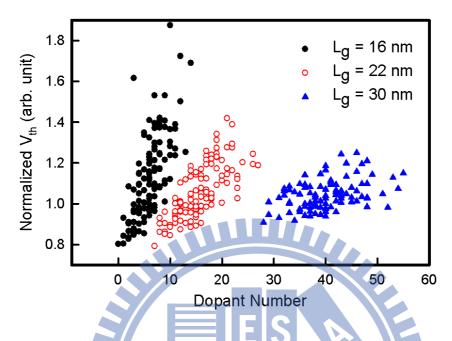

| 3.4 | (a) Discrete dopants randomly distributed in $(150 \text{ nm})^3$ cube with average                                                                                                                                                                                                                                                                                                                                              |    |

|     | concentration of $1.48 \times 10^{18}$ cm <sup>-3</sup> . 5000 dopants are within the cube, but                                                                                                                                                                                                                                                                                                                                  |    |

|     | dopants may vary from 26 to 55 (average number is 40) within each of                                                                                                                                                                                                                                                                                                                                                             |    |

|     | the sub-cubes of $(30 \text{ nm})^3$ , [(b) and (d)]. The sub are then used for RDF                                                                                                                                                                                                                                                                                                                                              |    |

|     | simulation (c). The statistically generated discrete-dopant distributions for                                                                                                                                                                                                                                                                                                                                                    |    |

|     | (e)22- and (f)16-nm-gate length                                                                                                                                                                                                                                                                                                                                                                                                  | 55 |

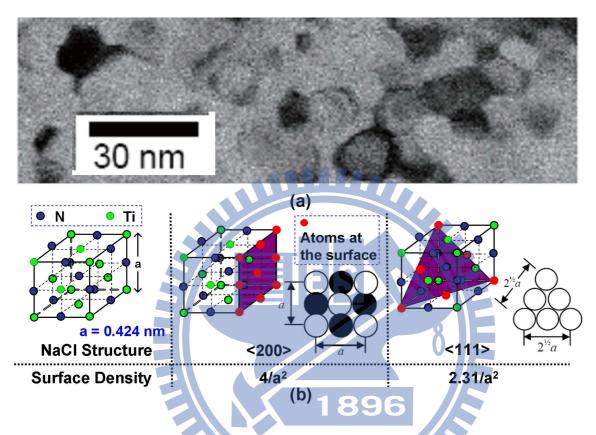

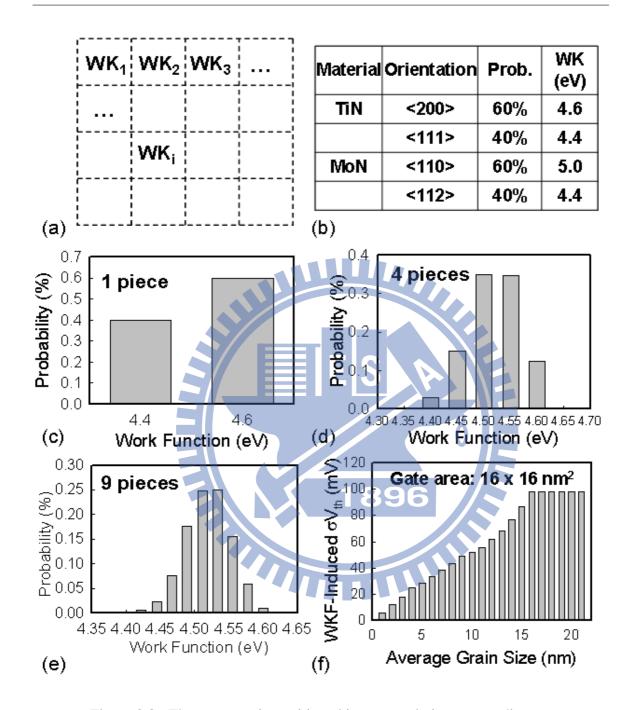

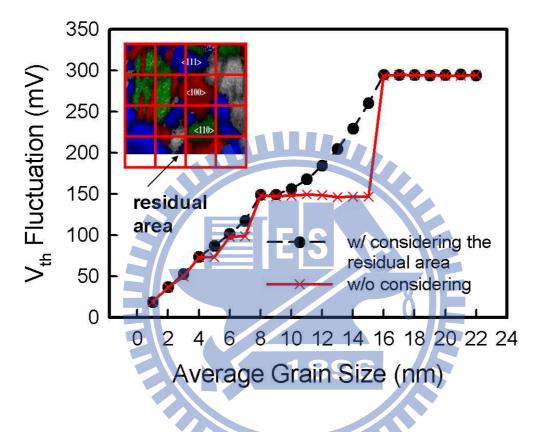

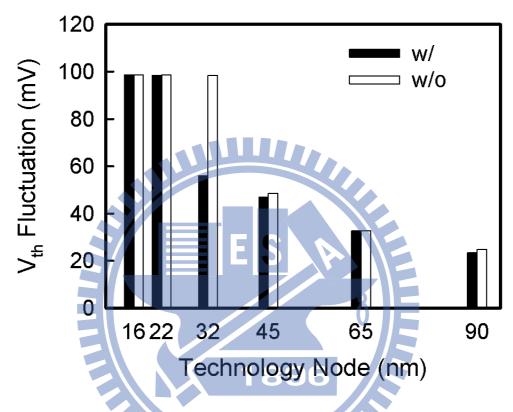

- 3.7 (a) The SEM pictures and illustration of TiN surface, which containing numbers of grain with various grain orientation. (b) An illustration of crystal structure of copper with <200>, and <111> orientation. Each grain orientation has its own strength of dipoles and therefore different workfunction. Therefore, the combination of device workfunction will become a probabilistic distribution rather than a deterministic value. . . . . . . . 60

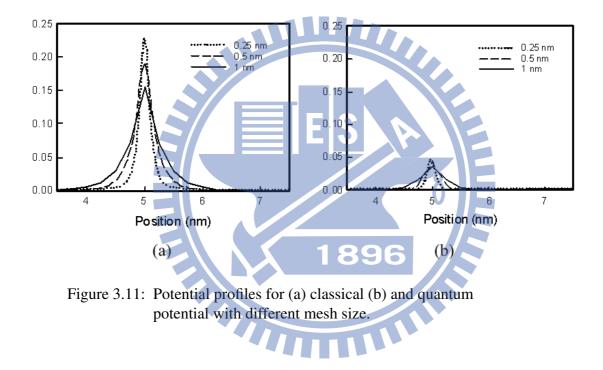

- 3.12 Meshing and dopant distribution for (a) long channel and (b) nanoscale transistors. The fine mesh in nanoscale transistor creates problems of singularities in the Coulomb potential and un-physically trap majority carriers.

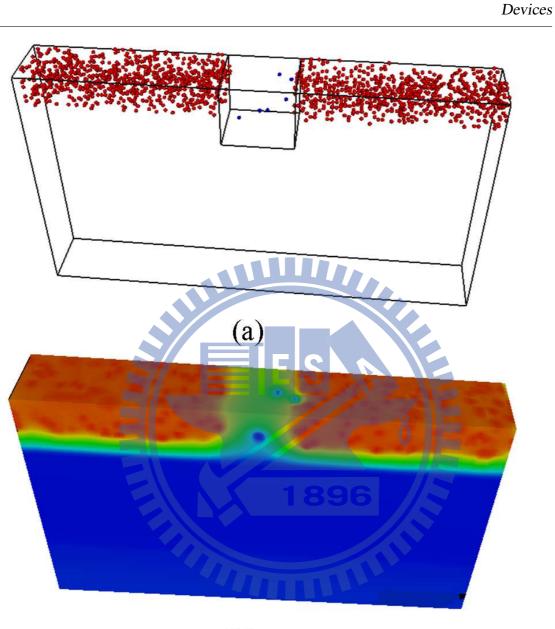

- 4.1 (a) The dopant distributions for the fully discrete scheme in 16-nm-gate transistor. Both source/drain and channel dopants are placed randomly in device. (b) The associated potential distribution, in which the effective device gate length was disturbed.

80

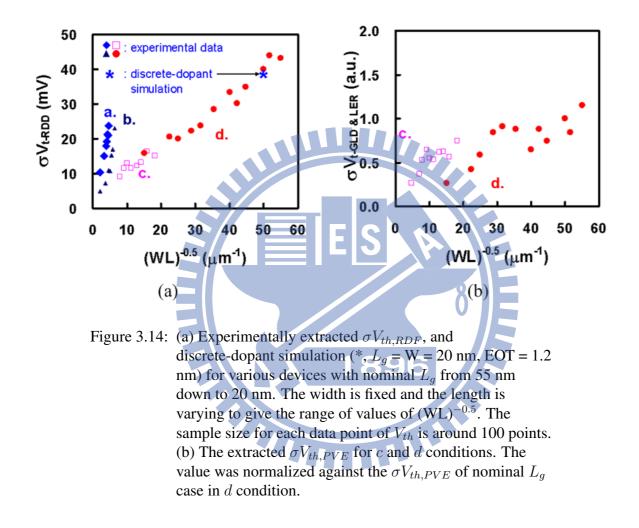

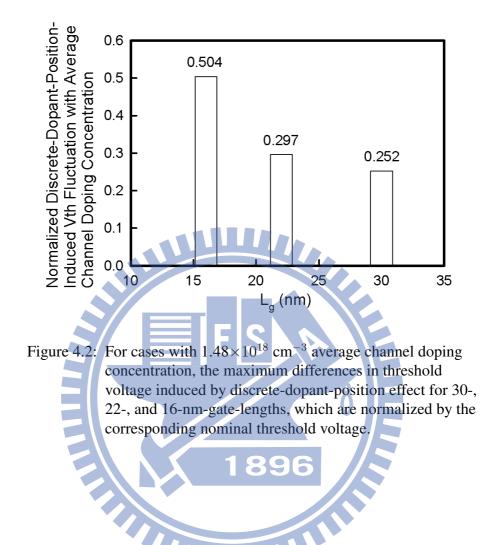

| 4.2 | For cases with $1.48 \times 10^{18}$ cm <sup>-3</sup> average channel doping concentration, |

|-----|---------------------------------------------------------------------------------------------|

|     | the maximum differences in threshold voltage induced by discrete-dopant-                    |

|     | position effect for 30-, 22-, and 16-nm-gate-lengths, which are normalized                  |

|     | by the corresponding nominal threshold voltage                                              |

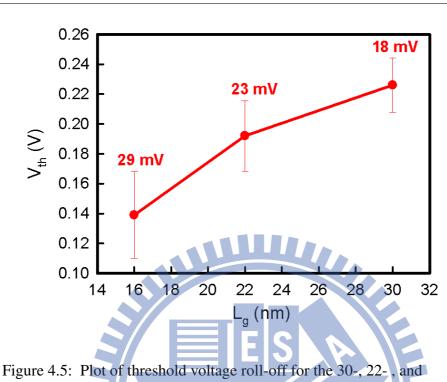

- 4.5 Plot of threshold voltage roll-off for the 30-, 22-, and 16-nm-gate bulkFinFETs, where the bars indicate the fluctuation of threshold voltage. . . . 86

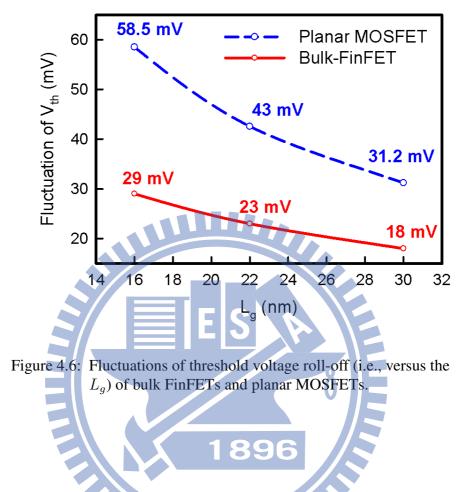

- 4.6 Fluctuations of threshold voltage roll-off (i.e., versus the  $L_g$ ) of bulk Fin-FETs and planar MOSFETs. 87

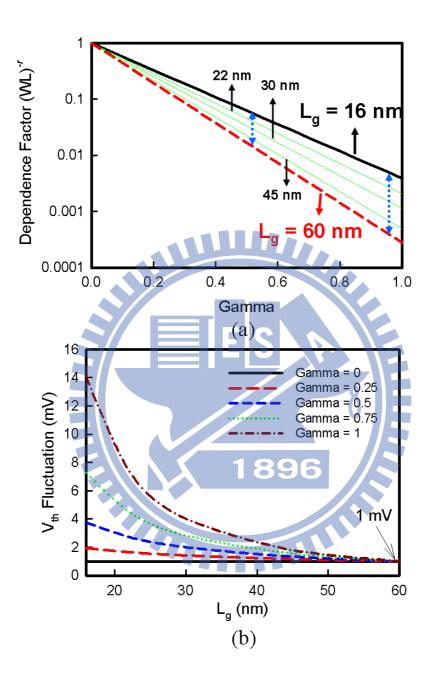

- 4.7 Threshold voltage fluctuation as a function of device dimension. (a) Plots of dependence factor on  $\gamma$  for various device dimensions. (b) Fluctuation of threshold voltage for the 60-nm-gate device was assumed to be 1 mV. . . 88

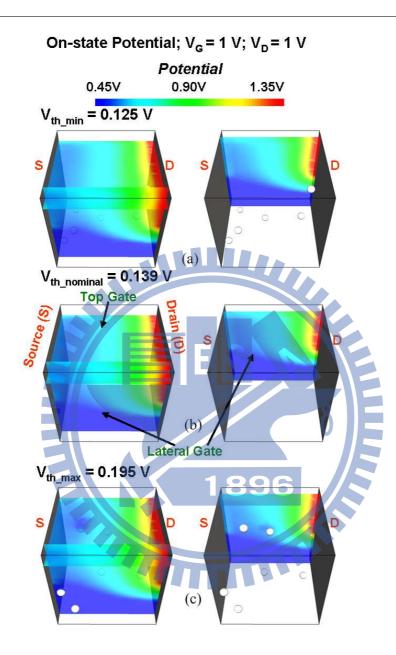

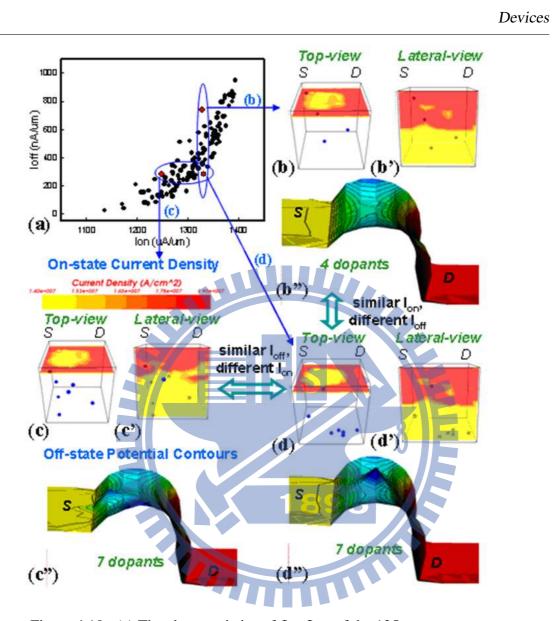

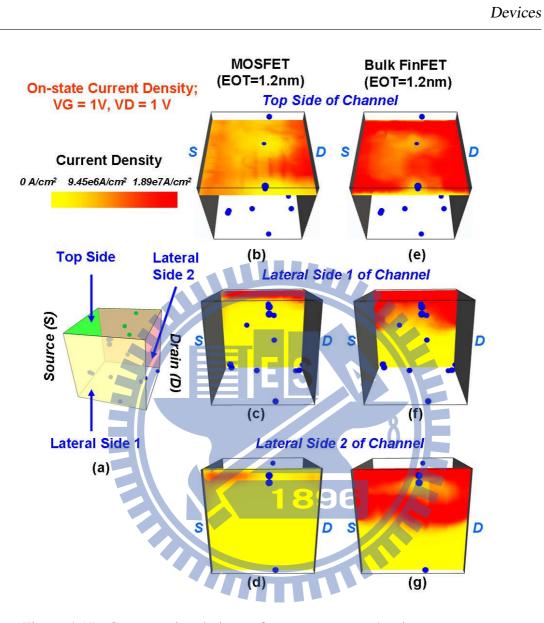

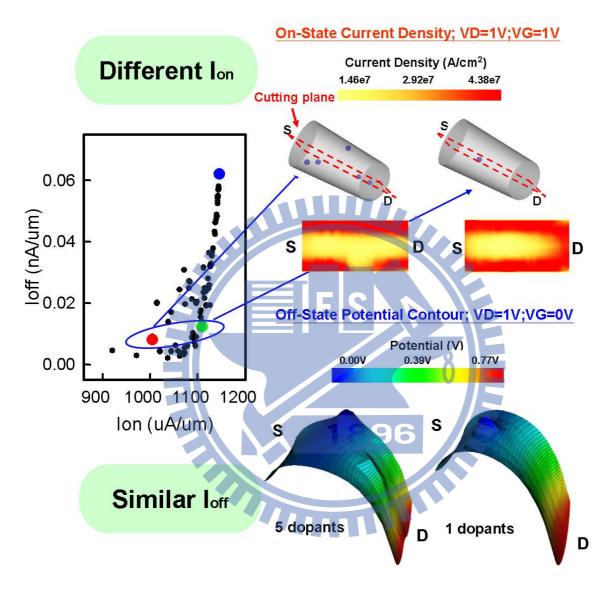

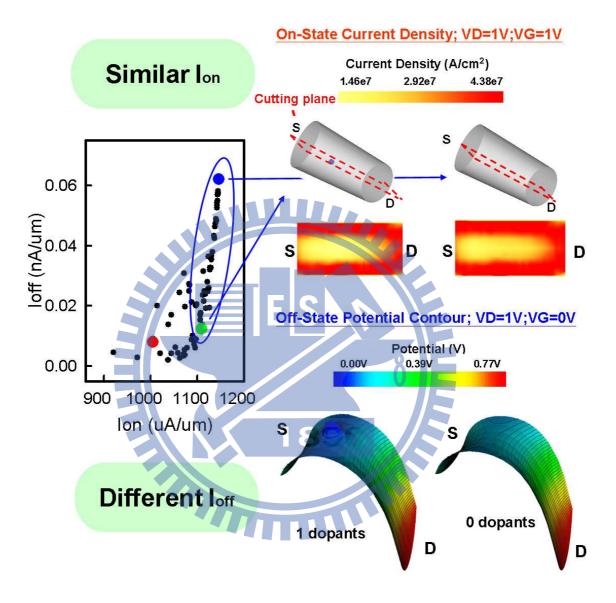

- 4.10 (a) The characteristics of  $I_{on}$ - $I_{off}$  of the 125 discrete-dopant 16-nm-gate bulk FinFETs. Three cases are selected to evaluate similar  $I_{on}$  but different  $I_{off}$  (plots of (b) and (c)) and similar  $I_{off}$  but different  $I_{on}$  (plots of (c) and (d). Plots of (b)-(d) and (b')-(d') show the corresponding top and lateral views of the on-state current density, which are extracted at the 1 nm below the gate oxide, respectively. Plots of (b")-(d") show the off-state potential contours.

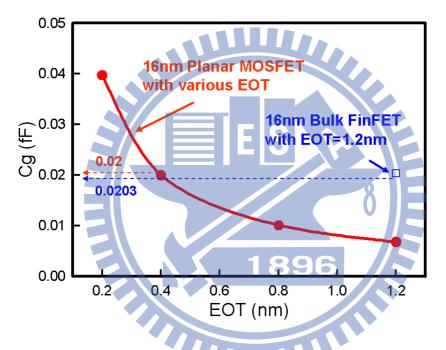

| 4.11 | The gate capacitance as a function of the EOT, where the solid line shows |    |

|------|---------------------------------------------------------------------------|----|

|      | the planar MOSFETs with various EOT and the square symbol indicates       |    |

|      | the bulk FinFET device with 1.2 nm EOT                                    | 94 |

- 4.20 The (a) single-gate; (b) double-gate; (c) triple-gate; and (d) quadruple surrounding-gate for the dopant position/number-sensitive device simulation.106

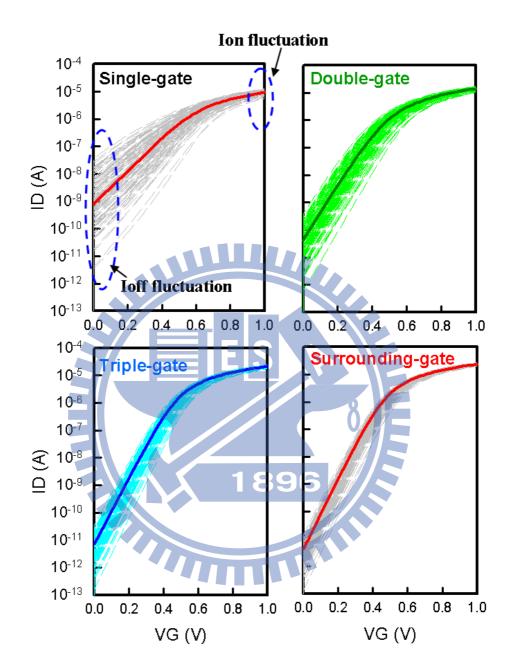

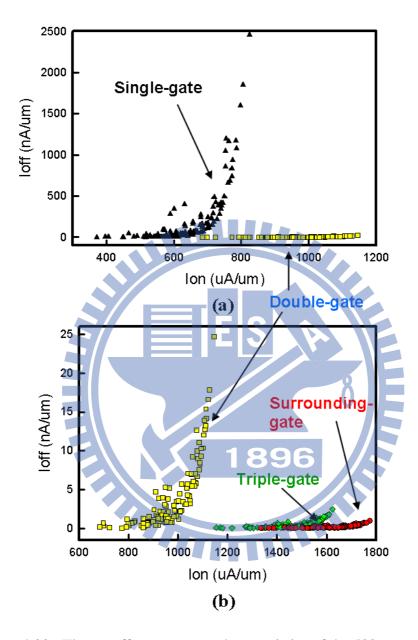

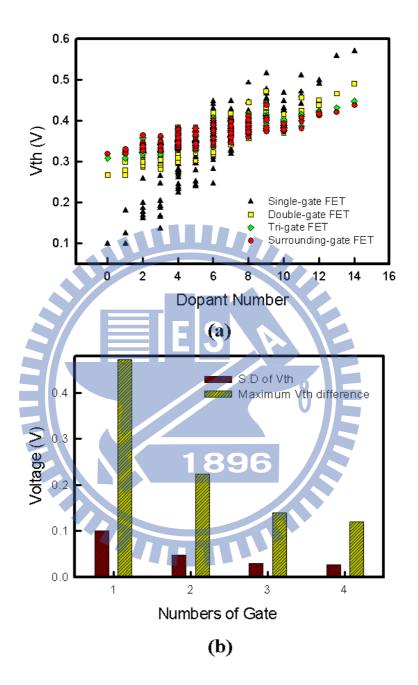

- 4.22 The  $I_D$ - $V_G$  characteristics of the 500 discrete-dopant-fluctuated 16-nm-gate single- and multiple-gate SOI devices, where the solid lines indicate the nominal case and the dash lines indicate the discretely doped cases. . . . . 109

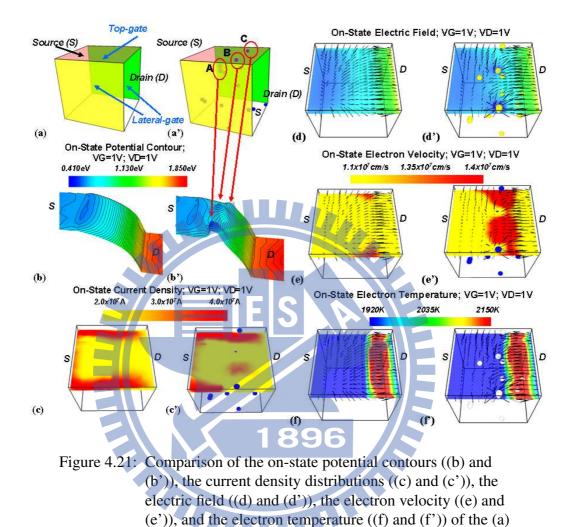

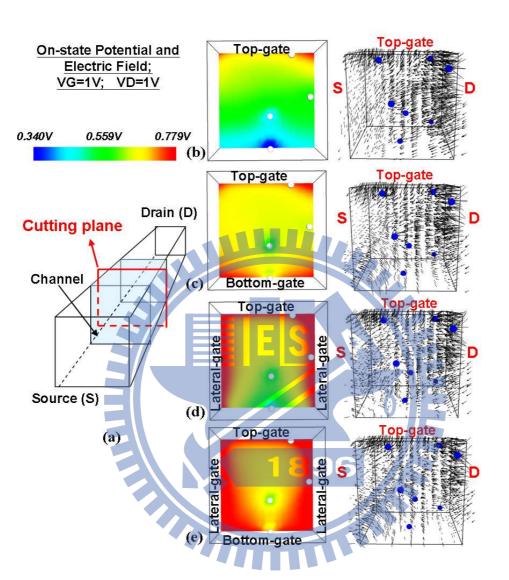

- 4.25 Plots of the on-state potential and 3D electric field distribution of the 16nm-gate SOI MOSFET with the (b) single- (c) double-, (d) triple- and (e) quadruple surrounding-gate structure. The cross-sectional plots of the onstate potential distributions are extracted along the center of the device's channel, as shown in (a).

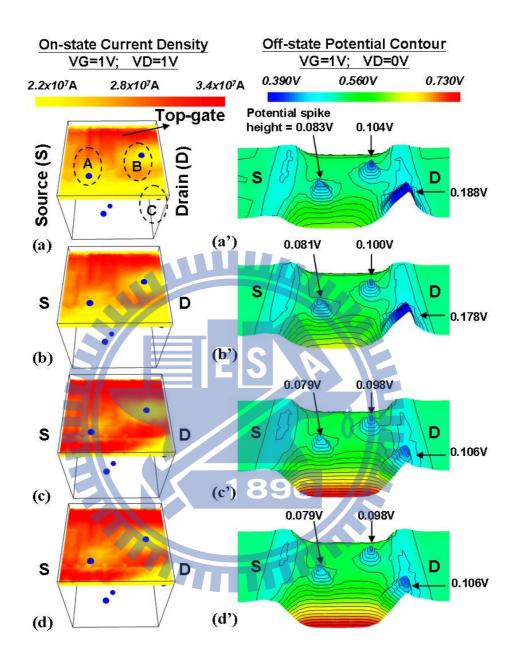

- 4.26 Plots of the on-state current density distributions ((a)-(d)) and the off-state potential contours ((a')-(d')) of the 16-nm-gate SOI MOSFETs ((a) and (a') are for the single-gate; double-gate: (b) and (b'); triple-gate: (c) and (c'); quadruple surrounding-gate: (d) and (d')). The potential spikes in (a')-(d') are induced by corresponding dopants in channel (spikes A, B, and C shown in (a)). The height of potential spikes is decreased as gate number is increased. All cross-sectional plots of the on-state current density distributions and off-state potential contours are extracted at 1 nm below the top-gate oxide.

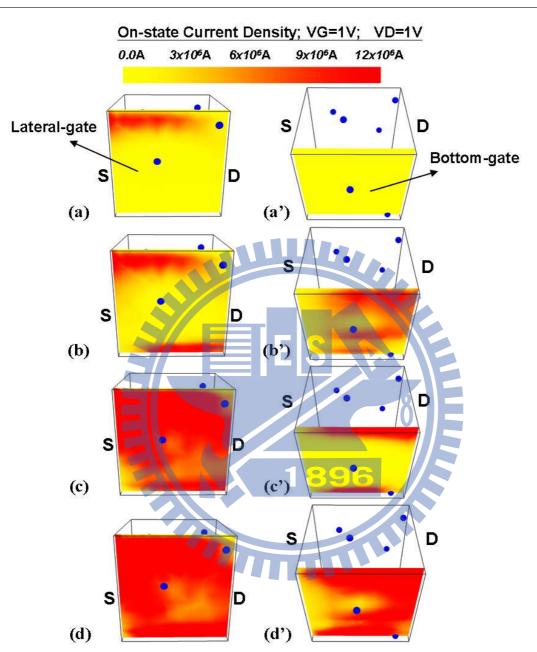

- 4.27 Plots of the lateral-side ((a)-(d)) and bottom-gate ((a')-(d')) on-state current density distributions of the 16-nm-gate devices ((a) single-gate; (b) double-gate; (c) triple-gate; (d) quadruple surrounding-gate). All cross-sectional figures are extracted at 1 nm below the lateral-side and bottom-gate oxides. 116

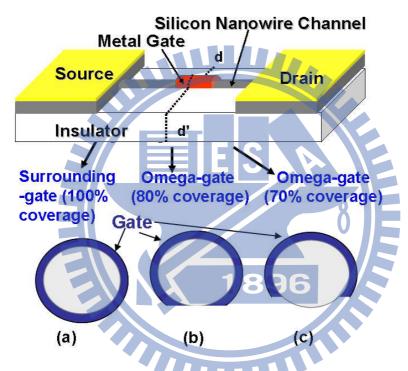

| 4.28 | The 16-nm-gate silicon nanowire transistor with structures of (a) surrounding- |

|------|--------------------------------------------------------------------------------|

|      | gate (i.e., 100% coverage), (b) the omega-gate with 80% coverage-ratio,        |

|      | and (c) the omega-gate with 70% coverage-ratio                                 |

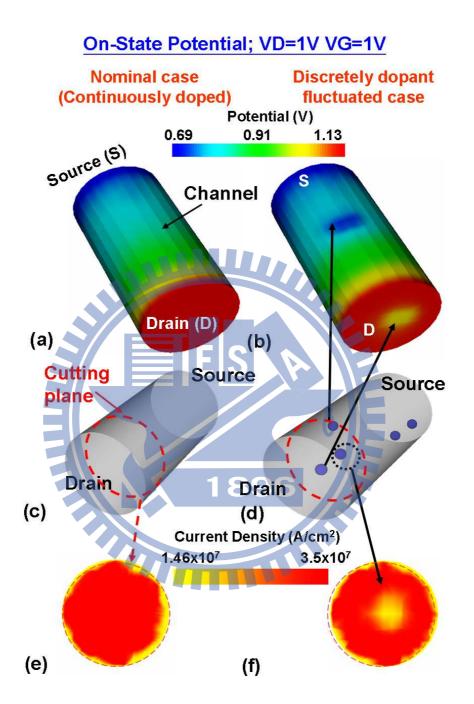

| 4.29 | Comparison of the on-state potential ((a) and (b)), the current density dis-   |

|      | tributions ((e) and (f)) of the (c) the nominal case and (d) discretely doped  |

|      | cases. The potential fluctuations are induced by corresponding dopants in (d)) |

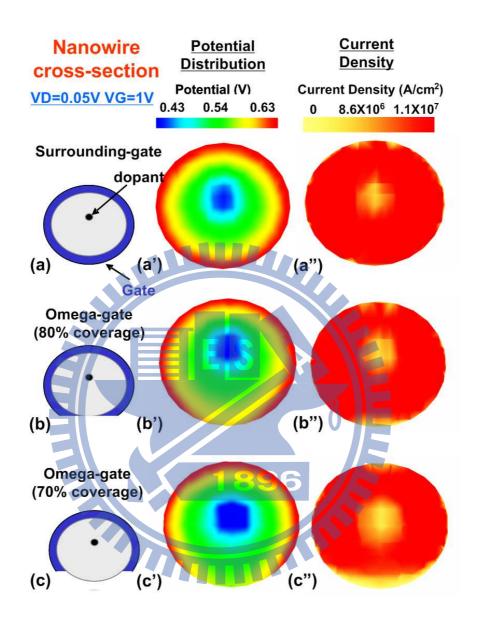

| 4.30 | Comparison of potential (plots of (a'), (b'), and (c')) and current den-       |

|      | sity distribution (plots of (a"), (b"), and (c")) in nanowire transistors with |

|      | surrounding-gate (100% gate-coverage-ratio) and omega-gate (80% and            |

|      | 70% gate-coverage-ratio) structures                                            |

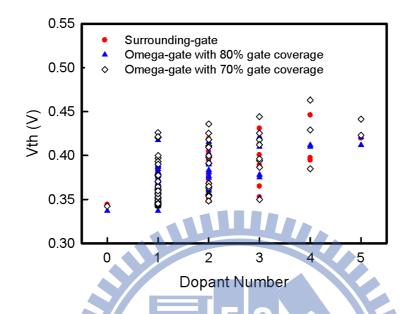

| 4.31 | Comparison of the threshold voltage fluctuation of the 16-nm-gate sili-        |

|      | con nanowire FET with surrounding-gate, omega-gate with 80%, and 70%           |

|      | gate-coverage-ratio                                                            |

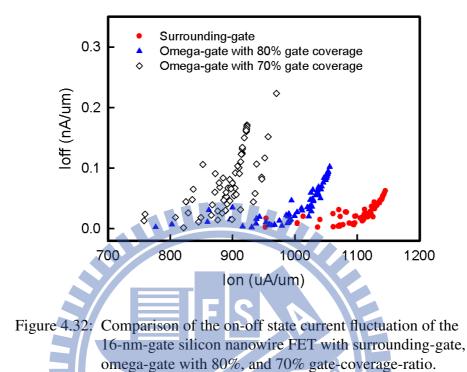

| 4.32 | Comparison of the on-off state current fluctuation of the 16-nm-gate sili-     |

|      | con nanowire FET with surrounding-gate, omega-gate with $80\%$ , and $70\%$    |

|      | gate-coverage-ratio                                                            |

| 4.33 | Effect of discrete-dopant-position in silicon nanowire FET, where the de-      |

|      | vices are with different $I_{on}$ but similar $I_{off}$                        |

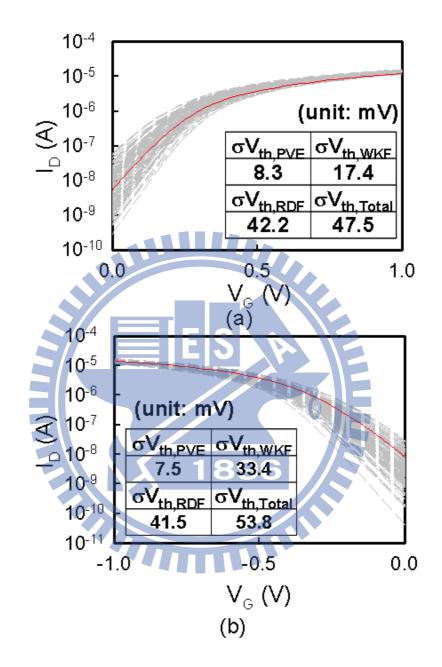

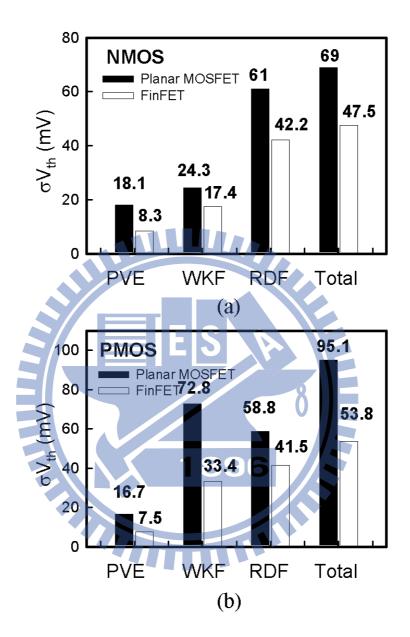

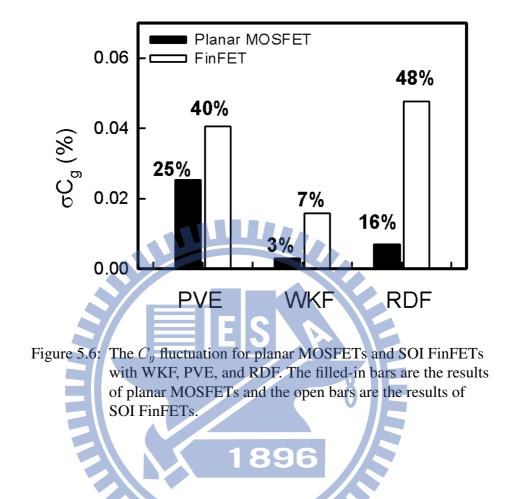

| 5.3 | The summarized $V_{th}$ fluctuation for (a) NMOSFETs and (b) PMOSFETs,                                       |

|-----|--------------------------------------------------------------------------------------------------------------|

|     | where the filled-in bars are the results of planar MOSFETs and the open                                      |

|     | bard are the results of FinFETs                                                                              |

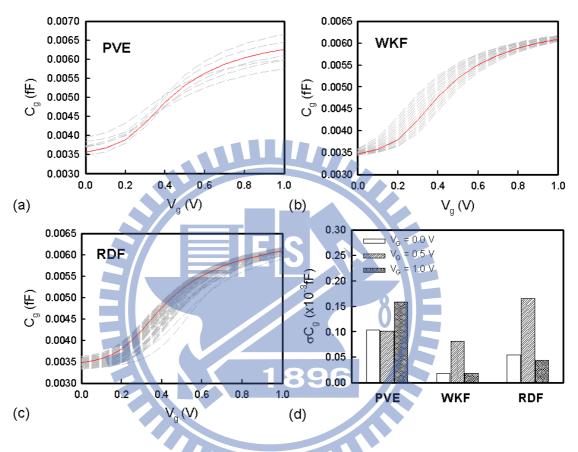

| 5.4 | The $C_g$ - $V_G$ characteristics for the explored devices with (a) PVE, (b) WKF,                            |

|     | and (c) RDF. (d) The $C_g$ fluctuation for 16-nm-gate MOSFETs with WKF,                                      |

|     | PVE, and RDF. The applied voltage for the bars are $V_G = 0, 0.5, \text{ and } 1 \text{ V},$<br>respectively |

|     | respectively                                                                                                 |

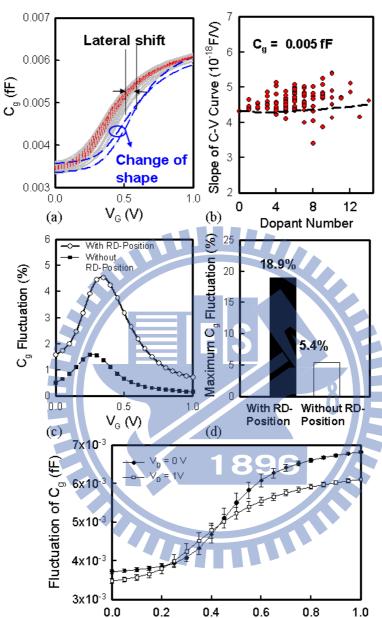

| 5.5 | The (a) $C_g$ - $V_G$ curves and (b) the slope of the $C_g$ - $V_G$ curves for cases                         |

|     | with and without taking random-dopant-position effect into consideration,                                    |

|     | where the solid line shows the nominal case and the dashed lines are random-                                 |

|     | dopant-fluctuated devices. The solid and dot lines in (a) are the cases with                                 |

|     | and without random-dopant-position effect, respectively. The dash line in                                    |

|     | (b) indicates the cases without random-dopant-position effect, and the sym-                                  |

|     | bols are the cases with random-dopant-position effect. The (c) normalized                                    |

|     | gate capacitance fluctuation and (d) maximum gate capacitance fluctuation                                    |

|     | are calculated. (e) The C fluctuation with different drain bias                                              |

- 6.3 (a) The voltage transfer curves for the studied 16-nm-gate planar MOSFET circuit. (b) The noise margins, NM<sub>L</sub> and NM<sub>H</sub>, as a function of the dopant number in the NMOSFET and PMOSFET.

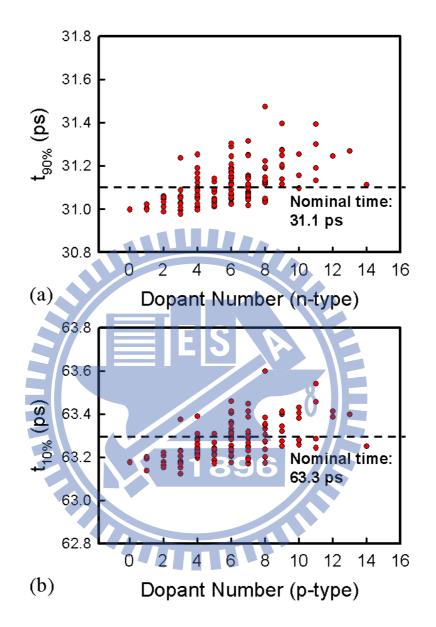

| 6.4  | (a) The input and output signals for the discrete-dopant-fluctuated 16-nm-         |

|------|------------------------------------------------------------------------------------|

|      | gate planar inverter circuit. The magnified plots show (b) the fall and (c)        |

|      | the rise transitions, where the rise time, fall time, high-to-low delay time,      |

|      | and low-to-high delay time are defined                                             |

| 6.5  | The fluctuations of (a) fall and (b) rise signal transition points as a function   |

|      | of dopant number in n-type and p-type MOSFETs for the discrete dopant              |

|      | fluctuated inverter circuits                                                       |

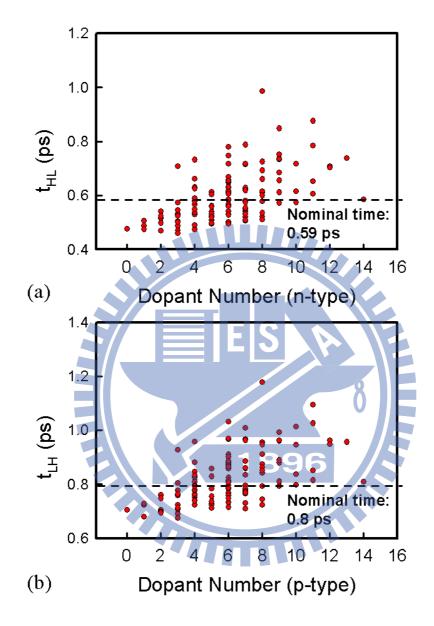

| 6.6  | The fluctuations of (a) high-to-low and (b) low-to-high delay time as a            |

|      | function of dopant number in n-type and p-type MOSFETs for the discrete            |

|      | dopant fluctuated inverter circuits                                                |

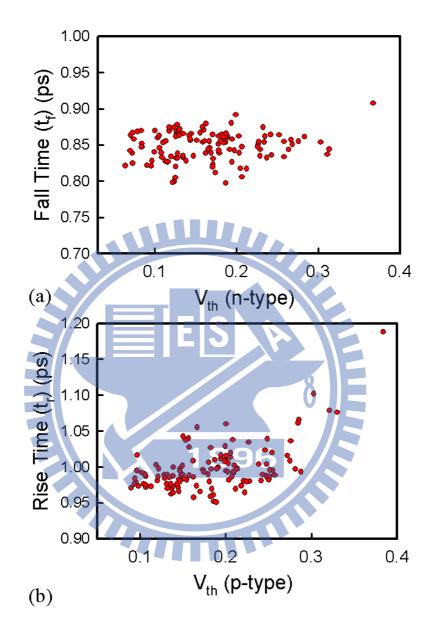

| 6.7  | The fluctuations of (a) the fall and (b) rise time as a function of the thresh-    |

|      | old voltage in the n-type and p-type MOSFETs for the discrete-dopant-              |

|      | fluctuated CMOS inverters                                                          |

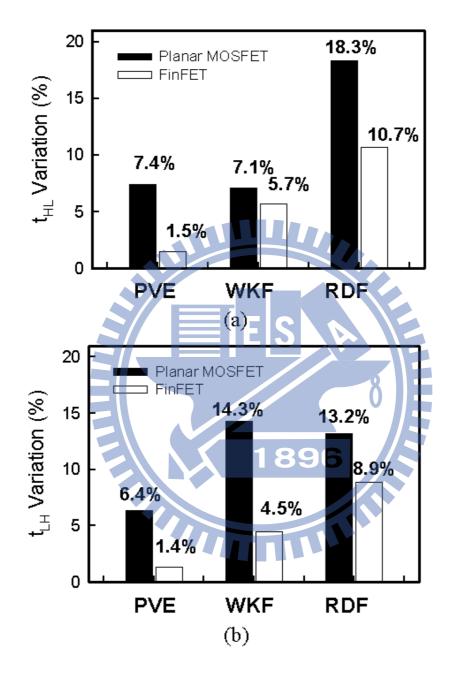

| 6.8  | Comparison of the variations of (a) $t_{HL}$ and (b) $t_{LH}$ with respect to WKF, |

|      | PVE, and RDF for the planar MOSFETs and FinFETs                                    |

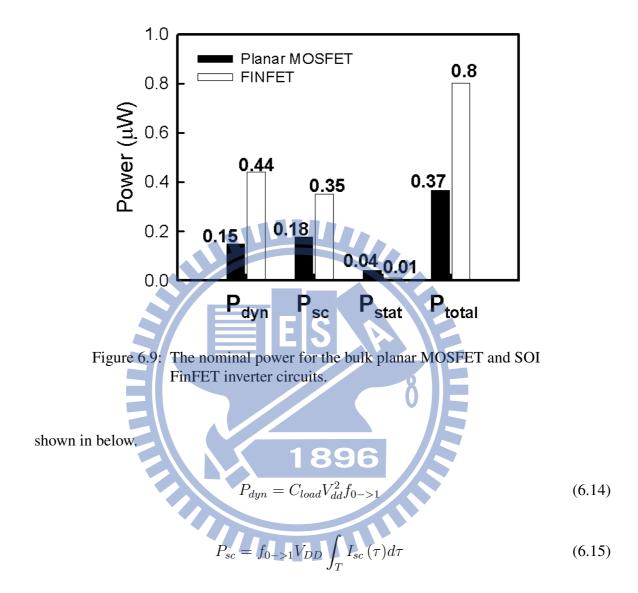

| 6.9  | The nominal power for the bulk planar MOSFET and SOI FinFET inverter               |

|      | circuits                                                                           |

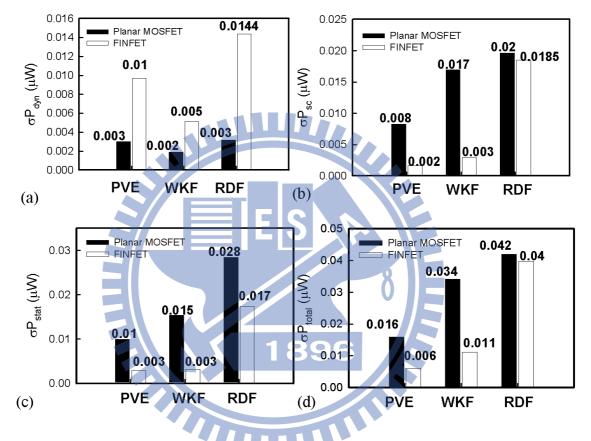

| 6.10 | The (a) dynamic power, (b) short-circuit power, (c) static power, and (d)          |

|      | total power fluctuations for the explored devices with WKF, PVE, and RDF. 165      |

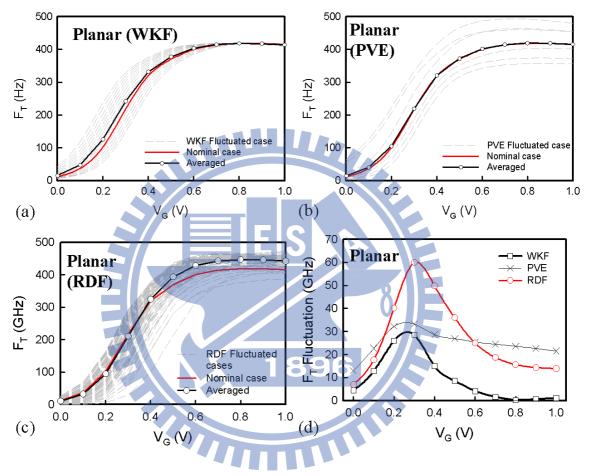

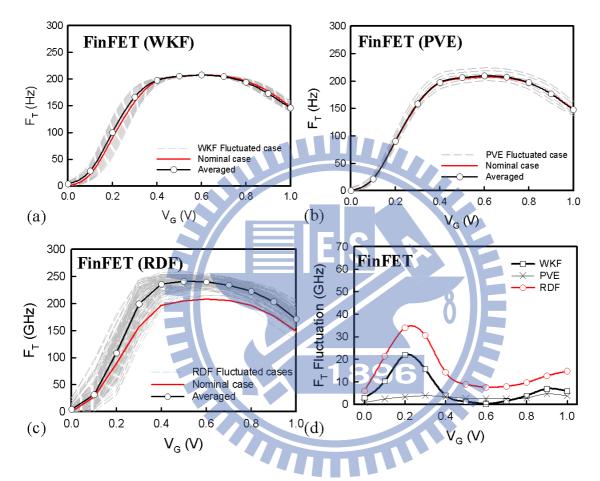

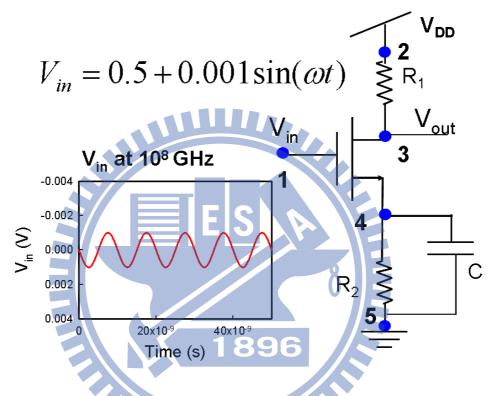

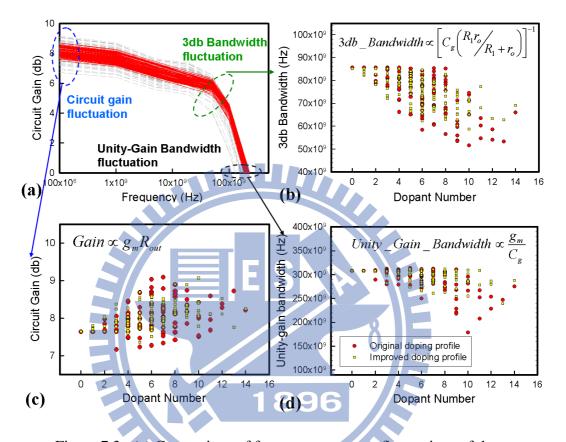

| 6.11 The common-source circuit is used as a tested circuit to explore the fluctu-            |

|----------------------------------------------------------------------------------------------|

| ation of high-frequency characteristics. The input signal is a sinusoid input                |

| wave with 0.5 V offset. The frequency is sweep from $1 \times 10^8$ Hz to $1 \times 10^{13}$ |

| Hz                                                                                           |

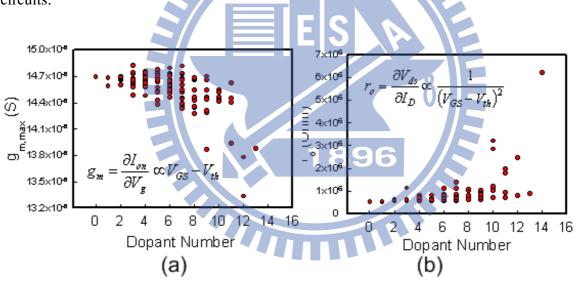

| 6.12 DC characteristic fluctuations of (a) $g_{m,max}$ , and (b) $r_o$ of the 125 discrete   |

| dopant fluctuated 16-nm-gate planar MOSFET. The definitions are shown in the insets          |

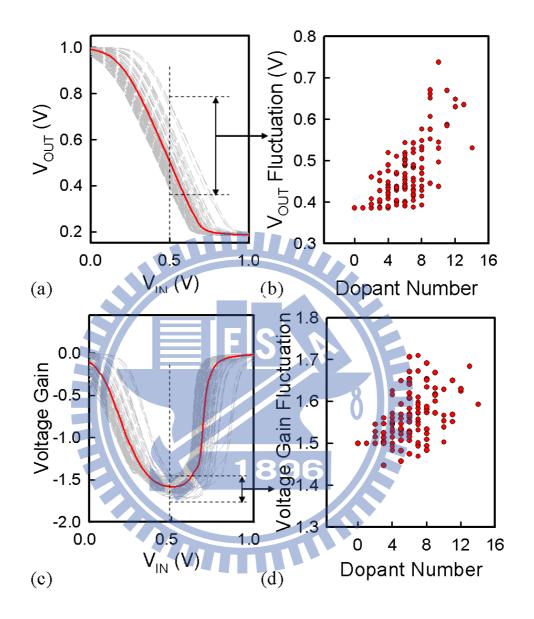

| 6.13 The (a) voltage-transfer-curve, (b) the output voltage, (c) the voltage gain,           |

| (d) and the fluctuation of voltage gain for the studied discrete-dopant-fluctuated           |

| 16-nm-gate common-source circuits. The solid line shows the capacitance                      |

| of the nominal case (continuously doped channel with $1.48 \times 10^{18} \ { m cm}^{-3}$    |

| doping concentration) and the dashed lines are the random-dopant-fluctuated                  |

| devices                                                                                      |

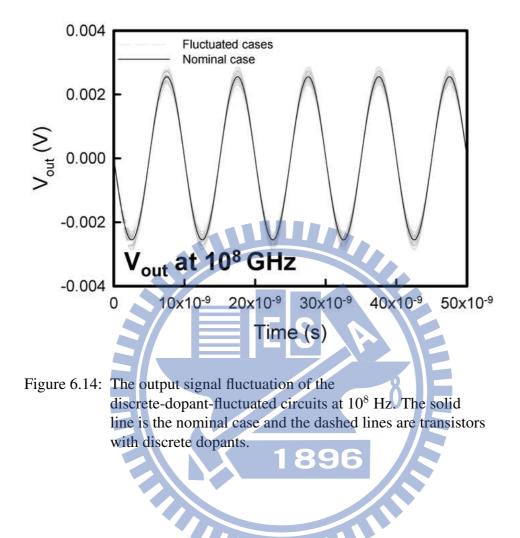

| 6.14 The output signal fluctuation of the discrete-dopant-fluctuated circuits at             |

| $10^8$ Hz. The solid line is the nominal case and the dashed lines are transis-              |

| tors with discrete dopants                                                                   |

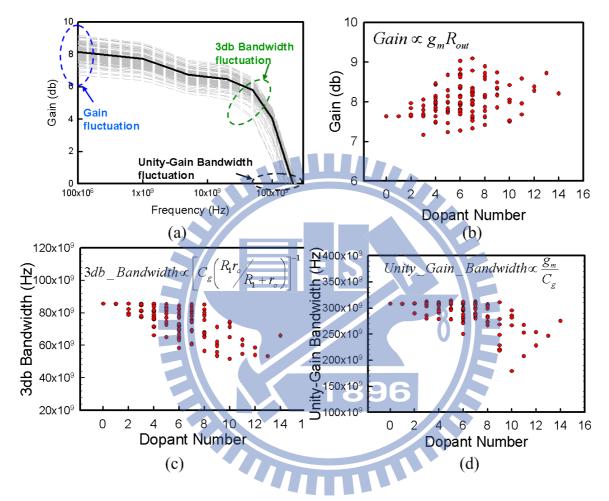

| 6.15 The (a) frequency response, (b) high-frequency circuit gain, (c) 3dB band-              |

| width, (d) and unity-gain bandwidth fluctuations of the studied discrete-                    |

| dopant-fluctuated 16-nm-gate common-source circuits                                          |

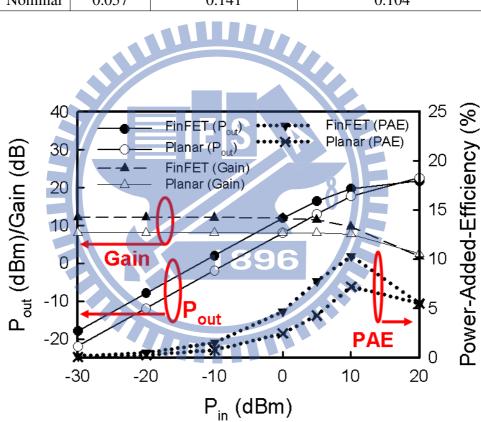

| 6.16 | Output power, circuit gain, and power-added-efficiency of the explored de-                        |

|------|---------------------------------------------------------------------------------------------------|

|      | vices as a function of input power                                                                |

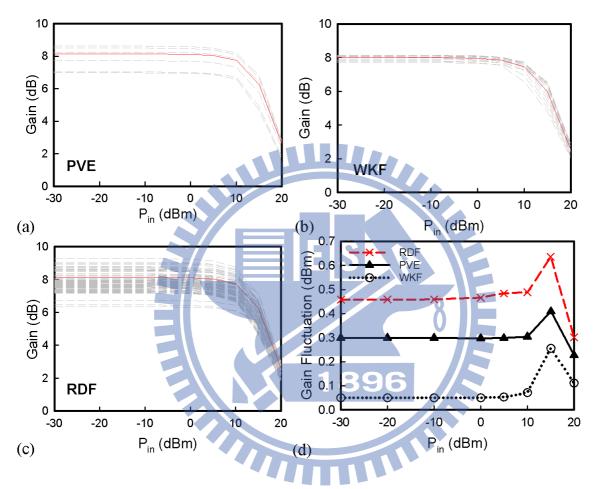

| 6.17 | The circuit gain characteristics of the planar MOSFETs with (a)PVE, (b)WKF,                       |

|      | and (c)RDF fluctuations, respectively. (d) The summarized circuit fluctua-                        |

|      | tions                                                                                             |

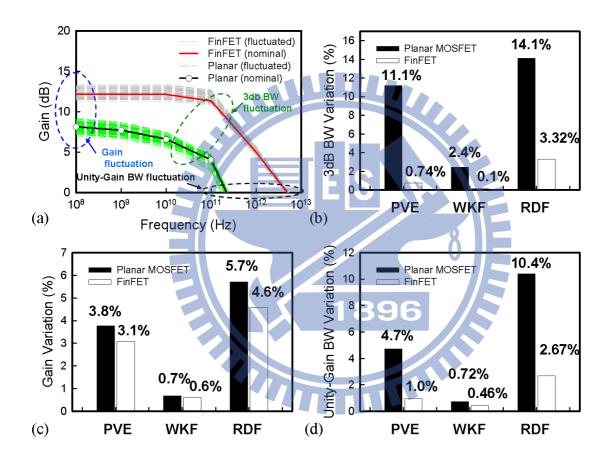

| 6.18 | (a) The frequency response of the planar MOSFET and FinFET common-                                |

|      | source amplifiers, in which (b) 3dB bandwidth, (c) gain, and (d) unity-gain                       |

|      | bandwidth are extracted                                                                           |

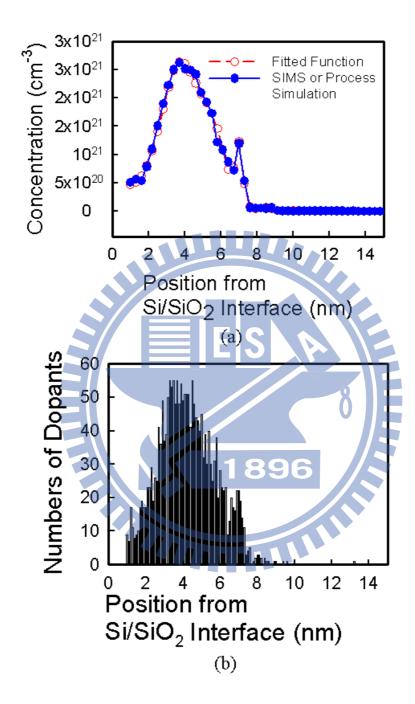

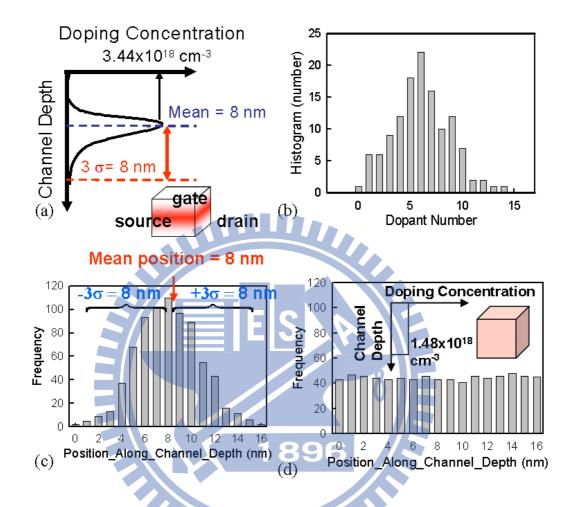

| 7.1  | There will be 758 dopants are within a large rectangular solid, in which the                      |

|      | equivalent doping concentration is $1.48 \times 10^{18}$ cm <sup>+3</sup> ). The dopant distribu- |

|      | tion in the direction of channel depth follows the normal distribution (a).                       |

|      | Similarly, dopants within the $(16 \text{ nm})^3$ cubes may vary from zero to 14 (the             |

|      | average number is six) (b). The vertical dopant distribution of the vertical                      |

|      | doping profile engineering and the original doping profile are shown in (c)                       |

|      | and (d), respectively                                                                             |

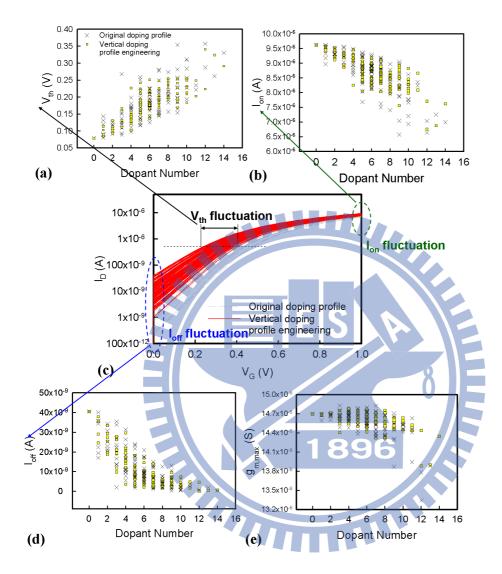

| 7.2  | DC characteristic fluctuations of the 250 discrete dopant fluctuated 16-nm-                       |

|      | gate planar MOSFET from the original and the improved doping profile.                             |

|      | The studied fluctuations of (a) threshold voltage, (b) on-state current, (c)                      |

$I_D$ - $V_G$  curves, (d) off-state current, (e) and maximum transconductance. . . 184

- 7.5 The explored  $I_D$ - $V_G$  and high frequency response characteristics for the proposed inverse lateral asymmetry doping profile and original doping profile.189

# **Chapter 1**

# Introduction

This chapter presents an introduction of this thesis. It begins with an introduction of nanoscale transistors, and its structure evolution from planar device to vertical channel, such as double-gate, triple-gate, and surrounding-gate transistors. The literature review of current research status and motivation are then introduced.

# 1.1 Toward Nanoscale Transistor Era

Evolution of complementary metal-oxide-semiconductor (CMOS) technology in the past 40 years has followed the path of device scaling for achieving density, speed and power improvements. The 2007 International Roadmap for Semiconductors (ITRS) projected that sub-l0-nm-gate length will be launched before 2015[1]. The most critical issues for

continuing the device scaling will be performance enhancement (short channel effect, leakage current, power consumption, and so on) and yield (intrinsic parameter fluctuations). In the past several decades, planar metal-oxide-semiconductor FETs (MOSFETs) have been the core of very-large-scale integration (VLSI) circuits and memories [2,3]; however, as gate length scales, they started to suffer from undesirable short-channel effects (SCEs) in scaled dimensions. The significant SCEs not only increases standby power dissipation, but also enlarges electrical characteristic fluctuations, such as the deviation of threshold voltage, drive current, mismatch, and so on. Various technologies, such as, mobility enhancement [4,5], metal-gate with high- $\kappa$  dielectrics [6-8], optimal doping profile design [9-11], lithography [12-14], vertical channel transistor [15-39], have been proposed to enhance the transistor performance.

Figure 1.1: The major sources of intrinsic parameter fluctuations: the gate length deviation, line edge roughness, and random dopant fluctuation [15].

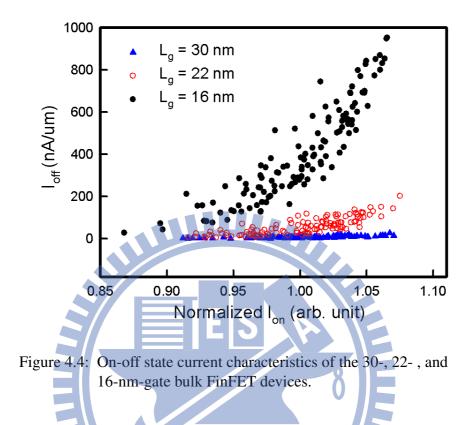

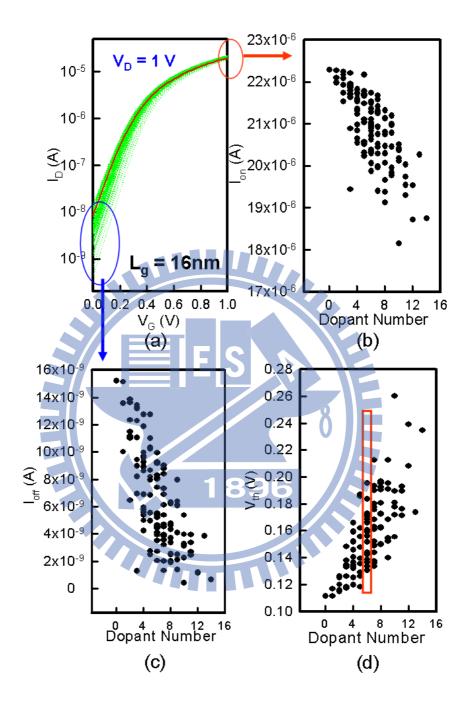

Figure 1.3: Experimental  $I_{on}$ - $I_{off}$  characteristics of NMOSFETs with  $L_g$  down to 20 nm for the (a) width = 200 nm and (b) width = 20 nm at  $V_D$  = 1.0 V. The  $I_{on}$  was normalized against the on-current of nominal  $L_g$  case, i.e. the 20 nm  $L_g$  case.

Gate lengths of scaled MOSFETs are now under 30 nm in 45-nm node high-performance circuits [5,40-43]. Transistor scaling down to sub-20 nm and even beyond has been widely noticed encountering much more challenges at short channel control than previous generations. The worsened short channel control enlarges electrical characteristic fluctuations, such as the deviation of threshold voltage, drive current, mis-match, and so on. Yield analysis and optimization, which take into account the manufacturing tolerances, model uncertainties, variations in the process parameters, etc., are known as indispensable components of the circuit design methodology [44-48]. Additionally, the fluctuation is intrinsically increased with the scaling of transistor feature size, even not considering worsened short channel control [15,20-27]. Figure 1.1 shows the major sources of intrinsic parameter fluctuations, including the gate length deviation [15, 27, 36, 57-61], line edge roughness [15, 27, 36, 57-61], and random dopant fluctuation [21-27,62-89]. The fluctuation caused by granularity of the poly-silicon gate [90-93], silicon film thickness variation [94,95], and random telegraph signal [96,97] are also important factors in device intrinsic fluctuation, which dependents on the device structure. Figures 1.2 and 1.3 show the experimental  $V_{th}$  fluctuation and the on- and off-state currents ( $I_{on}$ - $I_{off}$ ) characteristics of the n-typed MOSFETs (NMOSFETs) down to 20 nm gates. The gate length  $L_q$  values in Fig. 1.2 are estimated from the gate capacitances in analysis data, and we presume the widths of all samples in Figs. 1.2(a) and 1.2(b) are 200 nm and 20 nm, respectively. As expected, the

$\sigma V_{th}$  roll-off characteristics of 20-nm-wide devices are much more scattered than that of 200 nm-wide devices. Notably, in Fig. 1.2, the maximum  $V_{th}$  difference for 20-nm-gate length device has approached 150 mV, which is larger than the desired  $V_{th}$ , 140 mV. The  $I_{on}$ - $I_{off}$  characteristic fluctuation becomes even worsened in Fig. 1.3. The maximum  $V_{th}$  difference for 20-nm-gate length device is over 250 mV; moreover, in some cases, their  $V_{th}$  are zero and can not be used in circuits and systems.

## **1.2 Vertical Channel Transistor Architecture**

As the gate lengths of MOSFETs scales below sub-30 nm, the Field effect transistors (FETs) with multiple-gate structures, such as fin-type FETs (FinFETs) have been of great interest due to the excellent controlling ability of carriers in the device's channel, which suppressed the short-channel effect [15-17]. The succession of device structure from planar to vertical channel transistors has become the main trend in VLSI technologies. Figure 1.4 plots an evolution of transistor architecture from planar MOSFETS to ultra-thinbody silicon-on-insulator (UTB SOI), double-gate, omega gate, and nanowire FinFETs. The transistors with vertical channel are with large gate-to-channel coverage ratio and have very thin body to control short-channel-effect.

Figure 1.4: The evolution of transistor architecture from planar MOSFETs to ultra-thin-body silicon-on-insulator, double-gate, omega gate, and nanowire FinFETs.

### **1.2.1** FinFET Process Steps

This section presents the manufacturing process of 25-nm-gate FinFETs. The process result is exhibited. The process simulation is similar to the sub-10-nm-gate nanowire FinFETs in [15-17,20], which is the state-of-art nanowire FinFETs transistor. The process flow used in this work is summarized:

- 1. Si fin and STI patterning, T<sub>si</sub> trimmed down upon STI etching;

- 2. Well and threshold voltage implantation;

- 3. Gate oxide growth (physical thickness 1.4 nm);

- 4. Gate deposition (in-situ doped N<sup>+</sup> poly silicon);

- 5. Poly Si chemical mechanical polishing;

- 6. Gate hard mask deposited and patterning (Hard mask trimmed down upon etching);

- 7. Poly gate etching;

- 8. Pocket and lightly doped drain (LDD) implantation;

- 9. Oxide/Nitride combo spacer formation;

- 10. Source/Drain implant;

- 11. Low-thermal-budget activation process;

- 12. Contact formation; and

- 13. Copper interconnect.

After Si fin patterning and shallow-trench isolation (STI) formation, the device width is trimmed down upon STI etching. Well and threshold voltage implantation are performed to adjust threshold voltage  $(V_{th})$  of transistor. Then, to relieve the etch damage, a sacrificial oxide is removed before gate oxidation. Thermal oxide is grown and in-situ heavily doped N<sup>+</sup> poly-silicon is deposited. After the deposition and trimmed down of gate hard mask, the pocket and lightly doped drain (LDD) implantation techniques are used for the suppression of the short channel effect and hot carrier effect. Composite spacer of silicon oxide and nitride is deposited and etched anisotropically. After the gate and spacer formation, heavily doped N<sup>+</sup> junction are made with Phosphorous implantation. Low-thermal-budget activation process is used for dopant activation and control of doping profile. After interlayer-dielectric deposition, wolfram is used for metal contact plugging and copper is used for interconnection. Finally, alloying anneal is performed. We notice that the narrow width device trimmed down upon STI etching and low-thermal-budget activation process are the critical steps in fabrication of nanoscale FinFET transistor.

# 1.2.2 Process Simulation Using TCAD

The process simulation of FinFET is presented by using TCAD simulator [134]. Figure 1.5 presents the simulation result. After the Si fin patterning, STI patterning, and trimming, a silicon fin with substrate are formed, as displayed in Fig. 1.5(a"). The dark brown region in Fig. 1.5(a) and white region in Fig. 1.5(a") are SiO<sub>2</sub>. The doping concentration in this step is background doping with  $1.0 \times 10^{15}$  cm<sup>-3</sup> boron concentration. Figures 1.5(b)- 1.5(b")

Figure 1.5: The process simulation result for FinFETs. ((a)-(a"))The device structure after Si fin patterning, STI. The doping concentration in this step is background doping with  $1.0 \times 10^{15}$  cm<sup>-3</sup> boron concentration.((b)-(b"))After Well/V<sub>th</sub> implantation and annealing, the dopants are activated after thermal annealing. The fabrication process then goes to gate formulation, pocket and LDD implantation. The gate oxide is formulated after the gate oxide growth ((c)-(c")). ((d)-(d"))After spacer formation and source/drain implantation, the final device structure is shown.

shows the doping concentration after the well and threshold voltage implantation. The dopants are activated after thermal annealing. The fabrication process then goes to gate formulation, pocket and LDD implantation. The gate oxide is formulated after the gate oxide growth, as shown in Fig. 1.5(c'). The structure of heavily doped poly-silicon gate is then constructed and displayed in Fig. 1.5(c). The results of spacer and final source/drain implantation are presented in Fig. 1.5(d)- 1.5(d'').

## **1.3 Current Research Status and Motivation**

This section reviews the current status of research and problem. Then the motivation of this thesis is drawn. The problems is first addressed as below.

- 1. There have been many studies of the intrinsic parameter fluctuations, including the process variation [15,27,36,57-61], random dopant fluctuation [21-27,62-89], and poly-silicon gate [90-93] on planar MOSFETs. However, the studies of FinFETs fluctuation is not enough [15,23,27,55,84]. Moreover, the extensive exploration of multi-gate channel transistor as well as comparison with planar MOSFETs are lacked.

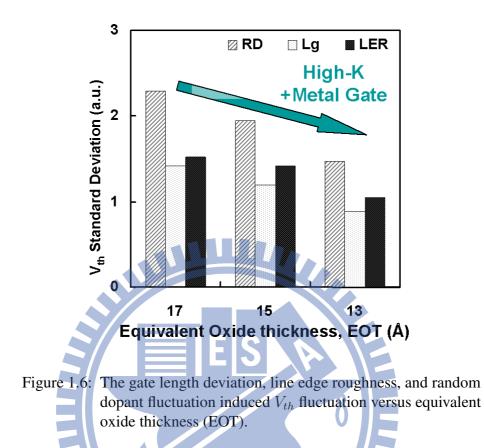

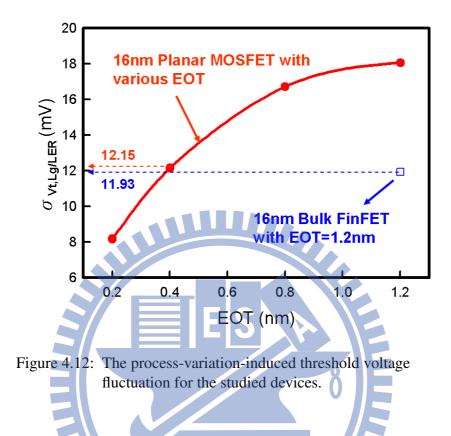

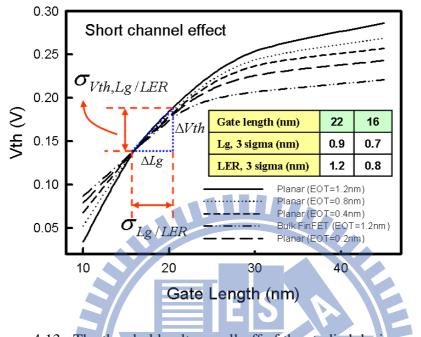

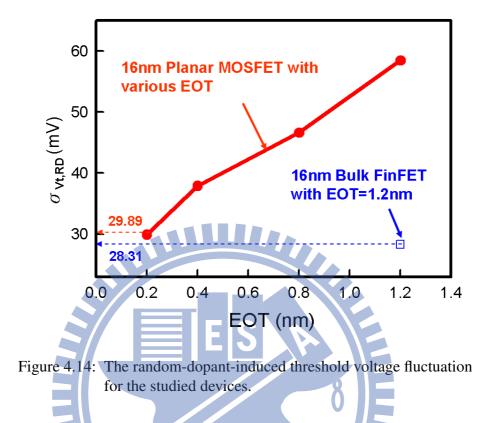

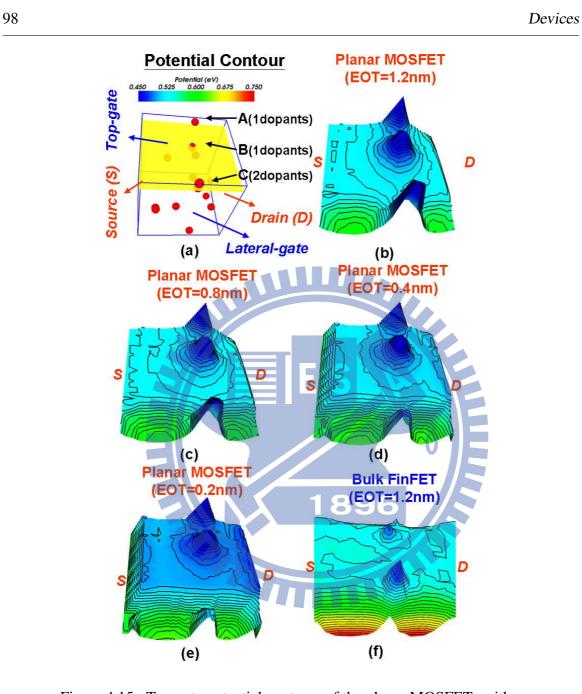

- 2. The use thin gate oxide becomes an important alternative research object [63] to further suppress the impact of fluctuation. Figure 1.6 shows the gate length deviation, line edge roughness, and random dopant fluctuation induced  $V_{th}$  fluctuation versus

equivalent oxide thickness (EOT). The EOT reduction can be achieved by the introduction of metal-gate and high- $\kappa$  dielectric for low standby power devices. All of the comparisons are based on the same off-sate (leakage) current. In principal, the standard deviation of  $V_{th}$  induced by the three aforementioned sources can all be reduced with decreased gate dielectric thickness, due to less surface potential perturbation under the enhanced gate controllability. This improvement will depend on implementation of reliable high- $\kappa$  gate dielectrics and well work-function modulated

89

metal gate.

- 3. High-κ/metal-gate technology has been recently recognized as the key to sub-45 nm transistor fabrication due to the small gate leakage current with an increased gate capacitance. Moreover, the sheet resistance is reduced with the use of metal as gate material. Comparing to the poly-gate technology, the metal-gate material will not react with high-κ material and therefore there existing less interface charge and V<sub>th</sub> pinning effect. The gate depletion in poly-gate material is no longer existed. Additionally, the phono scattering effect is significantly reduced due to the less quantum resonance effect. However, the use of metal as a gate material introduces a new source of random variation due to the dependency of workfunction on the orientation of metal grains [121,122]. The grain orientation of metal is uncontrollable during growth period.

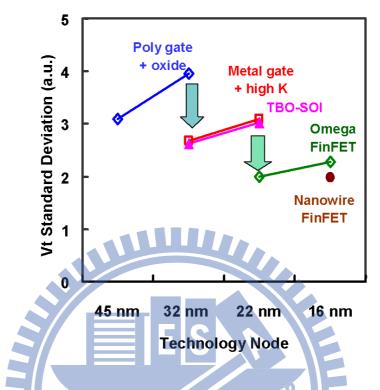

- 4. The use of vertical channel transistor to suppress the intrinsic parameter fluctuation is crucial. Figure 1.7 reviews the threshold voltage (V<sub>th</sub>) fluctuation versus technology node [15]. At 32-nm node, the thinner gate dielectric thickness could be achieved by the introduction of metal gate (for eliminating poly depletion) and high-κ (for thinner equivalent-oxide thickness but not increasing gate leakage) materials. Another opportunity is not scaling gate dielectric thickness but enhancing short channel control with SOI substrate. Special attention will be paid to thin-buried-oxide SOI [49]. At sub-22 nm node, planar SOI will no more be a good device option, because

Figure 1.7: The threshold voltage fluctuation versus technology node.

very thin body (less than 10 nm) is necessary for SCE control but meanwhile the thin body will degrade drive current due to "quantum confinement" [50]. Then non-planar transistors such as FinFETs may emerge instead [51-56]. Their  $V_{th}$  fluctuation characteristics should be addressed as well.

5. So far the most of aforementioned works are focused on the fluctuation of DC characteristics, the investigation of device's AC as well as circuit's fluctuations are lacked [84-91]. Though several works have addressed the importance of device variability in circuit, the simulation approach uses the compact model, which can not capture

the random-dopant-position induced fluctuation and may underestimate the influence of fluctuation.

To deal with the aforementioned problems, this work extensively study the FinFET variability and its fluctuation on circuits by a statistically-sound 3D "atomistic" coupled devicecircuit simulation approach [64-67,115-118]. The impact of individual fluctuation sources, consisting of gate length deviation, line edge roughness, random-dopant-fluctuation, and workfunction fluctuation, on the device's DC/AC and circuit's timing/power/high-frequency characteristic fluctuations are explored. The dominant fluctuation source in each characteristics are found. For the device characteristic fluctuations, the "atomistic" simulation approach is effective to capture not only the randomness of doping concentration but also the random placement of dopants induced device variability. Moreover, a statistic simulation approach is applied to characterize the emerging workfunction fluctuation induced variability. The physical model of devices has been calibrated with experiential data [15-17,63]. To accurately describe the device variability in circuits, the circuit characteristics fluctuation are obtained by solving the both device transport and circuit nodal equations (so it's called coupled device-circuit simulation). Unlike the compact model simulation approach, the coupled device-circuit simulation approach solves the device transport characteristics in circuit simulation and therefore provide the most device physics inside circuit

fluctuation. The extensive study assesses the fluctuations on circuit performance and reliability, which can in turn be used to optimize nanoscale MOSFET and circuits.

# 1.4 Outline

This dissertation is organized as follows. Chapter 2 shows the used device model and numerical methods. The quantum-mechanical corrected transport equations and numerical simulation methods are introduced, where a nanoscale FinFET is used as an example for simulation and calibration. Chapter 3 introduces the computer characterization technique for studying the effect of intrinsic parameter fluctuations including process-variation-effect (PVE), random dopant fluctuation (RDF), and workfunction fluctuation (WKF). The accuracy of characterization has been confirmed. Chapter 4 presents the random-dopantinduced characteristics fluctuation in vertical-channel transistors, where the impact of discrete dopant fluctuation on transistor physical and electrical characteristics are explored. This chapter also extensively explores the random-dopant-fluctuation in SOI transistors from single-gate to double-gate, triple-gate, and surrounding-gate transistor architectures. The effect of surrounding-gate coverage ratio on fluctuation resistivity is also discussed. Chapter 5 examines the impact of the intrinsic parameter fluctuations, PVE, RDF, WKF, in nanoscale FinFETs. The implications of device variability in circuits are explored in Chapter 6, in which the coupled device-circuit simulation approach is used instead of compact modeling approach for pursuing best accuracy. Finally, conclusions are drawn, suppression technique are prospected, and future work is suggested.

# **Chapter 2**

tions

# **Device Model and Numerical Methods**

2.1 The Quantum-Mechanical Corrected Transport Equa-

## 2.1.1 The Density-Gradient Equations

The technology computer-aided design (TCAD) simulations, such as process and device simulations, are widely used for the analysis of semiconductor devices. The process simulation can generate the device geometry and doping profile according to the parameters of the fabrication processes. The output of process simulation is then used in the device simulation to estimate device characteristics. The drift-diffusion (DD) and hydrodynamic (HD) models play a crucial role in the development of semiconductor device simulator in the macroscopic point of view. The DD model was derived from Maxwell's equation as well as charges' conservation law and has been successfully applied to study device transport behavior, in the past decades. It assumes local isothermal conditions and is still widely employed in semiconductor device design.

Classical drift-diffusion model consists of at least three coupled partial differential equations (PDEs) for, such as electrostatic potential and electron-hole densities. When device channel is specified, a set of the DD equations in semiconductor device simulation is solved:

$$\Delta \phi = \frac{q}{\varepsilon_s} (n - p + D), \qquad (2.1)$$

$$\frac{1}{q} \nabla \cdot J_n = R(n, p), \qquad (2.2)$$

and

$$\nabla \cdot J_p = -R(n,p), \tag{2.3}$$

where  $\phi$  is the electrostatic potential and its unit is volt. n and p are classical electron and hole concentrations ( $cm^{-3}$ ). q is the elementary charge and its unit is coulomb. The net doping concentration is  $D(x, y, z) = N_D^+(x, y, z) - N_A^-(x, y, z)$ . R is the net recombination rate ( $cm^{-3}s^{-1}$ ). The carrier's currents densities are given by

$$J_n = -q\mu_n n \bigtriangledown \phi + qD_n \bigtriangledown n, \tag{2.4}$$

and

$$J_p = -q\mu_p p \bigtriangledown \phi - qD_p \bigtriangledown p, \tag{2.5}$$

where  $\mu_n$  and  $\mu_p$  are the carrier mobility  $(cm^2/V - s)$ . The diffusion coefficients,  $D_n$  and  $D_p$   $(cm^2/s)$ , satisfy the Einstein relation.

The quantum mechanical effects should be considered in the device simulation when the dimensions of the devices shrunk into nanometer scale. Various theoretical approaches have been presented to study the quantum confinement effects, such as full quantum mechanical model (e.g. nonequilibrium Green's function) and quantum corrections to the classical drift-diffusion (DD) or hydrodynamic (HD) transport models. A set of Schrödinger-Poisson (SP) equations has been applied to study the quantum confinement effect in the inversion layers as well as the quantum transport between source and drain, but it is a timeconsuming task in the TCAD application to realistic device characterization. Therefore, various quantum correction models, density gradient (DG) [99-103], Hänsch[104], modified local density approximation (MLDA)[105], effective potential (EP)[106-108], and unitfied quantum correction Model[109], have been proposed for classical DD or HD transport models. In this investigation, the density gradient was coupled with the DD model and solved for the quantum mechanical effects. The density gradient equation can be expressed as,

$$\vec{J_n} = -q\mu_n n \bigtriangledown \phi + qD_n \bigtriangledown n - qn\mu_n \bigtriangledown \gamma_n, \tag{2.6}$$

$$\vec{J_p} = -q\mu_p p \bigtriangledown \phi - qD_p \bigtriangledown p + qp\mu_p \bigtriangledown \gamma_p, \tag{2.7}$$

where  $\gamma_n$  and  $\gamma_p$  are the quantum potentials for electrons and holes.  $\gamma_n = 2b_n \frac{\nabla^2 \sqrt{n}}{\sqrt{n}}$ .  $\gamma_p = 2b_p \frac{\nabla^2 \sqrt{p}}{\sqrt{p}} b_n$  and  $b_p$  are density-gradient coefficients for electrons and holes.  $b_n = \hbar^2/(12qm_n^*)$  and  $b_p = \hbar^2/(12qm_p^*)$ .  $m_n^*$  and  $m_p^*$  are effective masses for the electrons and holes.  $\hbar$  is the Planck constant.  $b_n$  and  $b_p$  in Eqs. (2.6) and (2.7) are the density gradient coefficient which determines the strength of the gradient effect in the electron and hole gas. The last term in the right hand side of Eqs. (2.6) and (2.7) are referred to as "quantum diffusion", which makes the electron continuity equation has a fourth-order partial differential equation. Therefore, such an approach is highly sensitive to noise in the local carrier density, and the methodology is highly important in cases of strong quantization. To calculate the numerical solution of the multidimensional density-gradient model, firstly we decouple the coupled partial differential equations (PDEs); approximated with the finite volume method over nonuniform mesh. The corresponding system of the nonlinear algebraic equations is then solved with the monotone iteration methods. Iteration will be terminated and post-processes will be performed when the specified stopping criteria for inner and outer iteration loops are satisfied, respectively.

#### 2.1.2 The Mobility Model

According to Mathiessen's rule [113,114], the mobility model used in the device simulation can be expressed as:

$$\frac{1}{\mu} = \frac{D}{\mu_{surf\_aps}} + \frac{D}{\mu_{surf\_rs}} + \frac{1}{\mu_{bulk}},$$

(2.8)

where  $D = \exp(x/l_{crit})$ , x is the distance from the interface and  $l_{crit}$  is a fitting parameter. The mobility consists of three parts: (1) the surface contribution due to acoustic phonon scattering, where  $N_i = N_A + N_D$ ,  $T_0 = 300$  K, E is the transverse electric field normal to the interface of semiconductor and insulator, B and C are parameters which based on physically derived quantities,  $N_0$  and  $\tau$  are fitting parameters, T is lattice temperature, and K is the temperature dependence of the probability of surface phonon scattering; (2) the contribution attributed to surface roughness scattering is  $\mu_{surf,aps} = \frac{B}{E} + \frac{C(N_i/N_0)^{\tau}}{E^{1/3}(T/T_0)^K}$ , where  $\Xi = A + \frac{\alpha \cdot (n+p)N_{ref}^{\tau}}{(N_i+N_1)^{\nu}}$ ,  $E_{ref} = 1$  V/cm is a reference electric field to ensure a unitless numerator in  $\mu_{surf,rs}$ ,  $N_{ref} = 1$  cm<sup>-3</sup> is a reference doping concentration to cancel the unit of the term raised to the power v in the denominator of  $\Xi$ ,  $\delta$  is a constant that depends on the details of the technology, such as oxide growth conditions,  $N_1 = 1$  cm<sup>-3</sup>, A,  $\alpha$ , and  $\eta$  are fitting parameters; (3) and the bulk mobility is  $\mu_{bulk} = \mu_L(\frac{T}{T_0})^{-\xi}$ , where  $\mu_L$  is the mobility due to bulk phonon scattering and  $\xi$  is a fitting parameter.

# 2.2 The Numerical Simulation Methods

In this section, we will introduce the adaptive numerical methods in the following discussion. The implemented adaptive computing technique for semiconductor device simulation is mainly based on Gummel's decoupling method [114, 124, 125], FV approximation [112, 126], Monotone iterative method [135, 136], a posteriori error estimation [112], and an unstructure meshing scheme [111, 114, 124, 125]. This simulation methodology has recently been developed for different device simulation [112, 126, 127]. The Gummel's decoupling method controls an iterative loop over two or more coupled equations. It is used when a fully coupled method would use too many resources of a given machine, or when the problem is not yet solved and a full coupling of the equations would diverge.

### 2.2.1 The Gummel Decoupling Method

To explore the transport behavior of transistors, the five coupled PDEs are numerically solved with Gummel's decoupling method. With a given initial guess  $(\phi^{(0)}, n^{(0)}, p^{(0)}, \gamma_n^{(0)}, \gamma_p^{(0)})$  and for each Gummel's iteration index g, g = 0, 1, ..., we first solve the nonlinear Poisson equation as well as density-gradient-corrected quantum potential equations.

$$\Delta \phi^{(g+1)} = \frac{q}{\varepsilon_s} (n^{(g)} - p^{(g)} + D(x, y) + BT(\phi^{(g+1)})).$$

(2.9)

$$\gamma_n^{(g+1)} = 2b_n \frac{\nabla^2 \sqrt{n^{(g)}}}{\sqrt{n^{(g)}}}.$$

(2.10)

$$\gamma_p^{(g+1)} = 2b_p \frac{\nabla^2 \sqrt{p^{(g)}}}{\sqrt{p^{(g)}}}.$$

(2.11)

The nonlinear Poisson equation is solved for  $\phi^{(g+1)}$ ,  $\gamma_n^{(g+1)}$ , and  $\gamma_p^{(g+1)}$  given the previous states  $n^{(g)}$  and  $p^{(g)}$ . The quantum-corrected current continuity equation of electron is then solved for  $n^{(g+1)}$  with now the known functions  $\phi^{(g+1)}$ ,  $p^{(g)}$ ,  $\gamma_n^{(g+1)}$ , and  $\gamma_p^{(g+1)}$ .

$$\frac{1}{q}\nabla \cdot (-q\mu_n n^{(g+1)}\nabla\phi^{(g+1)} + qD_n^{(g+1)}\nabla n^{(g+1)} - qn^{(g+1)}\mu_n \nabla \gamma_n^{(g+1)}) = R(n^{(g+1)}, p^{(g)}).$$

(2.12)

Finally, we solve the quantum-corrected current continuity equation of hole with known  $\phi^{(g+1)}$ ,  $n^{(g+1)}$ ,  $\gamma_n^{(g+1)}$ , and  $\gamma_p^{(g+1)}$

$$\frac{1}{q}\nabla \cdot (-q\mu_p p^{(g+1)}\nabla \phi^{(g+1)} - qD_p^{(g+1)}\nabla p^{(g+1)} + qp^{(g+1)}\mu_p \nabla \gamma_p^{(g+1)}) = -R(n^{(g+1)}, p^{(g+1)})$$

(2.13)

for  $p^{(g+1)}$  until all preset stopping criteria are satisfied. Equations (2.9), (2.12), and (2.13) are associated with proper boundary condition, respectively. We note that Eqs. (2.9), (2.12), and (2.13) are now three individual semilinear PDEs to be solved for each Gummel's iteration. An outer iteration in the procedure of device simulation is then defined by Gummel's decoupling method. We note that analysis of Gummel's decoupling method in device simulation have been reported [110, 112, 114, 124–128, 130]. Then we can solve each decoupled PDEs with adaptive computing technique.

The Gummel's decoupling method

Begin

While  $\phi$ , n, and p in outer loop (Gummel's loop) are not convergent

If  $\phi$  is convergent

Solve the nonlinear Poisson equation as well as density-gradient-

corrected quantum potential by adaptive computing technique.

End If

If n is convergent

Solve the quantum-corrected current continuity equation of electron

with adaptive computing technique.

End If

If p is convergent

Solve the quantum-corrected current continuity equation of hole

with adaptive computing technique.

End If

End While

Call for next calculation.

$End \; \mbox{The Gummel's decoupling algorithm}$

### 2.2.2 The Adaptive Finite Volume Method

The discretization of semiconductor is performed based on adaptive 1-irregular mesh, triangular mesh, and finite volume (FV) approximation. The finite volume method is a numerical method for solving PDEs. It calculates the values of the conserved variables across the volume. Before using adaptive finite volume method to solve Poisson equation, we must understand the follow steps:

- (1) Weak Formulation transforms into weak problem;

- (2) Discretize the simulation area by one-irregular mesh;

- (3) Form equation "Ax=B" by using FV method; and

- (4) Error estimation and mesh refinement.

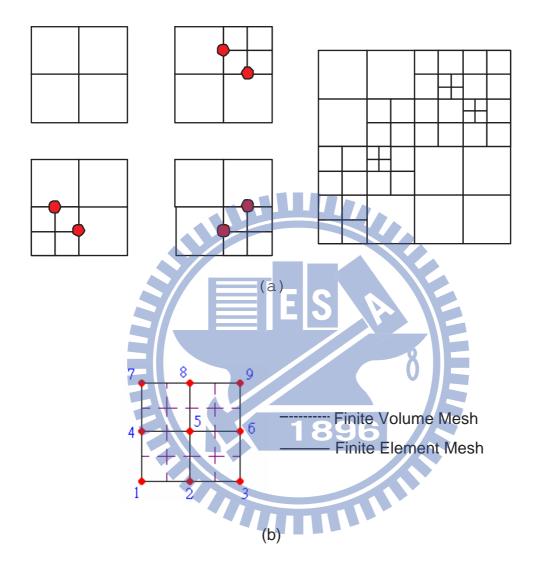

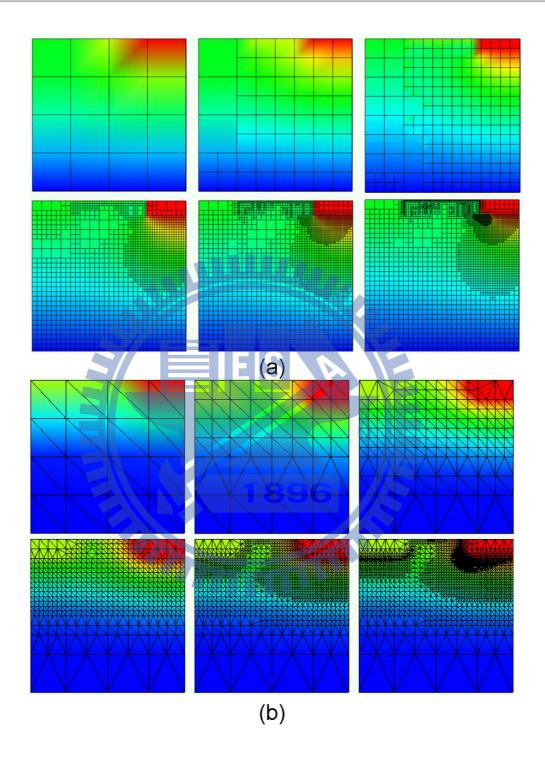

The discretized step divides into structured mesh and unstructured mesh. If according to geometry, it divides into rectangle mesh and triangle mesh. But the rectangle mesh is easier to build than the triangle mesh. The one-irregular method is shown in Fig. 2.1. Figures 2.2(a) and 2.2(b) are the discretization scheme by finite volume method and finite element method, respectively. The initial mesh contains 25 nodes and then refined based on the estimation of solution error element by element. Notably, the process of mesh refinement is guided by the result of error estimation automatically. As shown in plots, at the refinest level most of refined meshes are intensively located near the surface of channel and the junction of the drain side due to large variation of the solution gradient.

Figure 2.1: The plot of FV method. (a) One-Irregular mesh, and (b) the difference between finite element mesh and finite volume mesh.

Figure 2.2: The mesh used for the solution process. Illustrations of MOSFET source/drain junction discretization. The p/n junction is discretized by (a) adaptive finite volume method and (b) adaptive finite element method.

### 2.2.3 The Monotone Iterative Method

In previous subsection, we apply a finite volume method with nonuniform mesh technique to discretize the above PDEs in each directions. Using the divergence theorem on a finite hexahedral volume and considering the tensor-product meshes for the hexahedral volume, the discretized Poisson equation can be written as

$$\xi_{i+1,j,k}\phi_{i+1,j,k} + \xi_{i-1,j,k}\phi_{i-1,j,k} + \xi_{i,j+1,k}\phi_{i,j+1,k} + \xi_{i,j-1,k}\phi_{i,j-1,k} + \xi_{i,j,k+1}\phi_{i,j,k+1} + \xi_{i,j,k-1}\phi_{i,j,k-1} + \xi_{i,j,k}\phi_{i,j,k}$$

$$= \tau_{i,j,k} \left[ \frac{qn_i}{\varepsilon_{si}} \left( \exp\left(\frac{\phi_{i,j,k}}{V_T}\right) - \exp\left(-\frac{\phi_{i,j,k}}{V_T}\right) \right) - \frac{q\left(N_D^+ - N_A^-\right)_{i,j,k}}{\varepsilon_{si}} \right], \quad (2.14)$$

where the arranged coefficients  $\xi_{i,j,k}$  and  $\tau_{i,j,k}$  for all i, j, and k are direct results from the integral approximations with the quadrature rule. After employing the boundary conditions, the above set of equations for the approximations  $\phi_{i,j,k}$  at the nodes  $\mathbf{X}_{i,j,k} = (x_i, y_j, z_k)$  can be written together as the compact matrix form,

$$\mathbf{A}\Phi = -\mathbf{B}\left(\Phi\right). \tag{2.15}$$

$\Phi$  is the unknown vector formed by  $\phi_{i,j,k}$  in the natural ordering, **B** is the vector of nonlinear functions corresponding to the finite volume discretization of equations. The matrix **A** is a seven-banded block-tridiagonal form. We note all coefficients in Eq. (2.14) are nonnegative and the following relation:

$$\xi_{i,j,k} \ge \xi_{i+1,j,k} + \xi_{i-1,j,k} + \xi_{i,j+1,k} + \xi_{i,j-1,k} + \xi_{i,j,k+1} + \xi_{i,j,k-1}$$

which holds for all  $X_{i,j,k}$ . Based on these observations, it can be shown A is an irreducible M-matrix. The right-hand side of Eq. (2.14) is continuously differentiable function with respect to  $\phi$ , and the derivative of this nonlinear function is nonnegative. Then we can write A = D - L - U and proceed to the description of the iterative method for solving the Eq. (2.15) arising from the finite volume discretization of semiconductor nonlinear Poisson equation. D, L, and U are diagonal, lower triangular, and upper triangular matrices of A, respectively. This method for solving the multi-dimensional semiconductor nonlinear Poisson equation consists of only single iteration loop as follows:

$$(\mathbf{D} + \lambda \mathbf{I}) \Theta^{(m+1)} = (\mathbf{L} + \mathbf{U}) \Theta^{(m)} - \mathbf{B} \Theta^{(m)} + \lambda \mathbf{I} \Theta^{(m)}, \qquad (2.16)$$

where the superscript index m is the iteration index; I is an identity matrix and  $\lambda$ I is a diagonal matrix determined by the function B. The Eq. (2.16) can be regarded as a Jacobi type iterative scheme. This result demonstrates the solution sequence generating from iterative formula, Eq. (2.16), will converge monotonically to the solution of Eq. (2.15) for all choices of the initial guess. The proof has been validated in reference [135, 136]. Together with a Gummel's decoupling method, the monotone iterative method for the numerical solution of the nonlinear Poisson equation can be applied to solve various semiconductor device models. Compared with the Newton's iterative method, the monotone iterative method is easy implementing, relatively robust and fast with much less computation time, and its algorithm is inherently parallel in large-scale computing. The algorithm of the monotone

iterative method is summarized as follows:

- (1) Take an initial guess for  $\Theta^{(m)}$ ;

- (2) Let m = 1 and set (i, j, k) = (1, 1, 1);

- (3) Determine the parameter of monotone iterative approach  $\lambda I$  instantaneously;

- (4) Compute the  $\Theta^{(m+1)}$  with Eq. (2.16), and

- (5) Perform convergence test. If it converges, then break, else m = m + 1 and return to (3).

# 2.3 A 25-nm FinFET Simulation and Calibration

In this section, electrical characteristics of 25-nm-gate round-top-gate fin-typed field effect transistors (FinFETs) on silicon wafers are calibrated and explored. Furthermore, by considering different short-channel effects, dependence of the device performance on the non-ideal fin angle and fin height is investigated. Optimal structure configuration for the round-top-gate bulk FinFETs is thus drawn to show the strategy of fabrication in sub-25 nm metal oxide semiconductor field effect transistors devices. The physical models have been calibrated with experimentally measured data.

Field effect transistors with multiple-gate structures, such as fin-type FETs (FinFETs) have been of great interest due to the excellent controlling ability of carriers in the device's channel, which suppressed the short-channel effect. Channel doping for adjusting

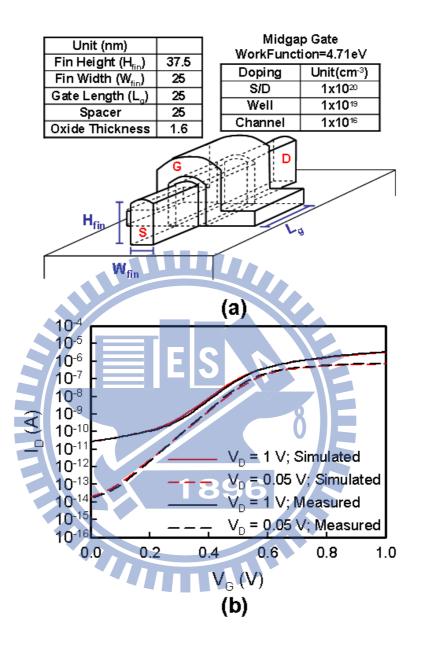

Figure 2.3: (a) An illustration of the simulated fin-type field effect transistors. The top of the fin is formed to a round shape naturally and the fin bottom is not actually rectangular for the lithography and silicon etching processes. (b) The  $I_D$ - $V_G$  curves for the FinFETs. The red and black lines are the simulated and measured data, respectively.

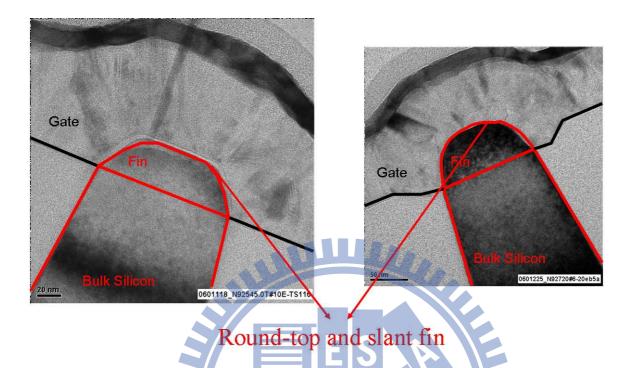

Figure 2.4: SEM pictures of bulk FinFETs with a round-top and slant fin.

the threshold voltage is still necessary in nowadays manufacturing process. Various studies have been reported to simulate the multiple-gate device by using 3D quantum/classical models, and device models coupled with process models. We herein use the 3D quantumcorrected drift-diffusion models to simulated the characteristics of bulk FinFETs. The employed device models have been calibrated. Figure 2.3(a) shows the geometry and parameters of the simulated FinFET with 4.71 eV workfunction, 37.5 nm fin height ( $H_{fin}$ ), 25 nm fin width ( $W_{fin}$ ), 25 nm gate length ( $L_g$ ) and 1.6 nm oxide thickness. The device is with a round-shape top due to the limit of manufacturing ability. In fabricating the nanoscale

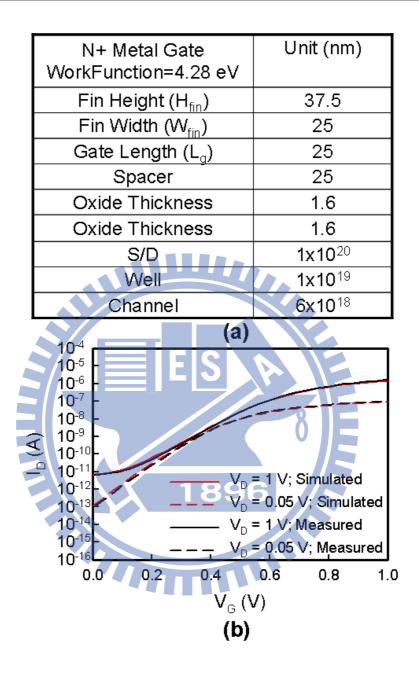

Figure 2.5: (a) The device dimension and parameter setting of the simulated fin-type field effect transistors, in which the device workfunction is 4.28 eV. (b) The characteristics of the  $I_D$ - $V_G$  curves for the FinFETs. The red and black lines are the simulated and measured data, respectively. The simulation shows a good agreement with measurement data, which represents the accuracy of the calibrated 3D device simulation.

FinFETs, the minimum dimension of the device has transferred from the gate length to the fin thickness. Top of the fin is formed to a round shape naturally and the fin bottom is not actually rectangular for the lithography and silicon etching processes, as shown in Fig. 2.4. These non-ideal processes will result in a wider fin bottom with respect to the fin top; thus it leads to a slanted edge of the channel fin [51-56]. Such geometric derivation degrades device performance and raises serious SCEs, such as a large subthreshold swing, low ratio of the on- and off-state currents, and large drain induced barrier lowering. The measurement and simulated results are presented in Fig. 2.3(b), where the red and black lines are the simulated and measured data, respectively. The simulation shows a good agreement with measurement data. Similarly, we change the device workfunction and parameters as shown in Fig. 2.5(a). The simulated data in Fig. 2.5(b) also exhibit a good accuracy with measurement data, which represents the accuracy of the calibrated 3D device simulation. The properties of the material are summarized in Tab. 2.1.

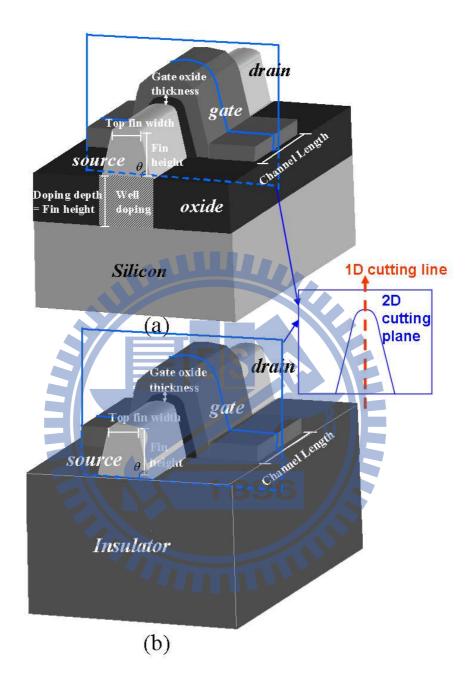

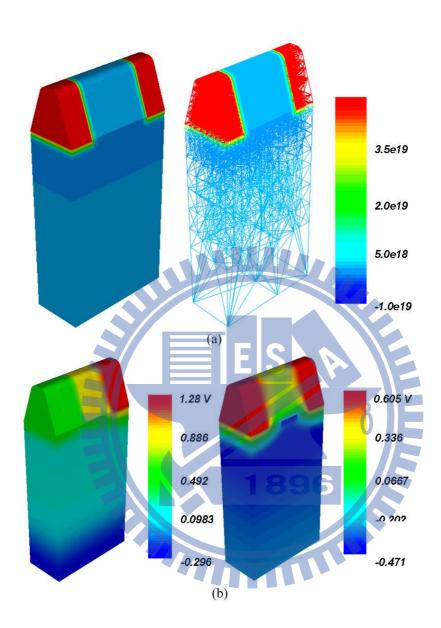

Then we change the device geometry setting to explore the electrical characteristics of 25-nm-gate round-top-gate FinFETs on silicon wafers, as shown in Fig. 2.6. The oxide thickness, the fin width, and the fin height are fixed at 1.2 nm, 20 nm and 50 nm, respectively. Figures 2.7(a) shows a 3D doping profile and the corresponding refined mesh of the device, where the color of the mesh indicates the assigned doping concentration at meshing lines. The fin height = 50 nm and the fin angle = 70°. Plots of the 3D simulated on-

Figure 2.6: Three-dimensional schematic plots for the (a) bulk FinFETs and (b) SOI FinFETs.  $\Theta$  is the fin angle and the inset shows a 2D cutting-plane extracting from the center of channel.

Figure 2.7: (a) A plot of the 3D doping profile of the round-top-gate bulk FinFET. The left plot is the contour of doping profile and the right one is the corresponding mesh. (b) The left plot is the on-state potential of the round-top bulk FinFET and the right one is the off-state potential.

Figure 2.8: Plots of the 2D cutting plane of the simulated on-state ( $V_D = 1.0 \text{ V}$  and  $V_G = 1.0 \text{ V}$ ) (a) potential and (b) electron density at the center of channel of the 30 nm-height bulk FinFET. The fin angles are the 90°, 80°, and 70°, respectively.

Figure 2.9: Plots of the 2D cutting plane of the on-state (a) potential and (b) electron density at the center of channel of the 40 nm-height bulk FinFET. The fin angles are the 90°, 80°, and 70°, respectively.

Figure 2.10: Plots of the 2D cutting plane of the on-state ((a) potential and (b) electron density at the center of channel of the 50 nm-height bulk FinFET. The fin angles are the 90°, 80°, and 70°, respectively.

#### Table 2.1: Material parameters setting for silicon, poly-silicon, $SiO_2$ and $Si_3N_4$ . The epsilon is the ratio of the permittivities of material and vacuum.

| Silicon                               | Poly-Si                                                                                                        | SiO <sub>2</sub>                                                                                                                                        | Si <sub>3</sub> N <sub>4</sub>                             |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| 11.7                                  | 11.7                                                                                                           | 3.9                                                                                                                                                     | 7.5                                                        |