# 第一章 序論

### 1.1 研究背景

微機電系統(Micro-Electro-Mechanical-System, MEMS)是整合電子、機械、材料、光學、化學、控制等專業領域之工程技術於一微小元件,使其具有特殊功能的系統元件[1]。在近來半導體科技的發展,一切要求微小化、積體化、智慧化的前提下,許多產品以微機電模組的方式製造以降低成本,不但經濟有效且可提高其性能、品質與可靠度,所以微機電系統的發展在世界各地都備受矚目,同時被認為是最具發展潛力及前瞻性的研究領域,是目前世界各國積極投入的核心工業[2]。微機電系統又被稱為微系統科技(Microsystem Technology, MST),主要稱微系統技術是因涵蓋範圍較大,定義係利用微技術、系統技術及材料與效應技術,製造出尺寸為「微米」的微感測器、微致動器及訊號處理元件等。微系統技術早期發展是以半導體技術應用在機械上,最近數年已經擴展至通訊、光電、醫學、交通等領域上,因此國際上,如日本及歐洲等國才以微系統技術稱呼之[3]。在本文中統一採用一般稱呼,稱之為微機電系統。

MEMS 的製造主要是使用半導體製作技術,如應用沉積技術,在矽基板上覆蓋所需材料,利用微影技術將設計之圖案形狀先成形於矽基板,再利用蝕刻技術將所成形圖案顯現出來,重複這些步驟可完成所需結構。其與積體電路(IC)並存,均以矽為基板,相同利用化學沉積、離子植入、擴散蝕刻、微影等技術。兩者技術相通,應用不同:IC 技術的成功為微機電技術奠定了發展的基礎,但 MEMS 結構較複雜,含光學、機械功能,其設計、製造依產品應用不同而差異較大,是高度的系統整合技術。微機電技術使得許多傳統大型系統無法完成的工作得以實行,並使原本可以進行的工作在效率上大幅提升,為人類生活帶來深刻且全面的影響,也成為奈米科技發展必經之路[4]。

歐盟在1992年為推動 MEMS 或 MST技術的研發與商業化應用即成立了 NEXUS(Network of Excellence in Multifunctional

Microsystem),當時對 MEMS 定義為:具有微米級的結構,及微結構所提供技術功能。對於各類微結構的製造而言,微機電系統一路發展的理念便是結合精密機械加工技術以及半導體製造技術,試圖將各種結構「微小化」與「整合」[3]。在 MEMS 的領域中,目前可被用以製作微結構的方法可分為四類:面型矽基加工、體型矽基加工、LIGA技術及各種微機械加工技術,面型矽基加工係指利用半導體製程之薄膜沉積及蝕刻技術在晶片上製作微機械元件。體型矽基加工係指利用非等向性蝕刻、蝕刻終止與蝕刻幕罩等技術刻蝕單晶矽本身製作微機械元件。LIGA技術係結合 X 光光刻術(X-ray lithography)、電鑄與微成形來製作高深寬比微機械結構。微機械加工則利用切削加工、放電加工或射出成型等方法來製作微機械元件[5]。其中各有其優缺點,如微結構的製作品質不一,也需考量成本及量產問題等。

以製作光碟讀寫系統內的繞射光柵為例,若以傳統的精密加工法製造係利用精密刻線機以鑽石刀具切削加工而得,生產成本極其高昂且量產性不大。採用 LIGA 技術[6]先將微結構以 X 光光刻術轉移光罩圖案,再以電鑄技術翻模,而後使用微成形技術即可大量量產。然而 X 光深刻技術雖可以製造出高深寬比且高精度的元件,使用光源卻甚昂貴,因此才有類 LIGA 製程[7]的開發,例如採用便宜光源-紫外光源替代等。另一方面而言,若能利用光學微影與乾式蝕刻以製作母片,然後再配合微成形技術來大量複製塑膠材質的光柵元件以取代石英光柵,則無論材料成本或是生產成本皆可大幅降低[8]。

微成形一般是由射出成形(injection molding)或熱壓成形(hot embossing)技術來達成。各有其優缺點及使用之限制,熱壓成形技術因為具有材料流動率低(low flow rate)、流動距離短(low material flow)的特性,因此特別適合用來成形微細結構與光學元件[9],且其可達高深寬比之製作(>10),所熱壓高分子平板之厚度要求不高(<0.5 mm)。射出成形所要求之平板厚度至少需 2 mm,對於有特殊要求厚度之元件即無法製作[10]。

此外,熱壓成形所需之機器設備既簡單又極具彈性,在熱壓製程

更改時往往僅需更改幾個控制參數,且任何一種製程所製作出來的模 仁皆能經由熱壓成形技術來達到轉印的目的。但其一次成形之週期過 長,不如射出成形之成形周期較短,量產部份可靠加大成形面積來彌 補[10]。

在利用熱壓成形法製作微結構時,熱壓完成後冷卻脫模的過程中,因為模仁與熱壓材料之高分子冷卻收縮率不同,會對材料產生剪斷、拉扯的現象,導致脫模時缺陷的產生,所以如何能夠在脫模過程中保持材料的完整性及良好的轉印性,便成為熱壓成形技術中一個重要且關鍵的技術。

#### 1.2 研究動機與目的

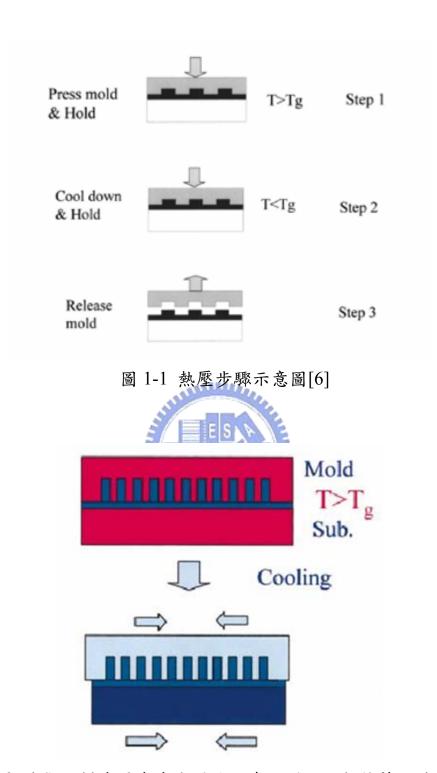

隨著塑膠工業的迅速發展,微小成形品的生產技術正趨成熟,所生產的成形品具體積小、精度高、成本低等優點,使得由熱壓成形或射出成形技術所製造的微成形品受到越來越多行業重視,成為金屬等材料製造的微型零組件極佳替代品。目前在熱壓成形、射出成形技術的研究當中,皆著重在製程技術與產品應用的開發上,製造高深寬比的微結構更是重點之一。然而對於微成形的脫模步驟時會產生缺陷的影響,卻仍無系統性的研究。由於熱壓成形、射出成形技術皆須提高溫度至材料之玻璃轉移溫度之上使材料呈融熔狀,再進行保壓步驟,待保壓結束後經適當降溫步驟,即可將高分子材料由模穴中脫模,如圖1-1 所示[11]。尺寸效應的影響下,材料膨脹係數的不同,造成冷卻步驟時不同材料的冷卻收縮率差異更大,因此在冷卻步驟即會有夾持的影響,如圖1-2 所示[11],進而在脫模步驟造成微結構斷裂。

有鑑於此,在本研究中將利用半導體製程中摻雜之技術,引入熱電阻的觀念,設計出實驗,希冀以此想法製作之模仁在冷卻步驟能藉由施加電壓使模仁局部加熱,釋放微結構中殘留的應力,以解決微結構熱壓成形或是射出成形完成後,脫模時可能產生的問題及形成的缺陷。再者,製作嵌入式的壓力、溫度感測器於模仁中,於射出成形或熱壓成形時一方面即時監測模仁的溫度及壓力,一方面控制及尋找成

形時最佳化的參數,以提升成形品的品質。

### 1.3 文獻回顧

LIGA 源自德國核能研究所,1980 年初期所發展出來的一種製程,是德文(Lithographie、GaVanoformung、Abformung)之縮寫,譯成英文為 lithogrophy、electroforming、micro molding,中文則為 X 光光刻術、電鑄、微成形。LIGA 結合 X 光光刻術、電鑄翻模及微成形技術中之精密射出(injection)或熱壓成型(hot embossing)三種主要技術,適合量產高深寬比(aspect Ratio)低表面粗糙度(sub  $\mu$ m)直側壁的微結構,且材料的應用範圍廣泛,可製造金屬及塑膠的微結構。這些技術的特點使得 LIGA 被公認為最具有技術潛力開發高深寬比,高精度之 2D、3D 微結構之件及微系統[12]。

由於 LIGA 製程是一種整合性的製程,每一個技術皆可獨立出來做深入的研究。如 X 光光刻術方面不斷有人嘗試以更降低成本的方式進行微影製程, C. Harris 等人便是研究先在一層石墨板上塗佈厚膜光阻,顯影過後以鎳-金直接電鑄於其上,再移去光阻,以作為 X 光光罩[13]。在電鑄翻模方面,W. Backer 等人製作電鑄翻製金屬模仁,得到製程之最佳化參數與模仁良好之表面粗糙度[14]。H.Becker 與U.Heim 則提出可以矽基材直接作為熱壓之工具,在 4 吋晶圓上成形20μm 寬,深寬比為 7 之溝槽與十字結構,不需要使用到複雜如 LIGA之技術,省略掉電鑄翻模之步驟比起以往更能節省成本,並指出達到更高深寬比是未來努力目標[15,16]。

在微成形技術方面,L. Weber 等人提出微成形是使精密結構大量生產最有利的工具,在文獻中並提到以微成形技術製作的製品可能會產生未完成充填(filling)、收縮(shrinkage)、翹曲(warpage)與表面粗糙(surface roughness)等缺陷[17]。

而微成形技術中,有關於熱壓成形的研究,L. Lin 等人成功的整合了半導體製程與熱壓成形於 3D 微結構製作方面,他們先利用半導體製程將金字塔型(寬 30μm,高 21μm)的微結構製作於矽晶片上,將

具有微結構的矽晶片當作模仁,利用熱壓成形法,重複的再生塑膠微結構,這些塑膠微結構具有平滑表面的特性,同時高的良率與可靠性亦是他的特點之一[18]。M. Heckele 等人認為熱壓成形具有材料流動距離短與低剪切速率的優點,可避免產品產生內應力,適用於細微結構的成形。但因成形週期太長,只可用來製造量數少的高精密度與高品質塑膠微結構。不過可藉由加大成形面積與自動化製程來提高生產量與降低生產成本[9]。

以熱壓成形奈米結構方面:S. Y. Chou 等人提出以熱壓成形法可製作線寬 25nm,密集度為每一單獨結構間距 70nm,側邊垂直且表面平滑之結構[19]。更進一步的研究表示成形線寬可達 10nm,其製程的可重複性以及矽晶模仁的使用壽命可達 30 次以上,且在 15mm×18mm 之矽晶模仁面積上可得均勻成形結構。若是解決表面黏滯問題、尋得最佳化成形條件、熱膨脹效應與多層對準問題等,可在更大的矽基模仁面積上得到均勻熱壓成形結構[20]。隨後,R. W. Jaszewski 等人將奈米結構的成形面積放大到 100mmx100mm 以上,並提出負型模仁較易成形的觀點,模仁之壽命也提高到 50 次以上 [21]。H.-C. Scheera 等人選擇高分子量之熱塑性光阻,以溫度及壓力為參數進行奈米結構的成形試驗,由於材料黏滯性隨溫度升高而減低,且彈性性質僅有微小變化,在溫度及壓力增加時能增加光阻流動,對於尺寸較小且具週期性之奈米結構可得到極高的轉印性,其試片面積為 2cm X 2cm,成形之最佳化條件壓力在 100bar,而溫度是高於材料玻璃轉移溫度 90°C [22]。

成形奈米結構除了以熱壓轉印外,還有由下往上(bottom-up)堆積高分子形成結構: S. Y. Chou 等人藉由融熔聚合物的表面與模仁表面間的超距吸附力而使聚合物自行形成高度可達數百奈米的微結構 [23]。H. Schift 等人探討以 PMMA 薄膜製作微米、奈米結構時,在熱壓和脫模階段中的微結構成形特性。發現在模穴充填時會有壓縮與毛細管效應出現,且在特定條件下會產生具有一定特徵長度的週期紋樣,而模穴的尺寸大小和形狀會強烈影響材料的自組合現象[24]。

製作大尺寸結構易以肉眼分辨其成形結果,製做微小尺寸因為尺寸效應關係,不能適用許多巨觀世界之理論。在尋找最佳化之成形條件前,常以軟體模擬分析:N. Huber 及 Ch. Tsakmakis 藉由 ABAQUS軟體模擬塑膠熱壓成形脫膜時應力的分佈分析,包括有無基板、基板種類、以及殘餘層厚度對應力分佈的影響[25]。Hirai 等人以有限元素法對奈米熱壓的高分子材料變形過程模擬,對高分子高於其玻璃轉移點之變形在不同深寬比、初始材料厚度、壓力等條件下,以橡膠彈性模型來對材料變形後之截面積形狀進行數值模擬,其結果與實驗數據非常吻合[26,11]。

在利用摻雜(doping)技術於矽晶片上製作導電區域方面,A. D. McConnell 等人提出經過摻雜的多晶矽其熱導係數與晶粒大小、摻雜質的濃度及摻雜質的型式有關,在相同摻雜型式下,摻雜質濃度高的有較低的熱導係數;而摻雜質在一定的濃度下,摻雜磷原子的多晶矽其熱導係數會比摻雜硼原子的熱導係數來的高;而在室溫下,相同摻雜濃度時,單晶矽層的熱導係數是多晶矽層熱導係數的兩倍[27]。C. C. Huang 與 K. Najafi 研究顯示離子植佈所形成之磷之厚度受到退火時間及溫度之影響,約 0.2μm 至 0.3μm,及利用軟體模擬預測最佳化之植佈條件與退火參數及即將植佈之深度與濃度分布[28]。

引入熱電阻的觀念,黃重凱論文以製作智慧型模仁為目的,利用P型(100)之矽晶片為基材當作模仁,在其中製造出有適當阻值、能導電的區域,同時引入熱電阻的觀念,對導電區域通入電壓或電流,讓導電區域能夠導通並產生熱量,作為熱壓完成後降溫開模時模仁維持溫度的來源,希望在模具降溫到開模溫度時模仁能保持適當的高溫。其實驗結果得知,保持適當的高溫可以有效改善轉印性。同時溫度越高,導電區域阻值有下降的趨勢;壓力越高,導電區域阻值亦有下降的趨勢[29]。

在微感測器製作方面, F. Volklein 與 H. Baltes 利用兩二氧化矽結構層製作懸臂樑,在一懸臂樑上面有成長多晶矽,與另一不成長多晶矽之懸臂樑做對照,在施予電壓後達加熱效果,以量測多晶矽之熱傳

導係數[30]。P. Eriksson等人將熱傳導感測器製作成電路,成功量測以 PECVD 法製作之氮化矽之熱傳數值及比熱[31]。T. Toriyama 與 S. Sugiyamaw 推導出以 p 型晶圓製作之微感測器的壓電阻值方程式,p 型晶圓具電洞受壓力時電子移動而具壓電性質,以其方程式再與實驗做對照發現其預測相當近似[32]。A. A. Geisberger 等人製作微型四點探針之量測結構用以量側多晶矽之熱電性質,可量測出溫度相關之阻值與熱傳導係數之曲線圖,將此一實驗數據套入 3D 有限元素分析之模型為材料性質作模擬與實際之熱致動器做比較,在穩態與暫態分析上都能與實驗相佐證[33]。

而即時監控感測器方面,R. C. Luo等人利用半導體製程技術發展了薄膜式的壓力、溫度感測器陣列應用於射出成形時的即時監控。壓力感測器以具有壓電性質的錯鈦酸鉛(PbZrTiO3,PZT),在300℃下濺鍍於鋼片或矽晶片上,再利用退火技術,於650℃下使得薄膜能結晶成所需的壓電薄膜結構,最後製作出長寬約5mm×5mm,厚度約16000Å的壓電感測薄膜,並可利用電荷放大器將壓電訊號擷取至電腦。溫度感測器以RTD(Resistance Temperature Device)溫度感測器原理,利用鉑(Pt)電阻對溫度變化成正比且線性量測溫度範圍大(-200℃~750℃)的優點,製作長寬約1mm×1mm,厚度約2000Å的薄膜式溫度感測器。這個研究整合模具設計及塑膠射出成型機為一體,考量加上矩陣型感測器的檢測回授資訊,可適當調整所需參數,並應用適當的控制技術,將可自動檢測並調整參數使產品品質能完全掌握「341。

# 1.4 研究方法

本研究使用(110)P型矽晶圓為模仁基材,利用半導體相關製程, 在基材上製作多數密集且排列整齊之微結構區。並且,運用摻雜的技 術對矽晶圓的部份表面進行改質,使其電阻降至所要的範圍,以使矽 基模仁表面適當分佈有嵌入式電熱線。再於成形時對導電區域通入電 壓或電流,以使微結構區能均勻加熱,藉以消除模仁與微結構間的應 力作用,期望能改善模仁與材料因降溫時的收縮率之不同所產生的缺陷。

半導體相關製程的應用包括有:在基材上沈積二氧化矽及氮化矽之薄膜;利用微影製程將所設計的圖案轉印在之前沈積的二氧化矽及氮化矽薄膜上;再利用濕式與乾式蝕刻將開在二氧化矽層的圖案轉印到矽晶片上,未被蝕刻的二氧化矽及氮化矽層將在下一步驟摻雜時做為阻擋層,另外,僅在裸露部分的矽晶片上摻雜入磷原子,使其成為有阻值能導電的區域。

在嵌入式溫度感測器與壓力感測器方面,希望能藉由監控這些導電區域,其在溫度及壓力變化下的阻值改變情形,以瞭解模具內部的溫度及壓力分佈之變化,進而尋找成形時最佳化的參數,以提升成形品的品質

圖 1-2 冷卻脫模步驟會產生因收縮率不同而互相挾持之缺陷[6]