# National Chiao Tung University

# **EECS International Graduate Program**

# **Thesis**

記憶體追蹤方式在單指令多執行緒架構中資料分享程度之分析研究

A Memory Trace-Based Analysis for Data Sharing Degree in SIMT Architectures

Student: Luis Angel Garrido Platero

Advisor: Prof. Bo-Cheng Lai

**June, 2013**

TITITI

# 以記憶體追蹤方式在單指令多執行緒架構中資料分享程度之分析 研究

# A Memory Trace-Based Analysis for Data Sharing Degree in SIMT Architectures

研究生:盧以斯 Student: Luis Angel Garrido Platero

指導教授:賴伯承 Advisor: Bo-Cheng Lai

國立交通大學

**EECS International Graduate Program**

碩士論文

A Thesis

Submitted to the EECS International Graduate Program

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

**EECS**

June 2013

Hsinchu, Taiwan, Republic of China

中華民國一〇二年六月

# 以記憶體追蹤方式在單指令多執行緒架構中資料分享程度之分析研究

Student: Luis Angel Garrido Platero Advisors: Dr. Bo-Cheng Lai

# EECS International Graduate Program National Chiao Tung University

# **CHINESE ABSTRACT**

在本論文中,我們透過量化單一指令多執行續程式中記憶體存取的資料分享程度進而分析應用程式的區域特性。此外,我們也提供了不同執行環境下之資料分享的視覺化方法。為了量化資料分享程度,本論文使用含有執行階段記憶體位置的記憶體追蹤以完成記憶體存取的資料分享程度分析。 在此分析中,我們重新定義重複使用距離的概念以提供分析以及不同執行環境的需要。

### A Memory Trace-based Analysis for Data Sharing Degree of SIMT Architectures

Student: Luis Angel Garrido Platero Advisors: Dr. Bo-Cheng Lai

EECS International Graduate Program

National Chiao Tung University

# **ENGLISH ABSTRACT**

In this work, we address the problem of quantifying the data sharing degree of the memory access behavior within specific SIMT applications in order to quantify the locality characteristics of the application's workload. In addition, we also offer way to visualize the way the sharing patterns of the applications and the way they change under different models of runtime scenarios. For the purposes of quantifying the data sharing degree a memory trace is generated that contains information of the addresses accessed at a specific point of execution. Then, the information contained in the traces is used to perform the data sharing degree analysis of memory accesses. In this analysis, we have redefined the reuse distance concept in order to make it suitable to our analytical requirements, at the same time considering the particulars of the execution model previously mentioned.

### TABLE OF CONTENTS

| Chinese Abstract.                                                           | i   |

|-----------------------------------------------------------------------------|-----|

| English Abstract                                                            | ii  |

| Table of Contents.                                                          | iii |

| List of Tables                                                              | iv  |

| List of Figures.                                                            | v   |

| Symbols  I. INTRODUCTION                                                    | xvi |

| II. OVERVIEW OF SIMT PROCESSORS                                             |     |

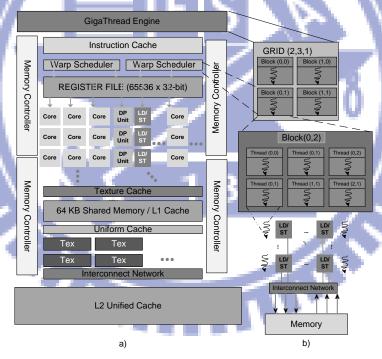

| 2.1 Hardware of GPU Architectures                                           | 6   |

| 2.2 Programming and execution abstractions of GPU                           |     |

| 2.3 Memory Hierarchy of GPUs                                                |     |

| III. LOCALITY ANALYSES IN CMP AND UNIPROCESSOR SYSTEMS                      | 9   |

| IV. DATA REUSE CHARACTERIZATION                                             | 12  |

| 4.1 Definition of the Data Reuse Degree                                     | 12  |

| 4.1 Definition of the Reuse Distance                                        |     |

| 4.1.1 Traditional reuse distance analyses                                   |     |

| 4.1.2 Reuse Distance for SIMT Processors                                    |     |

|                                                                             | 10  |

| V. ANALYSIS METHODOLOGY FOR                                                 | •   |

| DATA REUSE CHARACTERIZATION                                                 | 21  |

| VI. SCENARIOS FOR DATA REUSE CHARACTERIZATION                               | 26  |

| 5.1 Infinite resources, thread blocks are modeled as executing sequentially | 27  |

| 5.2 Infinite resources, analysis within each thread block                   | 27  |

| 5.3 Infinite resources, all thread are modeled as executing in parallel     | 28  |

| 5.4 Infinite resources, a number 'K' of thread blocks modeled as            |     |

| executing in parallel                                                       | 29  |

| 5.5   | Limited resources, 'K' block modeled as executing                |     |

|-------|------------------------------------------------------------------|-----|

|       | in parallel, within core cluster analysis                        | 31  |

| 5.6   | Limited resources, 'K' blocks modeled as executing in            |     |

|       | parallel, inter-core cluster                                     | 33  |

| VII.  | EXPERIMENTATION FRAMEWORK                                        | 35  |

| 6.1   | Trace Generation Stage                                           | 35  |

| 6.2   | Reference Stream Analysis Stage                                  | 36  |

| e     | 5.2.1 Model for Thread Blocks                                    | 36  |

| 6     | 5.2.2 Scheduling Policies                                        | 39  |

| 6     | 5.2.3 Core cluster modeling                                      | 43  |

| 6     | 5.2.4 Merging of reference streams                               | 44  |

| 6     | 6.2.5 Adjusting the position index of Mis                        | 48  |

| e     | Locality Analyzer Architecture: Putting it all together          | 50  |

| VIII. | APPLICATION OPTIMIZATION                                         | 52  |

| 8.1   | Thread Mapping Methodology                                       | 52  |

| IX.   | EXPERIMENTAL RESULTS                                             | 55  |

| 9.1   | Data Reuse Characteristic with serialized blocks                 |     |

|       | and on a per block basis                                         | 55  |

| 9.2   | Data Reuse Characteristic with varying parallelism capabilities  | 64  |

| 9.3   | Data Reuse Characteristic with limitations of SIMT Architectures | 73  |

| 9.4   | Data Reuse Characteristic when applying code optimizations       | 86  |

| X. RE | LATED WORK                                                       | 98  |

| XI.   | CONCLUSIONS                                                      | 101 |

| XII.  | REFERENCES                                                       | 103 |

## LIST OF TABLES

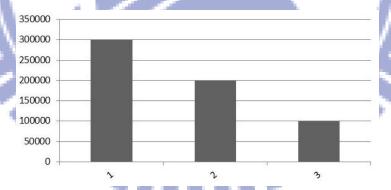

Table 1: APPLICATIONS USED FOR EXPERIMENTATION

### LIST OF FIGURES

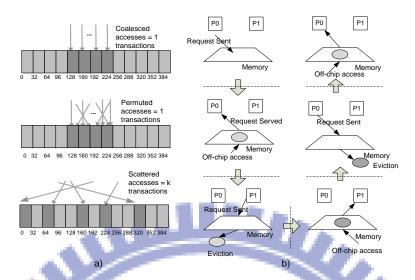

| Figure 1: Benefits obtained when taking advantage of the data reuse in SIMT applications. (a) DRAM memory transactions with and without coalescing. The first two cases from the top                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| illustrate the case for coalescing. The last case shows the case when coalescing is not possible.  (b) Illustration of the contention effect in a CMP                                                                                                                                                  |

| Figure 2: Diagram of a core cluster based on NVIDIA's Kepler GeForce GTX 680 GPU. (a) The core cluster with its internal hardware modules. (b) Illustration of the thread hierarchy in the SIMT programming model                                                                                      |

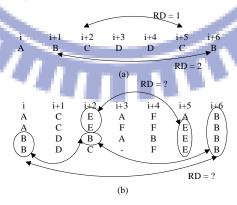

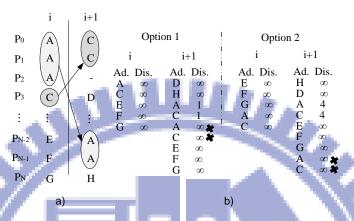

| Figure 3: Reuse distance concept and memory instruction reuse behavior in SIMT programs.  (a) Sample measurement of reuse distance in traditional multiprocessors. (b) Reuse distance behavior in SIMT architectures                                                                                   |

|                                                                                                                                                                                                                                                                                                        |

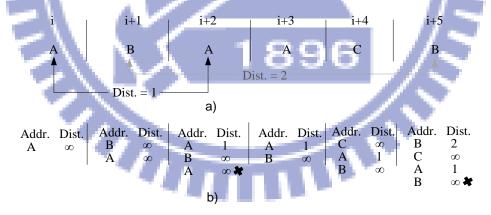

| Figure 4: A sample stream of memory instructions. The instruction array appears in the left column, the address array is presented in the middle column and the Reuse Degree for memory instructions ' $i$ ' $\rightarrow$ ' $i+2$ ' and ' $i+2$ ' $\rightarrow$ ' $i+4$ ' appears in the right column |

| Figure 5: Reuse distance analysis as applied in uniprocessor systems. (a) Sample memory trace. (b) Changes of the state of the stack as memory instructions are issued                                                                                                                                 |

| Figure 6: Reuse distance analysis in CMP systems with private memory subsystem. (a) Sample reference stream. (b) Stacks for the private memory subsystem                                                                                                                                               |

| Figure 7: Reuse distance analysis in CMPs with shared memory subsystem. (a) Sample reference stream. (b) Stacks for each memory subsystem                                                                                                                                                              |

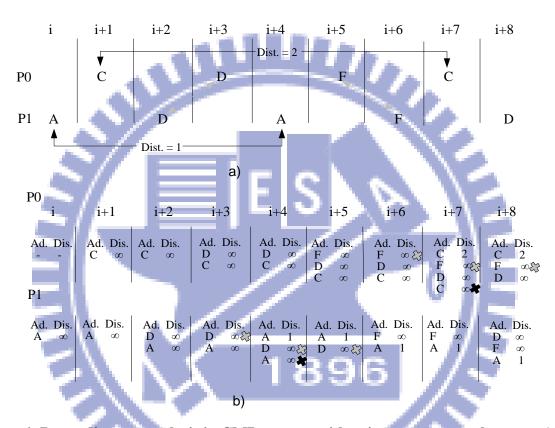

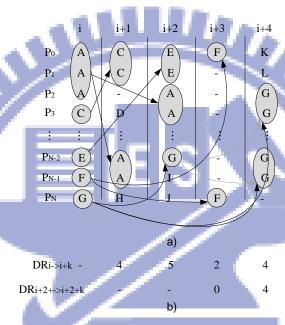

| Figure 8: Data reuse degree in a sample reference stream of a SIMT processor with 'N' processing cores. (a) Sample reference stream of a SIMT processor. (b) Data Reuse Degree for memory instructions ' $i' \rightarrow i' + k'$ and ' $i+2' \rightarrow i' + 2 + k'$                                 |

| Figure 9: Limitations when performing the baseline methodology for reuse distance analysis on SIMT processors. (a) Subset of the reference stream as it appears in Figure 7. (b) Possible ways to arrange the accessed addresses on the stacks                                                         |

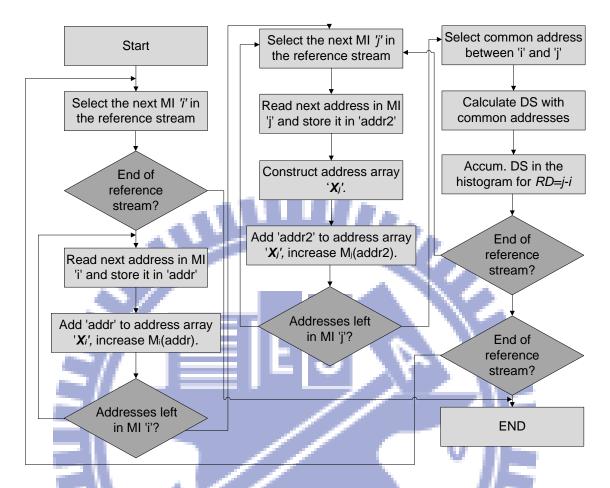

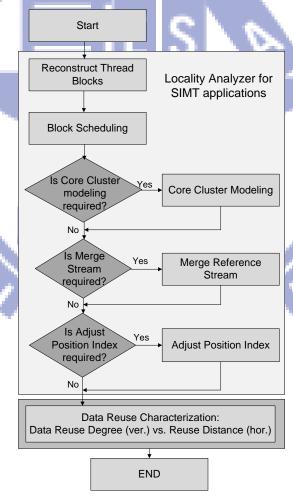

| Figure 10: Flow chart of the data reuse characterization methodology. This flow chart shows all the steps when performing the analysis over a reference stream                                                                                                                                         |

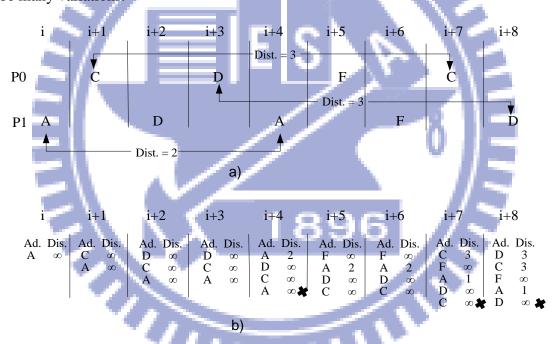

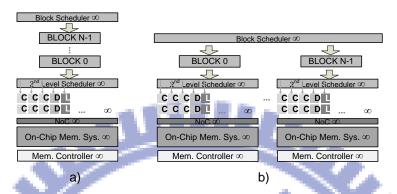

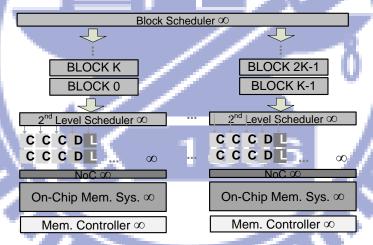

| Figure 11: Data reuse characterization. (a) Scenario 1. (b) Scenario 2. In these two scenarios, the SM is assumed ideal, as represented by the infinite signs in the figures above                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

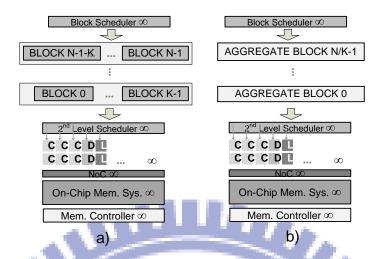

| Figure 12: Scenario 3 of data reuse characterization assuming ideal core clusters. (a) Illustrates the way blocks are intended to be executed. (b) Illustrates the Aggregate Block that results from merging the streams of all CTAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 13: Scenario 4 of the reuse degree characterization. Only 'K' blocks are modeled as executing concurrently. This is equivalent as having 'K' ideal core clusters, each one executing one block at the time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 14. (a) An ideal will be sent to the first the first term of the first term o |

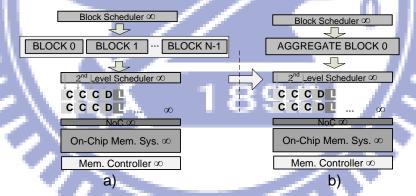

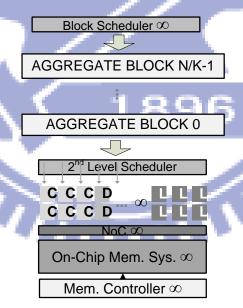

| Figure 14: (a) An ideal core cluster executing the reference streams of 'K' parallel blocks. (b) The streams of parallel blocks merged into a series of aggregate blocks, executed in sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

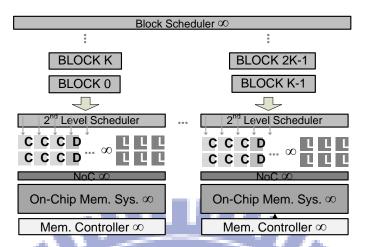

| Figure 15: Scenario 5 of the data reuse characterization analysis. Each core cluster has now a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| finite number of load/store instructions. The analysis is performed within each core cluster. 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 16: Scenario 6 of the data reuse characterization. The analysis is performed over the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| aggregate of the reference streams in every core cluster. The number of load/store units is the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| total sum across the core clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

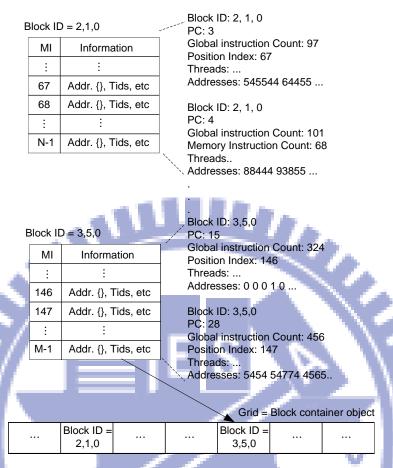

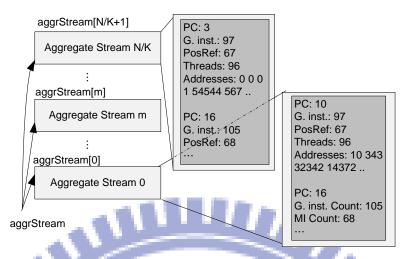

| Figure 17: Formation of Block objects within the Locality Analyzer. The block objects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| contain their individual reference stream which consists on a series of ordered MIs. Each MI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| has access information of its own                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

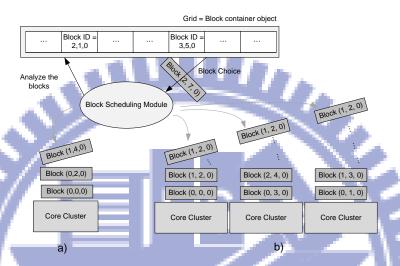

| Figure 18: Block scheduling module and block scheduling flow (a) Block scheduling module assigning blocks to a system with one core cluster. (b) Block scheduling module assigning blocks to a system with multiple core clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| olocks to a system with maturite core clusters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

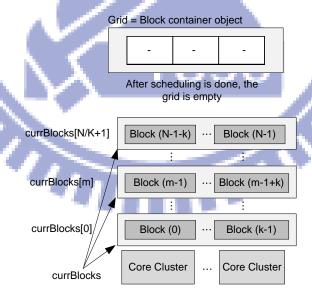

| Figure 19: After assigning blocks to the core clusters. The blocks are queued in each cluster, and are also inserted into the 'currBlocks' structure, which represents the arrays of concurrent slots.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

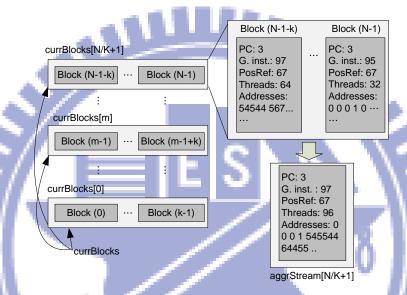

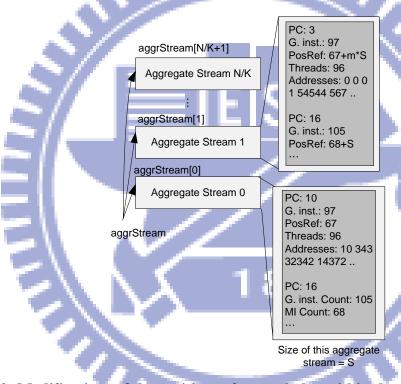

| Figure 20: Merging of reference streams from multiple blocks in the arrays of concurrent slots Scenarios 3, 4, and 6 are the only ones that employ this procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 21: The resulting reference stream of the aggregate blocks. It is possible to compare this with the streams shown in Figure 19. Notice how the 'Addresses' and 'Threads' fields are augmented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 22: Modifications of the position reference index within the reference stream. The value of the index of the MIs in streams other than the first will depend on the stream length of the streams before the current one                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 23: Block diagram of the architecture of the Locality Analyzer. This is a very general and simplified version of our framework                                                                                                                                                                      |

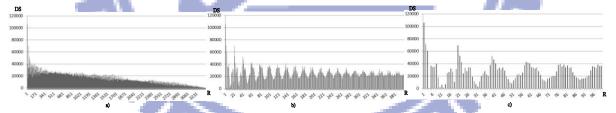

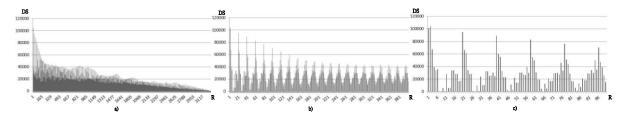

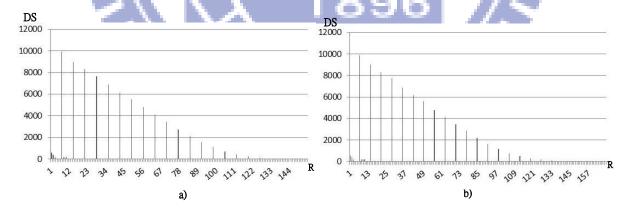

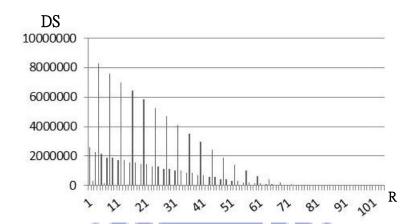

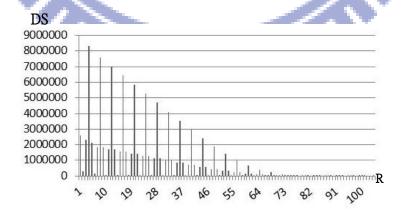

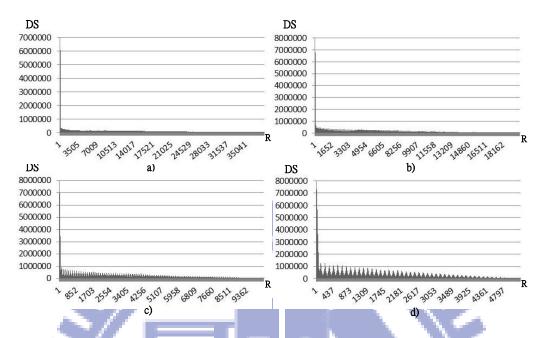

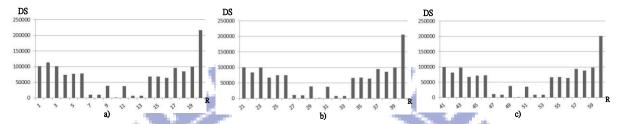

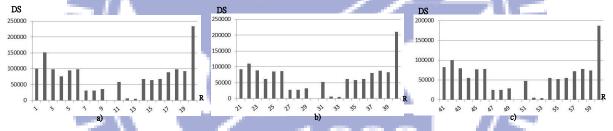

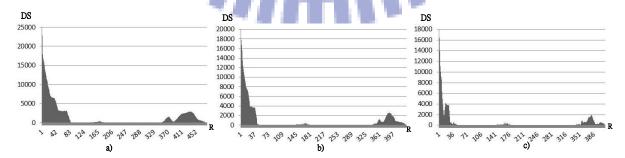

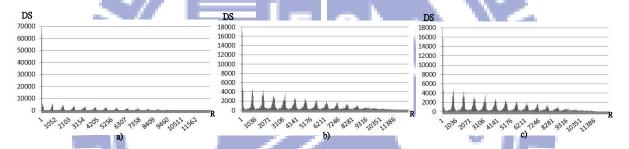

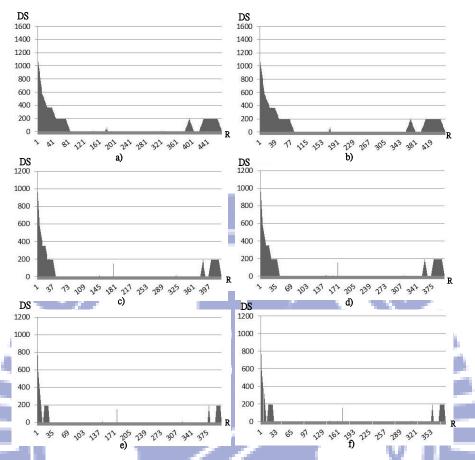

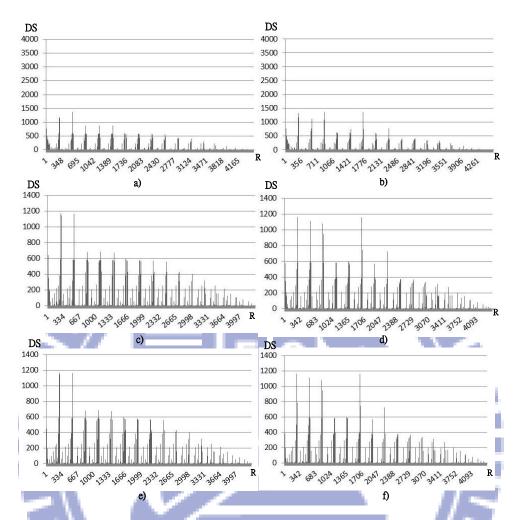

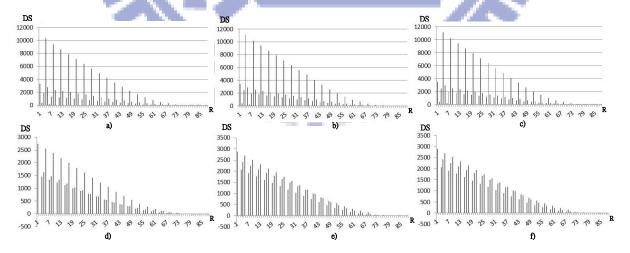

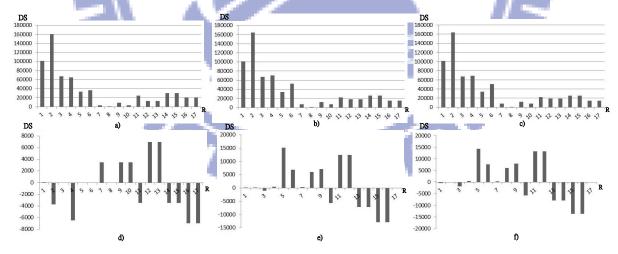

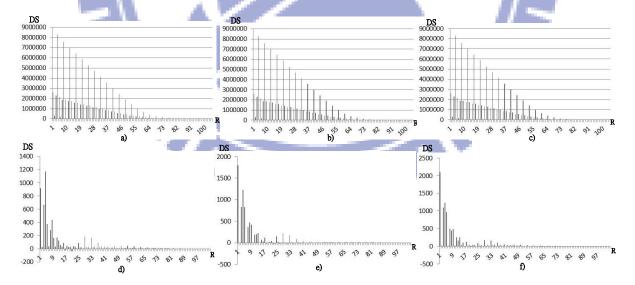

| Figure 24: Data reuse characteristic when modeling block execution sequentially for $sta$ . (a) Full reuse characteristic. (b) Showing the reuse characteristic for the range $RD = \{1, 400\}$ . (c) Showing the reuse characteristic for the range $RD = \{1, 100\}$ . Notice the particular patterns 56 |

| Figure 25: Data reuse characteristic when modeling block execution sequentially for $gsim$ . (a) Full reuse characteristic. (b) Showing the reuse characteristic for the range $RD = \{1, 400\}$ . (c) Showing the reuse characteristic for the range $RD = \{1, 100\}$                                    |

| Full reuse characteristic. (b) Showing the reuse characteristic for the range $RD=\{1, 400\}$ . (c) Showing the reuse characteristic for the range $RD=\{1, 100\}$                                                                                                                                         |

| Figure 27: Data reuse characteristic when modeling block execution sequentially for <i>vectoradd</i> . (a) Full reuse characteristic. (b) Showing the reuse characteristic for the range $RD=\{1, 400\}$ . (c) Showing the reuse characteristic for the range $RD=\{1, 100\}$                              |

| Figure 28: Source code for the kernels of <i>bfs</i> (a) and <i>sta</i> (b)                                                                                                                                                                                                                                |

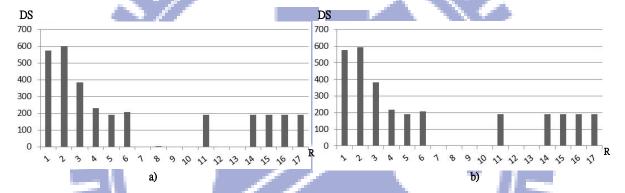

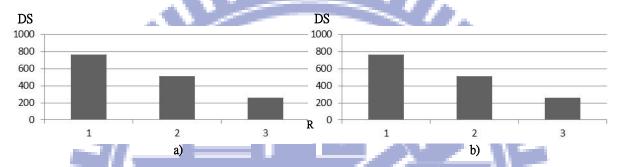

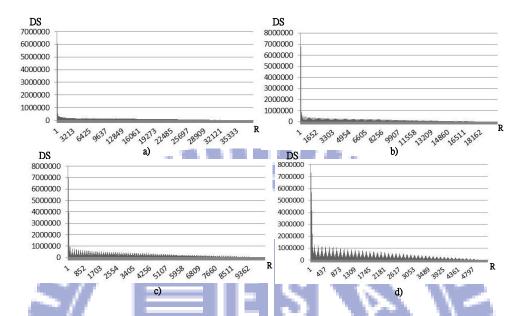

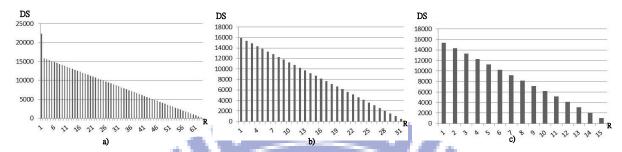

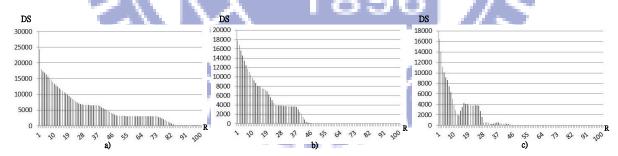

| Figure 29: Data reuse characteristic on a per block basis for <i>sta</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                                                                                                                              |

| Figure 30: Data reuse characteristic on a per block basis for <i>gsim</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                                                                                                                             |

| Figure 31: Data reuse characteristic on a per block basis for <i>bfs</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                                                                                                                              |

| Figure 32: Data reuse characteristic on a per block basis for <i>vectoradd</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                                                                                                                        |

| Figure 33: Data reuse characteristic on a per block basis for <i>nbf</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                                                                                                                              |

| Figure 34: Data reuse characteristic on a per block basis for <i>moldyn</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                          |

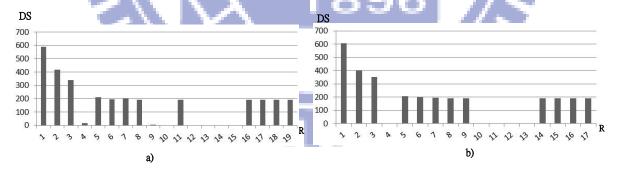

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 35: Data reuse characteristic on a per block basis for <i>irreg</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                           |

| Figure 36: Data reuse characteristic on a per block basis for <i>euler</i> . (a) Data reuse characteristic for thread block 0. (b) Full reuse characteristic for thread block 1                           |

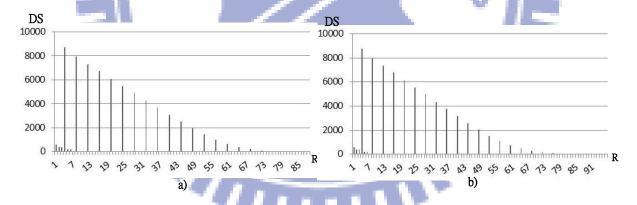

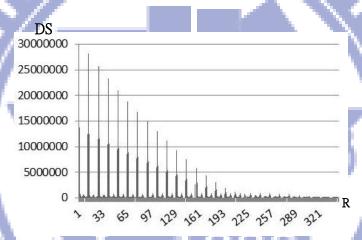

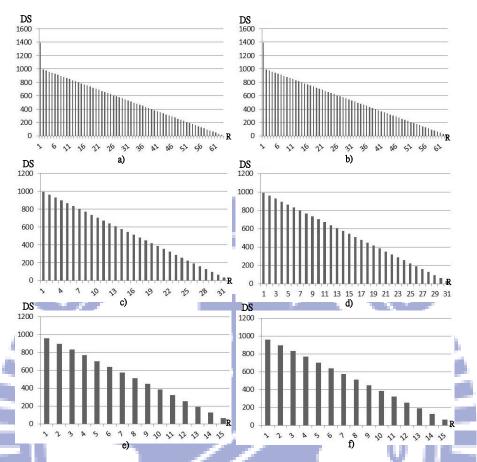

| Figure 37: Data reuse characteristic when modeling block execution when all blocks run in parallel for <i>sta</i>                                                                                         |

| Figure 38: Data reuse characteristic when modeling block execution when all blocks run in parallel for <i>gsim</i>                                                                                        |

| Figure 39: Data reuse characteristic when modeling block execution when all blocks run in                                                                                                                 |

| Figure 40: Data reuse characteristic when all blocks of <i>vectoradd</i> are modeled as executing in                                                                                                      |

| parallel                                                                                                                                                                                                  |

| Figure 41: Data reuse characteristic when all blocks of <i>nbf</i> are modeled as executing in parallel                                                                                                   |

| Figure 42: Data reuse characteristic when all blocks of <i>moldyn</i> are modeled as executing in parallel                                                                                                |

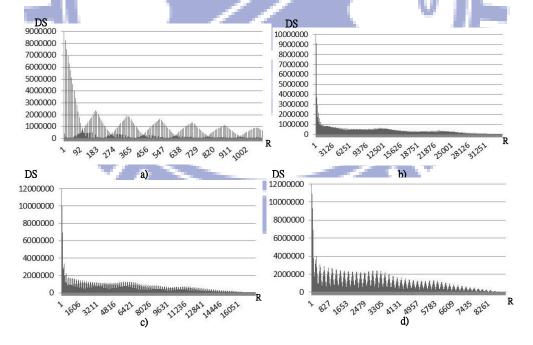

| Figure 43: Data reuse characteristic when all blocks of <i>irreg</i> are modeled as executing in parallel                                                                                                 |

| Figure 44: Data reuse characteristic when all blocks of <i>euler</i> are modeled as executing in parallel                                                                                                 |

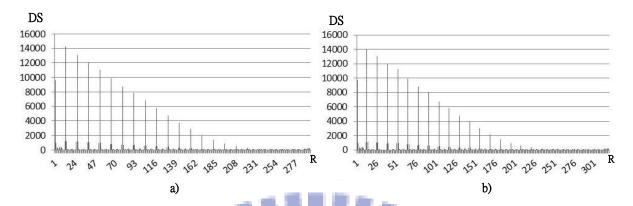

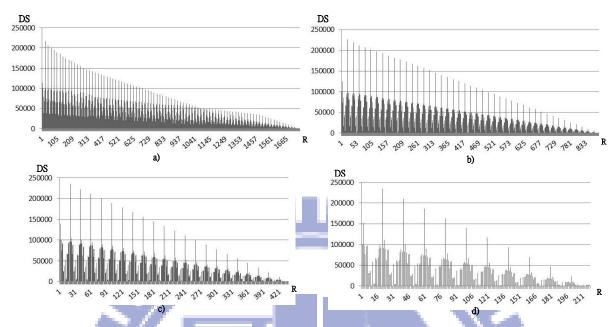

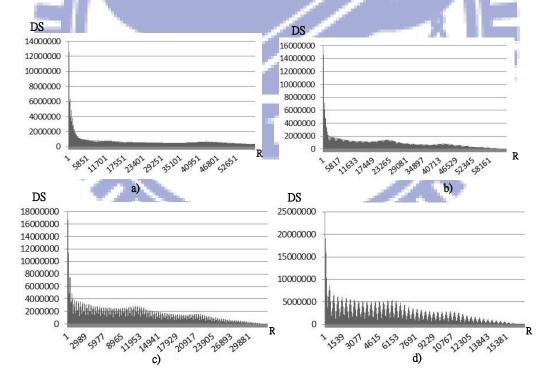

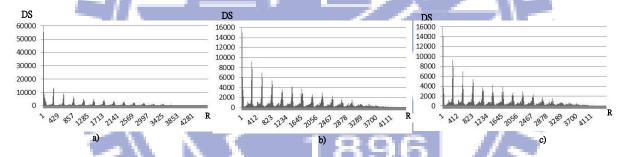

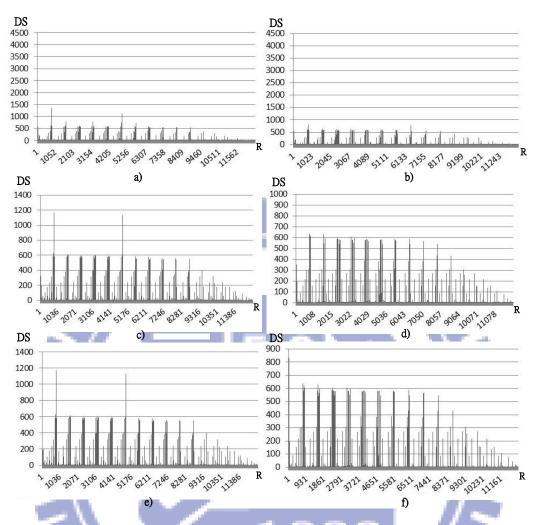

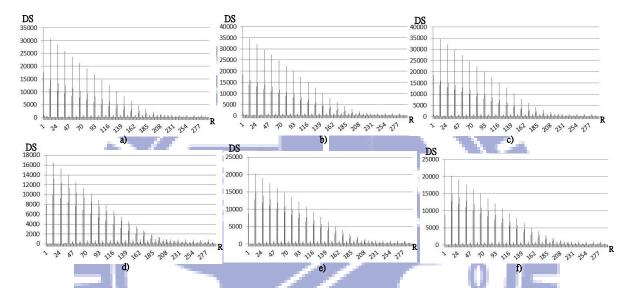

| Figure 45: Data reuse characteristic when only ' $K$ ' blocks of $sta$ are modeled as executing in parallel. (a) Data reuse characteristic for $K=2$ . (b) Data reuse characteristic for $K=4$ . (c) Data |

| reuse characteristic for $K=8$ . (d) Data reuse characteristic for $K=16$                                                                                                                                 |

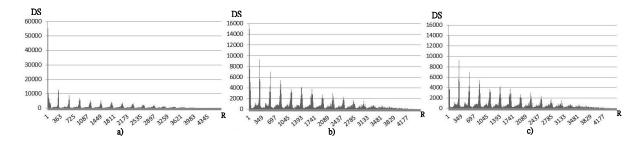

| parallel. (a) Data reuse characteristic when only $K$ blocks of <i>gsim</i> are modeled as executing in parallel. (a) Data reuse characteristic for $K=2$ . (b) Data reuse characteristic for $K=4$ . (c) Data reuse characteristic for $K=8$ . (d) Data reuse characteristic for $K=16$                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 47: Data reuse characteristic when only ' $K$ ' blocks of $bfs$ are modeled as executing in parallel. (a) Data reuse characteristic for $K=2$ . (b) Data reuse characteristic for $K=4$ . (c) Data reuse characteristic for $K=8$ . (d) Data reuse characteristic for $K=16$                                                                                                                                    |

| Figure 48: Data reuse characteristic when only ' $K$ ' blocks of <i>vectoradd</i> are modeled as executing in parallel. (a) Data reuse characteristic for $K=2$ . (b) Data reuse characteristic for $K=4$ . (c) Data reuse characteristic for $K=8$ . (d) Data reuse characteristic for $K=16$                                                                                                                         |

| Figure 49: Data reuse characteristic when only 'K' blocks of <i>nbf</i> are modeled as executing in parallel. (a) Data reuse characteristic for $K=2$ . (b) Data reuse characteristic for $K=4$ . (c) Data reuse characteristic for $K=8$ . (d) Data reuse characteristic for $K=16$                                                                                                                                   |

| Figure 50: Data reuse characteristic when only 'K' blocks of <i>moldyn</i> are modeled as executing in parallel. (a) Data reuse characteristic for $K=2$ . The reuse domain for this case is actually $RD=\{1,124030\}$ . The tool used to make the graphs could not display it properly. (b) Data reuse characteristic for $K=4$ . (c) Data reuse characteristic for $K=8$ . (d) Data reuse characteristic for $K=16$ |

| Figure 51: Data reuse characteristic when only 'K' blocks of <i>irreg</i> are modeled as executing in parallel. (a) Data reuse characteristic for K=2. (b) Data reuse characteristic for K=4. (c) Data reuse characteristic for K=8. (d) Data reuse characteristic                                                                                                                                                     |

| Figure 52: Data reuse characteristic when only 'K' blocks of <i>euler</i> are modeled as executing in parallel. (a) Data reuse characteristic for K=2. The reuse domain for this case is actually RD={1,66623}. The tool used to make the graphs could not display it properly. (b) Data reuse characteristic for K=4. (c) Data reuse characteristic for K=8. (d) Data reuse characteristic 71                         |

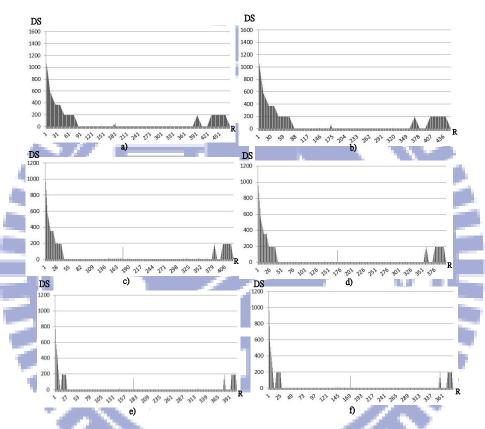

| Figure 53: Data reuse characteristic resulting when only $K=2$ blocks of $sta$ are modeled as executing in parallel. (a) Data reuse characteristic presented for reuse distance range $RD=\{1, 20\}$ . (b) Data reuse characteristic presented for reuse distance range $RD=\{21, 40\}$ . (c) Data reuse characteristic presented for reuse distance range $RD=\{41, 60\}$                                             |

| Figure 54: Data reuse characteristic resulting when only $K=16$ blocks of $sta$ are modeled as executing in parallel. (a) Data reuse characteristic presented for reuse distance range $RD=\{1, 20\}$ . (b) Data reuse characteristic presented for reuse distance range $RD=\{21, 40\}$ . (c) Data reuse characteristic presented for reuse distance range $RD=\{41, 60\}$                                            |

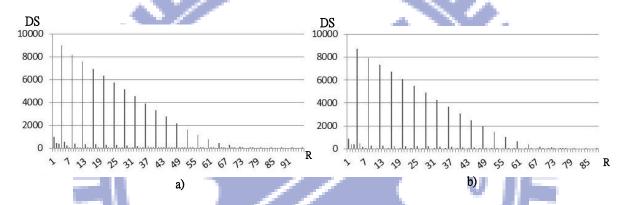

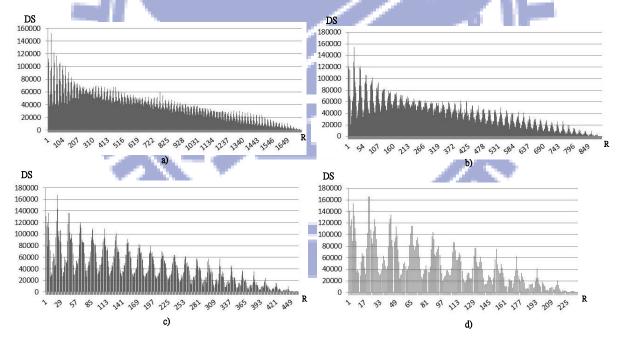

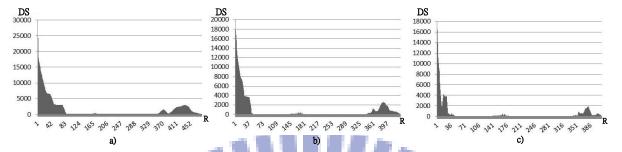

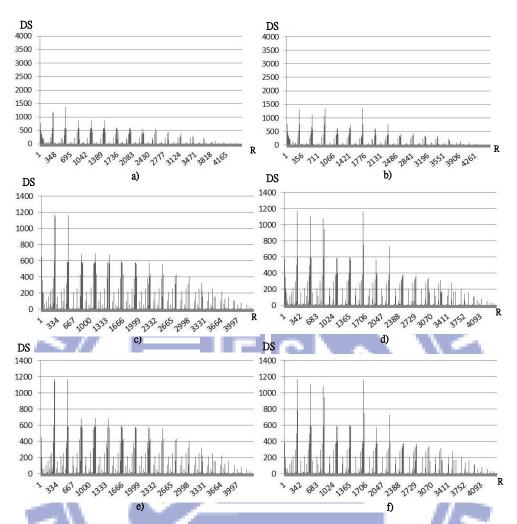

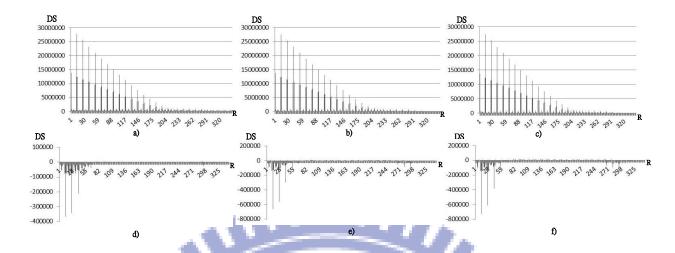

| Figure 55: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>sta</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 56: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>gsim</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster      |

| Figure 57: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>bfs</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster       |

| Figure 58: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>vectoradd</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster |

| Figure 59: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>nbf</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster       |

| Figure 60: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>irreg</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster     |

| Figure 61: Data reuse characteristic from the aggregate reference stream of all core clusters with varying number of load/store units in each core cluster for <i>euler</i> . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster     |

| Figure 62: Data reuse characteristic in reuse distance range $RD=\{0, 100\}$ of the aggregate reference stream of all core clusters with varying number of load/store units for $sta$ . (a) Data reuse characteristic for 16 load/store units per core cluster. (b) Data reuse characteristic for 32 load/store units per core cluster. (c) Data reuse characteristic for 64 load/store units per core cluster                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

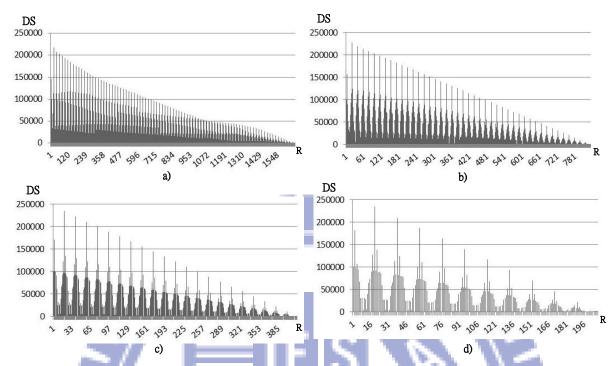

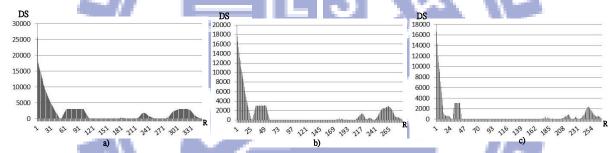

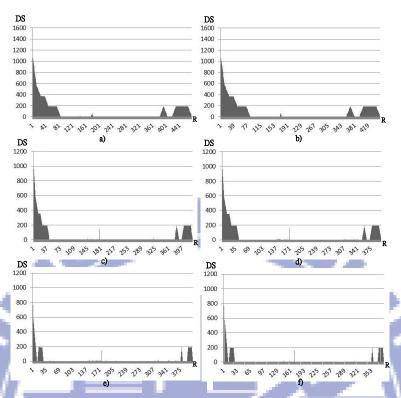

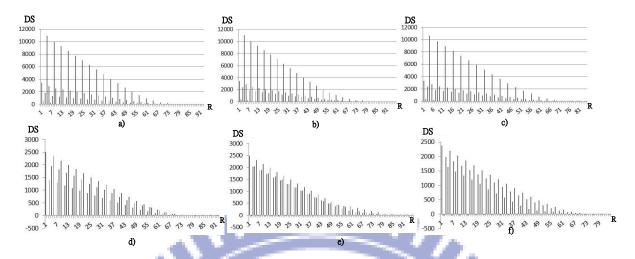

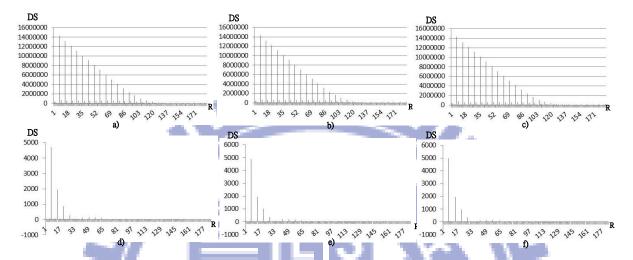

| Figure 63: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>sta</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units. (79                                                     |

| Figure 64: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>gsim</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units.                                                        |

| Figure 65: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>bfs</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units.                                                         |

| Figure 66: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>vectoradd</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units. (e) Second core cluster with 64 load/store units. |

| Figure 67: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>nbf</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units.                                                         |

| Figure 68: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>moldyn</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units.                                                      |

| Figure 69: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>irreg</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units.                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 70: Data reuse characteristic from the reference stream of the first and second core clusters with varying number of load/store units for <i>euler</i> . (a) First core cluster with 16 load/store units. (b) Second core cluster with 16 load/store units. (c) First core cluster with 32 load/store units. (d) Second core cluster with 32 load/store units. (e) First core cluster with 64 load/store units. (f) Second core cluster with 64 load/store units.                                                                                                                                                                     |

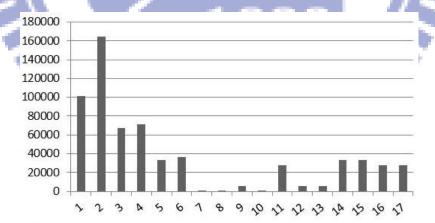

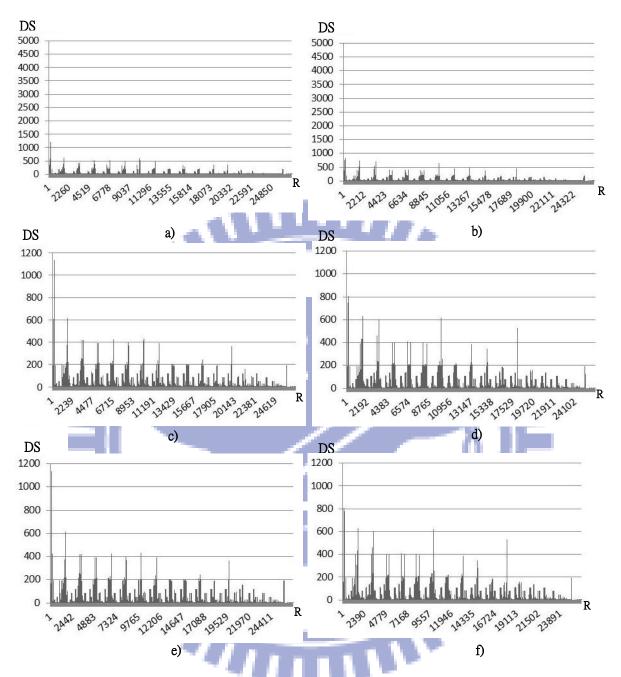

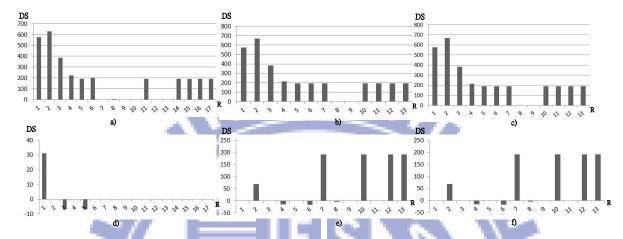

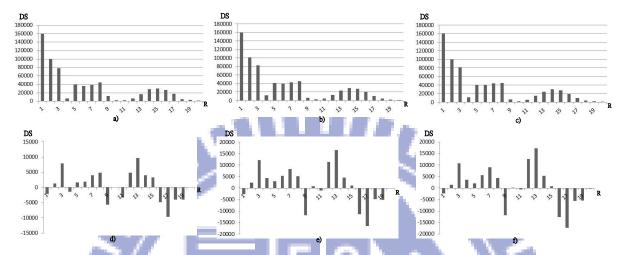

| Figure 71: Data reuse characteristic for block 0 of <i>sta</i> after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 17. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 802. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 802       |

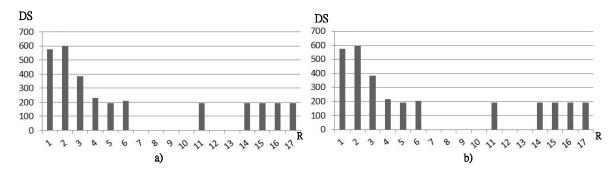

| Figure 72: Data reuse characteristic for block 0 of <i>gsim</i> after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 400. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 795. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 794     |

| Figure 73: Data reuse characteristic for block 0 of <i>bfs</i> after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 17. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 802 (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 802.       |

| Figure 74: Data reuse characteristic for block 0 of <i>nbf</i> after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 44458. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 60346 (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 60576 |

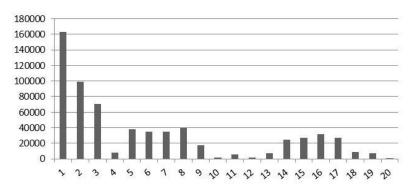

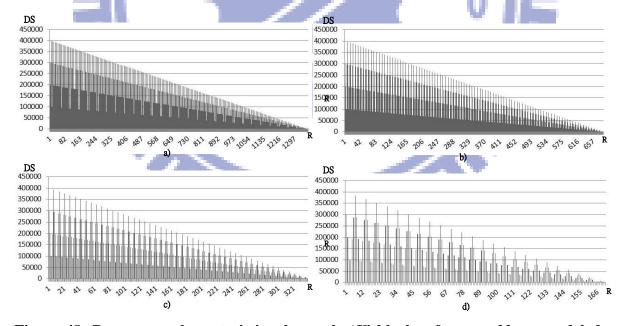

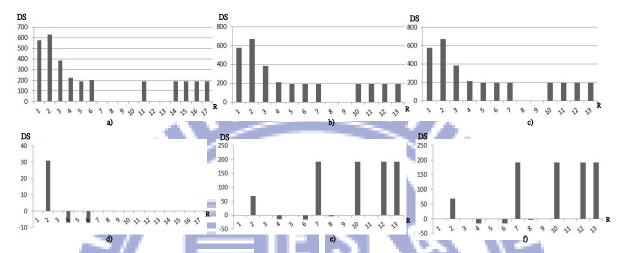

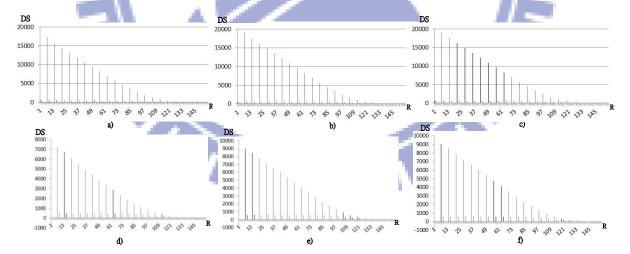

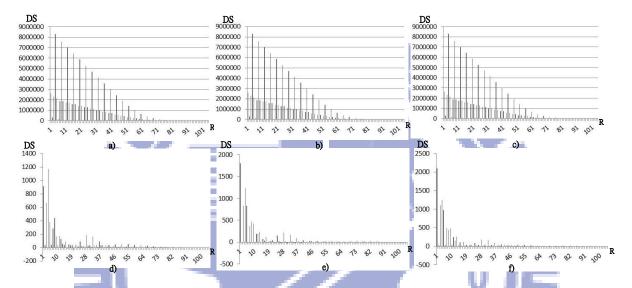

Figure 78: Data reuse characteristic for all blocks running in parallel of *sta* after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is -10216. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 14229. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 11940.... 92

Figure 79: Data reuse characteristic for all blocks running in parallel of *gsim* after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 8236. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 21363. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 17129.... 93

Figure 80: Data reuse characteristic for all blocks running in parallel of *bfs* after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp

clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is -10812. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 13361. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 11324.... 93

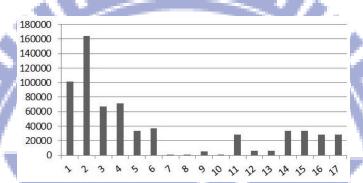

Figure 81: Data reuse characteristic for all blocks running in parallel of *nbf* after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 6053. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 7400. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 9138...... 94

Figure 83: Data reuse characteristic for all blocks running in parallel of *irreg* after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is -4445. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is -4402. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is -4647. ... 95

Figure 84: Data reuse characteristic for all blocks running in parallel of *euler* after coding optimizations. (a) After applying thread clustering. (b) After applying thread and warp clustering. (c) After applying thread clustering, warp clustering and block scheduling. (d) Comparison prior to optimizations and after thread clustering. Difference in the reuse degree is 8904. (e) Comparison prior to optimizations and after thread and warp clustering. Difference in the reuse degree is 7834. (f) Comparison prior to optimizations and after thread clustering, warp clustering and block scheduling. Difference in the reuse degree is 9172...... 96

#### **SYMBOLS**

DS: Data Reuse Degree, Data Sharing Degree.

RD: Reuse Distance.

R: short for Reuse Distance in Figures.

MI: memory instruction

M: multiplicity of an address in a memory instruction

$\mathbf{X}_{i \rightarrow j}$ : common address array between memory instructions 'i' and 'j'.

$X_i$ : address array of memory instruction 'i'.

#### I. INTRODUCTION