# The Effect of IEC-Like Fast Transients on *RC*-Triggered ESD Power Clamps

Cheng-Cheng Yen, Student Member, IEEE, and Ming-Dou Ker, Fellow, IEEE

Abstract—Four power-rail electrostatic-discharge (ESD) clamp circuits with different ESD-transient detection circuits have been fabricated in a 0.18- $\mu$ m CMOS process to investigate their susceptibility against electrical fast-transient (EFT) tests. Under EFT tests, where the integrated circuits in a microelectronic system have been powered up, the feedback loop used in the power-rail ESD clamp circuits may lock the ESD-clamping NMOS in a "latch-on" state. Such a latch-on ESD-clamping NMOS will conduct a huge current between the power lines to perform a latchuplike failure after EFT tests. A modified power-rail ESD clamp circuit has been proposed to solve this latchuplike failure and to provide a high-enough chip-level ESD robustness.

*Index Terms*—Electrical fast-transient (EFT) test, electromagnetic compatibility, electrostatic discharge (ESD), ESD protection circuit, latchup, system-level ESD stress.

# I. INTRODUCTION

W HOLE-CHIP electrostatic-discharge (ESD) protection has become a major reliability concern for modern integrated circuits (ICs) fabricated by scaled-down CMOS technologies [1]-[4]. The power-rail ESD clamp circuit located between the  $V_{\rm DD}$  and  $V_{\rm SS}$  lines in CMOS ICs has been designed for comprehensive ESD protection against the unexpected ESD damages located at the internal circuits of chips [5]–[7]. When the pin of a CMOS IC is zapped under the positive-to- $V_{\rm SS}$ (PS-mode), negative-to- $V_{\rm DD}$  (ND-mode), pin-to-pin, or  $V_{\rm DD}$ to-V<sub>SS</sub> ESD-stress conditions, the power-rail ESD clamp circuit can provide a low-impedance path between the  $V_{\rm DD}$ and  $V_{\rm SS}$  lines to efficiently discharge ESD current. Therefore, the power-rail ESD clamp circuit designed with high turn-on efficiency and fast turn-on speed is necessary for whole-chip ESD protection. In addition, some modified designs to further enhance the on-chip ESD protection performance of power-rail ESD clamp circuits had been reported [8]–[13].

Recently, electrical fast-transient (EFT) test [14] and systemlevel ESD stress [15] directly on the IC level have attracted

Manuscript received July 18, 2008; revised February 20, 2009. First published April 24, 2009; current version published May 20, 2009. This work was supported in part by the National Science Council (NSC), Taiwan, under Contract NSC 97-2221-E-009-170, by the Ministry of Economic Affairs, Taiwan, under Grant 97-EC-17-A-01-S1-104, and by Himax Technologies Inc., Taiwan. The review of this paper was arranged by Editor H. Jaouen.

C.-C. Yen is with the Nanoelectronics and Gigascale Systems Laboratory, Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan.

M.-D. Ker is with the Nanoelectronics and Gigascale Systems Laboratory, Institute of Electronics, National Chiao Tung University, Hsinchu 30010, Taiwan, and also with the Department of Electronic Engineering, I-Shou University, Kaohsiung 84041, Taiwan (e-mail: mdker@ieee.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2017625

more attention. Very few have been published so far, and [16]–[18] did not really address such current issues. Moreover, there are extensive discussions going on regarding what electrical transients that the IC actually receives. This tendency results from not only the integration of more functional circuits in a single chip but also the strict requirement of reliability regulation on the microelectronic system equipped with CMOS ICs. The EFT-induced transients act as exponential voltage pulse, which is different from the underdamped sinusoidal voltage waveforms generated from the system-level ESD test. Such EFT-induced electrical transients could cause transientinduced latchup (TLU) failure via the inevitable parasitic silicon-controlled rectifier in CMOS ICs [19]. It has also been reported [20], [21] that some CMOS ICs are very susceptible to electrical transient disturbance or system-level ESD stress, even though they have passed some component-level ESD specifications of human-body model (HBM) [22], machine model (MM) [23], and charged-device model (CDM) [24].

In this paper, the malfunction or wrong triggering behavior among four different on-chip power-rail ESD clamp circuits under EFT tests is investigated [25]. For some power-rail ESD clamp circuits designed with feedback loop in ESD-transient detection circuits, a serious latchuplike failure is caused by the latch-on state of the ESD-clamping NMOS after the EFT test. Furthermore, a modified design with additional NMOS reset function into the power-rail ESD clamp circuit is proposed to overcome such a latchuplike failure.

#### II. POWER-RAIL ESD CLAMP CIRCUITS

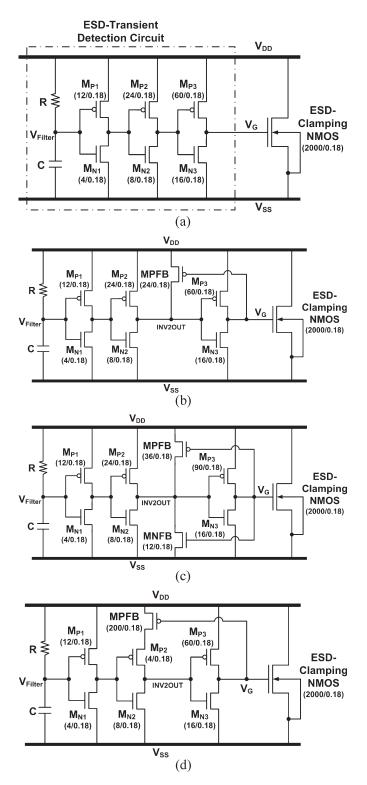

To provide effective on-chip ESD protection, four different power-rail ESD clamp circuits had been reported [8]–[12], which are shown in Fig. 1(a)–(d) with the names of the following: 1) power-rail ESD clamp circuit with typical *RC*-based detection; 2) power-rail ESD clamp circuit with PMOS feedback; 3) power-rail ESD clamp circuit with NMOS+PMOS feedback; and 4) power-rail ESD clamp circuit with cascaded PMOS feedback in this paper. Those power-rail ESD clamp circuits have been designed in the same silicon chip and fabricated in a 0.18- $\mu$ m CMOS process with oxide thickness of ~40 Å to investigate their susceptibility to EFT tests.

# A. Power-Rail ESD Clamp Circuit With Typical RC-Based Detection

The typical RC-based power-rail ESD clamp circuit is shown in Fig. 1(a) with a three-inverter buffer between the RC circuit and the ESD-clamping NMOS [8]. During the ESD zapping with the pulse rise time of  $\sim 10$  ns, the voltage level at the  $V_{\rm Filter}$  node is increased much more slowly than that on the  $V_{\rm DD}$  power line, because the RC circuit is designed with a time constant on the order of microseconds. Due to the delay of voltage increase at the  $V_{\rm Filter}$  node, the three-inverter buffer is powered by the ESD energy to conduct a voltage to the  $V_G$  node and then to turn on the ESD-clamping NMOS. The turned-on ESD-clamping NMOS, which provides a low-impedance path between the  $V_{\rm DD}$  and  $V_{\rm SS}$  power lines, will clamp the overstress ESD voltage to effectively protect the internal circuits against ESD damage. The turn-on time from the RC circuit is usually designed around  $\sim 100$  ns to meet the half-energy discharging time of the HBM ESD current waveform. After the designed turn-on time of  $\sim 100$  ns from the RC circuit, the residue of the ESD energy can be continually discharged through the ESDclamping NMOS, which has been kept in the snapback region after being triggered on by the ESD-transient detection circuit during ESD stress. Under normal circuit operating conditions, the power-rail ESD clamp circuit must be kept off to avoid power loss from  $V_{\rm DD}$  to  $V_{\rm SS}$ . To meet such a timing requirement, the RC time constant in the RC-based ESD-transient detection circuit is typically designed with 0.1–1  $\mu$ s to achieve the design constraints [8].

# B. Power-Rail ESD Clamp Circuit With PMOS Feedback

Another design consideration for the power-rail ESD clamp circuit is the circuit immunity to false triggering during a power-up condition. The power-rail ESD clamp circuit should be turned on when ESD stress appears across the  $V_{\rm DD}$  and  $V_{\rm SS}$  power lines but must be kept off when the IC is under a normal power-on condition. The *RC* time constant was usually designed around  $0.1-1 \,\mu$ s to meet such a requirement. However, the large *RC* time constant used in the power-rail ESD clamp circuit may cause false triggering during a fast power-up condition with a rise time of less than 10  $\mu$ s. The modified powerrail ESD clamp circuit incorporated with PMOS feedback, as shown in Fig. 1(b), was developed to mitigate such a mistrigger problem [9]. The transistor MPFB can help to keep the ESDclamping NMOS off during the normal power-up condition.

# C. Power-Rail ESD Clamp Circuit With NMOS+PMOS Feedback

In advanced CMOS technology with thinner gate oxide, the power-rail ESD clamp circuit with a large MOS capacitance in the RC timer had been found to cause significant standby power consumption due to the gate oxide leakage [10]. Thus, the power-rail ESD clamp circuit with small MOS capacitance is desired to combat the gate oxide leakage. It was reported that the power-rail ESD clamp circuit incorporated with a regenerative feedback network can be used to significantly reduce the RC time constant, as shown in Fig. 1(c) [11]. Transistors MPFB and MNFB in Fig. 1(c) provide a feedback loop to latch the ESD-clamping NMOS in the conductive state during an ESDstress condition. With this feedback loop in the power-rail ESD clamp circuit, the dynamic currents of  $M_{P2}$ ,  $M_{N2}$ , MPFB, and MNFB determine the critical voltage to trigger on the ESD-

Fig. 1. Four prior power-rail ESD clamp circuits designed with (a) typical RC-based detection, (b) PMOS feedback, (c) NMOS+PMOS feedback, and (d) cascaded PMOS feedback. The device dimensions of transistors in each circuit realized in a 0.18- $\mu$ m CMOS process are also indicated.

clamping NMOS. After the timing out of RC time constant in the ESD-transient detection circuit, transistor  $M_{P2}$  begins to conduct and increase the potential of the INV2OUT node. The settling potential of the INV2OUT node is set by the current balance between  $M_{P2}$  and MNFB. Thus, the device ratios of  $M_{P2}$  and MNFB in the power-rail ESD clamp circuit with NMOS+PMOS feedback should be appropriately selected.

# D. Power-Rail ESD Clamp Circuit With Cascaded PMOS Feedback

Another RC-based power-rail ESD clamp circuit with cascaded PMOS feedback was also developed to reduce the RCtime constant and solve the false-triggering issue during a fast power-up condition, as shown in Fig. 1(d) [12]. PMOS transistor MPFB is connected to form the cascaded feedback loop. During an ESD-stress condition, transistor MPFB is turned off, and the INV2OUT node is remained in a lowvoltage state. Thus, the turn-on time of the ESD-clamping NMOS in this design can be longer than that of the typical RC-based power-rail ESD clamp circuit. If the ESD-clamping NMOS is mistriggered during a fast power-up condition or by an overvoltage noise under normal operating conditions, the voltage on the INV2OUT node can be recharged up toward  $V_{\rm DD}$  by the subthreshold current of MPFB. Therefore, the ESDclamping NMOS will not stay at the latch-on state and turn itself off after the fast power-up condition.

#### E. Realization in Silicon Chip

Some simulations have been provided to realize the aforementioned four power-rail ESD clamp circuits in the CMOS process. The corresponding device dimensions of all transistors in these four power-rail ESD clamp circuits realized in a 0.18- $\mu$ m CMOS process are also shown in Fig. 1(a)–(d). To simply the comparison for the latchup-like failure in this paper, the *RC* values in the ESD-transient detection circuits of these four power-rail ESD clamp circuits are set with the same *R* of 50 k $\Omega$  and *C* of 2 pF in silicon fabrication. For EFT verification, the test chips are packaged in the 40-pin sidebrazed package without classical filtering on the evaluation printed circuit board.

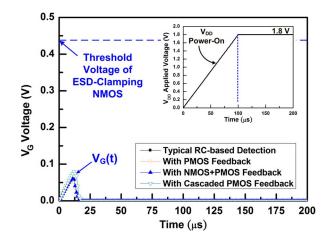

In the inset of Fig. 2, a  $V_{\rm DD}$  power-on waveform with a rise time of 0.1 ms and a voltage height of 1.8 V is applied to the  $V_{\rm DD}$  line of the power-rail ESD clamp circuits. During such a  $V_{\rm DD}$  power-on transition, the voltage waveforms on the  $V_G$  node among the four power-rail ESD clamp circuits are shown in Fig. 2. The  $V_G$  peak voltages in Fig. 2 are all below the threshold voltage (~0.44 V) of the NMOS, so the ESD-clamping NMOS in these four power-rail ESD clamp circuits will be kept off after the  $V_{\rm DD}$  power-on transition.

In the inset of Fig. 3, a fast-ramp voltage with a rise time of 10 ns is used to simulate the rising edge of the HBM ESD pulse. The pulse height of the fast-ramp voltage set of 5 V is used to monitor the voltage on the  $V_G$  node before the occurrence of drain breakdown at the ESD-clamping NMOS. As shown in Fig. 3, among these four power-rail ESD clamp circuits, the voltage waveforms on the  $V_G$  node are simultaneously increased when the fast-ramp voltage is applied to  $V_{DD}$ , whereas  $V_{SS}$  is grounded. With the NMOS+PMOS feedback or cascaded PMOS feedback in the power-rail ESD clamp circuits, the turn-on time (with  $V_G$  being greater than its threshold voltage) of the ESD-clamping NMOS is really extended much

Fig. 2. HSPICE-simulated voltage waveforms on the  $V_G$  node among the four prior power-rail ESD clamp circuits under a normal  $V_{\rm DD}$  power-on transition with a 0–1.8-V ramp voltage applied to  $V_{\rm DD}$ . The rise time of  $V_{\rm DD}$  ramp voltage is 0.1 ms in this simulation.

Fig. 3. HSPICE-simulated voltage waveforms on the  $V_G$  node among the four prior power-rail ESD clamp circuits under an ESD-stress condition. A 0–5-V ramp voltage with a rise time of 10 ns is used to simulate the rising edge of the HBM ESD pulse before the drain breakdown on the ESD-clamping NMOS.

longer than the default 100-ns RC time constant in the traditional design of Fig. 1(a) with typical RC-based detection.

# III. EFT TEST

#### A. Measurement Setup

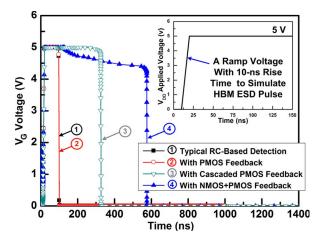

The IEC 61000-4-4 standard [14] has defined the immunity levels and test methods to verify the electronic equipment against repetitive EFTs. The EFT test is a test with repetitive bursts consisting of a number of fast pulses, which can be coupled into the power supply, control, signal, and ground ports of the electronic equipment. The minimum start values of the pulse peak are  $\pm 200$  V from the EFT tester. For EFT pulses with a repetition frequency of 5 kHz, the measured voltage waveforms with EFT voltages of -200 and +200 V on a  $50-\Omega$  load are shown in Fig. 4(a) and (b). With the impedance matching to  $50 \Omega$ , the measured pulse peak is half of the input EFT voltage. Therefore, the measured pulse peaks are -100and +100 V in Fig. 4(a) and (b), respectively. The waveform of a single EFT pulse has a rise time of  $\sim 5$  ns and a pulse duration (time interval at half of the peak EFT voltage) of  $\sim 50$  ns. With

Fig. 4. Measured voltage waveforms of EFT pulses on a 50- $\Omega$  load with a repetition rate of 5 kHz and EFT voltages of (a) -200 V and (b) +200 V.

an EFT repetition frequency of 5 kHz, the time interval between each pulse is 0.2 ms. By EFT regulation, the application time should be longer than 1 min, and both positive and negative polarities must be applied.

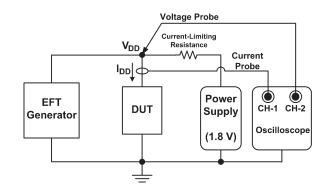

The measurement setup for the EFT test on a CMOS IC under a power-up condition is shown in Fig. 5. A supply voltage of 1.8 V is used as  $V_{\rm DD}$ , and the EFT generator is connected directly to the device under test (DUT) through a cable in this paper. The voltage and current waveforms on the DUT (at the  $V_{\rm DD}$  node) during/after the EFT test are monitored by a digital oscilloscope. With such a measurement setup, the susceptibility of different power-rail ESD clamp circuits against EFT tests can be evaluated. Before any EFT zapping, the initial  $V_{\rm DD}$  voltage level on the IC is measured to make sure the correct bias of 1.8 V. If the latchuplike failure occurs after EFT zapping, the potential on  $V_{\rm DD}$  node will be pulled down to a much lower level due to the latch-on state of the ESD-clamping NMOS, and  $I_{\rm DD}$  will be significantly increased.

### B. Measurement Results

With the EFT measurement setup shown in Fig. 5, the  $V_{DD}$  and  $I_{DD}$  transient responses can be recorded by the oscilloscope

Fig. 5. Measurement setup for a direct EFT test on a CMOS IC in the DUT powered with 1.8-V supply. The  $V_{\rm DD}$  and  $I_{\rm DD}$  transient waveforms are recorded by a digital oscilloscope with a sampling rate of 5 GS/s.

to clearly indicate whether the latchuplike failure occurs or not. For the power-rail ESD clamp circuits designed with typical RC-based detection or with PMOS feedback, the latchuplike failure does not occur after EFT tests because  $I_{DD}$  is still kept at zero, even though the EFT voltage is as high as -800 or +800 V.

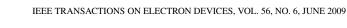

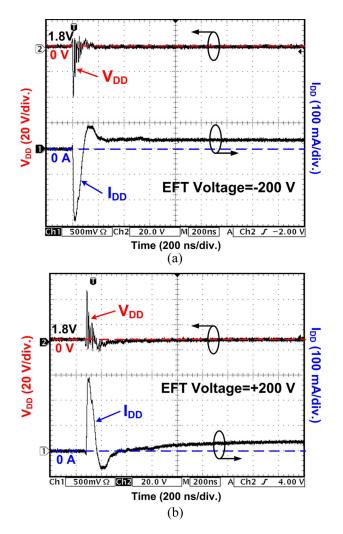

Fig. 6(a) and (b) shows the measured  $V_{\rm DD}$  and  $I_{\rm DD}$  transient responses on the power-rail ESD clamp circuit designed with NMOS+PMOS feedback under the EFT test with EFT voltages of -200 and +200 V, respectively. After the EFT test with an EFT voltage of -200 V, the latchuplike failure can be initiated in this power-rail ESD clamp circuit, because I<sub>DD</sub> is significantly increased and  $V_{DD}$  is pulled down, as shown in Fig. 6(a). The latchuplike failure can also be found in Fig. 6(b) due to the EFT test with an EFT voltage of +200 V. All the PMOS and NMOS devices in the ESD-transient detection circuits have been surrounded with double guard rings in the layout to guarantee no latchup issue in this part [26]. This implies that the feedback loop in the ESD-transient detection circuit is locked after the EFT test and continually keeps the ESD-clamping NMOS in the latch-on state. From the observed voltage and current waveforms, such a  $I_{\rm DD}$  is conducted by the latch-on state of the ESD-clamping NMOS after EFT tests. For the power-rail ESD clamp circuit designed with cascaded PMOS feedback, the measured  $V_{\rm DD}$  and  $I_{\rm DD}$  transient responses are shown in Fig. 7(a) and (b) under the EFT test with EFT voltages of -200 and +500 V, respectively. A similar latchuplike failure also occurs in this power-rail ESD clamp circuit due to the latch-on state of the ESD-clamping NMOS after EFT tests.

The susceptibility among the aforementioned four power-rail ESD clamp circuits against EFT tests is listed in Table I. From the experimental results, the power-rail ESD clamp circuit designed with NMOS+PMOS feedback is highly sensitive to TLU-like failure. The power-rail ESD clamp circuits designed with typical *RC*-based detection or with PMOS feedback are free to such a latchuplike failure under EFT tests.

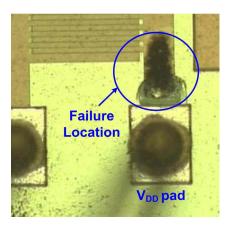

The failure location after the EFT test has been inspected, as shown in Fig. 8. The failure is located at the  $V_{\rm DD}$  metal line from the  $V_{\rm DD}$  pad to the power-rail ESD clamp circuit, which was drawn with a metal width of 30  $\mu$ m in the test chip. The current continually that is conducted through the latch-on state of the ESD-clamping NMOS, which is drawn with a large device dimension W/L of 2000  $\mu$ m/0.18  $\mu$ m for consideration

Fig. 6. Measured  $V_{\rm DD}$  and  $I_{\rm DD}$  transient waveforms on the power-rail ESD clamp circuit with NMOS+PMOS feedback under an EFT test with EFT voltages of (a) -200 V and (b) +200 V. Latchuplike failures occur after the EFT test with increased  $I_{\rm DD}$  and decreased  $V_{\rm DD}$ .

of high ESD robustness, causes such a burned-out failure on the metal line after EFT tests.

#### IV. MODIFIED POWER-RAIL ESD CLAMP CIRCUIT

In order to meet the EFT regulation, a modified design on the power-rail ESD clamp circuit without suffering a latchuplike failure is highly desired for CMOS ICs. It was ever reported that a power-rail ESD clamp circuit with a traditional rise time detector and a separated on-time control circuit can improve the immunity to false triggering [13]. In this paper, another modified power-rail ESD clamp circuit is proposed to avoid such a latchuplike failure. This new modified power-rail ESD clamp circuit can provide a high-enough chip-level ESD robustness but without suffering the latchuplike failure during the EFT test.

### A. Power-Rail ESD Clamp Circuit With NMOS Reset Function

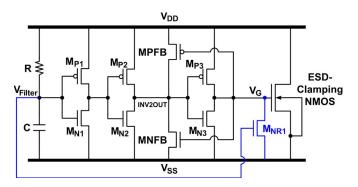

Fig. 9 shows the modified power-rail ESD clamp circuit with NMOS reset function to overcome the latchuplike failure, which is realized with NMOS+PMOS feedback and an additional NMOS device  $(M_{\rm NR1})$  to provide the reset function

Fig. 7. Measured  $V_{\rm DD}$  and  $I_{\rm DD}$  transient waveforms on the power-rail ESD clamp circuit with cascaded PMOS feedback under an EFT test with EFT voltages of (a) -200 V and (b) +500 V. Latchuplike failures occur after the EFT test with increased  $I_{\rm DD}$  and decreased  $V_{\rm DD}$  voltage.

TABLE I

Comparison on Susceptibility Against EFT Tests Among the

Four Prior Power-Rail ESD Clamp Circuits and the Modified

Power-Rail ESD Clamp Circuit With NMOS + PMOS Feedback

And NMOS Reset Function

| Power-Rail ESD<br>Clamp Circuits                      | Positive EFT<br>Voltage | Negative EFT<br>Voltage |

|-------------------------------------------------------|-------------------------|-------------------------|

| Typical RC-Based<br>Detection                         | Over +800 V             | Over -800 V             |

| With PMOS<br>Feedback                                 | Over +800 V             | Over -800 V             |

| With NMOS+PMOS<br>Feedback                            | Under +200 V            | Under -200 V            |

| With Cascaded<br>PMOS Feedback                        | +500 V                  | Under -200 V            |

| With NMOS+PMOS<br>Feedback and NMOS<br>Reset Function | Over +800 V             | Over -800 V             |

after EFT tests. When the ESD-clamping NMOS is latched on, the NMOS device  $(M_{\rm NR1})$  will be turned on after the timeout of RC time constant. Thus, the gate potential  $(V_G)$  of the

Fig. 8. Failure location of the power-rail ESD clamp circuit after EFT tests. The metal line connected between the  $V_{\rm DD}$  pad and the ESD-clamping NMOS is burned out due to the EFT test.

Fig. 9. Modified power-rail ESD clamp circuit designed with NMOS+PMOS feedback and additional NMOS reset function to overcome the latchuplike failure.

ESD-clamping NMOS will be pulled down toward 0 V to release the "latch-on" state after EFT tests. Compared with the power-rail ESD clamp circuit with NMOS+PMOS feedback, the modified power-rail ESD clamp circuit with NMOS reset function has a shorter turn-on time of ~380 ns on the  $V_G$ waveform by simulation when a 5-V ESD-like voltage ramp is applied to  $V_{DD}$ . The simulated  $V_G$  waveform is similar to those shown in Fig. 3.

#### **B.** Experimental Results

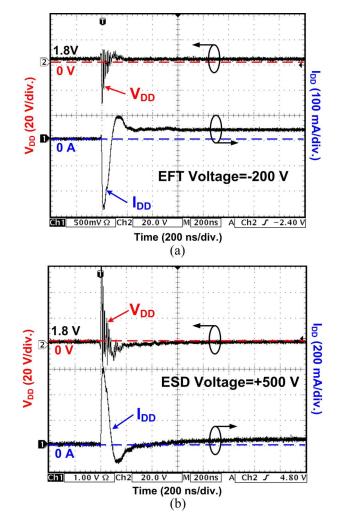

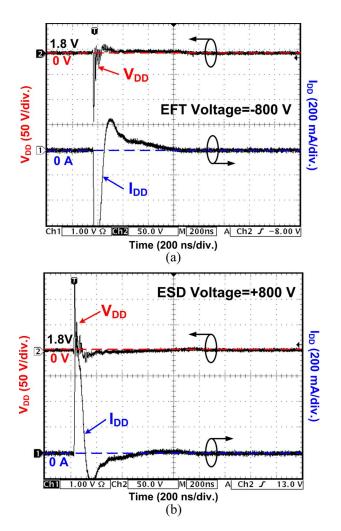

The measured  $V_{\rm DD}$  and  $I_{\rm DD}$  transient responses on the modified power-rail ESD clamp circuit under EFT tests with EFT voltages of -800 and +800 V are shown in Fig. 10(a) and (b), respectively. After the EFT test with a negative (positive) EFT voltage of -800 V (+800 V), the latchuplike failure does not occur in Fig. 10(a) [Fig. 10(b)], where neither  $I_{\rm DD}$  is not increased nor  $V_{\rm DD}$  is not pulled down after EFT tests. The susceptibility of the modified power-rail ESD clamp circuit with NMOS reset function against EFT tests has also been included in Table I for comparison with prior works.

To verify the chip-level ESD robustness among the powerrail ESD clamp circuits studied in this paper, the ESD-clamping NMOS has been drawn with the same large device dimension  $(W/L = 2000 \ \mu m/0.18 \mu m)$  for fair comparison. Therefore, the layout area of these five different power-rail ESD clamp

Fig. 10. Measured  $V_{\rm DD}$  and  $I_{\rm DD}$  transient waveforms on the modified powerrail ESD clamp circuit with additional NMOS reset function under an EFT test with EFT voltages of (a) -800 V and (b) +800 V. No latchuplike failure occurs in this EFT test.

circuits is dominated by the ESD-clamping NMOS, which is drawn as 95  $\mu$ m × 80  $\mu$ m. An ESD-transient detection circuit only occupies a smaller part in the whole layout area of each power-rail ESD clamp circuit, which is around 40  $\mu$ m × 80  $\mu$ m in the silicon chip. The modified power-rail ESD clamp circuit with NMOS reset function and the aforementioned four different power-rail ESD clamp circuits can all pass an HBM ESD stress of over ±8 kV and a CDM ESD stress of over ±1 kV in the 40-pin side-brazed package when the die size of the test chip is 1500  $\mu$ m × 1500  $\mu$ m.

#### V. CONCLUSION

Some of the advanced on-chip power-rail ESD clamp circuits with feedback loop have been found to suffer a latchuplike failure after EFT tests. The feedback loop used in the power-rail ESD clamp circuits provides a lock function to keep the ESD-clamping NMOS in a "latch-on" state. The latch-on ESD-clamping NMOS conducts a huge current between the  $V_{\rm DD}$  and  $V_{\rm SS}$  lines to perform this latchuplike failure after EFT tests. A modified design on the power-rail ESD clamp circuit with NMOS+PMOS feedback, with the additional NMOS reset

function to turn off the ESD-clamping NMOS after EFT tests, has been successfully verified in a 0.18- $\mu$ m CMOS process. The modified power-rail ESD clamp circuit with NMOS reset function can sustain the EFT voltage of over  $\pm 800$  V without causing a latchuplike failure after EFT tests. The chip-level ESD robustness of the modified power-rail ESD clamp circuit with NMOS reset function can still be kept as good as those of the prior power-rail ESD clamp circuits with feedback loop.

# ACKNOWLEDGMENT

The authors would like to thank C.-C. Tsai and Dr. T.-Y. Chen for their valuable technical discussions and the project supported by Himax Technologies, Inc., Taiwan.

#### REFERENCES

- [1] S. Voldman, ESD: Circuits and Devices. Hoboken, NJ: Wiley, 2006.

- [2] A. Amerasekera and C. Duvvury, ESD in Silicon Integrated Circuits, 2nd ed. Hoboken, NJ: Wiley, 2002.

- [3] S. Dabral and T. Maloney, Basic ESD and I/O Design. Hoboken, NJ: Wiley, 1988.

- [4] A. Wang, On-Chip ESD Protection for Integrated Circuits. Norwell, MA: Kluwer, 2002.

- [5] C. Duvvury, R. Rountree, and O. Adams, "Internal chip ESD phenomena beyond the protection circuit," *IEEE Trans. Electron Devices*, vol. 35, no. 12, pp. 2133–2139, Dec. 1998.

- [6] M.-D. Ker, "Whole-chip ESD protection design with efficient V<sub>DD</sub>-to-V<sub>SS</sub> clamp circuit for submicron CMOS VLSI," *IEEE Trans. Electron Devices*, vol. 46, no. 1, pp. 173–183, Jan. 1999.

- [7] M.-D. Ker, T.-Y. Chen, C.-Y. Wu, and H.-H. Chang, "ESD protection design on analog pin with very low input capacitance for high-frequency or current-mode applications," *IEEE J. Solid-State Circuits*, vol. 35, no. 8, pp. 1194–1199, Aug. 2000.

- [8] R. Merrill and E. Issaq, "ESD design methodology," in *Proc. EOS/ESD Symp.*, 1993, pp. 233–237.

- [9] P. Tong, W. Chen, R. Jiang, J. Hui, P. Xu, and P. Liu, "Active ESD shunt with transistor feedback to reduce latchup susceptibility or false triggering," in *Proc. IEEE IPFA*, 2004, pp. 89–92.

- [10] S. Poon and T. Maloney, "New considerations for MOSFET power clamps," in *Proc. EOS/ESD Symp.*, 2002, pp. 1–5.

- [11] J. Smith and G. Boselli, "A MOSFET power supply clamp with feedback enhanced triggering for ESD protection in advanced CMOS technologies," in *Proc. EOS/ESD Symp.*, 2003, pp. 8–16.

- [12] J. Li, R. Gauthier, and E. Rosenbaum, "A compact, timed-shutoff, MOSFET-based power clamp for on-chip ESD protection," in *Proc. EOS/ESD Symp.*, 2004, pp. 273–279.

- [13] M. Stockinger, J. Miller, M. Khazhinsky, C. Torres, J. Weldon, B. Preble, M. Bayer, M. Akers, and V. Kamat, "Boosted and distributed rail clamp networks for ESD protection in advanced CMOS technologies," in *Proc. EOS/ESD Symp.*, 2003, pp. 17–26.

- [14] EMC—Part 4-4: Testing and Measurement Techniques—Electrical Fast Transient/Burst Immunity Test, 2004. IEC 61000-4-4 International Standard.

- [15] EMC—Part 4-2: Testing and Measurement Techniques—Electrostatic Discharge Immunity Test, 2001. IEC 61000–4-2 International Standard.

- [16] G. Cerri, R. Leo, and V. Primiani, "Investigation of radiated susceptibility during EFT tests," *IEEE Trans. Electromagn. Compat.*, vol. 39, no. 4, pp. 298–303, Nov. 1997.

- [17] G. Cerri, R. Leo, and V. Primiani, "Electrical fast-transient: Conducted and radiated disturbance determination by a complete source modeling," *IEEE Trans. Electromagn. Compat.*, vol. 43, no. 1, pp. 37–44, Feb. 2001.

- [18] D. Smith, "An investigation into the performance of the IEC 1000-4-4 capacitive clamp," in *Proc. EOS/ESD Symp.*, 1996, pp. 223–226.

- [19] C.-C. Yen and M.-D. Ker, "Transient-induced latchup in CMOS integrated circuits due to electrical fast transient (EFT) test," in *Proc. IEEE IPFA*, Jul. 11–13, 2007, pp. 253–256.

- [20] D. Smith and A. Wallash, "Electromagnetic interference (EMI) inside a hard disk driver due to external ESD," in *Proc. EOS/ESD Symp.*, 2002, pp. 32–36.

- [21] M.-D. Ker and Y.-Y. Sung, "Hardware/firmware co-design in an 8-bits microcontroller to solve the system-level ESD issue on keyboard," in *Proc. EOS/ESD Symp.*, 1999, pp. 352–360.

- [22] ESD Association Standard Test Method ESD STM5.1-2001, for Electrostatic Discharge Sensitivity Testing—Human Body Model (HBM)—Component Level, 2001, Rome, NY: ESD Association.

- [23] ESD Association Standard Test Method ESD STM5.2-1999, for Electrostatic Discharge Sensitivity Testing—Machine Model (MM)—Component Level, 1999, Rome, NY: ESD Association.

- [24] ESD Association Standard Test Method ESD STM5.3.1-1999, for Electrostatic Discharge Sensitivity Testing—Charge Device Model—Component Level, 1999, Rome, NY: ESD Association.

- [25] M.-D. Ker and C.-C. Yen, "Unexpected failure in power-rail ESD clamp circuits of CMOS integrated circuits in microelectronics systems during electrical fast transient (EFT) test and the re-design solution," in *Proc. IEEE Int. Zurich Symp. Electromagn. Compat.*, 2007, pp. 69–72.

- [26] M.-D. Ker and W.-Y. Lo, "Methodology on extracting compact layout rules for latchup prevention in deep-submicron bulk CMOS technology," *IEEE Trans. Semicond. Manuf.*, vol. 16, no. 2, pp. 319–334, May 2003.

**Cheng-Cheng Yen** (S'07) received the B.S. degree from the Department of Electrical and Control Engineering and the M.S. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 1998 and 2000, respectively, where he is currently working toward the Ph.D. degree in the Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan.

His current research interests include transient detection circuits and IC reliability.

**Ming-Dou Ker** (S'92–M'94–SM'97–F'08) received the Ph.D. degree from the Institute of Electronics, National Chiao Tung University, Hsinchu, Taiwan, in 1993.

He was the Department Manager with the VLSI Design Division, Computer and Communication Research Laboratories, Industrial Technology Research Institute, Hsinchu. Since 2004, he has been a Full Professor with the Department of Electronics Engineering, NCTU. From 2006 to 2008, he was the Director of the Master Degree Program with the

College of Electrical Engineering and Computer Science, NCTU, as well as the Associate Executive Director of the National Science and Technology Program on System-on-Chip, Taiwan. In 2008, he was rotated to serve as the Chair Professor and the Vice-President of I-Shou University, Kaohsiung, Taiwan, where he is also currently with the Department of Electronic Engineering. He has proposed many inventions to improve the reliability and quality of integrated circuits, which have been granted with 139 U.S. patents and 144 Taiwan patents. He had been invited to teach and/or to consult the reliability and quality design for integrated circuits by hundreds of design houses and semiconductor companies in the worldwide IC industry. In the field of reliability and quality design for circuits and systems in CMOS technology, he has published over 360 technical papers in international journals and conferences. His current research interests include reliability and quality design for nanoelectronics and gigascale systems, high-speed and mixed-voltage I/O interface circuits, onglass circuits for system-on-panel applications, and biomimetic circuits and systems for intelligent prosthesis.

Dr. Ker has served as a member of the Technical Program Committee and the Session Chair of numerous international conferences. He served as the Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS. He has been selected as the Distinguished Lecturer in the IEEE Circuits and Systems Society (2006–2007) and the IEEE Electron Devices Society (2008–2009). He was the Foundation President of the Taiwan ESD Association. In 2008, he has been elevated as an IEEE Fellow "for his contributions to the electrostatic protection in integrated circuits and the performance optimization of VLSI microsystems." In 2009, he was awarded as one of the top ten Distinguished Inventors in Taiwan and one of the top hundred Distinguished Inventors in China.