國立交通大學

電控工程研究所

碩士論文

電網同步之鎖相迴路控制器的分析與設計

指導教授：林清安 教授

中華民國一〇二年七月

# 電網同步之鎖相迴路控制器的分析與設計

## Grid Synchronization Phase Locked Loop Controller Analysis and Design

研究 生：羊宣銘

Student : Hsuan-Ming Yang

指 導 教 授：林清 安

Advisor : Prof. Ching-An Lin

Submitted to Institute of Electrical and Control Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of Master

In

Electrical and Control Engineering

June 2013

Hsinchu, Taiwan, Republic of China

中 華 民 國 一 O 二 年 七 月

# 電網同步之鎖相迴路控制器的設計與分析

學生：羊宣銘

指導教授：林清安 教授

國立交通大學電控工程研究所

## 中文摘要

本論文主要探討電網上鎖相迴路中控制器的設計以及利用模擬比較電網發生故障時各種控制器響應的結果。因為同步參考框鎖相迴路無法處理三相電壓不平衡的故障，因此多重參考框鎖相迴路或雙通用積分器鎖相迴路等鎖相迴路被提出，這些鎖相迴路的控制器大多是利用比例積分回授控制來實現，這種控制器在反應速度和高頻抑制都有出色的表現，但因為零點的關係有最大超越量較大的問題。為改善此問題利用虛擬微分回授控制、自適性調整之比例積分控制和 Q 參數化等方式來設計控制器，並且分析這些控制方式的參數對線性化系統的暫態響應與高頻抑制能力的影響。在符合所需的規格要求下，利用最小的單位步階誤差絕對值積分和誤差平方積分兩種指標作為模擬時參數的選擇，在各種不同的電網故障條件時，如相位變化、雜訊干擾以及頻率變化，藉由誤差的指標、總諧波干擾以及穩態誤差比較各個控制器在實際系統中之優點及缺點。

# Grid Synchronization Phase Locked Loop Controller Design and Analysis

Student: Hsuan-Ming Yang

Advisor: Prof. Ching-An Lin

Institute of Electrical and Control Engineering

National Chiao Tung University

The thesis investigates grid synchronization phase locked loop (PLL) controllers design and compares the simulation results when grid fault occurs. Because synchronous reference frame PLL has poor phase-tracking performance when the voltage is unbalanced, others like multiple reference frame PLL and dual second order generalized integrator PLL are presented to overcome this drawback. These advanced PLLs controller also use the proportional integral (PI) controller. In general PI controllers can be designed to have fast response and effective attenuation of high order harmonics. The existence of a zero usually results in large overshoot in step response. This work presents pseudo-derivative feedback control, adaptive PI control and Q parameterization for better dynamic response, and the parameters are designed using the linear model with the minimum integral absolute error and integral square error in unit step response. Simulation results of these controllers under grid faults conditions are used to compare their performances.

## 誌謝

在交通大學電控所修讀碩士班的時間裡，特別感謝指導教授 林清安教授教導我學業以及實驗上的知識，在日常生活上也不吝與我分享處理事情的態度與經驗，使得研究所的過程中學習到許多珍貴的知識與經驗，且在撰寫論文期間用心地校閱斧正，方能使本論文得以順利完成。

感謝在研究所修習期間，父母對我生活與心靈上的支持與鼓勵，以及兄長分享自身的經驗與知識，因為這些幫助讓我的研究生活得以順遂，正因為家人們的支持與鼓舞讓而得以完成學業。

同時，感謝實驗室的同儕與學弟們，因為彼此間知識上的交流以及一同探討問題，讓我的知識與經驗得以精進與成長。亦感謝大學的同學們，在研究所期間生活上與心靈上的問題有你們的陪伴與幫忙，因為你們的協助與扶持使得這段時間內充滿了溫暖與動力。

# 目錄

|                             |     |

|-----------------------------|-----|

| 中文摘要                        | i   |

| 英文摘要                        | ii  |

| 誌謝                          | iii |

| 目錄                          | iv  |

| 表目錄                         | vi  |

| 圖目錄                         | vii |

| 一、緒論                        | 1   |

| 二、鎖相迴路的介紹                   | 3   |

| 2.1 電網上的故障分析                | 3   |

| 2.1.1 電網上常見的故障              | 3   |

| 2.1.2 三相電壓之座標轉換             | 6   |

| 2.2 同步參考框鎖相迴路               | 8   |

| 2.3 多重參考框鎖相迴路               | 12  |

| 2.4 雙通用積分器鎖相迴路              | 17  |

| 三、控制器設計與分析                  | 23  |

| 3.1 雙通用積分器鎖相迴路利用比例積分回授控制之分析 | 23  |

| 3.1.1 比例積分回授控制之最大相位裕度設計     | 24  |

| 3.1.2 比例積分回授控制系統的暫態響應之分析    | 26  |

| 3.1.3 比例積分回授控制高頻雜訊抑制能力之分析   | 28  |

| 3.1.4 比例積分回授控制穩態誤差之分析       | 30  |

| 3.2 雙通用積分器鎖相迴路利用虛擬微分回授控制之分析 | 30  |

| 3.2.1 虛擬微分回授控制和比例積分回授控制的比較  | 31  |

| 3.2.2 虛擬微分回授控制穩定度之分析        | 35  |

| 3.2.3 虛擬微分回授控制暫態響應之分析       | 37  |

|                                 |    |

|---------------------------------|----|

| 3.2.4 虛擬微分回授控制高頻雜訊抑制能力之分析 ..... | 39 |

| 3.2.5 虛擬微分回授控制穩態誤差之分析 .....     | 41 |

| 3.3 自適性調整之比例積分回授控制 .....        | 42 |

| 3.3.1 自適性調整的設計與穩定度之分析 .....     | 43 |

| 3.3.2 自適性調整頻率之分析 .....          | 45 |

| 3.4 Q 參數化設計高階之控制器 .....         | 46 |

| 3.4.1 Q 參數化設計之假設 .....          | 47 |

| 3.4.2 Q 參數化參數設計之分析 .....        | 48 |

| 3.4.3 Q 參數化一維自由度之設計與分析 .....    | 50 |

| 3.4.4 Q 參數化二維自由度之設計與分析 .....    | 52 |

| 四、控制器之模擬與驗證 .....               | 55 |

| 4.1 控制器參數設計 .....               | 55 |

| 4.1.1 比例積分回授控制參數設計 .....        | 55 |

| 4.1.2 虛擬微分回授控制參數設計 .....        | 57 |

| 4.1.3 自適性調整之比例積分回授控制參數設計 .....  | 59 |

| 4.1.4 一維自由度之 Q 參數化控制器參數設計 ..... | 61 |

| 4.1.5 二維自由度之 Q 參數化控制器參數設計 ..... | 64 |

| 4.2 鎖相迴路系統的模擬與驗證 .....          | 66 |

| 4.2.1 相位步階變化之模擬結果 .....         | 66 |

| 4.2.2 不平衡三相電壓與高頻雜訊之模擬結果 .....   | 71 |

| 4.2.3 頻率步階變化之模擬結果 .....         | 75 |

| 4.3 模擬結果總結 .....                | 78 |

| 五、結論 .....                      | 79 |

| 參考資料 .....                      | 81 |

| 附錄 .....                        | 85 |

## 表目錄

|                            |    |

|----------------------------|----|

| 表 2.1: 不同的三相電壓不平衡錯誤及其向量示意圖 | 4  |

| 表 3.1: Q 參數分母之係數           | 48 |

| 表 3.2: Q 參數分子之係數           | 48 |

| 表 4.1: 比例積分回授控制之參數         | 57 |

| 表 4.2: 虛擬微分回授控制之參數         | 59 |

| 表 4.3: 自適性調整比例積分回授控制參數     | 61 |

| 表 4.4: 一維自由度 Q 參數化設計之參數    | 63 |

| 表 4.5: 二維自由度 Q 參數化設計之參數    | 66 |

| 表 4.6: 相位變化對各個控制器的影響       | 71 |

| 表 4.7: 不平衡故障與高頻雜訊對各個控制器的影響 | 75 |

| 表 4.8: 頻率單位步階變化對於不同控制器之比較  | 78 |

# 圖目錄

|                                 |    |

|---------------------------------|----|

| 圖 2.1: 平衡及不平衡三相電壓向量示意圖          | 4  |

| 圖 2.2: 同步參考框鎖相迴路之系統方塊圖          | 8  |

| 圖 2.3: 同步參考框鎖相迴路線性化之系統方塊圖       | 9  |

| 圖 2.4: 輸入之電壓波形與估測之正向序三相電壓波形     | 10 |

| 圖 2.5: 平衡與不平衡狀態下估測之電壓及相位        | 10 |

| 圖 2.6: 同步參考框鎖相迴路加上低通濾波器之系統方塊圖   | 10 |

| 圖 2.7: 輸入之電壓波形和估測之正向序三相電壓波形     | 11 |

| 圖 2.8: 有加低通濾波器和未加裝的估測電壓及相位之比較   | 12 |

| 圖 2.9: 多重參考框鎖相之系統方塊圖            | 12 |

| 圖 2.10: 多重參考框鎖相迴路等效之帶拒濾波器的波德圖   | 15 |

| 圖 2.11: 多重參考框鎖相迴路線性化系統方塊圖       | 15 |

| 圖 2.12: 多重參考框鎖相迴路線性化並簡化之系統方塊圖   | 16 |

| 圖 2.13: 估測相之正向序三相電壓波形           | 16 |

| 圖 2.14: 多重參考框鎖相迴路估測之電壓和相位       | 17 |

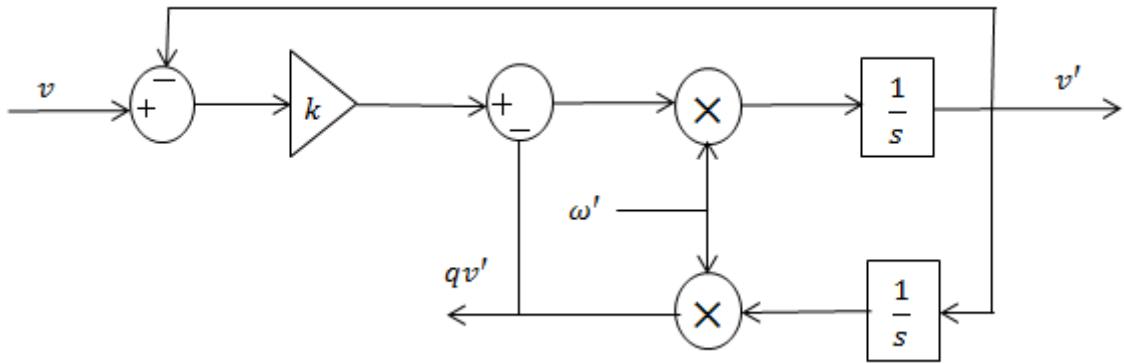

| 圖 2.15: 基本的二階通用積分器之系統方塊圖        | 18 |

| 圖 2.16: 改良過之二階通用積分器系統方塊圖        | 19 |

| 圖 2.17: 改良過之二階通用積分器 $D(s)$ 之波德圖 | 20 |

| 圖 2.18: 改良過之二階通用積分器 $Q(s)$ 之波德圖 | 20 |

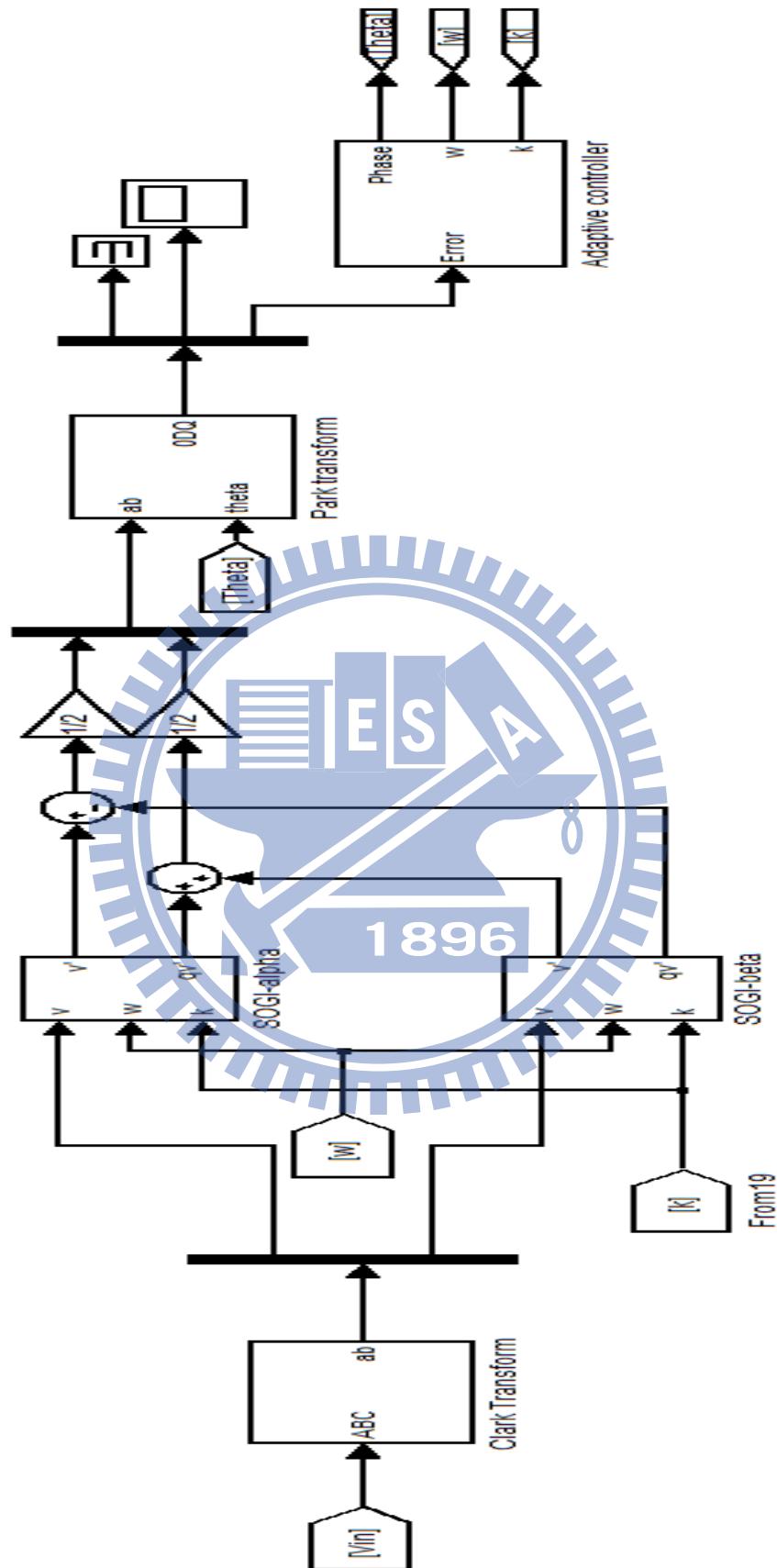

| 圖 2.19: 雙通用積分器鎖相迴路之系統方塊圖        | 20 |

| 圖 2.20: 輸入之電壓和估測之正向序三相電壓波形      | 21 |

| 圖 2.21: 雙通用積分器鎖相迴路估測之電壓和相位      | 22 |

| 圖 3.1: 雙通用積分器鎖相迴路之線性化系統方塊圖      | 24 |

| 圖 3.2: 參數 $g$ 和相位裕度之關係圖         | 26 |

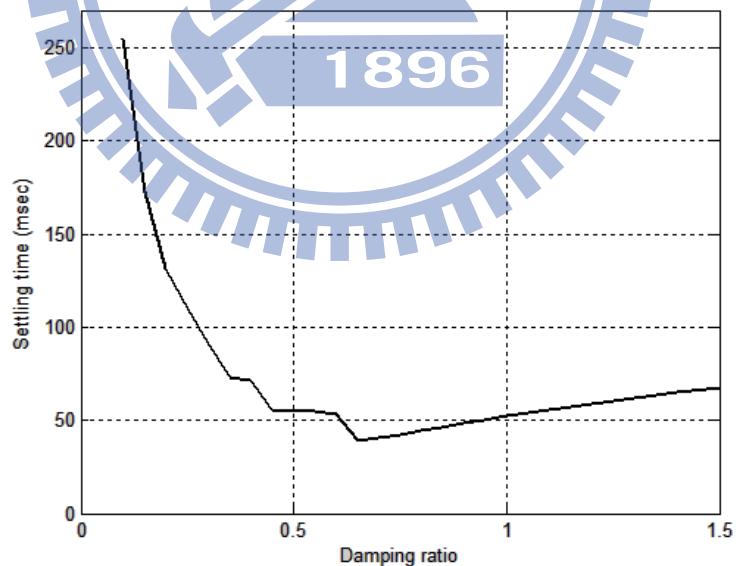

| 圖 3.3: 阻尼係數對穩定時間之影響             | 27 |

|                                         |    |

|-----------------------------------------|----|

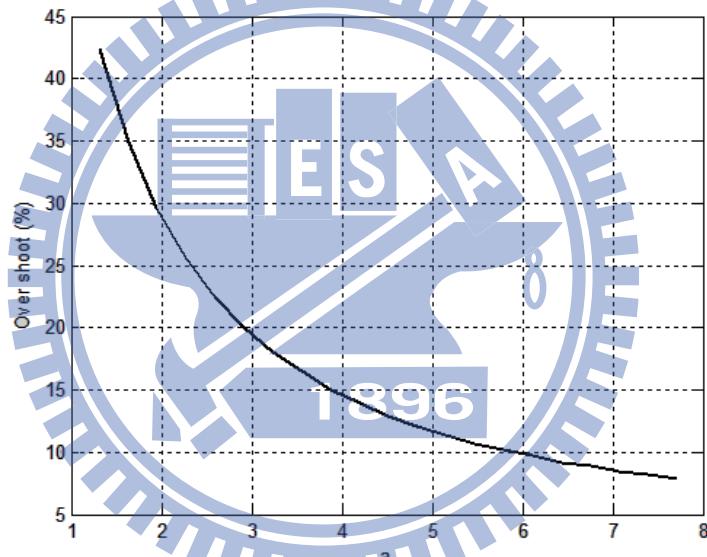

| 圖 3.4: 阻尼係數對最大超越量之影響                    | 28 |

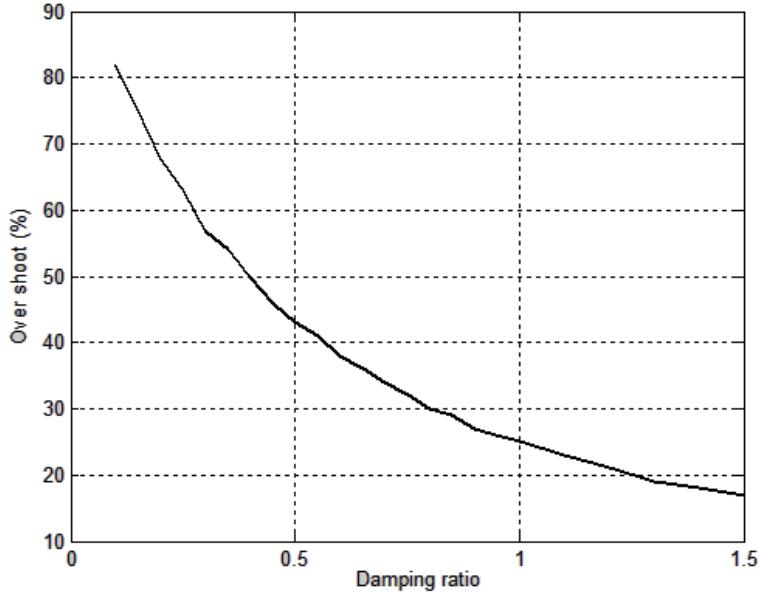

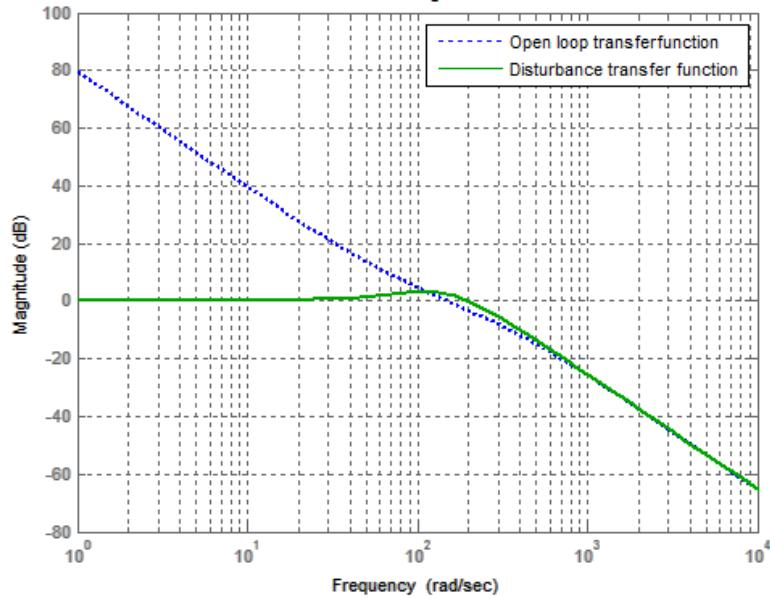

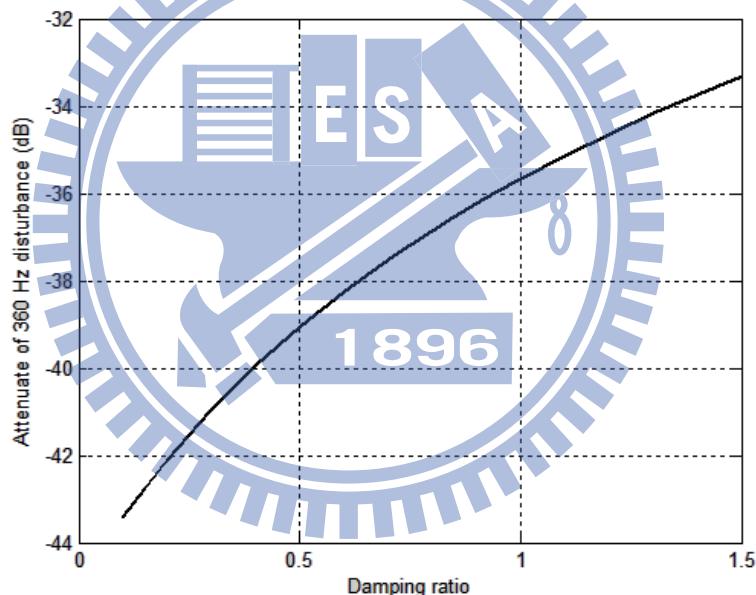

| 圖 3.5: 開路轉移函數和干擾的轉移函數之波德圖               | 29 |

| 圖 3.6: 阻尼係數對高頻抑制能力和之影響                  | 29 |

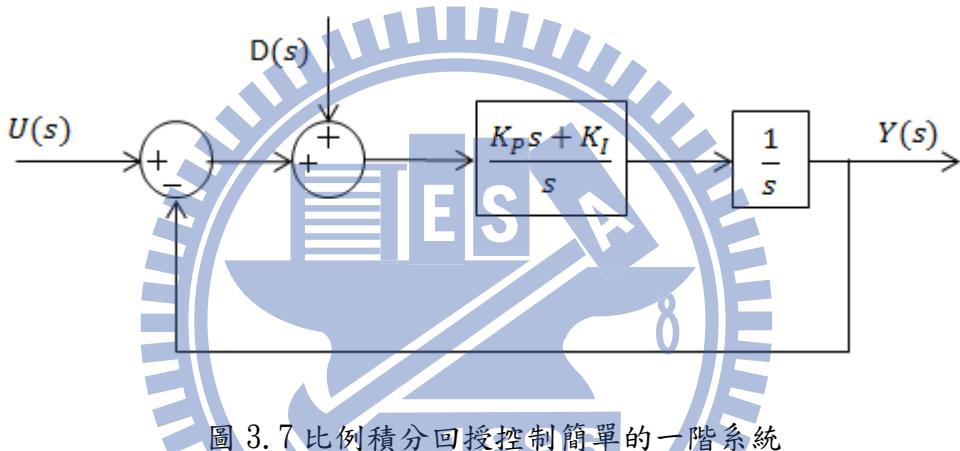

| 圖 3.7: 比例積分回授控制簡單的一階系統                  | 31 |

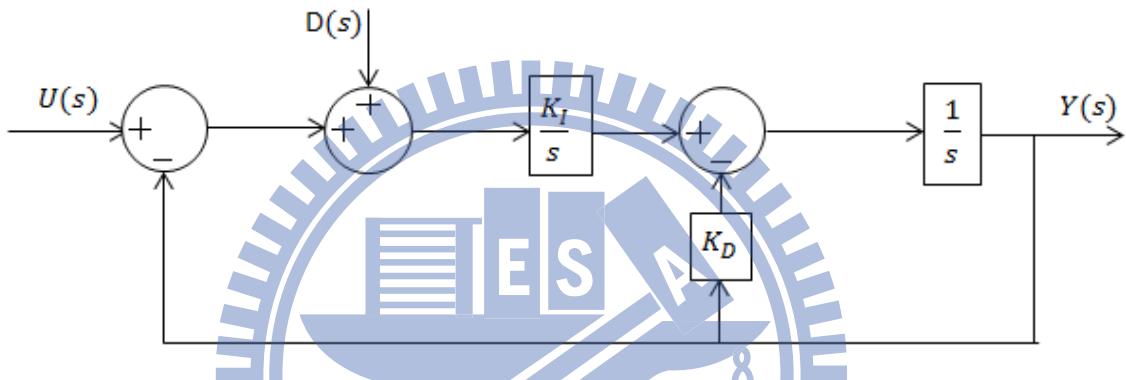

| 圖 3.8: 虛擬微分回授控制簡單的一階系統                  | 32 |

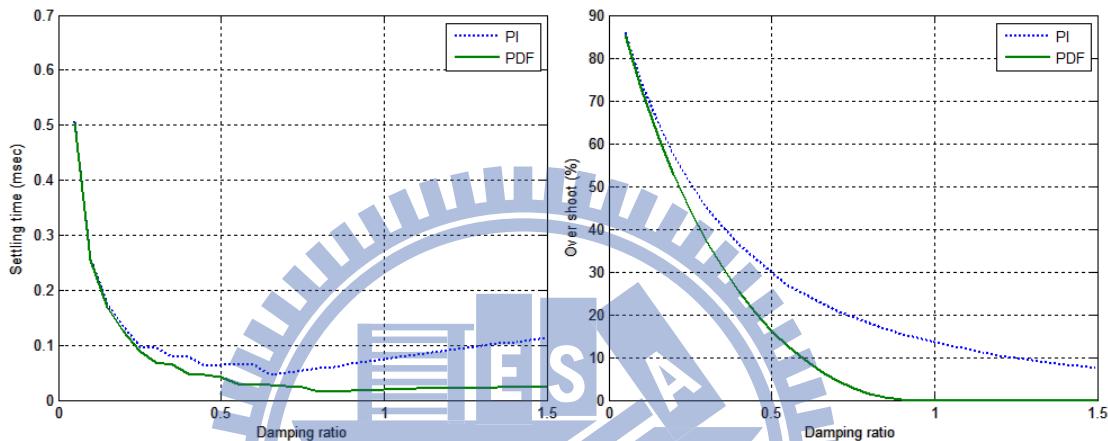

| 圖 3.9: 阻尼係數對穩定時間及最大超越量之影響               | 33 |

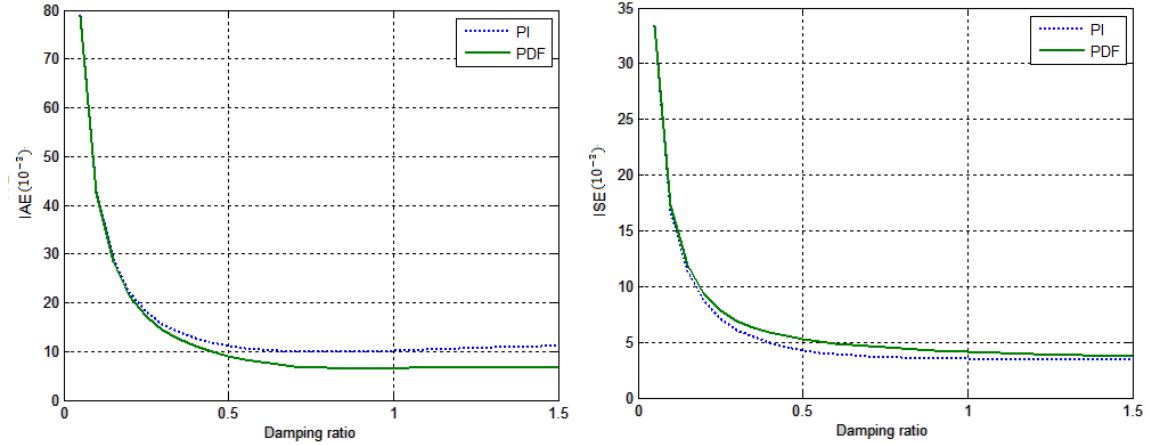

| 圖 3.10: 阻尼係數對 IAE 及 ISE 之影響             | 34 |

| 圖 3.11: 阻尼係數對高頻抑制能力之影響                  | 35 |

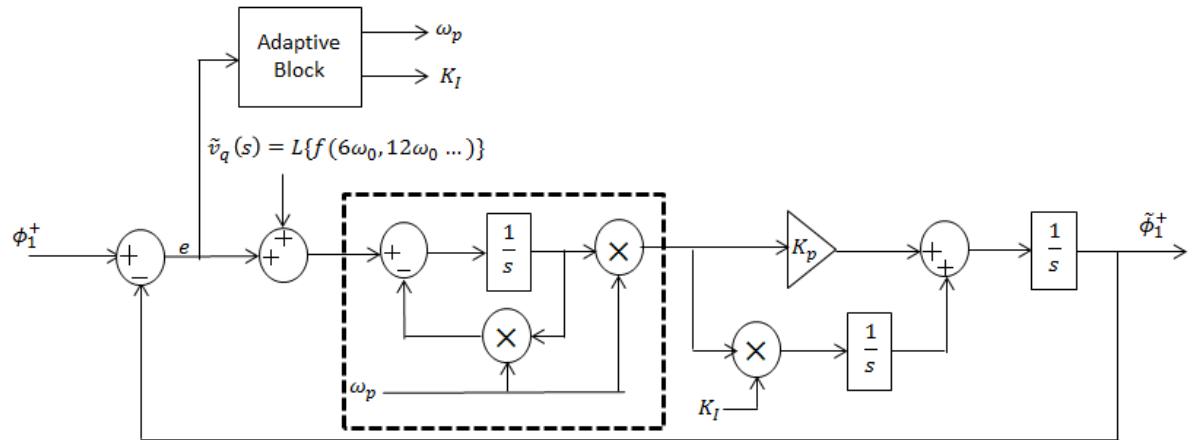

| 圖 3.12: 利用 PDF 之雙通用積分器鎖相迴路系統方塊圖         | 36 |

| 圖 3.13: 線性化之系統方塊圖                       | 36 |

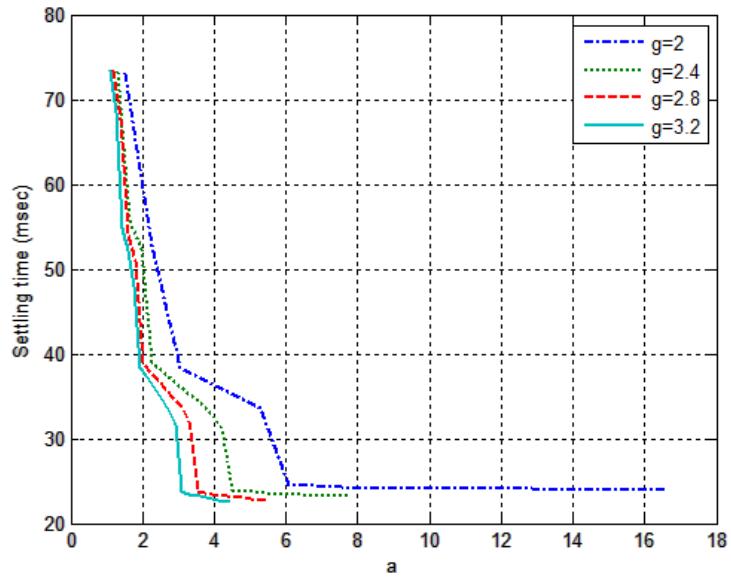

| 圖 3.14: 固定 $g$ 和增益穿越頻率下之 $a$ 對穩定時間之影響   | 38 |

| 圖 3.15: 固定 $g$ 和增益穿越頻率 $a$ 對最大超越量之影響    | 38 |

| 圖 3.16: 固定增益穿越頻率不同的 $g$ 和 $a$ 對穩定時間的影響  | 39 |

| 圖 3.17: 固定增益穿越頻率不同的 $g$ 和 $a$ 對最大超越量的影響 | 39 |

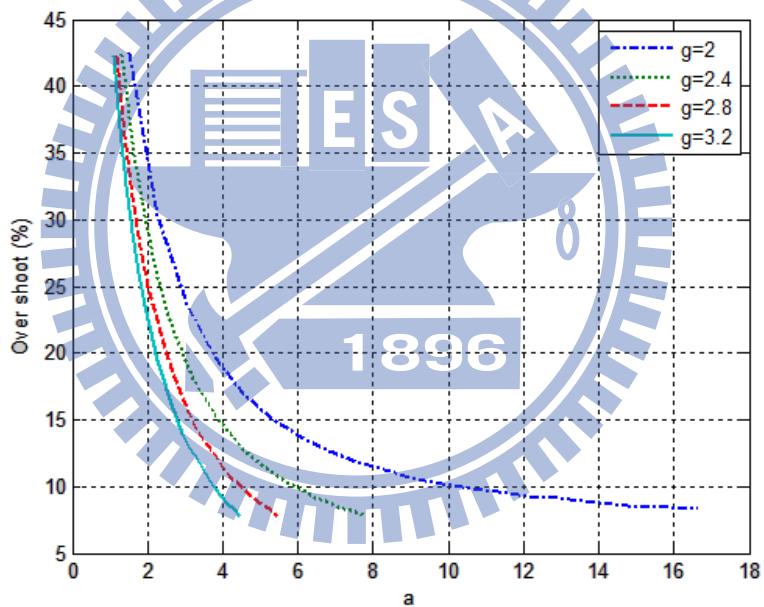

| 圖 3.18: 參數 $g$ 和 $a$ 對系統高頻抑制能力之影響       | 40 |

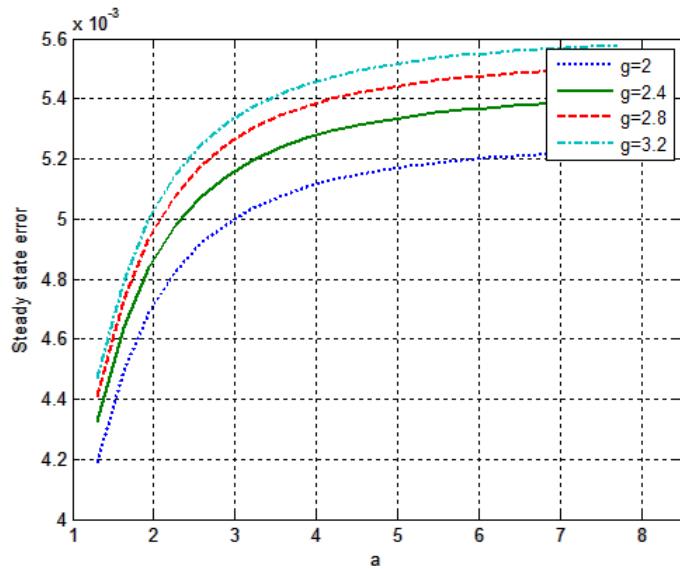

| 圖 3.19: 參數 $g$ 和 $a$ 對穩態誤差之影響           | 42 |

| 圖 3.20: 自適性比例積分控制線性化系統方塊圖               | 44 |

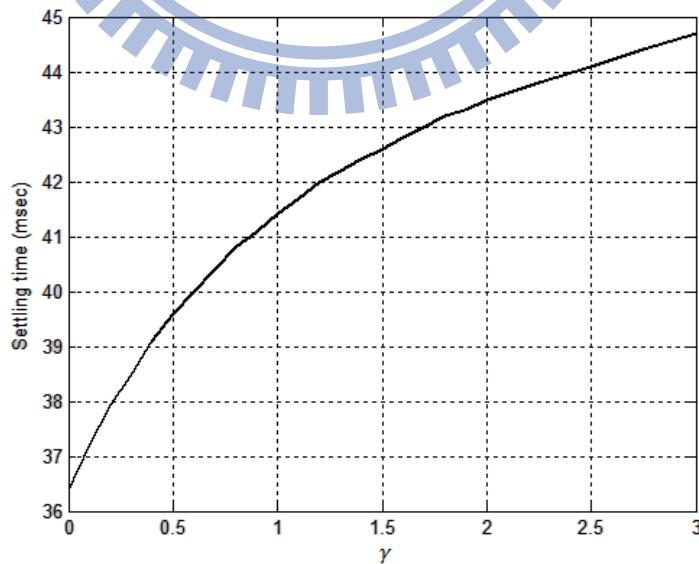

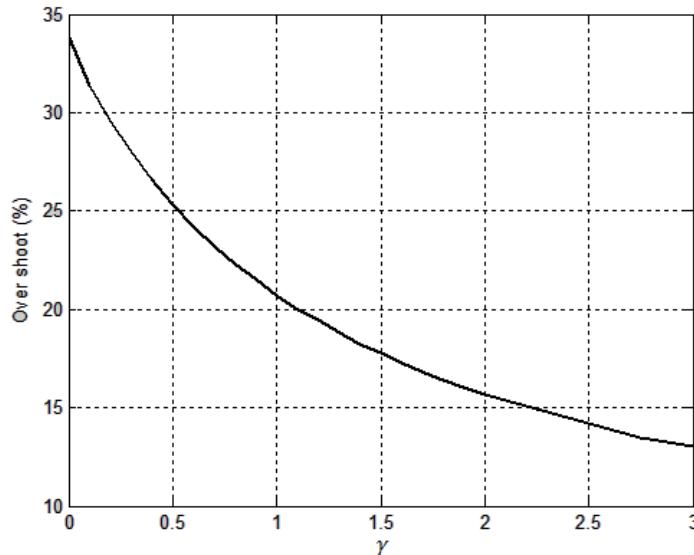

| 圖 3.21: 自適性係數對穩定時間的影響                   | 44 |

| 圖 3.22: 自適性係數對穩定時間的影響                   | 45 |

| 圖 3.23: 調整頻率對 IAE 和 ISE 的影響             | 46 |

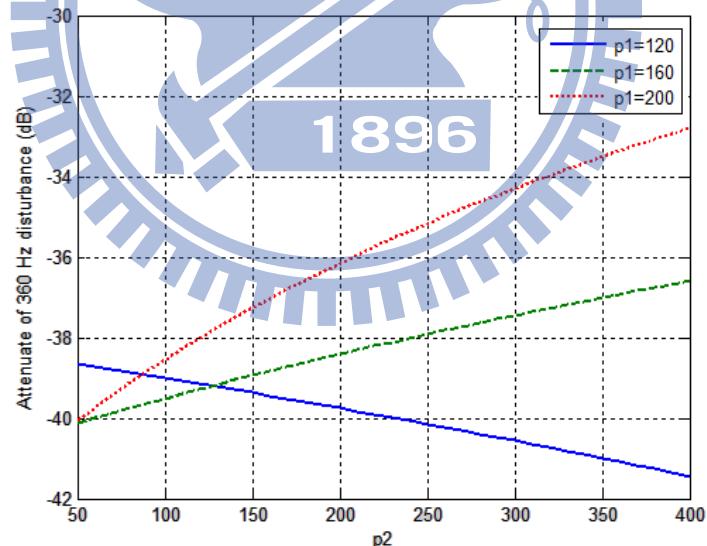

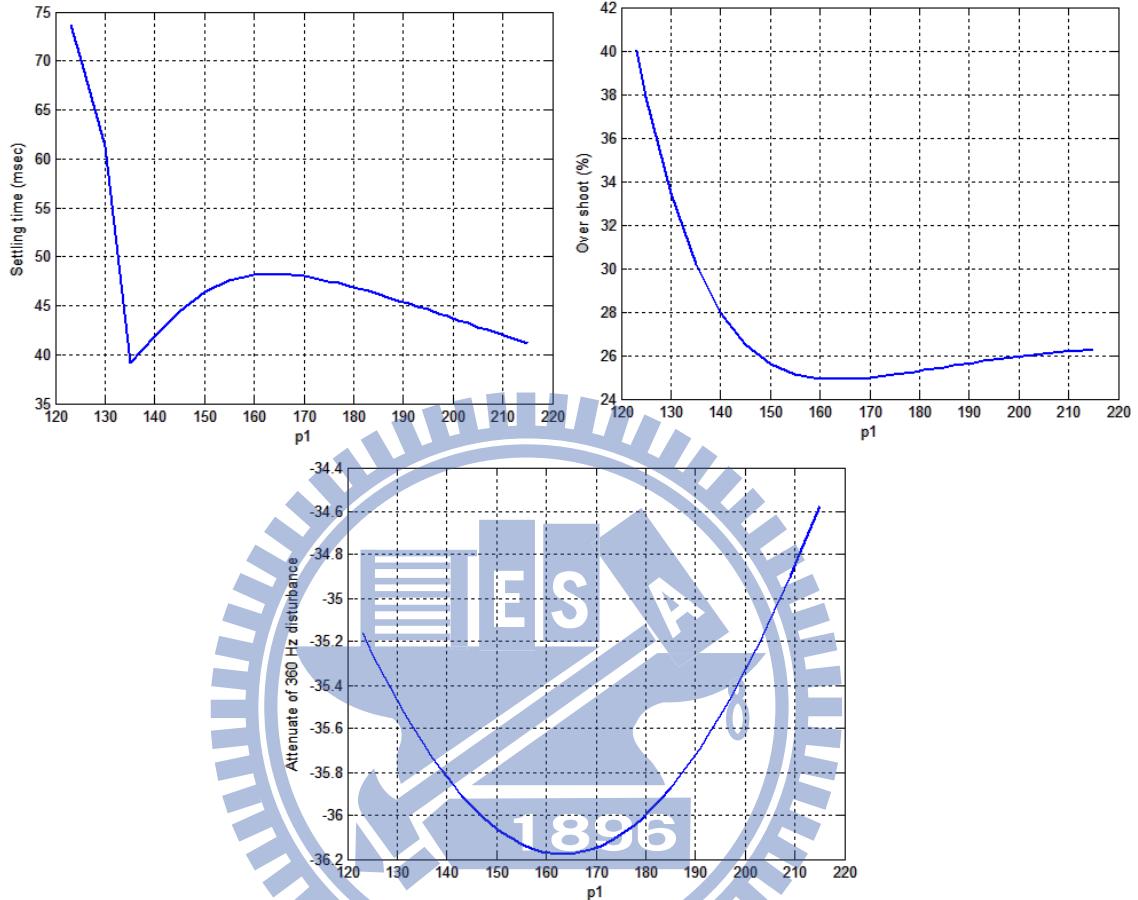

| 圖 3.24: $p_1$ 對於系統暫態之影響                 | 51 |

| 圖 3.25: $p_1$ 對高頻抑制能力之影響                | 51 |

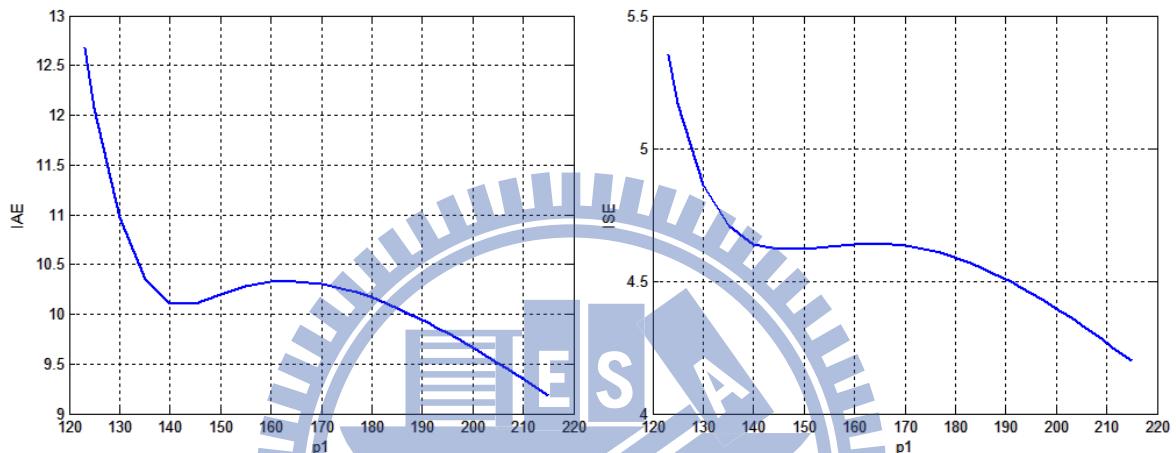

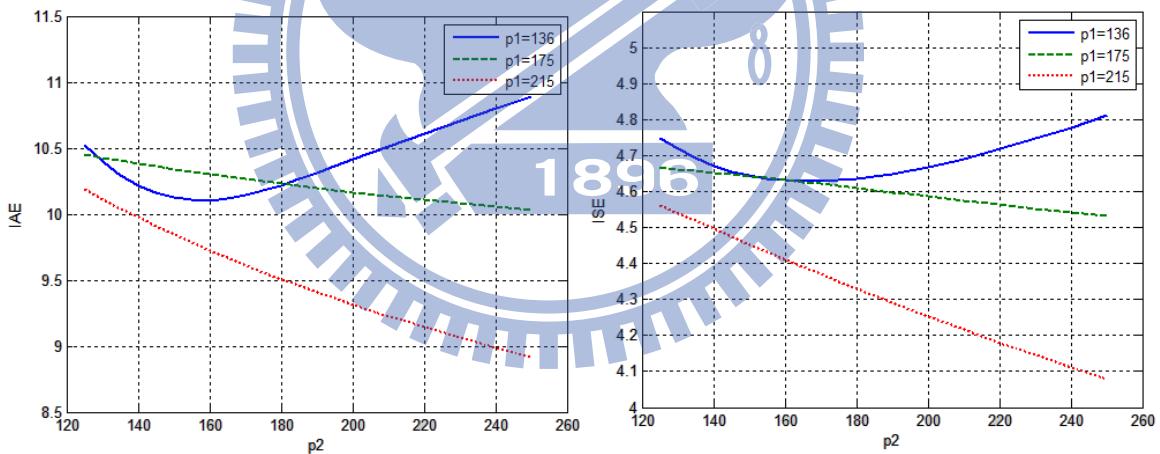

| 圖 3.26: $p_1$ 與 $p_2$ 對系統暫態響應之影響        | 53 |

| 圖 3.27: $p_1$ 與 $p_2$ 對高頻雜訊抑制之影響        | 53 |

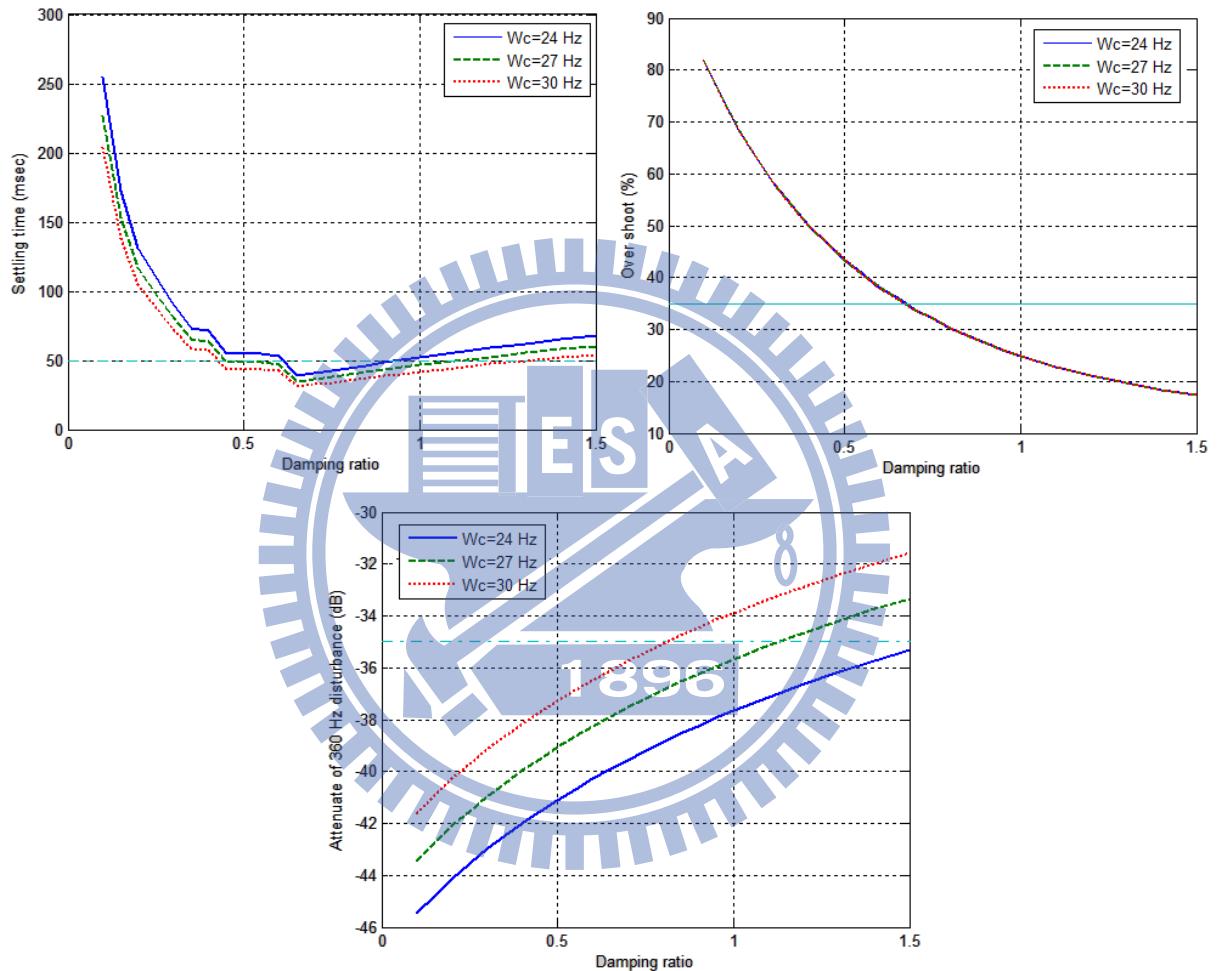

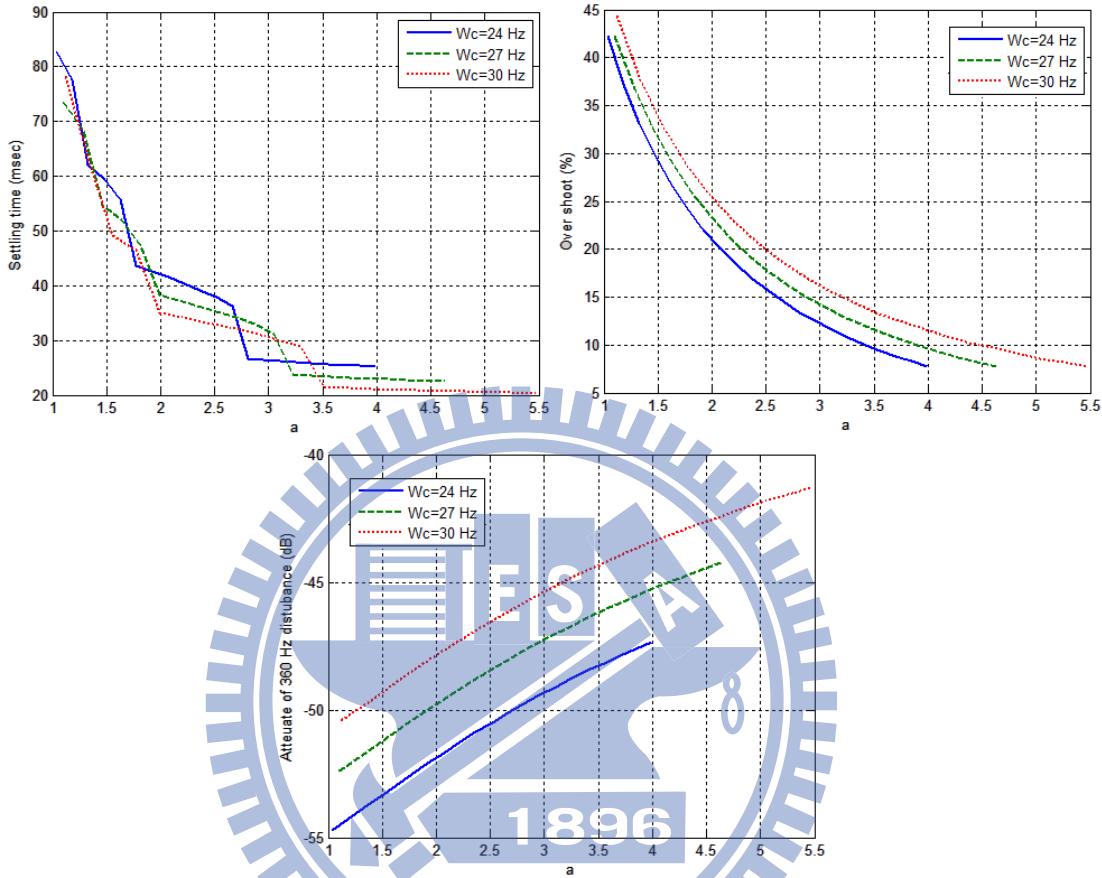

| 圖 4.1: 阻尼係數及增益穿越頻率對系統暫態和高頻抑制之影響         | 56 |

|                                                    |    |

|----------------------------------------------------|----|

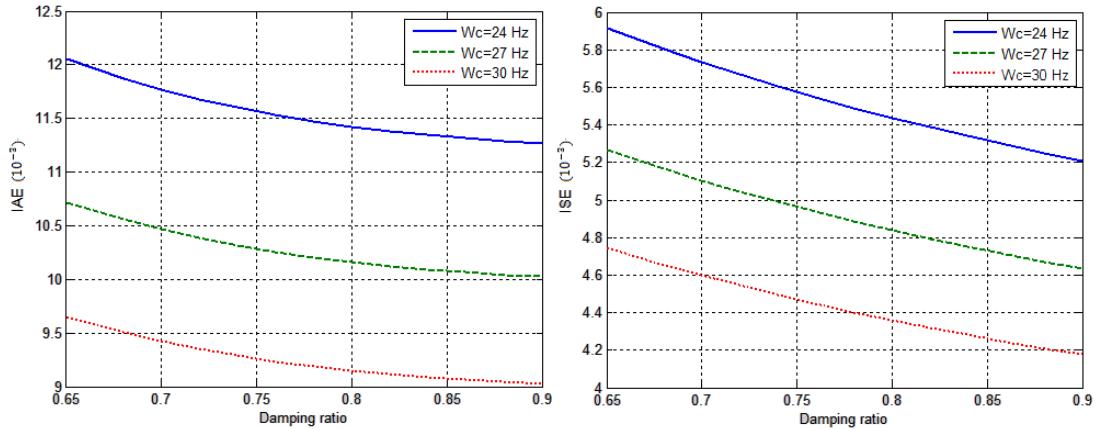

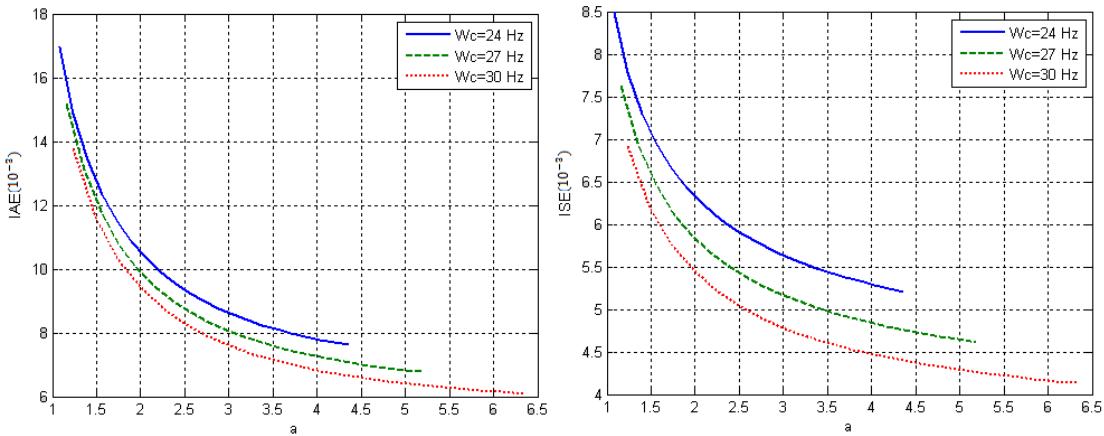

| 圖 4.2: 阻尼係數及增益穿越頻率對系統之 IAE 和 ISE 之影響               | 57 |

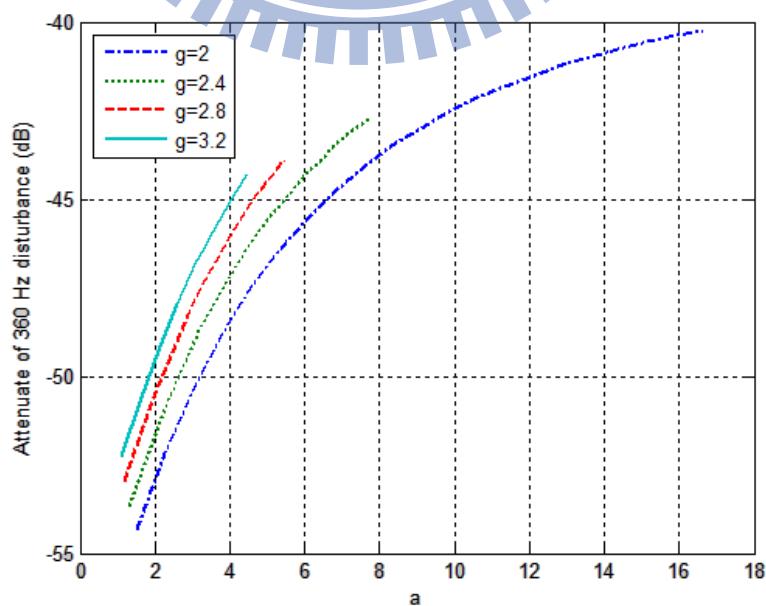

| 圖 4.3: 增益穿越頻率和 $a$ 值對系統暫態和高頻抑制的影響                  | 58 |

| 圖 4.4: 增益穿越頻率和 $a$ 值對系統之 IAE 和 ISE 之影響             | 59 |

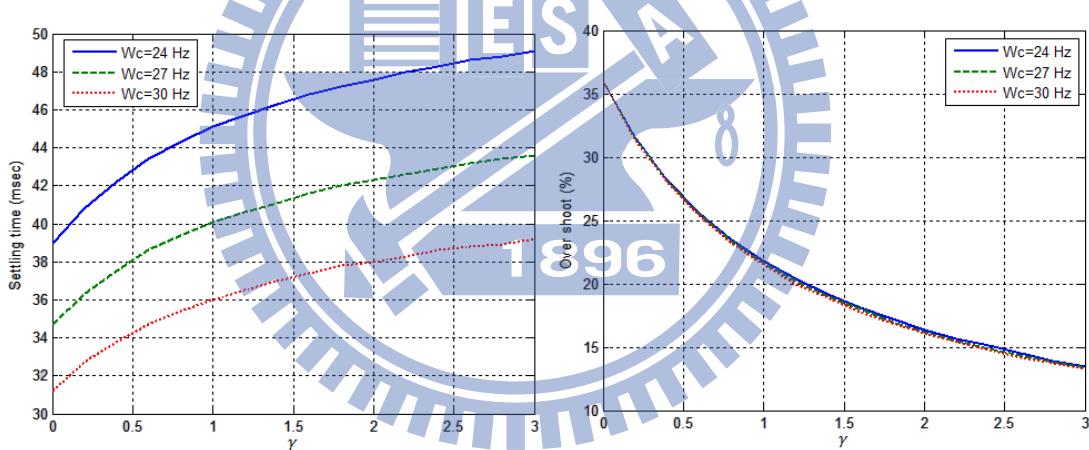

| 圖 4.5: 自適性係數和增益穿越頻率對系統暫態之影響                        | 60 |

| 圖 4.6: 自適性係數和增益穿越頻率對系統暫態之影響                        | 61 |

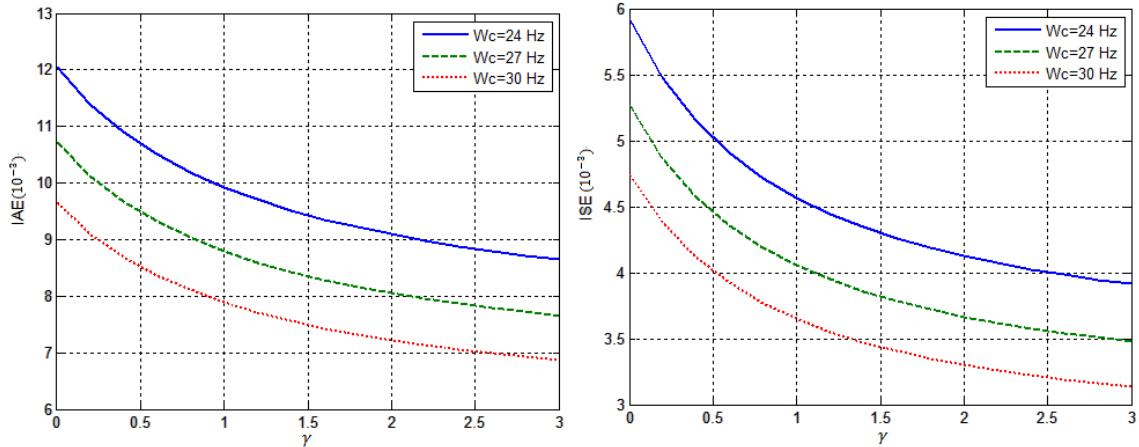

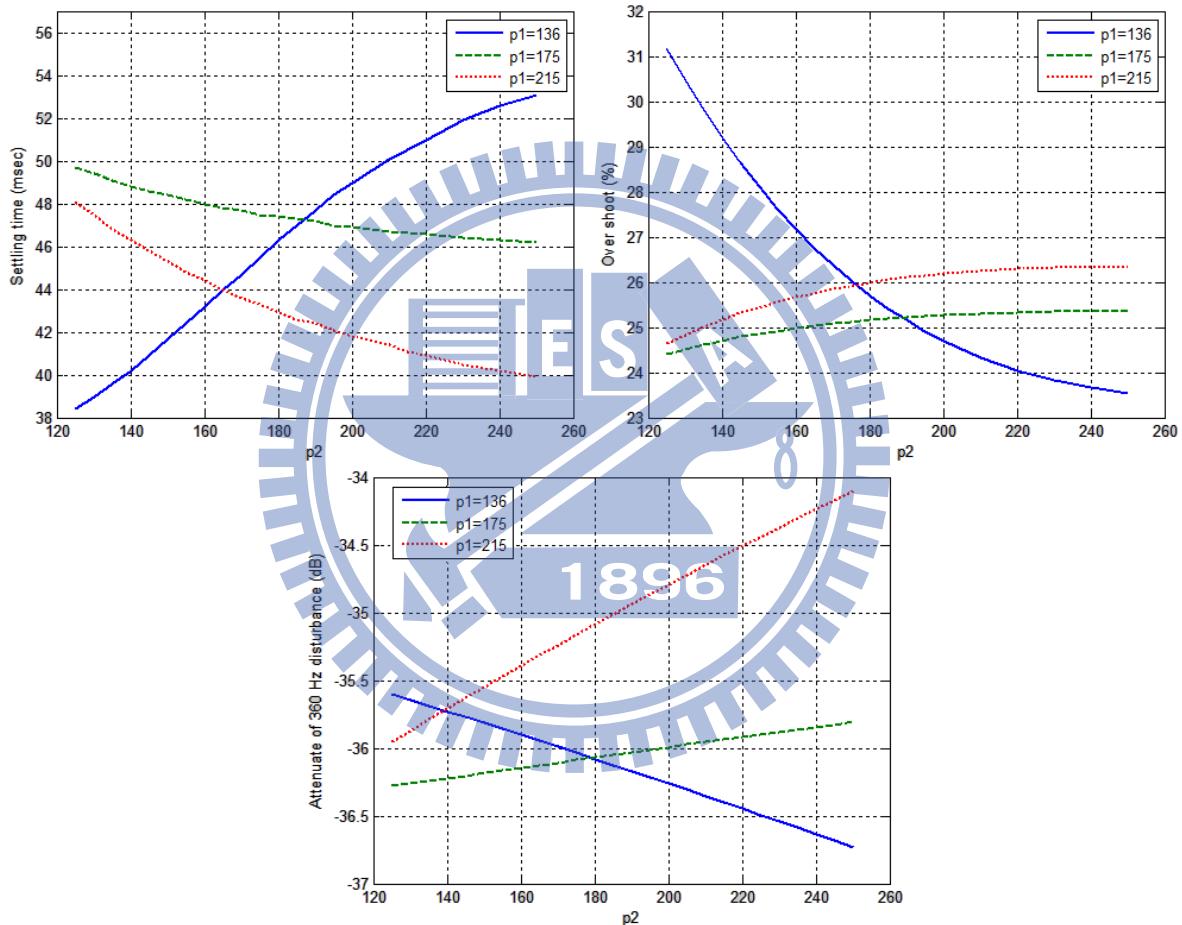

| 圖 4.7: Q 參數化設計 $p_1$ 對單位步階的暫態及高頻抑制的影響              | 62 |

| 圖 4.8: Q 參數化設計 $p_1$ 對單位步階的 IAE 及 ISE 之影響          | 63 |

| 圖 4.9: Q 參數化 $p_1$ 與 $p_2$ 對系統暫態和高頻抑制之影響           | 64 |

| 圖 4.10: Q 參數化 $p_1$ 與 $p_2$ 對於系統單位步階 IAE 和 ISE 的影響 | 65 |

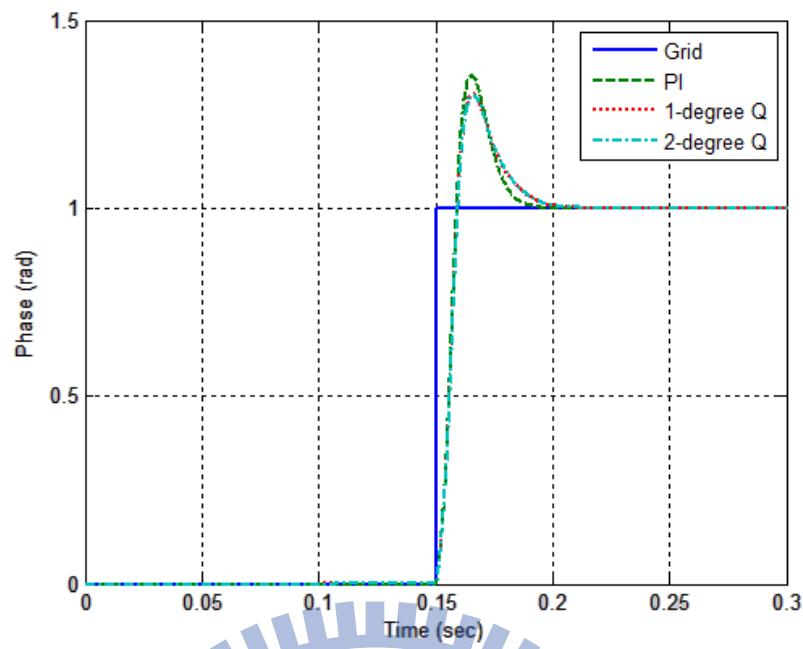

| 圖 4.11: 0.15 秒發生相位落後之三相電壓                          | 67 |

| 圖 4.12: 一強度位變化下系統估測相位模擬結果                          | 67 |

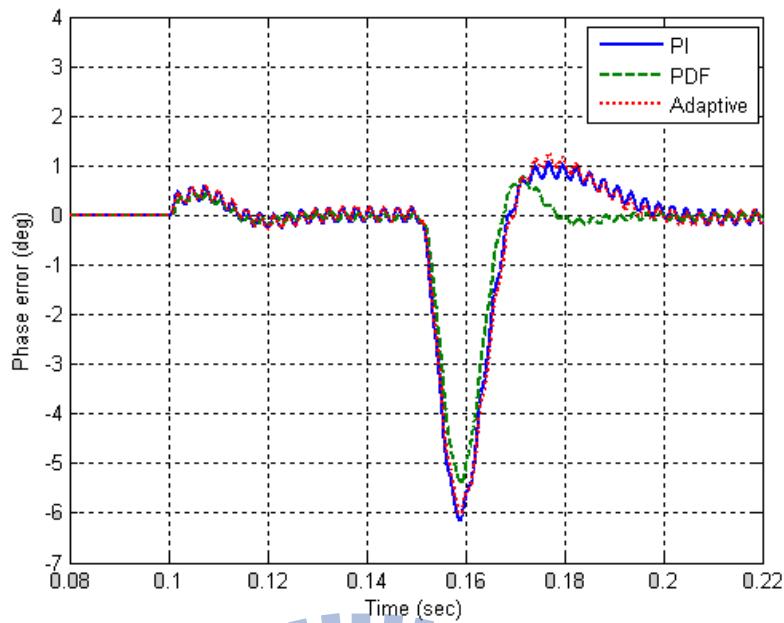

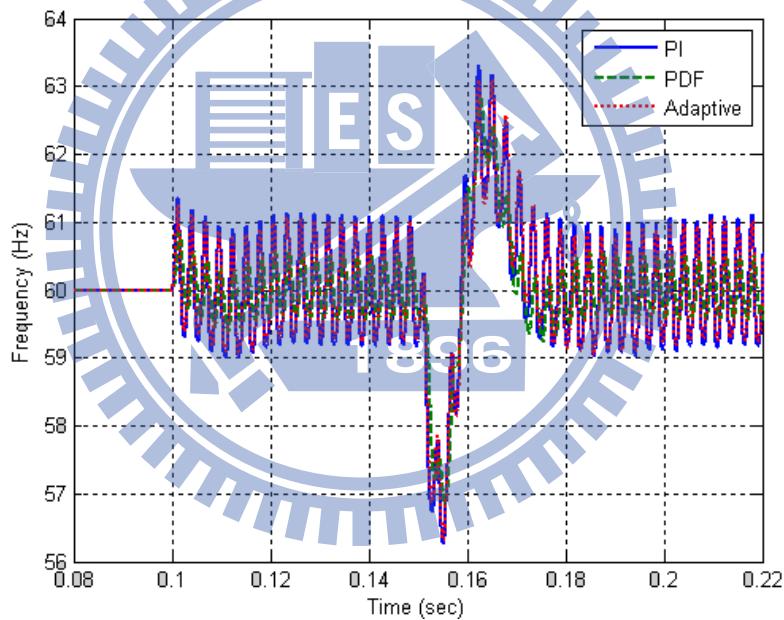

| 圖 4.13: 一強度位變化下系統相位誤差的結果                           | 68 |

| 圖 4.14: 一強度相位變化下系統估測頻率的結果                          | 68 |

| 圖 4.15: 一強度相位變化下系統估測頻率的結果                          | 69 |

| 圖 4.16: 一強度相位變化下系統相位誤差的結果                          | 69 |

| 圖 4.17: 一強度相位變化下系統估測頻率的結果                          | 70 |

| 圖 4.18: 不平衡且參有雜訊的三相電壓                              | 72 |

| 圖 4.19: 不平衡及高頻雜訊下不同控制器的相位誤差結果                      | 73 |

| 圖 4.20: 不平衡及高頻雜訊下不同控制器的估測頻率之結果                     | 73 |

| 圖 4.21: 不平衡及高頻雜訊下 Q 參數相位之誤差結果                      | 74 |

| 圖 4.22: 不平衡及高頻雜訊下 Q 參數估測頻率之結果                      | 74 |

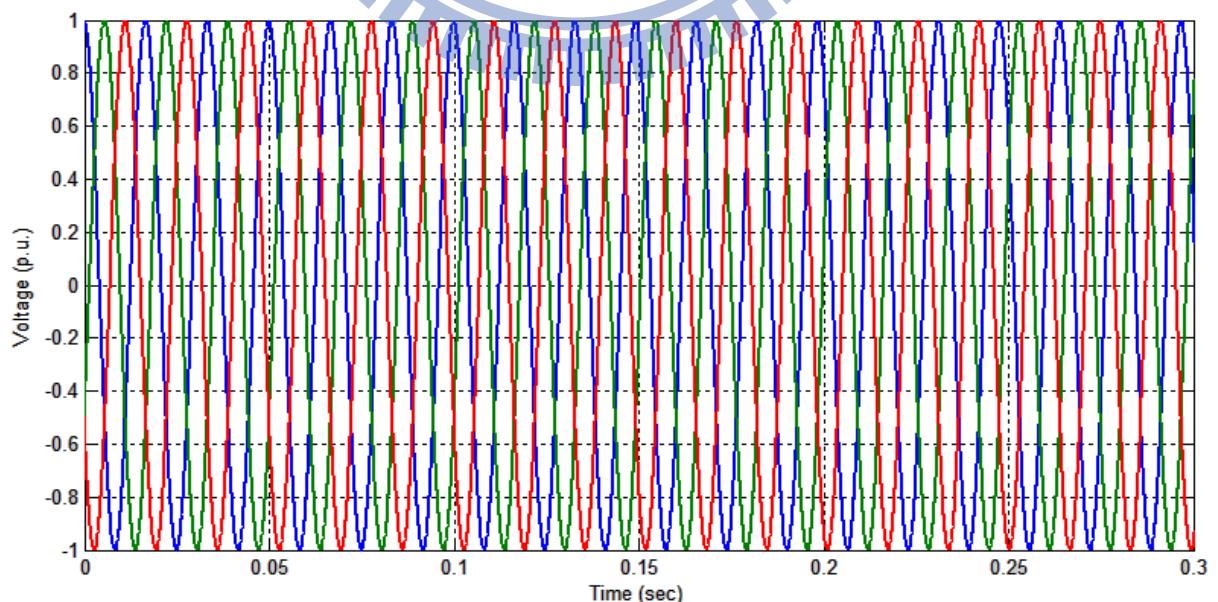

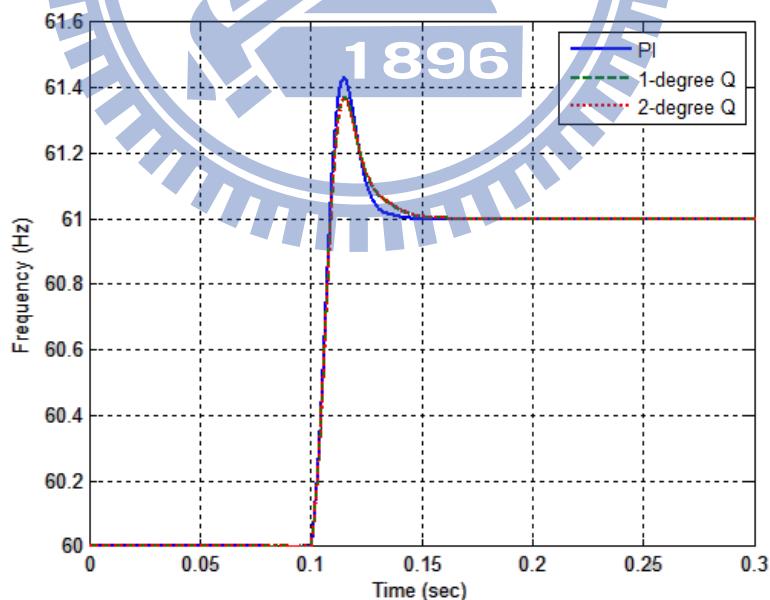

| 圖 4.23: 三相平衡電壓於 0.1 秒時頻率上升 1 Hz 之波形                | 75 |

| 圖 4.24: 頻率步階變化對不同控制器相位誤差的影響                        | 76 |

| 圖 4.25: 頻率步階變化對不同控制系統估測頻率的影響                       | 76 |

| 圖 4.26: 頻率步階變化對 Q 參數化系統相位誤差的影響                     | 77 |

|                                |    |

|--------------------------------|----|

| 圖 4.27: 頻率步階變化對 Q 參數化系統估測頻率的影響 | 77 |

| 圖 A.1: 通用積分器之方塊圖               | 85 |

| 圖 A.2: 雙通用積分器鎖相迴路之結構圖          | 86 |

| 圖 A.3: 比例積分控制器之方塊圖             | 87 |

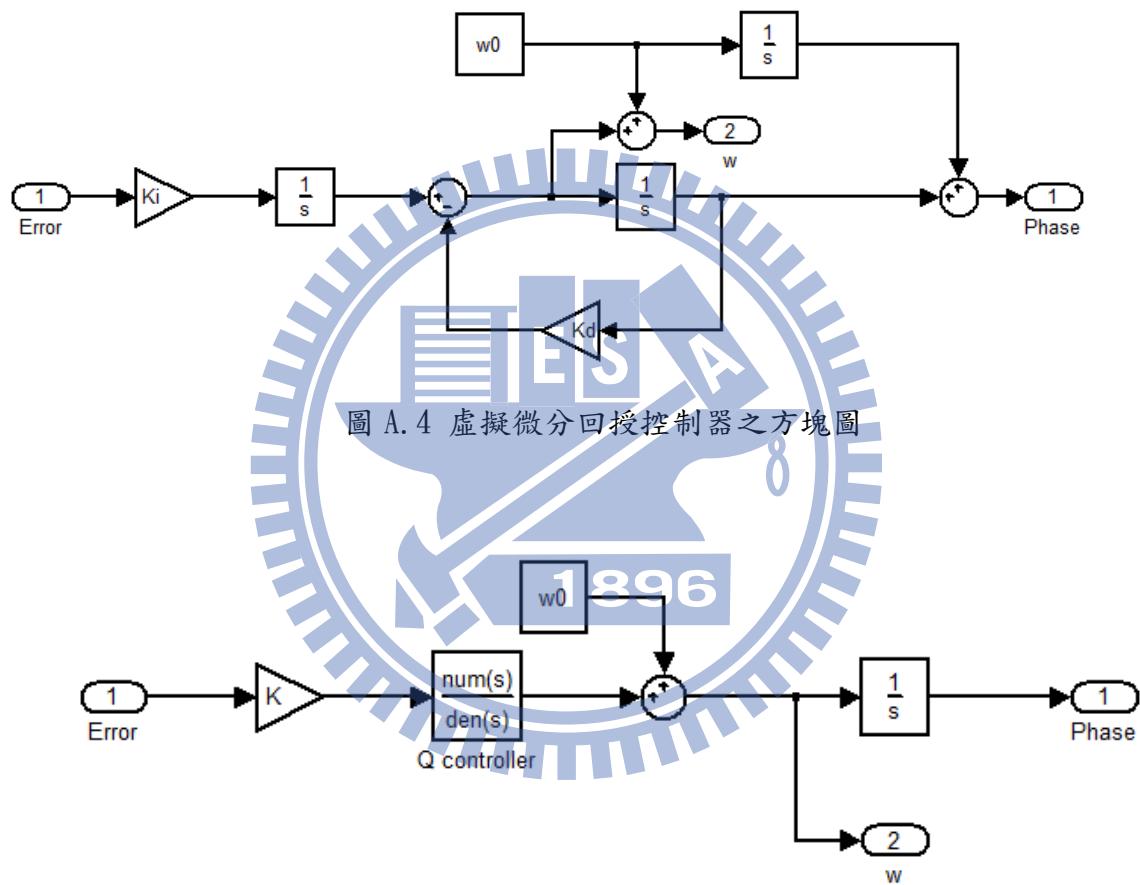

| 圖 A.4: 虛擬微分回授控制器之方塊圖           | 87 |

| 圖 A.5: Q 參數設計控制之方塊圖            | 87 |

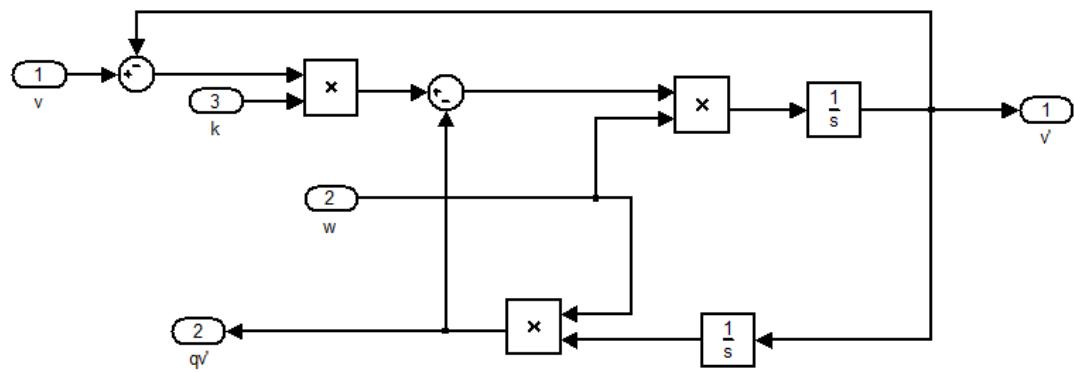

| 圖 A.6: 自適性調整之通用積分器方塊圖          | 88 |

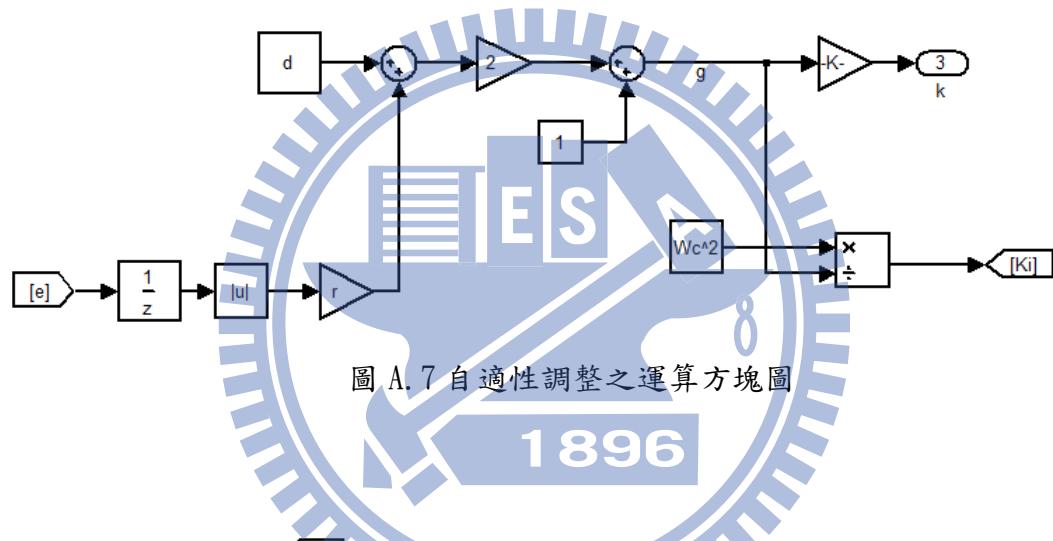

| 圖 A.7: 自適性調整之運算方塊圖             | 88 |

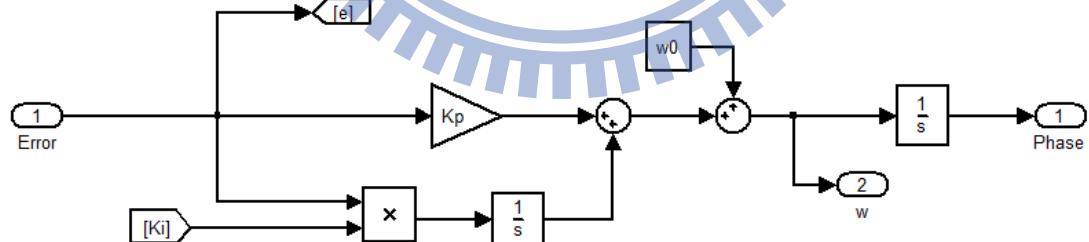

| 圖 A.8: 自適性調整之控制器方塊圖            | 88 |

| 圖 A.9: 自適性調整之雙通用積分器鎖相迴路系統結構圖   | 89 |

## 一、緒論

近年來因能源的缺乏以及石化燃料等發電原料價格的上揚，綠色能源等相關設備因而蓬勃發展，但這類新興能源容易受到環境的因素而影響系統的效能，電網比起以往需要更精確和穩定的控制技術和方法，歸功於現今數位晶片運算的進步及先進的積體電路製程使得現今足以將許多新穎的控制方法和技術得以實現。這類新興的綠色能源和電網相互連接的網路中有利用絕緣柵雙極電晶體(insulated gate bipolar transistor, IGBT)等電子元件所製成的換相器(converter)，讓這類發電設備在惡劣的條件下運作時不會因而拖垮或損害整個電網系統。換相器在切換開關的控制策略中需要電網上的電壓、電流、轉子轉速以及相位等資料做為操作行為的判斷，其中又因為電網上電壓以及電流皆為交流的訊號，分析上會利用克拉克轉換(Clark transform)及帕克轉換(Park transform)等座標轉換矩陣將交流訊號得以簡化利於控制，因此電網端的相位和頻率在電網的控制中又顯得格外重要。

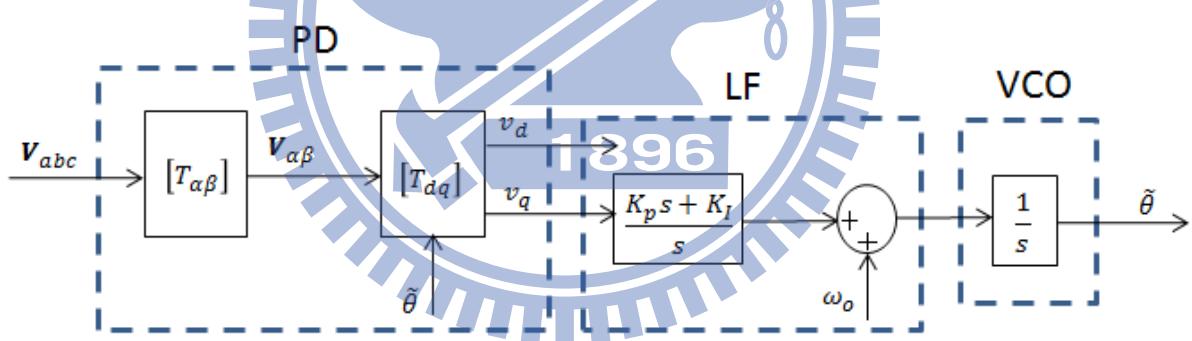

鎖相迴路的技術最早是大量地使用在積體電路設計之中，由於這類裝置可以有效地追蹤週期性訊號之相位和頻率的能力，如今這類的裝置也廣泛的使用在許多訊號控制的系統中。鎖相迴路結構主要可以分為三個部分，分別為相位偵測器(phase detector, PD)、迴路濾波器(loop filter, LF)以及電壓控制震盪器(voltage control oscillator, VCO)。鎖相迴路的作用方式是由相位偵測器得到相位誤差的訊號，經過迴路濾波器去除高頻雜訊的干擾，再利用電壓控制震盪器產生系統估測之相位。鎖相迴路主要的功用在於正確估測輸入訊號之相位，一個良好的鎖相迴路系統處於穩態下時應當讓估測之相位和輸入訊號之相位間的誤差必須為零或定值。在現今先進的電網控制中因為控制上的需要，追蹤電網上交流電的頻率和相角是個非常重要的課題，因此需要鎖相迴路的裝置來穩定地估測電網上的相位和頻率。

在電網上的鎖相迴路之中最簡單的架構是同步參考框鎖相迴路(synchronous conference frame phase lock loop, SRFPLL)，這種鎖相迴路的設計十分簡單是利用帕克轉換後的相位誤差訊號經過比例積分控制器(proportional integral controller)便可得到估

測之頻率，再利用一個積分器則可得到估測的相位。同步參考框鎖相迴路在三相平衡時是個很簡單且非常有效的鎖相迴路，可以準確及快速地得到電網的頻率和相位，但實際電網端上的電壓訊號並不是一個理想的弦波訊號，由於在電力網路中故障的發生是無可避免的，其中又以三相電壓不平衡是所有故障中發生的機率最高，造成故障的原因是高壓電線發生短路接地或著是電線間短路相接。因電壓發生三相不平衡故障時同步參考框鎖相迴路估測之相位將受到干擾而無法在控制中使用，近年來有許多不同形式的鎖相迴路相繼被提出都是為了解決當電網上發生故障的狀況下有效地估測系統的相位。

為了在電壓發生不平衡故障的狀況下，讓系統估測的相位和頻率足夠準確，許多新型的鎖相迴路架構相繼被提出，其中有許多方式是改善同步參考框鎖相迴路的缺點，利用特殊的濾波方式讓系統可以得到正確的正向序的基頻訊號，使得同步參考框鎖相迴路在電壓不平衡的條件下也可以準確的預估相位和頻率，如[1]-[4]。另一類的方式主要是利用瞬時對稱分量理論(instantaneous symmetrical component theory)做為基礎，利用正交訊號產生器(quadrature signal generator)所產生的正交訊號和原訊號做運算因而得到正向序的訊號，如[5]-[10]等方法，亦或著是利用延遲訊號消去法(delayed signal cancellation method)後再運用瞬時對稱分量理論的方式如[11][12]。另外還有一類是利用數位濾波器的方式得到正向序的訊號，例如利用帶拒濾波器濾除不需要的諧波訊號，如[13]和[14]，或是利用複數係數濾波器(complex-coefficient filter)的方式[15]，這種濾波器的特性是可以對於頻率和向序有很好的選擇性。

有不少文獻在比較以上先進的鎖相迴路間的效能差異[16]-[19]，但鎖相迴路不是僅利用相位偵測元件就達到估測相位的用途，控制器也是扮演很重要的角色。雖然常用的比例積分控制有許多優點，如結構簡單、響應快速、穩態誤差的效果也很好且參數設計也有許多的經驗和技巧，但是此種控制方式依舊存在著缺點，例如因為零點的關係使得暫態響應無法消除最大超越量的問題。本論文主要探討鎖相迴路的控制器是否有其餘控制方法可以運用，當系統處於電網的三相電壓發生各種故障時，在雙通用積分器鎖相迴路的結構下比較比例積分回授控制和其餘所提出之控制器效果的差異。

## 二、鎖相迴路的介紹

近來電網控制之研究的發展十分蓬勃，其中鎖相迴路的設計必須有能力排除各種因電網端上的故障所造成之影響，因此已經有許多文獻提出了不同的方法以及比較各個鎖相迴路的差異。本章僅介紹其中的三種鎖相迴路，除了最單純的同步參考框鎖相迴路外，另外兩種鎖相迴路分別為多重參考框鎖相迴路以及雙通用積分器鎖相迴路，除了介紹其作用原理外也分析這些鎖相迴路線性化後的特色和效果的比較。

### 2.1 電網上的故障分析

電力網路是個龐大而且複雜的系統，電網端上有許多大型發電機或馬達等裝置相聯，一旦某處發生了故障將影響系統的平衡，嚴重時甚至會讓整個系統崩潰。當某處發生故障時電網必須有能力偵測並且做出判斷，因此電網上利用換相器或繼電器等元件做為控制、監控以及保護電網的裝置。因為電網上的電壓訊號是利用交流電作為電力傳輸的方式，從控制上的觀點這種非線性而且隨時間變動的弦波訊號難以分析與運用，常見的方法是使用座標轉換的方式將訊號簡化，利於各種控制裝置有能力從故障中分析出正確的資訊來做出判斷。

#### 2.1.1 電網上常見的故障

電網上三相電壓在理想的情況下可視為三個各相差 120 度，有相同頻率及震幅的弦波訊號。但實際電網不可能永遠處於理想的狀態，因為整個電網有許多大型機具如發電機等與之相聯，電力的供應除了必須滿足整個電網所需之實功功率外，也因為存在許多電容和電感使得虛功的要求必須被滿足，當電網上虛功的供應不足時，會造成電網無法順利支持實功的傳輸，整個電網將會發生電壓崩潰的嚴重故障，因此電網必須具備虛功控制的能力。

除了因為虛功不足而造成的電壓崩潰外，另外一種常見的故障是三相電壓的不平衡故障，這種故障主要因為電網的輸電線發生了單相接地或雙相短路，這種故障會造成單

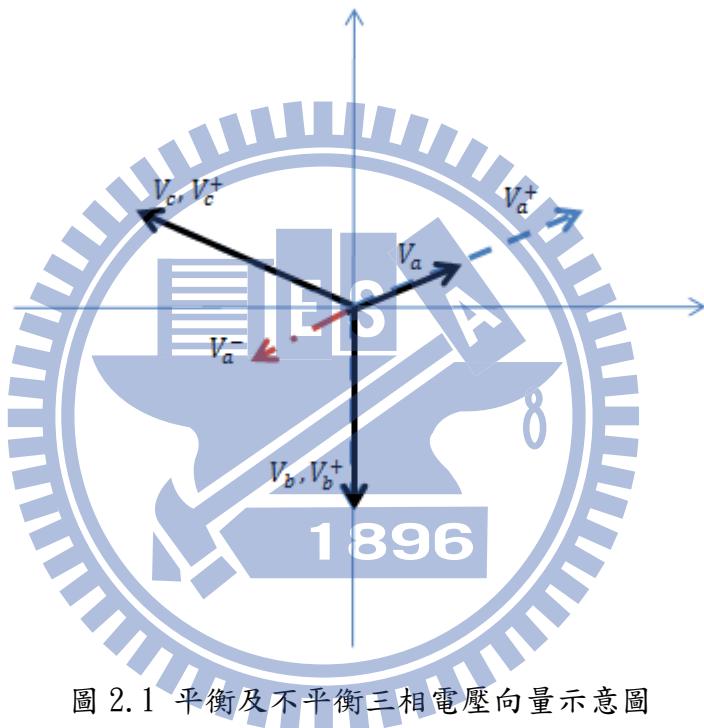

相或多相的電壓發生驟降的現象。當發生電壓驟降時三相電壓將不再是三個彼此平衡的相量，分析上常將因故障而造成不平衡的三相電壓視為正向序及負向序兩種不同的向量之合成，如圖 2.1 表示，其中正向序和負向序是兩組頻率大小相同可是震幅、相位和旋轉方向皆不相同的向量組，向量合成的結果會造成三相電壓的振幅以及相位不再相同，造成電網的控制上會發生問題。表 2.1 中表示著一些常見故障的範例以及三相電壓向量的分布情況，其中  $E$  為初始平衡電壓振幅， $V$  為故障發生後的電壓振幅。

圖 2.1 平衡及不平衡三相電壓向量示意圖

表 2.1 不同的三相電壓不平衡錯誤及其向量示意圖

| 故障類別   | 向量                                                                                                        | 向量圖 | 故障原因 |

|--------|-----------------------------------------------------------------------------------------------------------|-----|------|

| Type A | $V_a = V$<br>$V_b = -\frac{1}{2}V - j\frac{\sqrt{3}}{2}V$<br>$V_c = -\frac{1}{2}V + j\frac{\sqrt{3}}{2}V$ |     | 三相短路 |

|        |                                                                                                                                                                   |  |                  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------|

| Type B | $V_a = V$<br>$V_b = -\frac{1}{2}E - j\frac{\sqrt{3}}{2}E$<br>$V_c = -\frac{1}{2}E + j\frac{\sqrt{3}}{2}E$                                                         |  | 單相對線地短路          |

| Type C | $V_a = E$<br>$V_b = -\frac{1}{2}E - j\frac{\sqrt{3}}{2}V$<br>$V_c = -\frac{1}{2}E + j\frac{\sqrt{3}}{2}V$                                                         |  | 單相線對地短路<br>線對線短路 |

| Type D | $V_a = V$<br>$V_b = -\frac{1}{2}V - j\frac{\sqrt{3}}{2}E$<br>$V_c = -\frac{1}{2}V + j\frac{\sqrt{3}}{2}E$                                                         |  | 單相線對地短路<br>線對線短路 |

| Type E | $V_a = E$<br>$V_b = -\frac{1}{2}V - j\frac{\sqrt{3}}{2}E$<br>$V_c = -\frac{1}{2}V + j\frac{\sqrt{3}}{2}E$                                                         |  | 單相線對地短路<br>線對線短路 |

| Type F | $V_a = V$<br>$V_b = -\frac{1}{2}V - j(\frac{\sqrt{3}}{6}V + \frac{\sqrt{3}}{3}E)$<br>$V_c = -\frac{1}{2}V + j(\frac{\sqrt{3}}{6}V + \frac{\sqrt{3}}{3}E)$         |  | 雙相線對地短路          |

| Type G | $V_a = \frac{2}{3}E + \frac{1}{3}V$<br>$V_b = -\frac{1}{3}E - \frac{1}{6}V - j\frac{\sqrt{3}}{6}V$<br>$V_c = -\frac{1}{3}E - \frac{1}{6}V + j\frac{\sqrt{3}}{2}V$ |  | 雙相線對地短路          |

影響電網上電壓訊號除了因故障產生的問題外也有著許多的高頻諧波，不過因為與電網相接時大多利用全橋式整流器等元件，使得雜訊為非兩倍和三倍基頻倍數的諧波，例如 5 倍、7 倍、11 倍等[20]，若將電網上這些可能發生的狀況皆納入考量之中，在不失任何可能的情況下之三相電壓如(2.1)式所表示，其中  $V_n^+$  ( $V_n^-$ ) 和  $\phi_n^+$  ( $\phi_n^-$ ) 為第 n 倍頻率的振幅和相角，右上符號則代表的是電壓的向序。

$$\begin{bmatrix} v_a(t) \\ v_b(t) \\ v_c(t) \end{bmatrix} = \begin{bmatrix} \sum_{n=1}^{\infty} [V_n^+ \cos(n\omega t + \phi_n^+) + V_n^- \cos(n\omega t + \phi_n^-)] \\ \sum_{n=1}^{\infty} [V_n^+ \cos(n\omega t + \phi_n^+ - \frac{2}{3}\pi) + V_n^- \cos(n\omega t + \phi_n^- + \frac{2}{3}\pi)] \\ \sum_{n=1}^{\infty} [V_n^+ \cos(n\omega t + \phi_n^+ + \frac{2}{3}\pi) + V_n^- \cos(n\omega t + \phi_n^-) - \frac{2}{3}\pi] \end{bmatrix} \quad (2.1)$$

### 2.1.2 三相電壓之座標轉換

由於電網電壓是一個三維的向量並且大小為隨時間變化的弦波函數，要直接用在分析和控制上是一個複雜而且困難的函數，為了簡化一般利用克拉克轉換將三維的向量轉化為二維且彼此正交的向量如(2.2)。

$$\begin{bmatrix} v_{\alpha}(t) \\ v_{\beta}(t) \end{bmatrix} = [T_{\alpha\beta}] \begin{bmatrix} v_a(t) \\ v_b(t) \\ v_c(t) \end{bmatrix} = \begin{bmatrix} v_{\alpha}^+(t) \\ v_{\beta}^+(t) \end{bmatrix} + \begin{bmatrix} v_{\alpha}^-(t) \\ v_{\beta}^-(t) \end{bmatrix} \quad (2.2)$$

$$[T_{\alpha\beta}] = \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} \quad (2.3)$$

$$\begin{bmatrix} v_{\alpha}^+(t) \\ v_{\beta}^+(t) \end{bmatrix} = \begin{bmatrix} \sum_{n=1}^{\infty} V_n^+ \cos(n\omega t + \phi_n^+) \\ \sum_{n=1}^{\infty} V_n^+ \sin(n\omega t + \phi_n^+) \end{bmatrix} \quad (2.4)$$

$$\begin{bmatrix} v_\alpha^-(t) \\ v_\beta^-(t) \end{bmatrix} = \begin{bmatrix} \sum_{n=1}^{\infty} V_n^- \cos(n\omega t + \phi_n^-) \\ -\sum_{n=1}^{\infty} V_n^- \sin(n\omega t + \phi_n^-) \end{bmatrix} \quad (2.5)$$

經由方程式(2.2)所得到的訊號比起原始的三相電壓少了一個維度的向量，但大小依然為隨時間變化的弦波函數，在分析和控制上依舊存在不少的困難，所以再藉由帕克轉換，這是一種旋轉座標框的方法，希望將正交向量更進一步簡化為：

$$\begin{bmatrix} v_d(t) \\ v_q(t) \end{bmatrix} = [T_{dq}] \begin{bmatrix} v_\alpha(t) \\ v_\beta(t) \end{bmatrix} = \begin{bmatrix} v_d^+(t) \\ v_q^+(t) \end{bmatrix} + \begin{bmatrix} v_d^-(t) \\ v_q^-(t) \end{bmatrix} \quad (2.6)$$

$$[T_{dq}] = \begin{bmatrix} \cos(\tilde{\theta}) & \sin(\tilde{\theta}) \\ -\sin(\tilde{\theta}) & \cos(\tilde{\theta}) \end{bmatrix}, \tilde{\theta} = \tilde{\omega} + \tilde{\phi}_1^+ \quad (2.7)$$

$$\begin{bmatrix} v_d^+(t) \\ v_q^+(t) \end{bmatrix} = \begin{bmatrix} \sum_{n=1}^{\infty} V_n^+ \cos[(n\omega - \tilde{\omega})t + (\phi_n^+ - \tilde{\phi}_1^+)] \\ \sum_{n=1}^{\infty} V_n^+ \sin[(n\omega - \tilde{\omega})t + (\phi_n^+ - \tilde{\phi}_1^+)] \end{bmatrix} \quad (2.8)$$

$$\begin{bmatrix} v_d^-(t) \\ v_q^-(t) \end{bmatrix} = \begin{bmatrix} \sum_{n=1}^{\infty} V_n^- \cos[(n\omega + \tilde{\omega})t + (\phi_n^- + \tilde{\phi}_1^+)] \\ -\sum_{n=1}^{\infty} V_n^- \sin[(n\omega + \tilde{\omega})t + (\phi_n^- + \tilde{\phi}_1^+)] \end{bmatrix} \quad (2.9)$$

其中  $\tilde{\theta}$ 、 $\tilde{\omega}$ 、 $\tilde{\phi}$  分別為估測的相角、角速度及相位。由式(2.7)和式(2.8)可以發現當角速度鎖定時，即  $\tilde{\omega} = \omega$ ，則  $n = 1$  的正向序弦波函數會變為常數而其餘函數的頻率則是有所改變，可以表示為

$$\begin{bmatrix} v_d(t) \\ v_q(t) \end{bmatrix} = \begin{bmatrix} \bar{v}_d \\ \bar{v}_q \end{bmatrix} + \begin{bmatrix} v_{d,h}(t) \\ v_{q,h}(t) \end{bmatrix} \quad (2.10)$$

其中

$$\begin{cases} \bar{v}_d = V_1^+ \cos(\phi_1^+ - \tilde{\phi}_1^+) \\ \bar{v}_q = V_1^+ \sin(\phi_1^+ - \tilde{\phi}_1^+) \end{cases}$$

若系統是處於相位接近鎖定的條件下時，即  $\tilde{\omega} = \omega$  且， $\tilde{\phi}_1^+ \cong \phi_1^+$ ，則基頻的訊號近似為：

$$\begin{cases} \bar{v}_d = V_1^+ \cos(\phi_1^+ - \tilde{\phi}_1^+) \cong V_1^+ \\ \bar{v}_q = V_1^+ \sin(\phi_1^+ - \tilde{\phi}_1^+) \cong V_1^+ (\phi_1^+ - \tilde{\phi}_1^+) \end{cases} \quad (2.11)$$

由(2.11)的關係可以得知，藉由低通濾波器抑制高頻的諧波訊號便可以將此轉換後的非

時變訊號做為控制的輸入訊號，利用簡單的控制器便可以設計出對於相位有追蹤與鎖定效果的鎖相迴路，其中 d 軸分量可以做為預估基頻正向序的震幅大小，而 q 軸的分量則用來估測基頻的正向序的相位。

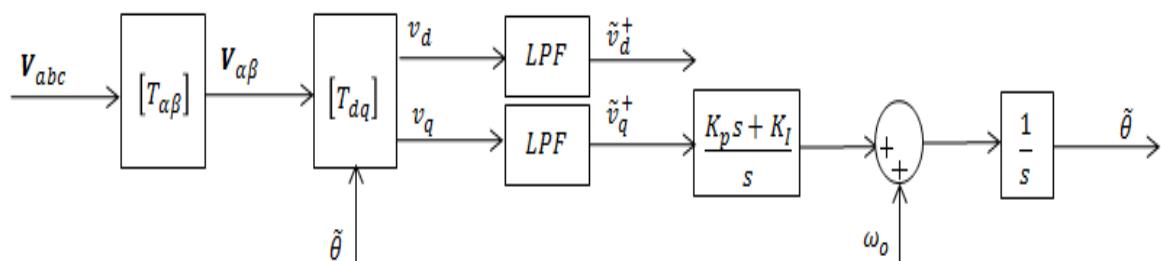

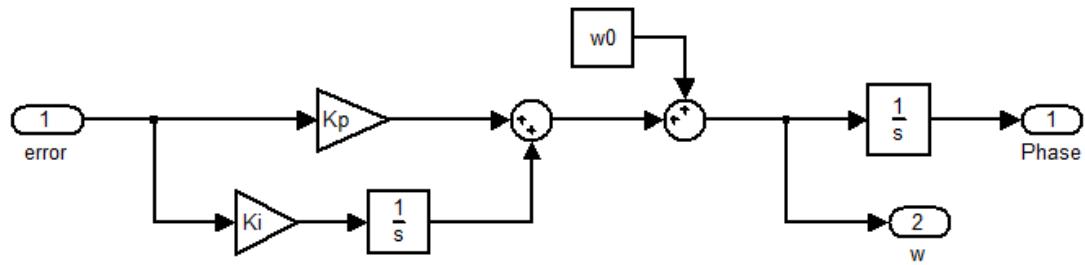

## 2.2 同步參考框鎖相迴路

電網上許多種類的鎖相迴路中，同步參考框鎖相迴路是一種很基本且簡單的架構，此種鎖相迴路的優點是結構十分簡單並且設計容易，僅應用前一小節中所提到的座標轉換矩陣和比例積分控制器便可以在實際應用於電網的鎖相迴路系統。當三相電壓經過克拉克及派克轉換後得到的 q 軸訊號做為比例積分控制器的訊號輸入再利用一個積分器便得到估測之相位，並且將相位回授給派克轉換而形成一個閉迴路的結構，其系統的方塊圖如圖 2.2 所示，圖中  $\tilde{\theta}$  為系統預估之相角，為了令鎖相迴路的反應速度加快一般估測之角速度會額外加上了電網上的基頻頻率  $\omega_o$ ，常用的基頻頻率大多為 60 Hz 或 50 Hz。

圖 2.2 同步參考框鎖相迴路之系統方塊圖

當同步參考框鎖相迴路在相位接近鎖定的條件下，整個鎖相迴路系統在線性化以及電壓經過標幺化後，得到之估測相位  $\tilde{\phi}_1^+$  和實際相位  $\phi_1^+$  的系統方塊圖關係如圖 2.3，在沒有高頻雜訊輸入的條件下輸入和輸出的閉迴路轉移函數為：

$$\frac{\tilde{\phi}_1^+(s)}{\phi_1^+(s)} = \frac{K_p s + K_I}{s^2 + K_p s + K_I} \quad (2.12)$$

圖 2.3 同步參考框鎖相迴路線性化之系統方塊圖

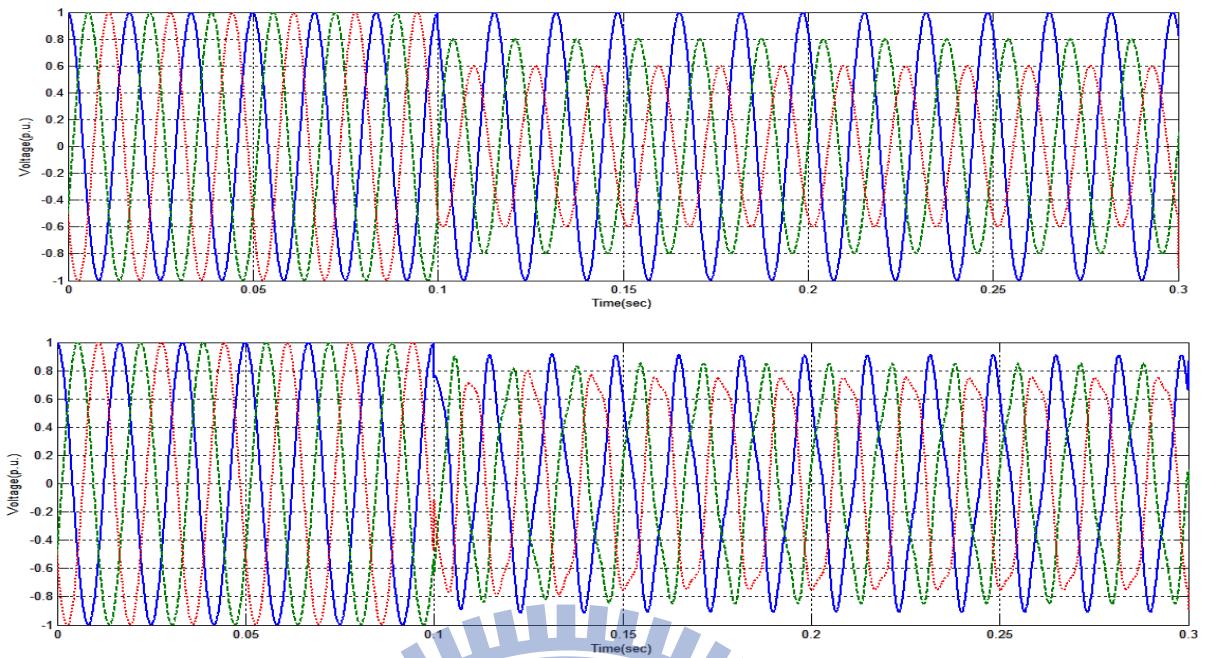

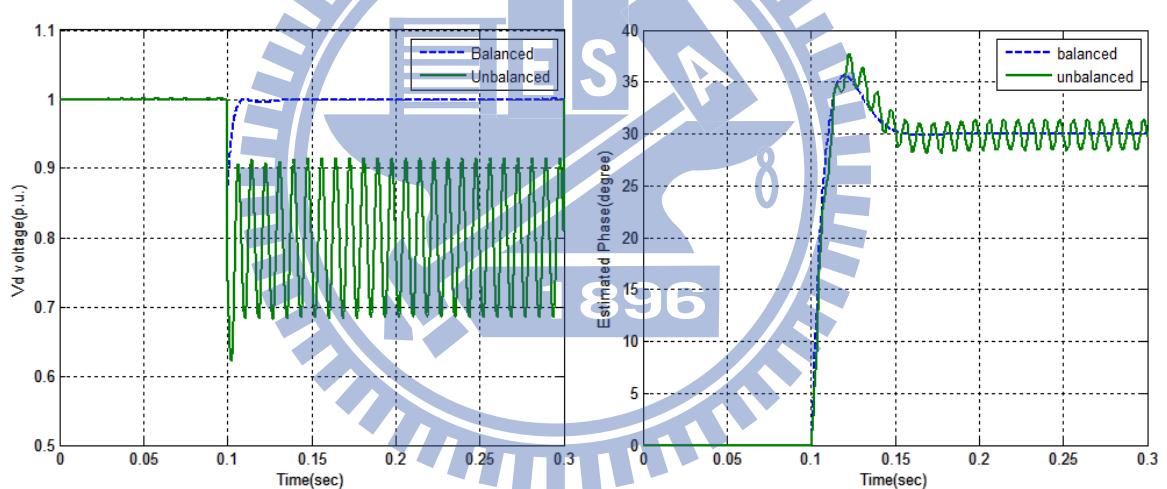

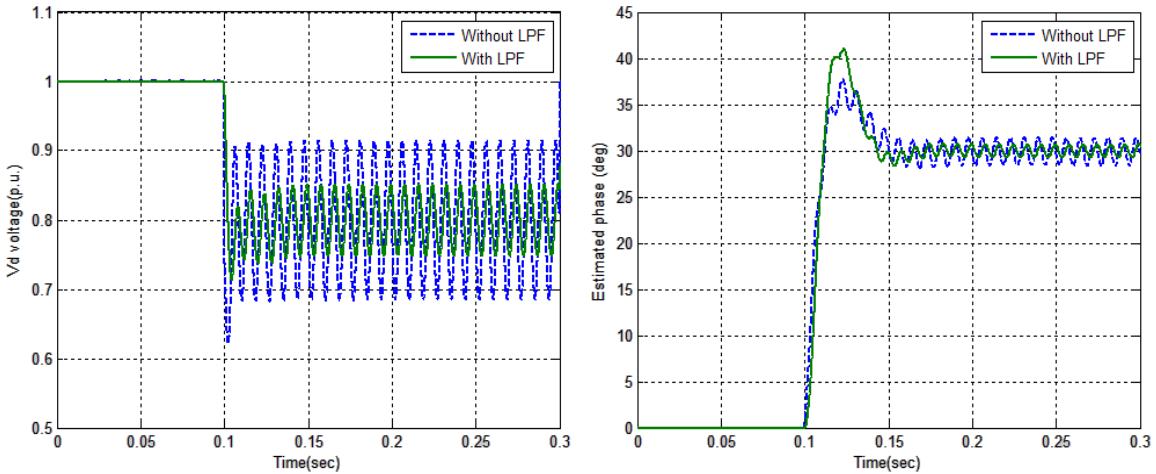

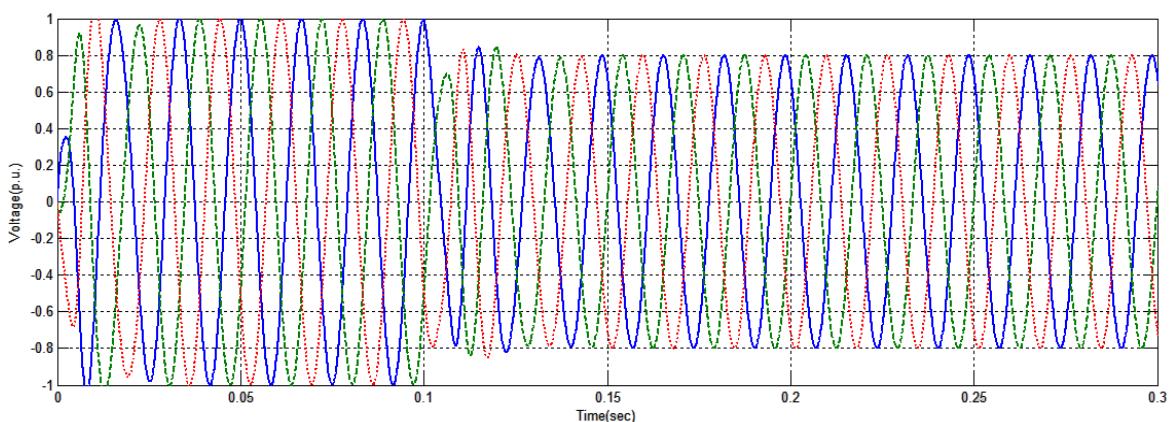

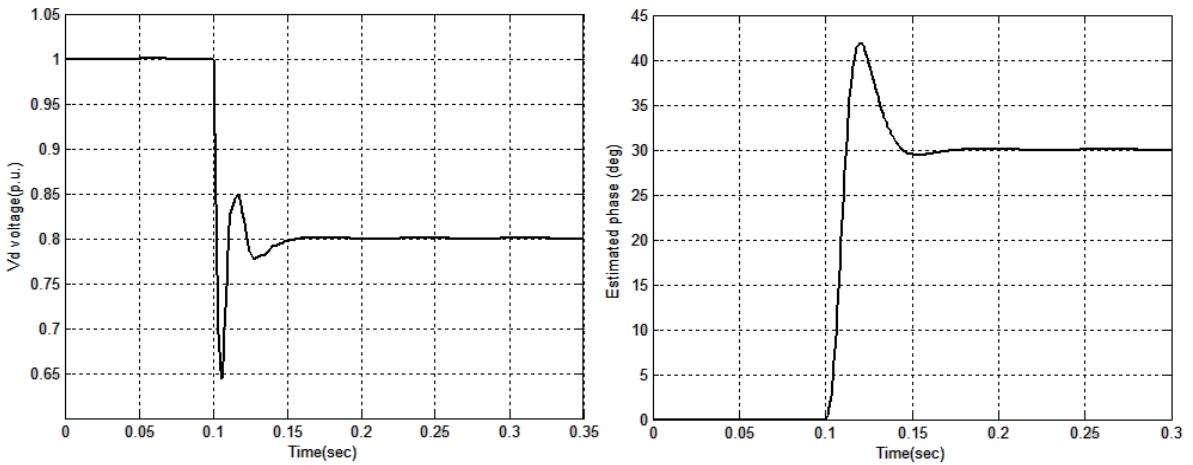

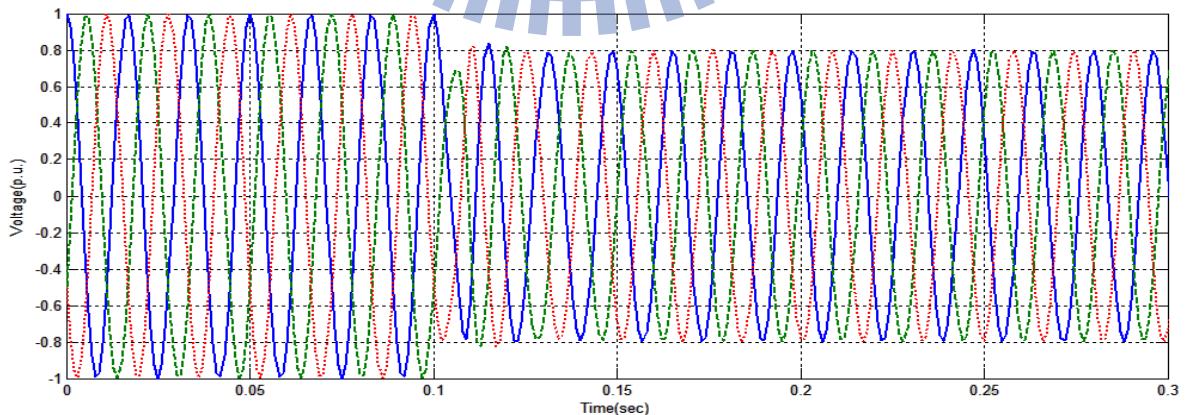

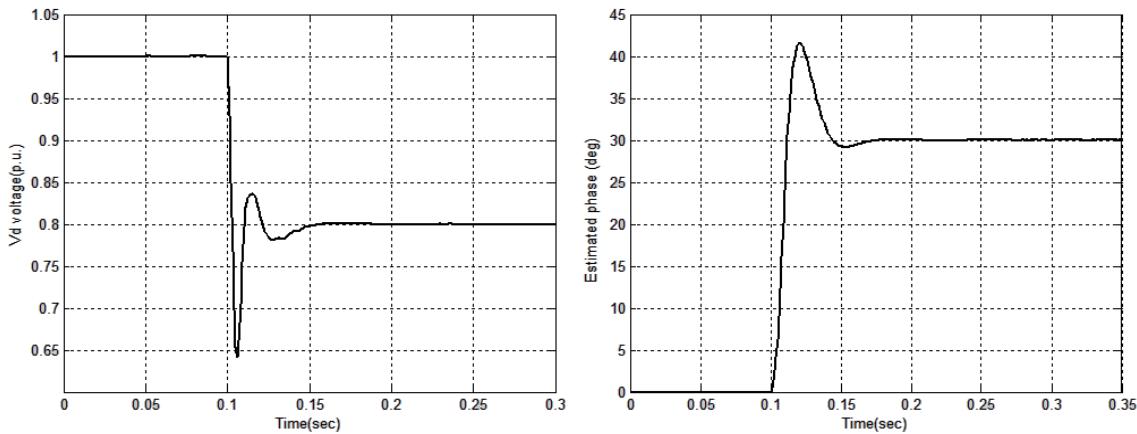

由(2.12)可以得知此系統為一個二階的系統，其分子因為比例積分控制器的關係而存在一個零點，系統的設計上十分簡單藉由調整比例積分控制器的參數來達到所需之系統規格的要求，同步參考框鎖相迴路在相位變化時將擁有不錯的暫態響應，而且對於高頻雜訊也有些許的抑制能力，另外系統的開路轉移函數有兩個在原點的極點因此為型態二之系統，對於相位步階和頻率步階的穩態誤差皆為零。以上特性對於鎖相迴路都是很好的特性，只可惜同步參考框鎖相迴路在電壓發生三相不平衡故障時其所估測之相位因為受到故障的影響而使得預估之相位會有嚴重的震盪行為，造成所估測相位的效果變差無法在其控制的系統上使用。圖 2.4 上圖為初始相位為零的平衡三相電壓在 0.1 秒時發生了不平衡之故障( $V_a = 1(p.u.)$ ,  $V_b = 0.8(p.u.)$ ,  $V_c = 0.6(p.u.)$ )並且同時各相的相位發生了 30 度的落後之三相電壓波型(藍線為 a 相，綠線為 b 相，紅線為 c 相)。圖 2.4 下圖為利用系統所估測的相位還原之正向序三相電壓，圖中因為電壓發生不平衡的故障使得系統估測到的相位並不理想而無法還原得到正確的正向序的平衡三相電壓。圖 2.5 分別為在三相處於平衡的條件下和不平衡的狀況發生時同步參考框鎖相迴路的 d 軸分量及預估相位的響應圖，由這兩張圖可以很明顯的看出在不平衡的條件下此種方法效果十分的不好，不論在估測相角還是估測振幅上都因三相不平衡的影響產生震盪的雜訊。

圖 2.4 輸入之電壓波形與估測之正向序三相電壓波形

圖 2.5 平衡與不平衡狀態下估測之電壓及相位

圖 2.6 同步參考框鎖相迴路加上低通濾波器之系統方塊圖

為解決同步參考框鎖相迴路無法處理不平衡故障的情況，加上低通率波器可以抑制因帕克轉換後成為兩倍基頻的負向序訊號其系統方塊圖如圖 2.6 表示。圖 2.7 和圖 2.8 的圖形分別表示為在一樣的不平衡三相電壓輸入下加裝低通濾波器之同步參考框鎖相迴路的模擬結果，圖 2.7 上圖為原始的三相電壓訊號而下圖為加裝低通濾波器後預估的正向序之三相電壓，圖 2.8 則是未加低通濾波器和額外加上低通濾波器兩者對於估測相位和估測震幅的結果。比較下可以發現當同步參考框鎖相迴路額外加上低通濾波器在處於電壓不平衡的條件下其相位追蹤的結果有改善的情形，但其結果依然存在著震盪的現象，若欲使濾波的效果更明顯必須將濾波器的截止頻率降低，但如此會嚴重增加響應時間。針對因為電壓的不平衡故障造成鎖相迴路的問題，有許多其他的鎖相迴路方法被提出，比起同步參考框鎖相迴路為解決在電壓不平衡狀況額外加上低通濾波器方法，其餘被提出的鎖相迴路的設計中不會有為消除不平衡故障的影響而造成低通濾波器額外拖累鎖相迴路的反應速度的問題，而且這類新穎的鎖相迴路是能夠完全消除因為電壓不平衡的故障造成的估測相位震盪之影響。

圖 2.7 輸入之電壓波形和估測之正向序三相電壓波形

圖 2.8 有加低通濾波器和未加裝的估測電壓及相位之比較

### 2.3 多重參考框鎖相迴路

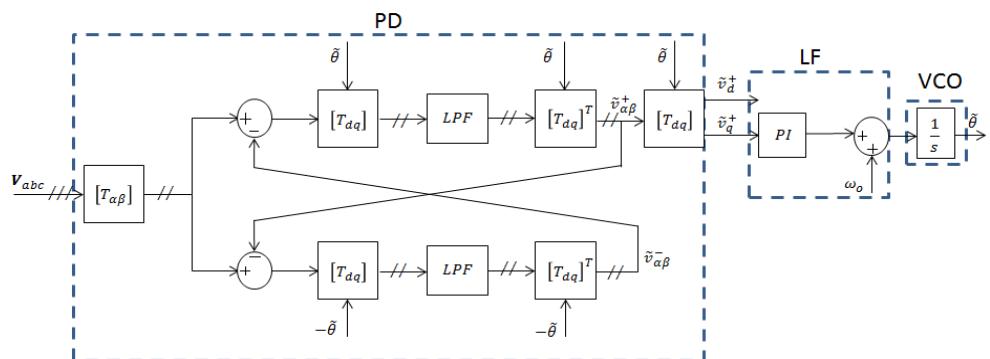

圖 2.9 表示著多重參考框鎖相迴路(Multiple Reference Frame PLL,MRF-PLL)的結構[4]，此種方法和解聯式雙同步參考框鎖相迴路(Decouple Double Synchronous Reference Frame PLL,DDSRF-PLL)[1]、[2]有類似的構想，兩者之間只是結構不同但多重參考框鎖相迴路的結構比較直觀。這一種類型的鎖相迴路主要設計目的是讓電壓訊號經過兩個相同但是旋轉方向相反的同步框後經過低通濾波器過濾因轉換後產生的兩倍頻率的諧波訊號分別得到估測出的正向序和負向序之電壓訊號，再將估測的兩種訊號回授相減而消去對於彼此的影響，因而得到解聯後的正向序以及負向序之分量，最後利用解聯後正向序的分量訊號經過比例積分控制器得到估測的相位。

圖 2.9 多重參考框鎖相之系統方塊圖

由圖 2.9 可以得到估測的正向序和負向序與輸入訊號的關係為：

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^+(t) \\ \tilde{v}_{\beta,1}^+(t) \end{bmatrix} = [T_{dq}]^T \left\{ \begin{bmatrix} LPF(t) & 0 \\ 0 & LPF(t) \end{bmatrix} * \left\{ [T_{dq}] \left\{ \begin{bmatrix} v_\alpha(t) \\ v_\beta(t) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^-(t) \\ \tilde{v}_{\beta,1}^-(t) \end{bmatrix} \right\} \right\} \right\} \quad (2.14)$$

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^-(t) \\ \tilde{v}_{\beta,1}^-(t) \end{bmatrix} = [T_{dq}] \left\{ \begin{bmatrix} LPF(t) & 0 \\ 0 & LPF(t) \end{bmatrix} * \left\{ [T_{dq}]^T \left\{ \begin{bmatrix} v_\alpha(t) \\ v_\beta(t) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^+(t) \\ \tilde{v}_{\beta,1}^+(t) \end{bmatrix} \right\} \right\} \right\} \quad (2.15)$$

其中方程式(2.14)和(2.15)中的低通濾波器的轉移函數為

$$LPF(s) = \frac{\omega_p}{s + \omega_p} \quad (2.16)$$

並且將式(2.14)和(2.15)的帕克轉換中之三角函數利用尤拉公式展開得到：

$$\begin{aligned} [T_{dq}] &= \begin{bmatrix} \cos(\tilde{\theta}) & \sin(\tilde{\theta}) \\ -\sin(\tilde{\theta}) & \cos(\tilde{\theta}) \end{bmatrix}, \tilde{\theta} = \tilde{\omega} + \tilde{\phi}_1^+ \\ &= \frac{1}{2} \begin{bmatrix} e^{j\tilde{\theta}} + e^{-j\tilde{\theta}} & -je^{j\tilde{\theta}} + je^{-j\tilde{\theta}} \\ je^{j\tilde{\theta}} - je^{-j\tilde{\theta}} & e^{j\tilde{\theta}} + e^{-j\tilde{\theta}} \end{bmatrix} \end{aligned} \quad (2.17)$$

式(2.17)代入式(2.14)和(2.15)並經過拉普拉斯轉換後為

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} = \begin{bmatrix} LPF(s + j\tilde{\omega}) + LPF(s - j\tilde{\omega}) & -jLPF(s + j\tilde{\omega}) + LPF(s - j\tilde{\omega}) \\ jLPF(s + j\tilde{\omega}) - jLPF(s - j\tilde{\omega}) & LPF(s + j\tilde{\omega}) + LPF(s - j\tilde{\omega}) \end{bmatrix} \times \left\{ \begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^-(s) \\ \tilde{v}_{\beta,1}^-(s) \end{bmatrix} \right\} \quad (2.18)$$

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^-(s) \\ \tilde{v}_{\beta,1}^-(s) \end{bmatrix} = \begin{bmatrix} LPF(s + j\tilde{\omega}) + LPF(s - j\tilde{\omega}) & jLPF(s + j\tilde{\omega}) - jLPF(s - j\tilde{\omega}) \\ -jLPF(s + j\tilde{\omega}) + jLPF(s - j\tilde{\omega}) & LPF(s + j\tilde{\omega}) + LPF(s - j\tilde{\omega}) \end{bmatrix} \times \left\{ \begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} \right\} \quad (2.19)$$

方程式(2.18)和(2.19)展開並整理後為

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} = \begin{bmatrix} \frac{\omega_p(s + \omega_p)}{(s + \omega_p)^2 + \tilde{\omega}^2} & -\frac{\tilde{\omega}\omega_p}{(s + \omega_p)^2 + \tilde{\omega}^2} \\ \frac{\tilde{\omega}\omega_p}{(s + \omega_p)^2 + \tilde{\omega}^2} & \frac{\omega_p(s + \omega_p)}{(s + \omega_p)^2 + \tilde{\omega}^2} \end{bmatrix} \left\{ \begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^-(s) \\ \tilde{v}_{\beta,1}^-(s) \end{bmatrix} \right\} \quad (2.20)$$

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^-(s) \\ \tilde{v}_{\beta,1}^-(s) \end{bmatrix} = \begin{bmatrix} \frac{\omega_p(s + \omega_p)}{(s + \omega_p)^2 + \tilde{\omega}^2} & \frac{\tilde{\omega}\omega_p}{(s + \omega_p)^2 + \tilde{\omega}^2} \\ -\frac{\tilde{\omega}\omega_p}{(s + \omega_p)^2 + \tilde{\omega}^2} & \frac{\omega_p(s + \omega_p)}{(s + \omega_p)^2 + \tilde{\omega}^2} \end{bmatrix} \left\{ \begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} \right\} \quad (2.21)$$

將(2.21)代入(2.20)可得到  $\alpha$   $\beta$  軸上的正向序和輸入訊號的關係矩陣為

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} = \begin{bmatrix} \frac{\omega_p s}{s^2 + 2\omega_p s + \tilde{\omega}^2} & -\frac{\tilde{\omega}\omega_p}{s^2 + 2\omega_p s + \tilde{\omega}^2} \\ \frac{\tilde{\omega}\omega_p}{s^2 + 2\omega_p s + \tilde{\omega}^2} & \frac{\omega_p s}{s^2 + 2\omega_p s + \tilde{\omega}^2} \end{bmatrix} \begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} \quad (2.22)$$

多重參考框鎖相迴路中正向序和負向序相減的運算方式，事實上可以視為一個帶拒濾波器的效果，因原本不平衡的電壓中經由帕克轉換而造成的兩倍基頻弦波訊號會被所推估之正向序和負向序的訊號相減而消去，其推導證明如下，以正向序為例將方程式(2.20)改寫後可以得到

$$\begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^-(s) \\ \tilde{v}_{\beta,1}^-(s) \end{bmatrix} = \left\{ \begin{bmatrix} \frac{\omega_p(s + \omega_p)}{(s + \omega_p)^2 + \tilde{\omega}^2} & -\frac{\tilde{\omega}\omega_p}{(s + \omega_p)^2 + \tilde{\omega}^2} \\ \frac{\tilde{\omega}\omega_p}{(s + \omega_p)^2 + \tilde{\omega}^2} & \frac{\omega_p(s + \omega_p)}{(s + \omega_p)^2 + \tilde{\omega}^2} \end{bmatrix} \right\}^{-1} \begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} \\ = \frac{1}{\omega_p} \begin{bmatrix} s + \omega_p & \tilde{\omega} \\ -\tilde{\omega} & s + \omega_p \end{bmatrix} \begin{bmatrix} \tilde{v}_{\alpha,1}^+(s) \\ \tilde{v}_{\beta,1}^+(s) \end{bmatrix} \quad (2.23)$$

將式(2.22)代入(2.23)中可以得到

$$\begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^-(s) \\ \tilde{v}_{\beta,1}^-(s) \end{bmatrix} = \begin{bmatrix} s^2 + \omega_p s + \tilde{\omega}^2 & -\tilde{\omega}\omega_p \\ s^2 + 2\omega_p s + \tilde{\omega}^2 & s^2 + 2\omega_p s + \tilde{\omega}^2 \\ \tilde{\omega}\omega_p & s^2 + \omega_p s + \tilde{\omega}^2 \\ s^2 + 2\omega_p s + \tilde{\omega}^2 & s^2 + 2\omega_p s + \tilde{\omega}^2 \end{bmatrix} \begin{bmatrix} v_\alpha(s) \\ v_\beta(s) \end{bmatrix} \quad (2.24)$$

且  $v_\alpha$  和  $v_\beta$  在穩定狀態下時兩者有相差九十度的相位的關係即：

$$v_\beta(j\omega) = -jv_\alpha(j\omega) \quad (2.25)$$

則將  $s = j\omega$  及(2.25)代入(2.24)可以得到其關係式

$$\begin{bmatrix} v_\alpha(j\omega) \\ v_\beta(j\omega) \end{bmatrix} - \begin{bmatrix} \tilde{v}_{\alpha,1}^-(j\omega) \\ \tilde{v}_{\beta,1}^-(j\omega) \end{bmatrix} = \frac{\tilde{\omega}^2 - \omega^2 + j\omega_p(\omega + \tilde{\omega})}{\tilde{\omega}^2 - \omega^2 + 2j\omega_p\omega} \begin{bmatrix} v_\alpha(j\omega) \\ v_\beta(j\omega) \end{bmatrix} \quad (2.26)$$

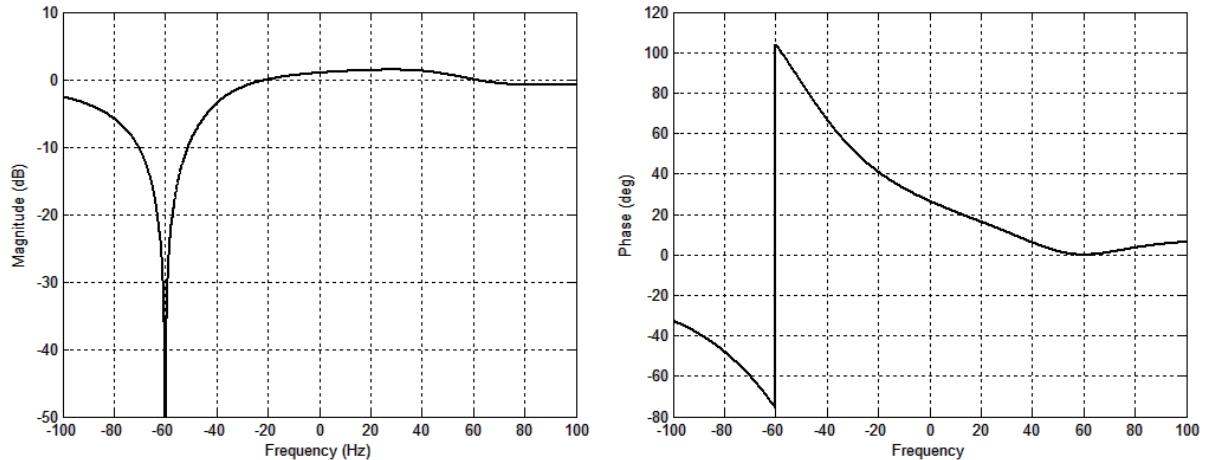

圖 2.10 所繪為低通濾波器的截止頻率為 30 Hz 時，方程式(2.26)其轉移函數的增益和相位對於頻率之關係圖。由圖可以得知這樣的結構對正向序的向量是一個截止頻率發生在負基頻頻率的帶拒濾波器，完全消除掉負向序向量的分量，在正向序之頻率時系統的增益為一，因此輸出之訊號完整地保留正向序向量的分量。

圖 2.10 多重參考框鎖相迴路等效之帶拒濾波器的波德圖

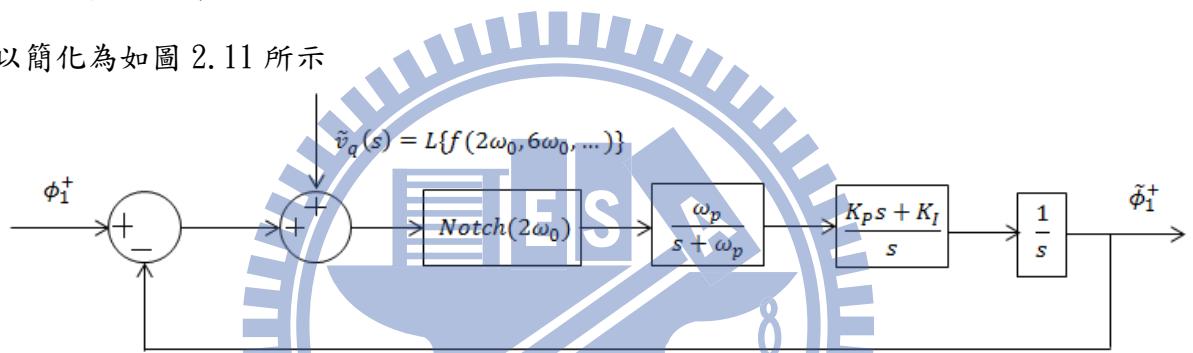

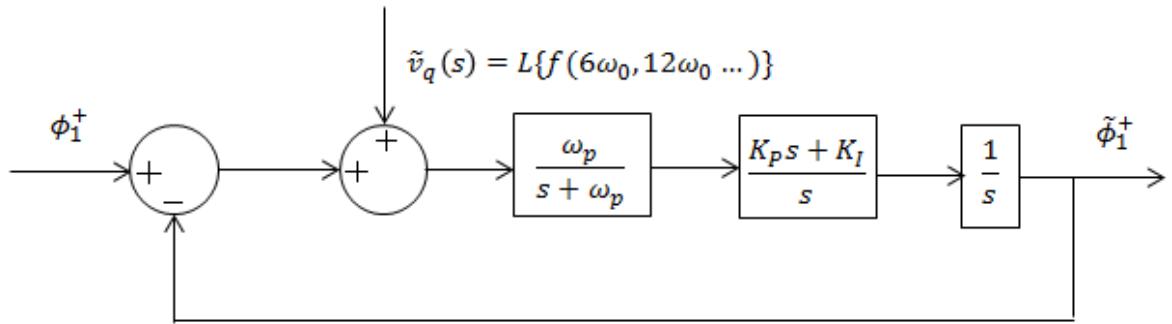

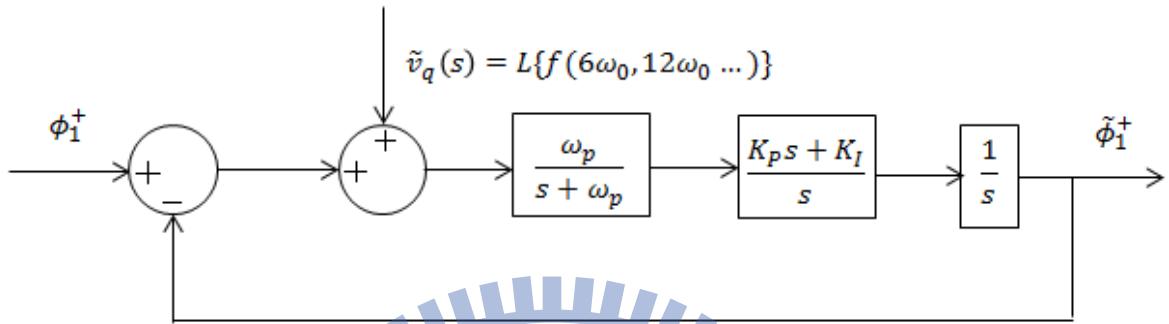

當多重參考框鎖相迴路在處相位接近鎖定的條件下，經過線性化後其系統方塊圖可以簡化為如圖 2.11 所示

圖 2.11 多重參考框鎖相迴路線性化系統方塊圖

一般情況下低通濾波器的截止頻率會低於等效之帶拒濾波器的兩倍基頻頻率之截止頻帶，所以在暫態分析上通常忽略帶拒濾波器造成的影響，並且將高頻諧波中兩倍頻率之諧波除去以簡化分析，在相位接近鎖定的條件下線性化後的系統方塊圖可以再簡化，如圖 2.12 所示。在沒有高頻雜訊輸入時，其輸出之估測相位和輸入之實際相位的開迴路與閉迴路轉移函數分別為

$$G(s) = \frac{\omega_p(K_p s + K_I)}{s^2(s + \omega_p)} \quad (2.27)$$

$$\frac{\tilde{\phi}_1^+(s)}{\phi_1^+(s)} = \frac{\omega_p(K_p s + K_I)}{s^3 + \omega_p s^2 + \omega_p K_p s + \omega_p K_I} \quad (2.28)$$

圖 2.12 多重參考框鎖相迴路線性化並簡化之系統方塊圖

由(2.27)可以得知此系統得轉移函數和加裝低通濾波器之同步參考框鎖相迴路的轉移函數相似，雖然低通濾波器的截止頻率一樣關係響應的速度以及對於高頻的抑制能力，但和同步參考框鎖相迴路相比此種方法可以完全消去因電壓三相不平衡故障造成對於估測相位和估測振幅之震盪情形。

為比較多重參考框鎖相迴路和同步參考框鎖相迴路的效果。考慮圖 2.4 的模擬條件，由圖 2.13 和 2.14 可以發現當三相的電壓在 0.1 秒發生故障後多重參考框鎖相迴路估測的正向序電壓會是三相平衡的電壓，也可以很穩定地追蹤到相位之變化以及電壓的振幅。此外在設計要求上對於高頻諧波有較嚴苛的要求時，例如需要完全消去六倍基頻的諧波時，更可以額外增加針對六倍基頻的參考框，讓估測相位時系統並不會經受到電網上六倍基頻諧波的影響，雖然這樣會增加額外的計算成本，但比起單純利用低通濾波器會有更好的高頻抑制效果。

圖 2.13 估測相之正向序三相電壓波形

圖 2.14 多重參考框鎖相迴路估測之電壓和相位

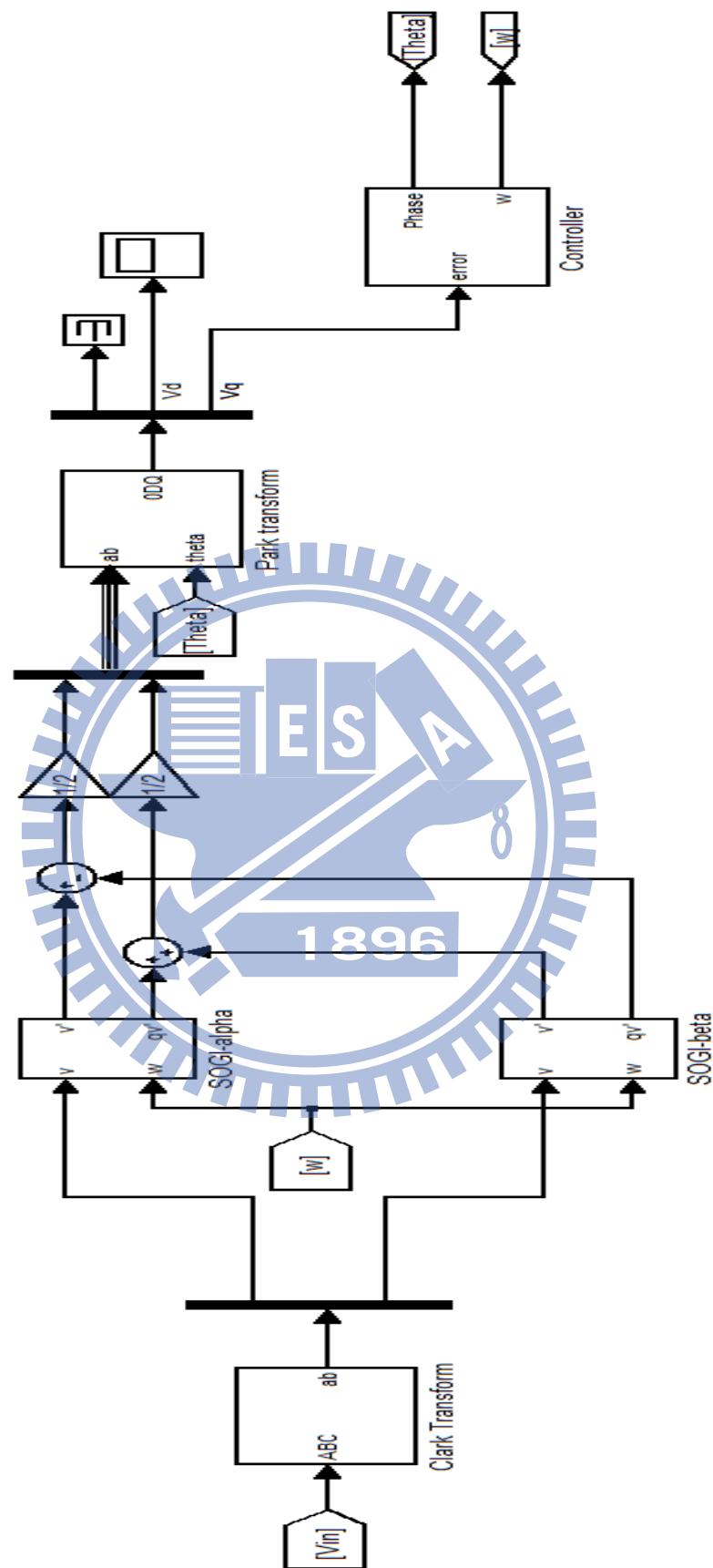

## 2.4 雙通用積分器鎖相迴路

不同於多重參考框鎖相迴路是運用兩個不同的參考框訊號相減的方式消去三相不平衡故障中負向序之分量的影響，這一種鎖相迴路則是利用由 Lyon 所提出的瞬時對稱分量分析法[21]可以經由運算的分析直接從三相電壓分別得到正向序和負向序的兩種向量的分量，比起多重參考框鎖相迴路中須利用兩個帕克轉換之矩陣方能得到正向序的分量，順時對稱分量法僅利用簡單的運算便可以分離出正向序和負向序的向量，一個瞬時的三相電壓其正向序及負向序分量的關係式如(2.29)和(2.30)所示

$$V_{abc}^+ = \frac{1}{3} \begin{bmatrix} 1 & a^2 & a \\ a & 1 & a^2 \\ a^2 & a & 1 \end{bmatrix} V_{abc} \quad (2.29)$$

$$V_{abc}^- = \frac{1}{3} \begin{bmatrix} 1 & a & a^2 \\ a^2 & 1 & a \\ a & a^2 & 1 \end{bmatrix} V_{abc} \quad (2.30)$$

其中  $a = e^{-j\frac{2}{3}\pi}$ ，利用(2.19)以及式(2.3)的克拉克轉換可以得到三相的瞬時電壓在正交軸上之正向序電壓的關係：

$$\begin{aligned}

V_{\alpha\beta}^+ &= \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ 0 & \frac{1}{2} & \frac{1}{2} \end{bmatrix} * V_{abc}^+ \\

&= \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ 0 & \frac{1}{2} & \frac{1}{2} \end{bmatrix} * \begin{bmatrix} 1 & a^2 & a \\ a & 1 & a^2 \\ a^2 & a & 1 \end{bmatrix} * V_{abc} \\

&= \frac{2}{3} \begin{bmatrix} 1 & -\frac{1}{2} & -\frac{1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ 0 & \frac{1}{2} & \frac{1}{2} \end{bmatrix} * \begin{bmatrix} 1 & a^2 & a \\ a & 1 & a^2 \\ a^2 & a & 1 \end{bmatrix} * \begin{bmatrix} 1 & 0 \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} \end{bmatrix} * V_{\alpha\beta} \\

&= \frac{1}{2} \begin{bmatrix} 1 & -q \\ q & 1 \end{bmatrix} V_{\alpha\beta}, q = e^{-j\frac{\pi}{2}}

\end{aligned} \tag{2.31}$$

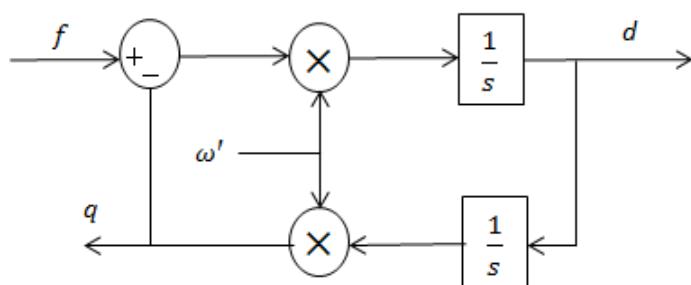

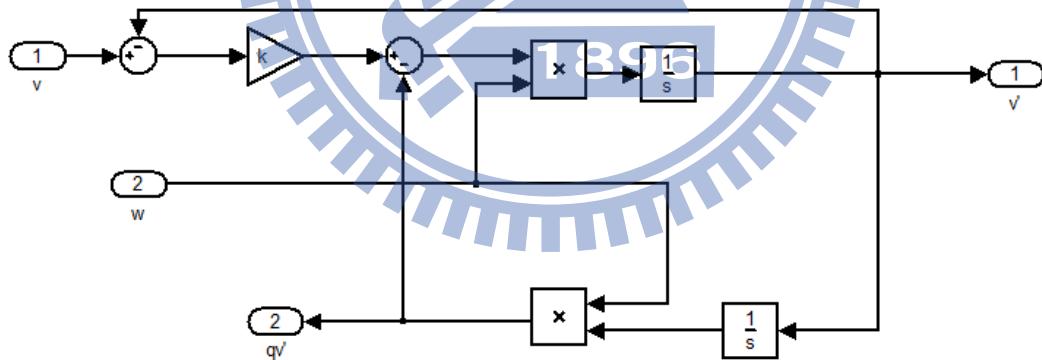

方程式(2.31)中  $q$  是相位落後 90 度並且和原訊號波形正交的運算元，因此僅需利用垂直訊號產生器便可得到三相電壓中正向序的分量。垂直訊號產生器的實現方式有很多種，最直接的方式是利用傳輸延遲的數位元件，但這種方式會因為系統的頻率發生變動時而無法獲得正確的相位落後訊號，因此較好的方式是用非線性的增強型鎖相迴路(Enhanced PLL, EPLL)[5]、[6]或二階通用積分器(Second order generalized integrator, SOGI)[8]-[10]。本論文中將利用二階通用積分器作為垂直訊號產生器其方塊圖如圖 2.15 所示，得知輸入和輸出的轉移函數為

$$F(s) = \frac{d}{f}(s) = \frac{s\omega'}{s^2 + \omega'^2} \tag{2.32}$$

圖 2.15 基本的二階通用積分器之系統方塊圖

圖 2.16 改良過之二階通用積分器系統方塊圖

由式(2.32)可以得知當二階通用積分器輸入  $f$  為一個步階函數時，輸出為一個在  $\omega'$  震盪之弦波，若輸入是頻率為  $\omega'$  的弦波訊號時二階通用積分器則成為讓弦波震幅隨時間增加之積分器。當改變二階通用積分器的結構為如圖 2.16 所示時，可用來追蹤輸入之弦波訊號，輸入  $v$  對於輸出  $v'$  的轉移函數可表示為：

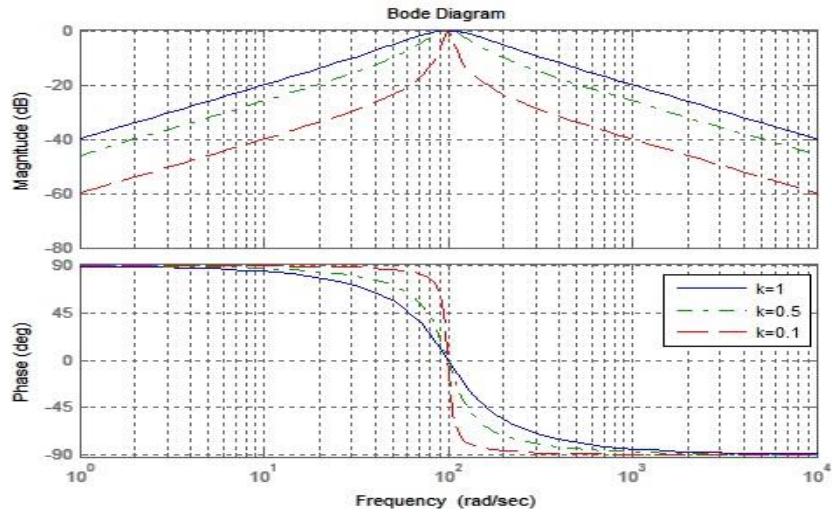

$$D(s) = \frac{v'}{v}(s) = \frac{k\omega's}{s^2 + k\omega's + \omega'^2} \quad (2.33)$$

其中  $k$  和  $\omega'$  分別決定系統的阻尼係數和共振頻率。圖 2.17 為輸出轉移函數之波德圖，從圖上可以得知  $v'$  在此系統中的響應相當於是帶通濾波器的效果，對於頻帶外之的訊號皆有抑制的能力，而  $k$  值的改變除了直接影響了濾波器的效果外，越小的  $k$  代表濾波器的頻寬就越窄，濾波效果越明顯。通用積分器的另一個輸出  $qv'$  和輸入的轉移函數可表示為：

$$Q(s) = \frac{qv'}{v}(s) = \frac{k\omega'^2}{s^2 + k\omega's + \omega'^2} \quad (2.34)$$

圖 2.18 為  $qv'$  的轉移函數之波德圖，從圖上得知  $qv'$  輸出的響應也是一個帶通濾波器的行為， $k$  值也影響著系統頻帶的寬度。當通用積分器之輸入訊號為一弦波時這兩個輸出訊號為相同頻率之弦波訊號，且  $qv'$  的相位總是落後  $v'$  相位 90 度，這個相位落後的現象不論在任何的輸入頻率、 $\omega'$  或  $k$  皆成立。因此利用通用積分器之特性當電網之基頻頻率為濾波器的頻寬中心時可分別得到正交軸上基頻頻率的原始訊號及其正交之訊號。

圖 2.17 改良過之二階通用積分器  $D(s)$  之波德圖

圖 2.18 改良過之二階通用積分器  $Q(s)$  之波德圖

圖 2.19 雙通用積分器鎖相迴路之系統方塊圖

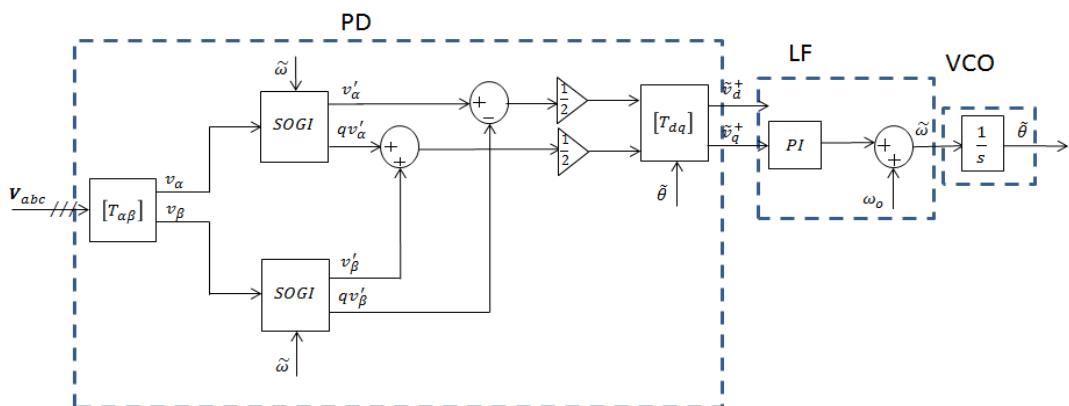

利用兩個二階通用積分器的特性和順時對稱分量分析的方法可以設計出一種結構簡單而且可以去除不平衡故障中負向序分量的鎖相迴路其方塊圖如圖 2.19 所示。將  $\alpha$  和  $\beta$  軸上的訊號分別利用二階通用積分器個別產生出兩組互相垂直的訊號，運算後得到正向序的訊號，再經過帕克轉換和利用比例積分控制器得到追蹤相角的效果，整個系統的輸入和輸出轉移函數為

$$\begin{bmatrix} \tilde{v}_{\alpha,1}^+ \\ \tilde{v}_{\beta,1}^+ \end{bmatrix} = \frac{1}{2} \begin{bmatrix} \frac{k\tilde{\omega}s}{s^2 + k\tilde{\omega}s + \tilde{\omega}^2} & -\frac{k\tilde{\omega}^2}{s^2 + k\tilde{\omega}s + \tilde{\omega}^2} \\ \frac{k\tilde{\omega}^2}{s^2 + k\tilde{\omega}s + \tilde{\omega}^2} & \frac{k\tilde{\omega}s}{s^2 + k\tilde{\omega}s + \tilde{\omega}^2} \end{bmatrix} \begin{bmatrix} v_\alpha \\ v_\beta \end{bmatrix} \quad (2.35)$$

比較(2.22)和(2.35)可以發現當式(2.22)的  $\omega_p = k\tilde{\omega}/2$  時，雙通用積分器鎖相迴路與多重參考框鎖相迴路之轉移函數是相同的，這兩種鎖相迴路在滿足這個條件下可以視為相同的控制結構，因此雙二階通用積分鎖相迴路在線性化後的系統可以等效為多重參考框鎖相迴路之線性化模型。圖 2.20 表示為輸入電壓和圖 2.4 有相同條件時估測之三相波形的結果，可知不平衡的三相電壓經過雙通用積分器後可以順利地分解出的正向序為三相平衡的波型。圖 2.21 表示當雙通用積分器鎖相迴路在三相電壓不平衡時其相位追蹤以及電壓估測的結果和多重參考框鎖相迴路一樣良好，不過兩者之間雙通用積分器鎖相迴路的結構較為簡單。

圖 2.20 輸入之電壓和估測之正向序三相電壓波形

圖 2.21 雙通用積分器鎖相迴路估測之電壓和相位

以上介紹的這三種鎖相迴路中，結構最簡單的同步參考框鎖相迴路只需設計比例積分控制器的參數，其系統就擁有良好的反應速度、不錯的高頻諧波抑制能力並且可以準確地估測相位和電壓，但最大的缺點為僅能在三相平衡的條件下才有良好的鎖相效果，雖然額外加上了低通濾波器可以降低不平衡故障的影響，但不平衡的干擾依然讓估測的相位無法在控制上使用。多重參考框鎖相迴路和雙通用積分器鎖相迴路則是當電網發生不平衡故障時可以有效地消除負向序的影響，且可以利用額外增加元件的方式得以消除特定頻率之雜訊如同[4]、[22]、[23]中所提出，理想上可以利用這種方式消除電網上全部的高頻諧波，但是整個系統必須付出成本增加的代價。一般情況下良好設計的比例積分回授控制對於追蹤相位及估測震幅大小擁有不錯的響應結果，且比例積分回授控制是一個十分常用的控制器，除了結構簡單外而且相位和頻率的變化之穩態誤差皆為零，因此在鎖相迴路中大多利用比例積分控制器來達到系統控制之目的，但是比例積分器存在一個影響系統暫態響應的零點，當追求快速的響應時卻不得不接受較大的最大超越量，若要兼顧最大超越量和反應速度卻又得必須犧牲系統對於高頻雜訊的抑制能力。若可以尋找新的控制方式在相同的要求內使得系統除了滿足相同的暫態響應要求並且有較低的最大超越量或在不犧牲高頻抑制能力的條件下使得暫態響應的結果更好，這樣的做法使得成本比較便宜而且系統的結構也比較簡單。

### 三、控制器設計與分析

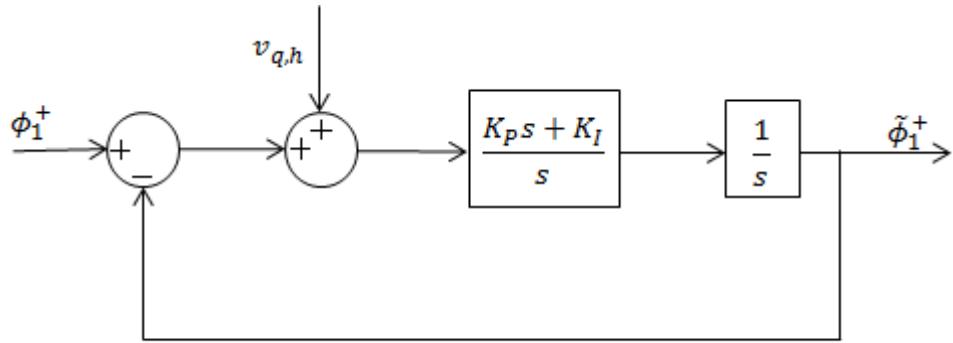

由於同步參考框鎖相迴路在不平衡電壓的情況下得到的結果不甚理想，實際電網運用的鎖相迴路系統大多會使用如多重參考框鎖相迴路或雙通用積分器鎖相迴路等這類可以完全消除不平衡故障的系統，當電網上的相位或頻率發生改變時，一般多是藉由帕克轉換後得到的  $q$  軸相位誤差訊號作為控制器的輸入來達到追蹤相位的目的。本論文主要是研究當利用雙通用積分器為鎖相迴路的相位偵測元件時，其控制器除了常用的比例積分回授控制外，是否有其餘的控制方式可以運用，並且分析不同控制方法運用於鎖相迴路時的暫態響應和高頻抑制能力。本章會探討虛擬微分回授控制、自適性調整之比例積分回授控制以及  $Q$  參數化等三種新的控制器設計方式。首先分析比例積分控制器的參數設計對於系統響應之影響和高頻諧波的抑制效果，再介紹虛擬微分回授控制和比例積分控制的差異，以及分析虛擬微分回授控制在鎖相迴路的控制，接著探討自適性調整之比例積分回授控制及  $Q$  參數化這兩種方式所設計出之控制器。由於鎖相迴路的系統實際上為一個非線性且和三角函數相關的系統，為了簡化系統利於探討，假設系統處於相位近乎鎖定的情況並且將之線性化，且由第二章第四節得知雙通用積分器鎖相迴路線性化之後等效為一個低通的濾波器，且等效之低通濾波器截止頻率和雙通用積分器必須滿足  $\omega_p = k\tilde{\omega}/2$  的關係。

#### 3.1 雙通用積分器鎖相迴路利用比例積分回授控制之分析

一般鎖相迴路大多是使用比例積分回授控制作為控制方法，原因不外乎因為比例積分回授控制結構十分簡單，對於暫態響應和高頻抑制上也都有不錯的表現，而且由於比例積分回授控制發展久遠在設計上有較多方法和經驗被提出，讓這種控制方式在各種不同的系統要求下足以選出最佳的控制之參數，本節將利用最大的相位裕度設計讓比例積分控制器參數達到最佳化設計。

### 3.1.1 比例積分回授控制系統之最大相位裕度設計

比例積分回授控制的分析及設計在[24]中主要是利用對稱最佳化設計法(symmetrical optimum method)[25]對比例積分控制器的參數做詳盡的分析與設計的探討，本節僅將簡略的分析以及探討其比例回授控制之暫態響應與高頻抑制的影響。

圖 3.1 雙通用積分器鎖相迴路之線性化系統方塊圖

利用第二章第四節中對於雙通用積分器鎖相迴路的分析，可以得知在相位接近鎖定的條件下其線性化後鎖相迴路的系統方塊圖為圖 3.1 所示，由圖中的可知在沒有輸入雜訊干擾，即  $\tilde{v}_q(s) = 0$  時，此線性化後系統之輸入相位和輸出預估相位之開路轉移函數如(3.1)。

$$G(s) = \frac{\omega_p(K_p s + K_I)}{s^2(s + \omega_p)} = \frac{\omega_p K_p(s + \omega_z)}{s^2(s + \omega_p)}, \omega_z = \frac{K_I}{K_p} \quad (3.1)$$

在[24]的參數設計中考慮系統最大相位裕度的設計，假設  $\omega_c$  為系統之開路增益截止頻率，即開路轉移函數在  $\omega = \omega_c$  時的增益為一，則由(3.1)得到增益與相位之關係為：

$$|G(j\omega_c)| = \frac{\omega_p K_p \sqrt{\omega_c^2 + \omega_z^2}}{\omega_c^2 \sqrt{\omega_c^2 + \omega_p^2}} = 1 \quad (3.2)$$

$$PM = \tan^{-1}\left(\frac{\omega_c}{\omega_z}\right) - \tan^{-1}\left(\frac{\omega_c}{\omega_p}\right) \quad (3.3)$$

為選擇增益穿越頻率以得到最大的相位裕度，將(3.3)對  $\omega_c$  微分可以得到關係式如(3.4)。

$$\frac{\frac{1}{\omega_z}}{1 + \left(\frac{\omega_c}{\omega_z}\right)^2} - \frac{\frac{1}{\omega_p}}{1 + \left(\frac{\omega_c}{\omega_p}\right)^2} = 0 \quad (3.4)$$

將方程式(3.4)整理後可以得到增益截止頻率的關係式為：

$$\omega_c = \sqrt{\omega_z \omega_p} \quad (3.5)$$

而且增益截止頻率必須滿足(3.2)的增益關係式，因此將(3.5)代入(3.2)式中可以得到

$$K_p = \sqrt{\omega_z \omega_p} = \omega_c \quad (3.6)$$

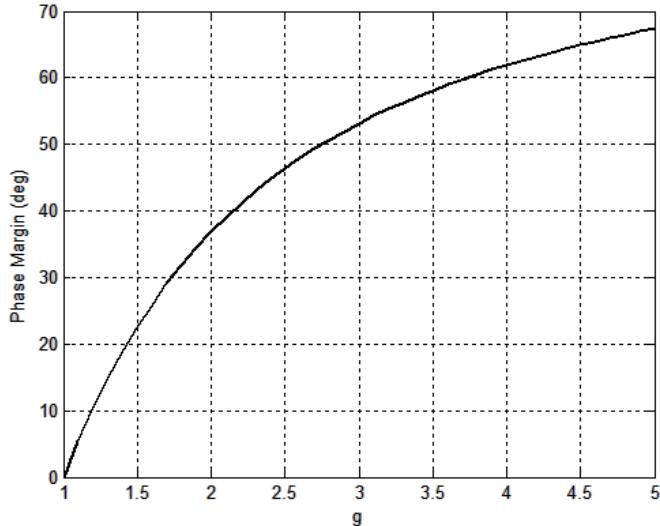

在決定 $\omega_p$ 和 $\omega_z$ 後，當增益穿越頻率滿足(3.6)的關係則系統將可以擁有在此增益穿越頻率下之最大相位裕度，若假設 $\omega_p = g^2 \omega_z$ 則由(3.5)和(3.6)可以得到 $K_p$ 、 $\omega_p$ 和 $\omega_z$ 之關係式為：

$$\begin{cases} K_p = \omega_c \\ \omega_p = g \omega_c \\ \omega_z = \frac{K_I}{K_p} = \frac{\omega_c}{g} \end{cases} \quad (3.7)$$

式(3.7)的關係式可知控制器參數設計 $K_p$ 、 $K_I$ 以及 $\omega_p$ 可完全藉由調整適當的參數 $g$ 和 $\omega_c$ 來決定，且所對應的相位裕度可以簡化為：

$$PM = \tan^{-1}(g) - \tan^{-1}\left(\frac{1}{g}\right) = \tan^{-1}\left(\frac{g^2 - 1}{2g}\right) \quad (3.8)$$

式(3.8)中餘切函數為一個遞增的函數且 $(g^2 - 1)/2g$ 也是一個 $g$ 的遞增函數，因此相位裕度對於 $g$ 的變動為嚴格遞增函數，因為：

$$\frac{d}{dg}\left(\frac{g^2 - 1}{2g}\right) = \frac{g^2 + 1}{2g^2} > 0 \quad (3.9)$$

式(3.8)的關係可用圖 3.2 表示，由圖中得知當 $g$ 值越大則系統的相位裕度也將越大，這是因為參數 $g$ 主要關係著 $\omega_p$ 和 $\omega_z$ 的值，當 $g$ 越大時低通濾波器造成的極點越遠而控制器之零點則越靠近原點所以系統的相位裕度也就越大。相位裕度是關係著系統的穩定度，太小的相位裕度可能因為干擾而導致系統不穩定，過大的相位裕度則對於系統沒甚麼特別的意義，一般系統的相位裕度大約都是建議介於 30 度至 60 度之間，在建議的相位裕度區間內參數 $g$ 可調整之範圍為 $1.732 < g < 3.373$ 之間。

圖 3.2 參數  $g$  和相位裕度之關係圖

### 3.1.2 比例積分回授控制系統的暫態響應之分析

鎖相迴路之暫態的性能要求是在系統發生相位或頻率變化時快速地達到相位和頻率的穩定追蹤效果，因此系統穩定時間的快慢是鎖相迴路最重要的暫態響應要求。為探討比例積分回授控制的參數對於暫態響應之影響，將(3.7)代入(3.1)中則系統之開路轉移函數改寫為：

$$G(s) = \frac{g\omega_c^2 s + \omega_c^3}{s^2(s + g\omega_c)} \quad (3.10)$$

由(3.10)式可知輸入相位和輸出預估相位之閉迴路轉移函數為

$$\begin{aligned} \frac{\tilde{\Phi}_1^+(s)}{\Phi_1^+(s)} &= \frac{g\omega_c^2 s + \omega_c^3}{s^3 + g\omega_c s^2 + g\omega_c^2 s + \omega_c^3} \\ &= \frac{\omega_c^2 [(2\zeta + 1)s + \omega_c]}{(s + \omega_c)[s^2 + 2\zeta\omega_c s + \omega_c^2]}, \quad g = 2\zeta + 1 \end{aligned} \quad (3.11)$$

當輸入相位發生步階變化如(3.12)，則輸出之預估相位的響應將為(3.13)所示。

$$\Phi_1^+(s) = \frac{A}{s} \quad (3.12)$$

$$\tilde{\Phi}_1^+(s) = \frac{A\omega_c^2 [(2\zeta + 1)s + \omega_c]}{s(s + \omega_c)[s^2 + 2\zeta\omega_c s + \omega_c^2]} \quad (3.13)$$

將(3.13)取反拉式轉換後可以得到在時域上的表示式，由不同阻尼係數的範圍分別表示為以下三種：

當  $\zeta < 1$  時輸出相位的預估函數為：

$$\tilde{\phi}_1^+(t) = A \left\{ e^{-t} + \frac{\zeta}{1-\zeta} e^{-\omega_c t} - \frac{1}{1-\zeta} e^{-\omega_c t} \cos \left[ \left( \omega_c \sqrt{1-\zeta^2} \right) t \right] \right\} \quad (3.14)$$

當  $\zeta = 1$  時輸出相位的預估函數為：

$$\tilde{\phi}_1^+(t) = A \{ e^{-t} - e^{-\omega_c t} - \omega_c t e^{-\omega_c t} + 2\omega_c^2 t^2 e^{-\omega_c t} \} \quad (3.15)$$

當  $\zeta > 1$  時輸出相位的預估函數為：

$$\tilde{\phi}_1^+(t) = A \left\{ e^{-t} + \frac{1}{1-\zeta} \zeta e^{-\omega_c t} - \frac{1}{2} e^{-(\zeta+\sqrt{\zeta^2-1})\omega_c t} - \frac{1}{2} e^{-(\zeta-\sqrt{\zeta^2-1})\omega_c t} \right\} \quad (3.16)$$

方程式(3.14)至(3.16)發現無論阻尼係數的值為多少系統的收斂速度和增益穿越頻率  $\omega_c$  有很大的直接關係，越大的  $\omega_c$  造成系統越快速的收斂速度。圖 3.3 與圖 3.4 為線性化後增益穿越頻率為 27 Hz 鎮相迴路系統相位發生單位步階變化時不同的阻尼係數對於系統之穩定時間和最大超越量之影響，可以發現主要影響系統響應速度的為增益穿越頻率，但當阻尼係數小於 0.5 時因為系統過於震盪，所以其穩定時間明顯較慢，且阻尼係數  $\zeta > 0.7$  後系統的穩定時間因響應速度變慢而上升。系統的最大超越量則是隨阻尼係數越大而降低，當阻尼係數介於 0.5 至 1 之間時是較好的選擇區間。

圖 3.3 阻尼係數對穩定時間之影響

圖 3.4 阻尼係數對最大超越量之影響

### 3.1.3 比例積分回授控制高頻雜訊抑制能力之分析

增益穿越頻率除了影響整個系統反應速度，同時也關係著鎖相迴路系統對於高頻雜訊的抑制能力，當增益穿越頻率越高時雖然系統的響應速度會越快，但高頻雜訊的抑制能力便會越差。探討高頻雜訊的輸入對於輸出之關係可以了解不同增益穿越頻率的影響，由圖 3.1 可以得知高頻雜訊輸入對於輸出估測相位的轉移函數為：

$$G_d(s) = \frac{\tilde{\Phi}_1^+(s)}{\tilde{\nu}_q(s)} = \frac{g\omega_c^2 s + \omega_c^3}{s^3 + g\omega_c s^2 + g\omega_c^2 s + \omega_c^3} \quad (3.17)$$

圖 3.5 表示增益穿越頻率為 25 Hz 時開迴路轉移函數和高頻雜訊之轉移函數的波德圖，圖中可知系統的開路轉移函數與高頻雜訊之轉移函數在高頻率的時候頻率與增益間的關係兩者間的效果是相同的，因此對於高頻雜訊其振幅的衰減可以由系統之開路轉移函數的近似結果得到：

$$\text{atten}_{\omega_h} = |G_{ol}(j\omega_h)| \approx -20\log \frac{\omega_h}{\omega_c} - 20\log \frac{\omega_h}{\omega_p} \quad (3.18)$$

圖 3.5 開路轉移函數和干擾的轉移函數之波德圖

### 3.6 阻尼係數對高頻抑制能力和之影響

由於電網中換相器的特性以及雙通用積分器是利用瞬時對稱分量法作為消去不平衡故障的方式，所以第一個諧波真正影響到鎖相迴路的頻率為負五倍或正七倍的基頻，且由於帕克轉換的關係實際上進入系統中的雜訊頻率為電網基頻的正六倍和負六倍，以台灣電網的頻率 60 Hz 為例，則第一個高頻諧波的頻率為  $\pm 360$  Hz。圖 3.6 為當系統的增益穿越頻率為 27 Hz 時對於正六倍基頻雜訊的抑制效果，越小的阻尼係數相當於系統的極點越接近原點，對於高頻的抑制效果越好。另外增益穿越頻率的高低也影響著系統

高頻抑制的能力但同時間也會影響著系統響應的快慢，不過這是一個無法兼顧兩者要求的兩難狀況，因此增益穿越頻率的選擇必須視系統的要求來決定。

### 3.1.4 比例積分回授控制穩態誤差之分析

最後探討比例積分回授對於輸入發生單位步階或單位斜坡變化時其穩態誤差的影響，利用終值定理可以得到其穩態誤差為：

$$\begin{aligned} E_{step} &= \lim_{s \rightarrow 0} \left( s * \frac{1}{1 + G(s)} * U(s) \right) \\ &= \lim_{s \rightarrow 0} \left( s * \frac{s^2(s + g\omega_c)}{s^3 + g\omega_c s^2 + g\omega_c^2 s + \omega_c^3} * \frac{1}{s} \right) = 0 \end{aligned} \quad (3.19)$$

$$\begin{aligned} E_{ramp} &= \lim_{s \rightarrow 0} \left( s * \frac{1}{1 + G(s)} * R(s) \right) \\ &= \lim_{s \rightarrow 0} \left( s * \frac{s^2(s + g\omega_c)}{s^3 + g\omega_c s^2 + g\omega_c^2 s + \omega_c^3} * \frac{1}{s^2} \right) = 0 \end{aligned} \quad (3.20)$$

由於比例積分回授控制的開迴路轉移函數為一個型態二之系統，不論是相位的步階變化或頻率的步階變化系統都可以達到沒有誤差的追蹤。

從以上最大相位設計的探討中可知雙通用積分器之參數及比例控制器之參數對於系統暫態響應、高頻雜訊抑制能力以及穩態誤差的影響。利用比例積分控制器設計的好處在於簡單而且分析不複雜，其比例積分回授控制的效果不論是暫態響應或穩態響應的效果都十分良好。

## 3.2 雙通用積分器鎖相迴路利用虛擬微分回授控制之分析

虛擬微分回授(Pseudo-derivative feedback, PDF)的控制方法[26]最早是由 R. M. Phelan 於 1977 年時提出，這種控制方式雖然沒有像比例積分回授控制那般常見，但其暫態響應的效果十分良好，而且結構也很簡單。不過虛擬微分回授制是利用結構上的改變使得系統擁有微分特性的好處，但是實際上並不會因為零點的關係而使得系統有較大的最大超越量以及較差的高頻抑制效果。

### 3.2.1 虛擬微分回授控制和比例積分回授控制的比較

由於虛擬微分回授控制和比例積分回授控制的結構以及系統的性質十分相似，所以常會將此兩種控制方法做比較，本小段將比較這種兩種控制方式分別對一個相同的一階系統做控制，簡略地闡述兩者系統以及單位步階響應的差異，在[27]和[28]中則有較為詳盡的分析和比較。圖 3.7 為利用比例積分回授控制一個簡單之一階的受控系統，由圖中可以得知此系統之閉迴路轉移函數為

$$\frac{Y(s)}{U(s)} = \frac{K_p s + K_I}{s^2 + K_p s + K_I} \quad (3.21)$$

圖 3.7 比例積分回授控制簡單的一階系統

由轉移函數(3.21)可以得知系統轉移函數中分子和分母的係數可藉由調整 $K_p$ 和 $K_I$ 而改變，一旦決定系統所需之極點位置時，其零點的位置後也隨之固定。由於比例積分回授控制的系統中存在了一個零點，而此零點使得整個系統有別於標準的二階系統，若利用標準二階系統來分析則系統之阻尼係數和自然無阻尼頻率為：

$$\xi = \frac{K_p}{2\sqrt{K_I}} \quad (3.22)$$

$$\omega_n = \sqrt{K_I} \quad (3.23)$$

在標準二階系統的轉移函數中，系統的單位步階響應的反應速率和自然無阻尼頻率成正比的關係，而且系統的阻尼係數決定暫態響應中最大超越量的大小，越大阻尼係數則代表越小的最大超越量。但因為比例積分回授控制的系統擁有一個零點，使得其暫態響應和標準的二階系統的響應並不相同。零點在此系統中相當於是對誤差做微分的效果，因

此對其暫態響應的影響是增加系統的最大超越量並且加快系統的上升時間，而對穩定時間則沒有任何顯著的影響，但當系統在阻尼係數超過一的條件下，最大超越量依然會存在於暫態響應之中，並無法像標準的二階系統般令最大超越量降至零，這是利用比例積分回授控制一個明顯的缺點。

將虛擬微分回授控制運用於一樣的一階受控系統，則其系統方塊圖如圖 3.8 所示，並且系統的輸入和輸出之閉迴路轉移函數為：

$$\frac{Y(s)}{U(s)} = \frac{K_I}{s^2 + K_D s + K_I} \quad (3.24)$$

圖 3.8 虛擬微分回授控制簡單的一階系統

由(3.24)可知系統的閉迴路轉移函數一樣是改變 $K_D$ 和 $K_I$ 來決定轉移函數的極點位置，和比例積分回授控制的轉移函數差別只在於分子項並沒有零點，而且此轉移函數為標準的二階系統，由標準的二階系統分析可以得到其阻尼係數和自然無阻尼頻率為：

$$\xi = \frac{K_D}{2\sqrt{K_I}} \quad (3.25)$$

$$\omega_n = \sqrt{K_I} \quad (3.26)$$

虛擬微分回授控制的暫態響應和比例積分回授控制有些類似的特性，自然無阻尼頻率一樣關係著系統暫態響應的速度，阻尼係數也一樣決定系統最大超越量的大小。由於轉移函數的分子並不存在一個零點，因此由標準二階系統的分析得知當系統的阻尼係數 $\xi \geq 1$ 時系統的最大超越量為零。

當這兩個系統的開路轉移函數在相同的增益穿越頻率的條件下，比較虛擬微分回授控制和比例積分回授控制對於單位步階響應的暫態關係之差異。由圖 3.9 得知阻尼係數

對於穩定時間和最大超越量的影響。當阻尼係數增加時不論是比例積分回授控制或虛擬微分回授控制其最大超越量皆有逐漸變小的趨勢，但僅有虛擬微分回授控制在阻尼係數大於 1 後最大超越量降為零。穩定時間的影響則是當阻尼係數約小於 0.6 時，兩者的穩定時間皆隨之下降，但當大於 0.6 後比例積分回授控制其穩定時間有逐漸增加的趨勢，而虛擬微分回授控制則是依然隨著阻尼係數增加而持續漸少，直到當阻尼係數大於 1 後穩定時間才大約維持在一個固定的值。

圖 3.9 阻尼係數對穩定時間及最大超越量之影響

除了用穩定時間和最大超越量比較兩種控制方式的優劣外，也利用誤差絕對值積分(Integer Absolute Error, IAE)和誤差平方積分(Integer Square Error, ISE)作為指標，當這兩個指標的數值越小時代表著輸出和輸入間的誤差越小，控制器的效果也就越好，其中誤差絕對值積分和誤差平方積分的公式為：

$$IAE = \int_0^t |e(t)| dt \quad (3.27)$$

$$ISE = \int_0^t e^2(t) dt \quad (3.28)$$

圖 3.10 是比例積分回授控制和虛擬微分回授控制的阻尼係數對於這兩種指標的比較，由圖中可以發現誤差絕對值積分和誤差平方積分兩個指標的數值皆隨著阻尼係數的增加而降低，在誤差平方積分的指標中兩者的結果十分接近，不過在誤差絕對值積分的指標中虛擬微分回授控制的效果是較比例積分回授控制擁有較好的結果。

圖 3.10 阻尼係數對 IAE 及 ISE 之影響

另外因為電網上存在許多高頻諧波的干擾，虛擬微分回授控制和比例積分回授控制兩者間對於高頻干擾輸入的分析是值得探討的問題。由兩個系統的方塊圖中得到雜訊干擾對於輸出之轉移函數分別為

$$\left. \frac{Y(s)}{D(s)} \right|_{U(s)=0} = G_{d\_PI}(s) = \frac{K_p s + K_I}{s^2 + K_p s + K_I} \quad (3.29)$$

$$\left. \frac{Y(s)}{D(s)} \right|_{U(s)=0} = G_{d\_PDF}(s) = \frac{K_I}{s^2 + K_D s + K_I} \quad (3.30)$$

當  $s = j\omega_h$  時可以得到系統對於高頻雜訊的增益抑制能力，其中  $\omega_h$  為高頻雜訊之頻率：

$$\text{atten}_{\omega_h} = 20 \log(|G_{d\_PI}(j\omega_h)|) = 20 \log \left( \frac{\sqrt{K_I^2 + K_p^2 \omega_h^2}}{\sqrt{(K_I - \omega_h^2)^2 + K_p^2 \omega_h^2}} \right) \quad (3.31)$$

$$\text{atten}_{\omega_h} = 20 \log(|G_{d\_PDF}(j\omega_h)|) = 20 \log \left( \frac{K_I}{\sqrt{(K_I - \omega_h^2)^2 + K_D^2 \omega_h^2}} \right) \quad (3.32)$$

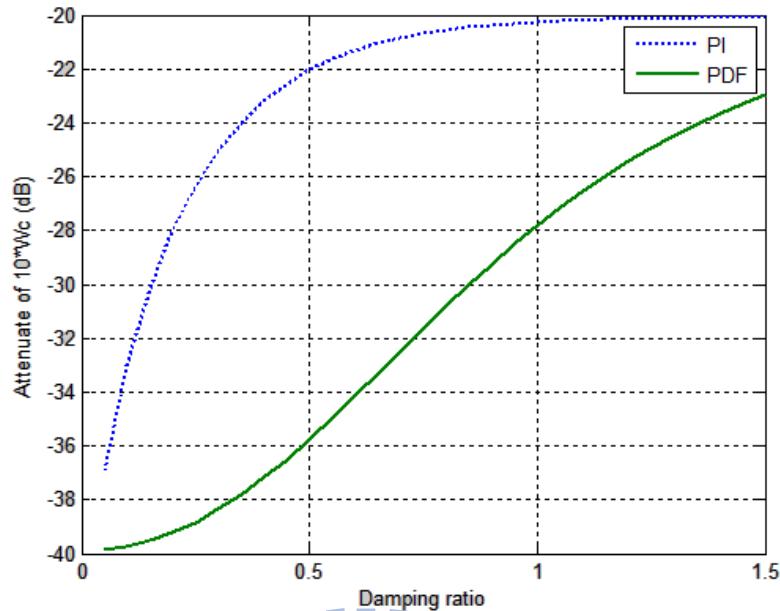

圖 3.11 為兩個系統的開路轉移函數有相同的增益穿越頻率時，其系統對於頻率為增益穿越頻率之十倍的高頻訊號之抑制效果。圖中顯示不論是哪一種控制的方式當阻尼係數越大時高頻雜訊抑制之效果便會越差，在相同的阻尼係數下時虛擬微分回授控制的高頻雜訊的抑制效果則是較優秀。

圖 3.11 阻尼係數對高頻抑制能力之影響

由以上的分析可知虛擬微分回授控制的暫態響應以及高頻抑制的效果較比例積分回授控制好，且在誤差絕對值積分和誤差平方積分的兩種指標比較中，雖然誤差平方積分兩者的差距是十分微小，但在誤差絕對值積分中的表現較為優良。這些代表虛擬微分回授控制比起比例積分控制在各方面都比較突出，不過在系統穩態誤差的表現上比例積分回授控制較好，因為比例積分回授控制為一個型態二的系統，所以不論是步階或是斜坡的穩態誤差都是零，但虛擬微分回授控制是型態一的系統，當系統發生斜坡變化時穩態誤差將固定為一個非零的常數。

### 3.2.2 虛擬微分回授控制穩定度之分析

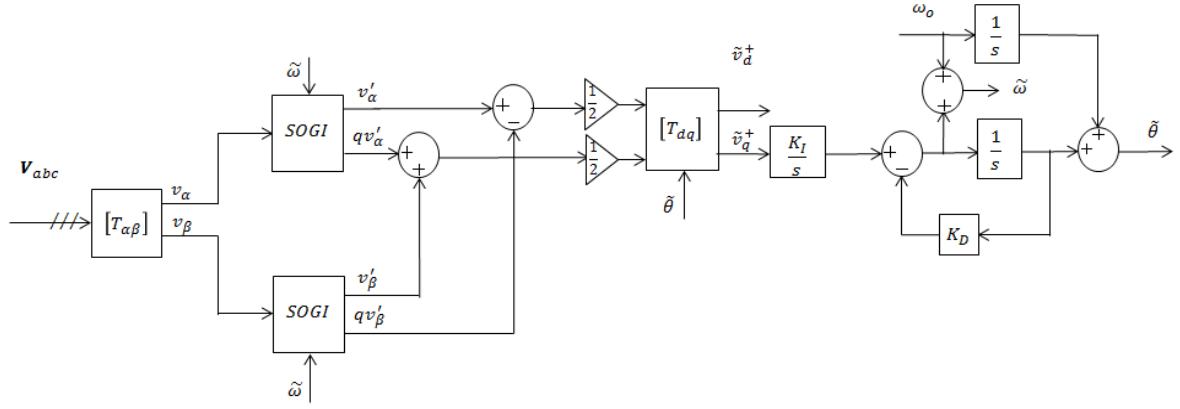

若是利用虛擬微分回授控制取代原來的比例積分回授控制，由前一小段中簡單系統的分析可以了解，比例積分回授控制因為其系統的分子有一個零點的關係，而造成的較大的最大超越量及較差的高頻抑制能力。虛擬微分回授控制的系統並沒有受到零點的影響，因此和比例積分回授控制相比可以擁有較小的最大超越量和較佳的高頻抑制能力。雙通用積分器鎖相迴路利用虛擬微分回授控制之系統方塊圖如圖 3.12 所示。當系統處於接近相位鎖定，且系統經過線性化以及電壓峰值的歸一化後可以得到如圖 3.13 所表示的系統方塊圖。

圖 3.12 利用 PDF 之雙通用積分器鎖相迴路系統方塊圖

圖 3.13 線性化之系統方塊圖

由圖 3.13 之系統方塊圖在忽略高頻雜訊的干擾下，得到輸入相位和預估之輸出相位的開迴路轉移函數為：

$$G(s) = \frac{\omega_p K_I}{s(s + \omega_p)(s + K_D)} \quad (3.33)$$

當系統的頻率為增益穿越頻率  $s = j\omega_c$  時相位裕度以及系統增益的關係為：

$$PM = 90 - \tan^{-1}\left(\frac{\omega_c}{\omega_p}\right) - \tan^{-1}\left(\frac{\omega_c}{K_D}\right) \quad (3.34)$$

$$|G(j\omega_c)| = \frac{\omega_p K_I}{\omega_c \sqrt{\omega_c^2 + \omega_p^2} \sqrt{\omega_c^2 + K_D^2}} = 1 \quad (3.35)$$

式(3.34)可以發現虛擬微分回授控制的相位由於沒有零點的關係，相位裕度並不會有極值的存在，為使系統穩定因此參數  $K_D$  可以調整的範圍將隨著低通濾波器的截止頻率  $\omega_p$  不同而改變，越大的截止頻率使得虛擬微分回授控制的參數  $K_D$  調整的範圍越狹窄。

### 3.2.3 虛擬微分回授控制暫態響應之分析

為分析虛擬微分回授控制的參數，將分別探討其微分增益和積分增益對於系統的影響，從方程式(3.33)可以發現影響相位裕度的兩個參數 $\omega_p$ 和 $K_D$ 直接影響了系統兩個極點的位置，而且也互相影響著彼此可以變動的範圍。為了簡化分析以利於比較兩種參數對系統的影響，假設低通濾波器的截止頻率滿足 $\omega_p = g\omega_c$ 的關係，並且同時微分增益也滿足 $K_D = a\omega_c$ 的假設，則相位裕度的關係式(3.34)改為：

$$PM = 90 - \tan^{-1}\left(\frac{1}{g}\right) - \tan^{-1}\left(\frac{1}{a}\right) \quad (3.36)$$

並且由系統的增益關係式(3.37)得到 $K_I$ 參數：

$$K_I = \omega_c^2 \sqrt{\left(1 + \frac{1}{g^2}\right)(1 + a^2)} \quad (3.37)$$

在固定增益穿越頻率和低通濾波器的截止頻率的情況下，由截止頻率參數 $g$ 利用方程式(3.36)可以得到參數 $a$ 的適當範圍，以 $g = 2.4$ 時為例係數 $a$ 介於 1.3089 和 7.7206 之間時，相位裕度才滿足介於 30 度和 60 度之間的要求。

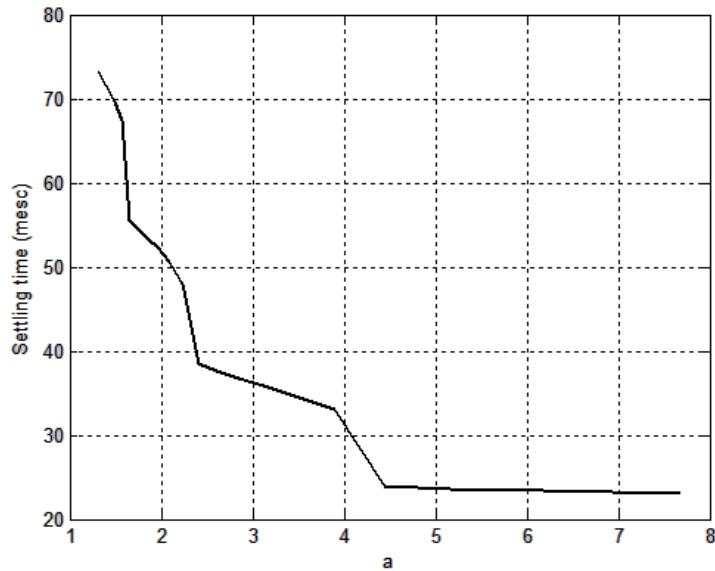

圖 3.14 和圖 3.15 所示為虛擬微分回授控制系統線性化後，當系統固定低通濾波器之截止頻率參數 $g$ 為 2.4 以及開路增益穿越函數為 27 Hz 時，微分增益 $a$ 值的改變對系統單位步階響應的穩定時間和最大超越量之關係圖。由圖中可以發現當  $a$ 值越大時系統的穩定時間和最大超越量皆越小，由於改變微分增益參數 $a$ 即代表著改變 $K_D$ 之極點位置，亦即當 $a$ 值越大時相當於虛擬微分回授控制中由 $K_D$ 影響的極點將越遠離原點，使得低通濾波器之截止頻率 $\omega_p$ 將對於系統的增益穿越頻率和暫態響應的影響就越大。

圖 3.14 固定  $g$  和增益穿越頻率下之  $a$  對穩定時間之影響

圖 3.15 固定  $g$  和增益穿越頻率  $a$  對最大超越量之影響

由於雙通用積分器等效之低通濾波器截止頻率的改變也會對系統單位步階的暫態響應有所影響，圖 3.16 和 3.17 為系統固定增益穿越頻率為 27 Hz，不同的低通濾波器之截止頻率參數  $g$  造成虛擬微分回授控制系統的單位步階響應之穩定時間和最大超越量之影響。由圖中可以發現為滿足相位裕度的要求因此  $K_D$  可以調整的範圍將隨著參數  $g$  的變大而變窄，參數  $g$  對系統暫態響應的影響和  $K_D$  造成的影響相比沒有那麼劇烈的差異，不過系統的單位步階響應之穩定時間和最大超越量在相同的微分增益下將隨著低通濾波器的截止頻率變大而減少。

圖 3.16 固定增益穿越頻率不同的 $g$ 和 $a$ 對穩定時間的影響

圖 3.17 固定增益穿越頻率不同的 $g$ 和 $a$ 對最大超越量的影響

### 3.2.4 虛擬微分回授控制高頻雜訊抑制能力之分析

系統的開路轉移函數之增益穿越頻率對於虛擬微分回授控制的影響和比例積分控制的情形類似，當增益穿越頻率越大時系統的響應速度將越快，設計上本應是選取越大的增益穿越頻率，但增益穿越頻率也關係著高頻雜訊干擾的抑制能力。由本節第一段中可得知相同的受控系統，虛擬微分回授控制的高頻抑制能力較比例積分回授控制好。從

系統之線性化方塊圖(3.13)得到當相位輸入為零時，虛擬微分回授控制之高頻雜訊輸入對於輸出之轉移函數為：

$$G_d(s) = \frac{\tilde{\Phi}_1^+(s)}{\tilde{v}_q(s)} = \frac{\omega_p K_I}{s^3 + (K_D + \omega_p)s^2 + K_D\omega_p s + \omega_p K_I} \quad (3.38)$$

由式(3.38)可知除了增益穿越頻率外，低通濾波器的截止頻率與微分增益的改變也影響著轉移函數中極點的位置與增益的大小，所以高頻抑制能力需要分別探討兩個參數改變時造成的影响。

圖 3.18 為系統的開路轉移函數在擁有相同的增益穿越頻率的情況下，高頻抑制能力對於不同的 $g$ 值和 $a$ 值下之結果，由圖中發現不論在哪種情況下當 $a$ 值越小時系統高頻雜訊的衰減效果越好，而在相同的 $a$ 值的情況下 $g$ 值越小系統的高頻雜訊抑制能力越好，但越小的 $a$ 值或越大 $g$ 值都會造成系統暫態響應的穩定時間和最大超越量的效果越差。由於 $g$ 值影響著等效之低通濾波器的截止頻率，或著說影響著雙通用積分器的帶通的頻寬，越小的 $g$ 則代表著越窄的頻寬，而越窄的頻寬則是會有較佳的濾波能力。而 $a$ 值則是代表整個系統中 $K_D$ 所影響的另一個極點之位置，當這系統的兩個極點越靠近原點便會增進高頻雜訊的抑制效果。因此關於系統對於高頻抑制的效果和系統暫態響應之間的抉擇問題在虛擬微分回授控制中也是存在的，如何抉擇的參數的值必須視系統的規格要求來決定。

圖 3.18 參數 $g$ 和 $a$ 對系統高頻抑制能力之影響

### 3.2.5 虛擬微分回授控制穩態誤差之分析

最後探討的是虛擬微分回授控制對系統穩態誤差的影響，因為虛擬微分回授控制為型態一的系統，當輸入為單位斜坡響應時其穩態誤差必定會存在一固定的值。由系統之開路轉移函數(3.33)和終值定理可以分別得到輸入為單位步階和單位斜坡變化時之穩態誤差為：

$$\begin{aligned} E_{step} &= \lim_{s \rightarrow 0} \left( s \times \frac{1}{1 + G(s)} \times U(s) \right) \\ &= \lim_{s \rightarrow 0} \left( s * \frac{s(s + \omega_p)(s + K_D)}{s(s + \omega_p)(s + K_D) + \omega_p K_I} \times \frac{1}{s} \right) = 0 \end{aligned} \quad (3.39)$$

$$\begin{aligned} E_{ramp} &= \lim_{s \rightarrow 0} \left( s \times \frac{1}{1 + G(s)} \times R(s) \right) \\ &= \lim_{s \rightarrow 0} \left( s \times \frac{s(s + \omega_p)(s + K_D)}{s(s + \omega_p)(s + K_D) + \omega_p K_I} \times \frac{1}{s^2} \right) = \frac{K_D}{K_I} \end{aligned} \quad (3.40)$$

若將  $K_D = a\omega_c$  以及  $K_I$  的關係式(3.24)代入(3.39)中可以得到

$$E_{ramp} = \frac{a}{\omega_c \sqrt{\left(1 + \frac{1}{g^2}\right)(1 + a^2)}} \quad (3.41)$$

由方程式(3.39)和(3.40)可以得知虛擬微分回授控制的穩態誤差的結果，在相位步階變化的穩態誤差將會在有限時間內收斂至零，而頻率的步階變化將會是收斂至一個常數值，此常數對於系統的參數  $g$ 、 $a$  以及開路轉移函數的增益穿越頻率的改變也都會有所變化，且由(3.41)可以得知增益穿越頻率和其穩態誤差是成反比的關係。圖 3.19 則為頻率發生步階變化時其穩態誤差的值對於兩個參數的影響，由圖中可以看出微分增益及低通濾波器的截止頻率越大，頻率步階響應的穩態誤差也越大。

圖 3.19 參數  $g$  和  $a$  對穩態誤差之影響

由以上的分析可以得知當利用虛擬微分回授控制作用於雙通用積分器鎖相迴路，其系統的暫態響應和比例積分控制器擁有相同的開迴路增益穿越頻率時，最大超越量和穩定時間的效果都比較好，而且系統高頻雜訊的抑制能力在適當的  $g$  值和  $a$  值的情況下效果也較好，唯一的缺點為虛擬微分回授控制在輸入的頻率發生步階變化時其穩態誤差將為一個固定的常數。不過一般電網上頻率的改變和相位改變相比，變化較為緩慢而且發生的機率也較低，而且實際的電網系統若頻率發生過大的變化時會有其他的保護機制以避免整個電網系統的崩潰，因此在鎖相迴路的控制上虛擬微分控制器雖然在頻率變化將會有極小的穩態誤差，但在其暫態響應上的優秀表現值得讓人探討在鎖相迴路上的應用。

### 3.3 自適性調整之比例積分回授控制

雖然虛擬微分回授控制在雙通用積分鎖相迴路的暫態效果有明顯的改善，但最大的缺點在於虛擬微分回授控制的方式無法讓系統頻率發生變化時的穩態誤差為零，即使發生頻率改變的機率與不平衡故障或相位改變相比少了很多，但當系統是注重在穩態誤差的要求時虛擬微分回授控制便無法使用。而比例積分回授控制的系統因為零點的關係而使得上升時間較快速，但也因為零點的微分效果使得系統的暫態響應中最大超越量有較大的情況發生。雖然可以藉由增加比例積分回授控制的阻尼係數讓零點的微分行為減輕

令最大超越量減少但是無法將最大超越量完全消除，而且從第三章第一節分析中可知越大的阻尼係數將會增加系統的穩定時間。若當系統的阻尼係數可以隨著系統估測相位與實際相位間的誤差而做改變，讓系統在誤差變大時提高阻尼係數以降低微分的效益令系統響應速度減緩因而降低響應的最大超越量，利用自適性調整的方式便解決比例積分回授控制中暫態響應的問題。

### 3.3.1 自適性調整的設計與穩定度之分析

由第三章第二節的比例積分回授控制參數分析中，可以發現阻尼係數會同時影響著系統的最大超越量和穩定時間，不過當阻尼係數大於 0.6 後隨著阻尼係數的增大系統的穩定時間雖然會些微的增加，但是系統的最大超越量則明顯的減小，若系統的阻尼係數將隨著誤差大小而改變，可以犧牲些微的穩定時間讓系統有較小的最大超越量，因此將阻尼係數和誤差大小的關係式設計為：

$$\zeta = \zeta_0 + \gamma \cdot |e| = \zeta_0 + \Delta\zeta \quad (3.42)$$

則由方程式(3.42)以及(3.7)之關係式可以得到其他相關的參數為

$$g = 2(\zeta_0 + \Delta\zeta) + 1 = g_0 + \Delta g \quad (3.43)$$

$$\omega_p = \omega_c(g_0 + \Delta g) \quad (3.44)$$

$$\omega_z = \frac{\omega_c}{(g_0 + \Delta g)} \quad (3.45)$$

因此可以得到比例積分控制器的參數可以改寫為：

$$\begin{cases} K_p = \omega_c \\ K_I = \frac{\omega_c^2}{g} = \frac{\omega_c^2}{2(\zeta_0 + \Delta\zeta) + 1} \end{cases} \quad (3.46)$$

利用以上的關係式，在系統相位接近鎖定的條件下，系統線性化的方塊圖如圖 3.20 所示，圖中虛線方塊部分為等效之低通濾波器，其中低通濾波器及積分增益須經由自適性運算單元得到。

圖 3.20 自適性比例積分控制線性化系統方塊圖

由於阻尼係數的改變是以增加的方式做變動，使得系統在暫態的過程中相位裕度會隨著誤差大小而有所變動，但由第三章第一節中可知在比例回授控制中阻尼係數的上升時相位裕度有增加的趨勢，系統最低的相位裕度是發生在系統誤差為零的時候，即原始比例積分回授控制之相位裕度，因此並不會因為自適性調整使得系統發生不穩定的現象。另外由方程式(3.46)可以發現這種自適性的設計在固定系統比例增益 $K_p$ 時當系統處於穩態狀態時，系統可以維持和原本比例積分回授控制時的增益穿越頻率，這將會造成系統碰到高頻雜訊時其抑制的能力會因阻尼係數的上升而有些微的下降，不過由於一般高頻雜訊的電壓震幅都較小所以實際上的影響效果並不嚴重。

圖 3.21 自適性係數對穩定時間的影響

圖 3.22 自適性係數對最大超越量的影響

圖 3.21 和圖 3.22 為自適性調整之阻尼係數對於線性化之系統發生單位步階變化的暫態響應之關係圖，而原本未加裝自適性調整之系統其比例積分回授控制的增益穿越頻率為 27 Hz 且阻尼係數設為 0.707。由圖中可以發現當(3.41)中的  $\gamma$  係數越大時最大超越量會逐漸變小，而穩定時間會隨著  $\gamma$  的上升而增加。

### 3.3.2 自適性調整頻率之分析

1896

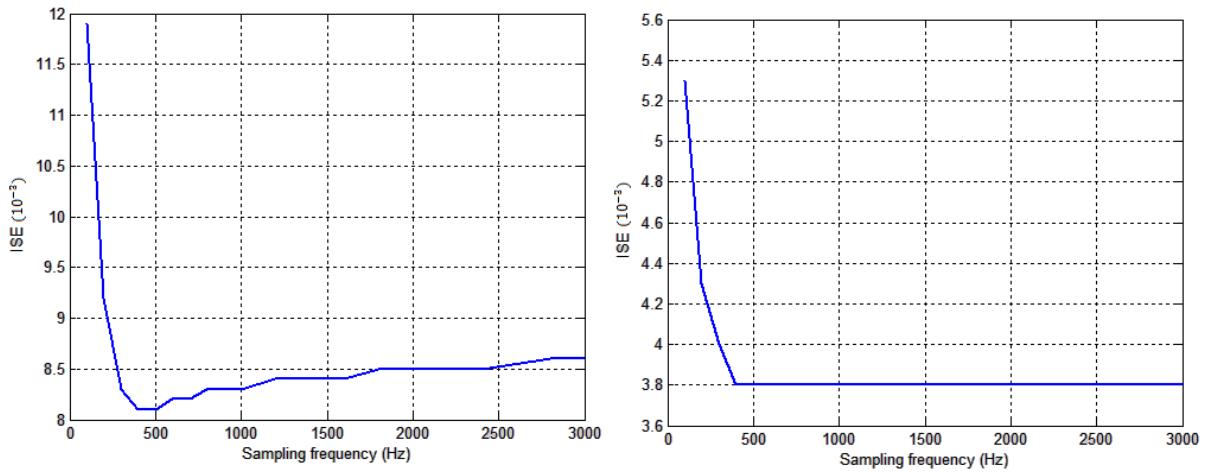

這種自適性調整的方式除了須考慮誤差之係數造成暫態響應的影響，需要多快的頻率來調整系統參數也是一個重要的問題，當調整的頻率太低時自適性控制的效果就不明顯，但越快的調整頻率代表越高的成本。圖 3.23 為在固定  $\gamma$  為 1.5 的條件時不同的取樣頻率對自適性調整效果的影響，圖中藉由當線性化之系統的單位步階變化之誤差絕對值積分和誤差平方積分來分別自適性調整頻率高低之效果的好壞，可以發現當調整的頻率超過 500 Hz 後其效果的改善將會十分的有限，因此可知自適性控制的調整頻率的需求並不用非常高的頻率就可以有良好的效果。

圖 3.23 調整頻率對 IAE 和 ISE 的影響

由以上的結論可以發現當比例積分回授控制的參數已經決定的情況下，利用自適性調整的機制將系統的阻尼係數隨著輸入相位和估測相位的誤差大小而改變時，當誤差大的時候藉由增加阻尼係數讓最大超越量降低，雖然會喪失系統上升時間的速度，但其穩定時間比起有相同大小之最大超越量的比例積分回授控制來得佳。另外自適性調整的更新頻率也並不是需要有很高的要求，大約在 500 Hz 的頻率便可以有效地降低調整頻率過慢所造成的影響，因此自適性調整的方式在控制上的成本並不會需要額外付出太大的負擔，就可以讓整個比例積分回授控制之鎖相迴路的暫態響應有不錯的改善效果。

### 3.4 Q 參數化設計高階之控制器

前兩小節之設計都是利用一階控制器並且希望讓鎖相迴路的系統響應可以達到良好之效果，雖然一階的控制器在參數設計上較為簡單以及所需的成本較低，且由於大多數的控制系統上控制器也多為一階的系統，所以設計上的資料和經驗也比較豐富。高階的控制器在設計上因為參數的自由度較多而使得設計與分析上較為困難，但也因為高階控制器可以設計之參數較多，其高階控制器系統的響應比起一階的控制器可以有較多的變化和可能性，本節將試著設計並且探討高階控制器運於鎖相迴路系統時響應的情形。

### 3.4.1 Q 參數化設計之假設

為探討高階控制器設計的可能，此論文中利用最佳化設計中設計閉迴路轉移函數的 Q 參數化(Q parameterization)方式[29]，此方法和前幾節最大的不同是要先設計出系統所需求之閉迴路轉移函數，再由設計出的閉迴路轉移函數推得出所需控制器之極點以及零點和增益的關係。若  $P(s)$  為受控系統之轉移函數，其中  $P(s)$  為一個真分數形式之轉移函數但極點不一定皆為穩定時，則假設受控系統須滿足下列要求：

- (1)  $P(s)$  的轉移函數必須不為  $s$  的零函數。

- (2) 受控系統之轉移函數和其倒數兩者間沒有共同的不穩定極點。

則整個系統之閉迴路轉移函數可表示為

$$H(s) = C(s) \times P(s) \times (1 + C(s)P(s))^{-1} = P(s) \times Q(s) \quad (3.47)$$

而控制器之轉移函數可以表示為：

$$C(s) = \frac{Q(s)}{(1 - P(s) \times Q(s))} \quad (3.48)$$

當利用 Q 參數化方式設計時閉迴路系統必須為穩定，且  $Q(s)$  必須滿足下列假設：

- (a)  $Q$  之轉移函數必須為有理函數。

- (b)  $Q$  必須有零點放置在受控系統所擁有的每一個不穩定之極點。

- (c) 對於受控系統或  $1 - P(s)Q(s)$  之不穩定極點必須被消去。

當  $p_l$  表示為受控系統之不同的不穩定極點時，可以將受控系統之轉移函數利用部分分式展開並且表示為：

$$P(s) = P_s(s) + \sum_{l=1}^n \frac{r_l}{s - p_l} \quad (3.49)$$

由假設(b)之條件因為  $Q(s)$  在  $p_l$  必須存在零點因此可以得到

$$Q(p_l) = 0, l = 1, 2, \dots, n \quad (3.50)$$

而且由假設(c)中的  $1 - P(s)Q(s)$  也必須消掉不穩定極點的條件可以得知

$$Q'(p_l) = \frac{1}{r_l}, l = 1, 2, \dots, n \quad (3.51)$$

以上的假設皆為在利用 Q 參數化設計時必須滿足的條件，而且 Q 參數化設計的雙通用積分器鎖相迴路之高階控制器在閉迴路的頻率響應分析上將會有很好的反應結果。雖然高階之控制器時階數越高在分析和設計就越趨於複雜和困難，而且成本也會隨之增加，但或許在合適的階數下控制器會擁有較比例回授控制好的效果。此節將會以分析分子與分母階數為二階之控制器為例，探討高階控制器對雙通用積分器鎖相迴路系統的影響。

### 3.4.2 Q 參數化參數設計之分析

本段將以設計分子和分母皆為兩次多項式之控制器為例，當滿足前一小段之假設的條件時可以由先前分析得知線性化的受控系統為(3.52)式，則所設計之 Q 的轉移函數表示如(3.53)所示，假設受控系統中的等效低通濾波器之極點  $\omega_p$  為已知，則利用 Q 參數化所設計之轉移函數的變數共有七個變數分別為增益、四個極點和三個零點。

$$P(s) = \frac{\omega_p}{s(s + \omega_p)} = \frac{1}{s} + \frac{-1}{(s + \omega_p)} \quad (3.52)$$

$$Q(s) = \frac{Ks(s + \omega_p)(s + z_1)(s + z_2)}{(s + p_1)(s + p_2)(s + p_3)(s + p_4)} \\ = \frac{K(s^4 + N_2s^3 + N_1s^2 + N_0s)}{s^4 + D_3s^3 + D_2s^2 + D_1s + D_0} \quad (3.53)$$

其中(3.52)中展開成多項式形式的分子和分母各階之係數如下表所示：

表 3-1 Q 參數分母之係數

|       |                                                       |

|-------|-------------------------------------------------------|

| $D_0$ | $p_1p_2p_3p_4$                                        |

| $D_1$ | $p_1p_2p_3 + p_1p_2p_4 + p_1p_3p_4 + p_2p_3p_4$       |

| $D_2$ | $p_1p_2 + p_1p_3 + p_1p_4 + p_2p_3 + p_2p_4 + p_3p_4$ |

| $D_3$ | $p_1 + p_2 + p_3 + p_4$                               |

表 3-2 Q 參數分子之係數

|       |                                      |

|-------|--------------------------------------|

| $N_0$ | $z_1z_2\omega_p$                     |

| $N_1$ | $z_1z_2 + \omega_pz_1 + \omega_pz_2$ |

| $N_2$ | $z_1 + z_2 + \omega_p$               |

由(3.47)和(3.48)得到系統之開迴路轉移函數和控制器之函數分別為：

$$H(s) = P(s) \times Q(s) = \frac{K\omega_p(s+z_1)(s+z_2)}{(s+p_1)(s+p_2)(s+p_3)(s+p_4)} \quad (3.54)$$

$$C(s) = \frac{Ks(s+\omega_p)(s+z_1)(s+z_2)}{s^4 + D_3s^3 + D_2s^2 + D_1s + D_0 - K\omega_p[s^2 + (z_1+z_2)s + z_1z_2]} \quad (3.55)$$

Q之轉移函數必須滿足前一小段中(c)之假設，所以(3.53)對s微分後得到：

$$Q'(s) = \frac{K(4s^3 + 3N_2s^2 + 2N_1s + N_0)}{s^4 + D_3s^3 + D_2s^2 + D_1s + D_0} - \frac{K(s^4 + N_2s^3 + N_1s^2 + N_0s)(4s^3 + 3D_3s^2 + 2D_2s^1 + D_1)}{(s^4 + D_3s^3 + D_2s^2 + D_1s + D_0)^2} \quad (3.56)$$

式(3.56)須滿足(3.51)之條件，將s=0和s=-\omega\_p代入可以得到：

$$Kz_1z_2\omega_p = p_1p_2p_3p_4 \quad (3.57)$$

$$K\omega_p = (\omega_p^2 - D_3\omega_p + D_2) \quad (3.58)$$

並且將(3.57)之關係式代入(3.55)中則控制器之轉移函數後可以改寫為

$$C(s) = \frac{K(s+\omega_p)(s+z_1)(s+z_2)}{s^3 + D_3s^2 + D_2s + D_1 - K\omega_p[s + (z_1+z_2)]} \quad (3.59)$$

另外因為滿足(3.58)的關係所以控制器中位於\omega\_p的零點也將會被消除掉，則此控制器之分子和分母都將會為二階之多項式。當系統要求斜坡變化之穩態誤差必須為零時，則整個系統之開迴路轉移函數必須為型態二之系統，即需有兩個在原點的極點，所以控制器有一個極點必須被放置在原點上，才可以達到系統對於斜坡之變化沒有穩態誤差的需求。在滿足這此條件下由(3.59)可以得到：

$$D_1 = K\omega_p(z_1 + z_2) \quad (3.60)$$

因此設計Q參數之轉移函數時利用(3.57)、(3.58)以及(3.60)之關係式得到零點和增益對於極點之關係，且讓Q參數化設計之控制器的自由度減少為四維，即為四個極點之位置。藉由不同的極點位置可以設計出讓鎖相迴路擁有良好暫態響應之控制器。本論文中在以下兩小段Q之設計分析上僅用一個維度之自由度以及有兩個維度之自由度來做分析，試圖在不同維度下瞭解Q所設計之極點對於系統之暫態響應以及高頻雜訊干擾的抑制能力做比較。

### 3.4.3 Q 參數化一維自由度之設計與分析

當 Q 參數化設計之轉移函數中四個極點皆被固定在同一位置時，整個 Q 參數化的設計將降至只有一個自由度的變化，即 Q 之轉移函數：

$$Q(s) = \frac{Ks(s + \omega_p)(s + z_1)(s + z_2)}{(s + p_1)^4} \quad (3.61)$$

則控制器須滿足(3.57)、(3.58)以及(3.60)之關係式並且經整理後可得

$$C(s) = \frac{Q(s)}{1 - P(s)Q(s)} = \frac{(s + z_1)(s + z_2)}{s(s + 4p_1 - \omega_p)} \quad (3.62)$$

式(3.62)可知由於控制器必須處於穩定所以極點和零點皆必須在 s 平面之左半平面，即：

$$p_1 \geq \frac{\omega_p}{4} \quad (3.63)$$

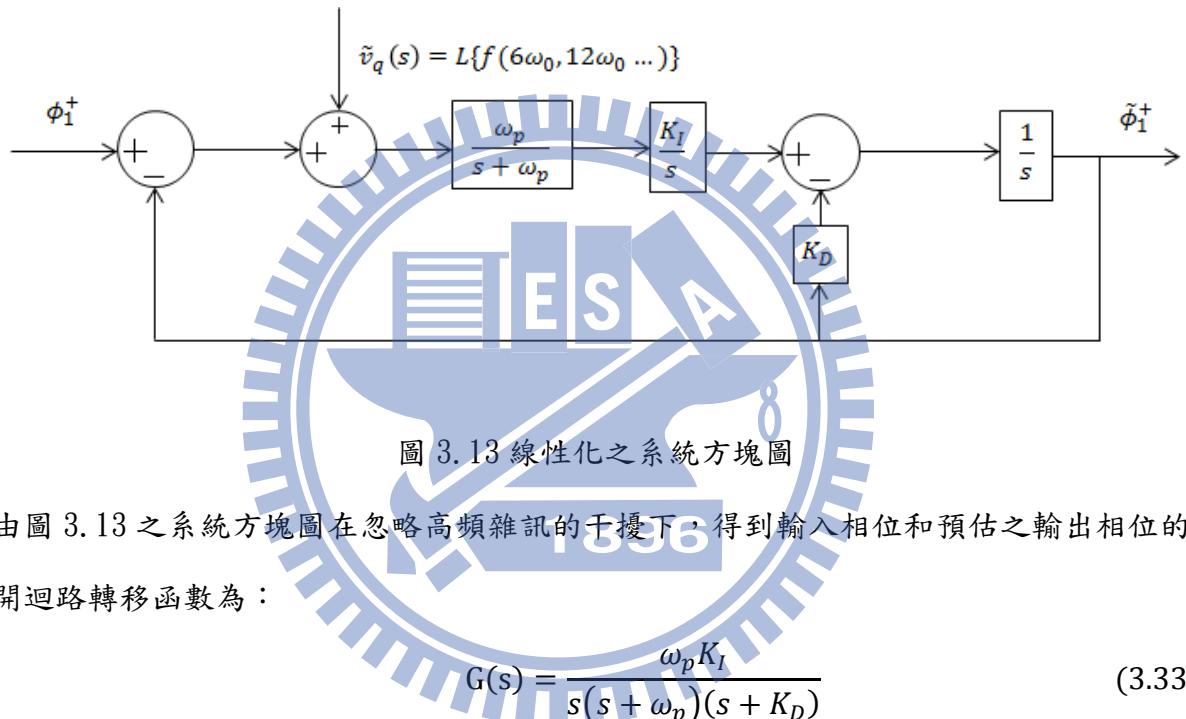

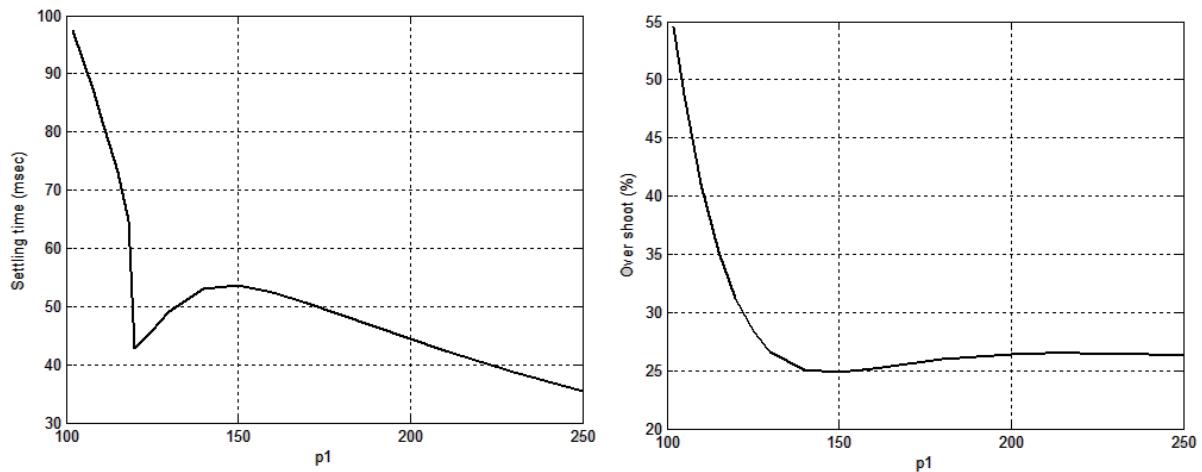

當通用積分器等效之低通濾波器的截止頻率約為 65 Hz 時，圖 3.24 為隨著  $p_1$  的改變對於系統暫態之最大超越量和穩定時間的影響。由圖中可以發現當  $p_1$  越接近不等式的條件時整個系統將會越不穩定，甚至當  $p_1$  小於 110 時由於控制器的極點較零點接近原點，造成開路轉移函數的相位裕度會在增益穿越頻率前就發生不足的現象，所以系統的穩定時間和最大超越量都因為較為震盪的關係而不甚理想。整體上系統會隨著  $p_1$  的增加使得的最大超越量和穩定時間會逐漸減小，不過穩定時間的變化較為複雜，可以藉由根軌跡的觀察解釋  $p_1$  的設計對於控制器之極點和零點的影響。

當  $p_1$  小於約 120 以前控制器的極點從原點附近隨著  $p_1$  增加而往左移動，並且逐漸和往實軸移動的共軛複根之零點靠近，此時系統因逐漸穩定而減輕震盪的現象讓穩定時間有明顯的下降。當  $p_1$  的值介於 120 和 150 之間時，控制器的極點和零點都將落於實軸之上，且控制器的極點將和其中一個零點相互靠近並且在約  $p_1$  為 135 時發生相互抵消的現象，之後隨著  $p_1$  變大則極點與零點才又再度分離，這區間內 Q 參數化設計的控制器發生極點和零點互相抵銷的現象，使得系統主要受到控制器未被抵銷之零點影響，而造成系統的穩定時間有些許上升。在  $p_1$  大於 150 後控制器之極點和零點開始分離對系統的影響逐漸明顯，而且極點將比零點更為遠離原點，而使得系統的穩定時間再度開始減少。

圖 3.24  $p_1$  對於系統暫態之影響

圖 3.25  $p_1$  對高頻抑制能力之影響

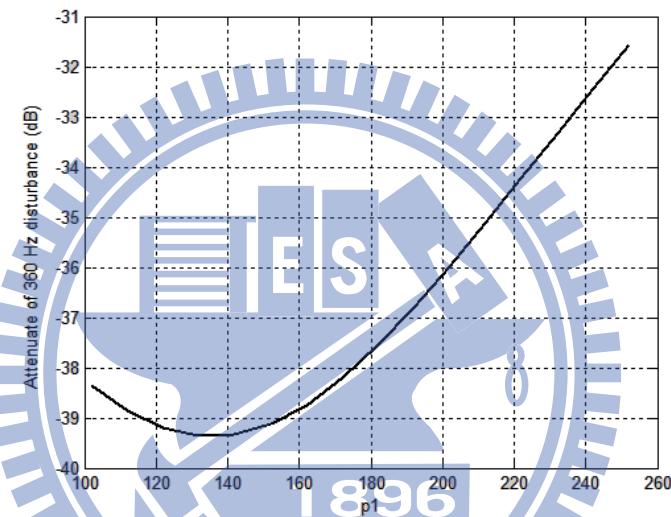

圖 3.25 則是說明著隨著  $p_1$  的變動造成鎖相迴路系統高頻響應的影響，在  $p_1$  小於 140 之前，由於控制器的極點較零點靠近原點且逐漸向零點靠近甚至發生互相抵銷的狀況，這段區間內的高頻抑制能力會有些微地改善，但隨著控制器的極點開始和零點彼此分開後，控制器的極點較零點遠離原點而使得抑制能力隨著  $p_1$  上升而逐漸下降。

上述的分析可得當 Q 參數化的設計只有一個自由度時，由於控制器的極點和零點的行為隨著  $p_1$  的變動而極為複雜，當控制器的極點和零點逐漸靠近系統的穩定時間逐漸上升且高頻抑制也有較佳的表現，在極點和零點相互低消時穩定時間和高頻的抑制有極值發生，隨後穩定時間隨著  $p_1$  的增加而減少，高頻的抑制能力也是越差，而最大超越量的影響則是在超過一定的值後便沒有顯著的改善。

### 3.4.4 Q 參數化兩維自由度之設計與分析

當 Q 之轉移函數其中三個極點是被固定在相同位置時，系統可以設計和調整的參數將會有兩個自由度，即 Q 之轉移函數為：

$$Q(s) = \frac{Ks(s + \omega_p)(s + z_1)(s + z_2)}{(s + p_1)^3(s + p_2)} \quad (3.64)$$

控制器之轉移函數在滿足(3.57)、(3.58)以及(3.60)之關係式並且經整理後可得：

$$C(s) = \frac{Q(s)}{1 - P(s)Q(s)} = \frac{(s + z_1)(s + z_2)}{s(s + 3p_1 + p_2 - \omega_p)} \quad (3.65)$$

為確保系統的穩定，控制器的極點必須被放置在 s 平面的左半平面中，當系統處於穩定時必須滿足：

$$3p_1 + p_2 \geq \omega_p \quad (3.66)$$

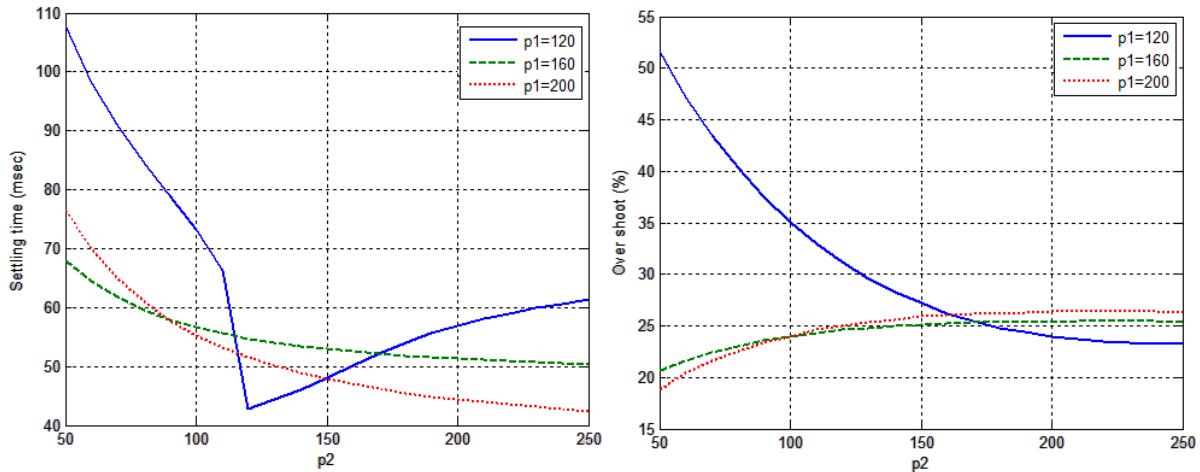

圖 3.26 為低通濾波器之截止頻率為 65 Hz 時探討不同的  $p_1$  和  $p_2$  對系統之暫態響應的影響。由圖中可以發現  $p_1$  的大小對於系統的影響有明顯的差異，當  $p_1$  為 120 時和其餘兩種情形的暫態響應的特性完全不相同，造成其控制器極點和零點的變化十分類似於一維自由度設計。

當  $p_1$  為 120 且  $p_2$  小於 115 時控制器的零點是為共軛複根的形式並且逐漸隨著  $p_2$  增加而往實軸移動，且控制器的極點也逐漸遠離原點並且靠近零點，此過程中將減少系統的震盪現象造成最大超越量和穩定時間都有減少。當  $p_2$  介於 115 和 180 之間時，控制器的極點與零點將逐漸靠近甚至發生互相抵消的現象，再隨著  $p_2$  的增加而分開。在  $p_2$  大於 180 之後雖然控制器的極點和零點也是彼此逐漸遠離，但此時零點比極點更為遠離原點，因而造成穩定時間逐漸上升。

當  $p_1$  為 160 以及 200 時的情況時，在  $p_2$  小於 100 時暫態的影響和預期有些差別， $p_1$  為 160 時暫態響應和  $p_1$  為 200 相比應有較快的穩定時間和較小之最大超越量，但這段區間內由於  $p_1$  為 160 時控制器的極點和零點發生互相抵銷的現象，因此造成和預期不同之差異，但兩者的參數對系統暫態的影響是類似的，隨著  $p_2$  的增加控制器的極點和零點皆遠離原點而造成穩定時間皆有減少，但最大超越量卻是些微的增加。

圖 3.26  $p_1$ 與 $p_2$ 對系統暫態響應之影響

圖 3.27 為  $p_1$ 與 $p_2$ 對鎖相迴路系統高頻雜訊抑制能力的影響，從圖中發現在  $p_1$  為 160 和 200 時高頻雜訊的抑制能力，皆隨著  $p_2$  的值變大造成控制器的極點較零點更為遠離原點而讓抑制效果降低。當  $p_1$  為 120 時則是因為在控制器的極點和零點分開之後， $p_2$  的增加令控制器的零點比控制器的極點更為遠離原點，因此高頻的抑制能力將隨著  $p_2$  的變大而增加。

圖 3.27  $p_1$ 與 $p_2$ 對高頻雜訊抑制能力之影響

$Q$  參數化的方式不論調整的自由度為二維或一維，鎖相迴路系統的響應和所設計的極點位置息息相關，尤其是在當設計的極點位置不是離原點很遠時會造成控制器的零點和極點位置十分相近甚至相互抵消，此時系統的暫態響應和高頻抑制的效果將類似於一階控制器補償的情形，但隨著極點被放置的越遠時系統的暫態有較好的趨向，不過高頻

的抑制能力卻也開始下降。

綜合以上不同的控制器運用於線性化後雙通用積分器鎖相迴路系統的分析，比例積分回授控制的優點在於已經發展悠久，設計上有較多的技巧可以使用，且暫態的響應和高頻抑制的能力都十分良好，雖然會因零點使得最大超越量較高。虛擬微分回授控制其結構差別在於系統的微分效果並沒有真正零點的存在，因此暫態響應以及高頻抑制能力都較比例積分回授控制來的出色許多，但系統僅為型態一無法完全消除針對頻率單位步階時的穩態誤差。自適性比例積分回授控制則有效降低比例積分回授控制最大超越量的問題，不過穩定時間些許地增加了。Q參數化的方式在設計上較為困難，但可以設計出高階的控制器，這章中只探討了分子和分母為二階多項式的控制器，其參數設計可以有效地降低最大超越量及穩定時間的可能，且可以設計出讓頻率的穩態誤差為零的系統。不過控制器控制的系統為一個非線性的系統，其反應的效果可能和線性的情形會有些微出入，且系統會有規格上的需求使得控制器參數變化的範圍將受到限制。

## 四、控制器之模擬與驗證

為比較第三章不同的控制方式應用於雙通用積分器鎖相迴路系統的差異，本章先探討在所需規格下不同控制器之參數的選擇，且藉著利用 MATLAB 中的 Simulink 來模擬，考量電網上可能會發生之故障，利用模擬的驗證來表現出不同的控制器對於鎖相迴路系統的響應情形。在許多探討不同鎖相迴路的文獻中，為比較不同的設計方式應用在鎖相迴路控制時之優劣，大多是用最大超越量，穩定時間以及高頻抑制能力來做為彼此間比較的依據。本章在模擬時除了各個不同控制器其線性化系統必須滿足規格要求外，尚利用單位步階的誤差絕對值積分和誤差平方積分做為控制器做為比較的指標。

### 4.1 控制器參數設計

為比較各個控制器的優劣必須先訂定鎖相迴路系統之規格，本論文所設計之鎖相迴路其電網的頻率以台灣電網頻率 60 Hz 作為基頻頻率，且雙通用積分器鎖相迴路系統之線性化模型對於單位步階之暫態規格的要求為穩定時間需小於 50 毫秒，最大超越量不得超過 35%，且對基頻之六倍頻率諧波必須最少要有-35dB 的抑制能力。由於本論文是利用雙通用積分器做為鎖相迴路的相位偵測單元，可以完全消除因三相電壓不平衡之故障造成的干擾，且為了避免其帶拒濾波器的頻帶影響到系統的操作[25]，線性化系統的開路轉移函數之增益穿越頻率有上限的存在，建議的範圍是落在介於兩倍基頻的四分之一和五分之一之間，即 24 Hz 至 30 Hz。此小節將探討各種控制器在滿足以上之規格要求下的變數範圍中，藉由選擇系統單位步階之誤差絕對值積分和誤差平方積分最小之參數來做為模擬之參數。

#### 4.1.1 比例積分回授控制參數設計

由第三章第一節中可知最大相位裕度設計的比例積分回授控制在單位步階響應下的線性化模型，其阻尼係數的改變會造成最大超越量與穩定時間的影響，而不同的開迴路增益穿越頻率也會改變系統的響應速度和高頻抑制的能力，為使系統滿足規格的要求

必須考量增益穿越頻率以及阻尼係數的因素。從圖 4.1 中發現穩定時間隨著增益穿越頻率的上升而下降，而阻尼係數在大於 0.6 後會使得穩定時間變慢。最大超越量僅隨著阻尼係數上升而減少。而越大的阻尼係數和增益穿越頻率則使得高頻抑制能力越差。因此由圖中可知在最低之增益截止頻率下阻尼係數須介於約 0.7 至 0.9 之間，而最高之增益穿越頻率其阻尼係數須介於 0.65 至 0.8 之間，方能使得系統滿足所需求之規格。

圖 4.1 阻尼係數及增益穿越頻率對系統暫態和高頻抑制之影響

為了比較符合系統規範圍內參數之優劣，利用系統單位步階的誤差絕對值之積分和誤差平方之積分作為指標，在滿足規格要求的條件下選擇誤差絕對值之積分和誤差平方之積分最小的設計參數。圖 4.2 為誤差絕對值之積分和誤差平方之積分對阻尼係數與增益穿越頻率的影響，兩種指標由圖中可以發現皆是隨著增益穿越頻率以及阻尼係數的上升而減少。

圖 4.2 阻尼係數及增益穿越頻率對系統之 IAE 和 ISE 之影響

由以上的結果可知當增益穿越頻率在 30 Hz 及阻尼係數為 0.8 時，此參數下的線性化之鎖相迴路系統暫態效果將會滿足規格設計的要求，且同時擁有最小的誤差絕對值之積分和誤差平方之積分。利用第三章分析中參數設計的關係式(3.7)可以得到比例積分回授控制的參數如表 4.1 所表示

表 4.1 比例積分回授控制之參數

|                       |                  |

|-----------------------|------------------|

| 增益穿越頻率 ( $\omega_c$ ) | 188.50 (rad/sec) |

| 比例增益 ( $K_p$ )        | 188.50           |

| 積分增益 ( $K_I$ )        | 13665.61         |

| 雙通用積分器之係數 ( $k$ )     | 2.6              |

#### 4.1.2 虛擬微分回授控制參數設計

第三章第二節中虛擬微分回授控制的分析可知系統暫態響應和高頻抑制除了受到微分增益、開迴路的增益穿越頻率以及等效之低通濾波器的截止頻率影響。為了比較不同控制器之差異，在設計虛擬微分回授控制時，應當除了控制器外將其餘之元件的參數固定，才能彰顯控制器對於鎖相迴路系統之差別。因此沿用前一小段所設計的等效低通濾波器之截止頻率，將線性化的模型中等效之低通濾波器的截止頻率設為 78 Hz，則單位步階的響應和高頻干擾抑制能力受到微分係數與增益截止頻率的影響如圖 4.3。由圖

中發現虛擬微分回授控制在參數  $a$  大於 1.5 以上不論增益穿越頻率為何皆可滿足系統規格之要求。當增益穿越頻率上升時穩定時間將會降低，但最大超越量在相同的  $a$  值下卻會增加，而高頻雜訊抑制能力也會變差。

圖 4.3 增益穿越頻率和  $a$  值對系統暫態和高頻抑制的影響

為了尋求虛擬微分回授控制在符合要求規格下的參數範圍中之最佳參數，利用系統單位步階的誤差絕對值之積分和誤差平方之積分來作為指標，圖 4.4 為兩種指標對於不同增益穿越頻率和不同  $a$  值的影響，圖中顯示出增益穿越頻率以及微分增益越大時系統的單位步階響應之誤差絕對值積分和誤差平方積分皆有降低的趨勢。

圖 4.4 增益穿越頻率和  $a$  值對系統之 IAE 和 ISE 之影響

總結以上的結果可以了解虛擬微分回授控制在不同的增益穿越頻率下，雖然高頻抑制能力會隨著增益穿越頻率以及微分增益的增加而稍微變差，但不論是何種增益超越頻率或微分增益，高頻抑制能力皆在規格要求內。系統的最大超越量和穩定時間則是隨著這兩個參數的上升都有較好的表現，而且系統發生單位步階響應時其誤差絕對值積分和誤差平方積分兩種指標的數值也都較低。因此在鎖相迴路中雙通用積分器之等效低通濾波器的截止頻率相同的條件下，利用第三章中虛擬微分回授之參數關係可以得到設計參數如表 4.2 所示。

表 4.2 虛擬微分回授控制之參數

|                       |                  |

|-----------------------|------------------|

| 增益穿越頻率 ( $\omega_c$ ) | 188.50 (rad/sec) |

| 微分增益 ( $K_D$ )        | 1195.175         |

| 積分增益 ( $K_I$ )        | 244357.277       |

| 雙通用積分器之係數 ( $k$ )     | 2.6              |

#### 4.1.3 自適性調整之比例積分回授控制參數設計

自適性調整之比例積分回授控制是藉由調整其阻尼係數，在誤差變大時系統阻尼係數增加而降低比例積分控制器的最大超越量。在第三章第一節比例積分回授控制參數分析中已知增益穿越頻率的改變會加快穩定時間但最大超越量則沒有顯著的改變，雖然自

適性調整最主要是改變阻尼係數有效地降低最大超越量，但卻會造成穩定時間的增加，使得系統可能成為超出規格外之設計。為避免加入自適性調整後系統可能無法滿足規格要求，而且為了在所需的規格要求內自適性調整有較大的調整範圍，將挑選初始之阻尼係數為 0.65，此時比例積分回授控制有最小之穩定時間，本段將討論在不同的增益穿越頻率下初始阻尼係數為 0.65 時自適性調整之參數的選擇。

圖 4.4 為自適性調整中誤差的係數在不同增益穿越頻率下造成整個系統暫態的影響，其中自適性調整的頻率為 1000 Hz，可以發現其暫態響應的結果和第三章所分析得到的結論相同。系統的穩定時間將會隨著自適性調整之係數的增加而變長，為滿足規格要求自適性之係數的調整範圍將隨著增益穿越頻率的不同而改變，越小的增益穿越頻率越有可能因為調整係數過大而使得系統的穩定時間超過規格的要求。系統的最大超越量則是因增益穿越頻率可以變動範圍並不廣所以變化十分不明顯。

圖 4.5 自適性係數和增益穿越頻率對系統暫態之影響

圖 4.6 為不同增益穿越頻率和自適性係數下系統單位步階的誤差絕對值積分和誤差平方積分的影響，由圖上可知當系統的增益穿越頻率及自適性之係數越大則系統的這兩個誤差指標將會越小，不過隨著自適性係數增大改善的效果也會逐漸變小，但在滿足規格要求下應當選擇範圍內最大的增益穿越頻率和足夠大的自適性係數。

圖 4.6 增益穿越頻率和自適性係數對於單位步階 IAE 和 ISE 的影響

由以上的討論和分析可知利用自適性調整的比例積分阻尼係數的方式，將使得原本在比例積分設計上屬於不符合規格之參數的範圍變成足以滿足所需求的規格，而使得整個比例積分回授控制的是設計上可以挑選擁有更快穩定時間及較佳高頻抑制能力的阻尼係數。因此利用以上自適性調整之係數的討論，在自適性調整之比例積分回授控制的阻尼係數為 0.65 時所設計出的參數如表 4.3 所列。

表 4.3 自適性調整比例積分回授控制參數

|                       |                 |

|-----------------------|-----------------|

| 增益穿越頻率 ( $\omega_c$ ) | 188.50(rad/sec) |

| 比例增益 ( $K_p$ )        | 188.50          |

| 積分增益 ( $K_{I0}$ )     | 13665.61        |

| 雙通用積分器之係數 ( $k_0$ )   | 2.3             |

| 自適性係數 ( $\gamma$ )    | 3               |

#### 4.1.4 一維自由度之 Q 參數化控制器參數設計

在第三章第五節的分析中不論是一維自由度還是二維自由度的設計，由於 Q 參數化的設計是一種設計閉迴路轉移函數的方法，除了系統所需規格要求要被滿足外，系統開迴路的增益穿越頻率也必須在限制範圍內。當雙通用積分器等效之低通濾波器的截止頻率和本節第一段中比例積分回授控制設計的截止頻率相同時，一維自由度之 Q 參數化的

$p_1$ 必須介於大約在 123 至 215 之間方能使得系統設計滿足這幾個條件。在這一個區間內隨著  $p_1$  的增加控制器之極點和零點的位置相當複雜也影響著整個系統的暫態響應與高頻的抑制。

圖 4.7 Q 參數化設計  $p_1$  對單位步階的暫態及高頻抑制之影響

圖 4.7 為 Q 參數設計中的  $p_1$  對線性化後的鎖相迴路暫態響應和高頻抑制的關係圖，當  $p_1$  小於於 135 時，由於控制器的極點隨著  $p_1$  增加而遠離原點並且朝向共軛複根的零點移動使得系統逐漸穩定，因此最大超越量、穩定時間以及高頻抑制的能力隨著  $p_1$  上升而有改善的效果。當  $p_1$  介於 140 至 162 之間時控制器的極點和零點會相互靠近，在這段區間內由於控制器的極點和零點的效果因相互靠近使得系統穩定時間上升而最大超越量和高頻抑制的改善效果卻逐漸平緩，大約在  $p_1$  為 162 時控制器極點和零點發生互相抵銷的現象，造成穩定時間、最大超越量以及高頻抑制出現區間的極值。然而在  $p_1$  大於 162 後控制器的極點和零點逐漸遠離，系統的穩定時間因為控制器的極點遠離原點的關係而減少但最大超越量和高頻的抑制也皆開始變差。

藉由單位步階的誤差絕對值積分和誤差平方積分兩個指標，在 $p_1$ 可調整的範圍內找出最好的參數設計。圖 4.8 為 $p_1$ 的改變對誤差絕對值積分和誤差平方積分的影響。 $p_1$ 小於 140 前兩種指標皆隨著 $p_1$ 增加而快速地減少，但在 $p_1$ 介於 140 至 162 之間時，因為控制器極點和零點發生相互抵銷的現象，使得指標有些微的上升。在 $p_1$ 大於 162 後，控制器的極點和零點又再度分離而且遠離原點，因此指標便又隨著 $p_1$ 增加而減少。在滿足開路增益頻率的範圍以及系統所要求的規格設計下，所以 $p_1$ 越大其指標有越好的效果。

圖 4.8 Q 參數化設計  $p_1$  對單位步階的 IAE 及 ISE 之影響

由以上的討論可以發現，除了上述在滿足系統要求規格的條件下，在 Q 參數一維自由度的設計中其開路增益轉移函數必須介於 24 Hz 和 30 Hz 之間，因此所 Q 設計之 $p_1$ 的大小必須介於 175 和 207 之間方才符合整個系統的要求。藉由分析系統的誤差絕對值積分和誤差平方積分後可以得到一維自由度之 Q 參數化的極點為 -207 是此範圍內最佳的選擇，其參數設計如表 4.4。

表 4.4 一維自由度 Q 參數化設計之參數

|                 |           |

|-----------------|-----------|

| Q 參數設計之極點       | -207      |

| Q 參數設計之控制器的非零極點 | -337.9115 |

| Q 參數設計之控制器第一個零點 | -326.297  |

| Q 參數設計之控制器第二個零點 | -61.505   |

| Q 參數設計之控制器增益    | 186.675   |

| 雙通用積分器之係數       | 2.6       |

#### 4.1.5 二維自由度之 Q 參數化控制器參數設計

當 Q 參數化擁有二維的自由度調整時，其系統的分析和參數的設計由第三章第五節中可知較一維自由度來得複雜，系統會因為  $p_1$  設計的不同而使得當  $p_2$  改變時控制器的極點和零點的位置有兩種不同狀況，因而造成系統暫態的影響大不相同。而且雙通用積分器鎖相迴路之開路的增益穿越頻率有其範圍的限制， $p_1$  的大小也影響著  $p_2$  可以調整的範圍，越大的  $p_1$  會令  $p_2$  調整範圍的上限降低。

圖 4.9 Q 參數化  $p_1$  與  $p_2$  對系統暫態和高頻抑制之影響

探討 Q 參數化設計中兩個參數改變成鎖相迴路系統的影響時，系統中等效低通濾波器的截止頻率和前一段相同必須和比例積分所設計的一樣。圖 4.9 中為兩個參數的改變造成系統暫態響應之最大超越量、穩定時間的影響以及高頻抑制能力的影響。圖中的結果可以發現和第三章第五節中分析二維自由度 Q 參數化的時候狀況類似，因  $p_1$  的關係控制器之極點和零點有兩種不同的情形。當  $p_1$  為 136 時對於系統的影響和其他兩種情況

有很大的差異，控制器的零點和極點隨著 $p_2$ 的上升而相互靠近，在 $p_2$ 為 215 左右時發生相互抵銷，而當 $p_2$ 超過 215 後控制的零點遠離原點的速度較極點快，在這樣的過程中最大超越量和高頻抑制的能力會隨著 $p_2$ 的增加而變好，但穩定時間將會上升。在 $p_1$ 為 175 和 215 時隨著 $p_2$ 的增加，控制器極點和零點兩者逐間分開，並且極點較零點遠離原點而讓穩定時間減少，但最大超越量和高頻抑制能力則是隨著 $p_2$ 變大而較差。

圖 4.10 為 Q 參數化之 $p_1$ 與 $p_2$ 對於系統單位的步階誤差絕對值積分和誤差平方積分的影響，可以看出這兩種指標的影響因為 $p_1$ 的大小會也是有不同的情況發生。較大的 $p_1$ 在 $p_2$ 增加時兩種指標的改善效果較好。當 $p_1$ 為 136 時且 $p_2$ 小於 160 時兩種指標皆隨著 $p_2$ 上升而變小，但在 $p_2$ 超過 160 後系統對於最大超越量降低的效益小於穩定時間增加的損失，造成兩種指標皆開始隨著 $p_2$ 增加而變大。但當 $p_1$ 為 175 和 215 時越大的 $p_2$ 雖然最大超越量有些微的上升但穩定時間有較明顯的變小，因此對於整個系統單位步階的誤差絕對值積分和誤差平方積分也因而降低。

圖 4.10 Q 參數化 $p_1$ 與 $p_2$ 對於系統單位步階 IAE 和 ISE 的影響

當 Q 參數化的極點擁有兩個自由維度後，對於參數選擇的範圍較一維來的廣泛，除了系統的開路增益穿越頻率的範圍限制會影響著受到 $p_1$ 與 $p_2$ 的調整範圍，系統的暫態響應和高頻雜訊的抑制能力在因 Q 參數化極點的位置而有不同的調整範圍，不過由系統單位步階的誤差絕對值積分和誤差平方積分可以發現 Q 參數的兩個極點位置離原點越遠這兩種誤差指標皆越小。因此二維自由度的 Q 參數化之參數的選擇，應在開路增益的範圍要求下選擇越大的 $p_1$ 讓指標維持在較低的區間，再藉由 $p_2$ 的調整讓整個系統的暫態響應

和高頻抑制能力符合所需設計的規格需求，其建議的參數如表 4.5

表 4.5 二維自由度 Q 參數化設計之參數

|                    |                  |

|--------------------|------------------|

| Q 參數設計之極點( $p_1$ ) | -215             |

| Q 參數設計之極點( $p_2$ ) | -180             |

| Q 參數設計之控制器的非零極點    | -334.912         |

| Q 參數設計之控制器零點       | -60.886、-324.158 |

| Q 參數設計之控制器增益       | 184.944          |

| 雙通用積分器之係數          | 2.6              |

## 4.2 鎮相迴路系統的模擬與驗證

由前一小節的分析可知滿足線性化系統所需的規格下，不同控制器的參數該如何決定，且所決定之參數在符合系統所要求的規格下其線性化的系統之單位步階的誤差絕對值積分和誤差平方積分兩種指標有最小的值。在這樣的參數設計下，試圖在電網系統常見的故障中比較各個控制器運用於雙通用積分器鎮相迴路的實際模型下之影響。在模擬中三相平衡電壓的頻率將以台灣交流電的 60 Hz 為基頻，且初始的三相相位皆為零。

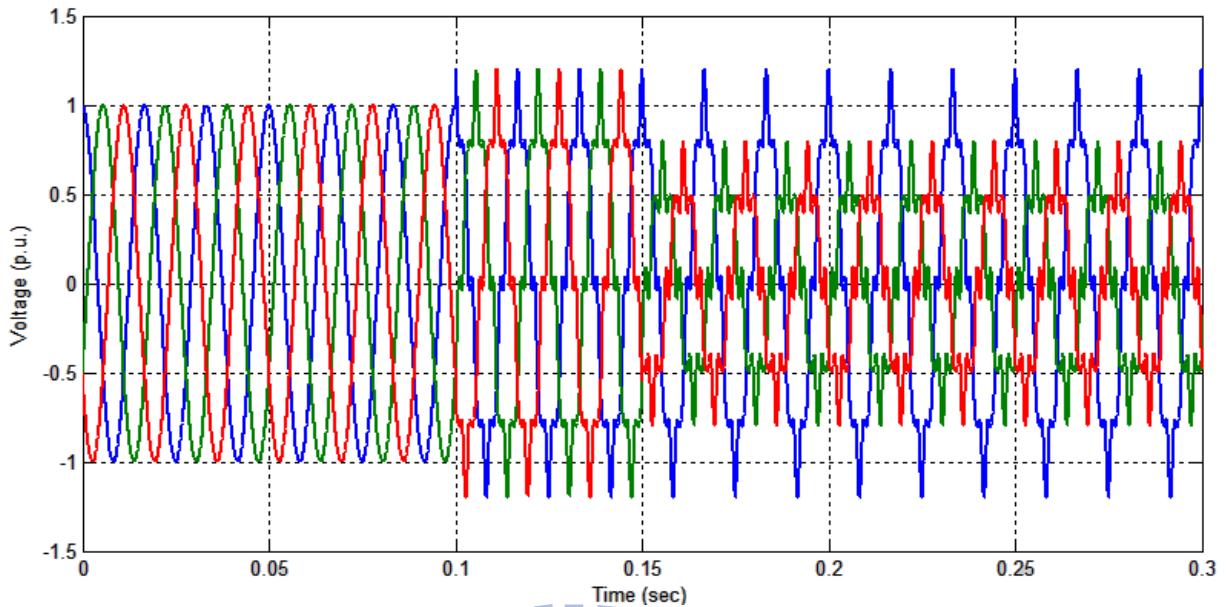

### 4.2.1 相位步階變化之模擬結果

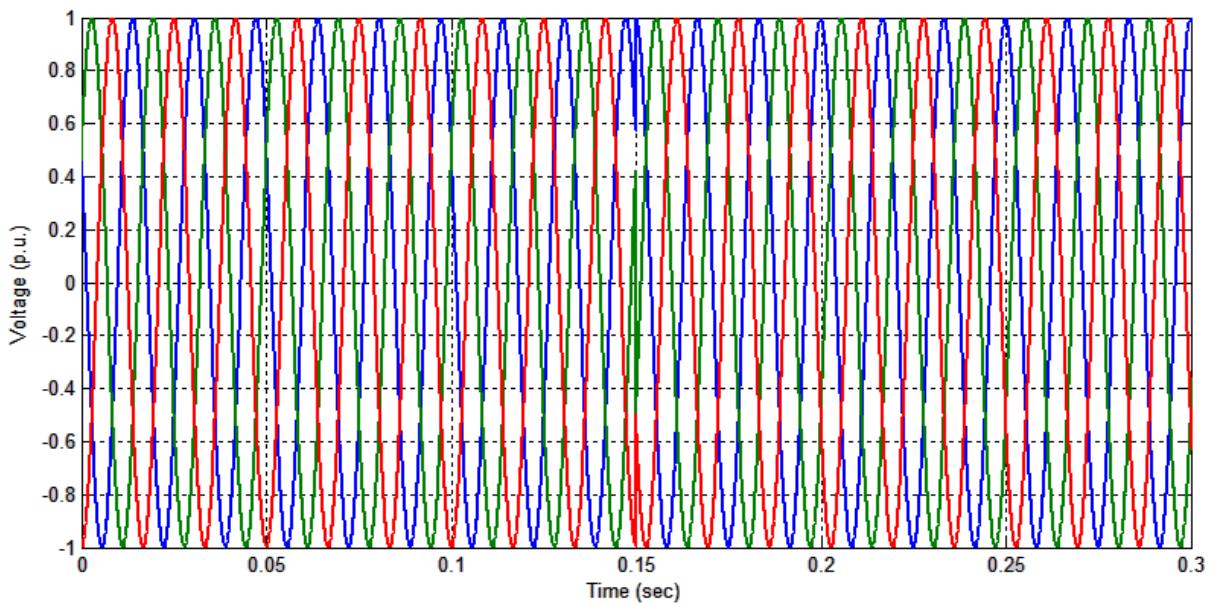

為探討三相電壓發生相位步階變化時不同控制系統的影響並且比較各個控制器之優劣，模擬輸入為平衡的三相電壓在 0.15 秒時各相皆發生一個強度量的相位落後，試著以此輸入探討當發生步階變化時不同控制系統相位響應的結果，其輸入之三相電壓的波形如圖 4.11。

圖 4.11 0.15 秒發生相位落後後之三相電壓

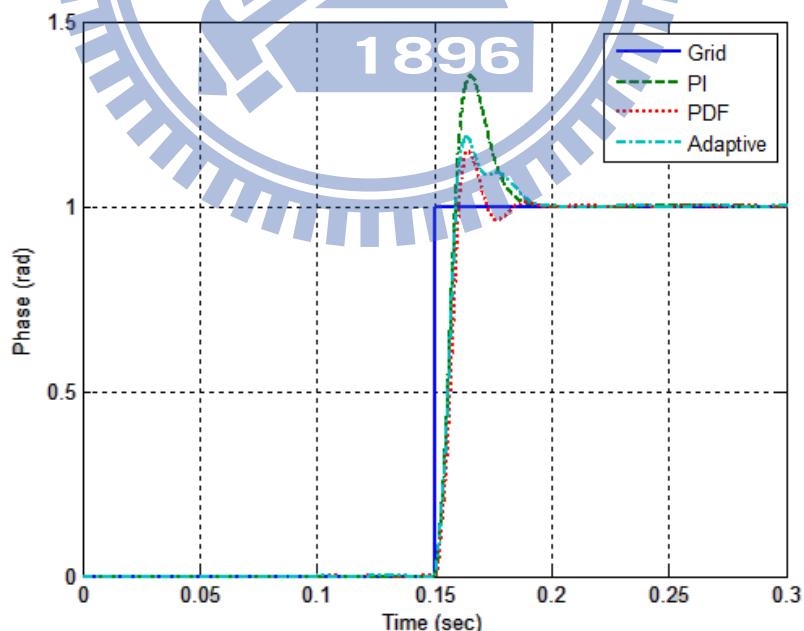

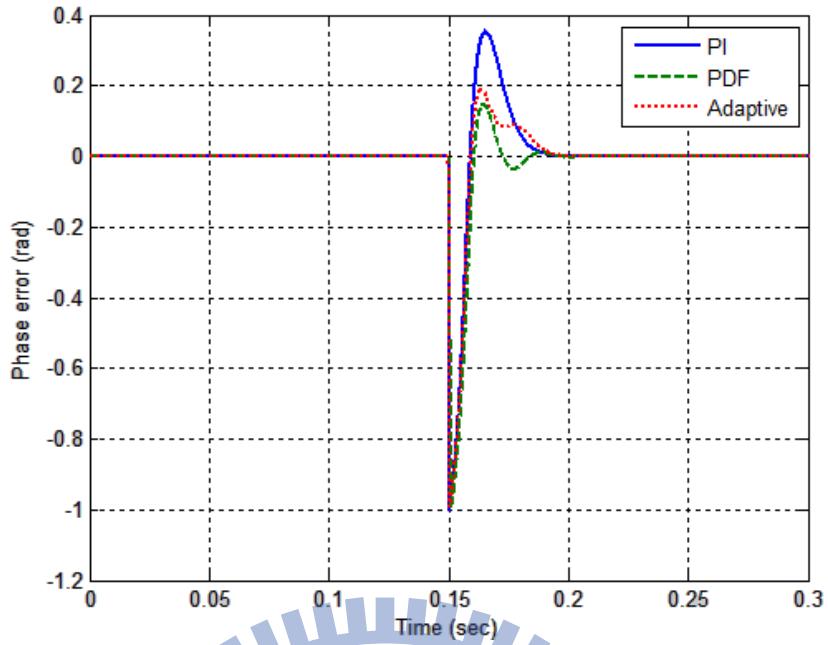

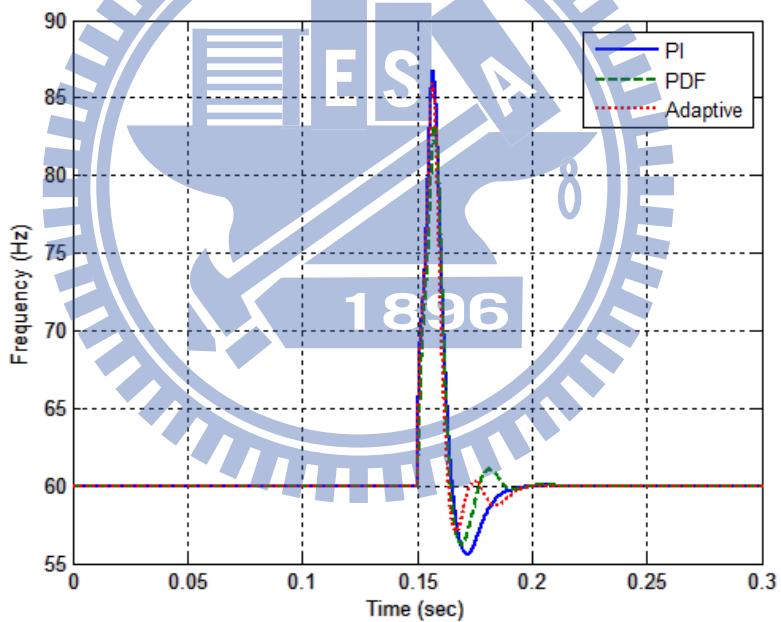

圖 4.12 為比例積分回授控制、虛擬微分回授控制以及自適性比例積分回授控制在實際鎖相迴路系統架構下的估測相位模擬結果。由圖 4.12 中可以很明顯的發現這三種控制器中比例積分回授控制的最大超越量最大，穩定時間最長但上升時間最短，而虛擬微分回授控制則是最大超越量最小，穩定時間最短但上升時間最慢。

圖 4.12 一強度相位變化下系統估測相位模擬的結果

圖 4.13 一強度相位變化下系統相位誤差的結果

圖 4.14 一強度的相位變化下系統估測頻率的結果

在三相電壓只有發生相位變化時系統的相位誤差以及估測頻率的影響由圖 4.13 和圖 4.14 中得到。由圖 4.13 中的結果可以得知三種控制器方式在相位變化時誤差的情況，由於比例積分回授控制相位誤差是三者中最高的，虛擬微分回授控制則最為緩和。對於系統的估測頻率而言，由於這個模擬是針對系統的相位變化所以不論是哪一種控制方式，皆能很準確地追蹤到電網的頻率而且對於頻率和相位的穩態誤差皆為零。

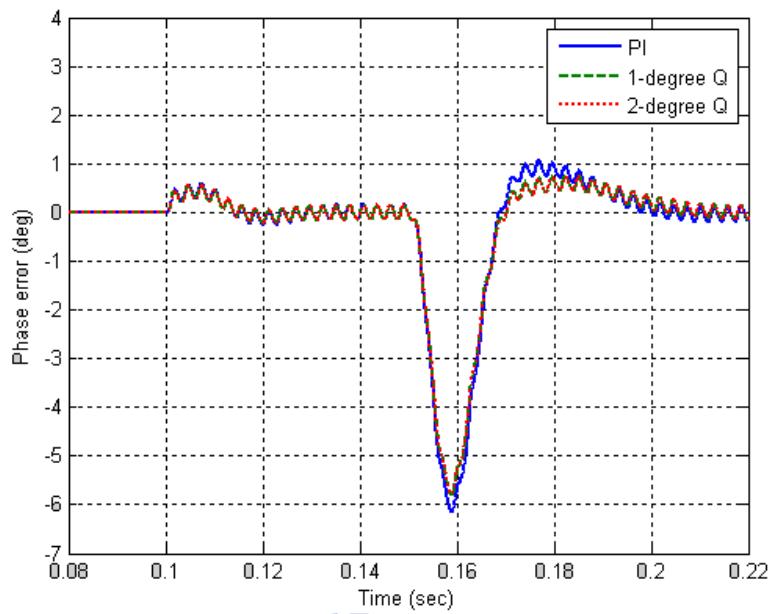

圖 4.15 一強度相位變化下系統估測相位的結果

圖 4.16 一強度相位變化下系統相位誤差的結果

圖 4.17 一強度相位變化下系統估測頻率的結果

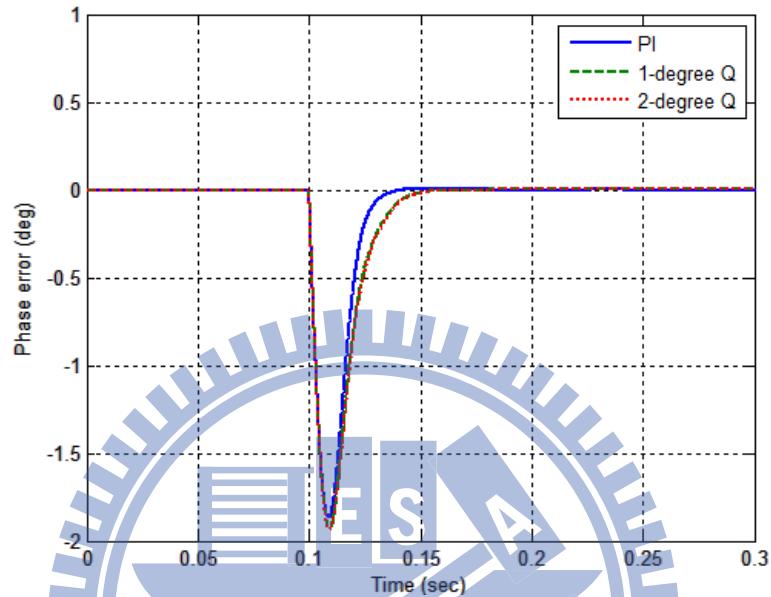

圖 4.15、4.16 以及圖 4.17 則分別為比例積分回授控制和一維自由度與二維自由度的 Q 參數化設計之估測相位、相位誤差以及估測頻率的模擬圖。由圖中發現 Q 參數化的設計中一維自由度和二維自由度兩者間差距非常微小。但不論是哪一種 Q 參數化設計其最大超越量皆是較比例回授控制來的小，只可惜 Q 參數設計的控制器的穩定時間則是較慢了些。圖 4.16 以及圖 4.17 則是表示著系統發生相位變化時對相位誤差及估測頻率的影響，對於單純電網相位變化的條件而言，由於 Q 參數的設計不論是一維自由度或二維自由度皆是型式二的系統，所以對於系統的頻率及相位皆可以良好的追蹤並且讓相位及頻率的穩態誤差皆為零。

表 4.6 則為各個不同控制器對於電網發生一個強度量的相位變化其各個控制系統所響應的數值比較，由系統的誤差絕對積分和誤差平方積分兩樣指標來做為控制器優劣的比較指標，在這些控制器當中系統相位的變化其相位追蹤效果較好的是虛擬微分回授控制和自適性調整之比例積分回授控制，而 Q 參數化的方式不論是一維自由度或二維自由度比起比例積分回授控制而言皆稍微差了一些，但彼此之間的效能並十分相近。

表 4.6 相位變化對各個控制器的影響

| 控制方法          | 2%穩定時間  | 最大超越量   | IAE                    | ISE                    |

|---------------|---------|---------|------------------------|------------------------|

| 比例積分回授控制      | 35.9 毫秒 | 35.36 % | $1.055 \times 10^{-2}$ | $5.567 \times 10^{-3}$ |

| 虛擬微分回授控制      | 31 毫秒   | 14.95 % | $8.046 \times 10^{-3}$ | $5.309 \times 10^{-3}$ |

| 自適性調整比例積分回授控制 | 38.5 毫秒 | 24.94%  | $8.653 \times 10^{-3}$ | $4.742 \times 10^{-3}$ |

| 一維自由度 Q 參數化   | 43.4 毫秒 | 30.36 % | $1.084 \times 10^{-2}$ | $5.446 \times 10^{-3}$ |

| 二維自由度 Q 參數化   | 44 毫秒   | 30.11 % | $1.09 \times 10^{-2}$  | $5.486 \times 10^{-3}$ |

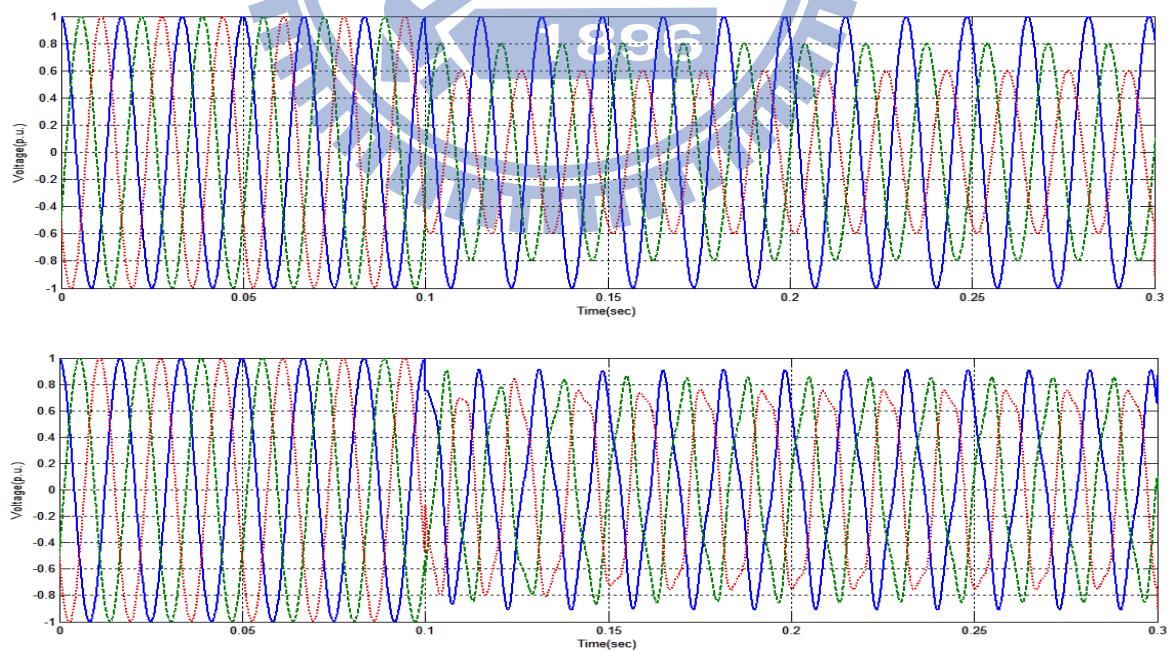

#### 4.2.2 不平衡三相電壓與高頻雜訊之模擬結果

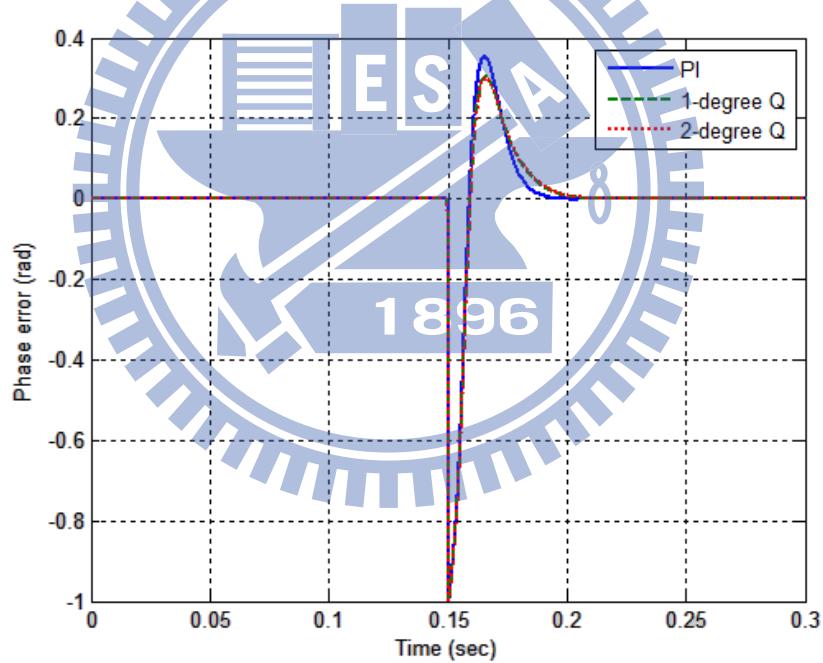

為探討電網端的三相電壓發生不平衡的狀況以及發生高頻雜訊時對不同控制方法的差異，讓原本三相的電壓在 0.1 秒時加入了正向序及負向序的雜訊其頻率分別為基頻的七倍及十一倍且雜訊的電壓震幅大小分別為 0.15 及 0.05 標么，並且在 0.15 秒時讓三相電壓發生型態為 E 之三相不平故障，其三相分別為 1 標么、0.6 標么、0.6 標么，其三相電壓波形如圖 4.18 所示。

圖 4.18 不平衡且參有雜訊的三相電壓

三相電壓在不平衡故障時鎖相迴路的系統主要是利用雙通用積分器以及順時對稱分量法來濾除負向序的電壓分量，而這種方式除了可以濾除不平衡故障造成的諧波外，有些特定頻率的雜訊也會因此而消除，僅剩下一些基頻之特定倍數的諧波。因為如此不平衡故障的發生在不同的控制中彼此的差異並不是很大，差別僅在於短暫的穩定過程中，但雙通用積分器無法濾除的高頻雜訊則必須由控制器來抑制其效果，以提升估測相位及頻率的準確度。

圖 4.19 和 4.20 分別為比例積分回授控制、虛擬微分回授控制以及自適性調整之比例積分回授控制在不平衡故障及含有高頻雜訊的三相電壓時其相位誤差及頻率誤差的結果。比例積分控制器所選擇之參數的高頻抑制能力僅是在恰好符合規格要求的設計。虛擬微分回授控制及自適性調整之比例積分控制的高頻抑制能力則是較好，而且因不平衡造成的暫態響應也有較好的表現。

圖 4.19 不平衡及高頻雜訊下不同控制器相位誤差結果

圖 4.20 不平衡及高頻雜訊下不同控制器估測頻率之結果

圖 4.21 和圖 4.22 則是 Q 參數化的控制對於電壓不平衡及含有雜訊的狀況下相位誤差和估測頻率的結果。對於 Q 參數化的設計而言，由於不平衡的干擾暫態較短暫所以在圖 4.21 中對於電壓發生不平衡故障時 Q 參數化的兩種設計方式其響應速度和比例積分回授控制差不多。在高頻雜訊的抑制能力方面，由於 Q 參數化的設計在前一節設計參數時對於高頻雜訊的抑制僅有符合規格內的設計而已，因此高頻抑制能力和比例積分控制相似。

圖 4.21 不平衡及高頻雜訊下 Q 參數相位誤差之結果

圖 4.22 不平衡及高頻雜訊下 Q 參數估測頻率之結果

不同的控制器對於電壓發生不平衡故障及受高頻雜訊的干擾的響應結果整體的比較如表 4.7 所示，其中除了誤差絕對值積分和誤差平方積分作為不同系統間的比較外，另外利用總諧波失真值(Totally harmonic distortion)(4.1)比較高頻雜訊經過控制器在估測相位上的抑制能力，由表中的數值可以了解在不平衡故障和高頻雜訊的情況下，虛擬微分回授控制和自適性調整之比例積分回授控制對高頻抑制的效果較佳。

$$\text{THD} = \frac{\sum_{n=1}^n (V_n^{+2} + V_n^{-2})}{V_1^2} \quad (4.1)$$

表 4.7 不平衡故障與高頻雜訊對各個控制器的影響

| 控制方式              | IAE                    | ISE                    | THD    |

|-------------------|------------------------|------------------------|--------|

| 比例積分回授控制          | $1.713 \times 10^{-3}$ | $8.449 \times 10^{-5}$ | 4.31 % |

| 虛擬微分回授控制          | $1.167 \times 10^{-3}$ | $5.786 \times 10^{-3}$ | 4.12 % |

| 自適性調整比例積分回授<br>控制 | $1.715 \times 10^{-3}$ | $8.453 \times 10^{-3}$ | 4.03 % |

| 一維自由度 Q 參數化設計     | $1.589 \times 10^{-3}$ | $7.426 \times 10^{-5}$ | 4.31 % |

| 二維自由度 Q 參數化設計     | $1.589 \times 10^{-3}$ | $7.345 \times 10^{-5}$ | 4.31 % |

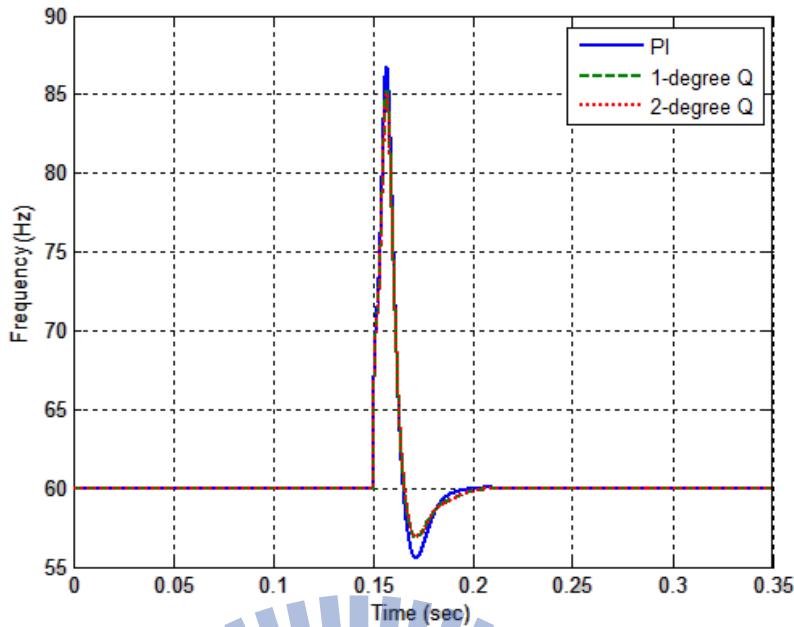

#### 4.2.3 頻率步階變化之模擬結果

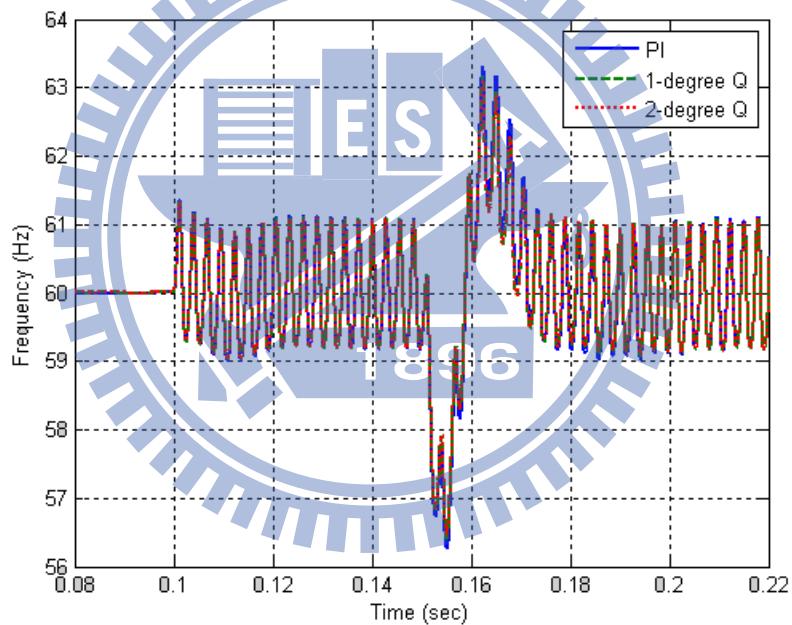

電網上三相電壓可能發生的故障除了相位變化、不平衡故障以及高頻雜訊的干擾外，頻率的變化也應該列入考慮之中，雖然頻率的變化比起前兩者的發生機率低了很多而且變化也都較為緩慢。當頻率變化時鎖相迴路其穩態誤差必須為固定的常數或零。此小段中將會討論頻率變化對於不同控制方式的影響。當平衡的三相電壓在鎖相迴路系統達到穩定後於 0.1 秒的時有 1 Hz 之步階變化，其三相電壓的波形如圖 4.23 所示。

圖 4.23 三相平衡電壓於 0.1 秒時頻率上升 1 Hz 之波形

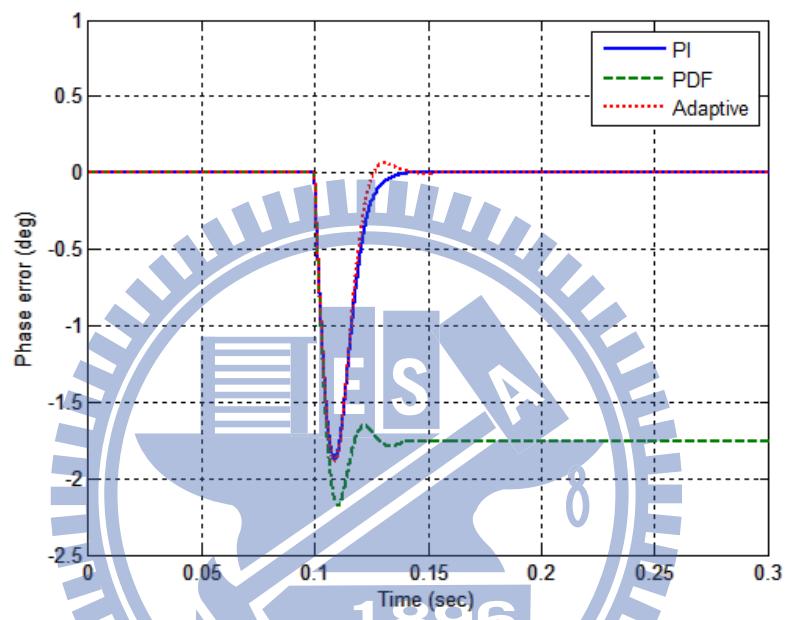

圖 4.24 和圖 4.25 為比例積分回授控制、虛擬微分回授控制以及自適性調整之比例積分回授控制在三相電壓發生頻率改變時相位誤差和估測頻率的結果，因比例積分控制器和自適性調整之比例積分控制器為型式二之系統，頻率變化的相位和頻率之誤差必定在有限時間內降至零。而虛擬微分回授控制僅是型式一的系統，所以三相電壓的頻率變動時其相位的穩態誤差將會存在一個固定的誤差值，在 1 Hz 的單位步階變化下相位的穩態誤差大約為 1.8 度。

圖 4.24 頻率步階變化對不同控制器相位誤差的影響

圖 4.25 頻率步階變化對不同控制系統估測頻率的影響

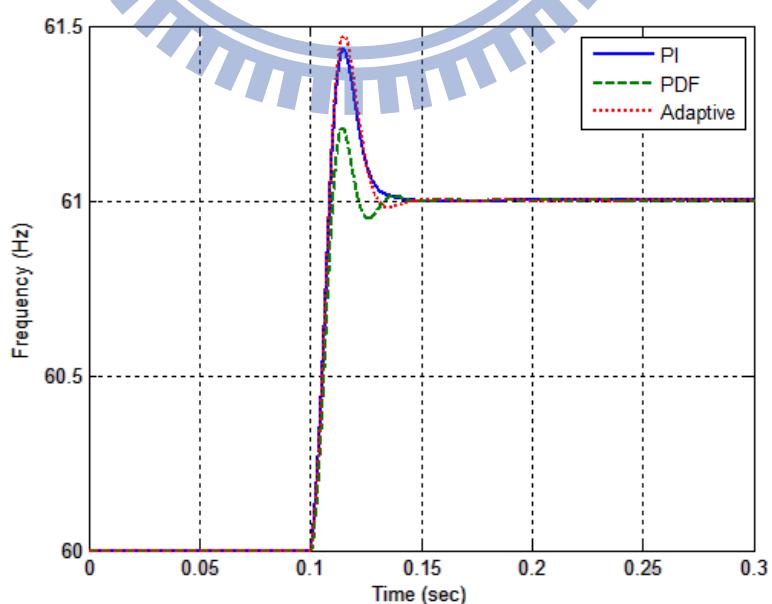

圖 4.26 和圖 4.27 則是比例積分回授控制以及兩種 Q 參數化設計之控制器於三相電壓發生頻率變化時的相位誤差及估測頻率的響應，不論是一維或二維自由度的 Q 參數化設計對於變化的響應速度皆較比例積分回授控制慢，不過因為 Q 參數化在設計時為型態二的系統所以對於頻率發生步階變化時，兩種設計方式的相位零穩態誤差都為零。

圖 4.26 頻率步階變化對 Q 參數化系統相位誤差的影響

圖 4.27 頻率步階變化對 Q 參數化系統估測頻率的影響

由輸入之三相電壓發生頻率變化的模擬可以發現，雖然虛擬微分回授控制對於頻率變化時估測頻率的響應速度較為快速，但由於鎖相迴路系統僅為型態一之系統，因此相位的穩態誤差將不會如比例積分控制或 Q 參數化所設計的控制器那般將穩態誤差降至零。表 4.8 表示不同控制器之間對於頻率改變的誤差絕對值積分、誤差平方積分以及相位穩態誤差間的比較。

表 4.8 頻率單位步階變化對於不同控制器之比較

|                | ISE                    | ISE                    | 相位穩態誤差(度) |

|----------------|------------------------|------------------------|-----------|

| 比例積分回授控制       | $4.838 \times 10^{-4}$ | $1.133 \times 10^{-5}$ | 0         |

| 虛擬微分回授控制       | $7.646 \times 10^{-3}$ | $2.357 \times 10^{-4}$ | 1.761     |

| 自適性調整之比例積分回授控制 | $4.657 \times 10^{-4}$ | $1.122 \times 10^{-5}$ | 0         |

| 一維自由度 Q 參數化設計  | $5.916 \times 10^{-4}$ | $1.343 \times 10^{-5}$ | 0         |

| 二維自由度 Q 參數化設計  | $6.013 \times 10^{-4}$ | $1.37 \times 10^{-5}$  | 0         |

### 4.3 模擬結果總結

由前一節的模擬分析可知運用於雙通用積分器之鎖相迴路的五種不同控制器中，當系統發生相位變化時在誤差絕對值積分和誤差平方積分兩個指標上表現最好的控制方法分別是虛擬微分回授控制和自適性調整之比例積分回授控制，這兩種控制方法又以虛擬微分回授控制的最大超越量、穩定時間較佳，而指標表示最差效果的是 Q 參數化設計之控制器。在高頻雜訊與不平衡故障的模擬中，高頻抑制能力中自適性調整之比例積分控制器效果最佳，虛擬微分回授控制的效果次佳，兩者間相差十分些微，而其餘三種控制器對高頻抑制的能力僅恰好滿足系統之規格。最後的模擬是當電網頻率發生變化時對不同控制器的影響，只有虛擬微分回授控制的穩態誤差不為零，其餘四種控制方式皆能準確地追蹤到頻率的變化，其性能的優劣由兩種誤差指標可知自適性調整之比例積分控制器依然為最佳而 Q 參數化設計的控制器最差。

## 五、結論

近日來新興能源發展蓬勃以及智慧型電網設計的實現，對於電網上的控制和估測的需求都逐漸變的更為重要，在電網上的鎖相迴路設計除了在理想狀態下可以準確地追蹤電網的頻率和相位外，在故障發生時其相位偵測的元件是需要有能力消除故障造成的影响，但若要將全部的故障種類都消去則是需付出相當高的代價，因此若當系統足以在故障發生時得到正向序訊號情況下，試著改變系統中的迴路濾波器和電壓控制震盪器，讓系統所估測之相位和頻率有良好的效果，成本上可以較為節省而且對於控制也保有足夠的準確度。

一般的鎖相迴路的控制器大多是利用比例積分回授和積分器作為實現的方式，而本論文提出的另外三種的控制方法中，虛擬微分回授控制由於結構簡單且和比例積分回授控制十分相似，最大的差別在於控制方式並不存在實際的零點，使得虛擬微分回授控制在相位變化時的追蹤有較快速的穩定時間、較小的最大超越量、較佳高頻抑制能力以及單位步階變化時誤差絕對值積分與誤差平方積分兩個指標也較小。雖然因為其開迴路轉移函數為型態一之系統，造成頻率的變化會存在非零的穩定誤差，但在電網系統中頻率變化的機率比起相位和不平衡故障的機率小以及變化較緩慢，所以虛擬微分回授控制在鎖相迴路中是一個可以考慮應用的控制器。

自適性調整之鎖相迴路利用隨著誤差改變阻尼係數的方式，在模擬中也證明可以有效地降低比例積分控制的最大超越量而且對高頻的抑制能力也很出色，雖然會犧牲些許的穩定時間，不過以誤差絕對值積分和誤差平方積分來看自適性調整的效果是非常好的。唯一的缺點便是越大的自適性係數會造成阻尼係數變動過大而讓系統在收斂上會變慢產生震盪的情形。

Q 參數化的設計在第四章的模擬驗證中證明其效果並沒有較比例積分來的好，不論是一維自由度或二維自由度的設計最大超越量雖然有下降的效果但是穩定時間也因此而拉長，使得誤差絕對值積分和誤差平方積分兩個指標並沒有明顯的減少，高頻諧波抑制的能力也沒有任何的改善，但或許在更高的自由維度或更高階的控制器設計有較好的

表現。

由於在電網鎖相迴路的設計中除了相位偵測的元件之外，迴路濾波器以及電壓控制震盪器兩個部分在高頻抑制以及響應速度上扮演著非常重要的腳色，本論文提出了三種的設計方式可以取代常用的比例積分回授控制，而且虛擬微分回授控制和自適性調整有更好的效果，希望本論文可以為以後鎖相迴路的相關研究者提供一些概念和幫助，也期望本論文對電網鎖相迴路設計的發展有一些貢獻並有其參考的價值。

## 參考資料

- [1] Rodriguez, P.; Pou, J.; Bergas, J.; Candela, J.I.; Burgos, R.P.; Boroyevich, D., "Decoupled Double Synchronous Reference Frame PLL for Power Converters Control," *Power Electronics, IEEE Transactions on* , vol.22, no.2, pp.584,592, March 2007

- [2] Rodriguez, P.; Luna, A.; Teodorescu, R.; Blaabjerg, F., "Grid Synchronization of Wind Turbine Converters under Transient Grid Faults using a Double Synchronous Reference Frame PLL," *Energy 2030 Conference, 2008. ENERGY 2008. IEEE* , vol., no., pp.1,8, 17-18 Nov. 2008

- [3] Rodriguez, P.; Luna, A.; Teodorescu, R.; Iov, F.; Blaabjerg, F., "Fault ride-through capability implementation in wind turbine converters using a decoupled double synchronous reference frame PLL," *Power Electronics and Applications, 2007 European Conference on* , vol., no., pp.1,10, 2-5 Sept. 2007

- [4] P. Xiao, K. A. Corzine, and G. K. Venayagamoorthy, "Multiple reference frame- based control of three-phase PWM boost rectifiers under unbalanced and distorted input conditions," *IEEE Trans. Power Electron.*, vol.23, no. 4, pp.2006-2017, July, 2008

- [5] Karimi-Ghartemani, M.; Iravani, M.R., "A new phase-locked loop (PLL) system," *Circuits and Systems, 2001. MWSCAS 2001. Proceedings of the 44th IEEE 2001 Midwest Symposium on* , vol.1, no., pp.421,424 vol.1, 2001

- [6] Karimi-Ghartemani, M.; Iravani, M.R., "A method for synchronization of power electronic converters in polluted and variable-frequency environments," *Power Systems, IEEE Transactions on* , vol.19, no.3, pp.1263,1270, Aug. 2004

- [7] Karimi-Ghartemani, M.; Mojiri, M.; Safaee, A.; Walseth, J.A.; Khajehhoddin, S.A.; Jain, P.; Bakhshai, A., "A New Phase-Locked Loop System for Three-Phase Applications," *Power Electronics, IEEE Transactions on* , vol.28, no.3, pp.1208,1218, March 2013

- [8] Rodriguez, P.; Teodorescu, R.; Candela, I.; Timbus, A.V.; Liserre, M.; Blaabjerg, F., "New Positive-sequence Voltage Detector for Grid Synchronization of Power Converters under Faulty Grid Conditions," *Power Electronics Specialists Conference, 2006. PESC '06. 37th IEEE* , vol., no., pp.1,7, 18-22 June 2006

- [9] Rodriguez, P.; Luna, A.; Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F., "Advanced Grid Synchronization System for Power Converters under Unbalanced and Distorted Operating Conditions," *IEEE Industrial Electronics, IECON 2006 - 32nd Annual Conference on* , vol., no., pp.5173,5178, 6-10 Nov. 2006

- [10] Rodriguez, P.; Luna, A.; Munoz-Aguilar, R.S.; Etxeberria-Otadui, I.; Teodorescu, R.; Blaabjerg, F., "A Stationary Reference Frame Grid Synchronization System for Three-Phase Grid-Connected Power Converters Under Adverse Grid Conditions," *Power Electronics, IEEE Transactions on* , vol.27, no.1, pp.99,112, Jan. 2012

- [11] Svensson, J.; Bongiorno, M.; Sannino, A., "Practical Implementation of Delayed Signal Cancellation Method for Phase-Sequence Separation," *Power Delivery, IEEE Transactions on* , vol.22, no.1, pp.18,26, Jan. 2007

- [12] Saccomando, G.; Svensson, J., "Transient operation of grid-connected voltage source converter under unbalanced voltage conditions," *Industry Applications Conference, 2001. Thirty-Sixth IAS Annual Meeting. Conference Record of the 2001 IEEE* , vol.4, no., pp.2419,2424 vol.4, Sept. 30 2001-Oct. 4 2001

- [13] Gonzalez-Espin, F.; Figueres, E.; Garcera, G., "An Adaptive Synchronous-Reference-Frame Phase-Locked Loop for Power Quality Improvement in a Polluted Utility Grid," *Industrial Electronics, IEEE Transactions on* , vol.59, no.6, pp.2718,2731, June 2012

- [14] Lee, K.; Lee, J.; Shin, D.; Yoo, D.; Kim, H., "A Novel Grid Synchronization PLL Method Based on Adaptive Low-Pass Notch Filter for Grid-connected PCS," *Industrial Electronics, IEEE Transactions on* , vol.PP, no.99, pp.1,1, 0

- [15] Xiaoqiang Guo; Weiyang Wu; Zhe Chen, "Multiple-Complex Coefficient-Filter-Based Phase-Locked Loop and Synchronization Technique for Three-Phase Grid-Interfaced Converters in Distributed Utility Networks," *Industrial Electronics, IEEE Transactions on* , vol.58, no.4, pp.1194,1204, April 2011

- [16] Limongi, L. R.; Bojoi, R.; Pica, C.; Profumo, F.; Tenconi, A., "Analysis and Comparison of Phase Locked Loop Techniques for Grid Utility Applications," *Power Conversion Conference - Nagoya, 2007. PCC '07* , vol., no., pp.674,681, 2-5 April 2007

- [17] Yazdani, D.; Pahlevaninezhad, M.; Bakhshai, A., "Three-phase grid synchronization techniques for grid connected converters in distributed generation systems," *Industrial Electronics, 2009. ISIE 2009. IEEE International Symposium on* , vol., no., pp.1105,1110, 5-8 July 2009

- [18] Gao, Siyu; Barnes, M., "Phase-locked loop for AC systems: Analyses and comparisons," *Power Electronics, Machines and Drives (PEMD 2012), 6th IET International Conference on* , vol., no., pp.1,6, 27-29 March 2012

- [19] Teodorescu, R.;Liserre M.;Rofriguez P.;, *Grid Converters for Photovoltaic and Wind Power Systems*. New York: IEEE-Wiley, 2011

- [20] N. Mohan, T. M. Undeland, and W. P. Robbins, *Power Electronics: Converters, Application, and Design, 3rd ed.* Hoboken, NJ: Wiley, 2003