# Effects of Minority-Carrier Response Behavior on Ge MOS Capacitor Characteristics: Experimental Measurements and Theoretical Simulations

Chao-Ching Cheng, Chao-Hsin Chien, *Associate Member, IEEE*, Guang-Li Luo, Yu-Ting Ling, Ruey-Dar Chang, *Member, IEEE*, Chi-Chung Kei, Chien-Nan Hsiao, Jun-Cheng Liu, and Chun-Yen Chang, *Life Fellow, IEEE*

Abstract-In this paper, we present MEDICI simulations of the admittance-voltage properties of Ge and Si MOS devices, including analyses of substrate conductance  $G_{

m sub}$  and high-low transition frequency  $f_{

m tran}$ , to explore the differences in the minority-carrier response. The Arrhenius-dependent  $G_{

m sub}$  characteristics revealed that a larger energy loss-by at least four orders of magnitude-occurs in Ge than in Si, reflecting the fast minority-carrier response rate, i.e., a higher value of  $f_{tran}$ . We confirmed that the higher intrinsic carrier concentration in Ge, through the generation/recombination of midgap trap levels as well as the diffusion mechanism, resulted in the onset of lowfrequency C-V curves in the kilohertz regime, accompanying the gate-independent inversion conductance. The experimental data obtained from Al<sub>2</sub>O<sub>3</sub>/Ge MOS capacitors were consistent with the values of  $G_{

m sub}$  and  $f_{

m tran}$  obtained from MEDICI predictions and theoretical calculations. In addition, upon increasing the inversion biases, we observed shifts in the  $G_{\rm sub}/f$  conductance peaks to low frequencies that mainly arose from the transition of minority carriers with bulk traps in the depletion layer. Meanwhile, we estimated that the bulky defects of ca.  $(2-4) \times 10^{15}$  cm<sup>-3</sup> exist in present-day low-doped Ge wafers.

Index Terms—Bulk trap, germanium (Ge), MEDICI simulation, minority-carrier response, MOS capacitor, substrate conductance.

### I. INTRODUCTION

ARIOUS high-k gate dielectrics, substrate materials, and device structures have been proposed to relieve the enormous scaling burden required to improve transistor perfor-

Manuscript received August 26, 2008; revised December 4, 2008. First published March 16, 2009; current version published April 22, 2009. This work was supported by the National Science Council of the Republic of China (Contract NSC94-2215-E009-066). The review of this paper was arranged by Editor H. S. Momose.

C.-C. Cheng, J.-C. Liu, and C.-Y. Chang are with the Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan.

C.-H. Chien is with the Department of Electronics Engineering, Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, and also with the National Nano Device Laboratory, Hsinchu 300, Taiwan.

G.-L. Luo is with the National Nano Device Laboratory, Hsinchu 300, Taiwan.

Y.-T. Ling and R.-D. Chang are with the Department and Graduate Institute of Electronic Engineering, Chang Gung University, Tao-Yuan 300, Taiwan.

C.-C. Kei is with the Instrument Technology Research Center, National Applied Research Laboratories, Hsinchu 300, Taiwan, and also with the National Tsing Hua University, Hsinchu 30013, Taiwan.

C.-N. Hsiao is with the Vacuum Technology Division, Instrument Technology Research Center, National Applied Research Laboratories, Hsinchu 300, Taiwan

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2016020

mance. High-k/Ge structure-based devices are considered new potential candidates to replace conventional Si MOSFETs for high-performance logic devices because of their high intrinsic carrier mobility. Much effort has been devoted to improve the high-k/Ge interface and junction leakage characteristics through both surface passivation [1]-[3] and process modification [4], [5]; several promising results have recently been demonstrated [6]-[8]. Interestingly, an uncommon electrical characteristic—the fast minority-carrier response—has been manifested during electrical measurements of Ge MOS capacitors; its variation with respect to the interface state response is also a noteworthy issue that requires clarification. In fact, many years ago, Nicollian and Brews [9] foresaw that it would be possible to observe an LF C-V curve for a narrow-gap material, such as Ge, at the standard HF used for traditional Si because of the higher intrinsic carrier concentration  $n_i$ . Such minority-carrier characteristics for capacitors deposited on Si substrates have been established and correlated to the effects of the temperature, doping concentration, and impurity contamination; however, similar studies using Ge substrates remain rare [10]–[12]. The influences of the doping concentration and the substrate type on this anomalous C–V behavior have been discovered in high-k/Ge MOS capacitors [13], [14]; the fundamental mechanisms were clarified through fitting of MOS-equivalent circuit models [10], [11] and measurements of Arrhenius-dependent conductance properties [12], respectively. In this paper, we utilized a 2-D MEDICI numerical simulator, accompanied by theoretical calculations, to comprehensively investigate the minority-carrier response—as functions of the doping concentration, measured frequency, and temperature—in terms of the electrical properties of Ge and Si MOS capacitors. We have also examined the underlying mechanistic differences through practical admittance measurements of atomic-layer-deposited (ALD) Al<sub>2</sub>O<sub>3</sub> thin films on both types of Ge substrates.

## II. MEDICI SIMULATION AND EXPERIMENTAL PROCEDURES

#### A. MEDICI Simulation Program

The computer simulation program MEDICI has been employed to predict the semiconductor device properties of several electronic structures, including HEMTs [15], MOSFETs [16],

silicon oxide high-k oxide silicon [17], photodetectors [18], and junction diodes [19]. By self-consistently solving the Poisson equation and the continuity equations in MEDICI, we can simulate the admittance properties of MOS structures containing SiO<sub>2</sub> (30 Å) and Al gates to examine the minority-carrier characteristics in Si and Ge. In addition, MEDICI makes it possible to perform simulations at relatively high frequencies and low temperatures by providing the appropriate physical models and parameters. Most importantly, the contributions of the interface states to both the capacitance and conductance loss at depletion can be omitted, which is beneficial to the analysis of admittance-voltage data in the inversion region. Apart from a large difference in the value of the energy bandgap for these two substrates, both carrier lifetime and mobility, which are dependent on the carrier concentration and the temperature, are critical in determining the minority-carrier generation behavior. Moreover, the bulk trap level at midgap was assumed for both substrates.

#### B. Fabrication of the MIS Capacitor

We prepared p- and n-type Ge wafers that were doped with Ga and Sb dopants at levels of ca.  $2 \times 10^{15}$  and ca.  $1 \times 10^{14}$  cm<sup>-3</sup>, respectively. The Si wafer, having a standard doping concentration of ca.  $1 \times 10^{16}$  cm<sup>-3</sup>, was also studied for comparison. All wafers were precleaned through a cyclic rinse with dilute hydrofluoric acid and deionized water. The Al<sub>2</sub>O<sub>3</sub> high-k layer was deposited using the ALD system at a substrate temperature of 100 °C; the physical thickness was ca.  $64(\pm 2)$  Å according to the established growth rate of ca. 1.06 Å/cycle. Trimethylaluminum [Al(CH<sub>3</sub>)<sub>3</sub>] and H<sub>2</sub>O were chosen as the metal source and oxidant, respectively; they were alternatively pulsed into the reactor for 1 s per pulse separated by a N<sub>2</sub> purge of 10 s to remove the redundant reactants. The top capacitor electrode was formed via a shadow mask by depositing electron-beam Pt at a film thickness of ca. 700 Å(area, ca.  $4 \times 10^{-4}$  cm<sup>2</sup>), whereas the backside contact was made through the thermal evaporation of Al. Finally, the entire MOS structure underwent forming gas annealing  $(N_2/H_2,\,90:10)$  at 300 °C for 30 min. The admittance-voltage characteristics were measured in the parallel mode using HP4284, and then they were corrected by excluding the series resistance and parasitic components. The temperature- and frequency-dependent electrical curves in depletion and weak inversion were investigated to explore the latent minority-carrier mechanism.

#### III. RESULTS AND DISCUSSION

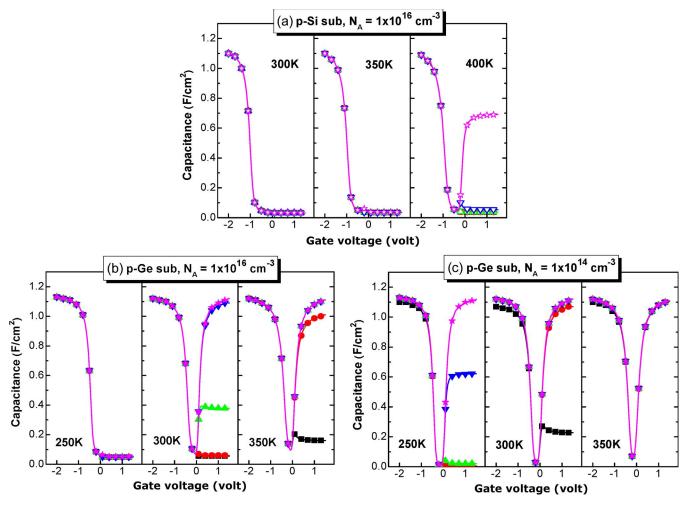

Figs. 1 and 2 present the simulated C-V and G-V characteristics of Al/SiO<sub>2</sub> gate stacks on p-Si and p-Ge substrates at various temperatures, respectively. It was observed that the dielectric on Si [Fig. 1(a)] obviously presented the LF C-V curves only when raising the temperature up to 400 K and reducing the frequency to as low as 100 Hz. In contrast, such LF curves readily occurred at 300 K for Ge systems in which the doping concentrations were  $10^{16}$  and  $10^{14}$  cm<sup>-3</sup> [Fig. 1(b) and (c), respectively]. We observed the minority-carrier behavior even at higher frequencies, e.g., 1 MHz, in the low-doped Ge.

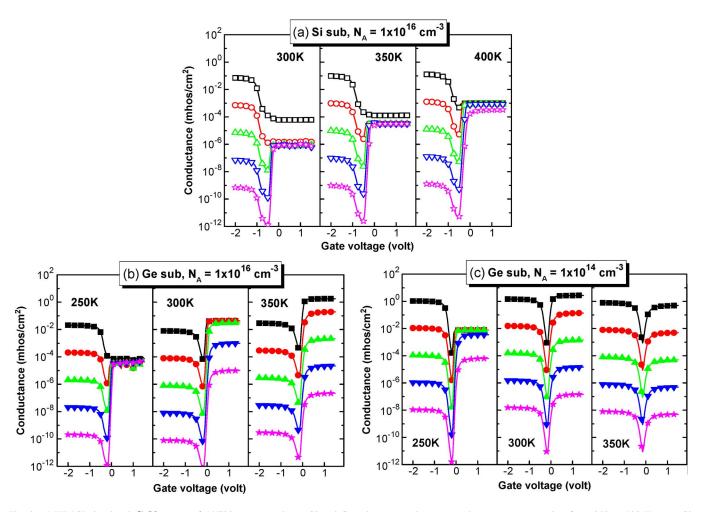

On the contrary, the complete HF C-V curves appeared only in the high-doped Ge at temperatures as low as 250 K. By examining the simulated conductance  $G_{\mathrm{mea}}$  in the Si case [Fig. 2(a)], the inversion conductance  $G_{inv}$  revealed frequency independence up to 100 kHz; the values increased by about two orders of magnitude as we increased the temperature from 300 to 400 K. From Fig. 2(b) and (c), the Ge counterpart reveals two distinct features: The  $G_{\mathrm{inv}}$  characteristics measured at low temperature (250 K) were identical to those in Si at high temperature (400 K); upon increasing the temperature to 350 K, the value of  $G_{inv}$  became proportional to the square of the angular frequency  $\omega$ , which is similar to the curves observed in accumulation. The resultant  $w^2$  dependence of G-V curves implied similar equivalent operation circuits in both accumulation and inversion for Ge MOS capacitors at higher temperatures, e.g., > 300 K. In general, the electrical differences in inversion between Ge and Si are dependent on the dominance of either the  $G_{inv}$  or  $wC_{inv}$  term, which are further correlated to the measured temperature, frequency, and properties of the substrate material. We will understand the minority-carrier conductance loss through the theoretical calculations of these two components, together with the following experimental findings. Note that the absence of interface states was assumed in simulation; hence, they did not contribute to the energy loss, thereby causing the onset of a deeper "dip" in depletion.

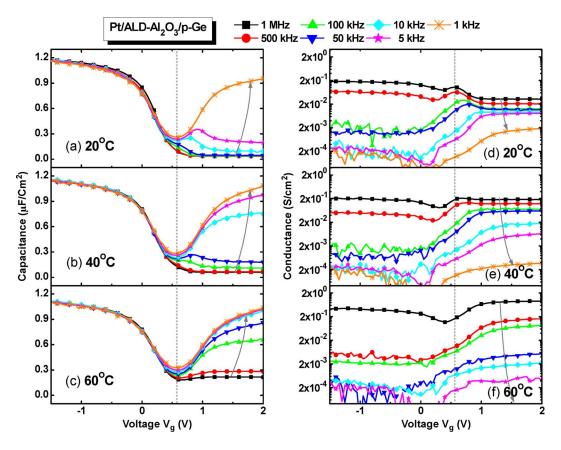

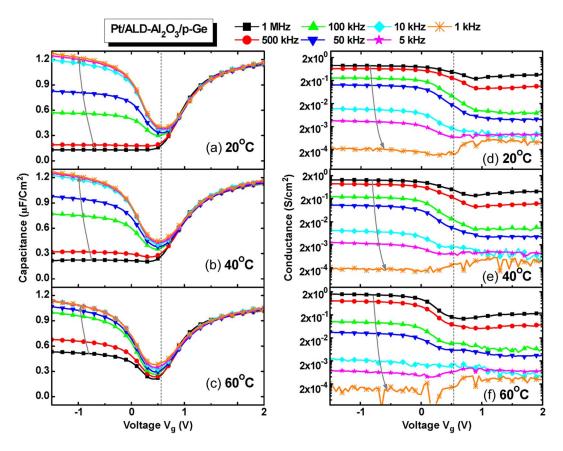

Figs. 3 and 4 display the measured C-V and G-V characteristics of Pt/ALD-Al $_2$ O $_3$  gate stacks deposited on p-Ge and n-Ge substrates, respectively. First, as illustrated in Figs. 3(a)–(c) and 4(a)–(c), the minority-carrier response occurred in C-V inversion for both types of Ge. The low-doped  $(10^{14}~{\rm cm}^{-3})$  n-Ge exhibited a relatively faster rate with respect to p-Ge  $(2\times 10^{15}~{\rm cm}^{-3})$ , which we attribute to the resultant high-minority-carrier concentration. Moreover, Figs. 3(d)–(f) and 4(d)–(f) display the gate-bias-independent values of  $G_{\rm inv}$  in Ge with more severe frequency dispersion upon increasing the measured temperature, unlike the exponential decline of the conductance curves in inversion for Si MOS capacitors (not shown here).

From the equivalent circuit model [20], the simulated values of  $G_{\rm sub}$  in inversion, i.e.,  $G_{\rm inv}$ , are the parallel combination of generation/recombination conductance  $G_{\rm gr}$  and diffusion conductance  $G_{\rm diff}$ , where  $G_{\rm gr}$  is due to the finite g-r within the depletion layer through the bulk traps, and  $G_{\rm diff}$  is due to the diffusion current of the minority carriers from the bulk to the edge of the depletion region. At lower temperatures,  $G_{\rm gr}$  is more significant [9], [20] and can be expressed using the equation

$$\frac{G_{\rm gr}}{A} = \frac{q}{\phi_S} \frac{n_i}{1} \frac{w}{\tau_T} \tag{1}$$

where  $\phi_S$  and w are the surface potential and depletion layer width in inversion, respectively, and  $\tau_T$  is the Shockley–Read–Hall lifetime determined by the density of g–r centers and the capture coefficients for electrons and holes, respectively. As the temperature further increases,  $G_{\rm diff}$  becomes

Fig. 1. MEDICI-simulated C-V curves of Al/SiO<sub>2</sub> gate stacks on Si and Ge substrates under measured temperatures ranging from 250 to 400 K. (a) p-Si,  $10^{16}$  cm<sup>-3</sup>. (b) p-Ge,  $10^{16}$  cm<sup>-3</sup>. (c) p-Ge,  $10^{16}$  cm<sup>-3</sup>. Note that the measured frequencies are labeled by solid symbols: square (1 MHz), circle (100 kHz), up-triangle (10 kHz), down-triangle (1 kHz), and star (100 Hz).

dominant because of the increasing function of  $n_i^2$  [9], [20], as revealed by the following equation:

$$\frac{G_{\text{diff}}}{A} = \frac{q^2}{kT} \frac{n_i^2}{N_{\text{mai}}} \frac{L_{\text{mir}}}{T_{\text{mir}}} = \frac{qN_{\text{mir}}\mu_{\text{mir}}}{L_{\text{mir}}}$$

(2)

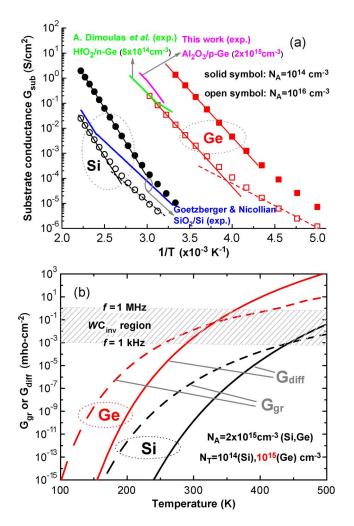

where  $N_{\mathrm{maj}}$  is the substrate doping concentration, and  $L_{\rm maj}(\tau_{\rm mir})$  and  $\mu_{\rm mir}$  are the diffusion length (lifetime) and mobility of minority carriers in the bulk material, respectively. To correctly observe the temperature dependence of the minority-carrier response behavior, all of the parameters are a function of the temperature in the calculations, except for  $\tau_T$ because of the weakly temperature dependence. In Fig. 5(a), we provide the simulated result of Arrhenius-dependent substrate conductance  $G_{\mathrm{sub}}$  in Si and Ge at various dopant concentrations  $(10^{14} \text{ and } 10^{16} \text{ cm}^{-3})$ , plotted with experimental data obtained from this and previous studies. Note that these values of  $G_{\mathrm{sub}}$ in inversion, i.e.,  $G_{inv}$ , can be extracted by directly subtracting the reactance of the insulator capacitor  $C_{\rm ins}$  from the commonly used parallel equivalent circuit. As seen for both Si and Ge cases, the simulated  $G_{\mathrm{sub}}$  curves can be divided into two stages: one dominated by  $G_{\mathrm{diff}}$  at high temperatures and the other by  $G_{\rm gr}$  at low temperatures. Most importantly, the values of  $G_{\rm inv}$ of the dielectric on Ge were larger than those on Si by at least

four orders of magnitude, which is indicative of a larger energy loss occurring in Ge. Both our data of  $Al_2O_3/p$ -Ge and the reported  $HfO_2/n$ -Ge structure [12] are in agreement with the simulation results for the  $SiO_2/p$ -Ge structure.

Using (1) and (2), we evaluated the respective components of  $G_{\rm gr}$  and  $G_{\rm diff}$  in  $G_{\rm inv}$  for these two substrates. A high bulk trap volume density  $N_T$  of  $10^{15}$  cm<sup>-3</sup> was assumed in Ge, which is relative to a value of  $10^{14}$  cm<sup>-3</sup> in Si, because Ge wafer quality has not yet developed to a satisfactory level. Fig. 5(b) reveals that the crossover temperature  $T_{\rm C}$  at which the transition is made from the g-r mechanism dominating to the diffusion-controlled process was ca. 330 K for p-Ge, which is close to the value of ca. 318 K characterized for high-k/n-Ge( $N_D$  = ca.  $7 \times 10^{14}$  cm<sup>-3</sup>) [12]. Relative to the value of  $T_{\rm C}$  of ca. 442 K for its Si counterpart, we ascribe the lower value for Ge to its higher value of  $n_i$ . Here, the deviations in the values of  $G_{\rm inv}$  evaluated via the MEDICI simulations and the theoretical calculation arose from the adopted material parameters, e.g., the  $N_T$  value. We also calculated the magnitude of the  $wC_{\rm inv}$  term for comparison with the values of  $G_{\rm inv}$  in these two substrates, where  $C_{\rm inv}$  is defined using the following [9]:

$$C_{\text{inv}} = \frac{\varepsilon_s \varepsilon_o}{\sqrt{2} L_D} \frac{n_i}{N_{\text{maj}}} \exp\left(\frac{-q\phi_S}{2kT}\right)$$

(3)

Fig. 2. MEDICI-simulated G–V curves of Al/SiO $_2$  gate stacks on Si and Ge substrates under measured temperatures ranging from 250 to 400 K. (a) p-Si,  $10^{16}$  cm $^{-3}$ . (b) p-Ge,  $10^{16}$  cm $^{-3}$ . (c) p-Ge,  $10^{16}$  cm $^{-3}$ . Note that the measured frequencies are labeled by solid symbols: square (1 MHz), circle (100 kHz), up-triangle (10 kHz), down-triangle (1 kHz), and star (100 Hz).

where  $\varepsilon_s$  is the substrate dielectric constant,  $L_D$  is the Debye length, and  $\phi_S$  is equal to  $2\phi_B$  at the threshold inversion point ( $\phi_B$  is the bulk potential). The calculations revealed that  $wC_{\rm inv}\gg G_{\rm inv}$  for the Si case at temperatures up to ca. 400 K; thus, the equivalent substrate circuit in inversion is often simplified further so that the depletion capacitance  $C_{\rm dep}$  changes in parallel only with the  $G_{\rm inv}$  term. This conclusion is only suitable for the Ge counterpart when the temperatures decrease below ca. 250 K; meanwhile, the opposite behavior, i.e.,  $wC_{\rm inv}\ll G_{\rm inv}$ , occurs at temperatures above ca. 350 K. That is, at intermediate temperatures (250–350 K), the minority-carrier response in Ge MOS capacitors is strongly dependent on the measured temperature and frequency.

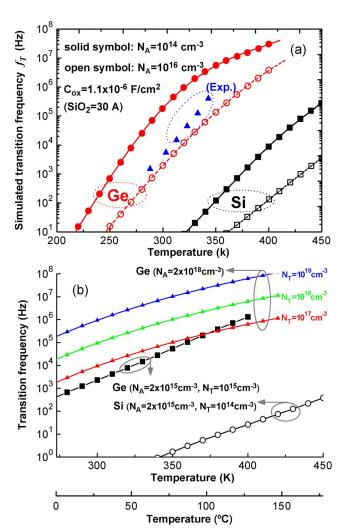

Here, we define the effective transition frequency  $f_{\rm tran}$ —at which the capacitance in inversion is midway between  $C_{\rm ins}$  and the HF capacitance  $C_{\rm hf}$ —as marking the onset of the LF C–V behavior. Our experimental data for  $f_{\rm tran}$  observed in Al<sub>2</sub>O<sub>3</sub>/p-Ge (Fig. 3) are within the MEDICI-simulated predictions in Fig. 6(a). The fast response rates in the Ge capacitors corresponded to the higher values of  $f_{\rm tran}$ , i.e., ca. 5 and 200 kHz at RT for Ge doped at  $10^{16}$  and  $10^{14}$  cm<sup>-3</sup>, respectively. Higher degrees of substrate doping and lower measured temperatures accordingly lowered the order of  $f_{\rm tran}$  due to the abatement of minority-carrier disturbance. From these studies,

we conclude that the two energy loss mechanisms, i.e.,  $G_{\rm gr}$  and  $G_{\rm diff}$ , are responsible for the supply of minority carriers to the inversion layer, providing LF-like C-V properties in the kilohertz regime. Previously, Bai *et al.*[14] reported an interesting phenomenon in HfO<sub>2</sub>/p-Ge: An increase in the degree of substrate doping from  $10^{15}$  to  $4\times10^{17}$  cm<sup>-3</sup> reduced the value of  $f_{\rm tran}$  from greater than 100 kHz to less than 10 kHz. Upon increasing the Ge concentration to  $3\times10^{18}$  cm<sup>-3</sup>, however, the value of  $f_{\rm tran}$  increased again to greater than 1 MHz, which is opposite to the trend that we expected. To explain this anomalous behavior, we correlated the value of  $f_{\rm tran}$  to the changes in  $G_{\rm inv}$  using the following equation [9]:

$$f_{\rm tran} = \frac{G_{\rm inv}}{2\pi C_{\rm ins}} \left( 1 - \frac{C_{\rm hf}}{C_{\rm ins}} \right) \tag{4}$$

using a value of  $C_{\rm ins}$  of 1.11  $\mu$ F/cm<sup>2</sup> as in our Al<sub>2</sub>O<sub>3</sub>/Ge cases, i.e., corresponding to the capacitance-equivalent thickness of 30 Å, and with the assumption that the number of bulk traps was proportional to the dopant concentration. We observe in Fig. 6(b) that Ge doped at  $10^{18}$  cm<sup>-3</sup> exhibited a relatively high value of  $f_{\rm tran}$  with respect to that of the low-doped Ge. Considering that the values of  $N_T$  ranging from ca.  $10^{14}$  to  $10^{16}$  cm<sup>-3</sup> have been reported for an intrinsic Ge epitaxial film [11]

Fig. 3. (a)–(c) C-V and (d)–(f) G-V curves of Pt/ALD-Al<sub>2</sub>O<sub>3</sub>/p-Ge MOS capacitors measured at temperatures of 20 °C, 40 °C, and 60 °C, respectively.

Fig. 4. (a)–(c) C–V and (d)–(f) G–V curves of Pt/ALD-Al<sub>2</sub>O<sub>3</sub>/n-Ge MOS capacitors measured at temperatures of 20 °C, 40 °C, and 60 °C, respectively.

Fig. 5. (a) Simulated Arrhenius-dependent substrate conductances  $G_{\rm sub}$  in Si and Ge at two dopant concentrations ( $10^{14}$  and  $10^{16}$  cm $^{-3}$ ), plotted with the experimental data obtained in this and previous studies [9], [12]. The simulated  $G_{\rm sub}$  data can be fitted by the (solid lines) diffusion conductances  $G_{\rm diff}$  and (dashed lines) g-r conductances  $G_{\rm gr}$ . (b) Calculations of temperature-dependent  $G_{\rm diff}$  and  $G_{\rm gr}$  in Si and Ge substrates having dopant concentrations of  $2\times 10^{15}$  cm $^{-3}$ . The values of  $N_T$  were  $10^{14}$  and  $10^{15}$  cm $^{-3}$  in Si and Ge, respectively. The values of the  $wC_{\rm inv}$  term were also calculated in terms of the frequency range 1 kHz–1 MHz.

and low-doped Ge substrates [21], [22], together with a maximum solid solubility of ca.  $10^{19}~\rm cm^{-3}$  for p-type dopants, we suspect that the highly doped p-Ge wafer might contain a large number of midgap traps (e.g.,  $10^{17}-10^{19}~\rm cm^{-3}$ ) inside the depletion layer [14], possibly arising from high degrees of Fe and Ni metal impurities [22], dopant precipitation, and/or metal—dopant combined defects. In reality, the density of bulky defects is governed not only by the wafer type and contamination by impurities but also by the device's fabrication [23], [24], in particular, the dielectric—Ge interface, which, in turn, influences the degree of the minority-carrier response on the measured frequency. In other words, the magnitude of  $G_{\rm gr}$  is probably comparable with that of  $G_{\rm diff}$ —possibly even exceeding it at higher temperatures—but  $G_{\rm diff}$  still immediately rules the inversion conductance  $G_{\rm inv}$  as the temperature increases further.

On the other hand, because the device equivalent circuit in inversion is similar to that in depletion, it is essential to

Fig. 6. (a) Simulated temperature-dependent transition frequencies  $f_{\rm tran}$  in Si and Ge at two dopant concentrations ( $10^{14}$  and  $10^{16}$  cm $^{-3}$ ), plotted along with our experimental data from Figs. 5 and 7. (b) Calculated temperature-dependent transition frequencies  $f_{\rm tran}$  in Si and Ge substrates, determined according to the material parameters in Fig. 8. Different values of  $N_T$  ( $10^{17}-10^{19}~{\rm cm}^{-3}$ ) were assumed for our highly doped Ge system.

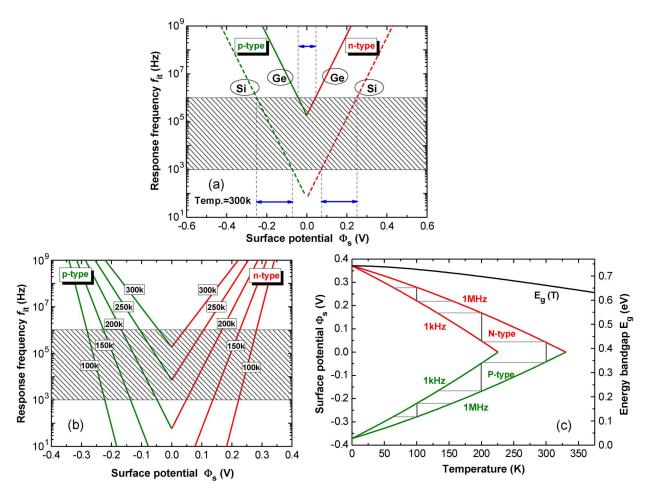

explore the differences between the minority-carrier-induced loss and the interface-state loss with respect to the measured frequency. Thus, we calculated the temperature dependence of the interface-state response frequency  $f_{\rm it}$  as a function of the surface potential using the following equation [9]:

$$f_{\rm it} = \frac{v_{\rm th}\sigma_{\rm cap}n_i}{\pi} \exp\left(\frac{-q\phi_S}{kT}\right)$$

(5)

where  $v_{\rm th}$  is the thermal velocity, and  $\sigma_{\rm cap}$  is the capture cross section. Supposing that the standard measured frequency is in the range  $10^3-10^6$  Hz, as depicted in Fig. 7(a), we can detect  $D_{\rm it}$  close to the midgap in Ge only at values of  $f_{\rm it}$  greater than  $10^5$  Hz, which is quite different from the  $D_{\rm it}$  response observed as low as  $10^3$  Hz in Si. Indeed, we observed depletion bumps at frequencies of 50–1000 kHz for the  $Al_2O_3/p$ -Ge capacitors (Fig. 3) and at 1–100 kHz for the  $Al_2O_3/p$ -Si capacitors (not shown here). In contrast, we did not observe any such bump for the corresponding n-Ge case (Fig. 4) because of the intense minority-carrier loss. The calculated results in Fig. 7(b) and (c) suggest that continuously decreasing the temperature from 300

Fig. 7. (a) Calculated response frequency  $f_{\rm it}$  of interface states plotted as a function of the surface potential  $\phi_S$  for Si and Ge capacitors at RT. (b) Temperature dependence of the plots of  $f_{\rm it}$  versus  $\phi_S$  for the Ge capacitor. The shadow region represents the standard frequency range 1 kHz–1 MHz used for the measurements. (c) Plot of the  $\phi_S$  dependence of observable  $D_{\rm it}$  in the Ge bandgap at various measured temperatures (within the standard frequency range). For comparison, the temperature dependence of the Ge bandgap is presented on the right-hand y-axis.

to 100 K is a practical means of extracting the overall distribution of  $D_{\rm it}$  within the Ge bandgap. Such a temperature-dependent conductance method is discussed in detail in a recent literature review by Martens *et al.*[10].

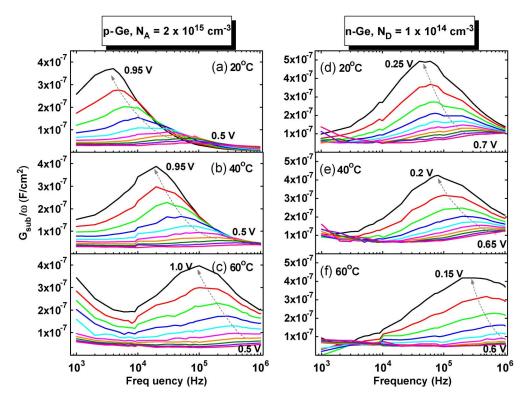

Fig. 8(a)–(f) displays the  $G_{

m sub}/f$  versus  $\log f$  characteristics for both types of Ge under gate biases ranging from the midgap to the inversion. We employed the statistical conductance model to estimate the values of the midgap  $D_{\rm it}$  for p-Ge and n-Ge of ca.  $7(\pm 1) \times 10^{11}$  and  $1.5(\pm 0.5) \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>, respectively. An interesting trend appeared for the devices biased into the inversion conditions: The  $G_{\rm sub}/f$  peak gradually moved to lower frequency, accompanied by an increased intensity, and upon raising the temperature; as a consequence, the overall conductance spectra shifted to higher frequency. Because of the presence of a high minority-carrier density, this phenomenon reveals that we must consider the communication of interface traps not only with majority carriers but also with minority carriers in Ge MOS capacitors. Even so, we still believe that such a shift in the frequency-dependent conductance peaks is mainly correlated to the  $G_{inv}$  loss within the substrate itself, overwhelming the  $D_{\rm it}$ -induced energy loss in inversion. We rationalize this behavior by considering the following observations. First, from the viewpoint of the  $f_{it}$  calculation, the  $G_{\rm sub}/f$  peaks appear far below  $10^5$  Hz, which is irrational for the  $D_{\rm it}$  response in Ge devices that are close to RT. Next, assuming that the transition of the surface minority carriers with  $D_{\rm it}$  dominates the conductance peaks in inversion, the resultant shorter lifetime in the charging/discharging of  $D_{\rm it}$  should shift them to higher frequency, rather than lower frequency, upon increasing the inversion biases. In fact, a  $\Lambda$ -shaped distribution in the trap time constant across the overall Ge bandgap was observed under a quite low temperature of 80 K when employing a full conductance measurement [10], in which the  $G_{

m sub}/f$  peaks shifted initially to lower frequency and subsequently to higher frequency with respect to the gate bias. In addition, according to the classical bulk trap model proposed by Nicollian and Brews [9], the resultant frequency of the  $G_{\rm sub}/f$  maximum should coincide with the value of  $f_{\text{tran}}$  observed in the C-V curves. Indeed, we observed that the conductance peaks (and values of  $f_{\rm tran}$ ) for p-Ge capacitors were located at ca. 4 (3), 20 (15), and 100 kHz (130 kHz) at 20 °C, 40 °C, and 60 °C, respectively, when  $V_a$  was equal to 1 V. The trends were also consistent for the n-Ge cases. In addition, we estimated the effective values of  $N_T$  simply from the corresponding magnitudes of  $G_{\text{sub}}/f$ by evaluating the depletion width swept out by 2-kT band bending; the resulting values of  $N_T$  for p-Ge and n-Ge were ca.  $3.9 \times 10^{15}$  and  $2.5 \times 10^{15}$  cm<sup>-3</sup>, respectively, reflecting high levels of bulky defects existing in these particular Ge wafers.

Fig. 8. Measured values of  $G_{\rm sub}/w$  plotted with respect to the log frequency for Pt/ALD-Al $_2$ O $_3$  gate stacks on (a)–(c) p-Ge and (d)–(f) n-Ge substrates at temperatures of 20 °C, 40 °C, and 60 °C, respectively.

#### IV. CONCLUSION

We have characterized the substrate conductance and transition frequency characteristics through MEDICI simulations and device experiments on Ge and Si substrates to understand their minority-carrier response behavior. The plot of the Arrhenius-dependent  $G_{\mathrm{sub}}$  indicated a larger energy loss occurring in Ge than in Si by at least four orders of magnitude, corresponding to the fast minority-carrier response rate. Our  $Al_2O_3/Ge$  MOS capacitors exhibited values of  $G_{\text{sub}}$  and  $f_{\text{tran}}$ that were both close to those of the MEDICI prediction. We have also validated that a high value of  $n_i$  in Ge, via the bulktrap generation/recombination as well as the diffusion from the bulk substrate, caused the onset of the LF C-V curves in the kilohertz regime and the gate-independent inversion conductance. In addition, we have suggested that the shift in the  $G_{\rm sub}/f$  conductance peaks to low frequency upon increasing the inversion bias is mainly due to the transition of minority carriers with bulk traps in the depletion layer, in which the value of  $N_T$  reached as high as ca.  $(2-4) \times 10^{15}$  cm<sup>-3</sup> in the lowdoped Ge.

#### REFERENCES

- [1] M. M. Frank, S. J. Koester, M. Copel, J. A. Ott, V. K. Paruchuri, and H. Shang, "Hafnium oxide gate dielectrics on sulfur-passivated germanium," *Appl. Phys. Lett.*, vol. 89, no. 11, pp. 112 905-1–112 905-3, Sep. 2006.

- [2] R. Xie, M. Yu, M. Y. Lai, L. Chan, and C. Zhu, "High-k gate stack on germanium substrate with fluorine incorporation," *Appl. Phys. Lett.*, vol. 92, no. 16, pp. 163 505-1–163 505-3, Apr. 2008.

- [3] N. Taoka, M. Harada, Y. Yamashita, T. Yamamoto, N. Sugiyama, and S.-I. Takagi, "Effects of Si passivation on Ge metal-insulatorsemiconductor interface properties and inversion-layer hole mobility," *Appl. Phys. Lett.*, vol. 92, no. 11, pp. 113511-1-113511-3, Mar. 2008.

- [4] E. Simoen, S. Sonde, C. Claeys, A. Satta, B. De Jaeger, R. Todi, and M. Meuris, "Processing factors impacting the leakage current and flicker noise of germanium p<sup>+</sup> – n junctions on silicon substrates," *J. Electrochem. Soc.*, vol. 155, no. 3, pp. H145–H150, 2008.

- [5] G. Nicholas, B. De Jaeger, D. P. Brunco, P. Zimmerman, G. Eneman, K. Martens, M. Meuris, and M. M. Heyns, "High-performance deep submicron Ge pMOSFETs with halo implants," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2503–2511, Sep. 2007.

- [6] P. Zimmerman, G. Nicholas, B. De Jaeger, B. Kaczer, A. Stesmans, L.-A. Ragnarsson, D. P. Brunco, F. E. Leys, M. Caymax, G. Winderickx, K. Opsomer, M. Meuris, and M. M. Heyns, "High performance Ge pMOS devices using a Si-compatible process flow," in *IEDM Tech. Dig.*, 2006, pp. 655–658.

- [7] K. Saraswat, C. O. Chui, K. Donghyun, T. Krishnamohan, and A. Pethe, "High mobility materials and novel device structures for high performance nanoscale MOSFETs," in *IEDM Tech. Dig.*, 2006, pp. 659–662.

- [8] N. Wu, Q. Zhang, N. Balasubramanian, D. S. H. Chan, and C. Zhu, "Characteristics of self-aligned gate-first Ge p- and n-channel MOSFETs using CVD HfO<sub>2</sub> gate dielectric and Si surface passivation," *IEEE Trans. Electron Devices*, vol. 54, no. 4, pp. 733–741, Apr. 2007.

- [9] E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology. New York: Wiley, 1982.

- [10] K. Martens, C. O. Chui, G. Brammertz, B. D. Jaeger, D. Kuzum, M. Meuris, M. M. Heyns, T. Krishnamohan, K. Saraswat, H. E. Maes, and G. Groeseneken, "On the correct extraction of interface trap density of MOS devices with high-mobility semiconductor substrates," *IEEE Trans. Electron Devices*, vol. 55, no. 2, pp. 547–556, Feb. 2008.

- [11] P. Batude, X. Garros, L. Clavelier, C. Le Royer, J. M. Hartmann, V. Loup, P. Besson, L. Vandroux, Y. Campidelli, S. Deleonibus, and F. Boulanger, "Insights on fundamental mechanisms impacting Ge metal oxide semiconductor capacitors with high-k/metal gate stacks," *J. Appl. Phys.*, vol. 102, no. 3, pp. 034 514-1–034 514-8, Aug. 2007.

- [12] A. Dimoulas, G. Vellianitis, G. Mavrou, E. K. Evangelou, and A. Sotiropoulos, "Intrinsic carrier effects in HfO<sub>2</sub>-Ge metalinsulator-semiconductor capacitors," *Appl. Phys. Lett.*, vol. 86, no. 22, pp. 223 507-1–223 507-3, May 2005.

- [13] C. O. Chui, F. Ito, and K. C. Saraswat, "Nanoscale germanium MOS dielectrics—Part I: Germanium oxynitrides," *IEEE Trans. Electron Devices*, vol. 53, no. 7, pp. 1501–1508, Jul. 2006.

- [14] W. Bai, N. Lu, P. Ritenour, M. L. Lee, D. A. Antoniadis, and D.-L. Kwong, "The electrical properties of HfO<sub>2</sub> dielectric on germanium

- and the substrate doping effect," *IEEE Trans. Electron Devices*, vol. 53, no. 10, pp. 2551–2558, Oct. 2006.

- [15] J.-C. Lin, P.-Y. Yang, and W.-C. Tsai, "Simulation and analysis of metamorphic high electron mobility transistors," *Microelectron. J.*, vol. 38, no. 2, pp. 251–254, Feb. 2007.

- [16] M. Zhu, P. Chen, R. K. Y. Fu, W. Liu, C. Lin, and P. K. Chu, "Simulation of suppression of floating-body effect in partially depleted SOI MOSFET using a  $\mathrm{Si}_{1-x}\mathrm{Ge}_x$  dual source structure," *Mater. Sci. Eng., B*, vol. 114–115, pp. 264–268, 2004.

- [17] Y. N. Yeo, Y. Q. Wang, S. K. Samanta, W. J. Yoo, G. Samudra, D. Gao, and C. C. Chong, "Simulation of trapping properties of high-k material as the charge storage layer for flash memory application," *Thin Solid Films*, vol. 504, no. 1/2, pp. 209–212, May 2006.

- [18] N. V. Sochinskii, M. Lozano, G. Pellegrini, and M. Ullan, "Simulation of CdTe: Ge crystal properties for nuclear radiation detectors," *Nucl. Instrum. Methods Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip.*, vol. 568, no. 1, pp. 451–454, Nov. 2006.

- [19] N. Keskitalo, A. Hallen, F. Masszi, and J. Olsson, "Simulation of forward bias injection in proton irradiated silicon pn-junctions," *Solid State Electron.*, vol. 39, no. 7, pp. 1087–1092, Jul. 1996.

- [20] Y. Nemirovsky and L. Bloom, "Admittance measurements of metal-insulator-semiconductor devices in p-type HgCdTe," J. Vac. Sci. Technol. A, Vac. Surf. Films, vol. 6, no. 4, pp. 2710–2715, Jul./Aug. 1988.

- [21] E. Simoen, C. Claeys, S. Sioncke, J. V. Steenbergen, M. Meuris, S. Forment, J. Vanhellemont, P. Clauws, and A. Theuwis, "Lifetime and leakage current considerations in metal-doped germanium," *J. Mater. Sci.: Mater. Electron.*, vol. 18, no. 7, pp. 799–804, Jul. 2007.

- Mater. Electron., vol. 18, no. 7, pp. 799–804, Jul. 2007.

[22] J. Vanhellemont and E. Simoen, "Brother silicon, sister germanium," J. Electrochem. Soc., vol. 154, no. 7, pp. H572–H583, 2007.

- [23] C. O. Chui, F. Ito, and K. C. Saraswat, "Nanoscale germanium MOS dielectrics—Part II: high-k gate dielectrics," *IEEE Trans. Electron Devices*, vol. 53, no. 7, pp. 1509–1516, Jul. 2006.

- [24] A. Dimoulas, D. P. Brunco, S. Ferrari, J. W. Seo, Y. Panayiotatos, A. Sotiropoulos, T. Conard, M. Caymax, S. Spiga, M. Fanciulli, C. Dieker, E. K. Evangelou, S. Galata, M. Houssa, and M. M. Heyns, "Interface engineering for Ge metal-oxide-semiconductor devices," *Thin Solid Films*, vol. 515, no. 16, pp. 6337–6343, Jun. 2007.

Chao-Ching Cheng received the B.S. degree in electronic engineering in 2003 from Chang-Gung University, Tao-Yuan, Taiwan, and the M.S. degree in electronic engineering in 2005 from the National Chiao-Tung University (NCTU), Hsinchu, Taiwan, where he is currently working toward the Ph.D. degree related to Ge and III–V MOSFETs in the Institute of Electronics.

His main research interests include the study of the interface and device properties of Ge and III–V substrates integrating with high-k materials, heteroepi-

taxial technology, and electrical characteristics of SiGe film in various III-V materials.

Chao-Hsin Chien (M'04–A'05) was born in 1968. He received the B.S., M.S., and Ph.D. degrees in electronics engineering from the National Chiao-Tung University (NCTU), Hsinchu, Taiwan, in 1990, 1992, and 1997, respectively. His Ph.D. dissertation research focused on plasma-induced charging damage on deep-submicrometer devices with ultrathin gate oxides.

In 1999, he was with the National Nano Device Laboratory, Hsinchu, as an Associate Researcher. He is currently an Associate Professor with the Depart-

ment of Electronics Engineering, Institute of Electronics, NCTU. His research interests and activities include high- $\kappa$  dielectric, novel nonvolatile memory devices, organic devices, and nanowires.

**Guang-Li Luo** received the Ph.D. degree in solidstate physics from the Chinese Academy of Sciences, Beijing, China, in 1997.

From 1997 to 2001, he was a Faculty Member with the Institute of Microelectronics, Tsinghua University, Beijing. In 2002, he was with the Microelectronics and Information Systems Research Center, National Chiao Tung University, Hsinchu, Taiwan, as an Assistant Researcher and then as an Associate Researcher. Since July 2005, he has been an Associate Researcher with the National Nano Device

Laboratory, Hsinchu. His research interests include SiGe epitaxy and related devices.

Yu-Ting Ling, photograph and biography not available at the time of publication.

Ruey-Dar Chang (S'89–M'90–S'96–M'98) was born in Taichung, Taiwan, in 1966. He received the B.S. degree in materials engineering from the National Cheng Kung University, Tainan, Taiwan, in 1988, the M.S. degree from the National Chiao Tung University, Hsinchu, Taiwan, in 1990, and the Ph.D. degree in electrical engineering from the University of Texas, Austin, in 1998.

From 1990 to 1994, he was with the Electronics Research and Service Organization/Industrial Technology Research Institute, Hsinchu, where he was

engaged in the development of process simulation and DRAM devices under the Submicron Project. In 1994, he joined the Vanguard International Semi-conductor Corporation, Hsinchu, where he was responsible for the DRAM device design and TCAD. Since 1998, he has been with the Department and Graduate Institute of Electronic Engineering, Chang Gung University, Tao-Yuan, Taiwan, where he is an Assistant Professor. He currently works on CMOS process modeling, doping profile characterization, TFT technology modeling, and power devices.

Chi-Chung Kei was born in Taiwan. He received the B.S. and M.S. degrees in materials science engineering in 2000 and 2002, respectively, from the National Tsing Hua University (NTHU), Hsinchu, Taiwan, where he is currently working toward the Ph.D. degree in materials science engineering.

He is currently an Associate Researcher with the Instrument Technology Research Center, National Applied Research Laboratories, Hsinchu. His research interests include the developments of atomic layer deposition and UHV metal-organic chemical

vapor deposition systems, and the fabrication and characterization of III–V compound semiconductors, high-k dielectrics, and nanostructured materials.

**Chien-Nan Hsiao** received the Ph.D. degree in materials science and engineering from Taiwan University, Taipei, Taiwan, in 2000.

He is currently a Researcher and the Director of the Vacuum Technology Division, Instrument Technology Researcher Center, National Applied Science Laboratories, Hsinchu, Taiwan. His research interests include synthesis and characterization thin-film materials and vacuum technology.

**Jun-Cheng Liu** was born in Kaohsiung, Taiwan. He received the M.S. degree in electronics engineering from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 2007.

He is currently with the Institute of Electronics, NCTU. His research interests focus on material analysis, device fabrication, and electrical measurements of the ALD high-*k*/Ge MOSFETs.

Chun-Yen Chang (S'69–M'70–SM'81–F'88–LF'05) was born in Feng-Shan, Taiwan. He received the B.S. degree in electrical engineering from the National Cheng Kung University (NCKU), Tainan, Taiwan, in 1960 and the M.S. and Ph.D. degrees from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1962 and 1969, respectively.

He has profoundly contributed to the areas of microelectronics, microwave, and optoelectronics, including the invention of the method of low-pressure MOCVD using triethylgallium to fabricate LED,

laser, and microwave devices. He pioneered works on Zn incorporation (1968), nitridation (1984), and fluorine incorporation (1984) in SiO<sub>2</sub> for ULSIs, as well as in the charge transfer in semiconductor-oxide-semiconductor system (1968), carrier transport across metal-semiconductor barriers (1970), and the theory of metal-semiconductor contact resistivity (1971). In 1963, he joined the NCTU to serve as an Instructor, establishing a high vacuum laboratory. In 1964, he and his colleagues established the nation's first and state-of-the-art Semiconductor Research Center, NCTU, with a facility for silicon planar device processing, where they made the nation's first Si planar transistor in April 1965 and, subsequently, the first IC and MOSFET in August 1966, which strongly forms the foundation of Taiwan's hi-tech development. From 1977 to 1987, he single-handedly established a strong electrical engineering and computer science program at the NCKU, where GaAs,  $\alpha$ -Si, and poly-Si research was established in Taiwan for the first time. He consecutively served as the Dean of Research (1987–1990), the Dean of Engineering (1990–1994), and the Dean of Electrical Engineering and Computer Science (1994–1995). Simultaneously, from 1990 to 1997, he served as the Founding President of the National Nano Device Laboratories, Hsinchu. Since August 1, 1998, he has been the President with the Institute of Electronics, NCTU. In 2002, to establish a strong system design capability, he initiated the "National program of system on chip," which is based on a strong Taiwanese semiconductor foundry.

Dr. Chang is a Member of Academia Sinica (1996) and a Foreign Associate of the National Academy of Engineering, U.S. (2000). He was a recipient of the 1987 IEEE Fellow Award, the 2000 Third Millennium Medal, and the 2007 Nikkei Asia Prize for Science category in Japan and regarded as "the father of Taiwan semiconductor industries."