# 國立交通大學

電子工程學系電子研究所

博士論文

-

低功耗前瞻靜態隨機記憶體之測試方法與錯誤模型

Test methodology and fault modeling for

low-power advanced SRAM

# 研究生:林政偉 指導教授:趙家佐

m

中華民國一〇二年八月

# 低功耗前瞻靜態隨機記憶體之測試方法與錯誤模型 Test methodology and fault modeling for low-power advanced SRAM

研究生:林政偉 Student : Chen-Wei Lin Advisor: Mango Chia-Tso Chao 指導教授:趙家佐 國立交通大學 電機學院 電子工程學系 電子研究所 博士論文 39 A Dissertation Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical and Computer Engineering National Chiao-Tung University in partial Fulfillment of the Requirements for the Degree of **Doctor of Philosophy** in **Electronics Engineering** August 2013 Hsinchu, Taiwan, Republic of China

中華民國一〇二年八月

低功耗前瞻靜態隨機記憶體之測試方法與錯誤模型

研究生:林政偉 指導教授:趙家佐

#### 國立交通大學

電機學院 電子工程學系 電子研究所

#### 摘要

對於新開發的低功耗和前瞻靜態隨機存記憶體(SRAM),製造缺陷在其上 所造成的錯誤行為往往比對於在傳統 SRAM 上造成之錯誤行為來說較為複雜。 在相關的研究並未被充分的討論的情況下,許多針對傳統 6T SRAM 之一般 性的測試方式都未被驗證,也因此無法滿足對於在製造與設計堅固和可靠 的低功耗 SRAM 與未來的製程技術配合的測試需要。在這篇論文中,我討論 了對於各種已在科技文獻中發表的低功耗 SRAM 設計的測試。針對不同的記 憶胞結構我進行了分類並分析相對應的錯誤行為,並開發至少四個可以處 理的不同的低功耗 SRAM 測試需要的測試方法。除了討論各種記憶胞結構, 我也延伸了從傳統的平面 CMOS 元件的討論,到目前極具前瞻性的 FinFET 元件,以及特殊的薄膜電晶體元件。對於該些前瞻的 SRAM,我進行了元件 等級的 TCAD 模擬、SPICE 模型提取和針對多晶矽通道模型建立之應用等, 以進行驗證所提出的測試方法與最佳化前瞻 SRAM 設計的相關參數。

# Test methodology and fault modeling for low-power advanced SRAM

Student : Chen-Wei Lin Advisor : Mango Chia-Tso Chao

## Department of Electronics Engineering

and Institute of Electronics

#### National Chiao-Tung University

#### Abstract

For the new-developed low-power and advanced SRAMs, the fault behaviors due to manufacture defects are often relatively complicated when being compared to the traditional 6T SRAM. And the complete analysis has not been fully discussed. As a result, the test effectiveness of conventional test methods for the 6T SRAM may not satisfy the need for producing robust and reliable low-power SRAMs with future technologies.

In this thesis, I have discussed the testing of various low-power SRAM designs which have been published in literatures. By categorizing the different cell structures and analyzing the corresponding faulty behaviors, I have developed at least four new test methods which can deal with the diverse needs of the low-power SRAM testing. In addition to including the various cell structures, I also extend the discussion to the SRAM which comes with the specific peripheral write-assist circuitry. For the data-aware write-assist SRAM,

a high-fault-coverage and time-efficient test method is proposed. Finally, the discussions of the special Gate-Oxide Short defects at the traditional planar bulk CMOS and the promising FinFET technology are also covered. For those advanced SRAMs, device-level TCAD simulation, SPICE model extraction, and circuit-level defect model establishing were proceeded to either verify the proposed test methods or to achieve high yield optimized advanced SRAM designing.

## Acknowledgements

First and foremost, I would like to express my greatest appreciation to my advisor, Professor Chia-Tso Chao (Mango, 趙家佐) for his suggestions and guidance. He is extremely patient to me in everything no matter for the research discussion or life planning. I also would like to thank my labmates: Hung-Hsin Chen, Hao-Yu Yang, and Chin-Yuan Huang. They assist me in dealing with the weighty experiments and research tasks for the past five years.

Finally, I appreciate my parents and my wife for the constant comfort and encouragement. Chen-Wei Lin

1111

National Chiao-Tung University

Im

2013, August

## Contents

| 中文摘要                                                 | Ι                 |

|------------------------------------------------------|-------------------|

| English Abstract                                     | II                |

| Acknowledge                                          | IV                |

| List of Tables                                       | IX                |

| List of Figures                                      | XII               |

| 1 Introduction                                       | 1                 |

| 2 Fault Models and Test Methods for Subthreshold SRA | Ms3               |

| 2.1 Categorization of Subthreshold SRAM Designs      | 5                 |

| 2.2 Test Methods for Stability Faults                | 6                 |

| 2.2.1. Background of Stability Faults                | 6                 |

| 2.2.2. Read Equivalent Stress                        | 7                 |

| 2.2.3. Severe Write                                  | .97               |

| 2.2.4. High-V-Write/Low-V-Read                       | 9                 |

| 2.3 Analysis of Open Defects in Type-A Subthresho    | ld SRAMs9         |

| 2.3.1 Design Overview of Type-A Subth                | reshold SRAMs9    |

| 2.3.2 Impact of Open Defects on Ty                   | pe-A Subthreshold |

| SRAMs                                                | 11                |

| 2.3.3 Effectiveness of Test Methods for T            | ype-A Designs13   |

| 2.4 Analysis of Open Defects in Type-B Subthreshold  | l SRAMs14         |

| 2.4.1 Introduction of Type-B Subthreshold            | d SRAMs14         |

| 2.4.2 Impact of Open Defects on Ty                   | pe-B Subthreshold |

| SRAMs                                                | 16                |

| 2.4.3 Effectiveness of Test Methods for T            | ype-B Designs17   |

| 2.5 Analysis of Open Defects in Type-C Subthreshold  | d SRAMs19         |

|   | 2.5.1 Introduction of Type-C Subthreshold SRAMs19                          |

|---|----------------------------------------------------------------------------|

|   | 2.5.2 Impact of Open Defects on Type-C Subthreshold                        |

|   | SRAMs21                                                                    |

|   | 2.5.3 Effectiveness of Test Methods for Type-C Designs22                   |

|   | 2.6 Address Decoder Faults in Subthreshold SRAMS24                         |

|   | 2.6.1 Type-A Subthreshold SRAM24                                           |

|   | 2.6.2 Type-B Subthreshold SRAM                                             |

|   | 2.6.3 Type-C Subthreshold SRAM                                             |

|   | 2.6.4 Address-Decoder Faults with Sequential Behavior30                    |

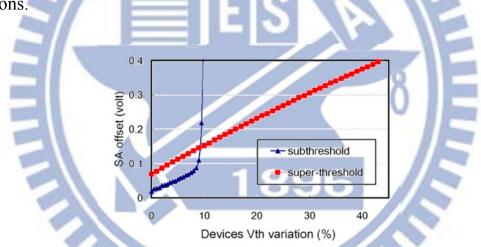

|   | 2.7 Fault Models for Sense Amplifier under Subthreshold Operations30       |

|   | 2.7.1 Open Defects                                                         |

|   | 2.7.2 V <sub>th</sub> Mismatch                                             |

|   | 2.8 Impact of Temperature at Test                                          |

|   | 2.9 Conclusion                                                             |

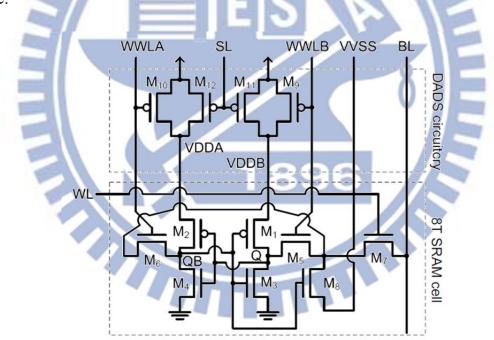

| 3 | Testing of a Low-V <sub>MIN</sub> Data-Aware Dynamic-Supply 8T SRAM37      |

|   | 3.1 Preliminary of the Low- $V_{MIN}$ Date-Aware Dynamic-Supply 8T         |

|   | SRAM                                                                       |

|   | 3.2 Using March C- to Detect Open Defects in the Low-V_{MIN} DADS 8T       |

|   | SRAM                                                                       |

|   | 3.3 Test Methods for the Open Defects at the Cross-Couple Inverters44      |

|   | 3.3.1 Floating Bit-Line Attacking Method44                                 |

|   | 3.3.2 Proposed Method: Self-Loop Attacking Method46                        |

|   | 3.3.3 Test Methods Comparison                                              |

|   | 3.4 Testing for The Open Defects in the DADS Circuitry50                   |

|   | 3.5 Conclusion                                                             |

| 4 | A Novel Circuit-level Model for Gate Oxide Short and its Testing Method in |

|   | SRAMs            |                                                             | 54    |

|---|------------------|-------------------------------------------------------------|-------|

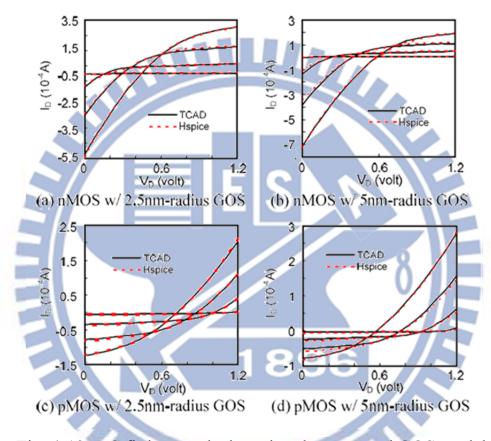

|   | 4.1 Experimen    | ntal Setup for TCAD and HSPICE                              | 57    |

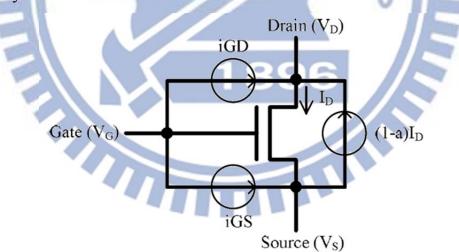

|   | 4.2 Previous C   | Circuit-Level GOS Models                                    | 59    |

|   | 4.2.1            | Bi-dimensional model                                        | 59    |

|   | 4.2.2            | Nonlinear non-split model 1 - JET_03                        | 60    |

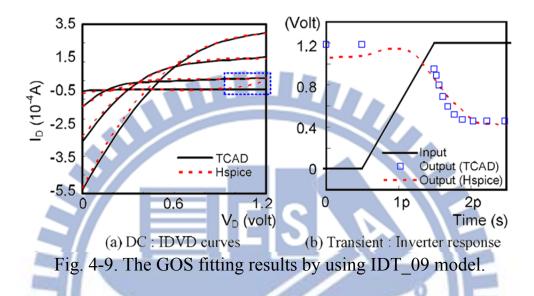

|   | 4.2.3            | Nonlinear non-split model 2 - IDT_09                        | 62    |

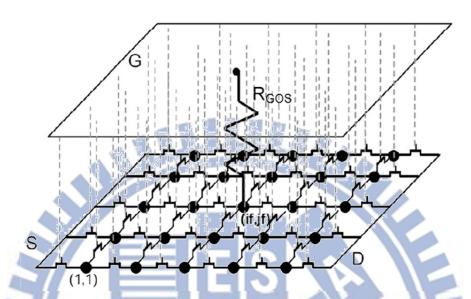

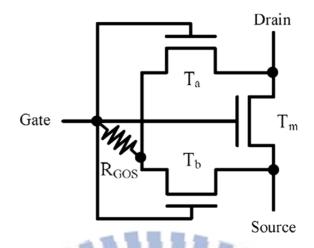

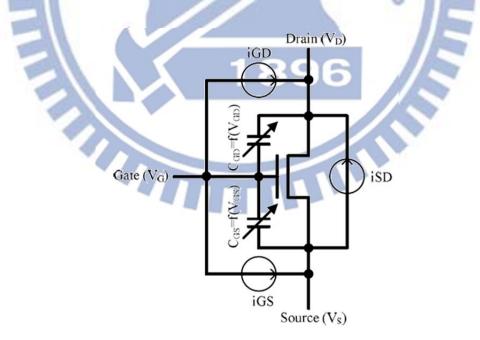

|   | 4.3 Proposed (   | GOS Model and The Comparison With Previous Works            | 64    |

|   | 4.3.1            | Proposed GOS model                                          | 64    |

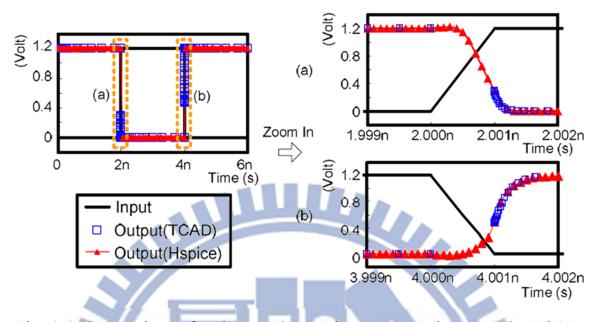

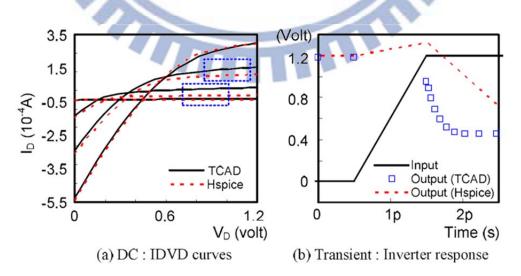

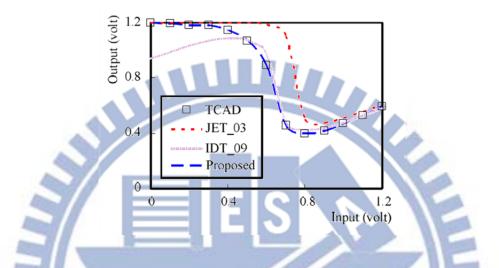

|   | 4.3.2            | Simulation comparisons on DC characteristics                | 66    |

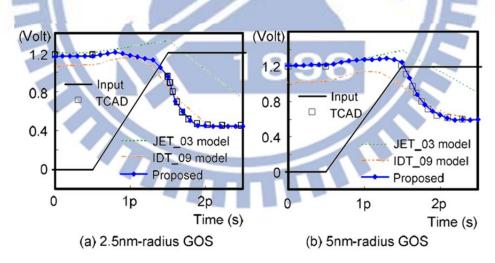

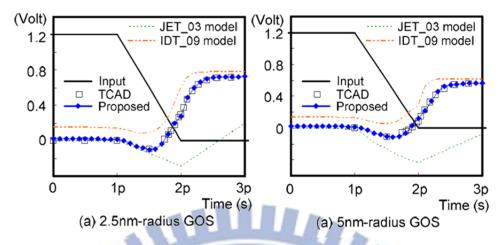

|   | 4.3.3            | Simulation comparisons on transient characteristics         | 67    |

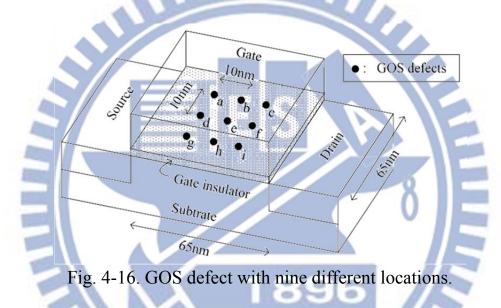

|   | 4.3.4            | Modeling GOS defects with different locations               | 70    |

|   | 4.4 Testing GO   | OS in SRAMs                                                 | 71    |

|   | 4.4.1            | Previous test methods                                       |       |

|   | 4.4.2            | Proposed DFT write operation                                | 75    |

|   | 4.4.3            | Detailed simulation result for detecting GOS                | 76    |

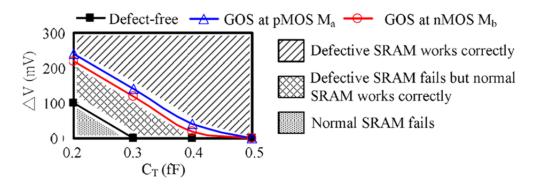

|   | 4.4.4            | Finding valid setting for $C_T$ and $\Delta V$              | 78    |

|   | 4.4.5            | Comparison with other GOS models in use                     | 79    |

|   | 4.5 Implement    | tation of The Proposed Test Method & Its Optimization       | 80    |

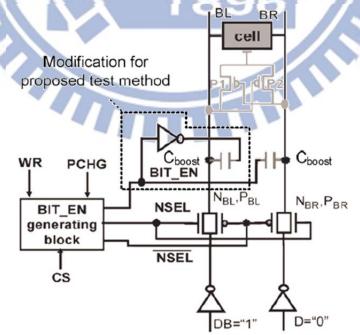

|   | 4.5.1            | Implementation and area overhead of DfT                     | 80    |

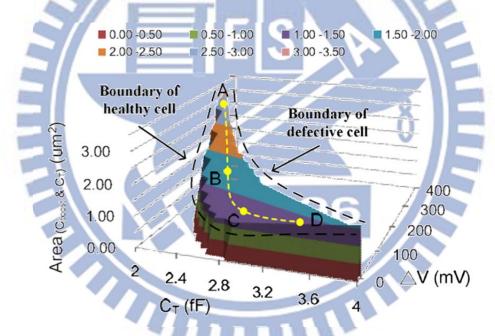

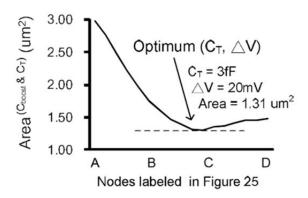

|   | 4.5.2            | Optimum ( $C_T$ , $\Delta V$ ) for minimizing area overhead | 82    |

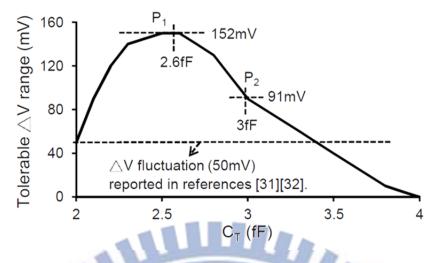

|   | 4.5.3            | Maximization of tolerable $\Delta V$ range against the pro- | ocess |

|   | Va               | ariation                                                    | 84    |

|   | 4.6 Conclusion   | n                                                           | 85    |

| 5 | Investigation of | of Gate Oxide Short in FinFETs and the Test Method          | s for |

|   | FinFET SRAM      | ۹s                                                          | 87    |

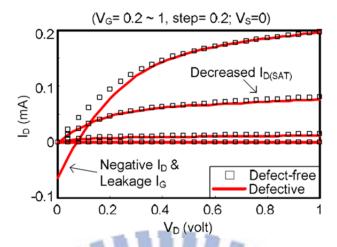

|   | 5.1 GOS Faul     | t Behaviors in Planar Bulk MOSFETs                          | 89    |

|     | 5.2 Experimen  | nt Setup90                                       |

|-----|----------------|--------------------------------------------------|

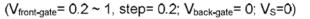

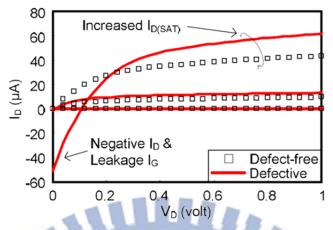

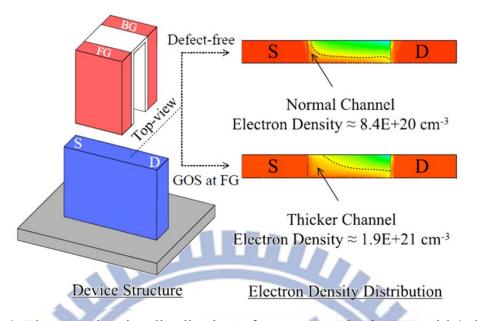

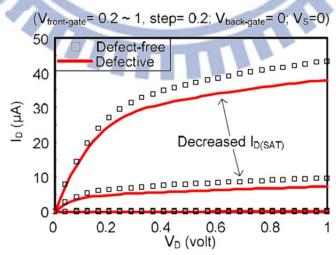

|     | 5.3 GOS Faul   | t Behaviors in FINFETs91                         |

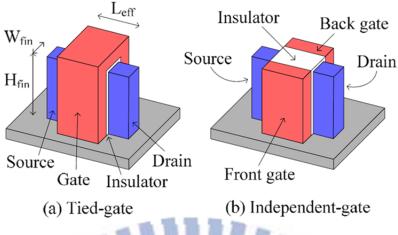

|     | 5.3.1          | Tied-Gate FinFET91                               |

|     | 5.3.2          | Independent-Gate FinFET92                        |

|     | 5.3.3          | Short Summary                                    |

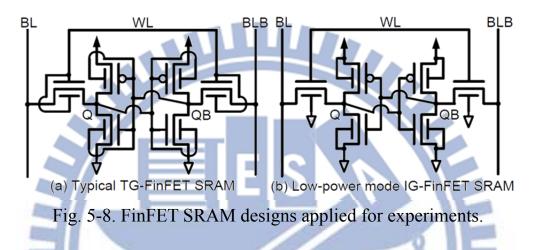

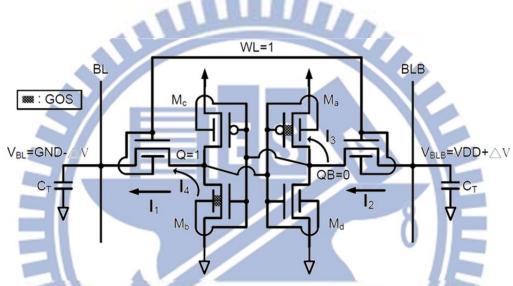

|     | 5.4 Testing of | GOS in FinFET SRAMs95                            |

|     | 5.4.1          | Traditional Tests: March Test and IDDQ Test96    |

|     | 5.4.2          | Proposed Test method for TG-FinFET based SRAM98  |

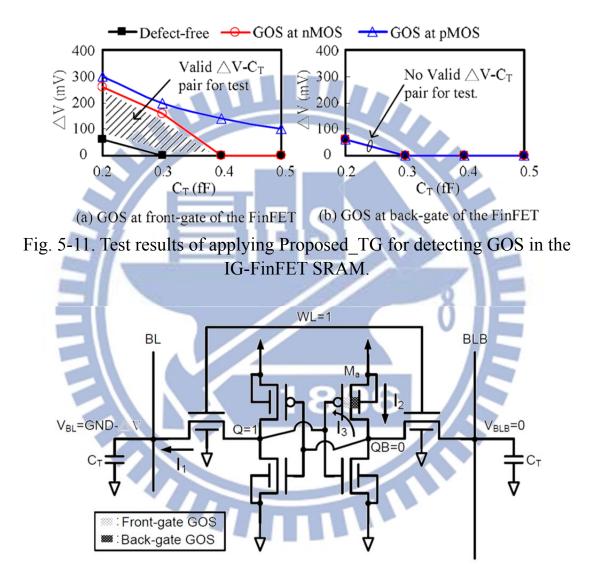

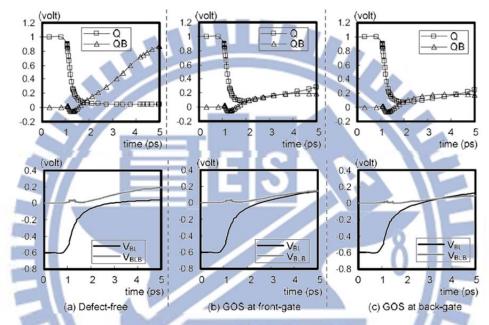

|     | 5.4.3          | Proposed Test method for IG-FinFET based SRAM100 |

|     |                | n                                                |

| 6   |                | E                                                |

| 7   |                |                                                  |

| Bib | liography      |                                                  |

| Pub | olication list |                                                  |

|     | 2              |                                                  |

|     | 2              | 1896                                             |

|     | 2              |                                                  |

|     |                |                                                  |

|     |                |                                                  |

|     |                |                                                  |

## List of Tables

| Table 2-ICategorization of subthreshold SRAM designs                                 |

|--------------------------------------------------------------------------------------|

| Table 2-II Faulty behavior of open defects on Type-A designs (Fig. 2-2, 2-3,         |

| 2-4)12                                                                               |

| Table 2-III Effectiveness of test methods for detecting STFs in Type-A               |

| designs13                                                                            |

| Table 2-IV Effectiveness of test methods for detecting fail-to-write gate open       |

| defects in Type-A designs14                                                          |

| Table 2-V Faulty behavior of open defects on Type-B designs (Fig. 2-5,               |

| 2-6)17                                                                               |

| Table 2-VI Effectiveness of test methods for detecting STFs in Type-B                |

| designs                                                                              |

| Table 2-VIIEffectiveness of test methods for detecting fail-to-write gate open       |

| defects in Type-B designs18                                                          |

| Table 2-VIII         Impact of using different backgrounds when testing fail-to-read |

| open defects in Type-B designs19                                                     |

| Table 2-IX Faulty behavior of open defects on Type-C designs (Fig. 2-7,              |

| 2-8)                                                                                 |

| Table 2-X Effectiveness of test methods for detecting STFs in Type-C                 |

| designs22                                                                            |

| Table 2-XI Impact of using different write voltages during LVW-HVR for               |

| Type-C designs23                                                                     |

| Table 2-XIIImpact of using different backgrounds when testing fail-to-read           |

| open defects in Type-C designs23                                                     |

| Table 2-XIIISetting of WL1 and WL2 for Type-C design                                 |

|--------------------------------------------------------------------------------------|

| Table 2-XIV         Faulty behavior of address decoder faults on Type-C designs      |

| (Fig. 2-8)                                                                           |

| Table 2-XVMinimum detectable resistance for open defects on a differential           |

| sense amplifier                                                                      |

| Table 2-XVI Minimum detectable resistance for open defects on a                      |

| single-ended sense amplifier32                                                       |

| Table 3-I    Control Signals for the 8T SRAM cell40                                  |

| Table 3-II    Test Results of March C- for Open Defects                              |

| Table 3-III Control Signals of the FBA Test Method                                   |

| Table 3-IV Test Results of the FBA Test Method                                       |

| Table 3-V         Final States of Defect-Free Cells and Test Results of Open Defects |

| of SLA under Process Corner TT48                                                     |

| Table 3-VI Final States of Defect-Free Cells under Various Process Corners49         |

| Table 3-VIITest Methods Comparison of Test Efficacy and Test Time                    |

| Table 3-VIII         Test Results of SLA for Open Defects in The DADS                |

| Circuitry                                                                            |

| Table 3-IX Simulation Results of Testing the Defects at M11 and M12 but              |

| under FF Process Corner                                                              |

| Table 4-I DC Characteristics and Parasitic Capacitances of a Defect-Free             |

| nMOS and pMOS57                                                                      |

| Table 4-IIDC Fitting Errors Resulting From Different GOS Models67                    |

| Table 4-III Fitting Errors of An Inverter's Delay Caused by Different GOS            |

| Models                                                                               |

| Table 4-IV IDVD Fitting Errors of GOS Models With Different Defect                   |

| Locations                                                                            |

## **List of Figures**

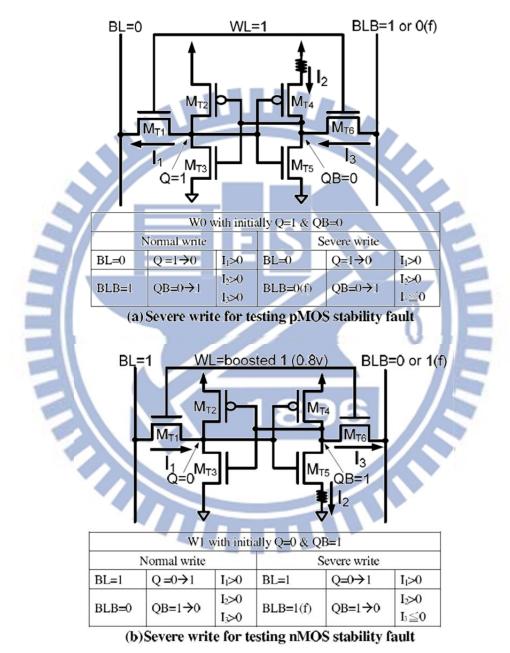

| Fig. 2-1 Illustration of severe write                                           |

|---------------------------------------------------------------------------------|

| Fig. 2-2 First Type-A subthreshold SRAM design [2-9]10                          |

| Fig. 2-3 Second Type-A subthreshold SRAM design [2-10]10                        |

| Fig. 2-4 Third Type-A subthreshold SRAM design [2-11]11                         |

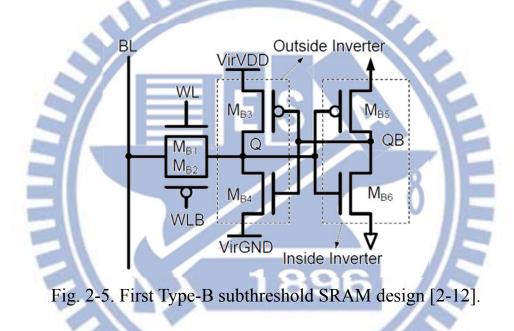

| Fig. 2-5 First Type-B subthreshold SRAM design [2-12]15                         |

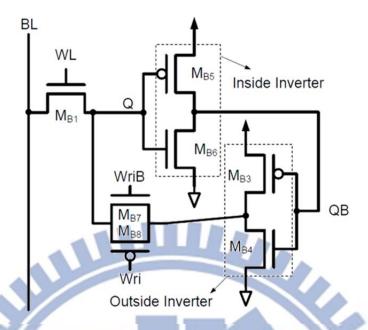

| Fig. 2-6 Second Type-B subthreshold SRAM design [2-13]16                        |

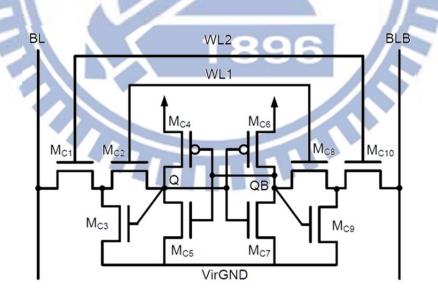

| Fig. 2-7 First Type-C subthreshold SRAM design [2-14]20                         |

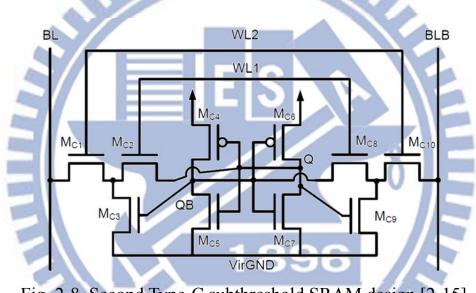

| Fig. 2-8 Second Type-C subthreshold SRAM design [2-15]21                        |

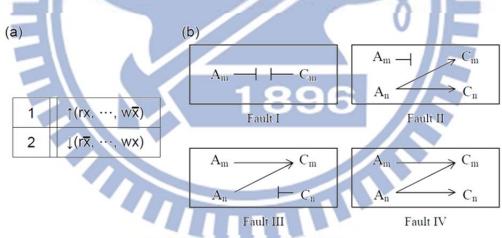

| Fig. 2-9 (a) Conventional march sequence for detecting ADFs; (b) Types of       |

| address decoder faults                                                          |

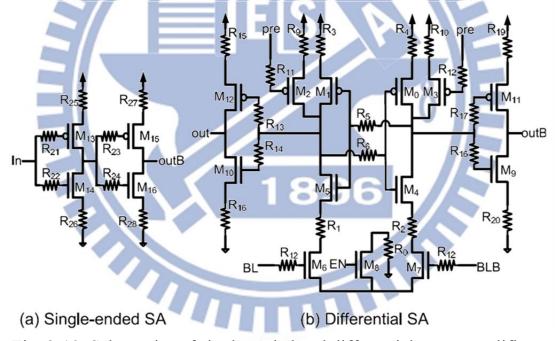

| Fig. 2-10 Schematics of single-ended and differential sense amplifiers31        |

| Fig. 2-11 99th percentile of the largest input voltage offset versus $V_{th}$   |

| mismatch for a differential SA operating at 0.4V and 1.2V,                      |

| respectively                                                                    |

| Fig. 2-12 99th percentile of the largest (smallest) input voltage for read 1(0) |

| for a single-ended SA operating at 1.2V                                         |

| Fig. 2-13 99th percentile of the largest (smallest) input voltage for read 1(0) |

| for a single-ended SA operating at 0.4V                                         |

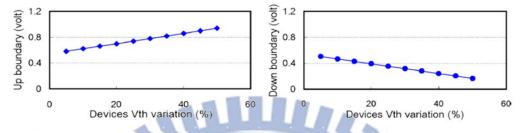

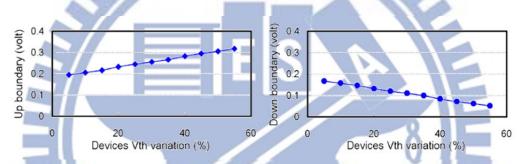

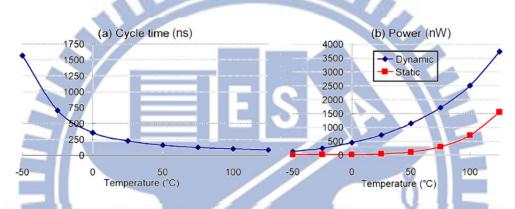

| Fig. 2-14 (a) Cycle time versus temperature and (b) Power consumption           |

| versus temperature for a 128x32 subthreshold SRAM array35                       |

| Fig. 3-1 Schematic of the low-VMIN data-aware dynamic-supply 8T SRAM            |

| [3-7]                                                                           |

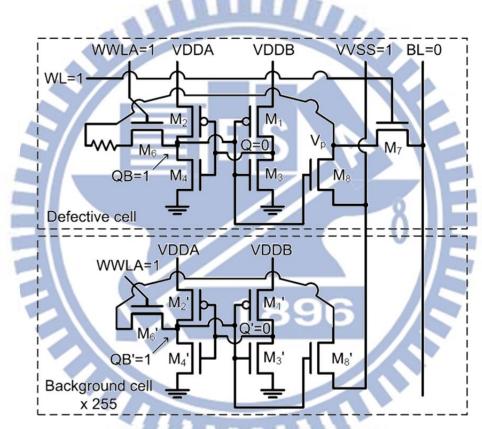

Fig. 3-2 Illustration of how background cells affect the testing of the defect at

| M643                                                                           |

|--------------------------------------------------------------------------------|

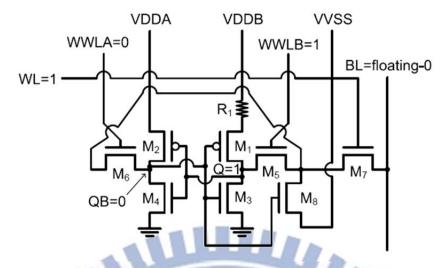

| Fig. 3-3 An example of floating bit-line attacking method: using floating-0 on |

| bit-line for detecting the open defects R145                                   |

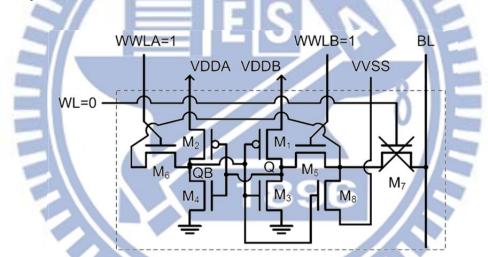

| Fig. 3-4 Configuration of the proposed self-loop attacking test method47       |

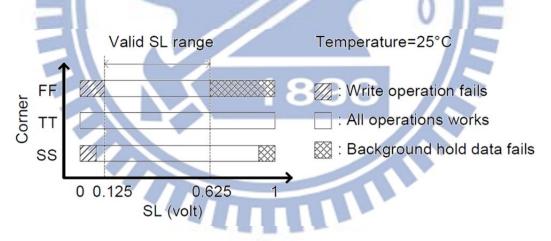

| Fig. 3-5 Valid SL range under different process corners                        |

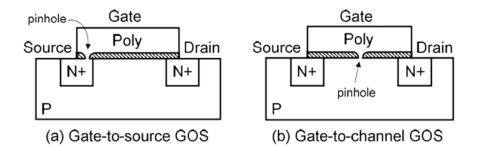

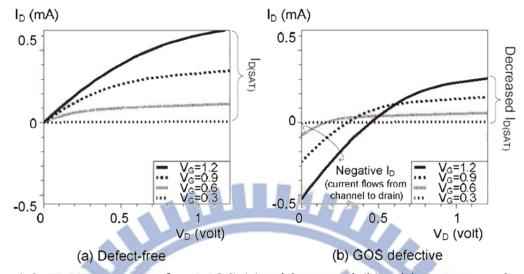

| Fig. 4-1 Cross-section view of a GOS-impacted MOSFET55                         |

| Fig. 4-2 IDVD curves of a nMOS (a) without and (b) with a gate-to-channel      |

| GOS56                                                                          |

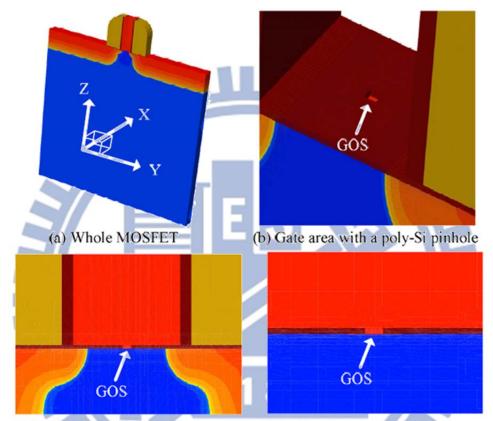

| Fig. 4-3 Representation of a 3D GOS-impacted MOSFET in TCAD58                  |

| Fig. 4-4 Comparison of an inverter's transient response between the TCAD       |

| simulation and the HSPICE simulation with extracted model cards59              |

| Fig. 4-5 An exemplary Bi-dimensional model with 5x5 internal points [4-11]60   |

| Fig. 4-6 The nonlinear non-split GOS model, JET_03, proposed in [4-21]61       |

| Fig. 4-7 The GOS fitting results by using JET_03 model61                       |

| Fig. 4-8 The nonlinear non-split GOS model, IDT_09, proposed in [4-22]62       |

| Fig. 4-9 The GOS fitting results by using IDT_09 model63                       |

| Fig. 4-10Schematic of the proposed GOS model                                   |

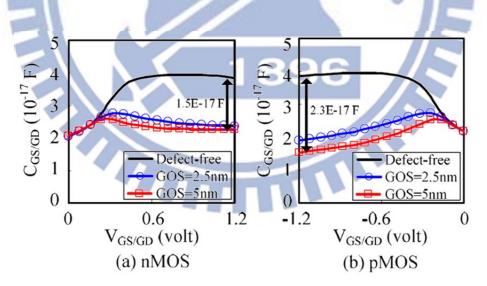

| Fig. 4-11 TCAD C-V simulation results for (a) nMOS and (b) pMOS, with          |

| and without a GOS65                                                            |

| Fig. 4-12DC fitting results by using the proposed GOS model                    |

| Fig. 4-13 An inverter's transfer function resulting from TCAD and different    |

| GOS models when a 5nm-radius GOS locates at the nMOS68                         |

| Fig. 4-14 Transient response of an inverter with a GOS on nMOS resulting       |

| from TCAD and different GOS models                                             |

| Fig. 4-15 Transient response of an inverter with a GOS on pMOS resulting       |

| from TCAD and different GOS models                                             |

XIII

| Fig. 4-16         | GOS defect with nine different locations70                                                            |

|-------------------|-------------------------------------------------------------------------------------------------------|

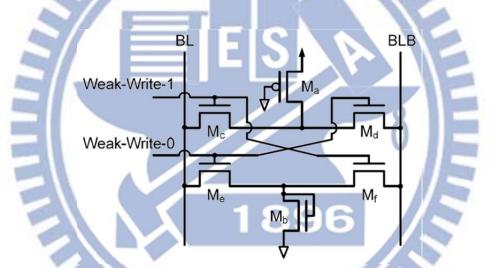

| Fig. 4-17         | Design-for-test (DfT) of weak write test mode [4-45]74                                                |

| Fig. 4-18         | Concept of the proposed DFT write operation for detecting GOS at                                      |

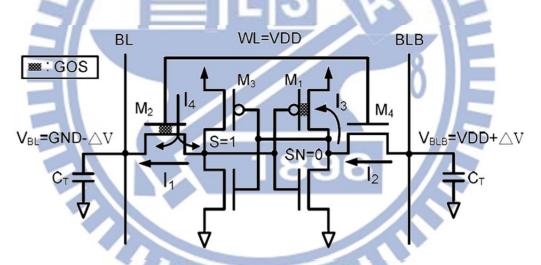

| pu                | ll-up pMOS and pass-gate nMOS75                                                                       |

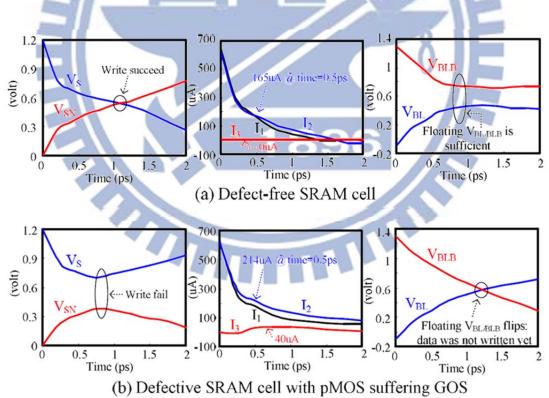

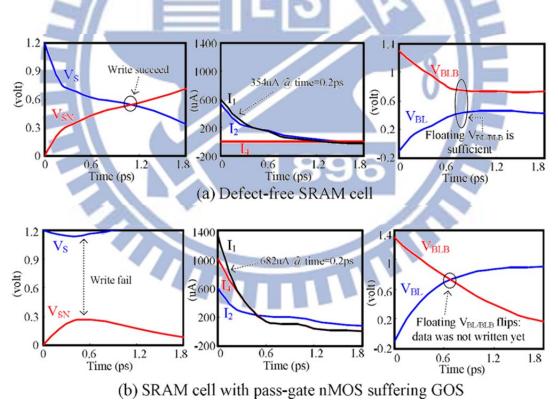

| Fig. 4-19         | $V_{S}\!/V_{SN}\!,~I_{1}\!/I_{2}\!/I_{3}\!,$ and $V_{BL}\!/V_{BLB}$ (a) without and (b) with a GOS at |

| pu                | ll-up pMOS when applying the proposed write operation76                                               |

| Fig. 4-20         | $V_{S}/V_{SN},\ I_{1}/I_{2}/I_{3},$ and $V_{BL}/V_{BLB}$ (a) without and (b) with a GOS at            |

| pa                | ss-gate nMOS when applying the proposed write operation77                                             |

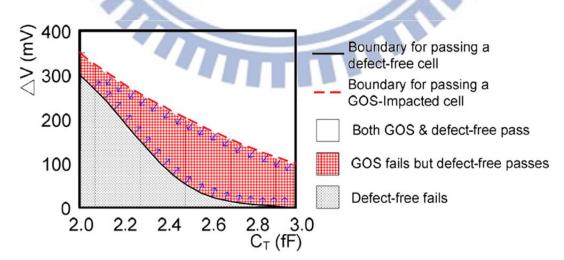

| Fig. 4-21         | Finding valid ( $C_T$ , $\Delta V$ ) combinations for detecting GOS at pull-up                        |

| pN                | 1OS                                                                                                   |

| Fig. 4-22         | Finding valid ( $C_T$ , $\Delta V$ ) combinations for detecting GOS at pull-up                        |

| pN                | 1OS or pass-gate nMOS79                                                                               |

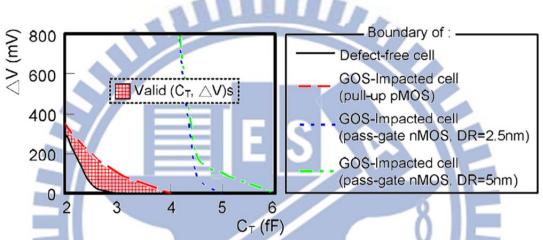

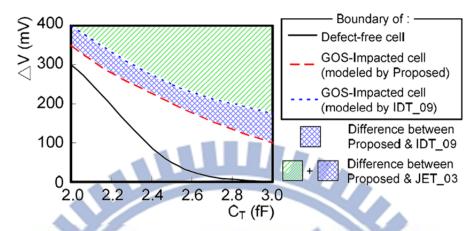

|                   | Finding valid ( $C_T$ , $\Delta V$ ) combinations by using different GOS                              |

|                   | odels                                                                                                 |

| Fig. 4-24         | Mutually-inverse boosting circuitry modified from [4-32]81                                            |

| Fig. 4-25         | Capacitor-occupied area of each valid ( $C_T$ , $\Delta V$ )                                          |

| Fig. 4-26         | Capacitor-occupied area of the preferred ( $C_T$ , $\Delta V$ )s in Figure                            |

| 4-2               | 25                                                                                                    |

| Fig. 4-27         | Tolerable $\Delta V$ range versus differently selected $C_T$ with two                                 |

| rec               | commended configurations for high-process-variation-immunity and                                      |

| lov               | w-area-cost purposes, respectively                                                                    |

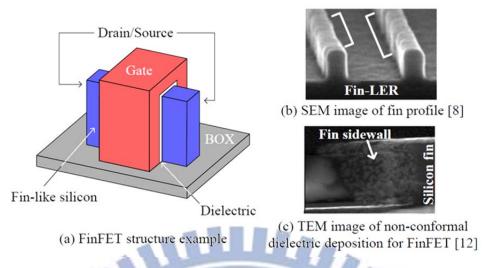

| Fig. 5-1 Fii      | nFET structure and images of the manufacture defects                                                  |

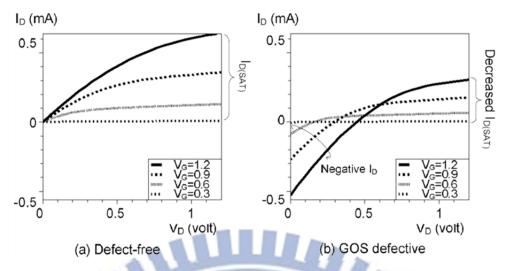

| Fig. 5-2 ID       | VD curves of a planar bulk n-type MOSFET (a) without and (b) with                                     |

| -                 | gate-to-channel GOS                                                                                   |

|                   | rspective view of the built FinFETs                                                                   |

| -                 | VD behaviors of TG FinFETs without/with GOS                                                           |

| <u>0</u> . c + iD | XIV                                                                                                   |

| Fig. 5-5 IDVD behaviors of IG FinFETs without/with GOS at the front-gate                                           |

|--------------------------------------------------------------------------------------------------------------------|

| dielectric                                                                                                         |

| Fig. 5-6 Electron density distribution of an n-type IG FinFET with/without GOS                                     |

| at front-gate dielectric94                                                                                         |

| Fig. 5-7 IDVD behaviors of IG FinFETs without/with GOS at the back-gate                                            |

| dielectric94                                                                                                       |

| Fig. 5-8 FinFET SRAM designs applied for experiments96                                                             |

| Fig. 5-9 Configuration of the Proposed_TG test method for detecting GOS in                                         |

| TG-FinFET SRAM                                                                                                     |

| Fig. 5-10 Minimum operatable $\Delta V-C_T$ for SRAMs passing the                                                  |

| Proposed_TG100                                                                                                     |

| Fig. 5-11 Test results of applying Proposed_TG for detecting GOS in the                                            |

| IG-FinFET SRAM101                                                                                                  |

| Fig. 5-12 Configuration of the Proposed_IG test method for detecting GOS in                                        |

| IG-FinFET SRAM101                                                                                                  |

| Fig. 5-13 Simulation details of the Proposed_IG detecting                                                          |

| front-gate/back-gate GOS at the same time ( $C_T=0.2$ fF, $\Delta V=0.62$ V)102                                    |

| Fig. 6-1 Flowchart showing the proposed cross-layer simulation                                                     |

| framework105                                                                                                       |

| Fig. 6-2 $V_{th}$ distribution of unit-size (1µm/1µm) TFTs: (a) Mean and max $V_{th}$ of                           |

| TFTs with different Si-grain size, and (b) $V_{th}$ distribution of Si-grain                                       |

| size at 300nm, 600nm, and 1000nm107                                                                                |

| Fig. 6-3 V <sub>th</sub> distribution for different-size (W=1 $\mu$ m, 1.2 $\mu$ m, 1.5 $\mu$ m, and 2 $\mu$ m) of |

| TFTs: (a) Si-grain size at 300nm, and (b) Si-grain size at 1000nm107                                               |

| Fig. 6-4 Mean and standard deviation of the characteristics of a unit-size TFT                                     |

| SRAM (all the TFTs are with width=length=1 $\mu$ m) when different xv                                              |

Si-grain sizes are applied: (a) SNM, (b) Read-SNM, (c) Write time, and

(b) Read time......108

Fig. 6-5 Individual yields and comprehensive yield for an SRAM design...109

# Chapter 1 Introduction

Due to the increasing demand of low-power system, a great amount of research effort has been spent in the past to develop the effective and economic SRAM designs which may operate with low supply voltage or even in the subthreshold region. The test methods regarding those newly developed SRAM designs have not yet been fully discussed. In Chapter 2, I have discussed the subthreshold SRAMs testing for which I have 1) categorized the various subthreshold SRAM designs and 2) studied the open defects in SRAM cells, address decoders, and sense amplifiers. Three test methods have been proposed to cope with the different faulty behaviors of each type of SRAMs. The discussion of device variation and temperature affection to designing and testing of the subthreshold SRAMs is also included.

In addition to the subthresold SRAMs, the 3rd chapter covers the testing of a special 8T SRAM design which operates at super-threshold region but with low supply voltage. The utilized data-aware write-assist technique of the cell makes the previous general SRAM testing method unable to detect the defects in the special structure, and hence I study the specific faulty syndrome and propose an effective and extremely time-saving test method.

Chapter 4 turns the viewpoints of testing from the SRAM cell structures to the hard-to-detect manufacture defect: gate-oxide short (GOS). GOS has become a common defect for advanced technologies as the gate-oxide thickness of a MOSFET is greatly reduced. However, the behavior of a GOS-impacted MOSFET is complicated and difficult to be accurately modeled at the circuit level. In this chapter, I first build a golden model of a GOS-impacted MOSFET by using Technology-CAD, and identify the limitation and inaccuracy of the previous GOS models. Next, I propose a novel circuit-level GOS model which provides a higher accuracy of its DC characteristics than any of the previous models while being able to represent a minimum-size GOS-impacted MOSFET. Also, the proposed model can fit the transient characteristics of a GOS by considering the capacitance change of the GOS-impacted MOSFET, which has not been discussed in the previous works. Last, I utilize the proposed GOS model to develop a novel GOS test method for SRAMs, which can effectively detect the GOS defects usually escaped from the conventional IDDQ test and March test.

Based on the work in Chapter 4, I further extend the discussion of GOS testing to FinFET SRAM in Chapter 5 which has become the promising technology for future VLSI. I investigate the fault behaviors of the gate oxide short in FinFETs. The investigation includes both tied-gate and independent-gate FinFETs. Based on the TCAD mixed-mode simulations, I discover that the gate oxide short in the two types of FinFETs causes different fault behaviors from each other. Compared to planar bulk MOSFETs, the fault behaviors are even more complex. In addition to the discussion at device level, I also discuss the corresponding SRAM testing. For detecting gate oxide short in FinFET SRAMs, I propose two new test methods. By using TCAD transient simulations, I prove the two methods' test efficacy of detecting the gate oxide shorts uncovered by traditional test methods.

Finally, in Chapter 6, I discuss the non-conventional technology for SRAM: low temperature poly silicon thin-film transistor (LTPS-TFT). Operation characteristics of LTPS-TFT based systems vary significantly with design choices and parameters (i.e., process, device, circuit and system). Due to the lack of cross-layer simulation tool, conventional designs only optimize the design layers in isolation, leading to sub-optimal solutions. I present a cross-layer simulation framework for the design of LTPS-TFT SRAM. The proposed simulation framework optimizes design parameters considering the entire design space and hence, greatly reduces design complexity and efforts. The benefits of the proposed framework are illustrated by case studies.

### Chapter 2

# Fault Models and Test Methods for Subthreshold SRAMs

Lowering supply voltage is the most straightforward but effective method to reduce circuit's overall power consumption, which is especially suitable for those portable, power-limiting, and not-timing-critical applications such as wireless sensor systems and implanted biomedical chips. Previous works [2-1] [2-2] have shown that the most power-saving supply voltage falls around the subthreshold region for CMOS digital circuits and some subthreshold digital circuits have already been demonstrated in silicon successfully. Also, the performance degradation imposed by the subthreshold operations can be compensated by using proper parallel architecture [2-3] [2-4], which further extends the application of a subthreshold system.

In the process of developing a robust subthreshold system, operating SRAMs at a subthreshold voltage is more challenging than operating digital circuits. Under subthreshold operations, the typical 6T SRAM design needs to face the following two major problems: (1) decrease of the static noise margin and (2) decrease of the write margin [2-5] [2-6]. It means that a 6T SRAM bit-cell operating at subthreshold region is more vulnerable to the noise and at the same time harder to write. The detailed reasons of the above phenomenon were explicitly discussed in [2-6]. Also, in order to increase the write margin, the size of the pass transistors in a 6T SRAM bit-cell needs to be increased, which may further jeopardize the static noise margin. Thus, for a 6T SRAM bit-cell, a proper combination of the 6 transistors' sizes are extremely hard to obtained under subthreshold operations, especially when the local process variation of advanced process technologies may significantly change the device characteristics and in turn break the fragile balance between the currents of the 6

transistors for read, write, and hold operations. Previous results [2-7] have shown that the minimum supply voltage for operating a 6T SRAM design is 0.7V based on a bulk CMOS 65nm technology [2-8] and a dynamic-double-gate SOI technology.

To overcome the above two problems and successfully operate a SRAM at subthreshold region, several new SRAM bit-cell designs [2-9]-[2-16] were proposed. Tackling the weak static noise margin, [2-9]-[2-11] [2-14] [2-15] utilized an extra read path (in addition to the original pass transistors) in their SRAM designs to isolate the cross-coupled inverters from the bit-lines during a read operation, which can effectively avoid potential half select or deceptive read destruction. Tackling the inability to write, techniques were utilized to either strengthen the driving capability of the pass transistors or loose the hold ability of the cross-couple inverters during the write operation. To achieve the former one during a write operation, [2-9] specified a boosted word-line voltage to access the pass transistors and [2-16] designed the pass transistor in a way that its reverse short channel effect can be utilized under subthreshold operations. To achieve the latter one during a write operation, [2-13] broke the loop of the cross-coupled inverters with additional transistors and [2-12][2-14][2-15] destroyed the functionality of one or both inverters by adjusting the voltage at its virtual ground and/or virtual VDD.

Although a significant amount of research effort has been put into the area of developing an effective and economic subthreshold SRAM design, however, the testing methodologies for those new subthreshold SRAM designs have not been fully discussed in the literature yet. In this paper, we will first categorize the new subthreshold SRAM designs into three types based on their design characteristics. For each type of subthreshold SRAM designs, we will then discuss the fault models associated with open defects and identify the faults which may or may not be easily detected by a traditional SRAM test algorithm. We will further discuss the corresponding test methodologies for each of the above hard-to-detect faults. Also, we will discuss the faulty behavior of address decoder faults on those new subthreshold SRAMs and show their difference to the address decoder faults on the traditional 6T SRAM. Next, we will discuss the impact of open defects and V<sub>th</sub> mismatch on sense amplifiers and compare their differences between subthreshold operations and superthreshold operations. A short discuss about the test temperature is provided as well. All the experimental results are collected from the simulation using an UMC 65nm low-leakage process technology.

#### 2.1 Categorization of Subthreshold SRAM Designs

The fault models of a subthreshold SRAM design is associated with its bit-cell structure, and so are their test methodologies. In this section, we categorize the subthreshold designs [2-9]-[2-15] based on the following two criteria regarding the bit-cell structure (Q1 and Q2). The later discussion about the fault behaviors will be based on the result of this categorization.

- Q1: Is its read path different from its write path?

- Q2: Does the design use a single-ended sense amplifier?

Based on Q1 and Q2, the subthreshold SRAM designs can be divided into Type A, B, C, and D as shown in Table 2-I. In fact, Type D represents the bit-cell sharing the read/write paths and utilizing a differential sense amplifier, i.e., the traditional 6T SRAM design. Thus, our later discussion will focus on the fault models and test methods only for the designs in Type A, B, and C. Note that the reason why Q1 and Q2 are used for categorization is because these two criteria can divide the subthreshold SRAM designs into categories that result in similar faulty behaviors.

|   |        |          | TA       | BLE 2-I                          | j, |

|---|--------|----------|----------|----------------------------------|----|

|   | Catego | rization | n of sub | othreshold SRAM designs          |    |

| ø | Туре   | Q1       | Q2       | Sub-V <sub>th</sub> SRAM designs |    |

| 4 | A      | Yes      | Yes      | [2-9]-[2-11]                     |    |

|   | В      | No       | Yes      | [2-12][2-13]                     |    |

|   | C      | Yes      | No       | [2-14][2-15]                     |    |

|   | D      | No       | No       | Typical 6T SRAM                  |    |

|   |        | -        |          |                                  |    |

In order to analyze their fault models, we used a UMC 65nm low-leakage process to implement each of the above bit-cell designs in a 128x32 array (128 bit-cells at a bit-line and 32 bit-cells at a word-line), including write drivers and sense amplifiers. Each row contains only one word and the word size is 32-bit. Under the defect-free condition, we first identified the minimum required cycle time for correct read or write operations at the TT corner and 25°C, and then defined the cycle time as 20% longer than the minimum required cycle time for each bit-cell design. On top of a defect-free design, we will later inject open defects and simulate whether the faulty design can function correctly within the

defined cycle time. A defect is detected if the result of the sense amplifier reports the wrong value.

#### 2.2 Test Methods for Stability Faults

#### 2.2.1 Background of Stability Faults

A stability fault defined in [2-17]-[2-20] refers to a small open defect on the source/drain of the four cross-coupled transistors, which may not fail a read or write operation under a typical operating condition but may fail under some corner conditions (such as significant IR drop, noise, or soft error). As a result, a stability fault may decrease the reliability of the SRAM but may not be easily detected by a conventional march sequence. Therefore, testing stability faults has become one of the most challenging tasks in current SRAM testing. Several test methods were proposed to detect the stability faults with as small resistance as possible [2-17]-[2-20].

For traditional 6T SRAMs, the past research effort mainly focused on the stability faults located on the source/drain of the pull-up pMOS transistors (such as  $M_{T2}$  and  $M_{T4}$  in Figure 2-1) and ignored the stability faults locating on the pull-down nMOS transistors (such as  $M_{T3}$  and  $M_{T5}$  in Figure 1), which can be detected relatively easily by a read operation because the bit-lines in general SRAMs are pre-charged to VDD during a read operation. If the nMOS transistors cannot successfully pull down a bit-line due to the open defects, then the pre-charged value (floating 1) will be read out, which is opposite to the expected value. On the other hand, if the pMOS transistors cannot successfully pull up the bit-line due to an open defect, then the pre-charged value (floating 1) just happens to be the expected value and hence the open defect cannot be detected.

However, for subthreshold SRAM designs, the read path can be separated from the write path, meaning that the weak pull-down ability of nMOS transistors will not directly affect the voltage at RBL during a read operation. Therefore, the importance of detecting the stability faults on the pull-down nMOS transistors ( $M_{T2}$  and  $M_{T4}$ ) become more significant for subthreshold SRAM design than that for traditional 6T SRAMs. In this paper, we will validate the effectiveness of the following test methods for defecting the stability faults locating on both the pMOS and nMOS transistors of subthreshold SRAMs. These testing methods include: (1) read equivalent stress, (2) severe write, and (3) low-V-write/high-V-read.

#### 2.2.2 Read Equivalent Stress

The idea of the read equivalent stress in the 6T SRAM design is to perform consecutive read operations to a designated bit-cell such that its word-line kept opened and its data stored by the cross-coupled inverters can be constantly attacked by the precharged VDD (floating 1) at bit-lines [2-17] [2-21]. However, for the subthreshold SRAMs which utilizes a different read path from its write path (such Type-A and Type-C), a read operation will turn on only its read word-line but not its write word-line. Such a read operation cannot attack the stored data and detect stability faults. Thus, to be able to apply read equivalent stress for Type-A and Type-C subthreshold SRAMs, specialized DFT circuit is required to turn on the write word-line and apply floating 1 at write bit-lines during a read operation at the test mode.

#### 2.2.3 Severe Write

The idea of severe write in the 6T SRAM design is to perform a write operation by setting BL and BLB to floating 0 and strong 0 at the test mode, instead of strong 1 (or floating 1) and strong 0 at the normal mode (as shown in Figure 2-1) [20]. With such a write operation, successfully writing in data becomes more difficult since the floating 0 is opposite to the target value at Q or QB. As a result, if an open defect falls on the source/drain of pMOS transistors (such as  $M_{T2}$  and  $M_{T4}$ ) and weakens the pull-up ability of an inverter, then the severe-write operation will fail to write the correct data and hence detect the open defect. Figure 2-1(a) illustrates how a severe write helps to detect an open defect on the pMOS transistor MT4.

In fact, the above severe write (floating 0 and strong 0) can only detect open defects on pMOS transistors. To detect the stability faults on nMOS transistors, a severe write should set BL and BLB to floating 1 and strong 1. However, the nMOS pass transistors ( $M_{T1}$  and  $M_{T6}$ ) are not suitable for passing a value 1, especially when operating at the subthreshold region (0.4V in our cases). Such a severe write cannot correctly write a data even when no defect exists in the subthreshold SRAM. Therefore, in order to use a severe write to detect stability

faults on nMOS transistors, we need to boost the voltage at WL by another  $V_t$  (0.8V in our case) to enhance the ability of passing a value 1 through the nMOS pass transistors during the test mode, which also requires extra DFT circuitry to realize. Figure 2-1(b) illustrates how this refined version of severe write can help the detection of an open defect on the nMOS transistor  $M_{T5}$ .

Fig. 2-1. Illustration of severe write.

#### 2.2.4 High-V-Write/Low-V-Read

The idea of low-V-write/high-V-read is similar to the severe write, which increases the difficulty of a write operation such that the degradation of pull-up or pull-down capability caused by an open defect may fail to write the correct data. At the same time, we also need to make sure that this difficult condition for write will not fail the design without any defect. It means that the low operating voltage for write cannot be too far away from the normal voltage. Also, changing the operating voltage on test equipment takes a significant amount of time (around 10 micro seconds in our experience). Thus, we need to apply the low-V write to each word, change the operating voltage to normal, and then read each word. A high-V read immediately after a low-V write is not allowed due to its large overhead on test-application time.

#### 2.3 Analysis of Open Defects in Type-A Subthreshold SRAMs

#### 2.3.1 Design Overview of Type-A Subthreshold SRAMs

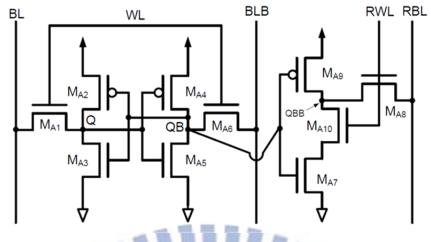

According to the categorization, Type-A subthreshold SRAM designs utilize a single-ended sense amplifier for read and build an extra read path in addition to the traditional 6T SRAM, which can protect the value stored in the cross-coupled inverters during read operations and improve its read SNM to the same level as its hold SNM. Figure 2-2 shows the first Type-A subthreshold SRAM design [2-9], where  $M_{A1}$  to  $M_{A6}$  represent the transistors in the traditional 6T SRAM and MA7 to MA10 represent the transistors in the read path. In this design, the original word-line (WL), bit-line (BL), and bit-line-bar (BLB) are only used for write operations. The new read word-line (RWL) and single-ended read bit-line (RBL) are only used for read operations. During a read operation, the value stored at QB (Q bar) will determine the value at QBB (Q bar bar) through an inverter (formed by  $M_{A7}$ ,  $M_{A9}$ , and  $M_{A10}$ ), and then determine the value at RBL. Also, the value of QBB is kept at 1 (VDD) or floating during the hold mode to reduce the leakage current of  $M_{A8}$  to RBL.

Fig. 2-2. First Type-A subthreshold SRAM design [2-9].

Figure 2-3 shows the second Type-A subthreshold SRAM design [2-10]. Similar to [2-9], [2-10] also use four transistors ( $M_{A7}$  to  $M_{A10}$ ) to build an extra read path. However, its QBB is always kept at 1 during the hold mode since the  $M_{A9}$  in [2-10] is controlled by RWL instead of QB. When reading a value 0 out, QBB is pulled down through the path formed by  $M_{A7}$  and  $M_{A10}$ . However, when reading a value 1 out, QBB is floating since  $M_{A9}$  is turned off by RWL. As a result, the pre-charged floating 1 at RBL will be read out.

Fig. 2-3. Second Type-A subthreshold SRAM design [2-10].

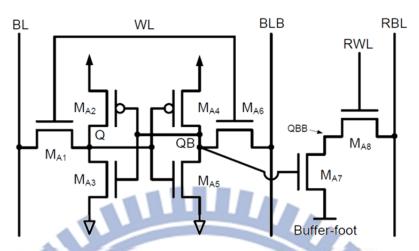

Figure 2-4 shows the third Type-A subthreshold SRAM design [2-11], which uses two transistors and one extra signal (named buffer-foot) to build the extra read path. During read, the signal buffer-foot is set to GND and hence its read mechanism is the same as [2-10]. It means that QBB is 0 and floating when reading 0 and 1, respectively. During hold, the signal buffer-foot is set to VDD,

meaning that QBB is either 1 or floating based on the value of QB.

Fig. 2-4. Third Type-A subthreshold SRAM design [2-11].

#### 2.3.2 Impact of Open Defects on Type-A Subthreshold SRAMs

In the following experiments, we inject an open defect with different resistances on each terminal (gate or source/drain) of each transistor and report the minimum resistance which can cause a failure on a read operation or a write operation for Type-A subthreshold SRAM designs. Table 2-II lists the minimum detectable resistance of each open defect (in Column 5) and the operation which the defect cause a failure at (in Column 4). Note that the result reported in Table 2-II is obtained based on the first Type-A design [2-9] at the TT corner and 25°C. A similar result can be obtained for the other two Type-A designs [2-10] [2-11]. In addition, once the a defect can generate a read failure or write failure, this defect can be easily detected by a conventional SRAM march sequence. Therefore, we only need to consider the open defects with a faulty resistance less than the minimum detectable resistance.

As Table 2-II shows, the open defects locating on the original 6T bit-cell  $(M_{A1} \text{ to } M_{A6})$  all fail on a write operation. The open defects locating on the source/drain of the four cross-coupled transistors  $(M_{A2} \text{ to } M_{A5})$  are first highlighted by a gray background color in Table 2-II. Those defects are classified as a stability fault in Section 2.2. Opposite to traditional 6T superthreshold SRAMs, no stability faults on the nMOS transistors  $(M_{A3} \text{ and } M_{A5})$  can be detected, but the stability faults on the pMOS transistors can be detected with a 60M $\Omega$  minimum detectable resistance for Type-A designs. This result demonstrates that detecting the stability faults on nMOS transistors is

more critical than that on pMOS transistors for Type-A designs. Also, all open defects on the gate of the six transistors ( $M_{A1}$  to  $M_{A6}$ ) have a minimum detectable resistance larger than 370M $\Omega$ , and hence are also relatively hard to detect.

| Faulty behavior of open defects on Type-A designs (Fig. 2-2, 2-3, 2-4). |                    |                        |                    |                                                                                                                                                                                          |  |

|-------------------------------------------------------------------------|--------------------|------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Transistor<br>property                                                  | Transistor<br>name | Transistor<br>terminal | Faulty<br>behavior | Min<br>detectable<br>resistance                                                                                                                                                          |  |

|                                                                         | M <sub>A1</sub>    | G                      | W0 fail            | 482MΩ                                                                                                                                                                                    |  |

| Write pass                                                              | IVIA1              | S/D                    | W0 fail            | 3.8MΩ                                                                                                                                                                                    |  |

| transistor                                                              | M <sub>A6</sub>    | G                      | W1 fail            | 500ΜΩ                                                                                                                                                                                    |  |

| 4                                                                       | IVIA6              | S/D                    | W1 fail            | 3.2MΩ                                                                                                                                                                                    |  |

|                                                                         | M <sub>A2</sub>    | G                      | W0 fail            | 900MΩ                                                                                                                                                                                    |  |

| Pull-up                                                                 | IVIA2              | S/D                    | W1 fail            | 60MΩ                                                                                                                                                                                     |  |

| pMOS                                                                    | M <sub>A4</sub>    | G                      | W1 fail            | 800MΩ                                                                                                                                                                                    |  |

|                                                                         | IVIA4              | S/D                    | W0 fail            | 60MΩ                                                                                                                                                                                     |  |

|                                                                         | м                  | G                      | W1 fail            | 370MΩ                                                                                                                                                                                    |  |

| Pull-down<br>nMOS                                                       | M <sub>A3</sub>    | S/D                    | -                  | $\infty$                                                                                                                                                                                 |  |

|                                                                         | м                  | G                      | W0 fail            | 370MΩ                                                                                                                                                                                    |  |

|                                                                         | M <sub>A5</sub>    | S/D                    | -                  | Min           detectable           resistance           482MΩ           3.8MΩ           500MΩ           3.2MΩ           900MΩ           60MΩ           800MΩ           370MΩ           ∞ |  |

| Read pass                                                               | M <sub>A8</sub>    | G                      | R0 fail            | 200ΜΩ                                                                                                                                                                                    |  |

| transistor                                                              | IVIA8              | S/D                    | R0 fail            | 16.9ΜΩ                                                                                                                                                                                   |  |

| Read-path                                                               | M                  | G                      | R0 fail            | 440MΩ                                                                                                                                                                                    |  |

| pull-down1                                                              | M <sub>A7</sub>    | S/D                    | R0 fail            | 5.1MΩ                                                                                                                                                                                    |  |

| Read-path                                                               | M                  | G                      | R0 fail            | 240MΩ                                                                                                                                                                                    |  |

| pull-down2                                                              | M <sub>A10</sub>   | S/D                    | R0 fail            | 5.1MΩ                                                                                                                                                                                    |  |

| Read-path                                                               | М                  | G                      | R0 fail            | 2GΩ                                                                                                                                                                                      |  |

| QBB set                                                                 | M <sub>A9</sub>    | S/D                    | -                  | $\infty$                                                                                                                                                                                 |  |

TABLE 2-II

Faulty behavior of open defects on Type-A designs (Fig. 2-2, 2-3, 2-4).

On the other hand, the open defects locating on the extra read path ( $M_{A7}$  to  $M_{A10}$ ) all fail on a read-0 operation. Also, the open defects on both gate and source/drain of  $M_{A9}$  are almost undetectable even though those open defects may reduce the ability of pulling up QBB. However, the read-1 operation does not rely on  $M_{A9}$  to pull up RBL and hence the malfunction of  $M_{A9}$  can hardly fail a read operation. For  $M_{A7}$ ,  $M_{A8}$ , and  $M_{A10}$ , the open defects on their gate is harder to detect than those on their source/drain.

#### 2.3.3 Effectiveness of Test Methods for Type-A Designs

In the following experiment, we attempt to reduce the minimum detectable resistance of each stability fault by applying (1) read equivalent stress (denoted as RES), (2) severe write, and (3) low-V-write/high-V-read (denoted as LVW-HVR) to Type-A subthreshold SRAM designs. Note that the read equivalent stress performed in this experiment will not stop repeating read operations until the minimum detectable resistance can hardly be decreased, which usually takes less than 10 repeated read operations. Also, the operating voltage for write and read in low-V-write/high-V-read is 0.36V and 0.4V, respectively. Table 2-III reports the minimum detectable resistance achieved by each test method. In Table 2-III, the test method W+R means a simple read operation after a write operation, which will actually achieve the same minimum detectable resistance as listed in Table 2-II.

TABLE 2-III

| Effectiveness of t | test methods for | detecting STFs in | n Type-A designs. |

|--------------------|------------------|-------------------|-------------------|

|                    |                  | U                 | 51 0              |

| Transistor<br>property | Transistor<br>name                             | W+R  | RES   | Severe W | LVW-HVR<br>(0.36V) |

|------------------------|------------------------------------------------|------|-------|----------|--------------------|

| Pull-up<br>pMOS        | M <sub>A2</sub> (S/D)<br>M <sub>A4</sub> (S/D) | 60ΜΩ | ×     | 6.6MΩ    | 39.4MΩ             |

| Pull-down<br>nMOS      | M <sub>A3</sub> (S/D)<br>M <sub>A5</sub> (S/D) | x    | 790ΜΩ | 4.3MΩ    | x                  |

As Table 2-III shows, severe write outperforms the other two test methods by achieving a  $6.6M\Omega$  minimum detectable resistance for pMOS stability faults and a  $4.3M\Omega$  minimum detectable resistance for nMOS stability faults. Meanwhile, read equivalence stress cannot detect any pMOS stability faults and its minimum detectable resistance for nMOS stability faults is still high (790M\Omega). Note that the read equivalence stress performs even worse than the simple read after write (W+R) for pMOS stability faults. This is because the W+R fails at its write operation but the read equivalent stress assumes that its initial value can be successfully written. Also, the low-V-write/high-V-read cannot detect any nMOS stability faults. In fact, if the boosted WL used in severe write is set to 0.7V, the minimum detectable resistances will be further decreased to the order of hundred-k $\Omega$ . However, if the boosted WL is set to 0.6V, no data can be written into the bit-cell even when no defect exists. Thus, defining a proper boosted voltage at WL is a critical factor when using severe write.

In addition, the severe write and LVW-HVR can also help to reduce the minimum detectable resistance at the gate of  $M_{A1}$  to  $M_{A6}$ , while read equivalent stress cannot. Table 2-IV shows the corresponding results, in which LVW-HVR achieves a lower minimum detectable resistance at the gate of write pass transistors and pull-up pMOS transistors ( $M_{A1}$ ,  $M_{A2}$ ,  $M_{A4}$ , and  $M_{A6}$ ) while the severe write achieves a lower minimum detectable resistance at the gate of pull-down nMOS transistors ( $M_{A3}$  and  $M_{A5}$ ). Overall, severe write is still the most effective test method for Type-A designs since it can cover open defects at the most places.

| Type-A designs. |             |       |             |          |         |

|-----------------|-------------|-------|-------------|----------|---------|

| Transistor      | Transistor  | W+R   | RES         | Severe W | LVW-HVR |

| property        | name        |       | <b>KL</b> 5 | Severe w | (0.36V) |

| Write pass      | $M_{A1}(G)$ | 482MΩ | 8           | 350MΩ    | 32.4MΩ  |

| transistor      | $M_{A6}(G)$ | 500MΩ | 8           | 420MΩ    | 29.9MΩ  |

| Pull-up         | $M_{A2}(G)$ | 900MΩ | 8           | 180MΩ    | 60MΩ    |

| pMOS            | $M_{A4}(G)$ | 800MΩ | $\infty$    | 200MΩ    | 60MΩ    |

| Pull-down       | $M_{A3}(G)$ | 370MΩ | $\infty$    | 110MΩ    | 260MΩ   |

| nMOS            | $M_{A5}(G)$ | 370MΩ | $\infty$    | 230MΩ    | 290ΜΩ   |

#### TABLE 2-IV

Effectiveness of test methods for detecting fail-to-write gate open defects in

#### 2.4 Analysis of Open Defects in Type-B Subthreshold SRAMs

#### 2.4.1 Introduction of Type-B Subthreshold SRAMs

According to the categorization shown in Table 2-I, a Type-B subthreshold SRAM design utilizes a single-ended sense amplifier for read and its read operations share the same path with its write operations. Such a bit-cell structure implies that its write operation is performed through a single bit-line as well, which further increases the difficulty of a write operation. Thus, in order to successfully write data through a single bit-line, Type-B subthreshold SRAM designs heavily rely on the design techniques which can effectively reduce the hold ability of the cross-coupled inverters during the write operation.

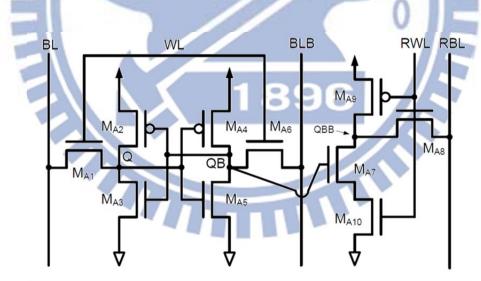

Figure 2-5 shows the first Type-B subthreshold SRAM design [2-12], which can adjust the hold ability of the cross-coupled inverters by controlling the voltage at virtual VDD (VirVDD) and virtual GND (VirGND). During a read operation or the hold mode, VirVDD and VirGND are set to VDD and GND as general SRAMs. During a write operation, VirVDD and VirGND will become an offset lower and an offset higher, respectively, which can break the outside inverter (formed by  $M_{B3}$  and  $M_{B4}$ ) and allows the voltage at Q to be directly affected by BL. Also, this design [2-12] utilizes a pMOS pass transistor ( $M_{B2}$ ) in addition to a normal nMOS pass transistor ( $M_{B1}$ ) simultaneously, such that both 1 and 0 can effectively passed through either  $M_{B2}$  or  $M_{B1}$ .

Figure 2-6 shows the second Type-B subthreshold SRAM design [2-13], which decreases the hold ability during a write operation by breaking the loop of the cross-coupled inverters through the control signals Wri and WriB (at  $M_{B8}$  and  $M_{B7}$ ). Once the loop is broken, the value at BL can be easily written into the bit-cell. After the write operation, the loop of the cross-coupled inverters will be recovered as normal.

Fig. 2-6. Second Type-B subthreshold SRAM design [2-13].

#### 2.4.2 Impact of Open Defects on Type-B Subthreshold SRAMs

Table 2-V lists the minimum detectable resistance and the corresponding faulty behavior of each open defect in Type-B designs. As Table 2-V shows, the open defect at the source/drain of  $M_{B4}$  does not cause a stability fault since the open defect falls on the path of read-0 and can be easily detected by a read-0 operation (with a 900k $\Omega$  minimum detectable resistance). Also, the stability fault at the outside pull-up pMOS  $M_{B3}$  is harder to detect than that at the inside transistors  $M_{B5}$  and  $M_{B6}$ . This is because the outside inverter is either destroyed or disconnected during a write operation, so that the value at Q is always correct. Even if a defect occurs on the outside pMOS  $M_{B3}$ , its weak pull-up ability will not lead to a wrong value at Q since the value at Q is already set by BL. However, if a defect occurs on the inside inverter, its weak pull-up or pull-down ability may delay the signal at QB and in turn result in a conflict at Q.

Table 2-V also shows that the open defects on the gate and source/drain of  $M_{B8}$  can hardly be detected, implying that the design [2-13] may not really need a pMOS transistor to pass a value 1 at the outside inverter's output to Q when the cross-coupled loop is reconnected right after a write operation. In addition, the minimum detectable resistance at each transistor's gate is still high and hence the corresponding open detect is also hard to detect.

| Faulty behavior of open defects on Type-В designs (Fig. 2-3, 2-6). |                    |                        |                    |                                                                                                                                                                                                                        |  |

|--------------------------------------------------------------------|--------------------|------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Transistor<br>property                                             | Transistor<br>name | Transistor<br>terminal | Faulty<br>behavior | Min<br>detectable<br>resistance                                                                                                                                                                                        |  |

|                                                                    | М                  | G                      | W0/R0 fail         | 2GΩ                                                                                                                                                                                                                    |  |

| Write pass                                                         | $M_{B1}$           | S/D                    | R0 fail            | 6.4MΩ                                                                                                                                                                                                                  |  |

| transistor                                                         | М                  | G                      | W1 fail            | 590ΜΩ                                                                                                                                                                                                                  |  |

|                                                                    | $M_{B2}$           | S/D                    | W1 fail            | 7.6MΩ                                                                                                                                                                                                                  |  |

| Outside                                                            |                    | G                      | W0 fail            | 4GΩ                                                                                                                                                                                                                    |  |

| pull-up<br>pMOS                                                    | M <sub>B3</sub>    | S/D                    | -                  | $\infty$                                                                                                                                                                                                               |  |

| Inside pull-up                                                     |                    | G                      | W0 fail            | 870ΜΩ                                                                                                                                                                                                                  |  |

| pMOS                                                               | M <sub>B5</sub>    | S/D                    | W0 fail            | 160MΩ                                                                                                                                                                                                                  |  |

| Outside                                                            |                    | G                      | W1 fail            | 2GΩ                                                                                                                                                                                                                    |  |

| pull-down<br>nMOS                                                  | M <sub>B4</sub>    | Es/D                   | R0 fail            | 900KΩ                                                                                                                                                                                                                  |  |

| Inside                                                             | No. 10             | G                      | W0 fail            | 970MΩ                                                                                                                                                                                                                  |  |

| pull-down<br>nMOS                                                  | M <sub>B6</sub>    | S/D                    | W1 fail            | 120ΜΩ                                                                                                                                                                                                                  |  |

|                                                                    | M                  | G                      | W1 fail            | 2GΩ                                                                                                                                                                                                                    |  |

| Cross-coupled                                                      | M <sub>B7</sub>    | S/D                    | R0 fail            | 45.8MΩ                                                                                                                                                                                                                 |  |

| loop switch                                                        | M                  | G                      | W0 fail            | 29GΩ                                                                                                                                                                                                                   |  |

|                                                                    | M <sub>B8</sub>    | S/D                    | -//>               | detectable         resistance         2GΩ         6.4MΩ         590MΩ         7.6MΩ         4GΩ         ∞         870MΩ         160MΩ         2GΩ         900KΩ         970MΩ         120MΩ         2GΩ         45.8MΩ |  |

TABLE 2-VFaulty behavior of open defects on Type-B designs (Fig. 2-5, 2-6)

#### 2.4.3 Effectiveness of Test Methods for Type-B Designs

Table 2-VI reports the minimum detectable resistance achieved by each test method for each stability fault in Type-B designs. Note that the severe write can only be applied to the design utilizing differential write mechanism (with BL and BLB), and hence cannot be applied to Type-B designs, which uses only one bit-line for write. As Table 2-VI shows, only read equivalent stress can detect the most hard-to-detect stability fault (at M<sub>B3</sub>) in Type-B designs. This is because, by breaking the hold ability of the cross-coupled inverters, write 1 to Q is easy. As a result, detecting stability fault at MB3 cannot be achieved by using a weak write. We can only rely on read operations to detect it. Also, read equivalent stress can reduce the minimum detectable resistance of the other two stability

faults. In addition, LVW-HVR cannot effectively reduce the minimum detectable resistance at transistors' gate for Type-B designs as it does for the Type-A designs. Table 2-VII shows the corresponding result at each transistor's gate. Therefore, read equivalent stress is more preferable than LVW-HVR for Type-B designs overall.

| Liitett           | Effectiveness of test methods for detecting 5115 in Type D designs. |       |       |         |         |  |

|-------------------|---------------------------------------------------------------------|-------|-------|---------|---------|--|

| Transistor        | Transistor                                                          | W+R   | RES   | LVW-HVR |         |  |

| property          | name                                                                | WTK   | KE5   | 0.38V-W | 0.36V-W |  |

| Pull-up           | M <sub>B3</sub> (S/D)                                               | 8     | 300KΩ | × ×     | <0      |  |

| pMOS              | $M_{B5}$ (S/D)                                                      | 160MΩ | 160MΩ | 150MΩ   | <0      |  |

| Pull-down<br>nMOS | M <sub>B6</sub> (S/D)                                               | 120MΩ | 62MΩ  | 43.7MΩ  | <0      |  |

TABLE 2-VI

Effectiveness of test methods for detecting STFs in Type-B designs.

#### TABLE 2-VII

Effectiveness of test methods for detecting fail-to-write gate open defects in

| Type-B designs.           |                     |            |                      |  |  |

|---------------------------|---------------------|------------|----------------------|--|--|

| Transistor<br>property    | Transistor name     | W+R        | LVW-HVR<br>(0.38V-W) |  |  |

| Write pass                | $M_{B1}(G)$         | $2G\Omega$ | $2G\Omega$           |  |  |

| transistor                | $M_{B2}(G)$         | 590MΩ      | 410MΩ                |  |  |

| Pull-up pMOS              | $M_{B3}(G)$         | 4GΩ        | 3GΩ                  |  |  |

|                           | $M_{B5}(G)$         | 870ΜΩ      | 790MΩ                |  |  |

| Outside<br>pull-down nMOS | M <sub>B4</sub> (G) | 2GΩ        | 430ΜΩ                |  |  |

| Inside pull-down<br>nMOS  | M <sub>B6</sub> (G) | 970ΜΩ      | 410MΩ                |  |  |

| Cross-coupled             | $M_{B7}(G)$         | 2GΩ        | 3GΩ                  |  |  |

| loop switch               | $M_{B8}(G)$         | 29GΩ       | 190GΩ                |  |  |

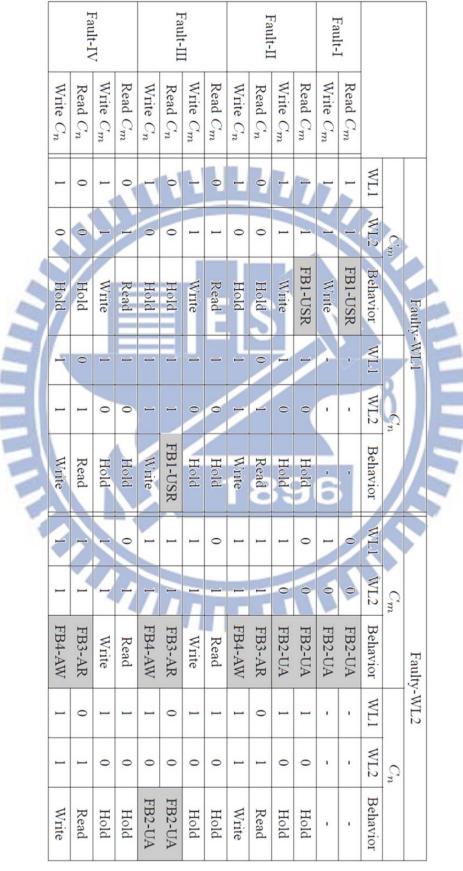

In Table 2-V, open defects on the source/drain of  $M_{B1}$ ,  $M_{B4}$ , and  $M_{B7}$  may result in a read-0 fail. Since Type-B designs use a single read path and BL is pre-charged to floating 1 for a read operation, a read-1 operation will never fail by an open defect on the bit-cell. In fact, the worst case of performing a read-0 operation occurs when the value of all other bit-cells at the same BL is set to 1, such that the leakage current from  $M_{B1}$  and  $M_{B2}$  can prevent the BL from being pulled down by the accessed bit-cell. Also, the devices need to be in the FF corner and operated at a high temperature. Such a condition can result in a more significant leakage current, even though the pull-down capability of the targeted read path is also increased at a higher temperature (will discuss more in Section 2.8).

In the following experiment, we attempt to observe the impact of setting the data of all other bit-cells at the same BL to the same value (0) or the opposite value (1) to the accessed bitcell when performing a read-0 operation in Type-B designs. Table 2-VIII lists the minimum detectable resistance of the three read-0-fail open defects with both background settings. The simulation is conducted based on the FF corner at 75°C. As the result shows, with the same data background, a large open defect may not be even detectable since the leakage at the same BL can help to pull down the data. With the opposite background, the minimum detectable resistance can be significantly reduced. Note that we have tried a similar experiment to Type-A designs but its difference of using different backgrounds is limited.

### TABLE 2-VIII

Impact of using different backgrounds when testing fail-to-read open defects in

|    | n    | 1    |      |

|----|------|------|------|

| IV | pe-B | desi | gns. |