# 國立交通大學

# 材料科學與工程學系

## 博士論文

以凱文錫球結構及有限元素分析法研究覆晶銲錫凸塊與微

凸塊的電遷移破壞機制

Study of Failure Mechanisms in Flip-Chip Solder Joints and

Microbumps under Electromigration Using Kelvin Bump

Structures and Finite-Element Analysis

研究生: 張元蔚

指導教授: 陳智

中華民國 102 年 8 月

# 以凱文錫球結構及有限元素分析法研究覆晶銲錫凸塊與微凸塊的電 遷移破壞機制

Study of Failure Mechanisms in Flip-Chip Solder Joints and Microbumps under Electromigration Using Kelvin Bump Structures and Finite-Element Analysis

研究生: 張元蔚 Student: Yuan-wei Chang

指導教授: 陳智 Advisor: Chih Chen

國立交通大學

材料科學與工程學系

博士論文

A Thesis

Submitted to Department of Materials Science and Engineering

College of Engineering

National Chiao Tung University

in partial fulfillment of the requirements

for the degree of Ph.D. in

Materials Science and Engineering

August 2013

Hsinchu, Taiwan, Republic of China

中華民國 102 年 8 月

### 摘要

於此研究中,共三種預先設計好、包含凱文錫球結構之銲錫凸塊被用於非破壞性觀測電遷移測試時的電阻變化。

第一種是覆晶銲錫凸塊,其凸塊電阻小於1毫歐姆、成長時呈現凹口向上之趨勢,直到凸塊電阻上升超過10毫歐姆時,會開始急遽上升而後斷路;內部對應之微結構是孔洞的成核與成長,孔洞首先生成於電流集中區然後沿著介金屬化合物與銲錫間介面成長,在測試的末期,電遷移導致的相粗化減緩了電遷移產生的破壞,且可以發現孔洞在電遷移測試末期會分成兩段;且根據實驗結果,我們計算得到一個可表達剩餘接觸面積與凸塊電阻的關係式。

第二種試片則是六微米高的微凸塊,其微凸塊電阻呈現凹口向下之行為,從 15 毫歐姆開始急遽增加,然後在測試 400 小時後達到一個定值,早期急劇增加 的幅度約5 毫歐姆,這與有限元素分析法所得之結果相符;在電遷移測試中,陰 極金屬墊層會與銲錫反應並將整個微凸塊轉變為 Ni<sub>3</sub>Sn<sub>4</sub> , Ni<sub>3</sub>Sn<sub>4</sub> 具有較銲錫佳之抗電遷移特性,所以導致凸塊電阻維持一個定值;在不同角度的凸塊電阻指出了電流集中效應雖然沒有發生在銲錫中,依舊發生在金屬墊層裡,對於微凸塊來說,完整的電壓降應該是由 0 度所量到的值,而這個值比 180 度所得到的值高了 7 倍,也就是說,其實微凸塊所造成的容/阻延遲相當的大;而為了要簡化描述微凸塊電阻、電流集中比與凸塊尺寸的關係,一個數值分析模型在此被提出,根據此模型,微凸塊電阻與電流集中的關係可以被表達為簡單的關係式。

最後一種試片則是十微米高的微凸塊,其電阻開始時呈現凹口向下,然後轉

變為凹口向上,原因在於,其銲錫的量太多,而無法被中介板端的金屬墊層消耗完;開始時,凹口向下的反應行為與矮的微凸塊相當接近,不過因為銲錫的量太多,所以在電子流向上(由中介板端流向晶片端)之微凸塊中,2微米厚之鎳層會受電遷移影響而融入銲錫中,當這些鎳用完以後,孔洞就會產生在這些金屬墊層本來的位置上,且造成電阻曲線又轉變成凹口向上。

根據這些結果,由凱文錫球結構所獲得凸塊電阻的曲線行為經由有限元素模型的幫助,可以在測試中用來檢視其微結構的變化,有限元素模型可以很清楚的表現出不同電遷移階段電流密度的演進,因此可以幫助預測電遷移破壞的機制;此外,凱文錫球結構與過去最常用於分析墊遷移之離菊花環結構完全的相容,兩個值可以在同時量測取得,此一點是凱文錫球結構之一大優勢。

1896

### **Abstract**

In this study, three types of solder bump samples with Kelvin bump structures were employed to monitor non-destructively the evolution of resistance during electromigration (EM) testing.

The first type of sample was flip-chip bumps. The bump resistance was found to be less than 1 m $\Omega$  and increase as a concave-up curve. After the bump resistance increased to more than 10 times its initial value, it started to grow rapidly and then failure. The corresponding microstructure showed void nucleation and propagation. The void first formed near the current crowding spot and then grew along the interface between the intermetallic compound (IMC) and the solder. At the end stage of EM testing, phase coarsening caused by EM retarded the failure, and the void split into two parts. The relation between the remaining contact area and the bump resistance was calculated.

The second type of sample was 6- $\mu$ m microbumps. The microbump resistance curve was concave-down. It started around 15 m $\Omega$ , increased rapidly in the beginning, and then reached a constant value after 400 hr of testing. The increase in the early stage of testing was around 5 m $\Omega$ , which was reasonable when compared with the results of finite-element models (FEMs). During EM testing, the cathode-side under-bump-metallization (UBM) reacted with the solder and transformed the entire microbump into Ni<sub>3</sub>Sn<sub>4</sub>. Ni<sub>3</sub>Sn<sub>4</sub> has better EM resistance than the solder and caused the bump resistance to remain at a constant value. The bump resistances at different angles indicated that current crowding still took place, but in the Cu UBM and not in the solder. The complete voltage drop across the microbump was the value obtained at

0°. However, the bump resistance obtained at 0° was 7 times larger than that measured at 180°. That is, the RC delay caused by microbump is actually very large. For simplicity of description on the relation between microbump resistances, crowding ratio, and structural dimensions, a numerical model was built. The expressions of microbump resistance and the crowding ratio were also obtained.

The last type of sample was the 10-µm microbumps. The resistance behaved first concave-down and then concave-up because the solder was too much for the interposer-side UBM to consume. The concave-down curve was first observed for the same reason as that of the low-bump-height case. However, the height of the solder was around 10 µm, which was too high for the interposer-sider UBM to react with. When the electrons flow upward (from interposer to chip), the interposer-side UBM, 2-µm Ni, was the cathode side. Driven by EM, the-2µm Ni quickly dissolved into the solder. After the 2-µm Ni ran out, the void was formed, causing the bump resistance curve to become concave-up again.

The solder height affected the failure mechanism. When the solder height was 25  $\mu$ m, void propagation was the main failure mechanism. When the solder height decreased to 10  $\mu$ m, the mechanism became the combination of void propagation and IMC growth. When it was 6  $\mu$ m, the failure mechanism changed to IMC growth only. The FEM described clearly the evolution of current density distribution at various stages of EM and therefore helped predict accurately the failure mechanism. Moreover, the Kelvin bump structure is compatible with the generally used daisy chain structure. Both bump resistance and daisy chain resistance could be obtained at the same time.

### 致謝

能夠博士班就讀期間順利完成本研究,敝人的指導教授陳智老師自是功不可沒,當我面臨研究瓶頸的時候不斷提供實貴而適切的建議與幫助,而在成果豐碩的時候也不吝於給予熱烈的鼓勵。此外,正所謂身教重於言教,陳智老師對於研究積極的熱誠與付出更是令我尊敬的榜樣,也因為追隨著陳智老師這樣的目標,本研究才得以順利完成。且於就學過程中,敝人經由陳智老師推薦而參與龍門計畫,因而難能可貴的得到了一年在異鄉求學的經驗,其中的感謝之情難以言述。

除了陳智老師以外,細數求學的過程中,還有太多需要感謝的人。潁超學長、 重光學長、世緯學長、章斌學長、程昶學長等人,於我碩士班時期就給予我很多 指導,讓我很快地就融入實驗室,若不是你們紮實教會我諸多基本的實驗技巧, 本研究不可能進行的如此順利;與我有諸多合作、亦師亦友的聖翔學長在就讀博 士班的這幾年間也給了我很多實質的幫助;筱芸學姊就出國交流的準備工作給了 我很多建議,特別是在 UCLA 的期間給了我很多幫助,讓我很快地就融入異鄉的 生活; 道奇學長、翔耀學長、詠湟學長、健民學長、佳凌學姊、宗寬學長、漢文、 右峻雖於研究上與我並無重大關聯,但於各自的研究領域皆有特殊的造詣,是我 十分尊敬的研究人員;以撒、韋嵐的研究領域雖與我沒有直接相關,但時常於我 有開放性的討論,讓我有機會可以對他們的研究有更多的認識,且對於一些心靈 與思想方面的討論,你們也給予我很多寶貴的意見;奕丞雖然因為逕讀博班的緣 故還是研究的新手,但其研究的熱誠、專注、細心是隱藏不了的,看著你也讓我 對於研究偶爾迷惘的心情又重新燃起熱情;若薇、秉儒、黎云等幾位,是我直接 指導過的學弟妹,非常感謝你們於實驗中細心聆聽我的交代並忍耐我在各方面的 堅持,其中若薇已為人妻,祝福妳的婚姻生活百年好合,而黎云目前尚未畢業, 也祝福妳在未來一年的碩士班生活中,一切研究順利;致嘉的思路靈活、做事紮 實,令我印象深刻,也默默改變了我對某些事物的看法;曉嚴、朝俊、竣傑、玉 龍過去與我私底下有不少聊天的機會,謝謝你們替我舒緩了不少情緒。還有天麟、 育安、瑋安、建志、岱霖、韋奇、明墉、偉豪、俊毅、皆安、岱陽、順財、宛霖、 書漢,雖然因為我餐與龍門計畫加上有些是新進的成員,所以相處的時間不長, 但也讓我的研究生活多了許多樂趣,如果少了任何一個實驗室成員的話,我的研 究恐怕不會有現在的成果。

在此還要感謝我的口試委員台大材料的高振宏老師、清大材料的廖建能老師、以及本所的張立老師在口試的過程中給予了很多珍貴的意見。

我的家人在我就讀博士班的過程中,儘管不懂我研究的目標,可是還是給我心裡上與經濟上無條件、無上限的支持,讓我在研究的時候沒有後顧之憂。最後,則是我摯愛的女友,感謝妳對於我忙碌、無法時時陪伴妳的理解,那溫柔、貼心的包容總是令我備感溫暖。你們是我研究的背後看不見的大功臣,謝謝你們。

# **Contents**

| 摘要                                                              | i   |

|-----------------------------------------------------------------|-----|

| Abstract                                                        | iii |

| 致謝                                                              | V   |

|                                                                 |     |

| Contents                                                        |     |

|                                                                 | ix  |

| List of Tables                                                  | xiv |

| Chapter 1. Introduction                                         |     |

| 1.1. Flip-Chip Technology                                       | 1   |

| 1.2. Microbump Technology                                       | 4   |

| 1.3. Electromigration                                           | 7   |

| 1.4. Current Crowding Effect                                    | 11  |

| 1.5. Failure Mechanisms of Solder Joints under Electromigration | 15  |

| 1.6. Interfacial Reaction                                       | 21  |

| 1.7. Kelvin Sensing                                             | 22  |

| 1.8. Finite-Element Method                                      | 25  |

| 1.9. Motivation                                                 | 26  |

| Chapter 2. Experimental                                         | 29  |

| 2.1. Flip-Chip Solder Bumps                                     | 29  |

| 2.1.1. Sample Structure                                         | 29  |

| 2.1.2. Kelvin Bump Structures and Experimental Procedures                | 32         |

|--------------------------------------------------------------------------|------------|

| 2.2. Six-Micro-Meter Microbumps                                          | 36         |

| 2.2.1. Sample Structure                                                  | 36         |

| 2.2.2. Kelvin Bump Structures and Experimental Procedures                | 39         |

| 2.3. Ten-Micro-Meter Microbumps                                          |            |

| 2.3.1. Sample Structure                                                  | 42         |

| 2.3.2. Kelvin Bump Structures and Electromigration Stressing Conditions  | <b>4</b> 4 |

| 2.4. Procedures of Finite-Element Modeling                               | 44         |

| 2.4.1. Element Type and Materials Properties                             | 45         |

| 2.4.2. Model Construction and Meshization                                | 48         |

| 2.4.3. Boundary Conditions and Solution                                  | 49         |

| 2.4.4. Post-processing                                                   | 51         |

| 2.5. Models                                                              |            |

| 2.5.1. Model of Flip-Chip bumps                                          | 51         |

| 2.5.2. Model of Microbumps                                               | 54         |

| 2.5.3. Model of Scallop Intermetallic Compounds                          | 57         |

| 2.6. Numerical Modeling of Current Crowding Effect                       | 59         |

|                                                                          |            |

| Chapter 3. Results                                                       | .63        |

| 3.1. Electromigration Test Results of Flip-Chip Bumps                    | 63         |

| 3.1.1. Bump Resistance of Flip-Chip Bumps                                |            |

| 3.1.2. Microstructure Evolution in Flip-Chip Bumps                       |            |

| 3.1.3. Void Growth Rate in Flip-Chip Bumps                               | 71         |

| 3.2. Electromigration Test Results of Six-Micro-Meter Microbumps         | 73         |

| 3.2.1. Bump Resistance of Six-Micro-Meter Microbumps                     | <b>7</b> 3 |

| 3.2.2. Microstructure Evolution in Six-Micro-Meter Microbumps            | 77         |

| 3.2.3. Bump Resistance at Different angles in Six-Micro-Meter Microbumps | 83         |

| 3.3. Electromigration Test Results of Ten-Micro-Meter Microbumps         | 85         |

| 3.3.1. Resistance of Ten-Micro-Meter Microbumps                          | 85         |

| 3.3.2. Microstructure Evolution in TenMicro-Meter Microbumps             | 88         |

| 3.4. Results of Finite-Element Analysis                                  | 92         |

| 3.4.1. Finite-Element Analysis of Scallop Intermetallic Compounds92       |

|---------------------------------------------------------------------------|

| 3.4.2. Finite-Element Analysis of Flip-Chip Bumps95                       |

| 3.4.3. Finite-Element Analysis of Six-Micro-Meter Microbumps98            |

| 3.4.4. Finite-Element Analysis of Ten-Micro-Meter Microbumps102           |

| <b>Chapter 4. Discussion104</b>                                           |

| 4.1. Bump Resistance of Flip-Chip Bumps 104                               |

| 4.2. Secondary Void Formation near End Stage of Electromigration  Testing |

| 4.3. Bump Resistance of Six-Micro-Meter Microbumps113                     |

| 4.4. Relation between Bump Resistance Behavior and Microstructure         |

| Evolution116                                                              |

| 4.5. Effect of Solder Height on Microstructure Evolution117               |

| 4.6. Effect of Magnitude of Applied Current on Microstructure             |

| <b>Evolution119</b>                                                       |

| 4.7. Integration between Kelvin Bump structures and Daisy Chain           |

| Structure119                                                              |

| Chapter 5. Conclusions                                                    |

| Chapter 6. References (MLA format) 124                                    |

| Chapter 7. Publication List133                                            |

# **Figure Captions**

| Figure 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (a) Tilt-view SEM image of solder bumps array on silicon die [2]; (b) a                            |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | flip-chip solder joint connecting the chip side and the substrate side [2];                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | and (c) the chip placed upside down onto the substrate and the joint                               |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | formed simultaneously between chip and substrate by reflow [1]                                     |  |  |

| Figure 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (a) Difference between 2D and 3D structure in fabrication of integration                           |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | circuits [19]; and (b) difference between SIP/SoC and 3D-IC technology                             |  |  |

| -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | [22]6                                                                                              |  |  |

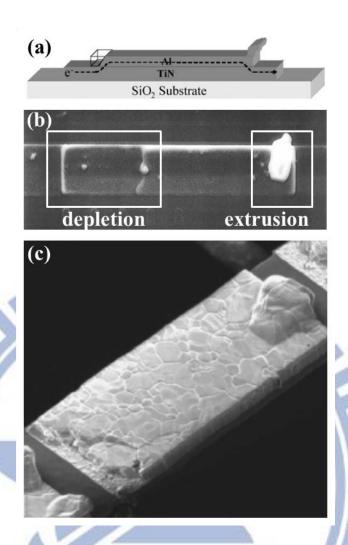

| Figure 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (a) Blech's structure, showing an aluminum strip deposited on a TiN layer                          |  |  |

| [2]; (b) morphology of a Cu strip tested for 99 hr at 350°C with 5 × 1 A/cm <sup>2</sup> current density [2]; and (c) two-dimensional conductor with graden strip tested for 99 hr at 350°C with 5 × 1 and 5 × |                                                                                                    |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                    |  |  |

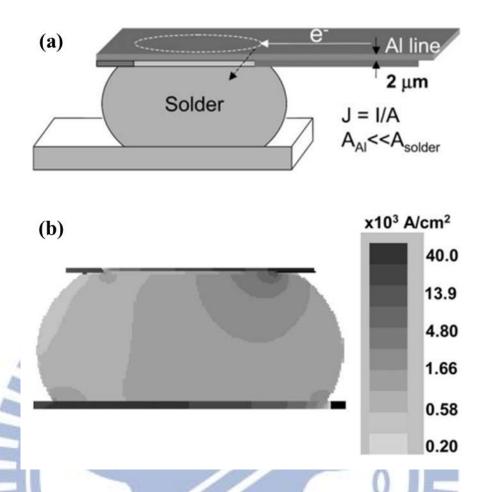

| Figure 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (a) Line-to-bump geometry of a flip-chip solder bump joining an                                    |  |  |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | interconnect line on the chip side (top) and a conduction trace on the                             |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | board side (bottom) [13]; and (b) two-dimensional simulation of current                            |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | distribution in a solder joint [13]                                                                |  |  |

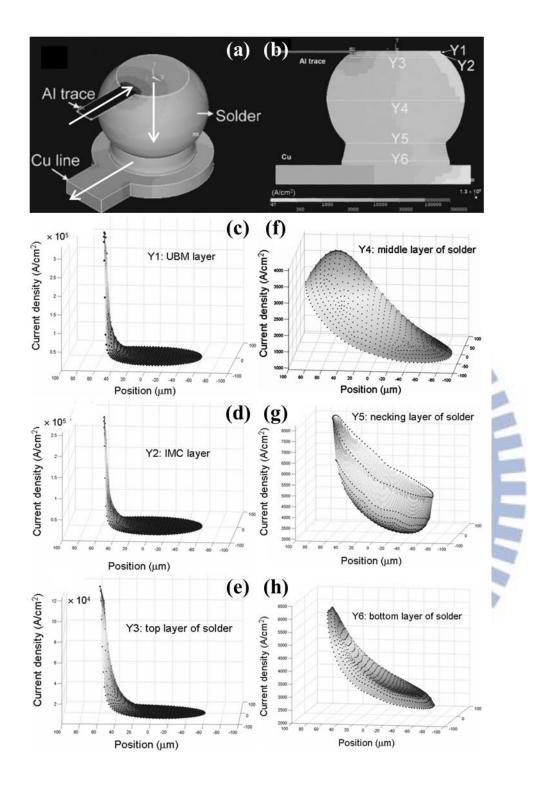

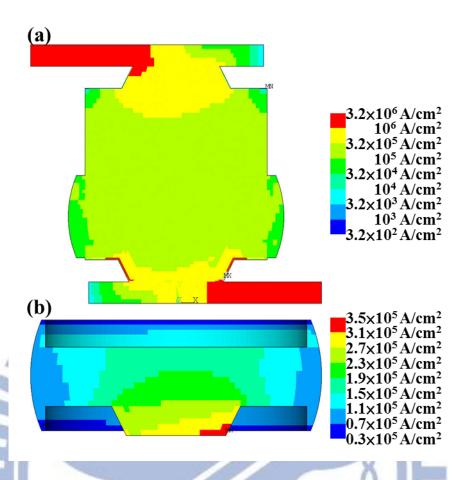

| Figure 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | (a) Oblique current density distribution in a solder joint with Ti/CrCu/Cu                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | thin-film UBM [31]; (b) cross-sectional current density distribution [31];                         |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3D current density distribution at the cross-section of (c) Y1, (d) Y2, (e)                        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Y3, (f) Y4, (g) Y5, and (h) Y6 [31]14                                                              |  |  |

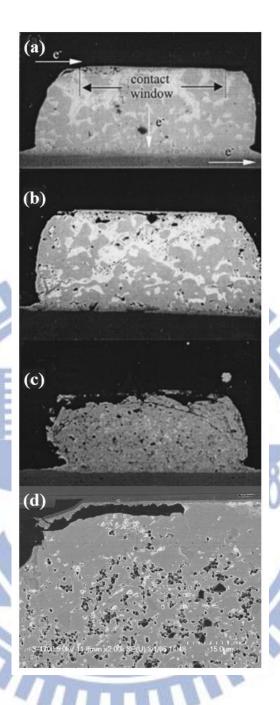

| Figure 1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SEM images of void formation and propagation in a flip-chip E-SnPb                                 |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | solder bump stressed at $125$ °C by $2.25 \times 10^4$ A/cm <sup>2</sup> for (a) 38 hr, (b) 40 hr, |  |  |

|                                                                              | and (c) 43 hr [16]; and (d) SEM image of void formation in a flip-chip                               |  |  |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

|                                                                              | 95.5Sn4.0Ag0.5Cu solder bump stressed at 146°C by $3.67 \times 10^4 \text{ A/cm}^2$                  |  |  |

|                                                                              | [29, 33]                                                                                             |  |  |

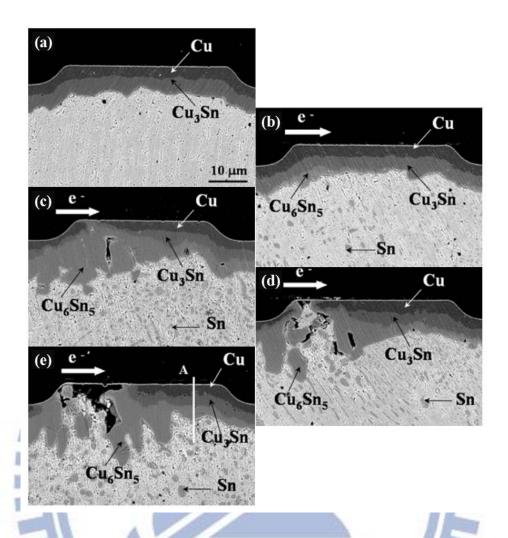

| Figure 1-7                                                                   | Solder joints current stressed at $140$ °C by $2.55 \times 10^4$ A/cm <sup>2</sup> for (a) 0 hr, (b) |  |  |

|                                                                              | 3 hr, (c) 12 hr, (d) 18 hr, and (e) 20 hr [17]19                                                     |  |  |

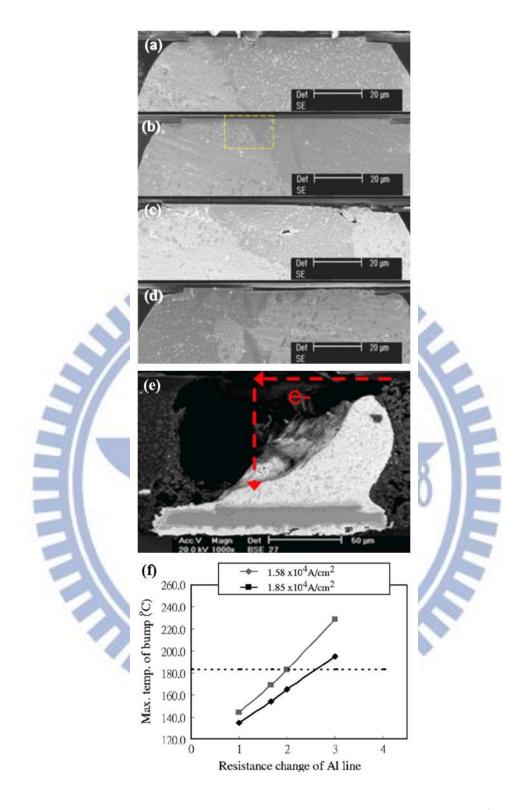

| Figure 1-8                                                                   | Top region of a solder bump after current stressing of $1.6 \times 10^4 \text{ A/cm}^2$ at           |  |  |

|                                                                              | 150℃ for (a) 30 min, (b) 60 min, (c) 100 min, and (d) 120 min [53]; (e)                              |  |  |

|                                                                              | melted solder joint due to large Joule heating before an open circuit [53];                          |  |  |

|                                                                              | and (f) relationship between maximum temperature of bumps and                                        |  |  |

| 4                                                                            | resistance change of Al line [54]20                                                                  |  |  |

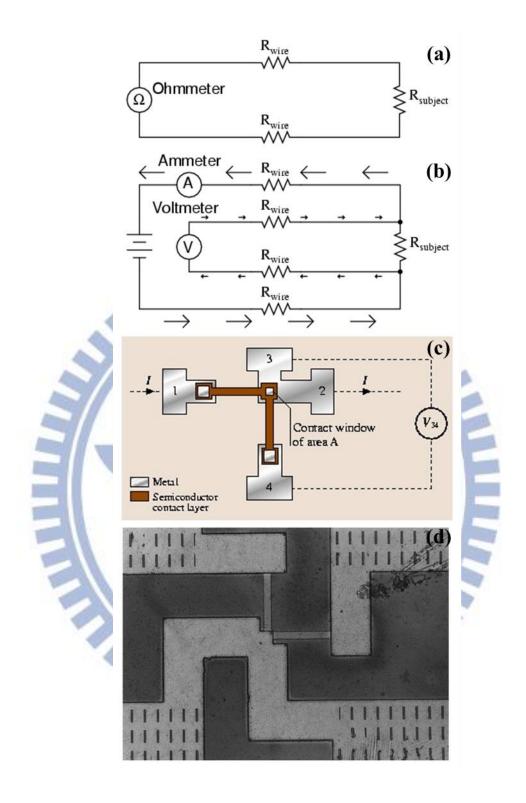

| Figure 1-9                                                                   | (a) Two-wire sensing; (b) Kelvin sensing (4-wire sensing); (c) schematic                             |  |  |

| of Kelvin sensing structure applied in semiconductor fabrication in          |                                                                                                      |  |  |

|                                                                              | [66]; and (d) Kelvin sensing structure fabricated [67]24                                             |  |  |

| Figure 2-1                                                                   | (a) Schematic illustration in plan-view of an entire flip-chip sample; (b)                           |  |  |

| schematic illustration of the flip-chip solder bump; and (c) cross-sectional |                                                                                                      |  |  |

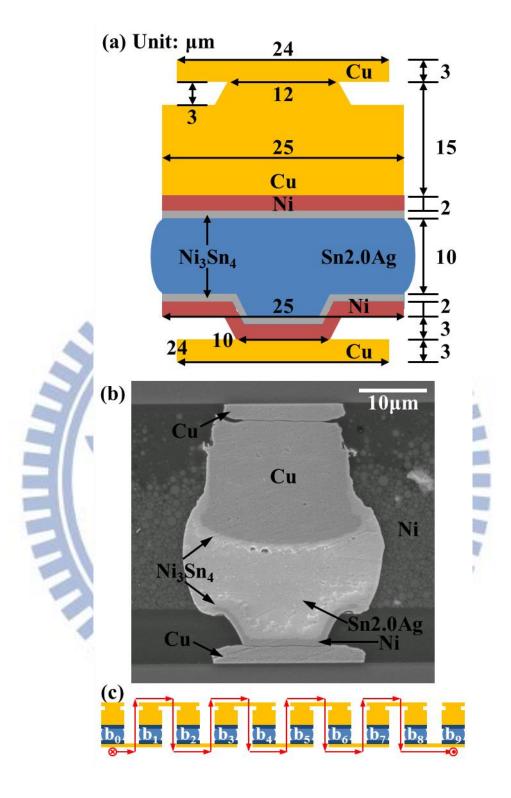

| 4                                                                            | SEM image of a flip-chip solder bump31                                                               |  |  |

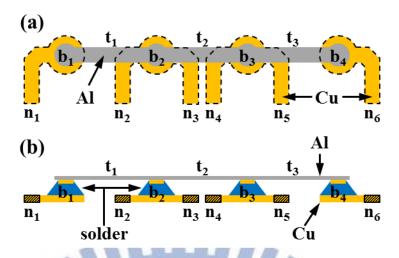

| Figure 2-2                                                                   | (a) Plan view and (b) front view of Kelvin bump structures in the                                    |  |  |

|                                                                              | flip-chip sample                                                                                     |  |  |

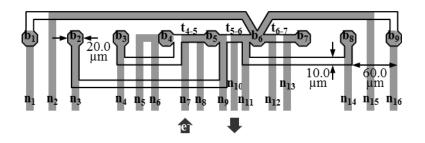

| Figure 2-4                                                                   | Kelvin bump structures in a 6-μm microbump41                                                         |  |  |

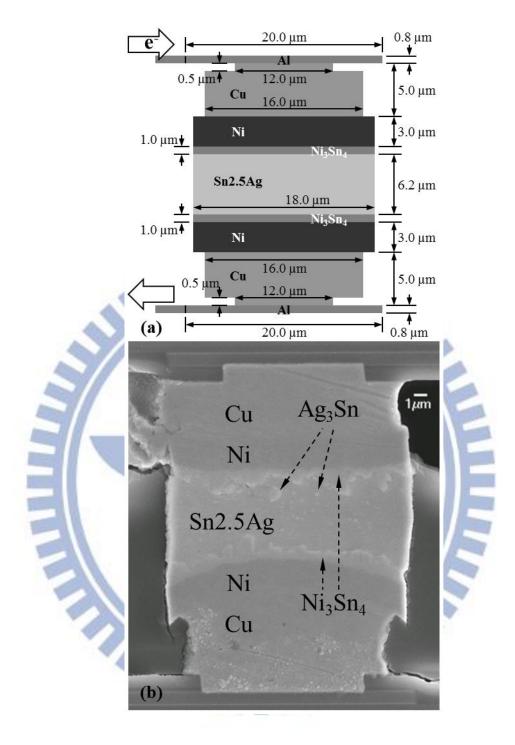

| Figure 2-5                                                                   | (a) Schematic plot and (b) cross-sectional SEM image of a 10-μm                                      |  |  |

|                                                                              | microbump; (c) 10-μm microbump structure tested                                                      |  |  |

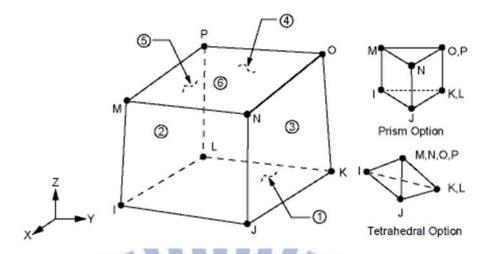

| Figure 2-6                                                                   | SOLID69 Geometry                                                                                     |  |  |

| Figure 2-7                                                                   | Procedures for building and solving a model                                                          |  |  |

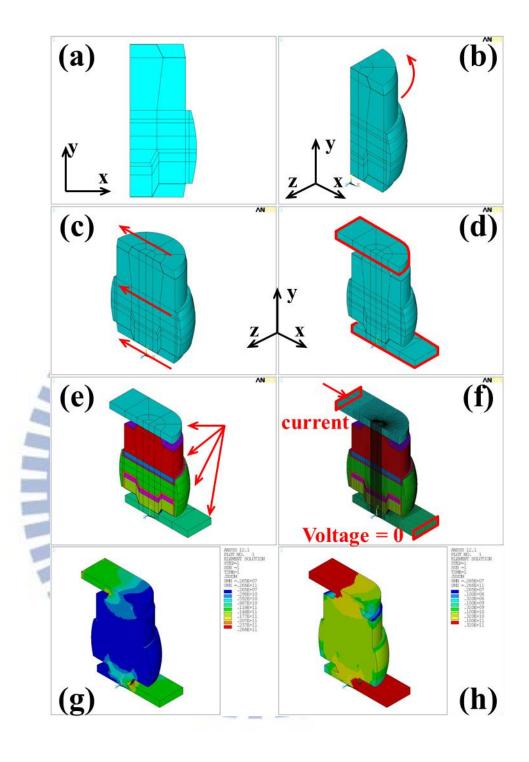

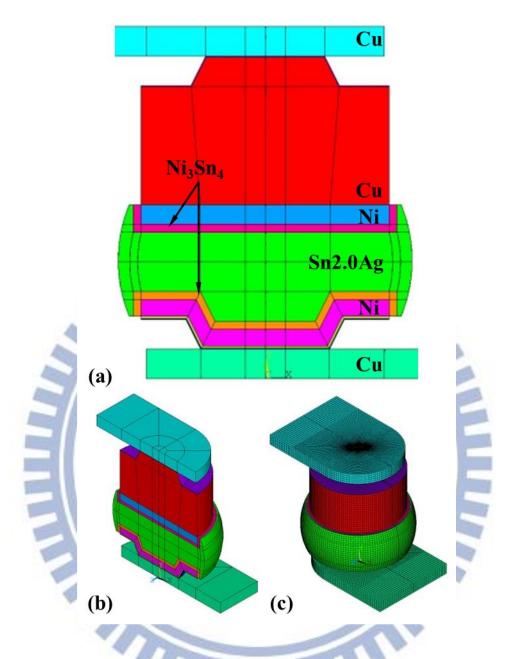

| Figure 2-8                                                                   | (a) Solid model cross-section of a flip-chip bump: (b) enlarged image of                             |  |  |

|             | the black-line region in (a); (c) oblique view of the solid model; and (d)                               |    |  |

|-------------|----------------------------------------------------------------------------------------------------------|----|--|

|             | element model of a flip-chip bump.                                                                       | 52 |  |

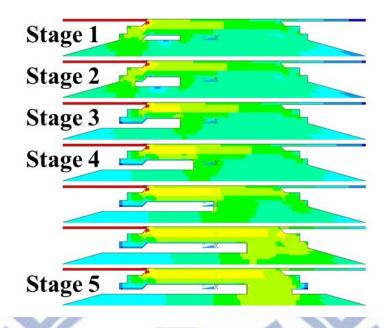

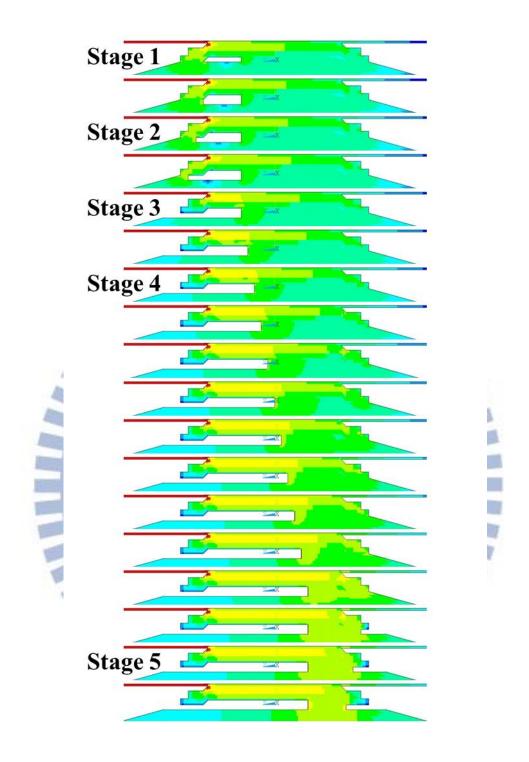

| Figure 2-9  | Different stages of void nucleation and propagation during EM test                                       | 53 |  |

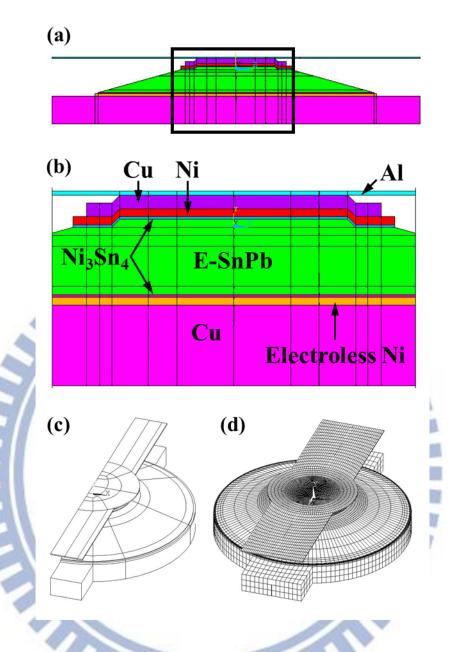

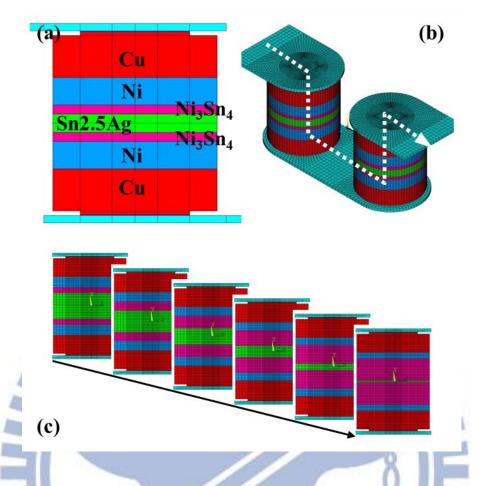

| Figure 2-11 | 1 (a) Cross-sectional view of solid model, (b) oblique view of solid model,                              |    |  |

|             | and (c) oblique view of element model of a 10-μm microbump                                               | 56 |  |

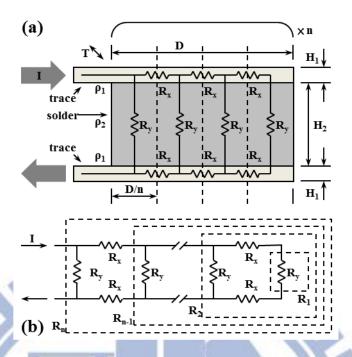

| Figure 2-13 | (a) Schematic plot of numerical model for calculating the resistance of a                                |    |  |

|             | microbump; and (b) the corresponding resistance network diagram                                          | 62 |  |

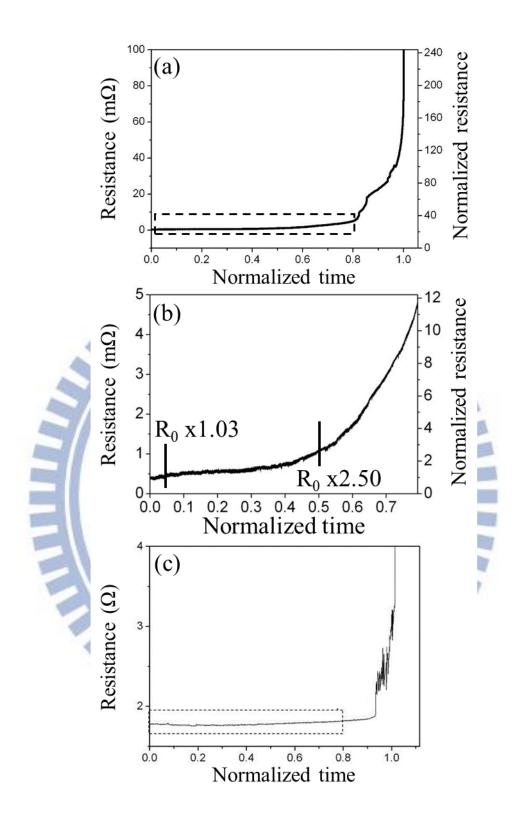

| Figure 3-1  | (a) Bump resistance curve of a flip-chip bump during EM test; (b)                                        |    |  |

|             | enlarged bump resistance curve of the dashed square in (a); and (c)                                      |    |  |

| 4           | resistance of entire circuit in the flip-chip sample.                                                    | 65 |  |

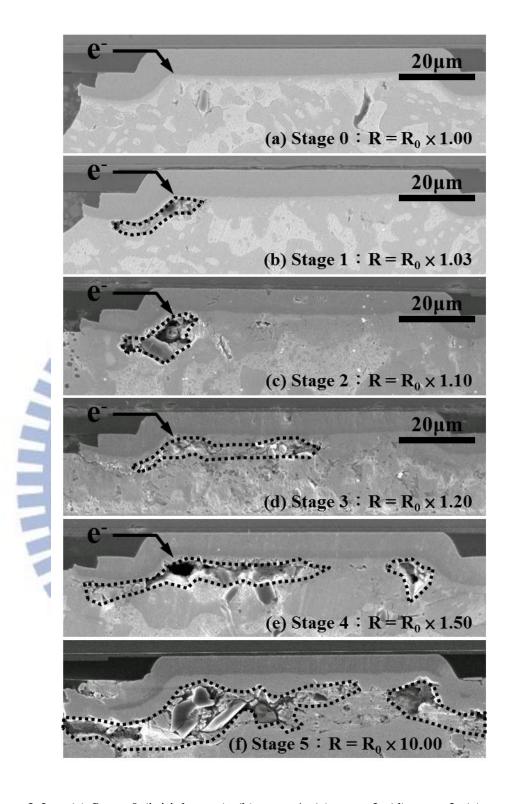

| Figure 3-2  | (a) Stage 0 (initial stage), (b) stage 1, (c) stage 2, (d) stage 3, (e) stage 4,                         |    |  |

|             | and (f) stage 5 of the failure caused by EM test                                                         | 68 |  |

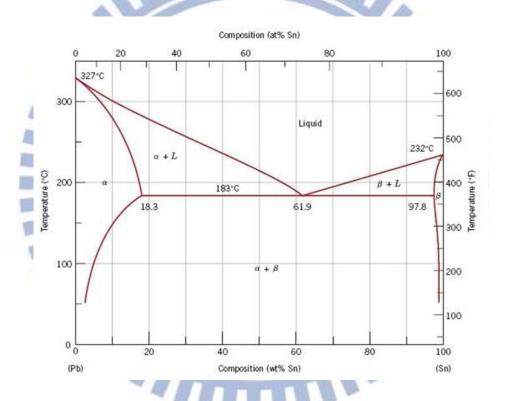

| Figure 3-3  | Binary Pb-Sn phase diagram.                                                                              | 69 |  |

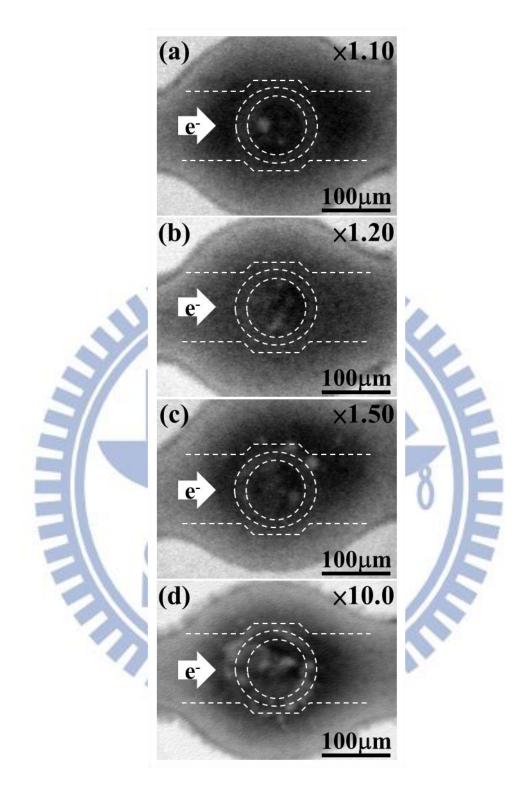

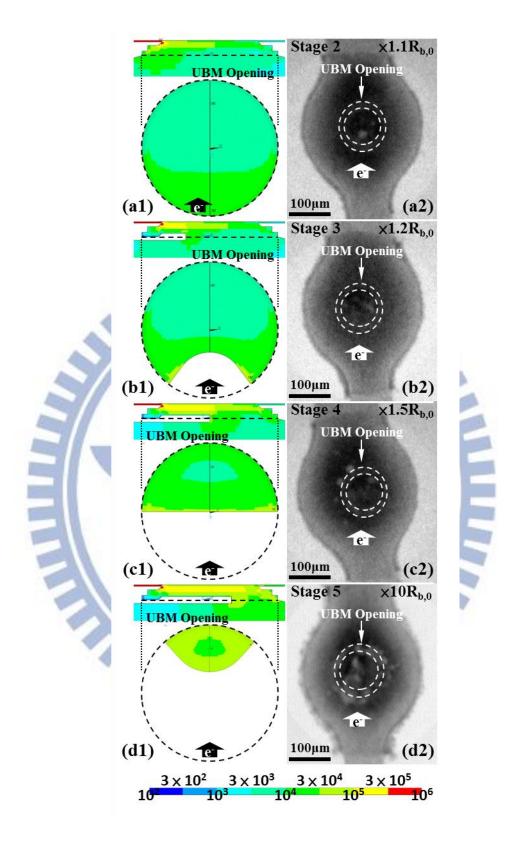

| Figure 3-4  | Plan-view X-ray image of (a) stage 2, (b) stage 3, (c) stage 4, and (d)                                  |    |  |

|             | stage 5                                                                                                  | 70 |  |

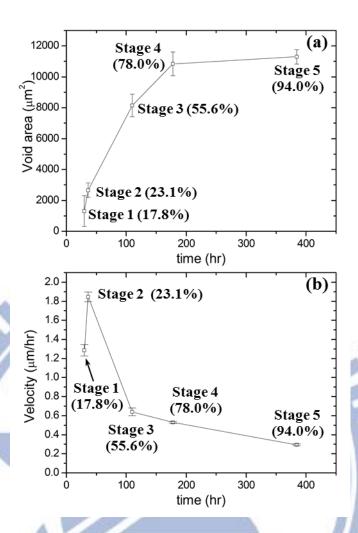

| Figure 3-5  | (a) Void depletion area at different stages during EM testing; and (b) void                              |    |  |

|             | depletion velocity along the interface at different stages during EM                                     |    |  |

|             | testing.                                                                                                 | 72 |  |

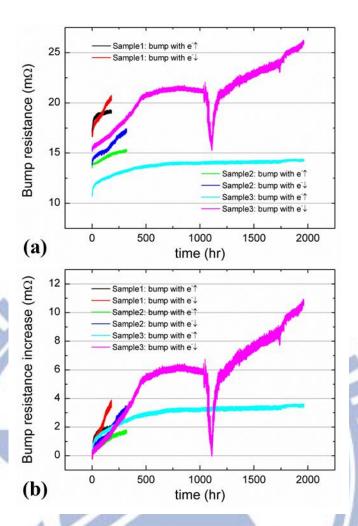

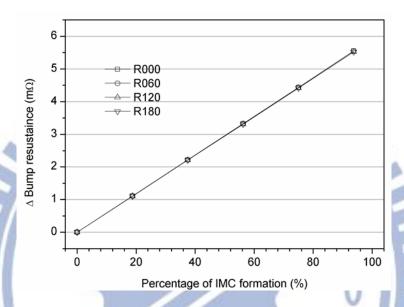

| Figure 3-6  | (a) Bump resistances and (b) increase in bump resistances of $6-\mu m$                                   |    |  |

|             | microbumps after current stressing by 0.12 A (4.6 $\times$ 10 <sup>4</sup> A/cm <sup>2</sup> ) on 150 °C |    |  |

|             | hot plate for different durations.                                                                       | 75 |  |

| Figure 3-7  | (a) Bump resistances and (b) increase in bump resistances of $6\text{-}\mu\text{m}$                      |    |  |

|             | microbumps after current stressing by 0.24 A (9.2 $\times$ 10 <sup>4</sup> A/cm <sup>2</sup> ) on 150 °C |    |  |

|             | hot plate for different durations.                                                                       | 76 |  |

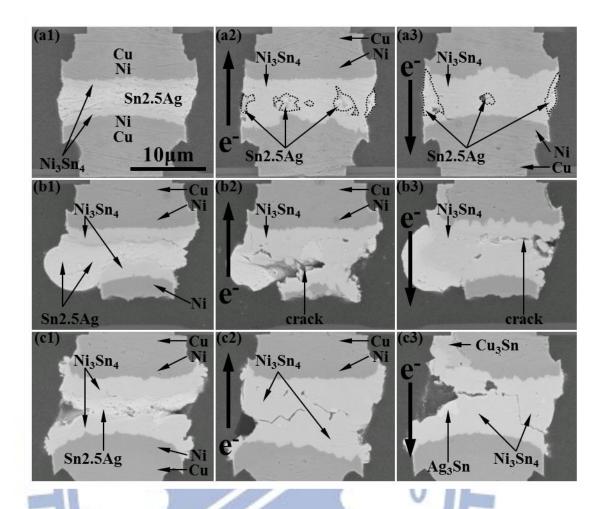

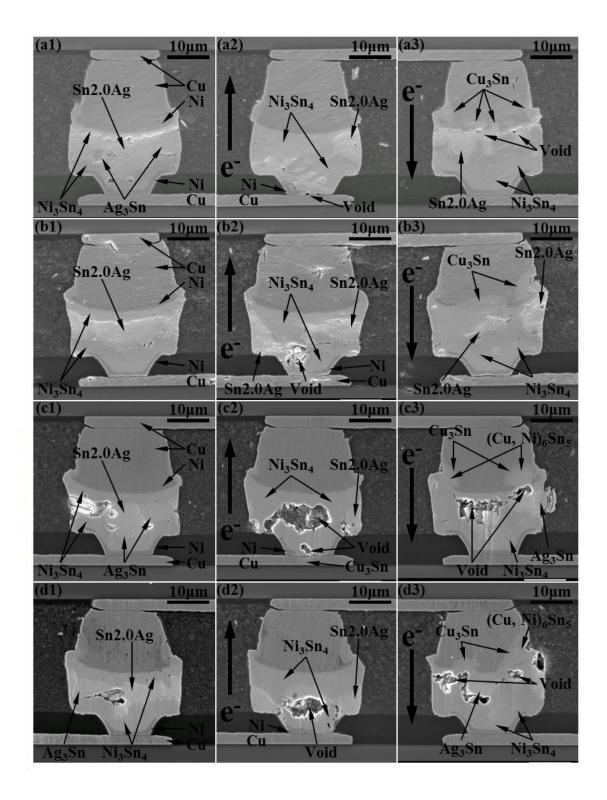

| Figure 3-8                                                               | 8-8 6-μm microbumps in samples EM tested for (a) 49.8 hr, (b) 321.6 hr, and                             |  |  |

|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|

|                                                                          | (c) 1961.8 hr by $0.12 \text{ A} (4.6 \times 10^4 \text{ A/cm}^2)$ on $150^{\circ}\text{C}$ hot plate81 |  |  |

| Figure 3-9 6-μm microbumps in samples EM tested for (a) 141.3 hr and (b) |                                                                                                         |  |  |

|                                                                          | by $0.24 \text{ A} (9.2 \times 10^4 \text{ A/cm}^2)$ on $150 ^{\circ}\text{C}$ hot plate82              |  |  |

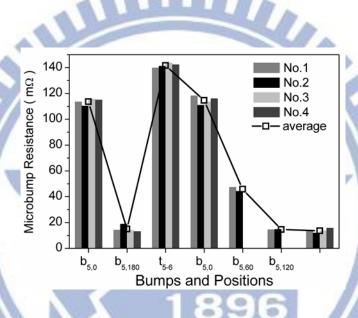

| Figure 3-10                                                              | Bump resistance of 6-µm microbumps at different angles and trace                                        |  |  |

|                                                                          | resistance of t <sub>5-6</sub> 84                                                                       |  |  |

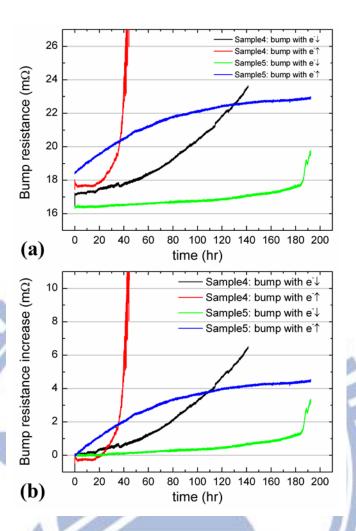

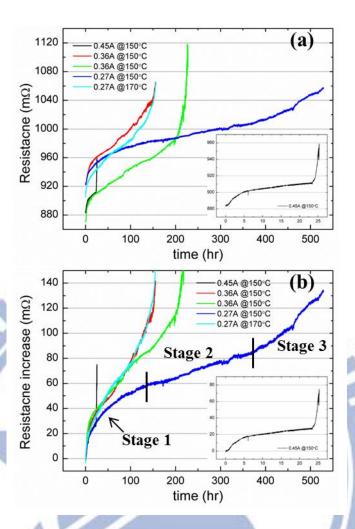

| Figure 3-11                                                              | (a) Bump resistance and (b) increase in bump resistance of 10-μm                                        |  |  |

|                                                                          | microbumps during EM testing87                                                                          |  |  |

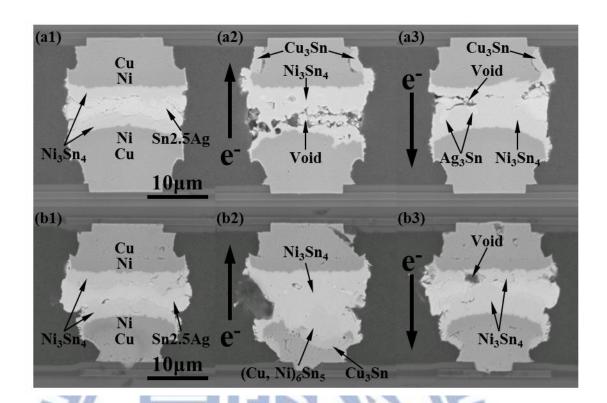

| Figure 3-12                                                              | 10- $\mu$ m microbump samples EM tested (a) for 25.3 hr by 0.45 A (1 $\times$ 10 <sup>5</sup>           |  |  |

| 4                                                                        | A/cm <sup>2</sup> ) in 150°C oven, (b) for 227.9 hr by 0.36 A $(8 \times 10^4 \text{ A/cm}^2)$ in       |  |  |

|                                                                          | $150$ °C oven, (c) for 529.1 hr by 0.27 A (6 × $10^4$ A/cm <sup>2</sup> ) in $150$ °C oven,             |  |  |

|                                                                          | and (d) for 194.3 hr by 0.27 A in 170°C oven90                                                          |  |  |

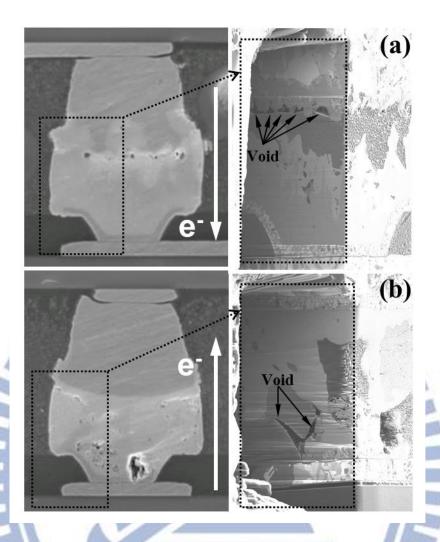

| Figure 3-13                                                              | The cross-sectional focused ion beam (FIB) image of the bump stressed                                   |  |  |

|                                                                          | by (a) downward electron flow and (b) upward electron flow91                                            |  |  |

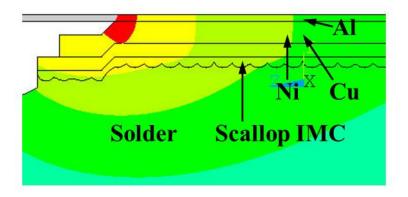

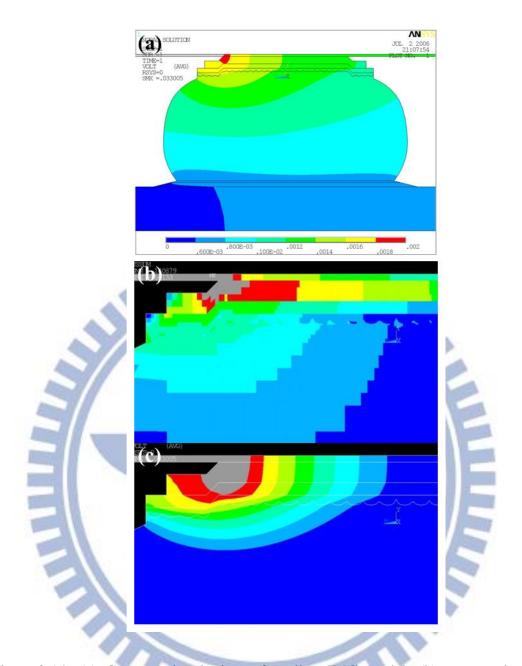

| Figure 3-14                                                              | (a) Cross-sectional view of scallop IMC model; (b) current density                                      |  |  |

|                                                                          | distribution and (c) voltage distribution of current crowding region in the                             |  |  |

|                                                                          | scallop IMC model                                                                                       |  |  |

| Figure 3-15                                                              | Voltage distribution of (a) scallop IMC model and (b) uniform-thickness                                 |  |  |

|                                                                          | IMC model. 94                                                                                           |  |  |

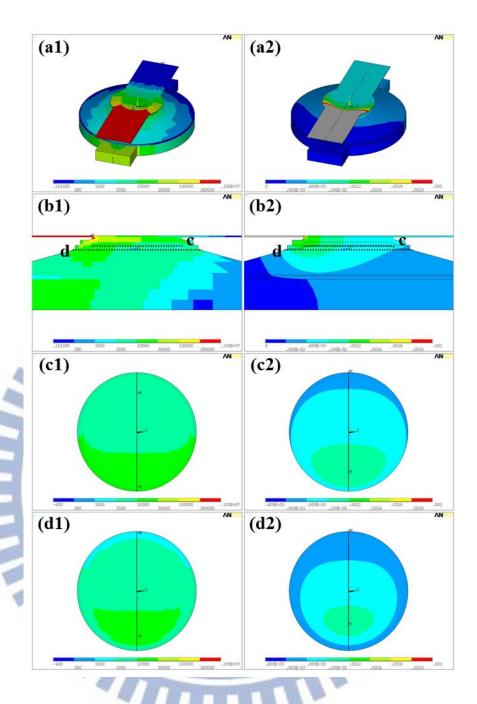

| Figure 3-16                                                              | (a) Oblique view and (b) cross-sectional view of the entire flip-chip bump                              |  |  |

|                                                                          | model; (c) plan-view distribution of the plane marked as "c" in (b); and (d)                            |  |  |

|                                                                          | plan-view distribution of the plane marked as "d" in (b)96                                              |  |  |

| Figure 3-17                                                              | Current density distribution near current-crowding region of different                                  |  |  |

|                                                                          | stages during void propagation caused by EM97                                                           |  |  |

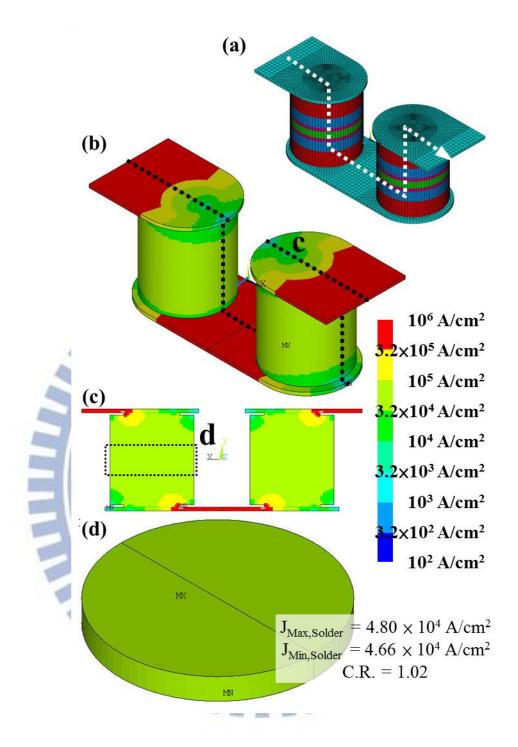

| Figure 3-18 (a) Oblique view of entire model and (b) oblique view of current density |                                                                            |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|

|                                                                                      | distribution of 6-µm microbumps; (c) current density distribution of       |  |  |  |  |

|                                                                                      | cross-section marked as "c" in (b); and (d) oblique current density        |  |  |  |  |

|                                                                                      | distribution of cross-section marked as "d" in (c)                         |  |  |  |  |

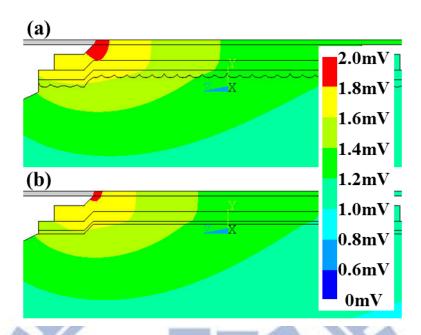

| Figure 3-19                                                                          | Bump resistance of a 6-µm microbump at different angles during uniform     |  |  |  |  |

|                                                                                      | growth of IMC 101                                                          |  |  |  |  |

| Figure 3-20                                                                          | Cross-sectional current density distribution of (a) entire model and (b)   |  |  |  |  |

|                                                                                      | solder part in 10-μm microbump                                             |  |  |  |  |

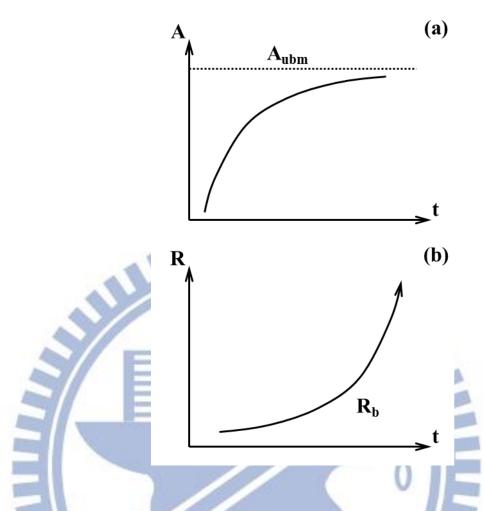

| Figure 4-1                                                                           | (a) Schematic void depletion area of flip-chip bumps; and (b) schematic    |  |  |  |  |

| 4                                                                                    | bump resistance of flip-chip bumps                                         |  |  |  |  |

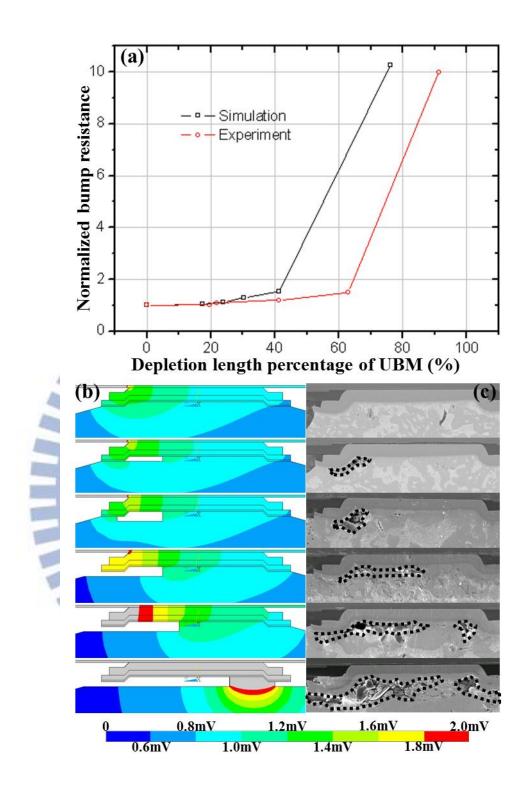

| Figure 4-2                                                                           | (a) Bump resistance curves obtained from FEM and Kelvin bump               |  |  |  |  |

|                                                                                      | structures; (b) cross-sectional voltage distribution in FEM; and (c)       |  |  |  |  |

|                                                                                      | cross-sectional microstructure at different stages of void propagation 108 |  |  |  |  |

| Figure 4-4                                                                           | Influence of design rule on relationship between passivation and Al pad112 |  |  |  |  |

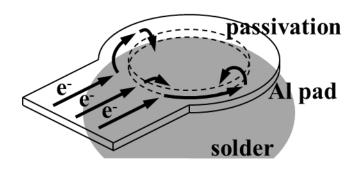

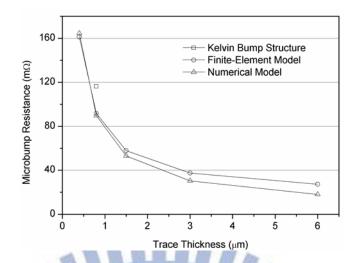

| Figure 4-5                                                                           | Microbump resistances obtained from Kelvin bump structures, FEM, and       |  |  |  |  |

| 4                                                                                    | numerical model with different Al trace thicknesses                        |  |  |  |  |

|                                                                                      |                                                                            |  |  |  |  |

|                                                                                      |                                                                            |  |  |  |  |

|                                                                                      |                                                                            |  |  |  |  |

|                                                                                      |                                                                            |  |  |  |  |

# **List of Tables**

| Table 1-1 | Melting temperatures, diffusivities, and diffusion mechanisms for Cu, Al, |  |  |

|-----------|---------------------------------------------------------------------------|--|--|

|           | Pb, and SnPb solder [2]10                                                 |  |  |

| Table 2-1 | Nodes used for measuring bump resistances of a flip-chip bump with        |  |  |

|           | current applied from n <sub>4</sub> to n <sub>3</sub>                     |  |  |

| Table 2-2 | Bump resistance values at the different stages                            |  |  |

| Table 2-3 | Nodes used for measuring resistances of a 6-µm microbump with current     |  |  |

| -         | applied from n <sub>10</sub> to n <sub>7</sub> 41                         |  |  |

| Table 2-4 | Materials properties used in this study47                                 |  |  |

| Table 3-1 | Current stressing time at different stages69                              |  |  |

| Table 3-2 | Bump resistance of 6-µm microbumps at different angles and trace          |  |  |

|           | resistance of t <sub>5-6</sub> 84                                         |  |  |

| Table 3-3 | Trace resistance and the bump resistances at different angles of a 6-µm   |  |  |

| 1         | microbump obtained using FEM                                              |  |  |

|           |                                                                           |  |  |

|           |                                                                           |  |  |

|           |                                                                           |  |  |

### **Chapter 1. Introduction**

### 1.1. Flip-Chip Technology

In order to satisfy the requirement of miniaturization of portable devices, flip-chip technology has been adopted for high-density packaging due to its excellent electrical characteristic and superior heat dissipation capability [1-2]. Owing to the demand for higher performance in microelectronics devices, flip-chip technology was adopted to generate more signals and power interconnections than wire bonding in electronic devices. In the 1960s, IBM first developed the flip-chip technology, known as controlled-collapse-chip-connection (C4) [3-5]. In the C4 technology, high-Pb solder with high melting temperature (around 320°C) was used as the joint material [6]. At that time, chips were aligned on ceramic substrates. This C4 technology gained wide utilization in the 1980s since it provided advantages in size, performance, flexibility, and reliability among all packaging methods. Because of area array capability in flip-chip technology, product size, solder bump height, and interconnect length are all effectively reduced, providing higher input/output (I/O) count and faster speed in electronic devices.

In the procedure of flip-chip assemblies, solder bumps need to be deposited first onto the under bump metallurgy (UBM) on the chip side. The functions for under bump metallurgies are: (1) to adhere well on the underlying metal line such as Al or Cu, and on the surrounding IC passivation layer, (2) to act as a strong barrier, thus preventing the diffusion of bump metals in the integrated circuit (IC), and (3) to become readily wettable to the bump metals during solder reflow. For example, a thin film Cr/Cu/Au UBM is adopted for the high-Pb solder alloy in the C4 technology.

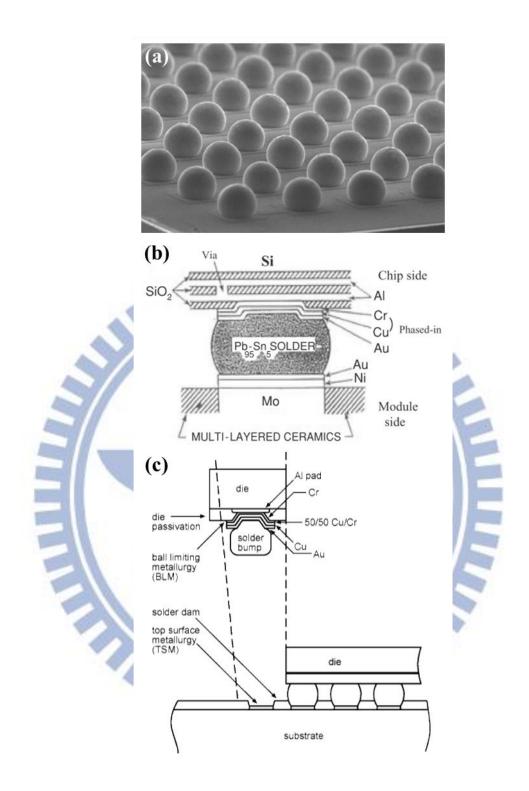

The tilt view of solder joints on silicon ship is shown in Figure 1-1 (a). Figure

1-1 (b) is the cross-sectional view of the flip-chip solder joints. As depicted in Figure 1-1 (c), the chip with IC is then placed upside down (flip-chip), and all the joints are formed simultaneously between chip and substrate during the reflowing process. In the flip-chip process, electrical connections are the array of solder bumps on the chip surface; hence, the interconnect distance between package and chip is effectively reduced. In addition, the consequent resistance / capacitance (RC) delay is also reduced, too. The density of I/O is limited by minimum distance between adjacent bonding pads. For high-end devices and when size reduction is the main concern, area-arrayed flip-chip technologies offer the only choice that meets the current needs.

However, the flip-chip technology continues to evolve due to certain concern. In order to reduce the budget of the consumer electronics, polymer substrates, such as Bismaleimide Triazine (BT) or Flame Retardant 4 (FR4), are induced to replace ceramic substrates. Consequently, high-Pb solder is no longer used due to its high melting temperature (320°C) since polymers have very low glass transition temperature. Instead, the eutectic SnPb (E-SnPb) solder alloy is used in view of its low melting point of 183°C. Next, owing to environment concern, Pb-free solder alloys replace toxic Pb-containing solder alloys thus rendering thin-film UBMs no longer suitable for the original purpose. Therefore, electroplated 5-μm Cu or 5-μm Cu/3-μm Ni was used as the UBM for the Pb-free solder joints to avoid balling that comes with the adoption of the Pb-free solder alloys. With these evolutions, several kinds of solder alloys and UBMs have been proposed for flip-chip assemblies, and the many combinations make the flip-chip technology complicated and complex to study. Nevertheless, knowledge of the best solder alloy and UBM will be of much use and provide lots of benefits to the companies.

Figure 1-1 (a) Tilt-view SEM image of solder bumps array on silicon die [2]; (b) a flip-chip solder joint connecting the chip side and the substrate side [2]; and (c) the chip placed upside down onto the substrate and the joint formed simultaneously between chip and substrate by reflow [1].

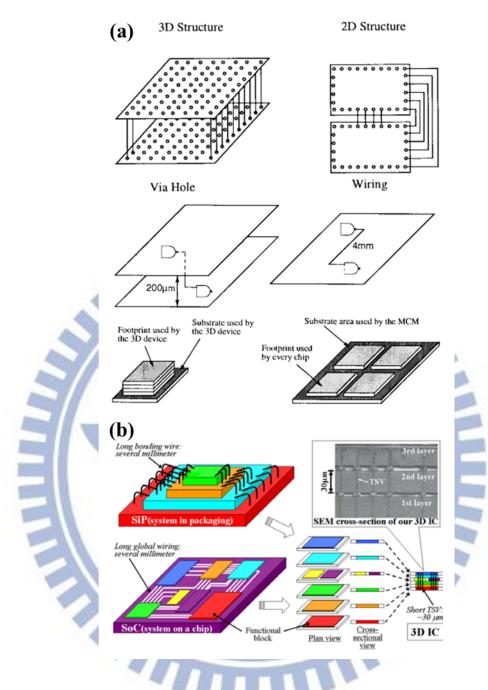

#### 1.2. Microbump Technology