國立交通大學

電機工程研究所

碩士論文

使用最小線間距之低功率高速晶片內部匯流排電路設計

Low-Power High-Speed On-Chip Bus Design with

Minimum Spacing

研究 生：許耿嘉

指導教授：蘇朝琴 教授

中華民國一百零二年十月

使用最小線間距之低功率高速晶片內部匯流排電路設計

Low-Power High-Speed On-Chip Bus Design with Minimum

Spacing

研究 生：許耿嘉

Student : Ken-Chia Hsu

指導教授：蘇朝琴 教授

Advisor : Chau-Chin Su

國 立 交 通 大 學

電控工程研究所

碩士論文

A Thesis

Submitted to Institute of Electrical and Computer Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of Master

in

Electrical Control Engineering

October 2013

Hsinchu, Taiwan, Republic of China

中 華 民 國 一 百 零 二 年 十 月

# 使用最小線間距之低功率高速晶片內部匯流排電路設計

研究生：許耿嘉

指導教授：蘇朝琴 教授

國立交通大學電機工程研究所

## 摘要

本論文提出一個使用最小線間距之低功率晶片內匯流排系統，工作電壓操作在臨界電壓上，大幅降低功率消耗。為了要節省面積的支出因此晶片內匯流排將採取最小線距，此舉讓線間耦合電容大幅上升，耦合效應也隨著耦合電容得增加造成更嚴重的信號抖動。為了要避免耦合效應之影響，常見的方式為加入屏蔽線接地包圍在信號線間，而此作法將大幅增加負載讓速度下降並消耗更多功率，因此我們採取部分屏蔽式匯流排架構，如同完全屏蔽讓耦合效應得到抑制又有較小的負載，較小的負載能減輕 ISI 效應，讓 ISI 效應與耦合雜訊得以取得最佳的平衡點。藉此讓匯流排得到足夠的保護以抑制信號抖動，相對較小的負載又能減少功率的消耗並讓速度提升。

本論文以 TSMC MSG90 製程製作，操作電壓為 1V，TT corner 下資料速率可達 2Gbps，功率消耗為 5.38mW，晶片布局面積為  $1\text{mm}^2$  ( $1\text{mm} \times 1\text{mm}$ )。

關鍵字：晶片內部匯流排、拔靴帶式電路、置入中繼器、低功率消耗、置入屏蔽

# Low-Power High-Speed On-Chip Bus Design with Minimum Spacing

Student: Chia-Ken Hsu      Advisor: Chau-Chin Su

Institute of Electrical and Computer Engineering

National Chiao Tung University

This thesis proposes a low power on-chip bus with minimum spacing. The supply voltage is near the threshold voltage of MOSFET to reduce the power consumption. To save the chip area we use minimum spacing, but this arrangement will increase the coupling capacitance between wires. With the increasing of coupling capacitance, jitter which due to coupling effect becomes more and more serious. This thesis proposes a partial shielding design. It protects wire from couple effect as fully shielded bus but with less loading. The less loading from ground shielding alleviates the inter symbol interference. The compromise between coupling noise and ISI effect can be optimized. It lets the bus be protected appropriately to be free from coupling jitter. At the same time, lets the power consumption decrease and data-rate increase with loading decrease.

The chip is implemented in TSMC MSG90nm process, and the supply voltage is 1V. At TT corner, the data rate is 2Gbps. The total power is 5.38mW, the chip area is 1mm<sup>2</sup> (1mm×1mm).

Keyword: on-chip bus, bootstrapped circuits, shielding insertion, low power consumption

# 致 謝

十幾年的學生成長即將於交大暫畫句點，回首過往每個逆境時刻，一張張臉就自記憶深處浮現出來，讓我知道看似順遂的求學之路其實是承蒙著無數人的幫助，由衷感謝支持著我的每一個人，人生有你們真是太棒了！

感謝我的指導老師 蘇朝琴教授，與老師討論之時，老師總能以不同的面向擊中問題的核心，刺激著我以多元的方式思考問題，對於研究嚴謹的態度，與講求邏輯的思考方式，讓我除了在學術知識上有所增長，更讓我學習做事的方法與面對問題應有的態度。感謝盈杰學長給予我的指導與幫助，學長豐富的經驗與知識，每每讓我在瓶頸中藉由與學長討論而得以突破。感謝我的戰友馬克與嘉哲，這三年來各種難關總是一起走過，到了最後也要一起跨出學校大門，碩班三年感謝有你們相伴！感謝紅豆與昶志、順煜、澤勝、弘宇、璟伊等學長們，還有皓鈞、子軒、可卿、可謙、勇志、政隆、怡婷等學弟妹們，因為你們讓 918LAB 充滿歡笑！

感謝我的室友們，打從中央開始的老室友感謝你們平時的幫助，往後的日子還要請你們多多關照。也謝謝家貓橙橙，西西，琪琪，有時心情不好遷怒你們，還讓你們每天吃一成不變的飼料，你們依然每天探頭過來磨蹭討摸，我會以每天讓你們吃罐頭為目標努力的！

感謝我的爸爸媽媽，你們給我的支持造就了我的全部，我不知道是能否達到你們的期望，然而作為第一步我會以不再讓你們擔心為目標，依照你們的樣子勤奮的生活、努力地做每件事！最後，感謝主，雖然還不是受洗的基督徒，然而每當遭逢難關總是習慣性地低頭祈禱，讓我能頂住壓力衝過每個浪頭。

2013.11.25

# 目錄

|                   |     |

|-------------------|-----|

| 摘要                | i   |

| Abstract          | ii  |

| 致 謝               | iii |

| 目 錄               | iv  |

| 第一章               | 1   |

| 緒論                | 1   |

| 1.1 研究動機          | 2   |

| 1.2 論文結構          | 3   |

| 第二章               | 4   |

| 背景回顧              | 4   |

| 2.1 低功率中繼器        | 4   |

| 2.2 拔靴帶式反向器電路     | 6   |

| 2.3 拔靴帶式反向器電路模擬結果 | 11  |

| 2.4 汇流排等效電容模型     | 13  |

| 2.5 中繼器交錯式排列      | 14  |

| 2.6 混和極性中繼器       | 15  |

---

|                           |           |

|---------------------------|-----------|

| 2.7 邊緣調整 .....            | 16        |

| 2.8 主動式屏蔽 .....           | 18        |

| <b>第三章 .....</b>          | <b>19</b> |

| <b>晶片內部匯流排模型 .....</b>    | <b>19</b> |

| 3.1 晶片內部匯流排模型 .....       | 19        |

| 3.2 晶片內部連接線模型 .....       | 20        |

| 3.3 估計時間常數 .....          | 22        |

| 3.4 置入中繼器之時間常數 .....      | 24        |

| 3.5 晶片內部匯流排電阻電容模型 .....   | 26        |

| <b>第四章 .....</b>          | <b>30</b> |

| <b>晶片內部匯流排系統 .....</b>    | <b>30</b> |

| 4.1 晶片內部匯流排系統 .....       | 30        |

| 4.2 轉態邊緣交錯機制 .....        | 32        |

| 4.3 緊耦合效應 .....           | 37        |

| 4.4 屏蔽比例分析 .....          | 42        |

| 4.5 ISI 抖動 .....          | 47        |

| 4.6 完全屏蔽與 85% 屏蔽之比較 ..... | 52        |

| <b>第五章 .....</b>          | <b>59</b> |

---

|                   |    |

|-------------------|----|

| 電路之實現.....        | 59 |

| 5.1 佈局架構簡介.....   | 59 |

| 5.2 偽隨機信號產生器..... | 61 |

| 5.3 轉態邊緣交錯機制..... | 62 |

| 5.4 匯流排電路.....    | 63 |

| 5.5 晶片佈局.....     | 64 |

| 5.6 模擬結果.....     | 66 |

| 5.7 量測環境設定.....   | 72 |

| 5.8 量測結果.....     | 74 |

| 規格與比較.....        | 78 |

| 第六章.....          | 80 |

| 結論.....           | 80 |

| 參考文獻.....         | 81 |

---

# 圖 目 錄

|                                            |    |

|--------------------------------------------|----|

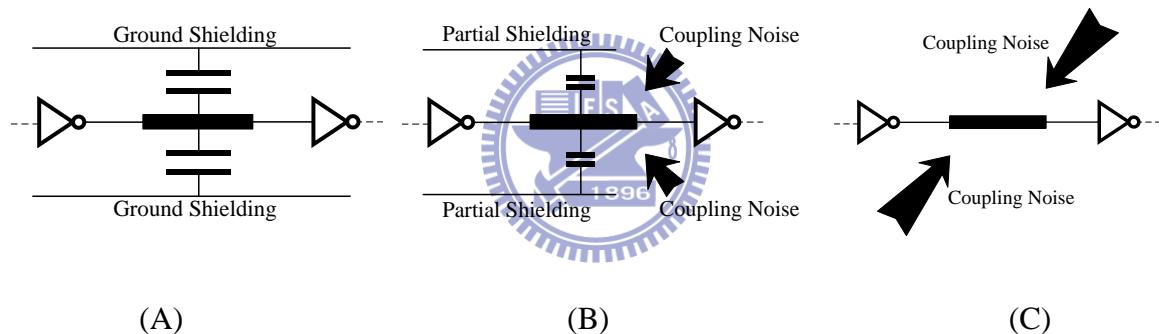

| 圖 1.1 匯流排之耦合電容與基底電容示意圖.....                | 2  |

| 圖 1.2 (A)完全屏蔽 (B)部分屏蔽 (C)沒有屏蔽 .....        | 3  |

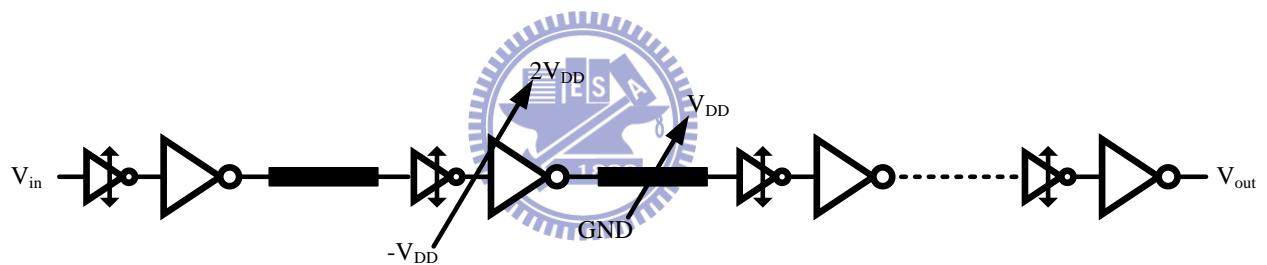

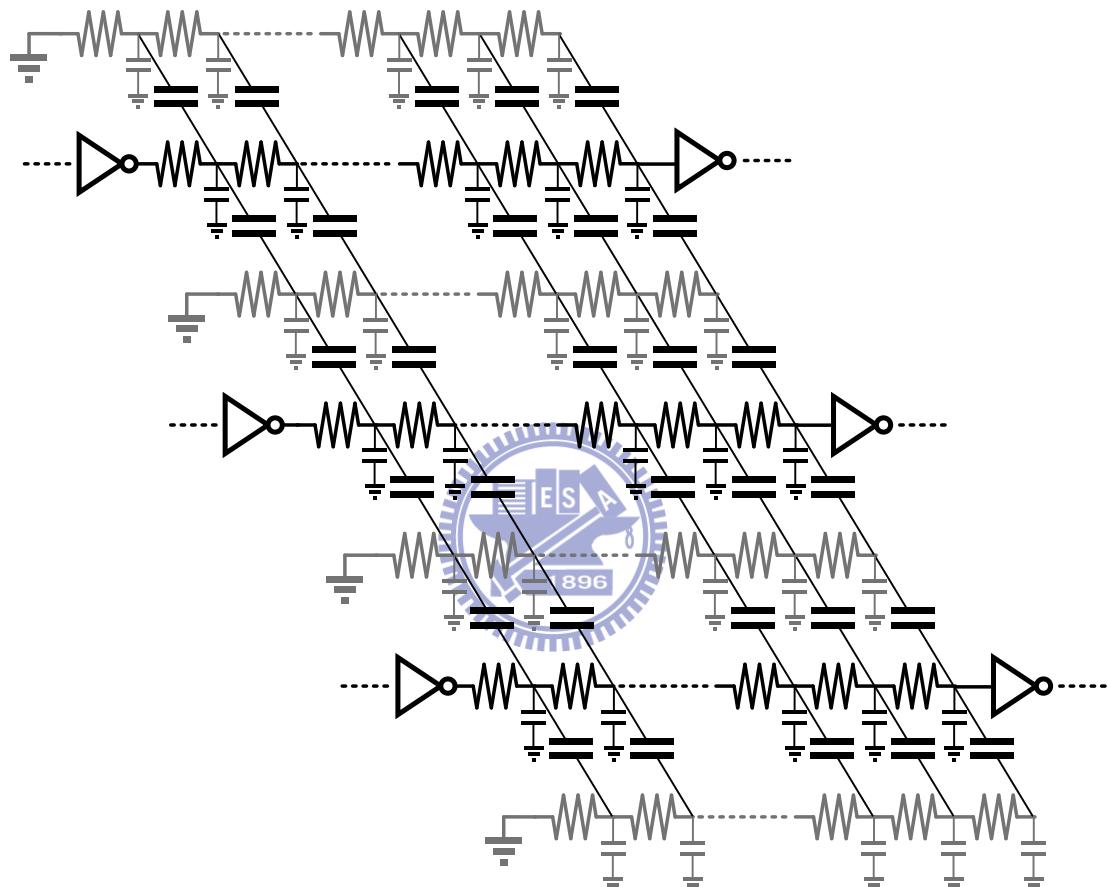

| 圖 2.1 置入了拔靴帶式中繼器的晶片內部傳輸線系統.....            | 4  |

| 圖 2.2 本論文的拔靴帶式晶片內部傳輸線系統.....               | 5  |

| 圖 2.3 本論文的拔靴帶式中繼器負載.....                   | 5  |

| 圖 2.4 拔靴帶式反相器.....                         | 6  |

| 圖 2.5 拔靴帶式反相器操作原理(輸入由 $V_{DD}$ 轉 0) .....  | 8  |

| 圖 2.6 拔靴帶式反相器操作原理(輸入由 0 轉 $V_{DD}$ ) ..... | 8  |

| 圖 2.7 拔靴帶式電路之 PN 介面示意圖 .....               | 9  |

| 圖 2.8 拔靴帶式電路在不同操作電壓下之升降壓效果模擬圖.....         | 10 |

| 圖 2.9 拔靴帶式反相器各節點電壓波形圖.....                 | 11 |

| 圖 2.10 拔靴帶式反相器與傳統 CMOS 反相器比較 .....         | 12 |

| 圖 2.11 平行線等效電容模型.....                      | 13 |

| 圖 2.12 中繼器以交錯的方式擺放.....                    | 14 |

| 圖 2.13 置入反相和非反相中繼器使得相鄰線互補轉態.....           | 15 |

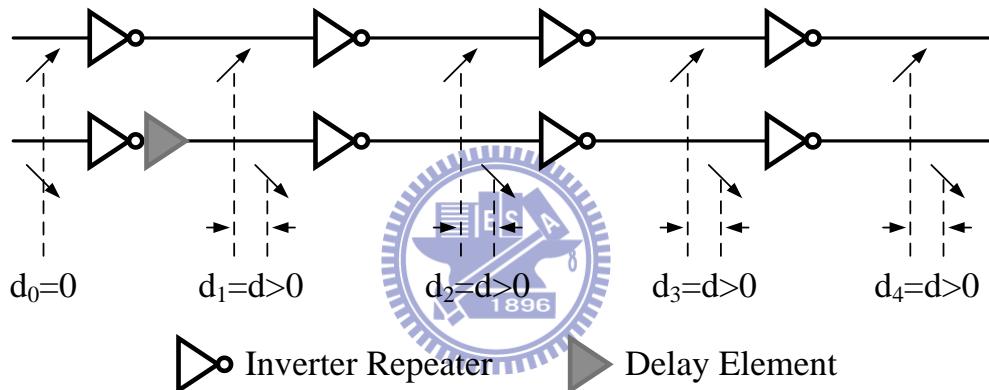

| 圖 2.14 加入延遲元件錯開相鄰線之轉態邊緣.....               | 16 |

| 圖 2.15 使用上升下降時間不對稱的中繼器來降低 MCF .....        | 17 |

| 圖 2.16 單邊邊緣調整以降低 MCF .....                 | 17 |

| 圖 2.17 主動式屏蔽.....                          | 18 |

| 圖 3.1 晶片內部連接線示意圖.....                      | 20 |

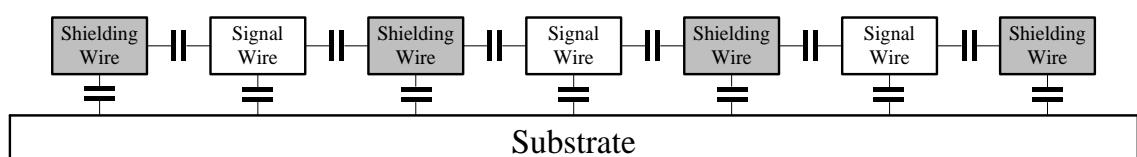

| 圖 3.2 晶片內連接線電容模型.....                      | 20 |

| 圖 3.3 結合式電阻電容模型.....                       | 22 |

| 圖 3.4 分散式電阻電容模型.....                       | 23 |

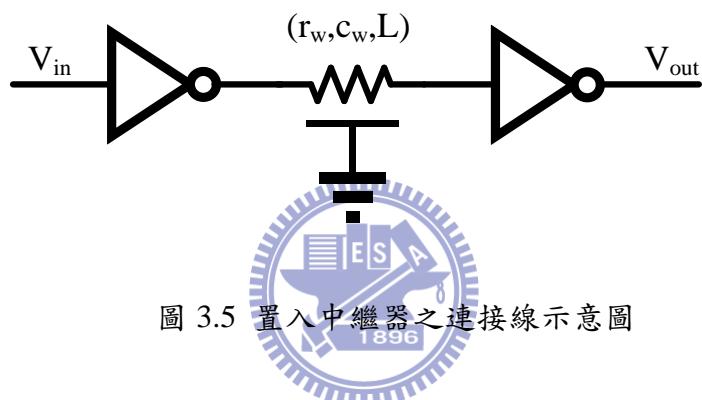

| 圖 3.5 置入中繼器之連接線示意圖.....                    | 24 |

---

|                                     |    |

|-------------------------------------|----|

| 圖 3.6 置入中繼器等效模型.....                | 24 |

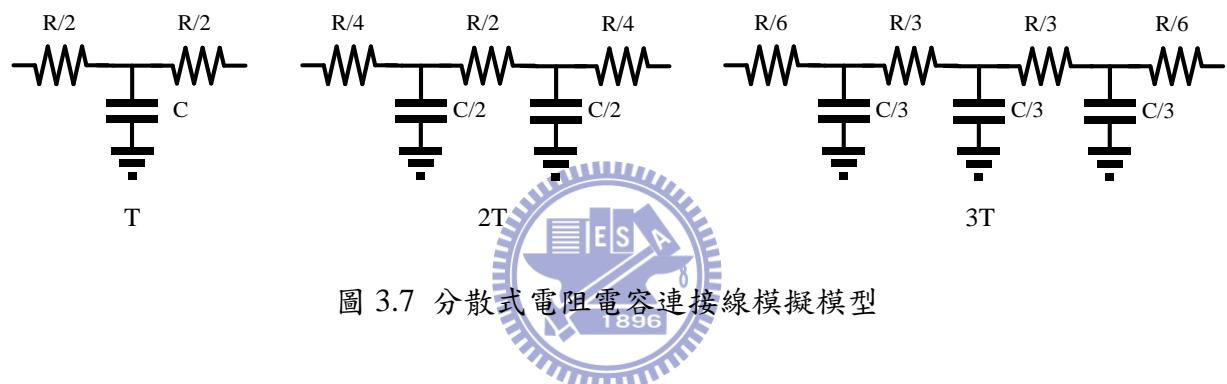

| 圖 3.7 分散式電阻電容連接線模擬模型.....           | 24 |

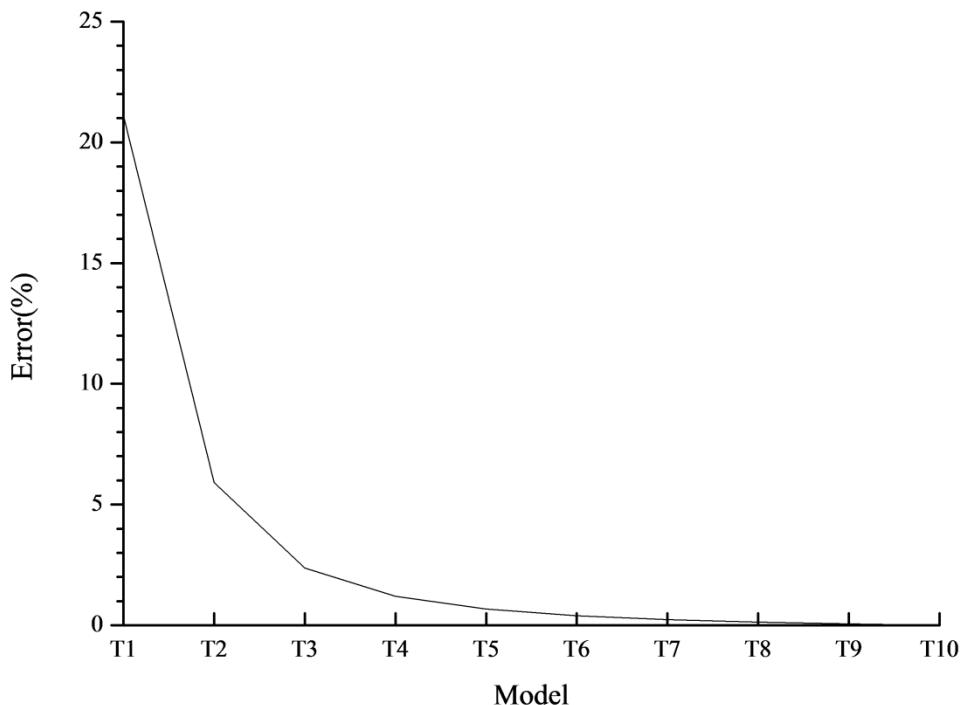

| 圖 3.8 T1-T10 模型之差異量 .....           | 27 |

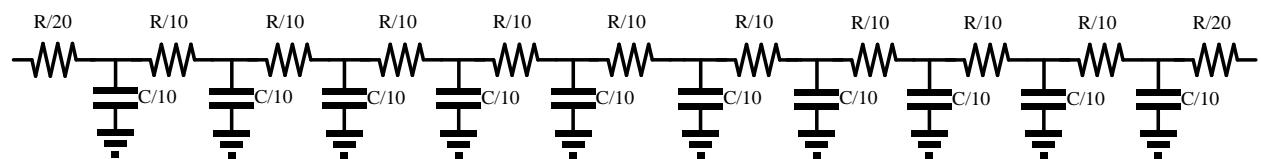

| 圖 3.9 T10 分散式模型 .....               | 28 |

| 圖 3.10 T10 匯流排模型 .....              | 28 |

| 圖 3.11 匯流排截面圖 .....                 | 28 |

| 圖 3.12 結合式匯流排模型.....                | 29 |

| 圖 4.1 (A)完全屏蔽 (B)部分屏蔽 (C)沒有屏蔽 ..... | 31 |

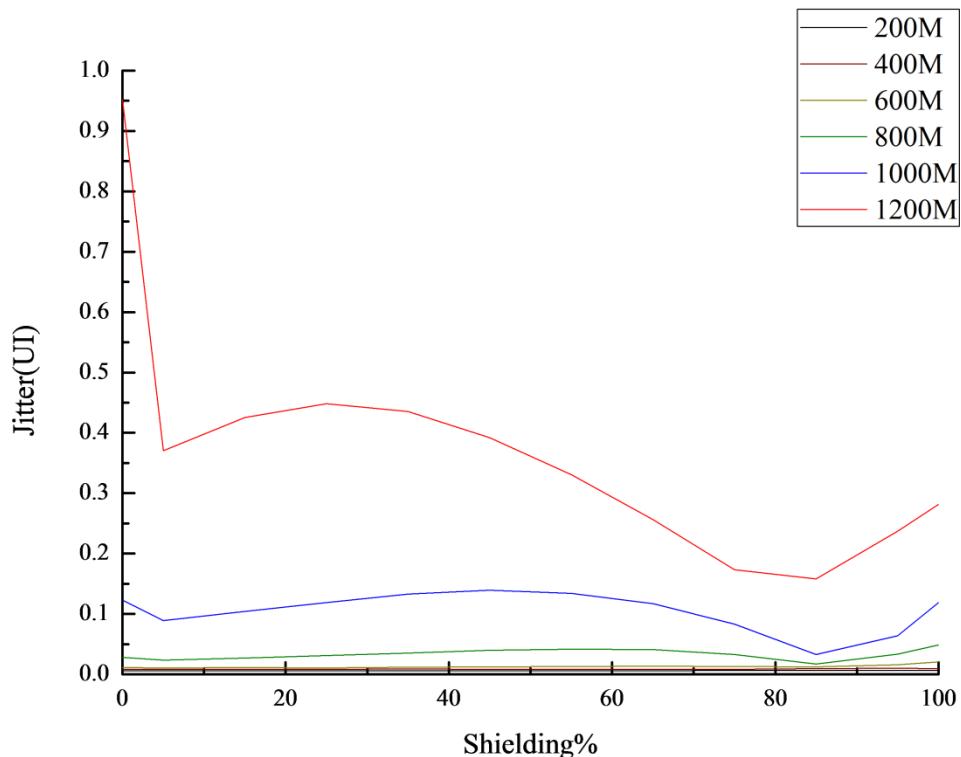

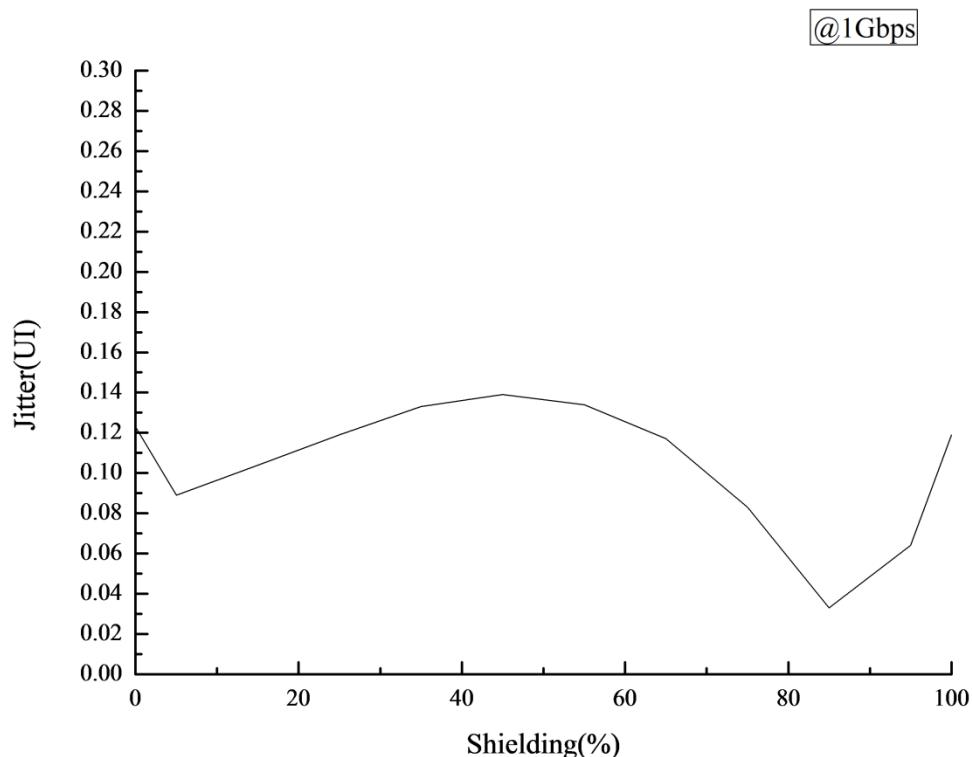

| 圖 4.2 使用屏蔽線保護之比例與信號抖動之關係.....       | 32 |

| 圖 4.3 平行線間等效電容.....                 | 33 |

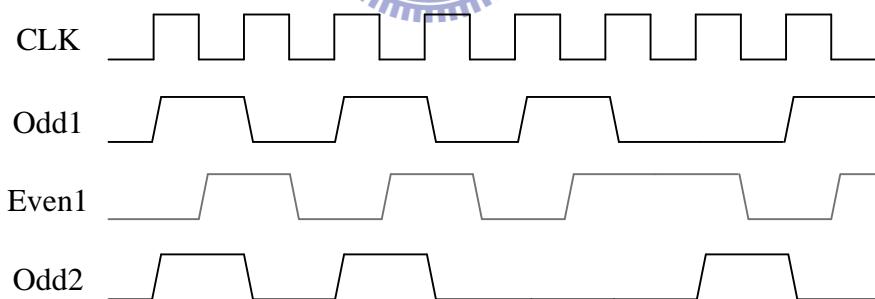

| 圖 4.4 轉態邊緣交錯機制示意圖 .....             | 35 |

| 圖 4.5 操作波形示意圖 .....                 | 35 |

| 圖 4.6 不使用轉態邊緣交錯機制 .....             | 36 |

| 圖 4.7 使用轉態邊緣交錯機制 .....              | 37 |

| 圖 4.8 正向突波模型 .....                  | 38 |

| 圖 4.9 反向突波模型 .....                  | 40 |

| 圖 4.10 耦合產生突波造成信號抖動.....            | 41 |

| 圖 4.11 部分屏蔽匯流排示意圖 .....             | 42 |

| 圖 4.12 加入屏蔽線後之匯流排模型 .....           | 43 |

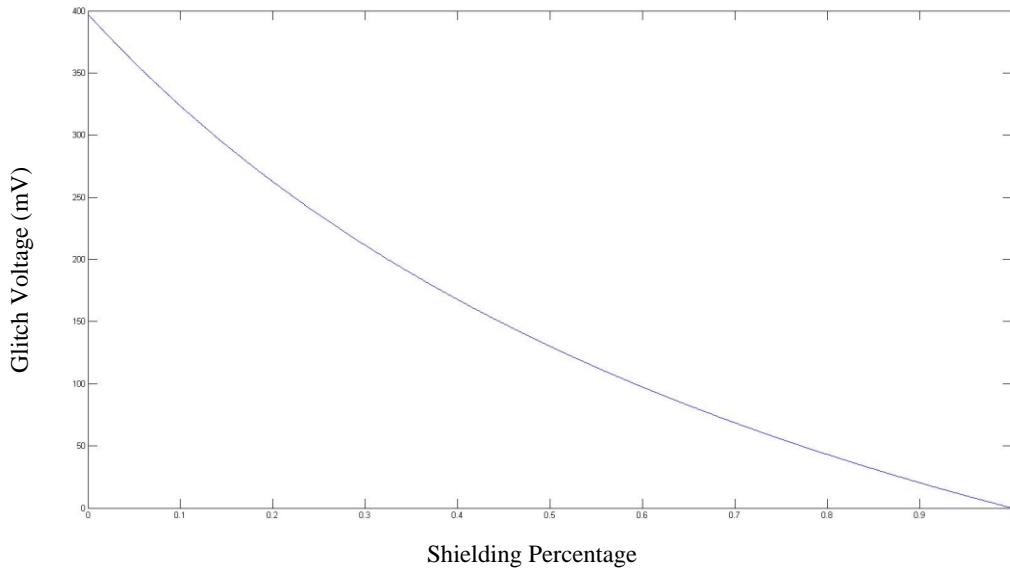

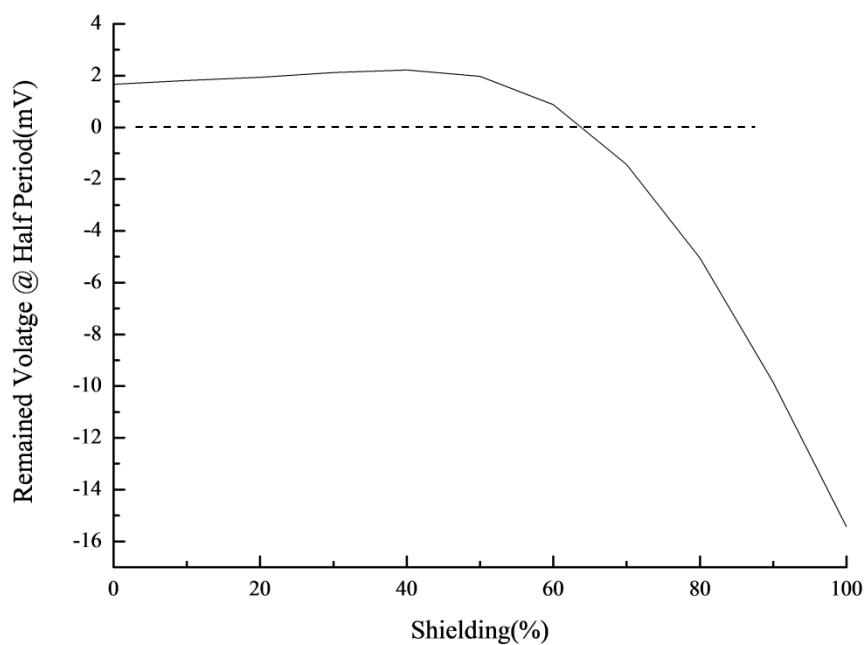

| 圖 4.13 突波電壓與屏蔽比例關係圖 .....           | 44 |

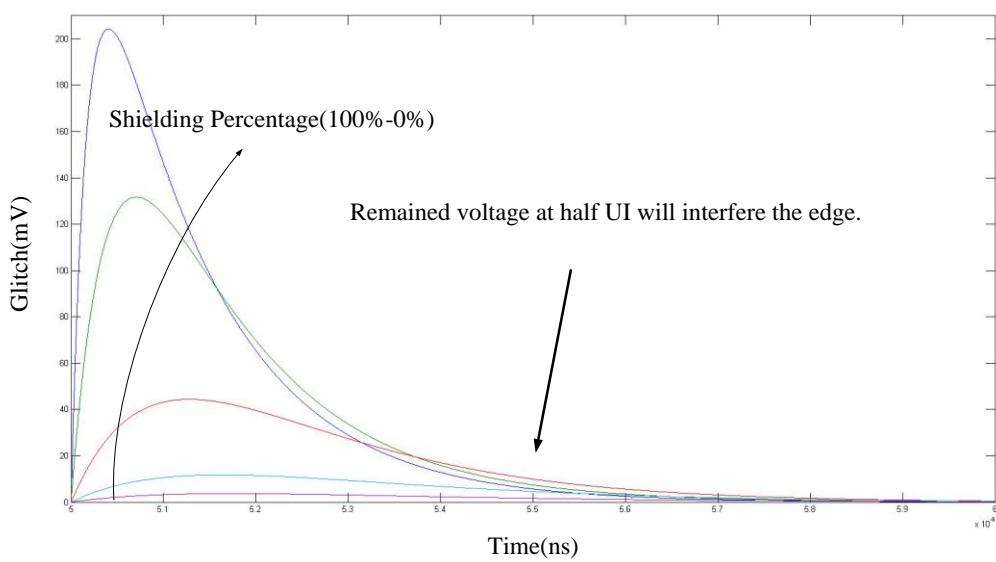

| 圖 4.14 不同屏蔽比例之突波電壓與半單位間隔後殘存電壓.....  | 44 |

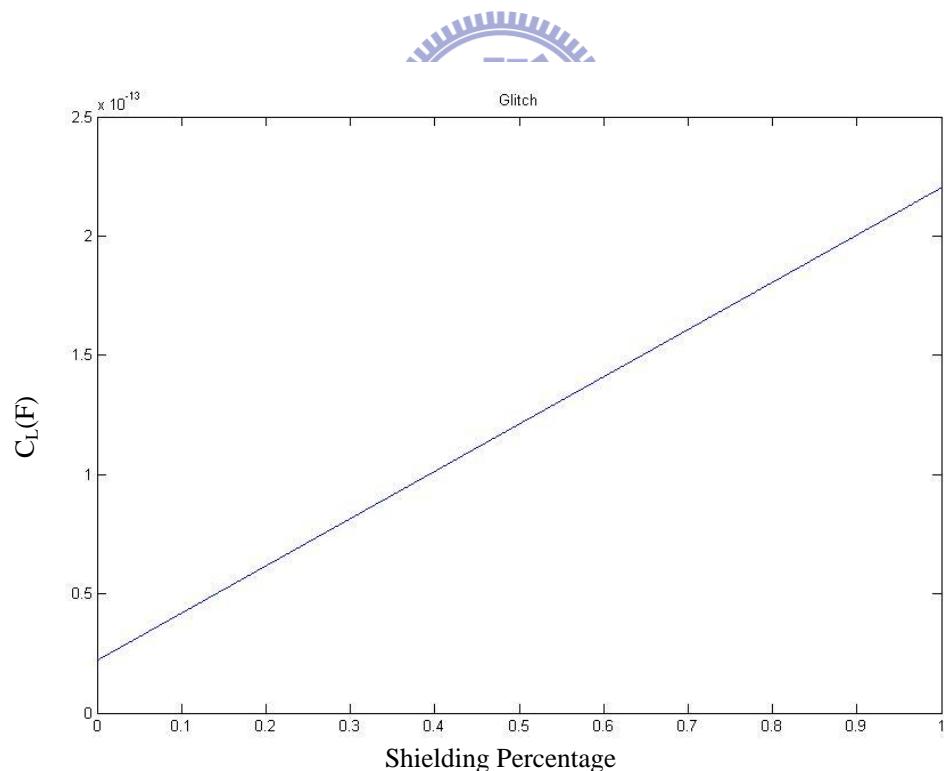

| 圖 4.15 負載電容與屏蔽比例關係圖 .....           | 45 |

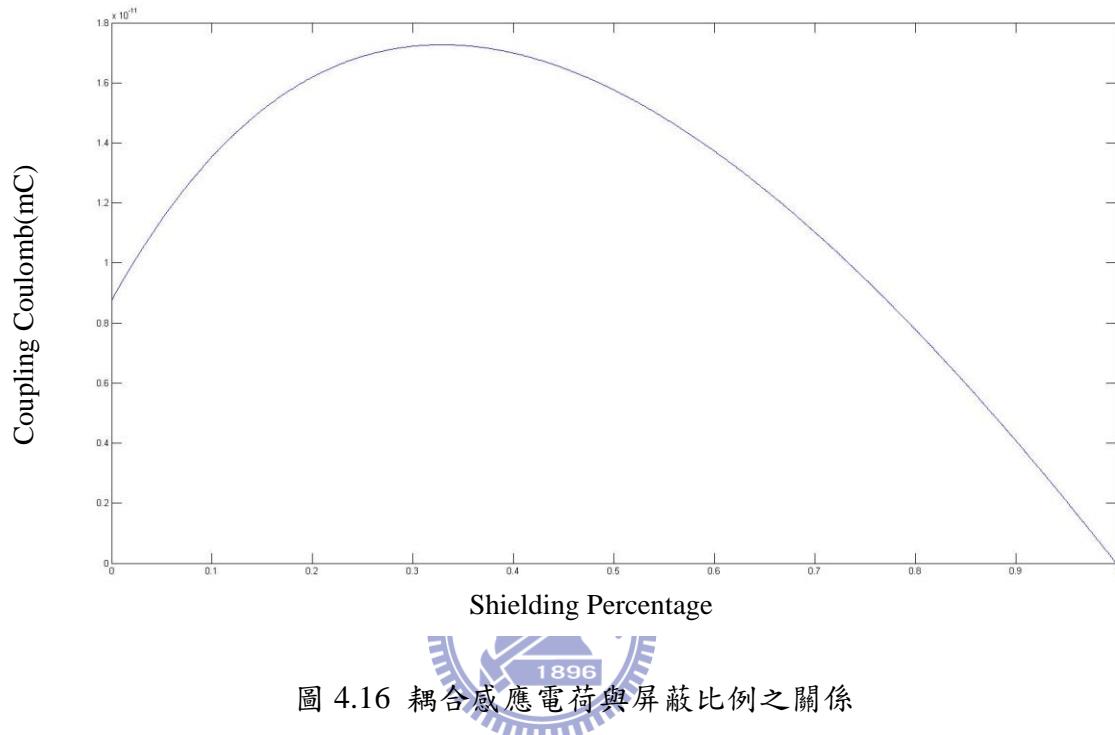

| 圖 4.16 耦合感應電荷與屏蔽比例之關係.....          | 46 |

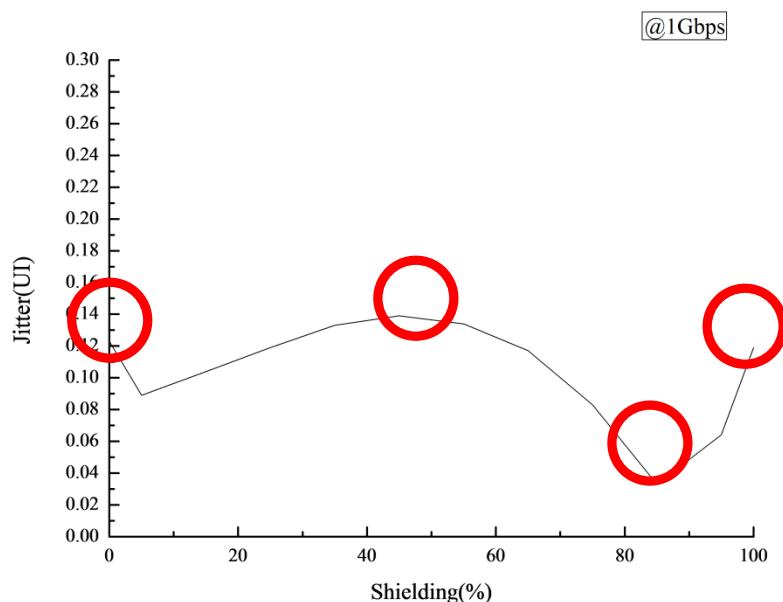

| 圖 4.17 信號抖動與屏蔽關係模擬圖 .....           | 47 |

| 圖 4.18 ISI 抖動之模擬結果@1Gbps.....       | 50 |

| 圖 4.19 本文所使用之拔靴帶式電路.....            | 51 |

---

|                                                               |    |

|---------------------------------------------------------------|----|

| 圖 4.20 節點 N3 之模擬波形.....                                       | 52 |

| 圖 4.21 信號抖動隨屏蔽比例變動@1Gbps .....                                | 53 |

| 圖 4.22 單側干擾源示意圖.....                                          | 53 |

| 圖 4.23 待測線之眼圖下降邊緣@85% 屏蔽.....                                 | 54 |

| 圖 4.24 待測線之眼圖下降邊緣@100% 屏蔽.....                                | 54 |

| 圖 4.25 耦合效應在完全屏蔽下之穿透效果.....                                   | 56 |

| 圖 4.26 正向耦合突波與屏蔽比例之關係.....                                    | 57 |

| 圖 4.27 半週期後殘存電壓與屏蔽比例之關係(1T model) .....                       | 58 |

| 圖 4.28 半週期後殘存電壓與屏蔽比例之關係(10T model) .....                      | 58 |

| 圖 5.1 0% 、50% 、85% 、100% 四個屏蔽比例作為測試電路 .....                   | 60 |

| 圖 5.2 測式電路之區塊圖.....                                           | 60 |

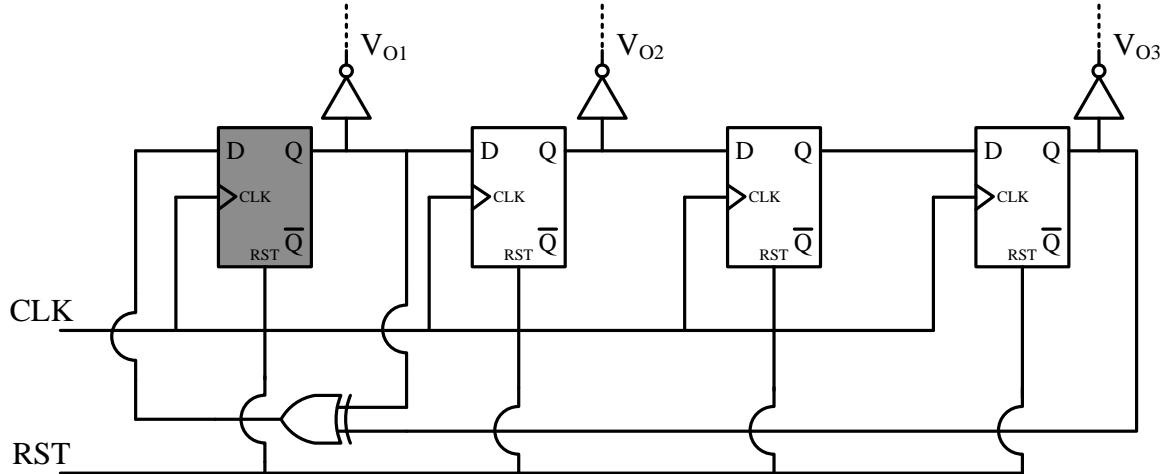

| 圖 5.3 四位元偽隨機信號產生器 .....                                       | 61 |

| 圖 5.4 轉態邊緣交錯機制處理後之波形圖.....                                    | 62 |

| 圖 5.5 匯流排中由中繼器間隔之 1mm 示意圖.....                                | 63 |

| 圖 5.6 晶片佈局圖 .....                                             | 64 |

| 圖 5.7 匯流排區塊佈局 .....                                           | 65 |

| 圖 5.8 匯流排電路之眼圖(0.5V 、25°C 、TT) .....                          | 66 |

| 圖 5.9 匯流排電路之眼圖(0.5V 、25°C 、FF).....                           | 69 |

| 圖 5.10 匯流排電路之眼圖(0.5V 、25°C 、SS).....                          | 70 |

| 圖 5.11 量測儀器設置圖 .....                                          | 72 |

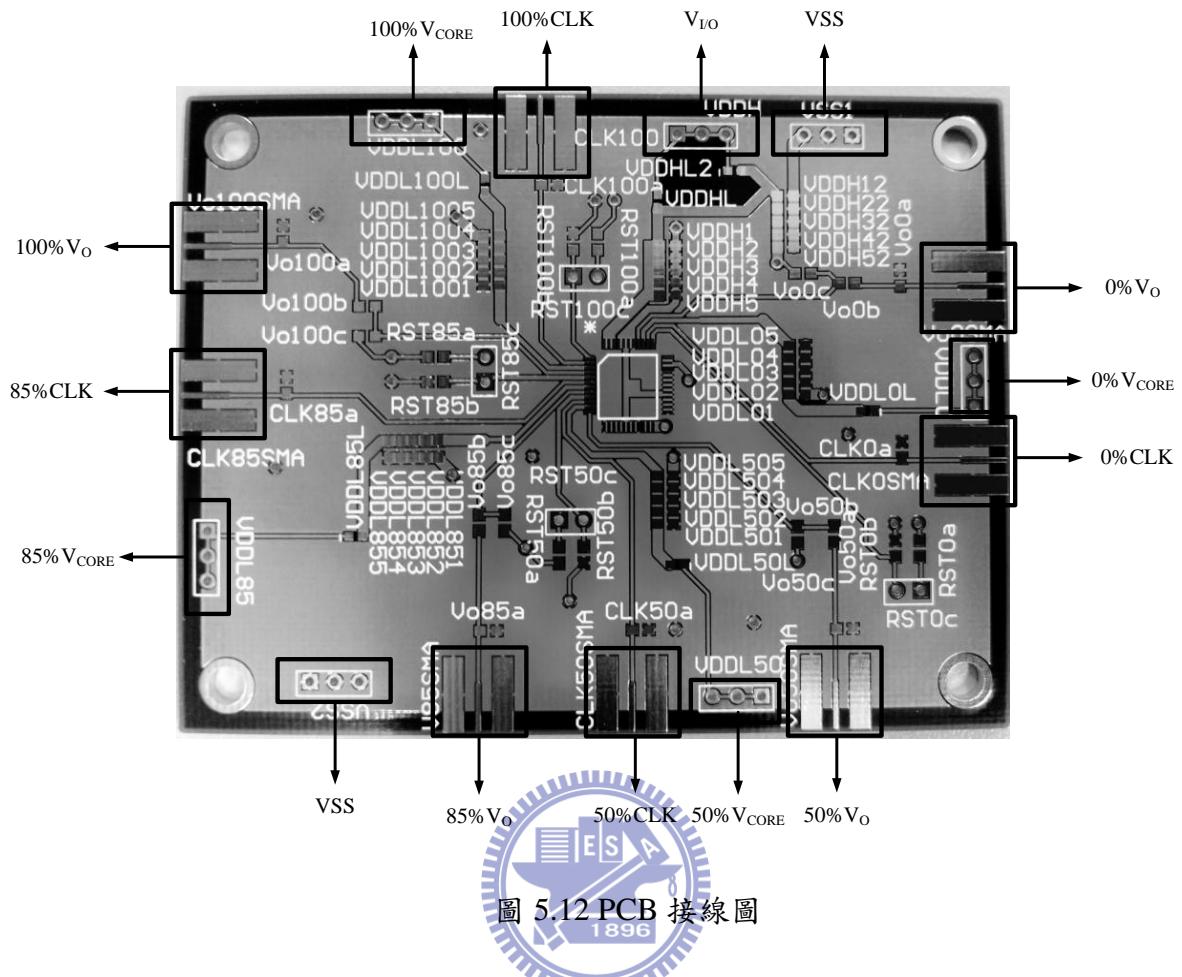

| 圖 5.12 PCB 接線圖 .....                                          | 73 |

| 圖 5.13 晶片打線圖 .....                                            | 73 |

| 圖 5.14 $V_{CORE}=1V$ 、 $V_{I/O}=0.56V$ 不同屏蔽下之眼圖 .....         | 74 |

| 圖 5.15 $V_{CORE}=1V$ 、 $V_{I/O}=1V$ 不同屏蔽下 0.8G-1.4G 之眼圖 ..... | 75 |

| 圖 5.16 $V_{CORE}=1V$ 、 $V_{I/O}=1V$ 不同屏蔽下 1.6G-2.2G 之眼圖 ..... | 76 |

| 圖 5.17 臨界資料速率下不同屏蔽比例之信號抖動.....                                | 77 |

---

# 表目錄

|                                                                |    |

|----------------------------------------------------------------|----|

| 表 1.1 各製程之單位耦合電容值.....                                         | 2  |

| 表 2.1 拔靴帶式電路在各操作電壓下之漏電與升壓效率.....                               | 10 |

| 表 3.1 MSG90 電阻、電容參照表.....                                      | 21 |

| 表 3.2 步階響應在結合式模型與分散式模型之效果.....                                 | 23 |

| 表 3.3 T1-T10 模型之差異量 .....                                      | 26 |

| 表 5.1 PAD 分配表 .....                                            | 65 |

| 表 5.2 TT corner 下 Post-simulation 與 Pre-simulation 比較表 .....   | 68 |

| 表 5.3 FF corner 下 Post-simulation 與 Pre-simulation 比較表 .....   | 70 |

| 表 5.4 SS corner 下 Post-simulation 與 Pre-simulation 比較表 .....   | 71 |

| 表 5.5 $V_{CORE}=1V$ 、 $V_{I/O}=0.56V$ 不同屏蔽下之信號抖動 .....         | 74 |

| 表 5.6 $V_{CORE}=1V$ 、 $V_{I/O}=1V$ 不同屏蔽下 0.8G-1.4G 之信號抖動 ..... | 75 |

| 表 5.7 $V_{CORE}=1V$ 、 $V_{I/O}=1V$ 不同屏蔽下 1.6G-2.2G 之信號抖動 ..... | 76 |

| 表 5.8 規格表.....                                                 | 78 |

| 表 5.9 比較表.....                                                 | 79 |

# 第一章

## 緒論

電子產品已成為現今生活中不可或缺的一部分，各式各樣的可攜式裝置蓬勃發展，因此如何做到輕薄短小與省電即是當前重要的課題。為了要縮小電子產品的體積，我們可以憑藉著現今積體電路的技術將電路板整合成一顆晶片，即是所謂的 SoC (System on Chip)，而要如何做到低功耗也是我們研究的目標。

隨著技術的演進，越來越多的模組整合進入 SoC，使得模組間之匯流排越來越長，若要顧及信號之完整度而使用常見的直流電源線作為保護會大幅增加負載，或是將傳輸線之距拉開來避免彼此的干擾則會增加大量的面積。而在模組內邏輯閘的延遲因電晶體尺寸的縮小而縮短的情況下，模組與模組之間的傳輸線延遲也日顯重要。而在現今倡導綠能還有可攜式裝置追求更長的使用時間之趨勢下，低功率的電路技術一直是研究的重點方向。因此要如何在功耗、面積與速度之間做取捨又要顧及信號之完整就是我們的研究目標。

## 1.1 研究動機

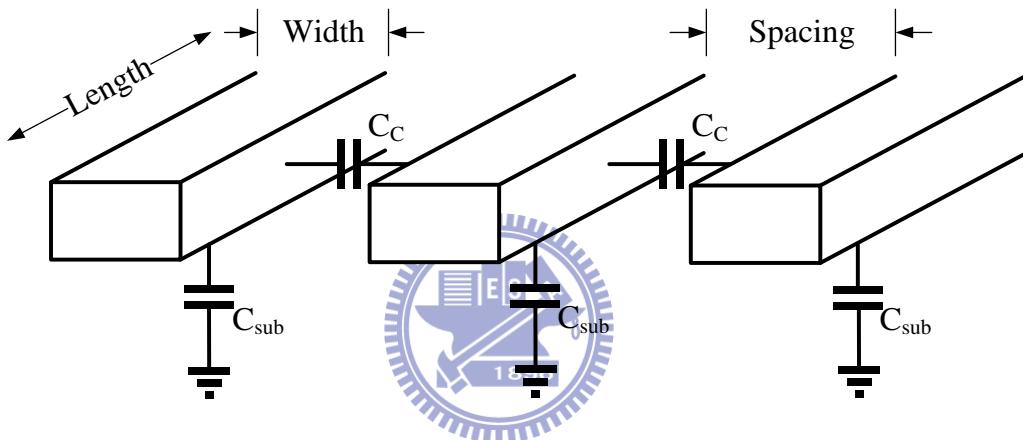

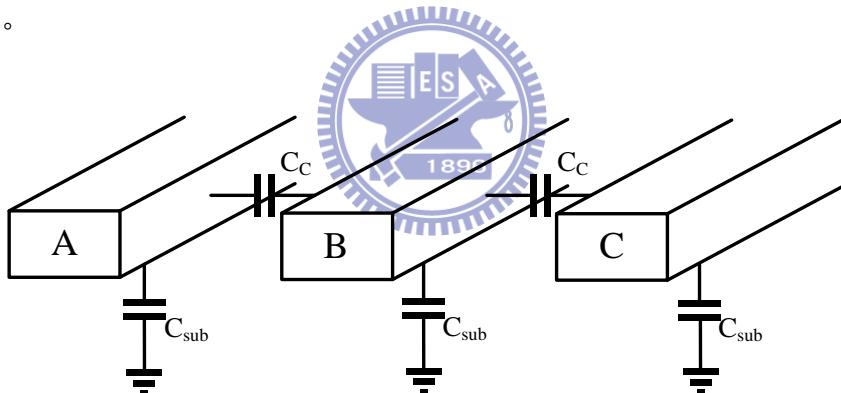

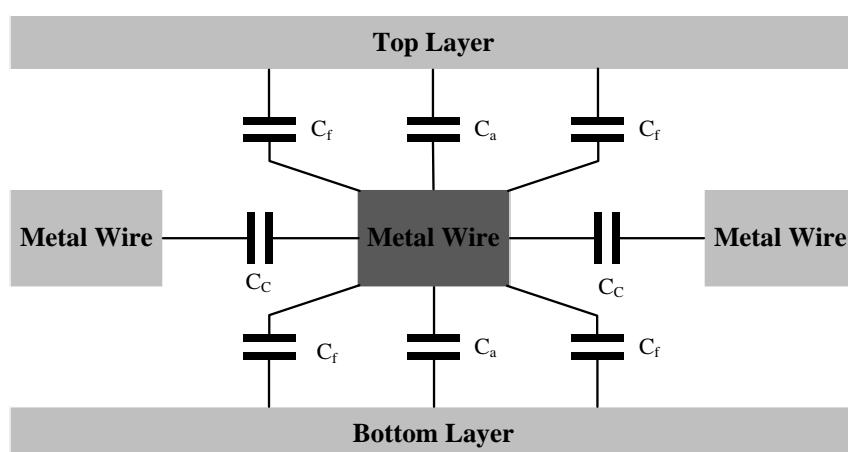

隨著製程的進步，晶片內匯流排逐漸成為晶片設計上的瓶頸。原因在於製程的進步縮小了電晶體的尺寸卻沒有縮短匯流排的長度，更而甚之，更多的模組進入了 SoC 使得匯流排的長度不減反增。此外，匯流排中彼此並排的傳輸線產生大量的耦合電容 (Coupling Capacitance)，如圖 1.1 所示，製程的進步縮短了導線間彼此的間距，使得這些耦合電容隨著製程的縮小而變大，如表 1.1 所示，而增加的耦合電容意味著更嚴重的串音現象(Crosstalk)與更多的負載電容。

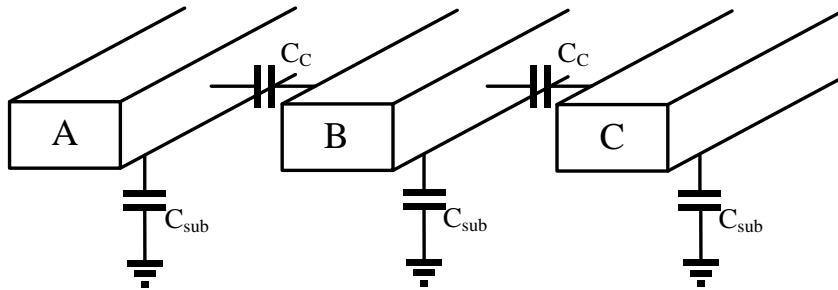

圖 1.1 匯流排之耦合電容與基底電容示意圖

| Tech. (nm)        | 90_SP       | 65_SP      | 55_SP       |

|-------------------|-------------|------------|-------------|

| $W_{min} (\mu m)$ | <b>0.14</b> | <b>0.1</b> | <b>0.09</b> |

| $S_{min} (\mu m)$ | <b>0.14</b> | <b>0.1</b> | <b>0.09</b> |

| $c_c (aF/\mu m)$  | <b>88</b>   | <b>88</b>  | <b>96</b>   |

表 1.1 各製程之單位耦合電容值

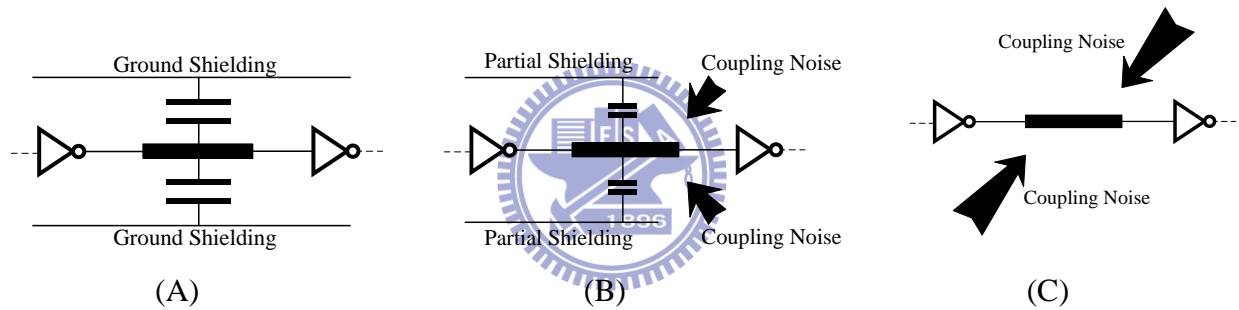

若要降低串音現象造的影響常見的做法有兩種;一為將直流電源線安插在相鄰的傳輸線間作為屏蔽(Shielding)[14]，此做法雖能大幅抑制串音現象卻要承受大量的耦合電容負

載，使得傳輸每位元所需焦耳 (J/bit)大幅上升。第二種是將傳輸線間之間距拉開[15]，這種做法雖然能在降低串音現象的同時也降低耦合電容造成的負載，但是此做法要付出大量的面積做為代價，因此在實務中通常難以使用。

如圖 1.2 所示，完全屏蔽(Fully Shielding)能完全免疫串音造成的雜訊，代價卻是大量的電容負載造成功耗上升，而沒有屏蔽(None Shielding)雖然負載小但有大量的雜訊進入導致訊號無法傳輸；因此我們的想法是在完全的屏蔽與沒有屏蔽之間取權衡，找出最佳的屏蔽比例(Partial Shielding)讓一部分我們可以接受的雜訊進入以換取負載的降低，使得速度得以提升與達到低功耗的目標。

圖 1.2 (A)完全屏蔽 (B)部分屏蔽 (C)沒有屏蔽

## 1.2 論文結構

本論文分為六個章節，第一章為緒論，說明匯流排之發展狀況、研究動機與論文結構。第二章為背景回顧，說明本論文所使用之本實驗室關於低壓匯流排之技術與介紹先前文獻所設計之匯流排系統。第三章為晶片匯流排之模型，介紹我們所使用的線間電阻與電容模型和其計算方式，另外也將匯流排內耦合效應之現象模型化，以此來做最佳化之計算。第四章為晶片內匯流排之設計與最佳化之結果。第五章為量測考量與結果。第六章則為結論與未來方向。

## 第二章

### 背景回顧

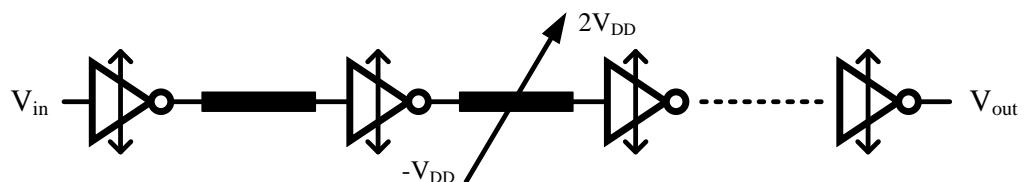

#### 2.1 低功率中繼器

為了達到低功率消耗，由基本的功率消耗公式  $P = \alpha f C V^2$  可知，降低系統的操作電壓為最直接有效的方式。但是當傳輸線系統的操作在低電壓的環境時，電路的操作速率將嚴重降低，將造成電路可運作的速度不如預期之外，當系統的操作電壓小於電晶體的門檻電壓時，電路更遭受嚴重的製程變異影響。

因此在低操作電壓的環境之下可考慮使用拔靴帶式反相器(bootstrapped inverter)作為中繼器，如圖 2.1 所示，將中繼器的輸出擺幅放大為  $2V_{DD} \sim -V_{DD}$ ，如此一來即可增加中繼器的驅動能力，增加傳輸線系統的操作速度，中繼器之擺放可見[1][2][3][4][5]。

圖 2.1 置入了拔靴帶式中繼器的晶片內部傳輸線系統

但此作法卻產生另一項問題：若使整條傳輸線負載的訊號擺幅放大為三倍，將造成功率消耗增加為九倍，此時電路的功率消耗與正常電壓操作時相同，得不到任何的好處。

因此我們所使用的作法如圖 2.2 所示，在傳統中繼器之前加入拔靴帶式電路，以增加中繼器的驅動能力。參考圖 2.3，如此作法雖然會增加拔靴帶式電路與中繼器之間負載( $C_1$ )的功率消耗為九倍，卻沒有增加主要傳輸線負載( $C_2$ )的功率消耗，因此只需多付出相對少量的功率消耗，即可增加傳輸線系統的操作速度，以達高速低功率消耗的目的。

圖 2.2 本論文的拔靴帶式晶片內部傳輸線系統

圖 2.3 本論文的拔靴帶式中繼器負載

## 2.2 拔靴帶式反向器電路

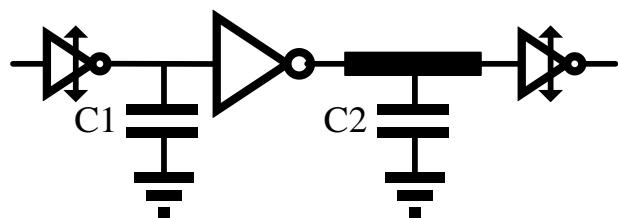

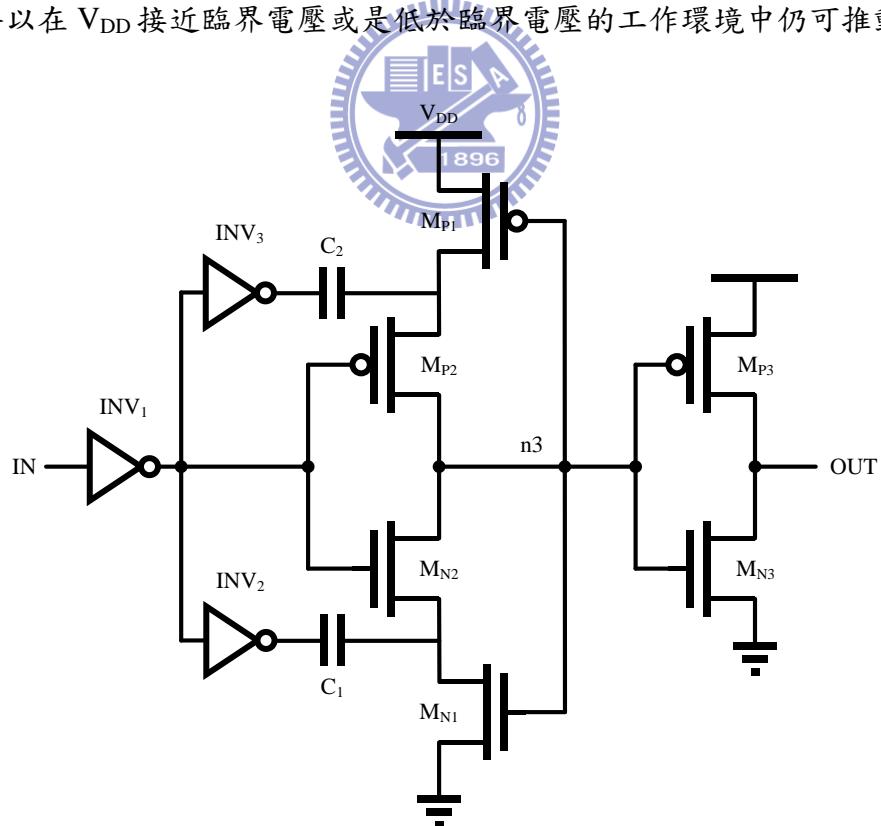

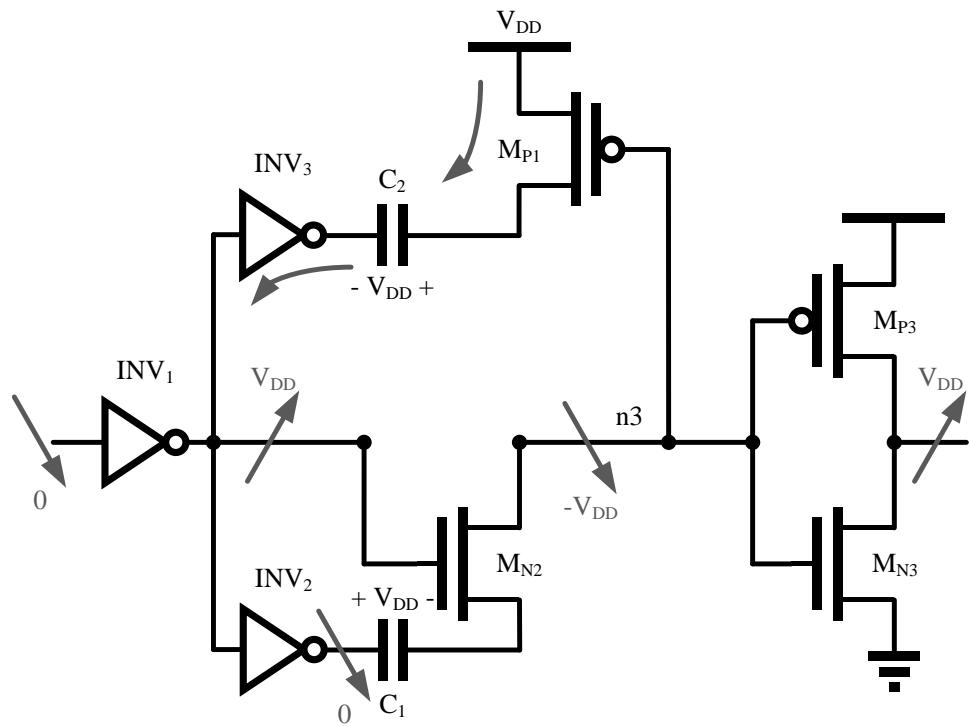

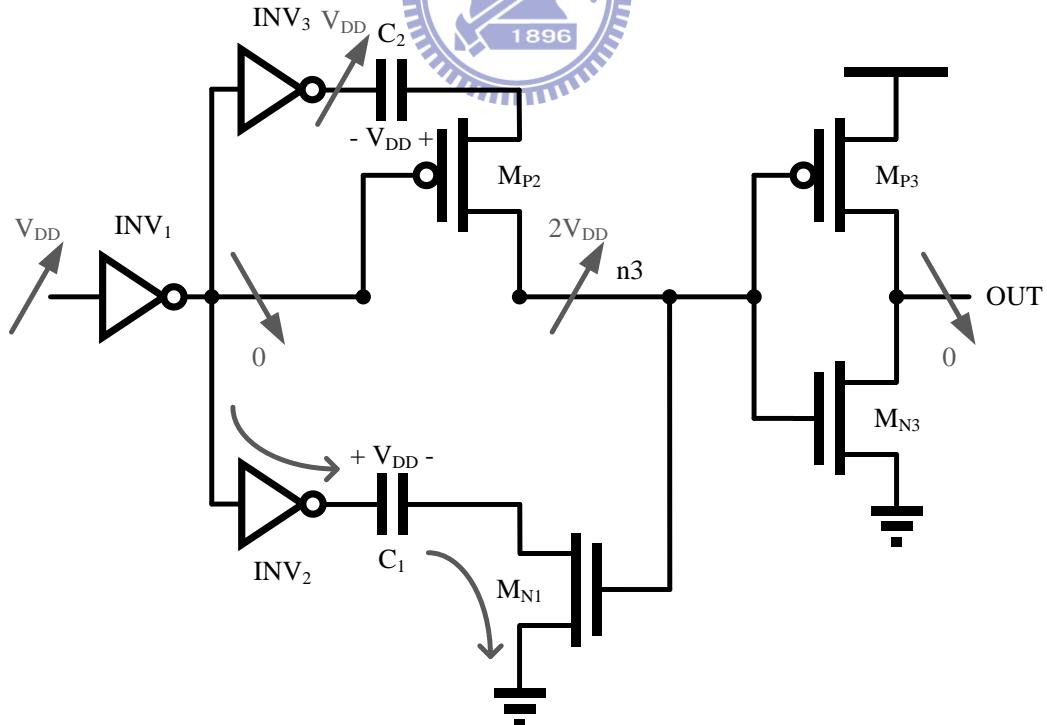

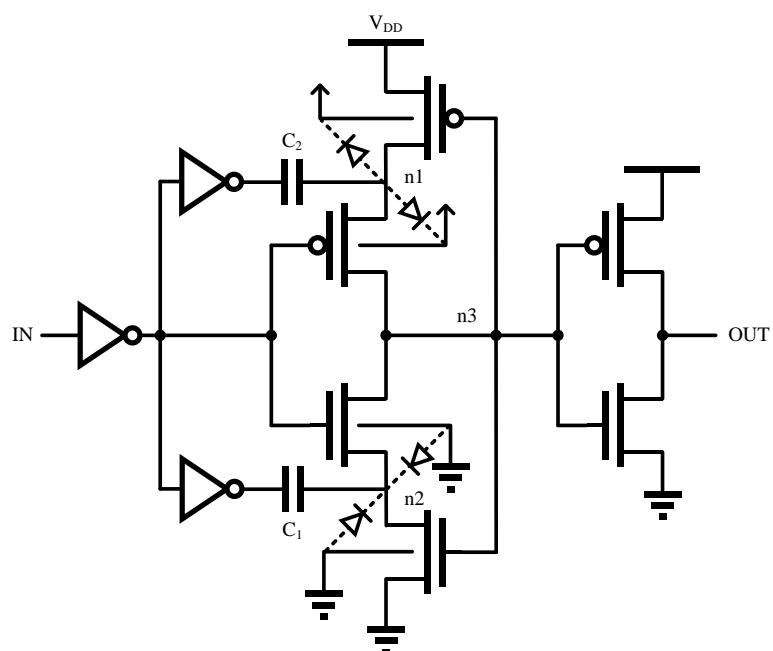

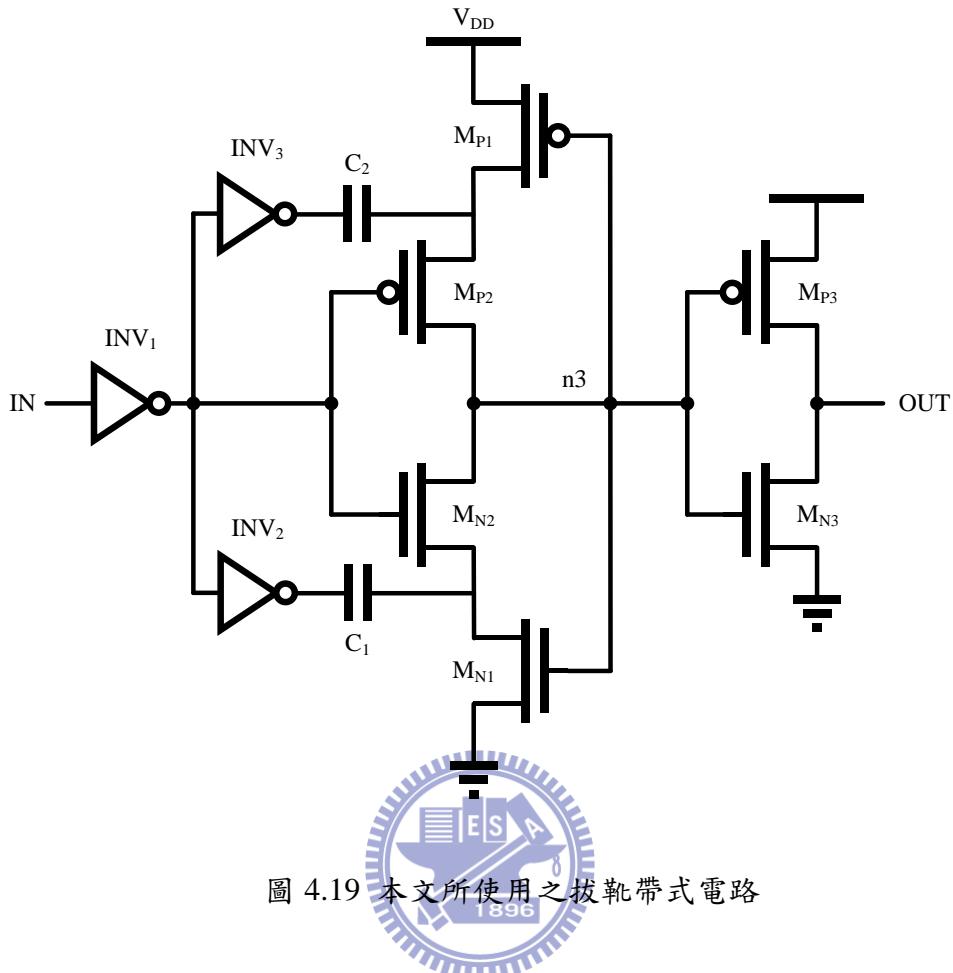

拔靴帶式反相器電路[6]如圖 2.4，此電路理想上可提供上下擺幅為正兩倍至負一倍之操作電壓驅動後方 CMOS 反相器電路，以提供較佳的驅動能力在低壓環境中驅動連接線的大負載。電路可分為兩個部份，電晶體  $M_{P1}$ 、 $INV_3$  與  $C_2$  負責將電壓提升到兩倍  $V_{DD}$ ，電晶體  $M_{N1}$ 、 $INV_2$  與  $C_1$  則讓電壓降到  $-V_{DD}$ 。其中  $M_{P1}$  負責讓  $C_2$  充電維持  $V_{DD}$  的壓差，而  $INV_3$  雖然看似一般反相器，但其作用在於充電時內部之 NMOS 導通提供 GND 電壓，而要升壓時則是 PMOS 導通讓  $V_{DD}$  再加上充飽電的  $C_2$  之  $V_{DD}$  壓差讓電壓升至兩倍  $V_{DD}$ 。 $M_{N1}$ 、 $INV_2$  與  $C_1$  之功能如同  $M_{P1}$ 、 $INV_3$  與  $C_2$  只是目的是讓電壓降到  $-V_{DD}$ 。 $M_{P2}$  與  $M_{N3}$  即作為開關切換兩倍  $V_{DD}$  與  $-V_{DD}$ ， $M_{P3}$  與  $M_{N3}$  則為一般的反相器電路作為驅動後級負載使用，因為前級拔靴帶式電路提供了兩倍  $V_{DD}$  至  $-V_{DD}$  的驅動電壓，使得此反相器得以在  $V_{DD}$  接近臨界電壓或是低於臨界電壓的工作環境中仍可推動大負載。

圖 2.4 拔靴帶式反相器

電路的升壓動作如圖 2.5 所示，當輸入訊號為  $V_{DD}$  轉 0 時，反相器  $INV_1$  的輸出為 0 轉  $V_{DD}$ ， $INV_2$  中之 NMOS 導通接地，經由  $INV_2$  中之 NMOS 之地再加上電容  $C_1$  上預先儲存的  $+V_{DD}$ -電壓差使電晶體  $M_{N2}$  的源極降壓至  $-V_{DD}$ ，反相器  $INV_1$  之  $V_{DD}$  輸出讓電晶體  $M_{N2}$  導通將  $-V_{DD}$  的電壓傳遞至後方，驅動 CMOS 反相器。同時電晶體  $M_{P1}$  的閘級電壓為  $-V_{DD}$ ，電晶體  $M_{P1}$  導通，此時  $INV_3$  中之 NMOS 導通提供地電壓，電容  $C_2$  經由  $M_{P1}$  源極之  $V_{DD}$  到  $INV_3$  中之 NMOS 的源極接地儲存電壓差  $-V_{DD+}$ 。在此時序中，電容  $C_1$  執行升壓動作(boost)，電容  $C_2$  執行重置動作(reset)。

當輸入訊號由 0 轉  $V_{DD}$  時，電路的動作如圖 2.6 所示。反相器  $INV_1$  的輸出由  $V_{DD}$  轉 0， $INV_3$  中之 PMOS 導通，使得  $M_{P2}$  之源極電壓經由  $INV_3$  中 PMOS 源極之  $V_{DD}$  加上電容  $C_2$  上預先儲存的  $-V_{DD+}$  電壓差推升至 2 倍  $V_{DD}$ ，此時  $INV_1$  之輸出為 0 導通  $M_{P2}$  讓  $2V_{DD}$  的電壓傳遞至後方，驅動 CMOS 反相器。同時電晶體  $M_{N1}$  閘級電壓為  $2V_{DD}$ ，電晶體  $M_{N1}$  導通， $INV_2$  中之 PMOS 導通連接  $V_{DD}$ ，電容  $C_1$  經由  $INV_2$  中 PMOS 之源極連接  $V_{DD}$  到  $M_{N1}$  之源極接地，儲存  $+V_{DD-}$  之電壓差。在此時序中，電容  $C_1$  執行重置動作(reset)，電容  $C_2$  執行升壓動作(boost)。

總結來說此電路就上述兩個模式下切換，在一邊將電壓往 2 倍  $V_{DD}$  或是  $-V_{DD}$  提升時，另一側之動作為讓其中之電容再次完全充電，以準備下次轉態時之升降壓所需。其中設計的考量就在於電容之充電完整與否，這關係到  $INV_3$  中之 NMOS 與  $M_{P1}$ ，還有  $INV_2$  中之 PMOS 與  $M_{N1}$  之間之比例關係，此外還有儲能原件會產生漏電之影響，將於後續章節詳述。

圖 2.5 拔靴帶式反相器操作原理(輸入由  $V_{DD}$  轉 0)圖 2.6 拔靴帶式反相器操作原理(輸入由 0 轉  $V_{DD}$ )

然而拔靴帶式電路有其使用上之限制，如圖 2.7 所示，Node1 上側電晶體之源極與下側電晶體之汲極與其基底端產生 PN 介面，在升壓過後 Node1 之電位將提升至  $2V_{DD}$ ，使得 PN 介面兩端有  $V_{DD}$  的順向壓差，如果操作電壓過大則此 PN 介面將導通而造成漏電，在 Node2 有相同的現象。實際模擬結果如圖 2.8 所示，在操作電壓為 0.5V 時理想上可將電壓提升至兩倍至 1V，然而考量內部節點上有寄生電容造成分壓，因此實際上僅能提升 52.2%，且有微量的漏電情形。若操作電壓往上提升為 1V，可以看到提升效率略降為 51.1% 而漏電情形加劇，此情形可以合理推測為 PN 介面上之跨壓已使其微導通。若我們再把操作電壓提升至 1.5V，此時升壓效率降至 48.5%，且 PN 介面順相導通造成嚴重的漏電情形。總結來說，拔靴帶式電路之升壓點受制於內部 PN 介面僅能提升至 PN 介面之導通電壓，超過此電壓將使得介面導通而漏電，使得升壓僅能維持在基底電位加上介面之導通電壓，在此製成下若加入考量寄生電容造成的分壓影響，最大的操作電壓約略在 1V，超過此電壓則會有嚴重的漏電現象讓升壓效率下降。

圖 2.7 拔靴帶式電路中 PN 介面示意圖

圖 2.8 拔靴帶式電路在不同操作電壓下之升降壓效果模擬圖

|                  | 0.5V     | 1V       | 1.5V      |

|------------------|----------|----------|-----------|

| Leakage rate     | 0.2mV/ns | 1.4mV/ns | 10.4mV/ns |

| Boost efficiency | 1.522    | 1.511    | 1.485     |

表 2.1 拔靴帶式電路在各操作電壓下之漏電與升壓效率

## 2.3 拔靴帶式反向器電路模擬結果

圖 2.9 拔靴帶式反相器各節點電壓波形圖

圖 2.7 為電路在操作時各節點的電壓波形。受到升降壓電容會與節點寄生電容分壓的影響，升降壓效果無法完全地達到  $2V_{DD}$  至  $-V_{DD}$ 。我們所使用的拔靴帶式反相器與傳統 CMOS 反相器比較如圖 2.8，可看出其在輸出驅動能力上好上許多。電路前端的反相器( $INV_1$ 、 $INV_2$  與  $INV_3$ )將升降壓電容( $C_1$  與  $C_2$ )與輸入隔開，如此一來即使輸入訊號的轉態時間較長，但經過電路前端的反相器後，訊號重整為斜率較陡峭的數位訊號，避免後端電路因訊號轉態緩慢，而受短路電流影響，造成升降壓的效果不如預期。因此依其功能，在此可稱前端的反相器有對波形整型(shaping)的效果。

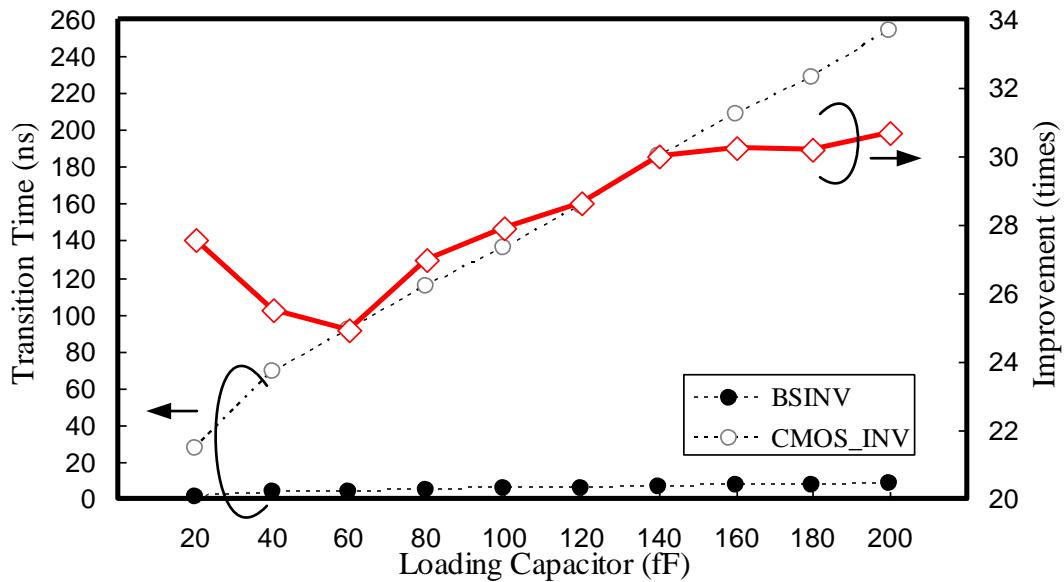

圖 2.10 拔靴帶式反相器與傳統 CMOS 反相器比較

總結拔靴帶式反相器的優點：(1) 在低壓時的反相器驅動能力改善效果良好。(2) 升壓電容的大小與負載無直接關係，適合推動大負載的應用。(3) 升壓後，電路受製程變異的影響較小。(4) 電路簡單而容易設計。

## 2.4 匯流排等效電容模型

晶片內匯流排間之傳輸線彼此緊密相鄰，使得耦合電容遠大於導線與基底間的基底電容，為線電容的主宰項，然而耦合電容之等效容值會隨著相鄰信號之式樣不同而有大幅度的差異。如圖 2.9 所示，這是估算平行線間等效電容的常見做法[7]，這模型以三條平行線為架構，中間為受測端兩旁則為干擾端，當兩邊受測端與干擾端進行同向轉態則耦合電容為零，只有對基底的電容；當干擾端一邊靜止另一邊與受測端進行同向轉態，我們看到的等效電容為基底電容加上一個耦合電容；當干擾端兩邊靜止或是一端與受測端進行同向轉態另一端則為反向轉態，此時等效電容為一個基底電容加上兩個耦合電容；當干擾端一邊為靜止一邊與受測端進行反向轉態，則等效電容為一個基底電容加上三個耦合電容；而當干擾端兩邊皆與受測端進行反向轉態，等效電容為一個基底電容加上四個耦合電容。

| Switch Pattern<br>(A,B,C)      | Effective Capacitance of Line B |

|--------------------------------|---------------------------------|

| (↑↑↑),(↓↓↓)                    | $C_{sub}$                       |

| (-↑↑),(↑↑-),(↓↓↑),(↓↓-)        | $C_{sub}+C_C$                   |

| (-↑-),(↓-),(↑↑),(↓↑),(↓↑),(↑↓) | $C_{sub}+2C_C$                  |

| (-↑↓),(↓↑),(↑↓-),(↓↑-)         | $C_{sub}+3C_C$                  |

| (↑↓↑),(↓↑↓)                    | $C_{sub}+4C_C$                  |

圖 2.11 平行線等效電容模型[7]

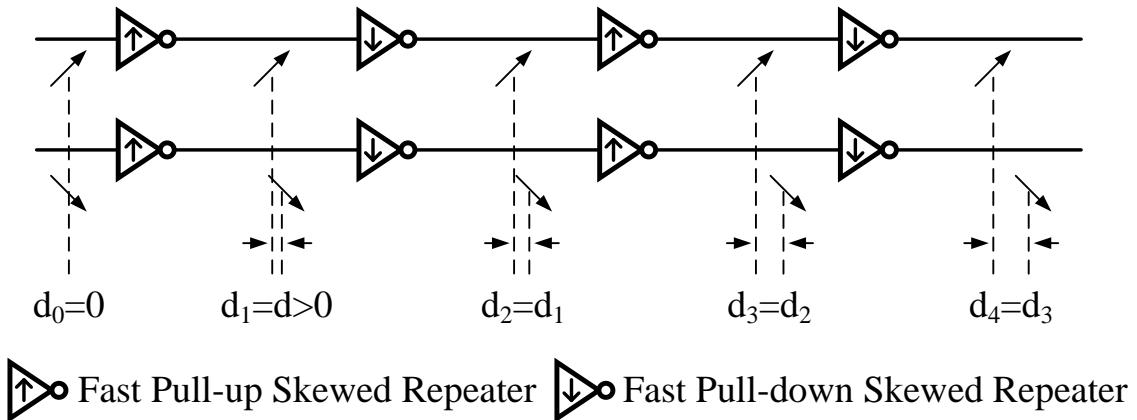

另一種常見的估算法為米勒耦合係數(Miller Coupling Factor)，討論兩相鄰平行線間等效耦合電容之倍數。當相鄰兩線為同向轉態則等效耦合電容為 0，因此係數為 0；當轉態時鄰端靜止則看到一個等效耦合電容，係數為 1；若違相鄰兩線為反向轉態則看到兩倍等效耦合電容，係數為 2。耦合電容值隨著信號的不同而會有大幅度的變動，從功耗的觀點上來看，等效電容的容值大小正比於功率的消耗，因此隨著不同的信號進入功耗可能會大幅上升。此外不同的等效電容值會影響充放電的時間使得上升下降的時間不同，也就造成延遲不確定性(Delay Uncertainty)，最明顯的影響就是會產生信號抖動(Jitter)。

## 2.5 中繼器交錯式排列

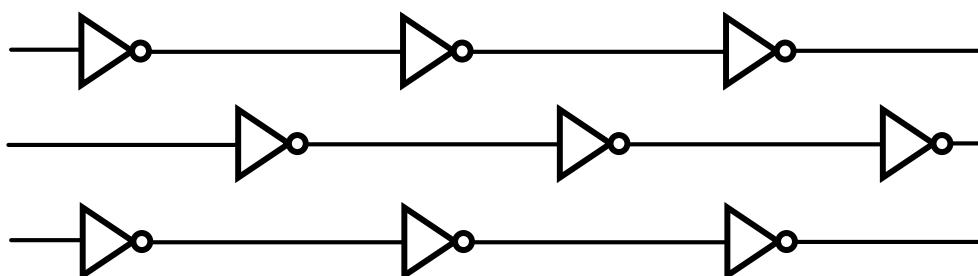

為了要解決串音現象與等效耦合電容變異造成的問題，將中繼器交錯排列(Stagger)是一種常見的方式[8]。如圖 2.10 所示，將中繼器以相互交錯的方式排列，當前一級的鄰線訊號轉態耦合進入中線，下一級鄰線則會反向轉態耦合抵消前一級對中線的影響，理想上可以將彼此干擾的串音現象相消。此外藉由這種交錯式的擺放，還能平衡隨著訊號改變而變異的耦合電容值，當相鄰線為反向轉態而看到 MCF 為 2 時，下一級則會變為同向轉態使得 MCF 為 0，而當相鄰線一邊轉態一邊靜止時，下一級仍會維持一邊靜止一邊轉態使得 MCF 為 1，將所有的轉態狀況平均下來可發現 MCF 為持在 1。

圖 2.12 中繼器以交錯的方式擺放[8]

然而要抵消串音現象產生的突波(Glitch)先決條件就是各級的邏輯閘延遲要趨近零，若邏輯閘延遲過長則前級產生的突波並無法與後級產生的突波相消，而是變成一前一後兩個反向的突波。而平衡等效的耦合電容值讓平均 MCF 維持在 1，避開了可能 MCF 為 2 的最差狀況，卻也讓 MCF 為 0 的最佳狀況消失，因此功耗能否降低要視進入的訊號而定。平均 MCF 維持在 1 理論上可以處理延遲不確定性的問題，然而若在前級已經產生的抖動並無法在後級抵消掉。此外中繼器擺放的位子也受到嚴格的限制[9]，若偏離理想的擺放位置則效果會大打折扣，然而在佈局上很難以匯流排走線為首要考量，因此實務上有使用的難度。

## 2.6 混和極性中繼器

為了要解決交錯式排列對於擺放位置過於敏感的限制，另一種方式是使用兩種不同極性的中繼器，使得相鄰線間前級與後級之轉態互補，藉以達到抵消或是平衡耦合造成的影响[12]。如圖 2.11 所示，奇數線使用一般的反相器為中繼器，偶數線則置入非反相的中繼器，假設第一段出現相鄰線為反向轉態使得  $MCF=2$  的最差情形，則第二段則會變成同向轉態使得  $MCF=0$ ，整段的平均 MCF 仍維持在 1，其它形式的訊號輸入也有一樣的互補效果，使得平均 MCF 接能穩定維持在 1。

圖 2.13 置入反相和非反相中繼器使得相鄰線互補轉態[12]

此種方式相較中繼器交錯式排列對於擺放位置的要求並不敏感，且平衡等效耦合電容有一樣的效果，然而依然面臨相同的問題，雖然平衡了等效耦合電容卻不能消除耦合造成的信號抖動。

## 2.7 邊緣調整

另一種降低等效耦合電容的技巧是調整轉態邊緣(Edge)[16][18]，如圖 2.14，錯開相鄰線間的轉態時機，如此一來 MCF 可以恆定在 1，避免延遲不確定性造成的信號抖動。

圖 2.14 加入延遲元件錯開相鄰線之轉態邊緣[16]

若使用上升下降時間不對稱的中繼器，如圖 2.15 所示，可以將 MCF 降低在 0 至 1 之間。兩邊訊號為反向轉態時因為上升下降時間的不對稱，讓兩邊轉態邊緣每經過一個中繼器就隔的越開始得 MCF 為 1；而當兩邊訊號為同向轉態時則兩邊信號之邊緣並不會錯開，因此 MCF 維持在 0。此種作法在功耗上因為 MCF 從 0 到 2 的變動有效壓制到 0 至 1，因此的確能有效降低功耗。然而這種做法直接影響了訊號的占空比(Duty Cycle)，加劇訊號的抖動是我們所不希望的。

圖 2.15 使用上升下降時間不對稱的中繼器來降低 MCF[16]

圖 2.16 的方式是只調整單邊的邊緣，讓上升邊緣縮減半個週期，因此上升的邊緣與下降邊緣彼此錯開，不會出現  $MCF=2$  的最差情形，使得  $MCF$  維持在 0 至 1 之間[17]。此做法雖能有效降低  $MCF$  然而  $MCF$  的變異也就代表著信號抖動。此外一般置入中繼器式的匯流排系統，其資料傳輸速率(Data Rate)為時鐘頻率(Clock Rate)兩倍，而此種作法之資料傳輸率只能和時鐘頻率一樣，也就代表著傳輸訊號無法達到此匯流排硬體速度的極限。

圖 2.16 單邊邊緣調整以降低 MCF[17]

## 2.8 主動式屏蔽

以直流電源線屏蔽能有效解決各種耦合造成的影響，然而造成的負載太大使整個匯流排的效能受要嚴重傷害，負載的增加也意味著功耗的上升。因此使用主動式屏蔽能提供良好的抗雜訊效果又不傷害到效能[19]，如圖 2.15 所示，在主要傳輸線兩旁加上屏蔽線，與直流屏蔽不同的是，兩旁的屏蔽線上不是直流訊號而是與受保護的主要傳輸線同步，因此主要信號不會受到雜訊的干擾，而因為兩旁的訊號與主訊號同步，因此 MCF 永遠在 0，讓主要傳輸線看到的等效負載變小，效能得以提升。

圖 2.17 主動式屏蔽[19]

然而此種作法只能保護特定線而無法在所有的傳輸線上使用，因此在晶片內匯流排這種每條線互為干擾與受害者的系統上並不適用。此外這種屏蔽方式的效果是否真能得到好處要經過審慎的計算，因為雖然降低了主要傳輸線上的等效耦合電容，卻要另外付出驅動兩旁屏蔽線的功耗，另外屏蔽線對其餘傳輸線造成影響也必須考量。

## 第三章

# 晶片內部匯流排模型

## 3.1 晶片內部匯流排模型

在此章節將介紹如何建立晶片內匯流排之模型，包括一般連接線電阻與電容模型之建立、時間常數之計算、與耦合效應模型之建立。連接線之電阻與電容模型依據實際製程參數與佈局建立，以三條連接線並排之形式表示一條匯流排模型。時間常數之計算將估計線電阻與線電容造成的時間常數，此外也將估計中繼器之時間常數。而耦合效應模型將以三條平行連接線之形式來建立，以此模擬相鄰信號之間彼此耦合之效果，此外我們也將建立平行線間加入屏蔽金屬線後之匯流排模型，以此來模擬耦合效應與負載增加之後所產生效應彼此之間的關係。

## 3.2 晶片內部連接線模型

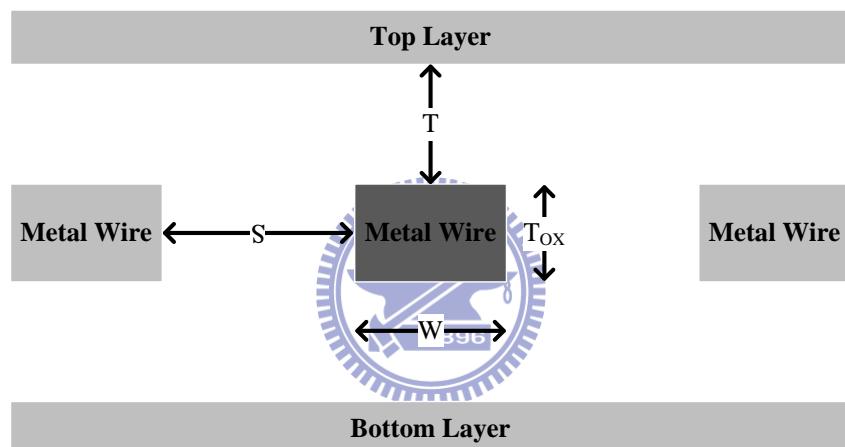

晶片內部連接線模型(on-chip interconnect model)如圖 3.1 與圖 3.2 所示。其中  $W$  為連接線寬度， $S$  為連接線間距， $T$  為連接線與上下層金屬的間距， $T_{OX}$  為連接線金屬層的厚度，而電容部分： $C_C$  為連接線與同一層金屬之間的耦合電容， $C_a$  為連接線與上下層金屬之間的平面電容， $C_f$  為連接線的邊緣電場電容。以下就連接線電阻與連接線電容的建立分別說明。

圖 3.1 晶片內部連接線示意圖

圖 3.2 晶片內連接線電容模型

連接線的單位長度電阻值可由下式導出，其中  $W$ 、 $T_{ox}$  如圖 3.1 所示， $\rho$  則為金屬材質的介電阻率。

$$r_{WIRE} = \frac{\rho}{W \times T_{ox}} \quad (3.1)$$

連接線的單位長度電容值如下式所示，其中  $C_C$  為連接線間的耦合電容， $C_a$  為連接線與上下層金屬間的平面電容， $C_f$  為連接線的邊緣電場電容，而  $W$  為連接線寬度， $S$  為連接線間距，請參見圖 3.1。

$$C_{WIRE} = 2C_C + 2C_a \cdot W + 4 \frac{C_f}{S} \quad (3.2)$$

以式 3.1 和式 3.2 帶入製程參數之後即可推估單位長度電阻值與單位長度電容值，然而在實際製作上理論值與實際數據仍有誤差，因此為了盡可能讓我們建立的模型接近實際環境，我們根據所使用的 TSMC MSG90 製程釋出的量測統計數值作為我們模型的依據。

我們模型建立的環境為 TSMC 90 MSG 製程，使用第五層金屬為連接線，不考慮上層板，而下層板則為基板，線寬為 0.14um，線間距為 0.14um。此環境之實際量測數據如表 3.1 所示，因此我們的單位長度電阻值為  $0.514 \Omega/\text{um}$ ，而單位線電容值則如式 3.3 所示，其值為  $7.34 \text{ fF}/\text{um}$ 。

$$C_{WIRE} = 2C_C + 2C_a \cdot W + 4 \frac{C_f}{S} \quad (3.3)$$

| Width(um) | Space(um) | $R_s$ (m $\Omega$ /sq) | $C_C$ (fF) | $C_a$ (fF) | $C_f$ (fF) |

|-----------|-----------|------------------------|------------|------------|------------|

| 0.14      | 0.14      | 72                     | 0.0991     | 1.42       | 2.91       |

表 3.1 MSG90 電阻、電容參照表

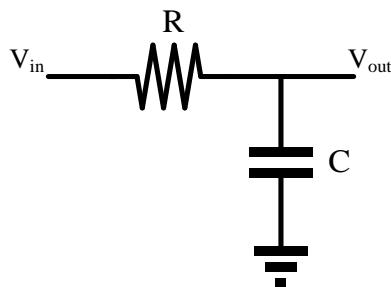

### 3.3 時間常數估計

晶片內部連接線時間常數之估計一般有兩種型式，分別為結合式模型(Lumped)與分散式模型(Distributed)兩種。結合式模型將每個線段的阻抗視為一個大電阻，每個線段的電容也同樣集合成一個大電容，如圖，因此整個線段的時間常數即為：

$$\tau = R \times C \quad (3.4)$$

圖 3.3 結合式電阻電容模型

結合式的電阻電容模型並不精確，然而其簡單的型式適合用來在第一時間評估電路特性或是用於簡化公式的推導。分散式的電阻電容模型如圖 3.4 所示，根據艾蒙延遲(Elmore delay)，若我們將一條連接線等份地切成 N 段，則所得的時間常數如下式：

$$\tau = \sum_{j=1}^N C_j \sum_{i=1}^j R_i \quad (3.5)$$

若我們所分割的段數遠大於一，則我們得到的近似結果如下：

$$\tau = RC \times \frac{N+1}{2N} \quad (3.6)$$

$$= \frac{RC}{2} (N \gg 1) \quad (3.7)$$

圖 3.4 分散式電阻電容模型

根據兩個模型我們得以估計電阻電容網路的各項延遲參數，包括延遲時間( $t_p$ )、時間常數( $\tau$ )、上升時間( $t_r$ )等，如下表所示[ 1]:

| Voltage Range | Lump Model | Distributed Model |

|---------------|------------|-------------------|

| 0→50%         | 0.69RC     | 0.38RC            |

| 0→63%         | RC         | 0.5RC             |

| 10%→90%       | 2.2RC      | 0.9RC             |

| 0→90%         | 2.3RC      | 1.0RC             |

表 3.2 步階響應在結合式模型與分散式模型之效果

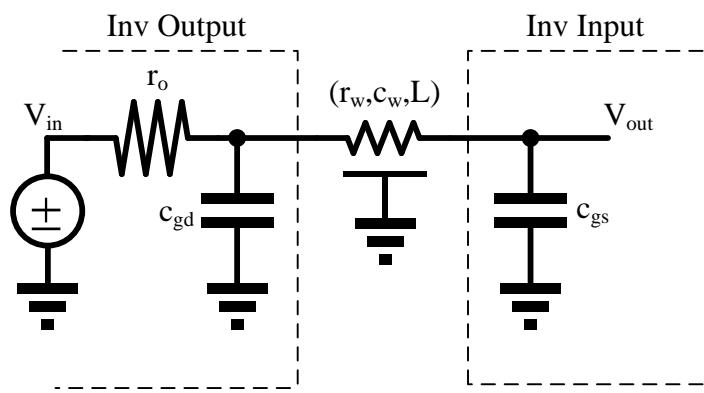

## 3.4 置入中繼器之時間常數

為了要降低傳輸線造成的延遲，我們一般會在長連接線中置入中繼器，本節將說明如何估算置入中繼器之後的時間常數[20]。置入中繼器之連接線示意圖如圖 3.5，其等效模型如圖 3.6 所示，時間常數如下所示：

$$\tau = r_o(c_{gd} + c_{gs}) + (r_o c_w + r_w c_{gs})L + \frac{r_w c_w}{2} L^2 \quad (3.8)$$

圖 3.6 置入中繼器等效模型

在未置入中繼器的情況下，傳輸線的時間常數  $\tau = R \times C$ ，訊號上升與下降時間為  $1.386RC$  (在此定義為  $20\% \sim 80\% V_{DD}$ )，傳輸延遲為  $0.693RC$  ( $0\% \sim 50\% V_{DD}$ )，若以置入一中繼器將傳輸線截為兩段為例，此時單段傳輸線之電容電阻變為一半，時間常數為  $0.25RC$ ，上升下降時間為：

$$T_r = T_f = 1.386 \left( \frac{R}{2} \times \frac{C}{2} \right) = 1.386 \left( \frac{1}{4} \times RC \right) \quad (3.9)$$

傳輸延遲則為：

$$\begin{aligned} T_d &= 0.69 \left( \frac{R}{2} \times \frac{C}{2} \right) + t_d + 0.69 \left( \frac{R}{2} \times \frac{C}{2} \right) \\ &= 0.69 \frac{RC}{2} + t_d \end{aligned} \quad (3.10)$$

因此若中繼器之傳輸延遲( $t_d$ )遠小於傳輸線造成的延遲，則置入一中繼器可降低一半之傳輸延遲。

以此模型得以評估每隔多長的連接線需要置入一組中繼器，有效降低訊號在連接線上的延遲。此外，因為數位邏輯運作上電晶體橫跨了截止區、飽和區與三極管區，因此  $r_o$  並非定值，經由 3.8 式我們可以得知當我們在一中繼器後掛上一個大的負載電容，則時間常數會由  $r_o C_L$  所主宰，因此我們可以藉由步階響應來逆推出一個平均  $r_o$ ，對於我們之後的公式推導有相當的幫助。

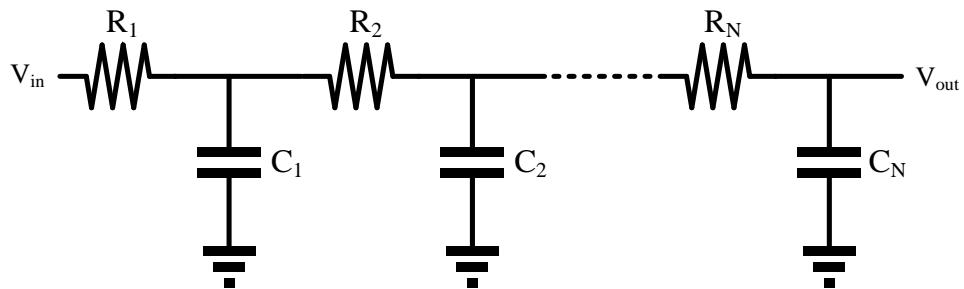

## 3.5 晶片內部匯流排電阻電容模型

匯流排之電容示意圖與晶片內部連接線的示意圖相同，請見圖 3.1 與圖 3.2。然而要觀察匯流排上的耦合效應我們需要建立匯流排電阻電容網路之 SPICE 模型，為了要模擬的精確不能僅以結合式模型表示，然而要是將匯流排以分散式模型呈現，分成越多多段當然越精準而模擬的時間也會大幅增加。因此要分成多少段才足夠精確，根據文獻 [1]指出，以 T3 模型來模擬，其誤差量已低於 3%。

圖 3.7 分散式電阻電容連接線模擬模型

根據我們要觀察耦合效應在匯流排上交互影響的用途，我們以相鄰線間耦合產生突波(Glitch)的模擬結果來驗證精準度，結果如圖 3.8 與表 3.3 所示，以 T10 模型為基準，模型間之差異量在 T3 已小於 3%。

|     | T1    | T2    | T3    | T4   | T5    | T6   | T7    | T8    | T9    | T10 |

|-----|-------|-------|-------|------|-------|------|-------|-------|-------|-----|

| 差異量 | 21.1% | 5.91% | 2.37% | 1.2% | 0.68% | 0.4% | 0.23% | 0.13% | 0.06% | 0   |

表 3.3 T1-T10 模型之差異量

圖 3.8 T1-T10 模型之差異量

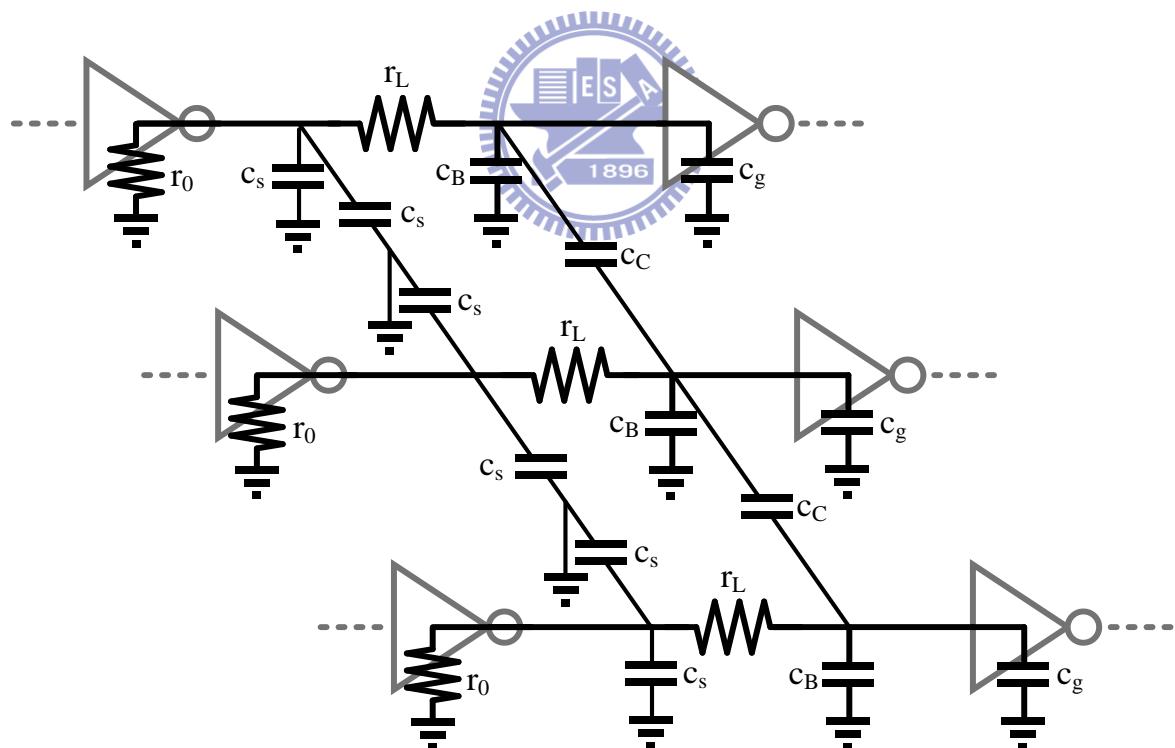

由上可知在要求模擬的精準度上，T3 的分散式模型已經足夠，然而因為我們需要分析屏蔽金屬線在匯流排中造成耦合與負載上帶來的影響，需要調整匯流排上屏蔽的比例，因此使用 T10 模型(圖 3.9)來模擬較合乎我們的需求。以下為使用 T10 之匯流排模型，其示意圖如圖 3.10 所示，深色部分為傳輸線，淺色部分則為屏蔽金屬，三條傳輸線被屏蔽金屬所包圍，每條金屬線皆以 T10 分散式模型表示，傳輸線與屏蔽線間之相鄰節點以耦合電容連接。若要調整屏蔽的比例則可按百分比拿掉中間屏蔽金屬的電阻電容之後以相鄰傳輸線間之耦合電容取代。

圖 3.9 T10 分散式模型

圖 3.10 T10 汇流排模型

圖 3.11 汇流排截面圖

SPICE 上我們使用 T10 分散式模型來模擬匯流排，然而在理論推導上為了要降低計算的難度，我們使用結合式模型作為我們推導的依據。如圖 3.12 所示，其中  $r_o$  為前級中繼器之輸出阻抗、 $R_L$  為單位線電阻、 $C_C$  為單位耦合電容、 $C_L$  包含連接線對基板之單位電容( $C_B$ )與對隔絕金屬線之單位電容( $C_S$ )。我們假設有 S% 的連接線被隔絕金屬保護而總長為 L，則：

$$c_C = C_C * L * (1 - S\%) \quad (3.11)$$

$$c_L = 2 * C_S * L * S\% + C_B \quad (3.12)$$

圖 3.12 結合式匯流排模型

## 第四章

# 晶片內部匯流排系統

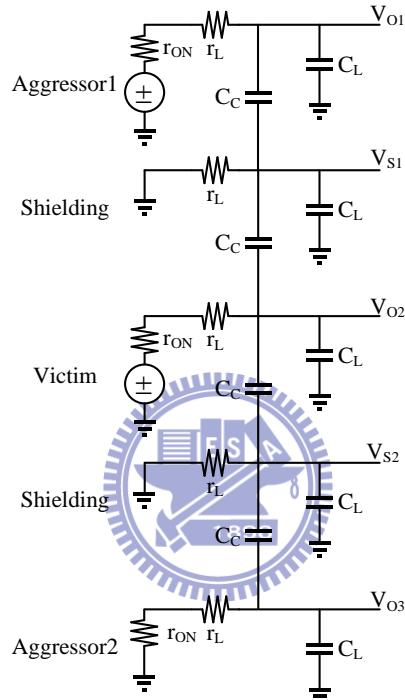

## 4.1 晶片內部匯流排系統

隨著製程的演進，晶片的面積不斷縮小而操作的速度則是越來越快，然而元件隨著製程縮小匯流排的長度卻因為更多的電路整合進入晶片內而不減反增，此外製的縮小也讓相鄰線間的寄生電容隨著距離的縮短而變大，因此不論是在面積上或是速度上，匯流排都逐漸成為晶片設計上的瓶頸。

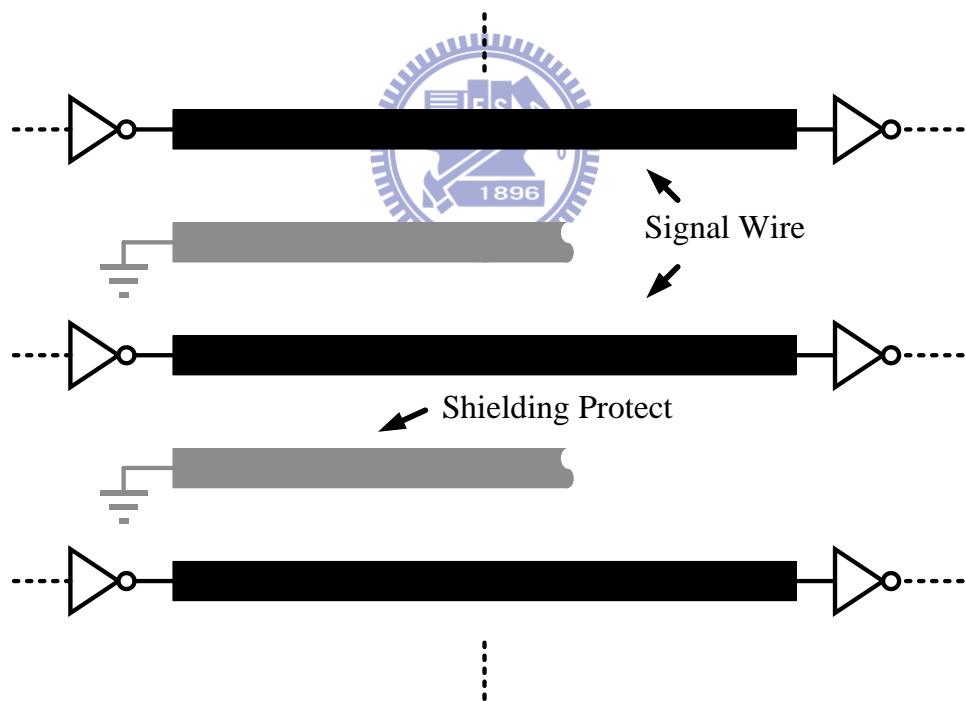

在面積、速度與功耗的取捨上，要達成高速而低功率消耗，我們使用拔靴帶式中繼器找到突破的方法，這部分已在第二章 1 到 3 節表示。此章將主要說明降低匯流排面積之考量。為了要降低匯流排所使用的面積，我們希望匯流排能以最高的密

度排列，然而此做法最大的問題就是緊密排列的平行連接線會造成嚴重的串音現象，讓連接線彼此的間距相隔越短，其耦合電容就越大，串音現象就越發嚴重，因此一般為了要避免串音現象會安插屏蔽線在連接線之間，以此來隔絕串音現象，然而此做法帶來大量的負載使得操作速度無法提升且造成更多的功率消耗。

我們的想法則是使用屏蔽線保護部分的連接線，將串音現象抑制到我們得以容忍的範圍即可，而拿掉部分的屏蔽線則可降低屏蔽線造成的負載，以此換取速度上的提升或是降低功率的消耗，如圖 4.1 所示：

圖 4.1 (A)完全屏蔽 (B)部分屏蔽 (C)沒有屏蔽

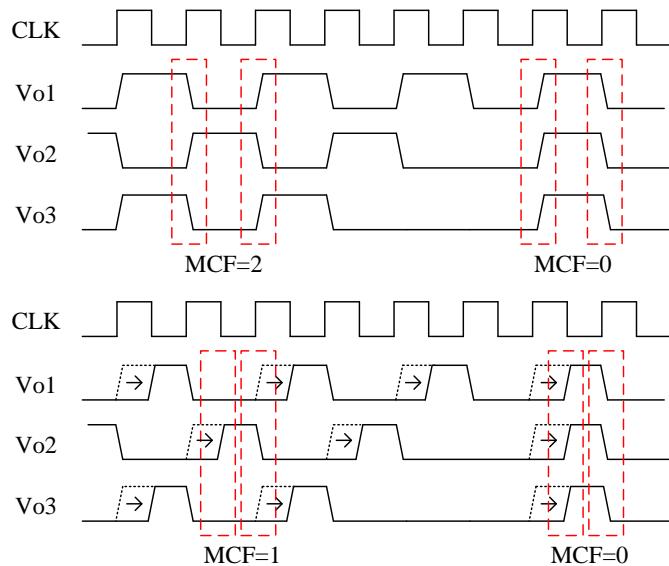

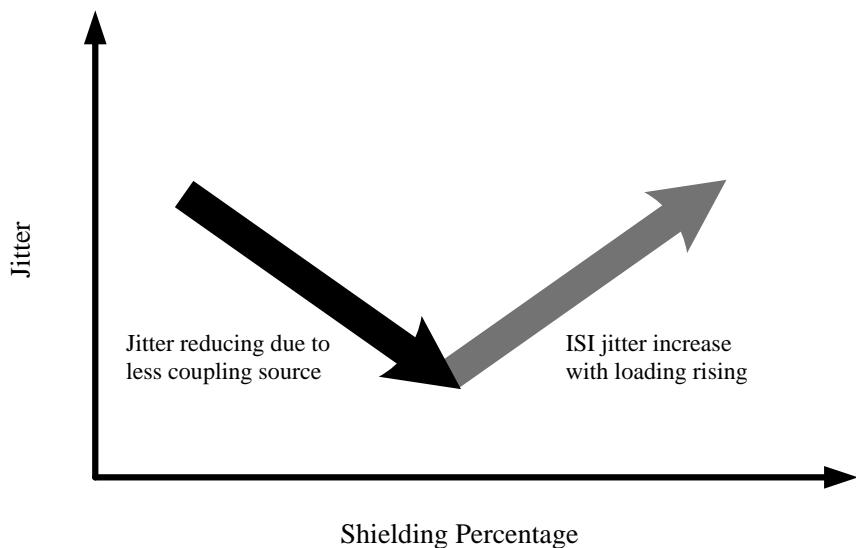

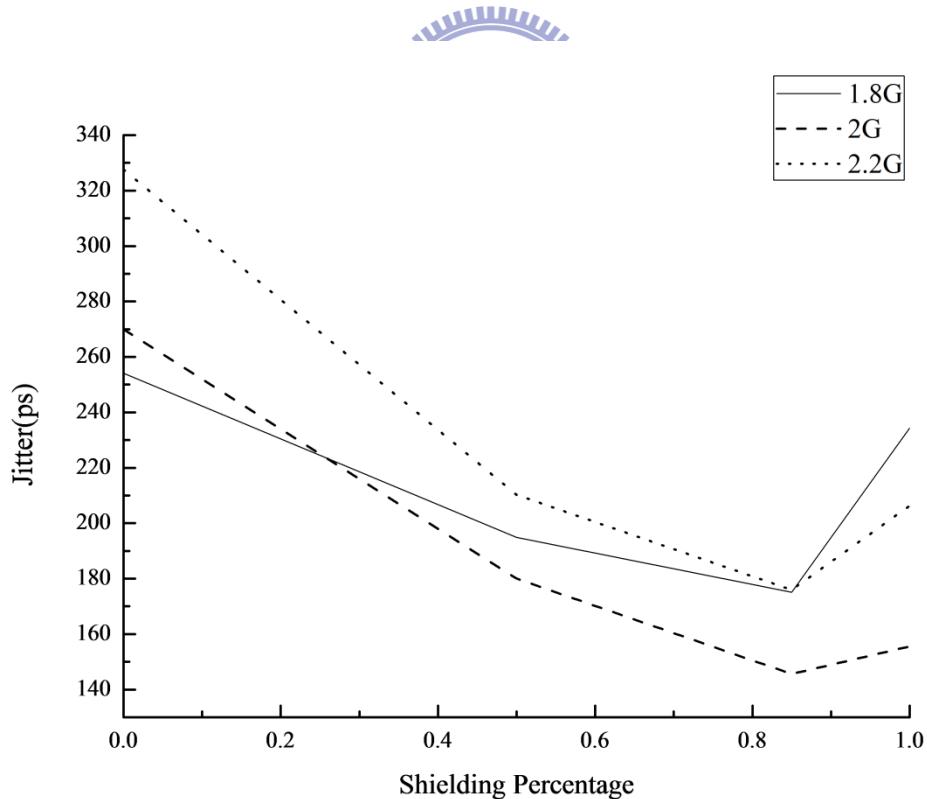

以信號的抖動來看耦合效應與負載效應造成的影响，如圖 4.2 所示，我們預期信號的抖動會先因為屏蔽線所保護的比例增加使得耦合效應得到抑制而降低，隨後因為屏蔽線增加帶來的負載效應造成 ISI 信號抖動[21]。

圖 4.2 使用屏蔽線保護之比例與信號抖動之關係

為了要驗證我們預期的結果，於本章中將建立耦合效應之模型[22]與 ISI 效應之模型[23]，藉由此模型找出最佳的屏蔽比例使信號抖動抑制於一定範圍內以此降低功耗或是提升速度，此外也提出降低耦合效應造成信號抖動之方法，並分析耦合效應實與 ISI 效應實際對於信號抖動之成因。

## 4.2 轉態邊緣交錯機制

匯流排在沒有屏蔽線保護的狀況下將會有嚴重的耦合效應進而導致信號抖動。若以電容負載來看，如圖 4.3 所示隨著不同信號組合，等效的耦合電容值( $C_C$ )在 0~4 倍變化，等效電容值的不同也就造成充放電時間不同因而產生上升下降時間的差異，也就造成信號的抖動。

| Switch Pattern<br>(A,B,C)           | Effective Capacitance of Line B |

|-------------------------------------|---------------------------------|

| (↑↑↑),(↓↓↓)                         | $C_{sub}$                       |

| (-↑↑),(↑↑-),(-↓↓),(↓↓-)             | $C_{sub}+C_C$                   |

| (-↑-),(-↓-),(↑↑↓),(↓↑↑),(↓↓↑),(↑↓↓) | $C_{sub}+2C_C$                  |

| (-↑↓),(-↓↑),(↑↓-),(↓↑-)             | $C_{sub}+3C_C$                  |

| (↑↓↑),(↓↑↓)                         | $C_{sub}+4C_C$                  |

圖 4.3 平行線間等效電容

我們藉由圖 4.3 中連接線 B 上之訊號的上升邊緣來觀察這個現象，若連接線 B 上之訊號上升時相鄰的兩線都在穩態則其所見到的等效電容為  $C_{sub}+2C_C$ ，訊號 B 之電壓對時間的關係如式 4.1 所示，其中 R 為線電阻與輸出阻抗。

$$v(t) = (1 - e^{-\frac{t}{R(C_{sub}+2C_C)}}) \quad (4.1)$$

我們定義信號的抖動為在轉態的臨界電壓(Threshold Voltage)上之時間差，我們假設臨界電壓為  $v_{th}$  而通過臨界電壓的時間為  $t_0$ ，根據式 4.1 我們可以導出時間對電壓之關係式：

$$t = R(C_{sub} + 2C_C) \ln\left(\frac{1}{1-v}\right) \quad (4.2)$$

Let  $v(t_0) = v_{th}$

$$t_0 = R(C_{sub} + 2C_c) \ln\left(\frac{1}{1-v_{th}}\right) \quad (4.3)$$

$$\Delta t_c = R(C_g + \Delta C_c) \ln\left(\frac{1}{1-v_{th}}\right) \quad (4.4)$$

式 4.4 即是因為耦合效應造成等效電容變異所產生的信號抖動，根據圖 4.3 電容值之變異範圍為  $0C_C$  到  $4C_C$ ，所以信號的抖動如下式：

$$Jitter = R(C_g + 4C_c) \ln\left(\frac{1}{1-v_{th}}\right) - R(C_g) \ln\left(\frac{1}{1-v_{th}}\right) \quad .$$

(4.5)

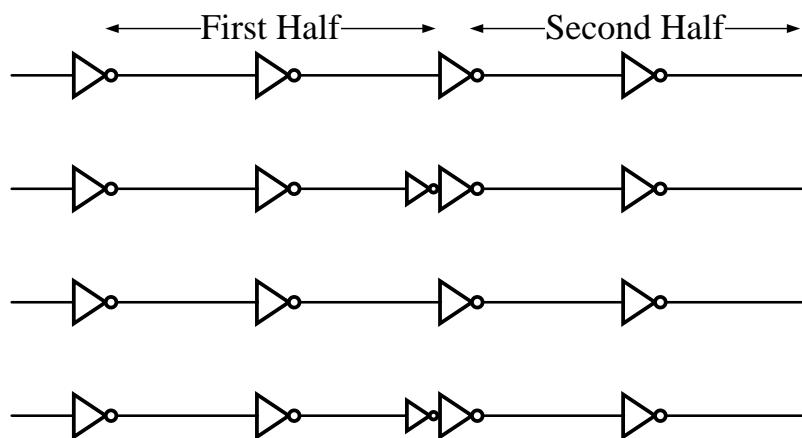

為了要處理耦合效應產生的信號抖動，我們的想法是讓相鄰線間彼此的訊號相差 180 度的相位差，使得相鄰的信號轉態時都相差半個週期。處理過後的信號在轉態時相鄰的信號永遠都是處在穩態，因此等效的電容值固定為  $C_{sub}+2C_C$ ，沒有等效容值的變異理想上所有信號的上升與下降時間皆一致，也就沒有耦合效應產生的信號抖動。

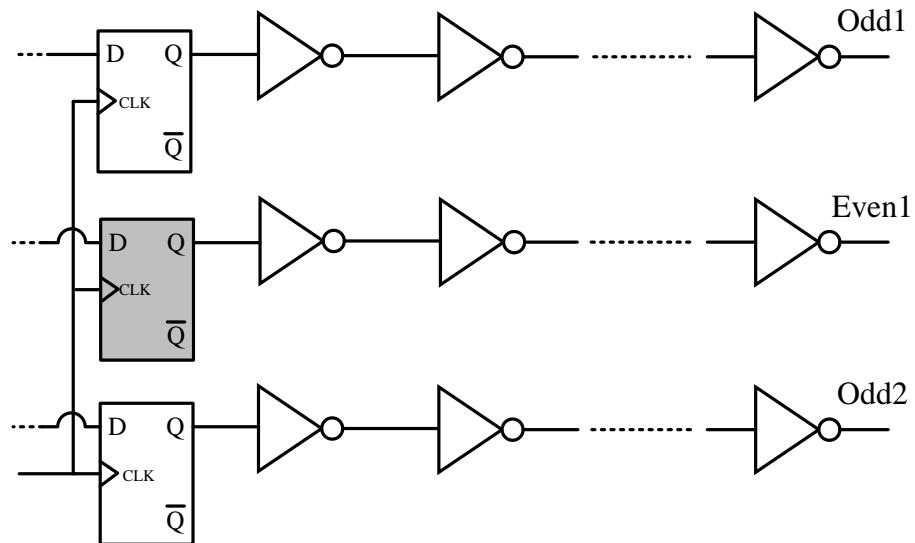

而要實踐這個方法相當的簡單，我們在所有的奇數連接線前加上正緣觸發的 D 型正反器，而偶數連接線前則是負緣觸發 D 型正反器，如圖 4.4 所示：

圖 4.4 轉態邊緣交錯機制示意圖

圖 4.5 操作波形示意圖

操作波形如圖 4.5 所示，我們使用不歸零資料編碼(NRZ)，需要一組頻率等同於資料傳輸速率的時鐘訊號來控制正反器。如圖所示，所有的訊號在轉態時相鄰線上的信號一定都維持在穩態。

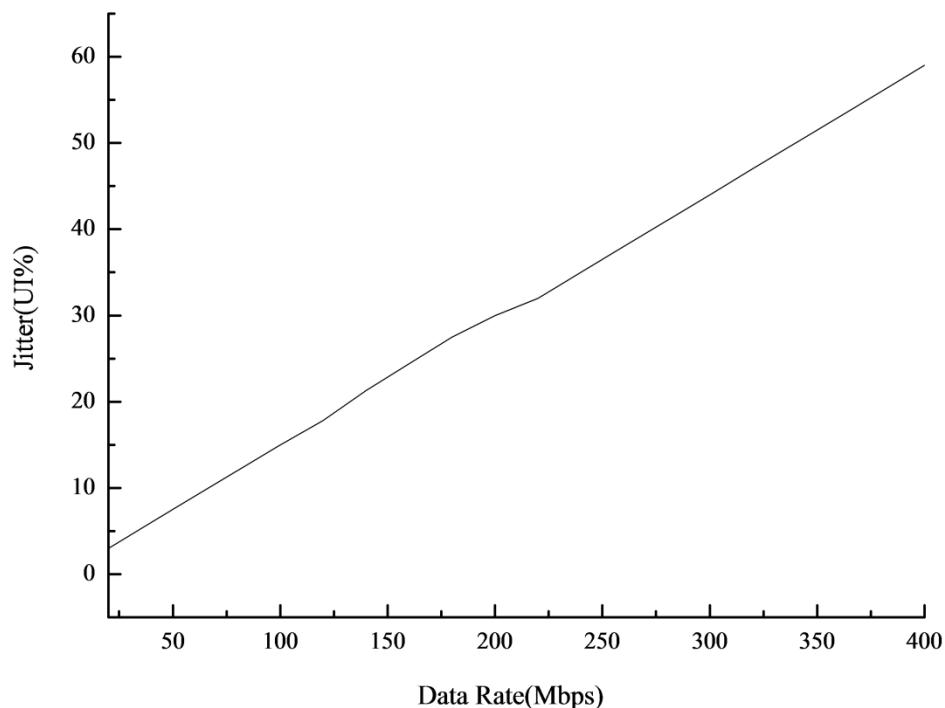

模擬結果如圖 4.6 與圖 4.7 所示，圖 4.6 為沒有使用轉態邊緣交錯機制之結果，我們可以看到匯流排受到耦合效應干擾而產生嚴重的信號抖動，若目標為將抖動抑制在 10%UI 內，則不使用此機制約略只能操作在 100Mbps。

圖 4.6 不使用轉態邊緣交錯機制

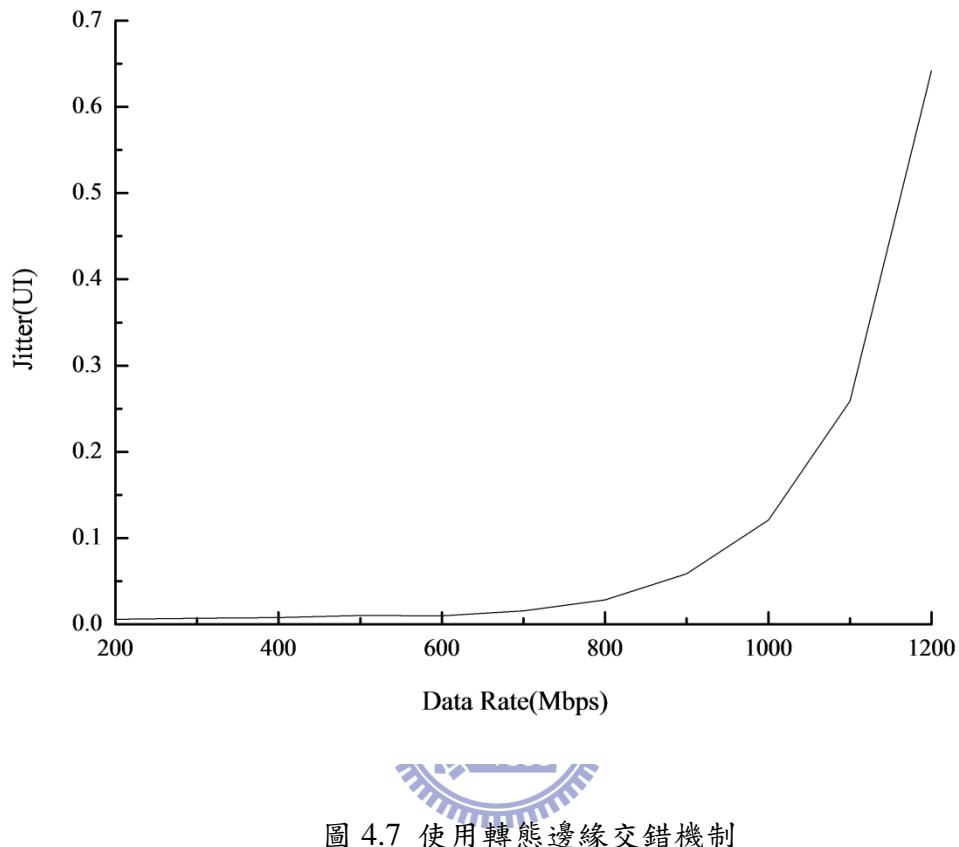

而在使用轉態邊緣交錯機制後，在抖動 10%UI 的相同條件下速度則得到顯著的提升，得以操作在 1Gbps，如圖 4.7 所示。

圖 4.7 使用轉態邊緣交錯機制

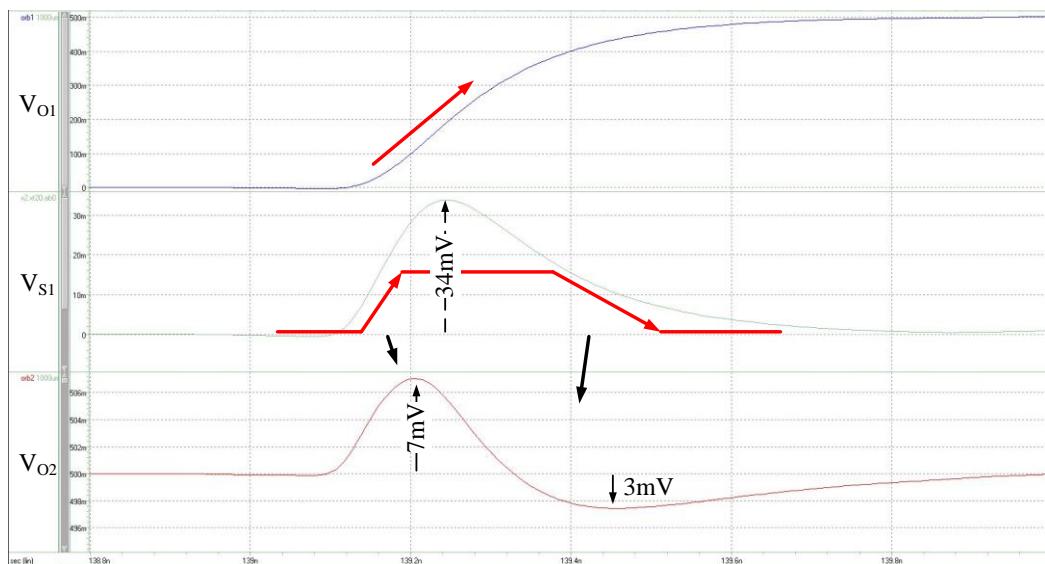

### 4.3 耦合效應

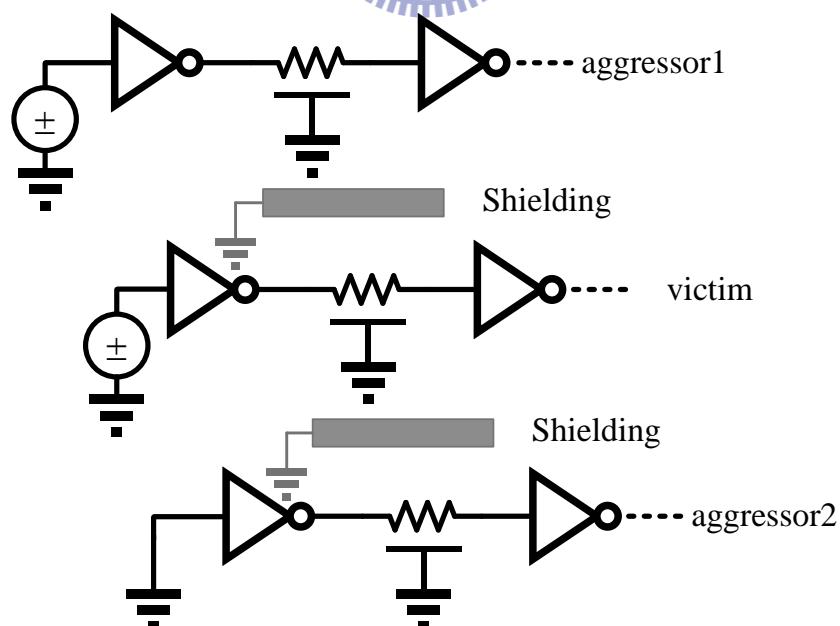

理想上，匯流排上的信號經過轉態邊緣交錯機制處理過後，轉態邊緣已經不會受到耦合效應的影響，因而不會有信號的抖動，然而我們發現因為耦合效應而產生的突波 (Glitch)，以往的考量多是防止造成誤動作，在特定狀況下也會對轉態邊緣造成影響進而產生信號抖動。我們先將匯流排模型中耦合出的突波模型化，再分析突波對於信號抖動的影響。

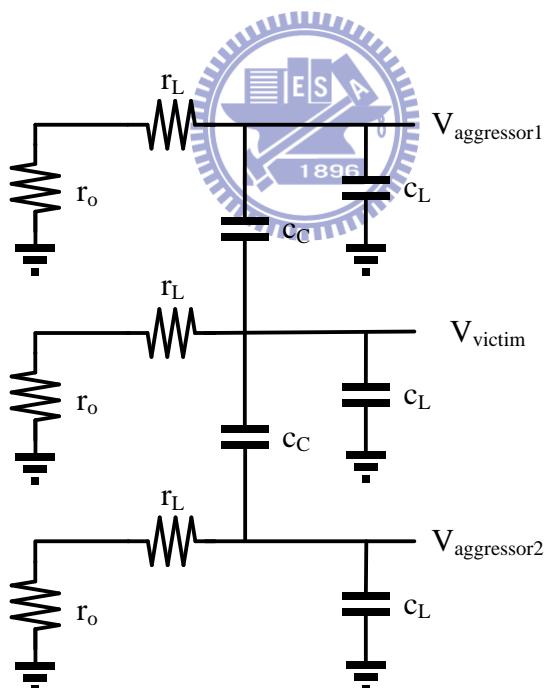

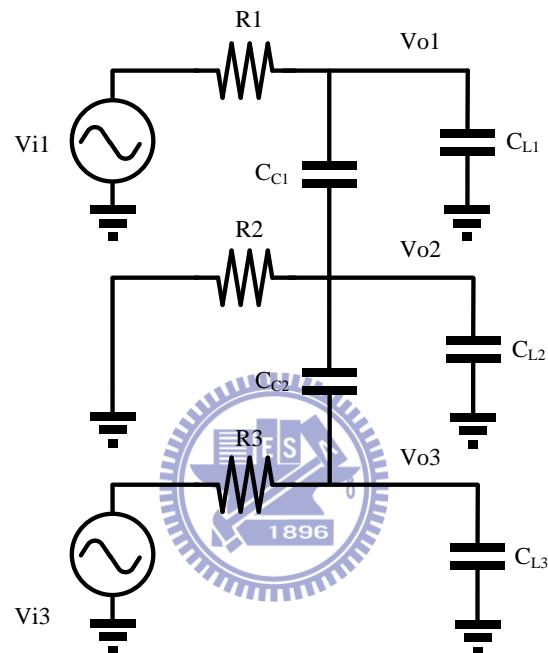

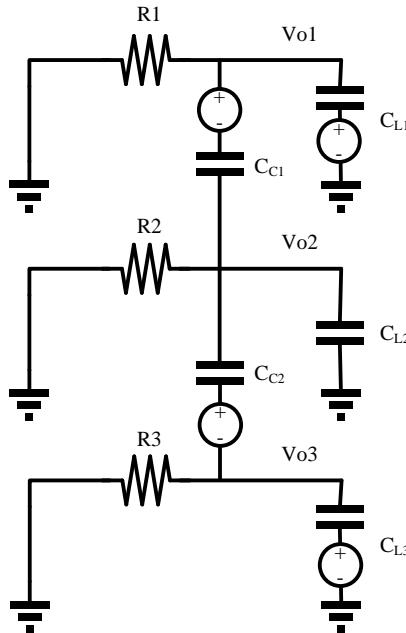

我們以結合式匯流排模型來進行耦合生成突波之推導，如圖 4.8 所示，我們以中間之連接線作為觀察突波產生的待測線，兩旁之連接線作為造成耦合突波之干擾線，其中  $R1$ 、 $R2$ 、 $R3$  包含了線電阻與中繼器之輸出阻抗， $CL1$ 、 $CL2$ 、 $CL3$  則是線與中繼器之寄生電容， $CC1$  與  $CC2$  則為

圖 4.8 正向突波模型

我們先計算  $Vi1$  對  $Vo2$  造成的影响，之後再依據重疊定理加入  $Vi3$  造成的影响，根據克希荷夫電流定律分別解出  $Vo1$ 、 $Vo2$ 、 $Vo3$  三個節點的電流公式，在此我們假設  $Vi1$  與  $Vi3$  為兩個上升步階函數電壓源並在複頻域進行計算：

$$\frac{V_{O1} - \frac{V_{DD}}{s}}{R_1} + sC_{C1}(V_{O1} - V_{O2}) + sC_{L1}V_{O1} = 0 \quad (4.6)$$

$$\frac{V_{O2}}{R_2} + sC_{C1}(V_{O2} - V_{O1}) + sC_{C2}(V_{O2} - V_{O3}) + sC_{L2}V_{O2} = 0 \quad (4.7)$$

$$\frac{V_{O3}}{R_1} + sC_{C2}(V_{O3} - V_{O2}) + sC_{L3}V_{O3} = 0 \quad (4.8)$$

接著我們假設  $R=R_1=R_2=R_3$ 、 $C_L=C_{L1}=C_{L2}=C_{L3}$ 、 $C_C=C_{C1}=C_{C2}$ ，並且將式 4.6 與式 4.8 代入式 4.7 解出  $V_{O2}$ :

$$V_{O2} = \frac{RC_C V_{DD}}{3s^2 R^2 C_C C_L + 3sRC_C + 2sRC_L + s^2 R^2 C_L^2 + 1} \quad (4.9)$$

$$V_{O2} = V_{DD} \left[ \frac{-\frac{1}{3}RC_L}{1+sRC_L} + \frac{\frac{1}{3}R(C_L + 3C_C)}{1+sR(C_L + 3C_C)} \right] \quad (4.10)$$

依據逆拉普拉斯變換解得  $V_{O2}$  對時域之關係:

$$V_{O2}(t) = \frac{V_{DD}}{3} \left( -e^{\frac{-t}{RC_L}} + e^{\frac{-t}{R(C_L + 3C_C)}} \right) \quad (4.11)$$

因為  $V_{i3}$  對於  $V_{O2}$  的關係與  $V_{i1}$  對於  $V_{O2}$  完全相同，因此根據重疊定理我們可以得出  $V_{i1}$  與  $V_{i3}$  對  $V_{O2}$  所產生的突波電壓為:

$$V_{O2}(t) = u(t) \frac{2V_{DD}}{3} \left( -e^{\frac{-t}{RC_L}} + e^{\frac{-t}{R(C_L + 3C_C)}} \right) \quad (4.12)$$

而當兩旁干擾線為下降步階函數即會在中間維持穩態的待測線上出現反向突波，示意圖如圖 4.9 所示，推導的過程與正向突波之生成大致相同，結果如式 4.13：

$$V_o(t) = u(t) \frac{2V_{DD}}{3} (e^{\frac{-t}{RC_L}} - e^{\frac{-t}{R(C_L+3C_C)}}) \quad (4.13)$$

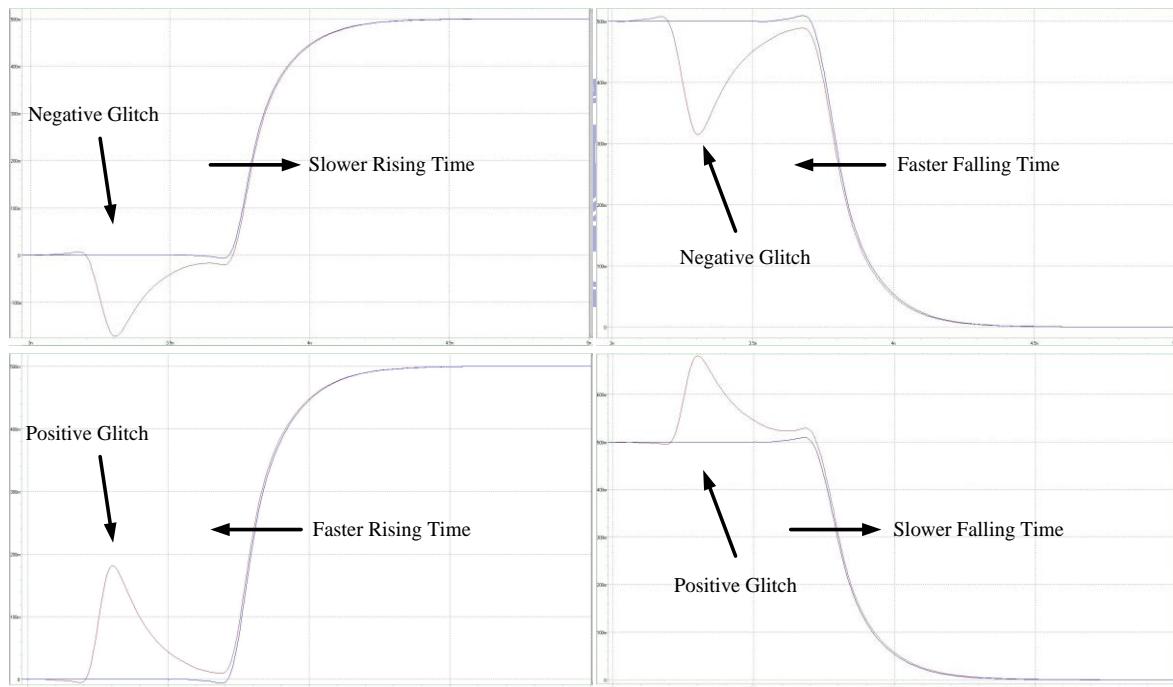

一般狀況下，耦合產生的突波只要不會越過臨界電壓造成數位電路的誤動作對於系統就沒有實質的影響，然而在圖 4.10 中出現的情形顯示在速度達到一定程度後，突波無法在半個單位間隔(Unit Interval, UI)內回到穩態電壓，因而造成待測線上之信號轉態邊緣受到突波的干擾，當反向突波後信號上升則上升時間會較不受干擾的狀態下慢，反相突波後之下降時間則較不受擾的狀態快，而當正向突波在上升邊緣前，此上升邊緣會變快，而正向突波在下降邊緣之前，則下降時間較慢，上升下降時間的變異也就是所謂

的信號抖動。當兩旁干擾線同為上升或是下降轉態產生最大的正向突波或是反向突波這兩個極端值，進而造成待測線上訊號轉態有四個上升下降時間之變異，而耦合效應造成的信號抖動之值就在於這四個極端值間取最大差值。為了要抑制這種現象最直接的想法就是降低耦合效應所產生的突波大小，若能抑制突波使其在影響轉態邊緣之前即能回到穩態電壓就不會造成信號抖動的產生。而一般處理耦合效應產生突波的辦法為拉開連接線彼此之間的間距或是在連接線間加入接地的屏蔽線以此來保護信號的傳輸，然而拉開連接線的間距與我們使用最小面積來設計我們匯流排系統的目標相違，因此我們希望能夠以加入屏蔽線的方式來處理。

圖 4.10 耦合產生突波造成信號抖動

## 4.4 屏蔽比例分析

我們希望藉由加入屏蔽線來抑制相鄰傳輸線間彼此的耦合效應，然而加入屏蔽線雖能有效抑制耦合效應，但連接線與屏蔽線更加接近的間距使得線間之耦合電容值上升，電容負載的增加導致功耗的上升與速度的下降。因此如果我們在一段匯流排中讓一部份的信號線被屏蔽線所保護而一部份的信號線裸露出來，如圖 4.11 所示，耦合產生的突波會透過裸露出來的部分進入信號線中，然而如果我們能找出一個屏蔽比例將耦合效應產生的影響控制在容忍範圍內，如此一來能讓信號線避免多餘屏蔽線所造成的負載，以此換取功耗的下降與速度的提升。

圖 4.11 部分屏蔽匯流排示意圖

根據我們先前推導的耦合突波模型，我們在其中加入屏蔽線相關的參數，模型圖如

圖 4.12 所示，其中  $C_C$  為信號線與信線間之耦合電容， $C_B$  為對基板電容， $C_S$  則為信號線到屏蔽線間之電容，我們假設有  $x\%$  的信號線被屏蔽線所包圍則：

$$c_L = C_B + C_g + x\%2C_S \quad (4.14)$$

$$c_C = C_C(1-x\%) \quad (4.15)$$

根據式 4.12，加入屏蔽線相關參數後的正向突波對時域關係式為：

$$V_o(t) = \frac{2V_{DD}}{3} \left( -e^{\frac{-t}{R(C_B + x\%2C_S)}} + e^{\frac{-t}{R[C_B + x\%2C_S + 3C_C(1-x\%)]}} \right) \quad (4.16)$$

圖 4.12 加入屏蔽線後之匯流排模型

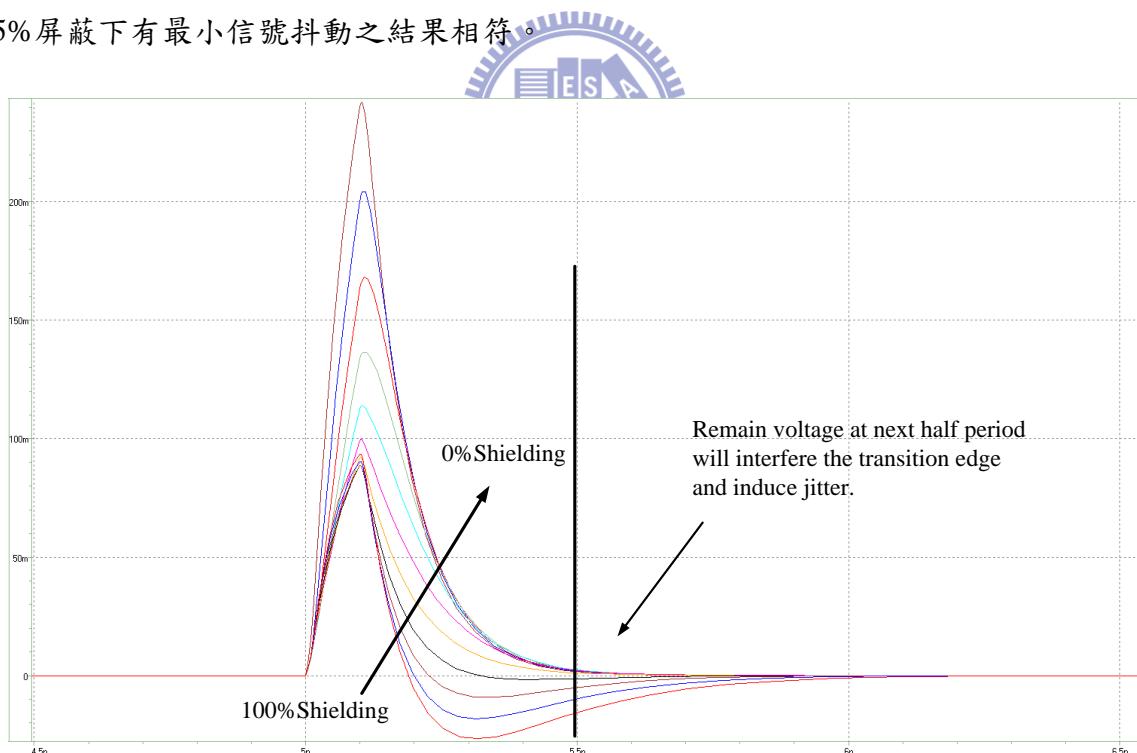

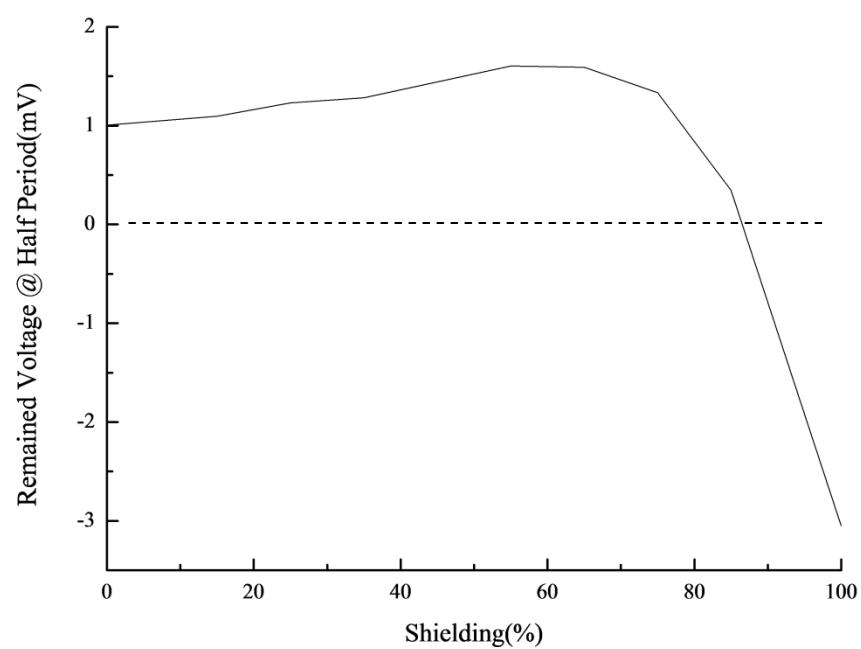

我們可以發現突波之電壓峰值隨著屏蔽的比例之上升而降低，如圖 4.13 所示：

圖 4.13 突波電壓與屏蔽比例關係圖

圖 4.14 不同屏蔽比例之突波電壓與半單位間隔後殘存電壓

然而我們關注的點在於耦合產生的突波是否能在轉態邊緣前回到穩態電壓，如圖 4.14 所示，因此突波電壓的峰值並不是重點，而是要看半個單位間隔後突波殘存的電壓值，殘存的電壓值越接近穩態電壓則造成的信號抖動就越少。

為了估算最佳的屏蔽比例讓信號抖動的影響降至最低，我們發現所有的突波都是經由相同的中繼器之輸出阻抗來進行放電，因此耦合進入待測線中之電荷量越多則放電的時間越長，也就代表轉態邊緣上之電壓值越高，信號的抖動就越嚴重。我們將突波峰值去乘上待測線之負載電容即能得出兩旁干擾線耦合到待測線上之電荷量，待測線上之負載電容隨屏蔽比例之變化如圖 4.15 所示：

圖 4.15 負載電容與屏蔽比例關係圖

耦合突波之峰值隨著屏蔽的比例而下降，然而負載電容值隨著屏蔽比例的上升而增加，而將負載電容乘上突波之峰值電壓後，如圖 4.16 所示，在約略百分之四十的屏蔽比例下有最大的耦合感應電荷，隨著屏蔽的比例提高感應電荷量隨之下降。

從信號抖動的模擬圖來看，圖 4.17 為各個屏蔽比例在不同速度下之信號抖動，可以發現在低速時信號的抖動在各個屏蔽比例下並無顯著差異，然而當速度接近 1Gbs 時，如同我們預期的耦合效應開始造成信號抖動，在 40% 屏蔽比例時有一個峰值出現之後隨之下降，在超過 85% 之後再度上升，這部分是受到 ISI 效應與其他因素影響所致，將會在後續章節詳述。

圖 4.17 信號抖動與屏蔽關係模擬圖

## 4.5 ISI 抖動

一般之數位邏輯電路當輸入信號為隨機資料時常會發生 ISI 抖動，特別是在操作在接近臨界速度時特別嚴重。我們首先假設一串數位資料，：

$$r(t) = \sum_{n=-\infty}^{\infty} a_n p(t - nT) \quad (4.17)$$

其中  $a_n$  表示此筆資料為 0 或 1， $p(t)$  則由步階函數組成：

$$p(t) = s(t) - s(t - T) \quad (4.18)$$

$$r(t) = \sum_{n=-\infty}^{\infty} a_n [s(t - nT) - s(t - (n+1)T)] \quad (4.19)$$

我們用泰勒級數在臨界電壓展開此函式：

$$s(t-nT) = s(t_0-nT) + (t-t_0)s^{(1)}(t_0-nT) \quad (4.19)$$

$$r(t) = \sum_{n=-\infty}^{\infty} a_n [s(t_0-nT) + (t-t_0)s^{(1)}(t_0-nT) - s(t_0-(n+1)T) - (t-t_0)s^{(1)}(t_0-(n+1)T)] \quad (4.20)$$

接著我們假設在  $t_c$  時穿越臨界電壓  $v_{th}$ :

$$r(t_c) = v_{th}$$

$$\begin{aligned} v_{th} &= \sum_{n=-\infty}^{\infty} a_n [s(t_0-nT) + (t_c-t_0)s^{(1)}(t_0-nT) - s(t_0-(n+1)T) - (t_c-t_0)s^{(1)}(t_0-(n+1)T)] \\ &= \sum_{n=-\infty}^{\infty} a_n \{ (t_c-t_0) \delta^{(1)}(t_0(nT-s))^{(1)}_0 - (t_c-t_0) \delta^{(1)}(t_0(nT-s))^{(1)}_0 \} \\ &= \sum_{n=-\infty}^{\infty} a_n (t_c-t_0) \delta^{(1)}(t_0(nT-s))^{(1)}_0 + \sum_{n=-\infty}^{\infty} a_n (t_c-t_0) \delta^{(1)}(t_0(nT-s))^{(1)}_0 \quad (4.21) \end{aligned}$$

則信號的抖動  $\Delta t_c = (t_c - t_0)$ :

$$\Delta t_c = \frac{\sum_{n=-\infty}^{\infty} a_n [s(t_0-nT) - s(t_0-(n+1)T)]}{\sum_{n=-\infty}^{\infty} a_n [s^{(1)}(t_0-nT) - s^{(1)}(t_0-(n+1)T)]} \quad (4.22)$$

若我們以連續的三個位元來看信號 ISI 抖動，則有 001、110、010、101 四種情形，

當信號為 001 時  $\Delta t_c$  之分子為  $v_{th} - s(t_0)$ ，因為  $s(t_0) = v_{th}$  而我們假設  $v_{th} = 0.5$ ，所以  $t_c = t_0$ 。

而當信號為 110 時分子為  $v_{th} - [s(t_0+2T) - s(t_0+T) + s(t_0+T) - s(t_0)]$ ，因為為連續之 1 信

號我們假設兩位元前也是 1，因此  $s(t_0+2T) = 1$ ， $t_c = t_0$ 。而當信號為 010 時：

$$\Delta t_c = \frac{v_{th} - [s(t_0 + T) - s(t_0)]}{s^{(1)}(t_0 + T) - s^{(1)}(t_0)}$$

因為  $s(t_0) = v_{th}$ ，因此

$$\Delta t_c = \frac{1 - s(t_0 + T)}{s^{(1)}(t_0 + T) - s^{(1)}(t_0)} \quad (4.23)$$

而當信號為 101 時

$$\Delta t_c = \frac{v_{th} - [s(t_0 + 2T) - s(t_0 + T) + s(t_0)]}{s^{(1)}(t_0 + 2T) - s^{(1)}(t_0 + T) + s^{(1)}(t_0)}$$

在此我們都假設兩位元前皆為連續 1 之穩態，因此  $s(t_0 + 2T) = 1$ ， $s^{(1)}(t_0 + 2T) = 0$ ，

因此當信號為 101 之抖動：

$$\begin{aligned} \Delta t_c &= \frac{v_{th} - [1 - s(t_0 + T) + s(t_0)]}{-s^{(1)}(t_0 + T) + s^{(1)}(t_0)} \\ &= \frac{-[1 - s(t_0 + T)]}{-s^{(1)}(t_0 + T) + s^{(1)}(t_0)} \\ &= \frac{1 - s(t_0 + T)}{s^{(1)}(t_0 + T) - s^{(1)}(t_0)} \end{aligned} \quad (4.24)$$

由上述推導可知，ISI 抖動受到信號轉態斜率之影響，轉態斜率越小則信號抖動越大，因此負載越大使得上升下降時間越長會讓信號受到 ISI 之影響愈加劇烈。我們

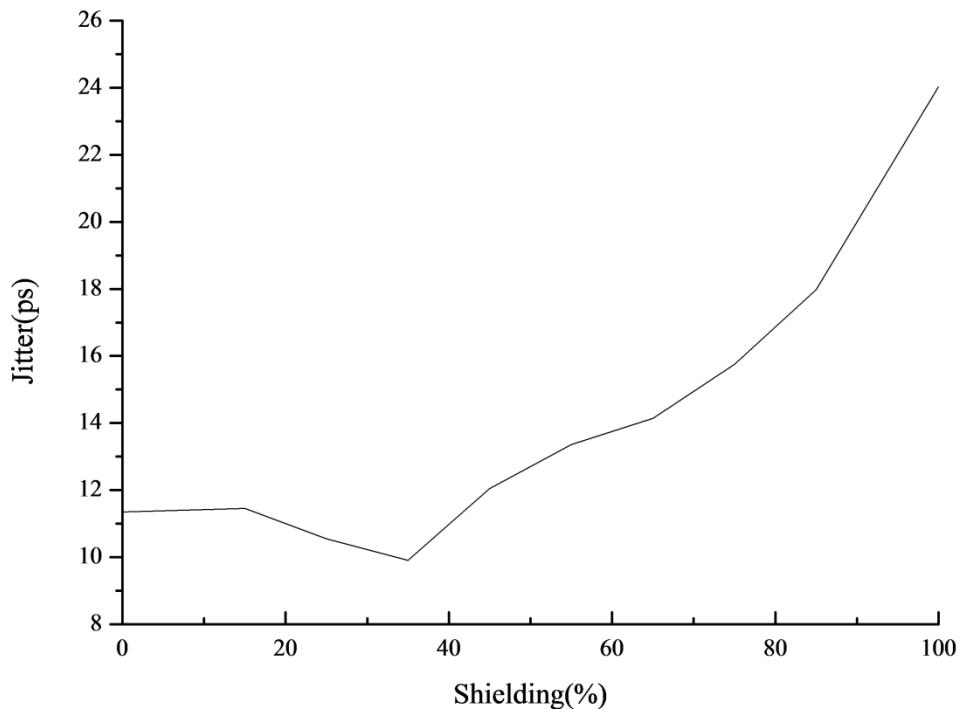

讓匯流排兩旁沒有干擾線影響之情形下，以 1Gbps 之隨機資料進行 Spice 模擬，模擬結果如圖 4.18 所示，隨著屏蔽比例之上升信號抖動的程度也隨之增加。

圖 4.18 ISI 抖動之模擬結果@1Gbps

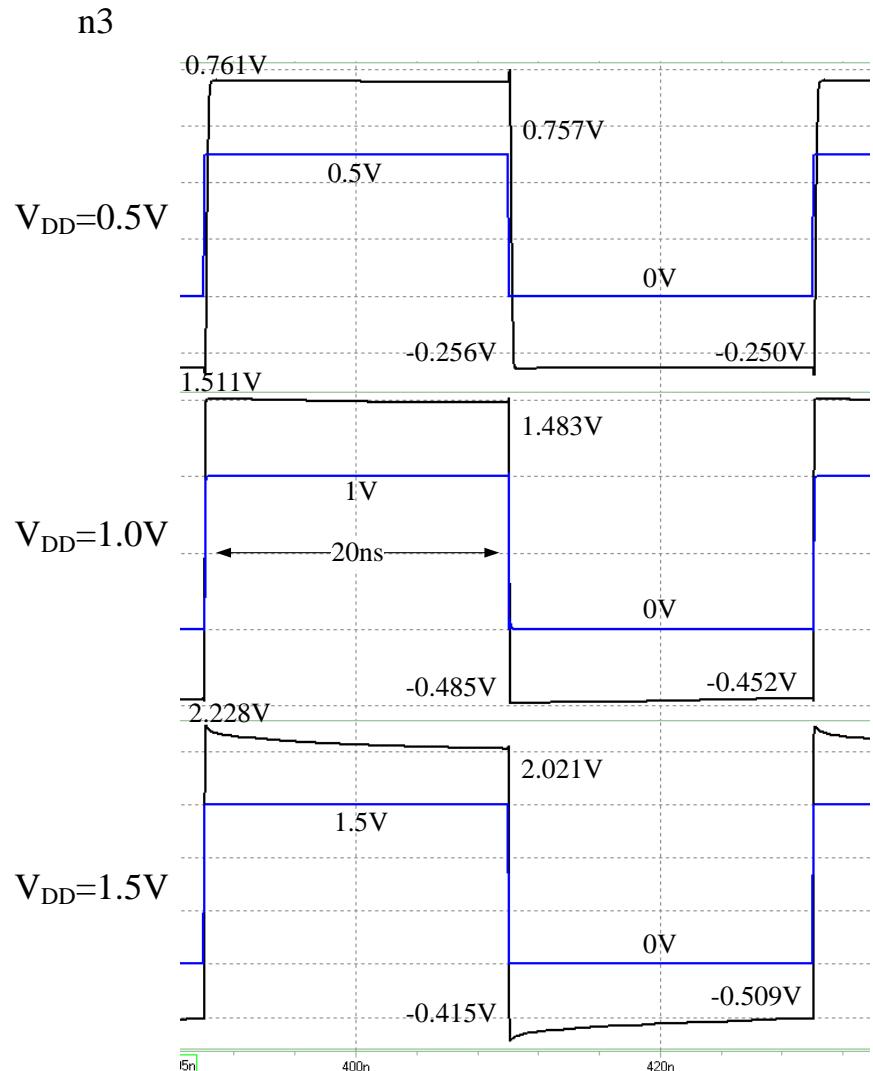

而另一個造成 ISI 抖動的原因在於我們做為中繼器使用得拔靴帶式電路。因為拔靴帶式電路中含有升降壓電容，當電容充放電不及或是有漏電情形產生就會造成信號抖動。在一般之拔靴帶式電路應用在低壓環境中，負責充放電容之電晶體因在低壓環境中因而驅動能力有限，若操作速度過快則升降壓電容容易產生充放電不完全之情形。而我們所使用之拔靴帶式電路，如圖 4.18 所示，則讓負責對升降壓電容充放電之電晶體  $M_{P1}$  與  $M_{N1}$  由升降壓過後之節點所驅動，因此能提供較大的電流給升降壓電容以提升充放電時間。

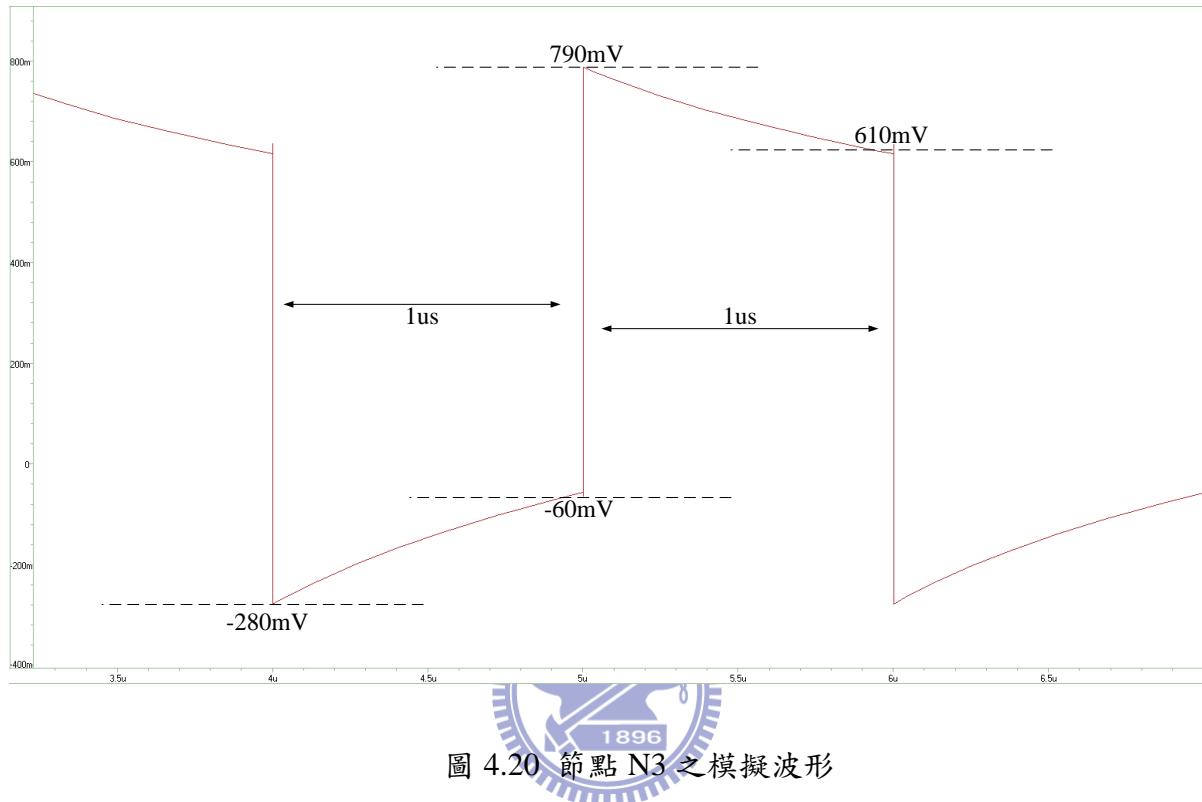

圖 4.19 本文所使用之拔靴帶式電路

而另一個問題即是電容充放電完成後會有漏電之情形，若是輸入之信號為適當的時鐘訊號讓內部之升降壓電容之容值定期刷新則不會有此問題，然而當頻率過慢或是輸入訊號回隨機資料而有連續之零或是連續之一之情形產生，則電容上之電壓則會因漏電問題而產生改變，模擬結果如圖 4.20 所示，此圖為節點 N3 在  $V_{DD}=0.5V$ 、輸入信號為 500KHz 之時鐘信號之模擬結果，N3 為圖 4.19 中升降壓後之節點，理想上拔靴帶式電路會將電壓拉到兩倍  $V_{DD}$  與  $-V_{DD}$ ，然而因為內部寄生電容之緣故使得升降壓之效果約略只有理想上的 70%，從模擬結果上可以看見節點 N3 無法維持升降壓過後之電壓值，而是以 1ns 漏掉近 0.2mV 之速度在漏電，這些微電壓變化造成驅動後級電路之能力變動，也就代表上升時間與下降時間不同而造成信號抖動，因此使用此拔靴帶式電路無法操作在極低速之狀況，如果在輸入訊號為連續之零或是連續之一時也會有嚴重之信號抖

動產生。

## 4.6 完全屏蔽與 85%屏蔽之比較

由 4.4 節中圖 4.18 可知，隨著負載的增加 ISI 抖動的確是隨之上升，而圖 4.21 輸入信號一樣是 1Gbps 的隨機資料，不同的是兩旁有干擾線一樣是 1Gbps 隨機資料作為干擾源，並經過邊緣交錯機制處理，0%-85%之信號抖動隨著屏蔽增減而改變已於前面章節分析，而 85%-100%隨著屏蔽的增加信號抖動加劇根據我們之前的假設為負載增加致使 ISI 抖動愈發嚴重，然而與圖 4.18 相比信號抖動隨著屏蔽增加的量明顯大上許多。

我們先讓匯流排中一側的干擾源關閉以詳細觀察信號在匯流排中耦合後之情形，示意圖如圖 4.22 所示，波形圖如圖 4.23 與圖 4.24 所示：

圖 4.21 信號抖動隨屏蔽比例變動@1Gbps

圖 4.22 單側干擾源示意圖

圖 4.23 待測線之眼圖下降邊緣@85% 屏蔽

圖 4.24 待測線之眼圖下降邊緣@100% 屏蔽

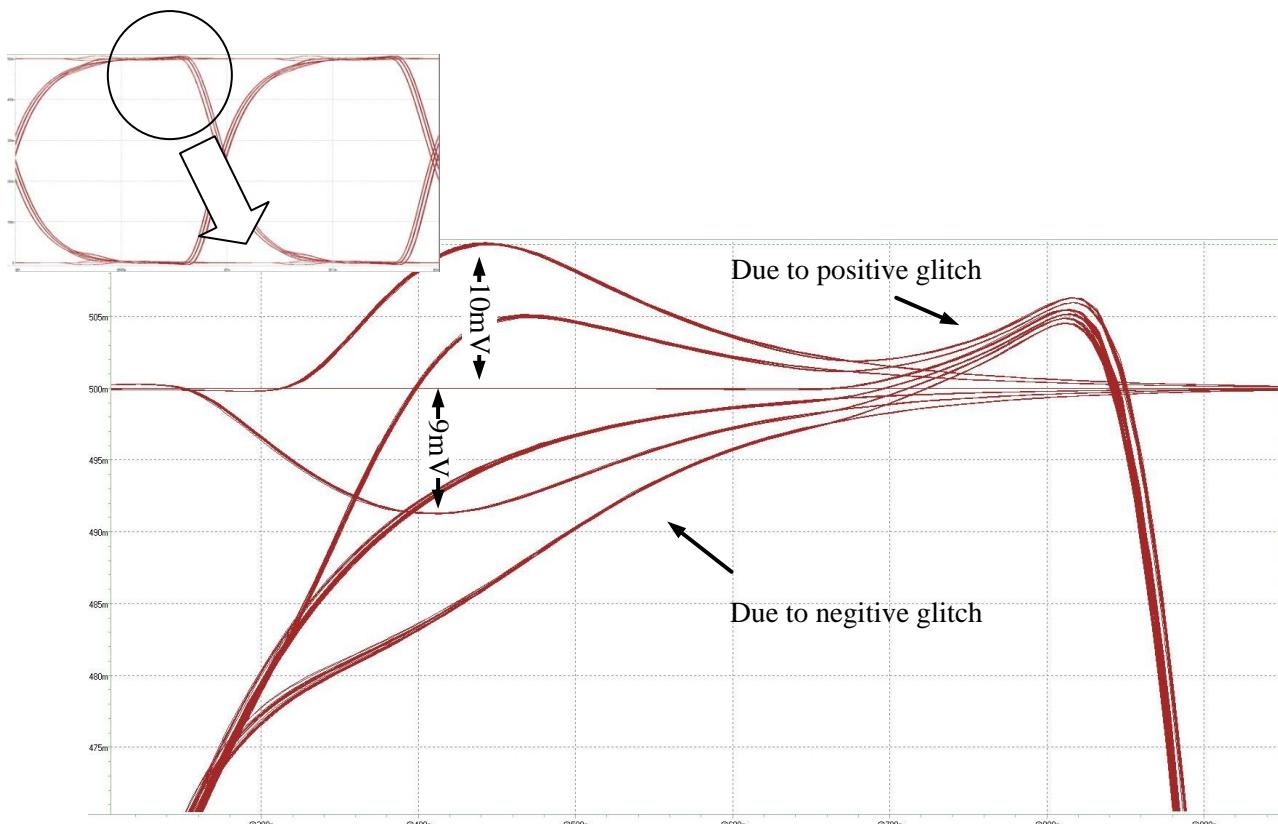

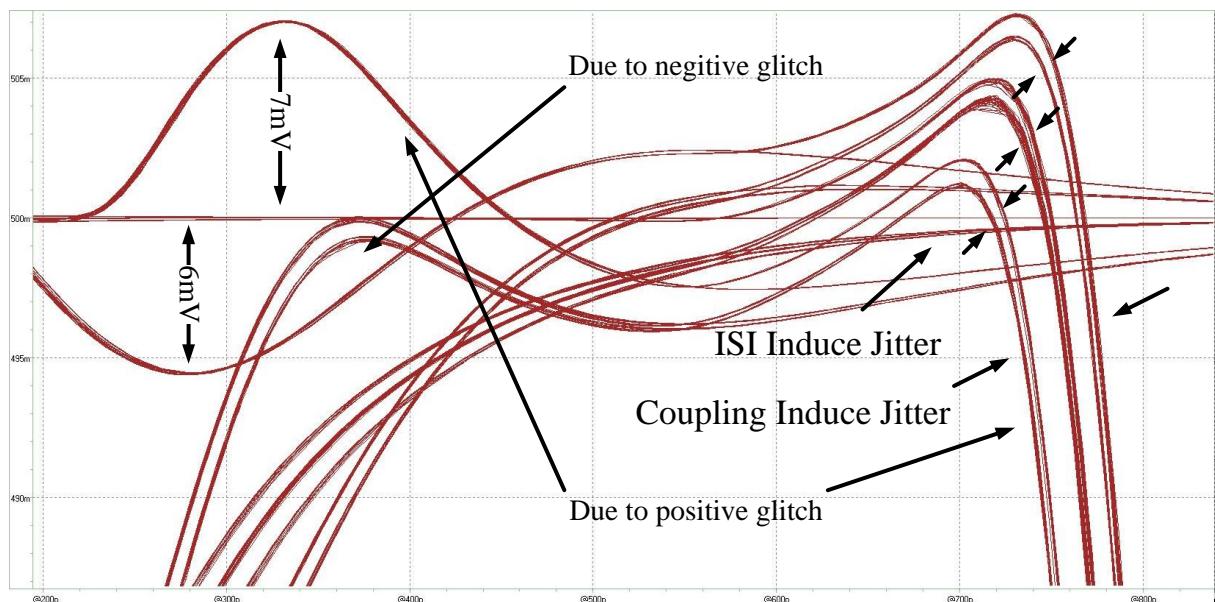

圖 4.23 為屏蔽比例 85% 只有單側干擾源之待測線上模擬結果，我們以下降邊緣為例，上升邊緣之情形與之相同。我們可以看到當臨邊之干擾源轉態時會在待測線上產生突波，如同在 4.2 節中之分析，當臨邊往上轉態使得待測線上產生正向突波，而此突波讓待測線之下降邊緣自較高之電位開始轉態，因此下降時間較長，而當臨邊為向下轉態而產生反向突波，讓待測線之下降邊緣自較低之位準開始轉態，因此下降時間較短，這兩者之差值即為突波造成的信號抖動。而當我們將屏蔽比例加到 100% 可以發現臨邊之轉態仍會產生耦合突波而影響待測線。如圖 4.24 所示，突波使得下降邊緣分成主要三條不同的下降時間，而 ISI 造成的抖動因為訊號為 110 與 010 的差異，又讓每條線分岔為二。雖然 ISI 抖動在 100% 屏蔽中較於 85% 屏蔽明顯大了許多，然而信號的抖動主要仍是耦合產生的突波所造成。

理想上，100% 的屏蔽是希望完全去除耦合效應造成的影響，然而比較圖 4.23 與 4.24 之後可以發現完全屏蔽和 85% 對於耦合突波之抑制效果差異並不大，最直接的理由為理想上將屏蔽線視為完全接地，因此耦合造成的影響無法穿越屏蔽線，但是實際上屏蔽線與信號線相同，都是一條細長導線只有尾端接地，因此有與信號線相同的線電阻與線電容，如圖 4.22 所示，所有耦合產生的影響仍要經過這些電阻電容才能排除，而在此同時有一部份的耦合信號就會透過屏蔽線與信號線間之耦合電容再耦合到信號線上。

仔細比較圖 4.23 與圖 4.24 可以發現，在圖 4.24 中正向突波讓下降邊緣在時間上往內縮減，而反向突波讓邊緣向外擴張。這與我們前面所述正向突波會拉長下降時間，反向突波會降低下降時間的結論，如圖 4.23 所示，恰恰相反，而要如何解釋這個現象可由圖 4.25 所示，當在完全屏蔽時干擾線產生一個上升邊緣，而此上升邊緣耦合到夾在干擾線與待測線上之屏蔽線上產生一正向突波，而此突波對於待測線來說可視為更為接

近的干擾源，我們將屏蔽線上之突波視為一個方波訊號，它的上升邊緣與下降邊緣皆分別對待測線耦合產生正向突波與反向突波，正向突波在影響到待測線之轉態邊緣前就已回到穩態電壓，然而反向突波則會在更接近待測線之轉態邊緣處產生影響，因此當干擾線為上升轉態產生正向突波而待測線向下轉態時，待測線之下降邊緣會向內縮減，若干擾線下降轉態產生反向突波則會讓待測線之下降邊緣向外擴張，如圖 4.24 中所示。若我們觀察眼圖之上升邊緣會有一樣的效應，只是方向相反。

圖 4.25 耦合效應在完全屏蔽下之穿透效果

我們藉由調整屏蔽比例來觀察這個現象，如圖 4.26 所示，可以發現屏蔽的增加讓耦合產生的突波峰值降低，然而如前面效應所述，在完全屏蔽上干擾線耦合造成的突波雖然較小，但殘存在半個週期後之電壓反而較大，而半個週期後就是轉態邊緣，因此殘存較大的電壓即造成較嚴重之信號抖動。總結來說殘留的正向電壓會讓減少上升時間，拉長下降時間，而反向電壓的殘留則會延長上升時間，降低下降時間。

在圖 4.26 中我們利用簡單的 1T 模型來掃描各個屏蔽比例下之干擾線上升在待測線上產生耦合突波與半個週期後殘存電壓之關係，每條線相差 10% 的屏蔽，我們可以發現在約略 70% 屏蔽時有最佳解讓殘存在半個週期後之電壓趨近於零，而當我們以較精準的 10T 模型進行 SPICE 模擬則在約略 85% 屏蔽處使殘存電壓趨近零，與前面預期 85% 屏蔽下有最小信號抖動之結果相符。

圖 4.26 正向耦合突波與屏蔽比例之關係

## 第五章

# 電路之實現

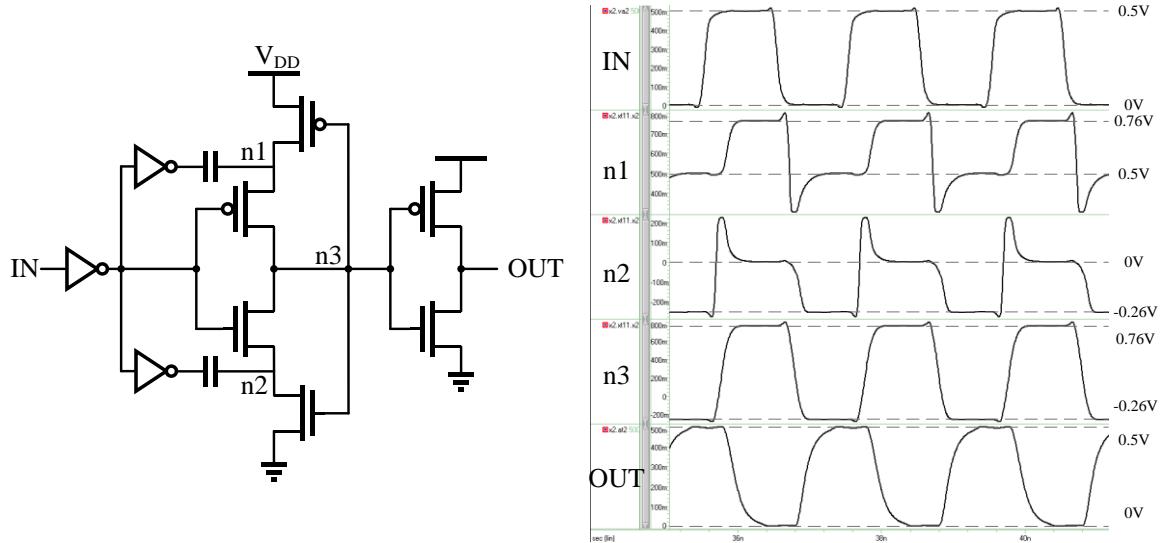

## 5.1 佈局架構簡介

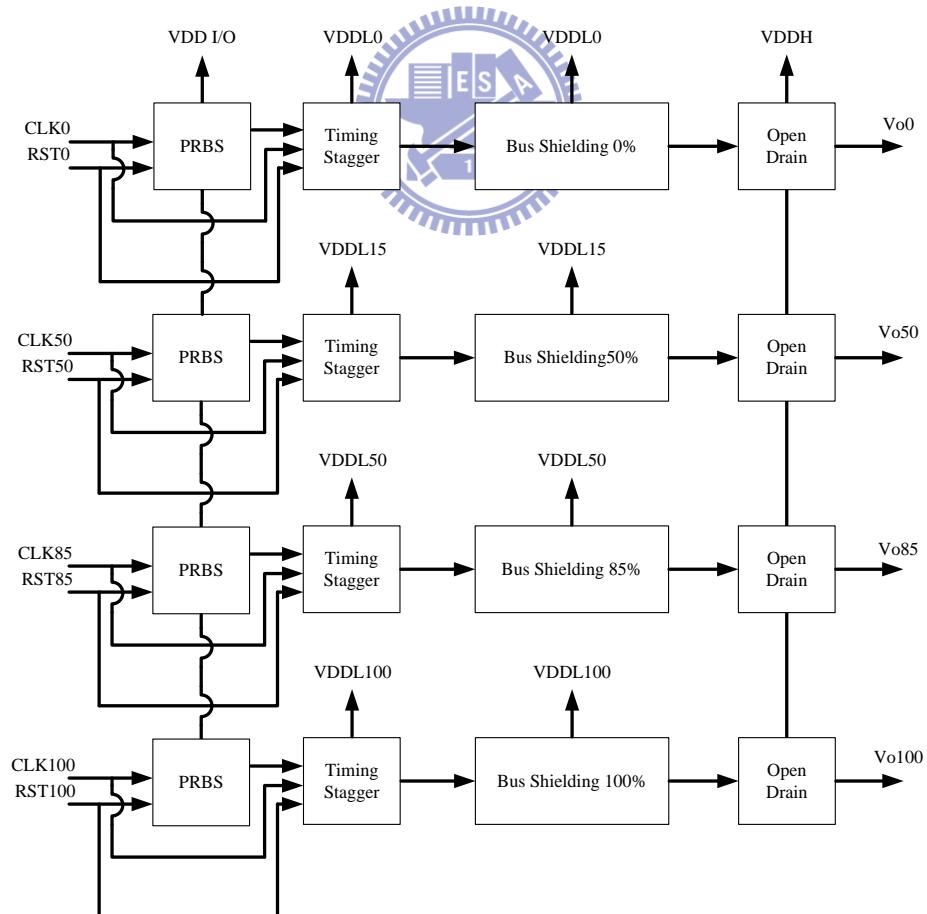

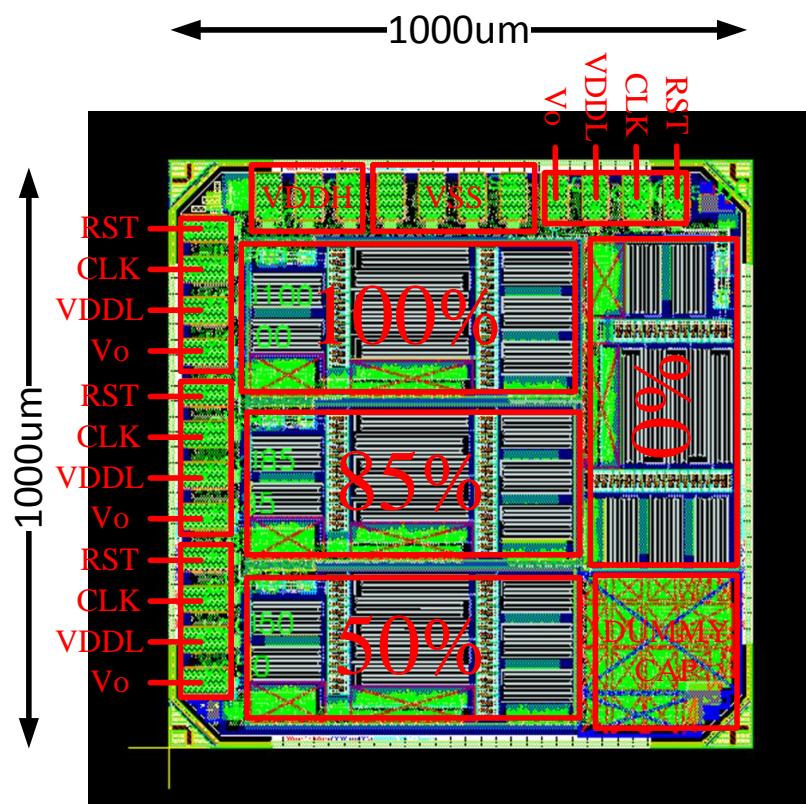

根據前面章節之模擬結果，我們挑選 0%、50%、85%、100% 四個屏蔽比例作為我們觀察不同屏蔽比例對於信號抖動抑制之測試電路，每個屏蔽比例各自獨立為一個區塊，擁有獨立的核心電壓，偽隨機信號產生器與輸入輸出埠。因為轉態時序之同步影響耦合效應甚巨，因此輸入匯流排中之一組待測信號與兩側之干擾信號無法由外部信號產生器輸入，而必須在每個屏蔽區塊建立獨自的偽隨機信號產生器以確保信號時序之同步。在偽隨機信號產生器之後為轉態邊緣交錯機制之電路，能將相鄰的信號彼此轉態邊緣相差  $180^\circ$  相位差。電壓分為兩組，一組為輸入/輸出埠所使用，另一組為匯流排電路之核心電壓，核心電壓每個區塊可以獨立調整，而輸入/輸出埠之電壓則使用一個埠。

圖 5.1 0%、50%、85%、100% 四個屏蔽比例作為測試電路

圖 5.2 測試電路之區塊圖

## 5.2 偽隨機信號產生器

若是進入匯流排中之信號彼此不同步，則之後要觀察匯流排中信號之耦合情形與控制轉態邊緣以降低信號抖動的機制皆無法正常運作，因此為了要追求信號同步，我們無法從晶片外部輸入信號，而必須在內部產生三組同步的隨機信號輸入匯流排中。

我們使用四位元的偽隨機信號產生器，如圖 5.3 所示，主要由四個 D 型正反器串連而成，將第四個與第一個正反器之輸出經互斥或閘輸入第一個正反器中，我們取第一個、第二個與第四個正反器之輸出加上緩衝器作為我們的三組同步的隨機信號，四個正反器中第一個正反器，圖 5.3 中灰色正反器，會重置到零而其餘正反器則重置到一，如此重置過後信號經由互斥或閘才會正常產生隨機信號。所產生之信號為 NRZ 信號，其資料速率等同於輸入之時鐘頻率，舉例來說當輸入 1000MHz 之時鐘信號，則所產生之隨機信號其資料速率為 1000Mbps。

圖 5.3 四位元偽隨機信號產生器

## 5.3 轉態邊緣交錯機制

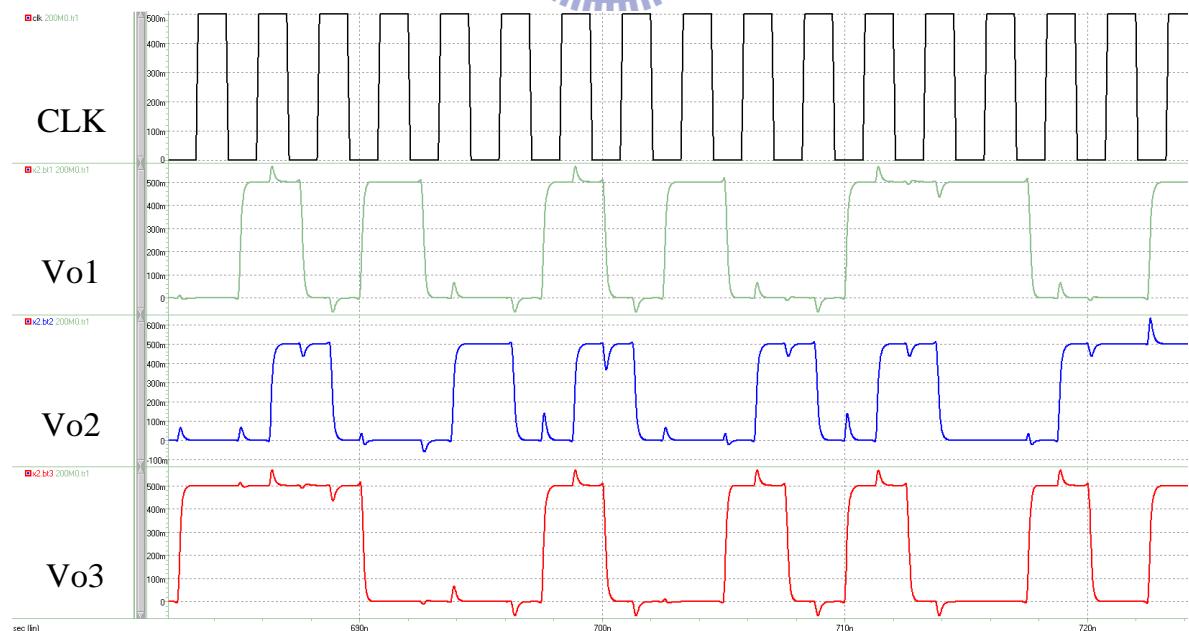

此機制之運作方式詳述於 4.2 節中，在匯流排前方交錯置入正緣觸發與負緣觸發之 D 型正反器，在輸入為 NRZ 資料時所需之時鐘信號等同於輸入信號之資料速率，舉例來說當輸入信號為 1000Mbps，則所需之時鐘信號為 1000MHz。而我們前面經由偽隨機信號產生器產生的輸入信號，其所需之時鐘頻率與其產生的輸出信號之資料速率是相同的，因此要產生 1000Mbps 的信號需要 1000MHz 之時鐘信號，我們可以發現產生隨機信號與轉態交錯機制所需之時鐘頻率相同，因此我們得以使用同一組時鐘信號來產生隨機資料並驅動轉態交錯機制。

其運作波形如圖 5.4 所示，此圖之輸入信號為 200Mbps。經由轉態邊緣交錯機制處理後，我們可以看到相鄰線轉態產生的耦合突波在離轉態邊緣半個週期後出現，有最長的時間讓突波回到穩態電壓，理想上能去除耦合造成的信號抖動。

圖 5.4 轉態邊緣交錯機制處理後之波形圖

## 5.4 汇流排電路

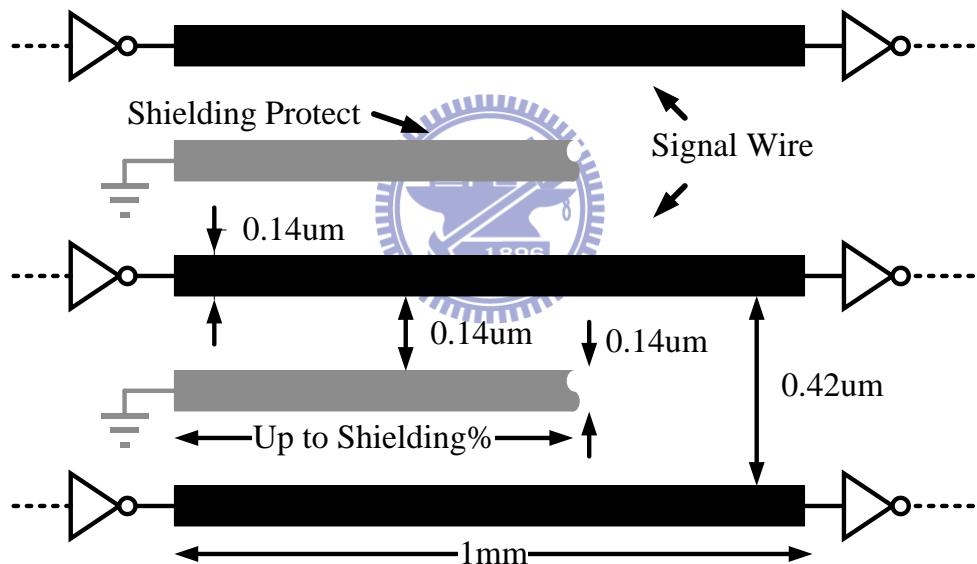

我們有四組匯流排分別加上 0%、50%、85% 與 100% 四種屏蔽比例作為我們的測式電路，我們以三條連接線作為一組匯流排，每條連接線總長為 10mm，將其用中繼器均分成 10 段，每段 1mm。屏蔽線由每段之中繼器起始並與中繼器共地，信號線與屏蔽線皆為最小寬度 0.14um，而信號線與屏蔽線之間距為 0.14um，信號線到信號線之間距則為 0.42um。

示意圖如圖 5.5 所示，黑線為信號線，灰線為屏蔽線：

圖 5.5 汇流排中由中繼器間隔之 1mm 示意圖

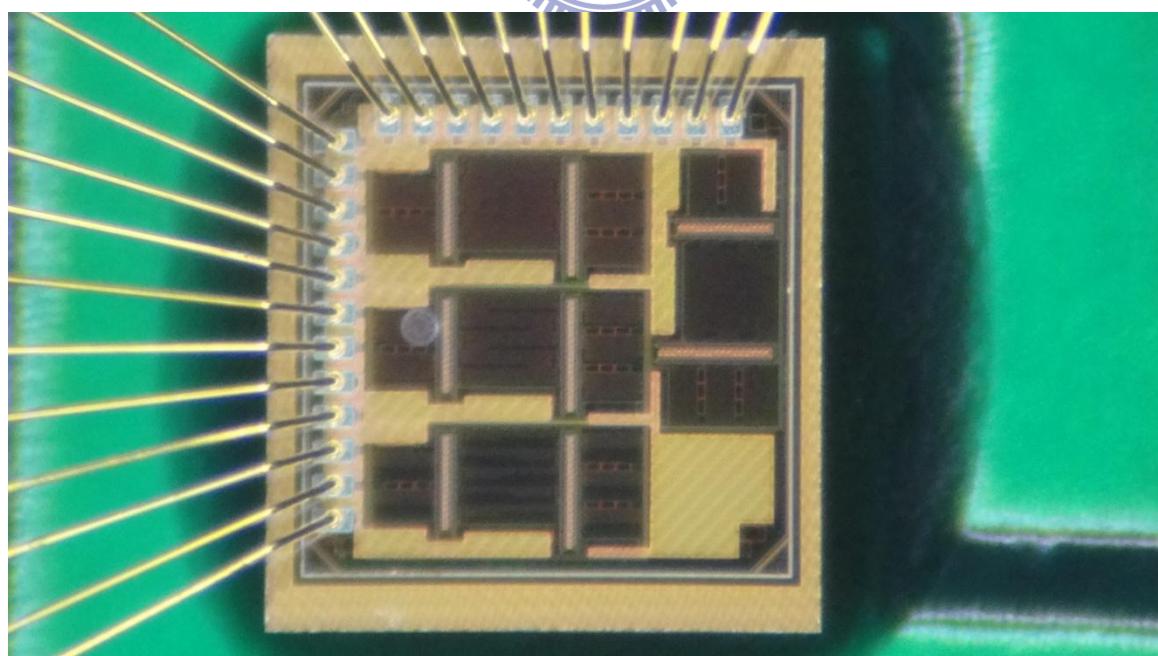

## 5.5 晶片佈局

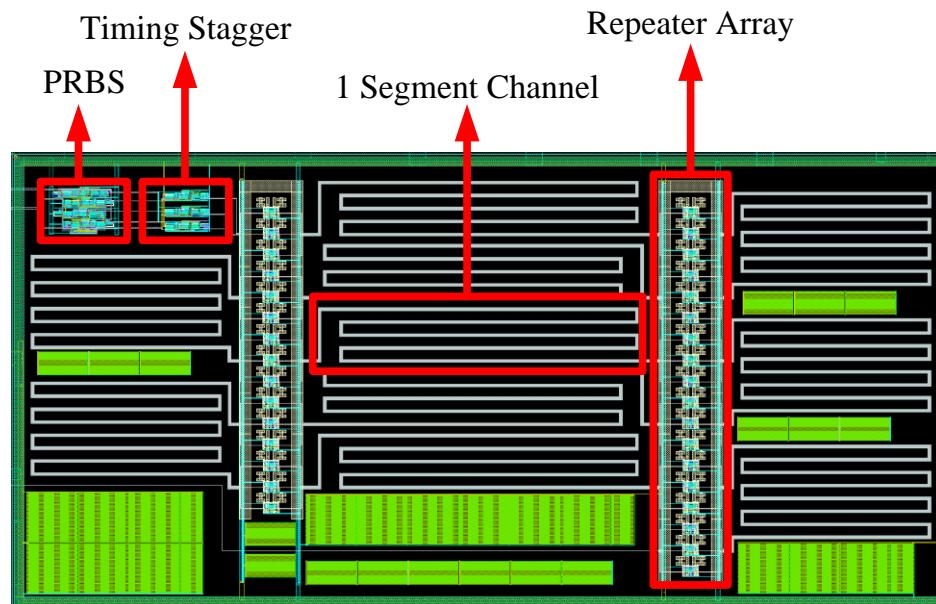

本晶片使用 TSMC MSG90 製程，面積為  $1\text{mm}^2$ ，內部分為四個主要區塊分別為四組不同屏蔽比例之匯流排電路，右下角則加入去耦合電容(Decoupled Capacitor)以降低電源雜訊之影響。在匯流排區塊中包含偽隨機信號產生器(PRBS)、轉態時機交錯機制(Timing Stagger)與 10 段 1mm 總長 1cm 之匯流排電路。

圖 5.6 晶片佈局圖

圖 5.7 匯流排區塊佈局

On-chip Bus X4

| Pin Name | RST | CLK | V <sub>DDL</sub> | V <sub>O</sub> |

|----------|-----|-----|------------------|----------------|

| Pads     | 1   | 1   | 1                | 1              |

| I/O      |                  |                 |

|----------|------------------|-----------------|

| Pin Name | V <sub>DDH</sub> | V <sub>SS</sub> |

| Pads     | 3                | 4               |

表 5.1 PAD 分配表

## 5.6 模擬結果

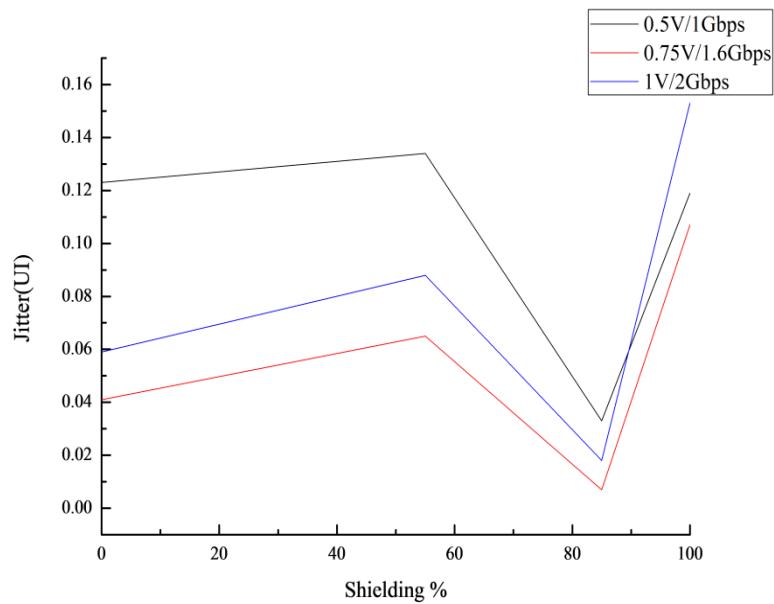

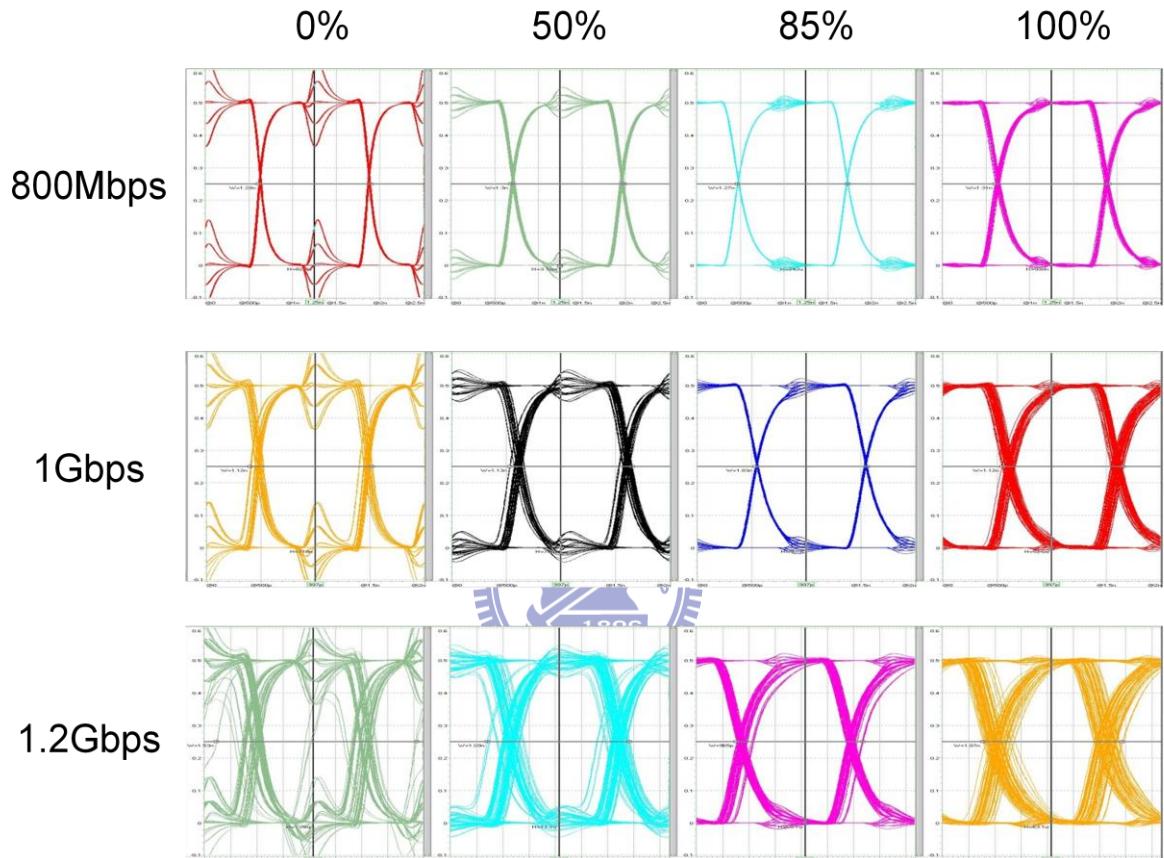

不同屏蔽比例之匯流排操作在工作電壓 0.5V，環境溫度 25°C，TT corner 下，800Mbps~1.2Gbps 之模擬結果如圖 5.8 所示：

圖 5.8 匯流排電路之眼圖(0.5V、25°C、TT)

如圖所示，在較低速的情況下干擾線造成的耦合突波會出現在接近單位間隔(UI)中間，讓耦合效應對於信號抖動之影響降低，隨著屏蔽比例的上升 ISI 影響上升。而當速度上升之後可以發現耦合造成的突波開始影響信號的轉態邊緣造成信號抖動，由 0% 與 50% 屏蔽可以明顯看出此現象。85% 獲得較佳的抑制效果而信號抖動較小，而在完全屏蔽後信號的抖動同 4.5 節中之分析，較在 85% 屏蔽中嚴重。

Post-simulation 與 Pre-simulation 之比較如表 5.2 所示，在 Post-simulation 上因為匯流排之走線為”之”字形排繞，多了許多耦合路徑並增加了額外的電阻與電容負載，因此信號抖動較 Pre-simulation 嚴重。我們可以看到 Post-simulation 之結果在匯流排完全沒有屏蔽下不論是在哪個速度信號都無法輸出，完全屏蔽的狀況下在速度超過 1.2Gbps 後信號無法輸出，而不論在哪種速度下在 85% 的屏蔽比例下都有最小的信號抖動。Post-simulation 較 Pre-simulation 與理論不符的部分在於，在 1Gbps 的速度下理論上 50% 屏蔽所受到的耦合影響較完全沒有屏蔽的匯流排大，然而在 Post-simulation 上完全沒有屏蔽的匯流排卻讓信號難以輸出，50% 的屏蔽對於匯流排有較佳的保護效果這是與前述推論相違之處。原因應是多出的負載讓上升下降時間延長，使得轉態邊緣吃到更多的突波電壓，因而造成更嚴重的信號抖動。

| 800Mbps  | 0%      | 50%     | 85%     | 100%    |

|----------|---------|---------|---------|---------|

| Post-Sim | Fail    | 0.056UI | 0.078UI | 0.072UI |

| Pre-Sim  | 0.028UI | 0.042UI | 0.017UI | 0.049UI |

| 1Gbps    | 0%      | 50%     | 85%    | 100%   |

|----------|---------|---------|--------|--------|

| Post-Sim | Fail    | 0.17UI  | 0.1UI  | 0.12UI |

| Pre-Sim  | 0.123UI | 0.134UI | 0.03UI | 0.12UI |

| 1.2Gbps  | 0%   | 50%     | 85%     | 100%    |

|----------|------|---------|---------|---------|

| Post-Sim | Fail | Fail    | 0.219UI | Fail    |

| Pre-Sim  | Fail | 0.331UI | 0.158UI | 0.282UI |

表 5.2 TT corner 下 Post-simulation 與 Pre-simulation 比較表

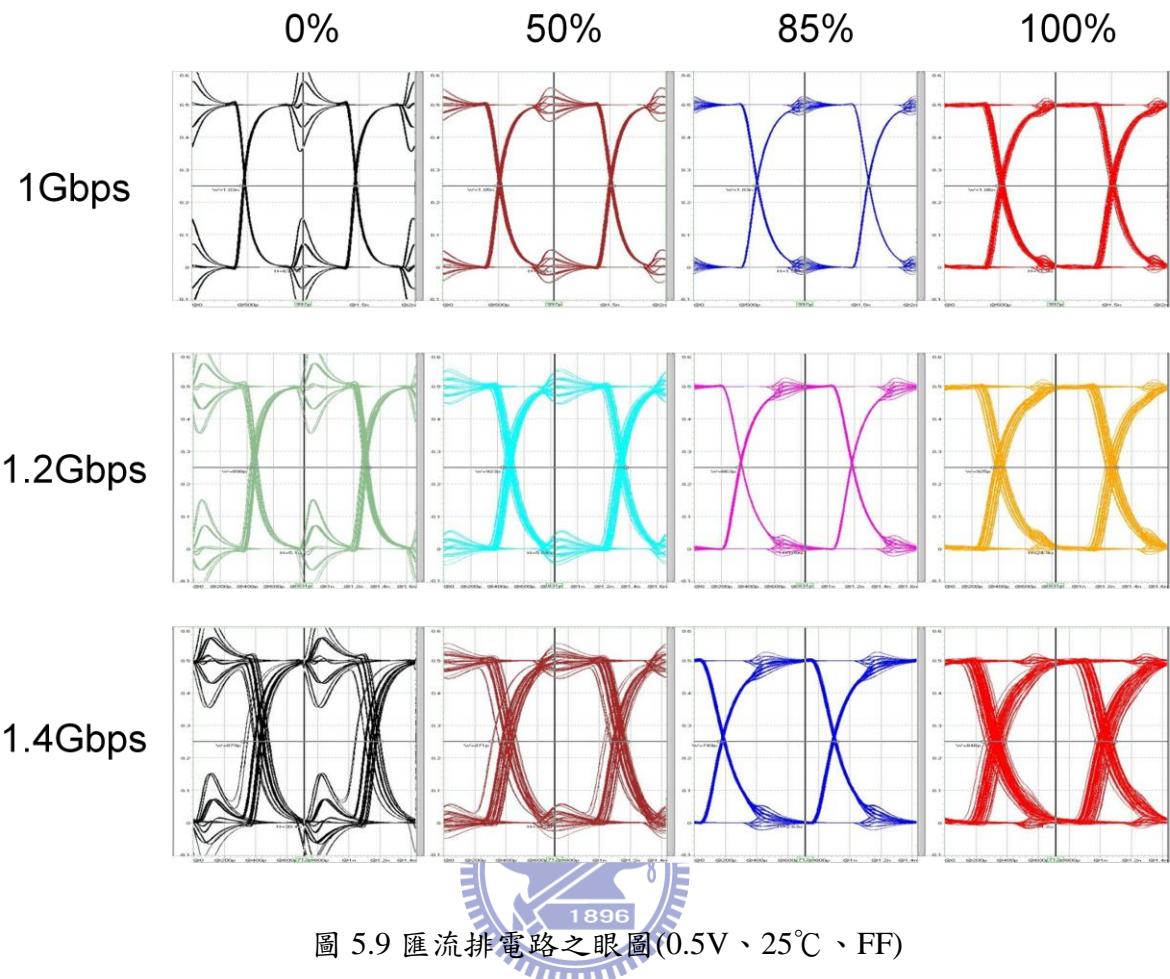

而在 FF corner，環境溫度  $25^{\circ}\text{C}$  的狀況下，模擬結果如圖 5.9 所示，眼圖之資訊列於表 5.3 中。較於 TT corner，在 FF corner 同速度下之信號的抖動較小，Pre-simulation 上之趨勢與 TT corner 相同，與我們的推論相符，皆是在 85% 屏蔽下有最佳的信號保護效果，起伏的趨勢大致是沒有屏蔽的信號抖動小於 50% 屏蔽，之後在 85% 的屏蔽有最低的信號抖動，而 100% 的屏蔽又讓信號抖動的量上升。在 Post-simulation 上，除了信號在 1Gbps 因驅動能力較強使得上升下降時間較短而不易讓突波影響到轉態邊緣，因而讓信號抖動與屏蔽比例較無關，當信號的操作速率越快則愈符合我們期待的效應，在 1.2Gbps 與 1.4Gbps 的操作速度上，在 85% 的屏蔽上皆有最小的信號抖動。

| 1Gb/s           | 0%      | 50%     | 85%     | 100%    |

|-----------------|---------|---------|---------|---------|

| <b>Post-Sim</b> | 0.152UI | 0.127UI | 0.151UI | 0.141UI |

| <b>Pre-Sim</b>  | 0.034UI | 0.045UI | 0.025UI | 0.991UI |

| 1.2Gb/s         | 0%      | 50%     | 85%     | 100%    |

|-----------------|---------|---------|---------|---------|

| <b>Post-Sim</b> | Fail    | 0.226UI | 0.198UI | 0.198UI |

| <b>Pre-Sim</b>  | 0.077UI | 0.107UI | 0.032UI | 0.110UI |

| 1.4Gbps  | 0%      | 50%     | 85%     | 100%    |

|----------|---------|---------|---------|---------|

| Post-Sim | Fail    | 0.487UI | 0.256UI | 0.321UI |

| Pre-Sim  | 0.227UI | 0.217UI | 0.046UI | 0.184UI |

表 5.3 FF corner 下 Post-simulation 與 Pre-simulation 比較表

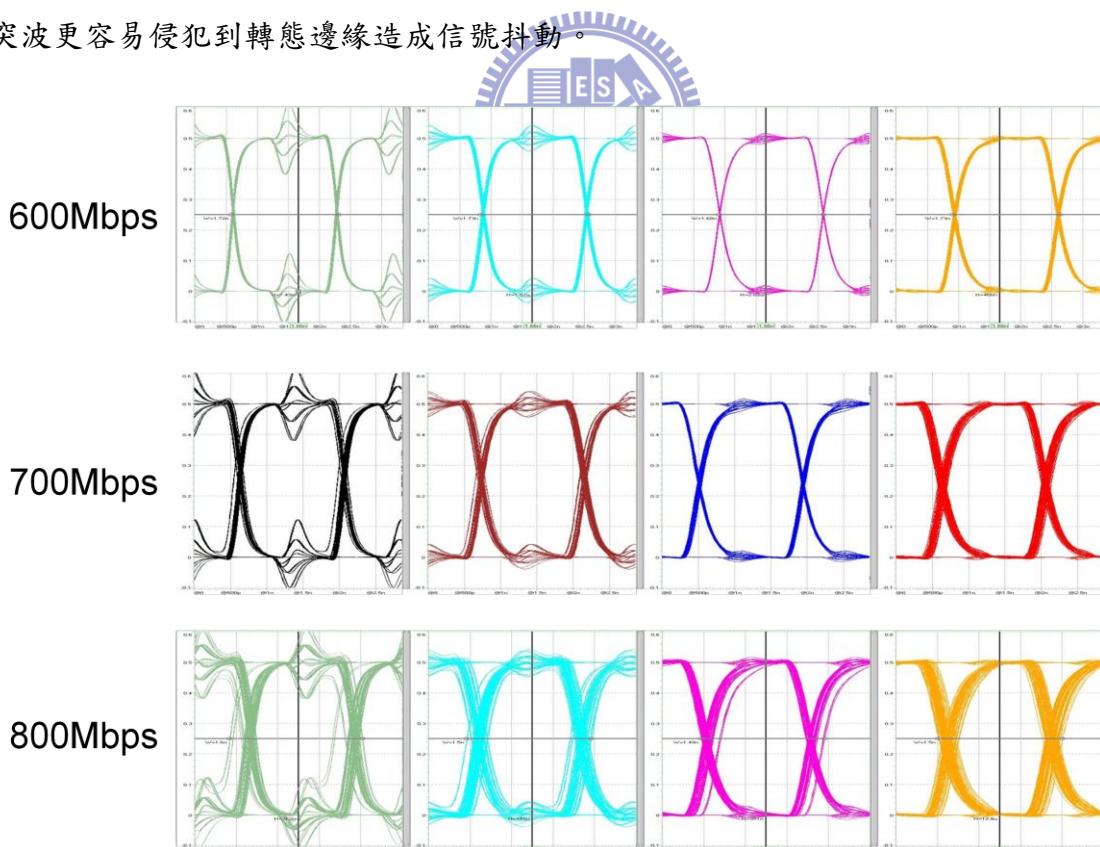

而在 FF corner 中之模擬結果與波形如圖 5.10 與表 5.4 所示。SS corner 驅動能力較弱因此操作速度較慢，而相同速度下之信號抖動較 TT corner 與 FF corner 要大上許多，原因在於在單位間隔中較緩慢的上升與下降時間占了更多比例，因此耦合產生所產生的突波更容易侵犯到轉態邊緣造成信號抖動。

圖 5.10 匯流排電路之眼圖(0.5V、25°C、SS)

在 Post-simulation 上，與我們所預期的結果大致相符，在 85% 的屏蔽下有最小的信號抖動，當速度上升則因能讓耦合突波回歸穩態電壓之時間變短，也就代表有更多的突波電壓殘留在轉態邊緣上，因而效果越明顯。

| <b>600Mbps</b>  | <b>0%</b> | <b>50%</b> | <b>85%</b> | <b>100%</b> |

|-----------------|-----------|------------|------------|-------------|

| <b>Post-Sim</b> | Fail      | 0.227UI    | 0.153UI    | 0.198UI     |

| <b>Pre-Sim</b>  | 0.033UI   | 0.040UI    | 0.010UI    | 0.037UI     |

| <b>700Mbps</b>  | <b>0%</b> | <b>50%</b> | <b>85%</b> | <b>100%</b> |

|-----------------|-----------|------------|------------|-------------|

| <b>Post-Sim</b> | Fail      | 0.583UI    | 0.234UI    | 0.256UI     |

| <b>Pre-Sim</b>  | 0.105UI   | 0.086UI    | 0.049UI    | 0.108UI     |

| <b>800Mbps</b>  | <b>0%</b> | <b>50%</b> | <b>85%</b> | <b>100%</b> |

|-----------------|-----------|------------|------------|-------------|

| <b>Post-Sim</b> | Fail      | Fail       | 0.408UI    | Fail        |

| <b>Pre-Sim</b>  | 0.283UI   | 0.203UI    | 0.181UI    | 0.198UI     |

表 5.4 SS corner 下 Post-simulation 與 Pre-simulation 比較表

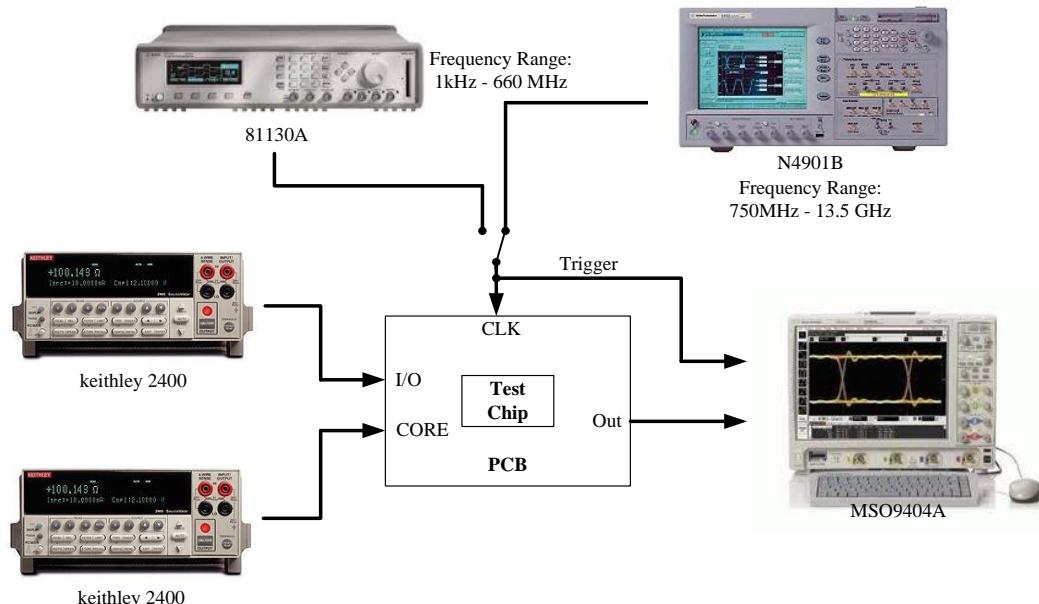

## 5.7 量測環境設定

我們以兩台 Keithley2400 分別提供 I/O 電壓與匯流排之 CORE 電壓並量測其功率消耗，Agilent 81130A 提供 200MHz~600MHz 時鐘訊號，Agilent N4901B 提供 800MHz ~2.6GHz 時鐘訊號，並以 Agilent MSO9404A 觀察輸出波形並量測信號抖動。

我們本來設定之操作環境為  $V_{CORE}=0.5V$ 、 $V_{I/O}=0.7V$  輸出 1Gbps 的信號，但是使用 Agilent N4901B 能提供之最低時鐘頻率為 800MHz，在此速度下若 I/O 之電壓維持在 0.7V 則前端之偽隨機信號產生器將無法正常重置因而無法輸出，又因為 I/O 與匯流排並沒有使用電壓位準移位電路(Level Shift)銜接因此電壓差不能太大。實際量測後，為了讓電路接上 Agilent N4901B 能正常運作，我們將  $V_{I/O}$  電壓提升至 1V， $V_{CORE}$  也提升至 1V，因為操作電壓為預設之兩倍，匯流排之操作速度也突破 2Gbps.

圖 5.11 量測儀器設置圖

圖 5.13 晶片打線圖

## 5.8 量測結果

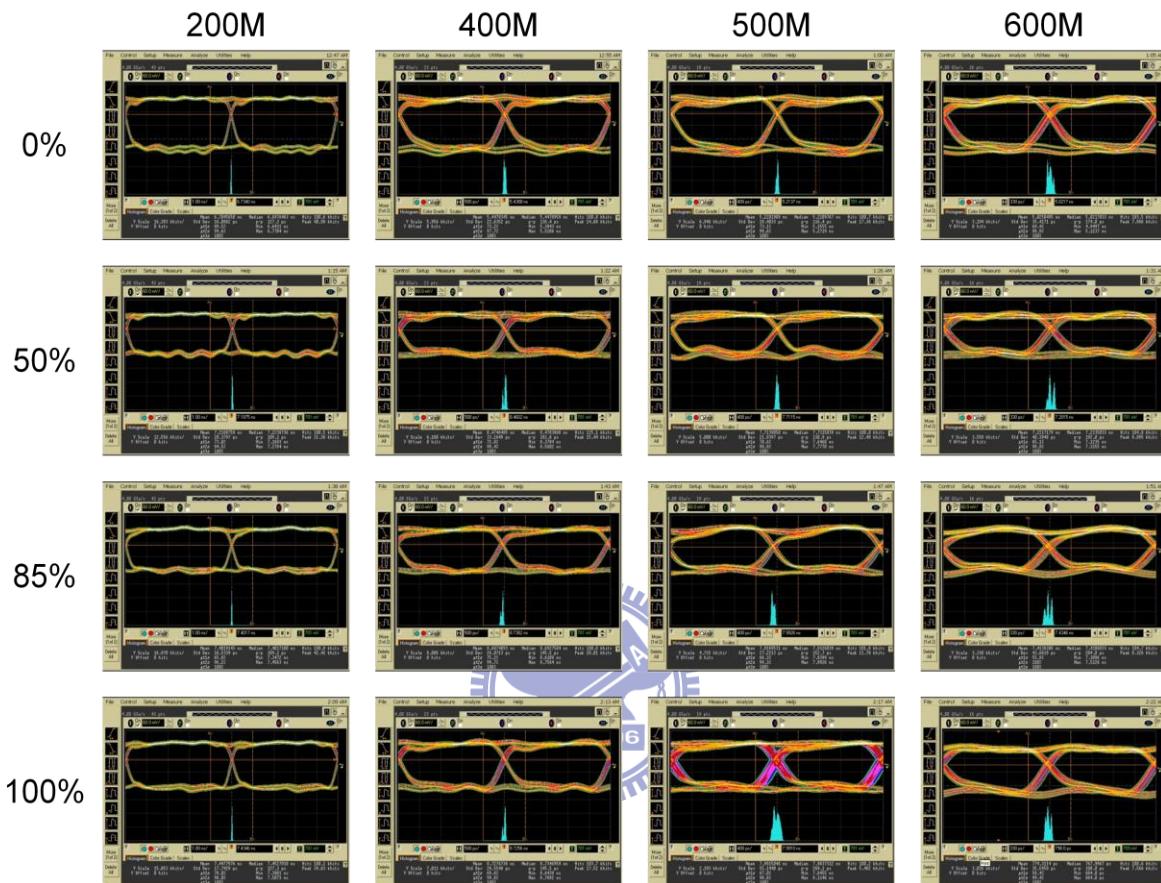

在不同屏蔽比例下，當  $V_{CORE}=1V$ 、 $V_{I/O}=0.56V$  量測結果如下：

圖 5.14  $V_{CORE}=1V$ 、 $V_{I/O}=0.56V$  不同屏蔽下之眼圖

| Shielding% | 200Mbps | 400Mbps | 500Mbps | 600Mbps |

|------------|---------|---------|---------|---------|

| 0%         | 127.3ps | 136.4ps | 116.4ps | 174ps   |

|            | 0.025UI | 0.055UI | 0.058UI | 0.104UI |

| 50%        | 109.1ps | 181.8ps | 130.9ps | 192ps   |

|            | 0.022UI | 0.072UI | 0.065UI | 0.115UI |

| 85%        | 109.1ps | 145.5ps | 152ps   | 204ps   |

|            | 0.022UI | 0.058UI | 0.076UI | 0.122UI |

| 100%       | 127.3ps | 145.5ps | 269.1ps | 180ps   |

|            | 0.025UI | 0.058UI | 0.135UI | 0.108UI |

表 5.5  $V_{CORE}=1V$ 、 $V_{I/O}=0.56V$  不同屏蔽下之信號抖動

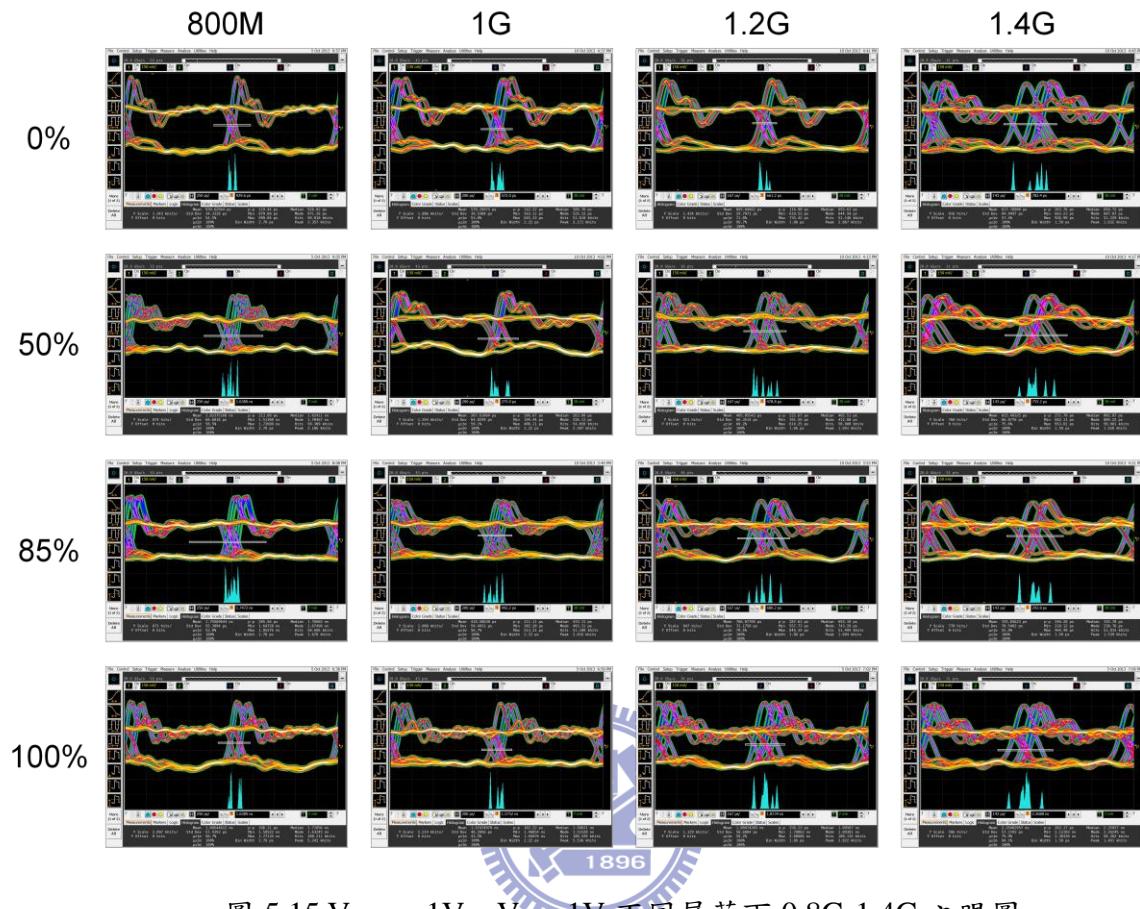

在不同屏蔽比例下，當  $V_{CORE}=1V$ 、 $V_{I/O}=1V$  量測結果如下：

圖 5.15  $V_{CORE}=1V$ 、 $V_{I/O}=1V$  不同屏蔽下 0.8G-1.4G 之眼圖

| Shielding% | 800Mbps | 1Gbps   | 1.2Gbps | 1.4Gbps |

|------------|---------|---------|---------|---------|

| 0%         | 119.4ps | 142.2ps | 116.9ps | 263.8ps |

|            | 0.096UI | 0.142UI | 0.14UI  | 0.369UI |

| 50%        | 213.9ps | 206.7ps | 222.7ps | 271.7ps |

|            | 0.171UI | 0.207UI | 0.267UI | 0.38UI  |

| 85%        | 205.6ps | 211.1ps | 287.6ps | 247.2ps |

|            | 0.164UI | 0.211UI | 0.345UI | 0.346UI |

| 100%       | 186.1ps | 162.2ps | 228.2ps | 262.2ps |

|            | 0.149UI | 0.162UI | 0.274UI | 0.367UI |

表 5.6  $V_{CORE}=1V$ 、 $V_{I/O}=1V$  不同屏蔽下 0.8G-1.4G 之信號抖動

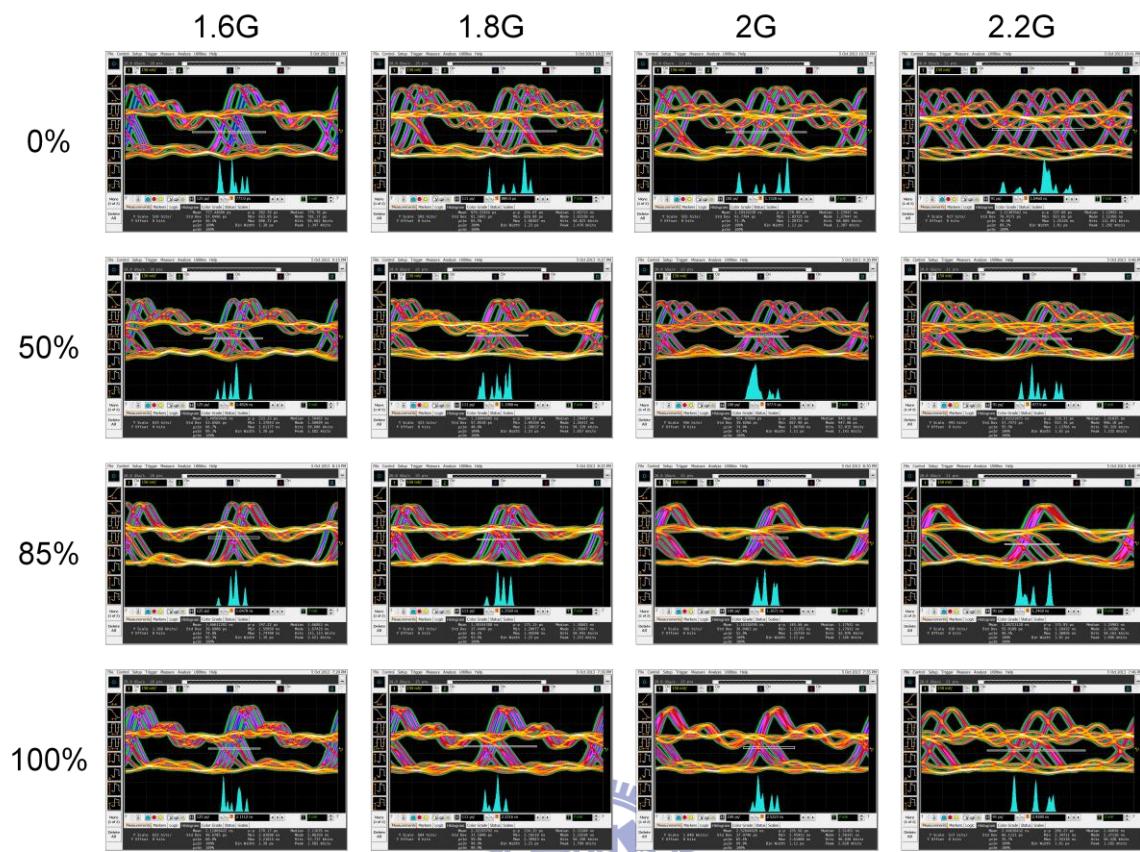

圖 5.16  $V_{CORE}=1V$ 、 $V_{I/O}=1V$  不同屏蔽下 1.6G-2.2G 之眼圖

| Shielding% | 1.6Gbps | 1.8Gbps | 2Gbps   | 2.2Gbps |

|------------|---------|---------|---------|---------|

| 0%         | 202.8ps | 254.1ps | 270ps   | 327.6ps |

|            | 0.324UI | 0.457UI | 0.54UI  | 0.721UI |

| 50%        | 233.3ps | 194.9ps | 180ps   | 210.3ps |

|            | 0.373UI | 0.351UI | 0.36UI  | 0.463UI |

| 85%        | 197.2ps | 175.1ps | 145.6ps | 175.9ps |

|            | 0.316UI | 0.315UI | 0.291UI | 0.387UI |

| 100%       | 179.2ps | 234.3ps | 155.6ps | 206.3ps |

|            | 0.287UI | 0.422UI | 0.311UI | 0.454UI |

表 5.7  $V_{CORE}=1V$ 、 $V_{I/O}=1V$  不同屏蔽下 1.6G-2.2G 之信號抖動

我們可以發現當  $V_{CORE}$  操作在 1V 時，匯流排得以傳輸超過 2Gbps 之信號，在  $V_{I/O}$  為 0.56V 並以較低之資料速率運作時，可以從圖 5.14 看見非常清晰的眼圖，輸出信號幾乎不受到 ISI 效應與耦合效應之影響。而當我們欲將速度提升至匯流排臨界時，為了讓偽隨機信號產生器也能在高速下正常運作需將  $V_{I/O}$  提升至 1V，然而因此在輸出端造成過大的電流而產生嚴重的過衝現象(overshoot)與振鈴(Ringing)，因為在製作印刷電路板時沒有考量到此問題因而沒有將輸入與輸出埠之電壓分開，若將兩埠分開則可讓輸入埠接上高電壓以利偽隨機信號產生器運作在高速環境，而輸出埠則可以較低電壓驅動以避免過大的電流造成過衝與振鈴。我們在各個屏蔽比例下皆可以發現上述現象，而隨著資料速率的提升可以發現耦合突波影響信號轉態邊緣造成信號抖動之效應隨之加劇，在接近臨界速度時，85% 屏蔽有最佳之抖動抑制如同我們之前所預期，而當資料速率到達 2.4Gbps 時，也僅有 85% 屏蔽得以傳送正確資料。

圖 5.17 臨界資料速率下不同屏蔽比例之信號抖動

## 規格與比較

表 5.8 為此晶片之模擬與量測規格表，由  $V_{CORE}$  提供電源的電路有匯流排與前級轉態邊緣交錯機制兩塊，從表中可知兩塊電路之功率消耗比例為 1:2，匯流排占 1/3 而轉態邊緣交錯機制占 2/3。功率消耗上大致符合  $fcv^2$  之規則，如在 Post-Simulation 中操作速度下降 40%，功率消耗也下降 40%，在量測中電壓變為 2 倍，操作速度變為 3.33 倍則 理論上功率消耗為 13.32 倍，量測上功率自 459uW 變為 5.38mW 約為 12 倍，大致符合我們的預期。

|                     | Postsim  |                   |                   | measurement       |                   |

|---------------------|----------|-------------------|-------------------|-------------------|-------------------|

|                     | Bus Only | With Time-Stagger | With Time-Stagger | With Time-Stagger | With Time-Stagger |

| $V_{DD}$            | 0.5V     | 0.5V              | 0.5V              | 0.5V              | 1V                |

| <b>Data Rate</b>    | 1Gbs     | 1Gbps             | 0.6Gbps           | 0.6Gbps           | 2Gbps             |

| <b>Space</b>        | 0.14um   | 0.14um            | 0.14um            | 0.14um            | 0.14im            |

| <b>Total Length</b> | 10mm     | 10mm              | 10mm              | 10mm              | 10mm              |

| <b>Jitter</b>       | 0.2UI    | 0.2UI             | 0.13UI            | 0.27UI            | 0.29mm            |

| <b>Power</b>        | 253uW    | 754uW             | 461uW             | 459uW             | 5.38mW            |

表 5.8 規格表

而與其他文獻之比較表如表 5.9 所示，在 180nm 製程下最小線間距為 0.28um 而在 90nm 製程中最小間距為 0.14um，我們使用最小間距相較於其他文獻使用 2 倍、4 倍或 5 倍之線間距有面積上的優勢。而在 pJ/bit 比較上，模擬結果僅次於使用相同 BT Repeater 架構，因為此架構在低於電晶體臨界電壓下能將驅動中繼器之電壓提升至臨界電壓以上，因此越低壓的環境越能突顯優勢，而在量測上因為儀器之限制無法在預期中  $V_{DD}=0.5V$  操作速度 1Gbps 之環境下操作，因此在將電壓提升至 1V 後雖然操作速度亦變為兩倍，然而在節省功率消耗上就不如預期之結果。

|                | TCAS1 08 [25]   | JSSC 10 [26]   | JSSC 12 [6]     | Proposed          |                   |

|----------------|-----------------|----------------|-----------------|-------------------|-------------------|

|                |                 |                |                 | Simulation        | Measurement       |

| Technology     | 180nm           | 90nm           | 55nm            | 90nm              | 90nm              |

| Topology       | INV Repeater    | Cap Coupling   | BT Repeater     | BT Repeater       | BT Repeater       |

| Shielding      | Fully Shielding | Single Channel | Fully Shielding | Partial Shielding | Partial Shielding |

| Supply Voltage | 1V              | 1.2V           | 0.3V            | 0.5V              | 1V                |

| Total Length   | 10mm            | 10mm           | 10mm            | 10mm              | 10mm              |

| Spacing        | 1.5um           | 2X0.3um        | 0.09um          | 0.14um            | 0.14um            |

| Data Rate      | 1.5Gbps         | 2Gbps          | 0.1Gbps         | 1Gbps             | 2Gbps             |

| pJ/bit         | 1.74            | 0.28           | 0.123           | 0.249             | 0.896             |

表 5.9 比較表

## 第六章

### 結論

隨著製程的演進，晶片內匯流排不論是在速度、功耗與面積上都逐漸成為晶片設計上的瓶頸，本論文之目標為使用最小線間距以降低匯流排之面積，使用拔靴帶式電路作為中繼器以降低操作電壓達到低功耗又能維持操作速度。使用最小線間距能大幅降低匯流排所占之面積，然而會受到嚴重的耦合效應影響產生大量信號抖動，若使用完全屏蔽線將信號線彼此隔絕又有嚴重的負載問題，因而我們使用轉態邊緣交錯機制讓耦合所造成的抖動與其他信號抖動源如 ISI 分開來，再以部分屏蔽加以保護。根據我們文中之分析，在 90nm 製程中使用最小線距並操作在 0.5V、1Gbps 的狀態下，在 85% 屏蔽有最佳之信號抖動抑制。於論文中我們將各個效應模組化，因此在不同的環境下只要將製程參數與操作條件帶入我們的模型中即能推算出最佳之屏蔽比例，達到信號抖動與功耗之平衡點。

在不考慮其他雜訊源的情形下只看耦合與 ISI 效應之影響，在匯流排操作速度瀕臨極限時能藉由調整到最佳屏蔽比例達到此匯流排所能傳送之最快資料速率，然而反過來說，屏蔽比例的調整也只有在高速端的應用才得以顯現其優勢，若速度不夠快讓耦合效應不會干擾到信號轉態，則屏蔽的增加只是徒增負載，造成多餘的功率消耗。且若加入其他雜訊源在  $V_{DD}$ 、地線或是屏蔽線上[24]都有可能主導信號抖動而讓調整屏蔽比例的效果無法呈現，本文僅針對耦合與 ISI 效應討論而找到適合的屏蔽比例，於實際應用上需要加上更多雜訊模型才足以在晶片內匯流排上應用。

## 參考文獻

- [1] M. L. Mui, K. Banerjee and A. Mehrotra, "A Global Interconnect Optimization Scheme for Nanometer Scale VLSI with Implications for Latency, Bandwidth, and Power Dissipation," *IEEE Trans. Electron Devices*, vol. 51, no. 2, pp. 195-203, Feb. 2004.

- [2] M. Tang and M. J. Fa, "Optimization of Global Interconnects in High Performance VLSI Circuits," *Proc. 19th Int. Conf. on VLSI Design 2006*, pp. 6, Jan. 2006.

- [3] L. X. Chun, and et al., "Global Interconnect Width and Spacing Optimization for Latency, Bandwidth and Power Dissipation," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2272-2279, Oct. 2005.

- [4] K. Banerjee and A. Mehrotra, "A Power-Optimal Repeater Insertion Methodology for Global Interconnects in Nanometer Designs," *IEEE Trans. Electron Devices*, vol. 49, no. 11, pp. 2001-2007, Nov. 2002.

- [5] V. V. Deodhar and J. A. Davis, "Optimization of Throughput Performance for Low-Power VLSI Interconnects," *IEEE Trans. Very Large Scale Integration Systems*, vol. 13, no. 3, pp. 308-318, Mar. 2005.

- [6] Yingchieh Ho and Chauchin Su, "A 0.1–0.3 V 40–123 fJ/bit/ch On-Chip Data Link With ISI-Suppressed Bootstrapped Repeaters" *IEEE Journal of Solid-State Circuits* Volume: 47 , Issue: 5 pp: 1242 - 1251 May 2012

- [7] P. Chen, D. K. Kirkpatrick, and K. Keutzer, "Miller factor for gate-level coupling delay calculation," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD)*, Nov. 2000, pp. 68–74.

- [8] A. B. Kahng, S. Muddu, E. Sarto, and R. Sharma, "Interconnect tuning strategies for high-performance ICs," in *Proc. Des. Autom. Test Eur. (DATE)*, 1998, pp. 471–478.

- [9] M. Ghoneima and Y. Ismail, "Optimum positioning of interleaved repeaters in bidirectional buses," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 24, no. 3, pp. 461–469, Mar. 2005.

- [10] J. Cong, T. Kong, and D. Z. Pan, "Buffer block planning for interconnect-driven floorplanning," in *Proc. IEEE/ACM Int. Conf. Comput.-Aided Des. (ICCAD)*, Nov. 1999, pp. 358–363.

- [11] C. J. Alpert, J. Hu, S. S. Sapatnekar, and P. G. Villarrubia, "A practical methodology for early buffer and wire resource allocation," *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 22, no. 5, pp. 573–583, May 2003.

- [12] C.J. Akl, M.A. Bayoumi, "Reducing Interconnect Delay Uncertainty via Hybrid Repeater Insertion, *IEEE Trans. VLSI*, vo1.16, no. 9, pp. 1230-1239, 2008.

- [13] P. Gupta and A. Kahng, "Wire swizzling to reduce delay uncertainty due to capacitive coupling", Proceedings of the 17th International Conference on VLSI Design, pp. 431-436, January 2004.

- [14] S. Khatri, A. Mehrotra, R. Brayton, R. H. J. M. Otten, and A. Sangiovanni-Vincentelli, "A novel VLSI layout fabric for deep sub-micron application," in Proc. IEEE/ACM Des. Autom. Conf. (DAC), Jun. 1999, pp. 491-496.

- [15] R. Arunachalam, E. Acar, and S. Nassif, "Optimal shielding/spacingmetrics for low power design," in Proc. IEEE Symp. VLSI, Feb. 2003, pp. 167-172.

- [16] M. Ghoneima, Y. I. Ismail, M. M. Khellah, J. W. Tschanz, V. De, "Reducing the effective coupling capacitance in buses using threshold voltage adjustment techniques," IEEE Trans. Circuits and Systems I: Regular Papers, vol. 53, no. 9, pp. 1928-1933, Sept. 2006.

- [17] J. sun Seo, H. Kaul, R. Krishnamurthy, D. Sylvester, and D. Blaauw, "A Robust Edge Encoding Technique for Energy-Efficient Multi-Cycle Interconnect," IEEE Trans. on VLSI Systems, vol. 19, no. 2, pp. 264-273, 2011.

- [18] M. Khellah, M. Ghoneima, J. Tschanz, Y. Ye, N. Kurd, J. Barkatullah, Y. Ismail, and V. De, "A skewed repeater bus architecture for on-chip energy reduction in microprocessors," in Proc. 2005 IEEE Int. Conf. Circuit Design, Oct. 2005.

- [19] H. Kaul, D. Sylvester, and D. Blaauw, "Performance optimization of critical nets through active shielding," IEEE Trans. Circuits and Systems, vol. 51, pp. 2417-2435, 2004.

- [20] J. M. RABAЕY, Digital Integrated Circuits A Design Perspective, Second Edition, Prentice-Hall, 2003.

- [21] N. Ou, T. Farahmand, A. Kuo, S. Tabatabaei, and A. Ivanov, "Jitter models for the design and test of gbps-speed serial interconnects," IEEE Design Test Comput., vol. 21, pp. 302-313, Jul.-Aug. 2004.

- [22] Y. Zhang, H. Li, Y. Min, and X. Li, "Selected Transition Time Adjustment for Tolerating Crosstalk Effects on Network-on-Chip Interconnects," IEEE Trans. Very Large Scale Integration Systems, vol. 19, no. 10, pp. 1787-1800, Oct. 2011.

- [23] J. Buckwalter, B. Analui, and A. Hajimiri, "Data-dependent jitter and crosstalk-induced bounded uncorrelated jitter in copper interconnects," in IEEE MTT-S Int. Microw. Symp. Dig., Jun. 2004, vol. 3, pp. 1627-1630.

- [24] S. Kose, E. Salman, E.G. Friedman, "Shielding Methodologies in the Presence of Power/Ground Noise," IEEE Trans. on VLSI Systems, vol. 19, no. 8, pp. 1458-1468, Aug 2011.

- [25] V. V. Deodhar and J. A. Davis, "Optimal voltage scaling, repeater insertion, and wire sizing for wave-pipelined global interconnects," IEEE Trans. on Circuits and Systems I:

---

Regular Papers, vol. 55, no. 4, pp. 1023-1030, May 2008.

- [26] E. Mensink, D. Schinkel, E. A. M. Klumperink, E. van Tuijl, and B. Nauta, "Power Efficient Gigabit Communication Over Capacitively Driven RC-Limited On-Chip Interconnects," IEEE Journal of Solid-State Circuits, vol. 45, no. 2, pp. 447-457, Feb. 2010.