Home Search Collections Journals About Contact us My IOPscience

Investigation of electrostatic integrity for ultra-thin-body GeOI MOSFET using analytical solution of Poisson's equation

This content has been downloaded from IOPscience. Please scroll down to see the full text. 2009 Semicond. Sci. Technol. 24 045017 (http://iopscience.iop.org/0268-1242/24/4/045017) View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11 This content was downloaded on 25/04/2014 at 10:43

Please note that terms and conditions apply.

Semicond. Sci. Technol. 24 (2009) 045017 (7pp)

# Investigation of electrostatic integrity for ultra-thin-body GeOI MOSFET using analytical solution of Poisson's equation

## Vita Pi-Ho Hu, Yu-Sheng Wu and Pin Su

Department of Electronics Engineering, National Chiao Tung University, 1001 University Road, Hsinchu, 300, Taiwan

E-mail: pinsu@faculty.nctu.edu.tw

Received 23 September 2008, in final form 2 January 2009 Published 17 March 2009 Online at stacks.iop.org/SST/24/045017

#### Abstract

The electrostatic integrity for UTB GeOI MOSFETs is examined comprehensively by using an analytical solution of Poisson's equation verified with TCAD simulation. Our results indicate that UTB GeOI MOSFETs with the ratio of channel length ( $L_g$ ) to channel thickness ( $T_{ch}$ ) around 5 can show comparable subthreshold swing to that of the SOI counterparts. The impact of the buried oxide thickness ( $T_{BOX}$ ) and back-gate bias ( $V_{back-gate}$ ) on the electrostatic integrity of GeOI devices is also examined.

(Some figures in this article are in colour only in the electronic version)

# 1. Introduction

Germanium as a pFET channel material has been recently proposed [1–6] to enable mobility scaling. However, its higher permittivity makes it very susceptible to short channel effects (SCEs). The ultra-thin body (UTB) MOSFETs with thin buried oxide (BOX) have emerged as an important candidate for CMOS scaling [7–9]. Germanium-on-insulator (GeOI) devices are expected to offer better electrostatic control over bulk Ge devices [10].

Several studies [10-12] have compared the electrostatic integrity of Ge and Si devices in the past. An et al [11] showed that the off-state leakage current of UTB GeOI devices is comparable to or even a little lower than that of SOI devices. Pethe *et al* [12] showed that the Ge double gate suffers worse SCEs and therefore has higher subthreshold swing than the Si device. Batail et al [10] showed that UTB GeOI devices present equivalent threshold voltage control as SOI devices. These studies, either employing numerical simulation or using a semi-empirical model with fitting parameters, have not shown consistent results. Moreover, analytical analysis of the UTB GeOI MOSFET has rarely been seen. In this work, we assess the electrostatic integrity for nanoscale UTB GeOI MOSFETs by using analytical solution of Poisson's equations and provide more scalable and predictive results for UTB GeOI MOSFET analysis. Following the 2007 edition of the International Technology Roadmap for Semiconductors [13], UTB MOSFETs for various generations are investigated. Through our theoretical model, a comprehensive analysis including the impact of  $T_{\text{BOX}}$ ,  $T_{\text{ch}}$  and  $V_{\text{back-gate}}$  on the electrostatic integrity of the UTB GeOI MOSFET is presented.

## 2. Analytical model and methodology

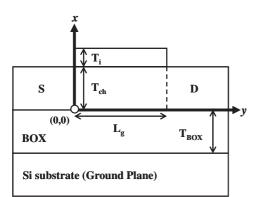

Our theoretical subtreshold swing for UTB GeOI is derived from analytical potential solution in the subthreshold region. Figure 1 shows a schematic sketch of a UTB MOSFET with thin BOX structure. In the subthreshold regime, the channel is fully depleted with negligible mobile carriers. Therefore, the channel potential distribution,  $\phi_{ch}(x, y)$ , satisfies Poisson's equation:

$$\frac{\partial^2 \phi_{\rm ch}(x, y)}{\partial x^2} + \frac{\partial^2 \phi_{\rm ch}(x, y)}{\partial y^2} = -\frac{q N_{\rm ch}}{\varepsilon_{\rm ch}}.$$

(1)

Since there is no charge in the BOX region, the BOX potential distribution,  $\phi_{\text{box}}(x, y)$ , satisfies the Laplace equation:

$$\frac{\partial^2 \phi_{\text{box}}(x, y)}{\partial x^2} + \frac{\partial^2 \phi_{\text{box}}(x, y)}{\partial y^2} = 0.$$

(2)

Figure 1. Schematic sketch of a UTB MOSFET with thin BOX structure investigated in this study.

Above,  $N_{ch}$  is the channel doping concentration and  $\varepsilon_{ch}$  is the permittivity of the channel. The required boundary conditions can be described as

$$\phi_{\rm ch}(T_{\rm ch}, y) + T_i \frac{\varepsilon_{\rm ch}}{\varepsilon_i} \cdot \left. \frac{\partial \phi_{\rm ch}(x, y)}{\partial x} \right|_{x=T_{\rm ch}} = V_g - V_{\rm fb}, \qquad (3a)$$

$$\phi_{\rm ch}(x,0) = -\phi_{\rm ms} + V_s,\tag{3b}$$

$$\phi_{\rm ch}(x, L_g) = -\phi_{\rm ms} + V_d, \qquad (3c)$$

$\phi_{\text{box}}(-T_{\text{BOX}}, y) = V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}}),$ (3d)

$$\phi_{\text{box}}(x, 0) = [V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}})] + \frac{(-\phi_{\text{ms}} + V_s) - [V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}})]}{T_{\text{BOX}}} x,$$

(3e)

$$\phi_{\text{box}}(x, L_g) = [V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}})] + \frac{(-\phi_{\text{ms}} + V_d) - [V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}})]}{T_{\text{BOX}}} x,$$

$$\varepsilon_{\rm ch} \cdot \frac{\partial \phi_{\rm ch}(x, y)}{\partial x} \bigg|_{x=0} = \varepsilon_{\rm ox} \cdot \frac{\partial \phi_{\rm box}(x, y)}{\partial x} \bigg|_{x=0}, \qquad (3g)$$

$$\frac{\partial \phi_{\rm ch}(x, y)}{\partial y} \bigg|_{x=0} = \left. \frac{\partial \phi_{\rm box}(x, y)}{\partial y} \right|_{x=0},\tag{3h}$$

where  $T_{ch}$ ,  $T_i$  and  $T_{BOX}$  are the thicknesses of the channel, gate insulator and buried oxide, respectively;  $L_g$  is the gate length;  $\varepsilon_i$  and  $\varepsilon_{ox}$  are the permittivities of the gate insulator and BOX, respectively;  $V_g$ ,  $V_{back-gate}$ ,  $V_d$  and  $V_s$  are the voltage biases of the gate, back-gate, drain and source, respectively;  $V_{fb}$  and  $V_{fb,back-gate}$  are the flat-band voltages of the gate and back-gate, respectively;  $\phi_{ms}$  is the built-in potential of the source/drain to the channel;  $E_{i,ch}$  and  $E_{i,sub}$  are the intrinsic Fermi levels of the channel and substrate (back-gate), respectively.

The corresponding 2D boundary value problem can be divided into two sub-problems, a 1D Poisson's equation and a 2D Laplace equation. Using the superposition principle, the complete channel potential solution is  $\phi_{ch}(x, y) = \phi_{ch,1}(x) + \phi_{ch,2}(x)$

$\phi_{ch,2}(x, y)$ , where  $\phi_{ch,1}(x)$  and  $\phi_{ch,2}(x, y)$  are solutions of 1D and 2D sub-problems in the channel, respectively. The 1D solution  $\phi_{ch,1}(x)$  can be expressed as

$$\phi_{\mathrm{ch},1}(x) = -\frac{qN_{\mathrm{ch}}}{2\varepsilon_{\mathrm{ch}}}x^2 + A \cdot x + B, \qquad (4a)$$

$$A = \left\{ (V_g - V_{fb}) - [V_{back-gate} - V_{fb,back-gate} + (E_{i,ch} - E_{i,sub})] + \frac{q N_{ch}}{2\varepsilon_{ch}} \left( T_{ch}^2 + 2\frac{\varepsilon_{ch}}{\varepsilon_i} T_i T_{ch} \right) \right\} / \left\{ T_{ch} + \frac{\varepsilon_{ch}}{\varepsilon_i} T_i + \frac{\varepsilon_{ch}}{\varepsilon_{ox}} T_{BOX} \right\},$$

(4b)

$$B = \frac{\varepsilon_{\rm ch}}{\varepsilon_{\rm ox}} T_{\rm BOX} \cdot A + [V_{\rm back-gate} - V_{\rm fb, back-gate} + (E_{i,\rm ch} - E_{i,\rm sub})].$$

(4c)

In solving the 2D sub-problem, the boundary condition of the gate dielectric/channel interface (3*a*) is simplified by converting the gate dielectric thickness to  $(\varepsilon_{ch}/\varepsilon_i)$  times and replacing the gate dielectric region with an equivalent channelmaterial region. The electric field discontinuity across the gate dielectric and channel interface can thus be eliminated. For the channel/BOX interface, both potential distribution in the channel ( $\phi_{ch,2}(x, y)$ ) and that in the BOX ( $\phi_{box,2}(x, y)$ ) have to be considered to satisfy the boundary conditions (3*g*) and (3*h*).

The 2D solution  $\phi_{ch,2}(x, y)$  can be obtained using the method of separation of variables:

$$\phi_{ch,2}(x, y) = \sum_{n} \{ [c_n \cdot \sinh(\gamma_n y) + c'_n \cdot \sinh(\gamma_n (L_g - y))] \cdot \sin(\gamma_n x) + e_n \cdot \sinh(\lambda_n (T_{ch} + (\varepsilon_{ch} / \varepsilon_i) T_i - x)) \cdot \sin(\lambda_n y) \}, \quad (5a)$$

where

$\gamma_n$

$$\lambda_n = (n\pi)/L_g,\tag{5b}$$

$$= (n\pi)/(T_{\rm ch} + (\varepsilon_{\rm ch}/\varepsilon_i)T_i).$$

(5c)

The coefficients  $c_n$ ,  $c'_n$  and  $e_n$  in (5*a*) can be expressed as

$$c_n = \frac{1}{\sinh(\lambda_n L_g)} \left[ 2(-\phi_{\rm ms} + V_d - B) \cdot \frac{1 - (-1)^n}{n\pi} + 2A \right]$$

$$\cdot \left( T_{\rm ch} + \frac{\varepsilon_{\rm ch}}{\varepsilon_i} T_i \right) \frac{(-1)^n}{n\pi} + 2 \left( T_{\rm ch} + \frac{\varepsilon_{\rm ch}}{\varepsilon_i} T_i \right)^2 \cdot \frac{(-1)^n - 1}{(n\pi)^3} \right],$$

(5d)

$$c'_{n} = \frac{1}{\sinh(\lambda_{n}L_{g})} \left[ 2(-\phi_{\rm ms} - B) \frac{1 - (-1)^{n}}{n\pi} + 2A \right]$$

$$\cdot \left( T_{\rm ch} + \frac{\varepsilon_{\rm ch}}{\varepsilon_{i}} T_{i} \right) \frac{(-1)^{n}}{n\pi} + 2 \left( T_{\rm ch} + \frac{\varepsilon_{\rm ch}}{\varepsilon_{i}} T_{i} \right)^{2} \cdot \frac{(-1)^{n} - 1}{(n\pi)^{3}} ,$$

(5e)

$$e_n = \frac{(\text{RHS}_n/\text{LHS}_n)}{\sinh\left(\frac{n\pi}{L_g}(T_{\text{ch}} + (\varepsilon_{\text{ch}}/\varepsilon_i)T_i)\right)},$$

(5f)

1.2 L<sub>a</sub>=40nm, T<sub>ch</sub>=10nm, T<sub>i</sub>=1nm =10nm, V<sub>d</sub>=0.05V, V<sub>a</sub>=0V y-direction BOX 1.0 (x=0.5\* CAD mode 0.8 <sup>e</sup>ch e16 cm Potential [V] 0.6 0.4 0.2 -direction (y=0.5\*L<sub>q</sub>) 0.0 0.2 0.4 0.6 0.8 0.0 1.0 **Normalized Position**

**Figure 2.** Analytical potential distribution compared with the result of TCAD simulation. A midgap work function (4.5 eV) is used.

where

LHS<sub>n</sub> =

$$\lambda_n \cdot \coth(\lambda_n T_{BOX})$$

+  $\frac{\varepsilon_{ch}}{\varepsilon_{ox}} \lambda_n \cdot \coth(\lambda_n((\varepsilon_{ch}/\varepsilon_i)T_i + T_{ch})),$  (5g)

$$\begin{aligned} \operatorname{RHS}_{n} &= 2 \frac{\varepsilon_{\mathrm{ch}}}{\varepsilon_{\mathrm{ox}}} A \cdot \frac{1 - (-1)^{n}}{n\pi} \\ &+ \sum_{m} \left\{ \left[ c_{n} \cdot \frac{(2\varepsilon_{\mathrm{ch}}/\varepsilon_{\mathrm{ox}})(-1)^{n+1}}{n\pi} \sinh(\lambda_{m}L_{g}) \\ &+ c_{n}' \cdot \frac{(2\varepsilon_{\mathrm{ch}}/\varepsilon_{\mathrm{ox}})}{n\pi} \sinh(\lambda_{m}L_{g})}{1 + (\gamma_{m}/\lambda_{n})^{2}} \right] \cdot \lambda_{m} \\ &- d_{n} \frac{m\pi}{T_{\mathrm{BOX}}} \frac{(-1)^{m+n+1}}{n\pi} \frac{2\sinh\left(\frac{m\pi}{T_{\mathrm{BOX}}}L_{g}\right)}{1 + (\gamma_{m}/\lambda_{n})^{2}} \\ &- d_{n}' \frac{m\pi}{T_{\mathrm{BOX}}} \frac{(-1)^{m}}{n\pi} \frac{2\sinh\left(\frac{m\pi}{T_{\mathrm{BOX}}}L_{g}\right)}{1 + (\gamma_{m}/\lambda_{n})^{2}} \right\}, \end{aligned}$$

(5*h*)

$$d_{n} = \frac{2}{\sinh(\gamma_{n}L_{g})} \left\{ [V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}})] \\ \cdot \frac{1 - (-1)^{n}}{n\pi} + [(-\phi_{\text{ms}} + V_{d} - B)] \cdot \frac{(-1)^{n+1}}{n\pi} \right\},$$

(5*i*)

$$d'_{n} = \frac{2}{\sinh(\gamma_{n}L_{g})} \left\{ [V_{\text{back-gate}} - V_{\text{fb,back-gate}} + (E_{i,\text{ch}} - E_{i,\text{sub}})] \\ \cdot \frac{1 - (-1)^{n}}{n\pi} + [(-\phi_{\text{ms}} - B)] \cdot \frac{(-1)^{n+1}}{n\pi} \right\}.$$

(5*j*)

Our analytical potential solution has been verified with TCAD simulation [14]. Figure 2 shows that our model is fairly accurate for various channel doping ( $N_{ch}$ ). Based on the potential solution, the subthreshold current can be derived by

$$I_d = \frac{q\mu_n W(kT/q) (n_i^2/N_{\rm ch}) [1 - \exp(-V_d/(kT/q))]}{\int_0^{L_g} dy / \int_0^{T_{\rm ch}} \exp[q\phi_{\rm ch}(x, y)/(kT)] dx}.$$

(6)

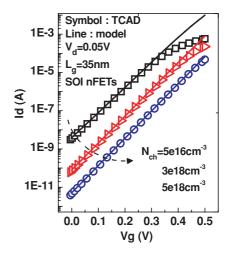

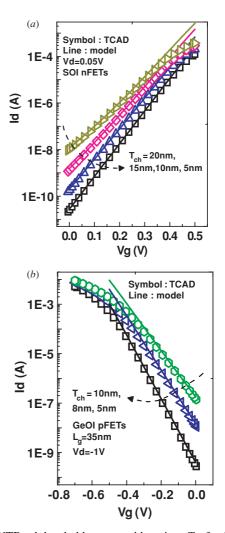

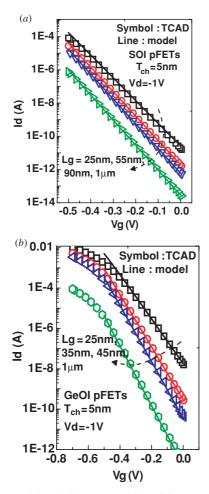

Figures 3–6 demonstrate that our UTB subthreshold current model is quite scalable with important device design

**Figure 3.** UTB SOI subthreshold current with heavily doped and lightly doped channels. Constant mobility model is used in both the analytical model and the TCAD simulation.

**Figure 4.** UTB subthreshold current with various  $T_{ch}$  for (*a*) nFET SOI devices and (*b*) pFET GeOI devices. Constant mobility model is used in both the analytical model and the TCAD simulation.

parameters such as  $N_{ch}$ ,  $T_{ch}$ ,  $L_g$  and  $V_{back-gate}$ . The UTB subthreshold current model shows good agreement with TCAD simulation for both N/P FET UTB SOI and GeOI

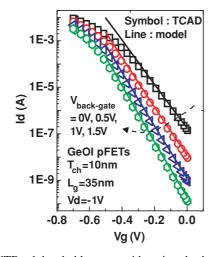

**Figure 5.** UTB subthreshold current with various back-gate biases for GeOI devices. Constant mobility model is used in both the analytical model and the TCAD simulation.

**Figure 6.** UTB subthreshold current with a wide range of gate lengths for (*a*) pFET SOI devices and (*b*) pFET GeOI devices. Constant mobility model is used in both the analytical model and the TCAD simulation.

devices. With the subthreshold current model, subthreshold swing can be obtained. Several papers recently published indicated that an accurate investigation of electrostatic integrity for bulk [15] and FDSOI [16] MOSFETs must

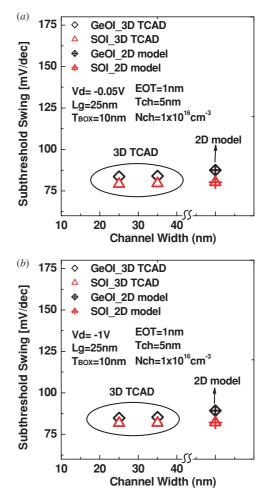

**Figure 7.** The impact of INWE on the subthreshold swing for the UTB thin BOX GeOI MOSFET with (*a*)  $V_d = -0.05$  V and (*b*)  $V_d = -1$  V.

be carried out by 3D Poisson analysis to consider the inverse narrow width effect (INWE). However, as shown in figure 7, for UTB thin BOX MOSFETs with a lightly doped channel, the impact of INWE on the subthreshold swing is insignificant. Therefore, our analytical subthreshold current model is sufficient for examining the electrostatic integrity of the UTB MOSFETs.

Compared with the TCAD device simulation, our methodology shows higher efficiency in determining the subthreshold current of a UTB MOSFET. For TCAD simulation, the CPU time needed for a single subthreshold current is about several minutes, while in our calculation several seconds only is needed.

In this work, important device parameters used for investigating the electrostatic integrity of the lightly doped  $(N_{\rm ch} = 1 \times 10^{16} \text{ cm}^{-3})$  pFET UTB MOSFET such as  $L_g$  and EOT for each generation are determined based on the ITRS roadmap [13].

## 3. Electrostatic integrity for UTB GeOI MOSFET

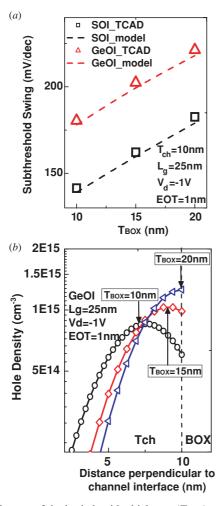

Figure 8 shows that due to higher permittivity, the hole conduction path of GeOI devices is closer to the back-gate

Figure 8. Hole density distribution for SOI and GeOI in the subthreshold region. The arrow tip indicates the hole conduction path.

**Figure 9.** Impact of the buried oxide thickness  $(T_{BOX})$  on (a) the subthreshold swing and (b) the hole density distribution in the subthreshold region.

interface  $(T_{ch}/BOX \text{ interface})$  than SOI devices. Thus, the GeOI device has worse electrostatic integrity than the SOI device generally. Figure 9 illustrates the impact of  $T_{\rm BOX}$  V P-H Hu et al

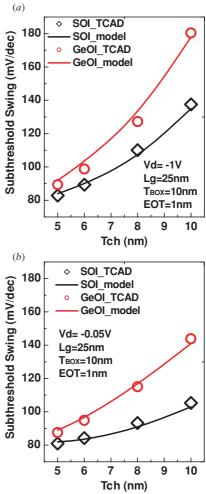

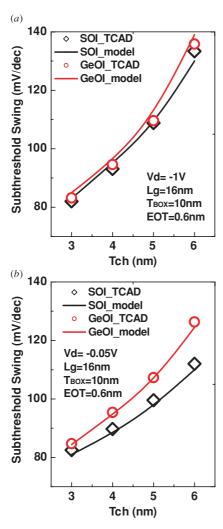

Figure 10. Impact of the channel thickness  $(T_{ch})$  on the subthreshold swing for (a)  $V_d = -1$  V and (b)  $V_d = -0.05$  V with  $L_g = 25$  nm.

on the subthreshold swing (figure 9(a)) and hole density distribution in the subthreshold region (figure 9(b)). At  $V_d = -1$  V, the SCEs of UTB devices result from the electric field coupling between the source and drain through BOX. As  $T_{\rm BOX}$  is scaled, the SCEs of UTB SOI and GeOI devices can be improved, and the UTB devices show lower subthreshold swing (figure 9(*a*)). Figure 9(*b*) shows that as  $T_{BOX}$  is scaled, the hole conduction path becomes closer to the front-gate surface  $(T_i/T_{ch} \text{ interface})$ . Therefore, thin BOX with stronger front-gate controllability is needed for GeOI devices.

Figure 10 shows the impact of  $T_{ch}$  on the subthreshold swing of SOI and GeOI devices for  $V_d = -1$  V and  $V_d =$ -0.05 V with  $L_g = 25$  nm. As  $T_{ch}$  is scaled, the subthreshold swing of the UTB device is reduced. When  $T_{ch} = 10$  nm, the GeOI device with worse electrostatic integrity shows larger subthreshold swing than that of the SOI device. When  $T_{ch}$  is scaled to 5 nm, the subthreshold swing of the GeOI device becomes comparable to that of the SOI device because the GeOI device with thin  $T_{ch}$  shows well-controlled electrostatic integrity. Moreover, the UTB devices with  $V_d = -1$  V and  $V_d = -0.05$  V show comparable subthreshold swing as  $T_{\rm ch} = 5$  nm. In other words, the impact of drain-induced barrier lowering (DIBL) on subthreshold swing can be suppressed

**Figure 11.** Impact of the channel thickness ( $T_{ch}$ ) on the subthreshold swing for (*a*)  $V_d = -1$  V and (*b*)  $V_d = -0.05$  V with  $L_g = 16$  nm.

when  $T_{ch}$  is scaled. Figure 11 shows the impact of  $T_{ch}$  on the subthreshold swing of UTB devices with  $L_g = 16$  nm. When  $T_{ch}$  is reduced to 3 nm, the GeOI device shows comparable subthreshold swing to that of SOI devices.

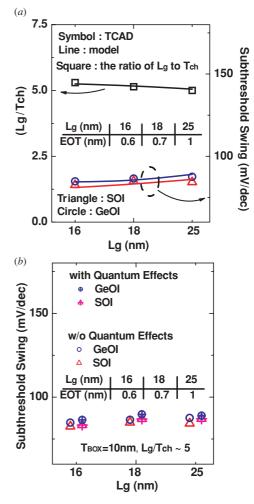

More generations of UTB devices are investigated for the device design of GeOI devices (figure 12(*a*)). As for the ITRS roadmap [13], the device design for SOI devices with a Si channel, the ratio of  $L_g$  to  $T_{ch}$  is around 3. Figure 12(*a*) shows that the GeOI devices with the ratio of  $L_g$  to  $T_{ch}$  around 5 can show well-controlled electrostatic integrity and comparable subthreshold swing to that of the SOI devices. Figure 12(*b*) shows that even considering quantum effects, the UTB GeOI and SOI MOSFETs still show comparable subthreshold swing as  $L_g/T_{ch}$  around 5. The comparison between UTB GeOI and SOI MOSFETs in figure 12 is based on the same off-current (2 × 10<sup>-8</sup> A  $\mu$ m<sup>-1</sup>) by adjusting the gate work function for both GeOI and SOI MOSFETs, respectively.

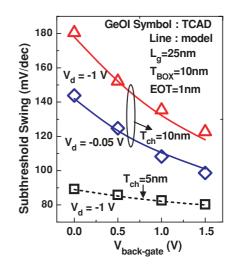

Besides  $T_{\text{BOX}}$  and  $T_{\text{ch}}$  scaling,  $V_{\text{back-gate}}$  is also beneficial for suppressing the SCEs of GeOI devices. Figure 13 shows the impact of  $V_{\text{back-gate}}$  on the subthreshold swing for  $L_g =$ 25 nm. As  $V_{\text{back-gate}}$  is increased, the subthreshold swing

**Figure 12.** (*a*) GeOI devices with  $L_g/T_{ch} \sim 5$  show comparable subthreshold swing to that of SOI devices at  $V_d = -0.05$  V. (*b*) The subthreshold swing comparison between the GeOI and SOI MOSFETs as quantum effects are considered by using the density gradient model in TCAD simulation [14].

**Figure 13.** Impact of the back-gate bias ( $V_{\text{back-gate}}$ ) on the subthreshold swing with  $L_g = 25 \text{ nm}$ .

of UTB devices is reduced. In figure 13, the subthreshold swing of the GeOI device with larger  $T_{ch}$  (= 10 nm) shows

higher sensitivity to  $V_{\text{back-gate}}$  as compared to that of the GeOI device with smaller  $T_{\text{ch}}$  (= 5 nm). The GeOI device shows better front-gate controllability and electrostatic integrity with increasing  $V_{\text{back-gate}}$  because the hole conduction path for the GeOI device becomes closer to the front-gate surface.

Besides UTB MOSFETs, silicon-on-nothing (SON) MOSFETs have also been proposed as a possible alternative scalable solution to satisfy the ITRS roadmap requirements [17, 18]. Therefore, the comparison of the electrostatic integrity among GeOI, SOI and SON is an important issue and merits investigation in the future.

## 4. Conclusion

We have investigated the electrostatic integrity for UTB GeOI devices using analytical solution of Poisson's equation verified with TCAD simulation. Especially, the impacts of  $T_{\rm BOX}$ ,  $T_{\rm ch}$  and  $V_{\rm back-gate}$  on the electrostatic integrity for the UTB GeOI MOSFET have been carefully examined. Our results indicate that the UTB GeOI MOSFETs with the device design of  $L_g/T_{\rm ch} \sim 5$  show acceptable and comparable subthreshold swing to that of SOI devices. The electrostatic integrity for the UTB GeOI MOSFET is very sensitive to the  $T_{\rm ch}$  scaling.  $T_{\rm BOX}$  reduction and positive  $V_{\rm back-gate}$  are also beneficial for suppressing the SCEs of pFET UTB GeOI MOSFETs. This study may provide insights for the UTB GeOI device design.

#### Acknowledgments

This work was supported in part by the National Science Council of Taiwan under contract NSC 97-2221-E-009-162, and in part by the Ministry of Education in Taiwan under ATU Program.

#### References

- [1] Ritenour A, Yu S, Lee M L, Lu N, Bai W, Pitera A, Fitzqerald E A, Kwong D L and Antoniadis D A 2003 Epitaxial strained germanium p-MOSFETs with HfO<sub>2</sub> gate dielectric and TaN gate electrode *IEDM Tech. Dig.* p 433

- [2] Shang H et al 2004 Selectively formed high mobility strained Ge pMOSFETs for high-performance CMOS IEDM Tech. Dig. p 157

- [3] Nicholas G, De J B, Brunco D P, Zimmerman P, Eneman G, Martens K, Meuris M and Heyns M M 2007 High-performance deep submicron Ge pMOSFETs with halo implants *IEEE Trans. Electron Devices* 54 2503

- Yamamoto T, Yamashita Y, Harada M, Taoka N, Ikeda K, Suzuki K, Kiso O, Sugiyama N and Takagi S 2007 High-performance 60 nm gate length germanium p\_MOSFETs with Ni germanide metal source/drain *IEDM Tech. Dig.* p 1041

- [5] Takagi S, Tezuka T, Irisawa T, Nakaharai S, Numata T, Usuda K, Sugiyama N, Shichijo M, Nakane R and Sugahara S 2007 Device structure and carrier transport properties of advanced CMOS using high mobility channels *Solid-State Electron.* 51 526

- [6] Bedell S, Majumdar A, Ott J A, Arnold J, Foqel K, Koester S J and Sdana D K 2008 Mobility scaling in short-channel length strained Ge-on-insulator P-MOSFETs *IEEE Electron Device Lett.* 29 811

- [7] Morita Y, Tsuchiya R, Ishigaki T, Sugii N, Iwamatsu T, Ipposhi T, Oda H, Inoue Y, Torii K and Kimura S 2008 Smallest Vth variability achieved by intrinsic silicon on thin BOX (SOTB) CMOS with single metal gate *Proc. VLSI Technology Symp.* p 166

- [8] Monfray S *et al* 2007 Localized SOI technology: an innovative low cost self aligned process for ultra thin Si-film on thin BOX integration for low power applications *IEDM Tech. Dig.* p 693

- [9] Tetsu O, Nobuyuki S and Toshiro H 2007 Impact of parameter variations and random dopant fluctuations on short channel fully depleted SOI MOSFETs with extremely thin BOX *IEEE Trans. Electron Devices* 28 740

- [10] Batail E, Monfray S, Pouydebasque A, Ghibaudo G and Skotnicki T 2008 Impact of scaling on electrostatics of germanium channel MOSFET—analytical study IEEE Silicon Nanoelectronics Workshop pp 1–8

- [11] An X, Huang R, Zhang X and Wang Y 2005 Comparison of device performance and scaling capability of thin body GOI and SOI MOSFETs Semicond. Sci. Technol. 20 1034

- [12] Pethe A, Krishnamohan T, Kim D, Oh S, Philip Wong H S and Saraswat K 2006 Investigation of the performance limits of III–V double gate nMOSFETs *IEEE Industry Micr. Symp.* p 47

- [13] International Technology Roadmap for Semiconductors http://www.itrs.net/

- [14] ISE TCAD Rel. 10.0 Manual (DESSIS) 2004

- [15] Noor A and Shekhar C 1996 A 3D analytical model for threshold voltage of small-geometry MOSFET *Solid-State Electron.* 39 745

- [16] Katti G, DasGupta N and DasGupta A 2004 Threshold voltage model for mesa-isolated small geometry fully depleted SOI MSOFETs based on analytical solution of 3-D Poisson's equation *IEEE Trans. Electron Devices* **51** 1169

- [17] Jurczak M, Skotnicki T, Paoli M, Tormen B, Regolini J, Morin C, Schiltz A, Martins J, Pantel R and Galvier J 1999 SON (silicon on nothing): a new device architecture for the ULSI era *Proc. VLSI Technology Symp.* p 29

- [18] Jurczak M et al 2000 Silicon-on-nothing (SON)—an innovative process for advanced CMOS IEEE Trans. Electron Devices 47 2179