## Cobalt nanodots formed by annealing the CoSiO layer for the application of the nonvolatile memory

Chih-Wei Hu, Ting-Chang Chang, Chun-Hao Tu, Pei-Kun Shueh, Chao-Cheng Lin, Simon M. Sze, Tseung-Yuen Tseng, and Min-Chen Chen

Citation: Applied Physics Letters **94**, 102106 (2009); doi: 10.1063/1.3097810

View online: http://dx.doi.org/10.1063/1.3097810

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/94/10?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Controlled fabrication of Si nanocrystal delta-layers in thin SiO2 layers by plasma immersion ion implantation for nonvolatile memories

Appl. Phys. Lett. 103, 253118 (2013); 10.1063/1.4848780

Robust unipolar resistive switching of Co nano-dots embedded ZrO2 thin film memories and their switching mechanism

J. Appl. Phys. **111**, 014505 (2012); 10.1063/1.3674322

Formation of iridium nanocrystals with highly thermal stability for the applications of nonvolatile memory device with excellent trapping ability

Appl. Phys. Lett. 97, 143507 (2010); 10.1063/1.3498049

Formation of cobalt-silicide nanocrystals in Ge-doped dielectric layer for the application on nonvolatile memory

Appl. Phys. Lett. 92, 152115 (2008); 10.1063/1.2908916

Surface composition and structure of Co 3 O 4 (110) and the effect of impurity segregation J. Vac. Sci. Technol. A 22, 1690 (2004); 10.1116/1.1763899

## Cobalt nanodots formed by annealing the CoSiO layer for the application of the nonvolatile memory

Chih-Wei Hu,<sup>1</sup> Ting-Chang Chang,<sup>2,a)</sup> Chun-Hao Tu,<sup>1</sup> Pei-Kun Shueh,<sup>1</sup> Chao-Cheng Lin,<sup>1</sup> Simon M. Sze,<sup>1</sup> Tseung-Yuen Tseng,<sup>1</sup> and Min-Chen Chen<sup>3</sup>

<sup>1</sup>Institute of Electronics, National Chiao Tung University, Hsin-Chu 300, Taiwan

<sup>2</sup>Department of Physics, Institute of Electro-Optical Engineering, and Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung 804, Taiwan

(Received 7 January 2009; accepted 19 February 2009; published online 12 March 2009)

<sup>5</sup>Department of Physics, National Sun Yat-Sen University, Kaohsiung 804, Taiwan

Co nanodot memory devices formed by oxidation processes were studied. Transmission electron microscopy and x-ray photoelectron spectroscopy analyses showed that overoxidation of the cobalt and silicon degraded the charge-storage ability seriously. However, a precapped oxide can mildly oxidize the CoSi<sub>2</sub> film to protect the overoxidation to occur. In addition, an oxygen-incorporated CoSi<sub>2</sub> film is proposed to improve the oxidation process further. Through incorporating the limited oxygen during sputtering process, the Co nanodot memory device obtains a larger memory window. Also, the reliability characteristic of the Co nanodot memory device formed by annealing the oxygen-incorporated CoSi<sub>2</sub> film has been demonstrated. © 2009 American Institute of Physics. [DOI: 10.1063/1.3097810]

Recently, nonvolatile memory (NVM) devices attract much attention as the demand of portable electronic products increasingly. However, the conventional floating gate (FG) memory invented by Kahng and Sze<sup>1</sup> will face many issues such as retention, endurance, and power consumption as the memory devices scale down.<sup>2,3</sup> Therefore, Tiwari *et al.* presented nanodot (ND) structure instead of the FG as the next generation NVM structure.<sup>4</sup> In the reported literature, the metallic ND memory devices show superior charge-storage ability due to its available work functions, better channel coupling, and lower quantum confinement. 5,6 In addition, Co is the potential material for applying into the NDs structure by its compatibility and low resistivity. 7,8 In the reported method, the method of forming Co NDs by direct oxidation of  $CoSi_2$  layer is advantageous to control the uniformity and distribution of NDs.  $^{9-12}$  However, the oxidation process during the Co NDs formation is a main parameter for the charge-storage properties of the memory devices.

In our work, Co NDs as the charge-storage centers were formed by oxidation process for three kinds of structures. Electrical and material analyses indicate that the chargestorage ability and Co NDs formation were related to the CoSi<sub>2</sub> oxidation process. A precapped oxide structure is confirmed to restrain the CoSi<sub>2</sub> film overoxidation. In addition, we also proposed a Co ND formation by annealing an oxygen-incorporated CoSi<sub>2</sub> (CoSiO) film. The trapping layer formed by annealing CoSiO film shows good memory effect and reliability characteristics. Furthermore, it is easier to control the oxidation process by the CoSiO film than by the precapped oxide.

First, a 5-nm-thick oxide was grown on the *p*-type silicon wafer in atmospheric pressure chemical vapor deposition furnace. Afterward, a 6-nm-thick CoSi<sub>2</sub> thin film was deposited by sputtering system in Ar ambient. Then, the samples were divided into two groups with (sample A) and without a 20 nm precapped oxide (sample B). Subsequently, the 700 °C rapidly thermal annealing process in O<sub>2</sub> ambient (RTO) was performed for 60 s to oxidize the Si and form the Co NDs. Then, plasma enhanced chemical vapor deposition (PECVD) was used to form the total 50-nm-thick blocking oxide. In addition, a 6-nm-thick CoSiO thin film was also prepared to investigate the oxidation behavior further. The

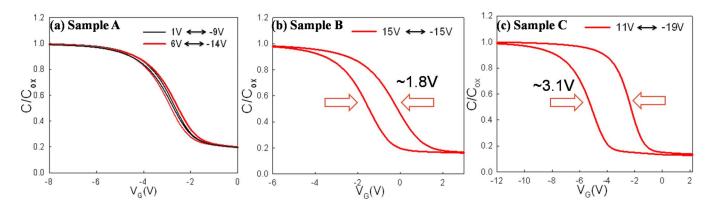

FIG. 1. (Color online) C-V hysteresis of (a) sample A (without a precapped oxide), (b) sample B (with a precapped oxide), and (c) sample C (CoSiO method).

<sup>&</sup>lt;sup>a)</sup>Electronic mail: tcchang@mail.phys.nsysu.edu.tw.

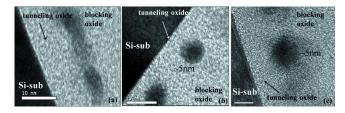

FIG. 2. (Color online) Cross-sectional TEM image of (a) sample A, (b) sample B, and (c) sample C.

TABLE I. List of the formed Co ND density, size, and memory window in samples A, B, and C.

|          | Annealing process | Size range (nm) | Density<br>(cm <sup>-2</sup> ) | Memory window (V) |

|----------|-------------------|-----------------|--------------------------------|-------------------|

| Sample A | RTO               |                 |                                | ~0.2              |

| Sample B | RTO               | 4-5             | $2.7 \times 10^{11}$           | 1.8               |

| Sample C | RTA               | 4–5             | $3.2 \times 10^{11}$           | 3.1               |

CoSiO thin film was deposited by sputtering the  $CoSi_2$  target in  $Ar/O_2$  [24/10 SCCM (SCCM denotes standard cubic centimeter per minute at STP)] environment (sample C). After the rapid thermal annealing (RTA) process and blocking oxide deposition, the top and bottom Al gate electrode were patterned. Capacitance-voltage (C-V) measurement was used to study the memory characteristics of these samples. Also, transmission electron microscopy (TEM) and x-ray photoelectron spectroscopy (XPS) were also adopted for Co ND formation.

Figure 1 exhibits the C-V characteristics of (a) sample A, (b) sample B, and (c) sample C. It is found a negligible flatband voltage ( $V_{\rm FB}$ ) shift was obtained in sample A after bidirectional gate voltage sweep. The memory window does not enlarge obviously even the voltage operation is increased. However, samples B and C show a  $V_{\rm FB}$  shift of 1.8 and 3.1 V under  $\pm$ 15 V gate voltage operation, respectively.

Figure 2 shows the TEM images of (a) sample A, (b) sample B, and (c) sample C. We find that the sample A causes no Co ND formation. However, the Co NDs are located at the interface of tunneling oxide in samples B and C obviously. Table I lists the Co NDs size, density, and the memory window of samples A, B, and C. Through comparing with the results of the *C-V* and TEM analyses, the oxidation process indeed affects the memory effect and NDs formation.

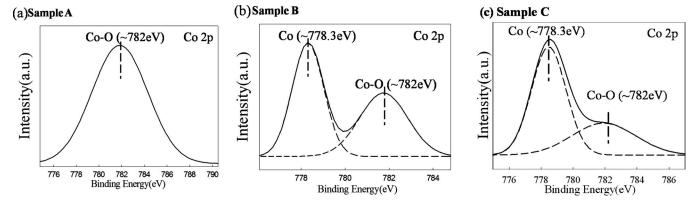

Figure 3 demonstrates the Co 2*p* XPS results of samples A, B, and C. Figure 3(a) shows that the main composition of the CoSi<sub>2</sub> layer after RTO process is Co–O binding

FIG. 3. Co 2p XPS analysis of (a) sample A, (b) sample B, and (c) sample C.

$(\sim 782 \text{ eV})$ . It means that the RTO process completely oxidized the trapping layer and retarded the Co NDs formation. Compared with samples A and B, we confirmed that the precapped oxide improves the formation of Co NDs. The CoSi<sub>2</sub> in sample B was transferred to partially CoO<sub>x</sub> and Co ( $\sim$ 778.3 eV), as shown in the Fig. 3(b). From the consideration of Gibbs free energy, the thermodynamics theory indicates that Si is easier to be oxidized than Co during RTO process. 13-15 The lower oxidation free energy for SiO<sub>2</sub> cause the formation of Co NDs embedded in SiO<sub>2</sub> dielectrics layer. However, the oxidation condition is difficult to be controlled for Co ND formation by the RTO system. 16 The softer oxidation condition by the precapped oxide only oxidize the Si and a small amount of Co. Nevertheless, the precapped oxide method needs an additional PECVD deposition. The CoSiO method to form Co NDs is easier and more effective. The XPS result in Fig. 3(c) indicates that the Co-O binding in sample C is lower than sample B because the oxygen content is limited by the sputtering parameter. The CoSi<sub>2</sub> oxidation only depends on the internal oxygen content of the CoSiO film. With the limited oxygen content, the Co element in the CoSiO layer prefers to form Co NDs, instead of forming  $CoO_x$ , which provides enough charge-storage sites.<sup>13</sup>

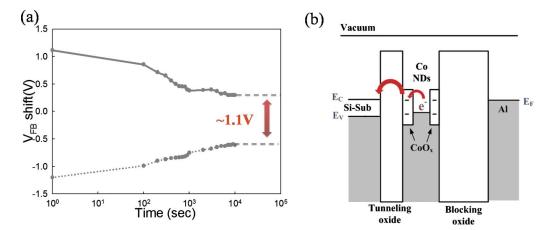

The reliability characteristic of sample C was also tested in the following experiment. The retention measurement was performed at room temperature by operating a  $\pm 15$  V gate voltage stress for 10 s and measured up to  $10^4$  s. It is found that sample C reveals obvious decay at the initial  $10^3$  s, as shown in Fig. 4(a). The decay at the initial duration resulted from some charges, which passed through the defect of the  $\text{CoO}_x$  are easier to tunnel back to the substrate as shown as the energy-band diagram of Fig. 4(b). <sup>17</sup> Nevertheless, the memory device maintains 1.1 V for  $10^4$  s steady after  $10^3$  s. The Co ND memory device using the annealed CoSiO film as trapping layer exhibits a good reliability characteristic for the application of NVM device.

In conclusion, Co ND memory devices formed by three kinds of structures have been shown in this work. Oxidation control during the Co ND formation is indicated as the important parameter to affect the charge-storage ability. The memory window was degraded because that the Si and Co

were completely oxidized in the virgin  $CoSi_2$  layer for overoxidation. With a limited oxygen flow by preoxide deposition, the Co ND performance is improved obviously. Furthermore, the Co ND formation can be more easily controlled by incorporating oxygen elements into  $CoSi_2$  layer during sputtering process. The Co-O content in annealed CoSiO layer is lower than in oxidized  $CoSi_2$  layer. Hence, Co NDs embedded in  $CoO_x$  and  $SiO_x$  layer contributes larger memory window than oxidizing  $CoSi_2$  layer with or without oxide capping.

This work was performed at National Nano Device Laboratory and was supported by the National Science Council of the Republic of China under Contract Nos. NSC 97-2112-M-110-009, NSC 97-2221-E-009-151, NSC 97-2221-E-009-148, and NSC 97-3114-M-110-001.

<sup>1</sup>D. Kahng and S. M. Sze, Bell Syst. Tech. J. **46**, 1288 (1967).

<sup>2</sup>J. De Blauwe, IEEE Trans. Nanotechnol. 1, 72 (2002).

<sup>3</sup>Z. Tan, S. K. Samanta, W. J. Yoo, and S. Lee, Appl. Phys. Lett. **86**, 013107 (2005).

<sup>4</sup>S. Tiwari, F. Rana, K. Chan, H. Hanafi, C. Wei, and D. Buchanan, Tech. Dig. - Int. Electron Devices Meet. **1995**, 521.

<sup>5</sup>A. Chandra and B. M. Clemens, Appl. Phys. Lett. **87**, 253113 (2005).

<sup>6</sup>K. S. Seol, S. J. Choi, J. Y. Choi, E. J. Jang, B. K. Kim, S. J. Park, D. G. Cha, I. Y. Song, J. B. Park, Y. Park, and S. H. Choi, Appl. Phys. Lett. 89, 083109 (2006).

<sup>7</sup>M. Takata, S. Kondoh, T. Sakaguchi, H. Choi, J.C. Shim, H. Kurino and M. Koyanagi, Tech. Dig. - Int. Electron Devices Meet. **2003**, 22.5.1.

Naidya, S. P. Murarka, and T. T. Sheng, J. Appl. Phys. 58, 971 (1985).

M. V. Rastei, R. Meckenstock, J. P. Bucher, E. Devaux, and Th. Ebbesen, Appl. Phys. Lett. 85, 2050 (2004).

<sup>10</sup>D. Zhao, Y. Zhu, and J. Liu, Solid-State Electron. **50**, 268 (2006).

<sup>11</sup>F. M. Yang, T. C. Chang, P. T. Liu, P. H. Yeh, Y. C. Yu, J. Y. Lin, S. M. Sze, and J. C. Lou, Appl. Phys. Lett. **90**, 132102 (2007).

<sup>12</sup>J. Y. Yang, K. S. Yoon, W. J. Choi, Y. H. Do, J. H. Kim, C. O. Kim, and J. P. Hong, Curr. Appl. Phys. 7, 147 (2007).

<sup>13</sup>J. Chevallier and A. N. Larson, Appl. Phys. A: Solids Surf. 39, 141 (1986).

<sup>14</sup>I. Barin and O. Knacke, Thermochemical Properties of Inorganic Substances (Springer, Berlin, 1977).

<sup>15</sup>M. Bartur and M. A. Nicolet, J. Appl. Phys. **54**, 5404 (1983).

<sup>16</sup>F. M. Yang and M. C. Chen, Thin Solid Films **207**, 75 (1992).

<sup>17</sup>A. Miura, Y. Uraoka, T. Fuyuki, S. Yoshii, and I. Yamashita, J. Appl. Phys. 103, 074503 (2008).