# 國立交通大學

## 材料科學與工程學系

### 博士論文

籍鎳捉聚改善鎳金屬誘發側向結晶之低溫複晶矽薄膜及奈 米通道電晶體效能研究

Improved Performance of NILC LTPS Thin-Film & Nanowire

Transistors through Ni-Gettering

1896

研 究 生:王寶明

指導教授:吳耀銓 教授

中華民國九十九年二月

### 藉鎳捉聚改善鎳金屬誘發側向結晶之低溫複晶矽薄膜及奈 米通道電晶體效能研究

# Improved Performance of NILC LTPS Thin-Film & Nanowire Transistors through Ni-Gettering

研究生:王寶明 Student: Bau-Ming Wang

指導教授:吳耀銓 博士 Advisor: Dr. YewChung Sermon Wu

#### 國立交通大學

材料科學與工程學系

A Thoris

Submitted to Department of Materials Science and Engineering

College of Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in Materials Science and Engineering in

February 2010

Hsinchu, Taiwan, Republic of China

中華民國九十九年二月

# 藉鎳捉聚改善鎳金屬誘發側向結晶之低溫複晶矽薄 膜及奈米通道電晶體效能研究

學生:王寶明

指導教授:吳耀銓 博士

### 國立交通大學材料科學與工程研究所

### 摘要

本論文主要研究鎳金屬誘發側向結晶(NILC)低溫複晶矽(LTPS)薄膜電晶體(TFTs)。其中,鎳金屬誘發複晶矽薄膜有鎳金屬殘留的問題,因此發展出有效的鎳金屬捉聚 (Ni-gettering)方法來降低鎳金屬誘發複晶矽薄膜中的鎳金屬殘留,論文中所提出的鎳金屬捉聚結構為鎳金屬捉聚層/蝕刻停止層。鎳金屬捉聚層採用非晶矽薄膜及磷佈植非晶矽薄膜二種,厚度為 100 nm。蝕刻停止層為化學法製備之二氧化矽(Chemical oxide, chem-SiO<sub>2</sub>),厚度約 5 nm。論文最後應用此鎳金屬捉聚法於鎳金屬誘發側向結晶複晶矽薄膜電晶體及矽奈米線通道電晶體(Si NW channel transistors)製作上,以探討鎳金屬對元件特性的影響。

首先,利用非晶矽薄膜及化學法製備之二氧化矽作為鎳金屬捉聚基版,成功將複晶矽中殘餘鎳捕捉至鎳金屬捉聚基板中。由 SEM 分析可發現鎳金屬捉聚後聚集在兩相鄰鎳金屬誘發側向結晶晶界(NILC/NILC boundary)的 NiSi<sub>2</sub> 蝕刻孔洞明顯減少。此種捉聚方

I

式,是藉由濃度梯度的擴散使得複晶矽中殘餘鎳金屬能成功的透過蝕刻停止層捕捉至上層鎳金屬捉聚層,因此可發現上層非晶矽由於鎳金屬的擴散而成長出鎳金屬誘發側向結晶複晶矽。此方法與先前實驗室使用之非晶矽薄膜/電漿輔助化學沈積之氮化矽比較,可大大降低鎳金屬捉聚時間。其主要原因為鎳原子在氮化矽的擴散速度慢但通過化學氧化層卻速度快。

除此之外,為提高非晶矽薄膜之鎳金屬捉聚效率。進一步使用離子佈植法將磷雜質 (Phosphorus dopant)佈植於非晶矽薄膜中,成功提高捉聚層之鎳金屬溶解度。由 SEM 分析可發現鎳金屬捉聚後聚集在兩相鄰鎳金屬誘發側向結晶晶界的 NiSi<sub>2</sub> 蝕刻孔洞幾乎不存在。磷離子佈植法雖可以提升鎳金屬捉聚效率,但其佈植濃度在 1x10<sup>16</sup> cm<sup>-2</sup> 才有明顯效果。且由 SIMS 分析結果發現鎳在捉聚層的分佈與磷佈植曲線相當一致。

#### 1896

將鎳金屬捉聚法應用在鎳金屬誘發側向結晶複晶矽薄膜電晶體製備上,從元件特性得知,鎳金屬誘發側向結晶複晶矽薄膜電晶體在經過鎳捉聚處理後,可獲得較佳的電特性及均勻性,如降低漏電流(Leakage current)及抑制臨界電壓(Threshold voltage)負偏移等,其主要原因為鎳金屬誘發側向結晶複晶矽薄膜之鎳金屬殘留量可有效降低。

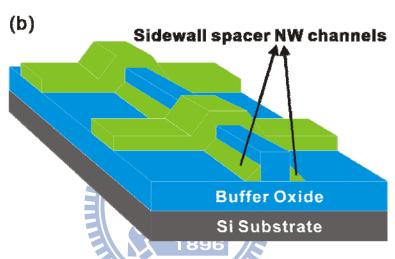

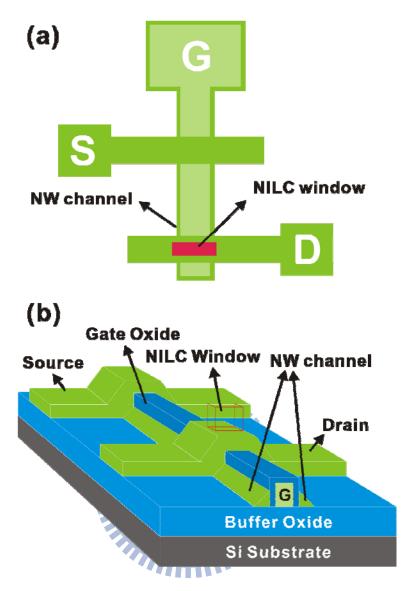

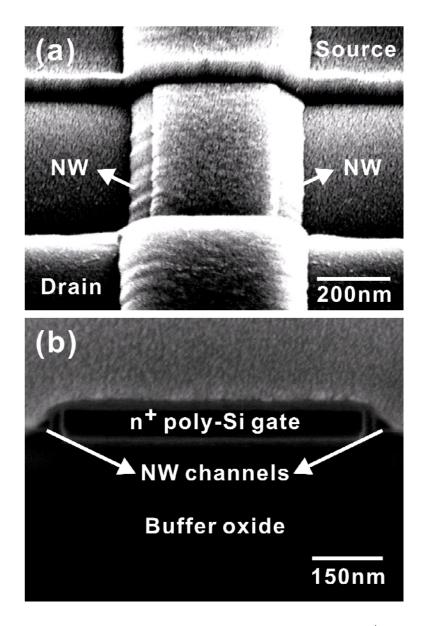

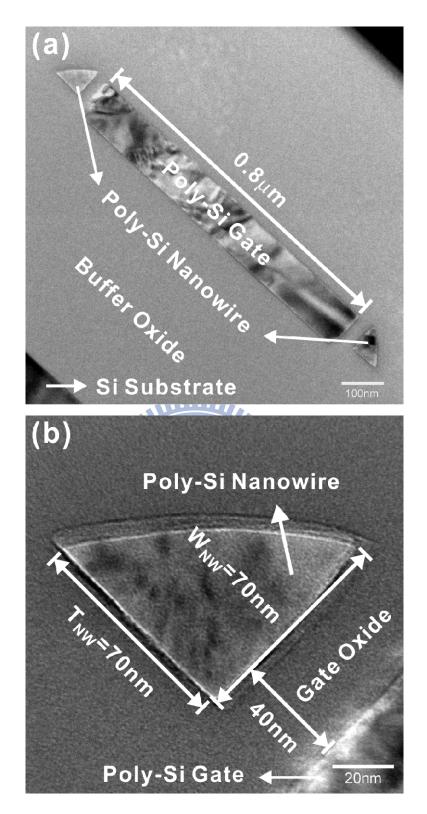

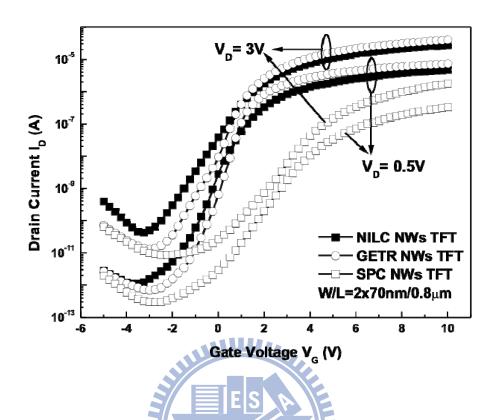

最後利用一個簡單及低成本的方法去製作矽奈米線通道電晶體。其製備之特點為利用一般製作 MOSFET 元件的側壁邊襯(Sidewall spacer)之概念,以底閘極薄膜電晶體結構在定義汲極和源極之同時,可自我對準形成奈米線通道。此複晶矽邊襯奈米線縱剖面近似三角形,其寬度及厚度可以控制至 70 nm。此奈米線通道薄膜電晶體比一般傳統薄膜

電晶體有比較好的通道控制能力。且經由鎮金屬捉聚處理後,鎮金屬誘發側向結晶複晶 矽奈米線通道電晶體在電性與均勻性上獲得提升。主要原因為多晶矽邊襯奈米線通道內 及其與氧化層之介面鎳金屬殘留量減少。

關鍵字: 鎮捉聚、化學氧化層、磷雜質、鎮金屬誘發側向結晶、低溫複晶矽、奈米線、 薄膜電晶體、矽奈米通道電晶體、側壁邊襯、漏電流

**Improved Performance of NILC LTPS Thin-Film & Nanowire Transistors through Ni-Gettering**

Student: Bau-Ming Wang

Advisor: Dr. YewChung Sermon Wu

Department of Materials Science and Engineering

National Chiao Tung University

**Abstract**

Low temperature polycrystalline silicon (LTPS) Ni-metal induced lateral crystallization

(NILC) thin-film transistors (TFTs) have been investigated in this thesis. Ni impurities

trapped inside the NILC poly-Si films is an issue. Therefore the Ni-gettering method is

proposed to effectively reduce Ni residues within the NILC poly-Si films. It involves using

gettering layers/etching stop layers as the Ni-gettering structure. The 100-nm-thick top  $\alpha$ -Si

and phosphorous-doped  $\alpha$ -Si layers serve as the gettering layers, while the middle

~5-nm-thick chem-SiO<sub>2</sub> layer is used as an etching stop layer. Moreover the proposed

gettering method is utilized in the fabrication of LTPS NILC TFTs and Si nanowire (NW)

channel transistors to investigate the effect of Ni-metal inside poly-Si on the device

performance.

First, the α-Si film is employed to getter Ni-silicides within NILC poly-Si film and Ni

IV

reduction is demonstrated by SEM. After the gettering process, fewer and smaller silicide-etching holes are found at the NILC/NILC boundaries. It is found that top  $\alpha$ -Si films, Ni-gettering layers, transfer into NILC poly-Si verified by SEM. This means that during the gettering process, Ni atoms diffused from the NILC poly-Si film through chem-SiO<sub>2</sub> into the Ni-gettering layer due to the concentration gradient. Compared with the previous  $\alpha$ -Si/PECVD-SiN<sub>x</sub> study, the thermal budget is greatly reduced. It's because of low Ni diffusivity in SiN<sub>x</sub> films resulting a long annealing time as 90 h at 550°C in N<sub>2</sub> ambient.

In order to improve the Ni-gettering efficiency, phosphorous-doped  $\alpha$ -Si films are further used by ion implantation. After a gettering process, there are almost no silicide-etching holes observed at the NILC/NILC boundaries. These results indicate that phosphorous dopants could improve the gettering efficiency of  $\alpha$ -Si due to the solubility enhancement of Ni impurities. But the gettering efficiency do not obviously improves until doping phosphorus ions reach a dose of  $1\times10^{16}$  cm<sup>-2</sup>. The concentration distribution of Ni is similar to that of phosphorous atoms since the projection range of phosphorous ions is set at the middle of the  $\alpha$ -Si film. This result also indicates that phosphorus could trap Ni atoms.

The proposed gettering method is further utilized in the fabrication of LTPS NILC TFTs.

As NILC TFTs are treated with a Ni-gettering process, they reveal lower leakage current, higher on/off current ratio, higher mobility, and better uniformity. These improvements are

all attributed to the reduction of Ni impurities in gettered poly-Si films.

Finally, a simple method and low-cost process is used to manufacture the NW channels. The feature of process is the method of forming sidewall spacer of MOSFET. The poly-Si sidewall spacer NW channels self-alignment form in the process of defining source/drain (S/D). Both the vertical width (W<sub>NW</sub>) and the horizontal sidewall thickness (T<sub>NW</sub>) of poly-Si NWs are about 70 nm. The cross-section of fabricated poly-Si NWs is similar to triangular shape by an anisotropic etching. Compared with the traditional TFTs, the side-gated NWs TFTs have higher channel controllability. Moreover, the performance of NILC NWs TFTs is improved after a Ni-gettering process. This is because of the reduction of Ni and NiSi<sub>2</sub> precipitates randomly trapped at poly-Si/gate oxide interfaces and poly-Si grain boundaries.

Keywords: Ni-Gettering, Chemical Oxide (chem-SiO<sub>2</sub>), Phosphorus Dopant, Nickel-Metal Induced Lateral Crystallization (NILC), Low Temperature Polycrystalline Silicon (LTPS), Nanowire (NW), Thin-Film Transistors (TFTs), Si Nanowire Channel Transistors, Sidewall Spacer, Leakage Current

### 誌謝

感謝指導教授<u>吳耀銓</u>博士在我博士生涯後半段給予辛勤的指導與提攜,在生活上及 論文研究上給予關懷及協助。也感謝<u>涂筆嘉</u>博士及<u>蔡明蒔</u>博士在碩士班期間及博士生涯 前半段的指導。另外感謝口試委員交通大學材料所<u>陳智</u>博士、<u>吳文偉</u>博士與隆達電子副 理<u>趙志偉</u>博士、工研院顯示所<u>胡國仁</u>博士,在博士論文口試時,對論文研究給予意見與 指導,讓本論文更加完備。

其次感謝交通大學奈米元件中心、國家奈米元件實驗室在實驗設備上的支持及協助。此外感謝國家奈米元件實驗室<u>李美儀</u>小姐、賴東彥先生、楊子明先生、吳鴻佑先生、孫旭昌先生、許倬綸先生、趙國芬小姐、賴明志先生、楊忠諺博士及蘇旺申博士等人在研究上的協助。也要感謝交通大學奈米元件中心何惟梅小姐、徐綉鑾小姐、范秀蘭小姐、蘇俊榮博士的幫助,讓我在奈米中心的實驗能順利完成。

由衷感謝實驗室的<u>趙志偉</u>學長、<u>胡國仁</u>學長、<u>侯智</u>元學長、<u>胡晟民、施協志、廖崢、</u> <u>1896</u> <u>1898</u> <u>1898</u>

僅此論文獻給我的家人,感謝他們在我求學期間給予無私的包容與支持,讓我在研 究上能無後顧之憂。

2010年2月于新竹交大

### **Contents**

| Abstract (Chinese) ı                                                                      |

|-------------------------------------------------------------------------------------------|

| Abstract (English)ıv                                                                      |

| Acknowledgment (Chinese)vıı                                                               |

| Contentsviii                                                                              |

| Figure Captionsxı                                                                         |

| Table Listsxvi                                                                            |

| Chapter 1 Introduction                                                                    |

| 1.1 An Overview of Polycrystalline Silicon Thin-Film Transistors (TFTs)                   |

| 1.2 Low-Temperature Polycrystalline Silicon (LTPS) Crystallization 4                      |

| 1.2.1 Solid-Phase Crystallization (SPC)                                                   |

| 1.2.2 Metal-Mediated Induced Crystallization 5                                            |

| 1.3 Metal Gettering from Silicon                                                          |

| 1.4 Silicon Nanowires (NWs) Fabrication                                                   |

| 1.4.1 Top-Down Method                                                                     |

| 1.4.2 Bottom-Up Method                                                                    |

| 1.5 Motivation and Thesis Organization                                                    |

| Chapter 2 Ni Reduction of Nickel-Mediated Crystallization Polycrystalline Silicon Using A |

| Ni-Gettering Process23                                                                    |

| ۷.                                 | .1             | Introd                                                          | uction                                                                    | 23                                                  |

|------------------------------------|----------------|-----------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|

| 2.                                 | .2             | Experi                                                          | mental Procedure2                                                         | 24                                                  |

|                                    |                | 2.2.1                                                           | Gettering of Ni Residues from NILC Poly-Si Films                          | 24                                                  |

|                                    |                | 2.2.2                                                           | Gettering of Ni Residues from NIC Poly-Si Films 2                         | 26                                                  |

|                                    |                | 2.2.3                                                           | Dopant Effect on NILC Rate                                                | 29                                                  |

| 2.                                 | .3             | Result                                                          | s and Discussion 3                                                        | 80                                                  |

|                                    |                | 2.3.1                                                           | Characterization of NILC Poly-Si Films                                    | 80                                                  |

|                                    |                | 2.3.2                                                           | Quality of chem-SiO <sub>2</sub> Layers                                   | 80                                                  |

|                                    |                | 2.3.3                                                           | Ni-Gettering Using chem-SiO <sub>2</sub> Interlayer                       | 35                                                  |

|                                    |                | 2.3.4                                                           | Improved Ni-Gettering Efficiency by Phosphorus Ions Implant 3             | 88                                                  |

|                                    |                | 2.3.5                                                           | Effect of Phosphorus Ions and Implant Damages on NILC Rate 4              | <b>1</b> 7                                          |

| 2.                                 | .4             | Summ                                                            | ary4                                                                      | 18                                                  |

|                                    |                |                                                                 |                                                                           |                                                     |

| Chapter                            | 3 I            | Using F                                                         | Phosphorous-Doped $\alpha$ -Si Gettering Layer to Improve NILC Poly-Si TF |                                                     |

|                                    |                |                                                                 |                                                                           |                                                     |

| Performa                           | anc            | e                                                               | 1896                                                                      | 52                                                  |

| Performa                           | anc<br>.1      | e                                                               |                                                                           | 5 <b>2</b>                                          |

| Performa 3.                        | .1<br>.2       | e<br>Introde                                                    | uction 5                                                                  | 5 <b>2</b>                                          |

| Performa 3.                        | .1<br>.2       | e<br>Introde                                                    | uction 5                                                                  | 52<br>52<br>53                                      |

| Performa 3.                        | .1<br>.2       | Introde Device                                                  | Fabrication 5                                                             | 52<br>53<br>56                                      |

| Performa 3.                        | .1<br>.2       | Introde Device Results 3.3.1                                    | T896  uction                                                              | 52<br>53<br>56<br>56                                |

| Performa 3. 3.                     | .1<br>.2<br>.3 | Device<br>Results<br>3.3.1<br>3.3.2<br>3.3.3                    | Fabrication                                                               | 52<br>52<br>53<br>56<br>56                          |

| Performa  3.  3.  3.               | .1<br>.2<br>.3 | Introde<br>Device<br>Results<br>3.3.1<br>3.3.2<br>3.3.3<br>Summ | Fabrication                                                               | 52<br>53<br>56<br>56<br>56<br>56                    |

| Performa 3. 3. 3. Chapter          | .1<br>.2<br>.3 | Introde<br>Device<br>Results<br>3.3.1<br>3.3.2<br>3.3.3<br>Summ | Fabrication                                                               | 52<br>53<br>56<br>56<br>56<br>56                    |

| Performa 3. 3. 3. Chapter Ni-Gette | .1<br>.2<br>.3 | Introde Device Results 3.3.1 3.3.2 3.3.3 Summ                   | Tabrication                                                               | 52<br>52<br>53<br>56<br>56<br>56<br>56<br><b>gh</b> |

| 4.2         | Device   | Fabrication                                             | 71  |

|-------------|----------|---------------------------------------------------------|-----|

| 4.3         | Results  | s and Discussion                                        | 77  |

|             | 4.3.1    | Characterization of Fabricated Poly-Si NWs              | 77  |

|             | 4.3.2    | Device Performances of Poly-Si NWs TFTs                 | 77  |

|             | 4.3.3    | Uniformity Improved in Poly-Si NWs TFTs by Ni-Gettering | 83  |

| 4.4         | Summ     | ary                                                     | 87  |

| Chapter 5 ( | Conclusi | ons and Future Work                                     | 88  |

| 5.1         | Conclu   | isions                                                  | 88  |

| 5.2         | Future   | Work                                                    | 90  |

| References  |          |                                                         | 92  |

| Vita        |          |                                                         |     |

| Publication | List     | 1896                                                    | 105 |

|             |          |                                                         |     |

# **Figure Captions**

| Figure | 1-1 The device structure of a top-gated thin-film transistor (TFT) 3                                                                                                                                                                                                                                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 1-2 The crystalline structures: (a) the diamond structure of Si and (b) the fluorite structure NiSi <sub>2</sub> 7                                                                                                                                                                                                                                                           |

| Figure | 1-3 The formation temperature map of thin-film Ni silicides on (a) $\alpha$ -Si, and (b) c-Si [44]                                                                                                                                                                                                                                                                           |

| Figure | 1-4 The equilibrium molar free-energy diagram for NiSi $_2$ in contact with $\alpha$ -Si and c-Si [38]9                                                                                                                                                                                                                                                                      |

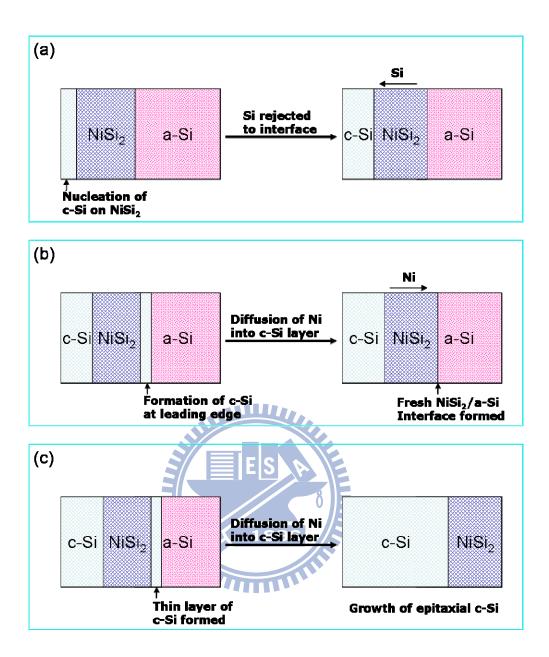

| Figure | 1-5 A possible modification of the c-Si growth mechanism involving the formation of a thin layer of c-Si at the $\alpha$ -Si/NiSi <sub>2</sub> interface [38]11                                                                                                                                                                                                              |

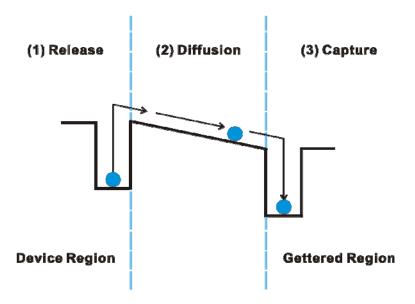

| Figure | 1-6 The concept of the gettering process including release, diffusion, and capture of the metal impurities [47].————————————————————————————————————                                                                                                                                                                                                                         |

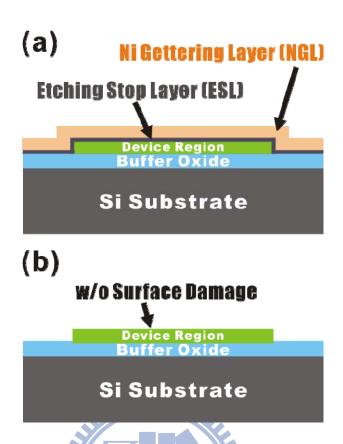

| Figure | 1-7 (a) A gettering structure with a Ni gettering layer and an etching stop layer, and (b) the device region protected well by an etching stop layer during the removal of the Ni gettering layer16                                                                                                                                                                          |

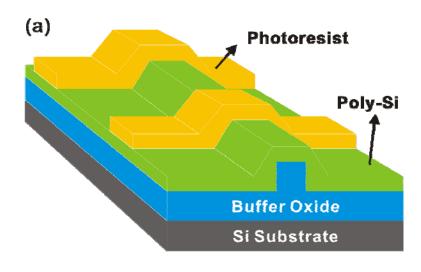

| Figure | 1-8 (a) Photoresist patterns on top of the poly-Si surface by the conventional lithography, and (b) the sidewall spacer NW channels fabricated by an anisotropic etching.————————————————————————————————————                                                                                                                                                                |

| Figure | 2-1 Schematic illustration of the Ni-gettering process: (a) fabrication of the NILC poly-Si film, (b) removal of unreacted Ni pads, (c) capped with an etching stop layer (chem-SiO <sub>2</sub> ) and a gettering layer ( $\alpha$ -Si or p- $\alpha$ -Si), and (d) removal of the gettering layer and the chem-SiO <sub>2</sub> layer.———————————————————————————————————— |

| Figure 2-2 Schematic illustration of the Ni-gettering process of the NIC poly-Si: (a) fabrication                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| of the NIC poly-Si film (b) removal of unreacted Ni films, and (c) capped with a                                                            |

| chem-SiO $_2$ layer and a gettering layer ( $\alpha\text{-Si}$ or p- $\alpha\text{-Si}$ )28                                                 |

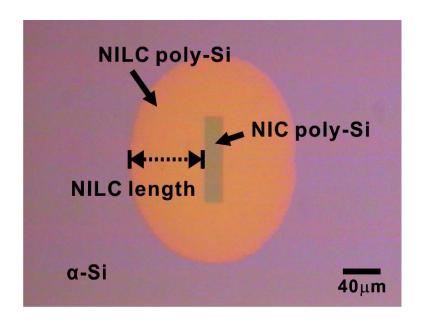

| Figure 2-3 OM image of the $\alpha$ -Si film after a NILC process carried out at $540^{\circ}$ C for 24 h in $N_2$                          |

| ambient31                                                                                                                                   |

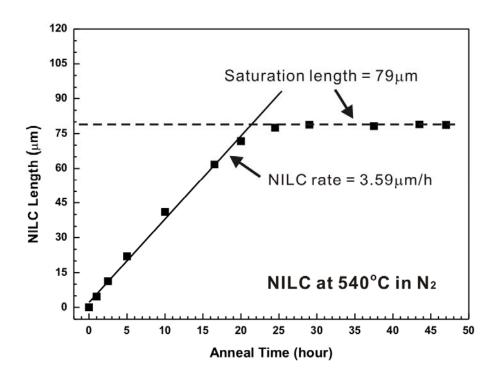

| Figure 2-4 The dependence of the NILC length on the anneal time. The NILC was carried out                                                   |

| at $540^{\circ}\text{C}$ in $N_2$ ambient32                                                                                                 |

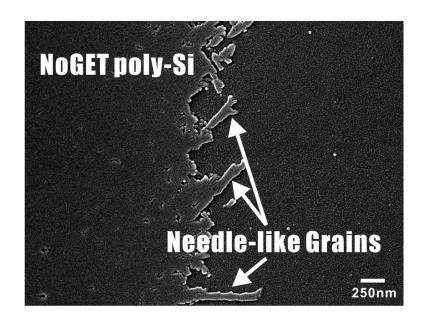

| Figure 2-5 SEM image of the NILC poly-Si grains treated with Secco-etching33                                                                |

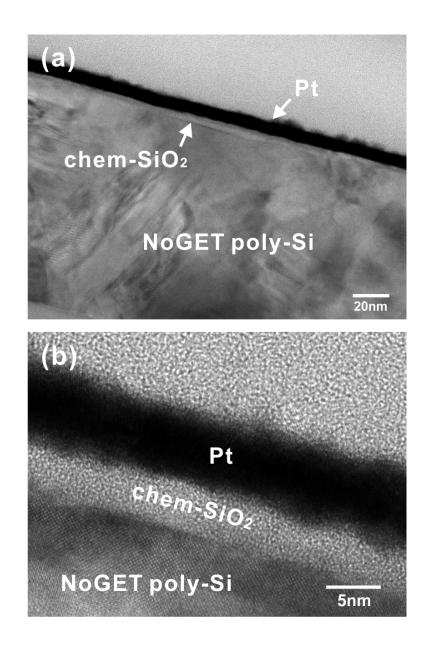

| Figure 2-6 (a) Cross-sectional TEM images of the NILC Poly-Si films capped with the chemical                                                |

| oxide films, and (b) the high magnification of a chemical oxide film around 5 nm thick.                                                     |

| Platinum (Pt) films were deposited on top of the chem-SiO <sub>2</sub> layers for image contrast.                                           |

| 34                                                                                                                                          |

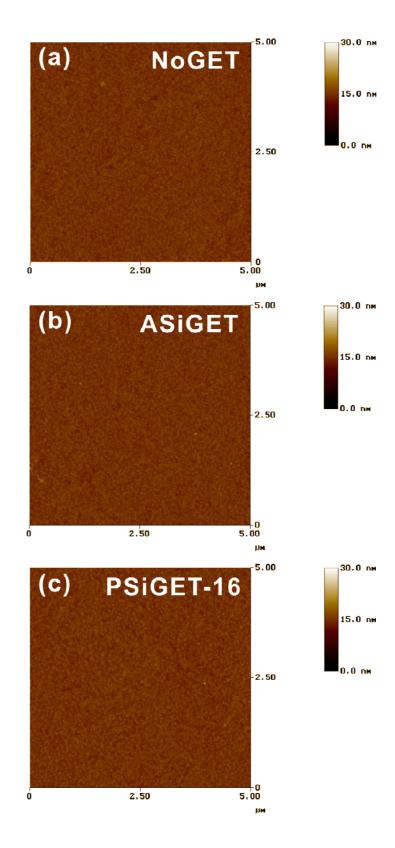

| Figure 2-7 AFM images of the NILC poly-Si surfaces (a) without Ni-gettering, and with                                                       |

| Ni-gettering by (b) a $\alpha$ -Si layer, and (c) a p- $\alpha$ -Si layer (the dosage was $1\times10^{16}$ cm $^{-2}$ )36                   |

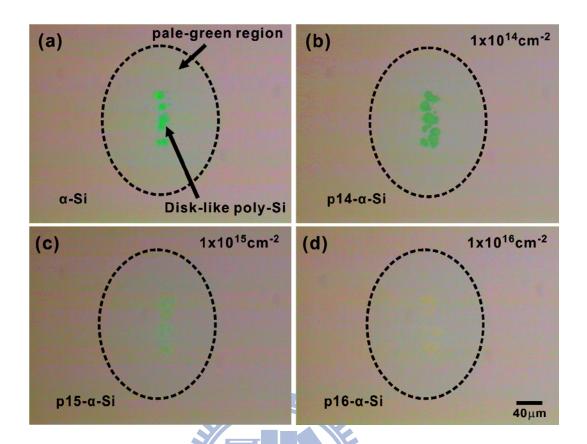

| Figure 2-8 OM images of the Ni-gettering layers: (a) a $\alpha$ -Si film deposited on a chem-SiO $_2$                                       |

| layer by LPCVD and then phosphorous ions implanted at a dosage of (b) $1\times10^{14}$ cm <sup>-2</sup> ,                                   |

| (c) 1×10 <sup>15</sup> cm <sup>-2</sup> , and (d) 1×10 <sup>16</sup> cm <sup>-2</sup> , respectively37                                      |

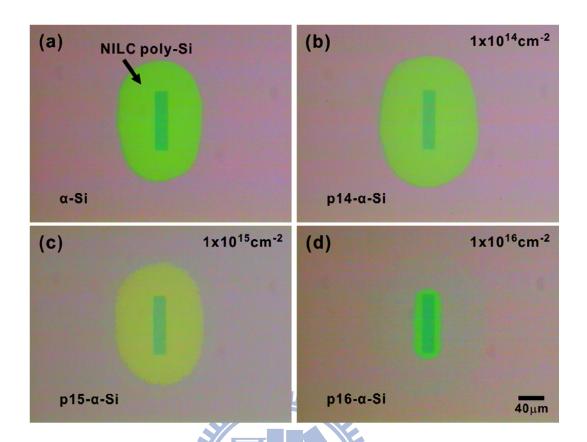

| Figure 2-9 OM images of the Ni-gettering phenomenon by (a) a $\alpha$ -Si film, and the                                                     |

| phosphorous-doped $\alpha$ -Si films at a dosage of (b) $1\times10^{14}$ cm <sup>-2</sup> , (c) $1\times10^{15}$ cm <sup>-2</sup> , and (d) |

| 1×10 <sup>16</sup> cm <sup>-2</sup> , respectively39                                                                                        |

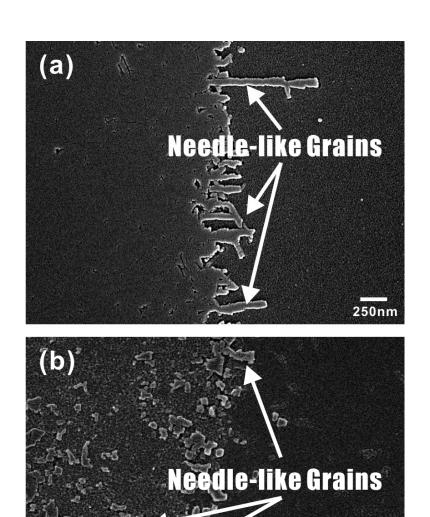

| Figure 2-10 SEM images of the NILC poly-Si grains of Ni-gettering layers: (a) a $\alpha$ -Si film, and (b                                   |

| a phosphorous-doped $\alpha$ -Si film at a dosage of $1\times10^{16}~\text{cm}^{-2}$ . Samples were treated                                 |

| with Secco-etching40                                                                                                                        |

| Figure 2-11 OM image of NILC/NILC boundary treated with TMAH etching42                                                                      |

| Figure 2-12 Schematic illustration of (a) silicide-etching holes at NILC/NILC boundaries, and                                               |

| and (f) PSiGET-16. Samples were treated with the silicide-etching solution43                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-13 (a) Cross-sectional TEM images of NIC Poly-Si films capped with chemical oxide films and gettering layers, and (b) the high magnification of a gettering layer around 110 nm thick. The gettering layer was implanted with 1×10 <sup>16</sup> cm <sup>-2</sup> phosphorous ions and the projection range (Rp) was about 50 nm in depth45                                                                                                                                                           |

| Figure 2-14 SIMS depth profiles of NIC poly-Si films treated with and without a Ni-gettering process46                                                                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2-15 NILC length vs. anneal time and different doping type. NILC was carried out at $540^{\circ}\text{C}$ in $N_2$ ambient49                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 2-16 NILC length vs. different doping type and dose after heat treatment at $540^{\circ}$ C for 16 h in $N_2$ ambient.——————50                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 3-1 Schematic illustration of the TFTs device fabrication: (a) the top view of the fabricated device, (b) fabrication of NILC-Si, (c) capped with an etching stop layer (chem-SiO <sub>2</sub> ) and a gettering layer (p- $\alpha$ -Si), (d) removal of the gettering layer and chem-SiO <sub>2</sub> layer, (e) capped with a low-temperature oxide (LTO) as gate-oxide and a $\alpha$ -Si film as gate material, and (f) capped with a LTO as the isolation layer and fabrication of Al electrodes54 |

| Figure 3-2 (a) OM image of the $\alpha$ -Si film after a NILC process carried out at 540°C for 24 h in $N_2$ ambient, and (b) SEM image of the NILC poly-Si grains treated with Secco-etching.                                                                                                                                                                                                                                                                                                                 |

| Figure 3-3 OM images of (a) a Ni-gettering layer, $\alpha$ -Si film, deposited on a chem-SiO $_2$ layer by LPCVD, and (b) the Ni-gettering phenomenon by a phosphorous-doped $\alpha$ -Si film at a dosage of $1\times10^{16}$ cm $^{-2}$ 58                                                                                                                                                                                                                                                                   |

| Figure 3-4 Schematic illustration of (a) silicide-etched holes at NILC/NILC boundaries, and SEM images of these holes in (b) the NILC-Si films and (c) the GETR-Si films. Samples                                                                                                                                                                                                                                                                                                                              |

| were treated with the silicide-etching solution60                                                                   |

|---------------------------------------------------------------------------------------------------------------------|

| Figure 3-5 Typical $I_D$ - $V_G$ transfer curves of the NILC TFT and the GETR TFT measured at $V_D$ = $\frac{1}{2}$ |

| V and $V_D$ = 0.1 V, respectively61                                                                                 |

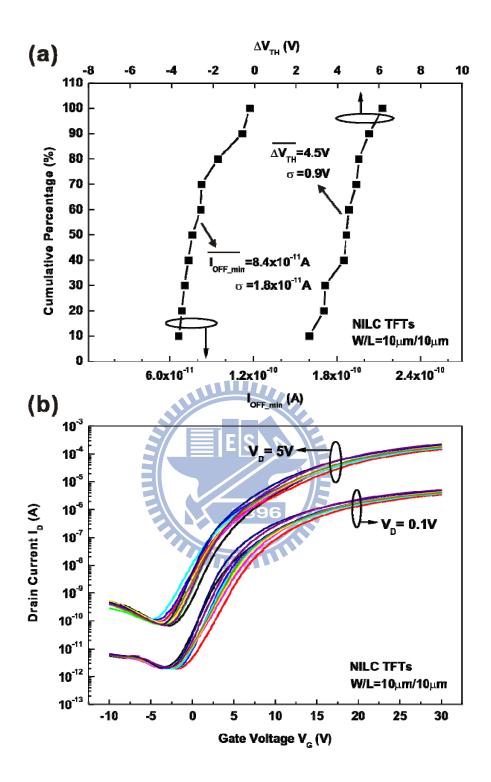

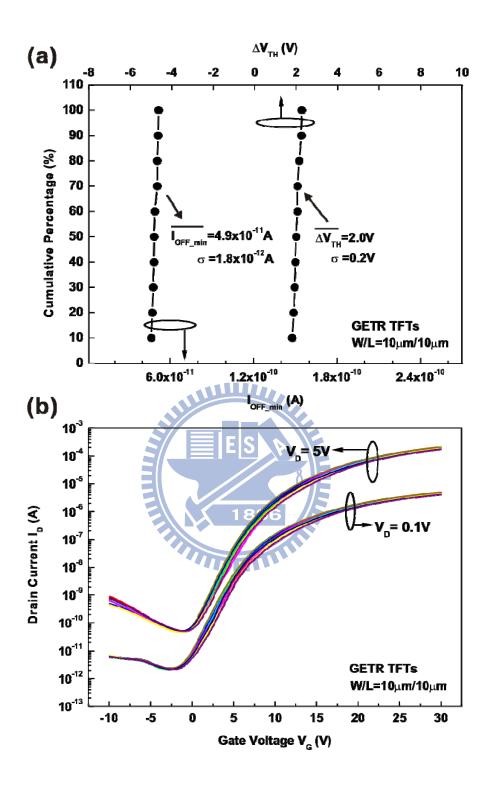

| Figure 3-6 (a) $\triangle V_{TH}$ and $I_{OFF\_min}$ were measured in ten NILC TFTs to investigate the              |

| device-to-device variation, and (b) the $I_D$ - $V_G$ transfer curves of ten NILC TFT                               |

| measured at $V_D$ = 5 V and $V_D$ = 0.1 V, respectively67                                                           |

| Figure 3-7 (a) $\triangle V_{TH}$ and $I_{OFF\_min}$ were measured in ten GETR TFTs to investigate the              |

| device-to-device variation, and (b) the $I_D\text{-}V_G$ transfer curves of ten GETR TFT                            |

| measured at $V_D$ = 5 V and $V_D$ = 0.1 V, respectively68                                                           |

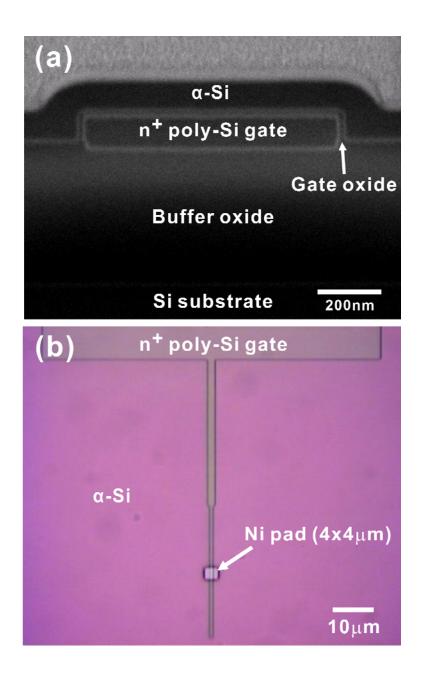

| Figure 4-1 (a) Cross-sectional SEM image of a 100-nm-thick LPCVD $\alpha\text{-Si}$ film capped on                  |

| 40-nm-thick TEOS oxide, and (b) OM image of a 4x4 $\mu m$ Ni pad on a $\alpha$ -Si film before                      |

| basic NILC process72                                                                                                |

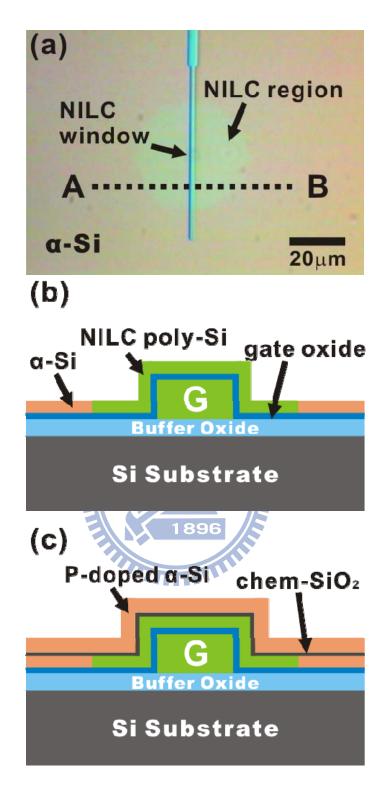

| Figure 4-2 (a) OM image of NILC poly-Si after annealing at $540^{\circ}$ C for 24 h in N <sub>2</sub> ambient, (b   |

| the cross-sectional view along the dashed line A to B in Fig. 4-2a, and (c) the                                     |

| Ni-gettering structure. 1896                                                                                        |

| Figure 4-3 (a) Top view of the proposed NILC poly-Si NWs TFT structure, and (b) the 3-I                             |

| schematic of poly-Si NWs TFTs75                                                                                     |

| Figure 4-4 SEM images of (a) top view and (b) side view of the source/drain (S/D) formation                         |

| with a couple of poly-Si NW channels after an anisotropic etching76                                                 |

| Figure 4-5 (a) Cross-sectional TEM image of the NILC NWs TFT with a couple of poly-Si NV                            |

| channels, and (b) the high magnification of poly-Si NWs in Fig. 4-3a78                                              |

| Figure 4-6 Comparison of transfer characteristics among SPC, NILC, and GETR NWs TFTs80                              |

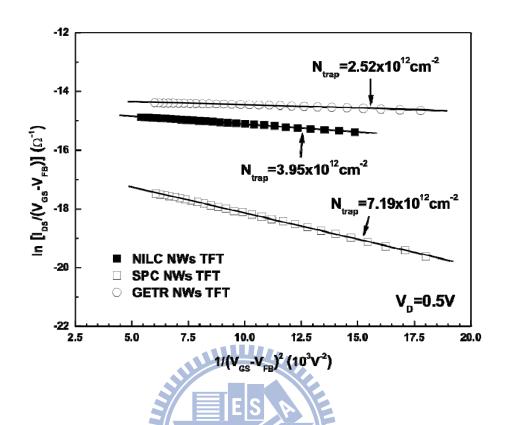

| Figure 4-7 Plot of $ln(I_D/V_G-V_{FB})$ versus $1/(V_G-V_{FB})^2$ and the extracted trap state density of SPC       |

| NILC and GETR NWs TFTs. $I_D$ was measured at $V_D = 0.5$ V82                                                       |

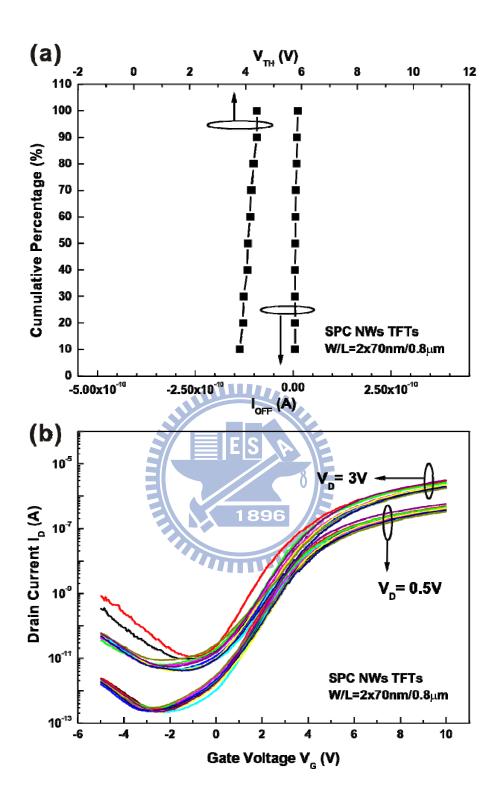

| Figure 4-8 (a) $V_{\text{TH}}$ and $I_{\text{OFF}}$ were measured in ten SPC NWs TFTs to investigate the            |

|        | device-to-device variation, and typical I <sub>D</sub> -V <sub>G</sub> transfer curves of ten (b) SPC NWs                                     | TFTs |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

|        | measured at $V_D$ = 3 V and $V_D$ = 0.5 V, respectively                                                                                       | -84  |

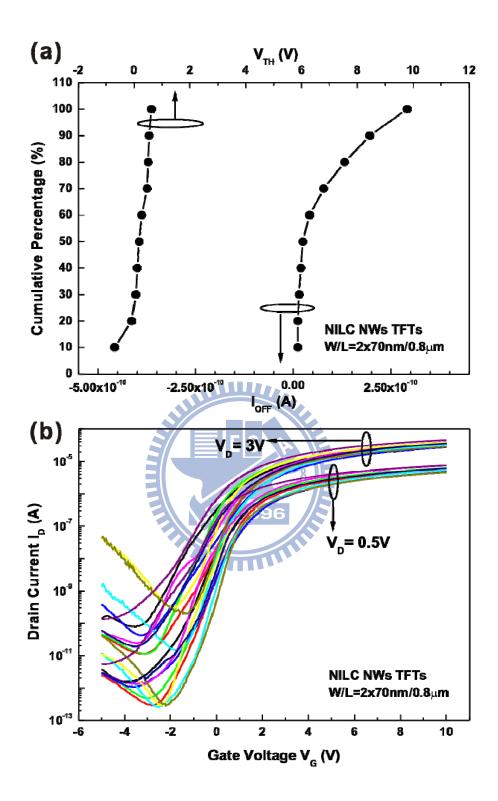

| Figure | 4-9 (a) $V_{\text{TH}}$ and $I_{\text{OFF}}$ were measured in ten NILC NWs TFTs to investigate                                                | the  |

|        | device-to-device variation, and typical $I_{\text{\scriptsize D}}\text{-}V_{\text{\scriptsize G}}$ transfer curves of ten (b) NILC NWs $^{-}$ | TFTs |

|        | measured at $V_D$ = 3 V and $V_D$ = 0.5 V, respectively                                                                                       | -85  |

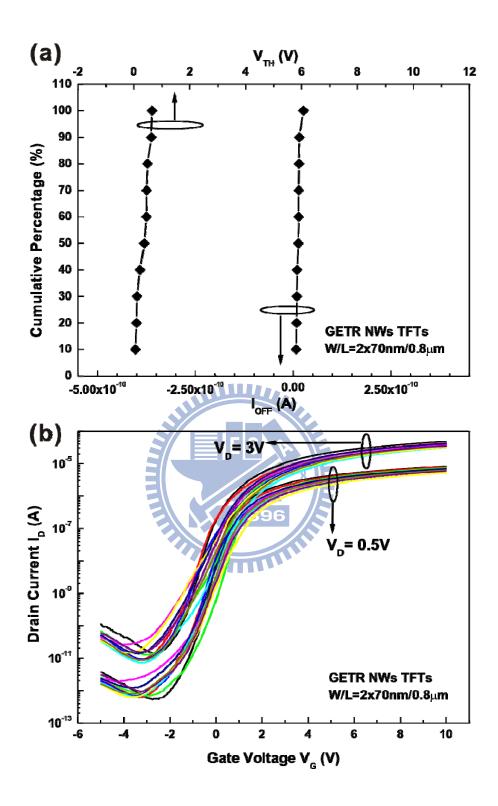

| Figure | 4-10 (a) $V_{\text{TH}}$ and $I_{\text{OFF}}$ were measured in ten NILC NWs TFTs to investigate                                               | the  |

|        | device-to-device variation, and typical $I_D\text{-}V_G$ transfer curves of ten (b) NILC NWs $^{-}$                                           | TFTs |

|        | measured at $V_D$ = 3 V and $V_D$ = 0.5 V, respectively                                                                                       | -86  |

## **Table Lists**

| Table 2-1 Relevant parameters of the Ni-gettering layers             | 27                    |

|----------------------------------------------------------------------|-----------------------|

| Table 3-1 Device characteristics of the NILC TFTs and the GETR TFTs. |                       |

| Table 4-1 Device characteristics of NILC, GETR and SPC NWs TFTs.     | Data were measured in |

| ten devices, respectively,                                           | 81                    |

### **Chapter 1 Introduction**

Low-temperature polycrystalline silicon (LTPS) thin-film transistors (TFTs) have attracted considerable interest for their use in active-matrix liquid crystal displays (AMLCDs) [1-3] and active-matrix organic light emitting displayers (AMOLEDs) [4-6] because they exhibit good electrical properties and can be integrated in peripheral circuits on inexpensive glass substrates. Since polycrystalline silicon (poly-Si) TFTs require glass substrates, intensive studies have been carried out to lower the crystallization temperature of amorphous silicon ( $\alpha$ -Si) films. Ni-metal induced lateral crystallization (NILC) is one of these efforts. [7-12] Unfortunately, the NILC poly-Si grain boundaries trap Ni and NiSi<sub>2</sub> precipitates, which increase the leakage current and shift the threshold voltage. [12–16] Therefore, Ni contamination inside the NILC poly-Si film should be reduced. The goal of this work is to getter nickel impurities within NILC poly-Si to improve the performance of LTPS NILC TFTs.

In this chapter, an overview of poly-Si TFTs is first reviewed. Then the processes of low temperature poly-Si crystallization and the metal gettering from Si are introduced. Finally, the architectures of LTPS NILC nanowires (NWs) for improving the performance of TFTs are discussed, followed with the motivation of this work.

### 1.1 An Overview of Polycrystalline Silicon Thin-Film Transistors (TFTs)

The  $\alpha$ -Si TFTs as the pixel switching device for active matrix liquid crystal displays (AMLCDs) is the mainstream technology due to low processing temperature (<350°C) compatible with the glass substrate. [17, 18] However the poor field-effect mobility (typically < 1 cm²/Vs) and the small on-current in  $\alpha$ -Si TFTs limit themselves as the switching elements only. Therefore, the poly-Si becomes an attractive candidate for AMLCDs.

In 1980, the high temperature poly-Si TFTs with electron field-effect mobility around 50 cm<sup>2</sup>/Vs were proposed. [19] This technique requires a high strain temperature substrate such as quartz, due to the gate insulator SiO<sub>2</sub> grown thermally at  $1050^{\circ}$ C. Hence several techniques for poly-Si TFTs fabrication at low temperature (below  $600^{\circ}$ C) began in 1980s. The low-cost glass replaced quartz substrate and made high-definition AMLCD more practical and less expensive. In fact, the field effect mobility in poly-Si TFTs is significantly higher than that of  $\alpha$ -Si about two orders of magnitudes. [20] The higher drive current allows small TFTs to be used as the pixel switching elements, resulting in higher aperture ratio and lower parasitic gate-line capacitance for improved display performance. [21]

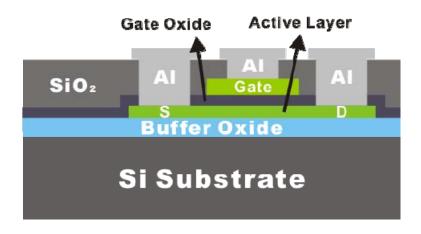

Device structure of TFTs unlike MOSFETs, the active layer separately forms on the substrate, as shown in Fig 1-1. The quality of crystallized poly-Si films is therefore quite sensitive to the performance of poly-Si TFTs. The crystallized poly-Si fabricated by various

**Figure 1-1** The device structure of a top-gated thin-film transistor (TFT).

techniques at low temperature such as: (1) solid phase crystallization (SPC), (2) Ni-metal induced lateral crystallization (NILC) will be reviewed in detail.

### 1.2 Low-Temperature Polycrystalline Silicon (LTPS) Crystallization

The most important step in the fabrication of LTPS TFTs has been considered as the crystallization of  $\alpha$ -Si films. The quality of crystallized poly-Si films plays an important role on the performance of poly-Si TFTs. Historically, solid phase crystallization (SPC) [22] is the first technology to produce poly-Si films for display applications, followed by metal mediated induced crystallization. The ultimate goal of the LTPS technology is to integrate the pixel-driving circuits on the display substrate. These two low-temperature poly-Si crystallization methods are introduced as follows:

#### 1.2.1 Solid-Phase Crystallization (SPC)

Amorphous Si ( $\alpha$ -Si) is a thermodynamically meta-stable phase. It requires a sufficient energy to overcome the initial energy barrier for transformation to polycrystalline phase. The transformation is carried out by annealing in a furnace at certain temperature (typically at  $600^{\circ}$ C) for duration time (about 24 h) to break and reorganize Si bonds. Since the solid state still stays during the phase transformation, the technique is called solid-phase crystallization (SPC). Deposited  $\alpha$ -Si thin films transformed to poly-Si using SPC method have obtained better TFT device electrical performance than as-deposited poly-Si films. [23]

In general, the poly-Si crystallized from  $\alpha$ -Si usually has larger grain size than that of as-deposited poly-Si. Most defects are generated at the grain boundaries in poly-Si films.

The phase transformation occurs through two processed, the nucleation and grain growth, and both have characteristic activation energies. [24] The nucleation activation energy is normally larger than the grain growth activation energy. [25] To enlarge poly-Si grains by SPC, it's necessary to suppress nucleation; therefore SPC is typically carried out at low temperature. Higher disorder structure requires higher energy barrier to form the Si nuclei. [26, 27] Hence SPC poly-Si grain size could be controlled by the selected  $\alpha$ -Si deposition method and condition.

Moreover, many surface-nucleation techniques during SPC are proposed to improve the 1896 quality of poly-Si films by oxygen [28], silicon [29], argon [30] doping at  $\alpha$ -Si/SiO<sub>2</sub> interface. After ion implantation, the heterogeneous nucleation at  $\alpha$ -Si/SiO<sub>2</sub> interface is suppressed, and fewer homogeneous nucleation sites initiate on the top free surface of  $\alpha$ -Si films. Therefore the larger SPC poly-Si grain size could be obtained.

### 1.2.2 Metal-Mediated Induced Crystallization

Several techniques based on the crystallization of the  $\alpha$ -Si film were reported since 1964 as Wagner and Ellis [31] found that the presence of small amounts of a metallic phase could enhance the Si crystal growth. In general, two groups can be classified in the MIC/MILC

mechanism. One is to form eutectics with Si (AI [32], Au [33], and Sb [34]) and another is metastable silicide forming metals (Ni [35-38], Pd [39, 40] and Co [41]). For example, the Al/silicon eutectic temperature is  $577^{\circ}$ C [42], but crystallization and type conversion of  $\alpha$ -Si films in contact with Al occurs at temperatures as low as  $200^{\circ}$ C.

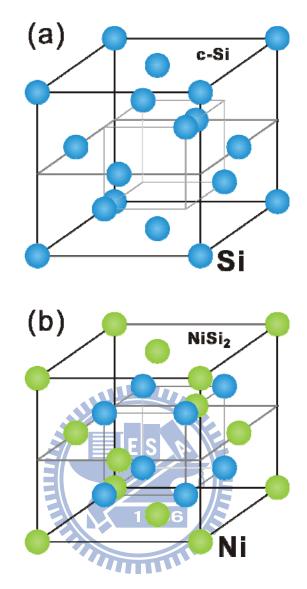

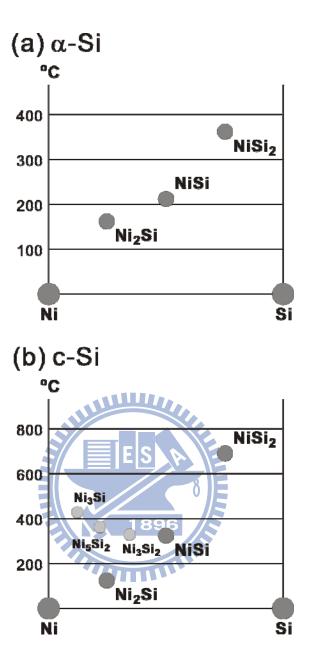

Figure 1-2 shows the diamond structure of Si and the fluorite structure of NiSi<sub>2</sub>. The lattice constant of Si and NiSi2 is 5.430 Å and 5.406 Å, respectively, leading to very small lattice mismatch of 0.4 % with Si. The Ni-metal is considerably suitable for the formation of epitaxial Si and is therefore employed for the fabrication of NILC poly-Si films in this thesis. When a Ni film is deposited on a c-Si substrate and annealed, the Ni<sub>2</sub>Si with PdCl<sub>2</sub> structure forms at ~200°C and transforms into NiSi with the MnP structure at 350-750°C. [43] These two phase-transformations are diffusion-controlled processes. Finally the NiSi transforms into the end phase NiSi2 by a nucleation-controlled process at high transformation temperature in the range 450-750°C. However, the NiSi transforming into the NiSi<sub>2</sub> is a diffusion-controlled process for the α-Si. Hence it's a low-temperature process as 350°C for NiSi<sub>2</sub> precipitate formation, as shown in Fig. 1-3 [44]. Subsequently, the NiSi<sub>2</sub> crystallites serve as the nuclei for crystallization. The diffusivity of Ni [45] in  $\alpha$ -Si is higher than that in c-Si. Thus the needle-like Si crystallite forms due to the diffusion of Ni in the  $\alpha$ -Si network.

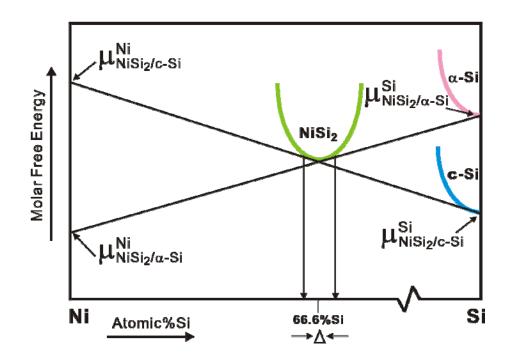

Figure 1-4 shows the equilibrium molar free-energy diagram [38] for NiSi<sub>2</sub> in contact

Figure 1-2 The crystalline structures: (a) the diamond structure of Si and (b) the fluorite structure  $NiSi_2$ .

Figure 1-3 The formation temperature map of thin-film Ni silicides on (a)  $\alpha$ -Si, and (b) c-Si [44].

Figure 1-4 The equilibrium molar free-energy diagram for  $\text{NiSi}_2$  in contact with  $\alpha\text{-Si}$  and c-Si

[38].

with α-Si and c-Si. Initially, several Ni-Si phases form in the silicide region and the NiSi<sub>2</sub> phase is found near the Si region [37]. The chemical potential of the Ni atoms is lower at the NiSi<sub>2</sub>/ $\alpha$ -Si interface and that of the Si atoms is lower at the NiSi<sub>2</sub>/c-Si interface. Thus there is a driving force for Ni atoms diffusing through NiSi<sub>2</sub> to α-Si and for Si atoms diffusing reversely. This result indicates that the  $\alpha$ -Si is consumed at the NiSi<sub>2</sub>/ $\alpha$ -Si during the migration of NiSi<sub>2</sub> crystallite. In 1993, C. Hayzelden and J. L. Batstone [38] found that a few layers of c-Si exist at the leading edge of the NiSi2 precipitate. Therefore they propose a possible modification of the growth mechanism, as shown in Fig 1-5. The nucleation of c-Si on NiSi2 initially occurs and Si atoms then diffuse through NiSi2 to c-Si, as illustrated in Fig. Next a c-Si nucleates at the leading edge of a migrating NiSi<sub>2</sub> precipitate. then diffuse through NiSi<sub>2</sub> to α-Si due to its ability to lower the chemical potential at the NiSi<sub>2</sub>/ $\alpha$ -Si, as shown in Fig 1-5b. A fresh c-Si forms at the NiSi<sub>2</sub>/ $\alpha$ -Si interface and the process repeats. Finally the needle-like Si crystallite is formed after the migration of NiSi<sub>2</sub> in a-Si network, as shown in Fig 1-5c

To enlarge poly-Si grain size, SPC is typically carried out at 600°C to increase the incubation time and decrease the grain growth rate. Therefore a long annealing time is required for the SPC method. In the NIC/NILC method, a short annealing time and the low temperature (>600°C) could be obtained, because of lower energy barrier of crystallization resulting from the reaction between Ni-metal and Si. However the undesirable Ni and NiSi<sub>2</sub>

Figure 1-5 A possible modification of the c-Si growth mechanism involving the formation of a thin layer of c-Si at the  $\alpha$ -Si/NiSi $_2$  interface [38].

precipitates would be trapped NILC poly-Si grain boundaries. The metal gettering from Si is a candidate to solve this issue.

### 1.3 Metal Gettering from Silicon

Transition-metals (Fe, Co, Ni and Pd) are ubiquitous in Si wafers, being introduced both during wafer growth and in subsequent processing. These metal impurities degrade the minority carrier lifetime and increase the leakage current. [46] The degradation of Si devices by metal impurities could be improved by metal gettering which is employed extensively in microelectronics and photovoltaics.

In general, the gettering process involves three steps: (1) the release of the impurities from the device region, (2) the diffusion of the impurities to the gettered region, and (3) the capture of the impurities at the gettered region, as shown in Fig. 1-6. [47] The energy barrier of the release of the impurities should be low and the captured impurities should not be release simply. Moreover, the distance between the captured region and the device region should be short; the impurities should diffuse quickly through the interface or the interlayer.

In 2000, S. M. Myers et al [48] proposed at least five distinct types of gettering mechanism, as follows: (1) metal-silicide precipitation, (2) segregation into second phase, (3) atomic trapping by defects, (4) interaction with electronic dopants, and (5) phosphorous-diffusion gettering and nonequilibrium processes. Gettering by metal-silicide precipitation

**Figure 1-6** The concept of the gettering process including release, diffusion, and capture of the metal impurities [47].

is an effective method to remove metal impurities from the device region. This mechanism, as introduced in chapter 1-2-2, has been implemented by back-side polycrystalline silicon gettering [49]. The next mechanism also involves a second phase, but one formed by a third elemental species, with the transition metal being a dilute constituent. For example, gettering by segregation into a deposited Al can take place using Al–Si liquid on the back side of the wafer [50, 51]. That is because of a higher solubility of the metallic impurity in the liquid Al-Si phase compared with that in solid Si.

The imperfections or defects in Si are expected to be the gettering sits. These defects are incompletely coordinated being associated with open regions in the lattice and with Si atoms and therefore reactive. S. M. Myers et al refers to such solute-defect reactions not involving second-phase formation as trapping, Most researchers introduce the cavities into Si to getter metal (Fe [52], Co [53], Ni [54, 55], Pt [56], Au [57, 58], and Cu [59, 60]) by ion-implanting He or H. Trapping is believed to occur through a complex chemisorption-like reaction on the cavity walls.

Most transition-metal solutes are charged in Si and this characteristic can be developed for gettering by the electronic dopants. A charged metal atom and a dopant atom with opposite charge may form a bound pair, due to the electrostatic attraction. Moreover the energy of the charged metal atom is reduced, as the level of electronic doping is sufficient to

shift the Fermi level. Therefore metal impurity (Mn, Fe, and Co) segregates from an intrinsic or lightly doped region into a highly doped zone (B-doped and P-doped Si). [61, 62]

W. Schröter found that SiP precipitates form near Si/PSG interface in phosphorous-diffusion gettering and are capable of removing Ni impurities to produce NiSi<sub>2</sub> particles [63]. An influence of SiP precipitation during gettering is suggested by metal-silicide precipitation at the SiP particles. This phenomenon is also found during phosphorous- diffusion gettering of Pt [64].

These gettering methods have been effectively employed to reduce metallic impurities in Si. However these gettering methods are complicated and require high process temperatures. Even back-side gettering by ion-implanting damage is not suitable for TFTs 1896 device, due to a 500-nm-thick buffer oxide located between NILC poly-Si and the Si substrate. Hence we proposed a gettering structure, as shown in Fig. 1-7. [65-67] The mechanism of gettering is classified in metal-silicide precipitation. For effective gettering, the solubility of Ni impurities in the Ni gettering layer should be higher than that in the device region and the Ni diffusivity in the etching stop layer should be high. Thus the etching stop layer should be thin for Ni atoms diffusing quickly and well protect the device region during the removal of the Ni gettering layer. In addition, C.-M. Hu proposed the contact holes gettering [68] and wafer bonding gettering [69] with no etching stop layers.

Figure 1-7 (a) A gettering structure with a Ni gettering layer and an etching stop layer, and (b) the device region protected well by an etching stop layer during the removal of the Ni gettering layer.

### 1.4 Silicon Nanowires (NWs) Fabrication

Low temperature poly-Si TFTs have been employed in flat panel displays. [1-6] The major advantage of poly-Si TFTs technology is its integration of driver electronics, sensors, memories, and peripheral circuits on the glass substrate for multifunctional active-matrix displays. Several techniques have been proposed to scale down poly-Si TFTs' device geometries for increasing the device density. Unfortunately, the undesirable short-channel effects (SCEs) in electrical characteristics have been found in the conventional planar short-channel poly-Si TFTs. Recently, lots of efforts on nonplanar device structures have been developed for better gate electrostatic control of the channel potential, such as nanowire channel. [70, 71] Si NWs with high surface-to-volume ratio feature have been adopted in memory devices [72], NW thin-film transistors (TFTs) [73], and biosensors [74]. In general, Si NWs fabrication could be classified into two types: top-down, and bottom-up, introduced as follows:

#### 1.4.1 Top-Down Method

Top-down method generally requires the advanced lithography techniques, such as deep UV [75], e-beam [76]. Fist, nano-scale patterns are defined on the substrates and Si NWs then form by dry-etching. These approaches are well developed for mass production, but very expensive equipments and cutting-edge technologies are required. In addition,

several techniques, like thermal flow [77], chemical shrink [78], and spacer patterning [79] have been reported to assist the nano-scale patterns fabrication by the conventional lithography tools (G-line and I-line steppers). The conventional lithography is relatively cheap for Si NWs fabrication.

### **1.4.2** Bottom-Up Method

In general, Si NWs fabricated by bottom-up method need to be assembled and align for the electronics compared with top-down method. The assembly techniques such as electric-field-directed assembly [80], microfluidic channel [81] and Langmuir-Blodgett (LB) technique [82] have been proposed. Electric field method is via interaction between electric field of two parallel electrodes and polarity of NWs. Fluidic channel method could obtain assembled NW arrays by flowing NWs suspension inside a polydimethylsiloxane (PDMS) mold and LB method could assemble large-area anisotropic NWs by a compression process.

Typically the bottom-up method contains three steps: (a) deposition methods to prepare the NWs, (2) synthesis of the NWs on a substrate, and (3) dispersion of NWs into a solution. Some deposition methods have been proposed including, laser ablation catalyst growth [83], chemical deposition catalyst growth [84] and oxide-assisted catalyst-free method [85]. The first two techniques use a metal nanocluster catalyst as the nucleation

oxide-assisted catalyst-free method could fabricate NWs without metal contamination, but it is not adapted to electronic devices due to lots of defects in NWs.

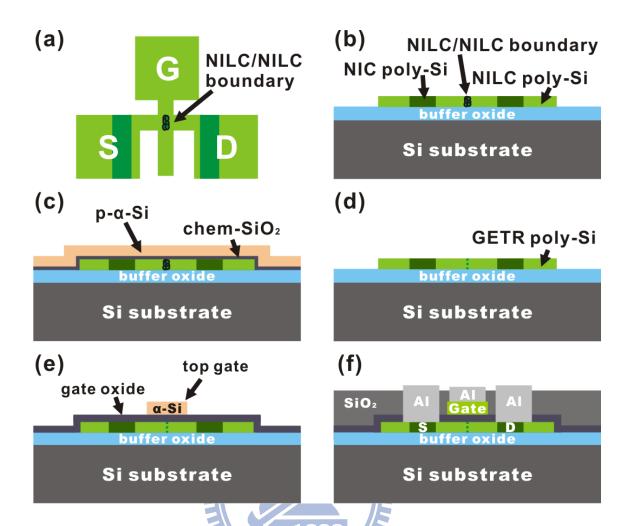

Recently, H.-C. Lin et al proposed a novel TFT structure with sidewall-spacer poly-Si nanowire channels. [86-88] The feature of process is the simple method of forming sidewall-spacer of MOSFET, as shown in Fig. 1-8b. Here we fabricate NILC poly-Si NWs TFTs similar to the sidewall-spacer method to investigate the effect of Ni residues on the performance of NILC poly-Si NWs TFTs.

## 1.5 Motivation and Thesis Organization

High-performance low-temperature polycrystalline silicon (poly-Si) thin-film transistors (TFTs) have attracted considerable interest for their application in flat panel displays. NILC is particularly attractive for forming superior, poly-Si films with good electrical characteristics However, NILC poly-Si grain boundaries trap Ni and NiSi<sub>2</sub> precipitates which increase the leakage current and shift the threshold voltage.

Here, we propose a technique that could effectively resolve the Ni-residue issues. Our method is using a gettering structure (Ni gettering layer/etching stop layer) to getter Ni impurities inside NILC poly-Si based on metal-silicide precipitation mechanism. It's a simple and effective process for improving the electrical properties of large area NILC TFTs. To

Figure 1-8 (a) Photoresist patterns on top of the poly-Si surface by the conventional lithography, and (b) the sidewall spacer NW channels fabricated by an anisotropic etching.

reduce thermal budget of the previous PECVD-SiN<sub>x</sub> gettering, around 5-nm-thick chemical oxide is proposed as an etching stop layer. This approach is compatible to traditional TFTs fabrication and costs cheaper compared with PECVD deposition. To further improve the gettering efficiency of  $\alpha$ -Si gettering layers, phosphorous dopant is introduced into  $\alpha$ -Si film. This is because phosphorous-diffusion could obtain solubility enhancement of Ni impurities.

In addition to improving the performance of NILC poly-Si thin-film and NW channel transistors, the gettering of nickel impurities within NILC poly-Si is carried out. Reduction of Ni-related defects trapped in the channel layer due to NILC poly-Si nature, could suppress the leakage current and negative shift of the threshold voltage. Moreover, NiSi<sub>2</sub> precipitates are randomly trapped at poly-Si/gate oxide interfaces and poly-Si grain boundaries. Hence the uniformity of device performance could be improved through a Ni-gettering process.

The dissertation is divided into five chapters listed below:

In chapter 1, an overview of poly-Si TFTs is reviewed, and then the processes of low temperature poly-Si crystallization, the metal gettering from Si, and Si NWs fabrication are introduced. Finally, the motivation of this study and the outline of the dissertation are provided.

In chapter 2, a simple and effective Ni-gettering process is proposed to reduce Ni impurities inside NIC and NILC poly-Si films. The phosphorous-doped  $\alpha$ -Si/chemical oxide

served as a gettering structure is introduced. Moreover, the influence of the phosphorous dopant concentration on the gettering efficiency is investigated. In this chapter, we also compare the effects of the phosphorous dopant and the argon dopant on NILC rate.

In chapter 3, the effects of Ni-gettering layers (p- $\alpha$ -Si/chem-SiO $_2$  films) on electrical characteristics of large area NILC TFTs is studied. The leakage current, threshold voltage, and the uniformity of NILC TFTs are studied after a Ni-gettering process.

In chapter 4, the fabrication of NILC poly-Si TFTs with a couple Si NWs is introduced.

The effect of Ni residues on the performance of NILC poly-Si NWs TFTs is investigated. The proposed gettering method is employed to improve the electrical characteristics of NILC poly-Si NWs TFTs.

Finally, conclusions and future work are given in chapter 5.

# Chapter 2 Ni Reduction of Nickel-Mediated Crystallization Polycrystalline Silicon Using A Ni-Gettering Process

### 2.1 Introduction

Several metal gettering methods have been employed to reduce the amount of undesired metallic impurities in Si. However these gettering methods are complicated and require high process temperatures. In previous studies [65], we have proposed a simple method for reducing Ni concentration inside the NILC film. It involves using  $\alpha$ -Si and silicon-nitride (SiN<sub>x</sub>) films as Ni-gettering layers. The top  $\alpha$ -Si layer served as a gettering layer, while the middle SiN<sub>x</sub> layer was used as an etching stop layer. However the gettering time required was 90 h due to low Ni diffusivity in SiN<sub>x</sub>. To reduce the thermal budget of the Ni-gettering process, we use  $\alpha$ -Si and chemical oxide (chem-SiO<sub>2</sub>) films as Ni-gettering layers, because Ni atoms transfer quickly through the nanothick-SiO<sub>2</sub> layer [89].

During the gettering process, Ni atoms were diffused from the NILC film to the  $\alpha$ -Si layer due to the concentration gradient. When the system reached equilibrium, no more Ni diffused into the gettering layer. At this point, the Ni concentration in the  $\alpha$ -Si layer was the

same as that in NILC. To improve the Ni-gettering efficiency, phosphorus-doped  $\alpha$ -Si (p- $\alpha$ -Si) films and chemical SiO<sub>2</sub> (chem-SiO<sub>2</sub>) layers are used as gettering layers. The effect of phosphorus dopant on the Ni-gettering efficiency is investigated in this chapter.

### 2.2 Experimental Procedure

### 2.2.1 Gettering of Ni Residues from NILC Poly-Si Films

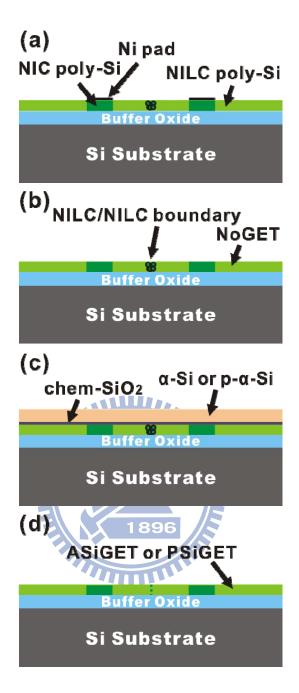

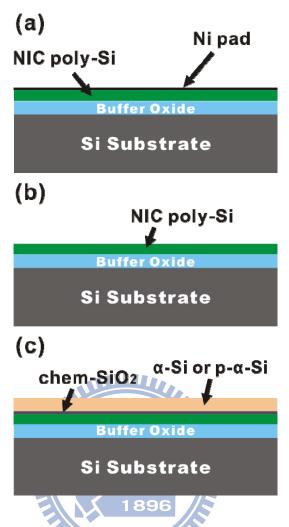

Three kinds of poly-Si films are investigated in this study. One is a poly-Si film fabricated by traditional NILC method without the gettering process (referred to as NoGET), and the others are poly-Si films fabricated by the same NILC method with different Ni-gettering layers (referred to as ASIGET and PSIGET). The NILC fabrication process began with capping 4-inch Si (100) wafers with 500-nm-thick wet thermal oxide. Silane-based 100-nm-thick  $\alpha$ -Si films were then deposited using low-pressure chemical vapor deposition (LPCVD) at 550°C in N<sub>2</sub> ambient. The photoresist was patterned to form desired Ni lines, and a 5-nm-thick Ni film was deposited on the  $\alpha$ -Si.

To form NoGET poly-Si films, samples were annealed at  $540^{\circ}$ C for 24 h in N<sub>2</sub> ambient, as shown in Fig. 2-1a. The unreacted Ni was then removed by a mixed solution of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> for 20 min. Finally, poly-Si films were dipped into 1% diluted hydrogen fluoride (DHF) solution to remove the annealing surface oxide, as illustrated in Fig. 2-1b.

As for the ASiGET poly-Si film, a NoGET poly-Si film was dipped into a mixed solution of

Figure 2-1 Schematic illustration of the Ni-gettering process: (a) fabrication of the NILC poly-Si film, (b) removal of unreacted Ni pads, (c) capped with an etching stop layer (chem-SiO<sub>2</sub>) and a gettering layer ( $\alpha$ -Si or p- $\alpha$ -Si), and (d) removal of the gettering layer and the chem-SiO<sub>2</sub> layer.

$H_2SO_4$  and  $H_2O_2$  for 10 min to form a chem-SiO<sub>2</sub> layer on the top of NILC poly-Si films. A 100-nm-thick  $\alpha$ -Si film was then deposited on the chem-SiO<sub>2</sub> layer using LPCVD at 550°C for 1 h in N<sub>2</sub> ambient, as shown in Fig. 2-1c. The top  $\alpha$ -Si film served as the Ni-gettering layer.

As for the PSiGET poly-Si films, phosphorus ions were implanted into  $\alpha$ -Si to form a p- $\alpha$ -Si film, as shown in Fig. 2-1c. The projection range (R<sub>p</sub>) of ions was set at the middle of the  $\alpha$ -Si film. The ion-accelerating energy was 35 keV. The dosage of phosphorus ions were 1×10<sup>14</sup> cm<sup>-2</sup>, 1×10<sup>15</sup> cm<sup>-2</sup> and 1×10<sup>16</sup> cm<sup>-2</sup>, respectively. Relevant parameters for the samples studied are summarized in Table 2-1.

Samples undergoing Ni-gettering were then annealed at 550°C for 12 h in N<sub>2</sub> ambient with the goal of removing the unwanted Ni metal inside the NILC poly-Si. Following the 1896 annealing process, the top Ni-gettering films were removed using 5% tetramethylammonium hydroxide (TMAH) solution for 2 min at 55°C, and the chem-SiO<sub>2</sub> layers were removed using 1% DHF solution, as illustrated in Fig. 2-1d. For the purpose of comparison, the NoGET poly-Si film was also subjected to an extended heat treatment at 550°C for 12 h in N<sub>2</sub> ambient.

### 2.2.2 Gettering of Ni Residues from NIC Poly-Si Films

The fabrication process of NIC poly-Si is shown in Fig. 2-2. Silane-based 100-nm-thick  $\alpha$ -Si films were deposited using LPCVD at 550°C in N<sub>2</sub> ambient, as displayed in Fig. 2-2a. A

**Table 2-1** Relevant parameters of the Ni-gettering layers.

| Sample    | Gettering Layer | Phosphorus Implantation |

|-----------|-----------------|-------------------------|

|           |                 | Dose(/cm <sup>2</sup> ) |

| NoGET     | w/o             | w/o                     |

| ASIGET    | α-Si            | w/o                     |

| PSiGET-14 | p14-α-Si        | 1x10 <sup>14</sup>      |

| PSiGET-15 | p15-α-Si        | 1x10 <sup>15</sup>      |

| PSiGET-16 | p16-α-Si        | 1x10 <sup>16</sup>      |

Figure 2-2 Schematic illustration of the Ni-gettering process of the NIC poly-Si: (a) fabrication of the NIC poly-Si film (b) removal of unreacted Ni films, and (c) capped with a chem-SiO<sub>2</sub> layer and a gettering layer ( $\alpha$ -Si or p- $\alpha$ -Si).

5-nm-thick Ni film was then deposited on the  $\alpha$ -Si, and subsequently annealed at 540°C for 24 h to form NIC poly-Si. The unreacted Ni was then removed by a mixed solution of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> for 20 min. Finally, poly-Si films were dipped into 1% DHF solution to remove the annealing surface oxide, as shown in Fig. 2-2b. The poly-Si film was dipped into a mixed solution of H<sub>2</sub>SO<sub>4</sub> and H<sub>2</sub>O<sub>2</sub> to form a chem-SiO<sub>2</sub> layer. A 100-nm-thick  $\alpha$ -Si film was then deposited on the chem-SiO<sub>2</sub> layer using LPCVD at 550°C for 1 h in N<sub>2</sub> ambient to form the  $\alpha$ -Si gettering layer, as illustrated in Fig. 2-2c. Phosphorous ions were implanted into  $\alpha$ -Si to form the p- $\alpha$ -Si gettering layer. The dosage of phosphorus ions and the ion-accelerating energy were 1×10<sup>16</sup> cm<sup>-2</sup> and 35 keV, respectively. Samples were then annealed at 550°C for 12 h in N<sub>2</sub> ambient.

### 2.2.3 Dopant Effect on NILC Rate

Three kinds of  $\alpha$ -Si films are investigated in this study. One is intrinsic  $\alpha$ -Si, and the others are  $\alpha$ -Si films introduced by argon ions and phosphorus ions, respectively. First, silane-based 100-nm-thick  $\alpha$ -Si films were deposited on oxide Si substrates using LPCVD, followed by ion implantation. The R<sub>p</sub> of ions was then set at the middle of the  $\alpha$ -Si film and the dosage was  $1\times10^{14}$  cm<sup>-2</sup>,  $1\times10^{15}$  cm<sup>-2</sup>, and  $1\times10^{16}$  cm<sup>-2</sup>, respectively. Then 5-nm-thick Ni lines were selectively deposited on sample surfaces. Finally the traditional NILC method was carried out at  $540^{\circ}$ C for 16 h in N<sub>2</sub> ambient.

### 2.3 Results and Discussion

### 2.3.1 Characterization of NILC Poly-Si Films

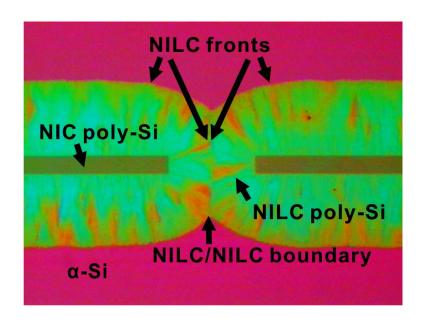

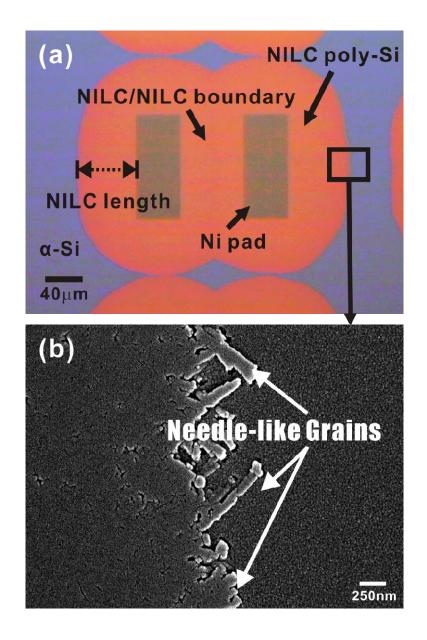

The length of the NILC poly-Si is about 79 $\mu$ m and almost saturated, as shown in Fig. 2-3. Since solid-phase crystallization (SPC) poly-Si grains formed near interface between  $\alpha$ -Si and NILC poly-Si, the NILC poly-Si grains laterally growth was blocked. Therefore we can obviously see the winding interface ( $\alpha$ -Si/NILC poly-Si). Before the NILC got saturated, we can examine NICL rate as 3.59  $\mu$ m/h, as shown in Fig. 2-4.

After a NILC fabrication process, the  $\alpha$ -Si and Ni silicide were etched away with Secco etching solution [90] and examined by scanning electron microscope (SEM). The NILC poly-Si is composed of needle-like poly-Si grains and grain size is about 100 nm, as displayed in Fig. 2-5.

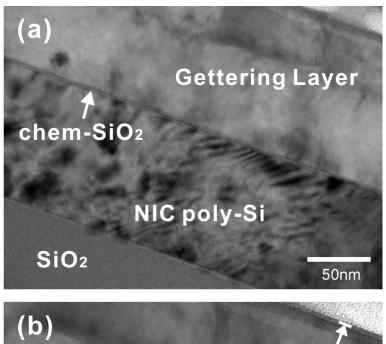

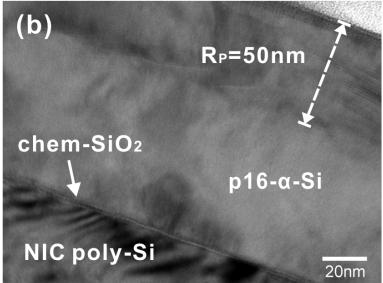

### 2.3.2 Quality of chem-SiO<sub>2</sub> Layers

To examine the quality of the chem-SiO<sub>2</sub> film, after the chem-SiO<sub>2</sub> layer was formed, platinum was deposited on top of the chem-SiO<sub>2</sub> film for image contrast in transmission electron microscopy (TEM) sample preparation. As shown in Fig. 2-6, the oxide layer is only about 5 nm thick. This chem-SiO<sub>2</sub> layer was used as an etching stop layer in the 5% TMAH etching solution. Moreover, this nano oxide layer also served as a diffusion interlayer during the Ni-gettering process. Ni atoms needed to diffuse from the NILC poly-Si through

Figure 2-3 OM image of the  $\alpha$ -Si film after a NILC process carried out at 540°C for 24 h in  $N_2$  ambient.

Figure 2-4 The dependence of the NILC length on the anneal time. The NILC was carried out at  $540^{\circ}$ C in  $N_2$  ambient.

**Figure 2-5** SEM image of the NILC poly-Si grains treated with Secco-etching.

Figure 2-6 (a) Cross-sectional TEM images of the NILC Poly-Si films capped with the chemical oxide films, and (b) the high magnification of a chemical oxide film around 5 nm thick. Platinum (Pt) films were deposited on top of the chem-SiO<sub>2</sub> layers for image contrast.

the thin chem- $SO_2$  into the Ni-gettering layer. The chem- $SiO_2$  in Fig. 2-6b tends to be porous and amorphous. Therefore Ni atoms possibly diffused through 5-nm-thick chem- $SiO_2$  faster compared with 30-nm-thick  $SiN_x$  [65] used before.

To study the effect of Ni-gettering on the surface roughness of the NILC poly-Si after gettering layers removal, the NILC poly-Si surfaces were measured using atomic force microscopy (AFM). As shown in Fig 2-7, the metal gettering did not change the surface roughness greatly: the root-mean-square (RMS) roughness of ASiGET (0.65 nm) and PSiGET-16 (0.69 nm) are almost the same as that of NoGET (0.64 nm). This seems that 5-nm-thick chem-SiO<sub>2</sub> layer did protect ASiGET and PSiGET-16 poly-Si surfaces during wet etching by 5% TMAH solution.

# 2.3.3 Ni-Gettering Using chem-SiO<sub>2</sub> Interlayer

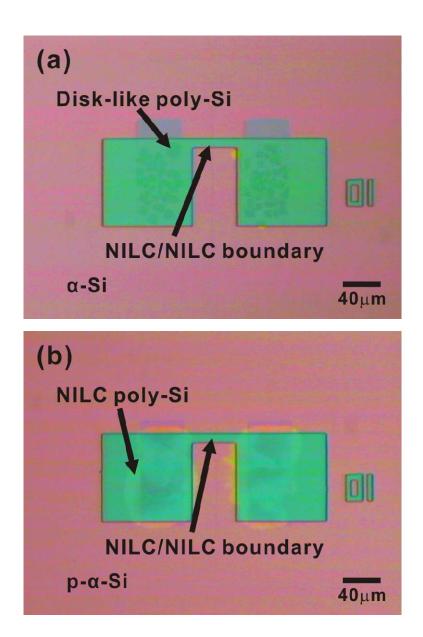

Figure 2-8a shows the optical microscopy (OM) images of the Ni-gettering layers after it was deposited on top of the chem-SiO<sub>2</sub> layer using LPCVD at 550°C for 1 h in N<sub>2</sub> ambient. The pink region is  $\alpha$ -Si and the green regions are disk-like poly-Si. This result indicates that during the deposition of  $\alpha$ -Si film, some Ni atoms had already diffused from the NIC area through the chem-SiO<sub>2</sub> layer into the gettering layer and caused  $\alpha$ -Si to be transformed into poly-Si grains by the NILC mechanism. However in the case of the  $\alpha$ -Si/SiN<sub>x</sub>-gettering process [65], no NILC poly-Si was observed on the gettering layer during the deposition of

Figure 2-7 AFM images of the NILC poly-Si surfaces (a) without Ni-gettering, and with Ni-gettering by (b) a  $\alpha$ -Si layer, and (c) a p- $\alpha$ -Si layer (the dosage was  $1\times10^{16}$  cm<sup>-2</sup>).

Figure 2-8 OM images of the Ni-gettering layers: (a) a  $\alpha$ -Si film deposited on a chem-SiO<sub>2</sub> layer by LPCVD and then phosphorous ions implanted at a dosage of (b)  $1\times10^{14}$  cm<sup>-2</sup>, (c)  $1\times10^{15}$  cm<sup>-2</sup>, and (d)  $1\times10^{16}$  cm<sup>-2</sup>, respectively.

α-Si. After phosphorus ions implantation, the green regions disappear, as illustrated in Fig.

2-8d. This means the original NILC poly-Si grains became amorphous through phosphorus ions bombard.

The pale-green region in Fig. 2-8a is the NILC poly-Si on the NoGET film underneath a chem-SiO<sub>2</sub> layer. This means that during the gettering process, Ni atoms diffused from the NoGET film through chem-SiO<sub>2</sub> into the Ni-gettering layer due to the concentration gradient. When Ni atoms reached the gettering film, enough Ni metal would be accumulated to form NiSi<sub>2</sub> precipitates, and  $\alpha$ -Si would then be transformed into needle-like poly-Si grains by the NILC mechanism. NILC poly-Si grains first appear right above the top of the NIC area, and then extend to the surrounding areas. This is because the Ni concentration above the NIC area was higher than that in other areas of the gettering film. Therefore, we can still see the NIC strip patterns, as displayed in Fig. 2-9.

### 2.3.4 Improved Ni-Gettering Efficiency by Phosphorus Ions Implant

After the gettering process, the gettering layers were examined by OM to investigate the gettering efficiency. The results are shown in Fig. 2-9. In Fig. 2-9a, the pink region is  $\alpha$ -Si and the green region is needle-like NILC poly-Si verified by SEM, as shown in Fig. 2-10a. The microstructure of NILC poly-Si, in Fig. 2-9d, is composed of needle-like poly-Si grains but etched away mostly by Secco etching solution, as illustrated in Fig. 2-10b. This means

Figure 2-9 OM images of the Ni-gettering phenomenon by (a) a  $\alpha$ -Si film, and the phosphorous-doped  $\alpha$ -Si films at a dosage of (b)  $1\times10^{14}$  cm<sup>-2</sup>, (c)  $1\times10^{15}$  cm<sup>-2</sup>, and (d)  $1\times10^{16}$  cm<sup>-2</sup>, respectively.

Figure 2-10 SEM images of the NILC poly-Si grains of Ni-gettering layers: (a) a  $\alpha$ -Si film, and (b) a phosphorous-doped  $\alpha$ -Si film at a dosage of  $1\times10^{16}$  cm<sup>-2</sup>. Samples were treated with Secco-etching.

250nm

that some implant damages formed in intrinsic  $\alpha$ -Si during ion implantation. When p16- $\alpha$ -Si was transformed into NILC poly-Si, the crystalline quality was poor and these damages or defects trapped Ni. Therefore a lot of NILC poly-Si grains were etched away.

Figure 2-9d also shows that the length of the NILC poly-Si growth on the p16- $\alpha$ -Si gettering layer is 13 $\mu$ m, which is much shorter than that (60  $\mu$ m) on the  $\alpha$ -Si gettering layer. Since the NILC grains were induced by indiffusion of Ni atoms, it seemed that phosphorus dopant did not improve the gettering efficiency of  $\alpha$ -Si. The further investigation of the dopant effect on the NILC rate is discussed in chapter 2-3-5.

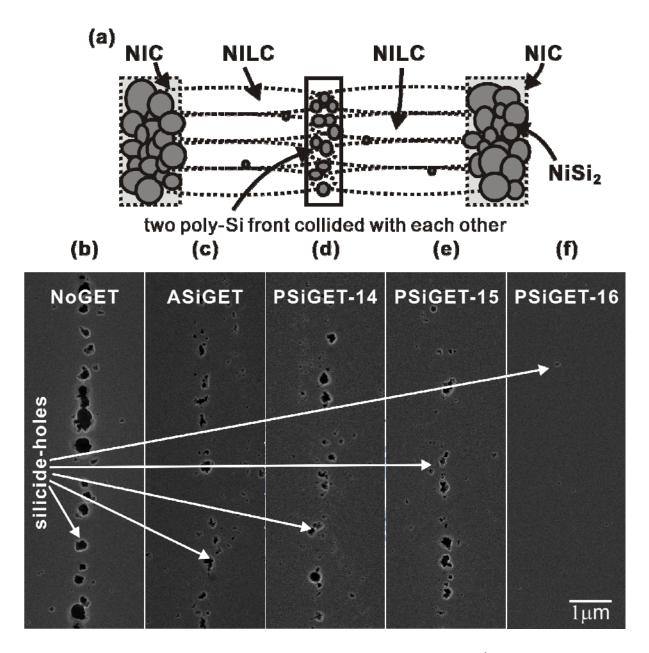

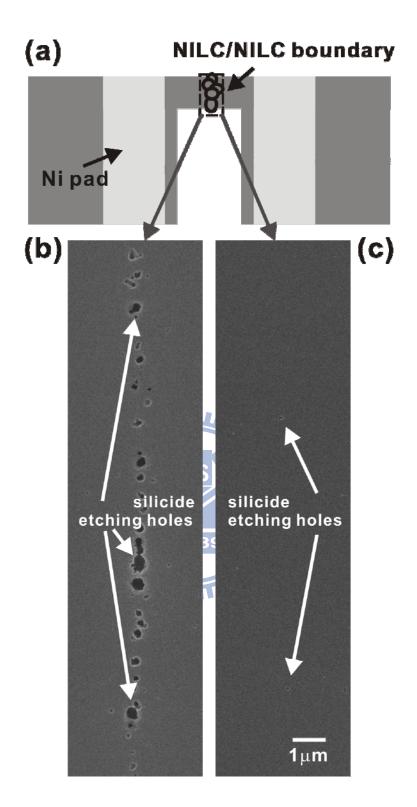

In addition to the gettering layer, the gettering efficiencies of ASiGET and PSiGET poly-Si films are also investigated. The NILC/NILC boundary in Fig. 2-11 is examined by SEM to 1896 compare Ni-gettering efficiency. After the gettering layer and chem-SiO<sub>2</sub> were removed, the samples were dipped into a silicide-etching solution (HNO<sub>3</sub>:NH<sub>4</sub>F:H<sub>2</sub>O=4:1:50). As shown in Fig. 2-12a and b, numerous holes are observed at the boundaries where two NILC poly-Si fronts intersected (NILC/NILC boundaries). These holes are residues of the Ni silicide that had been etched away by the silicide-etching solution. These silicide-etching holes seen in Fig. 2-12b are quite sensitive to the reduction of Ni residue in the NILC poly-Si, and are therefore ideal for elucidating the "Ni gettering" phenomenon observed.

After the gettering process, fewer and smaller silicide-etching holes are found at the

Figure 2-11 OM image of NILC/NILC boundary treated with TMAH etching.

Figure 2-12 Schematic illustration of (a) silicide-etching holes at NILC/NILC boundaries, and SEM images of etching holes of (b) NoGET, (c) ASiGET, (d) PSiGET-14, (e) PSiGET-15, and (f) PSiGET-16. Samples were treated with the silicide-etching solution.

NILC/NILC boundaries of ASiGET, PSiGET-14 and PSiGET-15 as shown in Fig. 2-12c-e. Furthermore, there are almost no silicide-etching holes observed at the NILC/NILC boundaries of PSiGET-16, as shown in Fig. 2-12f. These results indicate that phosphorous dopant did improve the gettering efficiency of  $\alpha$ -Si, which is different from our OM observation of gettering layers (Fig. 2-9). But the gettering efficiency obviously improves until doping phosphorus ions at a dose of  $1\times10^{16}$  cm<sup>-2</sup>.

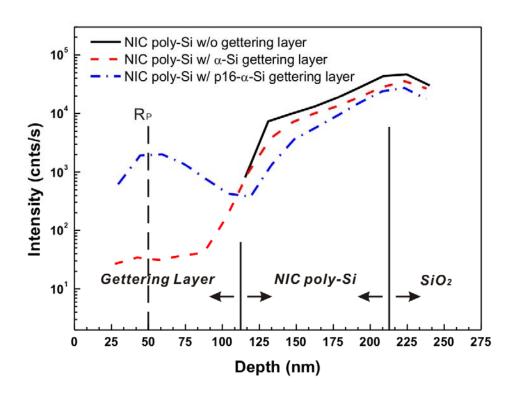

Secondary-ion mass spectroscopy (SIMS) was employed to clarify the Ni concentration in PSiGET-16 and ASiGET. Unfortunately, the Ni concentration in the NILC poly-Si is hard to measure since the SIMS sputtering area (125  $\mu$ m × 125  $\mu$ m) is much larger than that in the NILC poly-Si area. Therefore, we used NIC poly-Si to demonstrate that phosphorus dopant did improve the gettering efficiency of  $\alpha$ -Si. Furthermore, we verified the microstructure of gettering samples by TEM. The results are shown in Fig. 2-13. The top region of the gettering layer displays darker than the bottom region does. This means that implant strains remained inside the top region of p16- $\alpha$ -Si layer. The R<sub>p</sub> in Fig 2-13b is about 50 nm in depth and the gettering layer is about 110 nm thick.

Even though the Ni concentration in NIC poly-Si was much higher than that in NILC poly-Si, we can still have a preliminary understanding of the gettering efficiency of  $\alpha$ -Si films. Figure 2-14 shows that the Ni concentration of NIC poly-Si is reduced after the Ni-gettering

**Figure 2-13** (a) Cross-sectional TEM images of NIC Poly-Si films capped with chemical oxide films and gettering layers, and (b) the high magnification of a gettering layer around 110 nm thick. The gettering layer was implanted with 1×10<sup>16</sup> cm<sup>-2</sup> phosphorous ions and the projection range (Rp) was about 50 nm in depth.

Figure 2-14 SIMS depth profiles of NIC poly-Si films treated with and without a Ni-gettering process.

process. As can be seen, the Ni concentration in NIC poly-Si with the  $\alpha$ -Si gettering layer is relatively higher than that with the p16- $\alpha$ -Si gettering layer. Moreover, p16- $\alpha$ -Si layer traps many more Ni atoms than does  $\alpha$ -Si layer. These results indicate that phosphorous dopant did improve the gettering efficiency of  $\alpha$ -Si.

Figure 2-14 also shows that the middle of the p16- $\alpha$ -Si layer has a higher Ni concentration than other parts of the layer. This concentration distribution of Ni is similar to that of phosphorous atoms since the projection range of phosphorous ions is set at the middle of the  $\alpha$ -Si film. This result also indicates that phosphorus did trap Ni atoms.

In the gettering process, when more Ni atoms diffused into the gettering layer, more  $\alpha$ -Si would be transformed into poly-Si by the NILC mechanism. The gettering efficiency increased with the growth of NILC poly-Si grains. However, when the system reached equilibrium, no more Ni could diffuse into the gettering layer. At this point, the Ni concentration in the  $\alpha$ -Si gettering layer will be the same as that in ASiGET. However, the Ni concentration in the p16- $\alpha$ -Si gettering layer will be higher than that in PSiGET-16 since phosphorus implant traps Ni atoms. In other words, the gettering efficiency of  $\alpha$ -Si is indeed improved by phosphorous dopant at a dose of 1×10<sup>16</sup> cm<sup>-2</sup>.

### 2.3.5 Effect of Phosphorus Ions and Implant Damages on NILC Rate

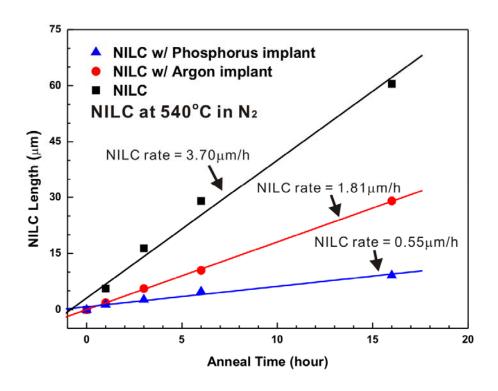

To further investigate the dopant effect on NILC rate, either phosphorus dopant or

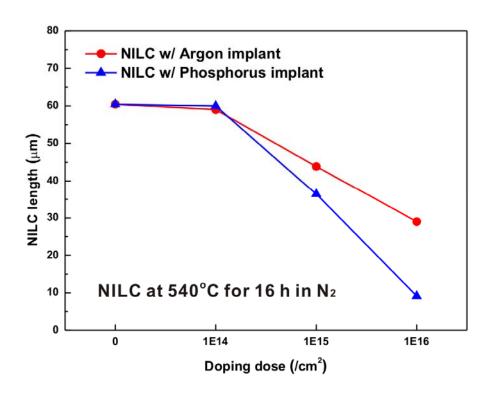

defects were introduced into the  $\alpha$ -Si, before NILC process. Figure 2-15 shows that the phosphorus dopant slows down NILC rate. As a result, the length of the NILC poly-Si growth on p- $\alpha$ -Si (Fig. 2-9) is much shorter than that on  $\alpha$ -Si. Figure 2-15 also shows that the NILC rate on the P-doped  $\alpha$ -Si film is 0.55  $\mu$ m/h, which is shorter than that (1.81  $\mu$ m/h) on the Ar-doped  $\alpha$ -Si film. Figure 2-16 reveals that the reduction in the NILC rate of the P-doped  $\alpha$ -Si film is more than for that of the Ar-doped  $\alpha$ -Si film. Compared to an intrinsic sample, a monotonic reduction in the NILC rate with an increasing dose of both implanted samples is observed. This seems that the phosphorus dopant trapped many more Ni atoms than did the argon dopant. A unified explanation is Ni trapping due to gettering by phosphorous, implant damage [91].

## 2.4 Summary

Two kinds of films are employed to investigate the effect of phosphorus dopant on the gettering efficiency of  $\alpha$ -Si. To form the ASiGET and PSiGET, a ~5-nm-thick porous chem-SiO<sub>2</sub> layer was capped on the top of the NoGET film, and then either  $\alpha$ -Si or p- $\alpha$ -Si film was deposited on the top of the chem-SiO<sub>2</sub> film. The chem-SiO<sub>2</sub> layer was used as an etching stop layer, while the Si film served as a gettering layer. It is found that the Ni concentration in the NoGET film is greatly reduced after gettering at 550°C for 12 h in N<sub>2</sub> ambient. Compared with those on the NoGET film, the silicide-etching holes found at the NILC/NILC boundaries of ASiGET are fewer and smaller, while almost no holes are

Figure 2-15 NILC length vs. anneal time and different doping type. NILC was carried out at  $540^{\circ}\text{C}$  in  $N_2$  ambient.

Figure 2-16 NILC length vs. different doping type and dose after heat treatment at  $540^{\circ}$ C for 16 h in  $N_2$  ambient.

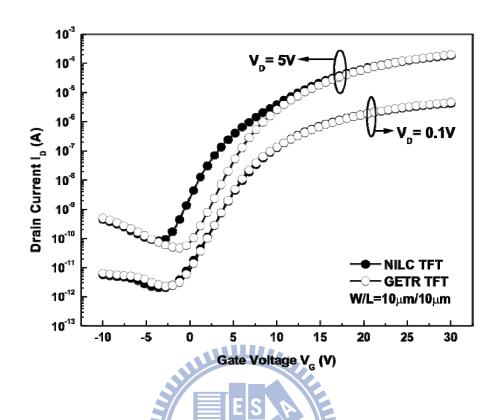

observed at the boundaries of PSiGET-16. These results indicate that phosphorous dopant could improve the gettering efficiency of  $\alpha$ -Si due to the solubility enhancement of Ni impurities.