# 國立交通大學

加速器光源科技與應用碩士學位學程

## 碩士論文

電漿處理對二氧化鉿/矽介面層抗輻射能力之 影響

Effect of plasma treatment on the radiation hardness of the HfO<sub>2</sub>/Si interfacial layer

研 究 生:廖雪君

指導教授:崔秉鉞 教授

許博淵 博士

中華民國一百零三年八月

#### 電漿處理對二氧化鈴/矽介面層抗輻射能力之影響

# Effect of plasma treatment on the radiation hardness of the HfO<sub>2</sub>/Si interfacial layer

研究生: 廖雪君 Student: Syue-Jyun Liao

指導教授:崔秉鉞 Advisor: Bing-Yue Tsui

許博淵 Bor-Yuan Shew

國立交通大學

加速器光源科技與應用碩士學位學程

碩士論文

#### A thesis

Submitted to Graduate Program for Science and Technology of Accelerator

**Light Source**

College of Engineering

National Chiao Tung University

In Partial Fulfillment of the Requirement

for the Degree of Master

in

Graduate Program for Science and Technology of Accelerator Light Source

August 2014

Hsinchu, Taiwan, Republic of China

中華民國一零三年八月

#### 電漿處理對二氧化鉿/矽介面層抗輻射能力之影響

研究生:廖雪君 指導教授:崔秉鉞 教授

許博淵 博士

國立交通大學加速器光源科技與應用碩士學位學程

# 摘要

極紫外光微影是最可能成為下個世代微影技術的選擇,但其光源屬於高能量輻射,若要應用於工業製程上,尚須考慮游離輻射對於電子元件所造成的影響。前人已利用金屬閘極/高介電常數介電質金氧半電容器研究不同材料、介面厚度、氧化層厚度和退火溫度之影響,但仍尚未透徹了解高介電質材料在極紫外光照射下的損傷。因而本論文研究著重於介面品質差異性之抗輻射能力,利用氨氣與氮氣電漿對介面層進行品改善。另外,我們也利用先進製程N型電晶體,研究經由高溫退火修復元件輻射損傷至照射前電性,是否降低元件之抗輻射能力,以及極紫外光照射對元件的正偏壓溫度不穩定性的可靠度分析。

先前研究成果已證實,游離輻射會在金氧半元件的閘極介電層中產生正電荷、邊緣缺陷和介面缺陷,從元件的電容-電壓曲線可看到位移、遲滯電壓增加和曲線變形等現象。經由電漿處理後發現,氮氣電漿試片經極紫外光照射後,平帶電壓增加量相對於對照組變化較少,且遲滯電壓與之相差無幾,介面缺陷變化是三者中最少,較適合採用於製程中。另外,氦氣電漿處理會因為大量氫離子掺入,使元件電性衰退,造成嚴重的電容-電壓曲線位移與變形,因此並不適合採用。且在5奈米氧化層試片,氦氣電漿試片之平帶電壓與介面能態增加量較多,但遲滯電壓所有條件差異性不大。接著採用10 keV之X-光,由於衰退長度與極紫外光相差非常大,以5奈米二氧化鉛為例,換算出X-光的吸收率與極紫外光相差約110倍,因

此各照射條件下,電性變化並不明顯。由上敘述可推論,三種條件為氮氣電漿試 片抗輻射能力最佳,而氨氣電漿試片最差,當氧化層調降為5奈米,雖然輻射影響 大幅下降,氨氣電漿試片仍為最不適合採用的電漿處理條件。

最後,我們探討退火對抗輻射力之影響,電晶體接受不同能量輻射照射,之 後經由高溫退火並再次照射輻射,證實其高溫退火可修復輻射損傷,但不會影響 抗輻射能力。然後我們利用臨界電壓對正偏壓溫度的不穩定性,於較弱之電場下 測試輻射對元件可靠度之影響,得知結果仍無法明確肯定輻射對可靠度之影響, 但證實於測試中,電場影響遠大於輻射影響。

Effect of plasma treatment on the radiation hardness of the HfO<sub>2</sub>/Si interfacial layer

Student: Syue-Jyun Liao Advisor: Bing-Yue Tsui

Bor-Yuan Shew

Graduate Program for Science and Technology of Accelerator Light Source

National Chiao Tung University

ABSTRACT

Extreme ultraviolet lithography (EUVL) is the most likely selection as the next generation lithography technology in the future. The radiation damage effect during exposing process should be considered because the energy of EUV is higher than chemical bonding energy of most dielectrics. The effects of oxide thickness, interfacial layer thickness, gate oxide material, and annealing temperature on the radition hardness of high-k/metal gate MIS capacitors have been studied previously. In this thesis, the radiation hardness of the HfO<sub>2</sub>/Si structure with plasma-treated interfacial layer is investigated. Moreover, state-of-the-art n-channel we prepare the Metal-Oxide-Semiconductor-Field-Effect-Transistor (nMOSFET) to study the effect of post-radiation annealing. In addition, we use positive bias temperature instability (PBTI) test to evaluate the radiation effect on the reliability property of nMOSFET.

Previous study reported that ionizing radiation would induce positive oxide charge, interface traps, and border traps in the gate oxide of MIS capacitor. These defects cause capacitance-voltage (C-V) curve shift, C-V curve distortion, and increment of hysteresis. After EUV irradiation, it is observed that N<sub>2</sub> plasma treatment increases the flatband voltage slightly. Furthermore, the increment of hysteresis is similar to that of the control

iii

sample and the interface traps increase is less than other samples. The experiment results imply that the  $N_2$  plasma treatment would improve the interface property by nitrogen incorporation. Besides, it is well suited for industrial processes.

On the other side, the electrical characteristics of the NH<sub>3</sub> plasma treated sample degrade after ionizing irradiation due to hydrogen incorporation. Evident shift and distortion of the C-V curve is observed. These results indicate that the NH<sub>3</sub> plasma treatment is not suitable to be used in industrial processes. As the radiation source changes to 10 keV X-ray, the effect of radiation damage on the C-V curves is unobvious because the percentage of photons which are absorbed by HfO<sub>2</sub> layer for EUV is 110 times larger than that for the 10 keV X-ray. In conclusion, N<sub>2</sub> plasma treatment is the best choice. The worst case is the NH<sub>3</sub> plasma treatment. As the thickness of HfO<sub>2</sub> decreases to 5 nm, the degradation of flatband voltage and hysteresis are reduced apparently. Similarly, the N<sub>2</sub> plasma sample still has the least flatband voltage shift and interface state generation. The worst case is NH<sub>3</sub> plasma sample, too.

Finally, we discuss the effect of annealing on radiation hardness. The state-of-the-art nMOSFET is irradiated by different radiation source. Next, it is annealed at 400 °C. After annealing, it is exposed again to the same dose irradiation. Experimental results indicate that high temperature annealing could recover the radiation damages. Moreover, the annealing wouldn't change the device radiation hardness. Afterward we evaluate the PBTI at weak electric field. We observe that no matter what radiation source is used, the distribution of threshold voltage degradation is nearly the same both at room temperature and 150 °C. It indicates that the reliability property of the state-of-the-art nMOSFET wouldn't be affect by ionizing radiation.

### 誌謝

終於可以開始寫這篇誌謝文章,也意味著碩士班生活要結束,這三 年在交大的日子,經歷了許許多多酸甜苦辣的事情,讓我從懵懂無知 漸漸的蛻變,並且內心也更加堅強。

這篇論文得以完成,首先要感謝我的指導教授 崔秉鉞老師。老師有著嚴謹的處事態度、豐富的學識、正直的性格以及對我們這些學生充滿教育的熱誠。在老師的指導下,從如何有效率的規劃實驗與時間安排開始學習,並且教導我們於做研究應該要有嚴謹的態度,讓我受益良多。到最後實驗結果分析與論文撰寫,老師也不厭其煩討論與逐字批改,讓我得以完成人生的一本著作。再來也要感謝共同指導老師許博淵博士,在光束線使用疑問上、設備商借還有相關知識等,若沒有許老師我們將在同步輻射寸步難行。

接著要感謝奈米中心、同步輻射中心以及國家元件實驗室,給予我實驗上極大的幫助。而實驗室的學長姐在實驗與理論上給我極大的幫助,讓我得以度過難關,給他們增添了許多麻煩,同學們和學弟妹們給予我勉勵與歡樂,讓我在做研究的時候再次有衝進。

最後我要謝謝家人以及朋友,感謝爸媽讓我讀書的時候沒有後顧之 憂,謝謝姐姐讓我吐吐苦水,在心灰意冷的時候讓我感到溫馨,而朋 友每過一段時間與你們相聚, 聊聊你們在研究、工作後的心得與建議, 與你們肆無忌憚的聊天。謝謝你們讓我在新竹以外有個避風港, 可以 暫時撇除一切, 重新充電有勇氣面對困難。

在此將此文獻給伴隨我,經歷過這段人生的大家,謝謝你們給我各

# 目錄

| 中文摘要                    | i   |

|-------------------------|-----|

| 英文摘要                    | iii |

| 誌謝                      | v   |

| 目錄                      | vii |

| 圖目錄                     | X   |

| 表目錄                     | XV  |

| 第一章 緒論                  | 1   |

| 1-1 微影技術的演變             | 1   |

| 1-2 輻射損傷影響              | 3   |

| 1-3 鋡氧化物金氧半元件及介面處理      | 4   |

| 1-3-1                   | 4   |

| 1-3-2 二氧化鉿及矽晶片介面品質      | 7   |

| 1-4 論文架構                | 8   |

| 第二章 元件製程與實驗步驟           | 14  |

| 2-1 元件製程                | 14  |

| 2-1-1 金氧半電容製程步驟         | 14  |

| 2-1-2 N型金氧半電晶體          | 15  |

| 2-2 國家同步輻射中心(NSRRC)實驗環境 | 16  |

|     | 2-2-1 | 07A1 光束線與實驗架設                            | . 16 |

|-----|-------|------------------------------------------|------|

|     | 2-2-1 | 08A1 光束線與實驗架設                            | . 17 |

|     | 2-2-3 | 輻射劑量計算                                   | . 18 |

| 2-3 | 電性    | 計算                                       | . 19 |

|     | 2-3-1 | 氧化缺陷(Oxide trap)和介面缺陷(Interface trap)計算。 | . 20 |

|     | 2-3-2 | 正偏壓變溫量測                                  | . 21 |

| 第三章 | 電漿    | 處理電容器之介面層對於抗輻射能力影響                       | . 31 |

| 3-1 | 元件:   | 與照光劑量介紹                                  | . 31 |

|     | 3-1-1 | 元件與實驗儀器介紹                                | . 31 |

|     | 3-1-2 | 元件結構                                     | . 32 |

|     | 3-1-3 | 基本電性                                     | . 33 |

| 3-2 | 金氧·   | 半電容之抗輻射能力                                | . 35 |

|     | 3-2-1 | 不同方式處理介面之抗輻射能力                           | . 35 |

|     | 3-2-2 | 不同能量對於抗輻射能力影響                            | . 38 |

|     | 3-2-3 | 靜置於室溫電性恢復情形                              | . 40 |

| 第四章 | 游離    | 輻射對金氧半場效電晶體之可靠度影響                        | . 65 |

| 4-1 | 電晶    | 體之基本電性                                   | . 65 |

| 4-2 | 不同    | 能量光源之抗輻射能力分析                             | . 65 |

|     | 4-2-1 | 極紫外光                                     | 66   |

|     | 4-2-2 | X-光                   | 67 |

|-----|-------|-----------------------|----|

| 4-3 | 照射    | 極紫外光後之可靠度             | 69 |

| 第五章 | 結論    | 與展望                   | 81 |

| 5-1 | 結論    |                       | 81 |

|     | 5-1-2 | 介面層電漿處理對金氧半電容之電性影響    | 81 |

|     | 5-1-2 | 介面層電漿處理對金氧半電容之抗輻射能力研究 | 82 |

|     | 5-1-3 | 輻射對於電晶體退火處理與可靠度之影響    | 83 |

| 5-2 | 2 後續  | 研究建議                  | 84 |

| 參考文 | 獻     |                       | 85 |

| 作者簡 | 歷     |                       | 93 |

# 1896

# 圖目錄

| 圖 | 1-1 | 未來可能應用之微影方式。10                       |

|---|-----|--------------------------------------|

| 圖 | 1-2 | 極紫外光與雙重曝光製程成本比較。10                   |

| 圖 | 1-3 | 奈米壓印之曝光流程。1                          |

| 圖 | 1-4 | EBDW 技術結構,(a)機體設計圖,(b)電子東路徑圖。1       |

| 圖 | 1-5 | 極紫外光微影系統架構圖。12                       |

| 圖 | 1-6 | P型電容於閘極上施予正偏壓,當經由照射輻射後電子電洞於          |

|   | 4   | 能帶傳導情形。12                            |

| 圖 | 1-7 | 遠距式電漿機台架構圖。12                        |

| 圖 | 2-1 | 金氧半電容剖面結構示意圖。22                      |

| 圖 | 2-2 | 先進電晶體閘極堆疊剖面結構圖。2                     |

| 圖 | 2-3 | 07A1 實驗站架設圖,(A)試片黏貼示意圖,(B)實驗設備設置     |

|   |     | 示意圖。24                               |

| 圖 | 2-4 | 07A1 實驗站定位示意圖,(A)X-光 0° 起始點,(B)對準線劃記 |

|   |     | 方式。24                                |

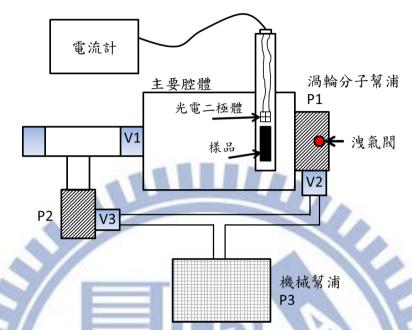

| 圖 | 2-5 | 08A1 實驗站機台架設示意圖。                     |

| 圖 | 2-6 | 08A1 實驗站機台實際架設狀況。                    |

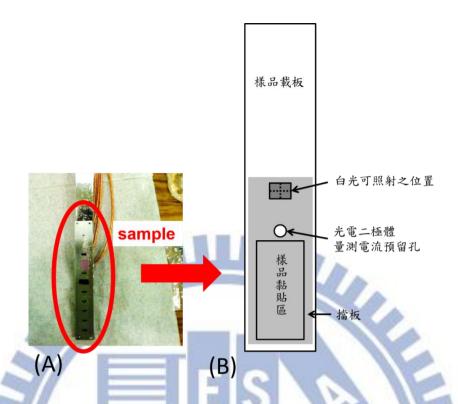

| 圖 | 2-7 | 試片黏貼於樣品載板之位置,(A)樣品載板實際構造,(B)樣品       |

|   |     | 載板黏貼位置示意圖。                           |

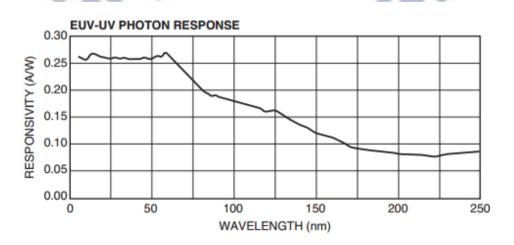

| 圖 | 2-8  | 光電二極體反應率-波長圖。26                                              |

|---|------|--------------------------------------------------------------|

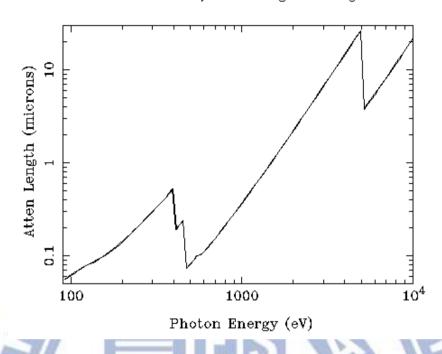

| 圖 | 2-9  | 不同能量的光源在於氮化鈦中之衰退長度。27                                        |

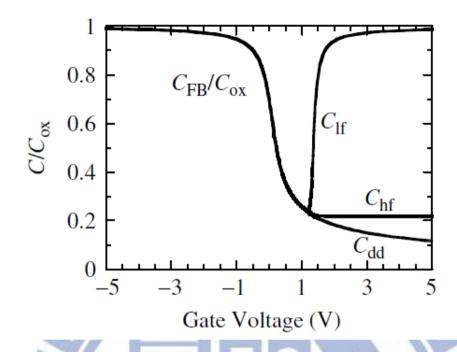

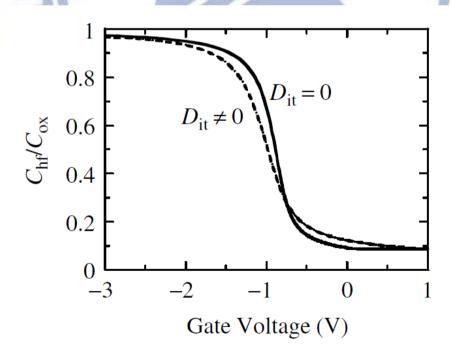

| 圖 | 2-10 | 金氧半電容理想電容-電壓圖。                                               |

| 圖 | 2-11 | 金氧半電容理想狀況(D <sub>it</sub> =0)和非理想狀況(D <sub>it</sub> ≠0)高頻電容- |

|   |      | 電壓圖。28                                                       |

| 昌 | 2-12 | 表面電位位於半能隙之能帶圖。29                                             |

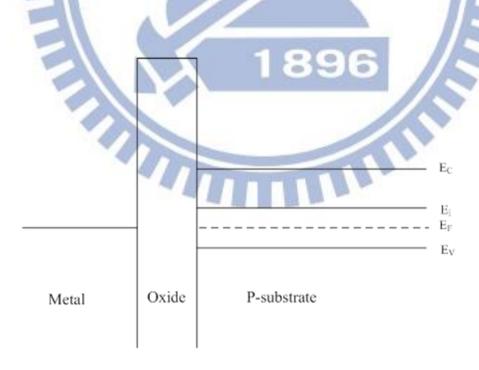

| 圖 | 2-13 | 平帶電壓能帶圖。                                                     |

| 圖 | 2-14 | PBTI 量測架構示意圖。30                                              |

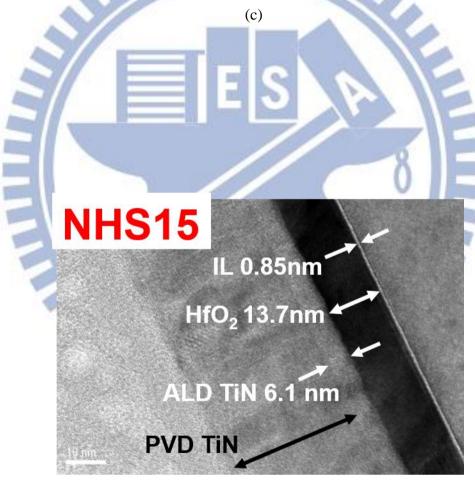

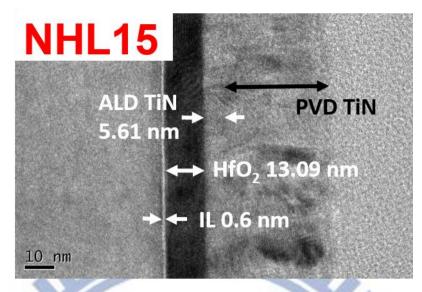

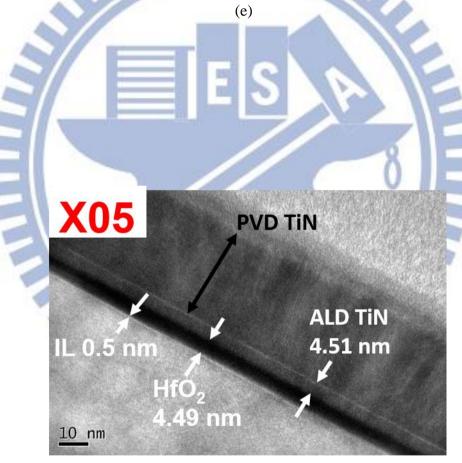

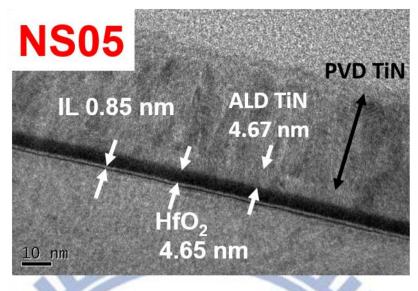

| 昌 | 3-1  | 閘極氧化層厚度 15 nm 和 5 nm 試片剖面結構之穿透式電子顯                           |

|   |      | 微鏡照片,(a)X15,(b)NS15,(c)NL15,(d)NHS15,(e)NHL15,               |

|   |      | (f)X05 , (g)NS05 , (h)NHS05 。                                |

| 昌 | 3-2  | 能量光譜散射儀(EDS)測量氮元素於試片薄膜各層所占百分                                 |

|   |      | 比,(a)為閘極氧化層 15 nm 之試片,(b)為閘極氧化層 5 nm 之                       |

|   |      | 試片。50                                                        |

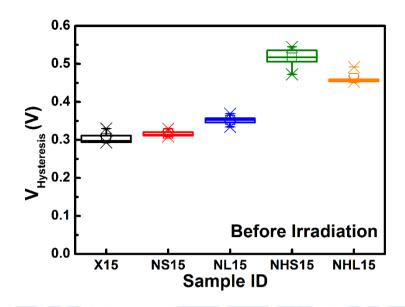

| 昌 | 3-3  | 閘極氧化層 15 nm 元件不同介面處理條件之電性比較,(a)為                             |

|   |      | X15 照射前電容-電壓曲線,(b)為 X15、NS15、NL15、NHS15                      |

|   |      | 和 NHL15 之平帶電壓, (c)為 X15、NS15、NL15、NHS15 和                    |

|   |      | NHL15 之遲滯電壓。52                                               |

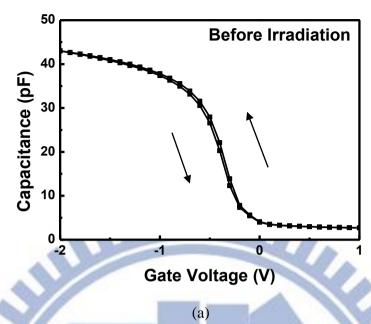

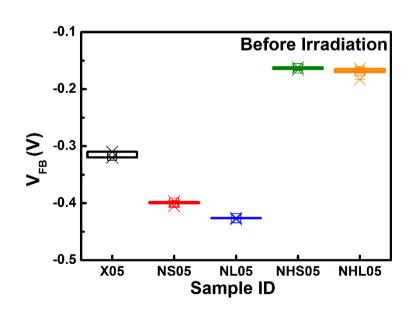

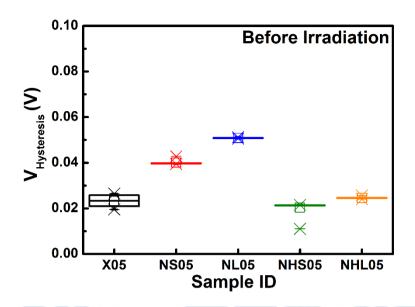

| 圖 | 3-4  | 閘極氧化層 5 nm 元件不同介面處理條件之電性比較,(a)為                              |

|       |       | X05 照射前電容-電壓曲線,(b)為 X05、NS05、NL05、NHS0                |

|-------|-------|-------------------------------------------------------|

|       |       | 和 NHL05 之平帶電壓, (c)為 X05、NS05、NL05、NHS05 和             |

|       |       | NHL05 之遲滯電壓。5                                         |

| 圖 3-5 | 5     | 所有條件照射前介面能態密度對能量分布比較圖,(a)為閘村                          |

|       |       | 氧化層 15 nm 元件,(b)為閘極氧化層 5 nm 元件。5                      |

| 圖 3-6 | 5     | 閘極氧化層 15 nm 試片,照射極紫外光前後之所有條件電性                        |

|       |       | 變化比較圖,(a)和(b)為平帶電壓變化,輻射劑量分別為 5                        |

|       | N N   | 和 275 mJ/cm <sup>2</sup> ,(c)和(d)為遲滯電壓變化,輻射劑量分別為 5    |

|       |       | ₹□ 275 mJ/cm <sup>2</sup> ·                           |

| 圖 3-7 | 7     | 閘極氧化層 5 nm 試片,照射極紫外光前後之所有條件電性變                        |

| 1     |       | 化比較圖,(a)和(b)為平帶電壓變化,輻射劑量分別為 50 禾                      |

|       | N. IN | 275 mJ/cm <sup>2</sup> ,(c)和(d)遲滯電壓變化,輻射劑量分別為 50 和 27 |

|       |       | mJ/cm <sup>2</sup> •                                  |

| 圖 3-8 | 8     | 閘極氧化層 15 nm 試片,照射極紫外光前後所有條件變化比                        |

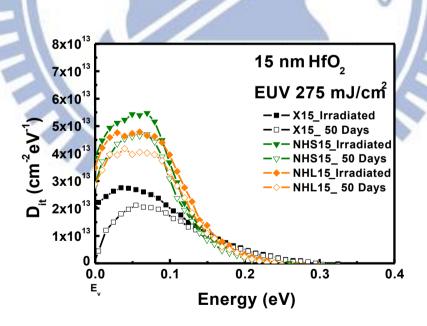

|       |       | 較之介面能態密度對能量分布圖,(a)為照射劑量 50 mJ/cm <sup>2</sup>         |

|       |       | (b)為照射劑量 275 mJ/cm <sup>2</sup> 。6                    |

| 圖 3-9 | 9     | 閘極氧化層 5 nm 試片,照射極紫外光前後變化比較之介面的                        |

|       |       | 態密度對能量分布圖,輻射劑量為 275 mJ/cm², (a)為 X05、                 |

|       |       | NS05 與 NL05, (b)為 X05、NHS05 與 NHL05。                  |

| 圖 3-10 | 閘極氧化層 15 nm 試片,經由極紫外光與 X-光照射後,所有                              |

|--------|---------------------------------------------------------------|

|        | 製程條件其電性數據變化比較圖,輻射劑量為 275 mJ/cm <sup>2</sup> ,(a)              |

|        | 為平帶電壓,(b)為遲滯電壓。62                                             |

| 圖 3-11 | 閘極氧化層 15 nm 試片,照射 X-光前後介面能態密度對能量                              |

|        | 分佈比較圖,輻射劑量為 275 mJ/cm <sup>2</sup> 。63                        |

| 圖 3-12 | 閘極氧化層 15 nm 試片,照射極紫外光與 X-光放置 50 天後,                           |

|        | 其之平帶電壓恢復百分比較。64                                               |

| 圖 3-13 | 試片編號 X15、NHS15 和 NHL15 之元件,照射極紫外光後與                           |

|        | 放置 50 天後之介面能態密度對能量變化比較圖,輻射劑量為                                 |

|        | 275 mJ/cm <sup>2</sup> °                                      |

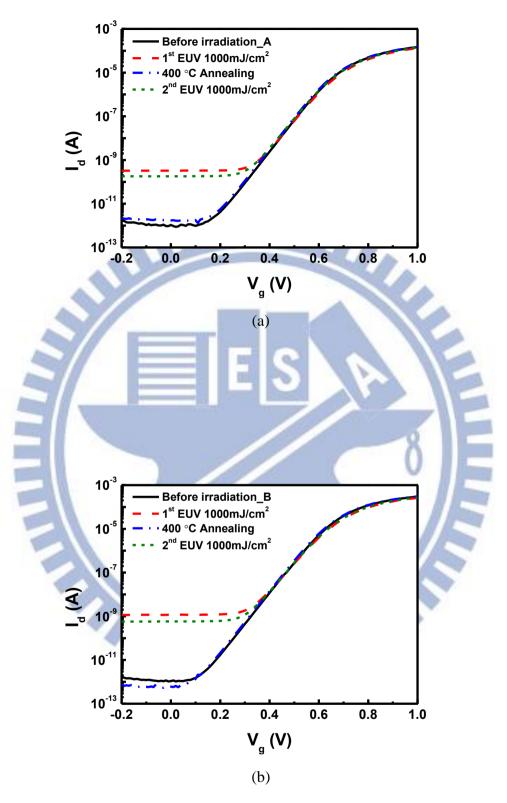

| 圖 4-1  | N 型先進製程電晶體經由 91.85 eV 之極紫外光照射 1000                            |

| 1      | mJ/cm <sup>2</sup> ,極紫外光照射前、照射後、400°C做真空退火與第二                 |

|        | 次照射極紫外光之 $I_d$ - $V_g$ 曲線,(a)試片 $A$ 與(b)試片 $B$ 。72            |

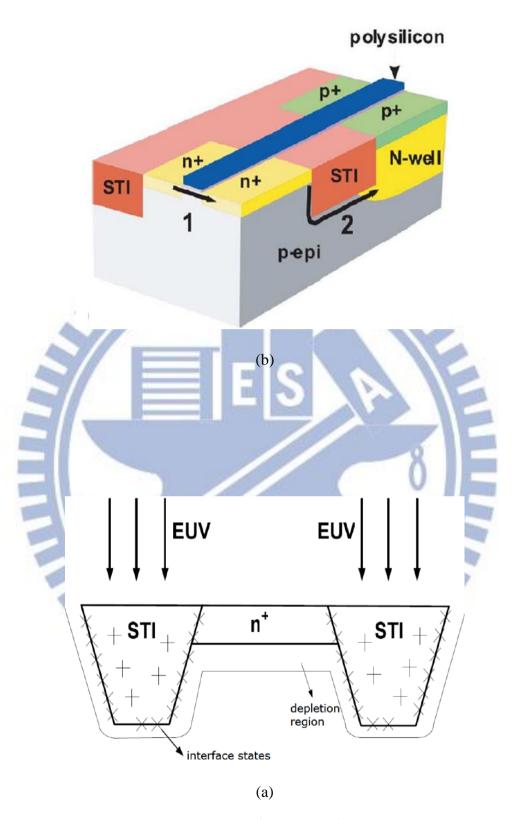

| 圖 4-2  | 兩種可能形成漏電路徑示意圖,(a)淺溝槽隔絕技術,(b)經由                                |

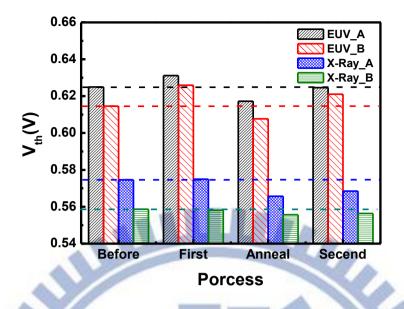

|        | 輻射後,導致關閉狀態漏電流增加之機制。73                                         |

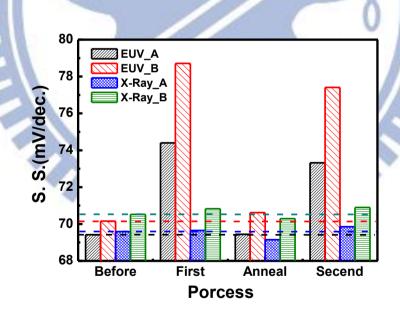

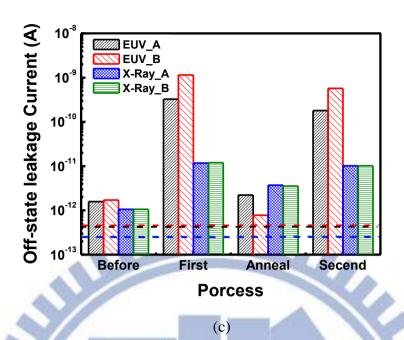

| 圖 4-3  | N 型先進製程電晶體經由極紫外光與 X-光照射 1000 mJ/cm <sup>2</sup>               |

|        | 後,照射前、照射後、400℃做真空退火與第二次照射之電                                   |

|        | 性變化曲線,(a)V <sub>th</sub> ,(b)S.S.,(c)關閉狀態漏電流。75               |

| 圖 4-5  | N 型先進製程電晶體偏壓前、偏壓 10000 秒後之 I <sub>d</sub> -V <sub>g</sub> 曲線, |

|       | (a)於常溫下,(b)於 150 °C。               | 77 |

|-------|------------------------------------|----|

| 圖 4-6 | 於常溫下,N 型先進製程電晶體之臨界電壓變化對偏壓時         | 間  |

|       | 分佈圖,(a)為未照射輻射,(b)以91.85 eV之極紫外光為光源 | ,  |

|       | 照射 1000 mJ/cm <sup>2</sup> 劑量。     | 78 |

| 圖 4-7 | 升溫至 150 °C,N型先進製程電晶體之臨界電壓變化對偏      | 壓  |

|       | 時間分佈圖,(a)為未照射輻射,(b)以91.85 eV之極紫外光  | 為  |

|       | 光源,照射 1000 mJ/cm <sup>2</sup> 劑量。  | 79 |

| 圖 4-8 | 輻射對於 PBTI 之影響趨勢圖,測量條件分別為偏壓 1.3 V   | ΄, |

|       | 施壓時間共 5000 秒。                      | 80 |

| 圖 4-9 | 輻射對於 PBTI 之影響趨勢圖,測量條件分別為偏壓 1.5 V   | ΄, |

|       | 施壓時間共 10000 秒。                     | 80 |

# 表目錄

| 表 | 2-1 | 所有試片實驗條件與相對應之代號。22                                   |

|---|-----|------------------------------------------------------|

| 表 | 3-1 | 電容元件實驗變數所對應之代號。42                                    |

| 表 | 3-2 | 元件照射輻射前之電性,(a)為閘極氧化層 15 nm 試片,(b)為                   |

|   |     | 閘極氧化層 5 nm 試片。43                                     |

| 表 | 3-3 | 照射極紫外光之前後平帶電壓和遲滯電壓差異,(a)為閘極氧                         |

|   |     | 化層 15 nm 試片,(b)為閘極氧化層 5 nm 試片。44                     |

| 表 | 3-4 | 閘極氧化層 15 nm 試片之照射 275 mJ/cm² 劑量,極紫外光                 |

|   | 5   | (91.85 keV)與 X-光(10 keV)照光前後差。45                     |

| 表 | 4-1 | 以 91.85 eV 之極紫外光為光源,劑量為 1000 mJ/cm <sup>2</sup> ,極紫外 |

|   |     | 光照射前、照射後、400 ℃做真空退火與第二次照射極紫外                         |

|   |     | 光之 V <sub>th</sub> 與 S.S.。71                         |

| 表 | 4-2 | 以 10 keV 之 X-光為光源,劑量為 1000 mJ/cm², X-光照射前、           |

|   |     | 照射後、400 ℃做真空退火與第二次照射 X-光之 V <sub>th</sub> 與 S.S.。    |

|   |     | 71                                                   |

## 第一章

### 緒論

#### 1-1 微影技術的演變

根據摩爾定律,每一年半,晶片上的電晶體數量就會增加一倍,從 1960 年代第一種微影系統 - 接觸式轉印(Contact printing)出現,70 年代後,工業製造應用主要以投影式機台(Projection)為主,解析度(Resolution)提升方法,以縮短光源波長( $\lambda$ )為主,如公式 1-1。

$$Resolution = \frac{k_1 \lambda}{NA} \tag{1-1}$$

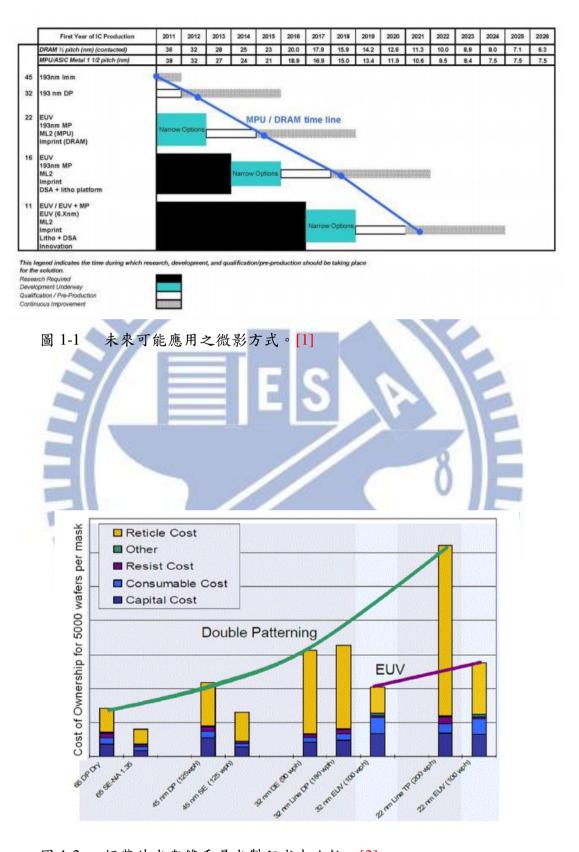

在公式 1-1 中,有兩個參數可以調變,ki 為比例常數, λ 為曝光光源波長,NA 為影像系統的孔徑大小。光源波長起先是由可見光 G-line (波長 436 nm) 到紫外光 I-line(365 nm),再到 248 nm 的 KrF 光源,微影系統演變至今,超大型積體電路廠商是以 ArF (193 nm)光源的浸潤式(Immersion)步進機(Stepper)和掃描機(Scanner)為最主要的曝光機台。但是,如圖 1-1 [1],當線寬到達 22 nm 以下,如果繼續使用上述提到的 193 nm 浸潤式系統,尚需輔以多重曝光技術才能達到目標。但因光單數增加使得成本和對準誤差增加,若能有更短波長的取代光源(極紫外光)或者是非光學(奈米壓印和電子束)微影技術,就不需要使用多重曝光技術,如圖 1-2 [2],以極紫外光為例,可看出製程成本大幅減少。這三種最有可能應用在下個世代的微影技術,簡單介紹於下:

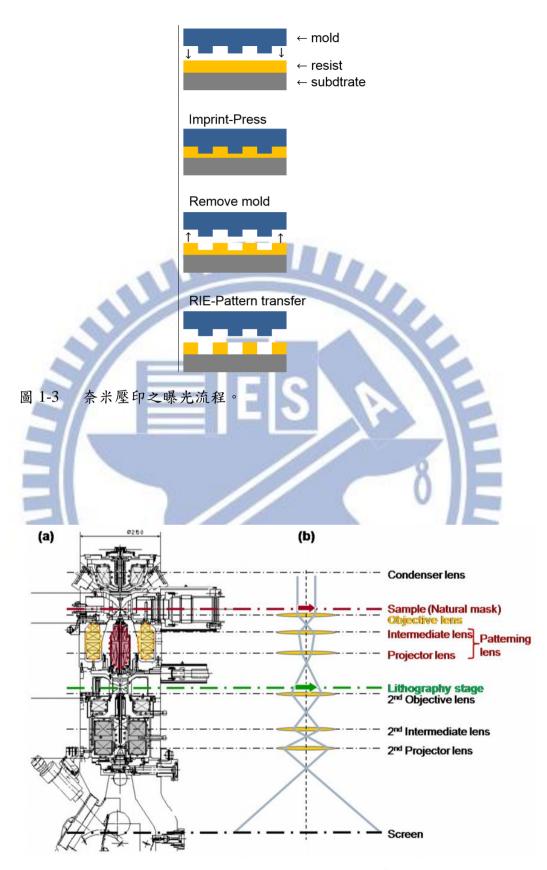

第一種是奈米壓印(Nanoimprint),此技術會事先將布局圖案製作成模版,利用壓印的方式將圖案轉印到光阻上,如圖 1-3。就參考文獻可知,已經可以做出 5 nm線寬 [3]。然而,要做出大面積且十幾奈米的線寬且要無缺陷,還是一個困難的問

題。另外,壓印方式為直接與光阻接觸,導致光阻有機會殘留在模板上,容易造成缺陷。模版的壽命,也是必須改善的問題。

第二種為電子東直接寫入(E-beam direct write, EBDW)技術,屬於無光罩曝光系統(Maskless lithography, ML2) [4],在現代製程中應用於製作光罩,好處是解析度高,可小於30 nm,景深大約20到30 μm,且不需光罩即可曝光,如圖1-4。但是,利用此方式的最大問題在於晶圓產出率很低,而一般製程廠商產能需求大約每小時兩百到三百片晶圓,電子東直接寫入不符合經濟效益,所以較不適合採用。但此系統佔地面積小,因此有人提出多重電子術曝光系統(Multi-Electron beam lithography),有望改善產能問題[5]。此外,還有另一個問題存在,電子散射(Electron scattering)導致毗鄰的曝光圖案相互影響,限制圖案的正確性,這主要由鄰近效應(Proximity Effect)所造成。

最後一種是極紫外光曝光(Extreme Ultra Violet Lithography, EUVL),基本原理為光學投影技術。雖然也是光學技術,但和 193 nm 浸潤式曝光也有許多差異。例如:此波段屬於軟 X-光,波長範圍從 4 nm 到 40 nm,容易被大部物質吸收,大多數都使用 13.4 nm 波長作為新光源,因為此波長有最佳的反射率(Reflectivity) [6]。但事實上,極紫外光在材料中的反射率還是很低,所以為了提高反射率至接近垂直入射的反射率,反射鏡的表面必須塗佈多層膜,即採用布拉格反射器(Bragg reflector) [6]。現今所用薄膜最佳的反射率 70%而已 [6],結構為鉬(Mo)/矽(Si)多層膜,鉬為高電子密度(Electron-density)的吸收層,矽為低電子密度的隔離層。由於當光線經過反射鏡,若鏡面有缺陷會降低反射率,並造成散射,這也是紫外光系統的問題之一 [6-7]。且為了避免光線被吸收,系統必須要在高真空中操作,另需無缺陷且高反射率的透鏡跟光罩來反射光束,以定義圖案,機台架構示意圖,如圖 1-5 [8]。

極紫外光有三種最常使用的光源產生方式:雷射激發電漿(Laser-produced plasma, LPP) [6, 9-12]、放電電漿(Discharge-produced plasma, DPP) [6, 9-10, 12]和同步輻射光源(Synchrotron)。雖然同步輻射光源最為穩定,但佔地面積太大且造價非常昂貴,所以只適合研究使用,通常工業用機台會以 LPP 和 DPP 兩種發光方式為主。目前艾斯摩爾公司(ASML)已實現採用 DPP 方式的極紫外光機台 [11],已有許多公司跟進採用,AMD、IBM 和東芝(Toshiba)使用此機台成功製造 22 nm 的元件 [13-15]。但機台造價仍比 193 nm 系統昂貴許多,如果能降低發光成本或提高光源強度以提升產量,較符合經濟效益。若能解決上述問題,極紫外光最有可能取代 193 nm 微影系統。

#### 1-2 輻射損傷影響

根據上一節的討論,我們認為極紫外光系統應用於10 nm 製程以下機率最大。因為極紫外光屬於高能輻射,尚需考慮輻射對於電子元件所造成的影響。輻射問題早於1960年代就開始被廣為討論,在當時已有許多科技被應用於外太空。在太空中有游離輻射,因此很多學者開始探討輻射對於電子產品的影響。隨著科技的演進,輻射不單只有在自然界產生,開始有人為發明而出現的輻射,應用於先進製程的超大型積體電路上,例如:離子植入(Ion implantation),電漿製程(Plasma process)等都是常用的技術。極紫外光是利用軟 X-光當作光源,能量高於193 nm光源,因此,若要將極紫外光微影導入生產線當中,就必須考慮到輻射對於電子元件會造成什麼樣的影響。

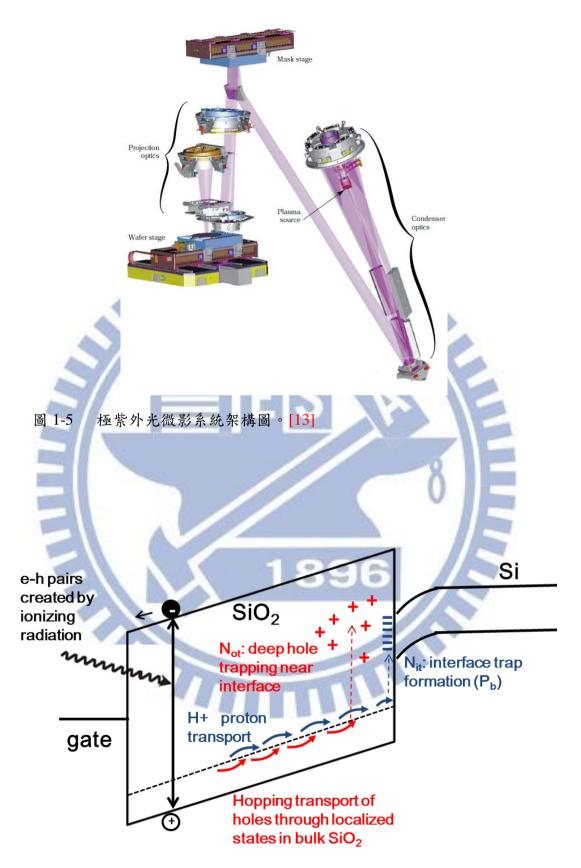

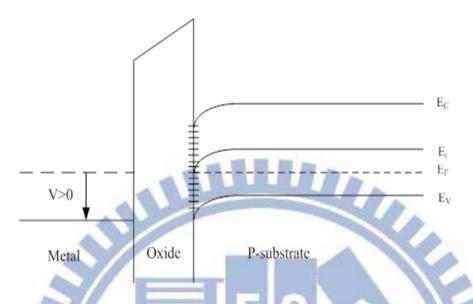

輻射導致損傷的機制可由圖 1-6 [16]為例,介紹輻射照射於元件產生之效應。 圖 1-6 為在一個 P 型基板金屬-氧化物-矽電容(MOS capacitor)的閘極(Gate)上,施加 正偏壓(Positive bias)的能帶圖(Band diagram)。當輻射的能量高於材料的能隙 (Bandgap),能量有可能會激發出電子-電洞對(e-h pairs)。這些電子-電洞對存在的 時間非常的短暫,大部分的電子會受到正偏壓影響,在微微秒(Picoseconds)內迅速往閘極方向移動,剩餘則會跟電洞複合(Recombine),而電洞將因為電場的關係,會往 Si/ SiO<sub>2</sub> (Si/SiO<sub>2</sub> interface)介面飄移,一部分將會被氧化層中靠近介面附近的能階(Localized states)捕捉,形成氧化層捕捉正電荷(Positive oxide trapped charges)。由於氫離子鍵結比起其它原子鍵結力更弱,斷鍵的氫離子會被驅動(Drift)到介面形成介面缺陷(Interface traps)。

在照完輻射之後,元件電氣特性會有非常嚴重改變 [16-18],例如:臨界電壓 (Threshold voltage,  $V_{th}$ )偏移、關閉狀態漏電流(Off-state leakage current)增加,甚至 是閘極導致汲極漏電流(Gate-Induced Drain Leakage, GIDL)更嚴重,這些通常是因其增加的氧化層捕捉正電荷和介面捕捉電荷(Interface trapped charges)導致。然而, 更嚴重的是所有特性都會隨著時間改變 [19],所以設計者就必須去評估效能和功用確保電路可以正常的運作。

#### 1-3 给氧化物金氧半元件及介面處理

現今電路需要具備高元件密度和較好的效能,根據電晶體電壓-電流公式 1-2,可以增加閘極電容密度,使閘極控制力提升。就電容公式 1-3 可知,降低閘極氧化層厚度可以增加電容密度。但是當降低氧化層厚度,雖可達到提升電流,卻會使閘極漏電流上升,而目前 SiO2 厚度已到達極限,漏電流不在可忍受範圍內,原因主要是載子直接穿隧機率上升,導致額外的功率消耗增加,所以解決方法必須找出可取代 SiO2 之材料 [20, 21]。

$$I_{D} = \frac{W}{L} \mu C_{ox} (V_{G} - V_{T} - \frac{V_{D}}{2}) V_{D}$$

(1-2)

$$C_{ox} = \frac{\kappa \varepsilon_0 A}{t_{ox}} \tag{1-3}$$

W為通道長度,L為通道寬度, $\mu$  為通道載子遷移率, $C_{ox}$  為在反轉狀態閘極下通道電容, $V_{G}$  閘極電壓。 $\kappa$  為相對介電質常數, $\epsilon_{0}$ 為真空電容率, $t_{ox}$  氧化層厚度。

挑選取代材料條件,第一材料之介電質必須高於  $SiO_2$ ,從等效厚度(Effect oxide thickness)公式來看,如公式 1-4。

$$EOT = d \frac{\epsilon_{SiO_2}}{\epsilon_{RRHH}}$$

(1-4)

EOT 為等效  $SiO_2$  之厚度,d 為取代材料之物理厚度, $\epsilon_{SiO_2}$ 為  $SiO_2$ 之介電質常數, $\epsilon_{RR}$  数, $\epsilon_{RR}$  数, $\epsilon_{RR}$  为取代材料之介電質常數。高介電質材料的好處為,相同的氧化層電容之下,相對於  $SiO_2$  的厚度,高介電質氧化物可以有較厚的氧化層,可使得載子穿隧能障的機率減小,降低漏電流。其次熱穩定性也必須考慮,因為高介電質材料沈積時,會與晶片表面反應,產生一層氧化物介於高介電材料與晶片之間,此介面層使得缺陷增加與遷移率下降,因此介面品質需謹慎考慮。

早期研究的高介電質氧化物包括三氧化二鋁(Al<sub>2</sub>O<sub>3</sub>) [22, 23]、二氧化鋯(ZrO<sub>2</sub>) [24, 25]、二氧化鈦(TiO<sub>2</sub>) [26, 27],還有二氧化鉿(HfO<sub>2</sub>) [28-30]。根據前人的研究總結,於矽晶片上前三種材料較不適合用來取代 SiO<sub>2</sub>,原因為三氧化二鋁的介電質常數不夠高,導致 EOT 調降幅度不夠,而二氧化鋯、二氧化鈦對於矽晶片的熱穩定性不夠好,在早期研究時,已發現難以整合於製程中,因此不採用。至於 HfO<sub>2</sub>,它的介電常數為 20~30 左右,實際厚度為等效厚度的 5~6 倍,因氧化層較厚,載子穿隧能障較高,不易造成漏電流,且遲滯現象較輕微與熱穩定性較佳。至今已有公司(例如:Samsung、Intel和TSMC等)生產 22 nm和 20 nm 製程的產品 [31-33],以鉛氧化物(例如 HfO<sub>2</sub> 跟 HfSiON等)取代原 SiO<sub>2</sub> 氧化層材料。

在開極材料方面,當氧化層的等效厚度降至 1 nm 等級,繼續使用多晶矽當開極就會有許多問題。當製程溫度超過 800 °C,硼離子會在氧化層中造成固定電荷 (Fixed charge),或者是穿透開極氧化層(Boron penetration),硼穿越氧化層到達通道,使晶片濃度改變,將導致臨界電壓飄移。此外,多晶矽開極靠近氧化層處會形成 開極空乏層(Gate depletion) [34],這空乏層會使通道位能(Channel potential)劣化,這也會導致 EOT 不能繼續調降。若使用金屬材料作為閘電極 [35,36],將無上述問題。搭配高介電質氧化物,還有增加通道載子遷移率、較高的轉導阻抗、較穩定的介面等優勢。雖然有製程溫度、P 和 N 型元件的開極能障必須要都匹配、材料穩定性、可靠度和製程相容性(Process compatibility)等問題,所以在材料選擇上都必須要多加考慮。目前工業界選擇搭配 HfO2之金屬是氮化鈦,因氮化鈦可匹配P 和 N 型 HfO2之電晶體的開極能障,與 HfO2之介面熱穩定性較好,通道載子遷移率也可以提升 [29,37,38]。因此,本論文採用 HfO2和氮化鈦分別作為開極氧化物及電極。

於 1-2 節有提到已有許多團隊研究關於 SiO<sub>2</sub> 的輻射傷害實驗,近 10 年來,因逐漸採用高介電質材料取代 SiO<sub>2</sub>,因而陸續有研究團隊進行輻射對於高介電係數介電質影響之研究。在 2000 年前後,開始有研究三氧化二鋁之團隊 [39, 40],採用輻射光源為 X-光,研究目的為了解三氧化二鋁元件抗輻射能力。而後確定 HfO<sub>2</sub> 較合適取代 SiO<sub>2</sub>,因此輻射對於 HfO<sub>2</sub> 元件之研究逐漸被看重,例如: J. A. Felix 和 D. M. Fleetwood 團隊研究輻射對於 HfO<sub>2</sub> 之元件電性、可靠度影響 [40-43]等相當透徹,但光源種類是以 X-光為主。接著,因極紫外光微影日益被看重,所以本實驗室開始著力於極紫外光對於高介電質元件影響之研究。起先為李勃學先生之論文 [44]為研究给氧化物與鋁氧化物之高介電質材料元件,證實三氧化二鋁之抗射能力最差。且得知不同高介電質材料之氧化層-矽介面層,對於極紫外光承受能力並不相同,如三氧化二鋁使用有機金屬化學氣相沉積系統(MOCVD)和原子層化學氣相沈積系統(ALD)製作之元件,MOCVD 元件之抗輻射能力較好,兩者差異在

於 SiO<sub>2</sub> 之介面層。有鑒於此,蘇婷婷小姐之論文 [45]為研究 HfO<sub>2</sub> 之介面差異(無、 1 nm 和 2 nm 介面層),結論為有化學氧化層介面層之元件較不易受輻射影響。但前兩位的研究,採用元件之間極氧化物厚度皆為 15 nm,相較之下,現今工業用間極 SiO<sub>2</sub> 厚度約 1 至 2 nm,15 nm HfO<sub>2</sub> 之等效厚度不適用。因此,孫銘鴻先生之論文 [46]是探討不同厚度 HfO<sub>2</sub> (5 nm、10 nm 和 15 nm)之抗輻射能力,證實越薄氧化層抗輻射能力越強。經由前三位學長姐之研究,雖然已對極紫外光對 HfO<sub>2</sub> 的影響有所了解,但當介面品質改變時,對於元件特性是否有影響,仍然有待查證。因此,本篇論文致力於探討極紫外光對 HfO<sub>2</sub>-Si 介面層品質之影響,接著下一小節將介紹論文中所用之改善介面方法。

#### 1-3-2 二氧化鉿及矽晶片介面品質

目前 HfO2 已應用在工業界,仍有問題需要考慮。如高溫製程過程中,沈積 HfO2 的熱穩定性(Thermodynamic stability),當 HfO2 在沈積時,會在矽晶片介面 (HfO2/SiO2)形成一層不希望有的反應層,這層介面可能會導致介面缺陷增加和遷 移率(Mobility)劣化。但是由蘇婷婷小姐之研究,可知不同 HfO2/SiO2 介面,確實對於元件電性造成影響,且已證實有介面層元件之抗輻射能力較好。所以,基於上述條件提出假設,做出可有較佳抗輻射能力之元件,且藉由改善介面層品質來減少缺陷增加和遷移率劣化。

可修補 SiO<sub>2</sub> 的內部缺陷。以上方法皆可讓電性有所提升,如介面能態密度(Interface state density)降低、漏電流降低和崩潰電壓增加,並且對於抗輻射能力已有許多研究皆證實擁有較好的特性 [51-55]。

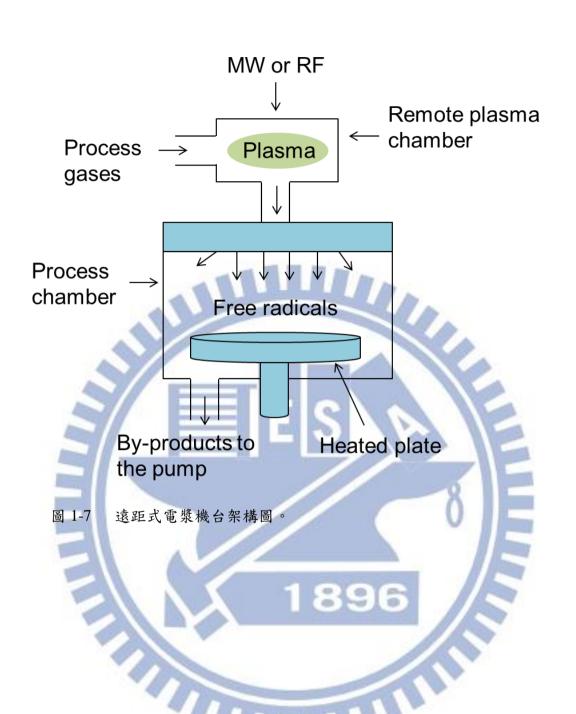

所以本篇論文中改善介面品質之方式是採用表面電漿處理。若以退火方式所形成之介面層較厚,會降低等效介質電常數,與原增加高介電質常數之目的相違,故不採用。電漿方式為遠距式電漿(Remote-type),此方式是以接地金屬將電漿中的電場/電流屏蔽,再利用氣流驅動,將電漿裡的「中性自由基氣體」吹出,如圖 1-7 為遠距式電漿機台之結構與運作流程。此種電漿方式雖然較直接式電漿(Direct-type Plasma)效率低,但考量此方式試片不會直接暴露在電場中與電漿接觸,導致電漿中的高電場及離子撞擊可能對試片造成損傷,因此採用遠距式電漿,希望元件有較好的介面品質與抗輻射能力。

#### 1-4 論文架構

第一章將介紹微影曝光演進過程,以及下世代微影技術奈米壓印、多重電子 束曝光系統和極紫外光微影,分析其優缺點與被採用的可能性,彙整歸納後,認 為極紫外光微影系統將是最有機會為工業界所採用。接著,因極紫外光波長極短 能量很強,輻射影響的重要性更需謹慎考量。且據目前趨勢來講,以HfO2取代SiO2 閘極廣為使用。因此,前人已進行相關研究,但僅限於不同材料、介面厚度、氧 化層厚度和退火溫度,尚未透徹瞭解高介電質材料。雖然已證實介面厚度之差異 性,但其品質之差異仍未查證,因而本篇論文研究著重於介面品質差異性之抗輻 射能力。

第二章說明論文中所使用之電容及電晶體元件結構與製程條件,實際製程完後之元件結構剖面示意圖和電子顯微鏡(Transmission Electron Microscope, TEM)所拍攝之照片,及在國家同步輻射中心的實驗站架設跟實驗步驟、輻射劑量計算方

法,並且介紹量測架構與資料萃取方法。

第三章內容為探討不同介面處理對電容元件特性造成改變,並且經由照射游離輻射觀察試片的抗輻射能力,與前人前研究結果相同得到較好的抗輻射能力。 光源分別為極紫外光與X-光,照射劑量為50和275 mJ/cm²,採取兩種劑量原因分別為,低劑量接近極紫外光微影曝光,氧化層接受的輻射劑量,高劑量則較易看出輻射對於元件之影響。於介面做電漿處理,也需判斷對於先進製程元件同前人研究成果相符,當閘極氧化成降至5 nm,元件之輻射損傷同樣有大幅下降之趨勢,以利應用於製程中。

第四章藉由先進製程之電晶體,實際了解輻射對於元件之運作影響,前人研究成果之可藉由高溫退火恢復受輻射損傷元件至照射前電性,因此本篇論文中討論此方法,當元件再次照射游離輻射,其輻射損傷與第一次照射相比,是否會使元件之抗輻射能力下降。接著元件可靠度是元件應用重要參考參數,於前人研究成果,證實較強之電場下,量測正偏壓溫度不穩定度 (Positive bias temperature instability, PBTI),並無法確認游離輻射對於元件之影響,因此為了解元件照射游離輻射後之可靠度,我們調降偏壓之電壓,降低電場對於可靠度量測影響之結果,以討論輻射本身的影響。

最後一章為本論文結論及未來值得繼續研究之方向。

圖 1-2 極紫外光與雙重曝光製程成本比較。[2]

圖 1-4 EBDW 技術結構,(a)機體設計圖,(b)電子東路徑圖。[4]

圖 1-6 P型電容於閘極上施予正偏壓,當經由照射輻射後電子電洞於能帶傳導情形。[16]

### 第二章

## 元件製程與實驗步驟

#### 2-1 元件製程

#### 2-1-1 金氧半電容製程步驟

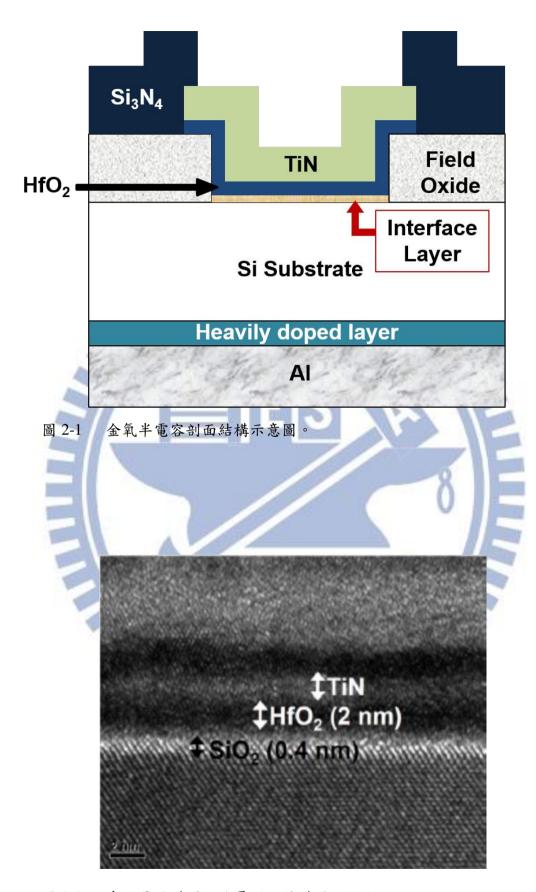

本論文所使用的電容結構如圖 2-1 所示,元件編號列於表 2-1,使用 N 型電阻係數為 1~10 歐姆-公分的 4 吋矽基板製作,製作地點為國立交通大學奈米中心 (NFC)及國研院奈米元件實驗室(NDL),製程步驟如下:

- 在P型晶背進行能量 40 keV,劑量 5×10<sup>15</sup> cm<sup>-2</sup>的 BF<sub>2</sub>+離子植入,以得到 較好的歐姆接觸(Ohmic contact)。此步驟由奈米元件實驗室代工製作。

- 2. 在奈米中心以標準 RCA 清洗製程清洗晶片表面。

- 3. 在奈米中心成長 300 nm SiO<sub>2</sub>,作為絕緣氧化層,氧化溫度為 1050 ℃。

- 4. 以第一道光罩定義主動區,再利用 BOE 濕蝕刻 SiO2。

- 5. 以標準 RCA clean 製程清洗晶片表面,但取消最後一道浸泡氫氟酸稀釋溶液(DHF, HF:H<sub>2</sub>O=1:100)的步驟,以保留經過 RCA-2 步驟所形成的化學氧化層(Chemical oxide, SiO<sub>x</sub>),目的是為了減少 HfO<sub>2</sub> 跟矽晶片介面的張力,減少鍵結缺陷,並使 HfO<sub>2</sub> 較容易沈積於表面。

- 6. 使用原子層化學氣相沈積系統(Atomic Layer Chemical Vapor Deposition System, ALD)沈積 15 nm 及 5 nm 兩種厚度的 HfO<sub>2</sub>, 前驅物為四(二甲氨基)化鉿 (Hf[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>, TDMAH)。沈積前利用 ALD 內部電漿,進行不同種類的遠端電漿(Remote plasma)表面處理,條件詳列於下:

#### A. 沒有做電漿處理

- B. 使用氮氣電漿,流量為12 sccm,功率為300瓦,時間為30秒或120秒,壓力約為20mTorr。

- C. 使用氨氣電漿,流量為 12 sccm,功率為 300 瓦,秒數為 30 秒 或 120 秒,壓力約為 20 mTorr。

- 7. 以原子層化學氣相沈積系統沈積氮化鈦 5 nm,作為閘極金屬,前驅物為四(二甲氨基)化鈦 (Ti[N(CH<sub>3</sub>)<sub>2</sub>]<sub>4</sub>,TDMAT)。因原子層化學氣相沈積速率較低,故僅沈積 5 nm,另以濺鍍方式增加厚度。

- 8. 於奈米元件實驗室以多層金屬漸鍍系統(PVD)沈積氮化鈦 35 nm,讓閘極厚度達到 40 nm。

- 使用奈米元件實驗室之金屬快速退火爐(RTA),在氦氣環境中,以500 ℃

退火30秒。

- 10. 以第二道光罩定義閘極圖案,並利用奈米元件實驗室之金屬乾式蝕刻機 (TCP 9600)蝕刻氮化鈦閘極。

- 11. 使用奈米元件實驗室之電漿輔助化學氣相沈積系統(Plasma enhanced chemical vapor deposition, PECVD)沈積 100 nm 氮化矽(SiN<sub>x</sub>) 保護層 (Passivation layer)。

- 12. 以第三道光罩定義出針測區域,並使用氫氟酸稀釋溶液蝕刻氮化矽。

- 13. 使用奈米中心的熱阻絲蒸鍍系統(Thermal Evaporation Coater)在晶片背面 鍍鋁電極 300 nm。

- 14. 以氮氫混合氣體(Forming gas, N<sub>2</sub>:H<sub>2</sub>=95:5)在400℃退火30分鐘。

#### 2-1-2 N型金氧半電晶體

本論文使用的N型金氧半電晶體製作方式為閘極後製(Gate last process)之平面式元件,閘極電極和介電層的材料分別採用氮化鈦和 HfO<sub>2</sub>,且於第一章提到 HfO<sub>2</sub>

會與矽晶片形成介面層,因此閘極氧化物包含 2 nm 的  $HfO_2$ 和 0.4 nm 的介面氧化層。使用淺溝渠隔離(Shallow trench isolation, STI)作為元件之間的隔離技術,源極與汲極(Source/Drain)採用自動對準鎮矽化物(Ni-silicide)技術以降低寄生電阻(Parasitic resistance),剖面結構圖如圖 2-2 所示。相較於其它條件製程,此製程之元件穩定性很好,有助於減少極紫外光研究電晶體之間差異性,受輻射損傷影響能較精準分析。

#### 2-2 國家同步輻射中心(NSRRC)實驗環境

本篇論文中所使用之 X-光與極紫外光皆屬於同步輻射光,供應光源之單位為國家同步輻射研究中心,於此單位之編號 07A1 與 08A1 光束線實驗。所以在本節之中,將分為兩小節介紹 07A1 與 08A1 光束線,和各實驗站實驗架設流程,最後一小節為輻射劑量計算方式。

# 2-2-1 07A1 光束線與實驗架設

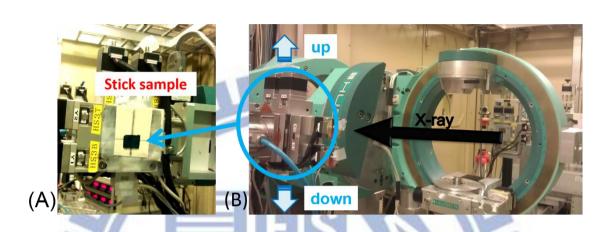

07A1 實驗站研究類型通常為 X-光掃描、X-光吸收光譜和微探針。可供應之能量範圍從 5 keV 到 23 keV。因光源能量較強不易被粒子吸收,所以實驗環境為大氣壓之下,光束截面積大小 0.5 mm  $\times$  0.2 mm,光通量約  $8.6\times10^{10}\sim2.4\times10^{13}$  photons/sec。本論文之實驗站架設如圖 2-3 所示,(A)為試片黏貼示意圖,(B)為實驗設備設置示意圖,試片放置與對準步驟條列於下:

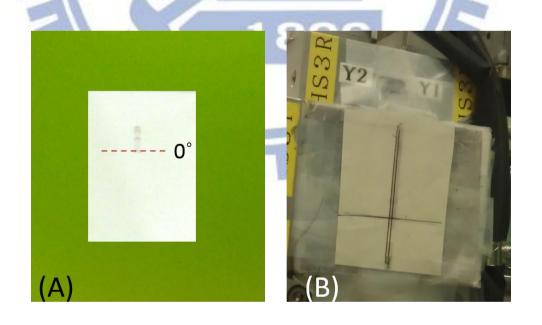

1. 取一張感熱紙,固定於擋板上,先將載板角度歸零,開啟X-光,此時光源位置會於紙上顯現光源圖案,如圖2-4 (A)所示,此圖案即為試片中心點對準位置,並畫出十字線以便對準,如圖2-4 (B)所示。

由光電二極體量測光束線電流,再藉由光電流轉換公式換算成電子數, 計算出每秒之接收輻射量。

MILLE

- 3. 將試片黏貼於感熱紙上,試片之刻號與十字線對準。

- 4. 設定曝光參數,而後開始照光。

- 5. 若有其它試片,則從步驟 2重新開始執行。

#### 2-2-1 08A1 光束線與實驗架設

08A1 光束線提供 15 到 200 eV 光源,包含極紫外光的能量(91.85 eV),所以本篇論文使用 08A1 作為光源供給,流量大約為 2x10<sup>10</sup> 每秒光通量,光源面積可達到 0.016 cm<sup>2</sup>。共有三個光柵可分別取出不同波段之光源,本實驗取 N=900/mm 之光柵,此光柵於各能量之光通量較為平均。應用領域為半導體電子表面與介面結構分析,例如:PES、ARPES、PAS 和 XPS 等分析。此條光束線由於能量較低,光線較易被其它物質所吸收,實驗必須於真空環境中進行。因此本論文之 08A1 實驗站為高真空系統,共有兩個高真空渦輪分子幫浦和一個機械幫浦,讓主要腔體真空值到達高真空,避免極紫外光被其餘粒子吸收,架構示意如圖 2-5 所示,實際架設情況如圖 2-6 所示。以下列為本實驗站操作之流程:

- 1. 破真空。關閉 V1、V2 和 V3 閥門、P1 與 P2 幫浦,等真空值提升至 10<sup>-4</sup> torr 以上。而後由 P1 幫浦上之洩壓閥吹氮氣。

- 2. 拿出試片載板。鬆開腔體上方之螺絲。

- 3. 黏貼實驗試片。利用碳膠貼於試片載板上,黏貼位置如圖 2-7 所示。載板放回主要腔體,確定載板可上下移動,不會碰觸腔體側壁,而後把試片移至最下方,確保打開閥門時,光源不會照射到試片,鎖緊腔體上方之螺絲。

- 4. 開始抽真空。打開 V2 和 V3 閥門, 開啟 P3 機械幫浦, 等待壓力降至 5×10-2

torr 以下。開啟 P1 與 P2 分子幫浦,等待壓力降至 1×10<sup>-7</sup>~5×10<sup>-8</sup> torr。

- 5. 白光定位。設定同步光源為白光,打開光束線閘門,利用望遠鏡觀測白光位置並調整,白光可照射之範圍,如圖 2-7 (B)。而後再把望遠鏡之視野中心點對於白光最亮之位置,關閉光束線閥門。

- 6. 測量光電流換算每秒輻射量。移動載板至光電二極體附近,改變光源能量為極紫外光 91.85 eV,在打開光束線閥門,上下、左右移動載板找出光電流最大值,關閉閥門,以光電流換算出每秒之接收輻射量。

- 7. 光源與望遠鏡對準。移動載板使欲照射之位置與望遠鏡之中心點對準。

- 開始照光。於打開光束線閥門同時倒數曝光秒數,倒數完畢時同時關閉 光束線閥門。

- 9. 若有其它試片在載板上,則回到步驟7重複執行。

- 10. 載板上全部試片照射完畢後,若有其它試片需要照射,則回步驟 1 重複 所有步驟。

### 2-2-3 輻射劑量計算

本篇論文之輻射量計算方式為,先計算出光通量(Flux)。07A1 光束線可直接得知光通量,不需自行計算。而 08A1 因無法直接得知光通量,需先利用光電二極體(Photo diode),將接受到之光能轉換成電能,藉由電流計量測電流值。本篇所採用之二極體為 International Radiation Detectors incorporation (IRD inc.)所製造,型號

反應效率公式 2-1,可得二極體轉換效率 $(\eta)$ 。因此當得知電流值,帶入光通量公式 2-2,即可得到光通量。

是 AXUV 100G。由產品手冊可得知反應效率(Responsivity),如圖 2-8 [56]。帶入

$$R = \eta \frac{q}{hf} \approx \eta \frac{\lambda(\mu m)}{1.23985(\mu m \times W/A)}$$

(2-1)

$$Flux = \frac{I}{n \times a} \tag{2-2}$$

以上公式 R 為反應效率 (Responsivity) , $\eta$  為二極體轉換效率 (quantum efficiency) , $\lambda$  為光源波長,I 為光電流值,q 為電子量。當得到光通量後,帶入每秒輻射劑量公式 2-3,得到每秒輻射劑量( $D_s$ )。

$$D_s = \frac{Flux \times E \times q}{Area} \tag{2-3}$$

Area 為面積,E為光源能量。但因影響電性最嚴重的是氧化層,氧化層上有金屬電極,所以需考慮輻射光穿透金屬閘極的衰退量,導致氧化層照射量較原預估值低,為了接近真實之曝光劑量,必須考慮光源穿透機率(Probability of radiation passing),如公式 2-4。

$$p(x) = e^{-\frac{x}{\lambda}} \tag{2-4}$$

P為穿透薄膜之機率, λ為衰退長度(Attenuation length), x 為薄膜厚度。由公式 2-4 可看出, 當薄膜厚度越薄,穿透機率越大。且因衰退長度會因能量和材料, 而有所改變,在本論文使用的能量範圍內,能量越強衰退長度越長,如圖 2-9 所示, X-光幾乎不會衰退,但極紫外光部分則須加以考量。

#### 2-3 電性計算

本節分為兩小節,分別介紹電容與電晶體電性分析方式。第一節為電容結構,利用電容-電壓量測(Capacitance-voltage (C-V) measurement),所得之數據以高頻率電容-電壓法(High-frequency C-V method,也稱作 Terman method)計算 [57]元件之介面能態密度對能量分佈。而另一小節為電晶體部分,是以正偏壓變溫量測 (Positively-biased temperature instability, PBTI)可靠度,臨界電壓以最大轉導值方法 (Maximum transconductance method)計算。

## 2-3-1 氧化缺陷(Oxide trap)和介面缺陷(Interface trap)計算

從 1-2 節可知,當電容經輻射照射後,有電子-電洞對產生,造成氧化缺陷、 介面缺陷和遲滯現象增加,造成電容-電壓圖扭曲或位移。本篇論文電容-電壓資料 萃取方法為高頻電容-電壓法步驟如下,先假設理想電容-電壓曲線為無介面缺陷, 計算出理論電容-電壓曲線,如圖 2-10。根據簡單的電容串聯公式:

$$\frac{1}{c} = \frac{1}{c_{ox}} + \frac{1}{c_d} \tag{2-5}$$

Cox 由測量值可得,而 Cd 由已知之晶片濃度,即可理論計算出電容與偏壓的關係,如公式 2-6 所示:

$$C_{\rm d} \equiv \frac{dQ_s}{d\varphi_s} = \frac{\varepsilon_s}{\sqrt{2}L_D} \frac{1 - e^{-\beta\varphi_s} + \frac{n_{p_0}}{p_{p_0}} (e^{\beta\varphi_s} - 1)}{F(\beta\varphi_s, \frac{n_{p_0}}{p_{p_0}})}$$

$$V_{\rm G} = \frac{Q_s}{c'_{ox}} + \varphi_s + V_{ideal\ FB}$$

$$(2-6)$$

$$F\left(\beta\varphi_{s}, \frac{n_{p0}}{p_{p0}}\right) = \sqrt{(e^{-\beta\varphi_{s}} + \beta\varphi_{s} - 1) + \frac{n_{p0}}{p_{p0}}(e^{\beta\varphi_{s}} - \beta\varphi_{s} - 1)} \geq 0$$

$$\beta \equiv \frac{q}{kT}$$

$$L_D \equiv \sqrt{\frac{\varepsilon_s}{p_{p0}q\beta}}$$

理想電容與測量差異如圖 2-11,先找出其中一點電壓之理想值電容,此電壓可得一表面電位,再藉由內插法得測量值相同電容之電壓,就可找到彼此電壓差 $\Delta V_G$ ,依此即建立 $\varphi_s$ - $V_G$ 關係,帶入公式 2-7 就可得介面缺陷密度 $(D_{it})$ 。

$$D_{it} = \frac{C_{ox}}{q} \frac{d\Delta V_G}{d\varphi_S}$$

(2-7)

## 2-3-2 正偏壓變溫量測

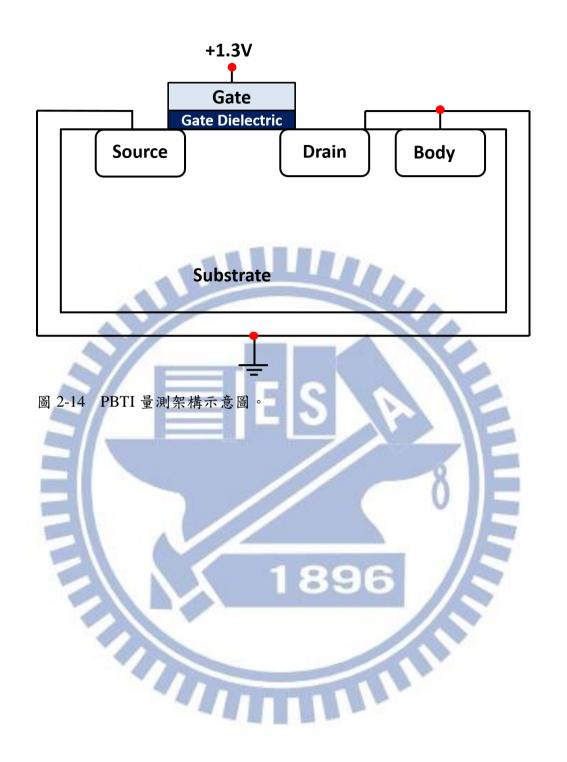

在本論文中,電晶體輻射照射之可靠度測試方法為正偏壓溫度不穩定性量測。 所使用量測條件為在閘極施予+1.3 V偏壓,其它三端接地,量測溫度為23與150 °C,閘極總加電壓時間為5000秒,於每段加電壓完後立即量測電壓-電流(I-V)特性, 確保氧化層中缺陷不會因延遲測量,而有捕獲電荷逸散(Detrap)的情形,架設線路 如圖2-14。

臨界電壓( $V_{th}$ )計算方式為最大轉導法(Gm)。首先算出最大轉導值相對之電壓值,外插出電流為0之電壓值,則此電壓值接近臨界電壓,如公式2-8。

$$V_{\text{th}} = V_{\text{Gm,max}} - \frac{V_{\text{D}}}{2} \tag{2-8}$$

表 2-1 所有試片實驗條件與相對應之代號。

| Sample ID | HfO <sub>2</sub> Thickness | Plasma          | Time    | Light/Dose                                                 |  |  |

|-----------|----------------------------|-----------------|---------|------------------------------------------------------------|--|--|

| X15       |                            | X               | X       |                                                            |  |  |

| NS15      |                            | $N_2$           | 30 sec  |                                                            |  |  |

| NL15      | 15 nm                      | $N_2$           | 120 sec | EUV X-ray 50/275 mJ/cm <sup>2</sup> 275 mJ/cm <sup>2</sup> |  |  |

| NHS15     |                            | $NH_3$          | 30 sec  | 30/2/3 HIJ/CHI 2/3 HIJ/CHI                                 |  |  |

| NHL15     |                            | $NH_3$          | 120 sec |                                                            |  |  |

| X05       |                            | X               | X       | 7                                                          |  |  |

| NS05      |                            | $N_2$           | 30 sec  |                                                            |  |  |

| NL05      | 5 nm                       | $N_2$           | 120 sec | EUV 2                                                      |  |  |

| NHS05     | <b>\</b> //                | NH <sub>3</sub> | 30 sec  | 50/275 mJ/cm <sup>2</sup>                                  |  |  |

| NHL05     | <b>//</b>                  | NH <sub>3</sub> | 120 sec |                                                            |  |  |

圖 2-2 先進電晶體閘極堆疊剖面結構圖。[46]

圖 2-3 07A1 實驗站架設圖,(A)試片黏貼示意圖,(B)實驗設備設置示意圖。

圖 2-4 07A1 實驗站定位示意圖,(A)X-光 0° 起始點,(B)對準線劃記方式。

圖 2-5 08A1 實驗站機台架設示意圖。

圖 2-6 08A1 實驗站機台實際架設狀況。[58]

圖 2-7 試片黏貼於樣品載板之位置,(A)樣品載板實際構造 [58],(B)樣品載板黏貼位置示意圖。

## 1896

圖 2-8 光電二極體反應率-波長圖。[56]

TiN Density=5.22, Angle=90.deg

圖 2-9 不同能量的光源在於氮化鈦中之衰退長度。[59]

## 1896

圖 2-10 金氧半電容理想電容-電壓圖。[59]

圖 2-11 金氧半電容理想狀況( $D_{it}$ =0)和非理想狀況( $D_{it}$  $\neq$ 0)高頻電容-電壓圖。 [59]

圖 2-12 表面電位位於半能隙之能帶圖。

圖 2-13 平帶電壓能帶圖。[46]

## 第三章

## 電漿處理電容器之介面層對於抗輻射能力影響

- 3-1 元件與照光劑量介紹

- 3-1-1 元件與實驗儀器介紹

本論文為了使於同次曝光中可照射元件較多,因此使用直徑 50 µm圓形之元件,面積約為 1.97×10<sup>-5</sup> cm<sup>2</sup>,且根據前人預估,光源面積大小約為 1.6×10<sup>-2</sup> cm<sup>2</sup>,因此於同一次曝光中,可以照射十個元件。每個元件的電極都採取上電極與背電極,氧化層厚度分別為 15 nm 與 5 nm,共有三種 HfO<sub>2</sub>/Si 基板介面層,分別為無電漿處理、氮氣電漿處理以及氨氣電漿處理,試片詳細製程條件已於第二章中介紹,依據不同製程步驟編號規則如表 3-1 所示。

輻射光源來至於國家同步輻射研究中心之 08A1(91.85 eV;極紫外光源)與 07A1(10 keV; X-光光源)光東線,光通量約為 1x10<sup>13</sup> photons/sec,達到 50 和 275 mJ/cm<sup>2</sup> 的照射秒數約為 5 與 28 秒。50 mJ/cm<sup>2</sup> 是接近於曝光系統之輻射劑量,為了較明顯看出照射前與照射後差異,方便分析電性變化,刻意提高劑量至 275 mJ/cm<sup>2</sup>。

而元件之電容-電壓特性曲線測量部分,皆由安捷倫精密阻抗儀 4284B 量測,量測頻率設定為 100 kHz。並且為了降低照射後自我修復的影響,皆於 24 小時內完成量測。

### 3-1-2 元件結構

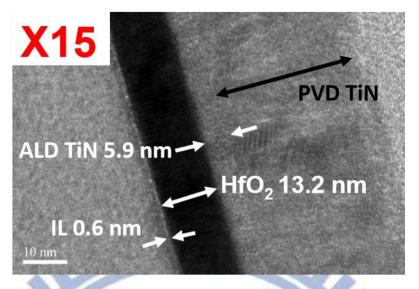

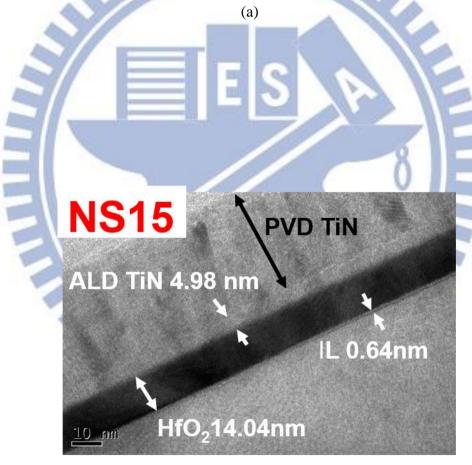

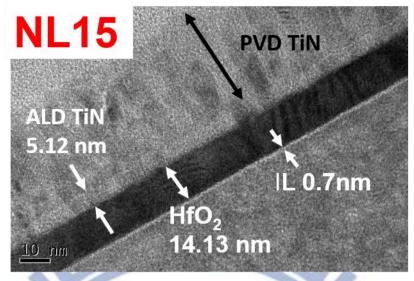

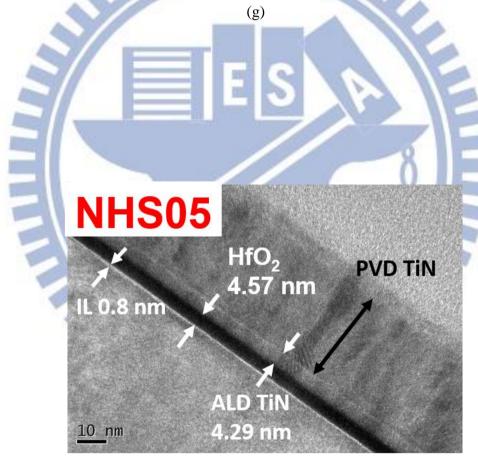

首先實際製程結構來看,如圖 3-1 (a)至(h)分別為氧化層厚度 15 nm 和 5 nm 之穿透式電子顯微鏡(TEM)照片,確定元件閘極氧化層厚度,以及經由電漿處理後氮元素是否有特別提高,進而影響閘極氧化層的成長速率。試片共分析八組條件, 15 nm 氧化層元件採取未經電漿處理、長短時間處理氮氣和氨氣電漿試片,另外 5 nm 氧化層元件與是確認厚度和元素分佈趨勢是否與 15 nm 相同,因此沒有挑選未經電漿處理、短時間處理氮氣和氨氣電將試片進行分析。從圖 3-1 可看到 X15、NS15、NL15、NHS15、NHL15、X05、NS05 和 NHS05 各條件 HfO2實際堆疊厚度分別為 13.2 nm、14.04 nm、14.13 nm、13.7 nm、13.09 nm、4.49 nm、4.65 nm 和 4.57 nm,而 HfO2/Si 基板之氧化接觸介面層(Interfacial layer, IL)厚度分別為 0.6 nm、0.64 nm、0.7 nm、0.85 nm、0.6 nm、0.5 nm、0.85 nm 和 0.8 nm,詳細實際測量參數皆列於表 3-2。

由上述可知經由電漿處理過後,HfO<sub>2</sub>厚度不論是 15 nm 與 5 nm,似有些許增加,有可能是由於電漿處理後,介面層表面鍵結改變,影響 HfO<sub>2</sub>的初始沈積速率。但是也有可能是試片間的製程變異。基本上厚度差異不大,應不致於影響實驗結果。不同條件試片之介面層厚度也略有不同,但是和電漿處理條件並無明顯趨勢,可能也是製程變異與取樣誤差。

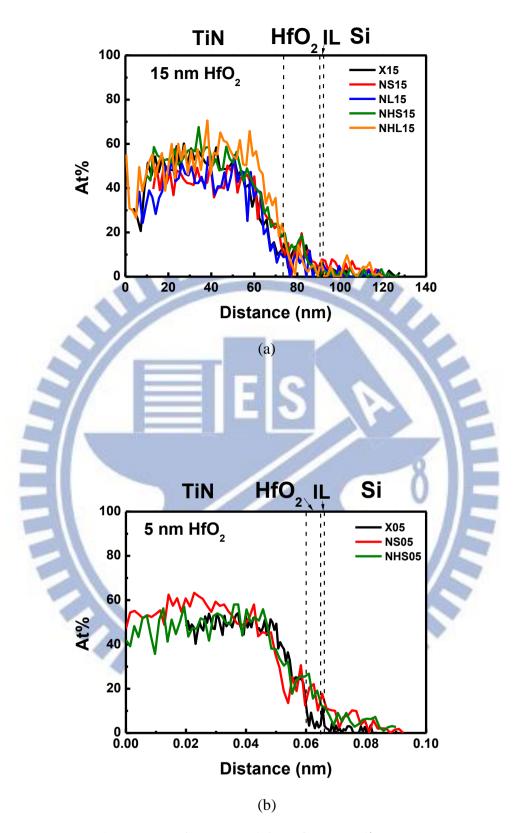

另外從元素分析來看,如圖 3-2 為前述 TEM 試片的能量光譜散射儀(EDS)測量的氮原子分佈,圖(a)為試片條件 X15、NS15、NL15、NHS15 和 NHL15 之氮原子分佈,而圖(b)為試片條件 X05、NS05 與 NHS05 之氮原子分佈,顏色與對應的條件分別為黑色未做電漿處理,紅色藍色為氮氣處理短長時間,而綠色橘色為氨氣處理短長時間。先從氧化層 15 nm 試片觀察,NS15、NL15、NHS15 和 NHL15 試片於介面處氮元素與 X15 相比略有增加,但並不明顯。而 5 nm 試片部分,在NS05 和 NHS05 氮元素比例確實有一峰值,然而在 X05 試片卻也有一峰值,推測

由於 HfO2 層太薄, 導致後續製程氮化鈦之氮原子,因為退火製程擴散至介面處, 因此三者雖然有較高的氮元素,所以無法確認是否由電漿處理增加原子比例。另 一個有可能原因為介面層不到 1 nm,這對於 EDS 元素分析的空間解析度有困難, 使得電子束偵測到鄰近之材料,因而會偵測到其它層的元素訊號情形產生。總結 上述實驗數據,從能量光譜散射儀量測結果,無法明確區分出不同電漿處理後之 間的氮元素分佈差異性。

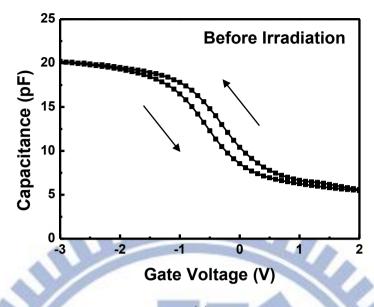

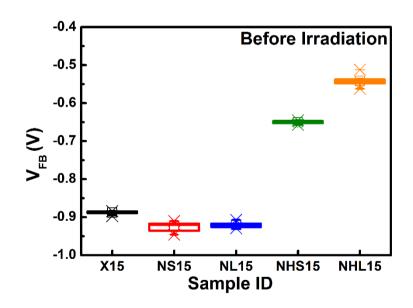

#### 基本雷性 3-1-3

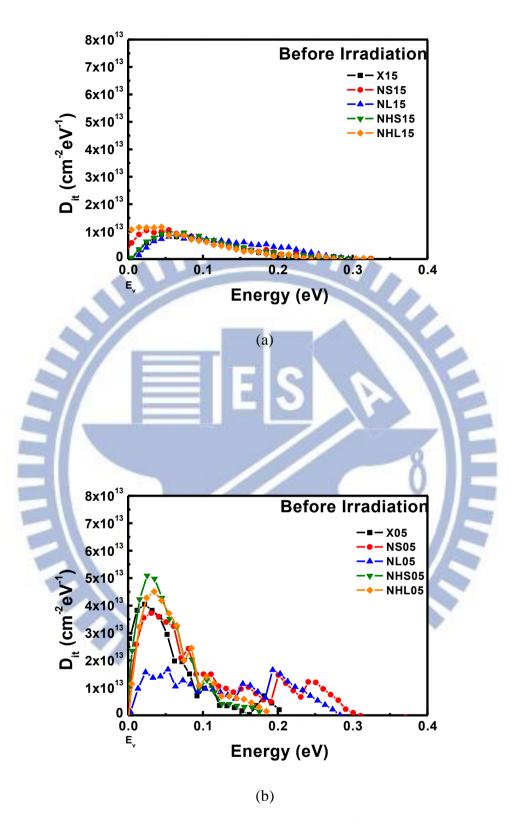

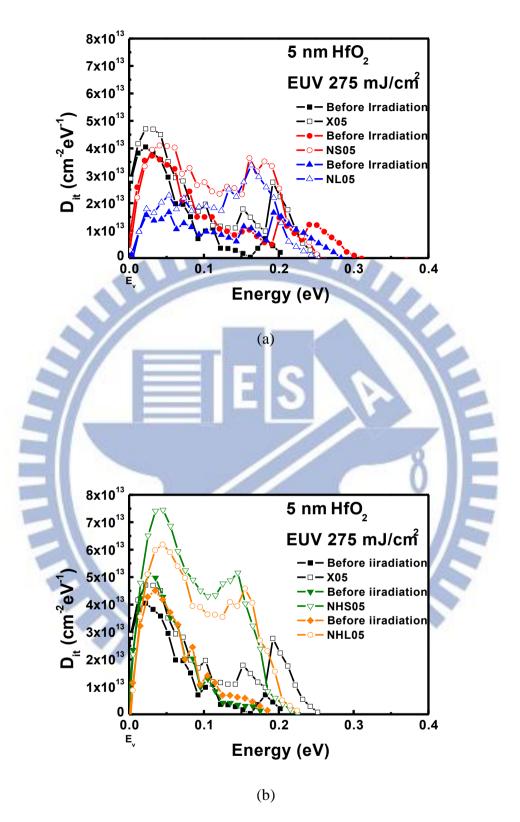

接著利用電容-電壓特性分析不同電漿處理方式的影響,如圖 3-3 所示,從圖 (a)可看到 X15 試片照射前電容-電壓曲線,而圖(b)和(c)為所有條件試片之平帶電 壓與遲滯雷壓雷性比較。此外,閘極氧化層為 5 nm 試片之雷容-電壓特性如圖 3-4 所示,圖(a)同樣為照射前電容-電壓曲線,而圖(b)和(c)為所有條件之平帶電壓與遲 滯電壓電性比較。顏色與數據對照分別為,黑色為對照組,紅色與藍色為氮氣漿 試片短時間與長時間,而綠色與橘色為氨氣電漿試片短時間與長時間。從照射後 同條件十個元件中平帶電壓變化量最大,做為此條件之數據,如此可知閘極氧化 層 15 nm 試片之平帶電壓(VFB)依照 X、NS、NL、NHS 和 NHL 條件順序分別為-0.884、 -0.917、-0.929、-0.654和-0.55(V),而閘極氧化層 5 nm 試片則為-0.315、-0.397、 -0.426、-0.162 和-0.164 (V)。遲滯電壓(V<sub>Hysteresis</sub>)15 nm 元件分別為 0.308、0.317、 0.356、0.536 和 0.454 (V), 而 5 nm 元件部分為 0.026、0.04、0.051、0.021 和 0.025 (V)。介面能態密度(D<sub>it</sub>)對能量分部圖,如圖 3-5 為所有條件照射前分部圖,而圖(a) 和(b)分別為閘極氧化層 15 nm 和 5 nm 之試片,顏色與試片對照分別為,黑色為對 照組,紅色與藍色為氮氣漿試片短時間與長時間,而綠色與橘色為氨氣電漿試片 短時間與長時間,各項實驗數據詳細列於表 3-2 與表 3-3。

首先分析各條件平帶電壓變化,從圖 3-3 (b)可看到 NS15 和 NL15 之平帶電壓相較於 X15 試片皆為負增加試片,代表著進行氮氣電漿處理,氧化層中的 Si-N 鍵結導致正電荷增加,因此電容-電壓曲線是往負向位移。反之 NHS15 和 NHL15 之平帶電壓皆為正增加(相較於 X15 試片),有可能為氨氣電漿處理增加介面 Si-H 鍵結,減少介面正電荷,因此從電容-電壓曲線是往正向位移。隨著時間增加會使得正電荷增加,導致平帶電壓於電漿時間較長之試片有負增加,且 5 nm 試片有相同的結果。

然後再從遲滯電壓部分分析,目前已知遲滯電壓主要肇因於邊界缺陷,HfO<sub>2</sub>/SiO<sub>2</sub>/Si 結構的邊界缺陷主要是在 HfO<sub>2</sub> 內,靠近 SiO<sub>2</sub> 的介面 [60],因此邊界缺陷和介面層處理方式理當無關。但是遲滯電壓可看到經過電漿處理的試片皆變差,尤其 NHL15 試片最為嚴重。推測造成原因為經由電漿處理 HfO<sub>2</sub> 矽基板之介面層後,在介面層表面產生氫或氮的鍵結,雖然可以消除多餘的懸鍵,但有可能因氫離子並未全部產生鍵結,或是氮原子增加介面應力產生缺陷。介面層表面的 Si-N以及 Si-H 鍵結可能影響起始的 HfO<sub>2</sub> 沈積,使得 HfO<sub>2</sub>/SiO<sub>2</sub> 介面缺陷(邊界缺陷)增加。最後量測時給予的偏壓,可能使得部分鍵結的氫離子受電場驅動飄移,因此遲滯現象變嚴重。而 5 nm HfO<sub>2</sub> 試片部分,則是因為介面電荷的影響會隨著氧化層厚度減薄而降低,所以遲滯現象皆不明顯。

接著由介面能態密度對能量分佈圖來看,如圖 3-5 (a)和(b)為閘極氧化層 15 nm 和 5 nm 試片的介面能態密度圖,線和符號分別代表的條件是,黑色方形代表對照組,紅色圓形與藍色三角形為氮氣漿試片短時間與長時間,而綠色倒三角形與橘色稜形為氨氣電漿試片短時間與長時間,從圖中可得知 15 nm 試片照射前經由電漿處理後,並不會特別使得介面能態有增加或減少的趨勢,而氨氣電漿試片雖然有較多 Si-H 鍵結,但是與其他條件相比並無較低之 Dit,推測由於對照組與氮氣電漿試片,在沈積 HfO2 時同樣含氫原子,因此由氧化層中的氫原子與邊緣缺陷鍵結,

所以全部試片的 Dir 都很接近,而 5 nm 試片亦然,試片僅長時間氦氣電漿處理後, 靠近價電帶邊緣能態數量減少。

最後根據以上電性數據,雖然元素分析並未發現明顯的氮元素濃度改變,但 是介面層經過不同電漿和時間處理,確實造成電容元件電性特性改變。

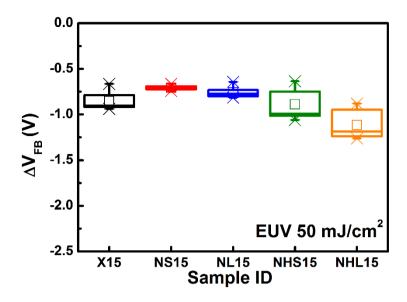

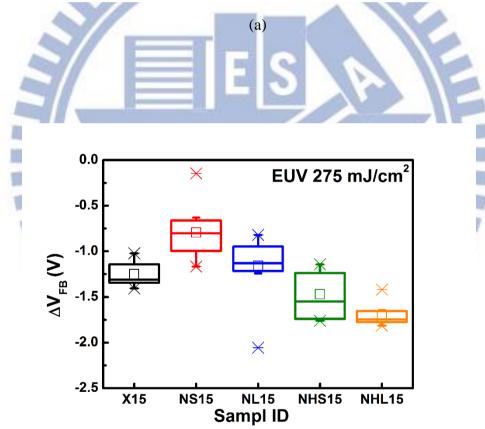

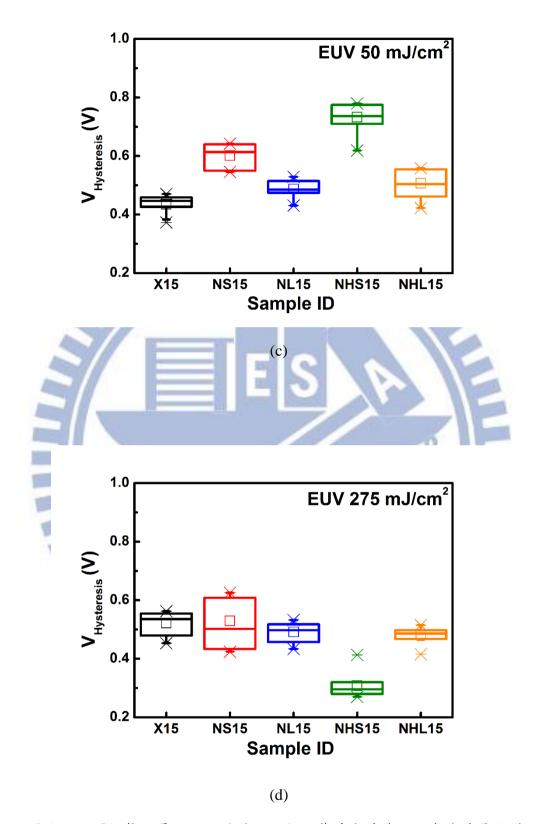

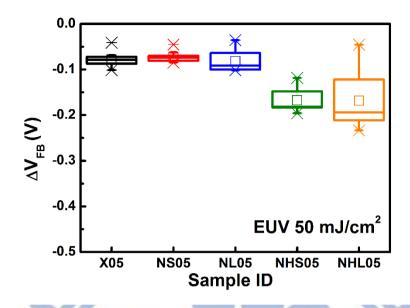

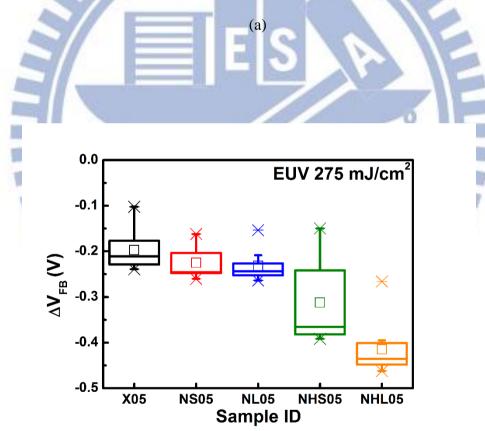

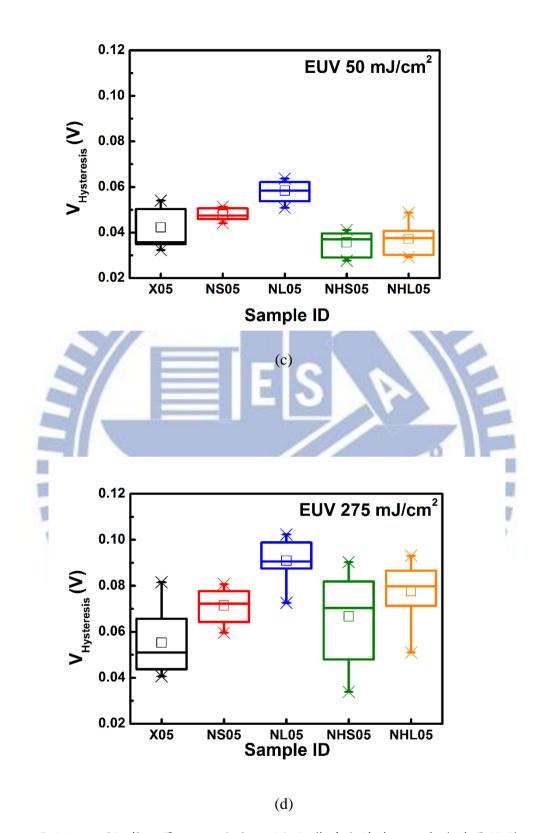

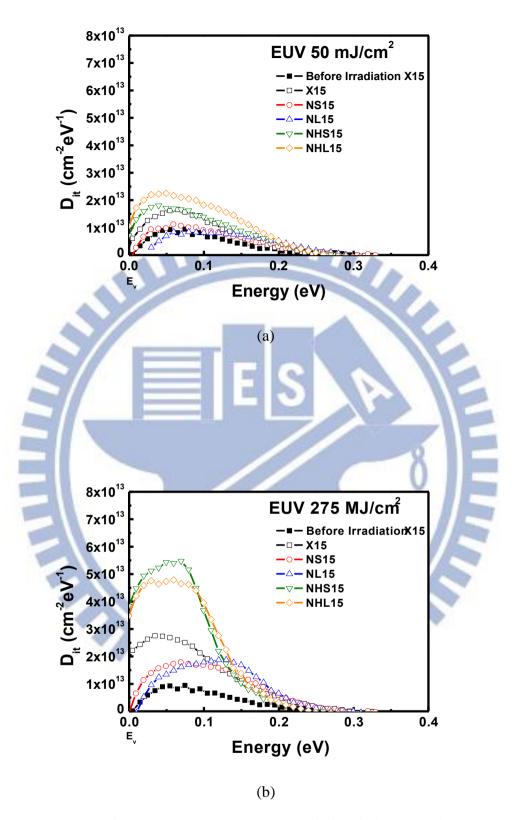

# 3-2 金氧半電容之抗輻射能力

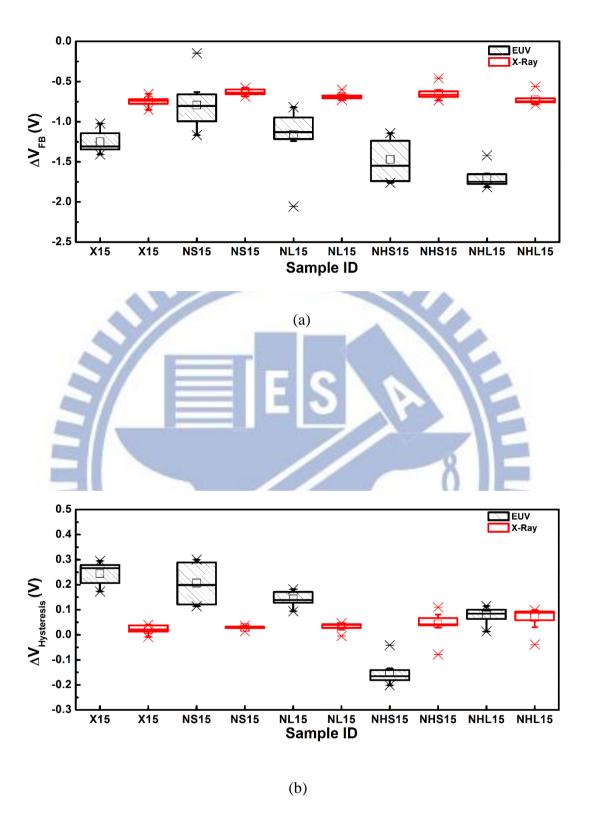

於上一節中我們已了解元件基本電性,接著進行極紫外光照射實驗,如圖 3-6 為閘極氧化層 15 nm 試片照射極紫外光前後的電性變化,照射劑量共使用 50 和 275 mJ/cm<sup>2</sup> 兩種,如圖(a)和(b)為低劑量與高劑量,所有條件平帶電壓變化,而圖(c)和 (d)為遲滯電壓所有條件變化。閘極氧化層 5 nm 試片則如圖 3-7 所示,低劑量與高 劑量之平帶電壓變化如圖(a)和(b)所示,而圖(c)和(d)為遲滯雷壓變化。顏色與數據 對照分別是,黑色為對照組,紅色與藍色為氮氣漿試片短時間與長時間,而綠色 與橘色為氨氣電漿試片短時間與長時間。此外介面能態密度變化對能量分佈圖, 閘極氧化層 15 nm 試片分佈圖如圖 3-8 所示,而圖(a)和(b)不同照射劑量,分別為 50 和 275 mJ/cm<sup>2</sup>,線和符號分別代表的條件是,實心代表為照射前,空心代表為 照射後,黑色方形為對照組,紅色圓形與藍色三角形為氮氣漿試片短時間與長時 間,而綠色倒三角形與橘色稜形為氨氣雷漿試片短時間與長時間。另外閘極氧化 層 5 nm 試片則如圖 3-9 所示,於此照射劑量為 275 mJ/cm<sup>2</sup>,而 5 nm 試片 Dit 圖線 和符號分別代表的條件與 15 nm 不同,圖(a)為試片條件 X05 (黑色/方形)、NS05(紅 色/圓形)與 NL05(藍色/三角形), 而圖(b)試片條件 X05(黑色/方形)、NHS05(綠色/ 倒三角形)與 NHL05(橘色/稜形),實心代表為照射前,空心代表為照射後,低劑量 試片的介面能態照射後實驗數據於照射前幾乎無變化。最後 15 nm 與 5 nm 氧化層

試片照射前和照射後各項數據分別列於表 3-3 (a)與(b)中。

首先從輻射造成之現象探討,由圖 3-6 (a)和(b)可以看到平帶電壓照射極紫外 光後皆向負方向位移。如同前人所作之結論 [44-46],造成原因為極紫外光此波段 較易被物質吸收,所以當氧化層接受輻射照射時,經由吸收輻射能量進而激發出 雷子-電洞對。這些雷子-電洞對於量測時,受到正偏壓影響,多數雷子會在微微秒 (ps)內往閘極移動,少數會跟電洞重組,而剩餘電洞則會受到電場關係往矽基板飄 移,一部份往基板之鉛氧化層飄移途中被捕捉,當電荷在往介面途中,或許會導 致部分能帶變形,這些區域能帶變形可能增加缺陷深度,導致電荷無法立即逃逸, 進而形成被氧化層捕捉正電荷,從電容-電壓曲線可觀察到之現象為曲線會往負方 向平行位移。然而除了氧化缺陷外,游離輻射同樣會產生介面缺陷,這是由於電 荷或氫離子在介面處被缺陷捕獲無法逃逸,因而形成被介面缺陷捕捉電荷,此現 象也會造成電容-電壓曲線變形,若是位於氧化層邊界處被陷住,則會形成邊界電 荷,使得遲滯現象增加。因為介面缺陷位於介電層與矽之交界處,以至於當閘極 電壓在變化過程中,表面電位改變時,介面缺陷會捕捉或是發射電子,導致帶電 量改變。類施體介面缺陷位於能帶下半部分,當費米能階彎曲低於介面位置,使 之空乏則會釋放出電子,形成帶正電荷,填滿為電中性,而類受體則位於能帶之 上半部,當費米能階彎曲高於介面位置,則被填滿接收電子,形成帶負電荷,空 乏為電中性。從本實驗之電容-電壓曲線變形均發生於上半部,可知極紫外光所造 成介面缺陷種類為類施體介面缺陷增加量較多。雖然先前之研究知道閘極氧化層 5 nm 試片之抗輻射能力較好,但期望了解對本研究之試片會有何影響,因此閘極氧 化層 15 nm 試片仍然為實驗條件之一,以其了解這三種缺陷變化情形。

由閘極氧化層 15 nm 試片實驗結果討論開始,從電容-電壓曲線變化詳細數據遲滯電壓、平帶電壓變化,如圖 3-6(a)~(d)所示,介面能態密度對能量分佈如圖 3-8 可知。以平帶電壓的變化而言,所有條件中氮氣電漿處理試片表現最為優異,接著是對照組試片,變化最大為氨氣電漿試片,推測是由於氮氣電漿處理將矽懸鍵

或是較弱的 Si-O 鍵結(4.5 eV)和 Si-H 鍵結替換成較強的 Si-N 鍵結(4.6 eV),以達到補強鍵結較鬆散化學氧化矽(Chemical oxide)的結果,使得平帶電壓變化較少,而氫氣電漿部分,則是因為產生較多的 Si-H 鍵結,經過輻射照射時易被打斷鍵結,因此有較多斷鍵得以捕捉電荷,使得平帶電壓變化量較多。

而遲滯電壓變化部分,如圖 3-6 (c)於低輻射劑量照射時,低秒數的電漿處理試片遲滯電壓較高,而長時間氨氣電漿試片較低,但是當輻射劑量增加時,如圖 3-6 (d)可以看到NHL、NL、NS試片和對照組分佈範圍尚且重疊,且大約都為 0.5 V,推測為在元件中可產生的邊緣缺陷數量有限,因此輻射劑量超過元件可承受劑量,最後遲滯電壓會約為一個固定值,而長短時間氨氣電漿試片遲滯電壓皆較其它條件低,目前還未有明確推測,仍需要更多元件測試。

再從圖 3-8 的介面能態密度對能量分佈來看, 氨氣電漿試片無論秒數長短都有大幅度變形, 其它條件則較不嚴重, 可從此判斷氨氣電漿試片有大量的類施體或類受體介面缺陷產生, 且從圖 3-7 得知靠近價帶的介面缺陷有大幅度的增加, 而NS、NL與 X 條件相比, 發現到經由氮氣電漿處理後的介面能態增加量,較未經電漿處理的試片少,推測原因是 Si-N 鍵結較 Si-O 鍵結強,較不易經由輻射照射後產生斷鍵。而氨氣電漿試片的介面缺陷卻是大量增加,推測原因為介面處理所採用的電漿含有氫離子, 介面氫原子鍵結相較於其它試片大量增加。極紫外光照射很容易造成 Si-H 斷鍵, 因而於介面層附近形成介面缺陷, 因此當氫含量較高的情況下,所產生的介面缺陷機率理所當然比較高。並且當輻射照射劑量提升至 275 mJ/cm²時,由於會產生更多的電子-電洞對於介面處被陷住,或者是氫鍵被打斷機率增加,所以在任何試片介面能態密度也會隨之增加。

當氧化層厚度下降為 5 nm,各項電性受輻射影響程度也大幅下降,如圖 3-7 (a)~(d)平帶電壓和遲滯電壓變化,而介面能態密度對能量變化則如圖 3-9 所示。輻射損傷下降原因為氧化層厚度下降,使得輻射穿透率增加,因此獲得能量機率也

會有所不同,15 nm HfO2的吸收率為37.61%,而5 nm HfO2的吸收率為14.55%, 能增加之被捕捉正電荷也有所限制。且因厚度降低後,被捕捉的正電荷可藉由基 板導帶之電子,穿隧過介面層至氧化層與其複合,消除掉被捕捉正電荷機率大幅 增加,所以平帶電壓位移也較少。而遲滯電壓未與15 nm 結果相同,從電容-電壓 曲線可看於照射前遲滯電壓就很小,照射後幾乎沒有改變。接著討論介面能態密 度變化情形,5 nm HfO2的試片照射50 mJ/cm²劑量之極紫外光,照射前後的介面 能態密度無太大變化。而275 mJ/cm²劑量產生較明顯的變化,可知對於閘極氧化 層5 nm HfO2之元件,當照射劑量增加同樣會產生較多介面能態。然而經由上述實 驗數據分析後,三種介面處理方式的優劣性,依然是氮氣電漿處理試片表現最好, 而氨氣電漿處理試片最差。

在此節中所介紹之介面處理方式,經由極紫外光照射後對於試片造成輻射損傷程度不同。由上述實驗結果得知氮氣電漿處理試片的抗輻射能力最好,平帶電壓與介面缺陷增加量最少,目前推論原因為 Si-N 鍵結,因而使得抗輻射能力增加,而遲滯電壓變化部分,由於不同輻射劑量分佈區間差異性太大,且於高劑量部分分佈區間過於接近,因此仍無法下定論。而氨氣電漿試片部分,平帶電壓和介面缺陷增加量最多,推測造成原因為 Si-H 鍵結較弱,再經由高能量輻射照射後,較容易造成斷鍵所致,因此氨氣電漿試片的抗輻射能力最差。至於未經電漿處理試片表現,相較其它電漿處理試片而言表現平庸。

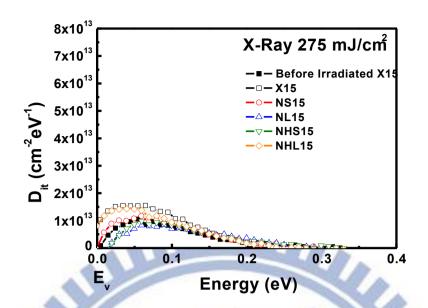

### 3-2-2 不同能量對於抗輻射能力影響

本節將討論不同輻射能量對於元件之抗輻射能力的影響,本論文使用的光源 為極紫外光與能量為10 keV之 X-光兩種輻射光源,皆由國家同步輻射中心所提供, 分別使用 08A1 與 07A1 光束線。照射元件部分只採用閘極氧化層 15 nm 試片,未 採用 5 nm 試片,原因為前人研究發現,閘極氧化層 5 nm 試片經由 X-光照射後, 元件抗輻射能力非常優異,並無明顯衰退,並且由於 X-光造成輻射損傷較小,在 5 nm 試片幾乎無變化,因而不利於比較不同能量光源造成輻射損傷研究。因此於 本論文使用 X15、NS15、NL15、NHS15 和 NHL15 五種條件之試片,而劑量方面 選擇 275 mJ/cm<sup>2</sup>。

如圖 3-10 (a)和(b)為照射極紫外光(黑色/斜線)與 X-光(紅色)後平帶電壓和遲滯電壓變化比較圖,而介面能態密度對能量分佈如圖 3-11 所示,線和符號分別代表的條件是,實心代表為照射前,空心代表為照射後,黑色方形為對照組,紅色圓形與藍色三角形為氦氣漿試片短時間與長時間,而綠色倒三角形與橘色稜形為氦氣電漿試片短時間與長時間。經由 X-光照射後,電容-電壓曲線位移與變形相較於極紫外光試片而言輕微許多,從圖 3-10 與圖 3-11 可到均較極紫外光變化少。首先看到平帶電壓變化,X-光較極紫外光受輻射影響輕微,且所有電漿試片與 X15 變化量分佈範圍差異不大。而遲滯電壓部分,X-光試片所有條件同樣未有明顯區別,氦氣電漿試片略高於其它條件,不同於 15 nm 試片的結果,但是分佈範圍仍非常接近,需要更多樣品數才能斷定。最後介面能態密度部分,從圖 3-11 可看到 NS和 NL 試片幾乎與照射 X-光前相同,而其它條件與極紫外光試片相比之下,受輻射影響非常輕微,甚至較極紫外光 50 mJ/cm² 試片少。

根據上述實驗結果極紫外光對於元件特性影響較嚴重,前人猜測原因為極紫外光雖然同屬於軟 X-光,但是兩種光源的能量相差很大,X-光能量大於極紫外光約 110 倍左右,因此衰退長度不同,以 15 nm  $HfO_2$  為例,極紫外光衰退長度為  $3.18 \times 10^{-2}$   $\mu m$ ,而 X-光為 5.17  $\mu m$ ,換算為吸收機率分別為 62.38 %和 0.29 %,極紫外光為 X-光的 110 倍,由此可知極紫外光產生被捕捉正電荷和介面缺陷變化量遠大於 X-光皆可預測,因而元件電性會嚴重衰退 [46]。

當元件所使用的閘極氧化層厚度從 15 nm 下降為 5 nm 時,所受到輻射損傷會隨著厚度降低,受影響程度也會下降,同樣從穿透機率公式可得知,所以 X-光的輻射損傷幾乎是可忽略。

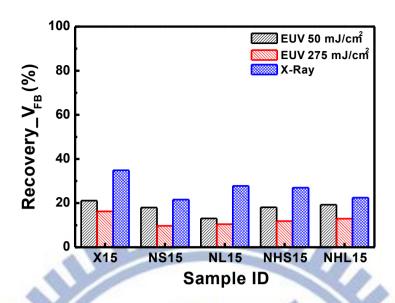

### 3-2-3 静置於室溫電性恢復情形

當照射輻射後,靜置於室溫中元件皆會有自我修復(Self-annealing)的情形發生, 像是氧化缺陷、介面缺陷和氧化層邊界缺陷將會部分恢復。因此,此節將會探討 本論文所製作之元件,照射輻射後電性大幅變化,放置於室溫自我修復 50 天後, 觀察電性恢復情形。

首先觀察極紫外光源輻射損傷修復情形,使用的元件為開極氧化層 15 nm HfO2,電性變化如圖 3-12 為照射極紫外光與 X-光放置 50 天後,平帶電壓恢復百分比比較圖,黑色(右斜線)和紅色(左斜線)分別為照射極紫外光劑量 50 和 275 mJ/cm²,藍色(稜格紋)為照射 X-光劑量 275 mJ/cm²。而圖 3-13 則為介面能態密度對能量分佈比較圖,X15(黑色/方形)、NHS15(綠色/倒三角形)與 NHL15(橘色/稜形),實心代表為照射前,空心代表為照射後。可看到試片經過放置室溫 50 天後皆有自我修復現象發生,可以看到平帶電壓為正增加,這意味著輻射引起被捕捉氧化正電荷(Radiation-induced trap charge)有部分隨著時間拉長而消除,可能原因為電子從矽基板穿隧至氧化層中,與氧化層中被捕捉電洞複合,或者是熱發射(Thermal emission)電子從氧化層的價電帶躍昇與被捕捉電洞複合。從平帶電壓恢復百分比來看大約 10~30 %,照射後變化量最多的極紫外光 275 mJ/cm²為恢復比例最低的試片,由於在不同處理條件中可消除的電洞為固定量,因此 X-光試片皆為恢復比分比較高的試片。且從圖 3-13 看照射後介面缺陷有大量增加之試片,靜置室溫後同

樣有較明顯減少,如對照組及氨氣電漿試片在靠近價電帶(Ev)之介面能態有較明顯減少,但是氦氣電漿試片放置50天後卻幾乎未有改變。

而當閘極氧化層 5 nm 試片,同於 15 nm 試片平帶電壓有些許正增加,而劑量為 50 mJ/cm²的試片,由於照射後變化量已經非常些微,因此放 50 天後幾乎未有恢復,但 275 mJ/cm²試片,恢復情形則較明顯可以觀察到,但是相對於 15 nm 試片同樣未有明顯變化。介面能態變化部分同 15 nm 試片,X05、NHS05 和 NHL05 試片有明顯修復,其它條件未有太大差異。

在 X-光部分,同電容-電壓曲線並未恢復至與照射前一致,被捕捉正電荷只能部分消除或與電子再結合,恢復量與極外光試片相比皆較少, D<sub>it</sub>幾乎未有改變。

如此可證明將試片放置於室溫中,元件所受的輻射損傷確實可以有部分回復,但無法完全恢復至照射前電性,仍需經過高溫退火才能恢復電性。而 5 nm 試片幾乎是未恢復,推測由於氧化層厚度較薄的關係,一開始被捕捉正電荷已經不多,再經由施予偏壓影響部分被捕捉電洞與電子再結合,且因為氧化層厚度只有 5 nm 更易逃逸,剩餘被捕捉正電荷在靜置室溫可被消除量則更少,而且在 15 nm 氧化層試片皆未有顯著恢復,因此 5 nm 試片於 50 mJ/cm² 幾乎沒有恢復是可以預期。

表 3-1 電容元件實驗變數所對應之代號。

| Sample ID | HfO <sub>2</sub> Thickness | Plasma          | Time    |

|-----------|----------------------------|-----------------|---------|

| X15       |                            | X               | X       |

| NS15      |                            | $N_2$           | 30 sec  |

| NL15      | 15 nm                      | $N_2$           | 120 sec |

| NHS15     |                            | $NH_3$          | 30 sec  |

| NHL15     |                            | $NH_3$          | 120 sec |

| X05       |                            | X               | X       |

| NS05      | A LULE                     | $N_2$           | 30 sec  |

| NL05      | 5 nm                       | $N_2$           | 120 sec |

| NHS05     |                            | NH <sub>3</sub> | 30 sec  |

| NHL05     |                            | NH <sub>3</sub> | 120 sec |

表 3-2 元件照射輻射前之電性,(a)為閘極氧化層 15 nm 試片,(b)為閘極氧化層 5 nm 試片。

| Sample ID                              | X15    | NS15   | NL15   | NHS15  | NHL15 |

|----------------------------------------|--------|--------|--------|--------|-------|

| HfO <sub>2</sub> thickness (nm)        | 13.2   | 14.04  | 14.13  | 13.7   | 13.09 |

| Interfacial layer thickness (nm)       | 0.6    | 0.64   | 0.7    | 0.85   | 0.6   |

| EOT (nm)                               | 3.33   | 3.38   | 3.6    | 3.41   | 3.56  |

| Flatband voltage (V <sub>FB</sub> )(V) | -0.884 | -0.917 | -0.929 | -0.645 | -0.55 |

| V <sub>Hysteresis</sub> (V)            | 0.308  | 0.317  | 0.356  | 0.536  | 0.454 |

(a)

| Sample ID                        | X05    | NS05   | NL05   | NHS05  | NHL05  |

|----------------------------------|--------|--------|--------|--------|--------|

| HfO <sub>2</sub> thickness       | 4.49   | 4.65   | 16     | 4.57   |        |

| Interfacial layer thickness (nm) | 0.5    | 0.85   |        | 0.8    |        |

| EOT (nm)                         | 1.57   | 1.63   | 1.85   | 1.64   | 1.72   |

| Flatband voltage $(V_{FB})(V)$   | -0.315 | -0.397 | -0.426 | -0.162 | -0.164 |

| V <sub>Hysteresis</sub> (V)      | 0.026  | 0.04   | 0.051  | 0.021  | 0.025  |

表 3-3 照射極紫外光之前後平帶電壓和遲滯電壓差異,(a)為閘極氧化層 15 nm 試片,(b)為閘極氧化層 5 nm 試片。

| Sample ID                    |                        | X15    | NS15   | NL15   | NHS15  | NHL15  |

|------------------------------|------------------------|--------|--------|--------|--------|--------|

| $\Delta V_{FB}(V)$           | 50 mJ/cm <sup>2</sup>  | -0.938 | -0.734 | -0.803 | -1.06  | -1.262 |

|                              | $275 \text{ mJ/cm}^2$  | -1.407 | -1.167 | -1.242 | -1.762 | -1.815 |

|                              | 50 mJ/cm <sup>2</sup>  | 0.103  | 0.258  | 0.091  | 0.153  | 0.027  |

| ΔV <sub>Hysteresis</sub> (V) | 275 mJ/cm <sup>2</sup> | 0.181  | 0.199  | 0.094  | -0.042 | 0.013  |

(a)

## ES

| Sample ID                    |                        | X05    | NS05   | NL05   | NHS05  | NHL05  |

|------------------------------|------------------------|--------|--------|--------|--------|--------|

| $\Delta V_{FB}(V)$           | 50 mJ/cm <sup>2</sup>  | -0.101 | -0.085 | -0.102 | -0.196 | -0.233 |

|                              | 275 mJ/cm <sup>2</sup> | -0.239 | -0.26  | -0.264 | -0.392 | -0.462 |

| AV (V)                       | 50 mJ/cm <sup>2</sup>  | 0.014  | 0.012  | 0.011  | 0.02   | 0.024  |

| ΔV <sub>Hysteresis</sub> (V) | 275 mJ/cm <sup>2</sup> | 0.045  | 0.038  | 0.043  | 0.052  | 0.057  |

(b)

| Sample ID                                       |      | X15    | NS15   | NL15   | NHS15  | NHL15  |

|-------------------------------------------------|------|--------|--------|--------|--------|--------|

|                                                 | 極紫外光 | -1.407 | -1.167 | -1.242 | -1.762 | -1.815 |

| $\Delta V_{\mathrm{FB}}\left(\mathrm{V}\right)$ | X-光  | -0.852 | -0.686 | -0.730 | -0.734 | -0.783 |

|                                                 | 極紫外光 | 0.181  | 0.199  | 0.094  | -0.042 | 0.013  |

| ΔV <sub>Hysteresis</sub> (V)                    | X-光  | 0.037  | 0.037  | 0.044  | 0.11   | 0.093  |

(b)

(d)

(f)

(h)

圖 3-2 能量光譜散射儀(EDS)測量氮元素於試片薄膜各層所占百分比,(a) 為閘極氧化層 15 nm 之試片,(b)為閘極氧化層 5 nm 之試片。

## ES

(b)

(c)

## ES

(b)

(c)

圖 3-5 所有條件照射前介面能態密度對能量分布比較圖,(a)為閘極氧化層 15 nm 元件,(b)為閘極氧化層 5 nm 元件。

(b)

圖 3-6 閘極氧化層 15 nm 試片,照射極紫外光前後之所有條件電性變化比較圖,(a)和(b)為平帶電壓變化,輻射劑量分別為 50 和 275 mJ/cm², (c)和(d)為遲滯電壓變化,輻射劑量分別為 50 和 275 mJ/cm²。

(b)

圖 3-7 閘極氧化層 5 nm 試片,照射極紫外光前後之所有條件電性變化比較圖,(a)和(b)為平帶電壓變化,輻射劑量分別為 50 和 275 mJ/cm²,(c)和(d)遲滯電壓變化,輻射劑量分別為 50 和 275 mJ/cm²。

圖 3-8 閘極氧化層 15 nm 試片,照射極紫外光前後所有條件變化比較之介 面能態密度對能量分布圖,(a)為照射劑量 50 mJ/cm²,(b)為照射劑量 275 mJ/cm²。

圖 3-10 閘極氧化層 15 nm 試片,經由極紫外光與 X-光照射後,所有製程條件其電性數據變化比較圖,輻射劑量為 275 mJ/cm²,(a)為平帶電壓,(b)為遲滯電壓。

圖 3-11 閘極氧化層 15 nm 試片,照射 X-光前後介面能態密度對能量分佈比較圖,輻射劑量為 275 mJ/cm<sup>2</sup>。

圖 3-12 閘極氧化層 15 nm 試片,照射極紫外光與 X-光放置 50 天後,其之平 帶電壓恢復百分比較。

圖 3-13 試片編號 X15、NHS15 和 NHL15 之元件,照射極紫外光後與放置 50 天後之介面能態密度對能量變化比較圖,輻射劑量為 275 mJ/cm<sup>2</sup>。

## 第四章

## 游離輻射對金氧半場效電晶體之可靠度影響

#### 4-1 電晶體之基本電性

在此章中,為了解輻射對於元件可靠度之影響,所採用之元件為先進製程電晶體。此元件之剖面結構自最底層至最上層分別為晶圓、0.4 nm 介面層和 2 nm HfO<sub>2</sub>,接著為 1.5 nm TiN 以調整臨界電壓,總閘極金屬厚度為 38 nm,最後是 40 nm 磷玻璃(PSG),元件剖面 TEM 照片如圖 2-2 所示。隔離(Isolation)製程方式是採用淺溝槽隔離(Shallow Trench Isolation, STI)。使用之光源為 08A1 與 07A1,光束線能量分別為 91.85 eV 與 10 keV,光通量分別為 1×10<sup>13</sup> 與 4×10<sup>10</sup>,所照射劑量均為 1000 mJ/cm²。根據各層厚度與公式 2-4 衰退長度公式,計算出極紫外光穿透至閘極氧化層上之機率約 29 %。而後因元件為奈米等級,以致於較難藉由水平儀對準,因此採取之實驗數據為照射後關閉狀況下漏電流變化最大的元件。

數據所用之電晶體閘極寬度/長度條件共有四種,分別為  $10 \, \mu m/0.4 \, \mu m \cdot 2 \, \mu m/2 \, \mu m \cdot 2 \, \mu m/0.35 \, \mu m$  和  $2 \, \mu m/0.12 \, \mu m$  ,所對照代號分別為  $A \cdot B \cdot C$  和 D 。而照射前基本電性,首先臨界電壓(Threshold Voltage,  $V_{th}$ )約為  $0.55 \sim 0.65 \, V$  ,關閉電流 (Off-state leakage current)約為  $10^{-12} \sim 10^{-13} \, A$ ,電流開關比(On/off ratio)約為  $10^6 \sim 10^8$ ,次臨界電壓擺輻(Subthreshold Swing, S.S.)約為  $68 \sim 72 \, mV/decade$ 。

## 4-2 不同能量光源之抗輻射能力分析

由孫銘鴻先生之研究得知,當場效電晶體照射輻射後,經過 400 °C真空退火,可以使受到輻射影響之電性,恢復至照射前的狀態 [46],因此本論文希望可以了

解高溫退火是否有再現性。本節討論經由 400 °C退火修復元件的輻射損傷,使得漏電流恢復至與照射前相同等級後,再次接受輻射照射,觀察元件電性是否會再度變差。

#### 4-2-1 極紫外光

如圖 4-1 為試片經極紫外光照射前(黑色/實線)、照射後(紅色/長虛線)、400 °C 真空退火後(藍色/常虛線與短虛線)、第二次照射後(綠色/短虛線)之  $I_d$ - $V_g$  曲線,而各條件電性數據如表 4-1 所示。首先由  $I_d$ - $V_g$  曲線可看出輻射照射後, $V_t$ h和 S.S. 變化量並不顯著,根據表 4-1 可知  $V_t$ h 變化量最大至 11 mV,而 S.S. 變化量約為 5 ~ 12 %,較明顯變化為漏電流上升幅度約為 100 倍,此現象造成積體電路功率消耗增加,是電路設計必須考慮的問題。

先前於第三章中得知,經輻射照射後,元件中被捕捉正電荷與介面能態捕捉電荷會增加,造成電容-電壓圖有大量的位移與嚴重的變形。而相對於第三章使用的氧化層厚度(5 nm 與 15 nm),雖然用於測試可靠度之元件氧化層只有 2 nm,閘極因穿透機率較高,導致損傷較輕微,但是 STI 氧化層之厚度對於極紫外光穿透機率極低,因此影響較為嚴重,所以推測此為漏電流上升原因之一。由於 STI 氧化層吸收極紫外光中幾乎所有能量,因而產生大量電子-電洞對,於 STI 氧化層中增加許多被捕捉正電荷,引起矽基板近隔絕層表面空乏甚至電子聚集形成反轉層,成為漏電路徑。漏電路徑於 CMOS 電路有兩種可能性,第一種在 N 型電晶體中,成為漏電路徑。漏電路徑於 CMOS 電路有兩種可能性,第一種在 N 型電晶體中,為源極與汲極之邊緣所形成,另一種為 N 型電晶體的源極或汲極與 P 型電晶體的 n-well 形成導通路徑,導致漏電流大幅上升 [45,46],如圖 4-2 (a)CMOS 元件漏電流路徑示意圖。

此外,輻射不僅產生被捕捉正電荷,也會產生介面能態,因此可能成為漏電流上升之原因。當N型電晶體給一負偏壓,使電晶體操作在截止區(Cut-off region),此時介面能態成為漏電流供給源頭,如圖 4-2 (b) N型電晶體之源極與汲極漏電路徑示意圖。於孫銘鴻先生的論文中,為了要知道漏電流是由於氧化層被捕捉電荷還是於介面被捕捉電荷,藉由量測n<sup>+</sup>-p接面於反向操作下,得到此時之 I<sub>d</sub>-V<sub>d</sub> 曲線,電流仍相當微小,這意味著被捕捉正電荷並未產生反轉層,只造成矽表面空乏,是空乏區中的介面缺陷激發電子-電洞對因而漏電流上升 [46]。

當元件以 400 ℃做真空退火後,其電性變化如圖 4-2,Vth 與 S.S.都恢復至接近照射前的電性,且照射後大幅上升之關閉狀態漏電流也下降至約 1×10<sup>-12</sup>,Vth、S.S.與漏電流詳細數據如表 4-2 所示。藉由高溫退火,使得被捕獲之電洞逃脫或與電子復合,正電荷減少,矽表面不再空乏,故漏電流降低。

再次照射後,與第一次照射極紫外光有相似狀況,如圖 4-3 所示,Vth最大增加 13 mV,而 S.S.增加約 6~10%沒有顯著變化,且漏電流同樣有大幅上升之情形。由 Id-Vg 曲線也並未因受輻射照射後,有大幅飄移,表示氧化層缺陷所捕捉之正電荷和第一次照射相較沒有增加。雖然再次接受輻射照射,但未使電性造成更嚴重衰退,表示輻射所造成之損傷皆可藉由 400°C真空退火修復。

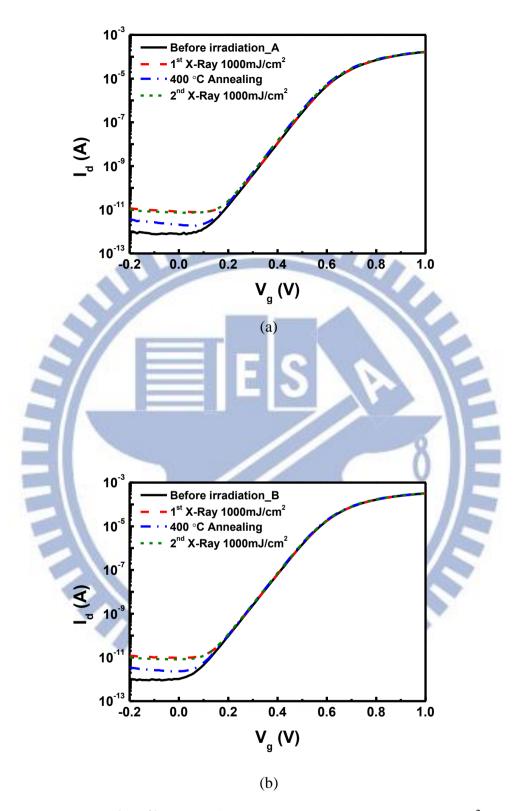

#### 4-2-2 X-光

接著光源改以能量  $10 \text{ keV} \ge X$ -光做為輻射光源,照射劑量同為  $1000 \text{ mJ/cm}^2$ ,如圖 4-4 所示為元件照射 X-光前(黑色/實線)、照射後(紅色/長虛線)、400 °C真空退火後(藍色/常虛線與短虛線)、第二次照射後(綠色/短虛線)之  $I_d$ - $V_g$  曲線,詳細實驗數據整理於表 4-2。從圖 4-4 之  $I_d$ - $V_g$  曲線看到電晶體的  $V_{th}$  和 S.S.幾乎無變化,臨界電壓減少 2 mV 以下,幾乎無變化,而次臨界擺幅衰退幅度小於 1%,唯獨漏電

流同樣有較顯著上升約10倍,但相較於極紫外光照射,影響程度較小。與極紫外光比較之 Vth、S.S.和關閉狀態漏電流實驗數據,如圖4-3所示,黑色(右斜線)與紅色(左斜線)代表為極紫外光試片,藍色(稜格紋)與綠色(橫直線)為X-光試片。

兩種光源差異性於第三章中已說明,其結論為由於極紫外光的吸收率遠大於 X-光,因此造成的輻射損傷也是極紫外光較為嚴重,於此節中,同樣可看到 X-光 受到的輻射傷害較小。

接著以 400 °C做真空退火後,其 Ia-Vg 曲線如圖 4-4 所示。Vth 有些微減少約 2~9 mV 與 S.S.都恢復至照射前電性,而關閉狀態漏電流約恢復至 5×10<sup>-11</sup>,可看到關閉狀態下 Id-Vg 曲線有傾斜,表示閘極邊緣有介面缺陷產生,介面缺陷形成供給源,當閘極電壓越負時,會在 n 型汲極邊緣形成空乏區,且因為汲極濃度較高,所以空乏區寬度會很窄,當空乏區能帶越彎曲超過能隙,此時能帶間會發生穿隧導通,因此介面能態會變成漏電流供給源,使得電子得以穿隧能帶至汲極造成漏電流會增加,因而可以看到閘極引發汲極漏電流(Gate-induced drain leakage, GIDL)。而極紫外光照射之元件無此現象的原因,推測由於兩者能量不同,X-光能量源高於極紫外光,因此造成介面缺陷增加,且經由退火介面缺陷可修復量較低,因此才能在關閉電流觀察到 GIDL 現象。雖然孫明鴻先生的實驗結果為經由高溫退火後,電性皆會恢復至與照射前相同,和本文不同,可能是元件差異所致。

最後再次照射 X-光,同樣漏電流又上升 10 倍, I<sub>d</sub>-V<sub>g</sub> 曲線如圖 4-4 所示,而 V<sub>th</sub>在退火後略增加 2~6 mV,但與照射前數據相比卻些微減少約 2~7 mV。相對來說,S.S.無論什麼條件下,變化幅度皆小於 1%。結論為在同一劑量下,氧化層缺陷與介面缺陷會增加固定量,並不易因受過兩次照射後,導致元件抗輻射能力下降。

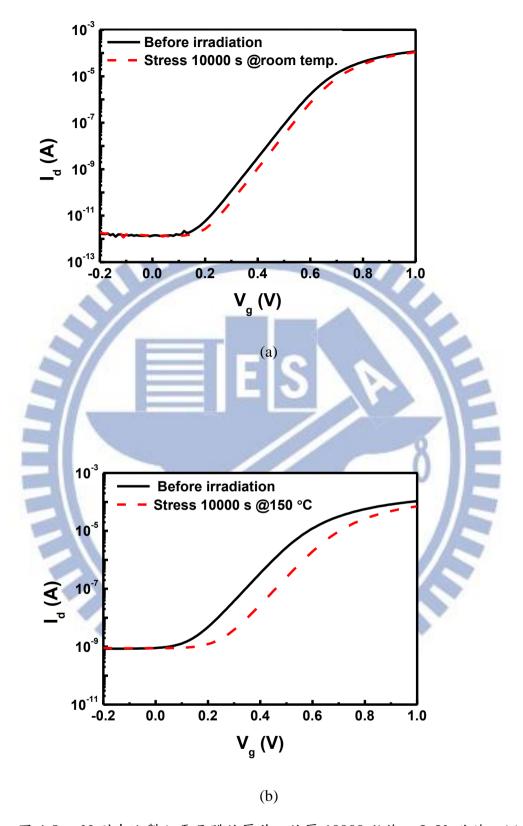

#### 4-3 照射極紫外光後之可靠度

在此節討論 N 型電晶體的可靠度,我們利用臨界電壓對正偏壓溫度的不穩定性(PBTI)測量,詳細內容已於 2-3-2 節中介紹,BTI 分別有給予正偏壓和負偏壓兩種,於先進製程元件中,閘極氧化層使用高介電常數的材料取代 SiO<sub>2</sub>,對於高介電常數材料而言,PBTI 衰退比 NBTI 嚴重許多,因此本論文採用 PBTI。

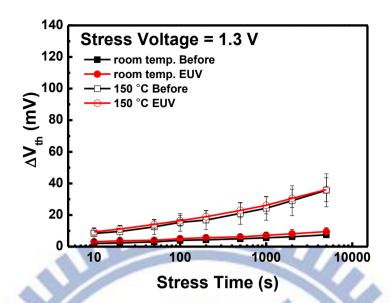

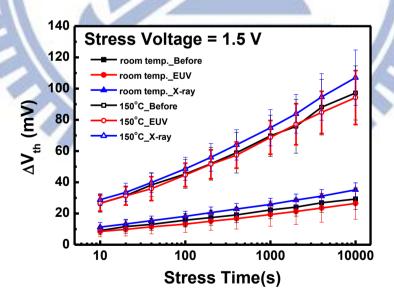

於蘇婷婷小姐 [45]和孫銘鴻先生 [46]的論文中已有部分研究資料,蘇小姐的實驗條件為試片照射極紫外光,劑量 2000 mJ/cm², PBTI 測量條件為 Vg 給予 1.5 V,電場大約為 10 MV/cm,施予 10000 秒。而孫先生使用光源為極紫外光和 X-光,劑量調降為 1000 mJ/cm², 測量條件同蘇小姐所使用。經由兩位研究得知,施壓 10000 秒後 Id-Vg 曲線會平行向右位移, S.S.未有明顯之改變, 如圖 4-5 所示, 黑色照光前,紅色虛線為施壓 10000 秒後,造成主因推測為氧化層被捕捉電荷增加,但由於 PBTI 影響遠大於輻射導致 Vu 增加,因此單就結論而言,游離輻射不會對先進製程的電晶體的 PBTI 可靠度有直接影響。而本論文希望降低閘極電壓,了解實際輻射對於先進製程電晶體之可靠度影響,使用極紫外做為輻射光源,照射劑量為 1000 mJ/cm²,量測偏壓為 1.3 V,施壓時間為 5000 秒。時間減少原因為在大電場下於 3000 秒內電洞就已經逸散或者與電子再結合,所以本論文減少量測時間,期望可以減少放置室溫自我修復情形。

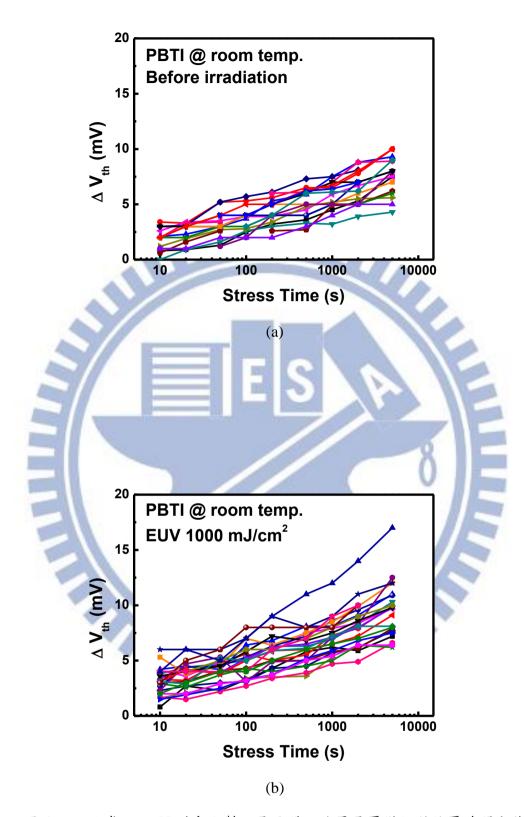

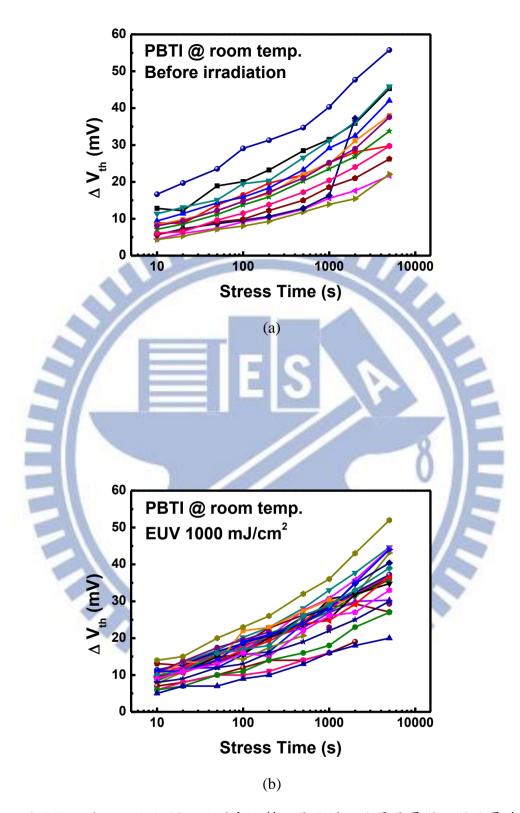

如圖 4-6 為在室溫下,測量 PBTI 所得之結果臨界電壓變化對偏壓時間關係,(a)和(b)分別為沒有照射輻射和照射極紫外光 1000 mJ/cm² 的結果。而圖 4-7 則為升溫至 150 °C測量 PBTI 結果,同樣圖(a)和(b)分為沒有照射輻射和照射極紫外光 1000 mJ/cm² 的結果。圖 4-7 為 PBTI 測量臨界電壓各條件分佈結果與偏壓時間關係,圖中所標示之點為平均值,而上下線範圍為一倍標準差。不同溫度與有無照射極紫外光之比較。經過 5000 秒的偏壓,無照射輻射元件於室溫下臨界電壓上升約 7.5 mV,150 °C下則是約 35 mV。受紫外光照射後,室溫條件上升約 10 mV,150 °C條件則

是約36 mV。從圖4-8 觀察兩者臨界電壓變化範圍,實心代表為常溫狀態下,空心為升溫情況下,黑色(方形)為未照射輻射,紅色(圓形)為照射極紫外光。可發現兩者分佈範圍大部分重疊,表示為電晶體之間的誤差,因此無法就變化量推論結果。以變化趨勢之斜率,照射前與照射後兩條曲線斜率成平行分佈,表示兩者衰退速率相同。本論文已降低電場,希望可以減少偏壓的影響,最後結論為當先進製程電晶體接受極紫外光照,其可靠度抗輻射能力非常好,輻射不是導致可靠度下降之主因。

與前人之研究做比較,務銘鴻先生使用偏壓條件為 1.5 V,而於本研究則是 1.3 V,當電場較強時,通過開極氧化物電流也會增加,缺陷增加量增加,被捕捉正電荷機率也會上升,導致臨界電壓變化。因此從實際測量來看,如圖 4-9 為孫銘鴻先生所做 PBTI 測試結果趨勢圖,實心代表為常溫狀態下,空心為升溫情況下,黑色 (方形)為未照射輻射,紅色(圓形)為照射極紫外光,藍色(三角形)為照射 X-光。他所使用之測試條件變化趨勢 150 °C施壓 5000 秒後,臨界電壓變化約為 50 mV,於本研究中約為 27 mV,而在室溫分別是 10 mV 與 5 mV,兩種溫度下,1.5 V 和 1.3 V 的造成臨界電壓變化大約差 2 倍左右,可以知道電場對於 PBTI 的影響是非常巨大。因此在 PBTI 測試中,因為電場對於測量影響大於輻射影響,輻射對於可靠度的影響並不明顯。

表 4-1 以 91.85 eV 之極紫外光為光源,劑量為 1000 mJ/cm²,極紫外光照射前、 照射後、400°C做真空退火與第二次照射極紫外光之 Vth 與 S.S.。

|                            | 極紫外光 1000 mJ/cm <sup>2</sup> |       |                |      |  |

|----------------------------|------------------------------|-------|----------------|------|--|

|                            | A                            | В     | A              | В    |  |

|                            | $V_{th}\left(V\right)$       |       | S.S. (mV/dec.) |      |  |

| Before irradiation         | 0.625                        | 0.615 | 69.4           | 69.4 |  |

| 1 <sup>st</sup> irradiated | 0.631                        | 0.626 | 74.4           | 74.4 |  |

| 400 °C Anneal              | 0.617                        | 0.608 | 69.4           | 69.4 |  |

| 2 <sup>nd</sup> irradiated | 0.625                        | 0.621 | 73.3           | 73.3 |  |

表 4-2 以 10 keV 之 X-光為光源,劑量為 1000 mJ/cm<sup>2</sup>, X-光照射前、照射後、 400 °C做真空退火與第二次照射 X-光之 V<sub>th</sub>與 S.S.。

|                            | X-光 1000 mJ/cm <sup>2</sup> |       |                |      |  |  |

|----------------------------|-----------------------------|-------|----------------|------|--|--|

|                            | A                           | В     | A              | В    |  |  |

|                            | $V_{th}(V)$                 |       | S.S. (mV/dec.) |      |  |  |

| Before irradiation         | 0.575                       | 0.559 | 69.6           | 70.5 |  |  |

| 1st irradiated             | 0.575                       | 0.558 | 69.7           | 70.8 |  |  |

| 400 °C Anneal              | 0.566                       | 0.556 | 69.2           | 70.3 |  |  |

| 2 <sup>nd</sup> irradiated | 0.568                       | 0.556 | 69.8           | 70.9 |  |  |

圖 4-1 N 型先進製程電晶體經由 91.85 eV 之極紫外光照射  $1000~mJ/cm^2$ ,極紫外光照射前、照射後、400~C做真空退火與第二次照射極紫外光之  $I_d$ - $V_g$  曲線,(a)試片 A 與(b)試片 B。

圖 4-2 兩種可能形成漏電路徑示意圖,(a)淺溝槽隔絕技術,(b)經由輻射後, 導致關閉狀態漏電流增加之機制。

# (a)

(b)

圖 4-3 N型先進製程電晶體經由極紫外光與 X-光照射 1000 mJ/cm²後,照射前、照射後、400 °C做真空退火與第二次照射之電性變化曲線,(a)Vth,(b)S.S.,(c)關閉狀態漏電流。

#

圖 4-4 N型先進製程電晶體經由 10 keV 之 X-光照射 1000 mJ/cm<sup>2</sup>,照光前、 照光後、400 ℃做真空退火與第二次照射 X-光之 I<sub>d</sub>-V<sub>g</sub> 曲線,(a)試片 A,(b)試片 B。

圖 4-5 N 型先進製程電晶體偏壓前、偏壓 10000 秒後之  $I_d$ - $V_g$  曲線,(a)於常溫下,(b)於 150 °C。

圖 4-6 於常溫下,N 型先進製程電晶體之臨界電壓變化對偏壓時間分佈圖, (a)為未照射輻射,(b)以 91.85 eV 之極紫外光為光源,照射 1000 mJ/cm²劑量。

圖 4-7 升溫至 150 ℃,N型先進製程電晶體之臨界電壓變化對偏壓時間分佈圖,(a)為未照射輻射,(b)以 91.85 eV 之極紫外光為光源,照射 1000mJ/cm²劑量。

圖 4-8 輻射對於 PBTI 之影響趨勢圖,測量條件分別為偏壓 1.3 V,施壓時 間共 5000 秒。

圖 4-9 輻射對於 PBTI 之影響趨勢圖,測量條件分別為偏壓 1.5 V,施壓時間共 10000 秒。

## 第五章

## 結論與展望

#### 5-1 結論

## 5-1-2 介面層電漿處理對金氧半電容之電性影響

在本論文中,對金屬閘極/高介電質氧化物之金氧半電容之氧化物/矽介面層進行不同的電漿處理,初始電性如第三章所述,氮氣電漿處理會造成平帶電壓負增加,我們推測為 Si-N 鍵結導致正電荷增加,然而氨氣電漿處理卻是造成正增加,造成不同結果的原因,猜測為氨氣電漿中氫離子修補介面層中的懸鍵,因而減少正電荷。並且當氧化層厚度降低至 5 nm 時,依然可看到相同現象。

接著討論遲滯電壓部分,所有電漿處理後之試片皆有增加趨勢,推測電漿處理在介面層表面產生氫或氮的鍵結,雖然可以消除多餘的懸鍵,但有可能因氫離子並未全部產生鍵結,或是氮原子增加介面應力產生缺陷。電漿處理也可能影響起始的 HfO2 沈積,使得 HfO2/SiO2 介面缺陷(邊界缺陷)增加。最後,量測時給予的偏壓,可能使得部分鍵結的氫離子受電場驅動飄移,因此遲滯現象變嚴重。5 nm HfO2 試片部分,則是因為介面電荷的影響會隨著氧化層厚度減薄而降低,所以遲滯現象不明顯。

介面能態密度於所有條件中差異並不明顯,無法斷定經由電漿處理會降低或增加,5 nm HfO2試片亦然,僅長時間氮氣電漿處理後,靠近價帶邊緣的能態數量減少。根據以上數據,雖然元素分析並未發現明顯的氮元素濃度改變,但是介面層經過不同電漿和時間處理,確實造成電容元件電性特性改變。

#### 5-1-2 介面層電漿處理對金氧半電容之抗輻射能力研究

介面層經由電漿處理確實看到不同的初始電性,因而我們也相信經過游離輻射照射後會有不同程度影響,且前人研究已證實游離輻射對金氧半電容會造成電性衰退,衰退原因為輻射引起氧化層正電荷堆積、介面能態和邊界缺陷增加,因而電容-電壓曲線可看到位移、遲滯、變形等現象皆較照射前嚴重,所以仍需經過輻射試驗,證實製程應用的可行性。

首先探討極紫外光對三種條件介面層所造成的影響,氦氣電漿處理的試片,平帶電壓增加量相對於對照組較少,且遲滯電壓與之相差無幾,介面缺陷變化則是三者中最少,表示相對其它條件有較佳的抗輻射能力,我們推測是由於 Si 懸鍵或是較弱之 Si-O 鍵結被替換成較強的 Si-N 鍵結,達到補強鍵結較鬆散化學氧化矽的結果,使得介面缺陷和平帶電壓增加較少。另外,氦氣電漿處理會因為大量氫離子掺入,產生較多的 Si-H 鍵結,使元件照射後的電性衰退較嚴重,從電容-電壓曲線可看到顯著的曲線位移與變形。氦氣電漿處理的試片在高劑量下遲滯電壓的變化相較其它條件低許多,我們猜測為照射前的遲滯電壓已經很大,輻射本身並不會增加太多邊界缺陷,因而遲滯電壓的變化量反而較少,其實遲滯電壓的實際值並不低。總結上列電性變化,三者之中氦氣電漿處理的抗輻射能力最佳,而氦氣電漿試片則是最差。

當閘極氧化層厚度降為 5 nm, 所有試片電性衰退有大幅度緩和,主要有三個原因,第一為較薄的閘極氧化層有較少的本質缺陷(Intrinsic defects)。第二原因為由輻射穿透公式 2-4 可知,較薄的閘極氧化層穿透機率較大,因此收輻射能量較少,造成電子-電洞對數量較少。最後一個為輻射所產生的電子-電洞對,由於閘極氧化層較薄,所以電荷較容易從矽晶片穿隧至閘極氧化層中,與被捕捉的正電荷再結

合或消除,亦或者電子電洞較容易逃逸出閘極氧化層。雖然輻射影響減輕,但是 抗輻射能力最差仍為氨氣電漿處理的試片,平帶電壓與介面能態增加最多,而遲 滯電壓沒有太大差異。

此外當輻射光源由極紫外光(91.85 eV)換為 X-光(10 keV)時,根據穿透機率公式 2-4,由於波長變短穿透機率大幅上升,因此被閘極氧化層吸收的能量也會隨之減少,所以可以看到各項電性衰退幅度都有減少,然而於氮氣和氨氣電漿試片介面能態密度甚至只有些微增加。根據本論文的研究發現極紫外光對不同電漿處理介面層,所造成的輻射影響遠大於 X-光。

放置 50 天後,再次量測照射極紫外光之金氧半電容,各條件之電性有部分回復,於 15 nm 閘極氧化層有較明顯變化,5 nm 閘極氧化層幾乎沒有回復,推測由於氧化層較薄,輻射引起的正電荷被捉數量較少,且氧化層愈薄,電荷量變化對於元件特性的影響愈輕微,因此 50 天過後 5 nm 閘極氧化層的試片幾乎沒有變化。而照射 X-光的試片,其介面電荷照射游離輻射後幾乎沒有增加,因此 50 天後差異性不大,平帶電壓與遲滯電壓相較極紫外光試片有較少的變化量。

## 1896

### 5-1-3 輻射對於電晶體退火處理與可靠度之影響

本論文使用先進製程電晶體研究利用退火修復輻射損傷方式對抗輻射能力造成的影響。當元件照射輻射後,次臨界擺幅和臨界電壓不會改變太多,然而關閉電流卻會上升 100 倍以上,經過 400 °C真空退火後所有電性皆會恢復至與照射前電性接近,再次照射輻射後電性衰退幅度與第一次相同,並不會改變元件之抗輻射能力,而 X-光則是有相同的情況,因此得知游離輻射所造成之氧化層被捕捉正電荷與介面電荷,產生量皆有固定量,並且不會因為已照射過一次游離輻射,使得元件之抗輻射能力有衰退現象。

接著利用臨界電壓對正偏壓溫度的不穩定性測試電晶體可靠度,於前人研究中因為量測給予電場太強,因而無法直接證明輻射對可靠度會造成影響,因此本論文偏壓調降為1.3 V,於5000 秒後,在攝氏150 度臨界電壓變化約為27 mV,而在室溫則是5 mV,兩種溫度下均為1.5 V 電壓條件變化量2倍左右,並且分布與趨勢皆相似,因此仍無法明確肯定輻射對於可靠度之影響,然而卻證實電場對於測量影響遠大於輻射影響,因而無法明確地觀測到輻射對於可靠度影響。

## 5-2 後續研究建議

在本論文中,已經證實使用不同電漿處理對於 HfO<sub>2</sub>/Si 晶片之介面層,確實會對元件電性造成影響,並且對於極紫外光與 X-光之抗輻射能力也會有所不同,然而不單只有此種方法,更還有其它值得研究主題。

首先於電漿處理之氣體,不單可以使用氮氣和氨氣,仍還有其它氣體可以選擇,像是  $CF_4$ 、 $O_2$ 和  $N_2O$  等,都是早在 90 年代在傳統  $SiO_2$  閘極介電層已被研究過。而品質改善處理方式也不只有遠距式電漿處理,更還有快速熱退火可以氧化出氧化層,上述都是可以再嘗試的製程。並且目前只對於 p 型晶片金氧半電容,有做不同介面層處理,而在 n 型晶片對介面層做處理,照射游離輻射之抗輻射能力還尚未被完全研究。

至於量測方面仍有可以了解的地方,例如:電流傳導機制與介電層崩潰機制, 照射試片未有充分數量可量測,所以於本論文中並未研究。或者是固定電壓施壓 (Constant voltage stress),可以了解介電層捕捉電荷電性。

於製程方面,目前只有製作 P 型金氧半電容,先進製程電晶體元件製程於本論文中,目前只有製作 N 型場效電晶體,因此於本研究中只對照射極紫光前後之PBTI 差異,而 NBTI 部分尚未有研究。

## 参考文獻

- [1] Lithography in International Technology Roadmap for Semiconductor, p. 14, 2011.

- [2] Lithography in international technology roadmap for semiconductor, p. 4, 2009.

- [3] M. D. Austin, H. Ge, W. Wu, M. Li, Z. Yu, D. Wasserman, S. A. Lyon, and S. Y. Choub, "Fabrication of 5 nm Linewidth and 14 nm Pitch Features", *Appl. Phys. Lett.*, vol. 84, pp. 5299-5301, 2004.

- [4] K. B. Kim, "A Novel Technique for Projection-type Electron-beam Lithography", *SPIE Newsroom*, DOI: 10.1117/2.1200812.1396, 2008.

- [5] J. J. H. Chen, S. J. Lin, T. Y. Fang, S. M. Chang, F. Krecinic, B. J. Lin, "Multiple Electron Beam Maskless Lithography for High-volume Manufacturing", in Proc. IEEE, DOI: 10.1109/VTSA.2009.5159308, pp. 96-97, 2009.

- [6] B. Wu and A. Kumar, "Extreme Ultraviolet Lithography: A Review", *J. Vac. Sci. Technol. B*, vol. 25, no. 6, pp. 1743-1761, 2007.

- [7] C. W. Gwyn, R. Stulen, D. Sweeney, and D. Attwood, "Extreme ultraviolet lithography", *J. Vac. Sci. Technol. B*, vol. 16, no. 6, pp.3142 -3149 1998.

- [8] A. M. Hawryluk and L. G. Seppala, "Soft X-ray Projection Lithography Using An X-ray Reduction Camera", *J. Vac. Sci. Technol. B*, vol. 6, no. 6, pp. 2162-2166, 1988.

- [9] F. Flohrer, K. Gaebel, D. Kloepfel, P. Koehler, I. Ahmad, S. Goetze, J. Kleinschmidt, V. Korobotchko, J. Ringling, G. Schriever, U. Stamm, "High Power Gas-discharge and Laser-plasma Based EUV Sources", in Proc. SPIE, DOI: 10.1117/12.465786, vol. 4631, pp. 264-270, 2002.

- [10] B. Wu and A. Kumar *Extreme Ultraviolet Lithography: Towards the Next Generation of Integrated Circuits*, p. 482, 2009 : McGraw-Hill Professional

- [11] J. Bonse Industrial Engineer Industrial Specification Management : ASML

- [12] V. Bakshi EUV Sources for Lithography, p.4 2006 :SPIE

- [13] O. Wood, C. S. Koay, K. Petrillo, H. Mizuno, S. Raghunathan, J. Arnold, D. Horak, M. Burkhardt, G. McIntyre, Y. Deng, B. L. Fontaine, U. Okoroanyanwu, A. Tchikoulaeva, T. Wallow, J. H. C. Chen, M. Colburn, S. S. C. Fan, B. S. Haran, and Y. Yin, "Integration of EUV Lithography in the Fabrication of 22-nm Node Devices", *in Proc. SPIE*, vol. 7271, DOI:10.1117/12.814379, pp. 727104-1-727104-10, 2009.

- [14] O. Wood, C. S. Koay, K. Petrillo, H. Mizuno, S. Raghunathan, J. Arnold, D. Horak, M. Burkhardt, G. Mcintyre, Y. Deng, B. L. Fontaine, U. Okoroanyanwu, T. Wallow, G. Landie, T. Standaert, S. Burns, C. Waskiewicz, H. Kawasaki, J. H. C. Chen, M. Colburn, B. Haran, S. S. C. Fan, Y. Yin, C. Holfeld, J. Techel, J. H. Peters, S. Bouten, B. Lee, B. Pierson, B. Kessels, R.t Routh, and K. Cummings, "EUV Lithography at the 22-nm Technology Node", *in Proc. SPIE*, vol. 7636, DOI:10.1117/12.847049, pp. 76361M-1-76361M-8, 2010.

- [15] A. Veloso, S. Demuynck, M. Ercken, A. M. Goethals, S. Locorotondo, F. Lazzarino, E. Altamirano, C. Huffman, A. D. Keersgieter, S. Brus, M. Demand, H. Struyf, J. D. Backer, J. Hermans, C. Delvaux, B. Baudemprez, T. Vandeweyer, F. Van Roey, C. Baerts, D. Goossens, H. Dekkers, P. Ong, N. Heylen, K. Kellens, H. Volders, A. Hikavyy, C. Vrancken, M. Rakowski, S. Verhaegen, M. Dusa1, L. Romijn1, C. Pigneret, A. Van Dijk1, R. Schreutelkamp, A. Cockburn, V. Gravey, H. Meiling, B. Hultermans, S. Lok, K. Shah, R. Rajagopalan, J. Gelatos, O. Richard, H. Bender, G. Vandenberghe, G. P. Beyer, P. Absil, T. Hoffmann, K. Ronse, and S. Biesemans, "Demonstration of Scaled 0.099 μm² FinFET 6T-SRAM Cell Using Full-Field EUV Lithography for (Sub-)22 nm Node Single-Patterning Technology", *in IEDM Tech. Dig.*, pp.1-4 2008.

- [16] T. P. Ma and P. V. Dressdorfer *Ionizing Radiation Effects in MOS Devices and Circuits*, p. 89, 1989 :Wiley

- [17] J. R. Schwank, M. R. Shaneyfelt, D. M. Fleetwood, J. A. Felix, P. E. Dodd, P. Paillet, and V. Ferlet-Cavrois, "Radiation Effects in MOS Oxides", *IEEE Trans. Nucl. Sci.*, vol. 55, no. 4, pp. 1833-1853, 2008.

- [18] N. S. Saks, M. G. Ancona, and J. A. Modolo, "Generation of Interface States by Ionizing Radiation in Very Thin MOS Oxides", *IEEE Trans. Nucl. Sci.*, vol. 33, no. 6, pp. 1185-1190, 1986.

- [19] D. B. Brown and N. S. Saks, "Time Dependence of Radiation-induced Interface Trap Formation in Metal-oxide-semiconductor Devices as A Function of Oxide Thickness and Applied Field", *Appl. Phys. Lett.*, vol. 70, no. 7, pp. 3734-3747, 1991.

- [20] B. H. Lee, L. Kang, R. Nieh, W. J. Qi and J. C. Lee, "Thermal Stability and Electrical Characteristics of Ultrathin Hafnium Oxide Gate Dielectric Reoxidized with Rapid Thermal Annealing", *Appl. Phys. Lett.*, vol. 76, no. 14, pp. 1926-1928, 2000.

- [21] G. D. Wilk, R. M. Wallace, and J. M. Anthony, "High-k Gate Dielectric: Current Status and Materials Properties Considerations", *J. Appl. Phys.*, vol. 89, no. 10, pp. 5243-5275, 2001.

- [22] T. M. Klein, D. Niu, W. S. Epling, W. Li, D. M. Maher, C. C. Hobbs, R. I. Hegde, I. J. R. Baumvol, and G. N. Parsons, "Evidence of Aluminum Silicate Formation During Chemical Vapor Deposition of Amorphous Al<sub>2</sub>O<sub>3</sub> Thin Films on Si(100)", *Appl. Phys. Lett.*, vol. 75, pp. 4001-4003, 1999.

- [23] L. Manchanda, W. H. Lee, J. E. Bower, F. H. Baumann, W. L. BroIwn, C. J. Case, R. C. Keller, Y. O. Kim, E. J. Laskowski, M. D. Morris, R. L. Opila, P. J. Silverman, T. W. Sorsch and G. R. Weber. "Gate Quality Doped High- κ Films for CMOS beyond 100 nm: 3-10 nm Al<sub>2</sub>O<sub>3</sub> with Low Leakage and Low Interface

- States", in IEDM Tech. Dig., pp. 605-608, 1998.

- [24] J. P. Chang, Y. S. Lin, S. Berger, A. Kepten, R. Bloom and S. Levy, "Ultrathin zirconium oxide films as alternative gate dielectrics", *J. Vac. Sci. Technol. B, Microelectron. Nanometer Struct.*, vol. 19, no. 16, pp.2137-2143 2001.

- [25] M. Copel, M. Gribelyuk and E. Gusev, "Structure and Stability of Ultrathin Zirconium Oxide Layers on Si(001)", *Appl. Phys. Lett.*, vol. 76, pp. 436-438, 2000.

- [26] S. A. Campbell, H. S. Kim, D. C. Gilmer, B. He, T. Ma and W. L. Gladfelter, "Titanium Dioxide (TiO<sub>2</sub>) Based Gate Insulators", *IBM J. Res.Develop.*, vol. 43, pp. 383-392, 1999.

- [27] S. A. Campbell, D. C. Gilmer, X. C. Wang, M. T. Hsieh, H. S. Kim, W. L. Gladfelter and J. Yan, "MOSFET Transistors Fabricated with High Permittivity TiO<sub>2</sub> Dielectrics", *IEEE Tran. Electron Devices*, vol. 44, pp. 104-109, 1997.

- [28] L. Kang, B. H. Lee, W. J. Qi, Y. Jeon, R. Nieh, S. Gopalan, K. Onishi, and J. C. Lee, "Electrical Characteristics of Highly Reliable Ultrathin Hafnium Oxide Gate Dielectric", *IEEE Electron Devices Lett.*, vol. 21, no. 4, pp.181-183, 2000.

- [29] R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, and M. Metz, "High-κ /Metal–Gate Stack and Its MOSFET Characteristics", *IEEE Electron Devices Lett.*, vol. 25, no. 6, pp. 408-410, 2004.

- [30] Y. S. Lin, R. Puthenkovilakam, and J. P. Chang, "Dielectric Property and Thermal Stability of HfO<sub>2</sub> on Silicon", *Applied Physics Letters*, vol. 81, pp. 2041-2043, 2002.

- [31] C. C. Wu, D. W. Lin, A. Keshavarzi, C. H. Huang, C. T. Chan, C. H. Tseng, C. L. Chen, C. Y. Hsieh, K. Y. Wong, M. L. Cheng, T. H. Li, Y. C. Lin, L. Y. Yang, C. P. Lin, C. S. Hou, H. C. Lin, J. L. Yang, K. F. Yu, M. J. Chen, T. H. Hsieh, Y. C. Peng, C. H. Chou, C. J. Lee, C. W. Huang, C. Y. Lu, F. K.

- Yang , H. K. Chen , L. W. Weng , P. C. Yen , S. H. Wang , S. W. Chang , S. W. Chuang , T. C. Gan , T. L. Wu , T. Y. Lee , W. S. Huang , Y. J. Huang , Y. W. Tseng , C. M. Wu , E. O. Yang , K. Y. Hsu , L. T. Lin , S. B. Wang , T. M. Kwok , C. C. Su , C. H. Tsai , M. J. Huang , H. M. Lin , A. S. Chang , S. H. Liao , L. S. Chen , J. H. Chen , P. S. Lim , X. F. Yu , S. Y. Ku , Y. B. Lee , P. C. Hsieh , P. W. Wang , Y. H. Chiu , S. S. Lin , H. J. Tao , M. Cao and Y. J. Mii, "High Performance 22/20nm FinFET CMOS Devices with Advanced High-  $\kappa$  /Metal Gate Scheme", *in IEDM Tech. Dig.*, pp.600-603, 2010.

- [32] C. Auth , C. Allen , A. Blattner , D. Bergstrom , M. Brazier , M. Bost , M. Buehler , V. Chikarmane , T. Ghani , T. Glassman , R. Grover , W. Han , D. Hanken , M. Hattendorf , P. Hentges , R. Heussner , J. Hicks , D. Ingerly , P. Jain , S. Jaloviar , R. James , D. Jones , J. Jopling , S. Joshi , C. Kenyon , H. Liu , R. McFadden , B. Mcintyre , J. Neirynck , C. Parker , L. Pipes , I. Post , S. Pradhan , M. Prince , S. Ramey , T. Reynolds , J. Roesler , J. Sandford , J. Seiple , P. Smith , C. Thomas , D. Towner , T. Troeger , C. Weber , P. Yashar , K. Zawadzki and K. Mistry "A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors", *Proc. VLSI Technol. Symp.*, pp.131-132, 2012.

- V. S. Basker , T. Standaert , H. Kawasaki , C. C. Yeh , K. Maitra , T. Yamashita , J. Faltermeier , H. Adhikari , H. Jagannathan , J. Wang , H. Sunamura , S. Kanakasabapathy , S. Schmitz , J. Cummings , A. Inada , C. H. Lin , P. Kulkarni , Y. Zhu , J. Kuss , T. Yamamoto , A. Kumar , J. Wahl , A. Yagishita , L. F. Edge , R. H. Kim , E. Mclellan , S. J. Holmes , R. C. Johnson , T. Levin , J. Demarest , M. Hane , M. Takayanagi , M. Colburn , V. K. Paruchuri , R. J. Miller , H. Bu , B. Doris , D. McHerron , E. Leobandung and J. O'Neill "A 0.063 μm² FinFET SRAM cell demonstration with conventional lithography using a novel integration scheme with aggressively scaled fin and gate pitch", *Proc. VLSI Technol. Symp.*, pp.19-20, 2010.

- [34] N. D. Arora, R. Rios, and C. L. Huang, "Modeling the Polysilicon Depletion Effect and Its Impact on Submicrometer CMOS Circuits Performance", *IEEE Trans. Electron Devices*, vol. 42, no. 5, pp. 935-943, 1995.

- [35] Y. C. Yeo, T. J. King, and C. M. Hu, "Metal-dielectric Band Alignment and Its Implications for Metal Gate Complementary Metal-oxide-semiconductor Technology", *J. Appl. Phys.*, vol. 92, no. 12, pp. 7266-7271, 2002.

- [36] C. Stork, Z. Yu, P. M. Zeitzoff and J. C. S. Woo, "The Impact of High-κ Gate Dielectrics and Metal Gate Electrodes on Sub-100 nm MOSFETs", *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1537-1544, 1999.

- [37] M. Fischetti, D. A. Neumayer, and E. A. Cartier, "Effective Electron Mobility in Si Inversion Layers in Metal-oxide-semiconductor Systems with A High-k Insulator: the Role of Remote Phonon Scattering", *J. Appl. Phys.*, vol. 90, pp.4587-4608, 2001.

- [38] S. Datta, G. Dewey, M. Doczy, B.S. Doyle, B. Jin, J. Kavalieros, R. Kotlyar, M. Metz, N. Zelick and R. Chau., "High Mobility Si/SiGe Strained Channel MOS Transistors with HfO<sub>2</sub>/TiN Gate Stack", *in IEDM Tech. Dig.*, pp. 653-656, 2003.

- [39] J. A. Felix, M. R. Shaneyfelt, D. M. Fleetwood, J. R. Schwank, P. E. Dodd, E. P. Gusev, R. M. Flemin, and C. D'Emic, "Charge Trapping and Annealing in High-κ Gate Dielectrics", *IEEE Trans. Nucl. Sci.*, vol. 51, no. 6, pp. 3143-3149, Dec. 2004.

- [40] X. J. Zhou, D. M. Fleetwood, J. A. Felix, E. P. Gusev, and C. D'Emic, "Bias-Temperature Instabilities and Radiation Effects in MOS Devices", *IEEE Trans. Nucl. Sci.*, vol. 52, no. 6, pp. 2231-2238, Dec. 2005.

- [41] D. K. Chen, F. E. Mamouni, X. J. Zhao, R. D. Schrimpf, D. M. Fleetwood, K. F. Galloway, S. Lee, H. Seo, G. Lucovsky, B. Jun and J.D. Cressler "Total Dose and Bias Temperature Stress Effects for HfSiON on Si MOS Capacitors", *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp.1931-1937, 2007.

- [42] S. K. Dixit, X. J. Zhou, R. D. Schrimpf, D. M. Fleetwood, S. T. Pantelides, R. Choi, G. Bersuker and L. C. Feldman, "Radiation Induced Charge Trapping in Ultrathin HfO<sub>2</sub>-Based MOSFETs", *IEEE Trans. Nucl. Sci.*, vol. 54, no. 6, pp. 1883-1890, Dec. 2007.

- [43] J. A. Felix, D. M. Fleetwood, R. D. Schrimpf, J. G. Hong, G. Lucovsky, J. R.

- Schwank and M. R. Shaneyfelt, "Total-Dose Radiation Response of Hafnium-Silicate Capacitors", *IEEE Trans. Nucl. Sci.*, vol. 49, no. 6, pp. 3191-3196, Dec. 2002.

- [44] P. H. Li, "Effect of Extreme Ultra-Violet Radiation on High Dielectric constant Dielectrics", National Chiao Tung University, Department of Electronics Engineering Institute of Electronics, 2010.

- [45] T. T. Su, "Effect of Interfacial Layer Engineering on the Radiation Hardness of Hf-based Dielectrics to EUV Irradiation", National Chiao Tung University, Graduate Program for Science and Technology of Accelerator Light Source, 2011.

- [46] M. H. Sung, "A Study on the Effect of Ionizing Radiation on MOS Devices with Various Hf-based Dielectric Thickness", National Chiao Tung University, Graduate Program for Science and Technology of Accelerator Light Source, 2013.

- [47] M. Bhat, J. Kim, J. Yan, G. W. Yoon, L. K. Han, and D. L. Kwong, "MOS Characteristics of Ultrathin NO-Grown Oxynitrides", *IEEE Electron Device Lett.*, pp.421 1994, 1994.

- [48] S. C. Song, H. F. Luan, C. H. Lee, A. Y. Mao, S. J. Lee, J. Gelpey, S. Marcus, and D. L. Kwong, "Ultra Thin High Quality Stack Nitride/Oxide Gate Dielectrics Prepared by in-situ Rapid Thermal N<sub>2</sub>O Oxidation of NH<sub>3</sub>-nitrided Si", *Proc. VLSI Tech. Symp.*, pp.137 -138 1999.

- [49] H. Hwang, W. Ting, D. L. Kwong, and J. Lee, "Electrical and Reliability Characteristics of Ultrathin Oxynitride Gate Dielectric Prepared by Rapid Thermal Processing in N<sub>2</sub>O", *in IEDM Tech. Dig.*, vol. 90, pp. 421-424, 1990.

- [50] J. Ahn, W. Ting, and D. L. Kwong, "Furnace Nitridation of Thermal SiO<sub>2</sub> in Pure N<sub>2</sub>O Ambient for ULSI MOS Applications", *IEEE Electron Devices Lett.*, vol. 13, no. 2, pp. 117-119, 1992.

- [51] G. J. Dunn, "Effect of Synchrotron X-ray Radiation on the Channel Hot-Carrier Reliability of Reoxidized Nitrided Silicon Dioxide", *IEEE Trans. Electron Devices*, vol. 12, no. 1, pp. 8-9, 1991.

- [52] F. L. Rerry, JR., R. J. Aucoin, M. L. Naiman, and S. D. Senturia, "Radiation Effect in Nitrided Oxides", *IEEE Electron Devices Lett.*, vol. 4, no. 6, pp. 191-193, 1991.

- [53] G. Q. Lo, A. B. Joshi, and D. L. Kwong, "Radiation Hardness of MOSFET's with N<sub>2</sub>O-Nitrided Gate Oxides", *IEEE Trans. Electron Devices*, vol. 40, no. 8, pp. 1565-1567, 1993.

- [54] Y. L. Wu and J. G. Hwu, "Improvement in radiation hardness of reoxidized nitrided oxide (RNO) in the absence of post-oxidation anneal", *IEEE Electron Device Lett.*, vol. 14, no. 1, 1993.

- [55] C. J. Anthony, M. J. Uren, and V. Nayar, "Radiation Hardness of N<sub>2</sub>O Grown Oxynitrides Assessed Using the Conductance Technique", *Appl. Phys. Lett.*, vol. 69, no. 14, pp. 2104-2106, 1996.

- [56] Opto Diode AXUV100G Datasheet :International Radiation Detectors, Inc. (IRD)

- [57] I. M. Terman, "An Investigation of Surface States at A Silicon/Silicon Dioxide Interface Cmploying Metal-oxide-silicon Diodes", *Solid-State Electronics*, vol. 5, no. 5, pp. 285-299, 1962.

- [58] K. C. Chen, "A Study on Effect of Ionizing Radiation on Resistive Random Access Memory", National Chiao Tung University, Graduate Program for Science and Technology of Accelerator Light Source, 2013.

- [59] D. K. Schroder Semiconductor Material and Device Characterization, 2006: Wiley

- [60] D. M. Fleetwood, P. S. Winokur, R. A. Reber Jr., T. L. Meisenheimer, J. R. Schwank, M. R. Shaneyfelt and L. C. Riewe, "Effects of Oxide Traps, Interface Traps, and "border traps" on Metal-oxide-semiconductor Devices", *J. Appl. Phys.*, vol. 73, pp. 5058-5074, 1993.

## 作者簡歷

姓名:廖雪君

性別:女

生日:民國77年11月22日

學歷:

新北市立高級中學 (93.9-96.6)

大同大學電機工程學系 (96.9-100.6)

國立交通大學加速器光源科技與應用碩士學位學程 (100.9-103.8)

碩士論文題目:

電漿處理對二氧化鉿/矽介面層抗輻射能力之影響

Effect of plasma treatment on the radiation hardness of the HfO<sub>2</sub>/Si interfacial

layer