# 國 立 交 通 大 學 電子工程學系電子研究所 博 士 論 文

用於MPEG-4 與H.264視訊編碼的移動估測設計

Design of Motion Estimation for MPEG-4 and H.264 Video

Coding

研究生: Esam A. Al\_Qaralleh

指導教授 : Dr. Tian-Sheuan Chang

Dr. Chein-Wei Jen

中華民國九十 5 年 6 月

#### 用於MPEG-4 與H.264視訊編碼的移動估測設計

Design of Motion Estimation for MPEG-4 and H.264 Video Coding

研究生: Esam A. Al\_Qaralleh

指導教授 : Dr. Tian-Sheuan Chang

Dr. Chein-Wei Jen

國立交通大學電子工程學系電子研究所 博士論文

A Dissertation

Submitted to department of Electronic Engineering and Institute of Electronics

College of Electrical Engineering

National Chiao Tung University

In Partial Fulfillment of the requirements for the Degree of Doctor of Philosophy

In

Electronic Engineering

July 2006

Hsinchu, Taiwan, Republic of China

中華民國九十 5 年 6 月

#### 國立交通大學

#### 論文口試委員會審定書

本校電子工程學系電子研究所博士班Esam A. Al\_Qaralleh 君

所提論文 Design of Motion Estimation for MPEG-4 and H.264 Video Coding 合於博士資格標準、業經本委員會評審認可。 教授 李鎮宜 教授 教授 陳紹基 教授 張添烜 教授

教授

教授

系主任:

教授

中華民國 95 月 19

# Department of Electronics Engineering & Institute of Electronics National Chiao Tung University Hsinchu, Taiwan, R.O.C.

Date: 19/7/2006

We have carefully read the dissertation entitled <u>Design of Motion Estimation</u>

for MPEG-4 and H.264 Video Coding. submitted by <u>Esam A. Al\_Qaralleh</u> in partial fulfillment of the requirements of the degree of DOCTOR OF PHILOSOPHY and recommend its acceptance.

| recommend its accept | ance.        |                  |

|----------------------|--------------|------------------|

| Yung-Chang           | Chen Chen    | An-Yeu (Andy) Wu |

| Jar-Ferr Yar         |              | Chen-Yi Lee      |

| Chein-Wei J          | Sei In       | Sau-Gee Chen     |

| Tian-Sheuar          | Chang        |                  |

| Thesis Advisor:      | lein-Wei Jen | Tian-Sheuan Chan |

| Director :           | Sau-Gee Chen | _                |

| Chairman :           | Chen-Yi Lee  | el               |

#### **ACKNOWLEDGE**

I would like to thank professor Tian-Sheuan Chang, for his supervision and support during this work. He is so kind and generous. This work won't be possible without his fruitful and valuable comments and directions throughout this work. Thank you.

To my first teacher professor Chein-Wei Jen, my deep appreciation and thankful for his supervision in the first years of my stay in Taiwan.

To all my friends and lab members who were always helpful and supportive, their friendly behavior made me feel comfortable during my stay in Taiwan which is my second home beside Jordan.

Esam A. Al\_Qaralleh

# **Table of Contents**

| Chapter 1 Introduction                                                                                       | 1                |

|--------------------------------------------------------------------------------------------------------------|------------------|

| 1.1 Overview of Video Coding                                                                                 | 1                |

| 1.2 Cores of Digital Video Technology                                                                        | 2                |

| 1.2.1 MPEG-4 Overview                                                                                        | 3                |

| 1.2.2 H.264 Overview                                                                                         | 6                |

| 1.3 Motivation and Contributions                                                                             | 8                |

| 1.4 Dissertation Organization                                                                                | 10               |

| Chapter 2 A Fast Binary Motion Estimation Algorithm and its Archite                                          | ecture Design 11 |

| 2.1 Overview of the MPEG-4 Video System                                                                      | 11               |

| 2.1.1 Video Object and Video Object Plane                                                                    | 11               |

| 2.1.2 MPEG-4 Binary Shape Coding                                                                             | 12               |

| 2.2 Motion Estimation for MPEG-4 Video                                                                       | 16               |

| 2.2.1 Block-matching Algorithm                                                                               | 17               |

| 2.2 Motion Estimation for MPEG-4 Video  2.2.1 Block-matching Algorithm  2.2.2 Search Range and Search Points | 18               |

| 2.3 Analysis of Binary Motion Estimation                                                                     |                  |

| 2.4 Previous Work on Binary Motion Estimation                                                                | 20               |

| 2.5 Motivation for Fast Binary Motion Estimation                                                             | 22               |

| 2.6 The Proposed Algorithm                                                                                   | 24               |

| 2.6.1 Software simulation results and analysis                                                               | 24               |

| 2.6.2 Block-matching Algorithm                                                                               | 25               |

| 2.6.3 Consideration for the Classification and Matching Methods                                              | 29               |

| 2.7 The Architecture Design                                                                                  | 30               |

| 2.7.1 Architecture Design                                                                                    | 30               |

| 2.7.2 PE Design                                                                                              | 31               |

| 2.7.3 Data reuse and data flow                                          | 32 |

|-------------------------------------------------------------------------|----|

| 2.7.4 Experiments results                                               | 34 |

| 2.7.5 Comparisons                                                       | 36 |

| 2.8 Summary                                                             | 37 |

| Chapter 3 Texture Motion Estimation for MPEG-4 and H.264                | 39 |

| 3.1 Introduction to Block Matching                                      | 39 |

| 3.2 Exploration of Algorithms                                           | 41 |

| 3.2.1 Proposed Algorithm-Software Approach                              | 42 |

| 3.3 Exploration of Architectures                                        | 53 |

| 3.3.1 ME Architectures – an overview                                    | 54 |

| 3.3.2 Proposed Architecture                                             | 54 |

| 3.4 Summary                                                             | 60 |

| Chapter 4 Data Reuse Exploration Between Vertical Adjacent Macro Blocks |    |

| 4.1 Introduction                                                        | 62 |

| 4.2 Data reuse in the motion estimation                                 | 63 |

| 4.3 Data reuse and parallel processing of vertical blocks               | 64 |

| 4.3.1 Proposed data reuse scheme                                        | 67 |

| 4.3.2 Architecture Design                                               | 70 |

| 4.3.3 Design comparisons                                                | 77 |

| 4.4 Summary                                                             | 78 |

| Chapter 5 Future Work and Conclusion                                    | 79 |

| 5.1 Contributions Summary                                               | 79 |

| 5.2 Future Work                                                         | 82 |

| 5.2.1 Fractional Motion Estimation                                      | 82 |

| 5.2.2 Mode Selection and Hilbert Transform.                             | 87 |

| 5.2.3 Binary Motion Estimation | 89 |

|--------------------------------|----|

| 5.3 Summary                    | 91 |

| References                     | 92 |

# List of Figures

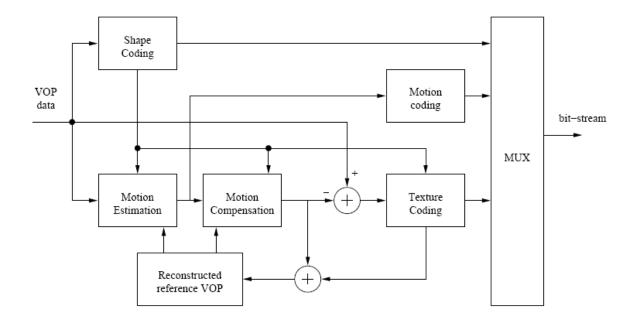

| FIG. 1.1 GENERAL STRUCTURE OF MPEG-4 VOP ENCODER                                                        |

|---------------------------------------------------------------------------------------------------------|

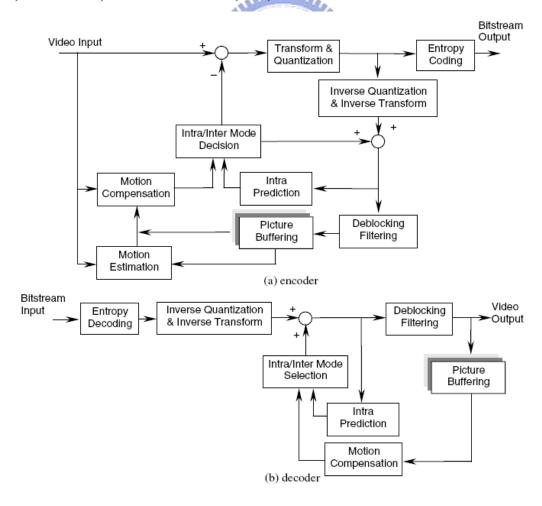

| FIG.1.2 THE BLOCK DIAGRAM OF H.264 ALGORITHM. 7                                                         |

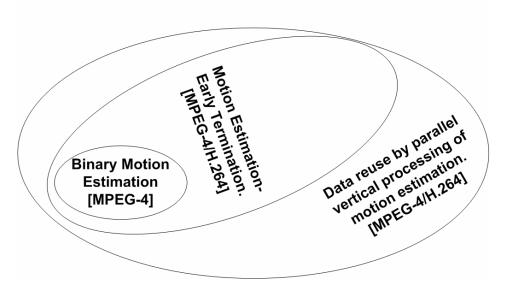

| FIG. 1.3 THE RELATIONS BETWEEN THE WORKS PRESENTED IN THIS THESIS                                       |

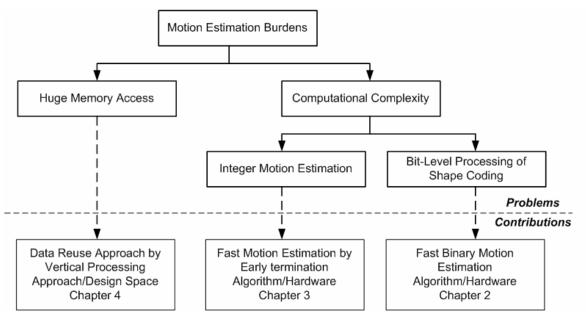

| FIG. 1.4 CONTRIBUTIONS OF THE WORKS PRESENTED IN THIS THESIS.                                           |

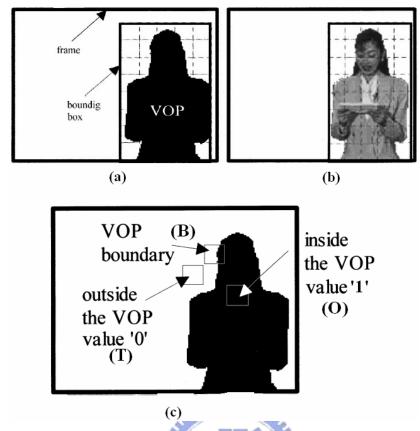

| FIG.2.1 VIDEO OBJECT PLANE (VOP)                                                                        |

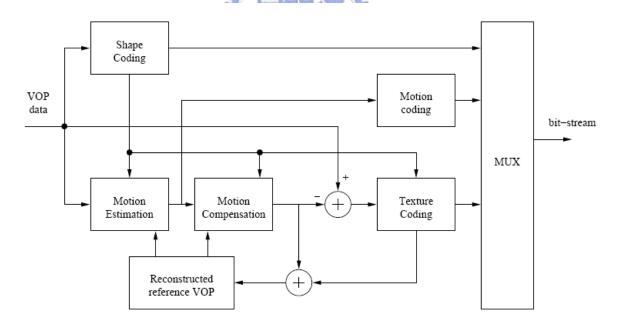

| FIG.2.2 GENERAL STRUCTURE OF MPEG-4 VOP ENCODER                                                         |

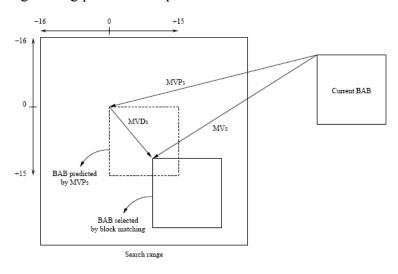

| FIG. 2.3 BLOCK MATCHING OF MOTION ESTIMATION FOR SHAPE                                                  |

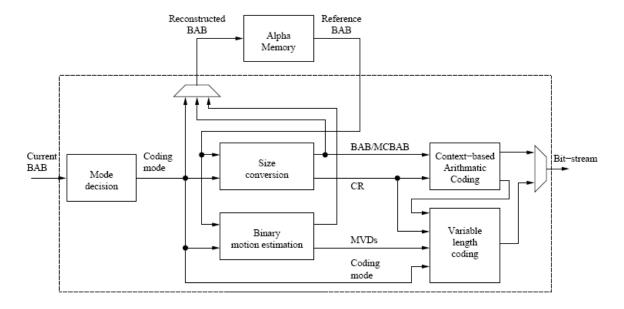

| FIG.2.4 BLOCK DIAGRAM OF MPEG-4 BINARY SHAPE ENCODING SYSTEM                                            |

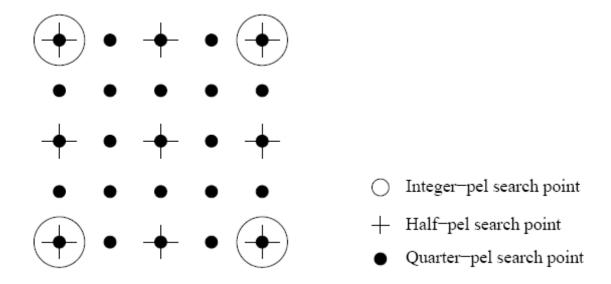

| FIG. 2.5 FRACTIONAL-PEL SEARCH POINTS                                                                   |

| FIG. 2.6 PSEUDO CODE FOR FULL-SEARCH BMA KERNEL FOR SHAPE MOTION ESTIMATION                             |

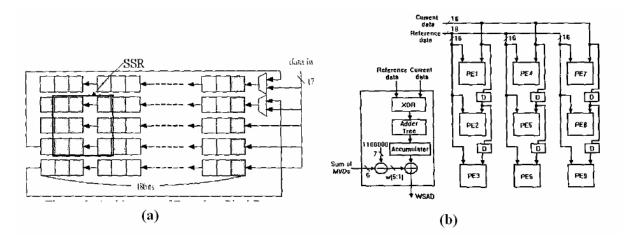

| FIG. 2.7 ARCHITECTURE DESIGN PRESENTED IN [11]                                                          |

| Fig. 2.8 Architecture design presented in [10].                                                         |

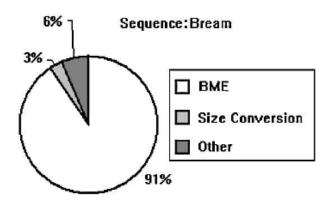

| FIG. 2.9 COMPUTATIONAL COMPLEXITY OF MPEG-4 SHAPE ENCODER. 23                                           |

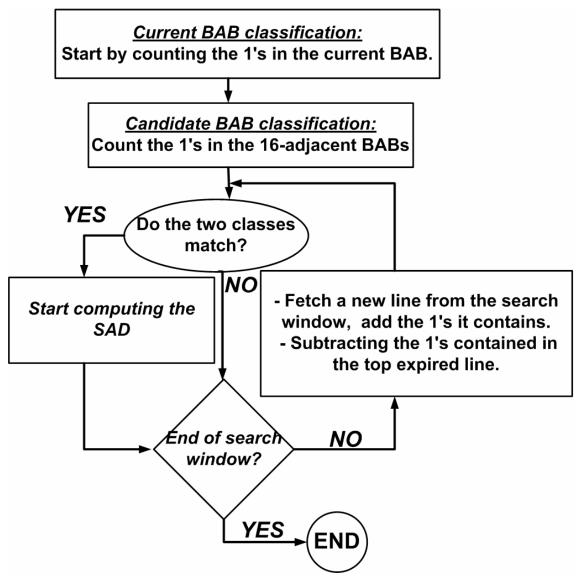

| Fig. 2.10 Flowchart for the proposed algorithm. 26                                                      |

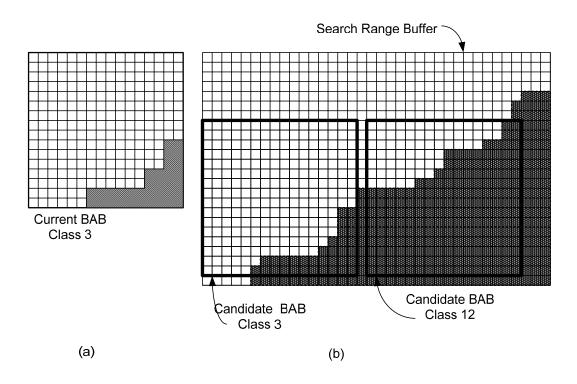

| FIG. 1.11 (A) CURRENT BAB CONTAINS CERTAIN NUMBER OF "1" BITS AND BELONGS TO CLASS 3. (B)               |

| SEARCH WINDOW SHOWING TWO BABS, EACH ONE FROM DIFFERENT CLASSES                                         |

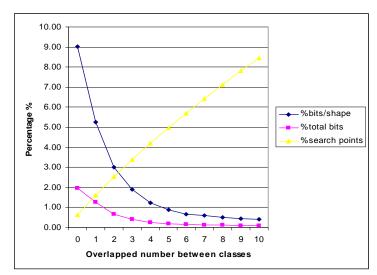

| FIG. 2.13 THE IMPACT OF CLASSES OVERLAPPING ON BITS/SHAPE, TOTAL ENCODED BIT-STREAM AND                 |

| THE NUMBER OF SEARCH POSITIONS. 28                                                                      |

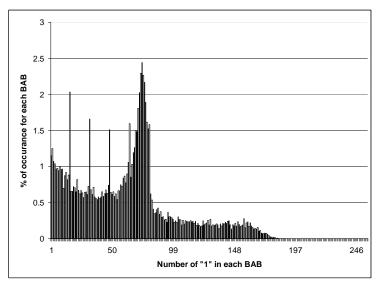

| FIG.2.13 THE PROBABILITY DISTRIBUTION FOR THE 256 CLASSES IN THE CONTAINER_2_OBJ                        |

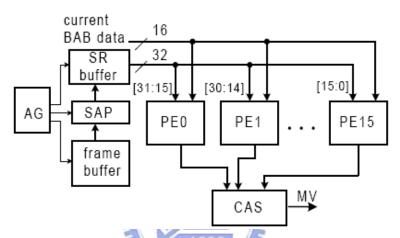

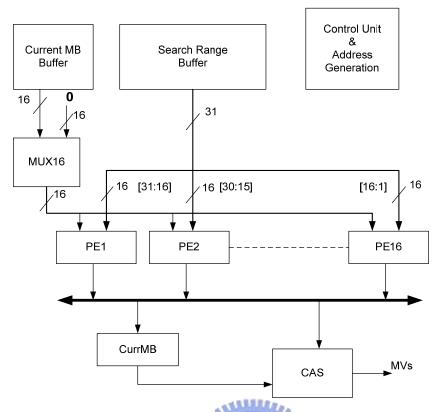

| FIG. 2.14 ARCHITECTURE BLOCK DIAGRAM OF THE PROPOSED ALGORITHM                                          |

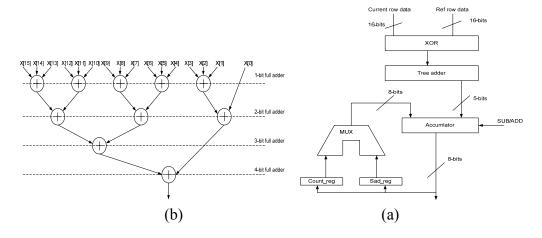

| FIG. 2.15 (A) THE SAD ARCHITECTURE, AND (B) THE TREE ADDER.                                             |

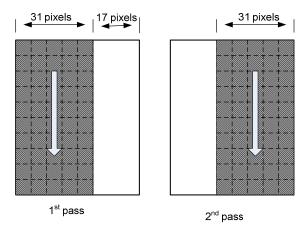

| FIG. 2.16 TWO PASSES NEEDED TO COVER THE SEARCH WINDOW                                                  |

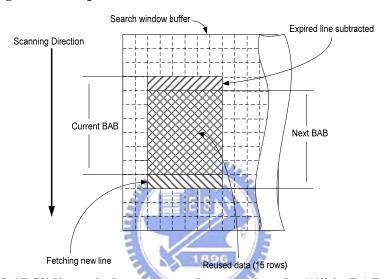

| FIG. 2.17 SLIDING WINDOW APPROACH: COUNTING THE "1" IN BABS                                             |

| FIG. 2.18 ADJACENT BABS BELONG TO THE SAME CLASS, AND MATCH THE SAME CLASS OF CURRMB.                   |

| SAD CALCULATION WILL BE HELD AT THE SAME TIME IN HARDWARE IMPLEMENTATION35                              |

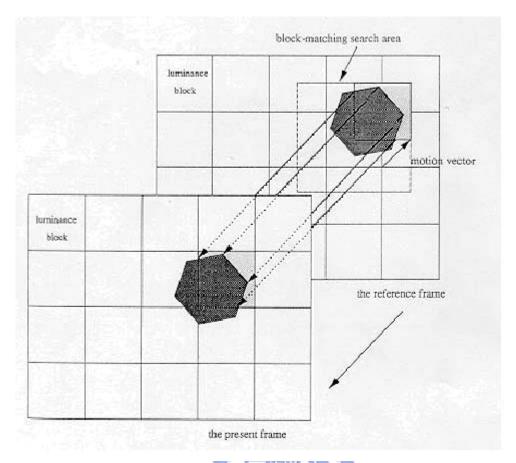

| FIG. 3.1 BLOCK MATCHING ALGORITHM. 40                                                                   |

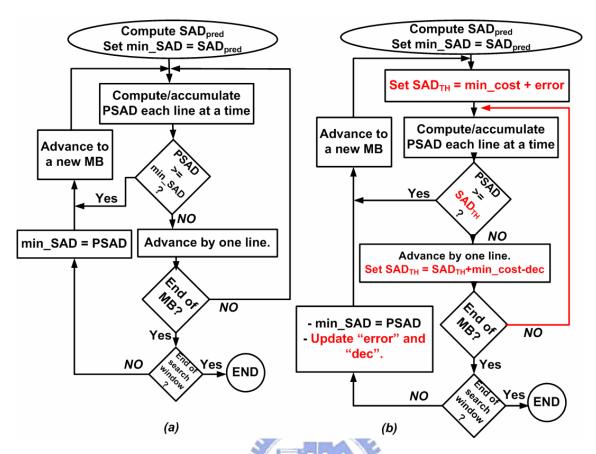

| FIG. 3.2 (A) ALGORITHM FLOW FOR THE PDS, AND (B) OUR PROPOSED ALGORITHM45                               |

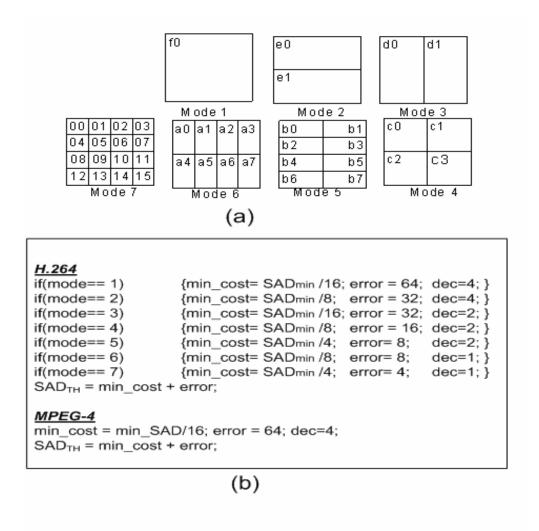

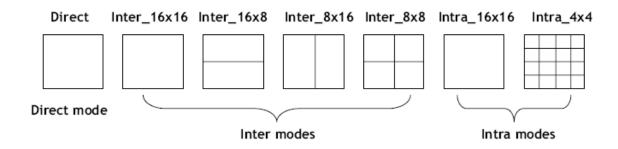

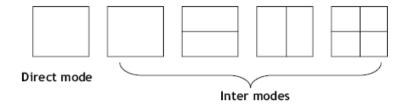

| FIG. 3.3 (A) SEVEN MACROBLOCK MODES IN H.264/AVC, (B) VALUES FOR SAD <sub>TH</sub> , ERROR, AND DEC FOR |

| DIFFERENT BLOCK SIZES IN H.264 AND THAT FOR MPEG-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 46                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

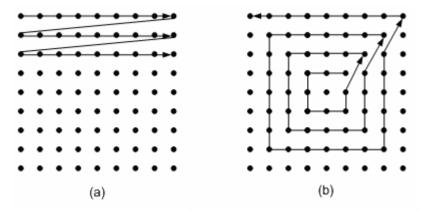

| FIG. 3.5 SCAN PATTERNS IN THE SEARCH WINDOW, (A) RASTER SCAN, AND (B) SPIRAL SCAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50                                  |

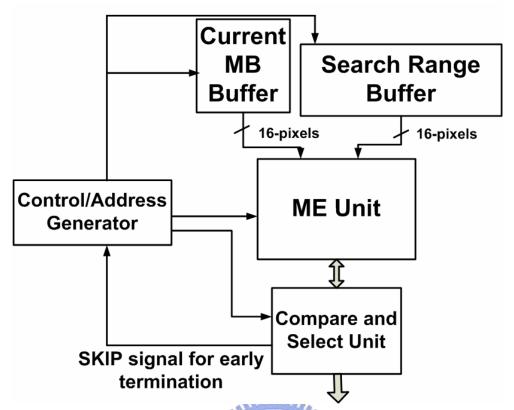

| FIG. 3.6 BLOCK DIAGRAM OF THE PROPOSED ARCHITECTURE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56                                  |

| FIG. 3.7 ME UNIT INTERNAL DESIGN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 58                                  |

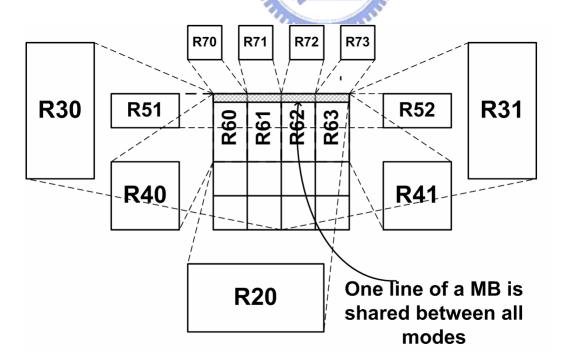

| FIG. 3.8 SPATIAL OVERLAPPING BETWEEN DIFFERENT MODES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58                                  |

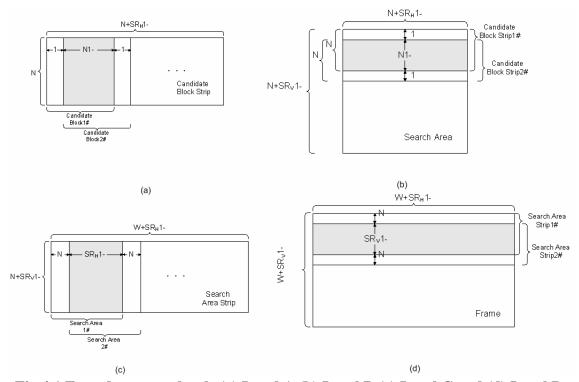

| FIG 4.1 FOUR DATA REUSE LEVELS (A) LEVEL A (B) LEVEL B (C) LEVEL C AND (D) LEVEL D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 65                                  |

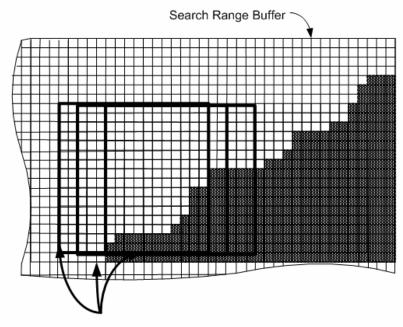

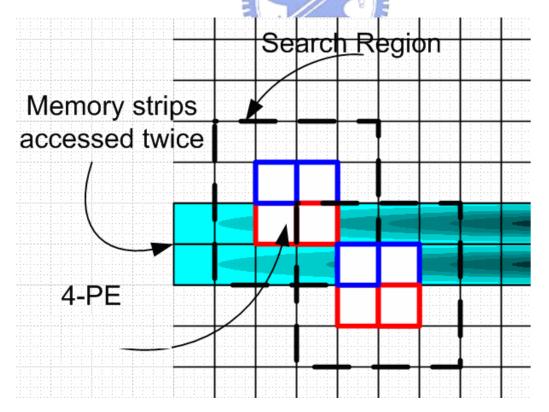

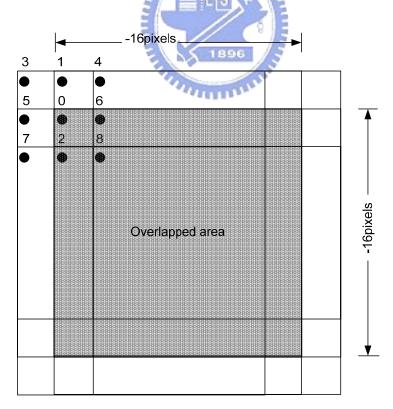

| FIG. 4.2 MEMORY ACCESS DIAGRAM IN [64]. THE OVERLAPPED SEARCH REGION (GRAY PART) WILL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | BE                                  |

| ACCESSED TWICE. EACH BLOCK IN THE DIAGRAM DENOTES ONE MB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 66                                  |

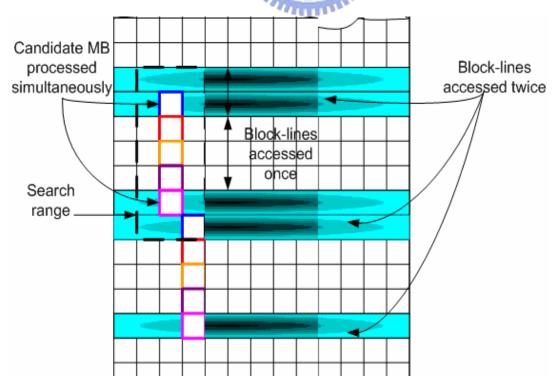

| FIG. 4.3 PROPOSED SCHEME WITH FIVE CURRENT BLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67                                  |

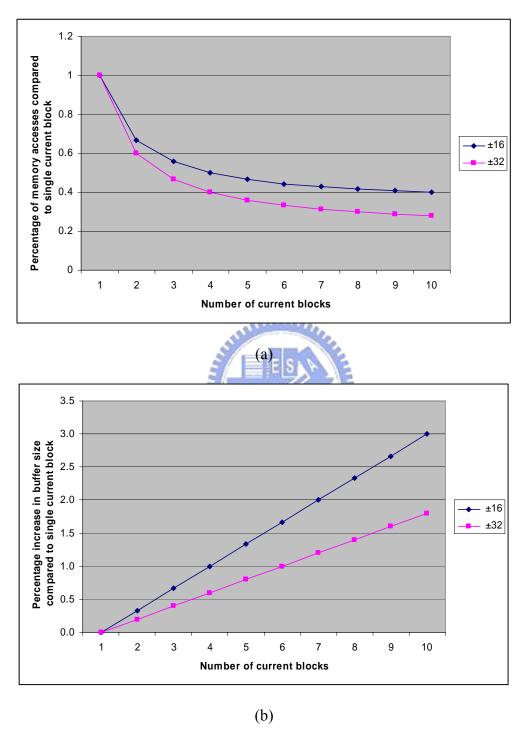

| FIG. 4.4 (A) PERCENTAGE OF NUMBER OF MEMORY WHEN NORMALIZED TO ONE CURRENT BLOCK, (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (B)                                 |

| THE PERCENTAGE INCREASE IN BUFFER MEMORY SIZE NORMALIZED TO ONE CURRENT BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | к. 71                               |

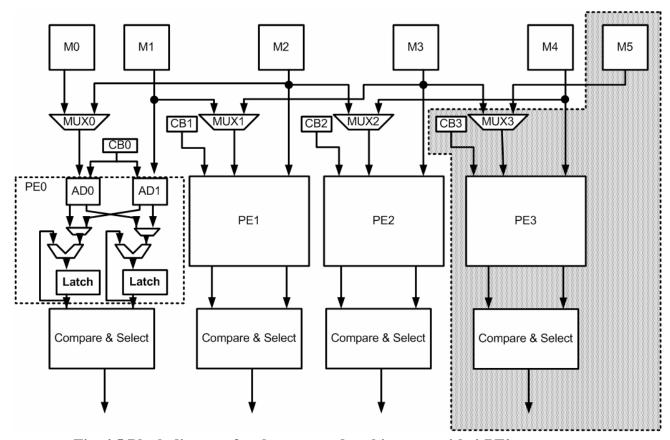

| FIG. 4.5 BLOCK DIAGRAM FOR THE PROPOSED ARCHITECTURE WITH 4-PE'S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 72                                  |

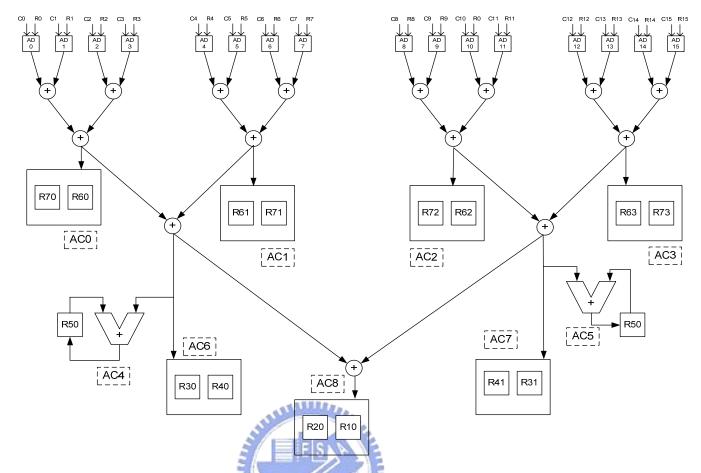

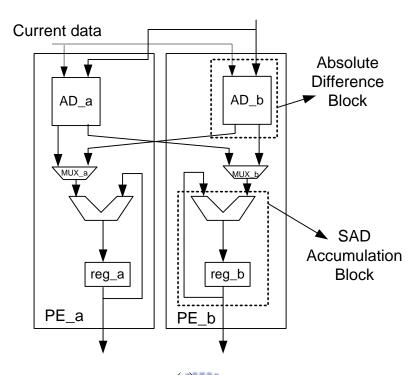

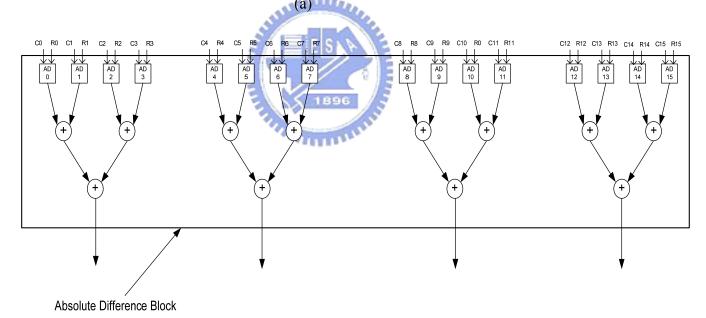

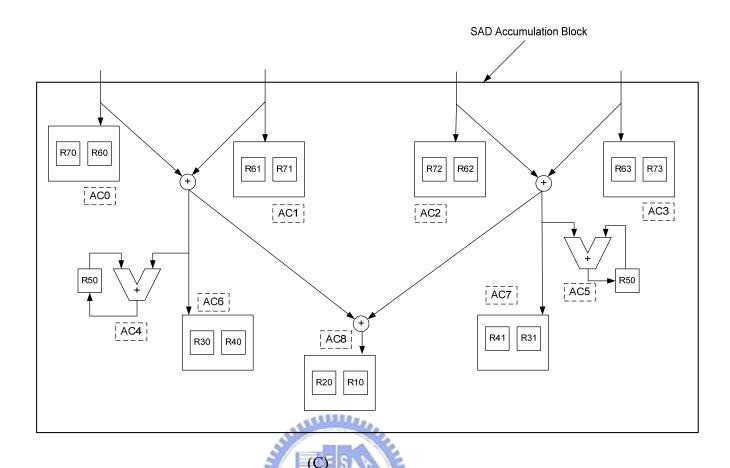

| FIG. 4.6 (A) DETAILED BLOCK DIAGRAM OF PE.(B) BLOCK DIAGRAM OF ABSOLUTE DIFFERENT BLO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CK                                  |

| (C) BLOCK DIAGRAM OF SAD ACCUMULATION BLOCK, WHERE AC DENOTES THE ACCUMULA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ГOR                                 |

| AND R DENOTES THE REGISTERS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 74                                  |

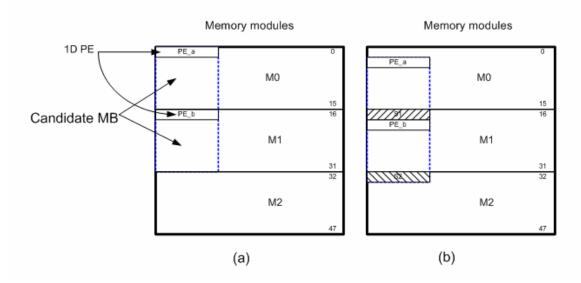

| FIG. 4.7 PE OPERATION FOR THE (A) FIRST CANDIDATE POSITION AND (B) SECOND CANDIDATE POSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | TION                                |

| SHOWING THE DATA MULTIPLEXING BETWEEN BOTH PE'S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                  |

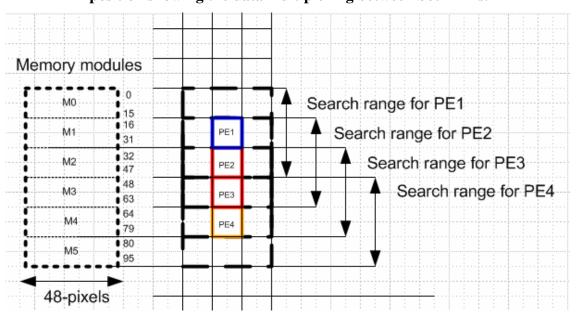

| FIG. 4.8 MAPPING OF MEMORY MODULES TO THE SEARCH RANGE FOR EVERY PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                     |

| FIG. 4.8 MAPPING OF MEMORY MODULES TO THE SEARCH RANGE FOR EVERY PE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75                                  |

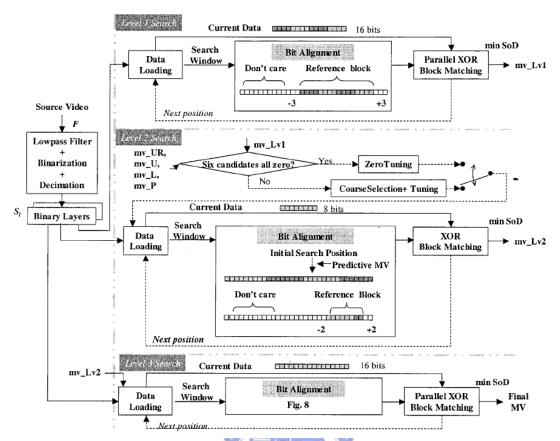

| A STATE OF THE PARTY OF THE PAR | 75<br><b>0</b> 83                   |

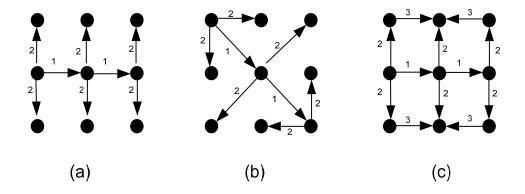

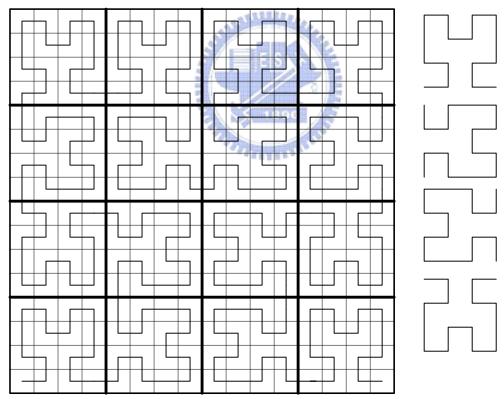

| FIG. 5.1 NINE SEARCH POSITIONS NUMBERED ACCORDING TO THEIR ACCESSING ORDER AS IN JM9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 75<br><b>0</b> 83<br>85             |

| FIG. 5.1 NINE SEARCH POSITIONS NUMBERED ACCORDING TO THEIR ACCESSING ORDER AS IN JM9.  FIG. 5.2 TESTING PATTERNS FOR THE PROPOSED ALGORITHM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 75<br><b>0</b> 83<br>85<br>86       |

| FIG. 5.1 NINE SEARCH POSITIONS NUMBERED ACCORDING TO THEIR ACCESSING ORDER AS IN JM9.0  FIG. 5.2 TESTING PATTERNS FOR THE PROPOSED ALGORITHM.  FIG. 5.3 SHOWS THE NINE SEARCHING POSITIONS, AND THE OVERLAPPED REGION BETWEEN THEM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75<br><b>0</b> 83<br>85<br>86<br>88 |

## List of Tables

| TABLE 2.1 BAB CODING MODES.                                                                                                | 16  |

|----------------------------------------------------------------------------------------------------------------------------|-----|

| TABLE 2.2 COMPUTATIONAL COMPLEXITY FOR MPEG-4 VIDEO ENCODING                                                               | 17  |

| TABLE 2.3 COMPLEXITY ANALYSIS OF BINARY MOTION ESTIMATION                                                                  | 20  |

| TABLE 2.4 16-CLASSES CLASSIFICATION, SHOWING THE NUMBER OF "1" IN EACH CLASS, AND THE                                      |     |

| RANGE OF "1" IN EVERY BAB THAT MATCHES WITH EACH CLASS                                                                     | 26  |

| TABLE 2.5 PERFORMANCE OF THE PROPOSED ALGORITHM AND THE FULL SEARCH METHOD WHEN                                            |     |

| SEARCH WINDOW IS ±16 AND 255 CLASSES WITHOUT OVERLAPPING.                                                                  | 27  |

| TABLE 2.6 PERFORMANCE OF THE PROPOSED ALGORITHM AND THE FULL SEARCH METHOD WHEN                                            |     |

| SEARCH WINDOW IS ±16 AND 255 CLASSES WITH 6 CLASSES OVERLAPPING                                                            | 28  |

| TABLE 2.7 COMPARISON BETWEEN DIFFERENT CLASSES.                                                                            | 28  |

| TABLE 2.8 RESULTS FOR DIVIDING CLASSES ACCORDING TO THE PROBABILITY OF CONTAINER_2 TEST                                    |     |

| SEQUENCE.                                                                                                                  | 29  |

| E E S A                                                                                                                    |     |

| TABLE 2.9 HARDWARE SIMULATION RESULTS FOR DIFFERENT CLASSES OVERLAPPING                                                    | 36  |

| TABLE 2.10 CHG_SP FOR VARIOUS SEARCH ALGORITHMS RELATIVE TO THE FULL SEARCH                                                |     |

| ALGORITHM.                                                                                                                 | 37  |

| TABLE 2.11 AVERAGE BIT-RATE FOR VARIOUS SEARCH ALGORITHMS. ALL ARE RELATIVE TO THE FU                                      | LL  |

| SEARCH ALGORITHM.                                                                                                          | 37  |

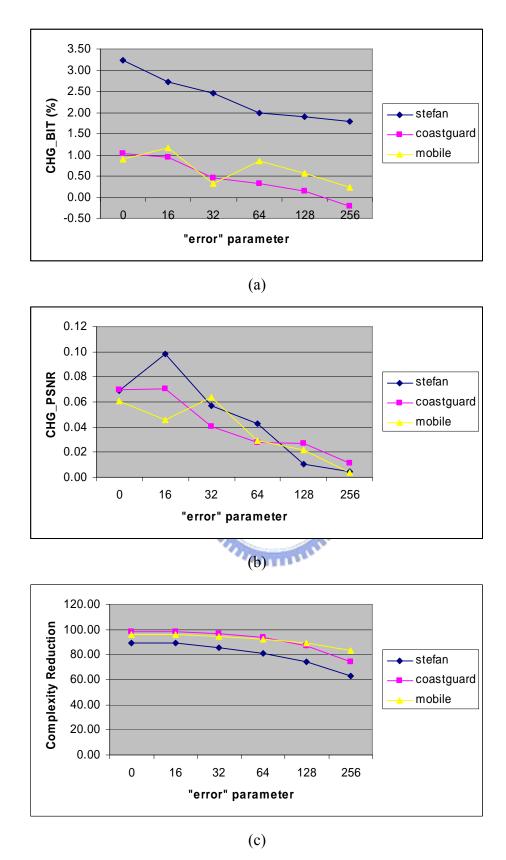

| Table 3.1 Experimental results for the proposed method with $Q_{\rm p}$ = 16                                               | 50  |

| Table 3.2 Experimental results for MPEG-4 with Spiral scan pattern, $Q_{\scriptscriptstyle P} = 16, {\rm and}  4 {\rm mv}$ |     |

| ENABLED.                                                                                                                   | 52  |

| Table 3.3 Experimental results for H.264 with spriral scan pattern, $Q_{\mbox{\tiny P}}$ = 28, ±32 SR , and                | D   |

| RDO disabled.                                                                                                              | 52  |

| TABLE 3.4 COMPARISON FOR DIFFERENT ALGORITHMS                                                                              | 53  |

| Table 3.5 The results of applying the hardware (H/W) conditions to JM9.0, $Q_P = 28, \pm 32$ S                             | SR, |

| AND RDO DISABLED                                                                                                           | 55  |

| TABLE 3.6 THE EFFECT OF DISABLING TERMINATION AFTER CERTAIN NUMBER OF LINES COMPARED                                       | то  |

| THE HARDWARE SIMULATION RESULTS.                                                                                           | 55  |

| TABLE 3.7 MODES GENERATED EVERY 4 CLOCK CYCLES                                                                             | 59  |

| * THE LABELS ARE AS INDICATED IN FIG. 3.3 (A)                                                |

|----------------------------------------------------------------------------------------------|

| TABLE 3.8 CLOCK CYCLES CONSUMED TO FINISH 16x16 SEARCH WINDOW FOR 50 FRAMES                  |

| TABLE 3.9 COMPARISON OF SOME VBSME CORE                                                      |

| TABLE 4.1 REDUNDANCY ACCESS COUNT AND BUFFER SIZE NEEDED BY EACH REUSE LEVEL                 |

| TABLE 4.1 NUMBER OF ACCESS AND SEARCH RANGE BUFFER SIZE FOR DIFFERENT NUMBER OF              |

| CURRENT BLOCKS. 68                                                                           |

| Table 4.2 Comparisons for CIF format, search range $\pm 16$ and using 4 PE. PE is assumed to |

| BE 1-D ARRAY                                                                                 |

| TABLE 4.3 MEMORY ACCESS CYCLES FOR DIFFERENT NUMBER OF CURRENT BLOCKS IN THE 2-D ARRAY       |

| CASE                                                                                         |

| TABLE 4.4 TIMING AND DATA ACCESSED FROM DIFFERENT MEMORY MODULES FOR EVERY PE76              |

| TABLE 4.5 COMPARISON BETWEEN OUR SCHEME AND OTHERS FOR 352×288 CIF FORMAT, SEARCH            |

| RANGE ±16 AND USING 4 CURRENT BLOCKS, WHERE N IS ASSUMED TO BE 16                            |

| TABLE 5.1 PSNR, ENCODED BIT STREAM AND COMPLEXITY REDUCTION FOR THE PROPOSED                 |

| ALGORITHM. 84                                                                                |

#### **Abstract**

Motion estimation is one of key part in modern video standards like MPEG-4 and H.264 to remove the temporal redundancy between video frames. However, it is also computational intensive and memory intensive. Thus, in this dissertation, we propose two designs, binary motion estimation and variable block size motion estimation, to reduce the computational load, and one vertical data reuse scheme to minimize the memory access.

The first work supports the binary motion estimation for shape coding adopted by MPEG-4. In binary motion estimation, its processing is at the bit level and thus is not suitable for general purpose processors due to their word-level processing capability. Thus, we propose a fast algorithm and its architecture that takes advantages of this bit level (binary level). With the count of bits in a block, the proposed algorithm classifies and tests every candidate search position and then skips those unlikely to be a match. The proposed algorithm can adaptively overlap matching between different classes to get more accurate motion vector or more skipping ratio. The proposed algorithm achieves a saving in computational complexity ranging from 96.69% to 99.71% comes with the expense of increasing the shape encoded bits by 0.7% to 12.8%. Due to the simplicity and the regularity of the algorithm, the proposed hardware is also regular and needs only 11582 gate count.

The second work supports the variable block size motion estimation. Variable block size limits the efficiency of early termination, but the algorithm shows good performance in this field. This design uses the early termination that adaptively changes its threshold to fit the variable block size and achieve early skipping. Different variables can be tuned by the algorithm to compromise between the high skipping ratio and the accurate motion vector. The proposed algorithm outperforms other similar algorithms with a complexity reduction of 78% and 51% for MPEG-4 and H.264 respectively. The hardware implementation of the algorithm can process one MB in 16 clock cycles, and completes a 16x16 search window in 4096 clock cycle without any termination process and an average 1032 clock cycles with termination process. The hardware uses only 16 registers and 31 adders and gate count of 16k.

Finally, the third work reduces the huge memory access by vertical processing adjacent current macroblocks. Vertical processing can achieve the same speed up of the horizontal processing but lower memory access especially for large search window. A design is introduced to demonstrate the efficiency of the vertical processing compared to horizontal processing using the same number of processing elements. This simple and regular design can be easily extended to any number of PE without extra cost to the control circuit or any change in the data flow. The required data bandwidth is reduced by 60.9% with four processing elements and 61k gate count when compared to the previous designs.

#### Introduction

#### 1.1 Overview of Video Coding

The rapid development of digital technology has brought the video to a new era. In the past, people used tapes and televisions, but today the digital video can be found everywhere in our daily life. The VCD and DVD have replaced traditional tapes owing the ease of preservation. As the computer networks become more and more popular, the video over network tends to be more and more important. The handheld devices probably will be one of the terminals for video broadcast in the near future.

The increasing demand to incorporate video data into telecommunications services, the corporate environment, the entertainment industry, and even at home has made digital video technology a necessity. A problem, however, is that still image and digital video data rates are very large, typically in the range of 150Mbits/sec. Data rates of this magnitude would consume a lot of the bandwidth, storage and computing resources in the typical personal computer. Therefore, Video Compression standards have been developed to eliminate picture redundancy, allowing video information to be transmitted and stored in a compact and efficient manner. Although the applications on video changes so rapidly, the bases of the video technology are still the same:

#### 1. Insensitivity to high frequency of human eye.

The human eye is lazy to the high frequency part of the signal. Thus, both compression of still images and video improves its compression ratio by largely discarding the high-frequency components.

#### 2. Spatial redundancy.

In a small area of the current coded frame, the pattern is usually lack of large variation. That is the pattern of the neighbors can be good prediction of currently coded area.

#### 3. Temporal redundancy.

The characteristics of video include the temporal similarity, which means almost no great changes exist between two close frames. By eliminating the temporal redundancy from the current coded frame, the data rate can be largely lowered. In fact, the applying of video coding tools to exploits the temporal redundancy is the major improvement in compression ratio.

Thus, most of the video coding standards, including IYU H.261, H.263, H.264, MPEG, MPEG-2, and MPEG-4, are established on similar fundamentals, such as block-based coding, DCT transform, motion estimation/compensation, and prediction of data and so on.

### 1.2 Cores of Digital Video Technology

Compression is the most important core technique of video applications at present. Video standards evolution starts from H.261, MPEG-1, MPEG-2/H.262, H.263, H.263+, H.263++, MPEG-4, H.26L, to the latest H.264/AVC. H.264/AVC outperforms its previous standards in compression performance due to many new prediction and entropy coding tools, such as, multiple reference frames, variable block sizes, intra prediction, context-based adaptive variable length coding, context-based adaptive binary arithmetic coding, deblocking and rate distortion optimized mode decision. This high performance comes with the expense of high computational complexity by one order.

The toughest challenge of video compression is real-time processing. For HDTV applications, several tera-operations/instructions per second (TOPS) of computing power and several tera-bytes per seconds (TB/s) of memory access are demanded. The required resources of real-time coding are far beyond the capabilities of today's general purpose processors. For mobile applications with much smaller image sizes, power

consumption is the most critical issue. If a processor-based software implementation is adopted, the operating frequency of the processor should be as high as hundreds of MHz, which will violate the strict power constraints. Although the complexity of mobile applications is much lower than that of HDTV applications, real-time compression is still too heavy burden for processors. Hence, application specific integrated circuits (ASICs) play the key role of video applications. Hardware-oriented algorithms and efficient VLSI architectures are urgently needed. Among all the video coding standards, block matching estimation is always the processing bottleneck. More than half, sometimes even up to 90% of computing power and memory access are dominated by motion estimation. Therefore we should pay attention to the motion estimation when developing a video coding system.

In the following two subsections, a brief introduction of two compression standards, MPEG-4 and H.264, showing their main features, basic functional blocks and the distinguished tools implemented in each of them.

#### 1.2.1 MPEG-4 Overview

MPEG-4 is an ISO standard (ISO/IEC international standard 14496) developed by the Moving Picture Experts Group (MPEG). It defines the deployment of non-proprietary multimedia content independently of platform or transmission medium. It has relied on and taken from a number of existing technologies while at the same time adding a number of innovative tools and concepts.

The MPEG-4 visual standard consists of a set of tools (as shown in Fig. 1.1) that enable applications by supporting several classes of functionalities. The most important features covered by MPEG-4 standard can be clustered in three categories and summarized as follows:

1. *Compression efficiency:* Compression efficiency has been the leading principle for MPEG-1 and MPEG-2 and in itself has enabled applications such as Digital TV and DVD. Improved coding efficiency and coding of multiple concurrent data streams will increase acceptance of applications based on the MPEG-4 standard.

- 2. Content-based interactivity: Coding and representing video objects rather than video frames enables content-based applications. It is one of the most important novelties offered by MPEG-4. Based on efficient representation of objects, object manipulation, bit stream editing, and object-based scalability allow new levels of content interactivity.

- 3. *Universal access:* Robustness in error-prone environments allows MPEG-4 encoded content to be accessible over a wide range of media, such as mobile networks as well as wired connections. In addition, object-based temporal and spatial scalability allow the user to decide where to use sparse resources, which can be the available bandwidth, but also the computing capacity or power consumption.

To support some of these functionalities, MPEG-4 should provide the capability to represent arbitrarily shaped video objects. Each object can be encoded with deferent parameters, and at deferent qualities. The shape of a video object can be represented in MPEG-4 by a binary or a gray level (alpha) plane. The texture is coded separately from its shape. In the following, two main parts of MPEG-4 will be discussed which are related to the work presented later in the thesis: shape coding and texture motion estimation.

Fig. 1.1 General structure of MPEG-4 VOP encoder

#### 1.2.1.1 Shape coding

The shape coding scheme also relies on motion estimation to compress the shape information even further. In MPEG-4 visual standard, two kinds of shape information are considered as inherent characteristics of a video object. These are referred to as binary and gray scale shape information. By binary shape information, one means label information that defines which portions (pixels) of the support of the object belong to the video object at a given time. The binary shape information is most commonly represented as a matrix with the same size as that of the bounding box of a Video Object Plan (VOP). Every element of the matrix can take one of the two possible values depending on whether the pixel is inside or outside the video object. Gray scale shape is a generalization of the concept of binary shape providing a possibility to represent transparent objects, and reduce aliasing effects. In gray scale, the shape information is represented by 8 bits, instead of a binary value.