# 國立交通大學電子工程學系電子研究所博士論文

新穎雙功函數金屬閘極製程技術之研發

Investigation of Novel Dual Work Function Metal

Gate Technologies

研究生: 李宗霖

指導教授: 張俊彦 博士

中華民國 九十五 年 六 月

# 新穎雙功函數金屬閘極製程技術之研發

# Investigation of Novel Dual Work Function Metal Gate Technologies

研究生:李宗霖 Student:Tzung-Lin Li

指導教授:張俊彦 博士 Advisor: Dr. Chun-Yen Chang

### 國立交通大學

電子工程學系 電子研究所

Submitted to Department of Electronics Engineering and

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of

Doctor of Philosophy

in

Electronics Engineering

June 2006

Hsinchu, Taiwan, Republic of China

中華民國九十五年六月

# 新穎雙功函數金屬閘極製程技術之研發

研究生:李宗霖 指導教授:張俊彦 博士

國立交通大學電子工程學系電子研究所博士論文

### 摘要

本論文的研究方向,主要為研發新穎之雙功函數金屬閘極製程技術。元件尺寸的微縮雖可以改善元件之操作特性,然而傳統的多晶矽閘極本質上的缺點,對元件特性的負面影響也將更加顯著。另一方面,隨著元件尺寸的微縮,閘極氧化層的厚度變薄也將導致閘極漏電流大幅上揚,為了有效降低閘極漏電流,近年來以高介電材質取代傳統二氧化矽的相關研究也被投注大量心力。然而多晶矽閘極搭配高介電材質,已被發現會有熱穩定性不佳的缺點,同時介面也存在著費米能階夾止效應,因此,金屬閘極製程的研發不僅可以克服上述多晶矽的本質缺點,對於與高介電材質間的熱穩定性、費米能階夾止效應等方面,也提供了可能的解答。此外,金屬閘極的低阻抗,對於元件的高頻操作特性亦有改善之效。

對於金屬閘極的製程技術與材料選擇有以下幾項基本要求,首先 它必須能夠在閘極介電層介面提供正確適當的功函數值,同時與閘極 介電層間需有良好的熱穩定性以確保在元件製程中可以保有穩定的特性,另外也必須可相容、整合於傳統的製程技術中。本論文中,我們提出了兩種新穎的雙功函數金屬閘極製程技術,一是利用金屬混合以形成雙元合金,二是以金屬矽化反應以形成金屬矽化物。應用了此等金屬功函數調變法後,早期被提出的雙功函數金屬閘極製程技術中,閘極介電層因金屬蝕刻導致厚度的不均勻性以及可靠度退化的現象將可被避免。在雙元合金的實驗中,我們先以同時性濺鍍的物理沈積法沈積鉛鉬雙元合金,藉以觀察其電性、化性。藉由改變各靶材的濺鍍功率可調變鉛鉬合金的組成,進而得到近乎線性且連續的功函數調變,其調變範圍可介於 3.93eV (純金屬鉛)與 4.93eV (純金屬鉬)之間。我們也發現鉛鉬合金在二氧化矽上的熱穩定性,雖然會隨著鉛含量的增加而變差,但至少都可達 400℃以上。

基於製程整合上的考量,我們進一步驗證了沈積鈴、鉬兩金屬層並經熱處理使其混合的方式以形成鉛鉬雙元合金,並藉此提出一雙功函數金屬閘極製程技術。由於達到完全的金屬混合以形成雙元合金所需的熱預算取決於兩金屬層的厚度總和 T<sub>M</sub> (T<sub>M</sub> = T<sub>Hf</sub> + T<sub>Mo</sub>),我們提出了一個概念:根據金屬沈積後製程所需經過的總熱處理預算,選用適當的金屬層總厚度,則可以避免掉對金屬閘極材質本身熱穩定性的要求。此外,我們也驗證了藉由改變鈴、鉬兩金屬層的厚度比例 T<sub>R</sub> (T<sub>R</sub> = T<sub>Hf</sub> / T<sub>Mo</sub>),可以精確地控制所形成的雙元合金的組成以及功函數值。上述的技術對於具有先進結構的元件諸如:FinFET、UTB-MOSFET 將相當具有吸引力,因為先進元件通常具有較薄的基板厚度,且基板的雜質摻雜濃度對元件臨界電壓的調變效果也大幅降低。此外,先進元件所需的閘極功函數值會隨基板厚度與閘極數目的

不同而有所差異,因此準確的功函數調變將會益形重要。

論文中所提出的第二種雙功函數金屬閘極製程技術則是應用了金屬的矽化反應。我們選擇在具有良好熱穩定性的金屬組上沈積了適當厚度的非晶矽,再藉由熱處理過程使其經由矽化反應生成矽化鉬,並藉此提出使用金屬鉬與矽化鉬作為閘極組合的雙功函數金屬閘極製程技術。在二氧化矽上,金屬鉬一矽化鉬之閘極組合所提供的功函數組合可適用於具有先進結構的元件,且矽化鉬亦被驗證具有良好的熱穩定性。另外我們發現在矽化反應之前,如果於非晶矽中佈植摻雜入雜質砷,則可進一步降低所生成矽化鉬的功函數值,進而拉大金屬鉬一矽化鉬之間的功函數差,將所提出的雙功函數金屬閘極製程技術之應用範圍擴大到傳統的本體元件。值得一提的是,此提出的新穎製程技術是利用金屬本身搭配本質或 n 型金屬矽化物來提供功函數差,有別於近期被廣泛研究的FUSI技術中利用 p 型與 n 型金屬矽化物來提供功函數差,有別於近期被廣泛研究的FUSI技術中利用 p 型與 n 型金屬矽化物來提供功函數差,有別於近期被廣泛研究的FUSI技術中利用 p 型與 n 型金屬矽化物來提供功函數差。由於避免了 p 型金屬矽化物的使用,因此可以消除硼穿透可能帶來的缺點。

我們同時也驗證了金屬鉬一矽化鉬之閘極組合在高介電材質上的特性。我們發現金屬鉬與矽化鉬在二氧化鉿的高介電閘極介電層上所得到的功函數值都分別略低於在二氧化矽上所得到的值,然而兩者間的功函數差值卻可維持。同時,矽化反應之前,於非晶矽中雜質砷的佈植仍然可以有效降低所形成矽化鉬在二氧化鉿上的功函數值,克服了FUSI技術在二氧化鉿高介電閘極介電層上,p型與n型金屬矽化物幾乎無功函數差的致命缺點。相較於FUSI技術,雖然同樣運用到金屬的矽化反應,然而我們的實驗結果卻顯示出費米能階夾止效應被

有效壓抑。對此我們猜測其原因是:我們所提出的金屬鉬-矽化鉬雙 功函數金屬閘極製程技術,其結構有效避免了非晶矽層在沈積過程以 及矽化反應之前與高介電閘極介電層的直接接觸。

**Investigation of Novel Dual Work Function Metal**

**Gate Technologies**

Student: Tzung-Lin Li

Advisor: Dr. Chun-Yen Chang

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

Abstract

Two novel dual work function metal gate technologies are investigated and

proposed. With the down-scaling of the device geometry for performance

improvement, inherent drawbacks of conventional polysilicon gate electrodes lead to

increasingly significant negative influence. In addition, the high-k gate dielectrics

have been introduced to replace the conventional silicon dioxide. Consequently, under

the same effective oxide thickness, the gate leakage current can be effectively reduced.

Unfortunately, polysilicon gates have been reported to be thermodynamically unstable

on many high-k materials and lead to Fermi-level pinning effect at the

polysilicon/high-k interface. Therefore, metal gates are expected to provide a turning

point in possessing a better thermal stability and a retardation of the Fermi-level

pinning effect. In addition, metal gates can possess a lower gate resistance and

enhance the device performance at higher frequency.

The basic requirements for a novel metal gate technology include providing

v

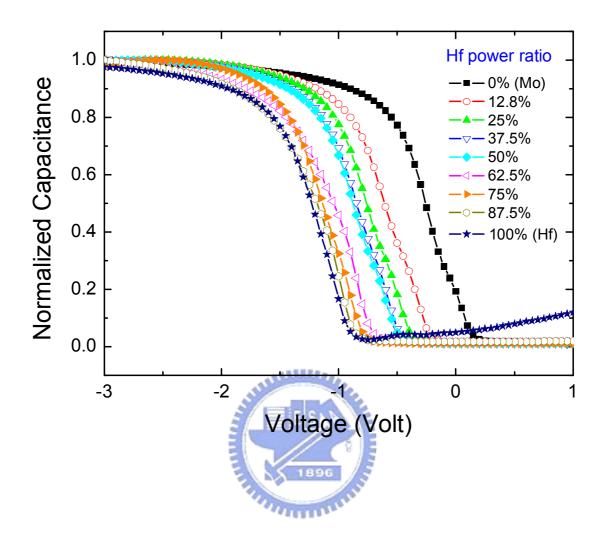

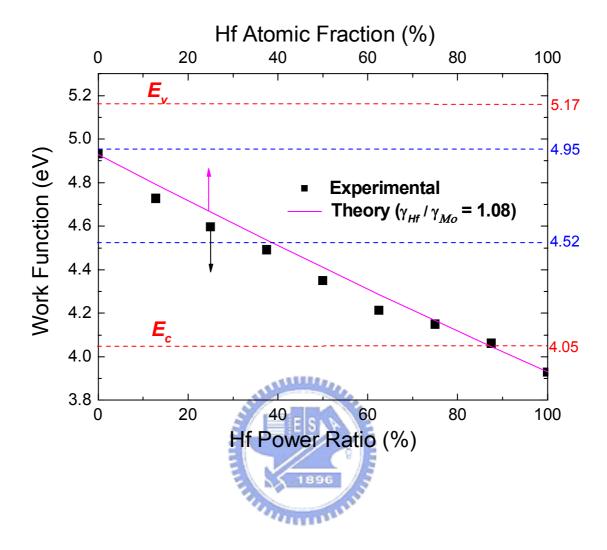

suitable work function values at the gate dielectric interface, the good enough thermal stability with the underlying gate dielectrics and a compatible device integration process. Two novel metal gate technologies are proposed in this dissertation. One is based on the metal intermixing technique, and the other is based on the silicidation technique. We firstly investigate the electrical and chemical characteristics of Hf-Mo binary alloys deposited by co-sputtering technique. A continuous and almost linear work function adjustment using  $Hf_xMo_{(1-x)}$  is demonstrated for the first time. The work function value of Hf-Mo binary alloy ranges from 3.93eV ( $\Phi_m$  of pure Hf) to 4.93eV ( $\Phi_m$  of pure Mo) and depends on the sputtering power ratio of each target. The thermal stabilities of Hf-Mo binary alloy on  $SiO_2$  are found to degrade with the increase of Hf atomic fraction, but all of the Hf-Mo binary alloys possess thermal stabilities at least higher than  $400^{\circ}C$ . The Hf-Mo binary alloys can be appropriate for a gate-last  $SiO_2$  CMOS process.

The practicable integration of Hf-Mo binary alloys into the dual metal gate process is also proposed. Hf<sub>x</sub>Mo<sub>(1-x)</sub> formed by metal intermixing of the Hf/Mo stack is firstly evaluated, and a novel dual work function metal gate technology is then proposed and demonstrated. A precise control over the work function of the Hf-Mo binary alloy by adjusting the composite metal thickness ratio  $T_R$  ( $T_R = T_{Hf} / T_{Mo}$ ) is demonstrated. Besides, the required thermal budget for a complete metal intermixing is demonstrated to depend on the total metal thickness,  $T_M$  ( $T_M = T_{Hf} + T_{Mo}$ ). Therefore, one can be allowed to get around the thermal stability issue by using an appropriate  $T_M$  value. This technique is not only attractive but especially important for devices with advanced transistor structures, such as FinFET and/or UTB-MOSFET devices, since the substrate doping modulation may not be an efficient way to adjust the threshold voltages of devices with advanced transistor structures.

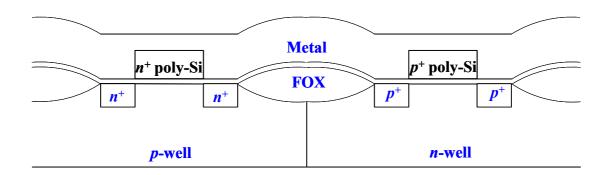

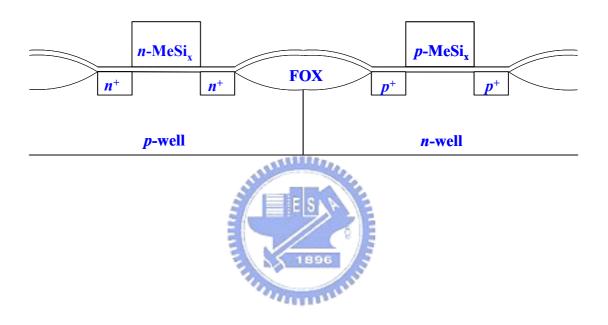

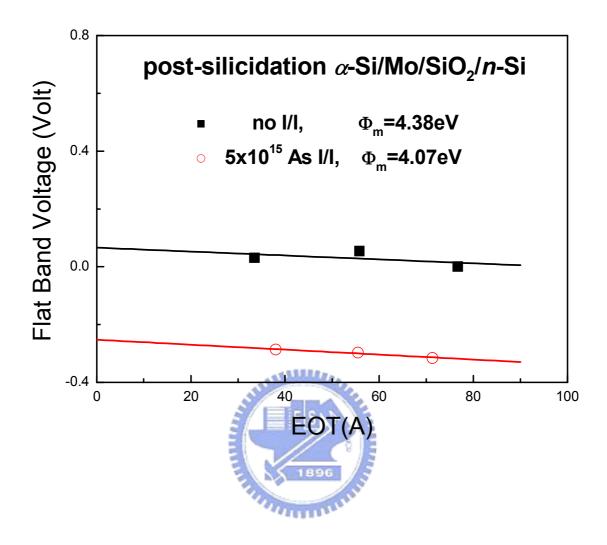

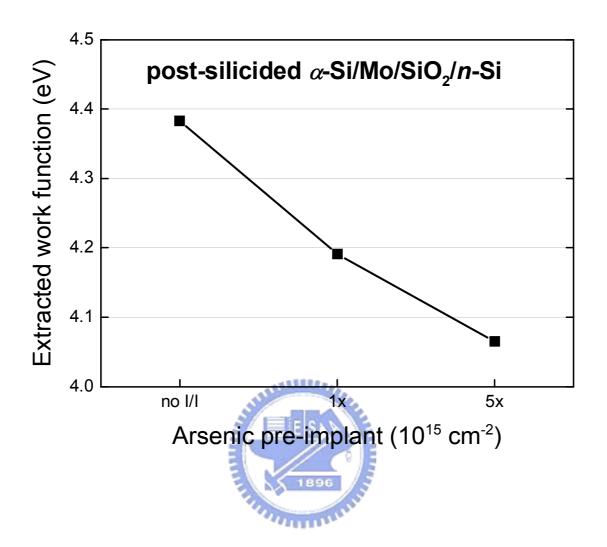

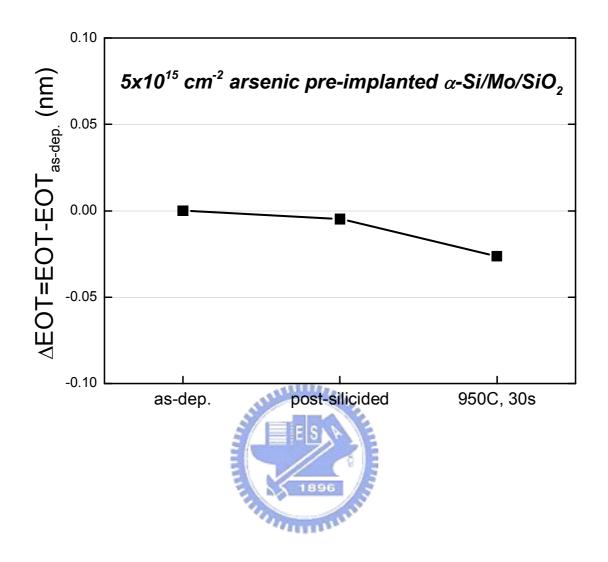

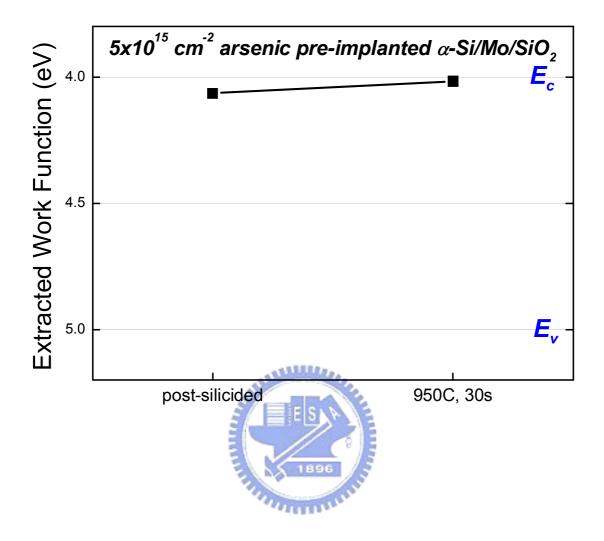

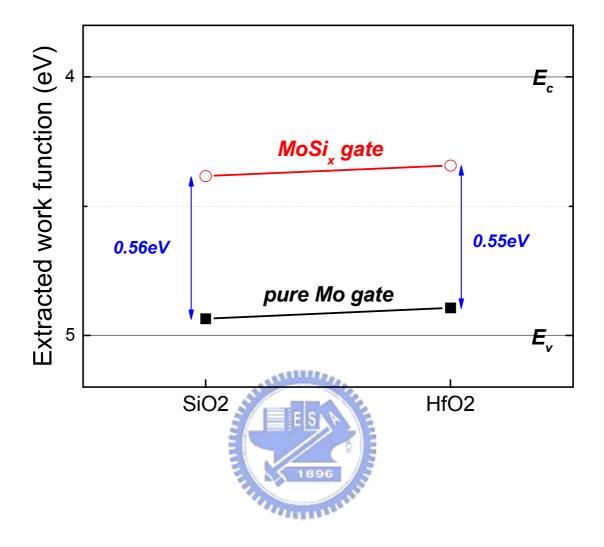

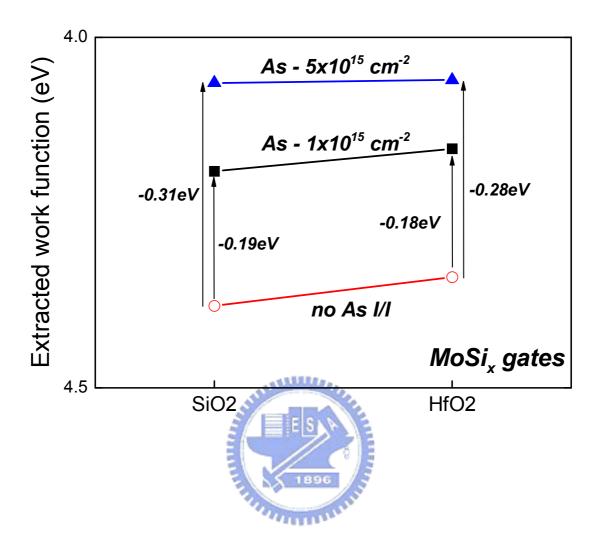

The other novel dual metal gate technology proposed in this dissertation is based on using the silicidation technique. The  $\alpha$ -Si/Mo stack was fabricated and thermal annealed to form MoSi<sub>x</sub>. The work function of MoSi<sub>x</sub> is found to be lower than that of Mo, and the thermal stability of MoSi<sub>x</sub> is evaluated to be higher than 950°C. Combining MoSi<sub>x</sub> with the pure Mo gate, a practical integration into the dual metal gate technology is then proposed. On the SiO<sub>2</sub> gate dielectric, the combination of Mo-MoSi<sub>x</sub> possesses a work function shift appropriate for devices with advanced transistor structures. Furthermore, the additional arsenic pre-implantation into the  $\alpha$ -Si layer prior to the silicidation annealing is demonstrated to effectively lower the work function of MoSi<sub>x</sub>. Consequently, the application of the proposed novel dual metal gate technology can be expanded to the conventional bulk devices. Besides, the new structure along with the ruling out of p-type metal silicide is also demonstrated to eliminate the boron penetration problem encountered with the reported FUSI method.

1000

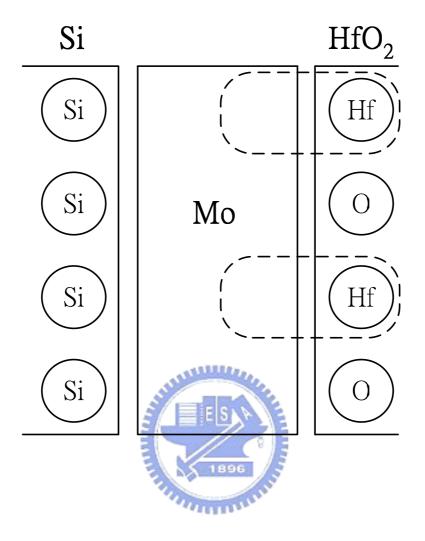

On high-k gate dielectric materials, the maintenance of the considerable work function shift is also demonstrated. The extracted  $\Phi_m$  value of pure Mo or MoSi<sub>2</sub> gate on HfO<sub>2</sub> is slightly lower than that on SiO<sub>2</sub>, but the  $\Phi_m$  difference between Mo and MoSi<sub>x</sub> is almost the same regardless of the underlying gate dielectric materials. The arsenic pre-implantation still has effect upon the modulation of  $\Phi_m$  of metal silicide on HfO<sub>2</sub>, even though the modulation range is a little smaller than that on SiO<sub>2</sub>. The influence of Fermi-level pinning effect, which has been reported to be responsible for the high threshold voltages of FUSI gated devices with the high-k gate dielectric, is also discussed. The Fermi-level pinning effect seems to be retarded in the proposed Mo-MoSi<sub>x</sub> dual metal gate technology. We speculate that the improvement may be attributed to the separation of silicon layer from the high-k gate dielectrics.

### 誌 謝

論文完成的同時,心中實是百感交集,感恩之心不曾少過。首先, 我要感謝一直支持、鼓勵我的指導教授 張俊彥校長,自碩士班起就 接受老師的研究指導,轉眼已有八年之久。老師除了在專業學術領域 上的創新遠見令我受益無窮外,不忮不求的風範也讓身為學生的我深 表欽佩,科技與人文並重的學風、國際級學者的氣度,也對我產生潛 移默化的影響,能有幸跟隨老師研究,我想是我人生中最重要的轉捩 點。

同時要感謝台灣積體電路製造公司的 胡正明教授。胡教授在半導體領域上的成就與造詣亦是國際馳名的,很感謝胡教授在研究方向上所提供的建議、支援與討論,讓碩士班時研究射頻電路設計,而在博士班轉換研究領域的我能不感到徬徨。另外也要感謝台灣積體電路製造公司的 王志豪博士,感謝他在繁忙的工作之餘,仍能全力提供我所需的幫助與支持。

另外謝謝我的直屬學弟:胡嘉欣、何武陵、陳弘斌、謝彥廷,很 高興有機會與各位合作研究,教學相長的過程也讓我獲益良多,希望 各位都能繼續努力,在自己的工作領域或研究成果上能有所突破。

當然還要感謝快速電子實驗室的所有成員,有你們的陪伴與相互 扶持,讓我的研究生活增添了許多的歡樂與色彩。尤其是陳經緯博士、彭辭修博士、黃啟環學弟,在我轉換研究領域時,他們的幫助與 扶持,讓我走得更為平順。也感謝吳師道博士、彭杜仁博士、楊宗熺 博士、以及各位學弟妹們:羅文政、陳漢譽、黃聖懿、涂峻豪、胡心 卉、鄭兆欽、馮立偉、陳怡誠、陳緯仁、余昱穎、林哲弘、劉峻丞、 張哲榮、邵而康、沈詩國,還有許多已經畢業分飛的 418 成員、好友 陳舒薇、張瑋怡以及其他關心我的人,有你們的陪伴讓我的求學過程 更值得回憶。

八年前隻身來到新竹求學,如今謹將這份成果獻給我最愛的家人,感謝爸媽含辛茹苦的扶養、支持、鼓勵與諒解,讓我毫無後顧之憂得以順利完成博士論文;也感謝女友伊喬六年來在感情與生活上的相伴照顧、包容體諒,陪我度過生活中的悲喜、生命中的起伏。因為你們,我的人生變得更完美,成就也變得更有意義。

李宗霖 誌於 風城交大 2006

# **Contents**

| Abstract (Chinese) |                                                       | i    |

|--------------------|-------------------------------------------------------|------|

| Abstract (English) |                                                       |      |

| Acknowledgement    |                                                       |      |

| Contents           |                                                       |      |

| Table Captions     |                                                       | xiii |

| Figure             | Captions                                              | xiv  |

| Chapt              | ter 1 Introduction                                    |      |

| 1.1                | Evolution of Gate Electrode Candidates                | 1    |

| 1.2                | Basic Requirements for Metal Gates                    | 4    |

| 1.3                | Metal Work Function Extraction Technique              | 6    |

| 1.4                | Organization of the Thesis                            | 8    |

|                    | References                                            | 11   |

| Chapt              | ter 2 Investigation of $Hf_xMo_{(1-x)}$ Binary Alloys |      |

| 2.1                | Backgrounds and Motivation                            | 23   |

| 2.2                | Experiment                                            | 25   |

| 2.3                | Results and Discussion                                | 26   |

| 2.4                | Summary                                               | 29   |

|                    | References                                            | 30   |

|                    |                                                       |      |

# Chapter 3 Integratable Dual Metal Gate Technology Using Hf<sub>x</sub>Mo<sub>(1-x)</sub> Binary Alloys

| 3.1                      | Backgrounds and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46                           |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 3.2                      | Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47                           |

| 3.3                      | Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48                           |

| 3.4                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                           |

|                          | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52                           |

| Chapta                   | er 4 Novel Dual Metal Gate Technology Using Mo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Si <sub>x</sub> Films        |

| 4.1                      | Backgrounds and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 62                           |

| 4.2                      | Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 64                           |

| 4.3                      | Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66                           |

| 4.4                      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 70                           |

|                          | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                           |

| Chapte                   | 1896                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                              |

| Спири                    | er 5 Investigation of MoSi <sub>x</sub> Based Dual N<br>Technology on the High-k Gate Dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1etal Gate                   |

| 5.1                      | No. of the last of | <b>1etal Gate</b> 96         |

| ·                        | Technology on the High-k Gate Dielectric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                              |

| 5.1                      | Technology on the High-k Gate Dielectric  Backgrounds and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 96                           |

| 5.1<br>5.2               | Technology on the High-k Gate Dielectric  Backgrounds and Motivation  Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 96<br>99                     |

| 5.1<br>5.2<br>5.3        | Technology on the High-k Gate Dielectric  Backgrounds and Motivation  Experiment  Results and Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 96<br>99<br>99               |

| 5.1<br>5.2<br>5.3        | Technology on the High-k Gate Dielectric  Backgrounds and Motivation  Experiment  Results and Discussion  Summary  References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96<br>99<br>99<br>101<br>102 |

| 5.1<br>5.2<br>5.3<br>5.4 | Technology on the High-k Gate Dielectric  Backgrounds and Motivation  Experiment  Results and Discussion  Summary  References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 96<br>99<br>99<br>101<br>102 |

# Vita (Chinese)

# **Publication List**

# **Table Captions**

# Chapter 2

Table 2.1 Sample conditions and extracted  $\Phi_m$  of co-sputtering experiment. (alloy samples :  $400^{\circ}\mathbb{C}$ , 30s; control samples : as-deposited)

# Chapter 3

Table 3.1 Sample conditions and extracted  $\Phi_m$  of metal intermixing experiment. (700°C, 30s for sample 2-1 and 2-2; 600°C, 30s for samples 2-3 and 2-4)

# **Figure Captions**

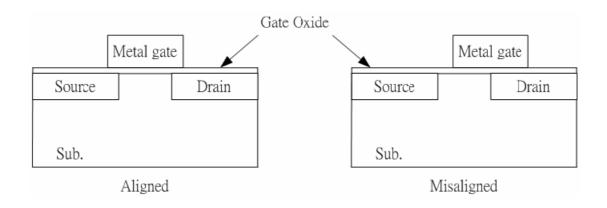

Illustration of gate misalignment.

# Chapter 1

Fig. 1.1

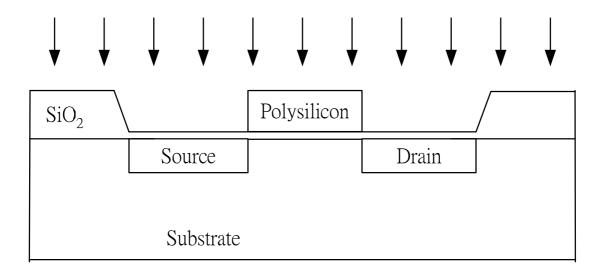

| Fig. 1.2  | Illustration of self-aligned process.                                       |

|-----------|-----------------------------------------------------------------------------|

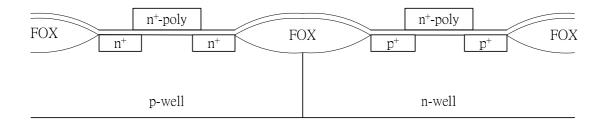

| Fig. 1.3  | Illustration of polysilicon gate technology using only $n^+$ -poly for both |

|           | <i>n</i> - and <i>p</i> -channel devices.                                   |

| Fig. 1.4  | Illustration of dual-doped polysilicon gate technology.                     |

| Fig. 1.5  | Illustration of the boron penetration.                                      |

| Fig. 1.6  | Illustration of the poly depletion effect.                                  |

| Chapter 2 | ESIN                                                                        |

| Fig. 2.1  | C-V curves of as-deposited co-sputtering samples. Wide-ranging flat         |

|           | band voltage shift can be observed.                                         |

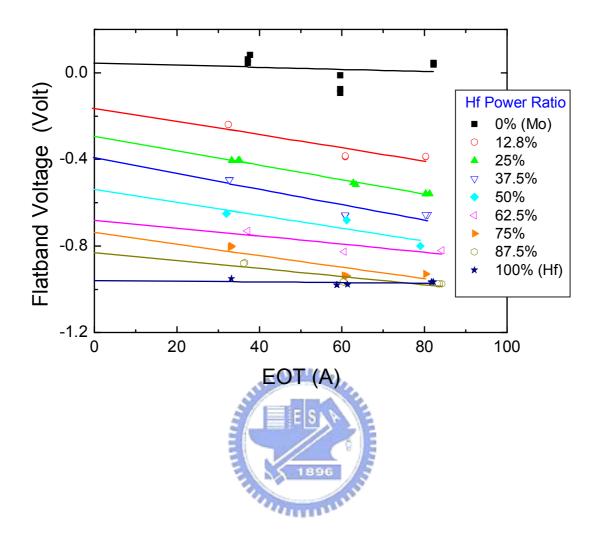

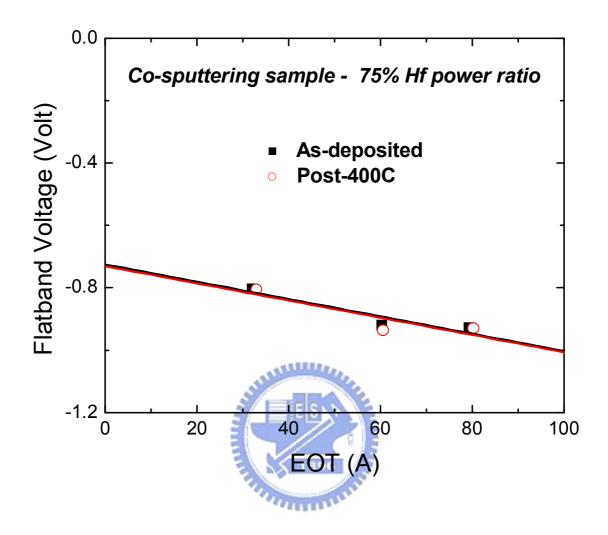

| Fig. 2.2  | All samples (Table I.) exhibited linear behavior in $V_{FB}$ vs. EOT curves |

|           | from which work function of each alloy could be extracted. (alloy           |

|           | samples: 400°C, 30s; control samples: as-deposited)                         |

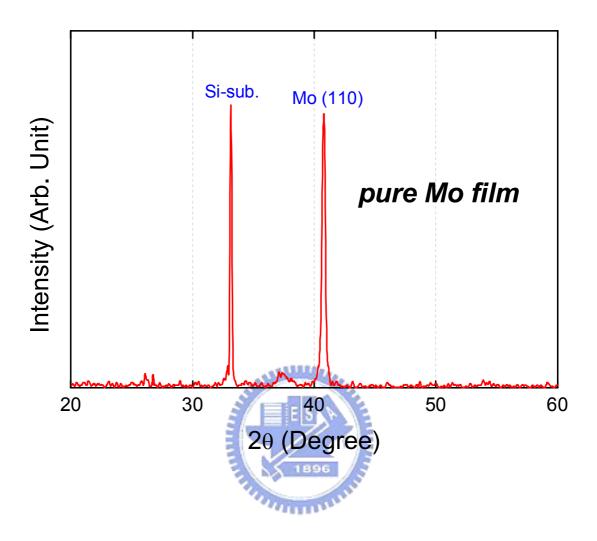

| Fig. 2.3  | The as-deposited pure Mo film is found to have (110) orientation.           |

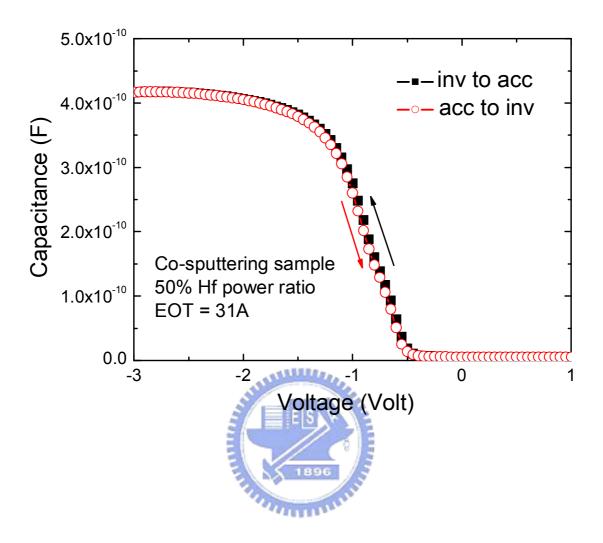

| Fig. 2.4  | Process quality was demonstrated, since the 50% Hf power ratio              |

|           | sample suffering maximum power summation during metal deposition            |

|           | still exhibited negligible hysteresis.                                      |

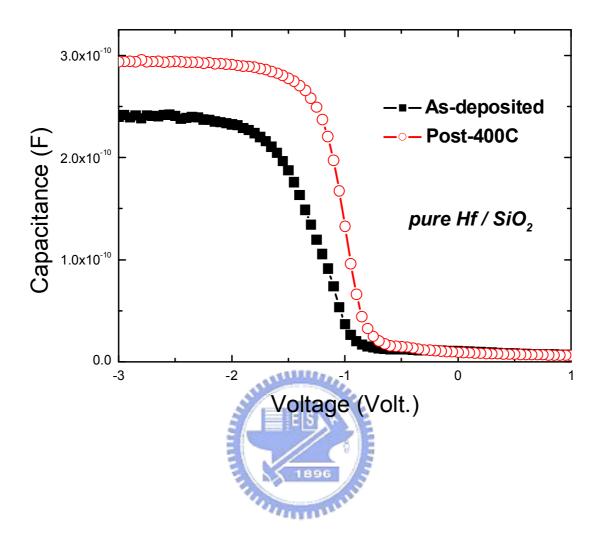

| Fig. 2.5  | C-V curve of post-400 °C annealing Hf gated capacitor shows                 |

|           | noticeable EOT variation and flatband voltage shift.                        |

| Fig. 2.6  | Post-400°C annealing co-sputtering sample shows negligible work             |

function variation.

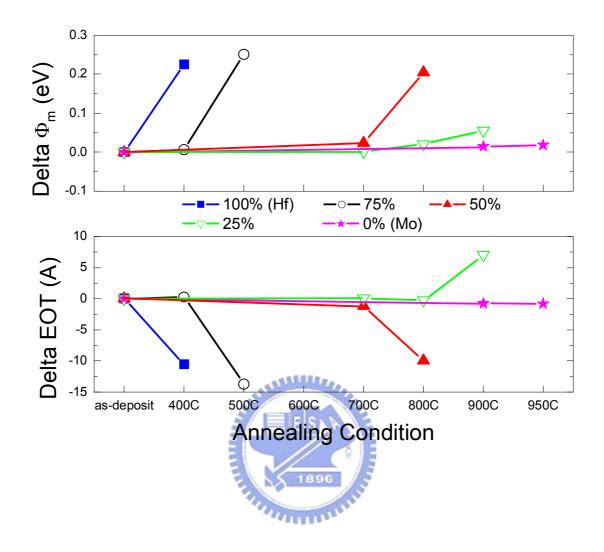

- Fig. 2.7 The dependence of  $\Phi_m$  and EOT variation on annealing temperature show that the thermal stability of alloy samples can be at least higher than  $400^{\circ}\text{C}$ .

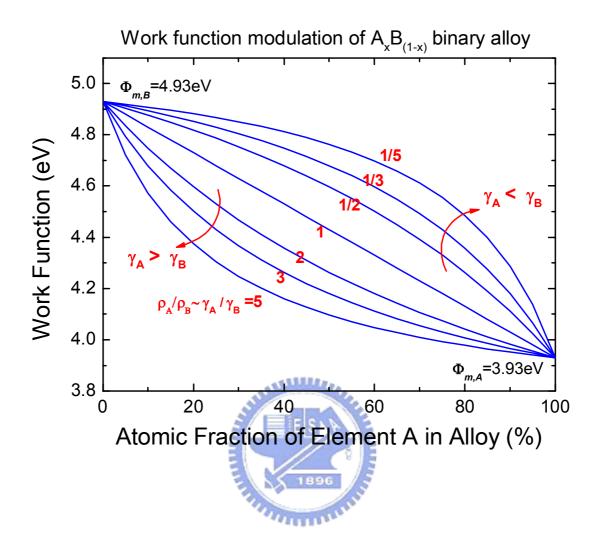

- Fig. 2.8 Calculated work function value versus atomic fraction in binary alloy as a function of  $\gamma$  ratio. Metals with similar  $\gamma$  (Sommerfeld factor) will lead to a linear work function modulation which is a compromise between modulation efficiency and immunity to process variation. ( $\Phi_{m.A}$  and  $\Phi_{m.B}$  are set to be 3.93 and 4.93eV for convenience)

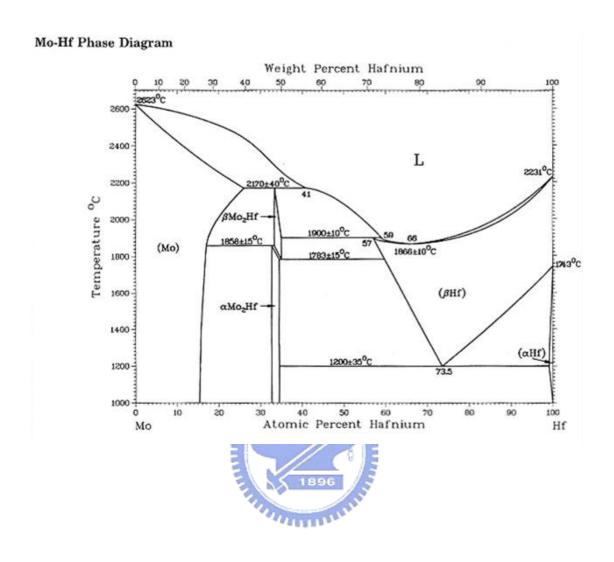

- Fig. 2.9 The phase diagram of Mo-Hf system.

- Fig. 2.10 Comparison between experimental (Table I.) and theoretical work function values. A slightly deviation in lower Hf power ratio regime may be attributed to different sputtering rate between Hf and Mo. ( $\gamma_{Hf}$  = 2.16,  $\gamma_{Mo}$  = 2.0 are used for calculation)

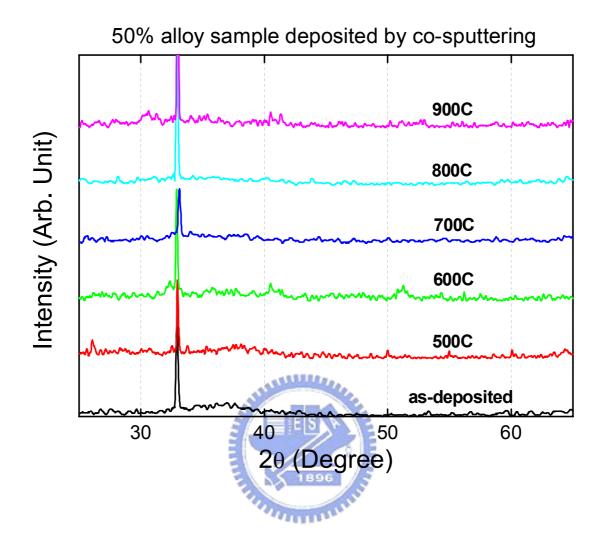

- Fig. 2.11 XRD spectra of 50% Hf power ratio co-sputtering sample exhibited an amorphous film structure and only the *c*-Si was featuring.

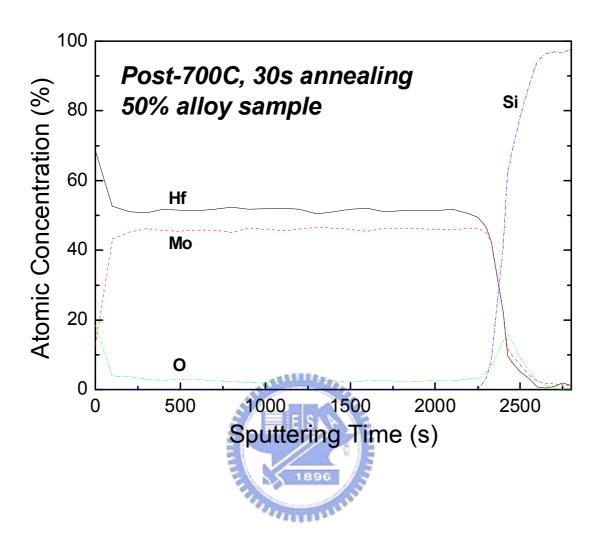

- Fig. 2.12 AES profile of post-annealing 50% Hf power ratio co-sputtering sample. A uniform composition and abrupt interface can be observed.

### Chapter 3

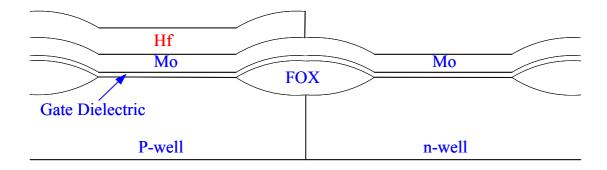

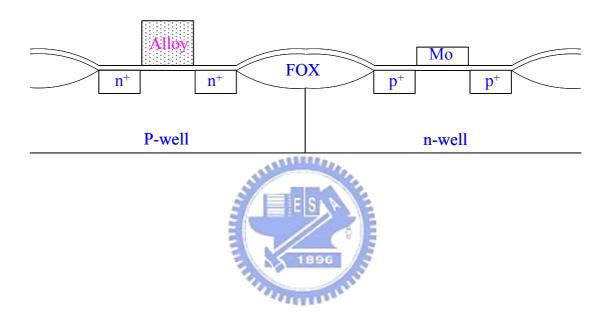

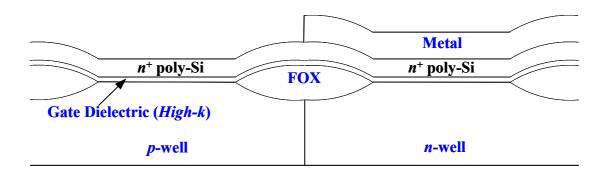

- Fig. 3.1 Schematics of dual metal gate technology using metal and alloy formed by metal intermixing. Metals need not to be etched away from the dielectric surface so the uniformity and integrity of gate dielectric can be preserved.

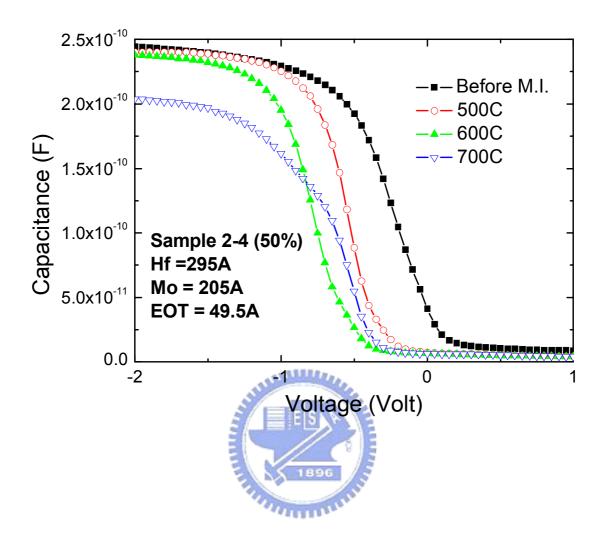

- Fig. 3.2 C-V curves of Hf-295Å/Mo-205Å/SiO<sub>2</sub> capacitor before and after

- thermal annealing. The optimal annealing temperature for this sample was found to be  $600^{\circ}\text{C}$  .

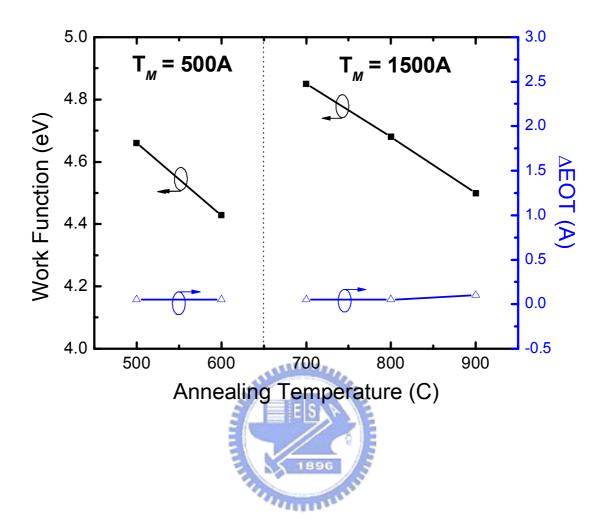

- Fig. 3.3 The increase of total metal thickness under the same composite metal thickness ratio can effectively rise the optimal annealing temperature.

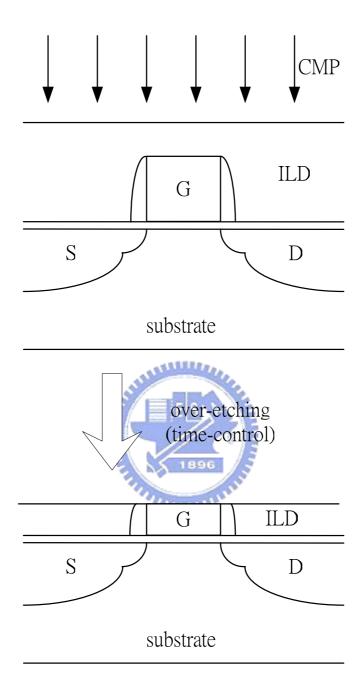

- Fig. 3.4 Illustration of thinning down of the gate electrode using ILD CMP.

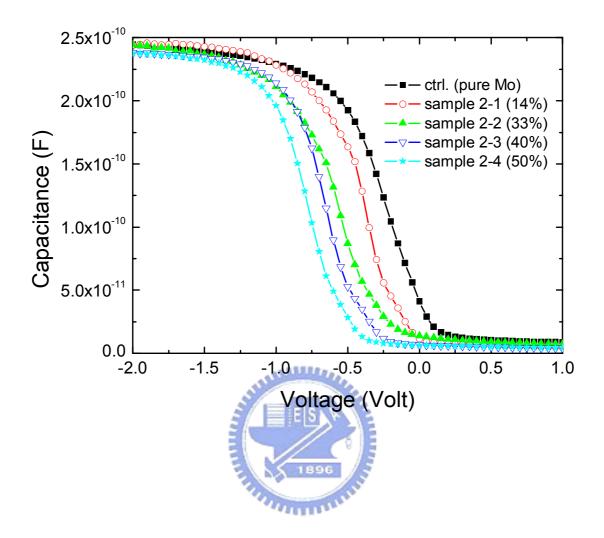

- Fig. 3.5 C-V curves of post-annealing Hf/Mo/SiO<sub>2</sub> capacitors as a function of Hf atomic fraction.

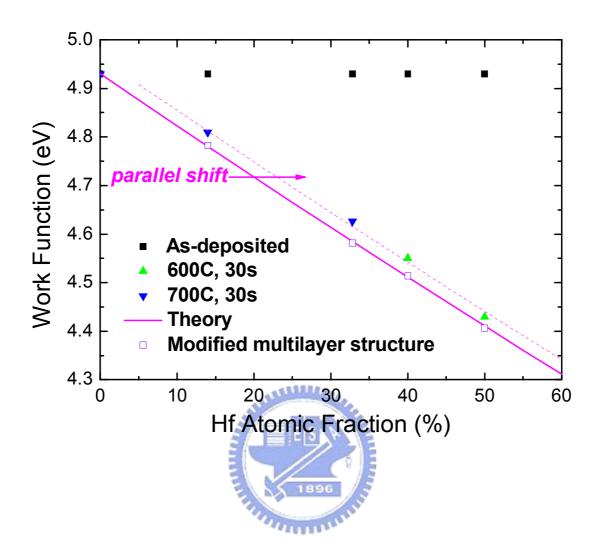

- Fig. 3.6 Comparison between experimental (Table II.) and theoretical results. A parallel shift may be attributed to the extra Hf consumption (~3%) due to surface oxidation. Also shown as open symbols are experimental results of multilayer (TiN/Mo/Hf/Mo) gated devices, good agreement on theoretical results can be achieved.

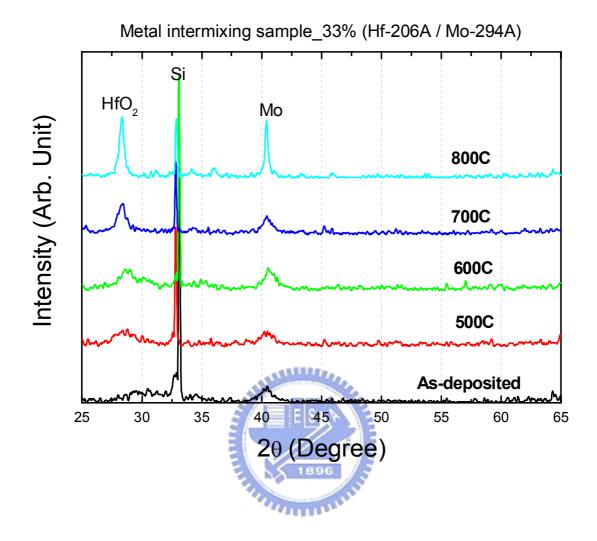

- Fig. 3.7 XRD spectra of metal intermixing sample (Hf-206Å/Mo-294Å/SiO<sub>2</sub>) exhibited HfO<sub>2</sub> peak as a result of oxidation of Hf at the top surface after thermal treatment.

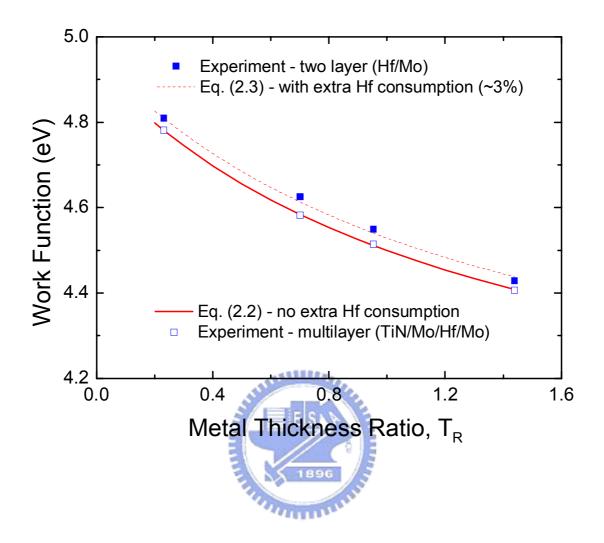

- Fig. 3.8 Post-annealing work functions extracted from two-layer (Hf/Mo) and multilayer (TiN/Mo/Hf/Mo) gated MOSCAP versus the composite metal thickness ratio ( $T_R = T_{Hf} / T_{Mo}$ ). Also shown are calculated results of derived quadratic equations with and without taking extra Hf consumption into account.

### Chapter 4

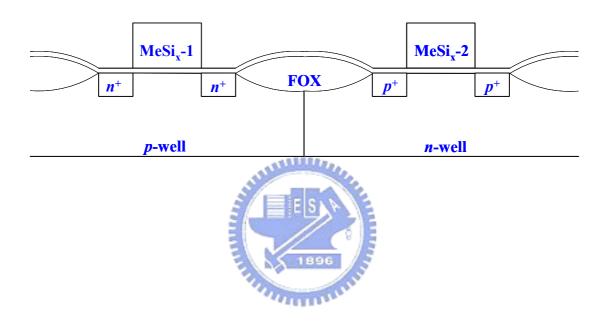

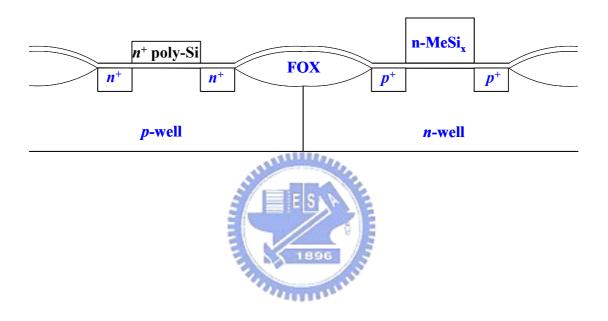

- Fig. 4.1 The schematic illustration of dual metal gate technology gated by the combination of different metal silicides.

- Fig. 4.2 The schematic illustration of the reported dual metal gate technology

- using FUSI method.

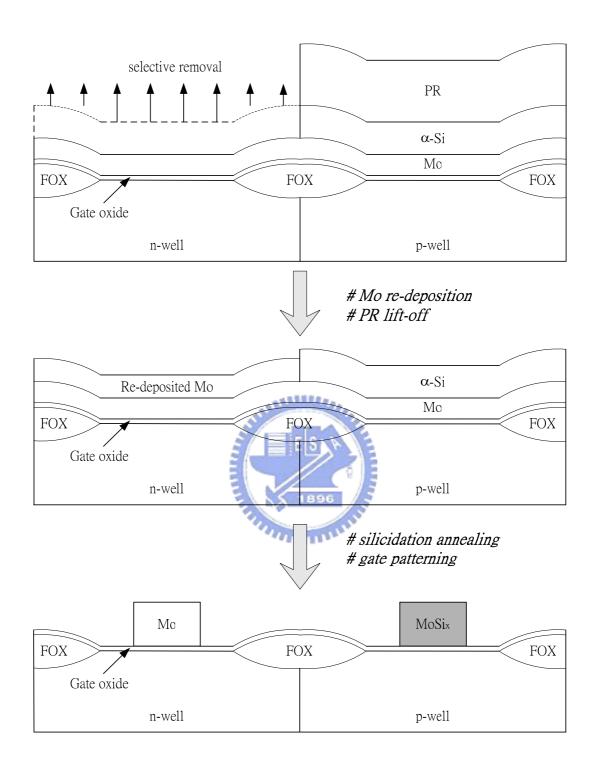

- Fig. 4.3 The schematic illustration of the proposed novel dual metal gate technology gated by the combination of metal and metal silicide.

- Fig. 4.4 The practical integration of the proposed novel dual metal gate technology gated by the combination of metal (Mo) and metal silicide (MoSi<sub>x</sub>).

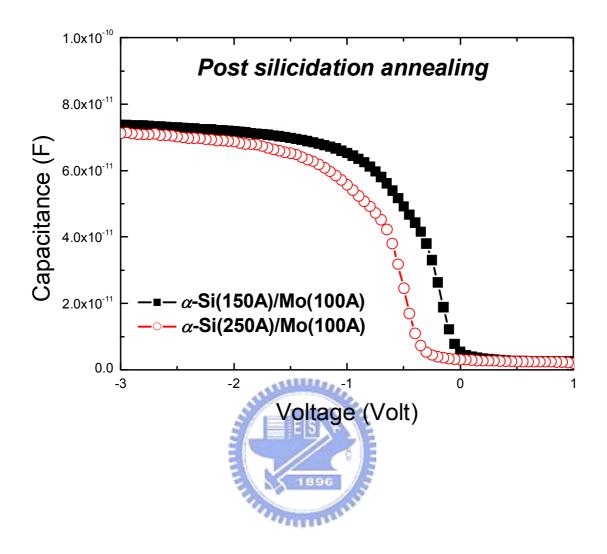

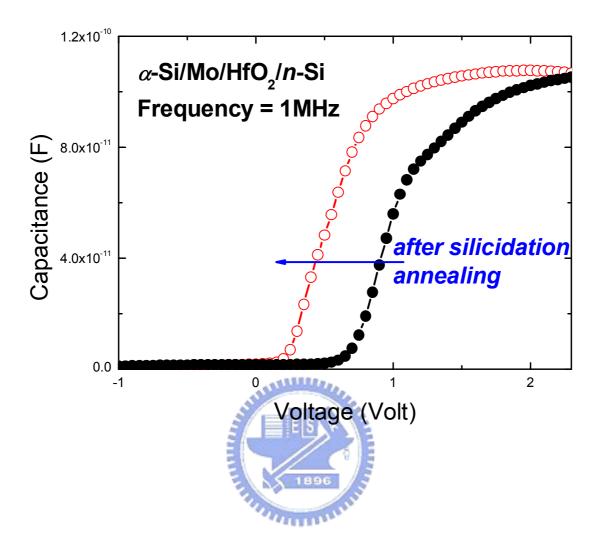

- Fig. 4.5 Capacitance-voltage curves of post-silicidation  $\alpha$ -Si/Mo/SiO<sub>2</sub>/p-Si MOSCAP as a function of the thickness of  $\alpha$ -Si.

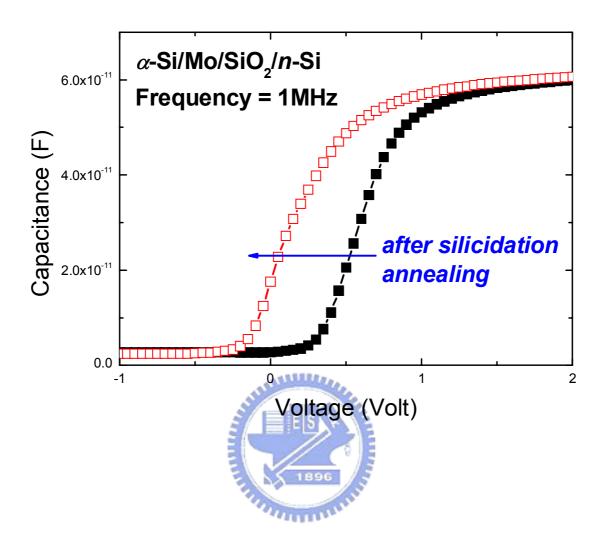

- Fig. 4.6 Capacitance-voltage characteristics of MOSCAP devices with  $\alpha$ -Si/Mo/SiO<sub>2</sub>/n-Si structure before and after silicidation annealing.

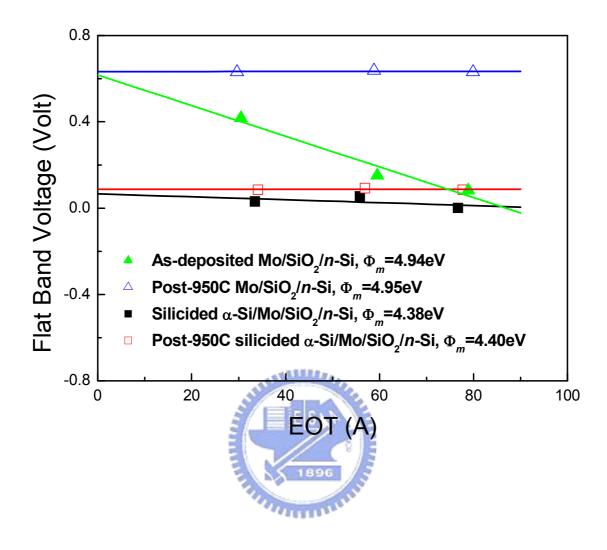

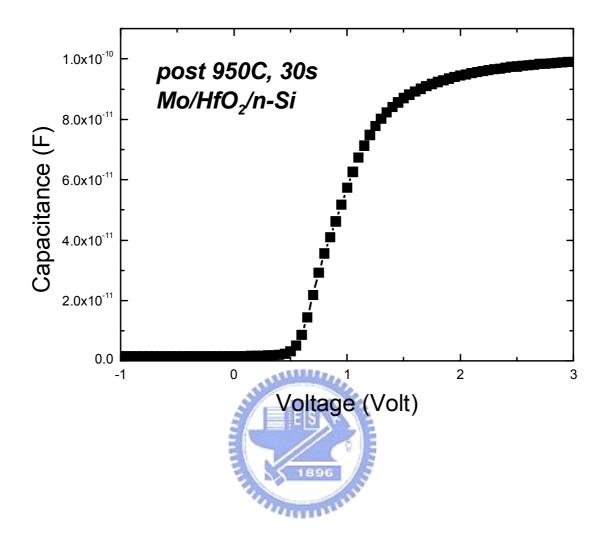

- Fig. 4.7 The  $V_{FB}$  versus EOT plots of Mo and MoSi<sub>x</sub> gated MOSCAP devices before and after 950°C RTA for thermal stability evaluation.

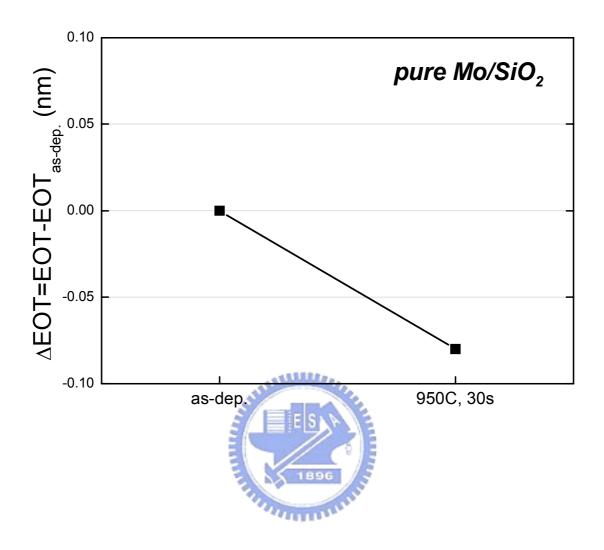

- Fig. 4.8 The dependence of the EOT variation on annealing conditions for MOSCAP devices with Mo/SiO<sub>2</sub>/*n*-Si structure.

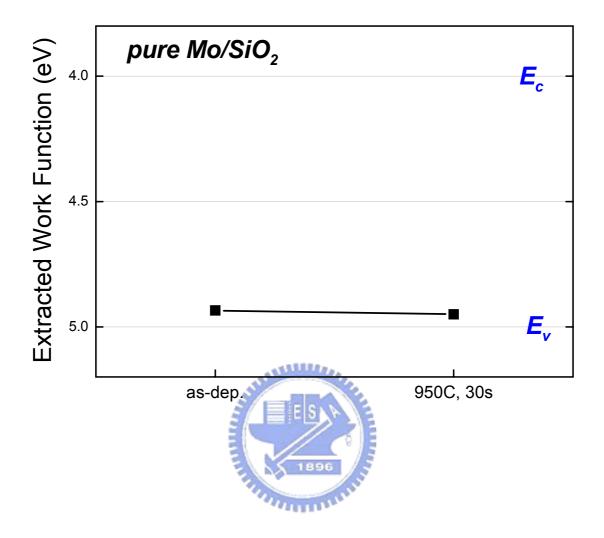

- Fig. 4.9 The dependence of the extracted work function value on annealing condition for MOSCAP devices with Mo/SiO<sub>2</sub>/*n*-Si structure.

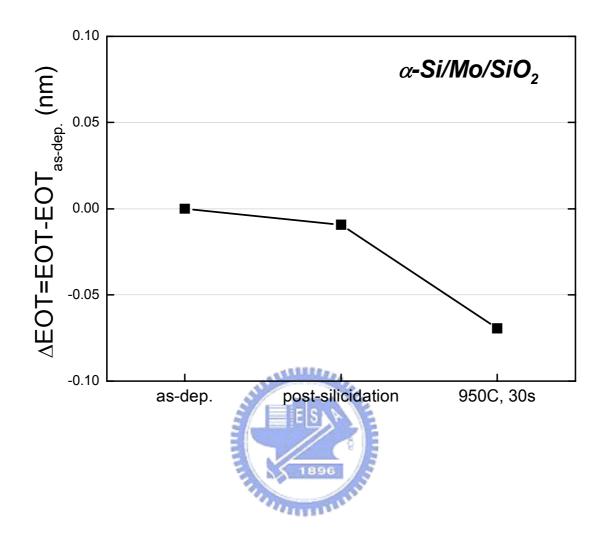

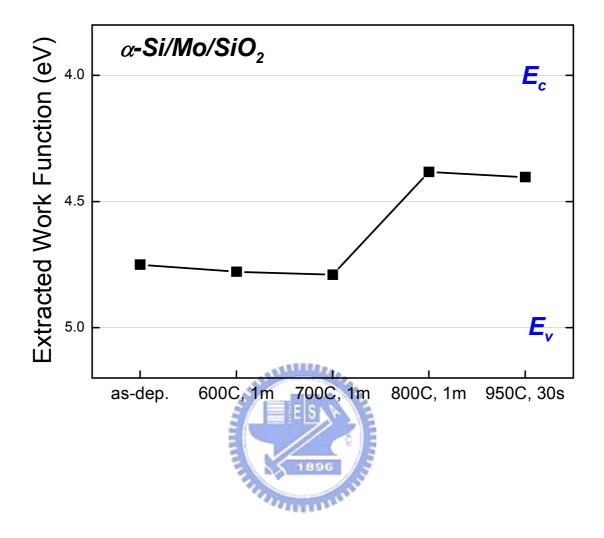

- Fig. 4.10 The dependence of the EOT variation on annealing conditions for MOSCAP devices with  $\alpha$ -Si/Mo/SiO<sub>2</sub>/n-Si structure.

- Fig. 4.11 The dependence of the extracted work function value on annealing temperature for MOSCAP devices with  $\alpha$ -Si/Mo/SiO<sub>2</sub>/n-Si structure.

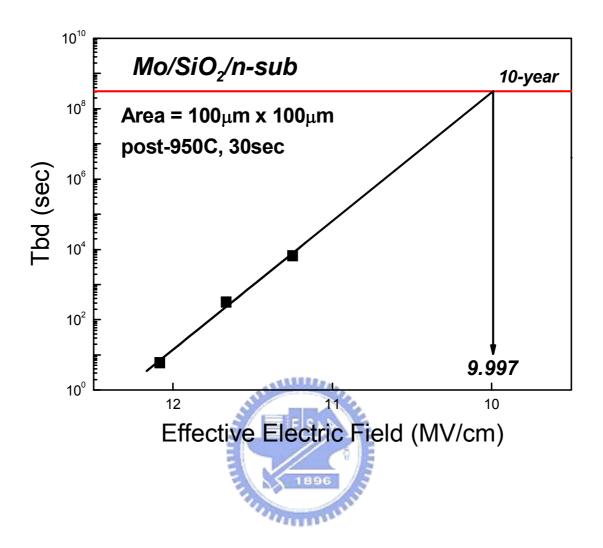

- Fig. 4.12 The TDDB lifetime projection of the Mo/SiO<sub>2</sub> device. Superior TDDB characteristic for pure Mo gate annealed by 950°C RTA for 30s is demonstrated.

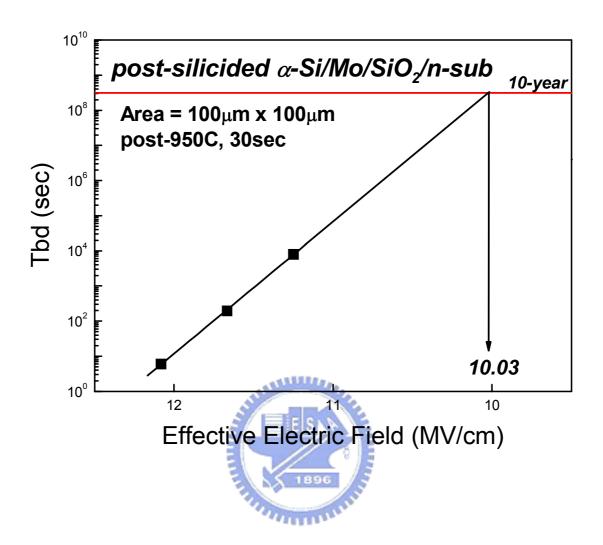

- Fig. 4.13 The TDDB lifetime projection of the post-silicidation  $\alpha$ -Si/Mo/SiO<sub>2</sub> device. Superior TDDB characteristic for MoSi<sub>x</sub> gate annealed by 950  $^{\circ}$ C RTA for 30s is demonstrated.

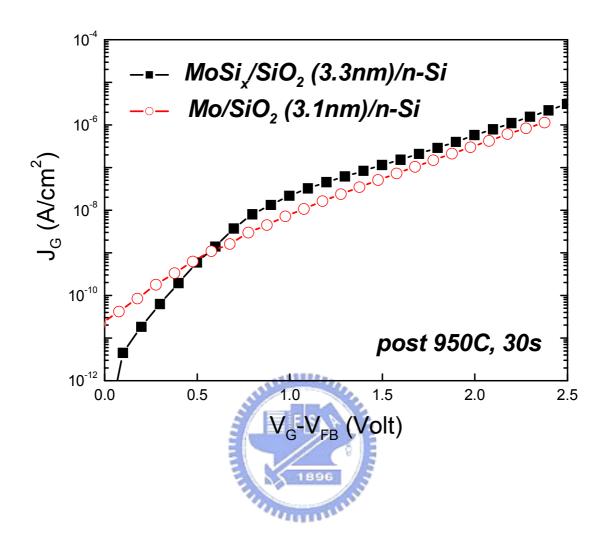

- Fig. 4.14 The accumulation leakage current densities of Mo/SiO<sub>2</sub>/n-Si and MoSi<sub>x</sub>/SiO<sub>2</sub>/n-Si devices annealed by 950°C for 30s.

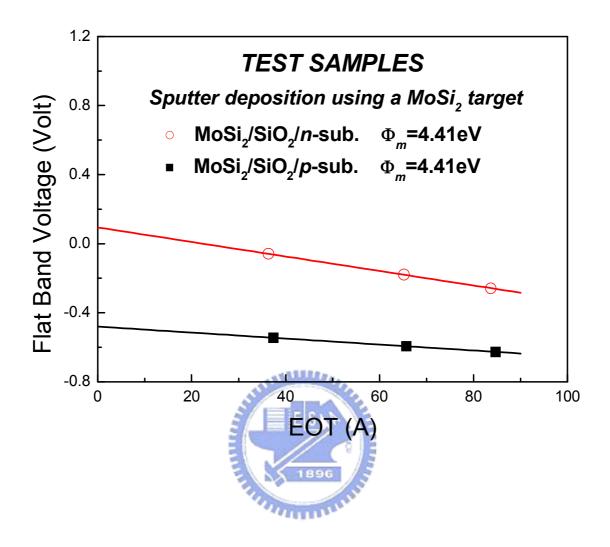

- Fig. 4.15 Work function extraction of MoSi<sub>2</sub> on SiO<sub>2</sub>. In this case, the MoSi<sub>2</sub> is sputtering-deposited using the MoSi<sub>2</sub> target.

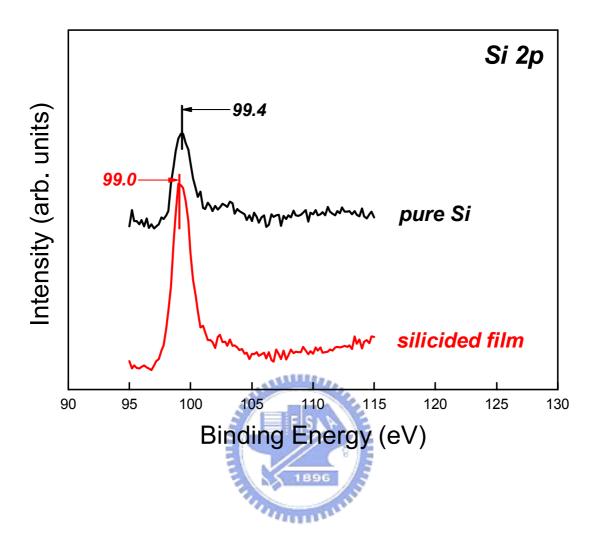

- Fig. 4.16 The x-ray photoelectron spectroscopy (XPS) analysis shows that the binding energy corresponding to the Si 2p spectra of silicided films is 0.4eV lower than that of pure Si.

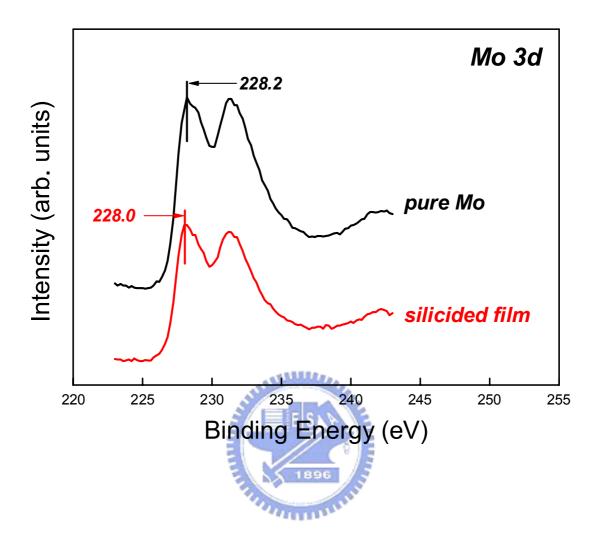

- Fig. 4.17 The x-ray photoelectron spectroscopy (XPS) analysis shows that the binding energy corresponding to the Mo 3d spectra of silicided films is 0.2eV lower than that of pure Mo.

- Fig. 4.18 The  $V_{FB}$  versus EOT plots of post-silicidation  $\alpha$ -Si/Mo gated MOSCAP devices with  $(5x10^{15} \text{cm}^{-2})$  and without arsenic pre-implantation dosage.

- Fig. 4.19 The dependence of  $\Phi_m$  values on the doses of arsenic pre-implantation.

- Fig. 4.20 The dependence of the EOT variation on annealing conditions for MOSCAP devices with  $\alpha$ -Si/Mo/SiO<sub>2</sub>/n-Si structure with  $5 \times 10^{15}$  cm<sup>-2</sup> arsenic pre-implantation.

- Fig. 4.21 The dependence of the extracted work function value on annealing conditions for MOSCAP devices with  $\alpha$ -Si/Mo/SiO<sub>2</sub>/n-Si structure with  $5 \times 10^{15}$  cm<sup>-2</sup> arsenic pre-implantation.

### Chapter 5

- Fig. 5.1 The schematic illustration of dual metal gate technology gated by the combination of polysilicon and metal silicide.

- Fig. 5.2 The capacitance-voltage characteristics of MOSCAP devices with

- α-Si/Mo/HfO<sub>2</sub>/*n*-Si structure before and after silicidation annealing.

- Fig. 5.3 The capacitance-voltage characteristics of pure Mo gated MOSCAP devices on the HfO<sub>2</sub> gate dielectric after RTA at 950°C for 30s.

- Fig. 5.4 The dependence of  $\Phi_m$  values on gate dielectric materials for pure Mo and MoSi<sub>x</sub> gate electrodes.

- Fig. 5.5 The dependence of  $\Phi_m$  values on gate dielectric materials for MoSi<sub>x</sub> gate electrodes with and without arsenic pre-implantation.

- Fig. 5.6 Schematic explanation of the machenism of Fermi-level pinning effect relaxation in the proposed novel approach.

## Chapter 1

### Introduction

### 1.1 EVOLUTION OF GATE ELECTRODE CANDIDATES

Before the mid-1970s, the doping technique was accomplished by the diffusion process in high-temperature furnaces. After the source/drain (S/D) diffusion, the thin gate oxide is grown and the metal gate is deposited. If the gate mask is misaligned with the S/D mask, the transistor will not work properly as shown in fig. 1.1. Oversized gate electrodes are required to ensure the complete gate coverage over the S/D. The gate misalignment issue leads to a great challenge especially when devices are scaled down.

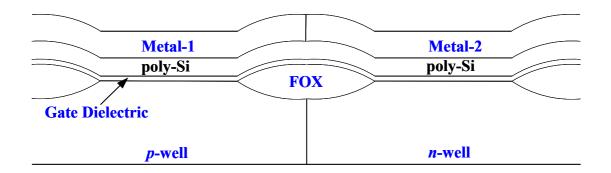

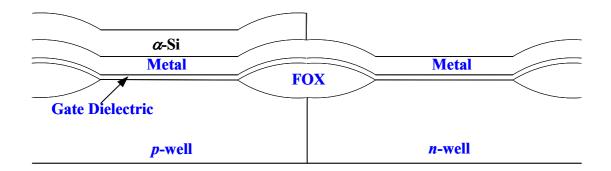

The application of ion implantation solved the gate alignment problem by using the so-called self-aligned S/D doping process as shown in fig. 1.2. In this case, the gate oxide is grown followed with the deposition, patterning, and etching of gate electrodes. The ion implantation is used to form the S/D region and a high temperature annealing process is required to repair the damage due to the implantation process and to activate the implanted dopant. Since the required annealing temperature is usually higher than the melting point of aluminum (Al), a different gate electrode candidate has to be introduced. Polysilicon and silicide/polysilicon stack (polycide) have been used as the gate materials for several device generations.

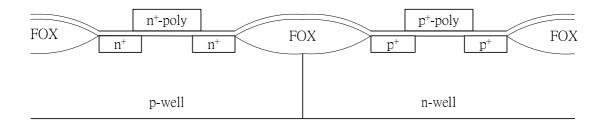

In the late-1980s, the need to reduce the power consumption of the integrated circuit (IC) was one of the major driving forces for complementary MOS (CMOS) devices development. Early CMOS based ICs used  $n^+$ -polysilicon as gate electrodes for both n-MOS and p-MOS devices as shown in fig. 1.3. To suppress the punch through in p-MOS devices, the substrate doping concentration will need to be increased. Along with the use of lower Fermi energy  $n^+$ -polysilicon as gate electrode, the threshold voltage of p-MOS will be too negative to be acceptable. A thin sheet of negative charges must therefore be placed at the Si/SiO<sub>2</sub> interface in p-MOS devices. This can be accomplished by implanting a shallow layer of boron atoms. The boron dose must be heavy enough to compensate the n-surface so that a thin p-region is formed and shifts the threshold voltage of p-MOS toward more positive value.

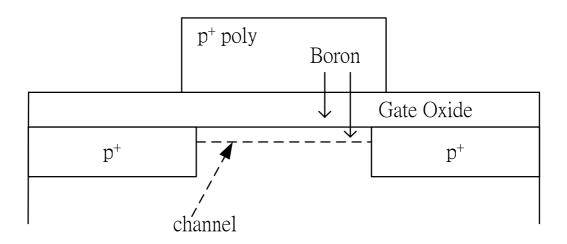

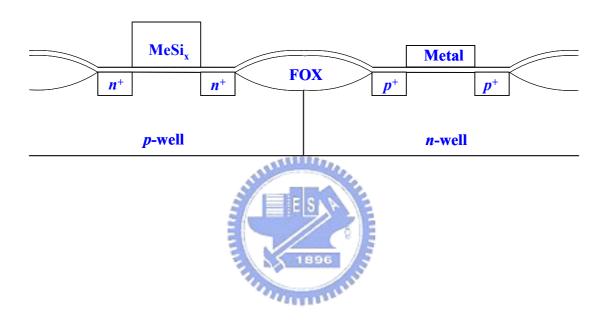

However, this technology ( $n^+$ -polysilicon for both n-MOS and p-MOS) will lead to a buried-channel p-MOS device which will exhibit enhanced susceptibility to short-channel effects. Solutions involving the use of gate electrodes other than  $n^+$ -polysilicon must therefore be explored. One alternative is to use  $n^+$ -polysilicon and  $p^+$ -polysilicon for n-MOS and p-MOS devices, respectively, as shown in fig. 1.4. Such a so-called dual-doped poly approach, however, introduces other problems. One drawback is the poor threshold voltage control in the p-MOS devices due to penetration of the boron atoms into the oxide or further into the silicon substrate, as shown in fig. 1.5, especially when a thin gate oxide is used [1]. It has also been found that the presence of fluorine in the gate oxide worsens the boron penetration problem [2, 3]. Such fluorine can be introduced into the gate oxide if the p-MOS S/D regions are formed using BF<sub>2</sub> implantation which is suggested for shallow junction formation.

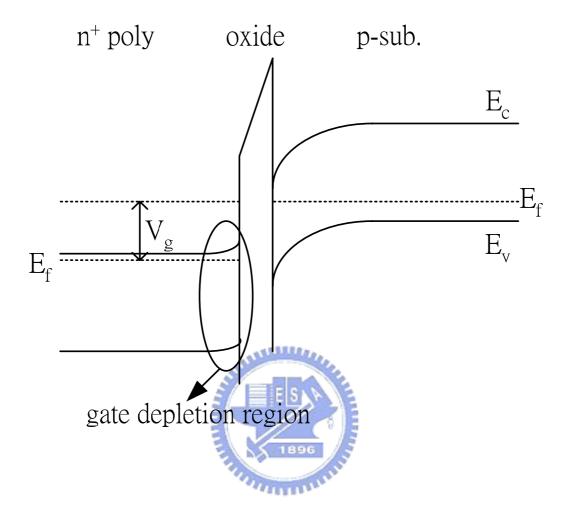

Another problem encountered with conventional polysilicon gates is the

so-called poly depletion effect as shown in fig. 1.6 [4]. If the polysilicon gate is not doped heavily enough, problems will arise from the depletion of the gate itself. Gate depletion results in an additional capacitance in series with the gate oxide capacitance, which in turn leads to a reduced inversion-layer charge density and degradation of the MOSFET transconductance. It is worth to note that the boron penetration and poly depletion effect in p-MOS devices will influence each other. Heavily boron concentration is needed for  $p^+$ -polysilicon to suppress the poly depletion effect in PMOS while it potentially makes the boron penetration problem more pronounced.

It is also worth to note that the shrinkage of oxide thickness can improve the device short channel performance, however, the increasing leakage current leads to the noticeable standby power. Replacing the conventional silicon dioxide gate stack with the novel high-k gate dielectric material draws more and more attention in the last several years. The use of the high-k gate dielectric can possesses larger physical oxide thickness under the same electrical oxide thickness and results in effective leakage current reduction. Several high-k materials have been investigated as new gate dielectric candidates such as TiO<sub>2</sub>, Ta<sub>2</sub>O<sub>3</sub>, Al<sub>2</sub>O<sub>3</sub>, ZrO<sub>2</sub>, HfO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> and Pr<sub>2</sub>O<sub>3</sub>. Among these candidates, HfO<sub>2</sub> not only has relatively high dielectric constant and bandgap but also exhibits the impressive thermal stability with the silicon substrate. The polysilicon/HfO<sub>2</sub> interface, however, will lead to the so-called Fermi-level pinning effect which is believed to have been caused by Si-Hf interaction and leads to high threshold voltages of MOSFET devices. Moreover, polysilicon gates are found to be thermodynamically unstable on many high-k materials [5, 6] so that metals are expected to provide a turning point in possessing a better thermal stability.

### 1.2 BASIC REQUIREMENTS FOR METAL GATES

The use of metal/high-k structure, however, will introduce several new challenges such as the choice of metal candidates, the development of a compatible process and the thermal stability issue between metal and high-k gate dielectric.

The work function value of the introduced metal candidate will significantly influence threshold voltages of fabricated devices. High performance CMOS technology generally requires two separate gate work function values for n-MOS and p-MOS devices. Providing appropriate work function values at the gate dielectric interface, one can achieve low and symmetric threshold voltages for *n*- and *p*-channel devices without high dosage channel implantation which potentially leads to the threshold voltage non-uniformity and the carrier mobility degradation. Metals with midgap work function, such as W and TiN, have been firstly adopted as gate candidates for symmetric threshold voltage values. However, the magnitude of resulted threshold voltages for both *n*- and *p*-channel devices would be too large to be acceptable [7, 8]. To avoid applying heavily counter channel doping, the dual work function metal gate technology has been proposed [9-11]. The major concept is similar to the dual-doped polysilicon technology where different gate materials with suitable work function values are served as gate candidates for *n*- and *p*-channel devices. The chosen metal candidates should provide suitable work function  $(\Phi_m)$ values at the dielectric interface. For instance, metal gates should possess work function values of about 4eV and 5eV to replace the conventional  $n^+$  and  $p^+$ -polysilicon gates, respectively, for surface-channel bulk devices. Moreover, several advanced devices with new transistor structures, such as FinFET and ultra-thin-body (UTB) MOSFET, have been developed recently [12-19]. These advanced devices have better gate-to-channel controllability. Consequently, the required gate work function values for low and symmetric threshold voltages will be different from those in bulk devices. Moreover, the adjustment of the substrate doping is no longer an effective way of threshold voltage control in advanced devices. Choosing metal gate candidates with suitable work function values becomes a more and more importance topic. The reported simulation results show that the required gate work function for *n*-and *p*-channel advanced devices are about 4.4~4.6eV and 4.8~5.0eV, respectively.

In addition, the chosen metal candidates should be able to possess good thermal stability with the underlying gate dielectric material. Consequently, the undesired interaction at metal/gate dielectric interface during the device fabrication process can be avoided, and the process induced  $\Phi_m$  and/or the equivalent oxide thickness (EOT) variations can be suppressed. Although the recently developed gate-last (also called replacement gate) technique can provide a new chance of using low thermal stable materials as gate electrodes [20-26], the fabrication process will become more complex and lead to new challenges such as dummy gate removal and metal polish.

The development of suitable process integration is also an important issue to avoid the possible process-induced performance degradation. Several metal gate technologies have been widely investigated in the last decade. The firstly proposed dual work function metal gate technology exhibits a straightforward fabrication process [9, 10]. Although the used Ti and Mo have suitable work function values for *n*- and *p*-channel devices, respectively, the proposed integration process inherently makes the gate dielectric material exposed to the metal etchant and leads to an

undesired reliability problem and oxide thickness non-uniformity.

To overcome this phenomenon, a novel dual work function metal gate technology using Ni-Ti interdiffusion has been proposed [27, 28]. Although this approach is quite material-dependent, it provides a lot of suggestions and recommendations on the dual metal gate technologies. Furthermore, a novel metal work function adjustment technique using nitrogen implantation has been proposed [29-32]. This approach is good at the ease of process integration but the modulated range of work function may not be large enough and the process stability will be a challenge.

Recently, a so-called fully silicidation (FUSI) method has been proposed to apply for implement of dual work function metal gate technology [33-38]. The front-end process is the same with the traditional dual-doped polysilicon gates CMOS technology while the conventional salicide process is modified. A metal layer thicker than that required for conventional salicide process is required to allow for full silicidation of the existed polysilicon gates. And dopants in the polysilicon are demonstrated to be able to modify the work function value of the formed metal silicide (MeSi) gates.

Several metal candidates, metal nitrides and binary alloys have also been widely investigated in the last five years. To sum up, the dual work function metal gate technology is drawing more and more attention.

### 1.3 METAL WORK FUNCTION EXTRACTION TECHNIQUE

There are several methods for the metal gate work function extraction. One is comparing the flat-band voltage shift of MOSCAP devices between the under test metal gate electrode and that with known work function value such as  $n^+$  poly-silicon. In this case, devices should be subjected to the similar process flow and the same thermal budget. From the known work function of  $n^+$  poly-silicon and flat-band voltage difference between  $n^+$  poly-silicon and the under test metal, the metal work function can be estimated. But the value of the extracted metal work function in this approach would be less precise due to the different gate electrode deposition processes for polysilicon and metal gates. In general, metal gates are deposited using sputtering system, and this physical vapor deposition (PVD) system will inherently result in more oxide charges contributing to flat-band voltage difference.

Another approach bases on the expression of the flat-band voltage in a MOS system [29]:

$$V_{FB} = \Phi_{ms} - \frac{Q_f}{C_{ox}} = \Phi_{ms} - \frac{Q_f}{\varepsilon_{ox}} t_{ox}$$

(1.1)

where  $Q_f$  is the density of fixed charges in the oxide,  $\varepsilon_{ox}$  is the permittivity of the dielectric material and  $t_{ox}$  is the thickness of the gate dielectric. To decouple the effect of fixed oxide charges, Capacitance-voltage measurements of MOSCAP devices with different oxide thicknesses will be performed to generate the flat-band voltage ( $V_{FB}$ ) versus the effective oxide thickness (EOT) plot. The intercept of  $V_{FB}$  axis corresponds to the value of  $\Phi_{ms}$ . The value of  $\Phi_s$  can be calculated according to the information of the electron affinity of silicon substrate, silicon energy bandgap and the potential difference between the intrinsic and doped silicon Fermi level. Work function values obtained in this way, however, would be fair approximations after accounting for

uncertainties in flat-band voltage determination and the contributions of interface trap state.

Notably, it has been reported that the quantum mechanical (QM) effect becomes significant in the oxide thickness extraction as oxide thickness is reduced [39, 40]. Carrier transporting in the channel is confined by a triangular energy well. Consequently, the charge centroid locates further from the surface than that predicted by the classic analysis. This quantum mechanical effect will contribute additional effective oxide thickness and then lead to a deviation in metal work function extraction. Several capacitor-voltage simulators with the consideration of quantum confinement effect, such as QMCV and NCSU-CV, have been proposed. In this thesis, we use the QMCV simulator established by UC Berkeley Device Group for the determinations of the flat-band voltage and effective oxide thickness.

### 1.4 ORGANIZATION OF THE THESIS

Two novel dual-work function metal gate technologies are proposed and investigated in this dissertation. First, the dual metal gate technology based on the use of Hf-Mo binary alloys is demonstrated. Second, the silicidation technique is used to implement a dual metal gate technology with metal-metal silicide combination.

In chapter 1, an introduction to the gate candidate evolution and a brief review of state-of-the-art metal gate technologies are discussed. Basic requirements of novel metal candidates are also addressed. Moreover, the used work function extraction technique in this dissertation is also mentioned.

In chapter 2, the electrical and chemical characteristics of Hf-Mo binary alloys are investigated. The continuous and almost linear work function adjustment using  $Hf_xMo_{(1-x)}$  is demonstrated for the first time. The work function value of Hf-Mo binary alloy deposited by co-sputtering ranges from 3.93eV ( $\Phi_m$  of pure Hf) to 4.93eV ( $\Phi_m$  of pure Mo) and depends on the sputtering power ratio of each target. The thermal stabilities of Hf-Mo binary alloys on  $SiO_2$  degrade with the increase of Hf atomic fraction, but all of them possess thermal stabilities at least higher than  $400^{\circ}$ C. The Hf-Mo binary alloys can still be suitable for the gate-last  $SiO_2$  CMOS process.

In chapter 3, the integration of Hf-Mo binary alloys into dual metal gate technology is proposed. For the ease of process integration,  $Hf_xMo_{(1-x)}$  formed by metal intermixing is evaluated, and a novel dual work function metal gate technology is proposed and demonstrated. One can be allowed to get around the thermal stability issue by using an appropriate metal thickness, and possess precise controllability of metal work function by adjusting the composite metal thickness ratio. This technique is not only attractive but especially important for FinFET and/or UTB-MOSFET applications.