#### CHAPTER 1

#### Introduction

# 1 General background and motivations

The mismatched heterostructures are important for the microelectronic and optoelectronic devices. The examples include SiGe heterojunction bipolar transistors (HBTs) [1], Ge photo-detector integrated on Si substrate [2,3], III-V high electron mobility transistors (HEMTs) [4], and II-VI semiconductors blue-green lasers [5]. In these examples, the lattice mismatched layers are pseudomorphic to the underlying semiconductor substrates. The lattice mismatched heterostructures can have high defect density in the epilayers. The induced defect is a crucial issue for utilizing these heterostructures for electronic and optoelectronic device applications. Therefore, it is important to restrain the defect densities in the heterostructures. In this investigation, novel techniques for controlling dislocation densities in the Si<sub>1-x</sub>Ge<sub>x</sub>, GaAs, ZnSe epilayers on Si substrates are demonstrated. Nickel germanosilicide Ohmic contacts are also studied in this dissertation since they are very important constituents for the Si<sub>1-x</sub>Ge<sub>x</sub>-based devices. Nevertheless, it was found that the thermal effect of germanosilicide was very different from that of the silicides in the Si technique. Therefore, the technology of the nickel germanosilicide contacts formed on Si<sub>1-x</sub>Ge<sub>x</sub> layer needs further study. In the first part of this chapter, the growth of the strained and relaxed Ge<sub>x</sub>Si<sub>1-x</sub> epilayers was introduced. Methods of growing relaxed Ge and Ge<sub>x</sub>Si<sub>1-x</sub> layers on the Si substrates were introduced and the mechanisms for the reduction of reduce threading dislocations in the lattice mismatched heterostructures were illustrated. Additionally, a novel technique for the growth of high-quality Ge epilayer on the Si substrate is introduced. This novel structure provides the possibility of growing III-V and II-VI epilayers on Si substrates due to the reduction of dislocation density in these films. In the second part, techniques for growing GaAs on Si in the past few years are reviewed. A method for growing high-quality GaAs layer on Si

substrate is also presented in this dissertation. In the third part, approaches for growing ZnSe layer on Si in previously years are reviewed. A technique for growing high-quality ZnSe layer on Si substrate is also discussed in this investigation. In the fourth part, metal germanosilicide contacts formation study in the past few years is reviewed. In order to improve the properties of the nickel silicide on Si<sub>1-x</sub>Ge<sub>x</sub>, a Si capping layer grown on top of Si<sub>1-x</sub>Ge<sub>x</sub> epilayers was introduced for the contact formation in this study. The last part of this chapter is the outline for this dissertation.

# 1-1 Growth of the Si<sub>1-x</sub>Ge<sub>x</sub> and Ge epitaxial layers on Si substrate

Strained Si<sub>1-x</sub>Ge<sub>x</sub> alloys have attracted considerable attention over the past few years. Early work by B. S. Meyerson in 1986 [6] demonstrated epitaxial growth of Si<sub>1-x</sub>Ge<sub>x</sub> by using ultrahigh vacuum/chemical vapor deposition (UHV/CVD). The technique of growing Si<sub>1-x</sub>Ge<sub>x</sub> films on Si substrate was first introduced in this time span, and the first case was applied to the epitaxial Si<sub>1-x</sub>Ge<sub>x</sub>-base heterojunction bipolar transistors (HBT's). In recent years, Si<sub>1-x</sub>Ge<sub>x</sub> layers were also applied to the well established (CMOS dominated) Si-based semiconductor industry. The strained-Si MOSFET is a promising device for the sub-100nm CMOS technology because of its high electron and hole mobilities. Developing this device currently requires a high-quality Si<sub>1-x</sub>Ge<sub>x</sub> virtual substrate. Relaxation of the lattice strain during epitaxial growth of the Si<sub>1-x</sub>Ge<sub>x</sub> layers always generates dislocation, surface roughness and cross-hatching. Nevertheless, the quality of the epilayer and the surface of the virtual substrate were quite unsatisfactory up to date. Several techniques for growing high Ge content in Ge<sub>x</sub>Si<sub>1-x</sub> epilayer have been reported but still need further improvement. As the scaling of Si or Si<sub>1-x</sub>Ge<sub>x</sub> MOSFET approaches its fundamental physics limit, the devices need new materials with high carrier mobility to improve the device performance. One of the promising materials is Ge due to its higher carrier mobility which results in larger drive current and the smaller bandgap for supply voltage scaling [16]. Inspired by the recent progress of high-k

dielectric gate in Si MOSFET applications, the Ge MOSFETs have attracted more and more attention and extensively investigated again [47,48].

Furthermore, a large lattice constant Ge semiconductor epitaxially grown on Si has been extensively studied in recent years. There are several applications such as solar cell [15] and Ge photo-detectors [2,3]. Especially application is provide a beneficial preliminary structure for III-V and II-VI devices integration on Si circuits in the future. Si<sub>1-x</sub>Ge<sub>x</sub> is a candidate as a buffer structure for growing Ge epitaxial layer on Si substrate. However, the major problems of growing Ge on Si are the high density of threading dislocations and the high surface roughness arising from the 4.2% lattice mismatch between Ge and Si. This is due to the epitaxial growth of lattice mismatched Si<sub>1-x</sub>Ge<sub>x</sub>/Si heterostructures when the thickness of epilayer beyond the critical thickness [17] which generally results in the formation of threading dislocation. Due to this reason various of techniques have been attempted to circumvent the problem of threading dislocation. There are the compositionally graded buffer (CGB) layer [18], low-temperature Si buffer layer [19], compliant silicon-on-insulator (SOI) substrate [20], two-step procedure [21], and selective area growth combined with thermal cycle annealing [22]. Among them, the CGB layers are the most practically and widely used ones today. However, the CGB layers still have two major challenges. First, these CGB layers often suffer from a thickness of approximately 10µm with a Ge composition ranging from zero to 1.0, which makes the integration of devices on the Si-base circuits difficult. Second, the CGB layers often exhibit a cross-hatch pattern, which makes the surfaces very rough [23]. In this study, we report a novel approach to obtaining a high-quality Ge layer. The total thickness of all epitaxial layers is only 2.6µm. The threading dislocation density in the top Ge layer can be reduced to approximately  $3\times10^6$  cm<sup>-2</sup>. The Ge surface roughness is only 32 Å.

### 1-2 Growth of the GaAs epilayer on Si substrate

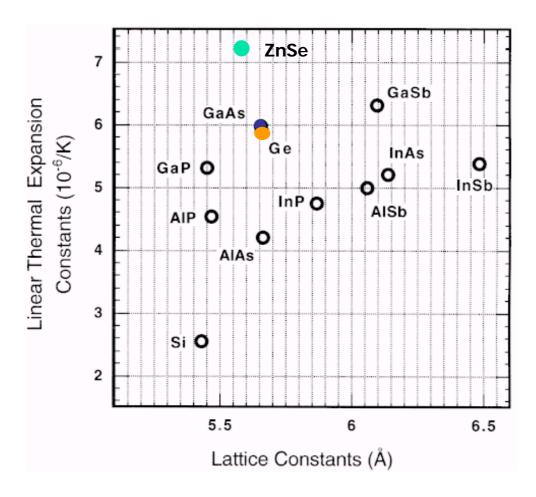

Single crystalline silicon (Si) is the most probable material for high-speed devices because of superior native oxide, low cost, large-area availability, high quality, and high thermal conductivity of the substrates. GaAs has advantages over Si for some applications due to its higher electron mobility, direct bandgap and wider bandgap. One way to take benefit of many of the best characteristics of both materials is to grow GaAs epitaxilly on Si substrates. There are several potential advantages of this structure such as system on chip (SOC), lower costs, thermal and manufacturing improvement. However, the GaAs on Si system has many problems. They are: high lattice mismatch between Si and GaAs (4%); a large thermal expansion coefficient (~63%) between GaAs and Si; highly stressed GaAs films on Si; the growth of polar materials on non-polar substrates; poor surface morphologies and auto doping of Si from substrate into the GaAs film [24]. Figure 1.1 shows lattice constants and linear thermal expansion coefficients of IV, III-V and II-VI [24]. For GaAs grown directly on Si substrate that negates the advantages of GaAs on Si system by generating large densities of dislocations in the GaAs epitaxial layers due to high lattice mismatch. While many methods for controlling and reducing the threading dislocation density (TDD) have been explored, including III-V buffers and/or thermal cycling [25-32], compositionally graded Ge<sub>x</sub>Si<sub>1-x</sub> buffer layer (CGB) is the most practical and is extensively used currently [25]. However, CGB layer approach faces two major challenges, which make the integration of the GaAs devices on the Si-based circuits difficult. First, the crosshatch pattern of the CGB layer makes its surface very rough [33]. Second, the CGB layer is very thick. Additionally, the inter-diffusion across the GaAs/Ge interface that occurs during epitaxial growth is important because it affects the control of the doping profile in GaAs. Several approaches have been proposed to suppress the Ge inter-diffusion, as reported in Refs [34,35]. In this thesis, the techniques of growing high-quality GaAs on Si with suppressed interdiffusion by using novel Ge/GeSi/Si, improved crystalline and optoelectronic property of GaAs on Si are investigated.

### 1-3 Growth of the ZnSe epilayer on Si substrate

ZnSe is a very interesting material for optoelectronics applications [36]. In recent years the mature molecular beam epitaxy (MBE) and other growth techniques [37] have been made in order to obtain high quality ZnSe layers. However, improvements of ZnSe epilayer crystal quality are necessary for commercial device production. The lack of suitable substrates to grow ZnSe is one of the problems impede the development of high performance optoelectronic devices. ZnSe substrates are now available but they are sparse and very expensive. Therefore, GaAs that has a small lattice mismatch to ZnSe (0.27%) has been the substrate of choice for the growth of the ZnSe epitaxial layers [38]. However, the heteroepitaxial growth of ZnSe on GaAs presents some intrinsic problems like the generation of dislocations when the epilayer thickness exceeds a critical thickness, the difference in the thermal expansion coefficients, surface segregation of Ga, etc. [39-41]. These problems are due to the crystal defects generated at the ZnSe/GaAs interface. Besides, Ge also has a small lattice mismatch to ZnSe, which is another suitable substrate for growing ZnSe/Ge heteroepitaxial [42]. A different approach for growing ZnSe layer is use the Si substrates [43]. Si substrates are cheaper and have better thermal and mechanical properties than GaAs substrates. Moreover, the possibility of integrating the optoelectronics based on ZnSe with Si circuit is one of the most important motivations to study the growth of ZnSe on Si. However, the large lattice mismatch (4.3%) between ZnSe and Si and the chemical reactions at the interface between these two materials make the growth of ZnSe on Si difficult [44-46].

In this thesis, the techniques for growing high-quality ZnSe on Si with suppressed interdiffusion by using novel Ge/GeSi/Si buffer structure is investigated, and improved the crystal properties of ZnSe on Si is achieved.

# 1-4 Nickel germanosilicide contact formation

For the high speed device applications the metal silicide based Ohmic contacts are very important constituents for the Si<sub>1-x</sub>Ge<sub>x</sub> based devices. Silicide was first introduced to LSI devices, as a MoSi<sub>2</sub> polycide word line in 256K DRAM in early 1980s, which was one of the first applications of polycide to LSI production. Then, WSi<sub>2</sub> polycide was popularly used for the gate electrode of logic LSIs from the middle of the 1980s because the sheet resistance of WSi<sub>2</sub> is smaller than that of the MoSi<sub>2</sub>. When the self-aligned silicidation (salicide) became popular in recent years, TiSi<sub>2</sub> was used in 1990s. TiSi<sub>2</sub> was selected as the material for salicide, because the sheet resistance is much smaller than WSi<sub>2</sub>. However, TiSi<sub>2</sub> was eventually found to be relatively difficult material to treat due to the controllability in thermal process, because high temperature process caused severe agglomeration. Thus, CoSi<sub>2</sub> replaced TiSi<sub>2</sub> from the late 1990s and have made the metallization process more suitable toward deep-sub micron CMOS. However, for the sub-100 nm technology node, the widely used CoSi<sub>2</sub> contact is expected to be replaced by NiSi contact, this is especially true for the Si<sub>1-x</sub>Ge<sub>x</sub> device applications in the future.

For the sub-100 nm Si<sub>1-x</sub>Ge<sub>x</sub>-based devices the metal germanosilicide Ohmic contacts are very important constituents. Germanosilicided Si<sub>1-x</sub>Ge<sub>x</sub> junction has attracted lots of attention due to its potential applications as the contacts for the SiGe based electronic devices such as the base metal for HBTs [7] and advanced SiGe source/drain for deep submicron CMOS [8]. The performances of the Si<sub>1-x</sub>Ge<sub>x</sub>-based devices, such as switching speed and high-power characteristics depend critically on the properties of these Ohmic contacts. Interfacial reactions of metals such as Co and Ni with Si<sub>1-x</sub>Ge<sub>x</sub> films to form metal silicide Ohmic contacts have been investigated [9-12]. Nickel silicide has attracted much attention as a potential alternative to cobalt silicide since it requires lower thermal budget. Additionally, the low-resistivity, one-step silicidation process with no adverse narrow line effect on sheet resistance makes Ni silicide an attractive candidate for use in self-alignment technology

[13,14]. Unfortunately, the morphological stability of the nickel germanosilicide film formed by direct annealing of nickel on Si<sub>1-x</sub>Ge<sub>x</sub> layer Ni-Si<sub>1-x</sub>Ge<sub>x</sub> is notably bad and the Ge segregation appeared duing the long time thermal (400°C) stress. For Si<sub>1-x</sub>Ge<sub>x</sub> based device applications, these problems shall be solved immediately. In this study, a suitable thickness of Si capping layer was deposited on the top of SiGe layer to improve the material and electrical properties of the Ohmic contacts is presented and excellent results were obtained.

#### 1-5 Outline of this dissertation

This dissertation presents the growth of heterostrucrure semiconductors (Ge<sub>x</sub>Si<sub>1-x</sub>, GaAs, ZnSe) on Si and nickel germanosilicide contacts on Si<sub>1-x</sub>Ge<sub>x</sub> layers and is divided into 6 chapters, including:

In Chapter 2, we present a mechanism of interface-blocking to reduce the threading dislocations in the  $Si_{1-x}Ge_x$  and Ge layers on Si (100) substrates. Additionally, growth of high-quality epitaxial Ge layers on a Si (100) substrate by using this mechanism is presented. Experimental results show that the dislocation density in the top Ge layer can be greatly reduced, and the surface is very smooth, while the total thickness of the structure is only  $2.6\mu m$ . This buffer structure also provides a virtual substrate to grow III-V and II-VI heterostructure on Si in this study.

In Chapter 3, the growth of high-quality GaAs layers on Si (100) substrate by using Ge/Si<sub>1-x</sub>Ge<sub>x</sub> buffer structure is proposed. The experimental results show that the dislocation density in the top GaAs layers can be greatly reduced, and the surface is kept very smooth after the growth, while the total thickness of the structure is only 5.1μm. Moreover, out-diffusion of Ge into the GaAs epilayer is also successfully suppressed using the 6° off-cut Ge/Ge<sub>0.95</sub>Si<sub>0.05</sub>/Ge<sub>0.9</sub>Si<sub>0.1</sub>/Si virtual substrate.

In Chapter 4, the epitaxial growth of ZnSe layers on Si substrates utilizing a  $Ge/Ge_{0.95}Si_{0.05}/Ge_{0.9}Si_{0.1}$  buffer structure is presented. In this study, we examine the material

and optical characteristics of ZnSe epilayer grown on Si. Additionally, atomic interdiffusion in the ZnSe epilayer is also investigated. In a sample with a large off-cut Si virtual substrate, the outdiffusion of Ge into the ZnSe epilayer is suppressed. The low-temperature PL measurements indicate that the sample with a large off-cut Si substrate improves its optical characteristic effectively. The X-ray diffraction analysis and transmission electron microscopy (TEM) results indicate that the crystallinity of the ZnSe epilayer on Si is markedly improved. The method of low temperature MEE and buffer layer growth with *in-situ* annealing can suppress the formation of the deep-level emission in the ZnSe/Ge/Ge<sub>x</sub>Si<sub>1-x</sub> structure effectively is also demonstrated.

In Chapter 5, we present the material and electrical properties of the nickel germanosilicide formed on various Si<sub>1-x</sub>Ge<sub>x</sub> (x=0, 0.2 and 0.3) layers, such as formed phase, agglomerates, sheet resistance and specific contact resistivity. Besides, thermal stability of the nickel germanosilicide on high-dose B<sup>+</sup>, BF<sub>2</sub><sup>+</sup>, P<sup>+</sup> and As<sup>+</sup>-implanted Si<sub>0.8</sub>Ge<sub>0.2</sub> epilayers are also investigated. The Si capping grown on the top of the Si<sub>1-x</sub>Ge<sub>x</sub> layers are adopted to improve the property of the nickel silicide Ohmic contacts. By using this method, the agglomeration occurred in the silicidation film is suppressed and the electrical characteristics are improved. Additionally, the morphological stability of the nickel germanosilicide after aging at temperature of 400°C is also discussed.

In Chapter 6, important conclusions are drawn. They are (1) the growth and characterization of the Si<sub>1-x</sub>Ge<sub>x</sub>, GaAs and ZnSe epilayers on Si (100) substrates are systematically studied. (2) The mechanism of interface-blocking is proposed to reduce the threading dislocations in the Si<sub>1-x</sub>Ge<sub>x</sub> and Ge epilayers on Si substrates and experimentally are demonstrated. (3) The high-quality epitaxial Ge layers on a Si substrate are achieved. (4) High-quality of GaAs and ZnSe epilayers grown on Si using Ge/Ge<sub>x</sub>Si<sub>1-x</sub>/Si buffer structure are successfully substantiated. (5) The properties of nickel germanosilicide contact on Si<sub>1-x</sub>Ge<sub>x</sub> are also investigated and improved.

### 1.6 References

- [1] David L. Harame, David C. Ahlgren, Douglas D. Coolbaugh, James S. Dunn, Gregory G. Freeman, John D. Gillis, Robert A. Groves, Gregory N. Hendersen, Robb A. Johnson, Alvin J. Joseph, Seshardi Subbanna, Alan M. Victor, Kimball M. Watson, Charles S. Webster, and Peter J. Zampardi, "Current status and future trends of SiGe BiCMOS technology", *IEEE Trans. Electron Devices*, vol. 48, no. 11, 2575, (2001).

- [2] R. Calarco, M. Fiordelisi, S. Lagomarsino, F. Scarinci, "Near-infrared metal-semiconductor-metal photodetector integrated on silicon", *Thin Solid Films* **391**, 138, (2001).

- [3] L. Colace, G. Masini, F. Galluzzi, G. Assanto, G. Capellini, L. Di. Gaspare, E. Palange and F. Evangelisti, "Metal-semiconductor-metal near-infrared light dector based on epitaxial Ge/Si", *Appl. Phys. Lett.* **72**, 3175 (1998).

- [4] N. J. Collier and J. R. A. Cleaver, "Novel dual-gate HEMT utilising multiple split gates", *Microelectronic Engineering* **41/42**, 457 (1998).

- [5] D. Eason, J. Ren, Z. Yu, C. Hughes, J. W. Cook, Jr., J. F. Schetzina, N. A. El-masry, Gene Cantwell, William C. Harsh, "Blue and green light-emitting diode structures grown by molecular beam epitaxy on ZnSe substrates", *J. Crystal Growth* **150**, 718 (1995).

- [6] B.S. Meyerson, "Low-temperature silicon epitaxy by ultrahigh vacuum/chemical vapor deposition", *Appl. Phys. Lett.* **48** (12), 797 (1986).

- [7] J. Eberhardt and E. Kasper, "Ni/Ag metallization for SiGe HBTs using a Ni silicide contact," *Semicond. Sci. Technol.* vol.16, L47-L49, 2001.

- [8] Mehmet C. Öztürk, Jing Liu, Hongxiang Mo and Nemanja Pesovic, "Advanced Si<sub>1-x</sub>Ge<sub>x</sub> Source/Drain and Contact Technologies for Sub-70nm CMOS," *in IEDM Tech. Dig.*, 375 (2002).

- [9] H. J. Huang, K. M. Chen, C. Y. Chang, and T. Y. Huang, "Study on Ge/Si ratio, silicidation, and strain relaxation of high temperature sputtered Co/Si<sub>1-x</sub>Ge<sub>x</sub> structures," *J.*

- Appl. Phys., vol. 88, no. 4, 1831 (2000).

- [10] B. I. Boyanov, P. T. Goeller, D. E. Sayers, and R. J. Nemanich, "Growth of epitaxial CoSi<sub>2</sub> on SiGe(001)", *J. Appl. Phys.*, vol. 86, no. 3, 1355 (1999).

- [11] Tsung-Hsi Yang, Guangli Luo Edward Yi Chang, Tsung-Yeh Yang, Hua-Chou Tseng, Chun-Yen Chang, "Study of Nickel Silicide Contact on Si/Si<sub>1-x</sub>Ge<sub>x</sub>," *IEEE Electron Device Letter*, vol. 24, no. 9, 544 (2003).

- [12] K. L. Pey, W. K. Choi, S. Chattopadhyay, H. B. Zhao, E. A. Fitzgerald, D. A. Antoniadis, and P. S. Lee, "Thermal reaction of nickel and Si<sub>0.75</sub>Ge<sub>0.25</sub> alloy," *J. Vac. Sci. Technol. A* **20** (6), 1903 (2002).

- [13] Hiroshi Iwai, Tatsuya Ohguro, Shun-ichiro Ohmi, "NiSi salicide technology for scaled CMOS," *Microelectronic Engineering* **60**, 157 (2002).

- [14] Mukai, S. Ozawa, H. Yagi, "Compatibility of NiSi in the self-aligned silicide process for deep submicrometer devices," *Thin Solid Films* **270**, 567 (1995).

- [15] Kazuo Nakajima, Shigeo Kodama, Satoru Miyashita, Gen Sazaki, and Satoshi Hiyamizu, "Growth of Ge-rich  $Si_xGe_{1-x}$  single crystal with uniform composition (x=0.02) on a compositionally graded crystal for use as GaAs solar cells", *J. Crystal Growth* **205**, 270 (1999).

- [16] Chi On Chui, Shriram Ramanathan, Baylor B. Triplett, Paul C. McIntyre, and Krishna C. Saraswat, "Germanium MOS capacitors incorporating ultrathin high-/spl kappa/ gate dielectric", *IEEE Electron Device Letter*, vol. 23, no. 8, 473 (2002).

- [17] J. W. Mathews, J. Vac. Sci. Technol. 12, 126 (1975).

- [18] S. B. Samavedam and E. A. Fitzgerald, "Novel dislocation structure and surface morphology effects in relaxed Ge/Si-Ge(graded)/Si structures", *J. Appl. Phys.* **81**, 3108 (1997).

- [19] C. S. Peng, H. Chen, Z. Y. Zhao, J. H. Li, D. Y. Dai, Q. Huang, J. M. Zhou, Y. H. Zhang, C. H. Tung, T. T. Sheng and J. Wang, "Strain relaxation of GeSi alloy with low dislocation

- density grown on low-temperature Si buffers", J. Cryst. Growth 201, 530 (1999).

- [20] Y. H. Luo, J. L. Liu, J. Wan, K. L. Wang, C. D. Moore, M. S. Goorsky, C. Chih and K. N. Tu, "Effective compliant substrate for low-dislocation relaxed SiGe growth", *Appl. Phys. Lett.* **78**, 1219 (2001).

- [21] A. Sakai, K. Sugimoto, T. Yamamoto, M. Okada, H. Ikeda, Y. Yasuda and S. Zaima, "Reduction of threading dislocation density in SiGe layers on Si (001) using a two-step strain-relaxation procedure", *Appl. Phys. Lett.* **79**, 3398 (2001).

- [22] H. C. Luan, D. R. Lim, K. K. Lee, K. M. Chen, J. G. Sandland, K. Wada and L. C. Kimerling, "High-quality Ge epilayers on Si with low treading-dislocation densities", *Appl. Phys. Lett.* **75**, 2909 (1999).

- [23] S. Yu. Shiryaev, F. Jenson and J. W. Peterson, "On the nature of cross-hatch patterns on compositionally graded  $Si_{1-x}Ge_x$  alloy layers", *Appl. Phys. Lett.* **64** ,3305 (1994).

- [24] H. Kawanami "Heteroepitaxial technologies of III-V on Si", *Solar Engergy Materials & Solar Cells*, **66** (2001) 479-486.

- [25] J. A. Carlin, S. A. Ringel, E. A. Fitzgerald, M. Bulsara and B. M. Keyes, "Impact of GaAs buffer thickness on electronic quality of GaAs grown on graded Ge/GeSi/Si substrates", *Appl. Phys. Lett.* **76**, no.14, 1884 (2000).

- [26] M. Yamaguchi, *J. Mater. Res.* **6**, 376 (1991).

- [27] R. K. Ahrenkiel, M. M. Al-Jassim, B. Keyes, D. Dunlavy, K. M. Jones, S. M. Vernon, and T. M. Dixon, "Minority Carrier Lifetime Of GaAs On Silicon", *J. Electrochem. Soc.* **137**, 996 (1990).

- [28] R. Venkatasubramanian, M. L. Timmons, J. B. Posthill, B. M. Keyes, and R. K. Ahrenkiel, "High Quality GaAs on Si using SiGe/Ge buffer layers", *J. Cryst. Growth* **107**, 489 (1991).

- [29] A. Freundlich, M. Leroux, J. C. Grenet, A. Leycuras, G. Neu, and C. Verie, Proc. 8th Eur. Comm. Photovoltaic Solar Energy Conf. (1988), p. 1522.

- [30] T. Soga, M. Kawai, K. Otsuka, T. Jimbo, and M. Umeno, Proc. 2 nd World Conf. on Photovoltaic Solar Energy Conversion (1998), p. 3733.

- [31] G. Wang, G. Y. Zhao, T. Soga, T. Jimbo, and M. Umeno, "Effect of H plasma passivation on the optical and electrical properties of GaAs-on-Si", *Jpn. J. Appl. Phys.*, Part 2, **37**, L1280 (1998).

- [32] M.T. Currie, S. B. Samavedam, T. A. Langdo, C. W. Leitz, and E. A. Fitzgerald, "Controlling threading dislocation densities in Ge on Si using graded SiGe layers and chemical-mechanical polishing", *Appl. Phys. Lett.* **72**, 1718 (1998).

- [33] S. Yu. Shiryaev, F. Jenson and J. W. Peterson, "On the nature of cross-hatch patterns on compositionally graded  $Si_{1-x}Ge_x$  alloy layers", *Appl. Phys. Lett.* **64**, 3305 (1994).

- [34] W. Li, Laaksonen, J. Haapamma, and M. Pessa, "Growth of device-quality GaAs layer directly on (001) Ge substrates by both solid-source and gas-source MBE", *J. Crystal Growth* **227-228**, 104-107 (2001).

- [35] R. M. Sieg, S. A. Ringel, S. M. Ting, E. A. Fitzgerald, and R. N. Sacks, "Anti-Phase Domain-Free Growth of GaAs on offcut (001) Ge Substrates by Molecular Beam Epitaxy With Suppressed Ge Outdiffusion", *J. Electron. Mater.* Vol. 27, No. 7, 900 (1998).

- [36] M. A. Haase, J. M. Depuydt, and H. Chang, "Blue-green laser diodes", *Appl. Phys. Lett.* **59**, 1272 (1991).

- [37] W. Xie, D. C. Grillo, R. L. Gunshor, M. Kobayashi, G. C. Hua, and N. Otsuka, "Blue/green *pn* junction electroluminescence from ZnSe-based multiple quantum-well stru"tures", *Appl. Phys. Lett.* **60**, 463 (1992).

- [38] L. H. Kuo, L. Salamanca Riba, B. J. Wu, G. M. Haugen, J. M. Depuydt, G. Hofler, and H. Cheng, "Generation of degradation defects, stacking faults, and misfit dislocations in ZnSe-based films grown on GaAs", *J. Vac. Sci. Technol.* B **13**, 1694 (1995).

- [39] J. Luyo-Alvarado, M. Meléndez-Lira, M. López- López, I. Hernandez-Calderón, M. E. Constantion, H. Navarro-Contreras, M. A. Vidal, Y. Takagi, K. Samonji, and H. Yonezu,

- "Optical and structural characterization of ZnSe films grown by molecular beam epitaxy on GaAs substrates with and without GaAs buffer layers", *J. Appl. Phys.* **84**, 1551 (1998).

- [40] M. López-López, A. Guillen-Cervantes, Z. Rivera-Alvarez, and I. Hernandez-Calderón, "Hillocks formation during the molecular beam epitaxial growth of ZnSe on GaAs substrates", *J. Cryst. Growth* **193**, 528 (1998).

- [41] G. Bratina, L. Vanzetti, A. Bonani, L. Sorba, J. Paggel, A. Franciosi, T. Peluso, and L. Tapfer, "Structural properties of ZnSe/GaAs(100) heterostructures with engineered band offsets", *J. Cryst. Growth* **159**, 703 (1996).

- [42] Toru Aoki, Motohiko Morita, Daiji Noda, Yoichiro Nakanishi, Yoshinori Hatanaka and Naoto Azuma, "ZnSe epitaxial growth on Si(100) and Ge(100) by H-radical assisted MOCVD", *Applied Surface Science* **113/114**, 23 (1997).

- [43] N. Mino, M. Kobayashi, M. Konagai, and K. Takahashi, "Epitaxial growth of high quality ZnSe on Si substrates by molecular beam epitaxy and application to dc electroluminescent cells", *J. Appl. Phys.* **58**, 793 (1985).

- [44] R. M. Park and H.A. Mar, "Molecular beam epitaxial growth of high quality ZnSe on (100) Si", *Appl. Phys. Lett.* **48**, 529 (1986).

- [45] L.T. Romano, J. Knall, R. D. Bringans and D. K. Biegelsen, "Misfit dislocations in ZnSe grown on vicinal Si(001) substrates", *Appl. Phys. Lett.* **65**, 869 (1994).

- [46] R. D. Bringans, D. K. Biegelsen, L. E. Swarts, F. A. Ponce and J. C. Tramontana, "Effect of interface chemistry on the growth of ZnSe on the Si (100) surface", *Phys. Rev. B* **45**, 13400 (1992).

- [47] H. Shang, K-L Lee, P. Kozlowski, C. D'Emic, I. Babich, E. Sikorski, M. Ieong, H-S. P. Wong, K. Guarini, and W. Haensch, "Self-aligned n-channel germanium MOSFETs with a thin Ge oxynitride gate dielectric and tungsten gate", *IEEE Electron Device Letter*, Vol. **25**, no. 3, 135 (2004).

- [48] N. Wu, Q. Zhang, C. Zhu, D. S. H. Chan, A. Du, N. Balasubramanian, M. F. Li, A. Chin,

J. K. O. Sin, and D-L Kwong, "A TaN-HfO/sub 2/-Ge pMOSFET with NovelSiH/sub 4/ surface passivation", *IEEE Electron Device Letter*, Vol. **25**. no.9, 631 (2004).

Fig. 1.1 Lattice constants vs linear thermal expansion coefficients of IV, III-V and II-VI.