### 國立交通大學

## 電子工程學系 電子研究所碩士班

碩士論文

適用於 H. 264 HDTV 解碼器之有效率動作補償記憶體架構

A Bandwidth-Efficient Motion Compensation Memory

Organization for H.264 HDTV Decoder

學生: 侯康正

指導教授: 李鎮宜教授

中華民國 九十五 年 七 月

#### 適用於 H. 264 HDTV 解碼器之有效率動作補償記憶體架構

# A Bandwidth-Efficient Motion Compensation Memory Organization for H.264 HDTV Decoder

研究生:侯康正 Student:Kang-Cheng Hou

指導教授:李鎮宜 Advisor: Chen-Yi Lee

國立交通大學電子工程學系電子研究所碩士班碩士論文

#### A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

**Electronics Engineering**

July 2006

Hsinchu, Taiwan, Republic of China

中華民國 九十五 年 七 月

#### 適用於 H. 264 HDTV 視訊標準之動作補償記憶體架構

學生:侯康正 指導教授:李鎮宜 教授

# 國立交通大學 電子工程學系 電子研究所碩士班

#### 摘要

在視訊解碼的領域中,H.264/AVC 是由 ITU-T/ISO 所提出新的視訊標準。由於 H.264/AVC 高壓縮率以及視訊品質的提昇,使得 H.264/AVC 是目前最受歡迎的標準。由 於數位電視的風行,而主要著重於視訊資料品質的 H.264 Main Profile 規格也漸漸被重視。因此對於高畫面的解析度上高速解碼及畫面品質的提昇是最重要的挑戰。而視訊解碼標準中,動作補償(Motion Compensation)架構一向是最重要的部份也是整個系統的核心所在。在 Main Profile 規格裡面寫了加強視訊品質而加入新的功能,例如:雙向預測、加權預測、直接預測編碼。在本論文中,針對支援 Main Profile 規格設計動態補償架構以符合高速的規格以及高品質的解析度。對於 H.264 解碼器中我們提出了有效的動作補償模組來提昇速度。此外,對於動作補償中小數點內插器的架構,我們提出了 2D 擴充行列式方法(Extended-2D Column Major Approach)以及新的架構來有效率的降低解碼器所需要的頻寬以及降低整個小數點內插器的複雜度。新的架構也合併了兩種 block 格式(Luma 以及 Chroma)的小數點內插器,使得這兩種格式都可以使用相同的架構。我們所提出的小數點內插器架構比起其他的架構可以有效降低複雜度 20%,而且所需要的頻寬可以降低約 50%~60%來提昇動作補償的速度。

此外,動作補償系統需要從外部記憶體 SDRAM 存取大量資料,因此對於外部記憶體的存取是影響整個解碼器系統的關鍵。增加外部 BUS 上的頻寬將會提昇動作補償的效能以及支援更大畫面的解析度。一般的記憶體控制器並沒有對於多媒體方面的各個模組作設計。在本篇論文中將會對於存取外部記憶體提出適用於 HDTV H.264 解碼器有效率的記憶體控制器。將可以支援解碼器中的模組對於外部存取的需求,例如:動態補償及去方塊效應濾波器(De-blocking filter)。實現彈性、高速的動態補償系統架構設計。另一方面,我們所提出的記憶體控制器可以支援 H.264 多重參考圖片的技術,並且可以有效率的利用單一記憶體即可存取所需要的參考圖片資料。我們所提出的記憶體架構可以提昇 BUS 利用率(Bus Utilization)至90%以上。透過我們所提出的動作補償架構以及記憶體架構,整個系統對於記憶體讀取的頻寬將會改善40%~50%。最後,我們解碼器系統 Throughput 在高位元率的壓縮比下可以也可以符合標準所訂定的 HDTV 規格。

A Bandwidth-Efficient Motion Compensation Memory

Organization for H.264 HDTV Decoder

Student: Kang-Cheng Hou Advisor: Dr. Chen-Yi Lee

Department of Electronics Engineering

Institute of Electronics

National Chiao Tung University

#### **ABSTRACT**

H.264/AVC is the new video coding standard of ITU-T Video Coding Experts Group (VCEG) and the ISO/IEC Moving Picture Experts Group (MEPG). H.264 is most popular video standard due to high compress rate and better quality. In particular, the baseline profile of H.264/AVC has been accomplished progressively. In recently year, digital TV is widely adopted so that H.264's Main Profile focus on quality of video will be attended gradually. Therefore, the improvement of resolution and quality for large frame will become important issue. Motion compensation always is important module and kernel of system in video standard. For enhancing quality of video, H.264's main profile adopts new features such as Bi-prediction, weighted prediction and direct mode coding. In this thesis, a bandwidth-efficient motion compensation system is proposed for high definition resolution supported by main profile in H.264/AVC. Presently, we provide a novel structure of motion compensation system in main profile to improve system throughput. Furthermore, we propose Combined Luma/Chroma interpolator architecture in motion compensation and a novel data-reuse technique: Ectended-2D Column Major Approach. Both Luma and Chroma MB

can be interpolated by combined Luma/Chroma interpolator. A combined Luma/Chroma interpolator is proposed in order to save area, which achieves approximately 44% cost reduction. Additionally, an Extend-2D column major approach is presented, which improves  $50\% \sim 60\%$  required bandwidth within decoder.

The video decoder should deal with large amount of data from external memory due to a real-time high-quality decoding demand. Therefore, both limited access time and bandwidth of memory access on BUS is bottleneck of entire video decoder. However, general memory controller may be not design for multimedia applications. In this thesis, the bandwidth-efficient memory controller architecture is proposed for H.264 decoder to increase limited bandwidth over external bus. The memory controller can support all module of H.264 decoder such as motion compensation and de-blocking filter, etc. Besides, the multiple reference pictures technique can be supported by our proposed memory controller, and can employ unique memory to store all required data for video decoder. About simulation results, the bus utilization can be improved up to 90% for our proposed memory controller. The bandwidth of memory access may be improved to 50% ~ 60% for entire video decoder adopting our proposed bandwidth-efficient motion compensation memory organization. Finally, the system throughput that is proposed by our proposed architecture can meet with specification with HDTV standard at high bit-rate.

## Acknowledgements

I would like to express my deepest gratitude to my advisor Dr. Chen-Yi Lee for his sophomore enthusiastic guidance and encouragement to overcome many difficulties throughout the research, and wholeheartedly give him and his family my best wishes.

Moreover, I would like to appreciate NSC for their financial support, my senior Si2 multimedia group mates for their discussions and comments during my research, especially for Yi-Hong Huang, and Jiun-Yan Yang. In addition, I would like to thank all members of Si2 group of NCTU for plenty of fruitful assistance and all engineers of CIC for their CAD supporting.

Finally, I give the greatest respect and love to my family and all my friends for their support and encouragement, and I want to express my highest appreciation. Sincerely, I hope them happy and happy forever.

# **Contents**

| Chapter 1 | Introduction                                 | 1            |

|-----------|----------------------------------------------|--------------|

| 1.1       | Motivation                                   | 1            |

| 1.2       | Thesis Organization                          | 2            |

| Chapter 2 | Motion Compensation Algorithm of             |              |

|           | H.264/AVC's Main Profile                     | 4            |

| 2.1       | Profiling                                    | 4            |

| 2.2       | Motion Compensation Process Flow             | 5            |

| 2.3       | Inter Prediction Algorithm for H.264/AVC's N | Main Profile |

|           |                                              | 7            |

| 2.3.1     | 1 Bi-directional Prediction                  | 8            |

| 2.3.2     | 2 Multiple Reference Frames                  | 10           |

| 2.4       | Motion Vector Prediction                     | 12           |

| 2.4.1     | 1 Traditional MV Prediction                  | 12           |

| 2.4.2     | 2 Direct Mode Coding                         | 14           |

| 2.5       | Fractional Interpolation                     | 15           |

| 2.6       | Weighted Prediction                          | 17           |

| 2      | .6.1 Explicit Mode                                   | 18  |

|--------|------------------------------------------------------|-----|

| 2      | .6.2 Implicit Mode                                   | 20  |

| 2.7    | Analysis                                             | 22  |

| 2.8    | Comparison for MC of Previous Standards              | 26  |

| 2.9    | Summary                                              | 27  |

| Chapte | r 3 A Bandwidth-efficient Motion Compensati          | ion |

|        | Architecture Design                                  | 29  |

| 3.1    | Motion Compensation Engine for H.264/AVC's Mai       | n   |

|        | Profile                                              | 30  |

| 3.2    | Motion Vector Predictor Design                       | 32  |

| 3      | .2.1 MVp Prediction Module                           | 33  |

| 3      | .2.2 Direct Mode Coding Design                       | 36  |

| 3.3    | Bandwidth-Efficient Factional Interpolator Design    | 38  |

| 3      | .3.1 Data Reuse Technique                            | 39  |

| 3      | .3.2 Combined Luma/Chroma Interpolation Architecture | 44  |

| 3      | .3.3 Simulation Results                              | 53  |

| 3.4    | Weighted Prediction                                  | 55  |

| 3.5    | Summary                                              | 56  |

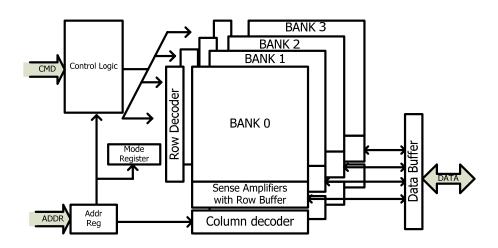

| Chapter 4 | 4 Bandwidth-Efficient SDRAM Mem                   | ory        |

|-----------|---------------------------------------------------|------------|

|           | Controller                                        | 58         |

| 4.1       | SDRAM Module Characteristics                      | 59         |

| 4.1.      | .1 Basic Concept of SDRAM                         | 59         |

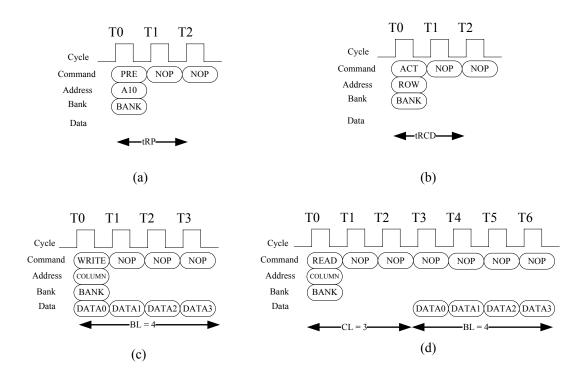

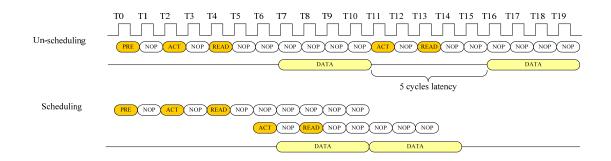

| 4.1.      | .2 Access Latency Analysis                        | 64         |

| 4.2       | Memory Controller Organization                    | 67         |

| 4.2.      | .1 Memory Access Scheduling                       | 68         |

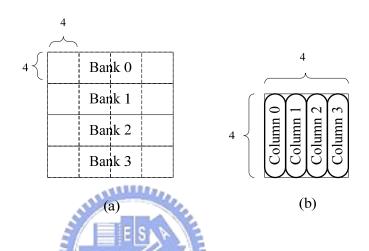

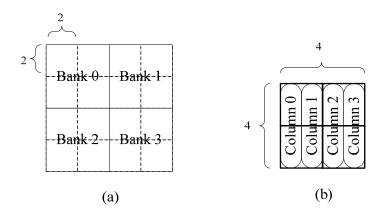

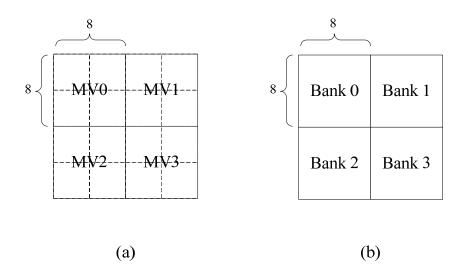

| 4.2.      | .2 Memory Arrangement                             | 70         |

| 4.2.      | .3 Multiple Reference Prediction                  | 74         |

| 4.2.      | .4 Architecture of bandwidth-efficient Memory Con | troller 76 |

| 4.3       | Simulation Results                                |            |

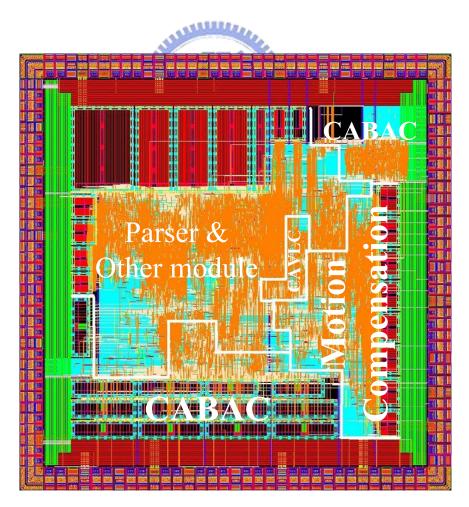

| Chapter : | 5 Chip Implementation                             | 90         |

| 5.1       | Chip Specification                                | 90         |

| Chapter ( | 6 Conclusion                                      | 93         |

| Bibliogra | phy                                               | 95         |

## **List of Figures**

| Figure 2.1 H.264 software (JM 9.2) profiling on ARM 7 processor                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2.2 The general score of motion compensation for H.264/AVC's main profile                                                                                                                                                                                                                                                    |

| Figure 2.3 General structure of H.264 encoder.                                                                                                                                                                                                                                                                                      |

| Figure 2.4 General structure of H.264 decoder                                                                                                                                                                                                                                                                                       |

| Figure 2.5 Macroblock partitions and sub-macroblock partitions                                                                                                                                                                                                                                                                      |

| Figure 2.6 Example using Bi-prediction: (a) previous/future (b) previous (c) future                                                                                                                                                                                                                                                 |

| Figure 2.7 The current block is predicted by $MV_{L0}$ and $MV_{L1}$ motion vector using  Bi-prediction                                                                                                                                                                                                                             |

| Figure 2.8 Bi-prediction with multiple reference pictures                                                                                                                                                                                                                                                                           |

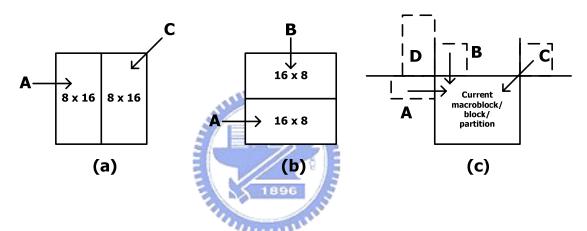

| Figure 2.9 (a) directional prediction for 8 x 16 block size, (b) directional prediction for 16 x 8 block size, (c) median prediction                                                                                                                                                                                                |

| Figure 2.10 Direct mode prediction for B slices                                                                                                                                                                                                                                                                                     |

| Figure 2.11 (a) luma half sample with 6-tap FIR, (b) luma horizontal/vertical quarter sample with bilinear filter, (c) luma diagonal quarter sample with bilinear filter (d) chroma sample with bilinear filter. Upper-case letters indicate the full samples and lower-case letter indicates the interpolated fractional samples 1 |

| Figure 2.12 Bit rate value between baseline and main profile                                                                                                                                                                                                                                                                        |

| Figure 2.13 PSNR between Baseline and Main profile                                                                                                                                                                                                                                                                                  |

| Figure 2.14 The proportion of integer/fraction motion vector for luma component in H.264/AVC main profile                                                                                                                                                                                                                           |

| Figure 2.15 The proportion of integer/fraction motion vector for chroma component in H.264/AVC main profile                                                                                                                                                                                                                         |

| Figure 3.1 The block diagram of H.264/AVC main profile decoder system                                                                                                                                                                                                                                                               |

| Figure 3.2 N | Motion compensation architecture for HDTV H.264/AVC main profile decoder                                                                                    |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.3 M | MV in shaded and oblique line region must be stored in row-FIFO32                                                                                           |

| Figure 3.4 M | Motion vector generator                                                                                                                                     |

| Figure 3.5 N | Neighboring motion vectors required for decoding all motion vectors in current macroblock                                                                   |

| Figure 3.6   | (a) block size position index, (b) directional prediction table (16x8, 8x16), (c) median prediction table (16x16, 8x8), (d) median prediction table (4x4)35 |

| Figure 3.7   | Pre-scalefactor generator design                                                                                                                            |

| Figure 3.8   | (a) Division free replacement (b) Multiplication-free replacement                                                                                           |

| Figure 3.9 ( | a) 4x4-block and 9x9 interpolation search windows for luma component interpolation (b) overlap region between neighboring blocks                            |

| Figure 3.10  | (a) 2x2-block and 3x3 interpolation search windows for chroma component interpolation (b) overlap region between neighboring blocks                         |

| _            | (a) row-major interpolating order (b) column-major interpolating order39  Luma component interpolation: (a) Interpolating block 4 and (b) Interpolating     |

| Figure 3.13  | block 3 (c) Interpolating block 6                                                                                                                           |

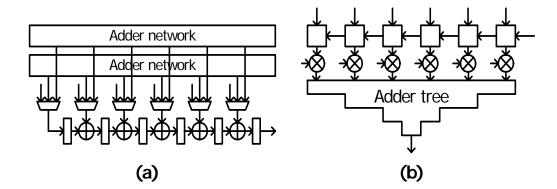

| Figure 3.14  | (a) Adder-chain based [23] (b) Adder-tree based [24] 1-D linear interpolator design                                                                         |

| Figure 3.15  | Separate 1-D interpolator design (no parallel)                                                                                                              |

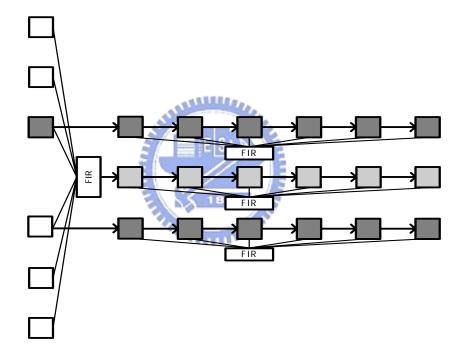

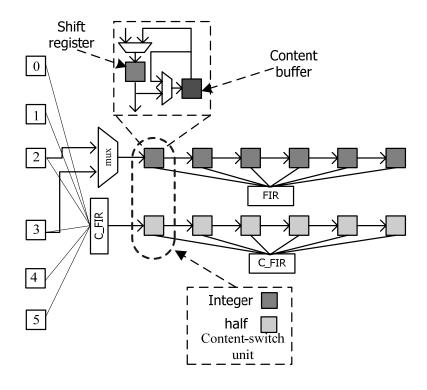

| Figure 3.16  | 4-parallel separate 1-D luma interpolator with content buffer                                                                                               |

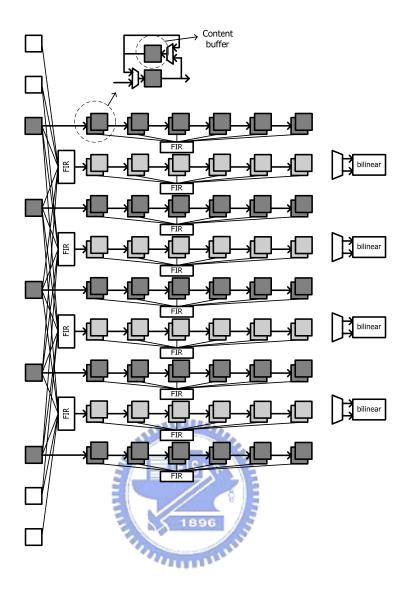

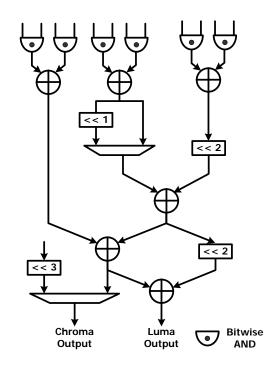

| Figure 3.17  | Combined luma/chroma interpolator architecture                                                                                                              |

| Figure 3.18  | Combined luma/chroma interpolator unit                                                                                                                      |

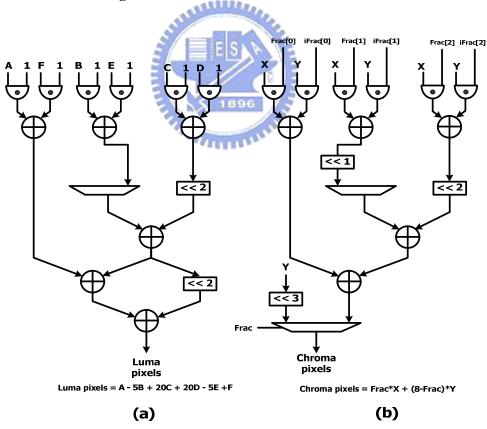

| Figure 3.19  | Combined luma/chroma FIR. 52                                                                                                                                |

| Figure 3.20  | (a)Process path for luma component interpolation (b) Process path for chroma component interpolation                                                        |

| Figure 3.21  | Required bandwidth for different data-reuse approach                                                                                                        |

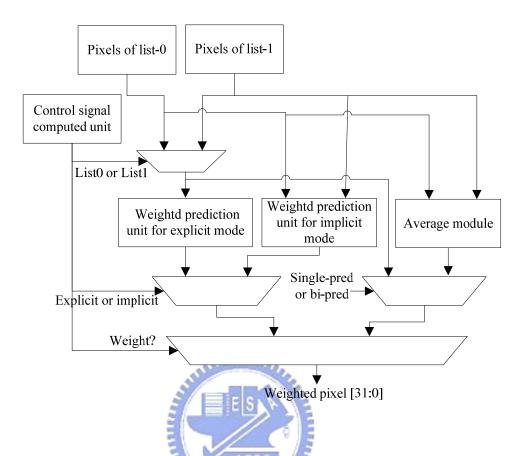

| Figure 3.22 A weighted prediction block diagram                                                                                                                                                                                             | 56 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.1 Modern SDRAM architecture                                                                                                                                                                                                        | 59 |

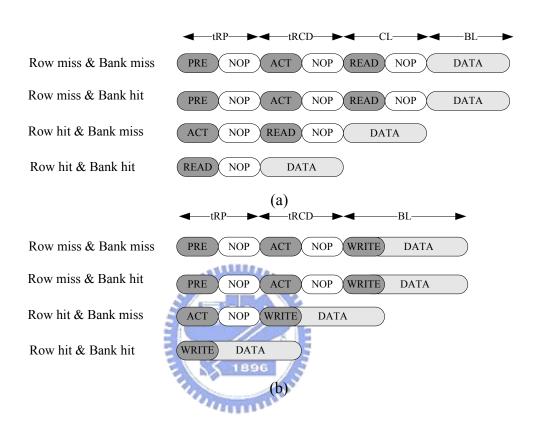

| Figure 4.2 SDRAM resource utilization of several commands: (a) PRECHARGE (b)  ACTIVE (c) WRITE (d) READ                                                                                                                                     | 62 |

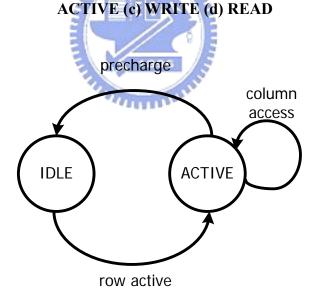

| Figure 4.3 Simplified bank state diagram.                                                                                                                                                                                                   | 62 |

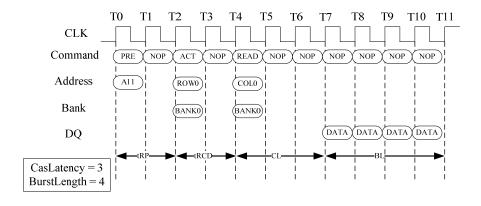

| Figure 4.4 Burst read operation with CasLatency=3 and BurstLength=4                                                                                                                                                                         | 63 |

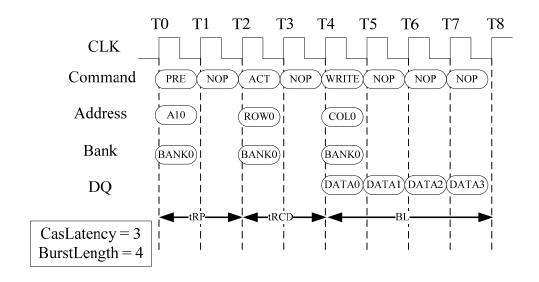

| Figure 4.5 Burst write operation with CasLatency=3 and BurstLength=4.                                                                                                                                                                       | 64 |

| Figure 4.6 Access latency for CL=2 (a) read access latency, (b) write access latency                                                                                                                                                        | 65 |

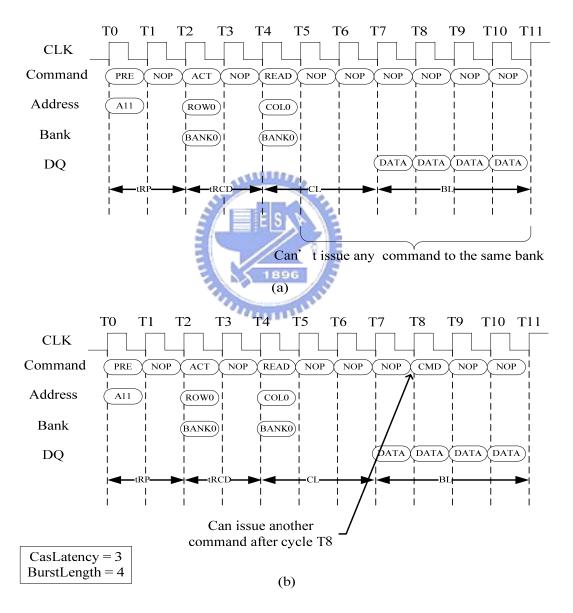

| Figure 4.7 (a) READ command with auto precharge, in the precharge period (tRP),  SDRAM cannot issue another command in the same bank (ex: bank 0). (b)  READ command without auto precharge, another command can be issued uthe tRP is met. |    |

| Figure 4.8 Two un-scheduling and scheduling read memory accesses for bank-miss and row-hit                                                                                                                                                  | 69 |

| Figure 4.9 Luma block (a) one 16 x 16 block arrangement (b) one 4 x 4 block-0 arrangement for MB-0                                                                                                                                          | 71 |

| Figure 4.10 Chroma block (a) one 8 x 8 block arrangement (b) one 4 x 4 block consist o block 0-3 arrangement                                                                                                                                |    |

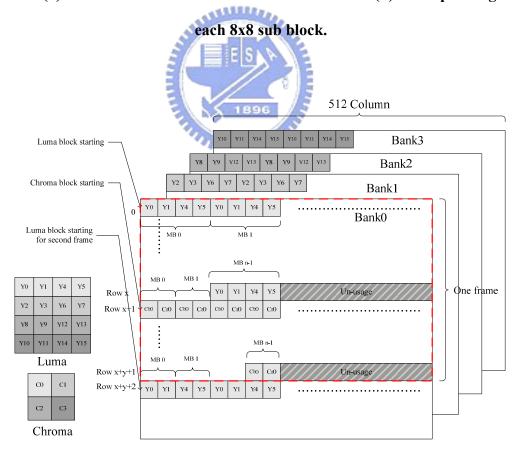

| Figure 4.11 (a) Co-located motion vector allocation in frame (b) corresponding bank for each 8x8 sub block                                                                                                                                  |    |

| Figure 4.12 The pixels arrangement of one frame are stored of SDRAM. The arrangeme of other banks is the same as bank0                                                                                                                      |    |

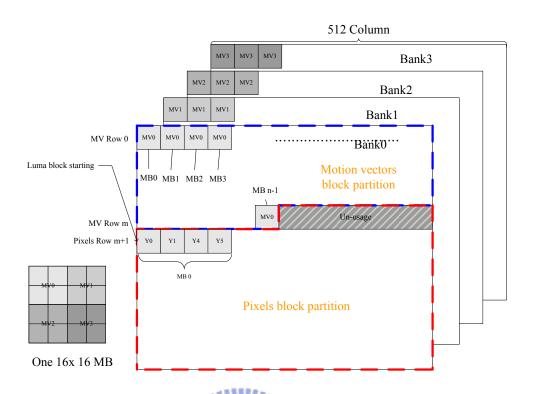

| Figure 4.13 The motion vector arrangement of one frame are stored of SDRAM. The arrangement of other banks is the same as bank0                                                                                                             | 73 |

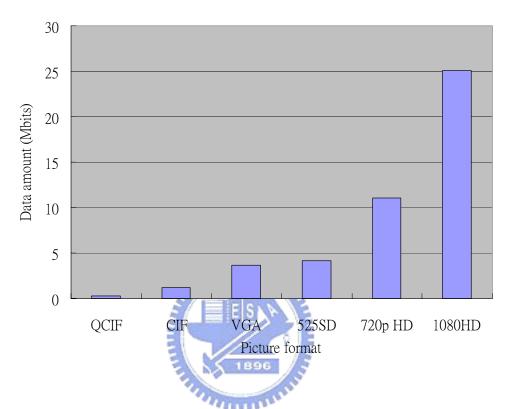

| Figure 4.14 Data amount of one decoding frame for different picture format                                                                                                                                                                  | 75 |

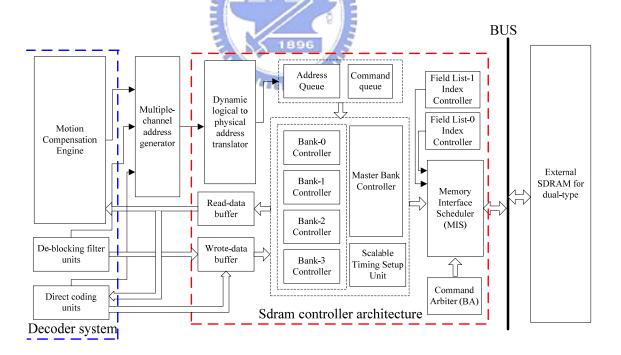

| Figure 4.15 Architecture of bandwidth-efficient memory controller for H.264/AVC                                                                                                                                                             | 76 |

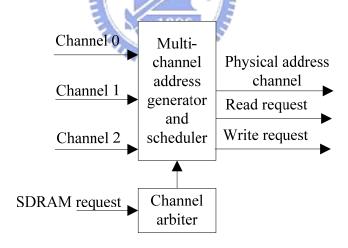

| Figure 4.16 Multi-channel address generator                                                                                                                                                                                                 | 77 |

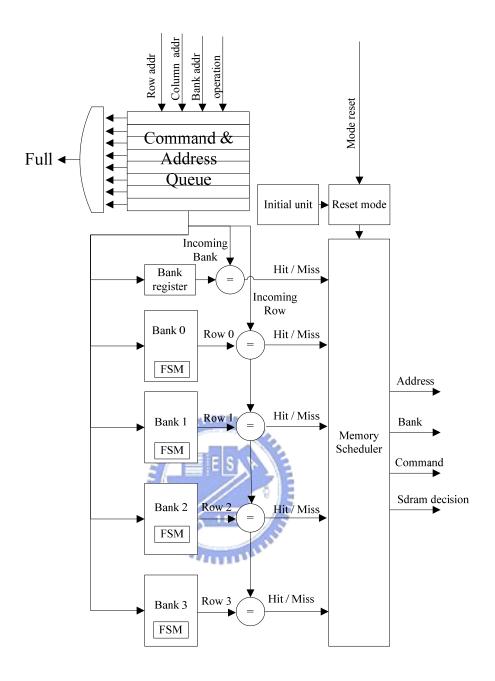

| Figure 4.17 Command and address queue and access status detection                                                                                                                                                                           | 79 |

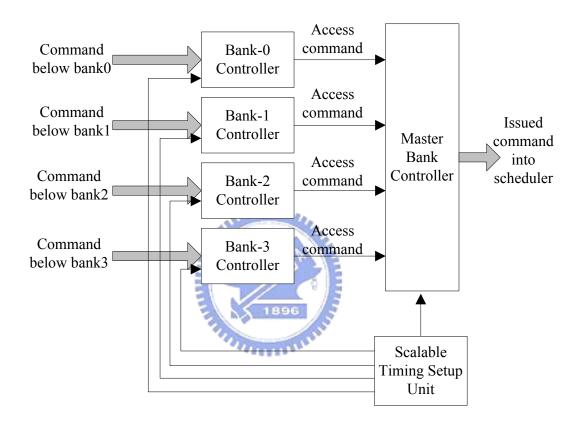

| Figure 4.18 The structure of bank controllers, master bank controller and timing unit                                                                                                                                                       | 80 |

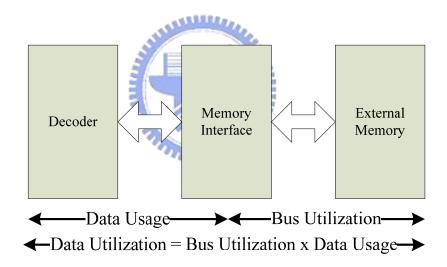

| Figure 4.19  | System level analysis relation                                                                    |

|--------------|---------------------------------------------------------------------------------------------------|

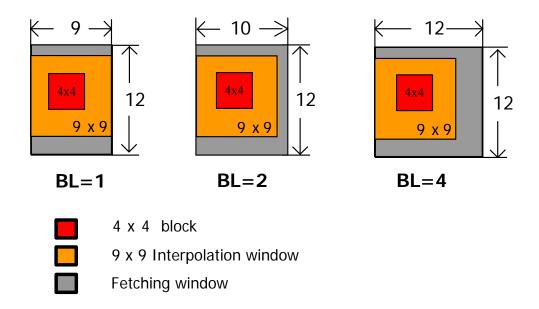

| Figure 4.20  | Fetching windows of 4x4 block between different burst length                                      |

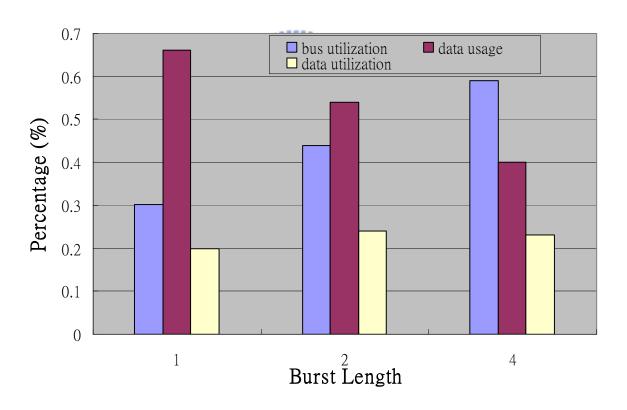

| Figure 4.21  | Unscheduled Bus utilization, Data usage and Data utilization for different burst length in memory |

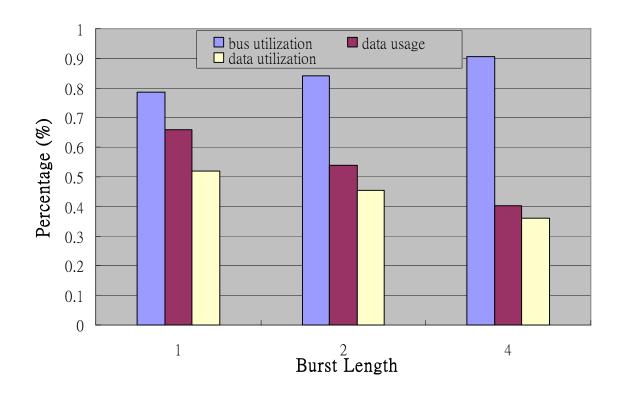

| Figure 4.22  | Scheduled Bus utilization, Data usage and Data utilization for different burst length in memory.  |

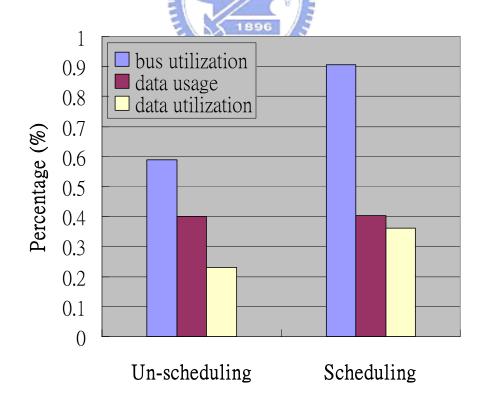

| Figure 4.23  | The data utilization between un-scheduling and scheduling                                         |

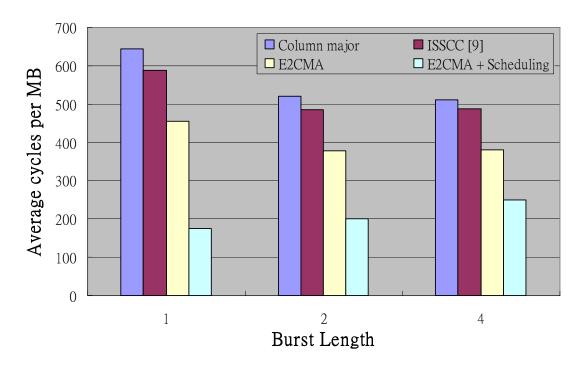

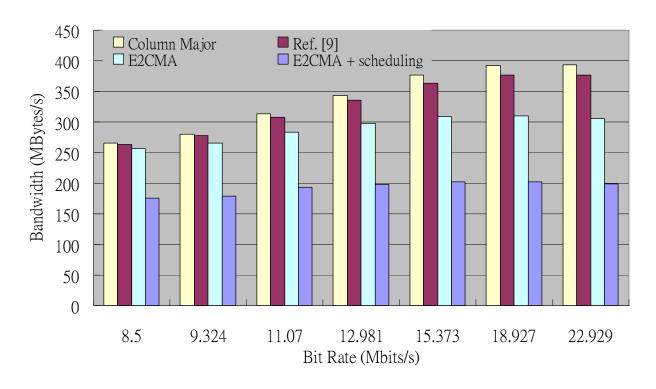

| Figure 4.24  | Average access cycles per MB between different burst length for access under BUS                  |

| Figure 4.25  | The bandwidth of memory access under external BUS among different bit-rate                        |

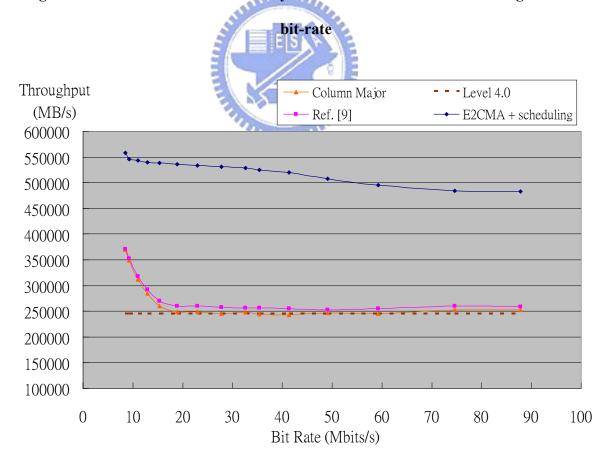

| Figure 4.26  | The throughput of motion compensation for different data-reuse approach when                      |

|              | operating frequency is 100Mhz.                                                                    |

| Figure 5.1 ( | CHIP photo for H.264/AVC main profile decoder92                                                   |

## **List of Tables**

| Table 2.1 comparison with different standard                                                                        |

|---------------------------------------------------------------------------------------------------------------------|

| Table 3.1 Analysis for different interpolating approach                                                             |

| Table 3.2 Comparison of execution cycles for different architectures                                                |

| Table 3.3 Simulation results of required memory bandwidth (MByte/s) per MB by using extend-2D column-major approach |

| Table 3.4 Comparison of interpolator architecture with other designs                                                |

| Table 4.1 CAS latency 65                                                                                            |

| Table 4.2 Characteristics of READ/WRITE access                                                                      |

| Table 4.3 Required memory size for different picture format supporting multiple reference pictures set 16           |

| Table 5.1 H.264/AVC main profile decoder specification for motion compensation90                                    |

| Table 5.2 Synthesis results of H.264/AVC's main profile decoder including SRAM91                                    |

| Table 5.3 On/Off-Chip memory size for different module in H.264 main profile decoder92                              |

# Chapter 1 Introduction

#### 1.1 Motivation

The early video technology such as MPEG-1, mainly approach targets on CD-ROM based video storage. Afterward, MPEG-2 standard is published, which can be backward compatible with MPEG-1, serves a wider range of application including video-on-demand (VOD), DVD and high definition TV. Up to now, H.264/AVC [1] is the newest generation video coding standard developed by the Joint Video Team (JVT), which consists of experts from ITU-T VCEG and ISO/IEC MPEG. The H.264/AVC can save about 25-45% bit-rate compared to MPEG-4 Advanced Simple Profile (ASP). Recently, digital video processing technologies have been widely applied in the many video systems, such as videophone, digital TV and VCR, multimedia, etc. In the future, a high-quality HDTV system would integrate the functions of a computer, the internet, and entertainment, so it should become a popular product in the market. Furthermore, digital TV is widely adopted by the next-generation digital video broadcasting (DVB) technology. However, the amount of video data is very huge for these applications. For example, high-quality HDTV system with 1080HD format produces 1,504Mbits/s when the frame rate is 30Hz at level 4 in a real-time system. Therefore, H.264/AVC provides Main profile which supports many efficient coding tools to obtain enormous compression rate. The ultra high coding efficiency comes from many new features, including sub-pixel inter prediction with variable block size (VBS) and multiple reference

frames, intra prediction, bi-prediction, weighted prediction, and entropy coding—CAVLC and CABAC. According to the runtime analysis of H.264/AVC decoder software, the motion compensation can use up to 55% of total decoding time. Thus, motion compensation can dominate performance of entire H.264/AVC decoder. Furthermore, the bandwidth requirement of decoder is extremely high and a bandwidth-efficient design is necessary to achieve high-quality real-time decoding processes for high definition approach.

For motion compensation, we need to refer the previous frame data from memory for motion compensations. Generally, the coding performance becomes better using more temporal information by motion compensation. High definition TV requires enormous data transmission particular in frame memory, and the memory overhead becomes high over bus. For real-time operation, the memory data must be accessed during a limited processing time. The memory design and its addressing become a bottleneck for entire video decoder. Because the multiple reference pictures is supported by H.264/AVC's main profile, the block data controlling and addressing become more complex. How to access the frame memory for real-time operation is an important issue, particular for HDTV systems. Thus, a memory access controller that efficiently communicates with external memory is essentially provided over the entire video decoder to manage data transfer and access conflict.

#### 1.2 Thesis Organization

The thesis is organized as follows. The algorithm description and analysis of H.264/AVC's main profile is introduced and discussed in Chapter 2. In Chapter 3, the proposed bandwidth-efficient motion compensation architecture for H.264/AVC video decoder is described first. Then, the motion compensation engine for supporting H.264/AVC's main profile specification is illustrated. We also propose the novel data-reuse technique to reduce the required bandwidth particularly in H.264/AVC fractional motion compensation.

Chapter 4 presents frame and motion vector memory organization including memory access controller for external SDRAM. We apply a memory scheduling technique to reduce the access latency under external BUS and provide a flexible data arrangement method to improve data hit rate. The CHIP implementation is given in Chapter 5. Finally, conclusion is shown in Chapter 6.

# Chapter 2 Motion Compensation Algorithm of H.264/AVC's Main Profile

Similar to previous video standard, motion compensation is an important part in a video decoder system. The feature is that the current picture is predicted by previous decoded pictures without requiring extra bit-streams. Thus, the transmission bandwidth can be reduced efficiently without degrading visual quality. Hence, H.264/AVC is used in a wide range of applications due to its better coding efficiency.

In this Chapter, we will introduce a basic structure and concept of H.264/AVC coding standard in Section 2.2. In H.264/AVC, The main profile is almost a superset of the baseline profile. Specifically, additional tools provided by main profile are Bi-directional predictions, direct mode coding, multiple reference frames and weighted prediction for motion compensation part. The detailed algorithms of features related to motion compensation are described in the following sections. Finally, we will list differences among video coding standards such as MPEG-2, MPEG-4, etc in Section 2.6.

#### 2.1 Profiling

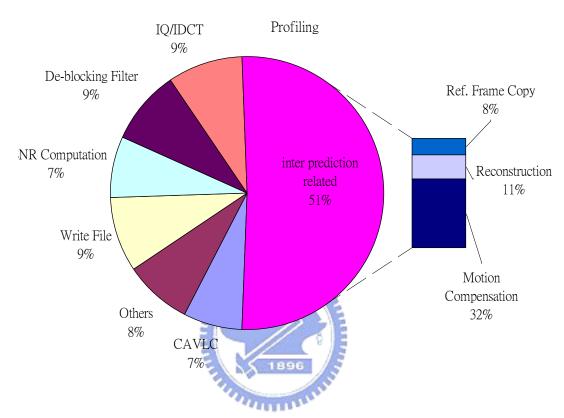

Figure.2.1 shows the profiling of H.264/AVC's main profile on ARM-7 processor. The reference software we adopt is JM 9.2 [3]. Specifically, inter prediction related modules, which occupy 51 % of the entire video decoder, include motion compensation, reconstruction,

and reference frame copy. If we improve this part efficiently, total performance of the decoder system will be increased as well. This dominated part can be greatly reduced by parallel processing, data-reuse scheme, or pipeline processing on the ASIC design.

Figure 2.1 H.264 software (JM 9.2) profiling on ARM 7 processor

#### 2.2 Motion Compensation Process Flow

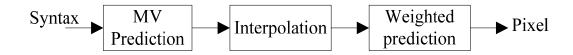

The score of motion compensation process flow has been explained as Figure 2.2. Data relating to inter prediction are received from syntax parser. It is processed to pixels through several functional units consist of MV prediction, Interpolation and Weighted Prediction.

Figure 2.2 The general score of motion compensation for H.264/AVC's main profile

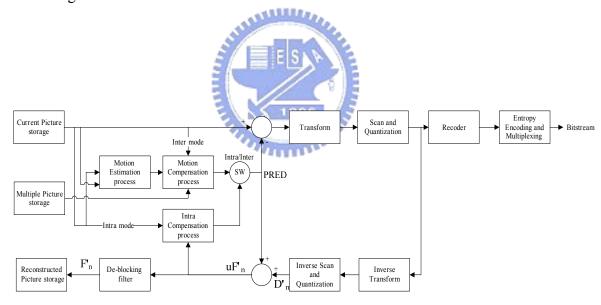

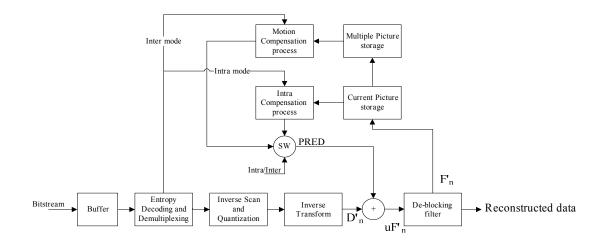

Figure 2.3 shows the basic block diagram of H.264/AVC encoding block diagram. The block diagram of decoder is shown in Figure 2.4. With the exception of the de-blocking filter, we can find that most of the basic functional components (prediction, transform, quantization, entropy coding, etc) exist in previous standards such as MPEG-1, MPEG-2, MPEG-4, H.263 but important changes of H.264 occur in the details of each functional block. Because the decoder is our research topic, we will focus on decoder process flow. The decoder receives a compressed bitstream from channel receiver side and thereby entropy decodes the data elements to produce a set of quantized coefficients X. These coefficients are scaled and inverse transformed to D'<sub>n</sub>. The motion compensation (MC block) reconstructs the PRED according to previous decoded data. The PRED adds D'<sub>n</sub> to produce uF'<sub>n</sub> prior to the deblocking filter.

Figure 2.3 General structure of H.264 encoder.

Figure 2.4 General structure of H.264 decoder

# 2.3 Inter Prediction Algorithm for H.264/AVC's Main Profile

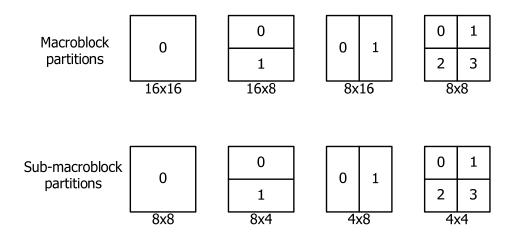

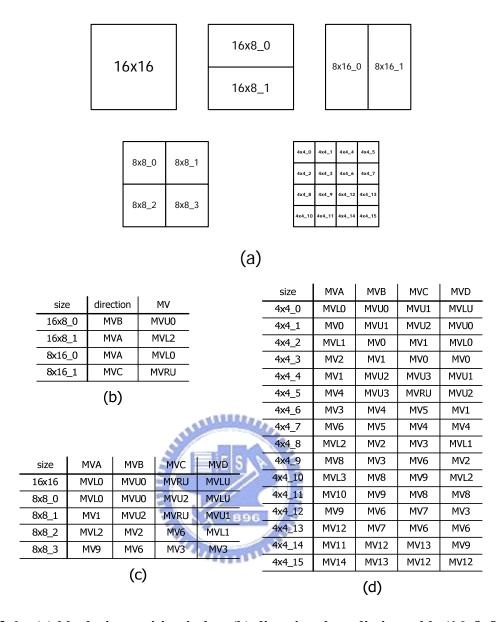

The inter prediction of H.264/AVC's main profile includes tree-structured hierarchical macroblock partitions and more flexible block size selection called as *variable block size* (*VBS*) compared with previous standards [1][2][4]. In case of motion compensated prediction, macroblocks are predicted from the image signal of transmitted reference images. For this purpose, each macroblock can be divided into smaller partitions such as 16x16, 16x8, and 8x8. The corresponding 8x8 sub-macroblock is further divided into partitions with block sizes of 8×4, 4×8 or 4×4. For each sub-macroblock partition, a motion vector may be independently selected and coded, but the reference picture index and prediction type of the sub-macroblock is used for all sub-macroblock partitions. Chroma components use the same partition as luma components. The smallest block size selection could reach as small as 4x4 and 2x2 for luma and chroma component respectively. For each macroblock partition, a reference picture index, prediction type (list-0, list-1, bi-pred), and a motion vector may be independently selected and coded. Figure 2.5 illustrates all types of partitions.

Figure 2.5 Macroblock partitions and sub-macroblock partitions

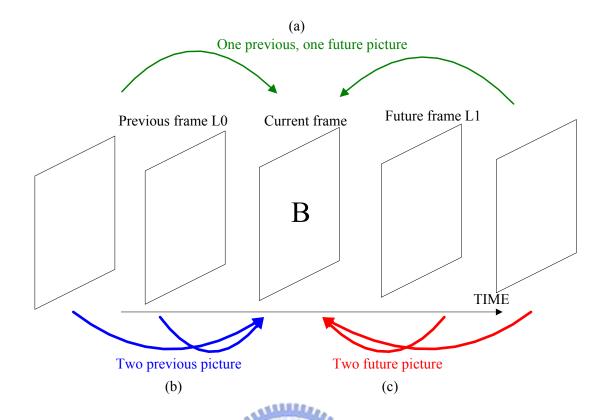

#### 2.3.1 Bi-directional Prediction

A bi-directional prediction is main feature provided by H.264/AVC main profile. Bi-prediction uses two lists of previously decoded reference pictures, list-1 and list-0. The reference picture is previous or future decoded pictures for B-slices. Each macroblock of B slices may be predicted from previous reference picture (list-1) and future reference picture (list-0). In P slices, only single directional prediction is used, and the allowable reference pictures are list-0. In B slices, list-0 and list-1 of reference pictures are considered. For B-slices, single directional prediction using either list 0 or list 1 is allowed, or bi-prediction using both list 0 and list 1 is allowed. Figure 2.6 gives three examples to illustrate Bi-prediction: (a) one previous and one future reference (similar to B-picture prediction in previous MPEG video standard), (b) two past references and (c) two future references.

Figure 2.6 Example using Bi-prediction: (a) previous/future (b) previous (c) future

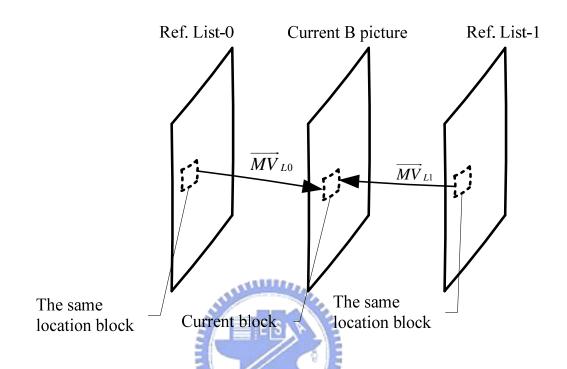

In the bi-prediction, a reference block is created from list-0 and list-1 reference pictures. Two motion compensated reference areas are obtained from a list-0 and list-1 picture respectively, and two separate motion vectors are required. Each sample of the prediction block is calculated as an average of motion vector of the list-0 and list-1 prediction sample. Except when using Weighted Prediction, the following equation is used:

$$Pred(i, j) = (Pred 0(i, j) + Pred 1(i, j) + 1) \gg 1$$

(2.2)

Where Pred0(i, j) and Pred1(i, j) are prediction samples derived from the list-0 and list-1 reference pictures and Pred(i, j) is a bi-predictive sample. After calculating each prediction sample, the reconstructed samples are a summation of residual and predicted data that is decoded by entropy decoding and intra/inter prediction respectively. The list-0 and list-1 motion vectors in bi-predictive macroblocks or blocks are predicted from neighboring motion vectors that have the same temporal direction. For instance, a motion vector for the

current macroblock pointing to a previous picture is predicted from other neighboring motion vectors that also point to previous pictures. It is illustrated as Figure 2.7. The prediction of motion vector is introduced as next section.

Figure 2.7 The current block is predicted by  $MV_{L0}$  and  $MV_{L1}$  motion vector using Bi-prediction

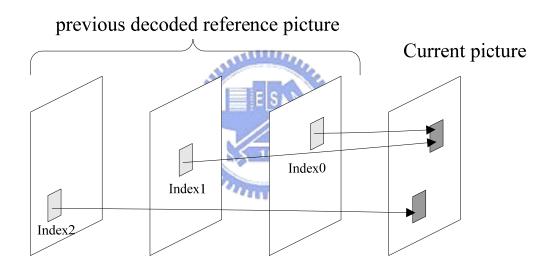

#### 2.3.2 Multiple Reference Frames

In H.264/AVC, multiple reference frames may be used for inter-prediction [4], with a reference frame index coded to indicate which multiple reference frames are used. When bi-prediction is used by applying weighted prediction, the list 0 and the list 1 predictors are averaged together to form a final predictor. For each sub-macroblock partition, a motion vector may be independently selected and coded, but the reference frame index and prediction type of the sub-macroblock is used for all of the sub-macroblock partitions. Figure 2.8 shows the bi-prediction with multiple reference frames. An index is a reference frame parameter. An additional picture reference parameter has to be transmitted together with the motion vector in

bitstream. H.264 uses picture order count (POC) to indicate relative distances between coded pictures and reference pictures. POC is used for scaling motion vectors in direct modes, and for weighting factor derivation in WP implicit mode that will be introduced in the following sections. Adopting multiple reference frames increases the access frequency according to a linear model: 25% complexity increase for each added frame. A negligible gain (less than 2%) in bit rate is observed for low and medium bit rates, but more significant savings can be achieved for high bit rate sequences (up to 14%) [4].

Figure 2.8 Bi-prediction with multiple reference pictures

Up to five different reference frames can be used for inter-picture coding resulting in better subjective video quality and more efficient coding. Providing multiple reference frames can also help make the H.264 bitstream more error resilient. The error resilient tools are supported by extended profile in H.264/AVC, which will not be discussed in this thesis. Note that this feature leads to increased memory requirement for both the encoder and the decoder since previously decoded and reconstructed multiple reference frames must be maintained in

memory. For storing large pixels of several reconstructed reference frames, the huge memory size is required such as SDRAM. Therefore, we will propose an efficient memory allocation method and SDRAM controller architecture so that remained decoded pictures can be efficiently stored in single external memory. The related concept will be introduced in Chapter 4.

#### 2.4 Motion Vector Prediction

The prediction for the decoded macroblock is determined by the set of motion vectors (MV) that are associated with that macroblock. The motion vectors indicate the position within the set of previously decoded frames from which each block of pixels will be predicted. A motion vector is generated by motion vector prediction. In baseline profile, motion vector is only generated by traditional MV prediction that includes median and directional prediction. Motion vector prediction of H.264/AVC's main profile supports new predictable method in Bi-predictive slices: direct mode, which except for traditional MV prediction. We introduce these motion vector generations in the following sub-sections.

#### 2.4.1 Traditional MV Prediction

The Motion vector is generated from motion vector difference (MVD) and motion vector prediction (MVP). The associated equations are expressed by (2. 1).

$$MVx = MVDx + MVPx$$

$$MVy = MVDy + MVPy$$

(2.1)

MVD is decoded from universal variable length decoder (UVLD) and MVP is predicted according to neighboring motion vectors. MVP algorithm, of which concept is similar to that for MPEG-4, contains directional prediction for 16 x 8 or 8 x 16 block size and median prediction for other block sizes. The detail of MVP decision is shown in Figure 2.9. Equation

of median prediction is expressed by (2. 2). The location of MVA, MVB, MVC, MVD which neighboring current block is depends on different block sizes. For example, MVA is a left neighboring block and MVC is a right-upper neighboring block when block size is 8x16 as Figure 2.9 (a) shows. The definition of neighboring motion vector is illustrated as Figure 2.9 for different block sizes. In addition, some boundary conditions or exceptions have to be handled carefully. For instance, when MVC is not available, its value is replaced by MVD. We do not go into details of those trivial boundary conditions over here.

$$MVP = median(MVA, MVB, MVC)$$

(2.2)

Figure 2.9 (a) directional prediction for 8 x 16 block size, (b) directional prediction for 16 x 8 block size, (c) median prediction

In addition to the motion-compensated block size described in Figure 2.5, a P macroblock can also be coded to P\_SKIP mode. For this coding mode, neither residual signal nor motion information is transmitted. That is, motion vectors are only decided according to MVP. The reconstructed data is obtained similar to that of macroblock type P\_16x16. Macroblocks coded in P\_SKIP are often located in large area with no scene change or slow motion. Besides the above techniques, H.264/AVC also supports multiple reference frames, weighted prediction and direct mode for B slice. These tools greatly improve coding efficiency. Application of de-blocking filter is a well-known method to improve image quality

by alleviating blocking artifacts. The de-blocking design in H.264/AVC is brought within motion-compensated prediction loop and the improvement in quality becomes more conspicuous.

#### 2.4.2 Direct Mode Coding

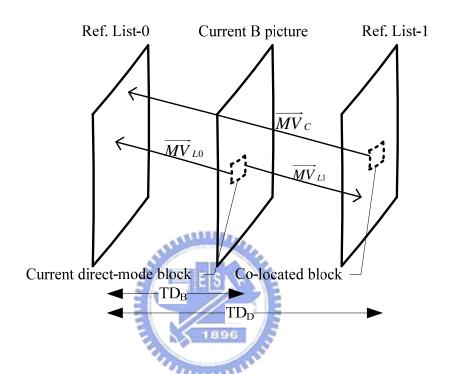

Figure 2.10 Direct mode prediction for B slices

Direct mode is another method for motion vector prediction. The direct-mode macroblock does not require such side information but derives reference frame, block size, and motion vector data from the subsequent inter pictures. Figure 2.10 is shown to illustrate the process of direct mode coding. This mode superimposes two prediction signals. One prediction signal is derived from the future inter picture and the other comes from a previous picture. The direct mode uses bidirectional prediction and allows residual coding of the prediction error. The forward and backward motion vectors  $\overline{MV}_{L0}$  and  $\overline{MV}_{L1}$  of this mode are derived from the motion vectors  $\overline{MV}_{C}$  used in the co-located macroblock of the future picture Ref. list-1. Note that the direct-mode macroblock uses the same partition as the co-located

macroblock. The prediction signal is calculated by a linear combination of two blocks that are determined by the forward and backward motion vectors pointing to two reference pictures list-0 and list-1. When using multiple reference picture prediction, the forward reference picture for the direct mode Ref. list-1 is chosen to be the future inter picture with the co-located macroblock. The forward and backward motion vectors for direct-mode blocks are calculated as following equation:

$$X = \frac{\left(16384 + \text{abs}\left(\frac{TD_D}{2}\right)\right)}{TD_D}$$

(2.3)

$$ScaleFactor = Clip(-1024, 1023, (TD_B \times X + 32) \gg 6)$$

$$(2.4)$$

$$\overrightarrow{MV}_{L0} = \left(ScaleFactor \times \overrightarrow{MV} + 128\right) \gg 8$$

(2.5)

$$\overrightarrow{MV}_{L1} = \overrightarrow{MV}_{L0} - \overrightarrow{MV} \tag{2.6}$$

Where  $\overline{MV}_{L0}$  is the forward motion vector,  $\overline{MV}_{L1}$  is the backward motion vector, and  $\overline{MV}_C$  represents the motion vector of the co-located block in the future inter picture. For B pictures,  $TD_D$  is the temporal distance between the previous and the future inter picture, and  $TD_B$  is the distance between the current B picture and the previous inter picture. In that case, the actual reference picture Ref. list-0 (which is also a reference picture for the co-located macroblock of the following picture) is used for the calculation of the temporal distances  $TD_D$  and  $TD_B$ . And when both the current macroblock and its co-located are in frame mode,  $TD_B$  is the temporal distance between the current B frame and the reference frame Ref. list-0, and  $TD_D$  is the temporal distance between the future reference frame Ref. list-0 and Ref. list-1.

#### 2.5 Fractional Interpolation

H.264/AVC main profile standard also supports high motion resolution that reaches quarter motion accuracy for luma component and eighth one for chroma component. This can

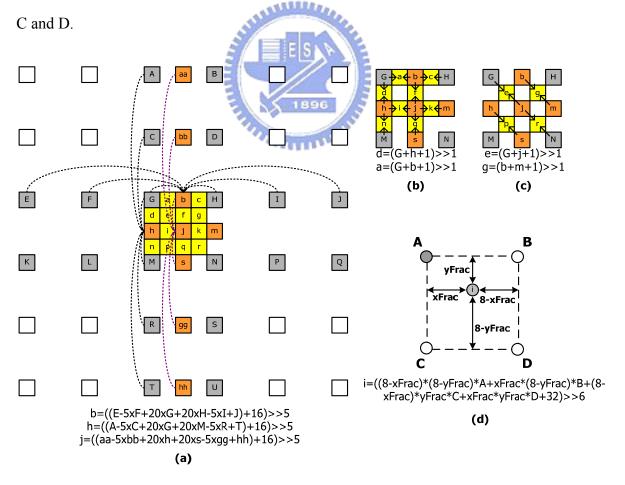

be found firstly in advances profile of MPEG-4 Visual standard; however, H.264/AVC reduces the complexity of interpolation processing comparison with MPEG-4 standard. Luma half sample interpolation is generated from integer-position samples using a 6-tap symmetrical Finite Impulse Response (FIR) filter with weights (1, -5, 20, 20, -5, 1). Once all the half-pel samples are available, the quarter samples are produced by linear interpolation using bilinear filter. Luma samples interpolation is shown in Figure 2.11(a)-(c). Quarter-pel resolution motion vectors in the luma component require eighth-sample resolution vectors in the chroma component assuming 4:2:0 chrominance format. Interpolated samples at eighth-sample intervals in chroma component are generated using bilinear interpolator illustrated in Figure 2.10 (d), and the displacement can achieve one-eighth accuracy. Each sub-sample position *i* is a linear combination of the neighboring integer sample positions A, B,

Figure 2.11 (a) luma half sample with 6-tap FIR, (b) luma horizontal/vertical quarter sample with bilinear filter, (c) luma diagonal quarter sample with bilinear filter, (d) chroma sample with bilinear filter. Upper-case letters indicate the full samples and lower-case letter indicates the interpolated fractional samples

From mathematical equations, they are both 2-D interpolation for luma and chroma interpolation. However, based on hardware implementation, these equations can be separated into two 1-D to reduce hardware cost, namely, horizontal filter first and than vertical one, or vice verse. In chapter 3, we will propose a novel architecture of interpolation to combine luma and chroma interpolation so that cost and complexity can be improved in ASIC design.

#### 2.6 Weighted Prediction

The weighted prediction (WP) tool has been adopted in the H.264/AVC Main and Extended profiles to improve coding efficiency by applying a multiplicative weighting factor and an additive offset to the motion compensated prediction [5] [6]. While the concept of applying a weighting factor to a reference picture prediction is not new, the inclusion of the WP tool in the H.264 standard marks the first time such a feature has been incorporated into an international video compression standard. Weighted prediction also compensates the brightness difference so that the reference frame is more strongly correlated to the current frame. The WP allows arbitrary multiplicative weighting factors and additive offsets to be applied to reference picture predictions in both P and B pictures. The WP tool is particularly effective for coding fading sequences. When applying to a single prediction, as in P pictures, WP is similar to a leaky prediction, which has been previously proposed for error resiliency. Leaky prediction becomes a special case of WP, with the scaling factor limited to the range  $0 \le a \le 1$ . The WP also allows negative scaling factors, and scaling factors greater than

one. A key difference of H.264's WP tool from previous proposals involving weighted prediction for compression efficiency is the association of the reference picture index with the weighting factor parameters, which allows for efficient signaling of these parameters.

Use of weighted prediction is indicated in the sequence parameter set for P slices using the weighted\_pred\_ide field, and for B slices using the weighted\_bipred\_ide field. There are two WP modes -- explicit mode, which is supported in P and B slices, and implicit mode, which is supported in B slices only. A single weighting factor and offset are associated with each reference picture index for each color component in each slice. In explicit mode, these WP parameters may be coded in the slice header. In implicit mode, these parameters are derived based on relative distance of the current picture and its reference pictures. For each macroblock or macroblock partition, the weighting parameters are based on the reference picture index (or indices in the case of bi-prediction) of the current macroblock or macroblock partition. The reference picture indices are either coded in the bitstream or may be derived, e.g., for skipped or direct mode macroblocks. The use of the reference picture index to signal which weighting parameters to apply is bit-rate efficient, as compared to requiring a weighting parameter index in the bitstream, because the reference index is already available based on other required bitstream fields.

#### 2.6.1 Explicit Mode

Use of explicit mode WP is indicated by weighted pred flag equal to 1 in the picture parameter set of P slices, or by weighted bipred idc equal to 1 in B slices. In explicit mode, the WP parameters are coded in the slice header for each coded slice. A multiplicative weighting factor and additive offset for each color component may be coded for each of the allowable reference picture in list 0 for P slices and B slices. The number of allowable reference pictures list 0 indicated picture parameter is in the num ref idx 10 active minus1, for and list 1 for В slices is indicated

num ref idx 11 -active minus1. The weighting factors and offsets used in a particular slice are included in the slice header when explicit mode WP is used. The allowable range of parameter values is constrained to 16-bit arithmetic operations in the inter prediction process. The dynamic range and precision of the weighting factors can be adjusted using the luma log weight denom and chroma log - weight denom fields, which are the binary logarithm of the denominator of the luma and chroma weighting factors, respectively. Higher values of the log weight denominator allow more fine-grained weighting factors but require additional bits for coding the weighting factors and limit the range of the effective scaling. For each allowable reference picture index in list 0, and for B slices also in list 1, flags are coded which indicate whether or not weighting parameters are present in the slice header for that reference picture index, separately for the luma and chroma components. If the weighting parameters are not present in the slice header for a given reference picture index and color component, a default weighting factor equivalent to a scaling factor of 1 and a zero offset are used. The multiplicative weighting factors are coded as luma weight 10, luma weight 11, chroma\_weight\_10, and chroma\_weight\_11. The additive offsets are coded as luma offset 10, luma offset 11, chroma offset 10, and chroma offset 11, respectively. For fades that are uniformly applied across the entire picture, a single weighting factor and offset are sufficient to efficiently code all macroblocks in a picture that are predicted from the same reference picture. When multiple reference pictures are used, the best weighting factor and offsets generally differ during a fade for the different reference pictures, as brightness levels are more different for more temporally distant pictures. Use of the reference picture index in the selection of the weighting parameters allows the coding efficiency gain of multiple reference picture prediction to be added to the coding efficiency gain of weighted prediction. For fades that are non-uniformly applied spatially across an image sequence, e.g. for lighting changes or camera flashes, more than one reference picture index can be associated with a particular reference picture are stored by using reference picture reordering commands. This allows different macroblocks in the same picture to use different weighting factors even when predicted from the same reference picture store. In explicit mode, the same weighting parameters that are used for single prediction are used together for bi-prediction. The final inter prediction is formed for the pixels of each macroblock or macroblock partition, based on the prediction type used as follows.

Single directional prediction from list-0:

$$SampleP = Clip 1(((SampleP0 \times W_0 + 2^{LWD-1}) \gg LWD) + O_0)$$

(2.7)

Single directional prediction from list-1:

$$SampleP = Clip1(((SampleP1 \times W_1 + 2^{LWD-1}) \gg LWD) + O_1)$$

(2.8)

Bi-prediction from list-0 and list-1:

$$SampleP = Clip1(((SampleP0 \times W_0 + SampleP1 \times W_1 + 2^{LWD}) \gg (LWD + 1)) + (O_0 + O_1 + 1) \gg 1)$$

(2.9)

Where Clip1 operation is an operator that clips to the range [0, 255], W0 and O0 are the list 0 reference picture weighting factor and offset, and W1 and O1 are the list 1 reference picture weighting factor and offset, and LWD is the log weight denominator rounding factor. SampleP0 and SampleP1 are the list 0 and list 1 initial predictors, and SampleP is the weighted predictor.

#### 2.6.2 Implicit Mode

Use of implicit mode is indicated by **weighted\_bipred\_idc** equal to 2 in B slices. In WP implicit mode, weighting factors are not explicitly transmitted in the slice header, but are derived based on relative distances between the current picture and the reference pictures, based on POC. Implicit mode is used only for bi-prediction coded macroblocks and macroblock partitions in B slices, including those using direct mode. The same formula for

bi-prediction as given in the preceding explicit mode section for bi-prediction is used, except that the offset values *O0* and *O1* are equal to zero, and the weighting factors *W0* and *W1* are derived using the formulas below:

$$X = (16384 + (TD_D \gg 1))/TD_D \tag{2.10}$$

$$Z = \text{Clip3}(-1024, 1023, (TD_{\scriptscriptstyle R} \times X + 32) \gg 6)$$

(2.11)

$$W_1 = Z \gg 2 \tag{2.12}$$

$$W_0 = 64 - W_1 \tag{2.13}$$

where  $TD_B$  is difference in the POC values between the list 1 reference picture and the list 0 reference picture, clipped to the range [-128, 127] and  $TD_D$  is difference in the POC values of the current picture and the list 0 reference picture, clipped to the range [-128, 127]. Macroblocks using single prediction (list 0 or list 1) do not use implicit mode WP. Implicit mode is most useful for low bit-rate applications, or for pictures that are broken into many slices for error resiliency, where the bits needed to code the WP parameters in explicit mode become significant contributors to overall bit-rate. For Bi-prediction macroblocks where the two predictors are from opposite temporal directions, as in traditional B pictures, the implicit mode WP formula becomes an interpolation formula. For example, with a traditional PBB picture pattern, weighting factors of (2/3, 1/3) are used in the first B picture and (1/3, 2/3) are used in the second B picture. For Bi-prediction macroblocks where the two predictors are both in the same temporal direction, the implicit mode WP formula becomes an extrapolation formula. For example if one predictor is from the immediately preceding picture and the other predictor is from two pictures preceding, weighting factors of (2,-1) are used. In our design, we implement division-free hardware with WP implicit mode according to equation (2.2)-(2.4). The detailed architecture is shown in the following sections.

For the PBB picture sequence, implicit and explicit mode performed similarly for the linear fade-out pattern, both with an average coding gain of 46.2%. For a non-linear S-curve

fade-out pattern with the PBB picture sequences, explicit mode outperformed implicit mode slightly, averaging a 41.3% gain vs. a 40.9% gain. The gains were lower for the fade-ins, with explicit mode outperforming implicit mode from 28.9% to 28.4% for the linear fade-in, and from 29.1% to 26.9% for S-Curve fade-in. Besides, a simple method for determining weighting factors has been described that achieves bit-rate reductions up to 67% for fade-to-black sequences.

#### 2.7 Analysis

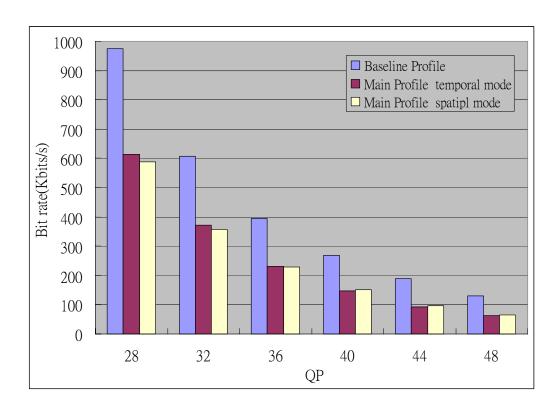

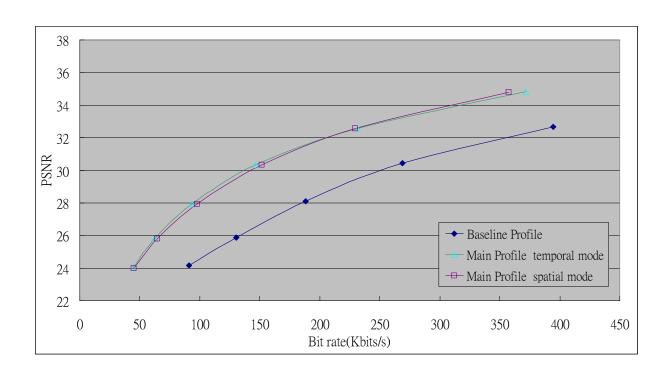

H.264/AVC main profile supports new features to improve performance such as PSNR, bit rate, and quality, etc. Analysis is performed for these features to show the improvement. For analyzed environment, a test sequence with CIF format is employed at 30fps. The frame orders are I-P-P and I-B-B-P-B-B for baseline and main profile, respectively. Figure 2.12 shows the bit rate of baseline and main profile using different Quantization Parameter (QP). From Figure 2.12, reduction of bit rate can be observed, and bit rate of main profile may save approximately 40% compared with that of baseline profile. Thus, main profile is suitable for high bit-rate system such as HDTV, HD-DVD devices.

Figure 2.12 Bit rate value between baseline and main profile

Besides, the rate-distortion of main profile is depicted as Figure 2.13. The PSNR of main profile with WP and main profile without WP are shown in the same Figure. At 200Kbps, the PSNR of the main profile is 31.8, which higher than PSNR of baseline is 28.4. Furthermore, performance of direct mode coding within main profile is illustrated as the same Figure. We can find that performance of spatial mode is a bit better than that of temporal mode in direct mode coding.

Figure 2.13 PSNR between Baseline and Main profile

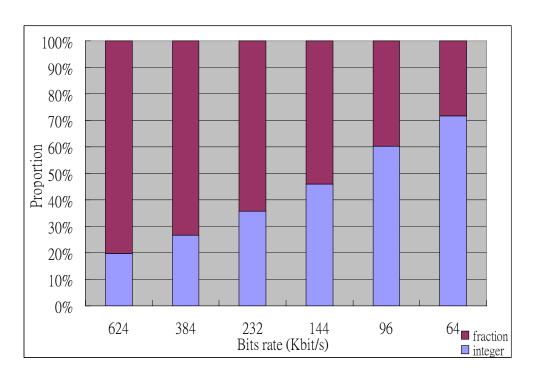

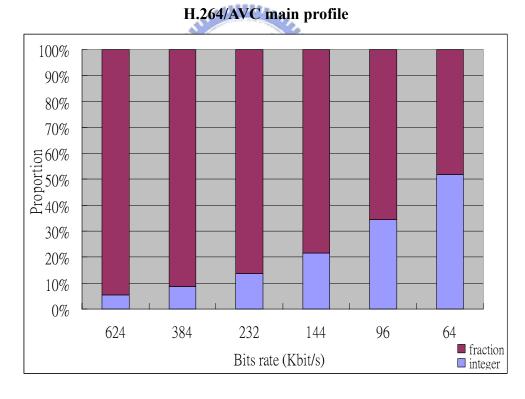

Figure 2.14 and Figure 2.15 show proportion of integer/fraction motion vector for luma and chroma component, respectively. In order to simulate the proportion, we select a general sequence with CIF format. The picture order is I-B-B-P-B-B-P-B-B. In high bit rate applications (384 kbps), the fractional motion vector occupies about 80 % and even in low bit rate (48 kbps) fractional part has a certain proportion (30 %). The higher fractional motion vector proportion means that the longer execution time is required to read pixels from external frame memory. This gap may become more obvious especially when SDRAM is used as frame memory. To reduce requisite fetching pixels from frame memory, the efficient data-reuse technique for fractional motion compensation will be proposed in Chapter 3.

Figure 2.14 The proportion of integer/fraction motion vector for luma component in

Figure 2.15 The proportion of integer/fraction motion vector for chroma component in  $\label{eq:H264/AVC} H.264/AVC \ main \ profile$

# 2.8 Comparison for MC of Previous Standards

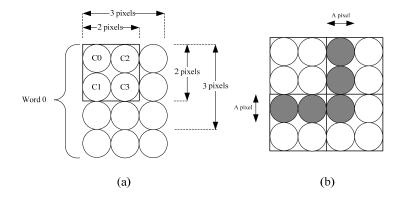

Considering the frame coding, Table 2.1 lists all fractional motion compensation features between different standards. Up to now, we can find fractional interpolation issue becomes more and more important in the state-of-the-art video coding. The interpolation window becomes larger for the same block size; namely, it requires much more cycles to interpolate each macroblock. For example, it requires 9 x 9 pixels window to interpolate luma 4 x 4-block for H.264/AVC; however, the identical size of interpolation window can be used to filter 8 x 8-block for MPEG-2 video decoder. Therefore, it's requires 1,296 pixels to interpolate 16 4 x 4-blocks. Especially note that luma and chroma interpolation for H.264/AVC are different compared with previous standards. That is, no matter what on algorithm level or hardware level, the interpolated computation sources can not be shared. Hence, the combination of luma and chroma parts could be improved to reduce gate count and we will give the discussion and implementation in Chapter 3. In addition, H.264/AVC supports direct mode coding and weighted prediction which will be not adopted by previous video standard. Therefore, novel structures of direct mode coding and weighted prediction are proposed in the same chapter.

Table 2.1 comparison with different standard

| Standard                    | MPEG-1/2                       | MPEG-4                                                | H.264@Main                                                      |  |

|-----------------------------|--------------------------------|-------------------------------------------------------|-----------------------------------------------------------------|--|

| MVp prediction              | Update from previous PMV value | Median prediction                                     | Median prediction Directional prediction Direct mode prediction |  |

| Luma block unit             | 16 x 16                        | 8 x 8                                                 | 4 x 4                                                           |  |

| Luma motion accuracy        | Half                           | Half, Quarter                                         | Half, Quarter                                                   |  |

|                             |                                | Half sample mode                                      |                                                                 |  |

|                             |                                | Bilinear                                              | Half: 6-tap FIR                                                 |  |

| Luma filter                 | Bilinear                       | Quarter sample mode                                   | Quarter: 6-tap FIR and                                          |  |

|                             |                                | Half: 8-tap FIR<br>Quarter: 8-tap FIR and<br>bilinear | bilinear                                                        |  |

| Luma interpolation window   | 17 x 17                        | 15 x 15                                               | 9 x 9                                                           |  |

| Chroma block unit           | 8 x 8                          | 4 x 4                                                 | 2 x 2                                                           |  |

| Chorma motion accuracy      | Half                           | Half, Quarter                                         | Eighth                                                          |  |

| Chorma filter               | Bilinear                       | Half sample mode                                      |                                                                 |  |

|                             |                                | Bilinear                                              | Bilinear                                                        |  |

|                             |                                | Quarter sample mode                                   |                                                                 |  |

|                             |                                | Half: 8-tap FIR<br>Quarter: 8-tap FIR and<br>bilinear |                                                                 |  |

| Chorma interpolation window | 9 x 9                          | 5 x 5                                                 | 3 x 3                                                           |  |

# 2.9 Summary

From the H.264/AVC profiling on ARM processor, we can find that an efficient hardware accelerator or ASIC design for motion compensation is crucial. For HDTV application, H.264/AVC main profile has provided several coding tools to deal with high-quality resolution. Bi-prediction and quarter-pel interpolation are proposed to improve coding efficiency. Weighted prediction is first adopted by video standard, and is a powerful tool for efficiently coding fading sequences. Bitstream size is reduced by direct mode coding which is adopted by H.264/AVC main profile for B-slices. In B-slices, inter prediction is performed by

using two frames so that motion compensation hardware are more complex. Furthermore, multiple reference frames is proposed so that memory requirement may be extremely increased. For above discussion, not only hardware accelerator but also bandwidth-efficient hardware is required to develop for high-definition system. Finally, the inter prediction for H.264/AVC and the comparison among different standards are also illustrated in this Chapter.

# Chapter 3 A Bandwidth-efficient Motion Compensation Architecture Design

In video standards, such as MPEG-1/2, MPEG-4 and H.264/AVC, motion compensation is an important part of entire decoder system, and always dominates system performance due to high computing power. Furthermore, the hardware design of motion compensation is more complex than other modules such as CAVLC, DCT, intra-prediction and De-blocking filter, etc. For HDTV application, motion compensation adopts new features which are supported by H.264/AVC main profile so that procedure and hardware of motion compensation are more and more complex in ASIC designs. Besides, inter-prediction requires large pixels of previous decoded reference frame to predict current frame, and external memory is decided as frame memory in our on-chip design. Moreover, multiple reference frames are employed to lead that more memory may be used to store pixels of several previous decoded reference frames. Thus, memory bandwidth which is data traffic under external BUS will be a bottleneck of motion compensation. A bandwidth-efficient motion compensation hardware accelerator has to be designed, which can be integrated into simplex architecture.

In this chapter, we will focus on motion compensation for high throughput and low cost designs. We propose a bandwidth-efficient motion compensation architecture which is suitable for high-quality system. Firstly, we will introduce whole bandwidth-efficient motion compensation architecture for H.264/AVC main profile. The hardware of detail module such as motion vector generation, interpolator, and weighted prediction will be discussed in

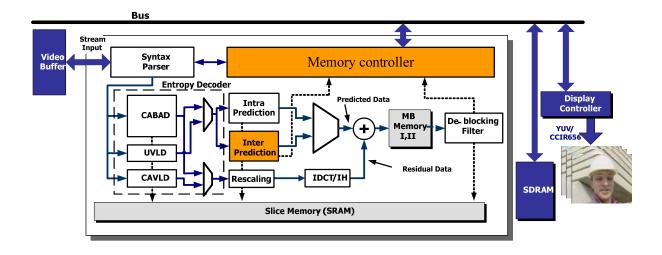

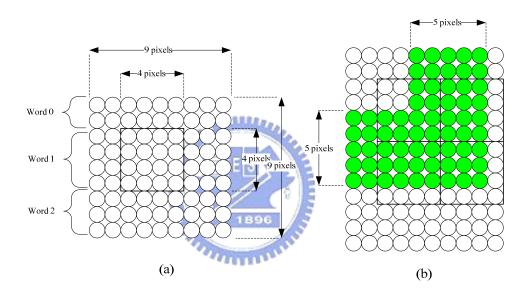

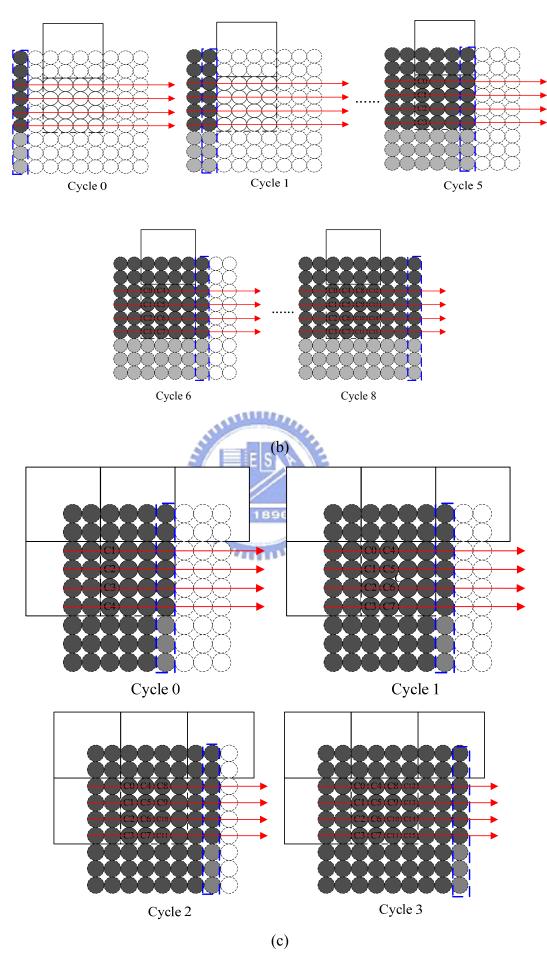

# 3.1 Motion Compensation Engine for H.264/AVC's Main Profile

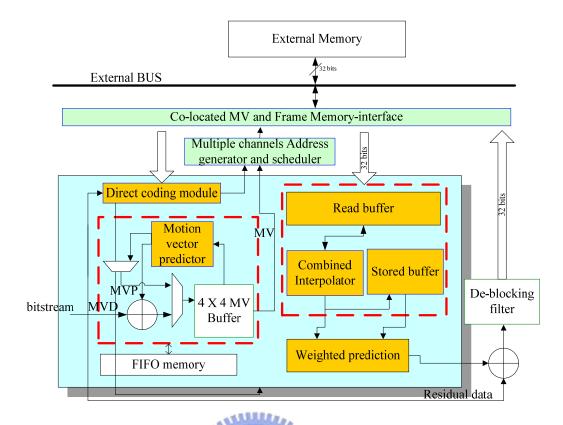

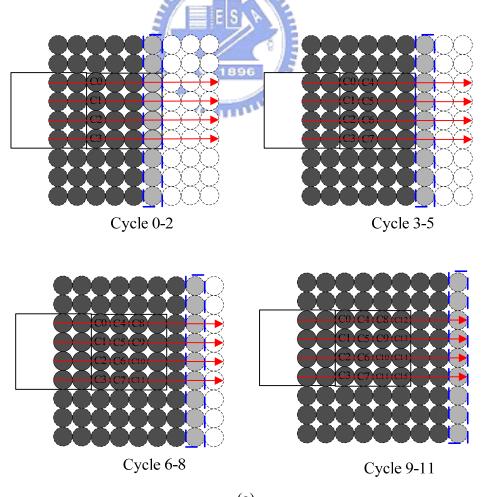

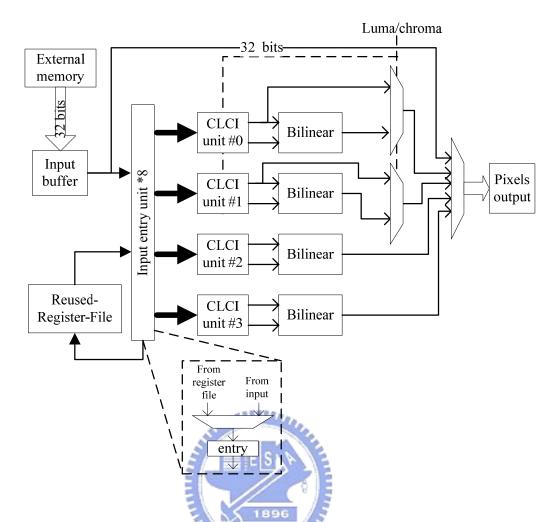

The H.264/AVC main profile decoder system is illustrated as Figure 3.1. First, the frame information in bitstream is decoded by entropy coding module includes CABAD and CAVLD. According macroblock type, the frame pixels can be decoded by intra-prediction and inter-prediction. The bus traffic is treated by memory controller which can be supported for module of video decoder. Figure 3.2 illustrates the entire bandwidth-efficient motion compensation architecture for H.264/AVC main profile. In H.264/AVC, a 4x4 block is the smallest element of the prediction block types in variable block size (VBS) and each 16x16 block can be decomposed into several 4x4 blocks. We adopt a 4x4 block-based pipeline to implement this motion compensation design in this design, because the 4x4 block is the smallest processing unit of pixels that the H.264/AVC adopts and 4x4 block-based pipeline can save the cost of storage buffer and the associated power reduction.

Figure 3.1 The block diagram of H.264/AVC main profile decoder system

Figure 3.2 Motion compensation architecture for HDTV H.264/AVC main profile

decoder

Excluding the memory controller, the proposed motion compensation architecture is presented in gray dotted area of Figure 3.2. The detailed discussion of frame memory access controller is shown in Chapter 4. The motion compensation architecture consists of three major parts that are motion vector generator (MVG), interpolator and weighted prediction. The decoded information is firstly loaded from bitstream into MVG. A MVG generates motion vector to predict current macroblock. In H264/AVC's main profile, motion vector is generated by two predicted methods: motion vector prediction (MVP) and direct mode coding. The details of MVG are described in the sub-section 3.2. According to motion vectors which are produced by MVG, corresponding reference pixels are loaded from external frame memory. In this chapter, we will not discuss memory such as memory controller and address generator, etc. Interpolators are invoked to produce fractional samples for both luma and chroma components. In this design, we employ two interpolators to simultaneously process

pixels of list-0 and list-1 because two motion vectors will point to two search areas in list-0 frame and list-1 frame in B-slices, respectively. When the motion vector is an integer value, corresponding reference pixels without interpolation directly feeds through weighted prediction. In the end of motion compensation processes, weighted prediction (WP) is performed by applying a multiplicative weighting factor and an additive offset in bitstream. These pixels obtained by weighted prediction add with residual data to create the unfiltered pixels. Finally, the de-blocking filter loads these pixels, and restores correct pixels into external memory after performing filter operations. Because the data bus of external frame memory is defined as 32bit, pixels which are loaded into interpolator are limited.

# 3.2 Motion Vector Predictor Design

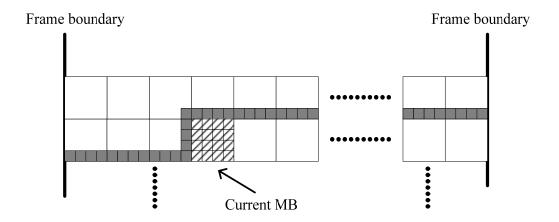

To facilitate a spatial prediction, we store motion vector for one row stripe of 4x4 blocks, four left neighboring 4x4 blocks and current 4x4 blocks into Row stored buffer. Figure 3.3 illustrates that shaded regions have to be stored for predicting oblique region.

Figure 3.3 MV in shaded and oblique line region must be stored in row-FIFO.

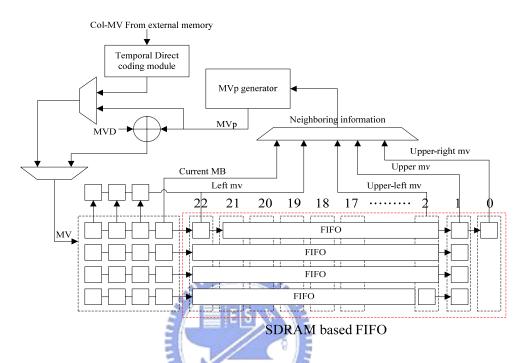

Firstly, motion vector generator is shown in Figure 3.4. Motion vector is obtained in two

predicted methods: MVP and direct mode coding. Note that direct mode coding is supported in B-slice. According to MB types, the motion vector is obtained by different predicted methods and stored into current motion vector buffer.

Figure 3.4 Motion vector generator

### 3.2.1 MVp Prediction Module

In the MVP generation method, the motion vector is generated by summing predicted motion vector (MVp) and MVD. For calculating MVp, we employ directional segmentation prediction in 8x16 or 16x8 block types and median prediction in other block types. These predictions are integrated into MVp generator. The MVp generator calculates MVp according to the motion vectors of the neighboring blocks in current frame. Thus the decoded motion vectors are required to be stored into FIFO buffer for the subsequent decoding. FIFO buffer stores the decoded motion vector pair (MVX, MVY). The depth and width of MV FIFO are dependent on the decoded frame width and search range respectively. For instance, for supporting 1080HD format, the total size of FIFO buffer is 968 x 10 bits (((120 blocks x 4 + 4))).

x = 2 = 968 4x4-block). Therefore, SRAM is selected as a FIFO buffer to store required decoded motion vectors in our design. Once the content of FIFO buffer will not be used in the future, the restored motion vector pair in FIFO buffer can be discarded. Furthermore, the 4 x 4 size of MV buffers is required because the maximum number of motion vectors per MB is 16. The motion vectors for current MB decoding store in this 4 x 4 MV buffers. Due to a Bi-prediction, two 4 x 4 MV buffers are required to store current two motion vectors for predicting motion vectors of list-0 frame and list-1 frame.

| MVLU | MVUO | MVU1 | MVU2 | MVU3 | MVRU |

|------|------|------|------|------|------|

| MVL0 | MVO  | MV1  | MV4  | MV5  |      |

| MVL1 | MV2  | мvз  | MV6  | MV7  |      |

| MVL2 | MV8  | мv9  | MV12 | MV13 |      |

| MVL3 | MV10 | MV11 | MV14 | MV15 |      |

Figure 3.5 Neighboring motion vectors required for decoding all motion vectors in current macroblock

When decoding current macroblock, the detail of required neighboring motion vectors is shown in Figure 3.5. To involve all kinds of VBS conditions, storages element is based on 4 x 4-block size that is the smallest element for H.264/AVC video decoder. Each square indicates one motion vector pair. To predict MV0-MV15 in current MB, it requires neighboring motion vectors in left-upper corner (MVLU), right-upper corner (MVRU), upper (MVU0-3) and left (MVL0-MVL3) positions., Neighboring motion vectors are shifted and stored into MV FIFO except for current MV.

Figure 3.6 (a) block size position index, (b) directional prediction table (16x8, 8x16), (c) median prediction table (16x16, 8x8), (d) median prediction table (4x4)

MVp is calculated according to MVA, MVB, MVC and MVD which are obtained from neighboring motion vectors according to block size position index for different macroblock types. The block size position index in one macroblock is illustrated in Figure 3.6 (a). MVA, MVB, MVC and MVD indicate the motion vectors located at left, upper, right-upper, left-upper neighboring macroblock/partition/block respectively as shown in Figure 2.8 (c). Figure 3.6 (b)-(d) lists all MVA, MVB, MVC and MVD for different block size position index. When MB type of current macroblock is 16x8 or 8x16, MVp can derived by directional

prediction, otherwise median prediction is involved. Furthermore, the above loop-up table (LUT) is required for motion vector prediction, many trivial boundary conditions and exceptions have to be handled. Here, we do not describe them for simplicity.

#### 3.2.2 Direct Mode Coding Design

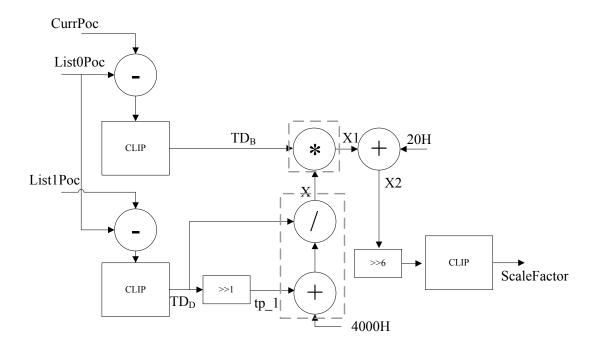

Except for MVp prediction, other way to predict current motion vectors is direct mode coding. In the direct mode coding, there are two types: spatial and temporal types [7] [8]. These types are user-defined in encoding processes. From above discussion, the PSNR of spatial mode is better than that of temporal mode. In our design, we implement both temporal and spatial modes and integrate it into MVG module. When a temporal mode is invoked, a temporal direct mode coding module calculates motion vector according to the picture order counts and co-located motion vectors in first list-1 frame. From above introduction of direct mode coding with temporal mode, we have to calculate the scalefactor value by equation 2.4. From Equation 2.5 and 2.6, two motion vectors from list-0 and list-1 frame are computed with scalefactor. Therefore, the scalefactor must be computed in advance. Figure 3.7 depicts hardware by which scalefactor is computed. We implement division-free and multiplication-free design to reduce hardware complexity. We employ some multiplexer and shifters to replace division and multiplication in gray dotted area and it is shown in Figure 3.8

Figure 3.7 Pre-scalefactor generator design

Figure 3.8 (a) Division free replacement (b) Multiplication-free replacement

Where CLIP operation is used to restrict TDB, TDD and scalefactor within range between -128 and 127. The CLIP operation is expanded as Equation 3.1. The complexity of this module is reduced efficiently by division-free and multiplication-free.

$$CLIP = (-128, 127, input\_value)$$

(3.1)

What is more, the process which produces motion vectors by spatial mode is the same as

median method for MVp prediction. Therefore, the hardware of MVp prediction module and spatial direct mode coding predictor can be shared. When the spatial mode is chosen, the predicted process acts as the MVp prediction, which needs motion vectors of the neighboring blocks to generate motion vector. Hence, we can employ MVp generator to generate motion vector without adding MVD.

# 3.3 Bandwidth-Efficient Factional Interpolator Design

Figure 3.9 (a) 4x4-block and 9x9 interpolation search windows for luma component interpolation (b) overlap region between neighboring blocks

Figure 3.10 (a) 2x2-block and 3x3 interpolation search windows for chroma component interpolation (b) overlap region between neighboring blocks

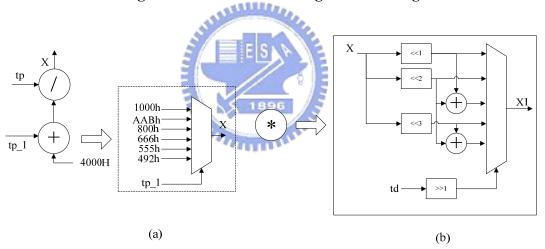

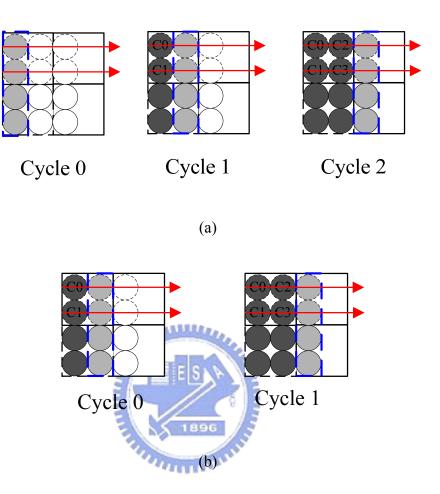

Interpolator design always dominates the throughput of H.264/AVC decoder. To interpolate each fractional sample value for each 4x4 block of luma component, it needs 9 x 9 interpolation window illustrated in Figure 3.9 (a). If two motion vectors of neighboring 4 x 4 blocks are the same, 5 x 9 overlapped region between two interpolation windows can be data reused. The overlapped region between neighboring blocks is shown in Figure 3.9 (b). We can find that maximum overlapped region is 65 pixels for luma search windows. For each 2 x 2 block of chroma component is shown in Figure 3.10, the size of interpolating search windows is 3 x 3 and 5 pixels can be reused between neighboring blocks. For above property, when interpolating current block, overlapped region cannot be fetched again. We will introduce the proposed data-reuse approach and give some examples in sub-section 3.3.1.

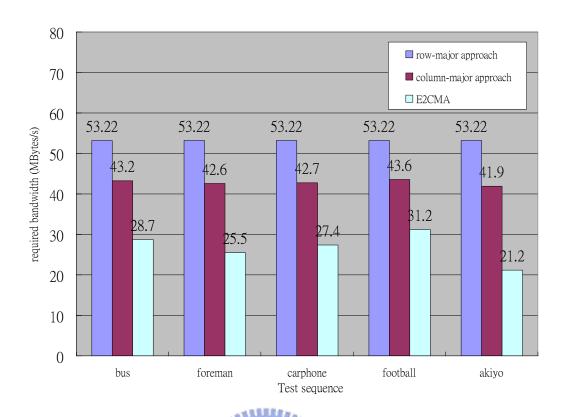

# 3.3.1 Data Reuse Technique

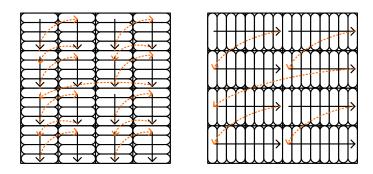

The scanning order of residual decoding for each macroblock is row-major interpolating order as shown in Figure 3.11 (a), and column-major interpolating order illustrated in Figure 3.11 (b). A dotted line indicates transition between interpolating processes. In comparison of row-major interpolating order and column-major interpolating order, we adopt a column-major interpolating order because the transition of column-major interpolating order is 5 times less than row-major order. Each transition causes that the overlap region could not be reused. Therefore, column-major one is the better selection because of less number of transitions.

Figure 3.11 (a) row-major interpolating order (b) column-major interpolating order