# 國立交通大學

## 電子工程學系 電子研究所

## 博士論文

適用於高速行動之無線都會區域網路之 基頻接收機設計 Design of Baseband Receiver for High-Mobility

Wireless Metropolitan Area Network

研 究 生:陳筱筠

指導教授:周世傑 教授

中華民國九十八年九月

### 適用於高速行動之無線都會區域網路之 基頻接收機設計

### Design of Baseband Receiver for High-Mobility Wireless Metropolitan Area Network

研究生:陳筱筠Student: Hsiao-Yun Chen指導教授:周世傑教授Advisor: Dr. Shyh-Jye Jou

國立交通大學 電子工程學系 電子研究所 博士論文

Submitted to Department of Electronics Engineering and

**A** Dissertation

College of Electrical and Computer Engineering

Institute of Electronics

National Chiao Tung University

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

in

**Electronics Engineering**

September 2009

Hsinchu, Taiwan, Republic of China

中華民國九十八年九月

### 適用於高速行動之無線都會區域網路之

#### 基頻接收機設計

研究生:陳筱筠

指導教授:周世傑 教授

#### 國立交通大學

電子工程學系 電子研究所

#### 摘要

近來,分集技術(diversity techniques)於無線通訊網路系統上受到各方矚目。 使用多根妥善分隔的天線於傳送端與接收端時,多輸入多輸出(multi-input multi-output; MIMO)系統可以明顯地提升頻譜效率與系統傳輸能力。而空時分 組碼(space-time block code; STBC)已被廣泛地應用於正交分頻多工(orthogonal frequency-division multiplexing; OFDM)系統上以得到傳送分集的增益效果,並 改善無線通訊系統之系統效能。IEEE 802.16e 標準已經採納空時分組碼與正交分 頻多工系統結合之系統應用(STBC-OFDM systems)。該標準為 IEEE 802.16-2004 標準之延伸,主要是為了支援無線都會區域網路之移動性而提出的修正規格。在 STBC-OFDM系統上,分集結合(diversity combing)、同調偵測與解碼(coherent detection and decoding)需要相當精確的通道狀態資訊(channel state information; CSI)。然而,精確的通道狀態資訊於行動無線通道上卻很難獲取。

在此論文中,我們提出應用於行動模式 IEEE 802.16e 規格之下行基頻接收 機設計方法,並且此基頻接收機可應用於兩根傳送天線與一根接收天線(2×1天 線)之 STBC-OFDM 系統上。主要目標是為了能提供高系統效能傳輸於車速達 120 km/hr 行動環境中。首先,我們提出簡單但有效之符元邊界偵測與載波頻率 漂移估計方法。接著,提出精確且擁有可接受的硬體複雜度之雨階段通道估測策 略,並且此種通道估測方法在與內插式通道估測方法比較上有明顯的傳輸效能提 升。此論文所提出之基頻接收機經由 2×1 天線之 STBC-OFDM 系統模擬驗證。 在車速 120 與 240 km/hr 的環境中應用於四相位偏移調變(quadrature phase shift keying; QPSK)之下,此接收機仍可分別達位元錯誤率(bit error rate; BER)約 10<sup>-3</sup>與 10<sup>-4</sup>,並且未使用任何通道編碼技術。我們以 90 nm CMOS 製程實現此接 收機晶片。在 16 正交振幅調變(16 quadrature amplitude modulation; 16-QAM) 下,此晶片最快可支援下行資料傳輸達 27.32 Mbps。在通道估測硬體設計上,我 們提出前置碼匹配(preamble match)、直接式多路徑干擾消除解相關器(straight multipath interference cancellation-based decorrelator)、最小平方估測器(least square estimator)及通道路徑解相關器(path decorrelator)等新的架構設計有效 地減少硬體面積需求與功率消耗。此接收機晶片核心面積為 2.4×2.4 mm<sup>2</sup>。在 78.4MHz 的操作頻率與 1 V 工作電壓下,其功率消耗為 68.48 mW。

此外,我們提出一組用於事列傳輸之傳輸碼,4-脈衝振幅調變對稱式傳輸碼 (4-PAM symmetric code),其主要用於差動4-脈衝振幅調變信號串列傳輸系統。 而此傳輸碼保留 8B/10B 之傳輸優點,如直流平衡之位元串列資料與提供足夠的 時序資料給予接收端進行時序回復等特性,並具有效降低時脈回復時所產生的資 料轉換邊界抖動之功能。此串列傳輸編、解碼器以 0.18 um 製程實現,並証明若 在接收端做時序回復時能夠有效的改善參考之時序資訊轉換邊界抖動達±25%資 料轉換時間。此 4-脈衝振幅調變信號串列傳輸編、解碼器之設計可分別操作於 819 MHz 與 704 MHz 並且源頭資料傳輸率可到達 13.1 Gbps 與 11.3Gbps。

ii

## Design of Baseband Receiver for High-Mobility Wireless Metropolitan Area Network

Student: Hsiao-Yun Chen

Advisor: Dr. Shyh-Jye Jou

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

#### Abstract

Recently, diversity techniques are receiving particular attention in wireless communication systems. By using well-separated antennas at the transmitter and/or receiver, the multiple-input and multiple-output (MIMO) systems can significantly increase the bandwidth efficiency and system capacity. Space-time block code (STBC) has suggested to be applied in an orthogonal frequency division multiplex (OFDM) system to utilize the transmit diversity for improving system performance in wireless communication systems. STBC-OFDM systems have been adopted in IEEE 802.16e which is an extension of IEEE 802.16-2004 for supporting mobility of wireless metropolitan area network (WMAN). However, for diversity combining, coherent detection and decoding, STBC-OFDM systems require accurate channel state information (CSI), which is particularly difficult to obtain in mobile wireless channels.

This dissertation proposes a downlink baseband receiver scheme for IEEE 802.16e in mobile mode. The proposed receiver is applied in STBC-OFDM system with two transmit antennas and one receive antenna and aims to provide high performance under the vehicle speed up to 120 km/hr. First, the simple and robust symbol boundary detection and carrier frequency offset estimation schemes are

proposed. Then, an accurate but hardware affordable two-stage channel estimation strategy is adopted to overcome the challenge of outdoor mobile channels. It has significant performance improvement as compared with the interpolation-based channel estimations. The performances of the proposed receiver have been demonstrated through the simulation of an STBC-OFDM system with two transmit antennas and one receive antenna. At vehicle speed of 120 and 240 hr/km for quadrature phase shift keying (QPSK) modulation, the proposed design can achieve the bit error rate (BER) of about  $10^{-4}$  and  $10^{-3}$  without using channel coding. The proposed receiver implemented in 90nm CMOS technology can support up to 27.32 Mbps (uncoded) downlink data transmission in 16 quadrature amplitude modulation (16-QAM). In the proposed channel estimator, novel architectures of a preamble match, a straight multipath interference cancellation (SMPIC)-based decorrelator, a least square (LS) estimator, and a path decorrelator are designed to reduce the area and power of the blocks. The receiver has the core area of 2.4×2.4 mm<sup>2</sup> and dissipates 68.48 mW at 78.4MHz operating frequency from a supply voltage 1 V.

####

In addition, a novel DC-balanced low-jitter transmission code, a 4-PAM symmetric code, for a 4-PAM signaling system is presented. The 4-PAM symmetric code preserves all the useful characteristics of 8B/10B transmission code, such as DC-balanced serial data and guaranteed transitions in the symbol stream for data/clock recovery. Moreover, the proposed method decreases the jitter of the timing transition of the data in the receiver. The design results using 0.18  $\mu$ m process demonstrate that the new transmission code can decrease the jitter of the transition point by  $\pm$  25% of the transition region. The operation speeds of the encoder and decoder for the 4-PAM symmetric code are 819 MHz with 16-bit inputs (throughput 13.1 Gbps) and 704 MHz with 16-bit outputs (throughput 11.3 Gbps), respectively.

#### 誌 謝

在碩、博研究生涯的兩千五百多個日子中,最要感謝的人莫過於我的指導教 授周世傑老師,無論在研究或做人處事上,老師總是給我許多的建議與鼓勵,指 引我讓我能以謹慎的態度去學習、思考並解決問題,心中對老師是無限的感恩。

再者要感謝我最可愛的學弟紹維與俊男,因為有你們的加油鼓勵與幫忙,讓 我有信心能去面對研究及生活上的種種挑戰,研究路上充滿喜悅。謝謝古孟霖學 長在演算法與論文撰寫上給我許多協助與討論,能和學長合作真的很開心也很愉 快。謝謝小胖,總是幫我解決繁瑣問題。謝謝舒蓉,我科法修課上的好伙伴。

謝謝實驗室所有一起成長、奮鬥的學長、同學和學弟妹們,TOTORO、育群、 庭楨、盈志、儷蓉、晉欽、誠文、阿賢、子捷、小朱、誌華、spice、阿樸、俊誼、 國光、運翔、祥甡、喻喧、明銓、代暘、志宇、馥淳、為凱、雅雪、祥譽、銘謙、 以樂,讓316 實驗室充滿許多歡笑與回憶。謝謝所有照顧我的長輩與好友們,在 我生活上給予各項的協助與鼓勵。謝謝大家。

感謝我的男友和我心愛的 maimai 一直陪伴在我身邊加油打氣,給我前進的 力量。最後要感謝我最親愛的家人,有你們的關懷與支持,讓我得以專心致力於 研究,感謝之情,不勝言表。謹將這份成就和喜悅與摯愛的家人分享。

筱筠

謹誌於 新竹

2009年9月

# Contents

| Chapter 1    | Introduction                                    | 1  |

|--------------|-------------------------------------------------|----|

| 1.1 B        | Background                                      | 1  |

| 1.2 N        | <i>Notivation</i>                               | 6  |

| 1.3 T        | Thesis Organization                             | 7  |

| Chapter 2    | Overview of IEEE 802.16e OFDMA and MIMO Systems | 9  |

| 2.1 I        | ntroduction                                     | 9  |

| 2.2 0        | Diverview of OFDMA                              | 10 |

| 2.3 N        | AIMO Systems                                    | 16 |

| 2.4 L        | EEE 802.16e OFDMA Specification                 | 17 |

| 2.4.1        | Frame Structure                                 | 17 |

| 2.4.2        | Preamble Format                                 | 20 |

| 2.4.3        | Pilot Modulation                                | 21 |

| 2.4.4        | Basic Specification in IEEE 802.16e OFDMA       | 22 |

| Chapter 3    | Downlink Baseband STBC-OFDM System Architecture | 25 |

| 3.1 I        | ntroduction                                     | 25 |

| 3.2 S        | System Specification and Design Targets         | 26 |

| <i>3.3 1</i> | Fransmitter Architecture                        | 28 |

| 3.3.1        | Channel Coding                                  | 30 |

| 3.3.         | 1.1 Randomization                               | 31 |

| 3.3.         | 1.2 FEC coding                                  | 31 |

| 3.3.         | 1.3 Interleaving                                | 32 |

| 3.3.2        | Signal Mapping                                  | 33 |

| 3.3.3        | Subcarrier Allocation                           | 33 |

| 3.3.4        | STBC Encoding                                   | 36 |

| 3.4 Receiver Architecture                                             | 37    |

|-----------------------------------------------------------------------|-------|

| 3.4.1 Synchronization                                                 | 38    |

| 3.4.1.1 Symbol Timing Synchronization                                 | 39    |

| 3.4.1.2 Carry Frequency Synchronization                               | 42    |

| 3.4.2 Channel Estimation                                              | 48    |

| 3.4.3 STBC Decoding                                                   | 49    |

| 3.4.4 Channel Decoding                                                | 49    |

| 3.4.4.1 De-interleaving                                               | 50    |

| 3.4.4.2 FEC Decoding                                                  | 50    |

| 3.4.4.3 De-randomization                                              | 50    |

| 3.5 System Simulation                                                 | 51    |

| 3.6 Summary                                                           | 57    |

| Chapter 4 A Robust Channel Estimator for STBC-OFDM Systems            | 59    |

| 4.1 Introduction                                                      | 59    |

| 4.2 Pilot-aided Channel Estimation Methods                            | 61    |

| 4.2.1 Interpolation-based Channel Estimation                          | 61    |

| 4.2.2 DFT-based Channel Estimation                                    | 63    |

| 4.3 Two-Stage Channel Estimation Method                               | 66    |

| 431 Initialization Stage 1896                                         | 66    |

| 4.3.2 Tracking Stage                                                  | 68    |

| <ul> <li>4.3.2 Tracking Stage</li></ul>                               | 70    |

| 4.4.1 Initialization Stage: Preamble Match                            |       |

| 4.4.2 Initialization Stage: SMPIC-based Decorrelator                  | 71    |

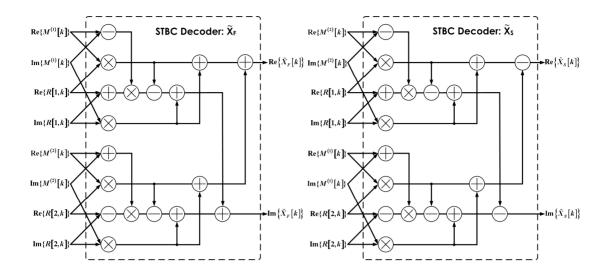

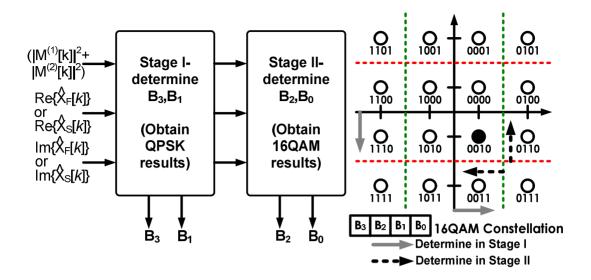

| 4.4.3 Tracking Stage: STBC Decoder and Demapper                       | 73    |

| 4.4.4 Tracking Stage: LS Estimator                                    | 74    |

| 4.4.5 Tracking Stage: Hessian Matrix Calculator and Path Decorrelator | 76    |

| 4.5 Computational Complexity                                          | 78    |

| 4.6 Simulation Results                                                | 80    |

| 4.7 Summary                                                           | 86    |

| Chapter 5 Novel Programmable FIR Filter Based on Higher Radix Recodin | ıg.87 |

| 5.1 Introduction                                                      | 87    |

| 5.2 Algorithm Reformulations                                          | 88    |

| 5.2.1 Higher Radix Recoding                                           |       |

| 5.2.2 Secondary Radix Recoding                                                                    | 89    |

|---------------------------------------------------------------------------------------------------|-------|

| 5.2.3 Algorithm Reformulation for FIR Filter                                                      | 91    |

| 5.3 Programmable FIR Filter Based on Higher Radix Booth Recoding                                  | 92    |

| 5.3.1 Higher Radix Booth Multiplier (HRBM)                                                        | 92    |

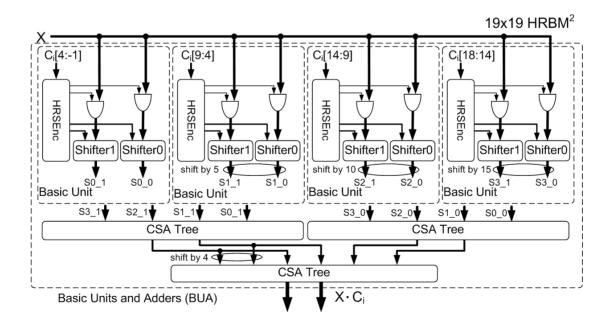

| 5.3.2 HRBM <sup>2</sup> Based on Secondary Radix Recoding                                         | 94    |

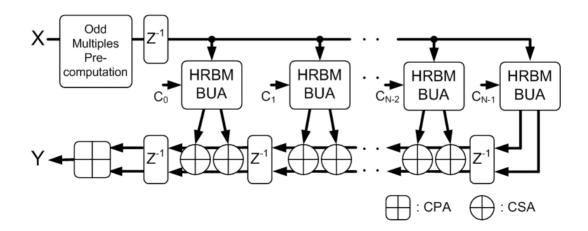

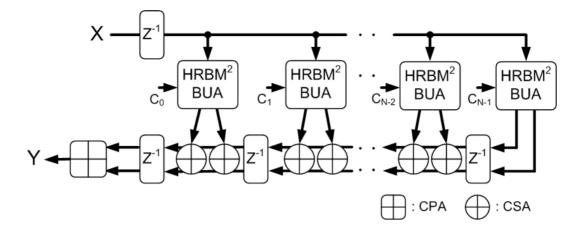

| 5.3.3 Programmable FIR Filter Architectures                                                       | 96    |

| 5.4 Results and Comparisons                                                                       | 97    |

| 5.5 Summary                                                                                       | 98    |

| Chapter 6 Downlink Baseband Receiver Implementation                                               | 101   |

| 6.1 Introduction                                                                                  | 101   |

| 6.2 Word Length Optimization                                                                      | 105   |

| 6.3 Synchronizer                                                                                  | 107   |

| <ul><li>6.3.1 Symbol Boundary Detector</li><li>6.3.2 Carrier Frequency Offset Estimator</li></ul> | 107   |

| 6.3.2 Carrier Frequency Offset Estimator                                                          | 109   |

| 6.4 Proposed Channel Estimator                                                                    | 114   |

| 6.4.1 Initialization Stage: Preamble Match                                                        | 114   |

| 6.4.2 Initialization Stage: SMPIC-based Decorrelator                                              | 116   |

| 6.4.2.1 Merge Sorting Network with Programmable and Partial Sorti                                 | ng    |

| Capability (MSNP <sup>2</sup> )                                                                   | 117   |

| 6.4.2.2 Triangular Decorrelator (TD)                                                              |       |

| 6.4.3 Tracking Stage: STBC Decoder and Demapper                                                   |       |

| 6.4.4 Tracking Stage: LS Estimator                                                                |       |

| 6.4.5 Tracking Stage: Hessian Matrix Calculator and Path Decorrelator.                            | 129   |

| 6.5 <i>FFT/IFFT module</i>                                                                        | 131   |

| 6.6 Data Flow of the Proposed Receiver                                                            | 134   |

| 6.7 Simulation Results                                                                            | 136   |

| 6.8 Design Results                                                                                | 138   |

| 6.9 Summary                                                                                       | 144   |

| Chapter 7 Conclusions                                                                             | 147   |

| Appendix A: A DC-balance Low-jitter Transmission Code for 4-PAM Sign                              | aling |

|                                                                                                   |       |

| A.1 Introduction                                                                                  | 149   |

| A.2 De.    | sign of the 4-PAM Symmetric Code                            | 150         |

|------------|-------------------------------------------------------------|-------------|

| A.2.1      | The Structure of 4-PAM Symmetric Code                       | 151         |

| A.2.2      | Low-jitter of Data Transitions                              | 153         |

| A.2.3      | The Design Concept of Running Disparity                     | 154         |

| A.2.4      | Error Detection                                             | 156         |

| A.2.5      | Comparison of Transmission Codes                            | 156         |

| A.3 Arc    | hitecture and Implementation of 4-PAM Symmetric Encoder / I | Decoder 157 |

| A.4 C      | onclusions                                                  | 162         |

| References |                                                             | 163         |

# **List of Tables**

| Table 1.1 Comparisons of wireless standards                               | 3   |

|---------------------------------------------------------------------------|-----|

| Table 2.1 Scalable OFDMA parameters                                       | 14  |

| Table 2.2 Major parameters of IEEE 802.16e OFDMA specification            | 23  |

| Table 3.1 Major parameters of the proposed STBC-OFDM system               | 27  |

| Table 3.2 Puncture configuration                                          | 32  |

| Table 3.3 STBC encoding                                                   | 37  |

| Table 3.4 Required SNR (dB) for BER<10 <sup>-6</sup> in AWGN channel      | 53  |

| Table 3.5 Required SNR (dB) for BER<10 <sup>-6</sup> in ITU Veh-A channel | 56  |

| Table 4.1 Computational complexity and storage requirements               | 79  |

| Table 5.1 Radix-16 recoding scheme of HREnc                               | 93  |

| Table 5.2 Radix-32-modulo-7 recoding scheme of HRSEnc                     | 95  |

| Table 5.3 Design results of 10-tap programmable FIR filter                | 98  |

| Table 6.1 Word lengths of several key signals in the proposed receiver    | 105 |

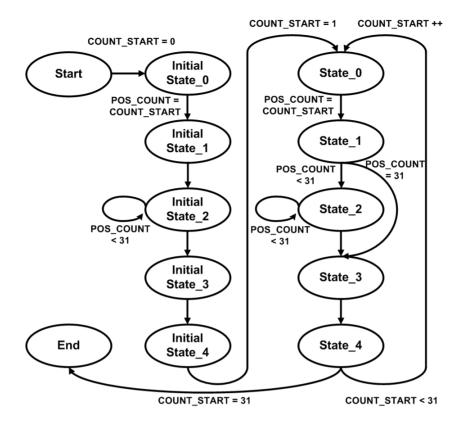

| Table 6.2 State definitions of the MSNP <sup>2</sup> state diagram        | 121 |

| Table 6.3 Control signals used in the MSNP <sup>2</sup> state diagram     | 122 |

| Table 6.4 Read or write address for the butterfly unit in each stage      | 133 |

| Table 6.5 Implementation results of the proposed receiver                 | 138 |

| Table 6.6 Implementation results of the proposed channel estimator        | 141 |

| Table 6.7 Comparison with other design operating at 200 MHz               | 144 |

| Table A.1 8B/10B, 8B5Q and 4-PAM symmetric transmission codes for 4-PAM   |     |

| system                                                                    | 157 |

| Table A.2 Synthesis results of the 4-PAM symmetric encoder / decoder      | 160 |

# **List of Figures**

| Fig. 1.1 Wireless network area definition [4].                                       | 2    |

|--------------------------------------------------------------------------------------|------|

| Fig. 1.2 Concept of AMC [15].                                                        | 5    |

|                                                                                      |      |

| Fig. 2.1 (a) Conventional non-overlapping sub-bands. (b) Overlapping sub-bands.      | 11   |

| Fig. 2.2 OFDM symbol with cyclic prefix.                                             | 11   |

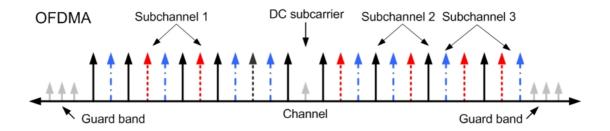

| Fig. 2.3 OFDMA subcarrier allocation.                                                | 12   |

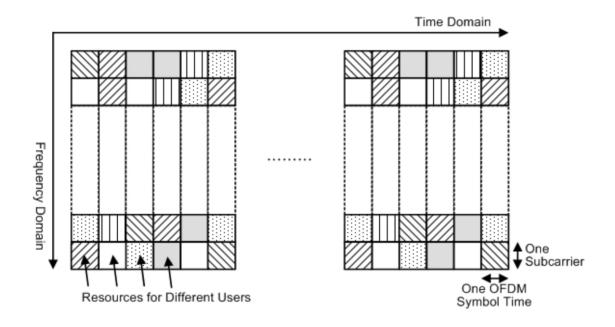

| Fig. 2.4 Two-dimensional resources of OFDMA transmission.                            | 12   |

| Fig. 2.5 Adjacent and distributed subcarrier allocations.                            | 13   |

| Fig. 2.6 An OFDM symbol.                                                             | 14   |

| Fig. 2.7 Two-dimensional basic terms in OFDMA data structure.                        | 15   |

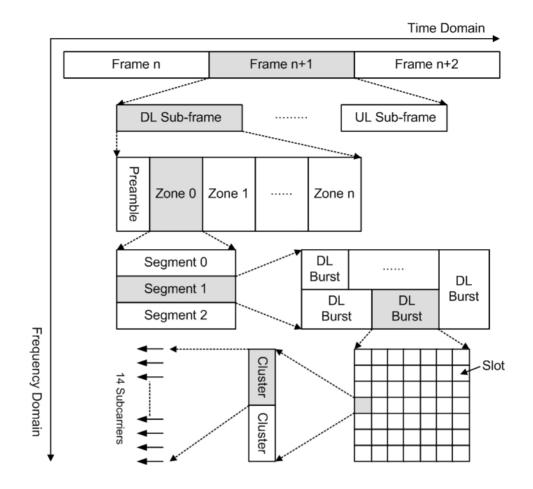

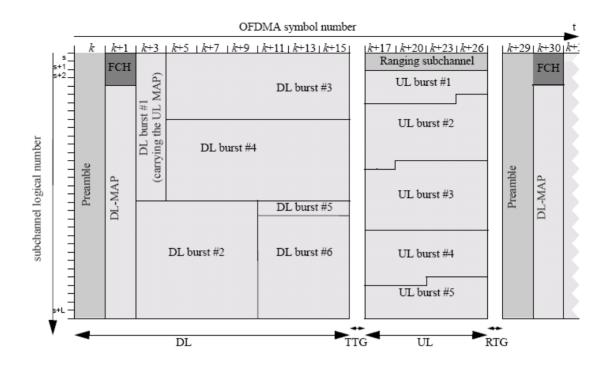

| Fig. 2.8 An OFDMA frame in TDD mode [8].                                             | 18   |

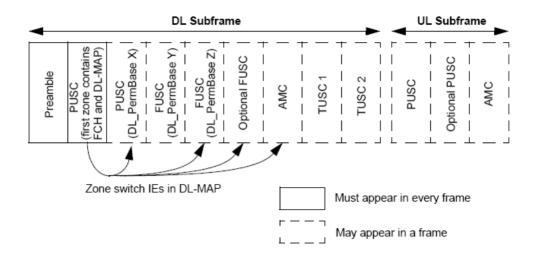

| Fig. 2.9 An OFDMA frame with multiple zones [8].                                     | 19   |

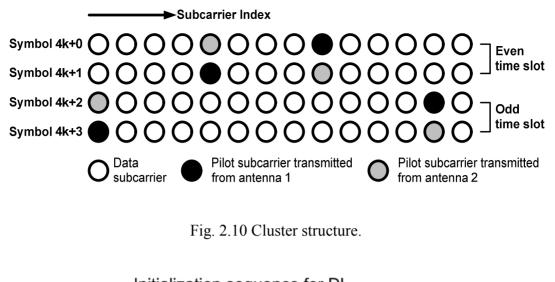

| Fig. 2.10 Cluster structure.                                                         | 21   |

| Fig. 2.11 PRBS generator for pilot modulation                                        | 21   |

|                                                                                      |      |

| Fig. 3.1 Frame format.                                                               | 28   |

| Fig. 3.2 (a) Transmitter and (b) receiver of the proposed STBC-OFDMA system w        | ith  |

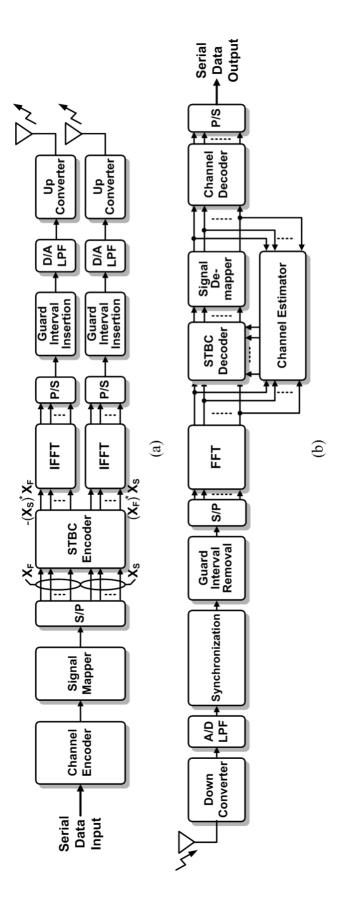

| two transmit antennas and one receive antenna.                                       | 29   |

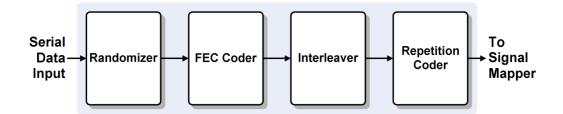

| Fig. 3.3 Block diagrams of channel coder.                                            | 30   |

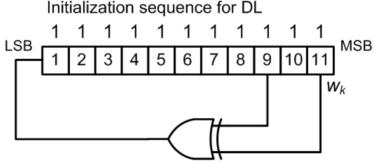

| Fig. 3.4 PRBS generator for data randomization.                                      | 31   |

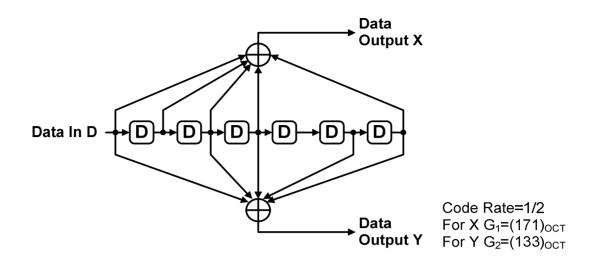

| Fig. 3.5 Convolutional encoder of code rate 1/2.                                     | 32   |

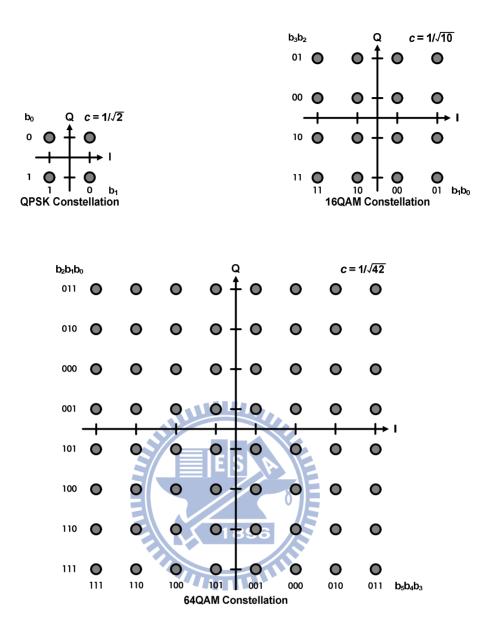

| Fig. 3.6 QPSK, 16-QAM and 64-QAM constellations.                                     | 34   |

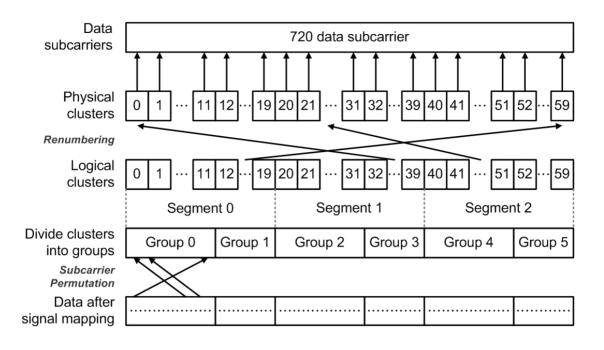

| Fig. 3.7 Subcarrier allocation of PUSC (FFT size = $1024$ ).                         | 35   |

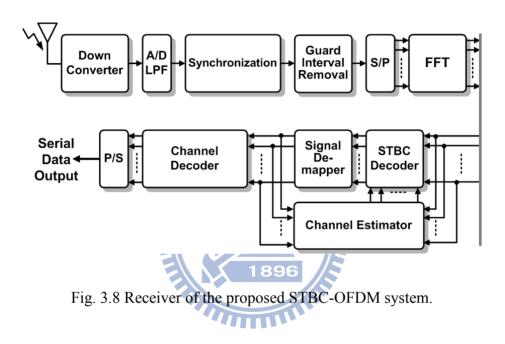

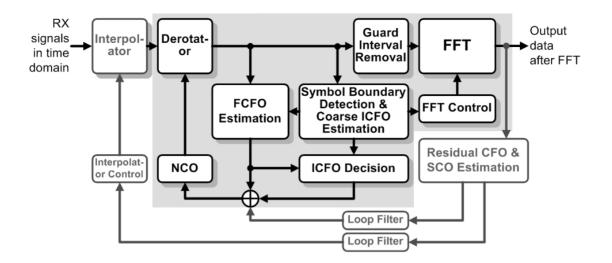

| Fig. 3.8 Receiver of the proposed STBC-OFDM system.                                  | 37   |

| Fig. 3.9 Synchronization architecture of the proposed STBC-OFDM system.              | 39   |

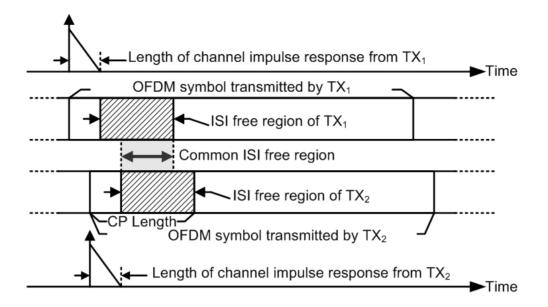

| Fig. 3.10 Common ISI free region of two transmit antennas.                           | 41   |

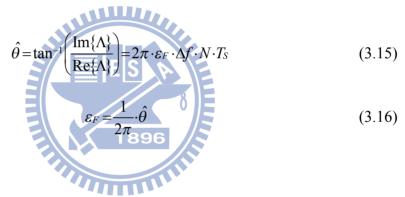

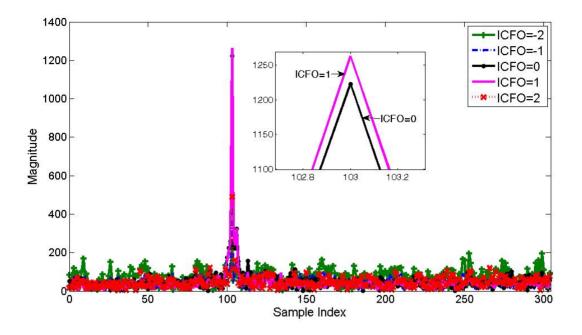

| Fig. 3.11 Matching results when CFO is 0.49 subcarrier spacing.                      | 44   |

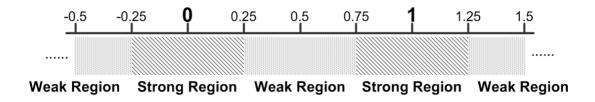

| Fig. 3.12 CFO region partition for the proposed ping-pong algorithm.                 | 45   |

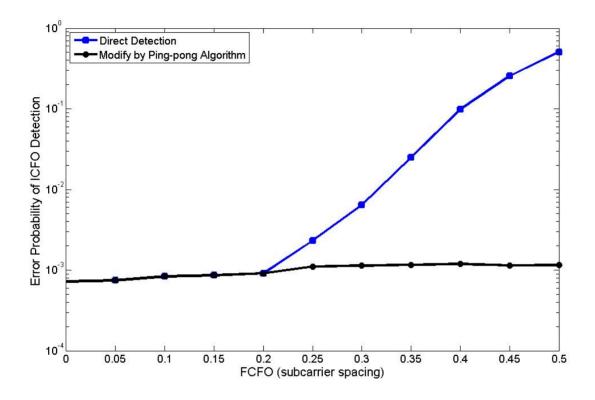

| Fig. 3.13 Error probability of the ICFO detection versus FCFO at $v_e$ of 60 km/hr v | with |

| $E_b/N_0$ of 16 dB.                                                                  | 45   |

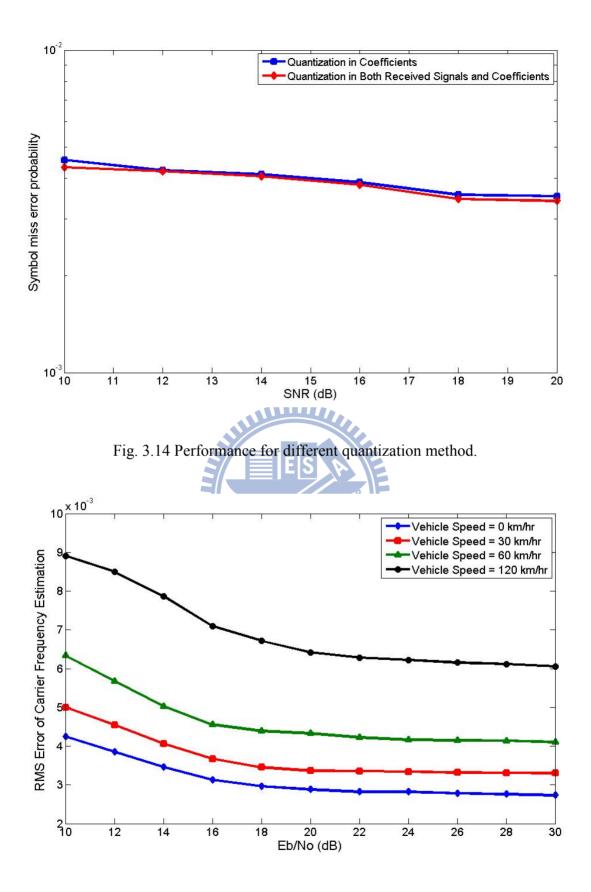

| Fig. 3.14 Performance for different quantization method.                             | 47   |

| Fig. 3.15 RMS errors of CFO under different vehicle speed.                                      | 47                 |

|-------------------------------------------------------------------------------------------------|--------------------|

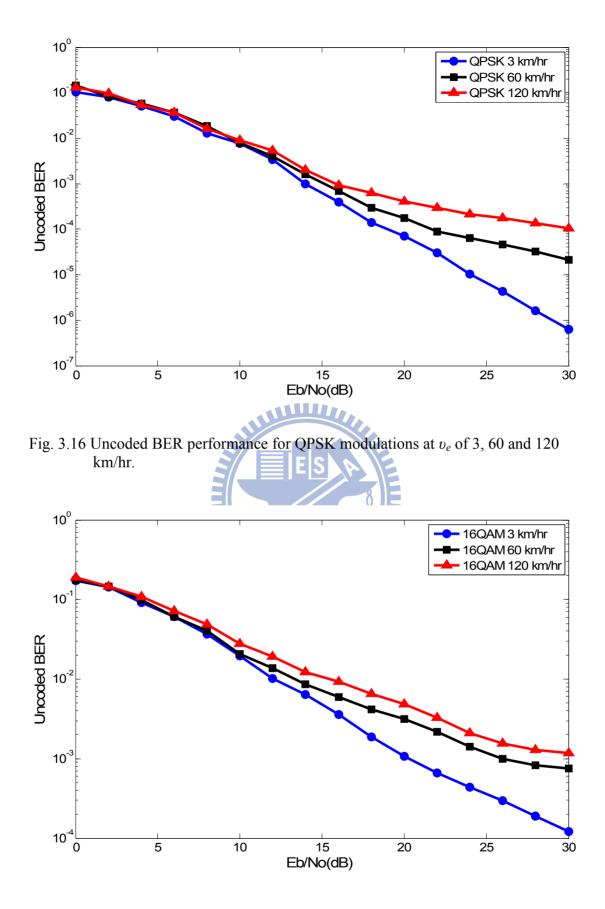

| Fig. 3.16 Uncoded BER performance for QPSK modulations at $v_e$ of 3, 60 and                    |                    |

| 120 km/hr.                                                                                      | 52                 |

| Fig. 3.17 Uncoded BER performance for 16-QAM modulations at $v_e$ of 3, 60 and                  |                    |

| 120 km/hr.                                                                                      | 52                 |

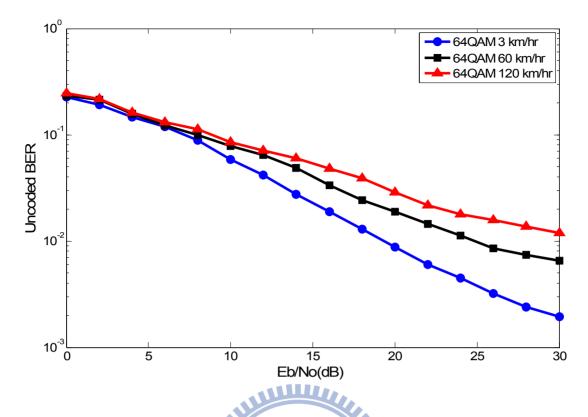

| Fig. 3.18 Uncoded BER performance for 64-QAM modulations at $v_e$ of 3, 60 and                  |                    |

| 120 km/hr.                                                                                      | 53                 |

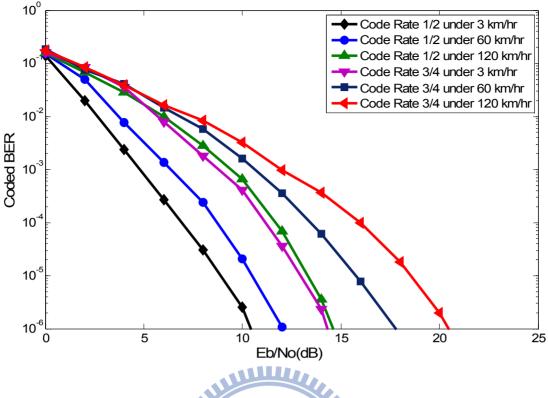

| Fig. 3.19 Coded BER performance for QPSK modulation.                                            | 54                 |

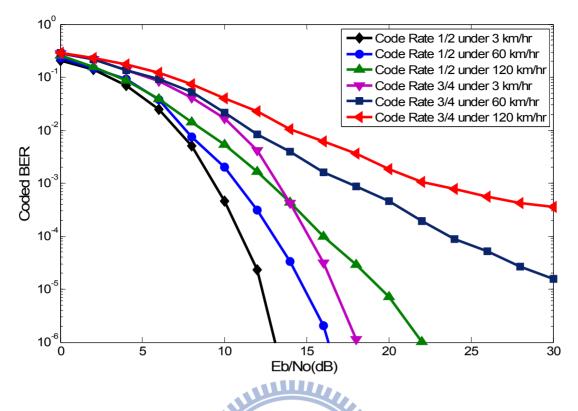

| Fig. 3.20 Coded BER performance for 16-QAM modulation.                                          | 55                 |

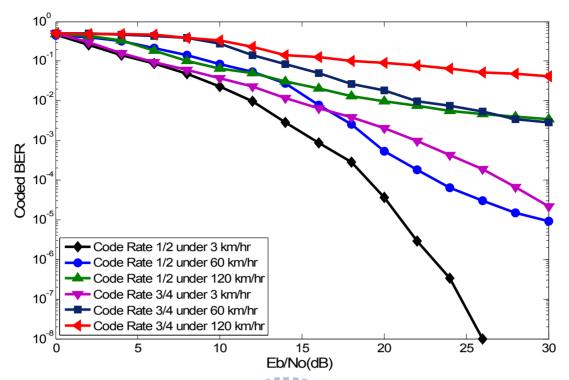

| Fig. 3.21 Coded BER performance for 64-QAM modulation.                                          | 56                 |

|                                                                                                 |                    |

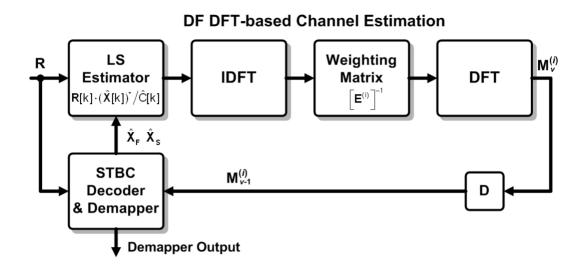

| Fig. 4.1 Block diagram of a classic DF DFT-based channel estimation method.                     | 64                 |

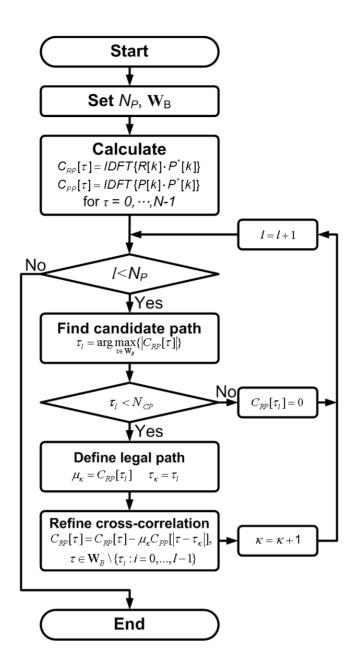

| Fig. 4.2 Flowchart of MPIC-based decorrelation method.                                          | 67                 |

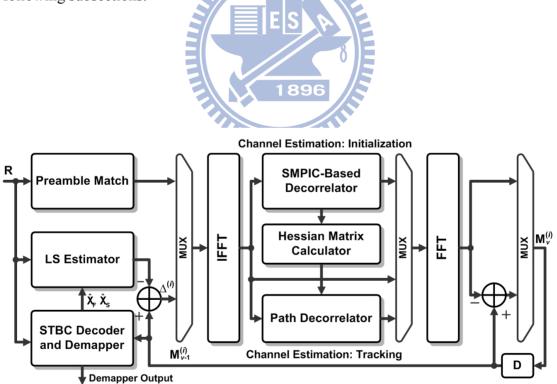

| Fig. 4.3 Overall block diagram of the proposed channel estimator.                               | 70                 |

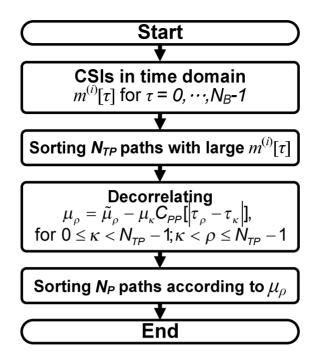

| Fig. 4.4 Flowchart of the proposed SMPIC-based decorrelation.                                   | 72                 |

| Fig. 4.5 Pilots transmitted in the cluster structures over different time slots.                | 76                 |

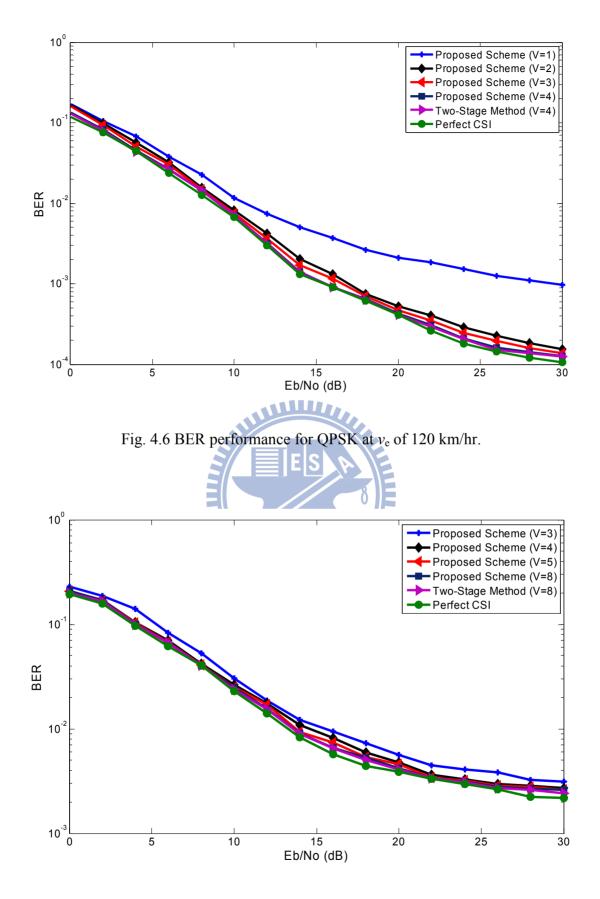

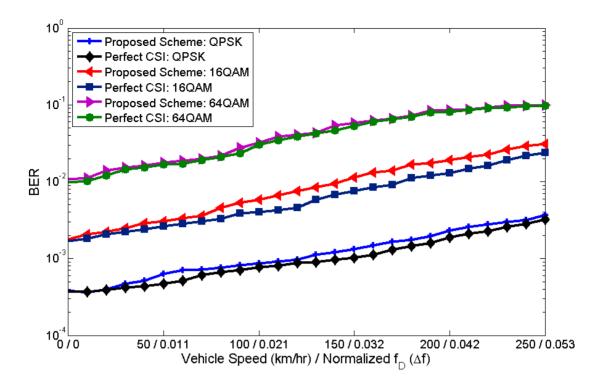

| Fig. 4.6 BER performance for QPSK at $v_e$ of 120 km/hr.                                        | 81                 |

| Fig. 4.7 BER performance for 16-QAM at $v_e$ of 120 km/hr.                                      | 81                 |

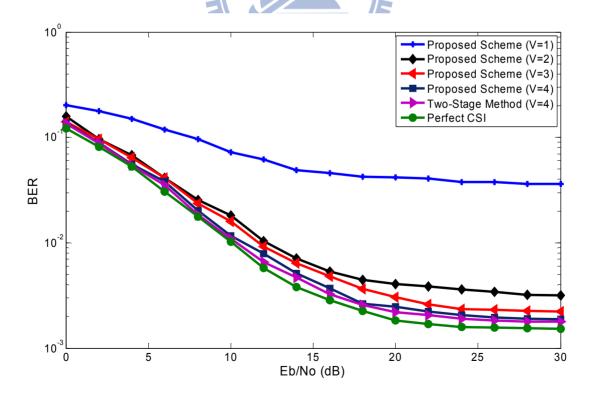

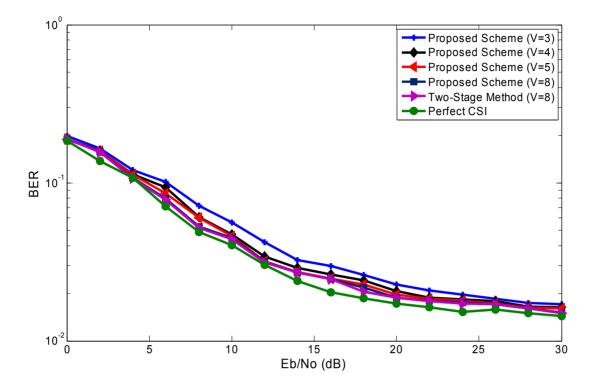

| Fig. 4.8 BER performance for QPSK at $v_e$ of 240 km/hr.                                        | 82                 |

| Fig. 4.9 BER performance for 16-QAM at $v_e$ of 240 km/hr.                                      | 83                 |

| Fig. 4.10 BER performances versus the vehicle speed.                                            | 84                 |

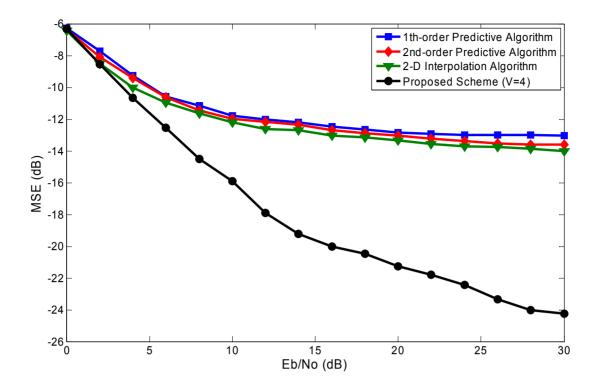

| Fig. 4.11 MSE of channel estimations using the proposed scheme, predic                          | ctive              |

| algorithms and 2-D interpolation-based methods at $v_e$ of 120 km/hr.                           | 85                 |

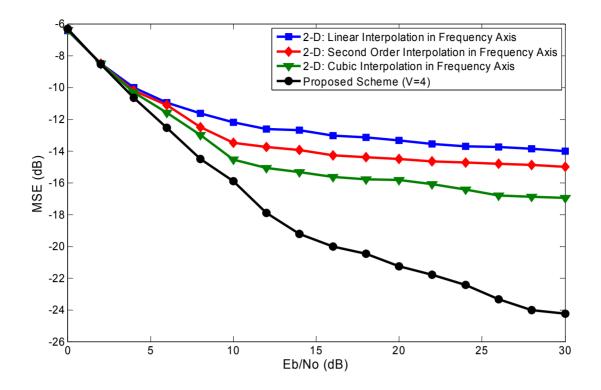

| Fig. 4.12 MSE of channel estimations using the proposed scheme and                              | 2-D                |

| interpolation-based methods with different interpolations in frequency axis at v                | $v_e$ of           |

| 120 km/hr.                                                                                      | 86                 |

|                                                                                                 |                    |

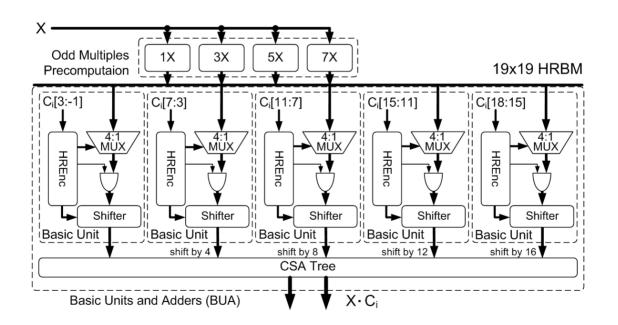

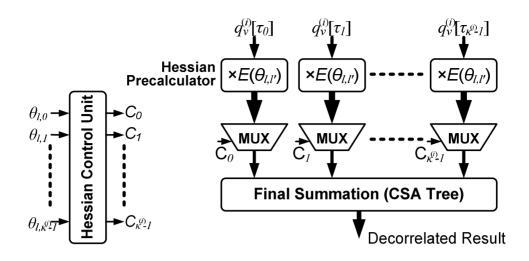

| Fig. 5.1 Parallel architecture of 19×19-bit radix-16 ( $\beta$ =24) HRBM.                       | 92                 |

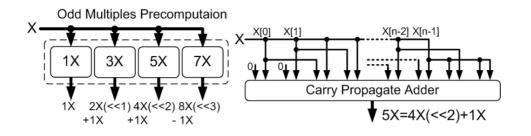

| Fig. 5.2 Odd multiples pre-computation structure and pre-compute 5× architecture                | e. 93              |

| Fig. 5.3 Parallel architecture of 19×19-bit radix-32-modulo-7 ( $\beta$ =25; $\lambda$ =7) HRBM | [ <sup>2</sup> .94 |

| Fig. 5.4 Programmable FIR filter using HRBM.                                                    | 96                 |

| Fig. 5.5 Programmable FIR filter using HRBM <sup>2</sup> .                                      | 97                 |

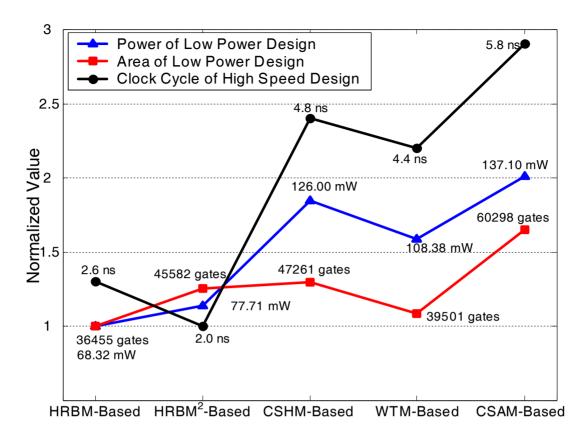

| Fig. 5.6 Design results comparison of different multiplier-based.                               | 99                 |

|                                                                                                 |                    |

| Fig. 6.1 Architectures of (a) the proposed downlink baseband receiver and (b)                   | ) the              |

|                                                                                                 | 100                |

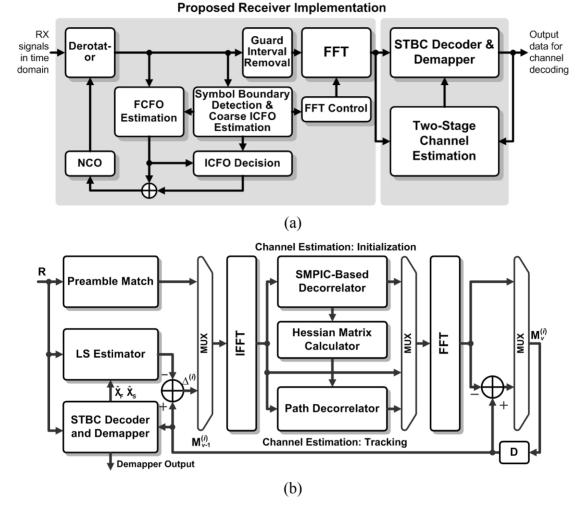

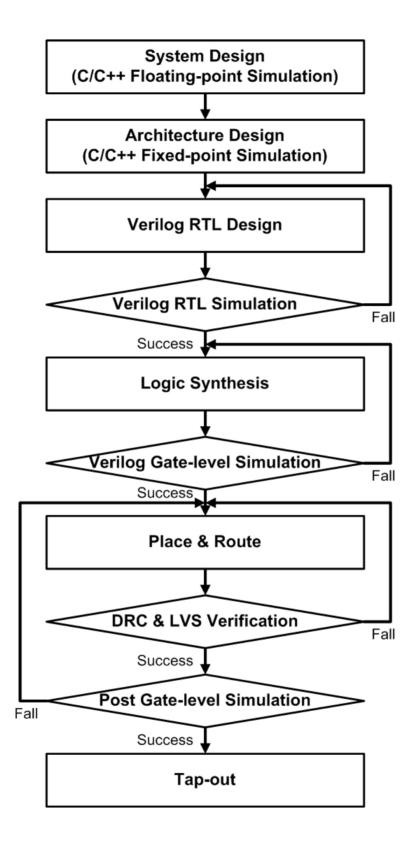

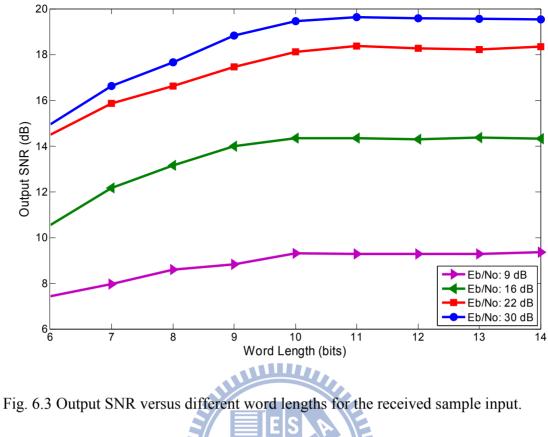

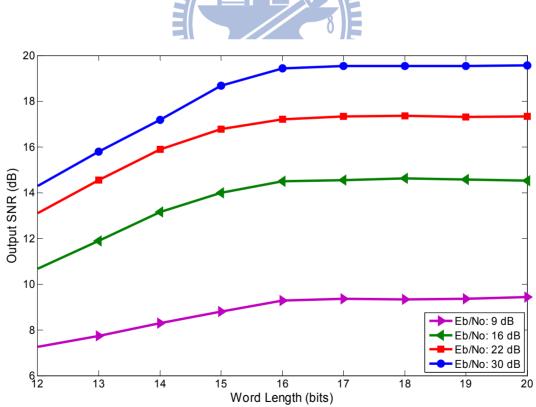

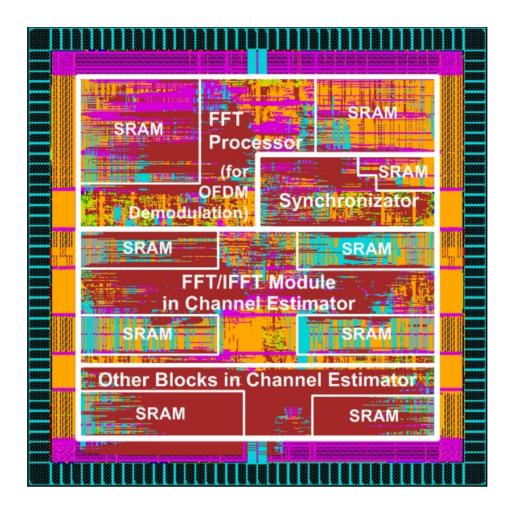

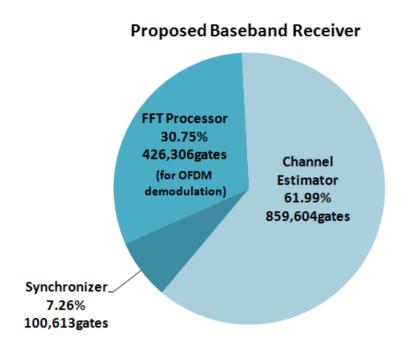

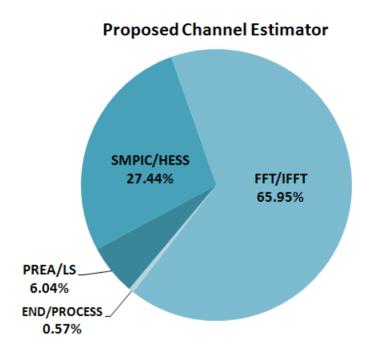

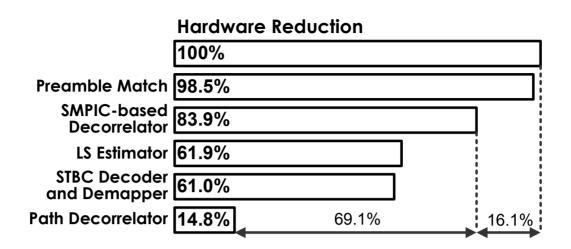

Fig. 6.1 Architectures of (a) the proposed downlink baseband receiver and (b) theproposed two-stage channel estimator with the STBC decoder and demapper.102Fig. 6.2 Implementation flow of the proposed receiver.104Fig. 6.3 Output SNR versus different word lengths for the received sample input.106

| Fig. 6.4 Output SNR versus different word lengths for the channel response                                                                                                              | output.   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                                                                                                         | 106       |

| Fig. 6.5 Match filter design.                                                                                                                                                           | 109       |

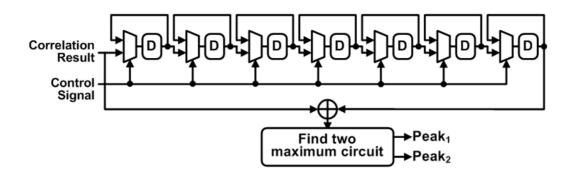

| Fig. 6.6 Storage units for storing previous correlation results.                                                                                                                        | 110       |

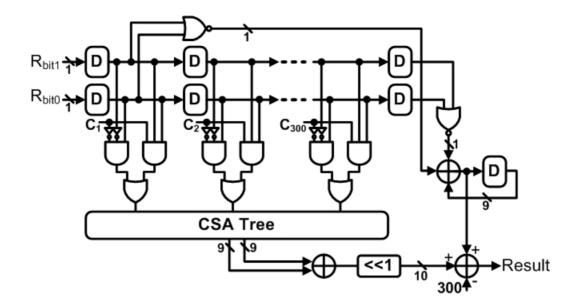

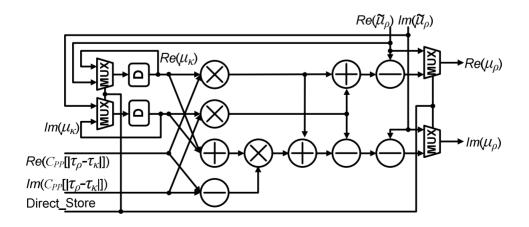

| Fig. 6.7 Cross correlation circuit for the FCFO estimation.                                                                                                                             | 110       |

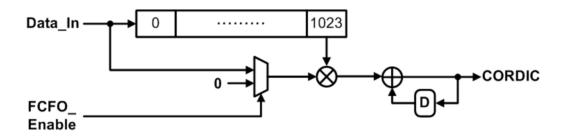

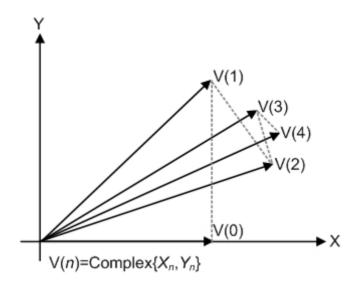

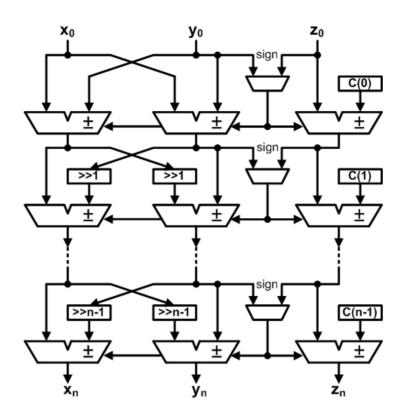

| Fig. 6.8 CORDIC rotation.                                                                                                                                                               | 112       |

| Fig. 6.9 CORDIC design.                                                                                                                                                                 | 114       |

| Fig. 6.10 Basic design unit of the preamble match.                                                                                                                                      | 115       |

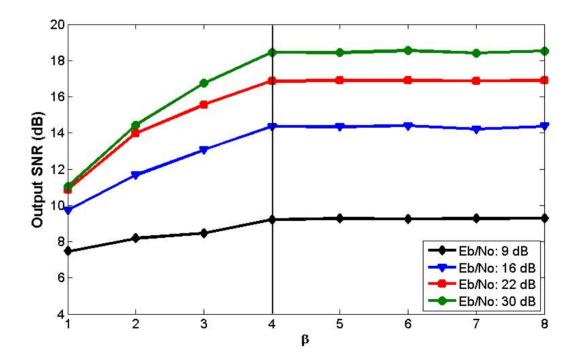

| Fig. 6.11 Output SNR versus the value of $\beta$ .                                                                                                                                      | 116       |

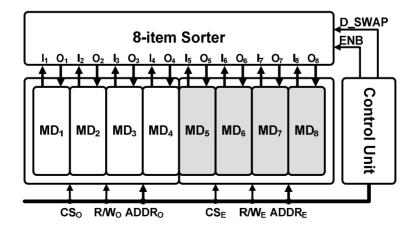

| Fig. 6.12 Block diagram of the $MSNP^2$ .                                                                                                                                               | 117       |

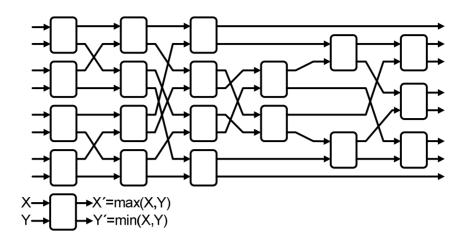

| Fig. 6.13 Batcher classic sorting network with I/O size of eight.                                                                                                                       | 118       |

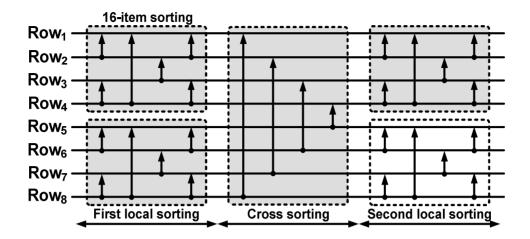

| Fig. 6.14 The memory bank arrangement of merge sorting network.                                                                                                                         | 118       |

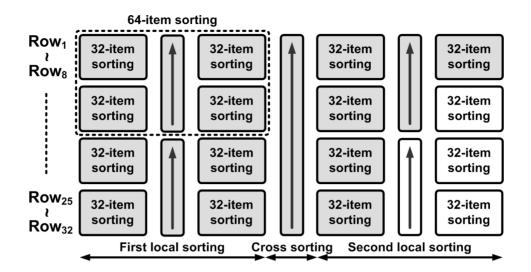

| Fig. 6.15 32-item merge sorting sequence.                                                                                                                                               | 119       |

| Fig. 6.16 128-item merge sorting sequence.                                                                                                                                              | 120       |

| Fig. 6.17 State diagram of the proposed MSNP <sup>2</sup> .                                                                                                                             | 121       |

| <ul> <li>Fig. 6.17 State diagram of the proposed MSNP<sup>2</sup>.</li> <li>Fig. 6.18 Design of the decorrelated unit.</li> <li>Fig. 6.19 Process steps of the TD operation.</li> </ul> | 123       |

| Fig. 6.19 Process steps of the TD operation.                                                                                                                                            | 124       |

| Fig. 6.20 State diagram of the proposed TD.                                                                                                                                             | 125       |

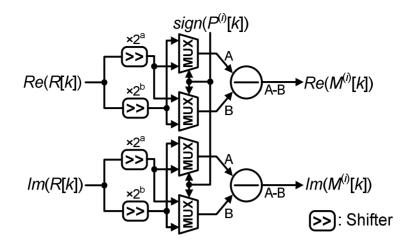

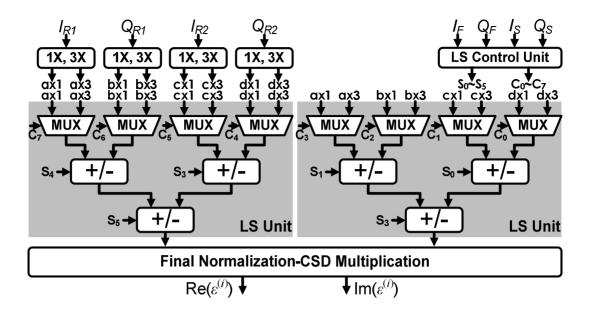

| Fig. 6.21 Design of the divider-free STBC decoder.                                                                                                                                      | 126       |

| Fig. 6.22 Block diagram of the two-stage dichotomy demapper.                                                                                                                            | 127       |

| Fig. 6.23 Design of the LS estimator.                                                                                                                                                   | 128       |

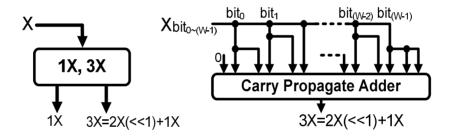

| Fig. 6.24 Design of the coordinate precalculator.                                                                                                                                       | 128       |

| Fig. 6.25 Block diagram of the path decorrelator.                                                                                                                                       | 130       |

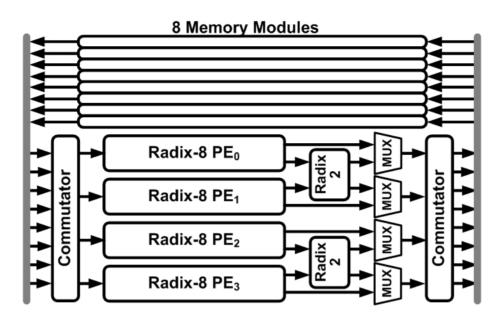

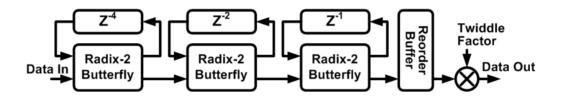

| Fig. 6.26 Radix-8 1024-point parallel memory-based FFT architecture.                                                                                                                    | 132       |

| Fig. 6.27 Radix-8 processing element.                                                                                                                                                   | 132       |

| Fig. 6.28 Addressing scheme of the write-in data.                                                                                                                                       | 133       |

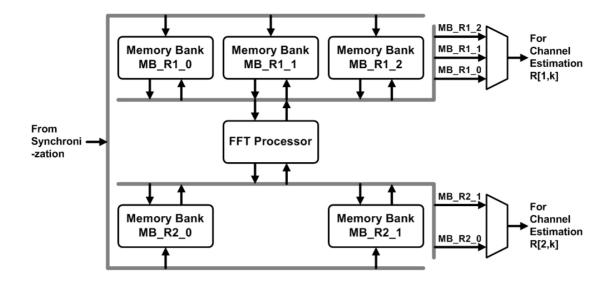

| Fig. 6.29 FFT processor arranged with five memory banks.                                                                                                                                | 135       |

| Fig. 6.30 Flow chart of the proposed receiver.                                                                                                                                          | 135       |

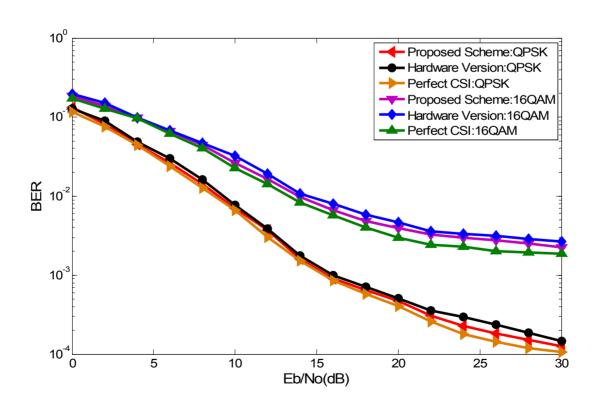

| Fig. 6.31 BER performances at $v_e$ of 120 km/hr.                                                                                                                                       | 136       |

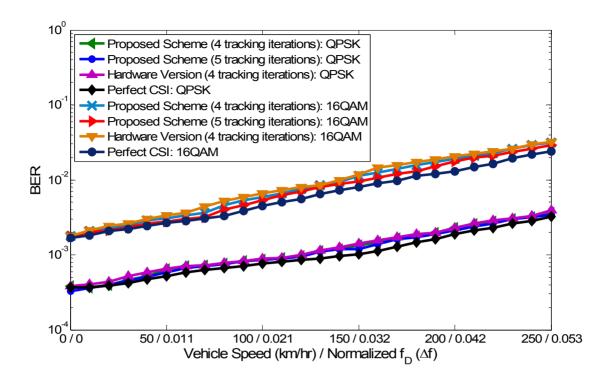

| Fig. 6.32 BER performances versus the vehicle speed.                                                                                                                                    | 137       |

| Fig. 6.33 Chip layout of the proposed STBC-OFDM downlink baseband rece                                                                                                                  | eiver IC. |

|                                                                                                                                                                                         | 139       |

| Fig. 6.34 Area proportion of the proposed STBC-OFDM downlink baseband                                                                                                                   | receiver. |

|                                                                                                                                                                                         | 140       |

| Fig. 6.35 Area proportion of the proposed two-stage channel estimator.                                                                                                                  | 142       |

| Fig. 6.36 Hardware reduction of the proposed channel estimator.                                                                                                                         | 143       |

|                                                                                                                                                                                         |           |

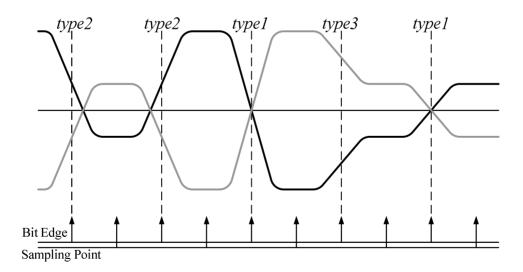

| Fig. A.1 Three transition types in the differential 4-PAM symbol stream.                                                                                                                | 150       |

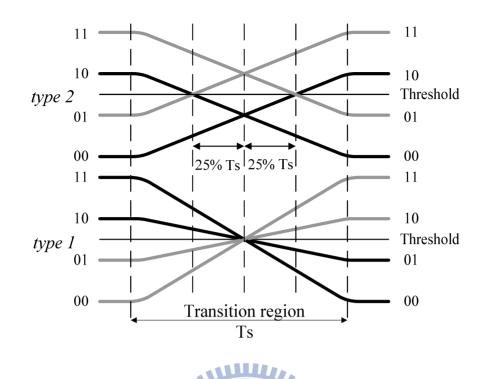

| Fig. A.2 Comparisons of type 1 and type 2 transitions in the differential 4-PAM |      |

|---------------------------------------------------------------------------------|------|

| signals.                                                                        | 152  |

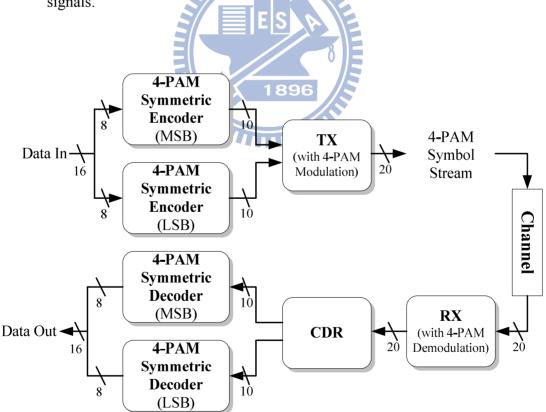

| Fig. A.3 Structure of 4-PAM symmetric encoders and decoders for 4-PAM signal    | ling |

| system.                                                                         | 152  |

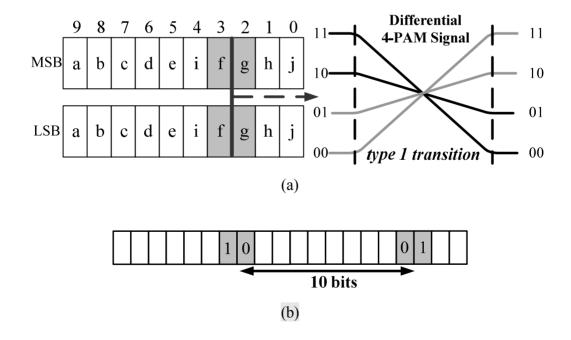

| Fig. A.4 (a) Type 1 transition in the 4-PAM symmetric code and (b) frame        |      |

| synchronization.                                                                | 153  |

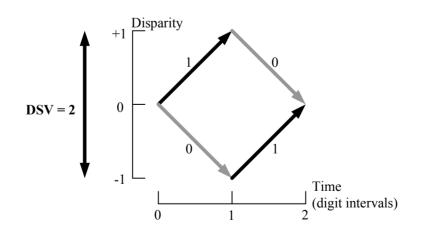

| Fig. A.5 Unit cell of running disparity.                                        | 154  |

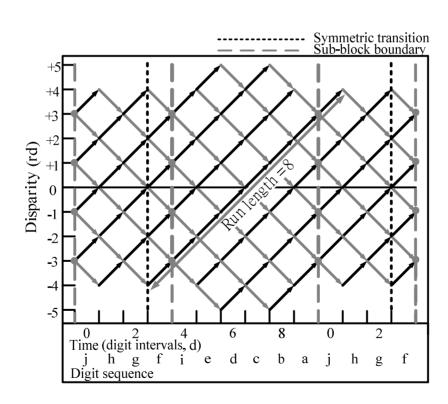

| Fig. A.6 Disparity versus time plot.                                            | 155  |

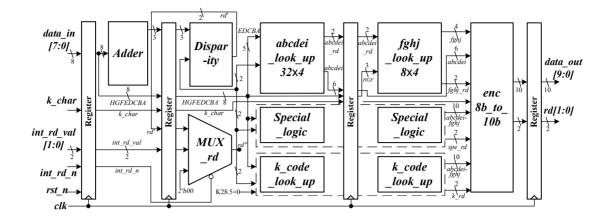

| Fig. A.7 Block diagram of the 4-PAM symmetric encoder.                          | 158  |

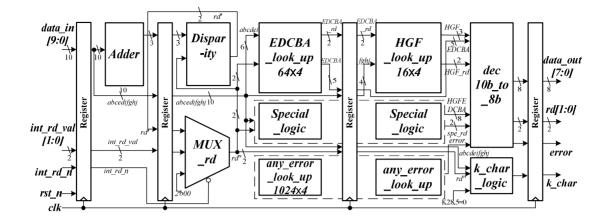

| Fig. A.8 Block diagram of the 4-PAM symmetric decoder.                          | 159  |

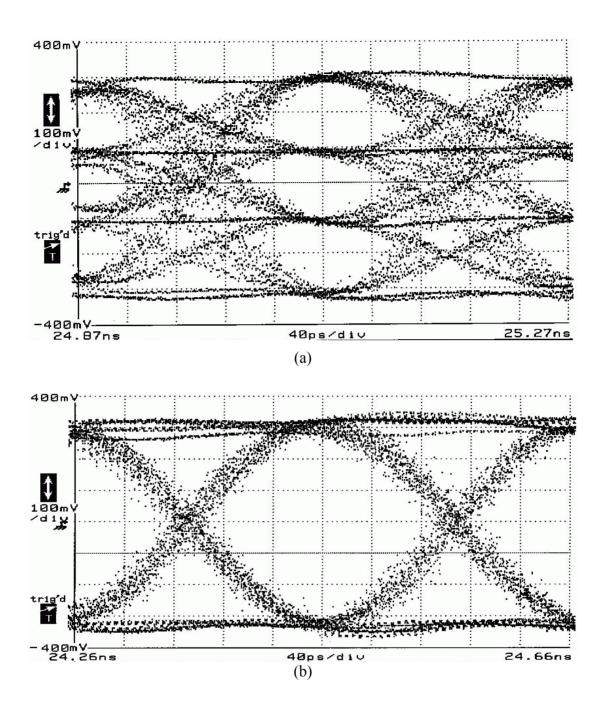

| Fig. A.9 Measurement results [90] of (a) all types of transitions and (b) only  |      |

| maximum-swing type1 transitions of the differential 4-PAM signal.               | 161  |

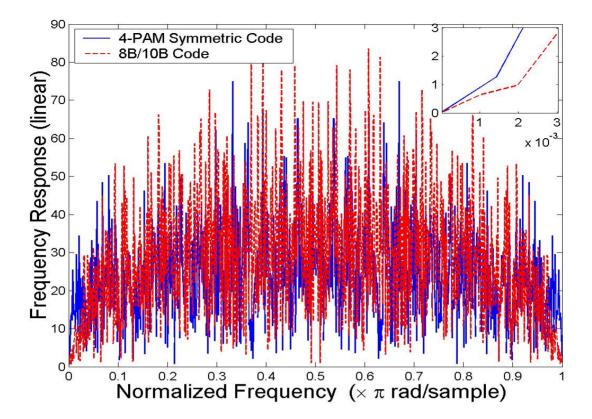

| Fig. A.10 Frequency responses of the 4-PAM symmetric code and the 8B/10B co     | de.  |

|                                                                                 | 162  |

# Chapter 1 Introduction

### 1.1 Background

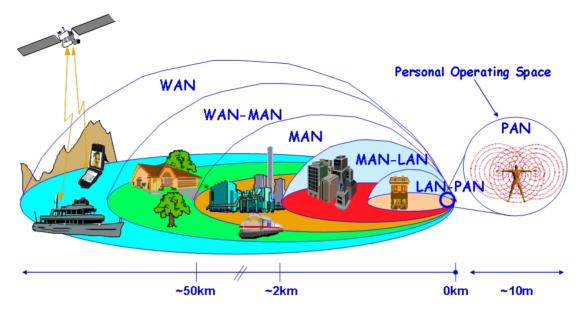

Data networking and telecommunication are fundamental changed by the wireless communication development, which is making integrated networks a reality. The users can enjoy the fully distributed computing and communications without the wire, any time, anywhere. There are two different types of wireless services: 1) the fixed wireless provides a set of services similar to that of the traditional fixed-line services but using wireless as the medium of transmission; 2) the mobile wireless offers the additional functionality of portability and mobility. IEEE (Institute of Electrical and Electronics Engineers) have developed different methods and standards of wireless communication based on various commercially driven requirements. As shown in Fig. 1.1, based on their specific application and transmission range, the standards of wireless communication can be roughly classified into four categories: Wireless Personal Area Network (WPAN), Wireless Local Area Network (WLAN), Wireless Metropolitan Area Network (WMAN) and Wireless Wide Area Network (WWAN). These categories are summarized in Table 1.1 and briefly introduced below.

• WPAN is a computer network which communicates devices centered on an individual personal workspace. The devices include cell phones and personal digital assistants (PDAs), laptops, PCs, printers, digital cameras and video game. The range of WPAN is typically within about 10 m. The

Fig. 1.1 Wireless network area definition [4].

standards of WPAN include IEEE 802.15.1 Bluetooth [1], IEEE 802.15.3 Ultra Wideband (UWB) [2], and IEEE 802.15.4 low-rate WPAN (LR-WPAN or ZigBee) [3].

- WLAN also uses radio communication in unlicensed band to realize the same functionality that a wired LAN has. It is designed to provide in-building broadband coverage. The range of WLAN is typically within about 100 m. IEEE 802.11 family defines a set standard (Wi-Fi) of WLAN which currently includes six over-the-air modulation techniques, and the most popular techniques are those defined by the a, b, g and n amendments to the original standard [5], [6]. However, the usage of IEEE 802.11 standard is restricted by the small transmitting range and the lack of mobility.

- WMAN is optimized for a larger geographical area than a WLAN, ranging from several blocks of buildings to entire cities, and initially proposed for last mile connectivity. WMAN is defined by IEEE 802.16 Working Group on Broadband Wireless Access (BWA) Standards and commercially known as Worldwide Interoperability for Microwave Access (WiMAX) which defines broadband Internet access from fixed or mobile devices via antennas.

|                   | 802.15                                                                           | 802.11                                                                                                                                           | 802.16                                                                                         | 802.20                                       |  |

|-------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Range             | 1-10 m                                                                           | 100 m                                                                                                                                            | 4-6 miles                                                                                      | 9 miles                                      |  |

| Application       | Personal<br>workspace                                                            | Indoor<br>environment                                                                                                                            | Outdoor fixed<br>or mobile<br>environment                                                      | Outdoor high<br>mobile<br>environment        |  |

| Spectrum          | Unlicensed                                                                       | Unlicensed                                                                                                                                       | Licensed<br>Unlicensed                                                                         | Licensed                                     |  |

| Frequency<br>Band | Adapt to different spec.                                                         | 2.4 GHz, 5 GHz                                                                                                                                   | 10-66 GHz<br>2-11 GHz                                                                          | < 3.5 GHz                                    |  |

| Data Rates        | 1-3 Mbps<br>for Bluetooth<br>11-55 Mbps for<br>UBW<br>20-250 Kbps<br>for LR-WPAN | Up to 54 Mbps in<br>20 MHz<br>bandwidth<br>for IEEE<br>802.11-2007<br>Up to 600 Mbps<br>using MIMO<br>in 40 MHz<br>bandwidth for<br>IEEE 802.11n | Up to 75 Mbps in<br>20 MHz<br>bandwidth for<br>IEEE<br>802.16-2004 and<br>IEEE<br>802.16e-2005 | Downlink<br>> 1 Mbps<br>Uplink<br>> 300 kbps |  |

| Channel           | NLOS                                                                             | NLOS                                                                                                                                             | LOS<br>(10-66 GHz)<br>NLOS<br>(2-11 GHz)                                                       | NLOS                                         |  |

TABLE 1.1COMPARISONS OF WIRELESS STANDARDS

The average cell ranges for WMAN networks is about 4-6 miles in non-line of sight (NLOS) environment, and service ranges up to 10 miles are in line of sight (LOS) applications [7], [8].

• WWAN is a computer network covering a more broad geographical area as contrasted with WMAN and optimized for full mobility up to vehicular speeds of 250 km/hr. WWAM is specified by IEEE 802.20 standard approved on June 2008 [9]. The air interface operates in bands below 3.5 GHz and with a peak data rate of over 1 Mbps.

Under the fast development of portable Internet services, the wireless communication technologies providing high data rate and credible performance have gradually became the mainstream in order to satisfy the requirements of various multimedia transmissions.

IEEE 802.16 working group established in 1999 standardizes the air interface and related functions associated with broadband WMAN. The first version of IEEE 802.16 standard (802.16.1) was an air interface for 10 to 66 GHz and completed in December 2001 [10]. It only supports single carrier (SC) modulation in the physical (PHY) layer with only a LOS capability. IEEE 802.16a standard ratified in January 2003 was an amendment to IEEE 802.16 [11]. It provides the capacities of a point-to-multipoint connection and NLOS transmission in the 2-11 GHz band. The PHY layer was therefore extended to include orthogonal frequency division multiplex (OFDM) and orthogonal frequency division multiple access (OFDMA). In September 2003, IEEE 802.16d was a revision project aiming to align the standard with aspects of the European Telecommunications Standards Institute (ETSI) HiperMAN standard [12]. This project concluded in 2004 with the release of IEEE 802.16-2004 [7] which superseded the earlier IEEE 802.16 documents. An industry consortium, WiMAX adopted IEEE 802.16-2004 as the first solution of fixed applications.

IEEE 802.16e-2005 (IEEE 802.16e) concluded in 2005 [8], which is often referred to as mobile WiMAX, is an extension of IEEE 802.16-2004 for providing high data rate transmission and mobility of WMAN. It enables mobile speed up to 120 km/hr, but also be backward compatible to support the fixed mode in IEEE 802.16-2004. Operation in mobile mode is limited to the licensed bands between 2-6 GHz; on the other hand, operation in fixed mode is limited to 2-11 GHz. It is based on an OFDMA technique to support multiple access scheme and multiple-input multiple-output (MIMO) systems over multipath fading channels. IEEE 802.16e is followed in this dissertation. Several distinct features of IEEE 802.16e standard are described as follows [13], [14]:

• Throughput: The technology at theoretical maximums could support about 75 Mbps in a 20 MHz channel using 64 quadrature amplitude modulation (QAM) with code rate 3/4. Moreover, MIMO technology can be exploited to further improve the transmission rate under good transmitting conditions.

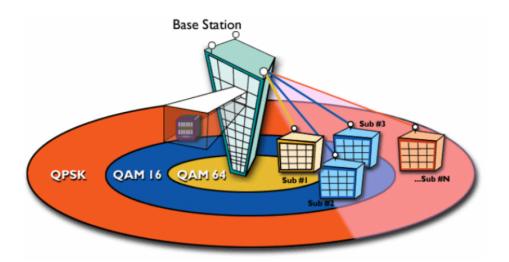

Fig. 1.2 Concept of AMC [15].

- Adaptive modulation and coding (AMC): IEEE 802.16e supports the dynamic adaptive modulation scheme which can adaptively configure the modulation and forward error correction coding schemes according to the channel conditions. As shown in Fig. 1.2, when the channel is good, the base station (BS) transmits data in 64-QAM with high code rate to achieve high transmission rate. In contrast, when the channel is poor, the base station chooses the small constellation and lower code rate to transmit. AMC significantly increases the transmission capacity and the coverage range.

- Quality of service (QoS): QoS is to resource reservation control mechanisms over the air interface on a frame-by-frame basis. It is the ability to provide different priority to different applications, users, or data flows, or to guarantee a certain level of performance to a data flow. The sub-channelization and medium access protocol (MAP) scheme let the scheduling in medium access control (MAC) layer become more flexible.

- Mobility: The mechanism of handover is optimized to be no longer than 50 ms. It can ensure the real-time operation without service degradation. This is especially important for the real-time applications such as Voice over Internet Protocol (VoIP). The system also supports the power

management with sleep and idle modes to extend the battery life of handheld subscriber devices.

• Security: The security specification is the most advanced in current wireless access systems. It offers Extensible Authentication Protocol (EAP) based authentication, Advanced Encryption Standard-Counter with CBC-MAC mode (AES-CCM) based authentication encryption, and Cipher-based Message Authentication Code (CMAC) and Hashed Message Authentication Code (HMAC) based control message protection scheme.

### **1.2** Motivation

IEEE 802.16e systems effectively provide wireless transmission of data using a variety of transmission modes from point-to-multipoint links to portable and fully mobile internet access. The research and development of IEEE 802.16e systems have gained more and more interest and became the worldwide topic. However, in mobile wireless communication, the channels often vary rapidly, which results in a large Doppler spread, particularly when the mobile station (MS) moves at a vehicular speed. A fundamental phenomenon that makes credible wireless transmission expensive and difficult is time-varying multipath fading. In order to improve the transmission quality in fast and selective fading channels, transmit diversity is an effective technology for reducing fading effect in mobile wireless communication, especially when receive diversity is expensive or impractical to acquire.

In recent years, space-time block code (STBC) [16], [17] has been shown to give high code efficiency and good performance. It is suggested to be applied in an OFDM system since OFDM systems with multiple antennas can provide better communication performance by utilizing transmit diversity [16]-[20]. Transmit diversity has been studied extensively as a method of combating impairments in wireless fading channels. However, the multiple antenna technologies bring some new challenges in attempts to realize STBC-OFDM systems. The most important challenge is the channel estimation [21]. Accurate channel state information (CSI) is

required for diversity combining, coherent detection, and decoding. Nevertheless, it is usually difficult to obtain in particular for time-varying multipath fading channels. Although STBC can still achieve the desired transmit diversity with small errors in CSI, a significant degradation is observed when the channel estimation error increases. Sending more preamble symbols or inserting more pilots in an OFDM symbol during the transmission could improve the channel estimation accuracy, but the bandwidth efficiency is also degraded. Hence, a robust channel estimation scheme is needed for good operation when the CSI is not exactly known. Moreover, the STBC-OFDM system performance is also susceptible to the synchronization errors which have been known to rotate the phase and destroy the orthogonality of an OFDM symbol. The mechanisms of synchronization are necessary to overcome these problems. As a result, the success of implementing an STBC-OFDM system in high mobility decides on two crucial challenges, synchronization and channel estimation.

In this dissertation, we focus on the design and development of a downlink baseband receiver applied in STBC-OFDM systems for IEEE 802.16e in mobile mode. Two main tasks, high quality synchronization and robust channel estimation, are performed. The proposed STBC-OFDM system is expected to present a solid foundation for WMAN system design in fixed and mobile wireless communication.

### **1.3** Thesis Organization

The rest of this dissertation is organized as follows. Chapter 2 introduces the concepts of OFDM, OFDMA and MIMO techniques and also briefly overviews the IEEE 802.16e OFDMA specification. Chapter 3 presents the architecture design and the performance simulation of the proposed STBC-OFDM system with two transmit antennas and one receive antenna. The proposed system aims to provide high performance for WMAN communication in fixed and mobile environments. It provides the simple and robust symbol boundary detection and carrier frequency offset estimation schemes and an accurate but hardware affordable two-stage channel estimation strategy to overcome the challenge of outdoor fading channels. In Chapter 4, the robust two-stage channel estimator for STBC-OFDM systems is proposed and analyzed. An efficient architecture of the proposed channel estimator is provided for

low-complexity hardware implementation while keeping the high performance. Chapter 5 discusses a novel programmable FIR filter based on higher radix recoding for low-power and high-performance applications. In order to verify the feasibility, the hardware implementation and the experimental results of the proposed receiver are presented in Chapter 6. Finally, Chapter 7 gives the conclusions of the proposed receiver. In addition, Appendix A presents a study of a DC-balanced low-jitter transmission code for 4-PAM signaling.

# Chapter 2 Overview of IEEE 802.16e OFDMA and MIMO Systems

### 2.1 Introduction

IEEE 802.16-2004 [7] specifies the air interface for fixed BWA systems and has been updated and extended to IEEE 802.16e-2005 [8] for mobile BWA systems with the concept of scalable OFDMA which is an effective technique for high bit rate applications over multipath channels. There are several specifications of IEEE 802.16e-2005 PHY layer for different applications and frequency range. For example, SC operates from 10 GHz to 66 GHz in LOS; besides, SCa, OFDM and OFDMA operate below 11 GHz in NLOS.

In this dissertation, we focus on the IEEE 802.16e OFDMA specification that supports the multi-antenna technology. We will briefly introduce the concepts of OFDM and OFDMA in this chapter. MIMO technologies will also be introduced. Finally, we give an overview of the IEEE802.16e OFDMA standard.

### 2.2 Overview of OFDMA

OFDM modulation offers an attractive technique for high-speed data transmission in mobile communication since it can effectively combat frequency-selective multipath fading using relatively simply frequency-domain equalization. OFDM has been widely adopted in several standards, e.g. digital video broadcasting for terrestrial (DVB-T) [22], high-speed WLAN and WMAN such as IEEE 802.11b/g (Wi-Fi) and IEEE 802.16 (WiMAX). Moreover, the high computational complexity of OFDM implementation has became possible due to the success development of digital signal processing (DSP) and very large scale integrated circuit (VLSI).

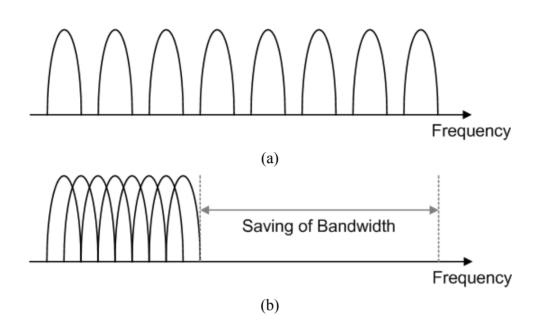

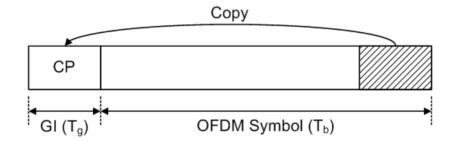

The concept of OFDM is coming from frequency division multiplexing (FDM). In FDM, the entire signal bandwidth is divided into several non-overlapping sub-bands as shown in Fig. 2.1 (a). The conventional parallel data transmission modulates each independent data on different sub-bands, and then these sub-bands are frequency-multiplexed. In order to prevent from the adjacent channel interference, the spectrum spacing allocated between sub-bands leads to inefficient utilization of the signal bandwidth. This problem is overcome by employing overlapping sub-bands as shown in Fig. 2.1 (b), and the signal bandwidth can be effectively utilized. Furthermore, OFDM technology is invented to divide the entire signal bandwidth is into mutual orthogonal overlapping subcarriers, and the orthogonality guarantees subcarrier transmission without interference from each other. As a result, the OFDM technology can achieve high spectral efficiency. Each transmitted signal in each narrow band subcarrier experiences flat channel fading; thus, the channel equalization can be performed by a simple one-tap frequency-domain equalizer. However, the channel delay spread causes the inter-symbol interference (ISI) which destroys the orthogonality of subcarriers in OFDM. In order to avoid ISI effect, a guard interval with the length longer than the maximum channel delay spread is inserted to the frond of an OFDM symbol. Although the guard interval can be used to resolve ISI problem, the loss of orthogonality among subcarriers causes inter-channel interference (ICI). A cyclic prefix (CP), which is equal to a part of the OFDM symbol tail, is widely adopted in current standards to maintain the subcarrier orthogonality and avoid ICI effect as shown in Fig. 2.2.

Fig. 2.1 (a) Conventional non-overlapping sub-bands. (b) Overlapping sub-bands.

Fig. 2.2 OFDM symbol with cyclic prefix.

OFDMA technology is a multi-user version of OFDM modulation, and it is a major multiple access method considered for 802.16e-2005 PHY provides layer is achieved communication. Multiple access mutually exclusive subsets of subcarriers to simultaneous low data rate transmission from several users. The all available subcarriers of uplink and downlink in OFDMA are divided into several subsets of subcarriers termed as sub-channels as shown in Fig. 2.3.

future wireless systems. IEEE OFDMA specification for multi-user in OFDMA by assigning individual users, which allows

OFDMA can be seen as an alternative to combining OFDM with time division

Fig. 2.3 OFDMA subcarrier allocation.

Fig. 2.4 Two-dimensional resources of OFDMA transmission.

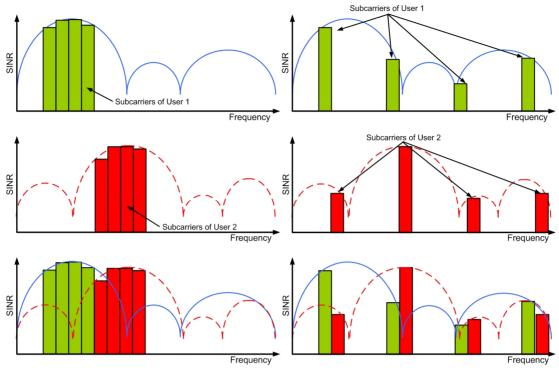

multiple access (TDMA) or time-domain statistical multiplexing, i.e. packet mode communication. As shown in Fig. 2.4, the resources of OFDMA transmission are partitioned in the time-frequency space, and time slots are assigned along the OFDM symbol index as well as OFDM subcarrier index. OFDMA is considered as highly suitable for broadband wireless networks due to the advantages including scalability, MIMO easy applying, and the multi-user diversity ability to take advantage of channel frequency selectivity. OFDMA has another advantage of that low-data-rate users can send continuously with low transmission power. Constant delay and shorter delay can be achieved. In IEEE 802.16e OFDMA specification, there are two types of data allocation for sub-channelization, contiguous and diversity. As shown in Fig. 2.5, the

Adjacent Subcarrier Allocation (AMC)

Distributed Subcarrier Allocation (FUSC, PUSC)

Fig. 2.5 Adjacent and distributed subcarrier allocations.

contiguous permutation collects contiguous subcarriers to form a sub-channel. On the contrary, the diversity permutation pseudo-randomly spread out the subcarriers of sub-channel over the entire bandwidth and brings the benefit of frequency diversity and robustness against the frequency select fading channel.

A concept of scalable OFDMA (S-OFDMA) [23] is also introduced to the IEEE 802.16e OFDMA specification, which supports for 128, 512, 1K, and 2K fast Fourier transform (FFT) sizes to address a variable bandwidth sizes from 1.25MHz to 20MHz for NLOS operations as shown in Table 2.1.

Several basic term definitions should be established to help us to follow IEEE 802.16e OFDMA specification.

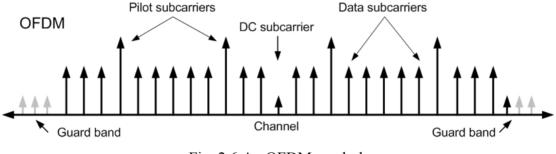

Subcarrier: An OFDM symbol is made up of subcarriers as shown in Fig.

2.6. There are three subcarrier types: data subcarriers for data transmission, pilot subcarriers for channel estimation purposes and null subcarriers for no transmission, guard bands, non-active subcarriers and

| Parameters                     | Values                   |     |      |      |

|--------------------------------|--------------------------|-----|------|------|

| System channel bandwidth (MHZ) | 1.25                     | 5   | 10   | 20   |

| FFT Size                       | 128                      | 512 | 1024 | 2048 |

| Sampling Factor                | 28/25                    |     |      |      |

| Sampling Frequency             | 1.4                      | 5.6 | 11.2 | 22.4 |

| CP Ratio                       | 1/32, 1/16, 1/8, and 1/4 |     |      |      |

| Modulation Mode                | QPSK, 16QAM, and 64QAM   |     |      |      |

| Subcarrier Frequency Spacing   | 10.94 kHz                |     |      |      |

| Frame Duration                 | Duration 5 ms            |     |      |      |

TABLE 2.1

Scalable OFDMA parameters

Fig. 2.6 An OFDM symbol.

the DC-subcarrier. Subcarrier spacing is 10.9375 KHz.

• *Sub-channel*: It is a set of subcarriers. IEEE 802.16 OFDMA systems define two modes of sub-channel building method. In the distributed subcarrier permutation mode, subcarriers of a sub-channel are not contiguous, and their distribution is determined by the permutation types of Partial Usage of Sub-channels (PUSC) and Full Usage of Sub-channels (FUSC). In adjacent subcarrier mode, sub-channels are constituted of bins and determined the distribution by the permutation type of AMC.

IEEE 802.16e OFDMA specification supports multiple schemes for dividing the frequency-domain and time-domain resources between users, which is called sub-channelization. The relationship between the basic terms of the two-dimensional units is shown in Fig. 2.7 and brief introduced as follows.

Fig. 2.7 Two-dimensional basic terms in the OFDMA data structure.

- *Frame*: It is an essential packet format of transmitted data sequence. A frame may contain both an uplink sub-frame and a downlink sub-frame.

- *Sub-frame*: It is a component to make up a frame and identified as an uplink sub-frame and a downlink sub-frame.

- *Zone*: A zone is the region of contiguous OFDMA symbols which are applied with the same permutation scheme (i.e., PUSC, FUSC or AMC). It is allowed to have different zones in a sub-frame.

- *Segment*: The set of available sub-channels form a segment which is applied with the same MAC definition. There can be three segments in a zone.

- *Burst*: It is a region which includes the contiguous sub-channel and OFDMA symbol to transmit the broadcast or unique data for

corresponding users.

- *Slot*: It is the minimum possible data allocation unit and spans both the time domain (OFDM symbol) and frequency domain (sub-channel). It contains 48 data subcarriers for all sub-channelization schemes, but their arrangement is different in different schemes [24].

- *Cluster*: It contains 14 adjacent subcarriers over 2 contiguous symbols with 4 pilot subcarriers in PUSC permutation scheme.

### 2.3 MIMO Systems

MIMO technology is the use of multiple antennas at both the transmitter and receiver to improve communication performance. IEEE 802.16e standard incorporates MIMO-OFDMA specification. MIMO is a current theme in wireless communication research since it can offer significant increases in data throughput, coverage range, and system reliability without additional bandwidth or transmit power. Nevertheless, these advantages usually conflict with one another, for example, increasing the data throughput will restrict the reliability improvement. Depending on application requirements, the MIMO technology can be divided into three main schemes, beamforming [25], spatial multiplexing (SM) [26] and space-time coding (STC) [27] as introduced below.

*Beamforming* technology achieves the spatial selectivity by using adaptive or fixed receive/transmit directional patterns for directional signal transmission or reception. The same signal is emitted from each transmit antennas with appropriate weighting and phasing such that the signal power is maximized at the receiver input. Beamforming can bring the advantages of improving the signal gain from constructive combining and reducing the multipath fading effect. Conventional beamforming employs a fixed directional pattern to filter the signals. In contrast, adaptive beamforming uses an adaptive directional pattern to filter the signals with properties of the signals actually received, and it can effectively reject the unwanted noise from other directions. This process may be carried out in the time or frequency domains. Note that beamforming requires knowledge of CSI at the transmitter.

*SM* technology is used to increase the transmission rate by using multiple antennas at both transmitter and receiver. It transmits a high rate data stream by dividing the stream into multiple lower rate sub-streams and transmitting these sub-streams from different transmit antennas in the same frequency channel. If these signals arrive at the receiver antennas with sufficiently different spatial signatures, the receiver can separate these streams. Spatial multiplexing can efficiently increase channel capacity at higher signal to noise ratio (SNR).

*STC* technology is to use multiple transmit antennas to improve the reliability of data transmission in wireless communication systems. It relies on transmitting multiple and redundant copies of the transmitted data stream to the receiver in the hope of the survival physical path between transmission and reception in a good enough channel state to allow reliable decoding. Space time codes can be separated into two main types, STBC and space-time trellis code (STTC). STBC is similarly to block codes and provides only diversity gain but has much less complexity of implementation than STTC. STTC distributes a trellis code over multiple antennas and multiple time slots and provides both coding gain and diversity gain.

More details on these schemes can be found in [27]. Herein, we focus in Alamouti's STBC in two transmit-antenna systems which will be introduced in Chapter 3.

# 2.4 IEEE 802.16e OFDMA Specification

IEEE 802.16e includes multiple PHY specifications such as, SC, SCa, OFDM, and OFDMA, for providing different channel conditions and applications. Herein, the OFDMA specification that supports the multi-antenna technology is followed in this dissertation.

#### 2.4.1 Frame Structure

In the licensed bands, IEEE 802.16 systems can support time-division duplexing (TDD) and frequency-division duplexing (FDD). The other license-exempt bands, the duplexing method shall be TDD. The frame can be composed of several zones that are

Fig. 2.8 An OFDMA frame in TDD mode [8].

divided according to subcarrier allocation methods or MIMO modes. In an FDD frame structure, the downlink (DL) and uplink (UL) sub-frames are allocated in a different frequency band without the transmit transition gap (TTG) and receive transition gap (RTG). In a TDD frame structure, the DL and UL sub-frames are allocated respectively on the same frequency band but at different time. Fig. 2.8 shows an example of an IEEE 802.16e OFDMA frame structure in TDD mode, which is a model frequently referred.

The frame structure consists of the following elements. The first symbol of a transmitted frame is a preamble symbol which is the known pattern in the receiver for the use of cell search, synchronization and channel estimation. Following the preamble symbol, the frame control header (FCH) with fixed size is transmitted for resource allocation such as the subcarriers used, length of DL-MAP and DL\_Frame\_Prefix. The quadrature phase shift keying (QPSK) modulation with code rate 1/2 and four repetitions is used for FCH transmission to ensure the robustness and reliable performance. DL\_MAP and UL\_MAP following FCH message for resource allocation of the various users in DL and UL data bursts. TTG is used to give BS and subscriber station (SS) enough time to change from downlink mode to uplink mode.

Fig. 2.9 An OFDMA frame with multiple zones [8].

For the same reason, RTG is inserted at the end of each frame. Besides, the ranging sub-channel specified in the UL\_MAP message is used for contention-based bandwidth request in UL transmission. ES

For supporting various physical channel conditions, IEEE 802.16 OFDMA systems define two modes of sub-channel building method: the distributed subcarrier permutation mode, including PUSC and FUSC types, and the adjacent subcarrier permutation mode, including AMC type. In this dissertation, PUSC is mainly supported and will be described for the subcarrier allocation scheme in Section 3.3.3. The ratio of these modes can be flexible in the IEEE 802.16 standard. However, one burst of data transmission consists of several slots, and one slot is the minimum possible data allocation unit. In addition, the definition of this slot depends on the OFDMA symbol structure, which varies for DL and UL, for FUSC and PUSC, and for distributed subcarrier permutations and adjacent subcarrier permutation. Fig. 2.9 shows an OFDMA frame with multiple zones. Due to no information about the permutation scheme, the first zone in the DL sub-frame is essentially PUSC to ensure the FCH and DL MAP can be received successfully. Depending on the requirements, the following zones can be applied in PUSC, FUSC, AMC, or Tile Usage of Sub-channels (TUSC). The information of zone transition is indicated in the DL MAP and UL MAP. The maximum number of DL zones in one DL sub-frame is eight. The maximum number of bursts to be decoded in one DL sub-frame is 64.

#### 2.4.2 Preamble Format

The preamble symbol consists of a specific pattern known to the receiver and occupies the duration of an OFDM symbol time. It is used for frame detection, synchronization and initial channel estimation. IEEE 802.16e standard provides three types of carrier sets for different segments in the preamble symbol which can be expressed as

$$PreambleCarrierSet_s = s + 3 \cdot k \tag{2.1}$$

where s=0,1,2 is the index of the carrier set, and k denotes a running subcarrier index. These subcarriers in the preamble symbol are modulated by binary phase shift keying (BPSK) with a specific Pseudo-Noise (PN) code. The PN series modulating the pilots in the preamble can be found in [7]. Each segment in a zone uses one type of preamble carrier sets. For different FFT size, there are total 114 PN series to be chosen by the ID cell parameter and the segment index. The guard band subcarriers are contained both on the left and right side of the spectrum. The DC subcarrier is always be zeroed even if the type of carry set is 0. The power of the preamble subcarriers is boosted by a factor,  $2\sqrt{2}$ , to increase the reliability of preamble. The pilot subcarriers  $p_k$  in the preamble symbol are modulated as

$$\operatorname{Re}\{p_k\} = 4\sqrt{2} \cdot \left(\frac{1}{2} - w_k\right), \quad \operatorname{Im}\{p_k\} = 0$$

(2.2)

where  $w_k$  denotes PN series, and Re{.} and Im{.} stand for the real part and the imaginary part of {.}.

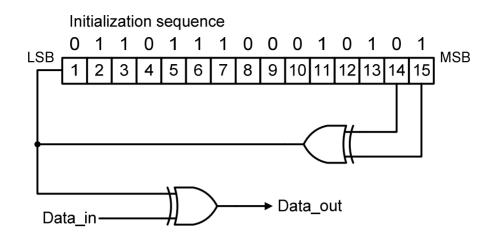

Fig. 2.11 PRBS generator for pilot modulation.

# Pilot Modulation

2.4.3

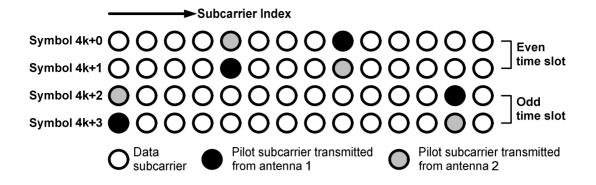

The OFDM symbol structure is constructed using pilots, data, and null subcarriers. The symbol is first divided into basic clusters and null carriers are allocated. In DL PUSC mode, pilots and data carriers are allocated within each cluster as shown in Fig. 2.10. For the proposed system with two transmit antennas, when the pilot subcarrier is transmitted from one antenna, the other antenna will not transmit a pilot on the same subcarrier to avoid the inter-antenna interference. The pilot location schemes periodically change every four OFDMA symbols.

The pseudo-random binary sequence (PRBS) generator depicted in Fig. 2.11 is used to produce a sequence,  $w_k$ . Each pilot is boosted 2.5 dB over the average non-boosted power of each data subcarriers. The value of the pilot modulation, on subcarrier k, shall be derived from  $w_k$ . The pilot subcarriers  $p_k$  are modulated as

$$\operatorname{Re}\{p_k\} = \frac{8}{3} \left(\frac{1}{2} - w_k\right), \quad \operatorname{Im}\{p_k\} = 0.$$

(2.3)

# 2.4.4 Basic Specification in IEEE 802.16e OFDMA

IEEE 802.16e OFDMA specification defines different transmission types according to different purposes and applications. The modulation schemes of QPSK, 16-QAM, and 64-QAM are supported for data subcarrier. The transmission types are constructed by different modulation schemes with different code rates such as QPSK 1/2, QPSK 3/4, 16-QAM 1/2, 16-QAM 3/4, 64-QAM 1/2, 64-QAM 2/3, and 64-QAM 3/4. The major parameters can be derived and described in Table 2.2.

| Parameters                            |                                                 | Deriving formulas                                                                                         |  |  |

|---------------------------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| FFT Size (N)                          |                                                 | 2048, 1024, 512, and 128                                                                                  |  |  |

| Channel Bandwidth (BW)                |                                                 | 1.25-20MHz                                                                                                |  |  |

| Sampling Factor ( <i>n</i> )          |                                                 | <i>n</i> =28/25 if BW is a multiple of 1.25,<br>1.5, 2, and 2.75 MHz<br><i>n</i> =8/7 for the other cases |  |  |

| Ratio of CP to Useful Symbol Time (G) |                                                 | 1/32, 1/16, 1/8, and 1/4                                                                                  |  |  |

| Sampling Frequency $(F_S)$            |                                                 | $floor(n \cdot BW/8000) \times 8000$                                                                      |  |  |

| Sampling Time                         |                                                 | $T_b/N$                                                                                                   |  |  |

| Subcarrier Spacing ( $\Delta f$ )     |                                                 | $F_{s}/N$                                                                                                 |  |  |

| Useful Symbol Time $(T_b)$            |                                                 | $1/\Delta f$                                                                                              |  |  |

| Guard Time $(T_g)$                    |                                                 | $G \cdot T_b$                                                                                             |  |  |

| OFDMA                                 | Symbol Duration ( <i>T<sub>s</sub></i> )        | $T_b + T_g$                                                                                               |  |  |

| Frame Duration $(T_F)$                |                                                 |                                                                                                           |  |  |

| Number                                | of OFDMA Symbols                                | $floor(T_F/T_S)$                                                                                          |  |  |

| DL<br>PUSC                            | Number of Null Subcarriers ( $N_{Null}$ )       |                                                                                                           |  |  |

|                                       | Number of Clusters $(N_C)$                      | $(N - N_{Null})/14$                                                                                       |  |  |

|                                       | Number of Sub-channels $(N_{SC})$               | $N_c/2$                                                                                                   |  |  |

|                                       | Number of Pilot Subcarriers $(N_{Pilot})$       | $N_C \times 2$                                                                                            |  |  |

|                                       | Number of Data Subcarriers (N <sub>Data</sub> ) | $N_C \times 12$                                                                                           |  |  |

TABLE 2.2

MAJOR PARAMETERS OF IEEE 802.16E OFDMA SPECIFICATION

# Chapter 3 Downlink Baseband STBC-OFDM System Architecture

# 3.1 Introduction

In this chapter, the proposed downlink baseband STBC-OFDM system architecture will be described. This architecture can provide high transmission rate in IEEE 802.16e downlink communication as an alternative solution for WMAN in fixed and mobile wireless communication.

Recently, STBC-OFDM systems have received a lot of attention [28], [29] and are also adopted in IEEE 802.16e systems. Although STBC-OFDM systems with multiple antennas can provide diversity gains to improve transmission efficiency and quality of mobile wireless systems, accurate CSI is required for diversity combining, coherent detection, and decoding. Moreover, the system performance is also susceptible to the synchronization error. Therefore, synchronization and channel estimation are two crucial challenges for realizing a successful STBC-OFDM system.

Hence, a downlink baseband receiver scheme for STBC-OFDM systems is proposed and can be applied in IEEE 802.16e specification. In the proposed receiver, two main tasks, synchronization and channel estimation, are implemented. The synchronization includes symbol timing detection and carrier frequency recovery. A novel match filter is proposed to precisely detect symbol boundary, and a ping-pong algorithm is presented to effectively improve the performance of carrier frequency synchronization [30]. Moreover, a refined two-stage channel estimation method with an initialization stage and a tracking stage is adopted to accurately estimate CSI over doubly selective fading channels [31], [32]. The initialization stage uses discrete Fourier transform (DFT)-based channel estimation method [33], [34] with the multipath interference cancellation (MPIC)-based decorrelation scheme to identify significant channel paths of the primary channel impulse responses. Then, the tracking stage uses decision-feedback (DF) DFT-based channel estimation with Newton's method [35], [36] to track the path variations of these paths.

The rest of this chapter is organized as follows. In Section 3.2, we describe the system specification of the proposed STBC-OFDM system with two transmit antennas and one receive antenna. In Section 3.3, we delineate the transmitter architecture. We then describe the proposed receiver in Section 3.4. The system simulation results are presented in Section 3.5. Finally, the conclusions of this chapter are drawn in Section 3.6.

# 3.2 System Specification and Design Targets

IEEE 802.16e includes multiple PHY specifications such as, SC, SCa, OFDM, and OFDMA, for providing different channel conditions and applications. The OFDMA specification that supports multi-antenna technology is adopted in the proposed STBC-OFDM system. In downlink transmission, the distributed subcarrier allocation of PUSC is supported, and the major parameters and the design targets of the proposed STBC-OFDM system are summarized in Table 3.1.

The system occupies a bandwidth of 10 MHz and operates in 2.5 GHz frequency band. The sampling frequency is 11.2 MHz. FFT size (*N*) is set to 1024. Each OFDM symbol is composed of 1024 subcarriers among which 720 and 120 subcarriers are used to transmit data symbols and pilots, and the remaining 184 subcarriers are used as either a DC subcarrier or virtual subcarriers. In IEEE 802.16e, the modulation schemes of QPSK, 16-QAM, and 64-QAM are supported for data subcarriers, while BPSK is adopted for pilot subcarriers and preamble symbol. In the hardware design, the data subcarrier modulation schemes target to support QPSK and 16-QAM. The length of CP is 128 sampling periods, i.e., 1/8 of the useful symbol time ( $T_b$ ). Fig. 3.1 depicts the frame format which starts with one preamble symbol and is followed by

#### TABLE 3.1

| MAJOR PARAMETERS AND DESIGN TARGETS OF THE PROPOSED STBC-OFDM |

|---------------------------------------------------------------|

| SYSTEM                                                        |

| Parameters                        |                                                   | Values          |

|-----------------------------------|---------------------------------------------------|-----------------|

| RF Frequency                      |                                                   | 2.5 GHz         |

| System Channel Bandwidth (BW)     |                                                   | 10 MHz          |

| Sampling Frequency $(F_S)$        |                                                   | 11.2 MHz        |

| FFT Size (N)                      |                                                   | 1024            |

| Subcarrier Spacing (⊿f)           |                                                   | 10.9 kHz        |

| Useful Symbol Time $(T_b)$        |                                                   | 91.4 µs         |