國 立 交 通 大 學

電機與控制工程學系

碩 士 論 文

應用於電生理記錄之低功率可調增益 CMOS

放大器晶片設計

**Low-Power Gain-Tunable CMOS Amplifier**

**Design for Neural Recording System**

研 究 生：謝宗哲

指 導 教 授：林 進 燈 博 士

中 華 民 國 九 十 五 年 六 月

應用於電生理記錄之低功率可調增益 CMOS

放大器晶片設計

**Low-Power Gain-Tunable CMOS Amplifier Design for

Neural Recording System**

研究 生：謝宗哲

Student : Zong-Jhe Shie

指 導 教 授：林 進 燈 博 士

Advisor : Dr. Chin-Teng Lin

國立交通大學

Submitted to Department of Electrical and Control Engineering

College of Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Electrical and Control Engineering

June 2006

Hsinchu, Taiwan, Republic of China

中華民國 九十五 年 六 月

# 應用於電生理記錄之低功率可調增益 CMOS

## 放大器晶片設計

**Low-Power Gain-Tunable CMOS Amplifier**

**Design for Neural Recording System**

學生：謝宗哲

指導教授：林進燈 博士

神經科學家與臨床醫師對於觀察腦部數以千億計神經元的同步活動反應有非常重要的需求，多頻道神經元記錄電極是基礎神經科學研究對於獲取臨床和神經元應用的重要發展。近來由於微機電技術的快速進步，侵入式神經元記錄電極可觀察到更多的神經元同步的反應，因此對於低功率生醫放大器發展的需求大增。本論文設計一個低功率可調變增益電生理放大器，具有三種工作模式，可依實驗情況調整。本研究之低功率生醫放大器使用 miller 的概念來實現電生理頻寬的需求，可大量降低因為神經元訊號處於低頻造成被動元件過大而非常困難整合成積體電路的問題，並且可去除因為電極產生的極大 DC offset (1-2V)。此晶片採用台積電 (TSMC) 0.35um 2p4m CMOS 製程，可調式增益為 59 dB ~ 88 dB，低頻 3 dB 頻率 161 Hz，高頻 3 dB 頻率 5.9 k Hz，供應電壓  $\pm 1V$ ，功率消耗 54.5 uW，晶片面積 1.58 mm  $\times$  1.906 mm。

# **Low-Power Gain-Tunable CMOS Amplifier**

## **Design for Neural Recording System**

Student: Zong-Jhe Shie

Advisor: Dr. Chin-Teng Lin

Department of Electrical and Control Engineering

National Chiao Tung University

### **Abstract**

There is a great demand for technologies that enable neuroscientists and clinicians to observe the simultaneous activity of large numbers of neurons in the brain. Multi-electrode neural recordings are important development in basic neuroscience research and knowledge gained from these studies is beginning to enable clinical and neural prosthetic applications. Recent advances in MEMS (micro-electro-mechanical-system) technology enhancement, the advent of fully implantable multi-electrode arrays that can observe more the simultaneous activity of neurons has created the great need for fully integrated low power bio-amplifier. We design a low-power and programmable gain neural recording amplifier which has three kinds of work mode adjust the case of experiment. The low power bio-amplifier uses the concept of Miller effect to realize the bandwidth of neural recording and can greatly reduce the size of passive device which is too hard to be integrated on chip. Simultaneously it could reject very large DC offsets from electrode-electrolyte interface. The resulting amplifier built in a standard 0.35um 2p4m CMOS process 、 programmable gain from 59 dB to 88 dB 、 pass signal from 161 Hz to 5.9 k Hz 、

power supply  $\pm 1\text{V}$  and a power dissipation of  $54.5\text{ }\mu\text{W}$  while consuming  $1.58\text{ mm}^2$  \*

$1.906\text{ mm}$  of chip area.

## 致謝

本論文的完成，首先要感謝指導教授林進燈博士這兩年來的悉心指導，在學業及研究方法上受益良多，在生活及待人處事上，老師更是提供非常多寶貴的觀念，讓我學習到非常非常多的知識。另外也要感謝口試委員們的建議與指教，使得本論文更為完整。

其次，感謝資訊媒體實驗室的學長仁峰博士、得正博士及經翔、俊谷、紹航、家昇、室友紹倫、祐任、家賢的相互砥礪，及所有學長、學弟妹們和腦科學研究中心在研究過程中所給我的鼓勵與協助。尤其是仁峰學長，在理論及程式技巧上給予我相當多的幫助與建議，讓我獲益良多。

感謝我的父母親謝大華先生和陳阿蘿女士對我的教育與栽培，並給予我精神及物質上的一切支援，使我能安心地致力於學業。此外也感謝女友陸淑對我不斷的關心與鼓勵。

謹以本論文獻給我的家人及所有關心我的師長與朋友們。

# 目錄

|                                          |           |

|------------------------------------------|-----------|

| 致謝 .....                                 | vi        |

| 目錄 .....                                 | vii       |

| 圖目錄 .....                                | ix        |

| 表目錄 .....                                | xi        |

| <b>第一章 緒論.....</b>                       | <b>12</b> |

| 1.1 簡介 .....                             | 12        |

| 1.2 論文架構 .....                           | 18        |

| <b>第二章 電生理訊號與相關研究歷史簡介.....</b>           | <b>19</b> |

| 2.1 電生理訊號 .....                          | 19        |

| 2.2 相關研究歷史簡介 .....                       | 21        |

| 2.2.1 美國密西根大學 .....                      | 22        |

| 2.2.2 美國猶它州大學 .....                      | 27        |

| 2.2.3 美國 Duke 大學 .....                   | 29        |

| 2.2.4 美國華盛頓大學 .....                      | 33        |

| 2.2.5 綜合比較 .....                         | 34        |

| <b>第三章 電生理記錄之低功率多頻道 CMOS 放大器設計 .....</b> | <b>37</b> |

| 3.1 設計架構 .....                           | 37        |

| 3.2 電路設計 .....                           | 42        |

| 3.2.1 前置放大器（緩衝器）設計 .....                 | 42        |

| 3.2.2 高通濾波器設計 .....                      | 44        |

| 3.2.3 低通濾波器 .....                        | 49        |

| 3.2.4 偏壓設計 .....                         | 51        |

|                             |           |

|-----------------------------|-----------|

| 3.3 測試考量 .....              | 51        |

| <b>第四章 晶片實現與結果驗證.....</b>   | <b>56</b> |

| 4.1 晶片設計流程與製作 .....         | 56        |

| 4.2 佈局後的模擬結果 .....          | 62        |

| 4.3 效能比較 .....              | 68        |

| <b>第五章 結論.....</b>          | <b>71</b> |

| 5.1 總結 .....                | 71        |

| 5.2 未來研究方向 .....            | 71        |

| <b>參考文獻 .....</b>           | <b>72</b> |

| <b>附    錄 .....</b>         | <b>78</b> |

| A. DRC .....                | 78        |

| B. LVS .....                | 79        |

| C. 晶片腳位分佈與訊號說明 .....        | 80        |

| D. Tapeout Review Form..... | 81        |

# 圖 目 錄

|                                           |    |

|-------------------------------------------|----|

| 圖 1.1 大腦結構圖 .....                         | 13 |

| 圖 1.2 10-20 國際標準位置 .....                  | 13 |

| 圖 1.3 電生理量測系統 .....                       | 16 |

| 圖 2.1 單一神經元典型電生理訊號 .....                  | 19 |

| 圖 2.2 單一神經元電生理訊號 .....                    | 20 |

| 圖 2.3 電生理訊號頻譜分析 .....                     | 20 |

| 圖 2.4 具訊號處理功能之侵入式微電極 .....                | 23 |

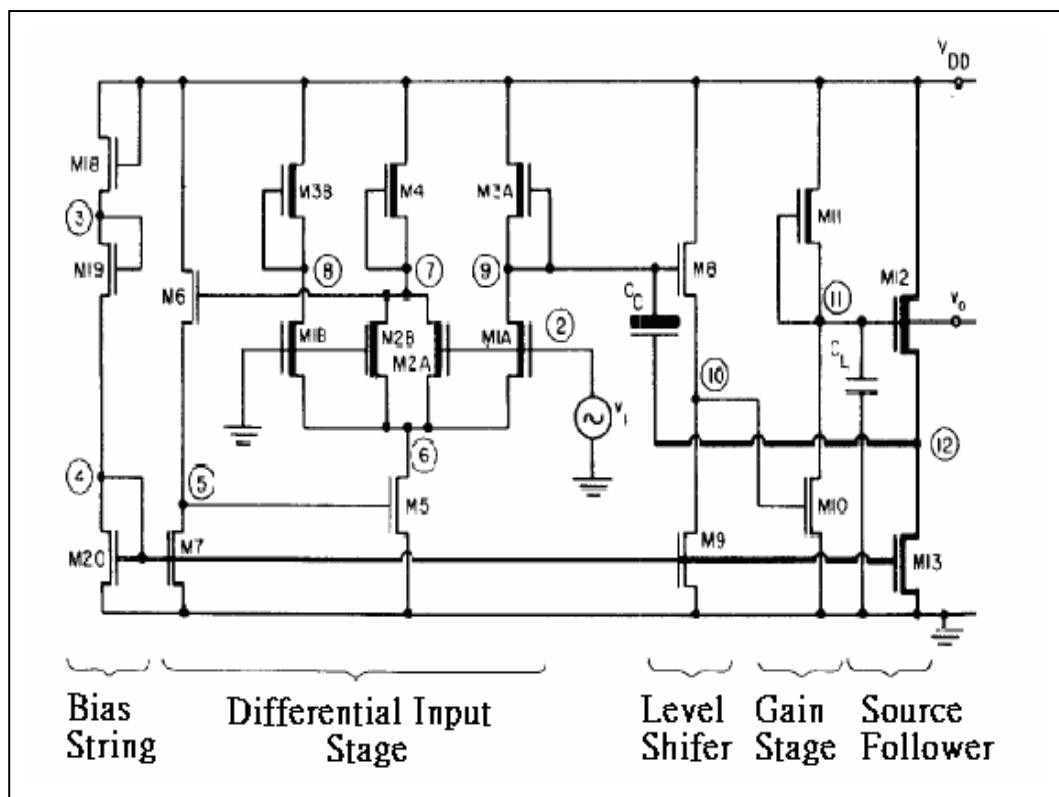

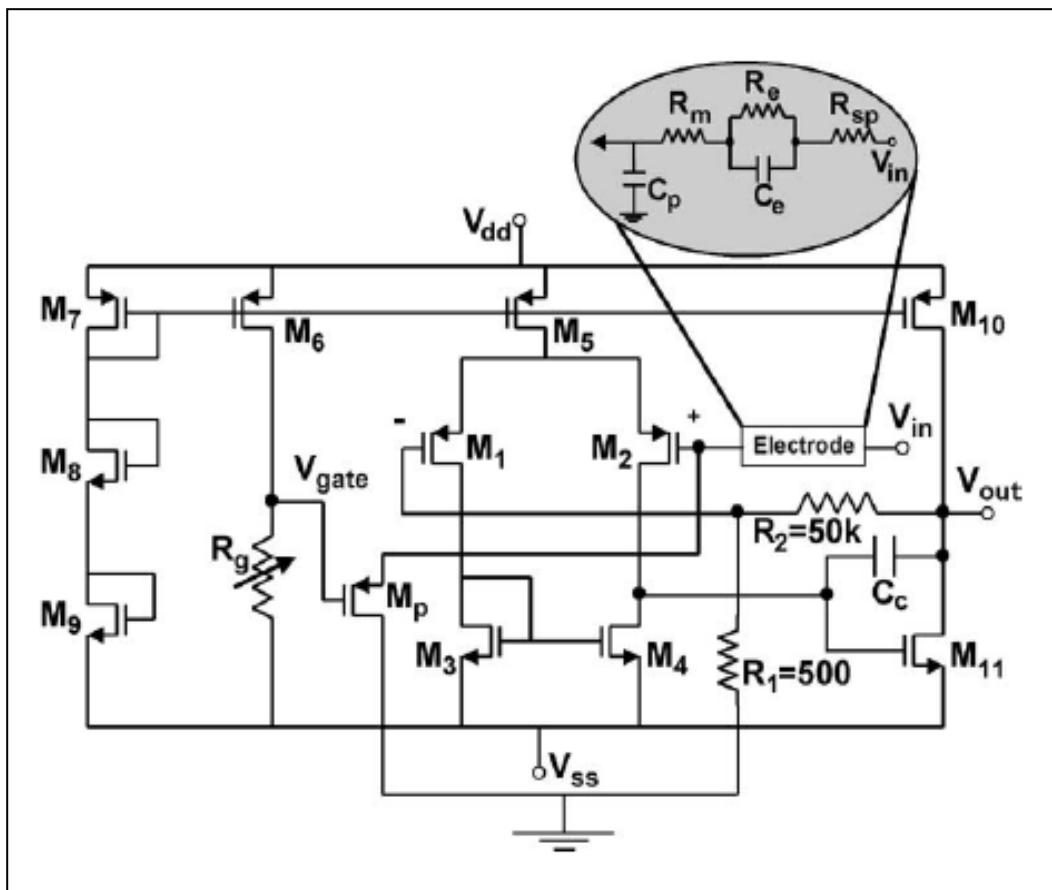

| 圖 2.5 Najafi 電生理放大器電路 .....               | 24 |

| 圖 2.6 Jin Ji 單一輸入電生理放大電路 .....            | 24 |

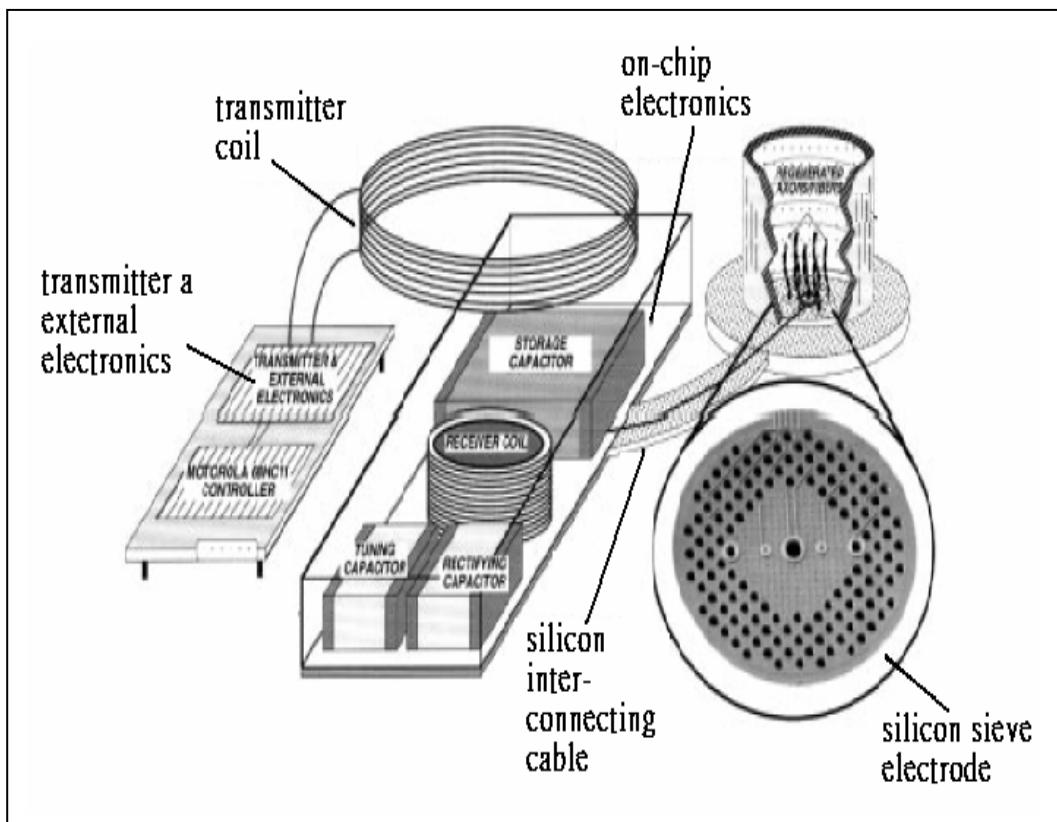

| 圖 2.7 電生理偵測無線系統 .....                     | 25 |

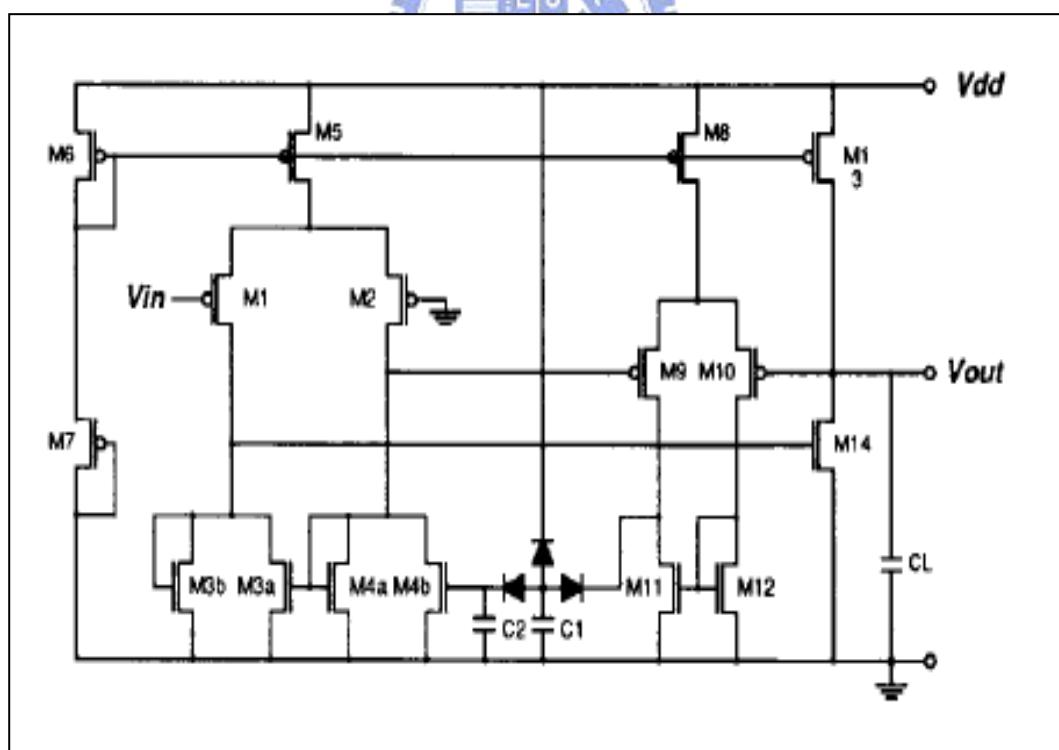

| 圖 2.9 Pedram 新型電生理放大器 .....               | 26 |

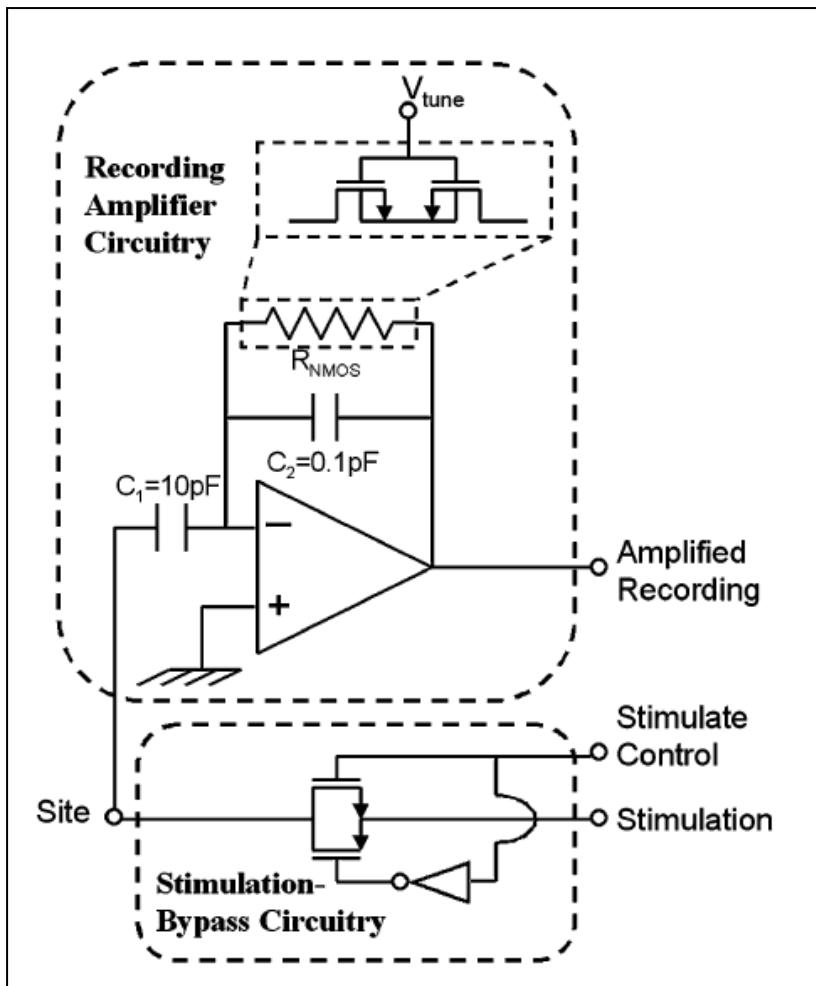

| 圖 2.10 Roy H. Olsson III 可調頻寬電生理放大器 ..... | 27 |

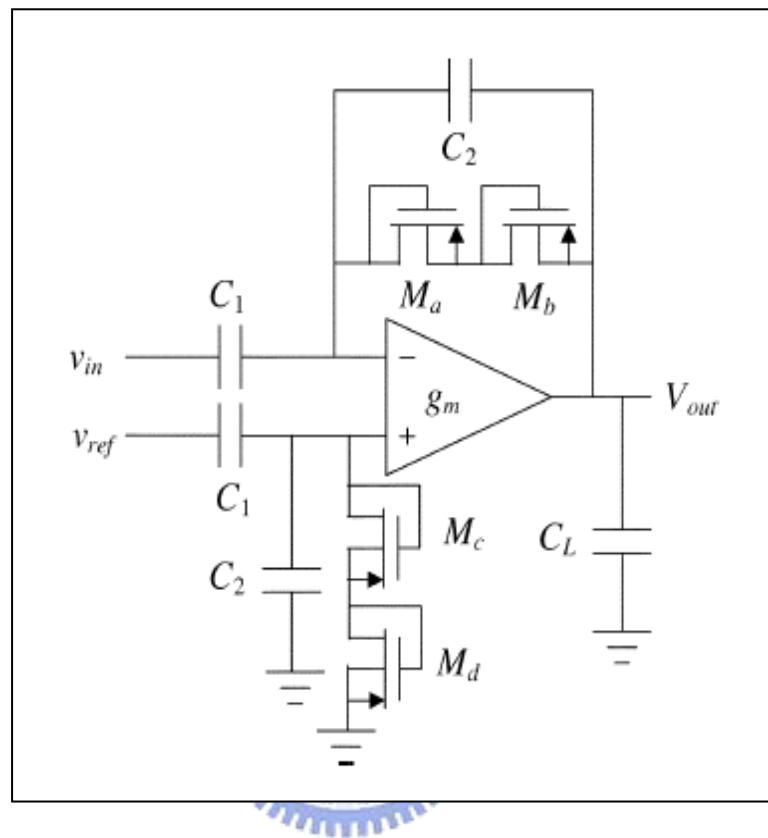

| 圖 2.11 Reid R. Harrison 電生理放大器 .....      | 28 |

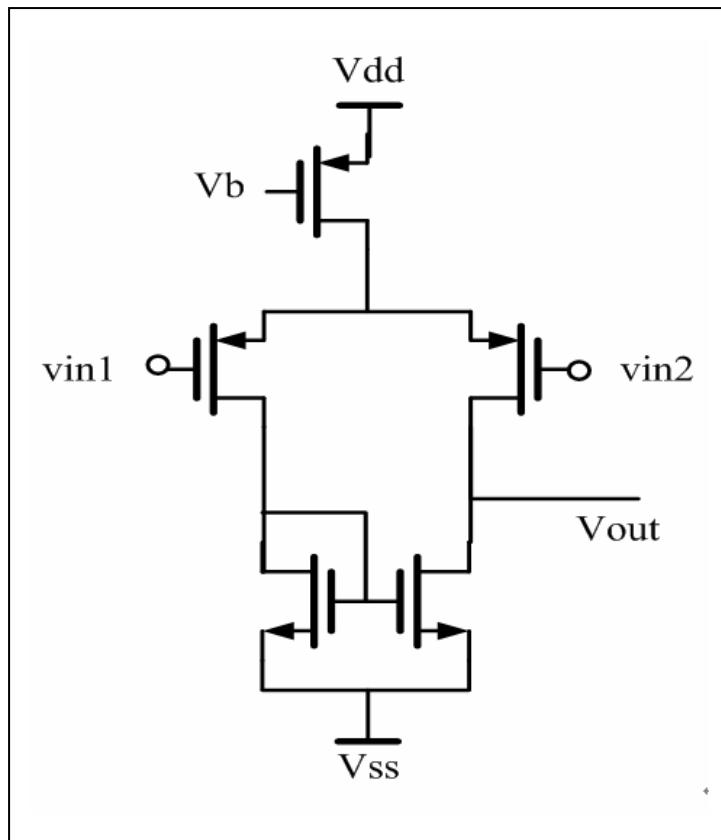

| 圖 2.12 應用於電生理放大器之 OTA 架構 .....            | 29 |

| 圖 2.13 Deborah S. Won 訊號處理流程 .....        | 30 |

| 圖 2.14 J. Morizio 電生理記錄放大器設計 .....        | 31 |

| 圖 2.15 Iyad Obeid 電生理放大器 .....            | 32 |

| 圖 2.16 電生理訊號 sorting 後波形 .....            | 32 |

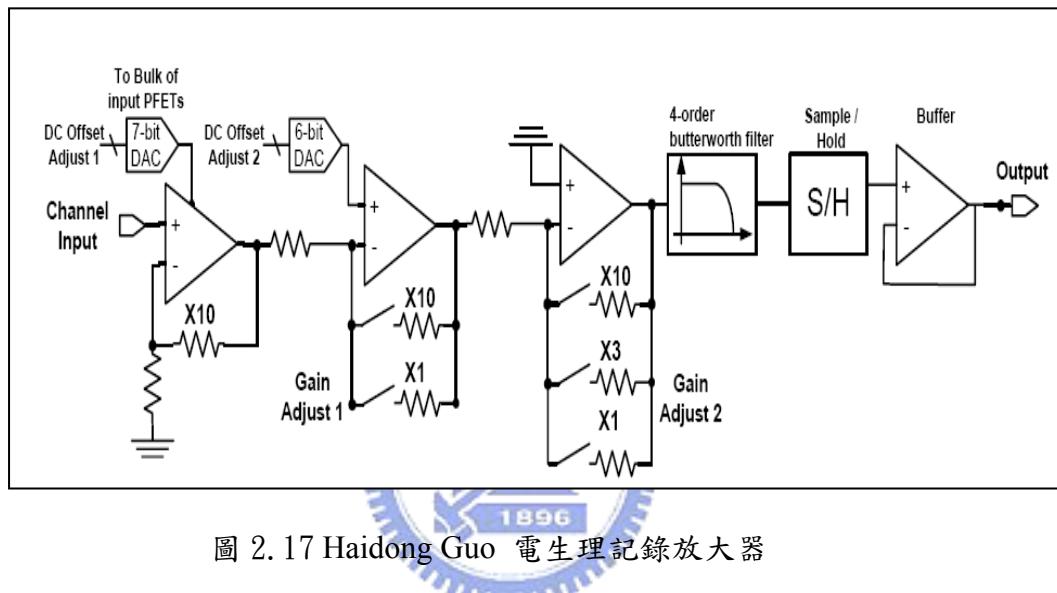

| 圖 2.17 Haidong Guo 電生理記錄放大器 .....         | 33 |

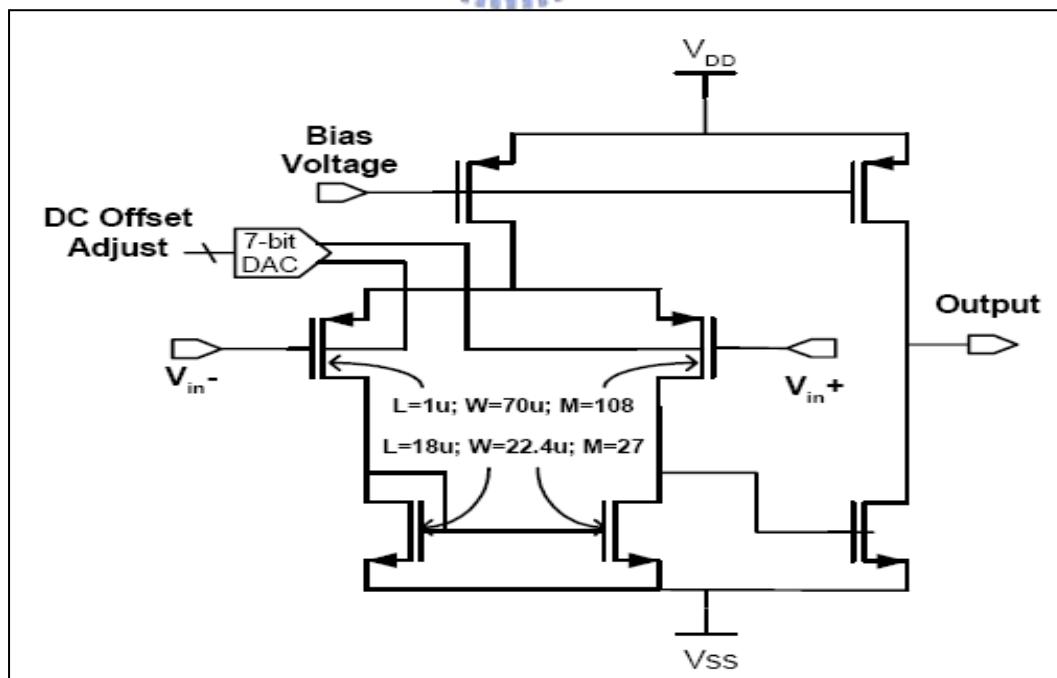

| 圖 2.18 放大器架構 .....                        | 33 |

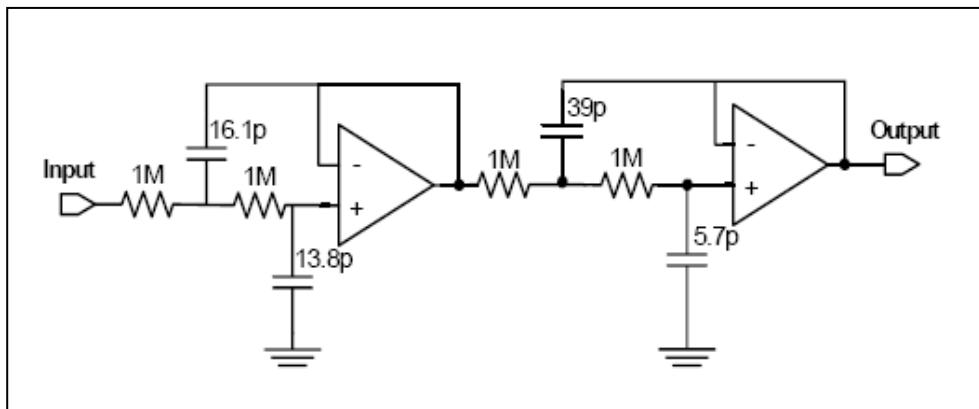

| 圖 2.19 4 階 butterworth filter .....       | 34 |

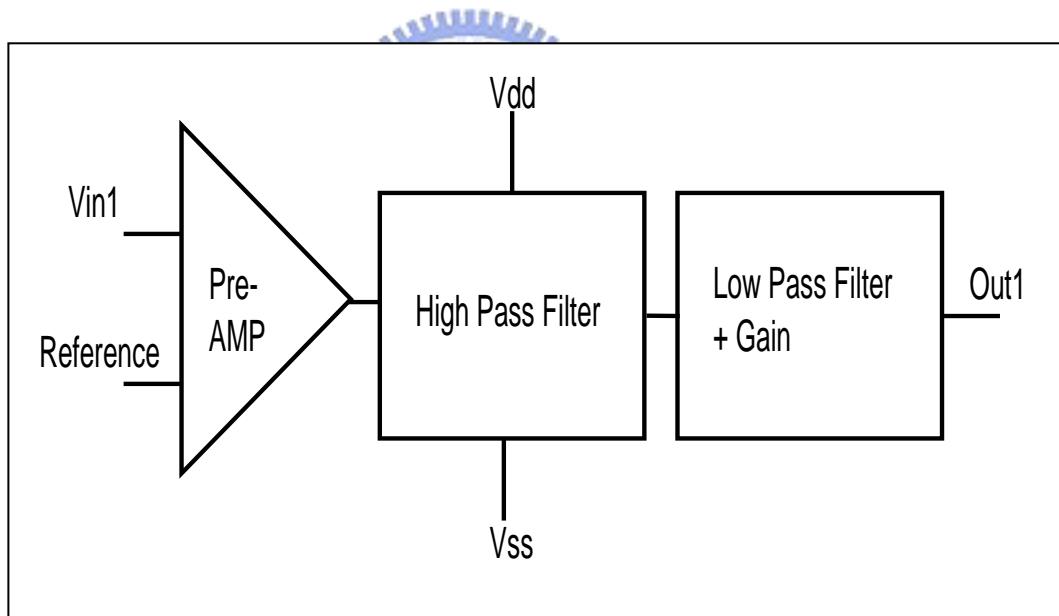

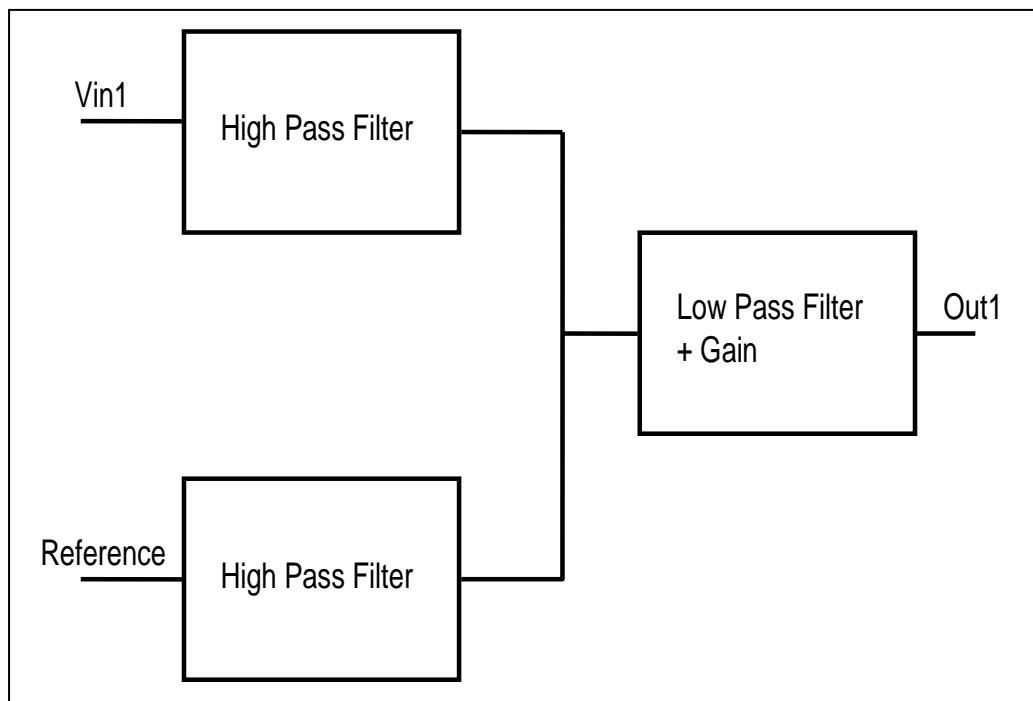

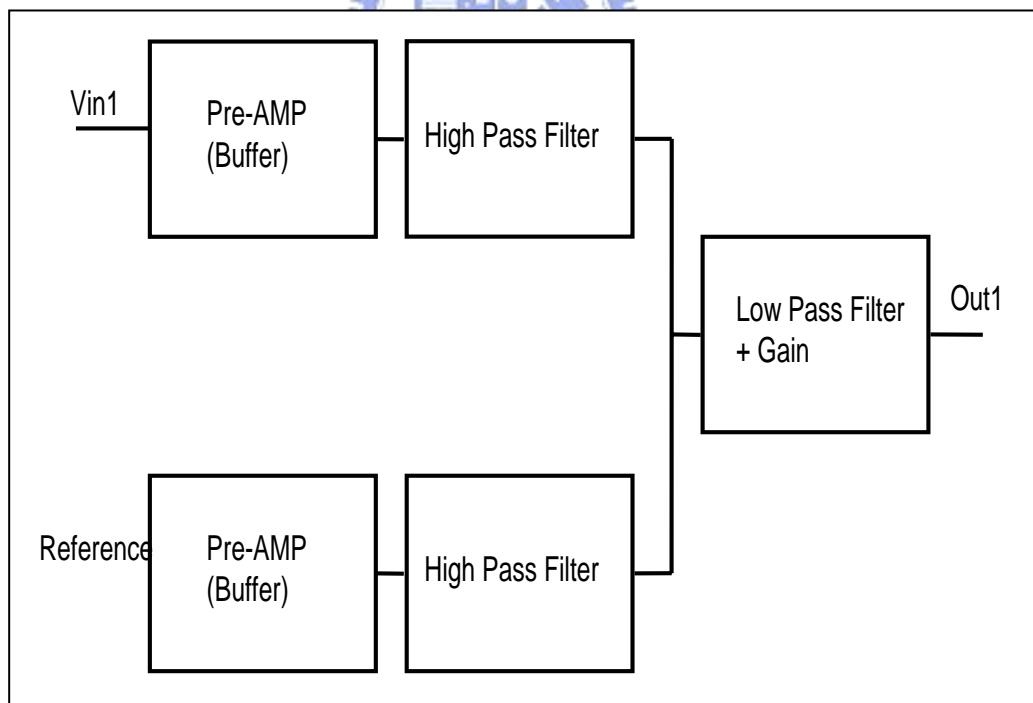

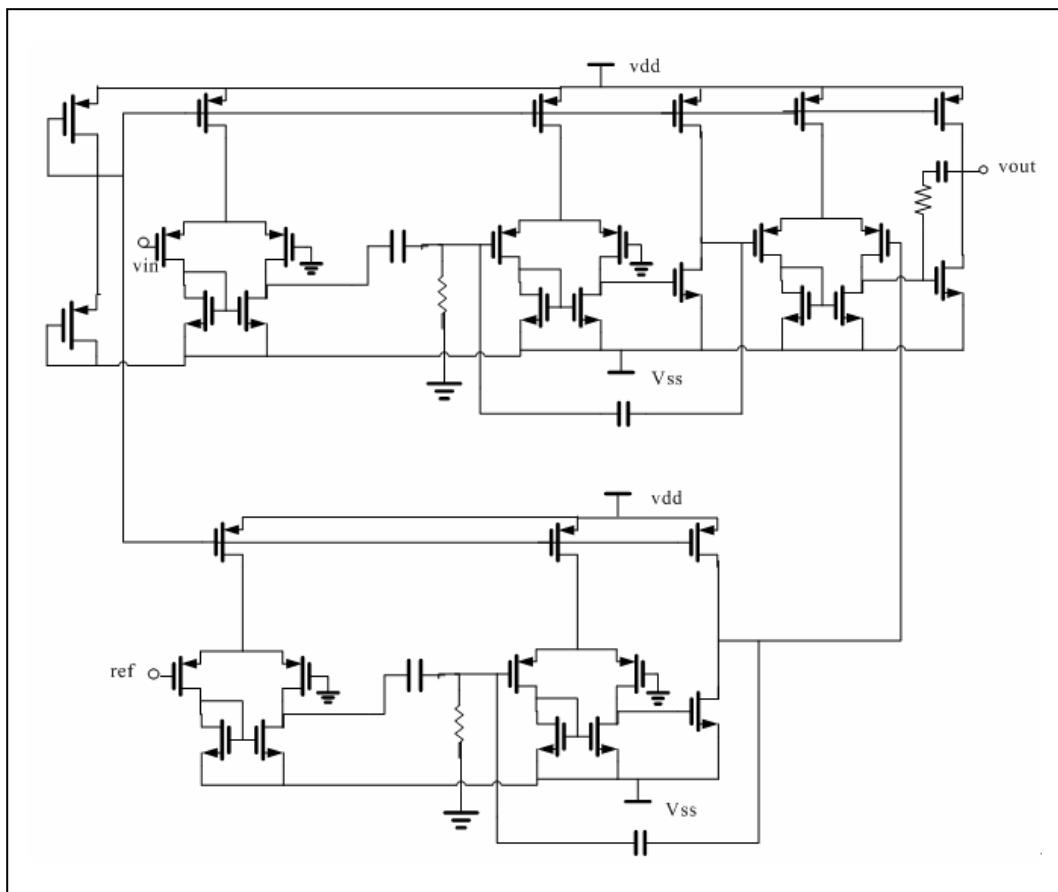

| 圖 3.1 模式 1 前置放大器 .....                    | 37 |

| 圖 3.2 模式 2 平行高通濾波 .....                   | 38 |

| 圖 3.3 模式 3 buffer .....                   | 38 |

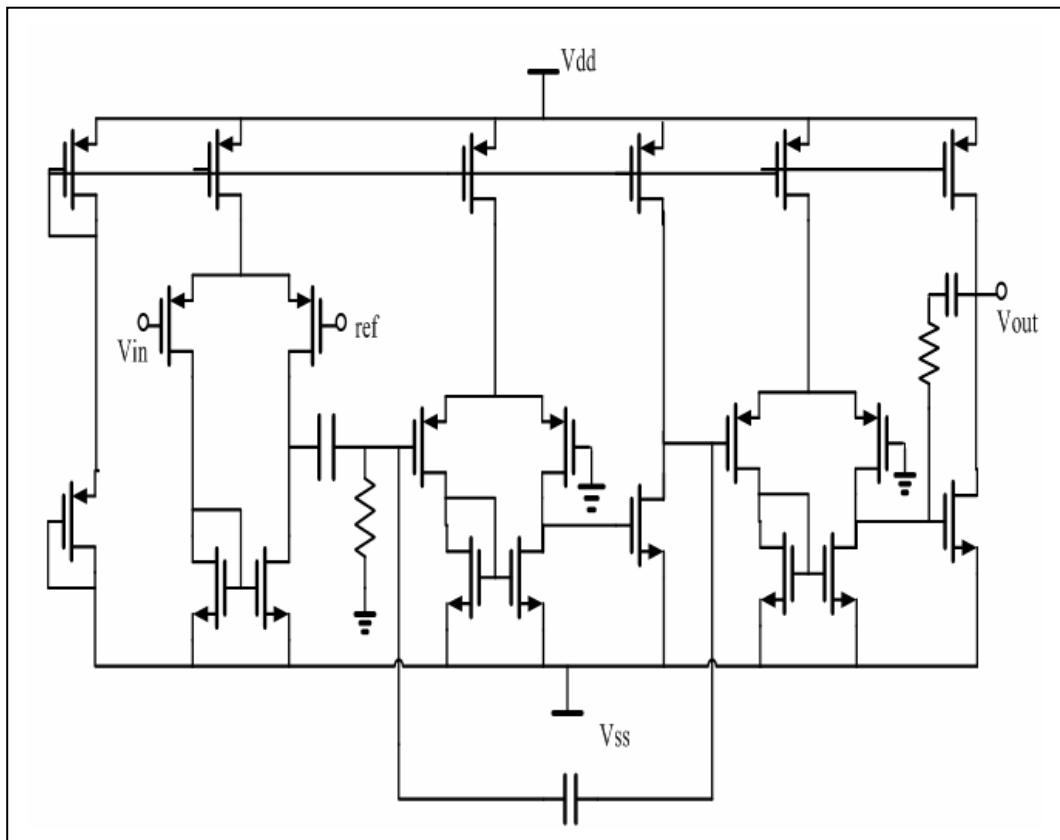

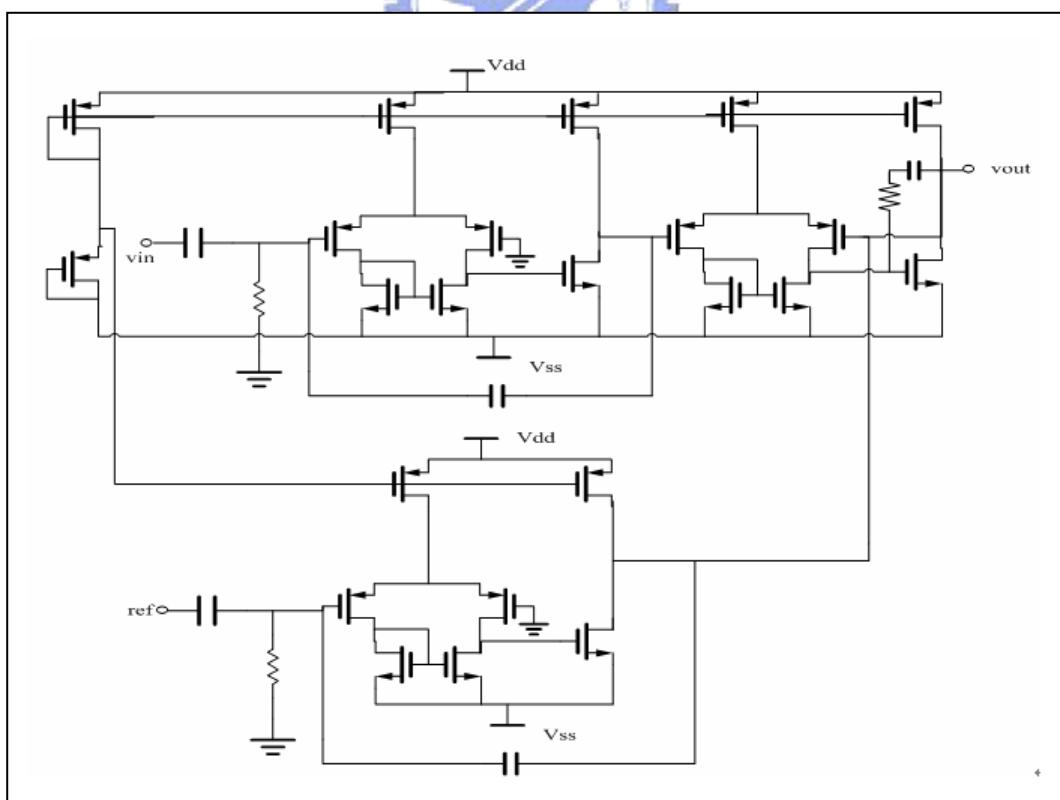

| 圖 3.4 模式 1 電路 .....                       | 40 |

| 圖 3.5 模式 2 電路 .....                       | 40 |

| 圖 3.6 模式 3 電路 .....                       | 41 |

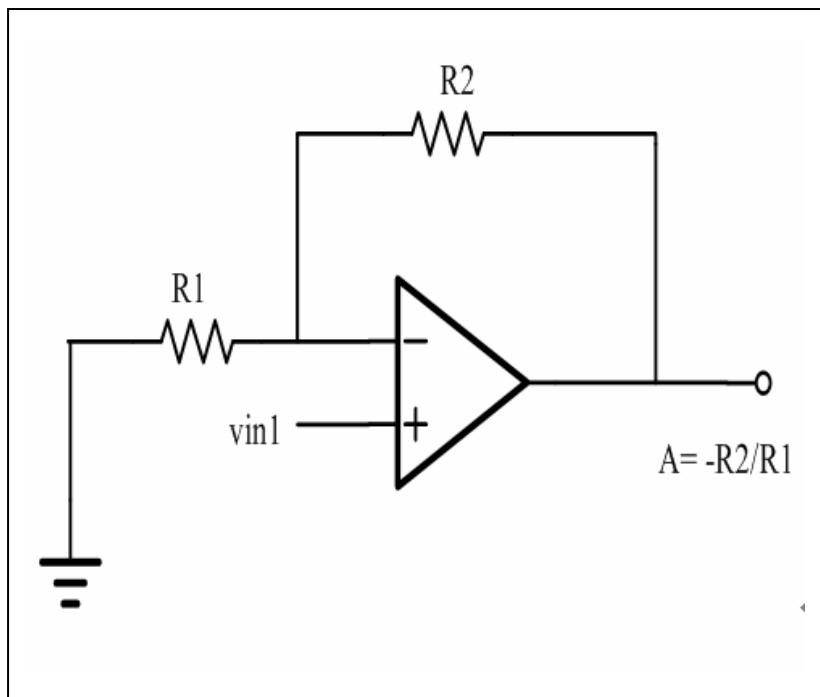

| 圖 3.7 前置放大器架構示意圖 .....                    | 43 |

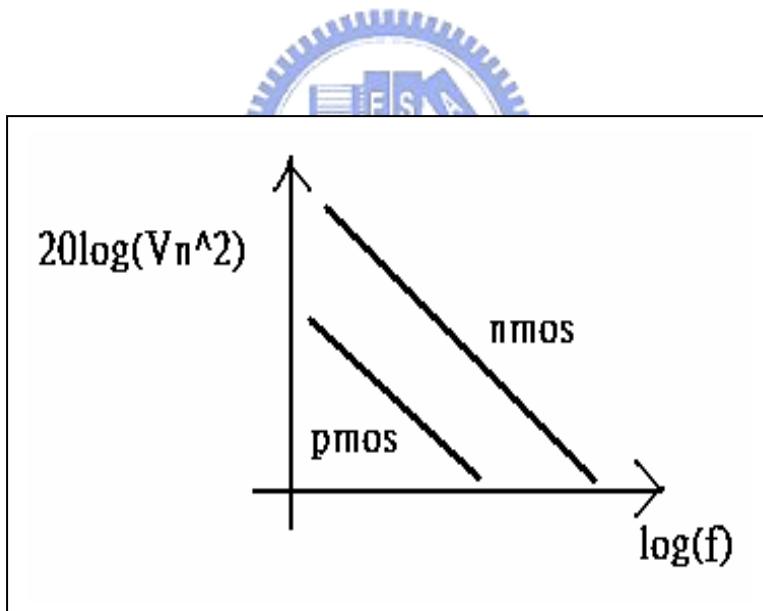

| 圖 3.8 flicker noise 頻譜分佈 .....            | 43 |

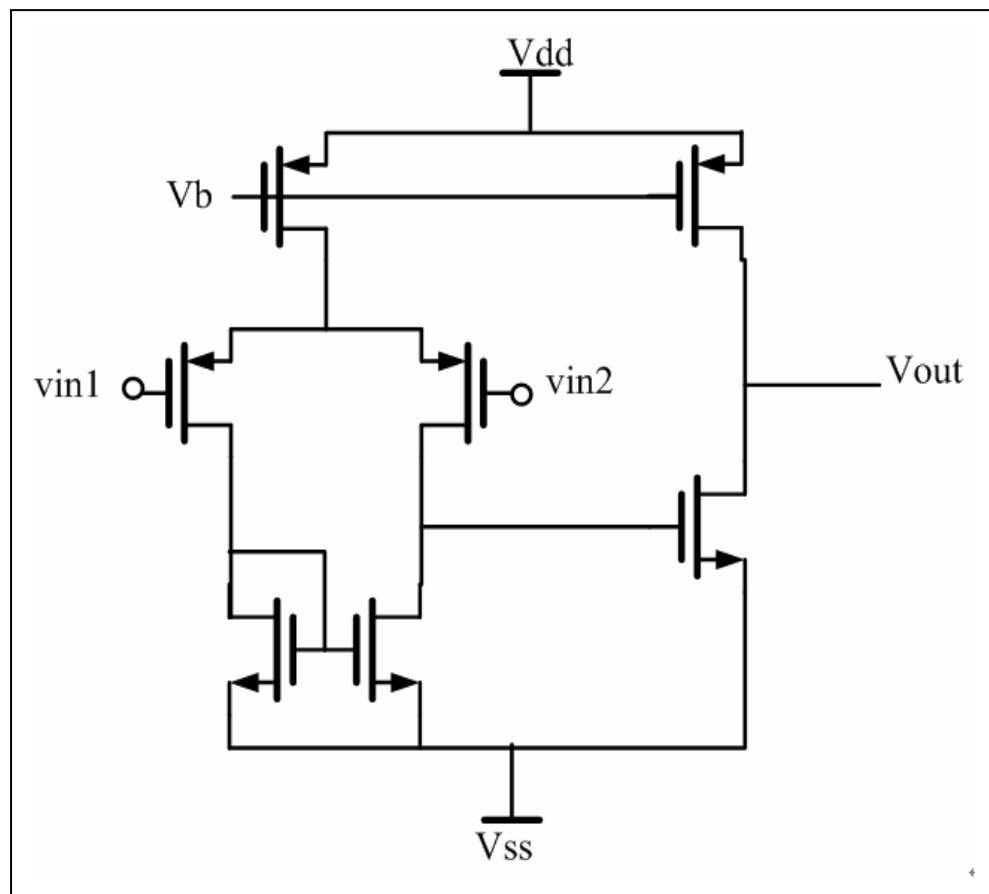

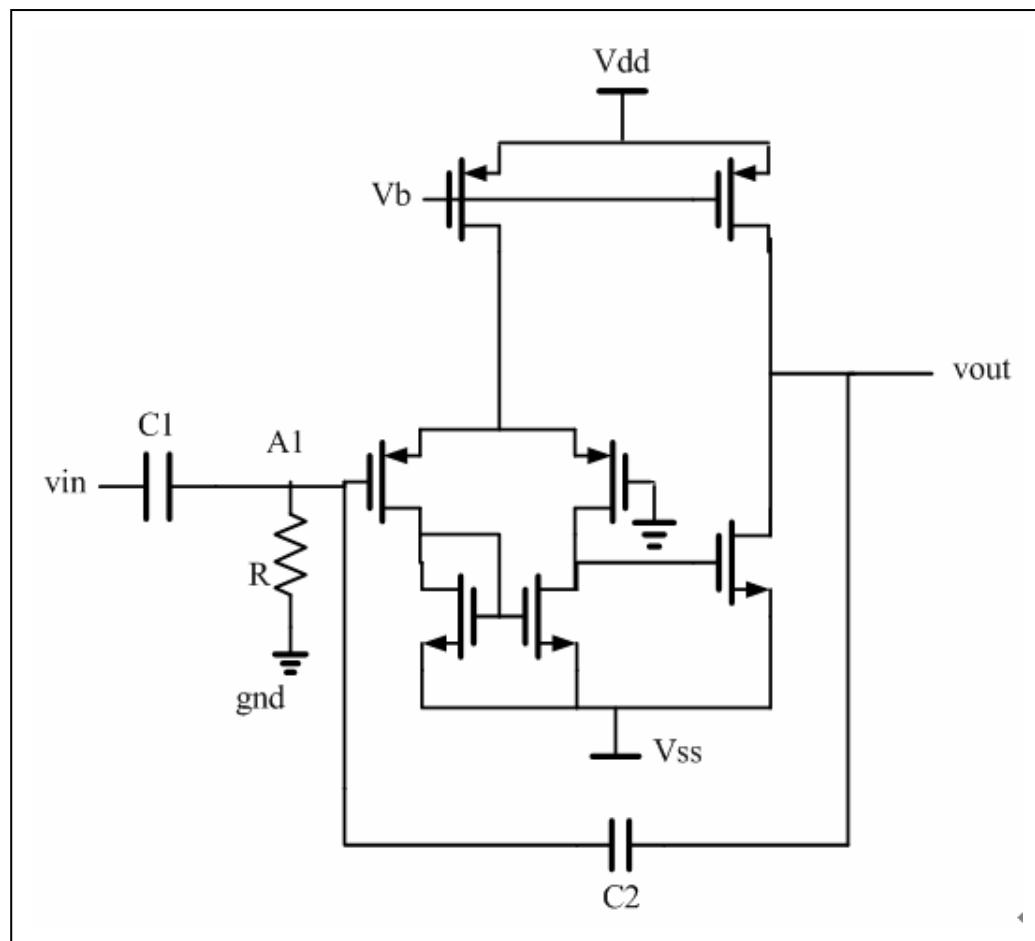

| 圖 3.9 前置放大器 .....                         | 44 |

| 圖 3.10 2-stage 電路架構圖 .....                | 46 |

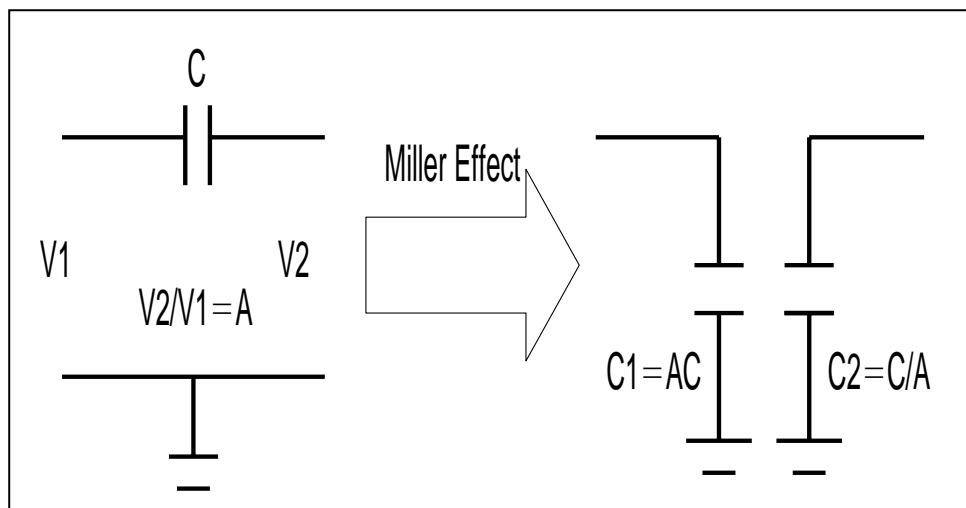

| 圖 3.11 Miller effect .....                | 47 |

| 圖 3.12 高通濾波器架構示意圖 .....                   | 47 |

| 圖 3.13 高通濾波器架構圖 .....                     | 48 |

| 圖 3.14 具放大功能的低通濾波器 .....                  | 50 |

|                                                          |    |

|----------------------------------------------------------|----|

| 圖 3.15 加入補償電阻前後之波德圖 .....                                | 50 |

| 圖 3.16 偏壓電路 .....                                        | 51 |

| 圖 3.17 完整架構 .....                                        | 52 |

| 圖 3.18 外接電阻選擇增益 .....                                    | 53 |

| 圖 3.19 當作buffer使用 .....                                  | 53 |

| 圖 3.20 補償高通濾波器不理想狀況 .....                                | 54 |

| 圖 3.21 補償低通濾波器不理想狀況 .....                                | 55 |

| 圖 4.1 設計流程 .....                                         | 56 |

| 圖 4.2 單位電容 .....                                         | 57 |

| 圖 4.3 加入DUMMY CELL與兩個contact的gardring圍住 .....            | 58 |

| 圖 4.4 單位電阻 1k .....                                      | 58 |

| 圖 4.5 加入DUMMY CELL與兩個contact的gardring圍住 .....            | 59 |

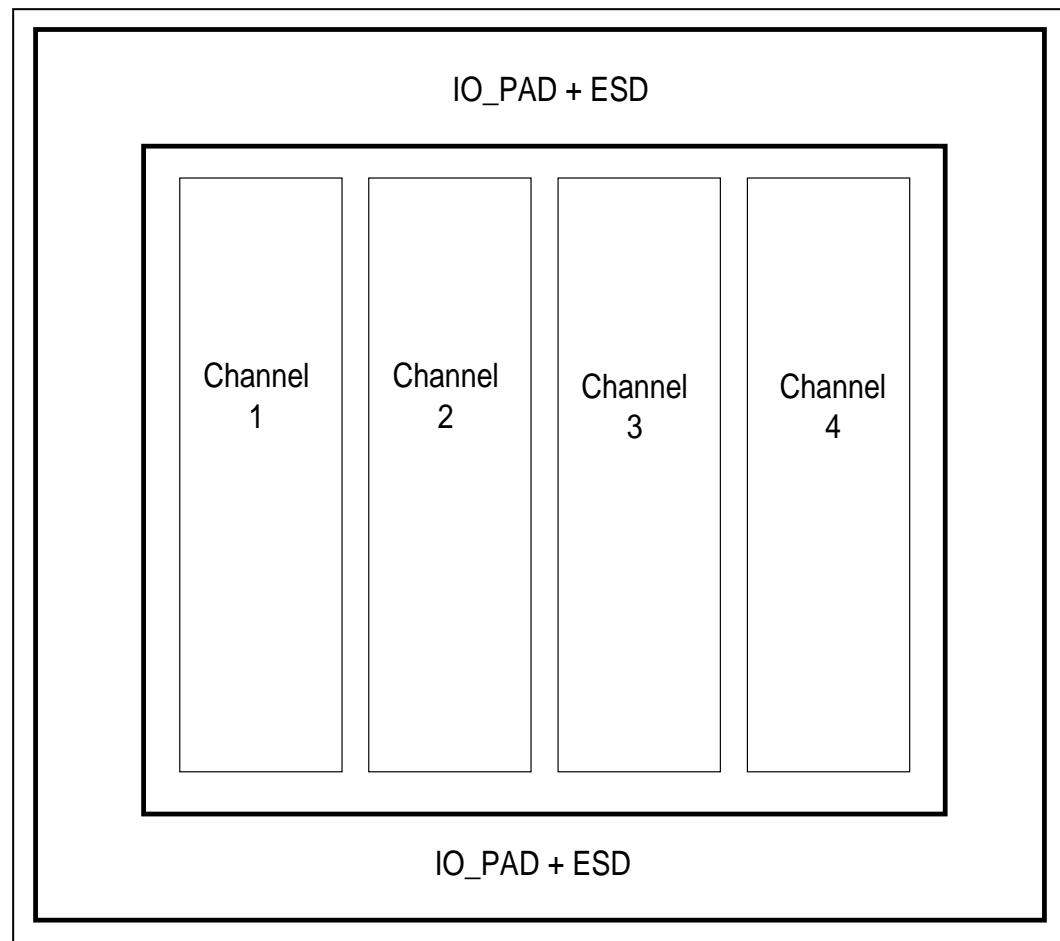

| 圖 4.6 1 channel電路佈局示意 .....                              | 59 |

| 圖 4.7 layout示意圖 .....                                    | 60 |

| 圖 4.8 layout 全圖 .....                                    | 61 |

| 圖 4.9 打線圖 .....                                          | 61 |

| 圖 4.10 前置放大器波德圖 .....                                    | 63 |

| 圖 4.11 輸入訊號有 0.5V的dc offset 加上 700uV的 1k Hz電生理訊號 .....   | 63 |

| 圖 4.12 OTA波德圖 .....                                      | 64 |

| 圖 4.13 高通濾波器的波德圖 .....                                   | 64 |

| 圖 4.14 具放大功能之低通濾波器的波德圖 .....                             | 65 |

| 圖 4.15 帶通濾波器頻譜響應 .....                                   | 65 |

| 圖 4.16 系統之phase margin約 85 度 .....                       | 66 |

| 圖 4.17 輸入訊號為為頻率 1k , 振幅 700 uV的且具有 0.5V的 dc offset ..... | 66 |

| 圖 4.18 混合訊號 .....                                        | 67 |

| 圖 4.19 溫度變化影響 .....                                      | 67 |

## 表 目 錄

|                                   |    |

|-----------------------------------|----|

| 表 1-1 腦電波種類 .....                 | 14 |

| 表 2.1 Reid R. Harrison被動元件值 ..... | 28 |

| 表 2.2 Deborah S. Won被動元件值 .....   | 30 |

| 表 2.3 每一級的gain 與頻寬 .....          | 30 |

| 表 2.4 綜合規格表 .....                 | 35 |

| 表 2.5 被動元件使用記錄 .....              | 36 |

| 表 3.1 模式比較 .....                  | 39 |

| 表 4.1 綜合比較表 .....                 | 68 |

| 表 4.2 被動元件使用比較記錄 .....            | 69 |

| 表 4.3 預計規格 .....                  | 70 |

# 第一章 緒論

## 1.1 簡介

大腦是由數以千億計的神經元所組成的，這些神經元是專門傳遞訊號的細胞，當位於細胞表面的受體接收到神經傳導物質時，神經元便會產生動作電位以傳遞訊息。隨著科技的進步，人類對生物醫學、預防醫學越來越發覺其重要性，而其中腦部的活動與訊息之意義，也因為科技的發展，人類慢慢開始具有一窺腦部的神秘世界，因此開始出現腦科學研究。

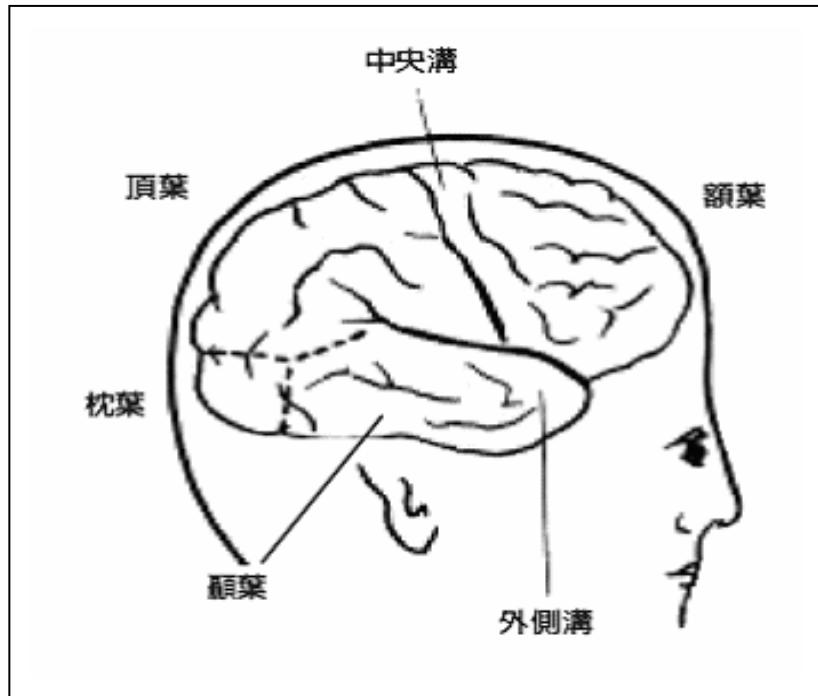

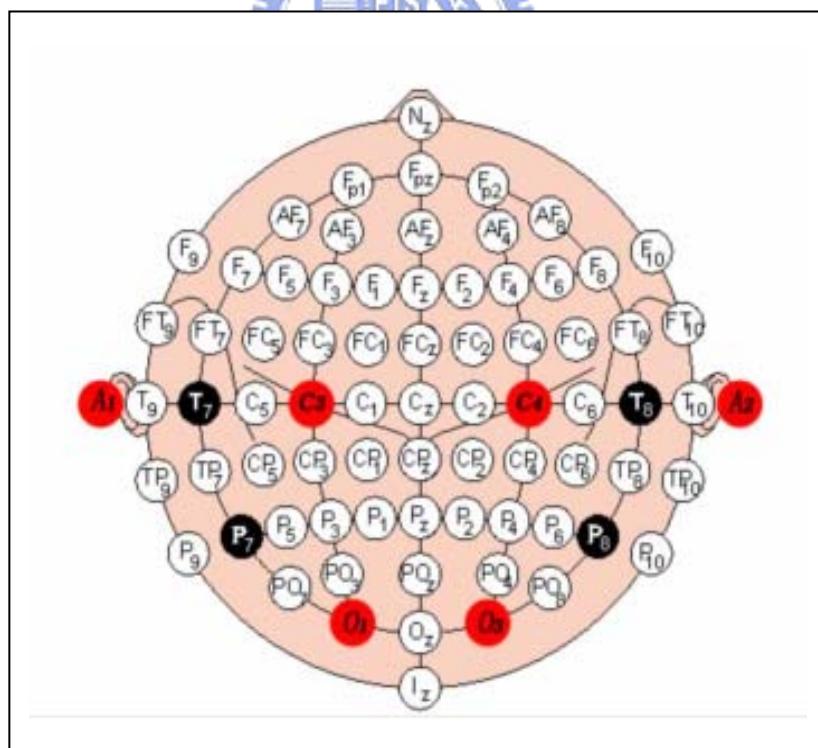

腦科學研究的歷史悠久，早期量測方式為『非侵入式』量測，大腦結構如圖 1.1。『非侵入式』量測方式為在頭皮貼乾、濕電極，量測腦內部神經元所產生的訊號。神經元藉由改變其細胞膜對帶電離子穿透性的方式傳遞訊號，而這個過程會沿著細胞膜產生電流。當一大群規則排列的神經元同時活動時，伴隨電流所產生的電場及磁場變化可以在頭皮上加以量測，所得電信號便是腦電波(electroencephalogram, EEG)。量測的方式為圖 1.2，國際標準 10-20 系統。

圖 1.1 大腦結構圖

圖 1.2 10-20 國際標準位置

腦電波的研究已經有相當的成果，目前可將睡眠期間腦電波區分為四種波段，如表 1-1。腦部在清醒與入睡階段皆表現出不同的腦波型態，整體上這些型態可由頻率(frequency)、振幅(amplitude)、和形狀(morphology)進行研判。腦波頻率可分為 4 種不同的波形，有  $\alpha$  波(8-13 Hz)、 $\beta$  波(>13 Hz)、 $\theta$  波(4-8 Hz)、及  $\delta$  波(<4 Hz)，腦波振幅則主要在確認超過 75 mV 的高振幅慢波。腦電波 (EEG) 訊號頻帶大多在 50 Hz 以下，主要是感測大量神經元所引起之電場磁場之變化，而與本研究觀察之神經元訊號頻段約在 1 k Hz 左右，主要是量測 action potential。

由於不同的大腦區位在進行不同認知活動時會有不同的活動，所產生的電位及磁場變化在頭皮上的強度以及分布情形也會有所不同。比較受試者進行不同認知作業時所伴隨腦電波或腦磁波變化的強度，以及這些變化在頭皮上的分布，可以知道是否有不同的大腦區位涉入這些認知作業以及其涉入的程度，而後推論進行該項認知作業時所涉及的認知歷程。腦電波能提供認知活動極佳的時序訊息，缺點是無法提供精確的腦部區位訊息。

表 1-1 腦電波種類

|                   | 頻段範圍     | 附註                                                      |

|-------------------|----------|---------------------------------------------------------|

| Alpha( $\alpha$ ) | 8-13 Hz  | 一般在正常人清醒並處於安靜、休息狀態的大腦活動狀態之下，會出現這樣的週期波。                  |

| Beta( $\beta$ )   | 13 Hz 以上 | 在清醒而警覺狀態時，這樣的波段很明顯，由 $\alpha$ 波轉換到 $\beta$ 波的過程，稱為腦波覺醒。 |

| Theta( $\theta$ ) | 4-8 Hz   | 主要出現在小孩的頂葉部及額葉部，當成人情緒受到壓力時也會出現，許多腦疾病患者可找到 $\theta$ 波    |

| Delta( $\delta$ ) | 低於 4 Hz  | 出現在深度睡眠、嬰兒及有嚴重器官性疾病患者身上                                 |

科學家為了更深入了解大腦神經系統的運作，發展侵入式微電極量測—電生理法。傳統電生理量測採用單一微電極記錄方式，其信號分析方式分作兩種，一種為場電位記錄（field potentials recording），另一種方法是單一神經元活動記錄（single unit recording）。

- 一. 場電位記錄提供大範圍腦部神經元活動變化，其訊息包含各神經元活動在時間和空間的變化情形，為巨觀的資訊。

- 二. 神經系統的功能單位為神經細記錄，透過單一神經元記錄可呈現個別神經元細胞的特性與功能。

自從三十年代玻璃微電極的發明以來，單一神經元記錄法是神經科學中最基本的方法，舉凡興奮、抑制、神經傳遞等神經生理中最基本的原理均由這種方法發現與闡明。但是一個高等生物腦中有數十億個以上的神經細胞，而感覺、運動及複雜的心智活動如何經由這數十億個神經細胞的聯合作用產生，使用單一神經元記錄法來研究前述的問題，便有「見樹不見林」的盲點。雖然現代生物醫學影像方法突飛猛進，已可以記錄各種行為及心智活動時，實驗動物或人的腦中各部位的血流量、代謝速率、特定基因表現量及傳遞物質作用的能力（如 2-DG、基因表現的組織化學染色、fMRI、PET 等法），但電生理方法仍是目前唯一可直接觀察記錄單一神經細胞信號的方法。

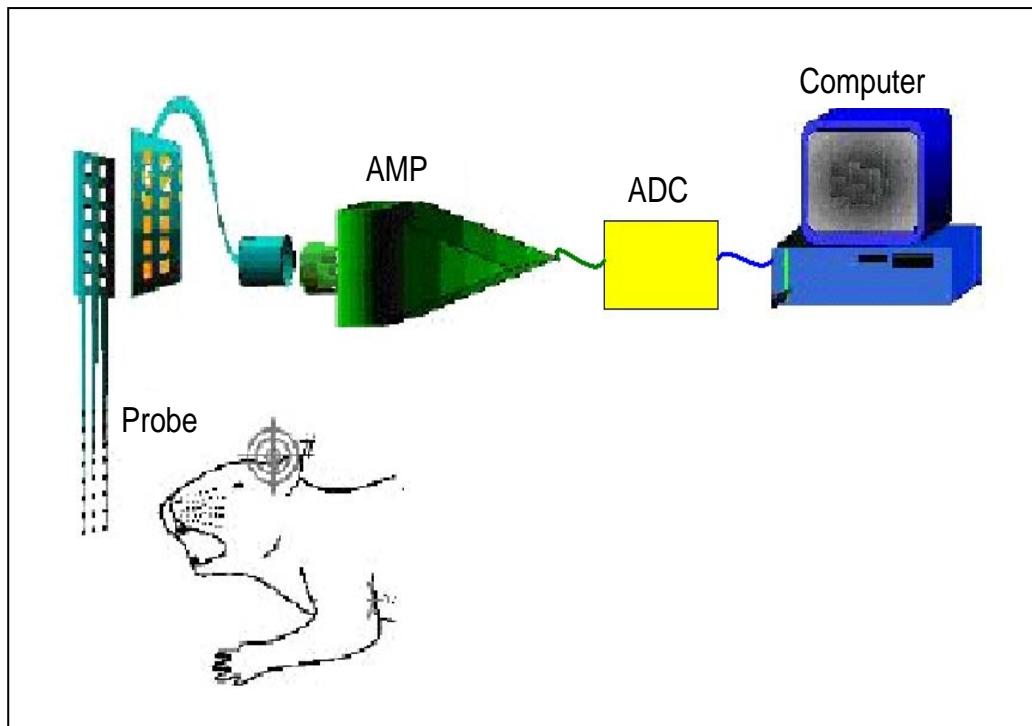

為了觀察神經元訊號，設計一個電生理量測系統如圖 1.3 所示，此系統由四個部分組成：侵入式神經元記錄電極、電生理記錄放大器、類比數位轉換器、運算電腦。多頻道神經元記錄電極是基礎神經科學研究對於獲取臨床和神經元應用的重要發展。近來由於微機電技術的快速進步，侵入式神經元記錄電極可觀察到更多的神經元同步的反應，因此對於低功率電生理放大器發展的需求大增。

圖 1.3 電生理量測系統

由於神經元訊號非常微弱 ( $10 \text{ }\mu\text{V}$ )，活動頻段  $100\text{--}10 \text{ k Hz}$ ，最主要的活動頻率範圍為  $1 \text{ k Hz}$ [13]，若將訊號透過神經元記錄電極直接接到 ADC，再傳輸至電腦將無法觀察分析，所以必須設計硬體放大電路以處理微弱的電生理訊號及克服外界的干擾問題。因此，本論文設計一個電生理記錄放大器，命名為應用於電生理記錄之低功率可調增益 CMOS 放大器晶片設計。本論文所發展多通道電生理活動電位記錄晶片，主要的貢獻可整合所開發多通道微電極探針、後端多通道信號記錄分析系統，期望能使腦科學研究有更進一步的發展。電生理記錄之低功率多頻道訊號處理晶片具有以下特點：

### 1. 具有三種工作模式：

提供了三種工作模式，讓實驗者可以實驗情況選擇工作模式。

### 2. 可調 gain:

提供 59 dB~88 dB 可調 gain，可依神經元訊號強弱，提供多元化的放大倍率，也可校正與神經元記錄電極和類比數位轉換器的阻抗匹配問題。

### 3. 低功率：

低功率有許多種作法，最直接的方式，就是設計低電壓操作電路，但是過低的電壓會因為製程飄移而造成難以符合五種製程飄移點。本論文已經測試過五種製程飄移，仍可正常工作。

### 4. 有效整合被動元件於晶片中：

國際公認電生理訊號活動頻寬為 100~400 Hz 起，3 k~10 k Hz 為止，最頻繁的頻帶在於 1 k Hz[13]，如果要整合被動元件於積體電路中，容易造成被動元件過大而無法以積體電路實驗，本研究可以有效整合被動元件於晶片中，只要提供電壓電源即可工作，無需外接被動元件。

本篇論文採用互補式金氧半電晶體的製程，有幾項潛在和明顯的價值，如提供了高輸入阻抗、CMOS 是最便宜的製程、利於整合前端神經元電極 CMOSMEMS 製程和數位電路、CMOS 光罩較少可得較高良率產品、可在低電壓操作、低消耗功率…等優點。根據理論完成生醫訊號放大器各個部份的電路設計、模擬結果及佈局。最後證明在此架構下的生醫訊號放大器，完全符合生醫訊號量測之需要。

## 1.2 論文架構

本篇論文中，第二章介紹電生理訊號來源及國外相關實驗室針對電生理記錄放大器的研究近況。第三章介紹本論文的設計方式與實作的電路，從放大器的設計到提供測試考量與測試方法。第四章在介紹晶片製作到佈局後的模擬結果，及效能比較。最後，在第五章作總結。

## 第二章 電生理訊號與相關研究 歷史簡介

本章介紹電生理訊號來源及國外相關實驗室針對電生理記錄放大器的研究近況。

### 2.1 電生理訊號

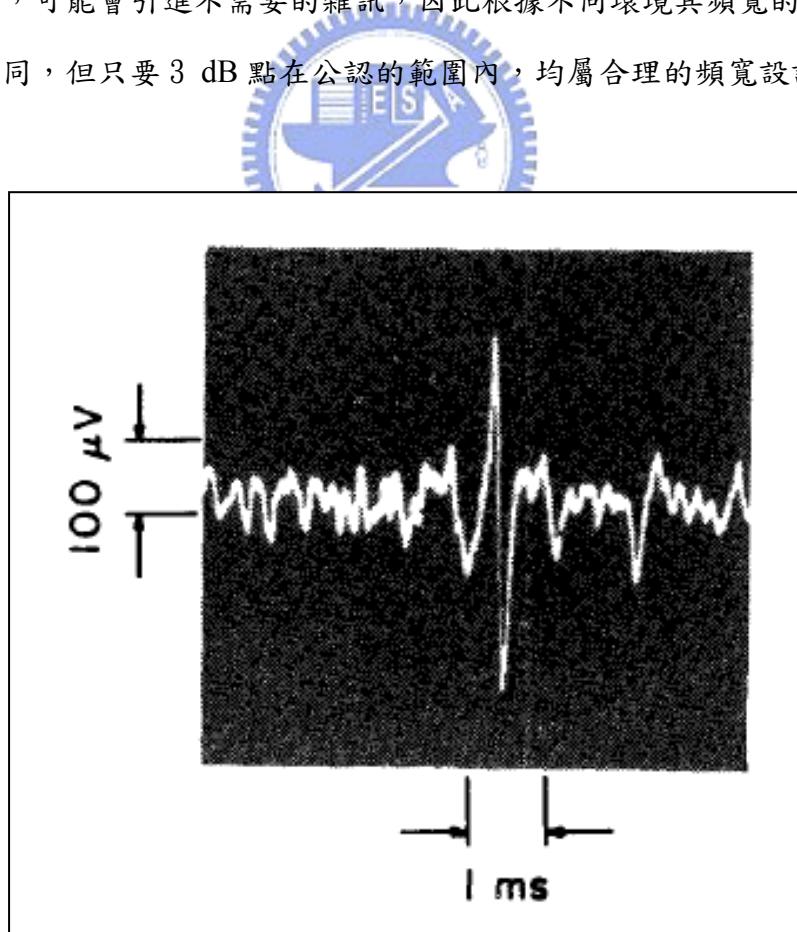

神經元發出來的訊號如圖 2.1 所示[18]，是 1986 年密西根大學 Khalil Najafi 所提供的一個從腦部皮質單一神經元放電所產生的典型訊號。一般而言，神經元所釋放的電訊號約  $50 \text{ } \mu\text{V} \sim 500 \text{ } \mu\text{V}$ ，頻寬則在  $100 \text{ Hz} \sim 400 \text{ Hz}$  起， $3 \text{ k} \sim 10 \text{ k } \text{Hz}$  止[13]。電生理訊號頻寬是經驗法則，頻寬如果太寬，所看到的訊號，可能會引進不需要的雜訊，因此根據不同環境其頻寬的設計需求都不盡相同，但只要  $3 \text{ dB}$  點在公認的範圍內，均屬合理的頻寬設計。

圖 2.1 單一神經元典型電生理訊號[18]

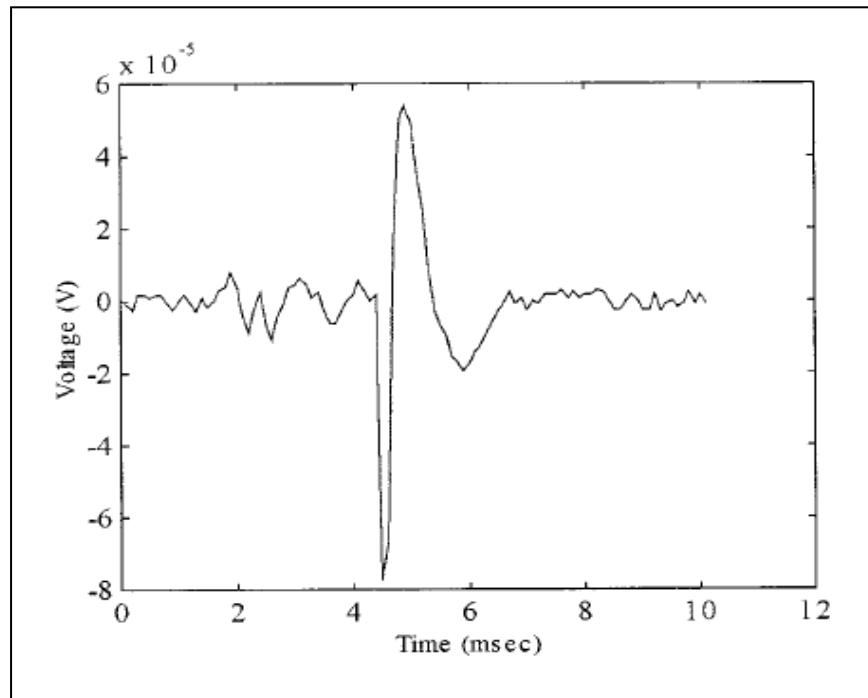

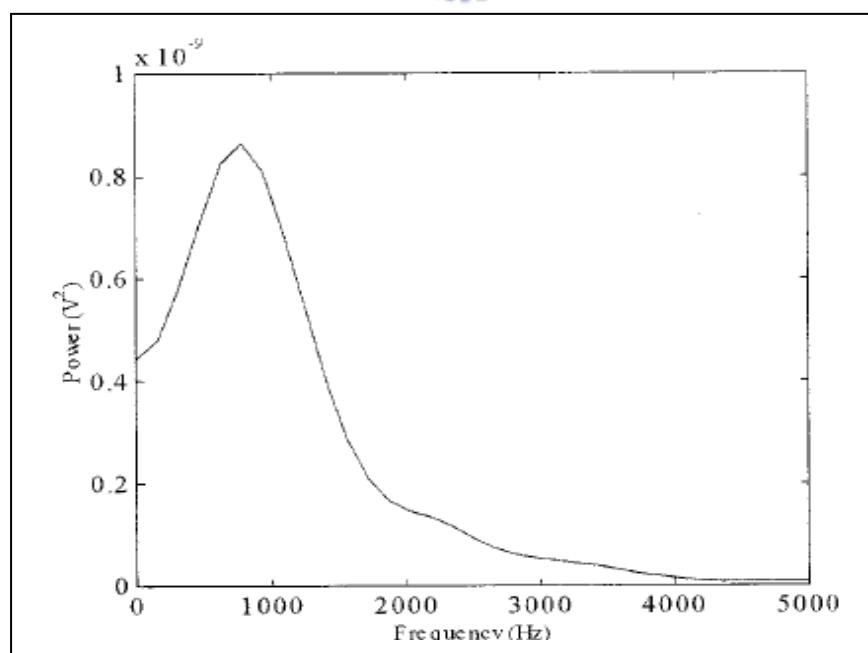

韓國漢城大學 Kyung-Hwan Kim 於 2000 年所發表的文獻中，針對圖 2.2 單一神經元產生的電生理訊號圖作 FFT，得到圖 2.3 的頻譜分析[19]。由圖 2.3，可以清楚看到頻率的分佈，在 1 k Hz 附近的訊號能量最多，是電生理訊號活動最頻繁的區域。

圖 2.2 單一神經元電生理訊號[19]

圖 2.3 電生理訊號頻譜分析[19]

2002 年密西根大學 Pedram Mohseni 發表於 EMBS/BMES 的論文中，說明在測試晶片的過程，以 100 mV 的 DC offset 來模擬侵入式神經元記錄電極與電解液所產生的直流雜訊[25]，這是因為神經元記錄電極產生的輸入雜訊約 5–10 uV 的範圍[41]。

基於經驗法則，在頻寬設計上不盡相同，雖然說只要符合國際公認頻寬 100 Hz~400 Hz 起，3 k~10 k Hz 止範圍內[13]，均屬合理頻寬，但是也有實驗室設計頻寬時，將高頻部分設計在 2 k Hz[45]，相對來說，有點過低。Rogers 和 Harris [4]使用 matlab tool 針對電生理訊號作分析，偵測 spike potential 的最佳頻寬在 1.4 k ~ 5.3 k Hz 間，此區間有 90% 的偵測率。

## 2.2 相關研究歷史簡介

許多研究人員在過去幾十年來陸續投入心力在電生理晶片開發研究，而發展至今也有幾種適用於電生理記錄晶片設計構想被提出。國外許多大學在電生理記錄放大器耕耘數十年，其中美國密西根大學 Khalil Najafi 與 Kensall D. Wise 對神經科學研究，提供許多供後人發展與參考的資訊 [11][14][18][25][26][27][28][29][36][37][39][40][41]。而後越來越多科學家對神經科學的發展感興趣，並且投入許多資源與時間進行研究，神經元記錄電極與電生理記錄放大器開始有人提出新架構，其中以美國猶它州大學 Harrison 於 2002 年提出的架構，被許多實驗室引用[5][22][23][31][32][33][34][35]。同年美國 Duke 大學 Deborah S. Won 也設計一多頻道神經元記錄放大器之架構[6][13][16]。此後許多大學也開始學習密西根大學提出的 telemetry 概念，往無線發展。受限於傳輸率，因此不可能傳輸全部的神經元訊號，所以發展出只觀察 spike potential，只要偵測到 spike action 的突波，就傳輸一個標記出去，有幾個實驗室針對 telemetry 的發展提出了研究論文[4][12][42][45]，其中美國華盛頓大學 Haidong Guo 於 2004 年提出電生理

記錄放大器架構，以 DAC 加在 body 上，用來消除因神經元記錄電極產生的 DC offset，與之前提出的方式比較，具不一樣的特點。

以下針對上述提及不同電生理訊號放大器，以發表者所屬的大學校名為代表（如美國密西根大學、美國猶它州大學、美國 Duke 大學、以及美國華盛頓大學），逐一討論介紹，並在第二章最後比較。

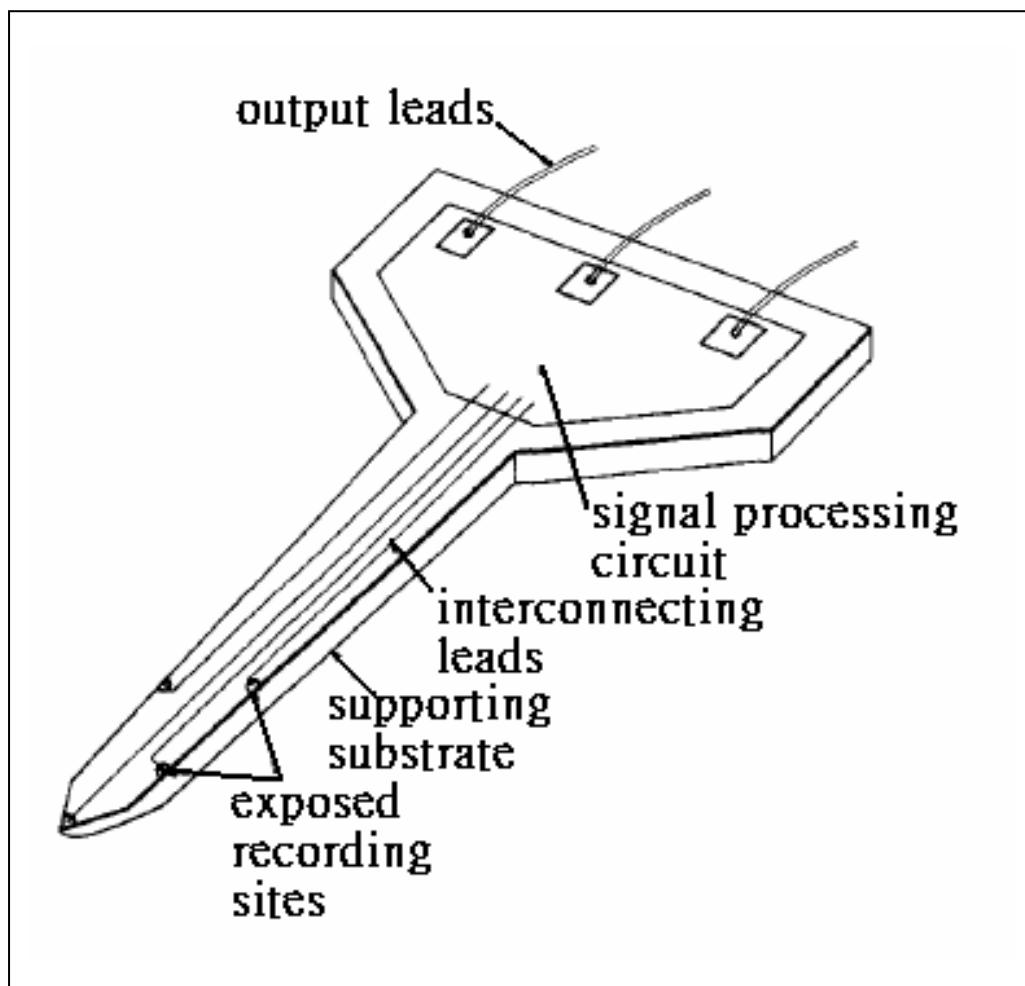

### 2.2.1 美國密西根大學

Khalil Najafi 與 Kensall D. Wise 在 1986 年發表具訊號處理功能之侵入式微電極於 IEEE Solid state circuits[18]，此時的發展，著重神經元記錄電極如圖 2.4，並且對電生理訊號作濾波放大，放大器電路如圖 2.5，頻寬為 100 Hz ~ 6 k Hz。

Jin Ji and Kensall D. Wise 在 1990 年 conference paper[14]，根據 1986 年設計之電極[18]，改良放大電路，電路架構如圖 2.6，，頻寬 5 Hz ~ 10 k Hz。此頻寬包含了市電雜訊進來，所以會有 60 Hz 的干擾。

而後 Tayfun Akin、Khalil Najafi、Robert M. Bradley 在 1994、1995 年發表兩篇 conference paper[39][40]，並且在 1998 年發表一篇 IEEE Solid state circuits[41]，此時的設計，已經發展成一套無線系統如圖 2.7，包含一個微機電極、內部連接線、晶片訊號處理、RF 遙測內部介面以及一個外部的傳送器。電生理放大器部分如圖 2.8，擷取的電生理頻寬為 100 Hz ~ 3.1 k Hz，高頻部分雖然 3 dB 點落在國際公認頻寬上[13]，但是太過於接近高頻的極限值，因此可能會因製程飄移導致取得的頻帶不合預期的疑慮。

Pedram Mohseni and Khalil Najafi 在 2002 年起，採用新的電生理放大器，主要的原因是因為早期的電生理放大器，使用 reverse-bias diode 來當濾波器，但是因為此方式會造成頻寬隨意性的飄移，導致降低電生理訊號的可靠度，因此提出了新的放大器架構如圖 2.9，將此新的放大器取代電生理無線系統中的舊放大器部分[25-29]。頻寬 50 Hz ~ 9.1 k Hz，低頻的部分，同樣包含了市電 60 Hz 交流雜訊，高頻部分可能引進太多不需要的訊號。

圖 2.4 具訊號處理功能之侵入式微電極

圖 2.5 Najafi 電生理放大器電路(1986)

圖 2.6 Jin Ji 單一輸入電生理放大電路(1990)

圖 2.7 電生理偵測無線系統[41]

圖 2.8 Tayfun Akin 電生理放大器(1998)

圖 2.9 Pedram 新型電生理放大器(2004)

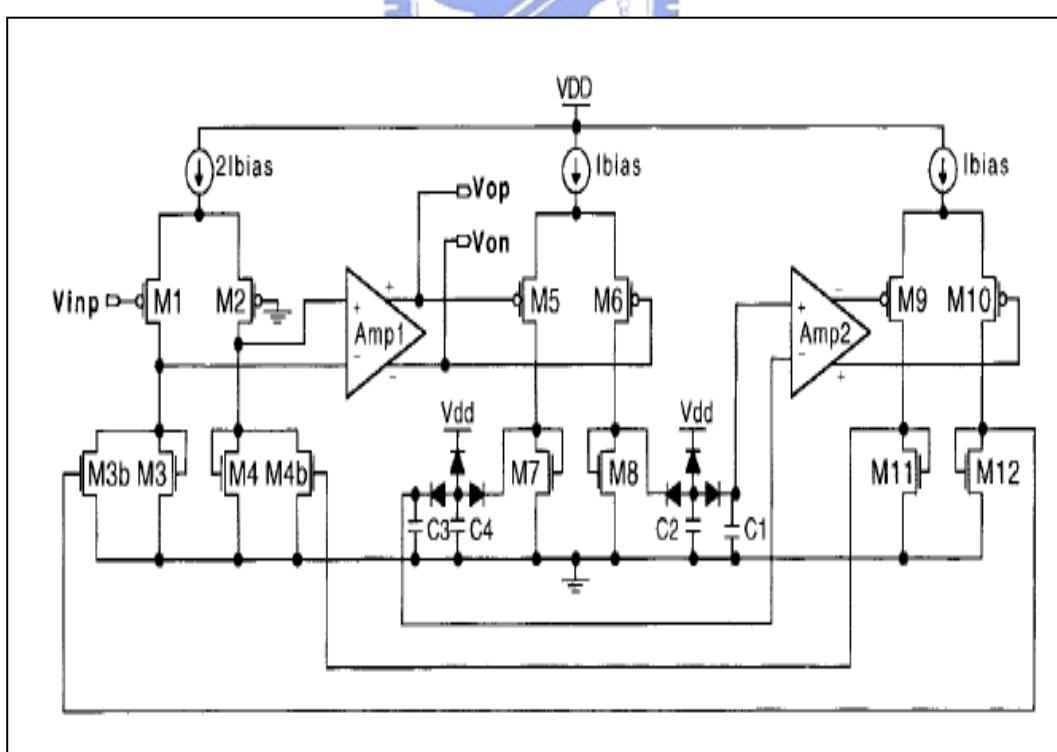

Roy H. Olsson III、Derek L. Buhl、Anton M. Sirota、Gyorgy Buzsaki、Kensall D. Wise 在 2005 年根據美國猶它州大學 Reid R. Harrison 2002 年 conference paper 提出的電生理放大器架構[31]，加以改良，提出可調整低頻 3 dB 頻寬的架構[36]，如圖 2.10。頻寬 可調式  $\sim 9.9$  k Hz。同年 Roy H. Olsson III and Kensall D. Wise 根據偵測 spike action 的突波，來壓縮傳送資料的大小[37]

圖 2.10 Roy H. Olsson III 可調頻寬電生理放大器(2005)

## 2.2.2 美國猶它州大學

Reid R. Harrison 在 2002 年 EMBS conference paper[31] 中，提出的架構如圖 2.11，利用 PMOS 設計成 diode-connection 方式，產生 pseudo-resister，取代設計電生理記錄放大器之龐大被動元件面積，但是電生理訊號的放大倍率，受限電容比值( $C_2/C_1$ )。此電生理記錄放大器之 OP 為一個 OTA 電路 (operational trans-conductance amplifier)，如圖 2.12。隔年在 Journal of Solid state circuits 上，描述較為詳盡的設計[32]，頻寬 0.025 Hz ~ 7.2 k Hz。此後 Reid R. Harrison 根據此設計，作為之後發展無線系統之放大器部分。在此之後的研究，以無線系統發展為主軸，並藉由設計偵測 spike action 之電路，

來降低無線系統傳送之資料。並在 2006 年 ISSCC 上，發表整合前端多頻道神經元記錄電極、電生理記錄放大器、RF 電路之結果[35]。

圖 2.11 Reid R. Harrison 電生理放大器(2002)

|    |      |

|----|------|

| C1 | 0.2p |

| C2 | 20p  |

表 2.1 Reid R. Harrison 被動元件值

圖 2.12 應用於電生理放大器之 OTA 架構

### 2.2.3 美國 Duke 大學

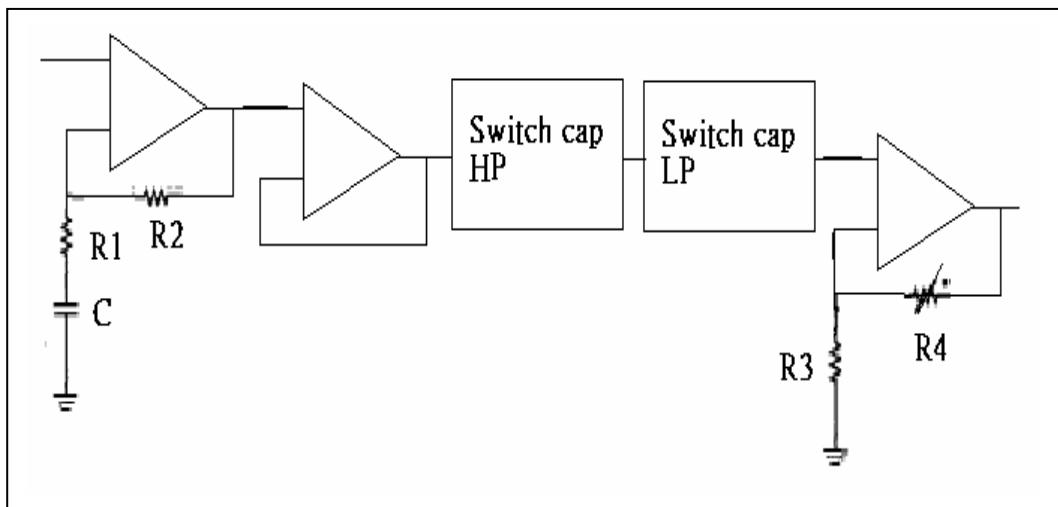

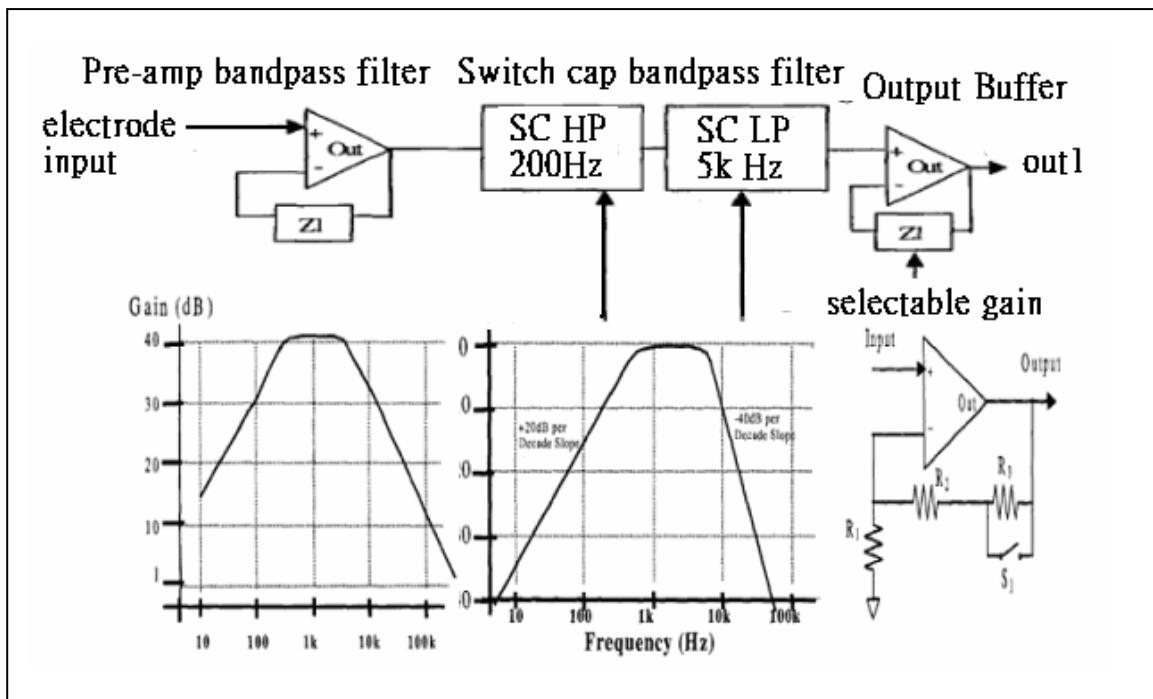

Deborah S. Won、Iyad Obeid、James C. Morizio、Miguel A.L. Nicolelis、Patrick D. Wolf 在 2002 年 EMBS/BMES conference paper 中 [6]，提出一處理電生理訊號架構流程，如圖 2.13，其中電容  $C=100\text{ nF}$  外接。頻寬  $500\text{ Hz} \sim 5.3\text{ kHz}$ 。

考慮面積問題，電容  $C$  外接，表 2.2 為被動元件值，表 2.3 每一級的 gain 與頻寬。因電容  $100\text{ nF}$  面積太大而無法整合於晶片內部，所以以外接方式實現。

圖 2.13 Deborah S. Won 訊號處理流程(2002)

| Device | Value                             |

|--------|-----------------------------------|

| R1     | 7.33 K $\Omega$                   |

| R2     | 1.008 M $\Omega$                  |

| R3     | 20 K $\Omega$                     |

| R4     | 160 K $\Omega$ (+640 K $\Omega$ ) |

| C (外接) | 100 nF                            |

表 2.2 Deborah S. Won 被動元件值

| Stage          | Gain (dB) | f-3dB (Hz) | Rolloff (dB/dec) |

|----------------|-----------|------------|------------------|

| Input (BPF)    | 43        | 200 , 15k  | -20 , -20        |

| Switch Cap HPF | -1.8      | 501        | -19              |

| Switch Cap LPF | -0.06     | 5.3k       | -35.8            |

| Output         | 20 , 32   | ~20k       | -20              |

表 2.3 每一級的 gain 與頻寬

J. Morizio、D. Won、I. Obeid、C. Bossetti、M. Nicolelis、P. Wolf 在 2003 年 EMBS conference paper 中提出該 16-channel 設計[16]。1-channel 每一個 block 的功能如圖 2.14。

圖 2.14 J. Morizio 電生理記錄放大器設計

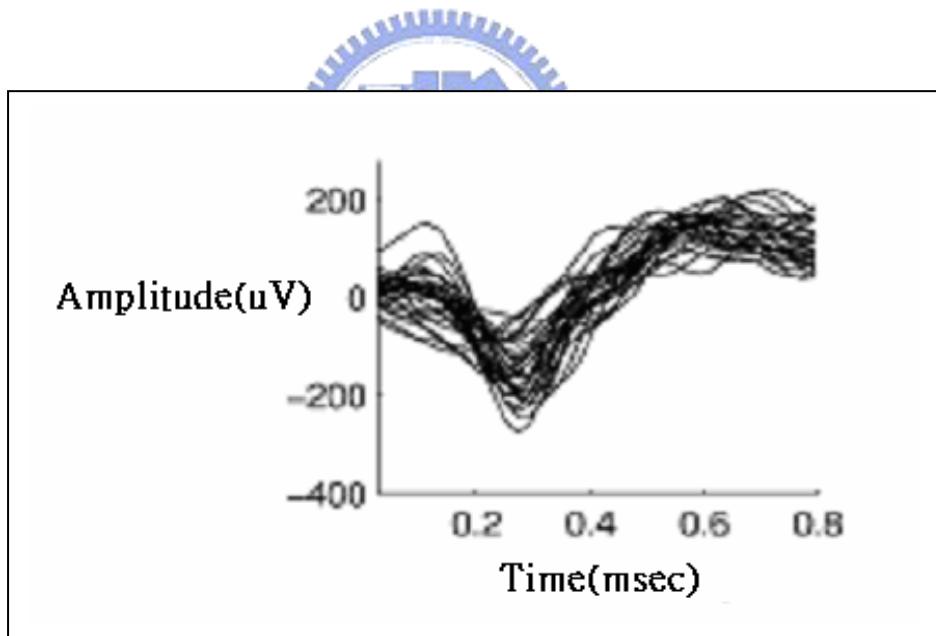

Iyad Obeid、James C. Morizio、Karen A. Moxon, Miguel A. L. Nicolelis、Patrick D. Wolf 在 2003 年 Biomedical engineering paper 上[13]，發表經由電生理記錄放大器之電生理訊號波形，並提出如果使用 switch-capacitor filter，會加入 switch noise 於電生理訊號中，以致於無法觀察電生理訊號，並將目前設計之架構，修剪為如圖 2.15 所示。頻寬約 200 Hz ~ 7.5 k Hz，放大倍率 250 倍或 500 倍，電容外接 100 nF。圖 2.16 為電生理訊號經過 sorting 後的波形。

圖 2.15 Iyad Obeid 電生理放大器

圖 2.16 電生理訊號 sorting 後波形

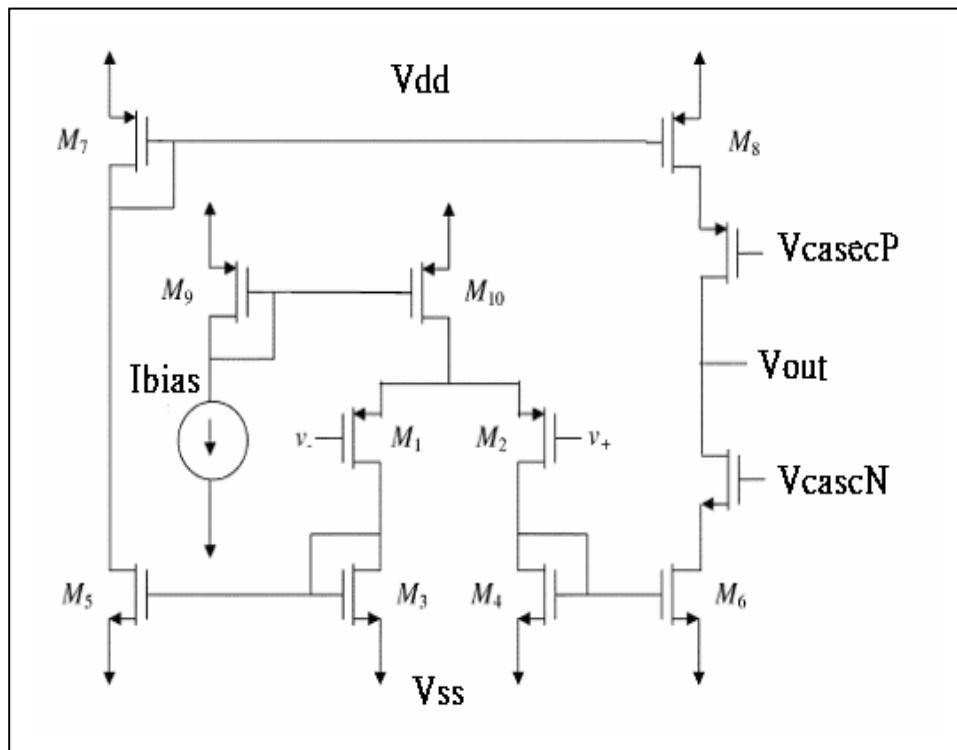

## 2.2.4 美國華盛頓大學

Haidong Guo、Corbin L. Champion、David M. Rector、George S. La Rue

在 2004 年 conference paper 上[12]，提出利用 DAC 加在 MOS 的 body 上，來消除神經元記錄電極產生的 DC-offset，圖 2.17 為設計流程，圖 2.18 為 OP 架構。濾波器設計如圖 2.19，為四階 butterworth filter，頻寬 1 Hz ~ 7 k Hz。

圖 2.17 Haidong Guo 電生理記錄放大器

圖 2.18 放大器架構

圖 2.19 4 階 butterworth filter

## 2.2.5 綜合比較

由上述四種不同電生理訊號放大器的結構分別由美國密西根大學、美國猶它州大學、美國 Duke 大學、美國華盛頓大學所發展，整理成表 2.4，並將為了達成電生理記錄時，神經元頻帶要求所需被動元件大小，列成表 2.5。其中以密西根大學發展最為悠久，早在 1980 年代，已經投入許多心力研究神經元記錄電極與電生理記錄放大器，目前已經發展成為無線系統，對於後來的研究者而言，提供了許多寶貴的資訊。在 2000 年之後，開始有許多國家的實驗室推動腦科學的發展，不論從電路硬體或演算法分析，都有可以改進或者正在被解決的問題，比如說在傳輸資料部分，也從傳送所有的 raw data 演化成只傳送 spike potential、為了發展實用性，low-power issue 越來越重要…等，希望藉由研究前人留下的點滴，設計出更適合電生理訊號放大之電路架構。

|                    |                                                                                             |                                                                                                  |                                      |                                                                                                   |                                                                 |

|--------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                    | Pedram Mohseni<br>Michigan , USA[27]                                                        | Reid R.Harrison<br>Utah , USA[31]                                                                | Iyad Obeid<br>Duke , USA[13]         | Haidong Guo<br>Washington ,US A[12]                                                               | Roy H. Olsson III , Michigan , USA[36]                          |

| Technology process | AMI 1.5um<br>2p2m                                                                           | AMI 1.5um<br>2p2m                                                                                | AMI 0.5um<br>2p3m                    | TSMC 0.25um                                                                                       | --                                                              |

| Voltage            | +1.5V                                                                                       | +2.5 V                                                                                           | +2.5 V                               | +1.5 V                                                                                            | +1.5 V                                                          |

| Gain(dB)           | 39.5                                                                                        | 39.5                                                                                             | 47.4、53.4                            | 20、29、40、<br>49.5、 60                                                                             | 38.9                                                            |

| BW (Hz)            | 26 ~ 6.5k                                                                                   | 0.025 ~ 7.2k                                                                                     | 211 ~ 7.5k                           | 1 ~ 7k                                                                                            | 可調 ~ 9.9k                                                       |

| Roll off (HP/LP)   | -20 / -20                                                                                   | -20 / -20                                                                                        | -20 / -20                            | -- / 4 order                                                                                      | -20 / -20                                                       |

| OP architecture    | P-type OTA                                                                                  | P-type OTA                                                                                       | N-type OTA                           | P-type OTA                                                                                        | P-type OTA                                                      |

| Power              | 133uW                                                                                       | 80uW                                                                                             | 950uW                                | 520uW                                                                                             | 68uW                                                            |

| Die size(mm*mm)    | --                                                                                          | 2.2 * 2.2                                                                                        | 4.2*3.8                              | 0.15*2                                                                                            | --                                                              |

| Output offset      | --                                                                                          | --                                                                                               | 37mV                                 | --                                                                                                | -45mV                                                           |

| P.M.               | 75.5                                                                                        | 52                                                                                               | --                                   | --                                                                                                | --                                                              |

| Implementation     | Single chip                                                                                 | Single chip                                                                                      | Discrete                             | Discrete                                                                                          | Single chip                                                     |

| Others             | 1. laser programmable 之 $R_g$ 提供 PMOS 當 pseudo-resister 來降低 HP 的 pole<br>2. 有 power-line 雜訊 | 1. 利用 pseudo-resister 來壓抑 HP pole<br>2. 使用電容值，來達到 40dB 的 gain (20P : 0.2P)<br>3. 有 power-line 雜訊 | 1. 被動元件 電容 C(100nF) 外接<br>2. 可調 gain | 1. 利用 DAC 加在 body 上，解決 input offset<br>2. 有設計 sample and hold<br>3. 有 power-line 雜訊<br>4. 可調 gain | 1. 用 Reid R. Harrison 架構實現<br>2. 需外加偏壓電壓來選擇 pseudo-resister 的效用 |

表 2.4 綜合規格表

|                     |                                          |                                       |                                 |                                        |                                               |

|---------------------|------------------------------------------|---------------------------------------|---------------------------------|----------------------------------------|-----------------------------------------------|

|                     | Pedram Mohseni<br>Michigan , USA<br>[27] | Reid R.<br>Harrison<br>Utah , USA[31] | Iyad Obeid<br>Duke ,<br>USA[13] | Haidong Guo<br>Washington ,USA<br>[12] | Roy H. Olsson<br>III<br>Michigan ,<br>USA[36] |

| Paper<br>publish    | 2002                                     | 2002                                  | 2003                            | 2004                                   | 2005                                          |

| R1                  | 500                                      | --                                    | 7.33k                           | 1M                                     | --                                            |

| R2                  | 50k                                      | --                                    | 1.008M                          | 1M                                     | --                                            |

| R3                  | 30k                                      | --                                    | 20k                             | 1M                                     | --                                            |

| R4                  | --                                       | --                                    | 800k                            | 1M                                     | --                                            |

| C1                  | 4p                                       | 0.2p                                  | 100nF 外接                        | 16.1p                                  | 0.1p                                          |

| C2                  | --                                       | 0.2p                                  | --                              | 13.8p                                  | 0.1p                                          |

| C3                  | --                                       | 20p                                   | --                              | 39p                                    | 10p                                           |

| C4                  | --                                       | 20p                                   | --                              | 5.7p                                   | 10p                                           |

| R summary           | 80.5k+pseudo<br>resister                 | pseudo resister                       | 1.827M                          | 4M                                     | pseudo resister                               |

| C summary           | 4p                                       | 40.4p                                 | 100nF 外接                        | 74.6p                                  | 22.2p                                         |

| BW(Hz)              | 26 ~ 6.5k                                | 0.025 ~<br>7.2k                       | 211 ~<br>7.5k                   | 1 ~ 7k                                 | 可調式 ~ 9.9k                                    |

| Roll off<br>(HP/LP) | -20 dB / -20<br>dB                       | -20 dB / -20<br>dB                    | -20dB /<br>-20dB                | -- / 4-order                           | -20 dB / -20<br>dB                            |

表 2.5 被動元件使用記錄

# 第三章 電生理記錄之低功率多頻道 CMOS 放大器設計

第三章介紹本論文的設計方式與實作的電路，從放大器的設計到提供測試考量與測試方法。

## 3.1 設計架構

本論文針對電生理訊號放大設計作考量，並提出三種可由使用者根據不同狀況作選擇的運作模式，前置放大器模式（圖 3.1）、平行高通濾波模式（圖 3.2）及 buffer 模式（圖 3.3）。

圖 3.1 模式 1 前置放大器

圖 3.2 模式 2 平行高通濾波

圖 3.3 模式 3 buffer

有三種模式主要考量，是針對電生理訊號常常會伴隨著當進行動物實驗時，會有電極與電解液發生約 100 mV 的 DC-offset[25]，如果對這些低頻大雜訊置之不理，非常有可能會對整個 IC 造成不正常工作的情況發生。因此設計成三種模式，主要的原因在於，為了日後發展電生理晶片的可能方向作佈局。簡單整理模式 1.2.3 之間的比較，如表 3.1 所示。

#### A. 模式 1：前置放大器

因為電生理訊號相當小，只有約 10  $\mu$ V 等級，所以需要適當的放大，以便處理訊號濾波的功能。因為伴隨低頻大雜訊，所以可接受的放大倍率，會受限於第一級輸出點的 swing 範圍。在需要時，也可外接電阻變成可調倍率的放大器或者當作緩衝器，後面測試考量時會詳細描述，電路架構如圖 3.4。

#### B. 模式 2：平行高通濾波

嘗試先經過高通濾波器，把低頻大雜訊先去除掉，再針對訊號作適當的放大處理。這種模式能有效在動物實驗時，濾除 large DC-offset，不過此作法會有訊號衰減的疑慮。為了避免有訊號過度衰減的情況產生，將模式 2 改良成模式 3 的設計。電路架構如圖 3.5。

#### C. 模式 3：buffer

整合了模式 1 與模式 2 的概念，發展成模式 3。此模式加入了一前置放大器，可先將電生理訊號經過適當放大後，在經過濾波去除低頻大雜訊，可避免訊號過度衰減的情況。電路架構如圖 3.6。

|    | 模式 1                                    | 模式 2            | 模式 3                              |

|----|-----------------------------------------|-----------------|-----------------------------------|

| 優點 | 電路所耗面積較小                                | 解決 DC-offset 問題 | ICMR 比模式 1 大，提供增益選擇，且可解決模式 2 之弱點。 |

| 弱點 | ICMR 受到 input DC offset 限制 (-0.14~0.12) | 有訊號衰減疑慮         | 面積比模式 1.2 稍大                      |

表 3.1 模式比較

圖 3.4 模式 1 電路

圖 3.5 模式 2 電路

圖 3.6 模式 3 電路

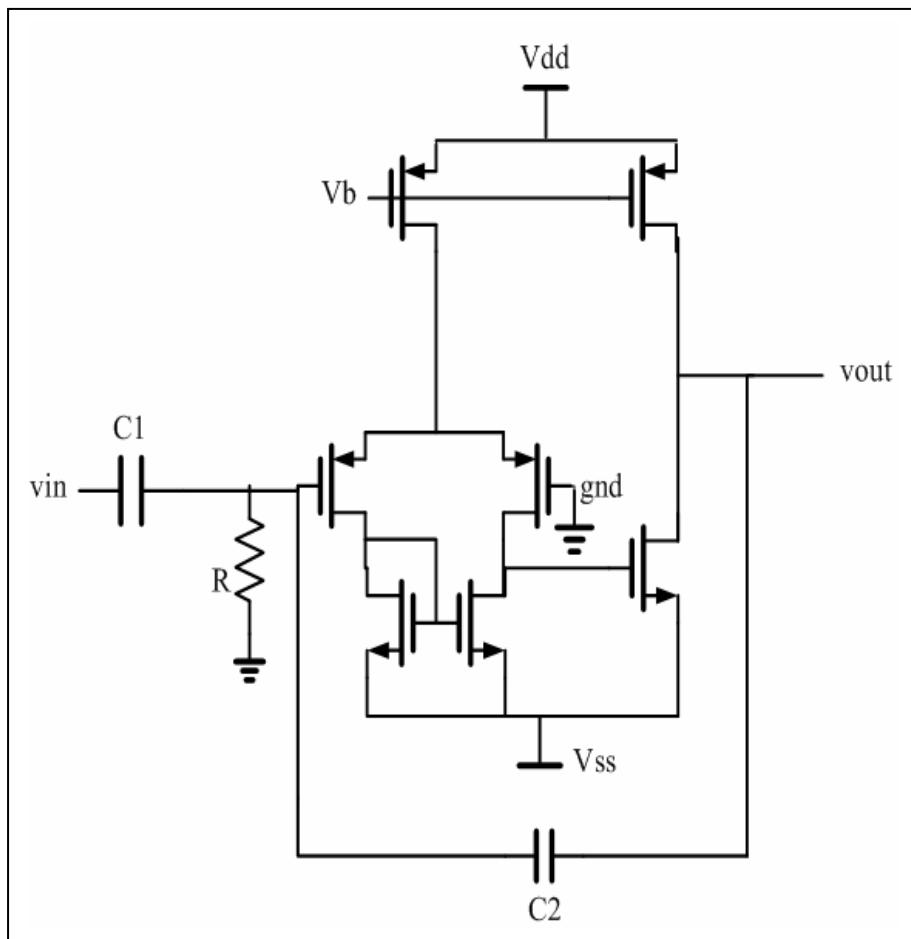

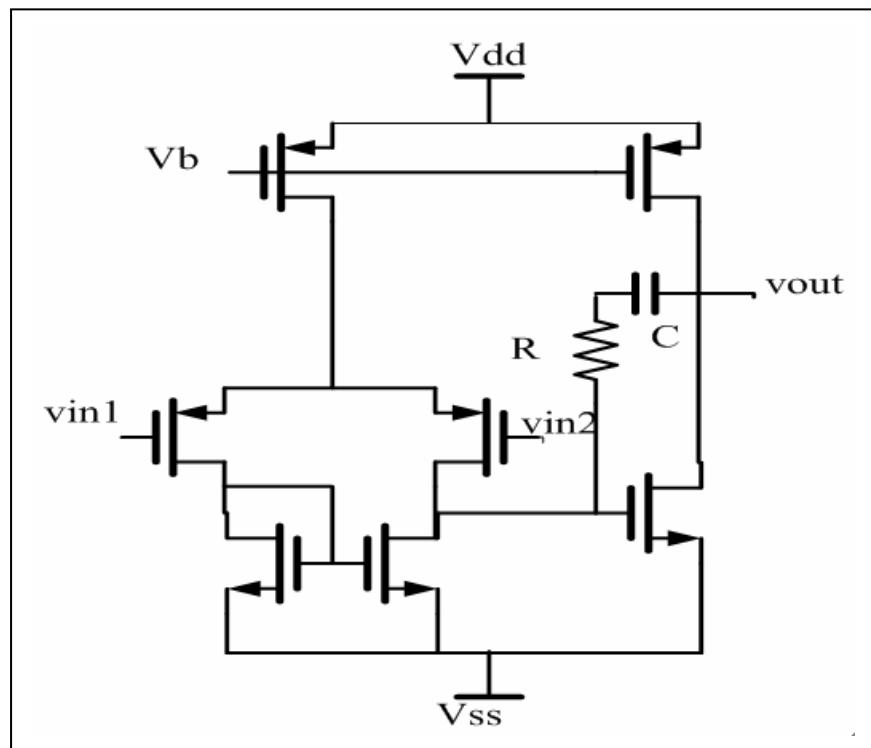

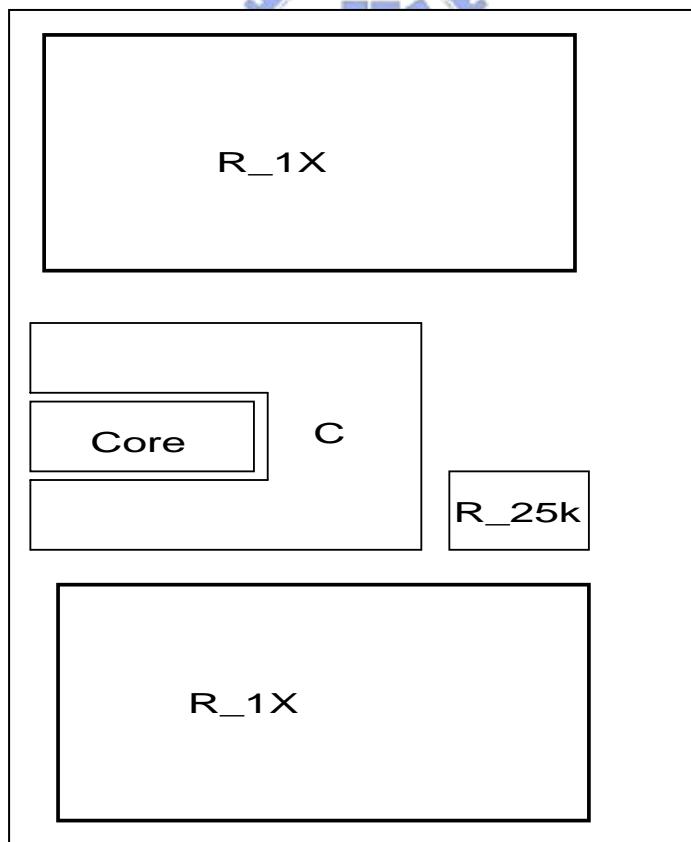

本論文的電生理訊號放大器設計，均以模式 3 為探討。模式 1 與模式 2，在測量考量時，會著墨介紹。模式 3 可分成三個部分（圖 3.3）。第一部分設計使用一個 pre-amp，必要時，也可使用外接電阻變成可調 gain 的放大器或者當作 buffer 使用，第二部分，是一個高通濾波器，第三部分是一個具放大器功能的低通濾波器。

低功率對電生理記錄放大器而言，越來越重要，因為隨著神經元記錄電極的進步，可偵測到越來越多的神經元訊號，也就需要越來越多的電生理記錄放大器，當眾多的電生理放大器因實驗需要，必須被長時間使用於記錄訊號，此時功率與散熱問題，是非常重要的議題。再加上未來無線傳輸系統是一種趨勢，電源供應必然不會再使用 power supply，電源必須用電池或其他可攜式的電能來源，因此低功率的需求已經成為研究電生理記錄放大器所要重視的問題。

本研究設計，與國外實驗室設計方式的差別，除了著重在於低功率之外，最大的差異在於盡量利用電路本身的特性來減少額外或多餘的設計。例如應用 miller 效應和頻率補償方式。以下小節針對電路設計作說明。

## 3.2 電路設計

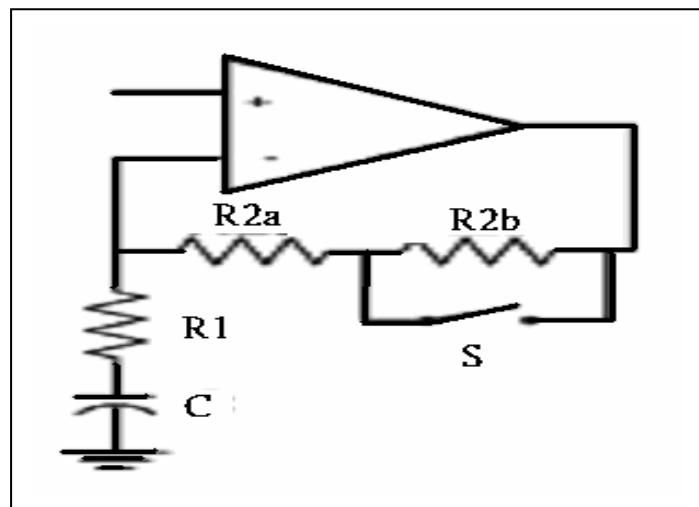

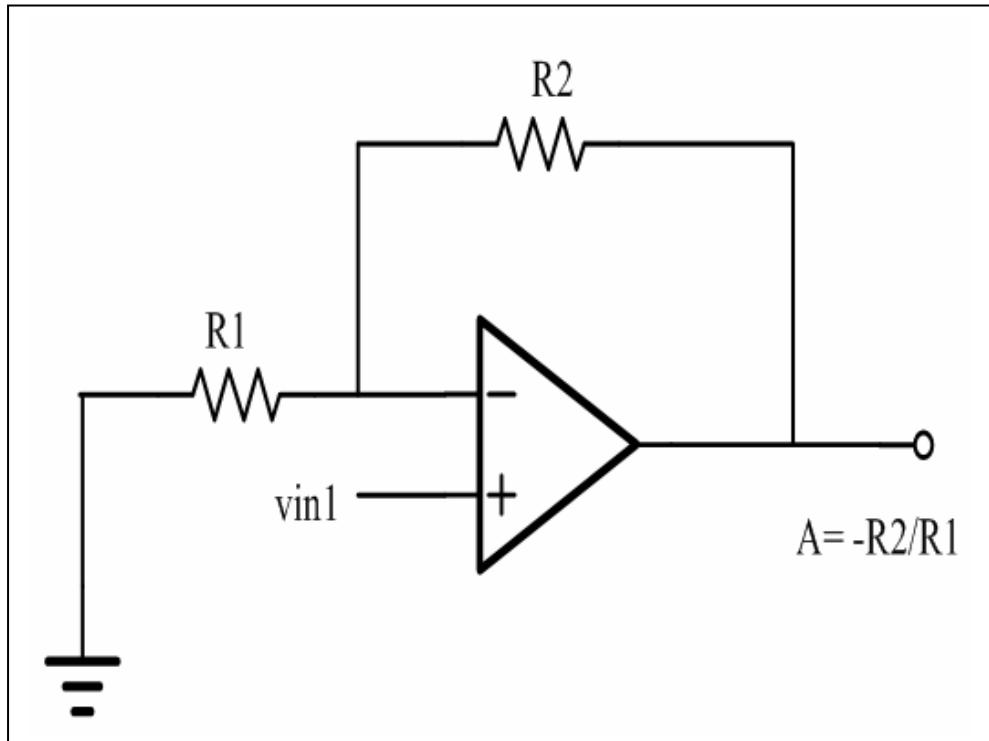

### 3.2.1 前置放大器（緩衝器）設計：

首先第一部份設計一個前置放大器，主要在於可事先放大電生理訊號，必要時，可當作 buffer 緩衝，也可適當的選擇外接電阻，以調整所需要的 gain，圖 3.7 為典型放大器的設計。前置放大器的 OP 電路選擇，採用差動放大器，輸入級有 PMOS 與 NMOS 兩種選擇，就 flicker noise 的觀點而言，PMOS 擁有比 NMOS 更好的抗雜訊的能力[1][2][9][10]，因此選擇 PMOS 當作 difference input pair 當作輸入級（flicker noise 分佈如圖 3.8）。

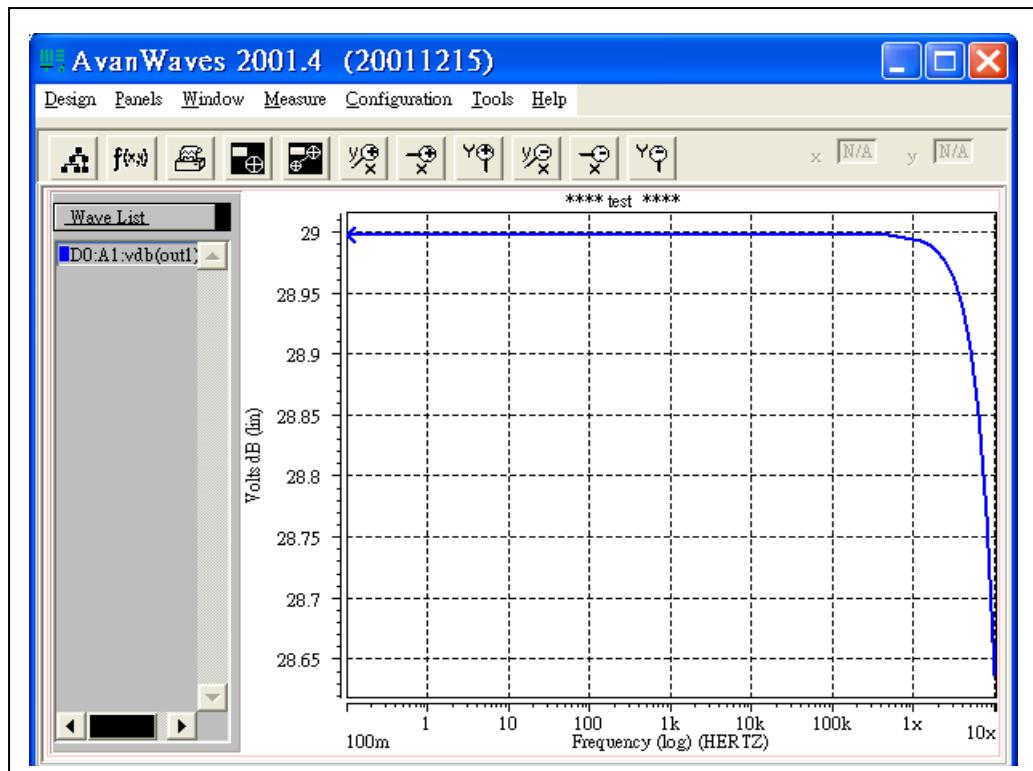

此前置放大器的電路架構如圖 3.9，可提供 29 dB 的 gain (約 28 倍)。經由適當安排，也可當作 buffer 使用，或提供 1~28 倍的可調放大倍率。設計時，供應電壓正負 1V，估計靜態總電流 6 uA，電晶體 over drive 電壓 0.1V ~0.2V，經過估算後，適當微調 W/L 的比值，測試通過製程飄移的 5 個 corner (FF、TT、SS、FS、SF) 均可正常工作。在 TT 的情況下，ICMR 為 -0.14V ~ 0.12 V。

圖 3.7 前置放大器架構示意圖

圖 3.8 flicker noise 頻譜分佈

圖 3.9 前置放大器

### 3.2.2 高通濾波器設計：

濾波器主要有 1. 被動濾波器、2. 主動濾波器及 3. SC 濾波器三種架構中考量[39]。

1. 被動濾波器由被動元件 RLC 組成，但是會造成電生理訊號的嚴重衰減。

2. 主動濾波器由 RC 與 OP 組成，會加入些微 OP 本身的 noise。

3. SC 濾波器會將 switch noise 引入電生理訊號，有實驗室提出不適合應用於電生理訊號[13]。

由以上的分析，架構 1 與 3 不適合用於電生理訊號晶片設計上，最後選擇主動濾波器。

主動濾波器的架構方式，有直接做成 band-pass filter，也有利用 HP+LP 的合成效應。應用於電生理的頻寬時，如果直接做成 band-pass filter，階數低的話，中間的平坦帶效果將會很差，容易得到一個 peak 值，階數高的話，被動元件數目多且數值大，將難以整合於一顆晶片中。所以選擇使用 HP+LP 的合成效應。

設計濾波器，我們需要一個 OP，在此就先設計一個 2 stage 的放大器，同樣就抗 flicker noise 而言，選擇用 PMOS input pair，圖 3.10 為 2 stage OTA 的電路架構。設計流過第一級與第二級 PMOS 的電流為 6 uA、3uA，MOS over drive 電壓  $0.1V \sim 0.2V$ ，透過計算，得到 W/L 的比值，適當微調該比值，即可測試通過製程飄移的 5 個 corner (FF、TT、SS、FS、SF)正常工作。此放大器具有 60 dB 的 gain。

第二部分要設計高通濾波器，主要是去除動物實驗時，因電極與電解液產生約 100 mV DC-offset 非常大的低頻雜訊。國際上公認電生理的頻寬[13]是從 100 – 400 Hz 起，直到 3 k – 10 k Hz 為止。所以適當的設計濾波器去除龐大的低頻雜訊，對後端的 ADC 及分析系統是非常必要的。濾波器設計不在於高階，太高階的濾波器，對系統極可能會造成不良影響，甚至會變成不穩定系統[6][13][16]。

國外實驗室，目前消除龐大的低頻雜訊，有美國 Duke 大學[6][13][16]，使用外接電容 100 nF 來達成去除低頻雜訊，該實驗室提出，如果使用 Switch capacitor filter 將會對電生理訊號加入 switch noise 的干擾。美國華盛頓大學[12]，以設計一個 DAC，將經過適當選擇數位控制轉成類比訊號的電訊號，加諸在於輸入級的 body，進而達到抵消電生理訊號的 DC offset，不過對於電生理訊號的來源，往往夾雜的低頻訊號，也有市電的雜訊，所以此設計，對真實訊號而言，是一大考驗。美國猶它州大學[5][22][23][32][33][34][35][36]，利用 PMOS 設計為 diode-connection 的方式，達到形成 pseudo-resister 的效果，因此可避免掉放入過於龐大的電阻值，該大學設計，

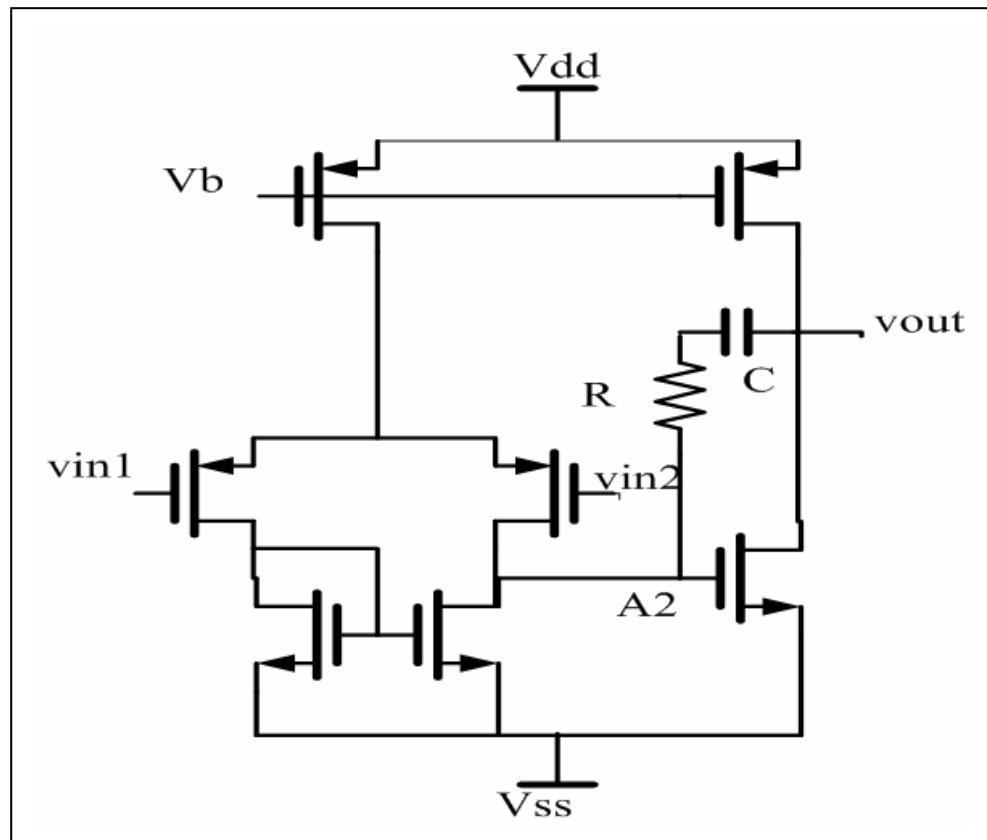

是以電容比值為增益的主要來源，所以設計上電容會達到 20 p，本研究設計，採用 Miller 的概念，如圖 3.11，利用 OP 的增益，來提高被動元件的效能。

圖 3.12 及 3.13 為設計的示意圖。

假設高通濾波器的極點在 200 Hz，則如果使用被動濾波器，我們可以得到 RC 的值為  $1.59 \text{ E-3}$ ，假設我們選定電容值 C 為 1 p，則電阻值為  $1.59 \text{ E9}$  ( $1.59 \text{ G}$ )，該電阻值過於龐大，如果提高電容 C 為 10 倍，電阻值降低 10，則電容 10 p 與電阻 159 M，這些都不太可能以積體電路實現。而 Switch-Capacitor filter，是由美國 Duke 大學 Iyad Obeid 提出，該研究結果顯示，會對電生理訊號加入 switch noise。所以根據以上的探討，主動濾波器是本論文設計的概念，並加入 Miller 效應來提高電容的效益。

圖 3.10 2-stage 電路架構圖

圖 3.11 Miller effect

圖 3.12 高通濾波器架構示意圖

圖 3.13 高通濾波器架構圖

電容效益提升，計算式如下

當 Miller 效應產生，可得電容  $AC$ ，其中

A: 增益、C: 電容

$$F = \frac{1}{2} \pi R A C$$

RC→RAC 提升 A 倍

故當  $A=60$  dB( 1000 倍 )

選擇  $R = 1 \text{ mega}$  、  $F = 150 \text{ Hz}$

可得  $C$  約  $1 \text{ pF}$

### 3.2.3 低通濾波器：

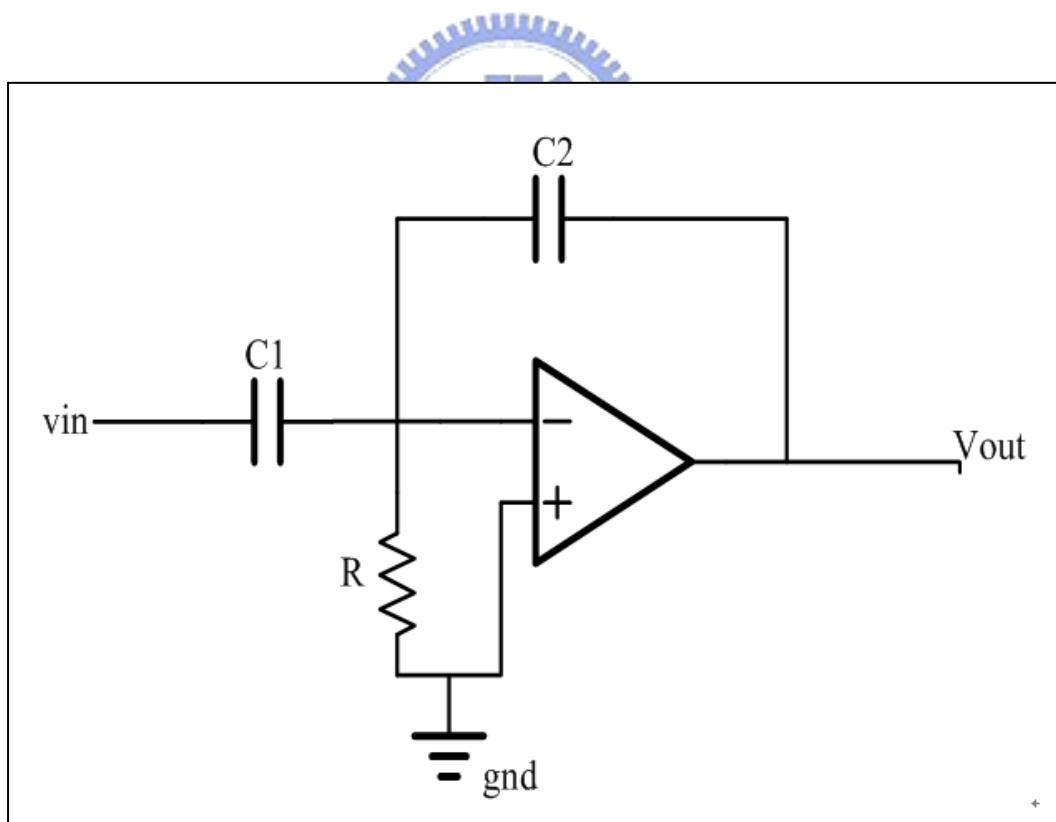

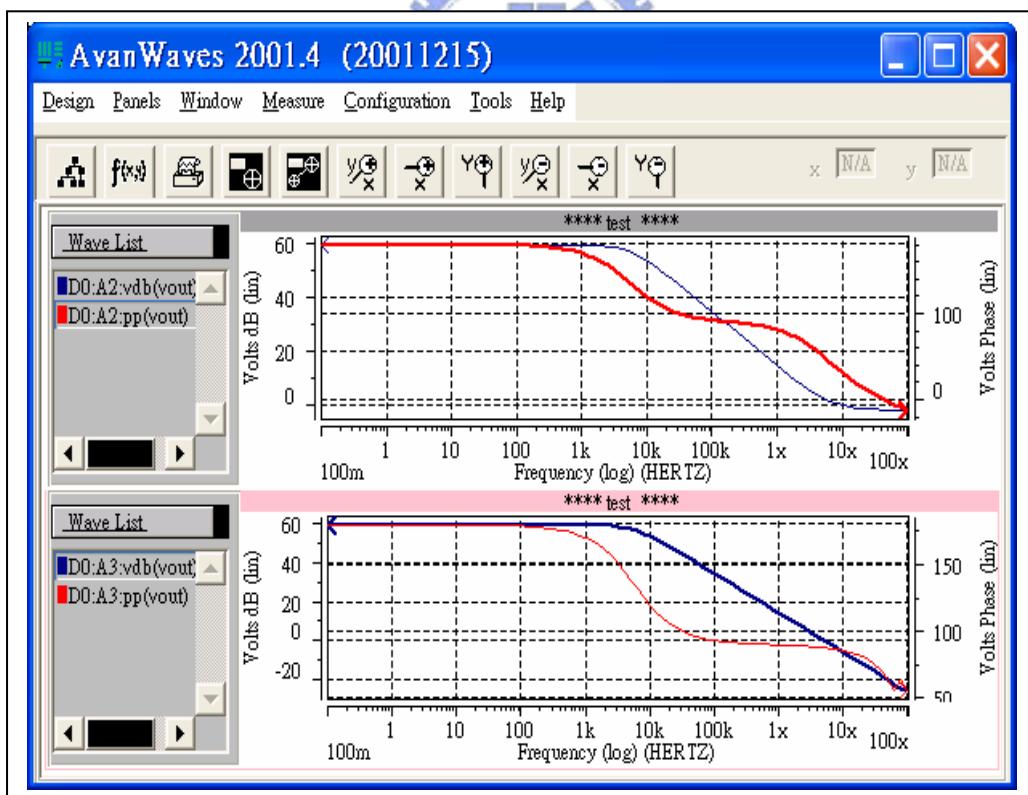

第三部分為具放大功能的低通濾波器，主要是利用回授控制，達到頻率補償實現低通濾波器，頻率補償原本是應用在於分離兩個較為接近的極點，形成一個主極點，進而提高電路的穩定度，不過在此，與其設計一個正統的低通濾波器，不如就利用電路本身的特性來達到低通濾波器的效果，這是我設計的概念。圖 3.14 為具放大功能的低通濾波器的架構。

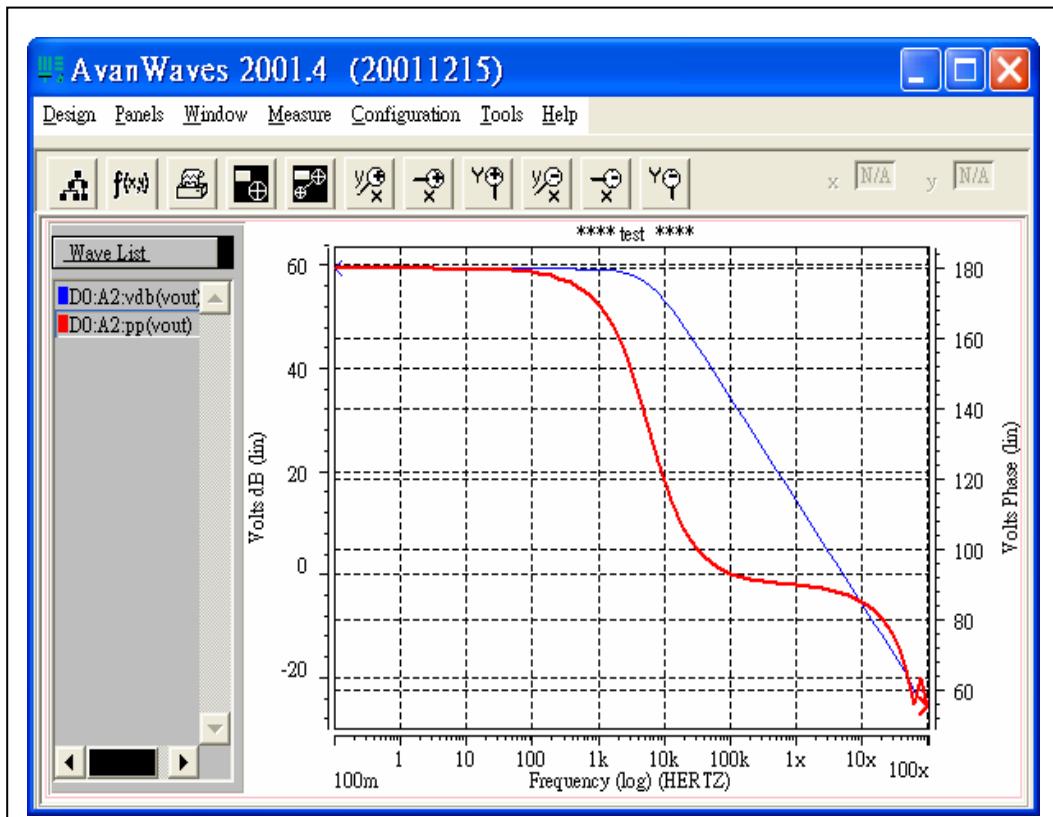

利用回授電路控制，會特別注意 closed loop 的 stability，如果設計不良，容易變成 unstable system。電路中，跨接電容形成 dominate pole，不過在設計時，常常會加入一適當電阻（圖 3.14），把 S domain 右半邊的一個 zero 紿 pole-zero cancellation 掉，提高系統的 phase margin。不過分析該設計中右半平面 zero 位置，在 6 mega 的地方，距離我們低通濾波器的主極點 6 k 相差 1000 倍，且已經是 stable system，但是為了提高 PM，加入一電阻，讓 PM 提高為 85 度。以下為計算之方程式，圖 3.15 為加入補償電阻前後之波德圖，可看見 phase margin 提高到 85 度。

$$F = \frac{1}{2} \pi R C$$

→  $F = 6 \text{ mega}$ ,  $C = 1 \text{ p}$

→  $R$  約當 25 k

設計時，取  $R = 24 \text{ k}$

圖 3.14 具放大功能的低通濾波器

圖 3.15 加入補償電阻前後之波德圖

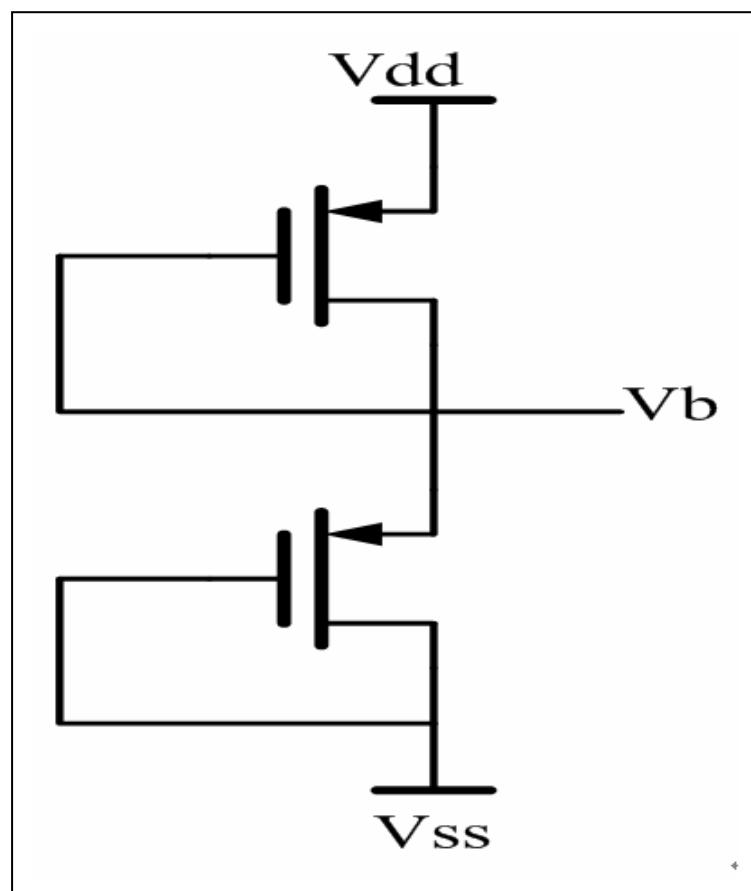

### 3.2.4 偏壓設計：

最後為提供偏壓的方式，採用2個PMOS組成，圖3.16為架構圖[11][25][27][40][41][42]。設計此偏壓電路提供系統一個適當偏壓點，經過計算與測試系統可接受的範圍，設計約0.13 V，設計電壓，因此設計完畢後，必須與整個系統連接上，並且測試5種製程飄移參數（FF、SS、TT、FS、SF），已確保系統可正常工作，測試後整體系統可合乎原本預期之設計。

圖 3.16 偏壓電路

### 3.3 測試考量

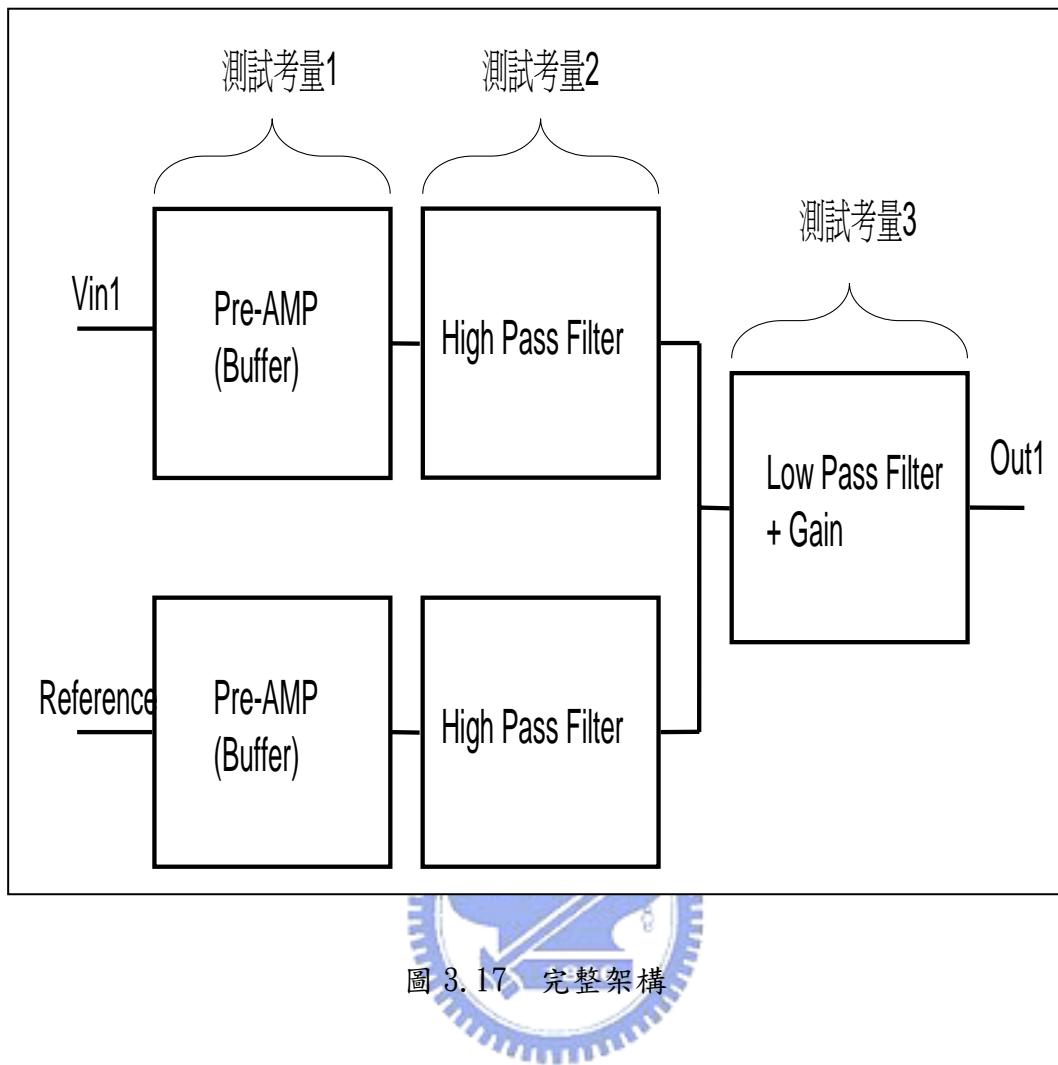

在測試上，拉出多個測試與驗證的節點。下圖 3.17 為整體架構，每一個方塊的輸入輸出均有設置節點，並考慮補償的方法，以下就每個方塊探討。

圖 3.17 完整架構

### 測試考量 1：前置放大器部分

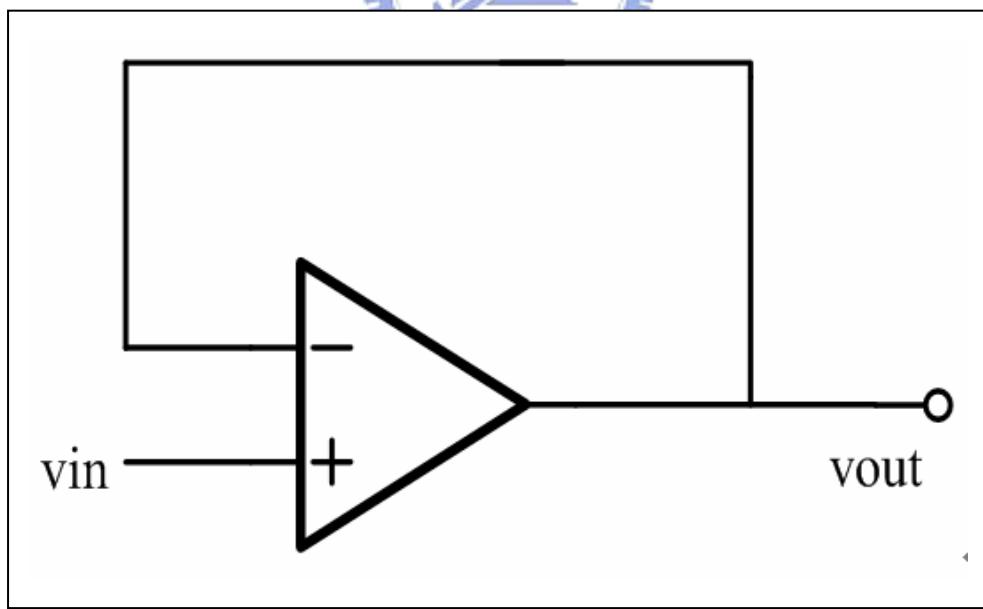

考慮電生理訊號如果經過前端電極後，直接接至高通濾波器，可能會因為訊號衰減而造成要觀察的電生理訊號有不良的影響，也可能會因為後端 ADC 負載的關係，導致 gain 不如預期，所以需要前置放大器。前置放大器有設計額外的節點，經由外接電阻比值  $R_2/R_1$ ，選擇調整放大倍率，提供 1~28 倍的倍率，如圖 3.18 前置放大器測試考量架構示意圖。必要時，也可當緩衝器，如圖 3.19 所示。

電阻  $R_1$ 、 $R_2$  的選擇，盡量以 Mega 級為主，因為阻抗匹配的問題，如果必須外加電阻，必須負載夠大，訊號才能順利傳遞，另外選擇大電阻，也可降低功率的消耗。

圖 3.18 外接電阻選擇增益

圖 3.19 當作 buffer 使用

## 測試考量 2：高通濾波器部分

有設立特殊節點 A1 和 gnd，當遇到因為頻寬不夠低或不理想時，可以外接電阻於 A1 和 gnd 之間補償，達到電生理訊號適當的頻寬。圖 3.20 高通濾波器測試考量架構示意圖。

如果低頻 3 dB 過低，可以並連電阻於 A1 和 gnd 之間，電阻選擇則依據電阻並連效應去計算，設計於 IC 裡的電阻為 1 mega 歐姆。如果低頻 3 dB 過高，則可外加電阻於 gnd 點和外面真正的 gnd 點，電阻選擇則依據電阻串連效應去計算。

圖 3.20 補償高通濾波器不理想狀況

### 測試考量 3：具放大功能之低通濾波器部分

有設立特殊節點 A2，當遇到頻寬不理想時，可外接電容補償。圖 3.21 低通濾波器測試考量架構示意圖。如果高頻 3 dB 點太高，可外接電容於 A2 和  $V_{out}$  之間，設計於 IC 中電容為 1 pF。

圖 3.21 補償低通濾波器不理想狀況

# 第四章 晶片實現與結果驗證

第四章在介紹晶片製作到佈局後的模擬結果，及效能比較。

## 4.1 晶片設計流程與製作

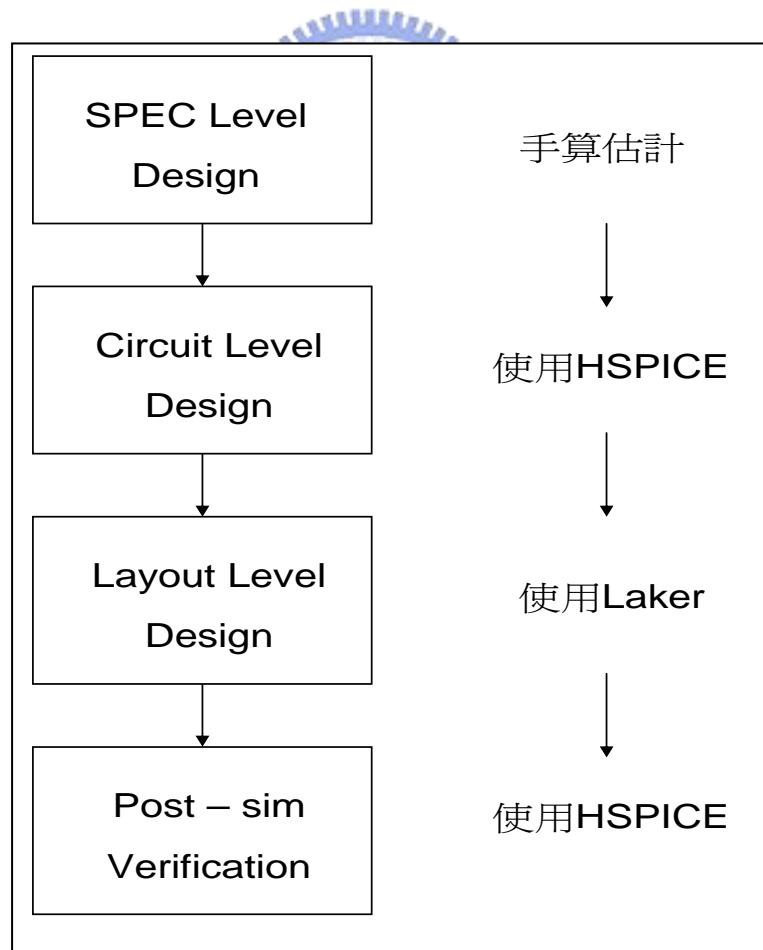

在設計電生理記錄放大器時，一開始先觀察電生理訊號有哪些反應與波形，參考其他相關實驗室之電路架構，思考自己要設計的架構後，提出一個構想，再利用 HSPICE 作 Transistor Level 的電路設計及動作驗證與模擬 (Pre-Simulation)，通過pre-simulation測試，就進入利用 Laker Tools 佈局，並且測試佈局後驗證 (Calibre DRC 和 LVS) 以及最後的模擬 (Post-Simulation)。流程如圖4.1所示。

圖 4.1 設計流程

佈局考量：

類比電路的抗雜訊能力低且對製程敏感度高，因此在佈局時，需要注意整體位置。基本的類比電路佈局考量，有匹配的問題，要加入 Dummy cell 來保護重要元件，最好也在核心的電路部分，使用保護環(Guard ring)將被動元件與核心電路隔離。

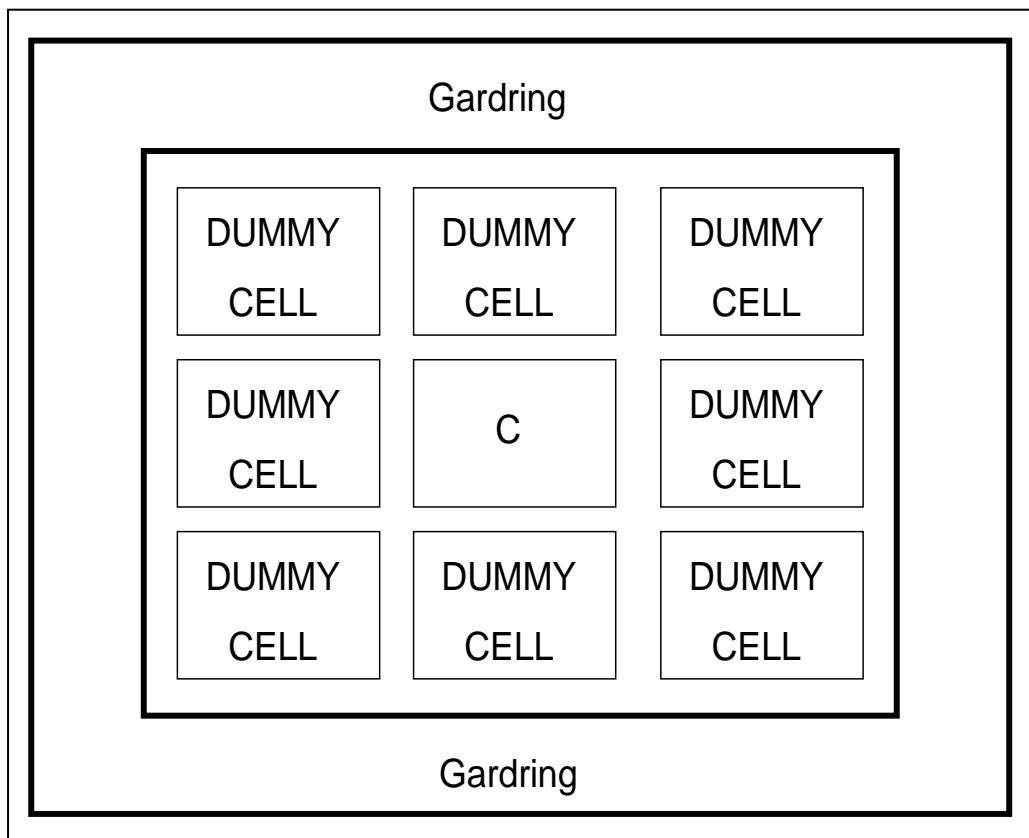

設計單位電容  $0.05 \text{ pF}$ ，45 度角切齊（圖 4.2）。利用單位電容繞成所需電容，加入 DUMMY CELL，並用兩個 contact 的 guard ring 圍住（圖 4.3）。

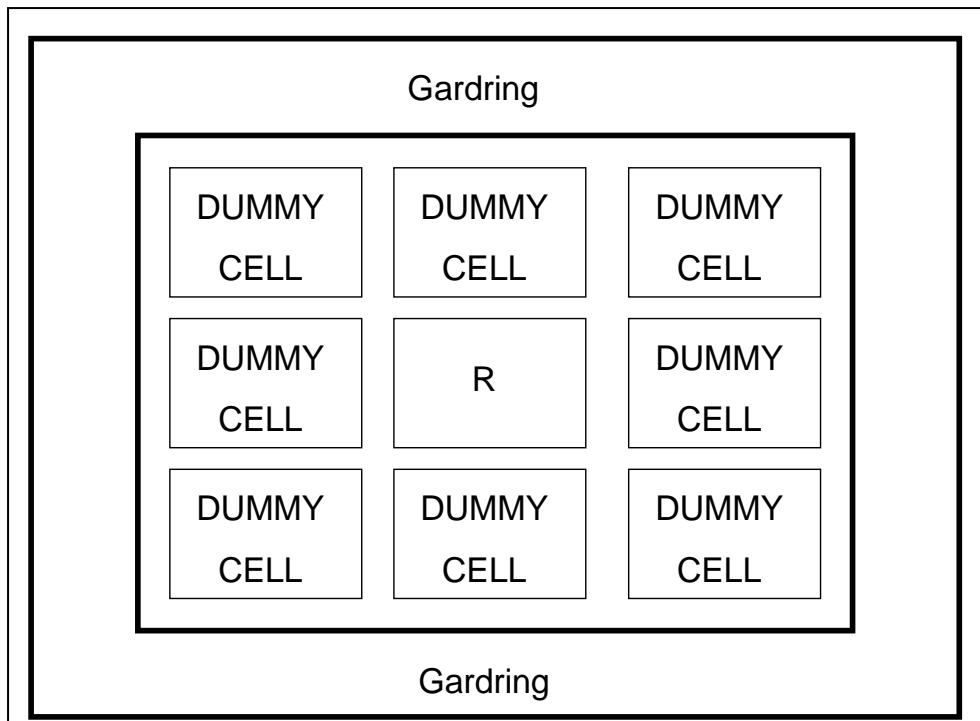

設計單位電阻  $1 \text{ k}$ ，使用 Diffusion（圖 4.4）。利用單位電阻繞成所需電阻，加入 DUMMY CELL，並用兩個 contact 的 guard ring 圍住（圖 4.5）。

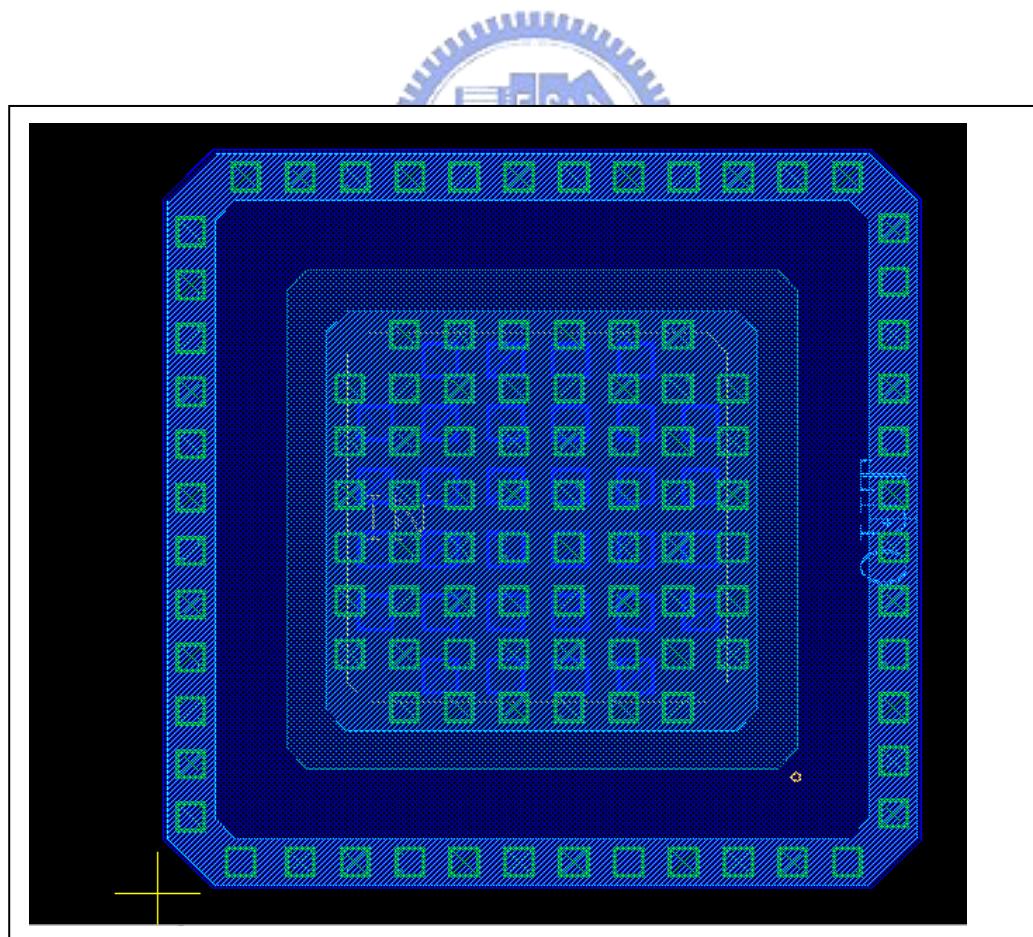

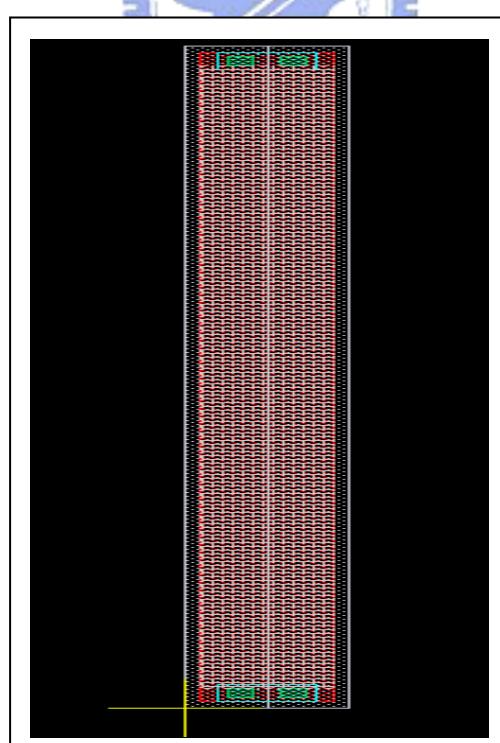

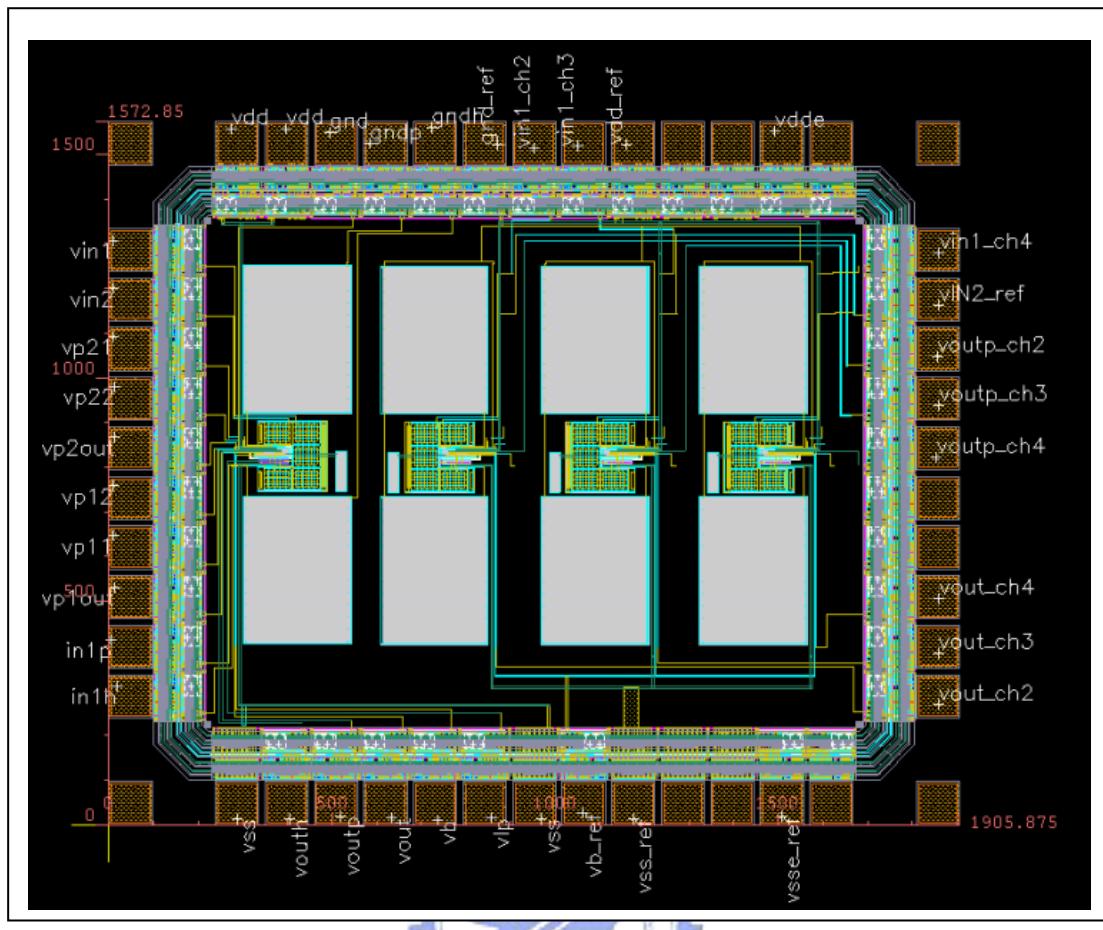

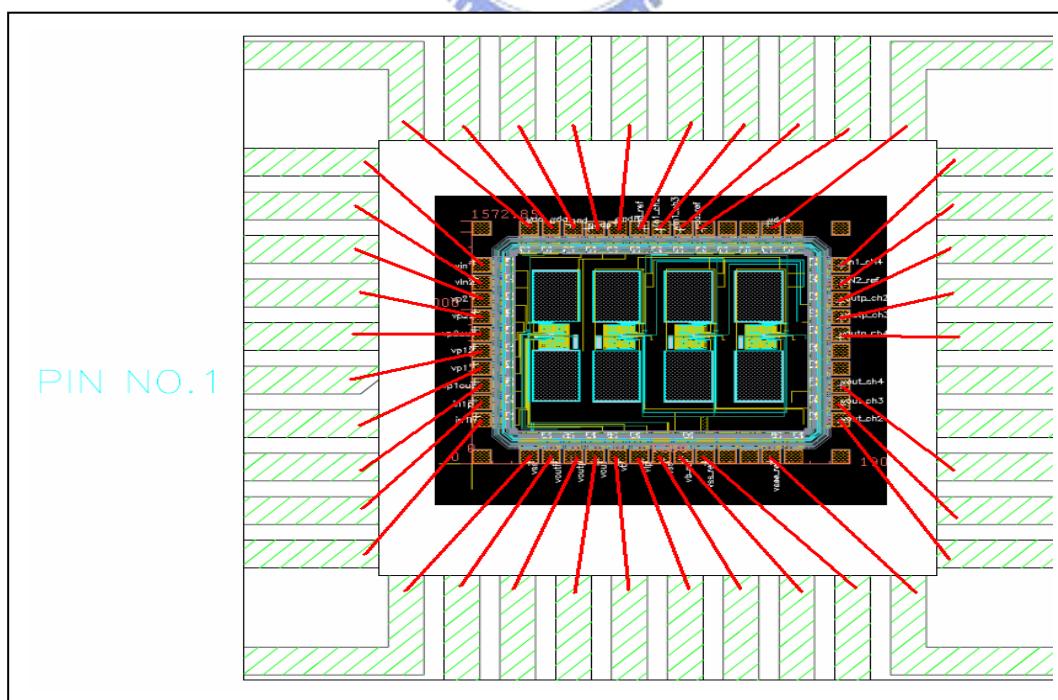

圖 4.6 為 1 channel 佈局示意，圖 4.7 為完整佈局示意，圖 4.8 為實際佈局圖，圖 4.9 為給封裝廠商看的打線圖。

圖 4.2 單位電容

圖 4.3 加入 DUMMY CELL 與兩個 contact 的 guard ring 圍住

圖 4.4 單位電阻  $1\text{ k}$

圖 4.5 加入 DUMMY CELL 與兩個 contact 的 guard ring 圍住

圖 4.6 1 channel 電路佈局示意

## 佈局平面圖

CKT name : NR chip

Technology : TSMC 2P4M 0.35um

Package : SB40

Chip Size : 1906 um \* 1580 um

Power Dissipation : 54.5uW (1-channel, HSPICE Results)

因 4-channel 中的 1 個 channel 當作測試與驗證用，所以輸入、輸出與測試的腳大約 20 pin，已經佔滿一半的腳位，考慮到拉線問題，將其他 3 個 channel 使用 mirror 方式，將腳位拉至另外半面，如 4.8。

圖 4.7 layout 示意圖

圖 4.8 layout 全圖

圖 4.9 打線圖

## 4.2 佈局後的模擬結果

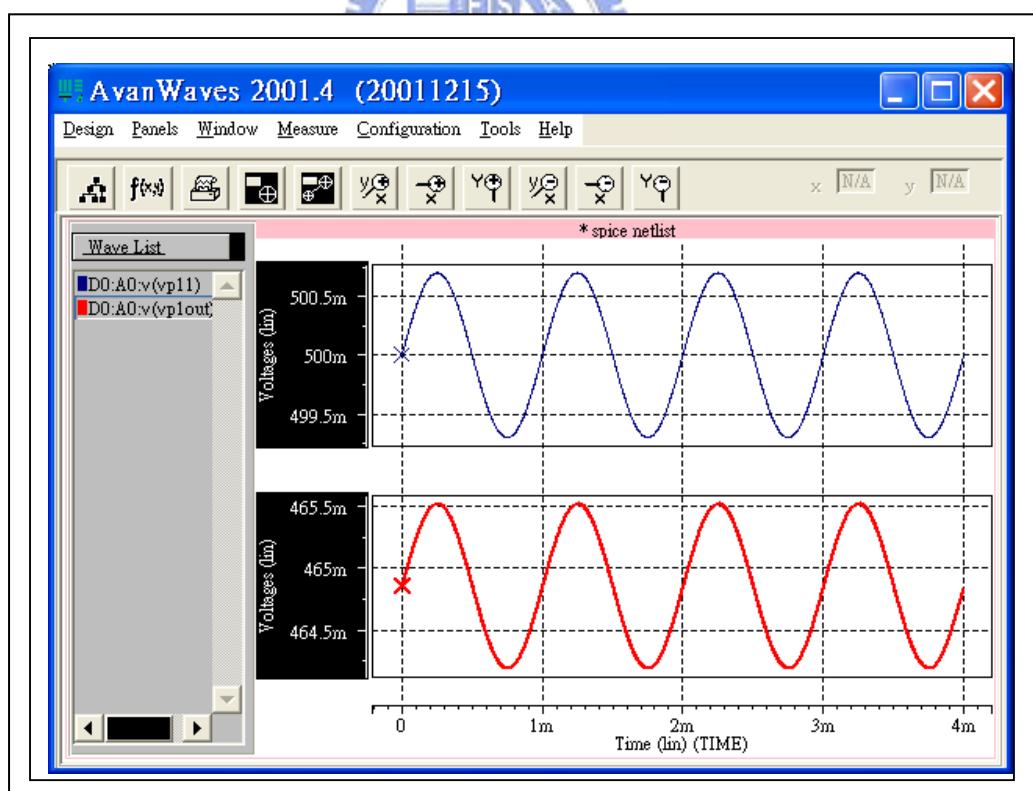

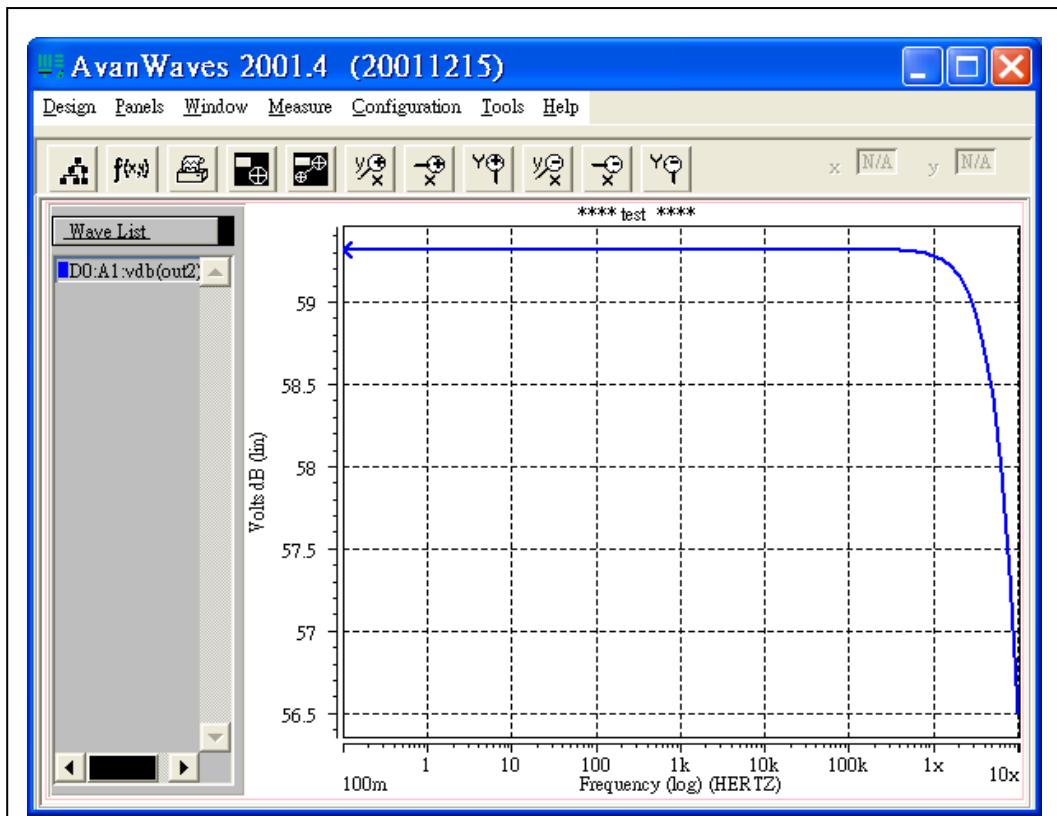

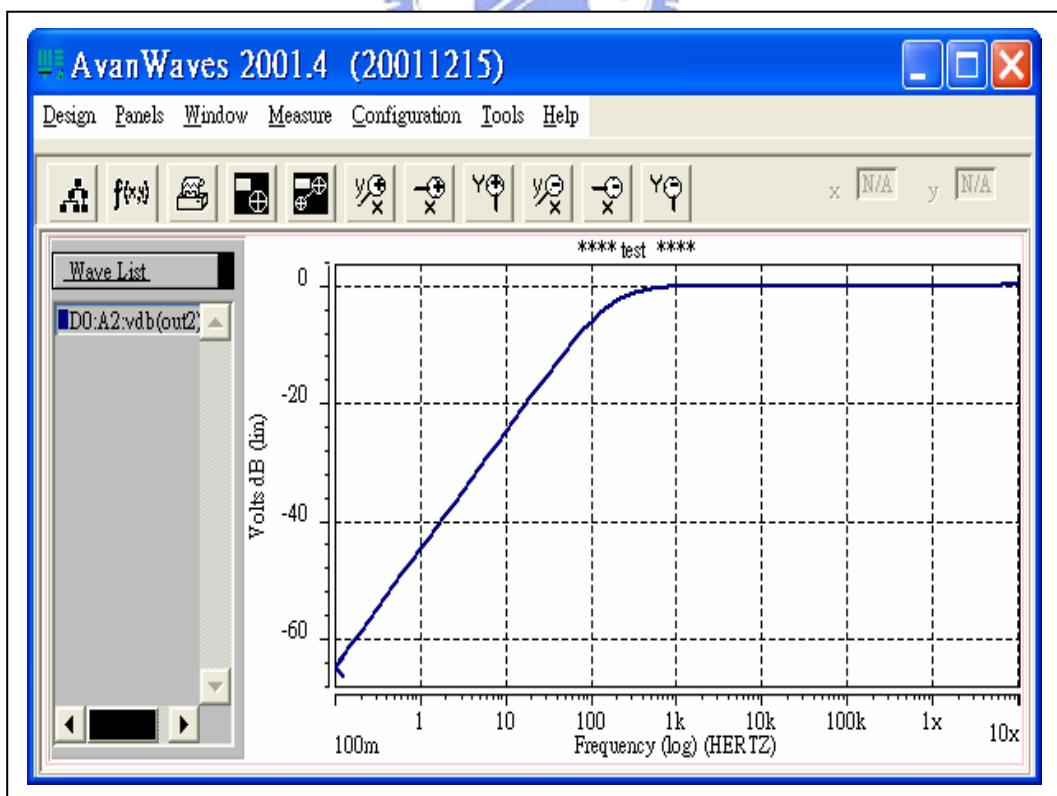

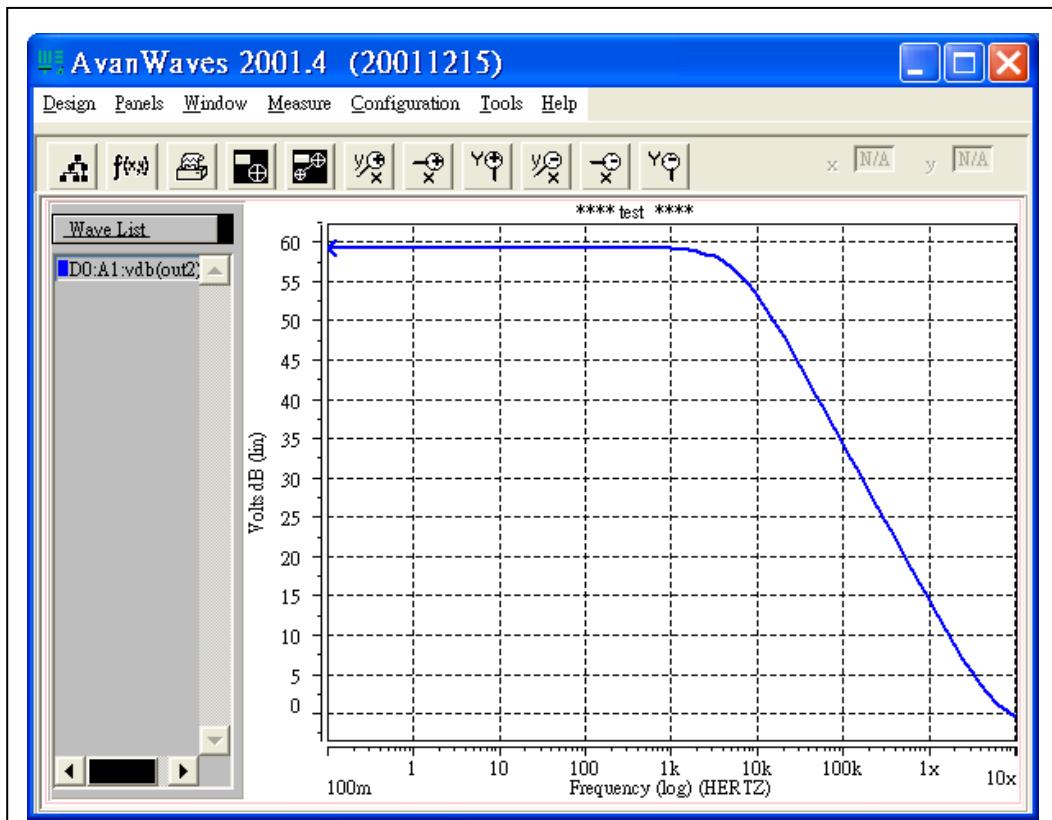

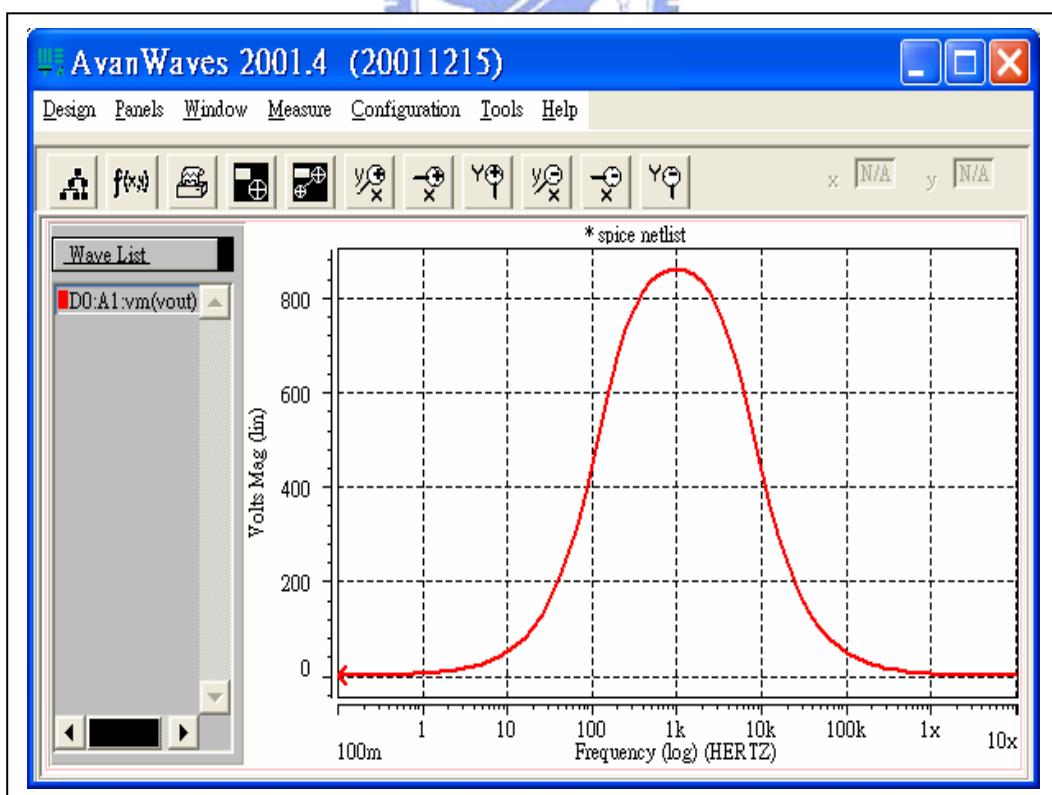

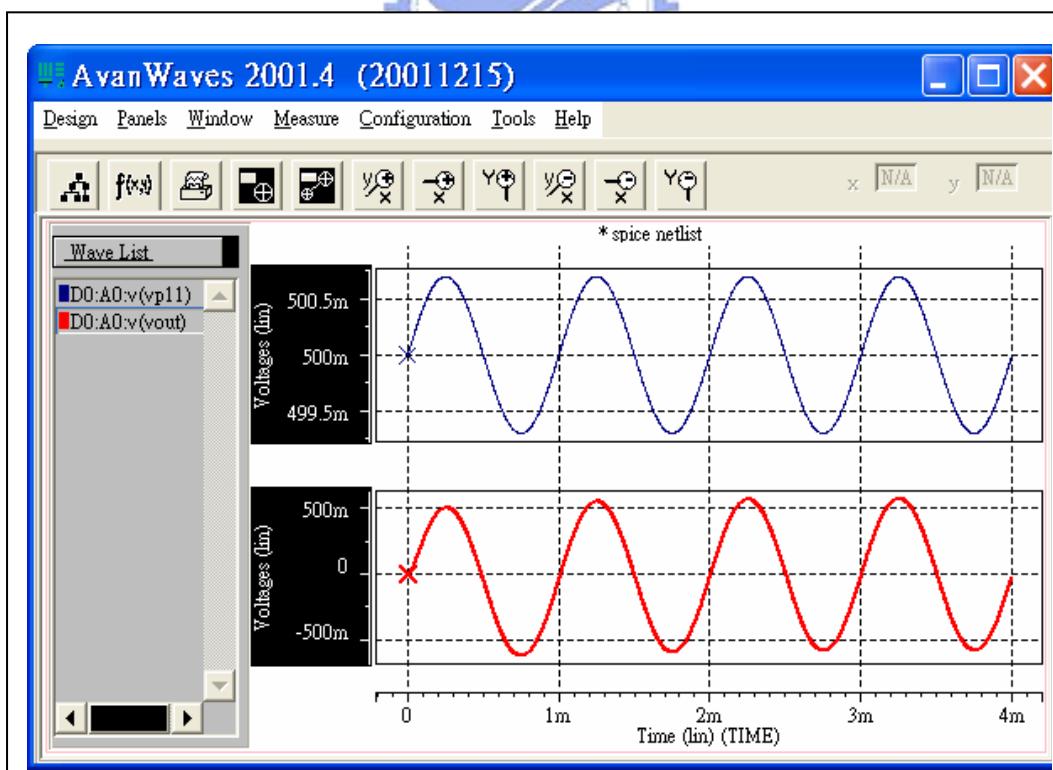

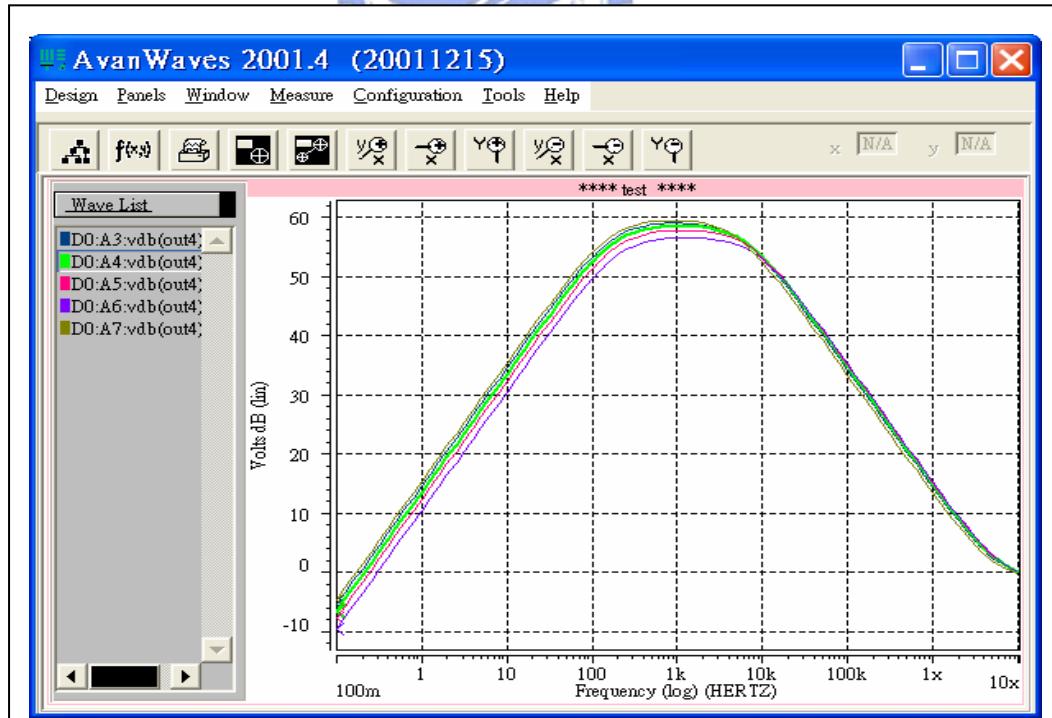

在圖 3.9 的架構介紹中，第一級為一個前放大器，圖 4.10 為前置放大器的波德圖。圖 4.11 為當 buffer 使用的情況，灌進輸入訊號有 0.5V 的 DC offset 加上 700 uV 的 1 k Hz 電生理訊號，可以看見輸出訊號也維持 700 uV 的振幅。圖 4.12 為二階放大器 OTA 的波德圖，提供將近 60 dB 的 gain。圖 4.13 為高通濾波器的波德圖，截止頻率在 161 Hz。圖 4.14 為具放大功能之低通濾波器的波德圖，截止頻率在 5.9 k Hz。圖 4.15 為合成一個帶通濾波器之頻譜響應，提供約 880 倍的增益，頻帶在 161 Hz 起，5.9 k Hz 止，合乎電生理的頻帶範圍。圖 4.16 為系統之 phase margin 約 85 度。

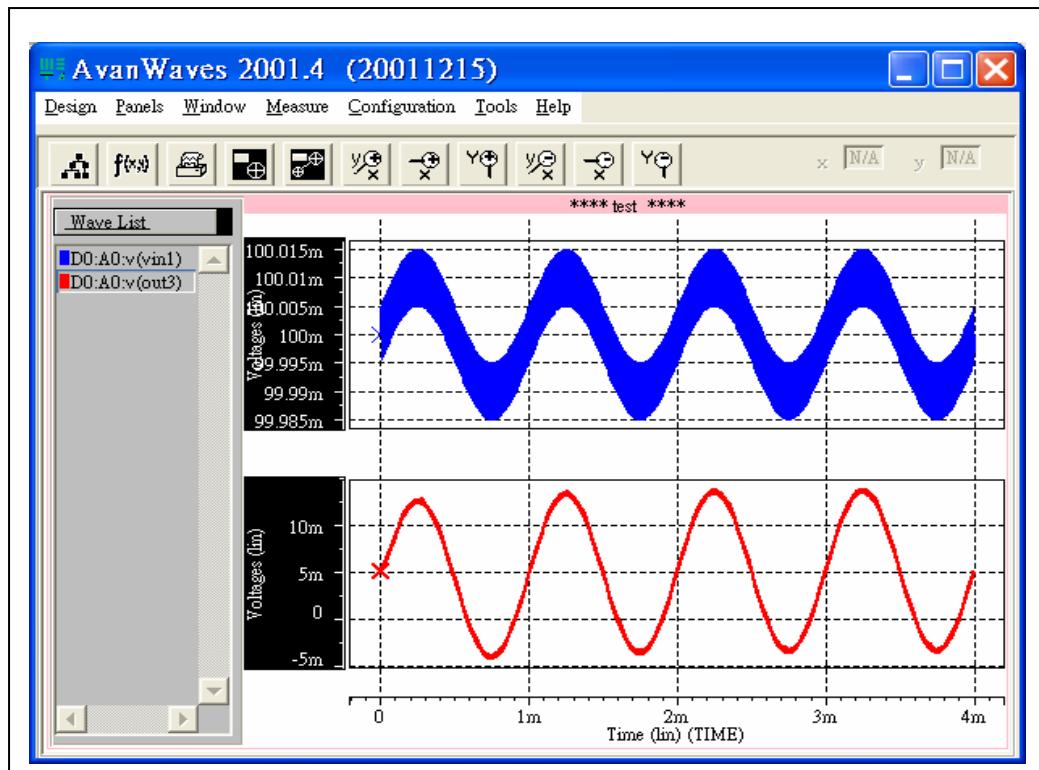

圖 4.17 輸入訊號為為頻率 1 k，振幅 700 uV 的且具有 0.5V 的 DC offset，輸出是經過設計的電生理記錄晶片，可得到  $700 \text{ uV} * 880 \text{ 倍} = 616 \text{ mV}$  的輸出電壓。根據電生理訊號大部分都是 10 uV 等級，但是根據資料顯示，電生理 spike action 訊號極大值在 500 uV。因此在模擬時，多預留點空間，灌進 700 uV 訊號測試。圖 4.18 為輸入合成訊號，假設電生理訊號頻率 1 k Hz，振幅 10 uV，加上神經元記錄電極產生的 100 mV DC-offset 和 100 k Hz 振幅為 5 uV 的雜訊。

圖 4.19，模擬各種溫度下對晶片的影響，模擬溫度範圍 5~85 度，由 5 度開始，每次增加 20 度，直到 85 度為止。由模擬結果得到，溫度變化對頻寬影響不大，主要的影響在於增益會隨溫度上升而下降。此影響，因為晶片有設計前放大器，故可以彌補因為溫度變化而產生的非理想效應。

表 4.1 為綜合比較表，列舉相關實驗室研究結果比較之，表 4.2 為相關實驗室提出之電生理記錄放大器之被動元件使用記錄，表 4.3 為預計規格表。

圖 4.10 前置放大器波德圖

圖 4.11 輸入訊號有 0.5V 的 DC offset 加上 700 uV 的 1 kHz 電生理訊號

圖 4.12 OTA波德圖

圖 4.13 高通濾波器的波德圖

圖 4.14 具放大功能之低通濾波器的波德圖

圖 4.15 帶通濾波器頻譜響應

圖 4.16 系統之 phase margin 約 85 度

圖 4.17 輸入訊號為為頻率 1 k，振幅 700 uV 的且具有 0.5V 的 DC offset

圖 4.18 為輸入合成訊號。（上）電生理訊號頻率 1 K，振幅 10 uV，加上神經元記錄電極產生的 100 mV DC-offset 和 100 kHz 振幅為 5 uV 的雜訊，（下）輸出結果

圖 4.19 溫度變化對電生理放大器的影響

### 4.3 效能比較

|                    | Pedram Mohseni<br>Michigan , USA[27]                                                        | Reid R.Harrison<br>Utah , USA[31]                                                                | Iyad Obeid<br>Duke , USA[13]         | Haidong Guo<br>Washington ,US A[12]                                                               | Proposed Design                                                       |

|--------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Technology process | AMI 1.5um<br>2p2m                                                                           | AMI 1.5um<br>2p2m                                                                                | AMI 0.5um<br>2p3m                    | TSMC 0.25um<br>1p5m                                                                               | TSMC 0.35um<br>2p4m                                                   |

| Voltage            | +1.5 V                                                                                      | +2.5 V                                                                                           | +2.5 V                               | +1.5 V                                                                                            | +1V                                                                   |

| Gain(dB)           | 39.5                                                                                        | 39.5                                                                                             | 47.4、53.4                            | 20、29、40、49.5、 60                                                                                 | 59dB ~ 88dB                                                           |

| BW (Hz)            | 26 ~ 6.5 k                                                                                  | 0.025 ~ 7.2 k                                                                                    | 211 ~ 7.5 k                          | 1 ~ 7 k                                                                                           | 161 ~ 5.9 k Hz                                                        |

| Roll off (HP/LP)   | -20 / -20                                                                                   | -20 / -20                                                                                        | -20 / -20                            | -- / 4 order                                                                                      | -20 / -20                                                             |

| OP architecture    | P-type OTA                                                                                  | P-type OTA                                                                                       | N-type OTA                           | P-type OTA                                                                                        | P-type OTA                                                            |

| Power/channel      | 133 uW                                                                                      | 80 uW                                                                                            | 950 uW                               | 520 uW                                                                                            | 54.5 uW                                                               |

| Die size(mm*mm)    | --                                                                                          | 2.2 * 2.2 (6 channel)                                                                            | 4.2*3.8 (16 channel)                 | 0.15*2 (1 channel)                                                                                | 1.906 * 1.58 (4 channel)                                              |

| Output offset      | --                                                                                          | --                                                                                               | 37mV                                 | --                                                                                                | 5.2mV                                                                 |

| P.M.               | 75.5                                                                                        | 52                                                                                               | --                                   | --                                                                                                | 85                                                                    |

| Implementation     | Single chip                                                                                 | Single chip                                                                                      | Discrete                             | Discrete                                                                                          | Single chip                                                           |

| Others             | 1. laser programmable 之 $R_g$ 提供 PMOS 當 pseudo-resistor 來降低 HP 的 pole<br>2. 有 power-line 雜訊 | 1. 利用 pseudo-resistor 來壓抑 HP pole<br>2. 使用電容值，來達到 40dB 的 gain (20P : 0.2P)<br>3. 有 power-line 雜訊 | 1. 被動元件 電容 C(100nF) 外接<br>2. 可調 gain | 1. 利用 DAC 加在 body 上，解決 input offset<br>2. 有設計 sample and hold<br>3. 有 power-line 雜訊<br>4. 可調 gain | 1. 利用 miller 效應來設計 HP filter<br>2. 將頻率補償方式運用設計 LPfilter<br>3. 可調 gain |

表 4.1 綜合比較表

|                     |                                          |                                        |                                  |                                        |                    |

|---------------------|------------------------------------------|----------------------------------------|----------------------------------|----------------------------------------|--------------------|

|                     | Pedram Mohseni<br>Michigan , USA<br>[27] | Reid R. Harrison<br>Utah , USA<br>[31] | Iyad Obeid<br>Duke , USA<br>[13] | Haidong Guo<br>Washington ,USA<br>[12] | Proposed<br>Design |

| Paper<br>publish    | 2002                                     | 2002                                   | 2003                             | 2004                                   | --                 |

| R1                  | 500                                      | --                                     | 7.33k                            | 1M                                     | 1M                 |

| R2                  | 50k                                      | --                                     | 1.008M                           | 1M                                     | 1M                 |

| R3                  | 30k                                      | --                                     | 20k                              | 1M                                     | --                 |

| R4                  | --                                       | --                                     | 800k                             | 1M                                     | --                 |

| C1                  | 4p                                       | 0.2p                                   | 100nF 外接                         | 16.1p                                  | 1p                 |

| C2                  | --                                       | 0.2p                                   | --                               | 13.8p                                  | 1p                 |

| C3                  | --                                       | 20p                                    | --                               | 39p                                    | 1p                 |

| C4                  | --                                       | 20p                                    | --                               | 5.7p                                   | --                 |

| R summary           | 80.5k+pseudo<br>resister                 | pseudo resister                        | 1.827M                           | 4M                                     | 2M                 |

| C summary           | 4p                                       | 40.4p                                  | 100nF 外接                         | 74.6p                                  | 3p                 |

| BW(Hz)              | 26 ~ 6.5 k                               | 0.025 ~ 7.2 k                          | 211 ~ 7.5 k                      | 1 ~ 7 k                                | 161 ~ 5.9 k        |

| Roll off<br>(HP/LP) | -20 dB / -20 dB                          | -20 dB / -20 dB                        | -20dB / -20dB                    | -- / 4-order                           | -20dB / -20dB      |

表 4.2 被動元件使用比較記錄

## 預計規格列表

|                      |                                  |

|----------------------|----------------------------------|

| Process Technology   | TSMC 0.35um 2p4m                 |

| Supply voltage       | $\pm 1$ Volt                     |

| channel              | 4                                |

| Gain                 | 59dB~88dB                        |

| Bandwidth            | 161~5.9 k Hz                     |

| UGF                  | 0.3~5.13 mega                    |

| Temperature range    | 5~85 度                           |

| Output offset        | 5.2mV                            |

| Phase margin         | 85 度                             |

| Roll off ( HP / LP ) | -20 dB / -20 dB                  |

| Power consumption    | 54.5 uW / channel                |

| ICMR (圖 5.1/圖 5.3)   | -0.14~0.12 / - infinite~infinite |

| Die size             | 1.906 mm * 1.58 mm               |

| Output loading       | 1G                               |

| Package              | SB40                             |

表 4.3 預計規格

# 第五章 結論

## 5.1 總結

在本論文中，首先以 CMOS 積體電路為基礎，發展出低功率電生理記錄放大器，在模擬上獲得成功。對於多頻道電生理訊號觀察，需要有體積小、功能簡單、容易操作、低電壓、低功率以便於長時間觀察神經元所產生的訊號，本研究基於上述原則而設計。半導體產業乃我國明星科技之一，CMOS 積體電路設計技術結合醫學應用，極可能成為下一波明星產業。本研究結合了 CMOS 積體電路設計並應用於醫學上，對這方面將來的發展有所助益。

## 5.2 未來研究方向

目前許多電生理記錄放大器因為神經元發出的訊號相對屬於低頻的訊號，因此有些研究發展被迫必須用外接電阻電容於晶片的方式來量測神經元所發出的訊號。透過本論文的研究，未來可以發展更 powerful 的 OP，提供 low power and high gain，搭配利用 Miller 效應，更可有效降低被動元件的值，對於固定尺寸的面積而言，可放下更多頻道的電路。

Low power 的設計，最直接的方法，就是使用低電壓，可是採用低電壓的狀況下設計，會遇到許多困難，比如 Gain、SR ...etc，因此這方面的問題，很值得去探討，找出更適合應用於電生理記錄放大器。

# 參考文獻

- [1] Phillip E. Allen and Douglas R. Holberg, CMOS Analog Circuit Design, second edition, Oxford University Press, Inc, 2002.

- [2] Behzad Razavi, Design of Analog CMOS Integrated Circuits, McGraw-Hill Education, 2004.

- [3] Charles Myers, Brandon Greenley, Daniel Thomas, Un-Ku Moon, "Continuous-time Filter Design Optimized for Reduced Die Area," *IEEE Transactions on Circuits and Systems —II: Express Briefs*, VOL. 51, NO. 3, MARCH 2004.

- [4] Christy L. Rogers and John G. Harris, "A Low-Power Analog Spike Detector for Extracellular Neural Recordings," *Circuits and Systems, ICECS 2004*.

- [5] C. Chestek, P. Samsukha, M. Tabib-Azar, R. Harrison, H. Chiel, S. Garverick, "Wireless Multi-channel Sensor for Neurodynamic Studies," *Proceedings of IEEE* 24-27 Oct. 2004.

- [6] Deborah S. Won, Iyad Obeid, James C. Morizio, Miguel A.L. Nicolelis, Patrick D. Wolf, "A Multichannel CMOS Analog Front End IC for Neural Recordings," *Proceedings of the second joint EMBS/BMES Conference* Houston, TX, USA. October 23-26, 2002.

- [7] E. Ibaragi, A. Hyogo, K. Sekine, "A 1-MHZ 7TH-ORDER CONTINUOUS-TIME LOWPASS FILTER USING VERY LOW DISTORTION CMOS OTAS," *Circuits and Systems, 2000. Proceedings. ISCAS 2000 Geneva*.

- [8] G.A. DeMichele, P. R. Troyk, "Integrated MultiChannel Wireless Biotelemetry System," *Engineering in Medicine and Biology Society, 2003.*

- [9] Roublik Gregorian, Introduction to CMOS OP-AMPS AND comparators, Wiley interscience, 1999.

- [10] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer, Analysis and design of analog integrated circuits, Fourth Edition, John Wiley & Sons, INC.

- [11] Hao Yu, Khalil Najafi, "Circuitry for A Wireless Microsystem for Neural Recording Microprobes," *Engineering in Medicine and Biology Society, 2001.*

- [12] Haidong Guo, Corbin L. Champion, David M. Rector and George S. La Rue, "A Low-Power Low-Noise Sensor IC," *Microelectronics and Electron Devices , 2004 IEEE Workshop.*

- [13] Iyad Obeid, James C. Morizio, Karen A. Moxon, Miguel A. L. Nicolelis, and Patrick D. Wolf, "Two Multichannel Integrated Circuits for Neural Recording and Signal Processing," *IEEE Transactions on Biomedical Engineering, VOL. 50, NO. 2, FEBRUARY 2003.*

- [14] Jin Ji, Kensall D. Wise, "An Implantable CMOS Analog Signal Processor for Multiplexed Microelectrode Recording Arrays," *Solid-State Sensor and Actuator Workshop 1990.*

- [15] Jan Crols and Michel Steyaert, "Switched-Opamp: An Approach to Realize Full CMOS Switched-Capacitor Circuits at Very Low Power Supply Voltages," *IEEE Journal of Solid-State Circuits, VOL. 29, NO. 8, AUGUST 1994.*

- [16] J. Morizio, D. Won, I. Obeid, C. Bossetti, M. Nicolelis, P. Wolf, "16-CHANNEL NEURAL PRE-CONDITIONING DEVICE," *Proceedings of the 1st International IEEE EMBS Conference on Neural Engineering* Capri Island, Italy. March 20-22,2003.

- [17] John G. Webster, Medical instrumentation application and design, Houghton Mifflin Company, 1978.

- [18] Khalil Najafi, and Kensall D. Wise, "An Implantable Multielectrode Array With On-Chip Signal Processing," *Solid-State Circuits, IEEE Journal of* Volume 21, Issue 6, Dec 1986.

- [19] Kyung Hwan Kim, Sung June Kim, "Noise Performance Design of CMOS Preamplifier for The Active Semiconductor Neural Probe," *Biomedical Engineering , IEEE Transactions on* Volume 47, Issue 8, Aug. 2000.

- [20] Maher E. Rizkalla, Mark M. Budnik, Mohamed El-Sharkawy, Akhouri s.C.Sinha, and Harry Gundrum, "Minimizing Cross-Talk for Multi-Channels VLSI Analog Chips," *Circuits and Systems, 2001. MWSCAS 2001.*

- [21] Maxim Pribytko, Patrick Quinn, "A CMOS Single-Ended OTA With High CMRR," *Solid-State Circuits Conference, 2003.*

- [22] Nathan M. Neihart and Reid R. Harrison, "A Low-Power FM Transmitter for Use in Neural Recording Applications," *Engineering in Medicine and Biology Society, 2004.*

- [23] Nathan M. Neihart, and Reid R. Harrison, "Micropower Circuits for Bidirectional Wireless Telemetry in Neural Recording Applications," *IEEE Transctions on Biomedical Engineering, VOL. 52, NO. 11, NOVEMBER 2005.*

- [24] PAUL R.GRAY, ROBERT G. MEYER, "MOS Operational Amplifier Design – A Tutorial Overview," *IEEE Journal of Solid-State Circuits*, VOL. SC-17, NO. 6, JANUARY 1982.

- [25] Pedram Mohseni and Khalil Najafi, "A Low Power Fully Integrated Bandpass Operational Amplifier For Biomedical Neural Recording Applications," *EMBS/BMES Conference, 2002*.

- [26] Pedram Mohseni and Khalil Najafi, "Wireless Multichannel biopotential recording using an integrated FM telemetry circuit," *Engineering in Medicine and Biology Society, 2004*.

- [27] Pedram Mohseni, Khalil Najafi, "A Fully Integrated Neural Recording Amplifier With DC Input Stabilization," *Biomedical Engineering, IEEE Transactions on* Volume 51, Issue 5, May 2004.

- [28] Pedram Mohseni, Khalil Najafi, Steven J. Eliades, and Xiaoqin Wang, "Wireless Multichannel Biopotential Recording Using an Integrated FM Telemetry Circuit," *Neural Systems and Rehabilitation Engineering, IEEE Transactions on* Volume 13, Issue 3, Sept. 2005.

- [29] Pedram Mohseni, Khalil Najafi, "A Battery-Powered 8-Channel Wireless FM IC for Biopotential Recording Applications," *ISSCC 2005 / Session 30 / Displays and Biosensors / 30.5*

- [30] Rinaldo Castello, Federico Montecchi, Francesco Rezzi, and Andrea Baschirotto, "Low-voltage analog filters," *Circuits and Systems I: Fundamental Theory and Applications, IEEE Transactions on* Volume 42, Issue 11, Nov. 1995.

- [31] Reid R. Harrison, "A Low-Power Low-Noise CMOS Amplifier for Neural Recording Applications," *Circuits and Systems, 2002. ISCAS 2002. IEEE International Symposium on* Volume 5, 26-29 May 2002.

- [32] Reid R. Harrison, and Cameron Charles, "A Low-Power Low-Noise CMOS Amplifier for Neural Recording Applications," *IEEE Journal of Solid-State Circuits*, VOL. 38, NO. 6, JUNE 2003.

- [33] Reid R. Harrison, "A Low-Power Integrated Circuit for Adaptive Detection of Action Potentials in Noisy Signals," *Proceedings of the 25<sup>th</sup> Annual International Conference of the IEEE EMBS* Cancun, Mexico September 17-21, 2003.

- [34] Reid R. Harrison, Gopal Santhanam, and Krishna V. Shenoy, "Local Field Potential Measurement With Low-Power Analog Integrated Circuit," *Engineering in Medicine and Biology Society, 2004*.

- [35] Reid Harrison, Paul Watkins, Ryan Kier, Robert Lovejoy, Daniel Black, Richard Normann, Florian Solzbacher, "A Low-Power Integrated Circuit for a Wireless 100-Electrode Neural Recording System," *ISSCC 2006 / Session 30 / Silicon for Biology / 30.2*

- [36] Roy H. Olsson III, Derek L. Buhl, Anton M. Sirota, Gyorgy Buzsaki, Kensall D. Wise, "Band-Tunable and Multiplexed Integrated Circuits for Simultaneous Recording and Stimulation With Microelectrode Arrays," *IEEE Transactions on Biomedical Engineering*, VOL. 52, NO. 7, JULY 2005.

- [37] Roy H. Olsson III, and Kensall D. Wise, "A Three-Dimensional Neural Recording Microsystem With Implantable Data Compression Circuitry," *IEEE Journal of Solid-State Circuits*, VOL. 40, NO. 12, DECEMBER 2005.

- [38] Rolf Schaumann, van valkenburg, Design if analog filter, Oxford University Press, Inc, 2001

- [39] Tayfun Akin and Khalil Najafi, "A Telemetrically Powered and Controlled Implantable Neural Recording System With CMOS Interface Circuitry," *Electrotechnical Conference, 1994*.

- [40] Tayfun Akin, Khalil Najafi, and R.M. Bradley, "An Implantable Multichannel Digital Neural Recording System For A Micromachined Sieve Electrode," *Solid-State Sensors and Actuators, 1995*.

- [41] Tayfun Akin, Khalil Najafi, Robert M. Bradley, "A Wireless Implantable Multichannel Digital Neural Recording System for a Micromachined Sieve Electrode," *IEEE Journal of Solid-State Circuits, VOL. 33, NO. 1, JANUARY 1998*.

- [42] T. Horiuchi, T. Swindell, D. Sander, and P. Abshire, "A Low-Power CMOS Neural Amplifier With Amplitude Measurement for Spike Sorting," *Circuits and Systems, 2004*.

- [43] W. Aloisi, G. Giustolisi, and G. Palumbo, "Exploiting The High-Frequency Performance of Low-Voltage Low-Power SC Filters," *Circuits and Systems II: Express Briefs, IEEE Transactions on Volume 51, Issue 2, Feb 2004*.

- [44] Xiaohua Fan, Chinmaya Mishra, Edgar Sanchez-Sinencio, "Single Miller Capacitor Frequency Compensation Technique for Low-Power Multistage Amplifiers," *IEEE Journal of Solid-State Circuits, VOL. 40, NO. 3, MARCH 2005*.

- [45] Xin Zhang, James C. Daly, Yong Cao, "32-Channel Full Customized CMOS Biosensor Chip for Extracellular Neural Signal Recording," *Neural Engineering, 2005*.

# 附錄

## 佈局驗證結果說明

### A. DRC

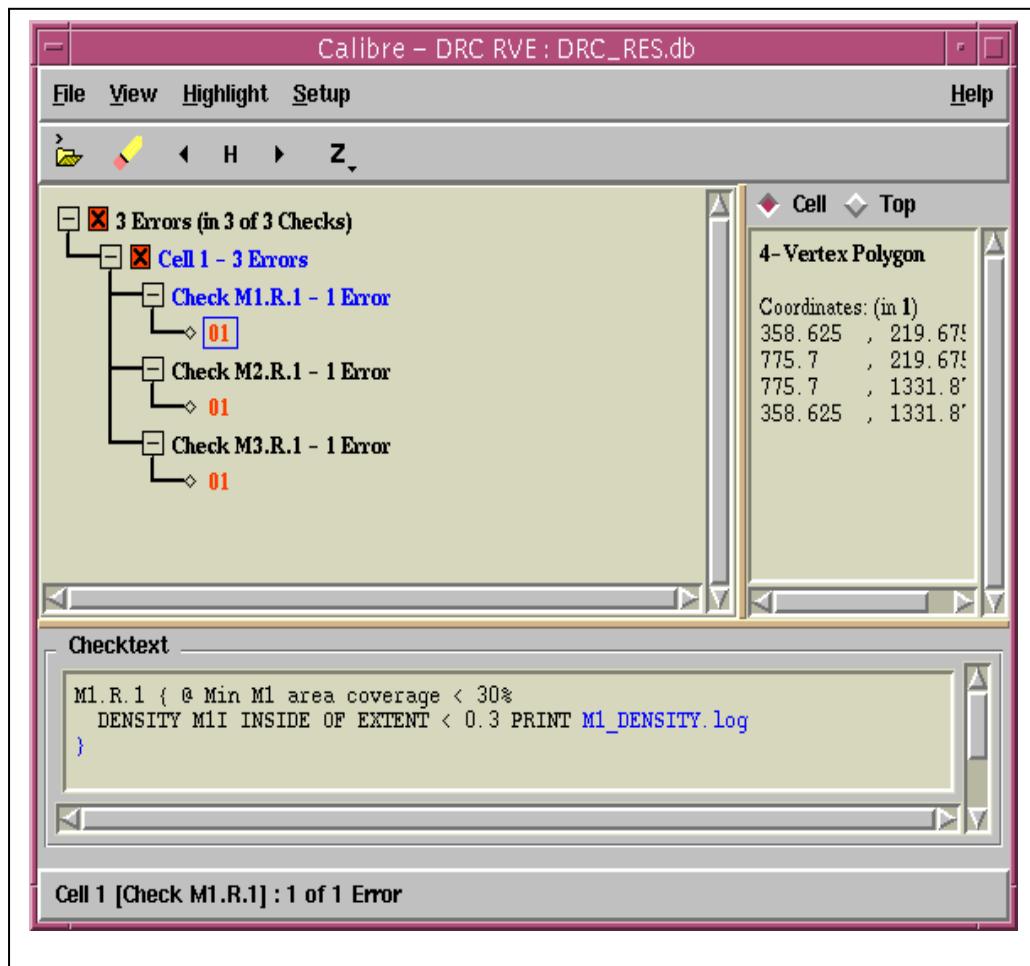

DRC error 為 metal 1、metal 2、metal 3 density < 30% , 此錯誤可忽略。

B. LVS

## LVS 驗證無誤

## C. 晶片腳位分佈與訊號說明

| Pin No. | 訊 號 名<br>稱 | I/O<br>direction | 訊 號 說<br>明     |

|---------|------------|------------------|----------------|

| 1       | Vp12       | I                | 前放大器輸入         |

| 2       | Vp11       | I                | 前放大器輸入         |

| 3       | Vp1out     | O                | 前放大器輸出         |

| 4       | In1p       | I/O              | 測試節點           |

| 5       | In1h       | I/O              | 測試節點           |

| 6       | Vss        | I                | Core 電源        |

| 7       | Vouth      | O                | 測試節點           |

| 8       | voutp      | O                | 測試節點           |

| 9       | vout       | O                | 最後輸出_ch1       |

| 10      | vb         | I/O              | 偏壓點            |

| 11      | vlp        | I/O              | 測試節點           |

| 12      | vss        | I                | Core 電源        |

| 13      | Vb_ref     | I/O              | 偏壓點            |

| 14      | Vss_ref    | O                | Core 電源        |

| 15      | vsse       | I                | ESD 電源         |

| 16      | Vout_ch2   | O                | 最後輸出_ch2       |

| 17      | Vout_ch3   | O                | 最後輸出_ch3       |

| 18      | Vout_ch4   | O                | 最後輸出_ch4       |

| 19      | vdde       | I                | ESD 電源         |

| 20      | vdde       | I                | ESD 電源         |

| 21      | Voutp_ch4  | O                | 前放大器輸出_ch4     |

| 22      | Voutp_ch3  | O                | 前放大器輸出_ch3     |

| 23      | Voutp_ch2  | O                | 前放大器輸出_ch2     |

| 24      | Vin2_ref   | I                | 共同參考輸入_ch2.3.4 |

| 25      | Vin1_ch4   | I                | 輸入_ch4         |

| 26      | vdde       | I                | ESD 電源         |

| 27      | Vdd_ref    | I                | Core 電源        |

| 28      | Vin1_ch3   | I                | 輸入_ch3         |

| 29      | Vin1_ch2   | I                | 輸入_ch2         |

| 30      | Gnd_ref    | I/O              | 測試節點           |

| 31      | gndh       | I/O              | 測試節點           |

| 32      | gndp       | I/O              | 測試節點           |

| 33      | gnd        | I/O              | 測試節點           |

| 34      | vdd        | I                | Core 電源        |

| 35      | vdd        | I                | Core 電源        |

| 36      | Vin1       | I                | 輸入_ch1         |

| 37      | Vin2       | I                | 輸入_ch1         |

| 38      | Vp21       | I                | 前放大器輸入_ch1     |

| 39      | Vp22       | I                | 前放大器輸入_ch1     |

| 40      | Vp2out     | O                | 前放大器輸出_ch1     |

# D. Tapeout Review Form

Tapeout review form 的用意在提醒設計者在設計、模擬、佈局、佈局驗證及 tapeout 時具備設計理念及了解應注意事項, 希望能藉此提昇晶片設計的成功率及達到完整的學習效果。因此, 請指導教授及設計者確實檢查該晶片設計過程是否已注意本表格之要求, 並在填寫確定後簽名, 若審查時發現設計內容與 Tapeout Review Form 之填寫不符, 很可能遭取消該晶片下線製作資格。可參考本表後所附範例確實填寫。

## 1 電路概述

1-1. 電路名稱: 開發出應用於電生理記錄之低功率多頻道訊號處理晶片

1-2. 製程名稱: TSMC .35 2P4M

1-3. 工作電壓: +1V

1-4. 工作頻率: 1K

1-5. 功率消耗: 54.5uW

1-6. 此電路架構於貴實驗室是否第一次設計? 是(接 2-1) 是

## 2 電路模擬考量

2-1. 已用 SS, SF, TT, FS, FF 中哪些不同狀態之 spice model 模擬? 是

2-2. 已模擬過電壓變動 +/-10% 中哪些情況對電路工作之影響? 是

2-3. 如何考量溫度變異之影響? 是

2-4. 如何考量電阻、電容製程變異之影響? 是

2-5. 模擬時是否加入 IO PAD、Bonding wire 的效應及考量測試儀器之負

載等影響? 是. 是否作 LPE 及 post layout simulation? 是

是 使用的軟體為 hspice & laker

## 3 Power Line 佈局考量

3-1. Power Line 畫多寬? 4.6um

3-2. 是否考量 power line current density? 是

3-3. 是否考量 Metal Line 之寄生電阻、電容? 是

## 4 DRC, LVS

4-1. 是否有作 whole chip 的 DRC 及 LVS? 是

4-2. 除了 PAD 上 DRC 的錯誤之外, 內部電路及與 PAD 連接的線路是否有錯? 是 錯誤原因為何? M1、M2、M3 density < 30%

4-3. 在作 LVS 的過程中, PIN 腳及元件是否 match? 是

4-4. 檢查 PAD 與 PAD 間是否有移位、短路或斷路的現象? 否

## 5 類比-混合訊號電路佈局考量(類比-混合訊號電路設計者填寫)

### 5-1 佈局對稱性及一致性考量

5-1-1 OP(Comparator) Input Stage是否對稱? 是

5-1-2 OP(Comparator) Input Stage是否對稱? 是

5-1-3 佈局中對稱元件是否使用dummy cell技巧? 是

5-1-4 對稱電容是否採用同心圓佈局? 是

5-1-5 對稱單位電容四周是否切成 45 度斜角? 是

5-1-6 對稱電容的單位面積是否一致? 是

單位電容面積多大? 11.1 um x 11.1 um

單位電容值多大? 0.05 pF

5-1-7 電阻採用哪一材質製作? N+ Diffusion

單位電阻值多大? 1K

### 5-2 電路雜訊佈局考量

5-2-1 是否將Analog及Digital的power line分開? 否

(目前沒有加入數位的設計)

5-2-2 Analog area是否用guard ring隔絕? 是

5-2-3 Digital area是否用guard ring隔絕? 否 (目前沒有加入數位的設計)

5-2-4 對於 sensitive line 是否 使用 shield 的技巧? 否

5-2-5 Analog guard ring及shield是否接至乾淨之電位? 否

5-2-6 是否將 sensitive line 儘量縮短及避免跨越 noise(clock)line? 是

5-2-7 電容的上下極板是否接對? 是

5-3 DRC驗證過程中，部分錯誤若為特殊考量，請說明 是

M1 & M2 & M3 density <30% 此錯誤可以忽略

5-4 LVS驗證過程中，電感電容或其他特殊元件的比對是否做過處理，

請說明 是

加入DUMMY CELL 減少製程上的飄移與shadow 現象

5-5 量測方式為 on wafer, on PCB or in package? 並說明量測時應該注意事項與量測地點

-

- 6 PAD Replacement 考量(使用 TSMC I/O PAD 設計者填寫)

- 6-1 已於申請表勾選申請使用 TSMC I/O PAD

- 6-2 個人設計的Cell名稱(cell-name)未與TSMC所提供之任一Pad Cell

名稱相同 是

- 6-3 採用Create Instance方式加入I/O Pad，未用Copy或Flatten破壞

Instance的結構 是

- 6-4 由IC Core部份拉線到Pad只拉到最邊緣部分，未過於覆蓋Pad 是

- 7 其他考量

- 甲、是否考量測試時的輸出量測點? 是

- 乙、是否考量電路之可修改性(如用 laser cut 設備) \_\_\_\_\_

設計者簽名: 謝宗哲 指導教授簽名: 林進燈 教授