# 國立交通大學

# 電信工程學系碩士班

### 碩士論文

被動分合波器與主動混頻器之整合及覆晶封裝之毫米波驅動放大器設計與實作

THE PERSON NAMED IN

Several Active Mixers with an Integrated Passive Balun and the Driving Amplifier for Flip Chip in Millimeter Wave

研究生:張家宏

指導教授:孟慶宗教授

中華民國九十五年六月

# 被動分合波器與主動混頻器之整合及覆晶封裝 之毫米波趨動放大器設計與實作

Several Active Mixers with an Integrated Passive Balun and the Driving Amplifier for Flip Chip in Millimeter Wave

研究生:張家宏 Student: Chia Hung Chang

指導教授:孟慶宗 博士 Advisor: Dr. Chin Chun Meng

國立交通大學

電信工程學系碩士班

碩士論文

A Thesis

Submitted to Department of Communication Engineering

College of Electric Engineering and Computer Science

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of

Master of Science

In

**Communication Engineering**

June 2006 Hsinchu, Taiwan, Republic of China

中華民國九十五年六月

### 中文摘要

本篇論文主要研究在射頻積體電路中被動分合波器與主動混頻器 整合。最後將介紹在毫米波電路中的趨動放大器,操作頻率在 60GHz, 並且採用傳輸線與共平面波導的方式來實現之。

在被動電路分合波器中,利用了 TSMC 0.35 um COMS 製程製作 Rat-Race 與 Marchand balun,因為在 IC 製程上被動電路往往佔據了很大的面積,所以更進一步將上述兩者分合波器微小化,以利於積體電路的實現。而混頻器部分利用 TSMC SiGe 0.35 um BICMOS 與 TSMC 0.13 um CMOS 製程製作 Cherry-Hooper 技術之微混頻器,在高頻使用 Cherry-Hooper 技術之混頻器可達到寬頻的效果。此外,並將被動電路部分整合進混頻器裡。另外在毫米波頻段利用 WIN 0.15 um PHEMT 製程設計趨動放大器,並且將晶片進行覆晶封裝,進而比較 flip-chip 之前後的差別。

### **Abstract**

In this thesis, we focus on the combine of the passive balun and active mixer in radio frequency integrated circuit. In the last, we will present the driving amplifier in millimeter wave circuit. The operating frequency is on 60GHz and using the micro-strip and coplanar strip line to implement.

In passive balun, we implement the Rat-Race and Marchand balun by using the TSMC 0.35 um CMOS technology process in circuit design. Because the passive circuit always occupy much size in the integrated circuit. So we miniaturized the Rat-Race and Marchand balun in design. And we implement the micro-mixer in Cherry-Hooper technique by using the TSMC SiGe 0.35 um BICMOS and TSMC 0.13 um CMOS technology process, respectively. The Cherry-Hooper mixer shows the wide bandwidth in high frequency. Besides, we combine the passive balun in mixer to Rat-Race and Marchand balun mixer. On the other hand, we design the driving amplifier in millimeter wave by using the WIN 0.15 um PHEMT process. And flip chip this amplifier to compare the difference in performance.

研究所兩年的時間,其實說長不長,說短也不算短,很感謝<u>孟慶宗</u>老師的指導,讓我成長許多,並克服了種種困難。並感謝<u>詹益仁</u>教授、 <u>郭仁財</u>教授與<u>鍾世忠</u>教授在百忙之餘能參加學生的口試並給予實貴的建 議,使我受益良多。在研究所期間,特別感謝<u>聖哲</u>的指導與量測方面的 幫忙,使得資料更加完善。而 PHEMT TEAM 在<u>珍儀</u>的帶領下與智凱的 指導再加上<u>約廷</u>這個生力軍的加入,得以將科專的計畫完成。

接下來感謝實驗室的大家。宗翰、聖哲、珍儀、宏儒、澤宏、宇文與智凱學長姐的指導讓我對於研究有更多的了解。同時要感謝實驗室的同學英杰與權輿的關懷以及課業上的幫忙,讓我這兩年的生活充實且愉快。此外,多謝學弟們 勝文、柏誼、冠璋與約廷的支持和幫忙,讓我這兩年的研究所生活充滿回憶。

特別感謝我的父、母與弟弟在求學過程,給我最大的支持及關懷。 讓我能夠堅持下去並完成學業。最後,僅把此論文的榮耀獻給我的家人 與以及身邊所有關懷我的朋友們。

### 目錄

| 摘要(中文)                                      | i    |

|---------------------------------------------|------|

| 摘要(英文)                                      | ii   |

| 致謝                                          | iii  |

| 目錄                                          | iv   |

| 圖目錄                                         | vii  |

| 表目錄                                         | xiii |

| 第一章 導論                                      | 1    |

| 1.1 研究動機                                    | 2    |

| 1.2 論文組織                                    | 2    |

| 第二章 被動電路分合波器之分析與設計                          | 3    |

| 2.1 前言                                      | 4    |

| 2.2 Marchand balun 理論分析與實作                  | 5    |

| 2.2.1 傳統式的 Marchand balun                   | 5    |

| 2.2.2 Marchand balun 理論分析                   | 6    |

| 2.2.3 變壓器型式 Marchand balun 實作與量測            | 22   |

| 2.2.4 微小化變壓器型式 Marchand balun 實作與量測         | 27   |

| 2.3 Rat race 理論分析與實作                        | 30   |

| 2.3.1 傳統式的 Rat race 理論分析                    | 30   |

| 2.3.2 相位反轉(Phase Inverter)之 Rat race 理論分析   | 35   |

| 2.3.3 交指型(Inter-digital)與相位反轉 Rat race 理論分析 | 38   |

| 2.3.4 交指型相位反轉之分合波器實作與量測                     | 41   |

| 2.3.5 變壓器型式相位反轉之分合波器實作與量測                   | 45   |

| 2.3.6 微小化變壓器型式相位反轉分合波器實作與量測                 | 48   |

| 第三章 Marchand balun 之混頻器設計                   | 51   |

| 3.1 前言                                      | 52   |

| 3.2 Marchand balun 之混頻器設計與實現                | 52   |

| 3.2.1 本地振盪源輸入極                              | 53   |

| 3.2.2 射頻輸入極                                 | 54   |

| 3.2.3 輸出緩衝極                                 | 55   |

| 3.2.4 晶片量測結果                                | 57   |

| 3.2.5 結果與討論                                 | 62   |

| 3.3 | 微小化 Marchand balun 之混頻器設計與實現           | 63  |

|-----|----------------------------------------|-----|

|     | 3.3.1 本地振盪源輸入極                         | 64  |

|     | 3.3.2 射頻輸入極                            | 65  |

|     | 3.3.3 輸出緩衝極                            | 65  |

|     | 3.3.4 晶片量測結果                           | 65  |

|     | 3.3.5 結果與討論                            | 70  |

| 第四章 | Rat race 之混頻器設計                        | 71  |

| 4.1 | 前言                                     | 72  |

| 4.2 | Transformer Rat race 之混頻器設計與實現         | 72  |

|     | 4.2.1 本地振盪源輸入極                         | 73  |

|     | 4.2.2 射頻輸入極                            | 74  |

|     | 4.2.3 輸出緩衝極                            | 74  |

|     | 4.2.4 晶片量測結果                           | 74  |

|     | 4.2.5 結果與討論                            | 79  |

| 4.3 | 微小化 Transformer Rat race 之混頻器設計與實現     | 80  |

|     | 4.3.1 本地振盪源輸入極                         | 81  |

|     | 4.3.2 射頻輸入極                            | 81  |

|     | 4.3.3 輸出緩衝極                            | 81  |

|     | 4.3.4 晶片量測結果                           | 82  |

|     | 4.3.5 結果與討論                            | 88  |

| 4.4 | 利用 Marchand balun 和交趾型相位轉換分合波器之降頻器設計與實 |     |

|     | 4.4.1 本地振盪源輸入極     4.4.2 射頻輸入極         | 90  |

|     | 4.4.2 射頻輸入極                            | 90  |

|     | 4.4.3 輸出緩衝極                            | 90  |

|     | 4.4.4 模擬結果                             | 91  |

|     | 4.4.5 結果與討論                            | 97  |

| 第五章 | 毫米波覆晶封裝之驅動放大器                          | 98  |

| 5.1 | 前言                                     | 99  |

| 5.2 | 基本放大器設計原理                              | 100 |

|     | 5.2.1 波源和負載之間的阻抗匹配                     | 100 |

|     | 5.2.2 穩定度                              | 103 |

| 5.3 | 覆晶封裝之 30GHz 微帶線型式驅動放大器                 | 105 |

|     | 5.3.1 架構簡介                             | 105 |

|     | 5.3.2 晶片量測結果                           | 106 |

|     | 5.3.3 覆晶封裝後(flip chip)量測結果比較           | 107 |

|     | 5.3.4 結果與討論                            | 110 |

| 5.4 | 覆晶封裝之 60GHz 微帶線型式驅動放大器                 | 111 |

|     | 5.4.1 架構簡介                             | 111 |

| 5.4.2 晶片量測結果                 | 112 |

|------------------------------|-----|

| 5.4.3 覆晶封裝後(flip chip)量測結果比較 | 113 |

| 5.4.4 結果與討論                  | 116 |

| 5.5 覆晶封裝之 60GHz 共平面波導驅動放大器   | 117 |

| 5.5.1 架構簡介                   | 117 |

| 5.5.2 晶片量測結果                 | 118 |

| 5.5.3 覆晶封裝後(flip chip)量測結果比較 | 119 |

| 5.5.4 結果與討論                  | 122 |

| 第六章 結論                       |     |

| <b>冬</b> 考文獻                 | 125 |

## 圖目錄

| 圖 | 2.1  | 傳統式的分合波器5                    |

|---|------|------------------------------|

| 圖 | 2.2  | 改良式 Marchand balun           |

| 圖 | 2.3  | Type I~IV Marchand balun7    |

| 圖 | 2.4  | Marchand balun 基本架構圖         |

| 圖 | 2.5  | Type I S11分析                 |

| 圖 | 2.6  | Type I S21分析                 |

| 昌 | 2.7  | Type I S31分析10               |

| 昌 | 2.8  | Type I S23分析10               |

| 昌 | 2.9  | Type I S32分析10               |

| 圖 | 2.10 | Type I S22分析                 |

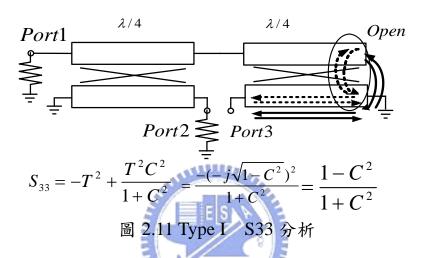

| 圖 | 2.11 | Type I S33分析                 |

| 圖 | 2.12 | Type I Marchand balun 示意圖11  |

| 圖 | 2.13 | Type I 訊號從埠1進入12             |

| 圖 | 2.14 | Type I 訊號從埠 2 進入12           |

| 圖 | 2.15 | Type I 訊號從埠3進入13             |

| 圖 | 2.16 | Type IV Marchand balun 示意圖14 |

| 圖 | 2.17 | Type IV 訊號從埠1進入14            |

| 圖 | 2.18 | Type IV 訊號從埠2進入15            |

| 圖 | 2.19 | Type IV 訊號從埠3進入15            |

| 昌 | 2.20 | Type V 分合波器示意圖17             |

| 昌 | 2.21 | Type V 訊號從埠1進入17             |

| 置 | 2.22 | Type V 訊號從埠2進入18             |

| 圖 | 2.23 | Type V 訊號從埠3進入                                    | .18 |

|---|------|---------------------------------------------------|-----|

| 置 | 2.24 | Type VI 分合波器示意圖                                   | .20 |

| 置 | 2.25 | Type VI 訊號從埠1進入                                   | .20 |

| 置 | 2.26 | Type VI 訊號從埠2進入                                   | .21 |

| 置 | 2.27 | Type VI訊號從埠3進入                                    | 21  |

| 置 | 2.28 | Transformer type Marchand balun                   | .23 |

| 置 | 2.29 | 輸入返回損耗 (S11)                                      | .24 |

| 置 | 2.30 | Magnitude (S21 & S31)                             | .24 |

| 邑 | 2.31 | Phase difference (S21 & S31)                      | .25 |

| 置 | 2.32 | Transformer Marchand balun die photo              | 25  |

| 置 | 2.33 | Miniaturized Transformer type Marchand balun      | 27  |

| 邑 | 2.34 | S參數                                               |     |

| 邑 | 2.35 | Phase difference (S21 & S31)                      | 28  |

| 邑 | 2.36 | Miniaturized Transformer Marchand balun die photo |     |

| 邑 | 2.37 | 傳統式Rat race                                       | .31 |

| 邑 | 2.38 | Rat race分合波器示意圖                                   |     |

| 邑 | 2.39 | 訊號埠3有單位振幅輸入時奇、偶模分解電路                              | 31  |

| 邑 | 2.40 | Rat race奇、偶模分解電路(埠3)                              | .32 |

| 置 | 2.41 | 訊號埠1有單位振幅輸入時奇、偶模分解電路                              | .33 |

| 置 | 2.42 | Rat race奇、偶模分解電路(埠1)                              | .34 |

| 置 | 2.43 | 相位返轉(phase inverter)示意圖                           | 35  |

| 置 | 2.44 | 奇、偶模之phase inverter分析示意圖                          | 36  |

| 置 | 2.45 | Phase Inverter Rat-race (a)偶模(b)奇模 等效半電路          | .36 |

| 圖 | 2.46 | 互易性雙埠網路T型等效電路                                     | .38 |

| 圖 | 2.47 | $\beta l < \frac{\pi}{2}$ 時傳輸線等效電路                | 39  |

| 置                                              | 2.48                                                                 | Step impedance等效電路示意圖                                                                                                                                                                                        | 40                                     |

|------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 邑                                              | 2.49                                                                 | Inter-digital and phase inverter Rat race                                                                                                                                                                    | 41                                     |

| 邑                                              | 2.50                                                                 | Magnitude (S11 & S21 & S31 & S41)                                                                                                                                                                            | 42                                     |

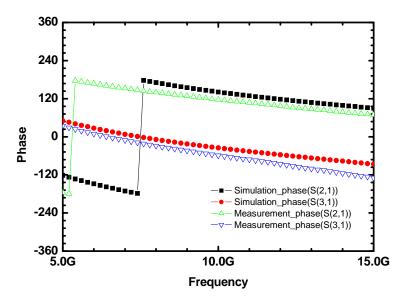

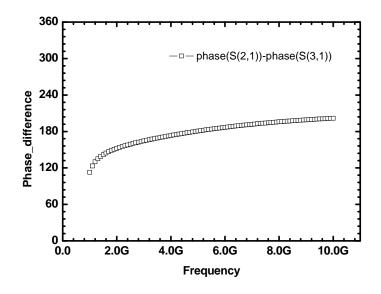

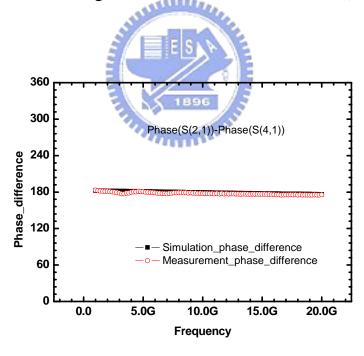

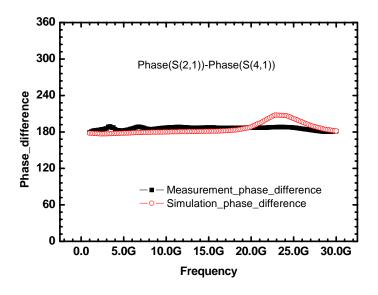

| 置                                              | 2.51                                                                 | Phase difference (S21 & S41)                                                                                                                                                                                 | 42                                     |

| 置                                              | 2.52                                                                 | Inter-digital phase inverter rat race die photo                                                                                                                                                              | 43                                     |

| 邑                                              | 2.53                                                                 | Transformer type phase inverter rat race                                                                                                                                                                     | 45                                     |

| 邑                                              | 2.54                                                                 | Magnitude (S11 & S21 & S31 & S41)                                                                                                                                                                            | 45                                     |

| 邑                                              | 2.55                                                                 | Phase difference (S21 & S41)                                                                                                                                                                                 | 46                                     |

| 邑                                              | 2.56                                                                 | Transformer phase inverter rat race die photo                                                                                                                                                                | 46                                     |

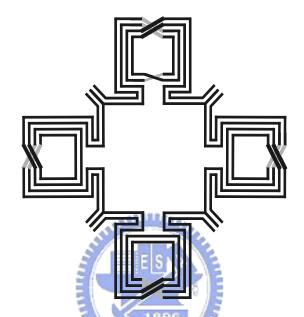

| 邑                                              | 2.57                                                                 | Miniaturized transformer type phase inverter rat race                                                                                                                                                        | 48                                     |

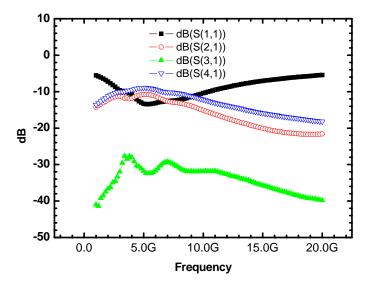

| 邑                                              | 2.58                                                                 | Magnitude (S11 & S21 & S31 & S41)                                                                                                                                                                            |                                        |

| 置                                              | 2.59                                                                 | Phase difference (S21 & S41)                                                                                                                                                                                 | 49                                     |

| 置                                              | 2.60                                                                 | Miniaturized transformer phase inverter rat race die photo                                                                                                                                                   | 49                                     |

|                                                |                                                                      |                                                                                                                                                                                                              |                                        |

| 昌                                              | 3.1                                                                  | Marchand balun 與 Cherry Hooper 技術降頻器電路                                                                                                                                                                       |                                        |

|                                                | 3.1                                                                  | 7 1836                                                                                                                                                                                                       |                                        |

| 昌                                              |                                                                      | Marchand balun 與 Cherry Hooper 技術降頻器電路                                                                                                                                                                       | 54                                     |

| 圖圖                                             | 3.2                                                                  | Transformer Marchand balun                                                                                                                                                                                   | 54                                     |

| <b>圖</b>                                       | <ul><li>3.2</li><li>3.3</li><li>3.4</li></ul>                        | Transformer Marchand balun微混頻器架構示意圖                                                                                                                                                                          | 54<br>55                               |

| <b>圖 圖 圖</b>                                   | <ul><li>3.2</li><li>3.3</li><li>3.4</li><li>3.5</li></ul>            | Transformer Marchand balun微混頻器架構示意圖                                                                                                                                                                          | 54<br>55<br>55                         |

|                                                | 3.2<br>3.3<br>3.4<br>3.5<br>3.6                                      | Transformer Marchand balun微混頻器架構示意圖                                                                                                                                                                          | 54<br>55<br>55<br>56                   |

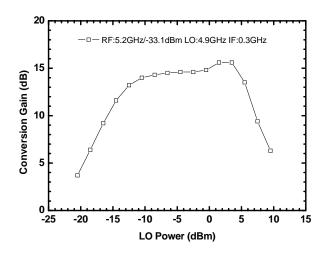

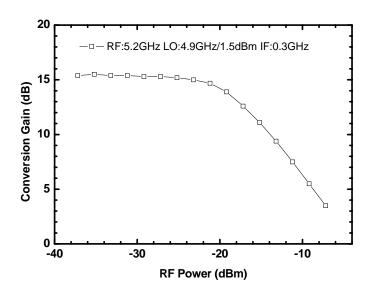

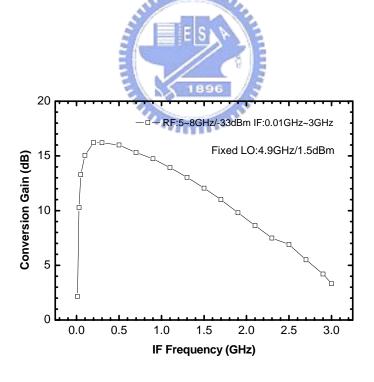

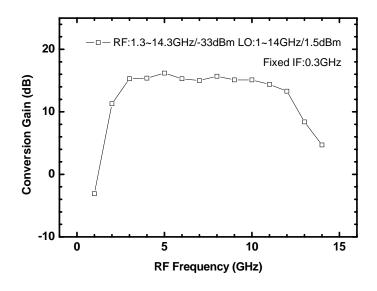

|                                                | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                               | Transformer Marchand balun. 微混頻器架構示意圖 Cherry Hooper technique employed in the micromixer 轉導與轉阻放大器小信號分析 轉換增益 VS. LO Power                                                                                     | 54<br>55<br>56<br>57                   |

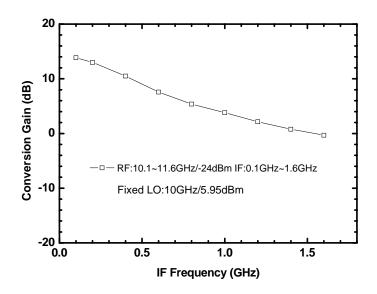

|                                                | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                        | Transformer Marchand balun. 微混頻器架構示意圖. Cherry Hooper technique employed in the micromixer. 轉導與轉阻放大器小信號分析. 轉換增益 VS. LO Power. 轉換增益 VS. RF Power (P1dB).                                                       | 54<br>55<br>56<br>57<br>57             |

|                                                | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                 | Transformer Marchand balun. 微混頻器架構示意圖 Cherry Hooper technique employed in the micromixer. 轉導與轉阻放大器小信號分析. 轉換增益 VS. LO Power. 轉換增益 VS. RF Power (P1dB). 轉換增益 VS. IF Frequency.                                 | 54<br>55<br>56<br>57<br>57             |

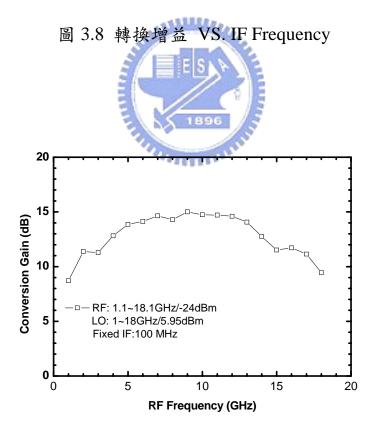

| <u>I</u> II I | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10         | Transformer Marchand balun. 微混頻器架構示意圖. Cherry Hooper technique employed in the micromixer. 轉導與轉阻放大器小信號分析. 轉換增益 VS. LO Power. 轉換增益 VS. RF Power (P1dB). 轉換增益 VS. IF Frequency. 轉換增益 VS. RF Frequency.         | 54<br>55<br>56<br>57<br>57<br>58<br>59 |

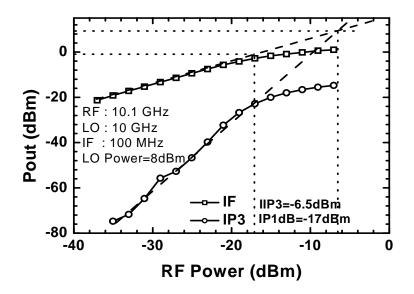

| <u>I</u> II I | 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11 | Transformer Marchand balun. 微混頻器架構示意圖.  Cherry Hooper technique employed in the micromixer. 轉導與轉阻放大器小信號分析. 轉換增益 VS. LO Power. 轉換增益 VS. RF Power (P1dB).  轉換增益 VS. IF Frequency.  轉換增益 VS. RF Frequency.  IM3 | 545556575859                           |

| 邑 | 3.14 | Marchand balun mixer die photo               | 61 |

|---|------|----------------------------------------------|----|

| 邑 | 3.15 | 微小化之 Marchand balun 與 Cherry Hooper 技術降頻器電路  | 63 |

| 邑 | 3.16 | 微小化分合波器示意圖                                   | 64 |

| 邑 | 3.17 | 轉換增益 VS. LO Power                            | 65 |

| 置 | 3.18 | 轉換增益 VS. RF Power (P1dB)                     | 66 |

| 邑 | 3.19 | 轉換增益 VS. IF Frequency                        | 66 |

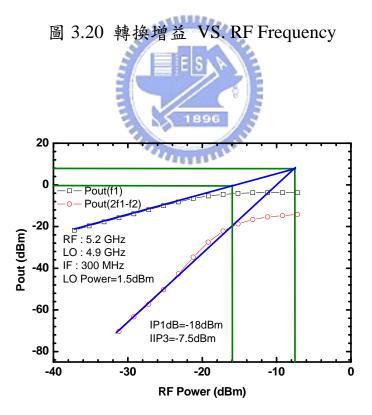

| 邑 | 3.20 | 轉換增益 VS. RF Frequency                        | 67 |

| 邑 | 3.21 | IM3                                          | 67 |

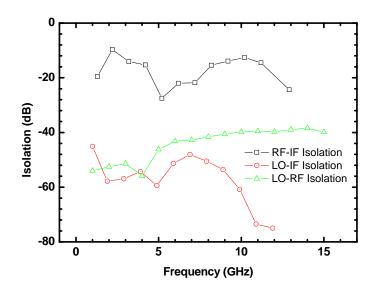

| 邑 | 3.22 | 隔離度                                          | 68 |

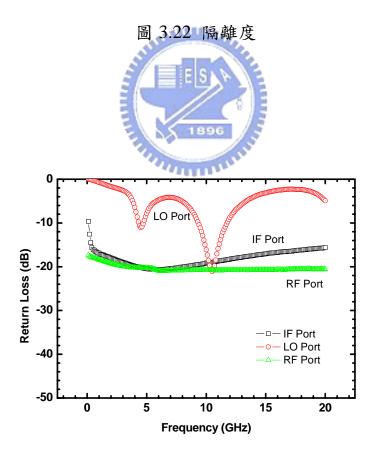

| 邑 | 3.23 | 返回損耗                                         | 68 |

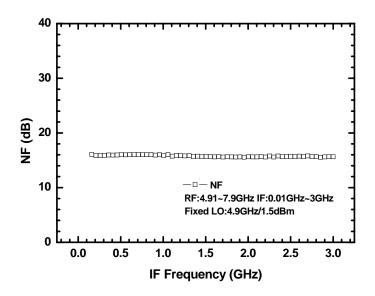

| 邑 | 3.24 | 雜訊指數                                         | 69 |

| 邑 | 3.25 | Miniaturized Marchand balun mixer die photo  | 70 |

| 邑 | 4.1  | Transformer Rat race 與 Cherry Hooper 技術降頻器電路 | 73 |

| 邑 | 4.2  | Transformer Rat race                         | 74 |

| 邑 | 4.3  | 轉換增益 VS. LO Power                            | 74 |

| 邑 | 4.4  | 轉換增益 VS. RF Power (P1dB)                     |    |

| 邑 | 4.5  | 轉換增益 VS. IF Frequency                        | 75 |

| 圖 | 4.6  | 轉換增益 VS. RF Frequency                        | 76 |

| 圖 | 4.7  | IM3                                          | 76 |

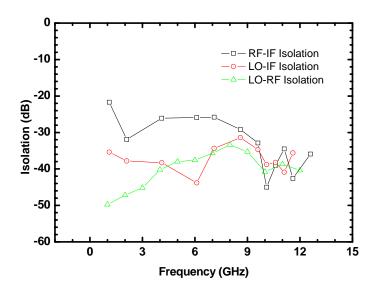

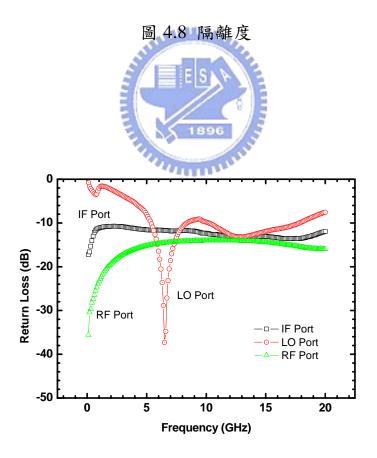

| 圖 | 4.8  | 隔離度                                          | 77 |

| 圖 | 4.9  | 返回損耗                                         | 77 |

| 圖 | 4.10 | 雜訊指數                                         | 78 |

| 圖 | 4.11 | Rat race mixer die photo                     | 79 |

| 圖 | 4.12 | 微小化之 Rat race 與 Cherry Hooper 技術降頻器電路        | 80 |

| 邑 | 4.13 | 轉換增益 VS. LO Power                            | 82 |

| 晑 | 4.14 | 轉換增益 VS RF Power (P1dB)                      | 82 |

| 逼 | 4.15 | 轉換增益 VS. IF Frequency                                     | 83  |

|---|------|-----------------------------------------------------------|-----|

| 昌 | 4.16 | 轉換增益 VS. RF Frequency                                     | 83  |

| 昌 | 4.17 | IM3 (LO: 3GHz)                                            | 84  |

| 圖 | 4.18 | IM3 (LO: 4.9GHz)                                          | 84  |

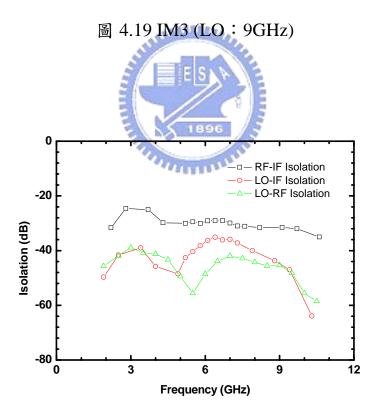

| 昌 | 4.19 | IM3 (LO: 9GHz)                                            | 85  |

| 圖 | 4.20 | 隔離度                                                       | 85  |

| 昌 | 4.21 | 返回損耗                                                      | 86  |

| 昌 | 4.22 | 雜訊指數                                                      | 86  |

| 昌 | 4.23 | Miniaturized Rat race mixer die photo                     | 87  |

| 昌 | 4.24 | Interdigital Rat race 與 Marchand balun 降頻器電路              | 89  |

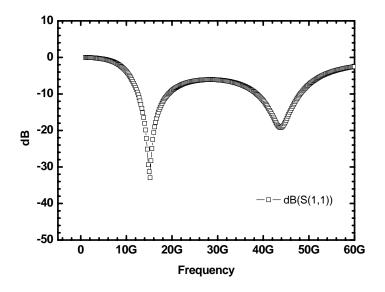

| 昌 | 4.25 | Marchand balun 返回損耗 (S11)                                 | 91  |

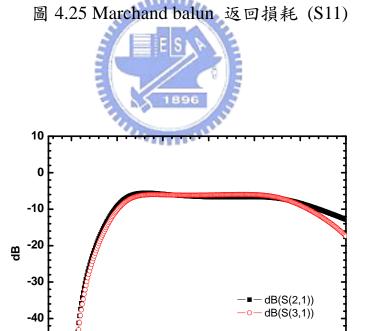

| 圖 | 4.26 | Marchand balun Magnitude (S21 & S31)                      | 91  |

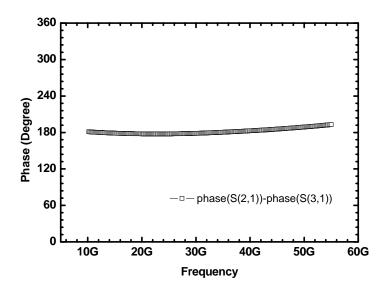

| 圖 | 4.27 | Marchand balun Phase difference (S21 & S31)               | 92  |

| 圖 | 4.28 | Inter-digital Rat race 返回損耗 (S11)                         | 92  |

| 圖 | 4.29 | Inter-digital Rat race Magnitude (S21 & S41)              | 93  |

| 置 | 4.30 | Inter-digital Rat race Phase difference (S21 & S41)       | 93  |

| 置 | 4.31 | 轉換增益 VS. LO Power                                         | 94  |

| 置 | 4.32 | 轉換增益 VS. RF Power (P1dB)                                  | 94  |

| 置 | 4.33 | 轉換增益 VS. IF Frequency                                     | 95  |

| 昌 | 4.34 | 轉換增益 VS. RF Frequency                                     | 95  |

| 置 | 4.35 | IM3                                                       | 96  |

| 置 | 4.36 | Inter-digital Rat race and Marchand balun mixer die photo | 97  |

| 昌 | 5.1  | 有載傳輸線示意圖                                                  | 100 |

| 昌 | 5.2  | L 型匹配方式                                                   | 102 |

| 圖 | 5.3  | 多級匹配方式                                                    | 102 |

| 晑 | 5.4  | 平衡式匹配方式                                                   | 102 |

| 置 | 5.5  | 四種加電阻穩定方式                                  | .104 |

|---|------|--------------------------------------------|------|

| 置 | 5.6  | 微帶線式 30 GHz 兩級趨動放大器架構                      | .105 |

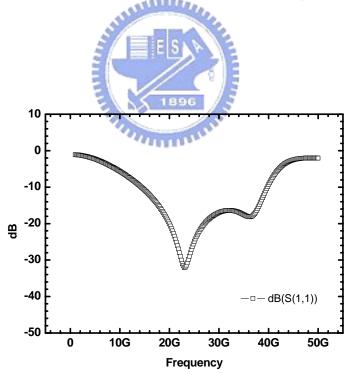

| 置 | 5.7  | S parameter measurement                    | .106 |

| 昌 | 5.8  | A 30 GHz driving amplifier die photo       | 106  |

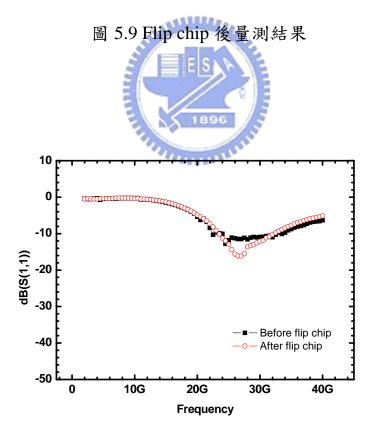

| 圖 | 5.9  | Flip chip 後量測結果                            | 107  |

| 置 | 5.10 | Flip chip 前後輸入返回損耗 (S11)比較                 | .107 |

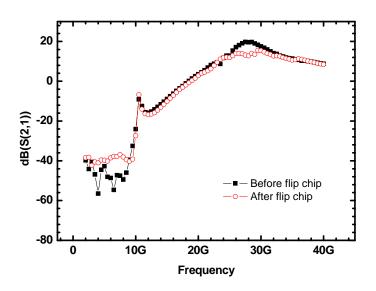

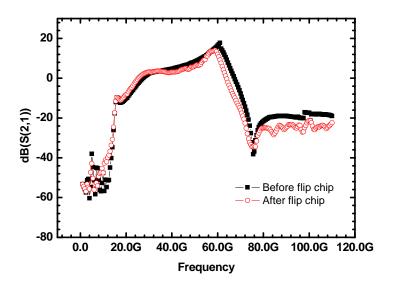

| 置 | 5.11 | Flip chip 前後 linear gain (S21)比較           | .108 |

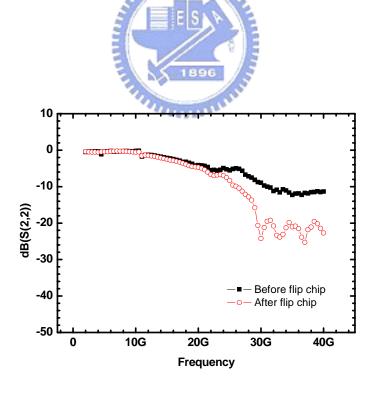

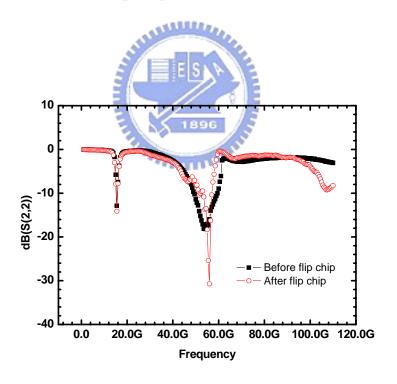

| 置 | 5.12 | Flip chip 前後輸出返回損耗 (S22)比較                 | .108 |

| 圖 | 5.13 | Flip chip 後 30 GHz MS amplifier die photo  | .109 |

| 圖 | 5.14 | 微帶線式 60 GHz 兩級趨動放大器架構                      | 111  |

| 圖 | 5.15 | S parameter measurement                    | .112 |

| 圖 | 5.16 | A 60 GHz driving amplifier die photo       |      |

| 圖 | 5.17 | Flip chip 後量測結果                            | .113 |

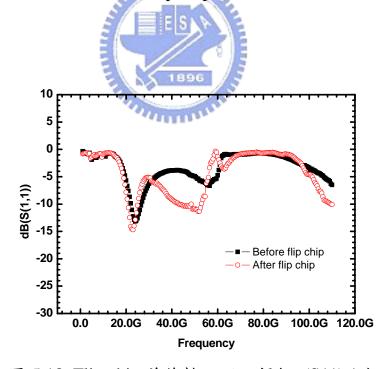

| 昌 | 5.18 | Flip chip 前後輸入返回損耗 (S11)比較                 | .113 |

| 昌 | 5.19 | Flip chip 前後 linear gain (S21)比較           | 114  |

| 昌 | 5.20 | Flip chip 前後輸出返回損耗 (S22)比較                 | .114 |

| 圖 | 5.21 | Flip chip 後 60 GHz MS amplifier die photo  | .115 |

| 圖 | 5.22 | 共平面波導式 60 GHz 兩級趨動放大器架構                    | .117 |

| 圖 | 5.23 | S parameter measurement                    | .118 |

| 圖 | 5.24 | A 60 GHz driving amplifier die photo       | 118  |

| 圖 | 5.25 | Flip chip 後量測結果                            | .119 |

| 圖 | 5.26 | Flip chip 前後輸入返回損耗 (S11)比較                 | .119 |

| 圖 | 5.27 | Flip chip 前後 linear gain (S21)比較           | .120 |

| 圖 | 5.28 | Flip chip 前後輸出返回損耗 (S22)比較                 | .120 |

| 圖 | 5.29 | Flip chip 後 60 GHz CPW amplifier die photo | .121 |

# 表目錄

| 表 2.1 Transformer Marchand balun Summary                            | 26  |

|---------------------------------------------------------------------|-----|

| 表 2.2 Miniaturized Transformer Marchand balun Summary               | 29  |

| 表 2.3 Inter-digital Phase inverter Rat race Summary                 | 43  |

| 表 2.4 Transformer type Phase inverter Rat race Summary              | 47  |

| 表 2.5 Miniaturized Transformer type Phase inverter Rat race Summary | 50  |

| 表 3.1 Marchand balun mixer Summary                                  | 61  |

| 表 3.2 Miniaturized Marchand balun mixer Summary                     | 69  |

| 表 4.1 Rat race mixer Summary                                        | 78  |

| 表 4.2 Miniaturized Rat race mixer Summary                           | 87  |

| 表 4.3 Inter-digital Rat race and Marchand balun mixer               | 96  |

| 表 5.1 Flip chip 前後之 30GHz Amplifier Summary                         | 109 |

| 表 5.2 Flip chip 前後之 60GHz Amplifier Summary                         | 115 |

| 表 5.3 Flip chip 前後之 CPW 60GHz Amplifier Summary                     | 121 |

# 第一章

### 1.1 研究動機

通訊產業蓬勃發展,無線通訊部分有 Wireless LAN 802.11a/b/g/n 的出現,以及 3G 將要來臨,使需求量大增,也因為個人無線通信的普及使得無線通信系統的需求量大量的成長,對於小型化,低價格,低功率的通信元件的需求也持續的增加。而為了成本與整合的考量,未來會趨向單一晶片來實現。而單晶射頻積體電路(RFIC)的優勢在於提供小面積、高重製性、高穩定性及在大量生產時的低價格方面,給射頻技術一個很好的選擇。另外,隨著製程技術的進步不斷地提升具有高截止頻率(f,)及高最大振盪頻率(fmax)的元件,因而更高操作頻率的射頻 IC 晶片不再遙不可及,尤其採用 Silicon 製程的微波、射頻晶片由於利於單晶片的整合,將是目前研究的重點。

### 1.2 論文組織

本篇論文將利用 TSMC SiGe 0.35 um BICMOS、TSMC 0.35 um COMS、TSMC 0.13 um CMOS 與 WIN 0.15 um PHEMT 製程技術來設計晶片。第二章主要介紹被動電路分合波器,包括 Marchand balun 和 Rat race。第三章和第四章主要是介紹將被動電路整合到混頻器內。第五章則是設計與實作 30GHz 和 60GHz 的趨動放大器,並利用覆晶 封裝的技術,比較 Flip chip 前後量測的區別。最後第六章則對於所有電路設計與實作結果做個結論。

# 第二章

被動電路分合波器之分析與設計

### 2.1 前言

近年來,由於無線通訊的普及,使得無線通訊系統的需求量大 量成長,對於單晶微波積體電路(MMIC)與射頻積體電路(RFIC)的通 訊元件需求量也持續的增加。而功率分波器(Power divider)與方向耦 合器(Directional coupler)為電路中極重要的零組件。其中常見的 180 度的分合波器 Marchand balun 或是 Rat race 可以產生不同相位與 3dB 功率,在 single-to-differential 的電路需求上是一種良好的選擇。Balun 為 balance to unbalance 的縮寫,是可將平衡式訊號與非平衡式訊號轉 换的元件,在無線系統中佔有相當重要成份,如 double-balanced mixer、push-pull amplifier、frequency doubler 及 phase shifter,都需要 balun 提供平衡式訊號。balun 有分主動式與被動式,主動式 balun 消 耗較大的功率、較高的雜訊指數與 spurious reponse、較低的功率 handing capability 與三階截斷點(Third-order intercept point),然而,在 現今講求低功率消耗的需求下,被動式 balun 較為適用,但被動式 balun 也有其缺點,通常尺寸過於龐大。在本章節我們將主要介紹 Marchand balun 與 Rat race 兩個分合波器來做討論,並且實現在積體 電路上,這兩種分合波器皆能提供一個寬頻的效果。另外若希望被動 電路做在IC上,所佔據的面積將會非常大,所以如果利用一些微小 化的方式或技術來將分合波器尺寸縮小是本章節重要的課題。

### 2.2 Marchand balun 理論分析與實作

本節一開始會介紹傳統式的 Marchand balun,接著進行目前常見的幾種 Marchand balun 型式做理論分析與設計上的考量,最後將 Marchand balun 整合到積體電路中,並實際量測電路的 performance 與觀察量測結果進行討論。

#### 2.2.1 傳統式的 Marchand balun

Marchand balun 包含兩對耦合線,其中耦合線有微帶線式耦合線 [1][2]、Lange couple 的耦合線、螺旋線圈式的耦合線與變壓器型式 (transformer type)之耦合線[3-7]。而傳統式的 balun 如圖 2.1 所示,一對耦合線一端接地,即為一最簡單的 balun 型態。

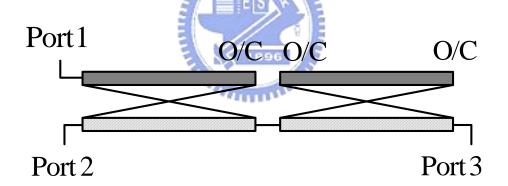

圖 2.1 傳統式的分合波器

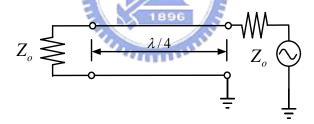

而如圖 2.2 為改良式的 Marchand balun,圖(a)為同軸線線型態,圖(b)為傳輸線型態,訊號從 port1 進去,在 port2 和 port3 會有大小相同而相位差 180 度的訊號輸出。與圖 2.1 傳統式的分合波器比起來多出一段耦合線,所以稱為補償式分合波器,也因此能提供另一共振腔來增加頻寬,所以 Marchand balun 是屬於寬頻的分合波器。

圖 2.2 改良式 Marchand balun

另外,從阻抗的觀點來看:

$$Z_{AB} = \frac{jZ_L Z_S \tan \theta}{Z_L + jZ_S \tan \theta} - jZ_2 \cot \theta$$

當在中心頻時,上式等於 $Z_L$ ,而不在中心頻時,因為開路傳輸線阻抗 $Z_2$ 相對起來很小,短路傳輸線阻抗 $Z_S$ 相對於 $Z_L$ 很大,因此, $Z_{AB}$ 仍然近似於 $Z_L$ ,這也就是為什麼補償式的 Marchand balun 能夠如此寬頻的原因。

### 2.2.2 Marchand balun 理論分析

在設計 Marchand balun 時,由於耦合線在中心頻長度為 $\lambda/4$ ,所以有著耦合係數 C 與傳輸係數 T,而耦合係數 C 與傳輸係數 T 兩者滿足:

$$\begin{cases} |C|^2 + |T|^2 = 1 & \text{without loss} \\ |C|^2 + |T|^2 < 1 & \text{with loss} \end{cases}$$

目前我們最常用的 Marchand balun 大部分都是如圖 2.2(b)所示,那種型態是一個開路端(open),兩個短路端(short),從這個可以延申出其它四種類似的 Marchand balun。如圖 2.3 所示。

圖 2.3 (a) Type I Marchand balun

圖 2.3 (b) Type II Marchand balun

圖 2.3 (c) Type III Marchand balun

圖 2.3 (d) Type IV Marchand balun

其中耦合線在中心頻長度皆為  $\lambda/4$ ,因為先由模擬軟體估算出是否這四種型態的 Marchand balun 皆能產生 differential 的效果,發現圖 2.3(b)型式的分合波器在埠 2 和埠 3 的功率分配大小不一致,且並沒有達到寬頻的效果,然後埠 2 和埠 3 的相位差也不好。而圖 2.3(c)型式的分合波器效果也並不是很好,因為 S11 無法做到很好的匹配。所以底下將會針對圖 2.3(a) Type I 與圖 2.3(d) Type IV 這兩種型態來做分析。

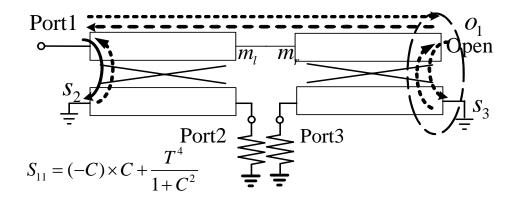

如圖 2.3(a) Type I 的示意圖如圖 2.4 所示,來做分析並試著討論 其中耦合係數 C 與傳輸係數 T 兩者之間的關係。

圖 2.4 Marchand balun 基本架構圖

圖 2.5 Type I S11 分析

由圖 2.5 所示,訊號從埠 1 進去,有兩個路徑,第一個路徑會耦合(C)到  $S_2$  短路端,再由  $S_2$  耦合回去到埠 1,此時傳回埠 1 的訊號已變為  $C \times (-1) \times C$  ,另一個路徑則由埠 2 所吸收。而訊號從埠 1 進去的第二個路徑會經過兩個傳輸係數(T)到開路端,到開路端後又會有兩種路徑,第一個路徑是直接反彈回去再經由兩個傳輸係數(T)到埠 1,此時埠 1 又接收到  $T^4$  的訊號,另一個路徑則是耦合到  $S_3$  再耦合回去到開路端後,從開路端經由兩個傳輸係數(T)到埠 1,此時埠 1 又接收到的  $T \times T \times C \times (-1) \times C \times T \times T$  訊號。這時我們會發現有個訊號會在開路端與  $S_3$  之間做重覆性的耦合與反彈形成一個迴路,所以我們可以由上面的示意圖將所有在埠 1 所接收到的訊號波加總起來得到 Return loss (S11):

$$S_{11} = (-C) \times C + \frac{T^4}{1 + C^2} = \frac{-2C^2 + 1 - C^2}{1 + C^2} = \frac{1 - 3C^2}{1 + C^2}$$

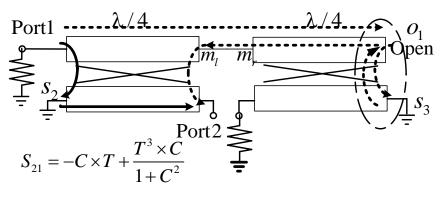

另外 S21 的分析示意圖可由圖 2.6 所示

圖 2.6 Type I S21 分析

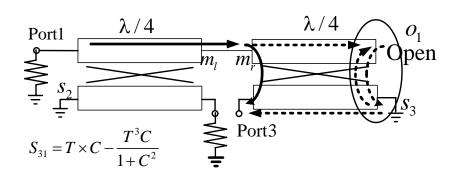

而 S31 的分析示意圖可由圖 2.7 所示

圖 2.7 Type I S31 分析

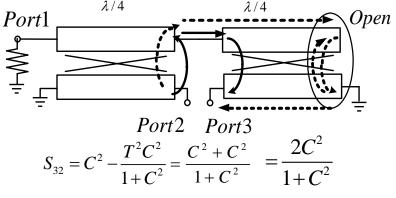

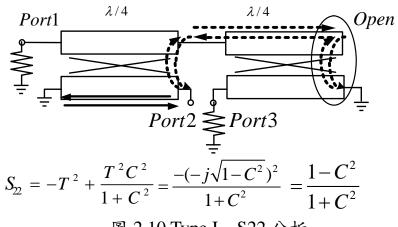

同上面的分析方式可以推導出 $S_{21}$ 與 $S_{31}$ ,我們可以很明顯的看出 $S_{21}$ 與 $S_{31}$ 剛好差一個負號,從數學上來看,兩者是大小相等,而方向相反,也就是相位差了180度。同理可推導其它S參數如下

$$S_{23} = C \times C - \frac{T^2 C^2}{1 + C^2} = \frac{C^2 + C^2}{1 + C^2} = \frac{2C^2}{1 + C^2}$$

圖 2.8 Type I S23 分析

回 2.8 Type 1 323 %  $\sqrt{4}$   $\lambda/4$

圖 2.9 Type I S32 分析

圖 2.10 Type I S22 分析

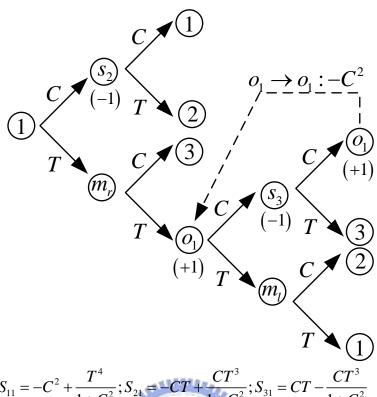

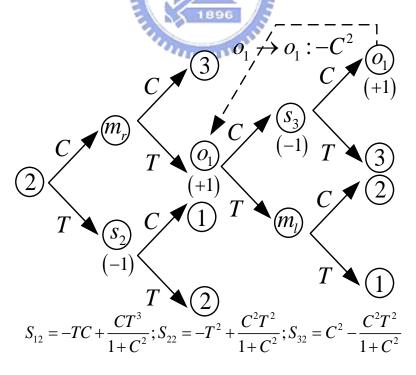

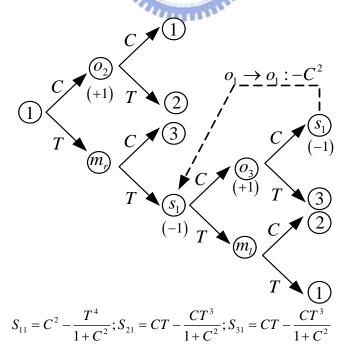

### (1) Type I 矩陣參數推導

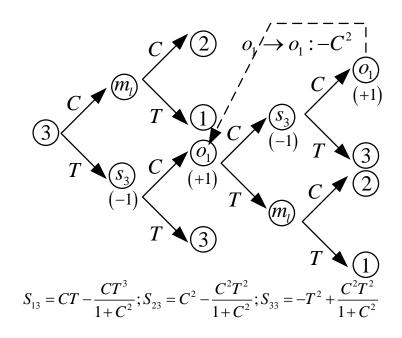

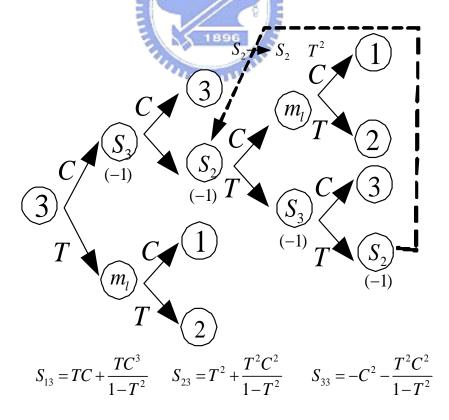

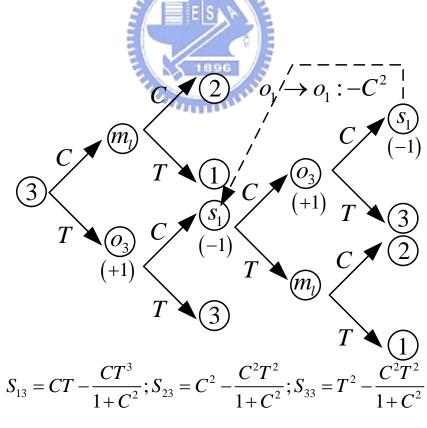

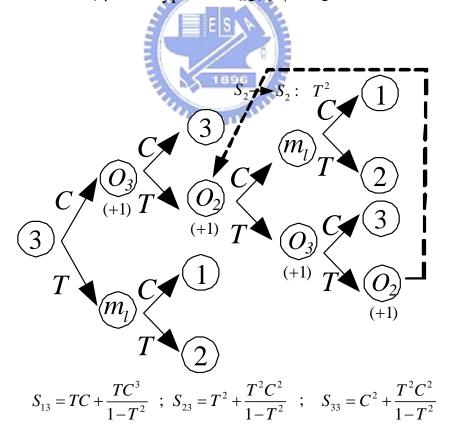

這樣子的看法很容易漏掉其中反射接收到的訊號,所以我們以樹 狀圖來表示,並推導出全部的 S 參數矩陣。先從底下的 Type I Marchand balun 將波的耦合與傳輸係數用樹狀圖表示出來:

圖 2.12 Type I Marchand balun 示意圖

$$S_{11} = -C^2 + \frac{T^4}{1 + C^2}; S_{21} = -CT + \frac{CT^3}{1 + C^2}; S_{31} = CT - \frac{CT^3}{1 + C^2}$$

### 圖 2.13 Type I 訊號從埠 1 進入

圖 2.14 Type I 訊號從埠 2 進入

圖 2.15 Type I 訊號從埠 3 進入

將上面所推導出來的所有 S 參數做整理可以下列矩陣表示之:

$$\begin{bmatrix} S \end{bmatrix}_{1st} = \begin{bmatrix} -C^2 + \frac{T^4}{1+C^2} & -CT + \frac{CT^3}{1+C^2} & CT - \frac{CT^3}{1+C^2} \\ -CT + \frac{CT^3}{1+C^2} & -T^2 + \frac{C^2T^2}{1+C^2} & C^2 - \frac{C^2T^2}{1+C^2} \\ CT - \frac{CT^3}{1+C^2} & C^2 - \frac{C^2T^2}{1+C^2} & -T^2 + \frac{C^2T^2}{1+C^2} \end{bmatrix}$$

由上面矩陣可以看出即使在有損耗的情況下仍然是保持反相的。

假設沒有損耗情況下將 $T=-j\sqrt{1-C^2}$ 代入上面矩陣中可得下列矩陣:

$$[S]_{1st} = \begin{bmatrix} \frac{1-3C^2}{1+C^2} & j\frac{2C\sqrt{1-C^2}}{1+C^2} & -j\frac{2C\sqrt{1-C^2}}{1+C^2} \\ j\frac{2C\sqrt{1-C^2}}{1+C^2} & \frac{1-C^2}{1+C^2} & \frac{2C^2}{1+C^2} \\ -j\frac{2C\sqrt{1-C^2}}{1+C^2} & \frac{2C^2}{1+C^2} & \frac{1-C^2}{1+C^2} \end{bmatrix}$$

所以在  $C = \sqrt{1/3}$  時,S11 會達到完美的匹配。

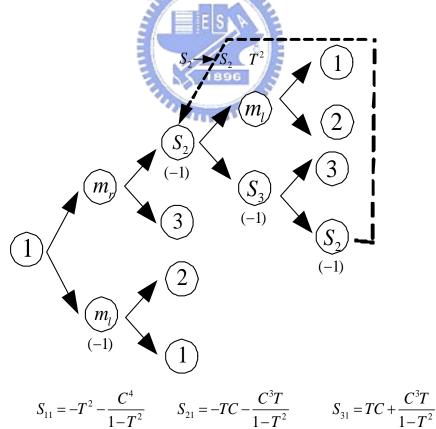

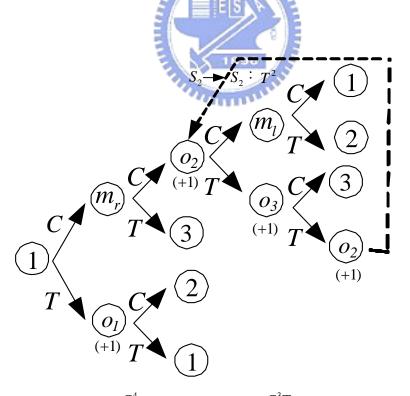

### (2) Type IV 矩陣參數推導

圖 2.16 Type IV Marchand balun 示意圖

接著再以樹狀圖將 Type IV 的 S 參數表示出來:

圖 2.17 Type IV 訊號從埠 1 進入

圖 2.18 Type IV 訊號從埠 2 進入

圖 2.19 Type IV 訊號從埠 3 進入

將上面所推導出來的所有 S 參數做整理可以下列矩陣表示之:

$$[S]_{4th} = \begin{bmatrix} -T^2 - \frac{C^4}{1 - T^2} & -TC - \frac{C^3T}{1 - T^2} & TC + \frac{TC^3}{1 - T^2} \\ -TC - \frac{C^3T}{1 - T^2} & -C^2 - \frac{C^2T^2}{1 - T^2} & T^2 + \frac{T^2C^2}{1 - T^2} \\ TC + \frac{C^3T}{1 - T^2} & T^2 + \frac{T^2C^2}{1 - T^2} & -C^2 - \frac{T^2C^2}{1 - T^2} \end{bmatrix}$$

由上面矩陣可以看出即使在有損耗的情況下仍然是保持反相的。 假設沒有損耗情況下將 $T=-j\sqrt{1-C^2}$ 代入上面矩陣中可得下列矩陣:

$$[S]_{4th} = \begin{bmatrix} \frac{2-3C^2}{2-C^2} & \frac{j2C\sqrt{1-C^2}}{2-C^2} & \frac{-j2C\sqrt{1-C^2}}{2-C^2} \\ \frac{j2C\sqrt{1-C^2}}{2-C^2} & \frac{-j2C\sqrt{1-C^2}}{2-C^2} & \frac{2C^2-2}{2-C^2} \\ \frac{-j2C\sqrt{1-C^2}}{2-C^2} & \frac{2C^2-2}{2-C^2} & \frac{-C^2}{2-C^2} \end{bmatrix}$$

所以在  $C = \sqrt{2/3}$  時,S11 會達到完美的匹配。

比較 Type I 與 Type IV 最後推導出來的矩陣,發現 Type I 的耦合量為  $C=\sqrt{1/3}$ ,而 Type IV 的耦合量為  $C=\sqrt{2/3}$  比 Type I 還要高,故在實作上比較不容易達到,但利用 EM 模擬軟體可以得知 Type IV 的頻寬會比 Type I 還要寬一點,雖然比較不容易實現。

#### (3) Type V 矩陣參數推導

另外觀察圖 2.12 與圖 2.16 可以發現一個有趣的現象,若將圖 2.12 Type I 的 Marchand balun 開路端變短路端,短路端變開路端,則形成如圖 2.20 Type V 的分合波器:

圖 2.20 Type V 分合波器示意圖

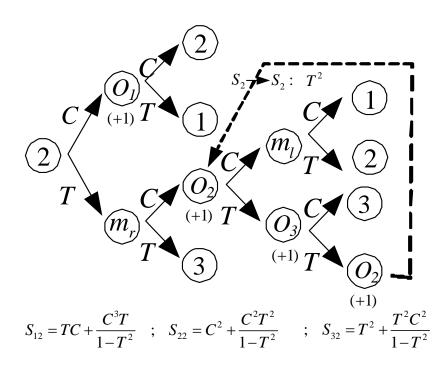

以樹狀圖將 Type IV 的 S 參數表示出來:

圖 2.21 Type V 訊號從埠 1 進入

圖 2.22 Type V 訊號從埠 2 進入

圖 2.23 Type V 訊號從埠 3 進入

將上面所推導出來的所有 S 參數做整理可以下列矩陣表示之:

$$[S]_{l_b,st} = \begin{bmatrix} C^2 - \frac{T^4}{1 + C^2} & CT - \frac{CT^3}{1 + C^2} & CT - \frac{CT^3}{1 + C^2} \\ CT - \frac{CT^3}{1 + C^2} & T^2 - \frac{C^2T^2}{1 + C^2} & C^2 - \frac{C^2T^2}{1 + C^2} \\ CT - \frac{CT^3}{1 + C^2} & C^2 - \frac{C^2T^2}{1 + C^2} & T^2 - \frac{C^2T^2}{1 + C^2} \end{bmatrix}$$

假設沒有損耗情況下,將 $T=-j\sqrt{1-C^2}$ 代入上面矩陣中可得下列矩陣:

$$[S]_{l_b st} = \begin{bmatrix} \frac{3C^2 - 1}{1 + C^2} & -j\frac{2C\sqrt{1 - C^2}}{1 + C^2} & -j\frac{2C\sqrt{1 - C^2}}{1 + C^2} \\ -j\frac{2C\sqrt{1 - C^2}}{1 + C^2} & \frac{C^2 - 1}{1 + C^2} & \frac{2C^2}{1 + C^2} \\ -j\frac{2C\sqrt{1 - C^2}}{1 + C^2} & \frac{2C^2}{1 + C^2} & \frac{C^2 - 1}{1 + C^2} \end{bmatrix}$$

由上面的矩陣可以看出在埠2和埠3所接收到的訊號為大小相等、方向也相同。這是與TypeI所不同的。所以我們可以依電路需求來選擇埠2和埠3是要同相亦或是反相的訊號。

倘若將圖 2.16 Type IV 的 Marchand balun 開路端變短路端,短路端變開路端,則形成如圖 2.24 Type VI 的分合波器,再以樹狀圖來推導出所有的矩陣參數來做比較。

### (4) Type VI 矩陣參數推導

圖 2.24 Type VI 分合波器示意圖

$S_{11} = T^2 + \frac{C^4}{1 - T^2}$ ;  $S_{21} = TC + \frac{C^3T}{1 - T^2}$ ;  $S_{31} = TC + \frac{C^3T}{1 - T^2}$

圖 2.25 Type VI 訊號從埠 1 進入

圖 2.26 Type VI 訊號從埠 2 進入

圖 2.27 Type VI 訊號從埠 3 進入

將上面所推導出來的所有 S 參數做整理可以下列矩陣表示之:

$$[S]_{4_{b}th} = \begin{bmatrix} T^{2} + \frac{C^{4}}{1 - T^{2}} & TC + \frac{C^{3}T}{1 - T^{2}} & TC + \frac{TC^{3}}{1 - T^{2}} \\ TC + \frac{C^{3}T}{1 - T^{2}} & C^{2} + \frac{C^{2}T^{2}}{1 - T^{2}} & T^{2} + \frac{T^{2}C^{2}}{1 - T^{2}} \\ TC + \frac{C^{3}T}{1 - T^{2}} & T^{2} + \frac{T^{2}C^{2}}{1 - T^{2}} & C^{2} + \frac{T^{2}C^{2}}{1 - T^{2}} \end{bmatrix}$$

假設沒有損耗情況下將 $T=-j\sqrt{1-C^2}$ 代入上面矩陣中可得下列矩陣:

$$[S]_{4_bth} = \begin{bmatrix} \frac{3C^2 - 2}{2 - C^2} & -\frac{j2C\sqrt{1 - C^2}}{2 - C^2} & \frac{-j2C\sqrt{1 - C^2}}{2 - C^2} \\ -\frac{j2C\sqrt{1 - C^2}}{2 - C^2} & \frac{C^2}{2 - C^2} & \frac{2C^2 - 2}{2 - C^2} \\ \frac{-j2C\sqrt{1 - C^2}}{2 - C^2} & \frac{2C^2 - 2}{2 - C^2} & \frac{C^2}{2 - C^2} \end{bmatrix}$$

由上面的矩陣可以看出在埠 2 和埠 3 所接收到的訊號仍然為大小相等、方向也相同。這是與 Type IV 所不同的。剛好可以和 Type I 和 Type V 這一組電路做對應。

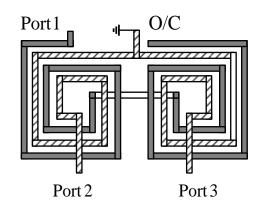

#### 2.2.3 變壓器型式 Marchand balun 實作與量測

根據上一小節討論的結果,因為在設計 Marchand balun 時,由於耦合線在中心頻長度為 $\lambda/4$ ,因此,若以微帶線式耦合線、Lange couple 的耦合線製作,電路尺寸將會很大,很難去整合在積體電路(IC)上,而以螺旋型線圈式或變壓器(transformer)型式之耦合線來看,除

了能夠縮小其 layout,也能靠傳輸線間增加互相耦合以減少金屬線的長度。本電路將以 Transformer 型態繞轉,可以增加其互感(mutual inductance)及互耦(mutual capacitance),因此,在相同長度的金屬線下,以繞線圈型的共振頻率比直線型還低,故變壓器型態的架構擁有比較小的尺寸,也就是說比較適合整合在積體電路中。

本電路我們將使用 Type I 形式的 Marchand balun 來設計,並利用 TSMC 0.35um CMOS 製程製作。整體架構可以由圖 2.24 所示:

圖 2.28 Transformer type Marchand balun

# 模擬與量測結果

圖 2.30 Magnitude (S21 & S31)

圖 2.31 Phase difference (S21 & S31)

圖 2.32 Transformer Marchand balun die photo

表 2.1 Transformer Marchand balun Summary

| Frequency                    | 11 GHZ          |

|------------------------------|-----------------|

| S11                          | -10 dB          |

| S21                          | -10.018 dB      |

| S31                          | -12.85 dB       |

| Phase difference of sum port | 180.23 deg      |

| Die size                     | 0.6 mm x 0.8 mm |

#### 結果與討論

由圖 2.25 輸入返回損耗 S11 量測結果可以看出 S11 從 5GHz 到 15GHz 皆有-10dB 以下,表示此 Marchand balun 具有非常寬頻的特性。再由圖 2.26 Magnitude (S21 & S31)來看,兩者的大小約差了兩到三 dB 左右,與之前所推導的理論結果並不是很符合,或許是因為在矽製程上製程損耗非常大,加上兩個 Transformer 之間的連接線 (Connecting Line)太長,約有 180 um,如圖 2.28 Die photo 所示導致兩邊的 Magnitude 不同。從圖 2.27 Phase difference 約持在 180 度左右的頻帶並沒有很寬頻,歸答原因可能是在量測時,因為埠 1 是 GSG 而埠 2 和埠 3 是採用 GSGSG 針,在量測時並無法一次同時量測,必須先量埠 1 和埠 2 時,把埠 3 的部分 Terminal 掉,可以量到 S21 與 S11的資訊。接著再量測 S11 與 S31 的資訊時把埠 2 的部分 Terminal 掉,所以量測過程中必須校正(Calibration)雨次,所導致的大小與相位差。

## 2.2.4 微小化變壓器型式 Marchand balun 實作與量測

延續上面的實作,為了將 Marchand balun 更加的微小化,利用在傳輸線兩端加電容的方式影響其共振頻率,使得操作頻率往下降,然後電路尺寸卻仍維持固定,即達到微小化的目的。利用 TSMC 0.35 um SiGe BiCMOS 製程進行實作,電路架構圖如圖 2.33 所示:

圖 2.33 Miniaturized Transformer type Marchand balun

#### 晶片模擬結果

圖 2.34 S 參數

圖 2.35 Phase difference (S21 & S31)

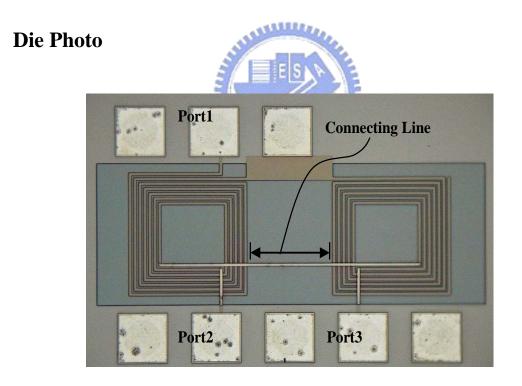

## **Die Photo**

圖 2.36 Miniaturized Transformer Marchand balun die photo

表 2.2 Miniaturized Transformer Marchand balun Summary

| Frequency                    | 5 GHZ           |

|------------------------------|-----------------|

| S11                          | -20 dB          |

| S21                          | -9 dB           |

| S31                          | -7 dB           |

| Phase difference of sum port | 180 deg         |

| Die size                     | 0.6 mm x 0.7 mm |

# 結果與討論

由圖 2.34 輸入返回損耗 S11 模擬結果可以看出 S11 在 5GHz 有 -10dB 以下,由 Magnitude (S21 & S31)來看,兩者的大小約差了兩 dB 左右,但若考慮到往後與混頻器結合,Magnitude 差別仍屬於可以接受的範圍,主要是相位差 180 即可。從圖 2.35 Phase difference 約持在 180 度左右的頻帶並沒有很寬頻,是因為加上電容後使得原本電路變的較窄頻,但與上一電路比較,尺寸維持一致,但操作頻率卻往下降了,達到微小化的目的。

#### 2.3 Rat race 理論分析與實作

在本章節我們將會討論 Rat race 4 埠的分合波器,並將它實現在積體電路中,因為被動電路分合波器要做在 ic 裡面所佔據的面積會非常大,所以必須採取一些微小化的方式才能整合到晶片裡面。底下將會討論從傳統式的 Rat race (尺寸很大)[8],進而利用相位反轉(phase inverter)的技術[9]讓整個電路尺寸大大的縮小,接著再利用交指型 (Inter-digital)[10][11][12]加上相位反轉(phase inverter)的方式讓 Rat race 又更進一步縮小,最後將以 TSMC 積體電路製程設計與製做。

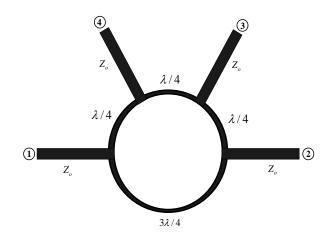

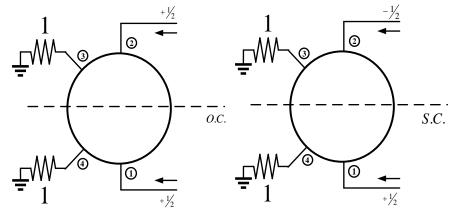

#### 2.3.1 傳統式的 Rat race 理論分析

Rat race 為一個四埠的網路,可以依電路需求選擇兩輸出埠之間有著 0 度或 180 度的相位差。如圖 2.37 所示為一個傳統式的 Rat race,若希望得到兩輸端為相同相位,可由埠 4 輸入,在埠 3 和埠 1 會得到大小和相位皆一樣的功率輸出,若由埠 1 輸入,在埠 2 和埠 4 會有180 度的相位差功率輸出。另外 Rat race 除了可以當分波器外,還可以當合波器使用,若信號從埠 1 和埠 3 輸入,在埠 4 為兩信號之和,而埠 2 則為兩信號之差。其 S 參數的矩陣可由下列表示之:

$$\mathbf{S}_{180} = \frac{-\mathbf{j}}{\sqrt{2}} \begin{bmatrix} 0 & -1 & 0 & 1 \\ -1 & 0 & 1 & 0 \\ 0 & 1 & 0 & 1 \\ 1 & 0 & 1 & 0 \end{bmatrix}$$

圖 2.37 傳統式 Rat race

圖 2.38 可以很清楚看出其功率分或合的情況。

圖 2.38 Rat race 分合波器示意圖

接著藉由奇、偶模的分析將 Rat race 分成兩個部分來看[13][14]

圖 2.39 訊號埠 3 有單位振幅輸入時奇、偶模分解電路

由圖 2.39 我們可以奇、偶模做重疊原理得到:

$$S_{13}=1/2 \text{ (Te-To)} \cdot S_{23}=1/2 \text{ (Te+To)} \cdot S_{33}=1/2 \text{ ($\Gamma$e+$\Gamma$o$)} \cdot S_{43}=1/2 \text{ ($\Gamma$e-$\Gamma$o$)}$$

$$S_{14} = 1/2 \; (\text{Te+To}) \; \; \cdot \; S_{24} = 1/2 \; (\text{Te-To}) \; \; \cdot \; S_{34} = 1/2 \; (\text{\Gammae-Fo}) \; \; \cdot \; S_{44} = 1/2 \; (\text{\Gammae+Fo})$$

圖 2.40 Rat race 奇、偶模分解電路(埠 3)

圖 2.40 表示 Rat race 分解成半電路後,以傳輸線表示的型態。再分別解出奇、偶模的 ABCD 矩陣。

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_e = \begin{bmatrix} 1 & 0 \\ \frac{j}{\sqrt{2}} & 1 \end{bmatrix} \begin{bmatrix} 0 & j\sqrt{2} \\ \frac{j}{\sqrt{2}} & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ -\frac{j}{\sqrt{2}} & 1 \end{bmatrix} = \begin{bmatrix} 1 & j\sqrt{2} \\ j\sqrt{2} & -1 \end{bmatrix}$$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_o = \begin{bmatrix} 1 & 0 \\ \frac{-j}{\sqrt{2}} & 1 \end{bmatrix} \begin{bmatrix} 0 & j\sqrt{2} \\ \frac{j}{\sqrt{2}} & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ \frac{j}{\sqrt{2}} & 1 \end{bmatrix} = \begin{bmatrix} -1 & j\sqrt{2} \\ j\sqrt{2} & 1 \end{bmatrix}$$

將所得到的 ABCD 矩陣代入下列式子算出等效奇、偶模 S 參數

$$S_{11} = \frac{A + \frac{B}{Z_0} - CZ_0 - D}{A + \frac{B}{Z_0} + CZ_0 + D}$$

$$S_{12} = \frac{2(AD - BC)}{A + \frac{B}{Z_0} + CZ_0 + D}$$

$$S_{21} = \frac{2}{A + \frac{B}{Z_0} + CZ_0 + D}$$

$$S_{22} = \frac{-A + \frac{B}{Z_0} - CZ_0 + D}{A + \frac{B}{Z_0} + CZ_0 + D}$$

得到

$$\begin{split} &\Gamma_e = S_{11e} = \frac{1+j\sqrt{2}-j\sqrt{2}+1}{1+j\sqrt{2}+j\sqrt{2}-1} = \frac{-j}{\sqrt{2}} \\ &T_e = S_{21e} = \frac{2}{1+j\sqrt{2}+j\sqrt{2}-1} = \frac{-j}{\sqrt{2}} \\ &\Gamma_o = S_{11o} = \frac{-1+j\sqrt{2}-j\sqrt{2}-1}{-1+j\sqrt{2}+j\sqrt{2}+1} = \frac{j}{\sqrt{2}} \\ &T_o = S_{21o} = \frac{2}{-1+j\sqrt{2}+j\sqrt{2}+1} = \frac{-j}{\sqrt{2}} \end{split}$$

$$S_{13}=1/2 \text{ (Te-To)}=0$$

$S_{23}=1/2 \text{ (Te+To)}=\frac{-j}{\sqrt{2}}$   $S_{33}=1/2 \text{ (\Gammae+\Gammao)}=0$   $S_{43}=1/2 \text{ (\Gammae-\Gammao)}=\frac{-j}{\sqrt{2}}$

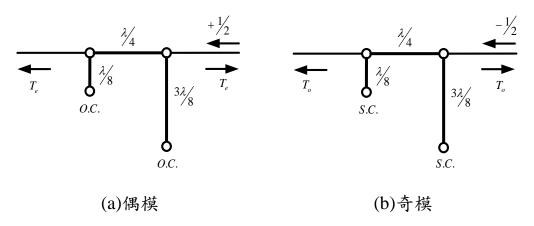

由上面所推導出來的結果可以看出訊號由埠 3 進去,而埠 2 和埠 4 會等功率且等相位,另外埠 3 則為隔離埠。符合一開始所推論的。接著我們繼續推導出若訊號由埠 1 進入,看是否埠 2 和埠 4 會得到大小相等,相位相反的訊號。如圖 2.41 所示:

圖 2.41 訊號埠 1 有單位振幅輸入時奇、偶模分解電路

由圖 2.41 我們可以奇、偶模做重疊原理得到:

$$S_{11}=1/2 (\Gamma e + \Gamma o) \cdot S_{21}=1/2 (\Gamma e - \Gamma o) \cdot S_{31}=1/2 (T e - T o) \cdot S_{41}=1/2 (T e + T o)$$

$$S_{12}=1/2 \text{ ($\Gamma$e-$\Gamma$o$) } \cdot S_{22}=1/2 \text{ ($\Gamma$e+$\Gamma$o$) } \cdot S_{32}=1/2 \text{ ($T$e+$T$o$) } \cdot S_{42}=1/2 \text{ ($T$e-$T$o$)}$$

圖 2.42 Rat race 奇、偶模分解電路(埠 1)

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_{e} = \begin{bmatrix} 1 & 0 \\ -j & 1 \end{bmatrix} \begin{bmatrix} 0 & j\sqrt{2} \\ j & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ j & \sqrt{2} \end{bmatrix} = \begin{bmatrix} -1 & j\sqrt{2} \\ j\sqrt{2} & 1 \end{bmatrix}$$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_{o} = \begin{bmatrix} 1 & 0 \\ j\sqrt{2} & 1 \end{bmatrix} \begin{bmatrix} 0 & j\sqrt{2} \\ j\sqrt{2} & 0 \end{bmatrix} \begin{bmatrix} 1 & 0 \\ -j & 1 \end{bmatrix} = \begin{bmatrix} 1 & j\sqrt{2} \\ j\sqrt{2} & -1 \end{bmatrix}$$

同理,將所得到的 ABCD 矩陣轉為等效奇、偶模 S 參數得到

$$\begin{split} &\Gamma_e = S_{11e} = \frac{-1 + j\sqrt{2} - j\sqrt{2} - 1}{-1 + j\sqrt{2} + j\sqrt{2} + 1} = \frac{j}{\sqrt{2}} \\ &T_e = S_{21e} = \frac{2}{-1 + j\sqrt{2} + j\sqrt{2} + 1} = \frac{-j}{\sqrt{2}} \\ &\Gamma_o = S_{11o} = \frac{1 + j\sqrt{2} - j\sqrt{2} + 1}{1 + j\sqrt{2} + j\sqrt{2} - 1} = \frac{-j}{\sqrt{2}} \\ &T_o = S_{21o} = \frac{2}{1 + j\sqrt{2} + j\sqrt{2} - 1} = \frac{-j}{\sqrt{2}} \end{split}$$

$$S_{11}=1/2 \text{ ($\Gamma e+\Gamma o$)=0}$$

$S_{21}=1/2 \text{ ($\Gamma e-\Gamma o$)}=\frac{j}{\sqrt{2}}$   $S_{31}=1/2 \text{ ($T e-T o$)}=0$   $S_{41}=1/2 \text{ ($T e+T o$)}=\frac{-j}{\sqrt{2}}$

由上面所推導出來的結果可以看出訊號由埠1進去,而埠2和埠 4會等功率且相位相反,另外埠3則為隔離埠。

#### 2.3.2 相位反轉(Phase Inverter)之 Rat race 理論分析

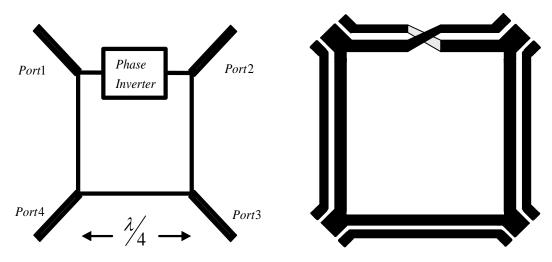

從 2.3.1 節所提到的環型 rat-race 電路分析,可以清楚的說明產生同相位與差動訊號的優點。但其常因  $3\lambda/4$  長度過長佔據了電路上很大的面積以及頻寬很窄的缺點所困擾。我們將延續上面推導並且利用  $\lambda/4$  長度加 180 度相位反轉(Phase Inverter)取代原本傳統環型 rat race的  $3\lambda/4$  的長度,亦可達到電路四埠的結構對稱性,且克服了傳統環型 rat race 窄頻的缺點。我們以 C.Y. Chang 於 2003 所提出的微小化 rat-race 做為設計依據[15],如圖 2.43 為 phase inverter 的 rat race。

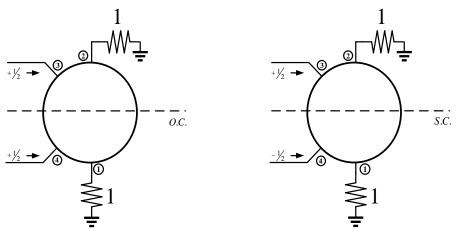

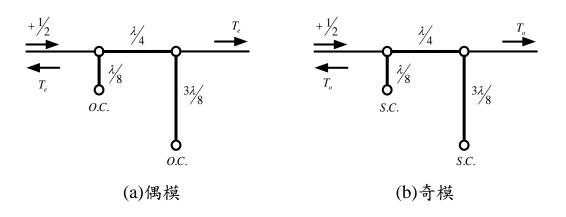

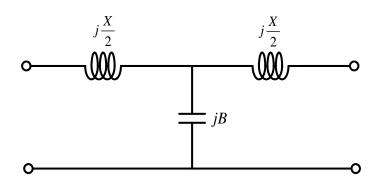

圖 2.43 相位反轉(phase inverter)示意圖

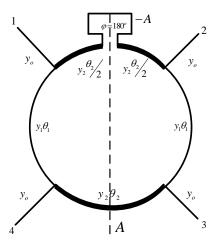

接著我們一樣利用奇、偶模半電路來做 phase inverter 電路分析。[9]

圖 2.44 奇、偶模之 phase inverter 分析示意圖

圖 2.45 Phase Inverter Rat-race (a)偶模(b)奇模 等效半電路

我們將圖 2.44 使用奇模、偶模半電路做分析(如圖 2.45),奇模 與偶模輸出入阻抗剛好是反對稱的,為簡化電路數學推導使  $b_1 = y_2 j \tan \frac{\theta_2}{2} \, \text{與} \, b_2 = -j \frac{y_2}{\tan \frac{\theta_2}{2}} \, , \, 求得奇、偶模的 \, \text{ABCD} 矩陣:}$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_{e} = \begin{bmatrix} \cos\theta_{1} + j\frac{b_{2}}{Y_{1}}\sin\theta_{1} & jY_{1}\sin\theta_{1} \\ b_{1}\cos\theta_{1} + jY_{1}\sin\theta_{1} + b_{1}b_{2}j\frac{1}{Y_{1}}\sin\theta_{1} + b_{2}\cos\theta_{1} & b_{1}j\frac{1}{Y_{1}}\sin\theta_{1} + \cos\theta_{1} \end{bmatrix}$$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix}_0 = \begin{bmatrix} \cos\theta_1 + j\frac{b_1}{Y_1}\sin\theta_1 & j\frac{1}{Y_1}\sin\theta_1 \\ b_2\cos\theta_1 + jY_1\sin\theta_1 + b_1b_2j\frac{1}{Y_1}\sin\theta_1 + b_1\cos\theta_1 & j\frac{b_2}{Y_1}\sin\theta_1\cos\theta_1 \end{bmatrix}$$

繼續將 ABCD 矩陣轉為 S 參數:

$$\begin{bmatrix} S \end{bmatrix}_e = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix}_e$$

$$S_{11e} = \frac{-Z_0 \cos \theta_1 (b_1 + b_2) + jZ_1 \sin \theta_1 (b_2 - b_1) + jZ_0 Y_1 \sin \theta_1 (-1 - b_2 b_1 Z_1^2 + Y_0^2 Z_1^2)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_2 b_1 Z_1^2 + Y_0^2 Z_1^2)}$$

$$S_{12e} = S_{21e} = \frac{2}{2\cos\theta_1 + (Z_0\cos\theta_1 + jZ_1\sin\theta_1)(b_1 + b_2) + jZ_0Y_1\sin\theta_1(1 + b_2b_1Z_1^2 + Y_0^2Z_1^2)}$$

$$S_{22e} = \frac{-Z_0 \cos \theta_1 (b_1 + b_2) + jZ_1 \sin \theta_1 (b_1 - b_2) + jZ_1 Z_0 \sin \theta_1 (-1 - b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_2 b_1 Z_1^2 + Y_0^2 Z_1^2)}$$

$$\begin{bmatrix} S \end{bmatrix}_o = \begin{bmatrix} S_{11} & S_{12} \\ S_{21} & S_{22} \end{bmatrix}_o$$

$$S_{11o} = \frac{-Z_0 \cos \theta_1 \left(b_1 + b_2\right) + jZ_1 \sin \theta_1 \left(b_1 - b_2\right) + jZ_0 Y_1 \sin \theta_1 \left(-1 - b_1 b_2 Z_1^2 + Y_0^2 Z_1^2\right)}{2 \cos \theta_1 + \left(Z_0 \cos \theta_1 + jZ_1 \sin \theta_1\right) \left(b_1 + b_2\right) + jZ_0 Y_1 \sin \theta_1 \left(1 + b_2 b_1 Z_1^2 + Y_0^2 Z_1^2\right)}$$

$$S_{12o} = S_{21o} = \frac{2}{2\cos\theta_1 + Z_0\cos\theta_1(b_2 + b_1) + jZ_1\sin\theta_1(b_1 + b_2) + jZ_1Y_1\sin\theta_1(1 + b_1b_2Z_1^2 + Y_0^2Z_1^2)}$$

$$S_{22o} = \frac{-Z_0 \cos \theta_1 (b_1 + b_2) + jZ_1 \sin \theta_1 (b_2 - b_1) + jZ_0 Y_1 \sin \theta_1 (-1 - b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)}{2 \cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1) (b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)}$$

轉換而得的 S 參數,將奇模與偶模做重疊原理得:

$$S_{34} = S_{43} = \frac{1}{2} (S_{11e} - S_{11o}) = \frac{jZ_1 \sin \theta_1 (b_2 - b_1)}{2\cos \theta_1 + (Z_0 \cos \theta_1 + jZ_1 \sin \theta_1)(b_1 + b_2) + jZ_0 Y_1 \sin \theta_1 (1 + b_1 b_2 Z_1^2 + Y_0^2 Z_1^2)} = -S_{12}$$

由上面的推導最後可以看出 Phase Inverter 提供了 180 度的效果,所以利用 Phase Inverter 加上  $\frac{1}{4}\lambda$  可以取代原本傳統環型  $\frac{3}{4}\lambda$  Rat race。 達到微小化的目的。

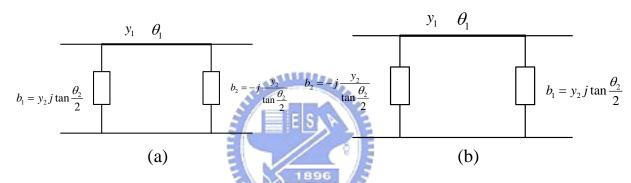

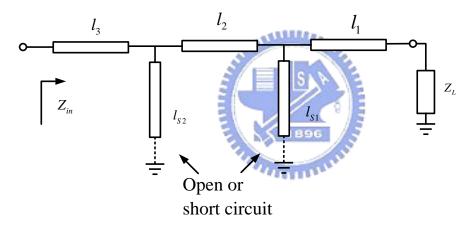

#### 2.3.3 交指型(Inter-digital)與相位反轉 Rat race 理論分析

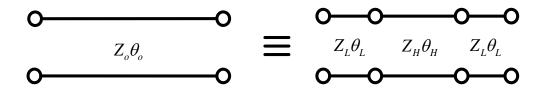

之前提到如何利用相位反轉的方式將 Rat race 的電路尺寸縮小,在本節將會介紹如何利用步階阻抗(Stepped impedance)將傳縮線縮短,達到整體微小化的目的。最後同樣會以 TSMC 0.35um CMOS 製程設計與製做交指型相位反轉的分合波器去驗證理論與實驗是相符的。如何將原本 $\lambda/4$ 的傳輸線縮小,我們將會利用 Stepped impedance來達到[15],也就是說將原本的傳輸線改為一個低阻抗、高阻抗、低阻抗相間的傳輸線,這樣會讓原本傳輸線更加縮小。

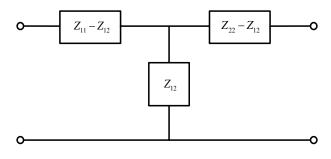

假設一段傳輸線的長度為l,特性阻抗為 $Z_o$ ,其 ABCD 矩陣可以表示為 $A=\cos\beta l$ 、 $B=jZ_o\sin\beta l$ 、 $C=jY_o\sin\beta l$ 、 $D=\cos\beta l$ ,轉換為Z 參數得到下列等式:

$$Z_{11} = Z_{22} = \frac{A}{C} = -jZ_o \cot \beta l$$

$$Z_{12} = Z_{21} = \frac{1}{C} = -jZ_o \cot \beta l$$

下圖 2.46 為雙埠 T 型等效電路

圖 2.46 互易性雙埠網路 T 型等效電路

其中串聯元件為

$$Z_{11} - Z_{12} = -jZ_o \left[ \frac{\cos \beta l - 1}{\sin \beta l} \right] = jZ_o \tan \left( \frac{\beta l}{2} \right)$$

並聯元件為 $Z_{12}$  ,如果當 $\beta l < \frac{\pi}{2}$  時,串聯元件為正電抗(電感),而並聯元件為負電抗(電容),等效電路圖如圖 2.47 所示:

圖 2.47  $\beta l < \frac{\pi}{2}$  時傳輸線等效電路

其中

$$\frac{X}{2} = Z_o \tan\left(\frac{\beta l}{2}\right)$$

、 $B = \frac{1}{Z_o} \sin\beta l$  , 假設當特性阻抗很高的時候

上式可近似為  $X\cong Z_o an rac{eta l}{2}$ 、  $B\cong 0$  ,整個傳輸線變成電感性,好像 一個串聯的電感。倘若當特性阻抗很低的時候上式可近似為  $X\cong 0$ 、  $B\cong Y_o \sin eta l$  ,整個傳輸線就變成電容性,好像一個串聯的電容。

有了上述的概念,我們可以知道 Stepped impedance 之低阻抗、 高阻抗、低阻抗相間的傳輸線,可以利用電容性、電感性、電容性相 間來取代。然而在傳輸線理論中,當傳輸線寬度很小的時候,呈現的 是高阻抗(電感性),而當傳輸線寬度很大的時候,呈現的是低阻抗(電 容性),在此我們將利用比寬度較小的傳輸線來表示高阻抗與交指型 雷容來表示低阻抗,以達到步階阻抗的傳輸線。

而步階阻抗傳輸線可由圖 2.48 表示之:

圖 2.48 Step impedance 等效電路示意圖

我們先計算兩者的 ABCD 矩陣如下:

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \cos \theta_o & jZ_o \sin \theta_o \\ j\frac{1}{Z_o} \sin \theta_o & \cos \theta_o \end{bmatrix}$$

$$\begin{bmatrix} A & B \\ C & D \end{bmatrix} = \begin{bmatrix} \cos \theta_L & jZ_L \sin \theta_L \\ j\frac{1}{Z_L} \sin \theta_L & \cos \theta_L \end{bmatrix} \begin{bmatrix} \cos \theta_H & jZ_H \sin \theta_H \\ j\frac{1}{Z_H} \sin \theta_H & \cos \theta_H \end{bmatrix} \begin{bmatrix} \cos \theta_L & jZ_L \sin \theta_L \\ j\frac{1}{Z_L} \sin \theta_L & \cos \theta_L \end{bmatrix}$$

假設  $Z_L << Z_o << Z_H$

則上述兩個的矩陣應該是相等的,經過展開計算後可得到

$$= \begin{bmatrix} \cos^2 \theta_L \cos \theta_H - \frac{Z_L}{Z_H} \sin \theta_L \sin \theta_H \cos \theta_L - \frac{Z_H}{Z_L} \sin \theta_L \sin \theta_H \cos \theta_L - \sin^2 \theta_L \cos \theta_H \\ 2j \frac{1}{Z_L} \cos \theta_L \cos \theta_H \sin \theta_L - j \frac{Z_H^2}{Z_L} \sin^2 \theta_L \sin \theta_H + j \frac{1}{Z_H} \cos^2 \theta_L \sin \theta_H \\ 2j Z_L \cos \theta_L \cos \theta_H \sin \theta_L - j \frac{Z_L^2}{Z_H} \sin^2 \theta_L \sin \theta_H + j Z_H \cos^2 \theta_L \sin \theta_H \\ \cos^2 \theta_L \cos \theta_H - \frac{Z_L}{Z_H} \sin \theta_L \sin \theta_H \cos \theta_L - \frac{Z_H}{Z_L} \sin \theta_L \sin \theta_H \cos \theta_L - \sin^2 \theta_L \cos \theta_H \end{bmatrix}$$

經整理後可得到下列兩個等式:

$$Z_{H} = \frac{Z_{o} \sin \theta_{o}}{\sin \theta_{H} \cos^{2} \theta_{L}} \qquad Z_{L} = \frac{Z_{H} \sin \theta_{H} \sin \theta_{L}}{2 \cos \theta_{H} \cos \theta_{L}}$$

有了這兩個等式,我們可以先估算所需要的特性阻抗值與其等效的電

容、電感值。並且利用交指型電容來實現。

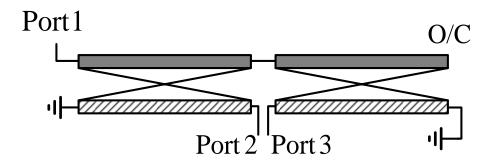

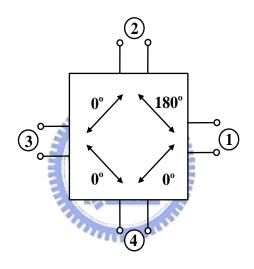

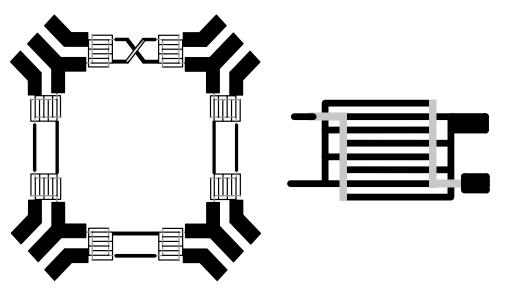

#### 2.3.4 交指型相位反轉之分合波器實作與量測

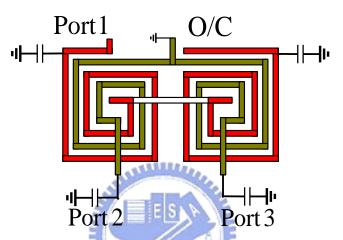

根據前面幾節的描述,我們採用交指型電容加上相位反轉的方式將電路尺寸微小化,電路架構如圖  $2.49~\mathrm{Mm}$  所示,訊號一開始是以共平面波導(Coplanar waveguide)的方式進入,然後轉換為轉共平面微帶線(Coplanar strip-line),其中金屬的寬度和金屬到地空隙寬度也必須做考量。在中間的 Phase inverter 產生了  $180~\mathrm{g}$  的效果,使得原先需要  $\frac{3}{4}\lambda$  的傳輸線以 $\frac{1}{4}\lambda$  的傳輸線加上 Phase inverter 來取代,而且也因為 phase inverter,讓此分合波器達到寬頻的效果。至於 $\frac{1}{4}\lambda$  的傳輸線則利用兩個交指型電容當低阻抗,而較細的傳輸線當高阻抗,再縮小原本的電路。接著以 EM 模擬軟體 IE3D 模擬其特性,預計埠 2 和埠 4 會等分功率且相位相反,而埠 3 為隔離埠,並利用 TSMC 0.35um CMOS 製程製作。

圖 2.49 Inter-digital and phase inverter Rat race

# 模擬與量測結果

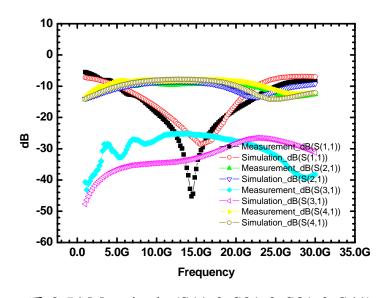

圖 2.50 Magnitude (S11 & S21 & S31 & S41)

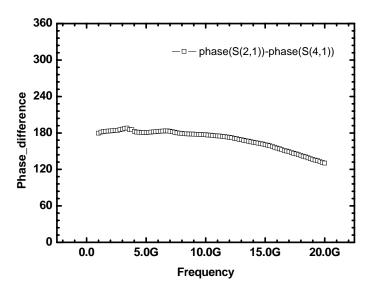

圖 2.51 Phase difference (S21 & S41)

# **Die Photo**

圖 2.52 Inter-digital phase inverter rat race die photo

表 2.3 Inter-digital Phase inverter Rat race Summary

| Frequency                    | 5 GHZ           |

|------------------------------|-----------------|

| S11                          | -11.5 dB        |

| S21                          | -7.3 dB         |

| S41                          | -6.7 dB         |

| S31                          | -38 dB          |

| Phase difference of sum port | 180.68 deg      |

| Die size                     | 1.5 mm x 1.5 mm |

#### 結果與討論

此晶片大小是 1.5 mm x 1.5 mm,可以由圖 2.52 Die photo 看出電路是非常對稱,並利用 NDL 的 Four-port 網路分析儀進行量測,因為此電路必須四面下針(GSG),目前能量測到的頻率並不高(受限於Calibration Kit),大約最高只能量到 20GHz~30GHz 而已,所以這也是當時在訂定規格所考慮到的,才會選擇 10GHz 為中心頻率。

由圖 2.50 量測結果可以發現此電路充分的表現出良好的特性,在 5GHz~15GHz,S11 都有在-10dB 以下,而且 Magnitude 幾乎貼在一起,因為是做在積體電路裡面損耗比較大,所以量測結果 S21 和 S41 大約-7dB 左右,仍然屬於可以接受的範圍內,並且可以很清楚的看出隨著頻率的上升,其 S21 和 S41 的 Magnitude 也慢慢的往下降。另外 S31 為隔離埠,由圖中也可以很明顯看出一直到 20GHz 都是在-30dB 以下,表示在在埠 3 訊號被完美的抵消掉,產生不錯的隔離度。

圖 2.51 量測結果可以很清楚的告訴我們相位差不管在任何頻率 皆為 180 度左右,與理論完全吻合且有抗拒損耗(loss)的效果。另外 利用低阻抗(low)、高阻抗(high)、低阻抗(low)相間的方式達到微小化 效果卓越,倘若只有利用相位反轉(phase inverter)方式在此頻段下 Die Size 大約要 2.2 mm x 2.2 mm,所以利用 Step impedance 成功的將電 路尺寸縮小約 60%左右,達到微小化且整合到積體電路中的目的。

#### 2.3.5 變壓器型式相位反轉之分合波器實作與量測

如之前所述,以變壓器型式之耦合線來看,除了能夠縮小其 layout 面積,也能靠傳輸線間增加互相耦合以減少金屬線的長度。本電路將利用 TSMC 0.35um CMOS 製程製作。電路架構如圖 2.53 所示:

圖 2.53 Transformer type phase inverter rat race

#### 模擬與量測結果

圖 2.54 Magnitude (S11 & S21 & S31 & S41)

圖 2.55 Phase difference (S21 & S41)

#### **Die Photo**

圖 2.56 Transformer phase inverter rat race die photo

表 2.4 Transformer type Phase inverter Rat race Summary

| Frequency                    | 15 GHZ          |

|------------------------------|-----------------|

| S11                          | -36.5 dB        |

| S21                          | -9.3 dB         |

| S41                          | -8 dB           |

| S31                          | -26 dB          |

| Phase difference of sum port | 180 deg         |

| Die size                     | 1.0 mm x 1.0 mm |

#### 結果與討論

此晶片大小是 1.0 mm x 1.0 mm,可以由圖 2.56 Die photo 看出電路是非常對稱,並利用 NDL 的 Four port 網路分析儀進行量測,且此電路為四面下針(GSG),由 Die size 可以看出比起交指型的分合波器電路尺寸又更加縮小,這是 Transformer type 的好處。從圖 2.55 來看輸出訊號是非常 balance 的訊號,從 5GHz ~ 25GHz 幾乎都維持在 180度左右的相位。而圖 2.54 的 S 參數特性也充分了表現出 rat race 的特性,雖然 Magnitude 差了大約 1dB,但達到了微小化的目的。

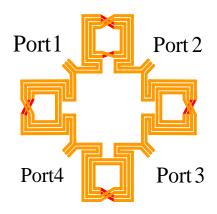

#### 2.3.6 微小化變壓器型式相位反轉分合波器實作與量測

延續上面的實作,為了將 rat race 更加的微小化,除了使用 Transformer type 以外,並利用在傳輸線兩端加電容的方式影響其共振頻率,使得操作頻率往下降,然後電路尺寸卻仍維持固定,即達到 微小化的目的。電路架構如圖 2.57 所示在 rat race 四邊加上電容:

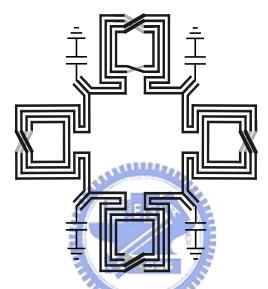

圖 2.57 Miniaturized transformer type phase inverter rat race

#### 晶片量測結果

圖 2.58 Magnitude (S11 & S21 & S31 & S41)

圖 2.59 Phase difference (S21 & S41)

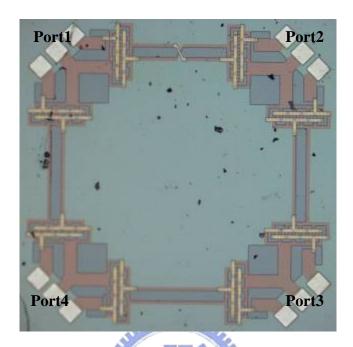

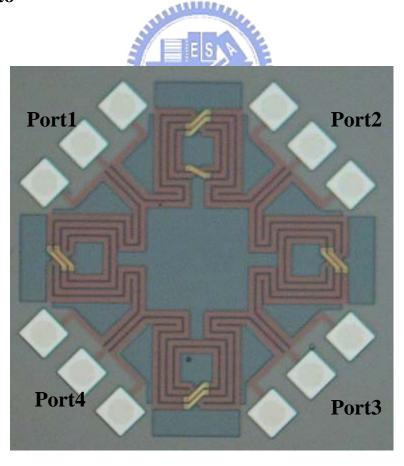

# Port4 Port3

圖 2.60 Miniaturized transformer phase inverter rat race die photo

表 2.5 Miniaturized Transformer type

Phase inverter Rat race Summary

| Frequency                    | 5 GHZ           |

|------------------------------|-----------------|

| S11                          | -13.34 dB       |

| S21                          | -10.7 dB        |

| S41                          | -8.9 dB         |

| S31                          | -31.7 dB        |

| Phase difference of sum port | 180.8 deg       |

| Die size                     | 1.0 mm x 1.0 mm |

#### 結果與討論

本電路已經傳統式的 rat race 從 phase inverter 再加上 transformer type 的方式,再利用電容影響其共振頻率,已將電路尺寸大大的縮小,利於整合至積體電路中,並利用 TSMC 0.35um CMOS 製程製作。我們可以觀察到與前一電路的差別是在於操作頻率變到 5GHz,而 Size 維持 1.0 mm x 1.0 mm,但缺點是受到電容影響變的較窄頻,且 Magnitude 亦差了將近 2dB,但並不影響與混頻器結合,因為 Gilbert mixer 對 Magnitude 較不受影響,只要相位仍維持 180 度即可,而由 圖 2.59 可看出從 2GHz~10GHz 相位幾乎都在 180 度左右。

# 第三章

Marchand balun 之混頻器設計

#### 3.1 前言

在射頻接收機中,混頻器扮演的一個很重要的角色。在本章節我們將實際將之前所提到的 Marchand balun 整合到混頻器裡,而混頻器架構將以 Gilbert cell mixer 為主體,並結合微波與類比的概念,將 Marchand balun 所產生的 differential 訊號置於混頻器的 LO 端,且利用微小化的方式將被動電路縮小,以利於在積體電路中實現。一般而言,吉伯特架構的混頻器對於 LO 與 RF 的相位是非常重要的,會對混頻器的隔離度造成很大的影響。而在設計混頻器時包含了如轉換增益(轉換增益)、頻寬(Bandwidth)、線性度(Linearity)、Noise Figure(雜訊指數)、埠對埠的隔離度(隔離度)、動態範圍(Dynamic range)、功率耗損(Power Consumption)、三階截斷點(Third order Intercept point)等都是必須考慮的重點,依照設計需求度系統架構有所不同。

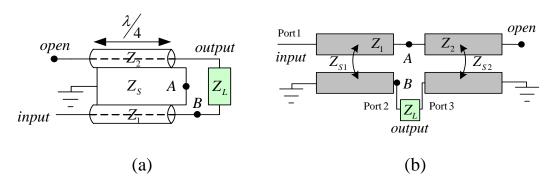

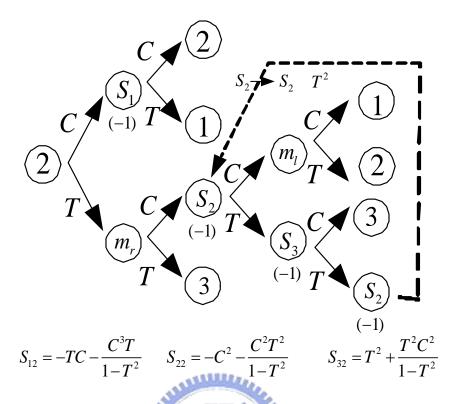

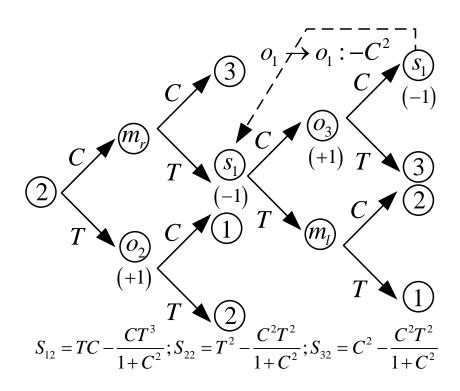

#### 3.2 Marchand balun 之混頻器設計與實現

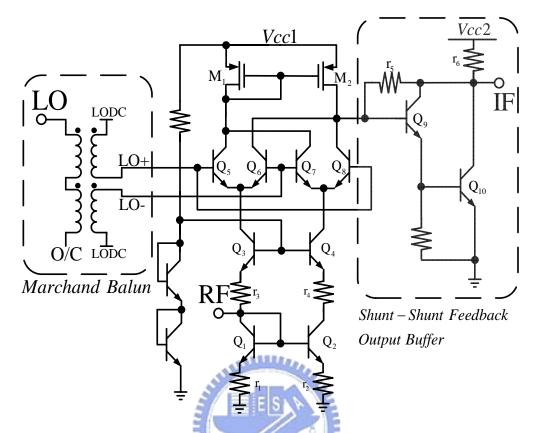

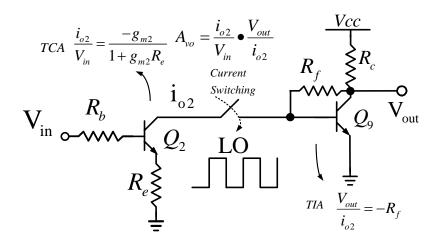

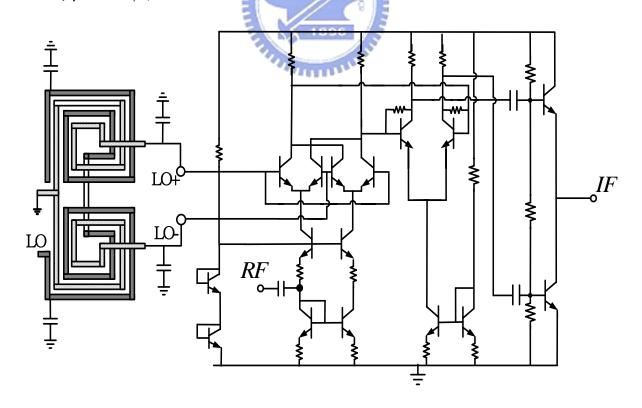

本電路利用了 TSMC 0.35 um SiGe BiCMOS 製程技術,實現一個中心頻率在 10GHz 左右的吉伯特降頻微混頻器[1]。為了減少量測上的不便,在混頻器的 LO、RF 與 IF 端均為單端輸入(出)。在 LO 端採用上一章節提到的 Marchand balun 來將不平衡信號轉為平衡式的訊號,在 RF 端利用微混頻器的方式單端轉雙端輸入,而 IF 端則應用 Cherry Hooper 架構式的 Buffer,將 diffrenctial 訊號轉為單端輸出。電

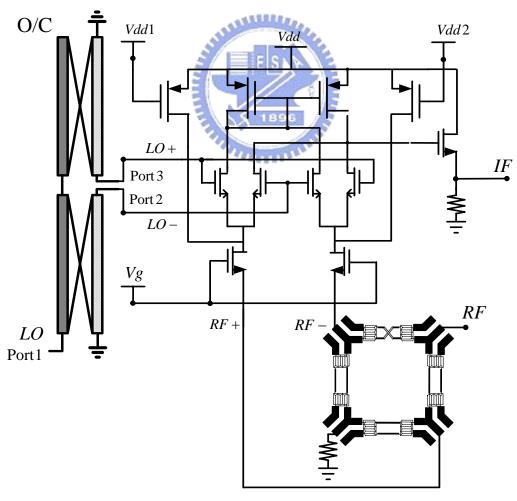

#### 路架構如圖 3.1 所示:

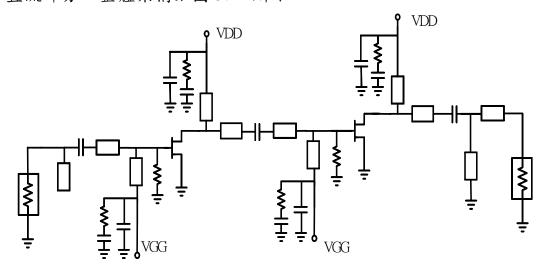

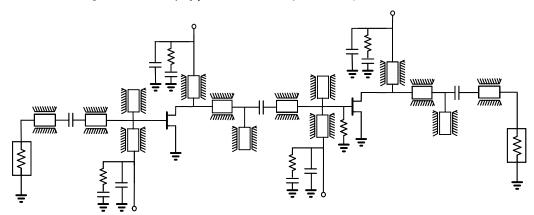

圖 3.1 Marchand balun 與 Cherry Hooper 技術降頻器電路

#### 3.2.1 本地震盪源輸入極

LO 端我們採用 Marchand balun 產生 differential 訊號,如圖 3.2 所示,我們可以看出此 Marchand balun 是由兩個四分之一波長 transformer 所組成,訊號由 port1 進去到另一端為開路,耦合到 port2 和 port3 出去,且為 differential 訊號,中間為 Common ground,在整合於混頻器時,LO 所需要的 DC 訊號由 Common ground 那一點灌入 混頻器內。此 Marchand balun 是採取上一章節所述之 Type I 的架構,也是一般最常用的型式[2]。

圖 3.2 Transformer Marchand balun

因為放在吉伯特混頻器的 LO 端,如果 Marchand balun 所產生的信號 Port2 & Port3 夠平衡,則埠對埠的隔離度會很好,相對的其 Magnitude 的要求則沒那麼嚴格,只要 LO 的功率夠大,足夠讓 Gilbert cell 的電晶體產生混頻的效果即可。

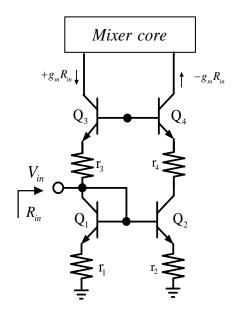

#### 3.2.2 射頻輸入極

1896

本電路主要採用 Gilbert cell mixer 為主要架構核心,由四個電晶體形成一個差動電流開關,當 LO 訊號夠大使電晶體能迅速切換,可達到讓 RF和 LO 訊號產生混頻的效果,因而產生降頻之動作。至於在射頻輸入極(RF)微混頻器為主體[3],如圖 3.3 在輸入端的轉導放大器,構成一個 Single to Differential 之電路,電阻 r1、r3 和電晶體的 1/gm 提供輸入電阻匹配,不同於傳統的吉伯架構混頻器需要外加匹配電路,如此可讓輸入匹配電路不會佔據太大之面積,並可達到寬頻匹配。另外,輸入訊號進入電晶體產生輸出電流,並利用電流鏡產生

一反相的輸出電流,因此只要單端輸入即可產生 differential 的電流。

圖 3.3 微混頻器架構示意圖

#### 3.2.3 輸出緩衝極

在輸出IF端,我們採用 Cherry Hooper 的放大機制單端輸出,不僅僅有提高增益的效果,而且頻寬也變更寬。因為 Gilbert cell 只提供 switch,整個微混頻器由 Q2 所主導,可由圖 3.4 來分析,Q2 所扮演的是一個轉導放大器(TCA),而 Q9 則為轉阻放大器(TIA)[4][5]。

圖 3.4 Cherry Hooper technique employed in the micromixer

#### 圖 3.5 為小信號分析,分為轉導與轉阻兩部分來討論

圖 3.5 轉導與轉阻放大器小信號分析

由上圖所示,我們可以寫出其電路的轉移函數

$$A_{v}(S) = \frac{i_{o2}}{V_{in}}(S) \cdot \frac{V_{out}}{i_{o2}}(S) = \frac{G_{m2}}{1 + S_{m_{P2}}} \times \frac{R_{m9}}{1 + S_{m_{P9}}}$$

由戴維寧等效電路可以求得

$$\begin{cases} \omega_{P2} = \frac{1}{C_{\pi^2} \frac{R_e + R_b}{1 + g_{m2} R_e}} \\ \omega_{P9} = \frac{1}{C_{\pi^9} \frac{R_f + R_c}{1 + g_{m9} R_c}} \end{cases} \begin{cases} G_{m2} = \frac{g_{m2}}{1 + g_{m2} R_e} \\ R_{m9} = -R_f \end{cases}$$

所以上面兩個極點皆受到 1+g<sub>m</sub>R 的影響,因而大大的降低電阻值, 使得極點向外延伸、電路頻寬拉大,以達到寬頻的機制。

另外在電路架構上, $R_f$ 是回授電阻可增加輸出頻寬,而 Darlinton pair 可增加速度,所以整體來看輸出級有著單端輸出與寬頻的特性。

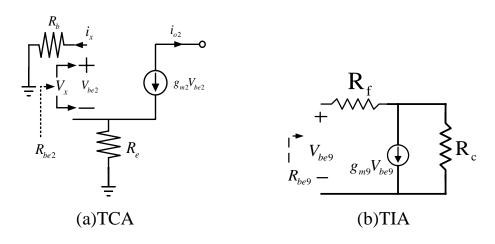

# 3.2.4 晶片量測結果

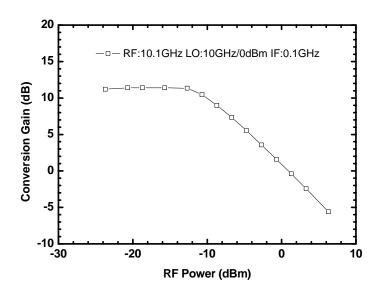

圖 3.7 轉換增益 VS. RF Power (P1dB)

圖 3.9 轉換增益 VS. RF Frequency

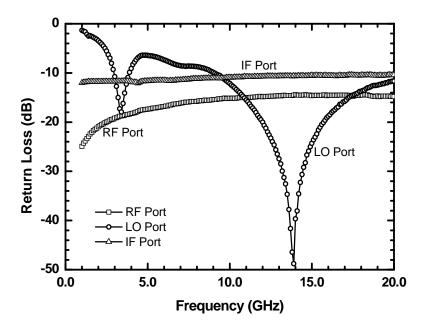

圖 3.11 隔離度

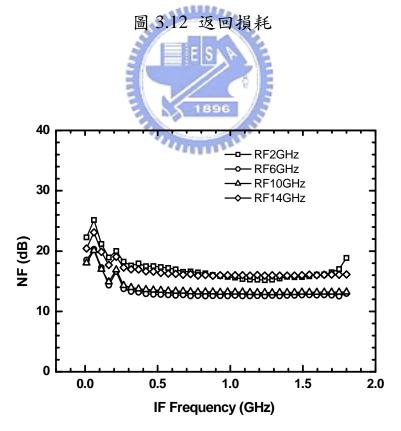

圖 3.13 雜訊指數

# 表 3.1 Marchand balun mixer Summary

| Process            | TSMC 0.35um SiGe BiCMOS |  |  |

|--------------------|-------------------------|--|--|

| DC Current         | 12mA & 13mA@5V          |  |  |

| Conversion Gain    | 14.25dB@LO:5.595dBm     |  |  |

| IP1dB              | -17dBm                  |  |  |

| IIP3               | -6.5dBm                 |  |  |

| LO-to-IF Isolation | -37dB                   |  |  |

| LO-to-RF Isolation | -37dB                   |  |  |

| RF-to-IF Isolation | -22dB                   |  |  |

| LO Return Loss     | -12dB                   |  |  |

| RF Return Loss     | -15dB                   |  |  |

| IF Return Loss     | -12dB                   |  |  |

| Chip Size          | 1.0mm x 1.0mm           |  |  |

# **Die Photo**

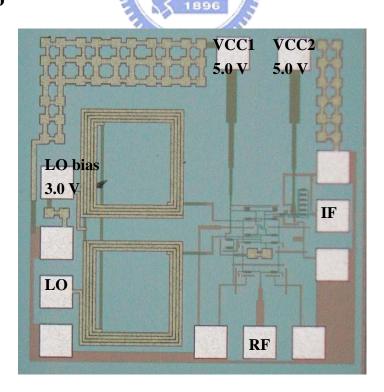

圖 3.14 Marchand balun mixer die photo

### 3.2.5 結果與討論

由上面量測結果可以看出將被動電路 Marchand balun 整合到積體電路中仍然有著不錯的特性,且晶片面積只有 1.0 x 1.0 mm。圖 3.6表示出在 LO Power=-9dB 時即有約 9dB 的轉換增益,代表此電路只需要低的 LO Power 即可趨動整個混頻器。而在 LO Power 為 5.95dBm時有最高的轉換增益。而圖 3.7 可看出 P1dB 約-17dBm,圖 3.8表示此電路在 IF 的頻寬。因為 Marchand balun 的作用,圖 3.9 顯示了 RF頻寬會有一個很寬的頻段,再次說明了 Marchand balun 具有寬頻的特性,結合混頻器後 RF 3dB 頻寬約從 3GHz~13GHz。

從圖 3.10 利用了雙調測試量 IM3,PIdB 約-17dBm,而 IIP3 約-6.5dBm。圖 3.11 為 RF to IF & RF to LO & LO to IF 的隔離度皆在-20dB 以下。從返回損耗來看圖 3.12 顯示因為微混頻器的效果,RF 埠均在-10dB 以下且有寬頻的匹配。而 LO 埠也因為 Marchand balun多少有匹配的效果,返迴損耗約在-10dB 左右,而在 IF 埠因為緩衝級也達到匹配的效果。至於雜訊指數方面表現也很好,最好的雜訊指數是在 RF 在 6GHz 和 10GHz 時只有約 13dB 的雜訊指數,其它頻率也都在-20dB 以內。

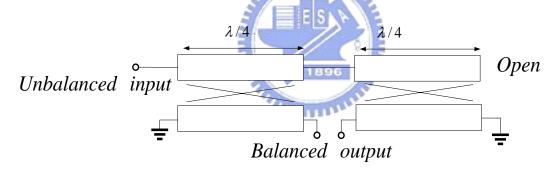

# 3.3 微小化 Marchand balun 之混頻器設計與實現

本電路利用了 TSMC 0.35 um SiGe BiCMOS 製程技術,實現一個中心頻率在 5GHz 左右的吉伯特降頻微混頻器。與上一小節的區別是在於將 Marchand balun 更進一步微小化,利用四邊加電容的方式 [6][7]讓操作頻率縮小,更容易整合到積體電路中。為了減少量測上的不便,在混頻器的 LO、RF與 IF 端均為單端輸入(出)。在 LO 端採用微小化的 Marchand balun 來將不平衡信號轉為平衡式的訊號,在 RF 端利用微混頻器的方式單端轉雙端輸入,而 IF 端則應用 Cherry Hooper 架構式的 Buffer,將 diffrenctial 訊號轉為單端輸出。電路架構如圖 3.15 所示:

圖 3.15 微小化之 Marchand balun 與 Cherry Hooper 技術降頻器電路

### 3.3.1 本地震盪源輸入極

LO 端我們採用 Marchand balun 產生 differential 訊號,與上一小節不同的是我們在四邊加電容,使得操作頻率往低頻走,一般而言,愈低頻的電路尺寸愈大,所以我們將原本操作在 17GHz 左右的Marchand balun,Size 為 180um x 450um,利用 lump 化的方式以電容影響其操作頻率,使其應用在 5GHz 左右的電路,但尺寸仍然維持180um x 450um,即達到微小化的目的。由微小化方式可見下圖 3.16

圖 3.16 微小化分合波器示意圖

所以我們可以將中間 couple line 利用之前所提的 transformer 來實現,使得共振頻率縮小。而中間同樣為 Common ground,在整合於混頻器時,LO 所需要的 DC 訊號由 Common ground 那一點灌入混頻器內。

### 3.3.2 射頻輸入極

本電路一樣是採用 Gilbert cell mixer 為主要架構核心,由四個電晶體形成一個差動電流開關,至於在射頻輸入極(RF)微混頻器為主體,如圖 3.3 在輸入端的轉導放大器(TCA),構成一個 Single to Differential 之電路。

### 3.3.3 輸出緩衝極

在輸出 IF端,我們仍然採用 Cherry Hooper 的放大機制單端輸出,為一個轉阻放大器(TIA),不僅僅有提高增益的效果,而且頻寬也變更寬。如之前的電路分析所示,因為兩個極點皆受到 1+g<sub>m</sub>R 的影響,使得極點向外延伸,以達到寬頻的機制。與上一個電路的差別在於沒有加 Darlinton pair,直接經過耦合電容做單端輸出。

West Committee

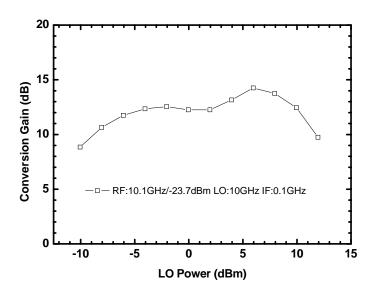

### 3.3.4 晶片量測結果

圖 3.17 轉換增益 VS. LO Power

圖 3.18 轉換增益 VS. RF Power (P1dB)

圖 3.19 轉換增益 VS. IF Frequency

圖 3.21 IM3

圖 3.23 返回損耗

圖 3.24 雜訊指數

# 表 3.2 Miniaturized Marchand balun mixer Summary

**Process** TSMC 0.35um SiGe BiCMOS DC Current 32mA@5V Conversion Gain 16.3dB@LO:1.5dBm IP1dB -18dBm IIP3 -7.5dBm LO-to-IF Isolation -55dB LO-to-RF Isolation -50dB RF-to-IF Isolation -27dB LO Return Loss -10dB RF Return Loss -20dB IF Return Loss -10dB 0.9 mm x 1.0 mm Chip Size

### Die photo

圖 3.25 Miniaturized Marchand balun mixer die photo

### 3.3.5 結果與討論

本電路主要是利用在被動電路 Marchand balun 四邊加上電容,影響其共振頻率進而達到微小化的效果,再與混頻器做結合。從上面量測結果來看有著不錯的特性。圖 3.17 顯示出在 LO=1.5dBm 時有16.3dB 的轉換增益,圖 3.19 因為電路架構中輸出耦合電容的效應,導致接近 0Hz 時轉換增益就往下掉。圖 3.20 為量測 RF 的頻寬,也因為 Marchand balun 的影響,RF 埠非常寬頻(3GHz~12GHz)。另外圖3.21 為隔離效果,圖 3.22 是各個埠的返回損耗,LO Port 約-10dB 左右,而 RF和 IF Port 皆在-15dB 以下,圖 3.24 雜訊指數之量測結果發現 IF 頻率一直到 3GHz 皆維持-16dB 左右的雜訊指數。所以將微小化後的 Marchand balun 和混頻器做結合仍有著相當不錯的特性。

# 第四章

Rat race 之混頻器設計

### 4.1 前言

上一章節我們整合被動電路 Marchand balun 與主動電路混頻 器,將之實現在積體電路上。而在本章節會利用到第二章所提到的 Rat race 分合波器整合到混頻器裡,但因為 Rat race 是四埠元件,所 以所佔據的面積會比三埠元件(Marchand balun)還要大許多,此時如 何將分合波器微小化將是很重要的課題。另外混頻器架構同樣以 Gilbert cell mixer 為主體,並結合微波與類比的概念,將 Rat race 所產 生的 differential 訊號置於混頻器的 LO 端,且利用微小化的方式將被 動電路縮小,以利於在積體電路中實現。如之前所述,以變壓器 (Transformer)型式之耦合線來看,除了能夠縮小其 layout 面積,也能 靠傳輸線間增加互相耦合以減少金屬線的長度。因為同時增加其互感 (mutual capacitance)及互耦(mutual inductance),因此,在相同長度的 金屬線下,以繞線圈型的共振頻率比直線型還低,擁有比較小的尺 寸,也就是說比較適合整合在積體電路中。

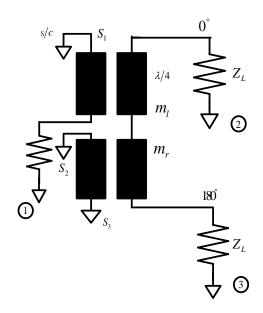

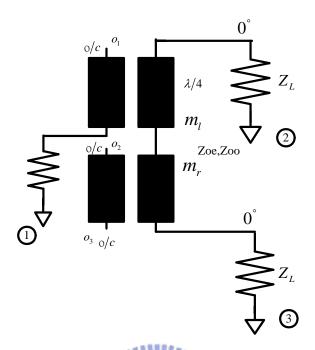

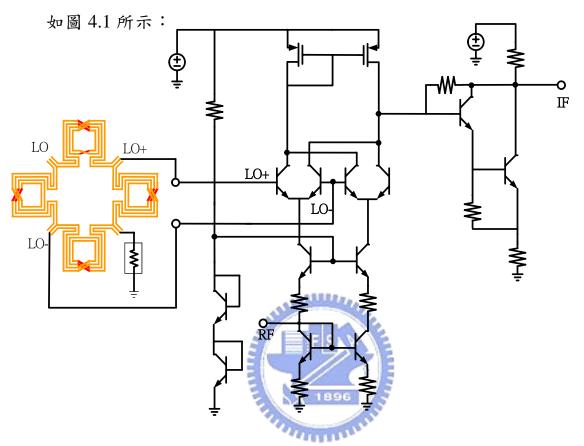

### 4.2 Transformer Rat race 之混頻器設計與實現

本電路利用了 TSMC 0.35 um SiGe BiCMOS 製程技術,實現一個中心頻率在 10GHz 左右的吉伯特降頻微混頻器[1]。為了減少量測上的不便,在混頻器的 LO、RF 與 IF 端均為單端輸入(出)。在 LO 端採用第二章節提到的 Rat race 來將不平衡信號轉為平衡式的訊號,在

RF 端利用微混頻器的方式單端轉雙端輸入,而 IF 端則應用 Cherry Hooper 架構式的 Buffer,將 diffrenctial 訊號轉為單端輸出。電路架構

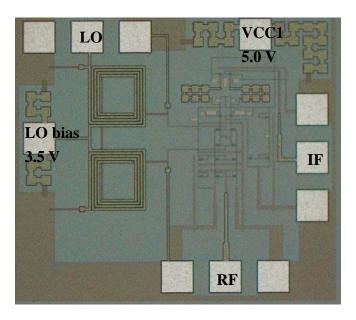

圖 4.1 Transformer Rat race 與 Cherry Hooper 技術降頻器電路

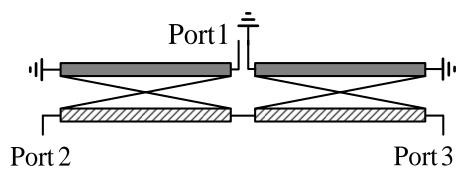

### 4.2.1 本地震盪源輸入極

LO 端我們採用 Rat race 產生 differential 訊號,如圖 4.2 所示,我們可以看出此 Rat race 是由四個四分之一波長 transformer 所組成, 訊號由 port1 進去, port2 和 port4 為 differential 訊號,且 port3 為隔離埠。因為利用了相位反轉的技術讓 Rat race 微小化,並以 Transformer 方式增加其耦合量讓電路尺寸更加縮小。

圖 4.2 Transformer Rat race

### 4.2.2 射頻輸入極

本電路主要採用微混頻器的架構[2],如圖 3.3 所示。

### 4.2.3 輸出緩衝極

在輸出 IF 端,我們亦採用 Cherry Hooper 的放大機制單端輸出,以 Darlinton pair 增加速度,使輸出級有單端輸出與寬頻的特性。[3][4]

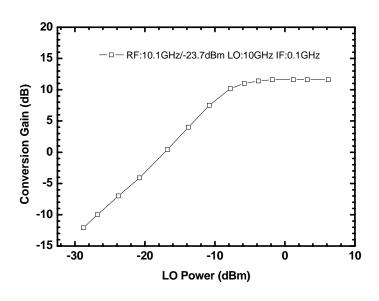

# 4.2.4 晶片量測結果

圖 4.3 轉換增益 VS. LO Power

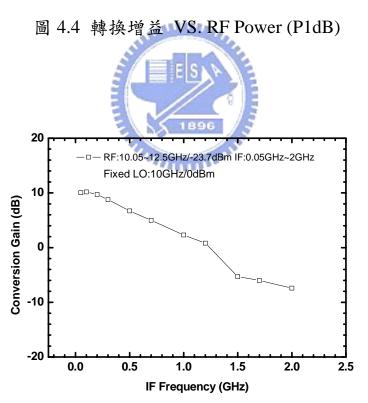

圖 4.5 轉換增益 VS. IF Frequency

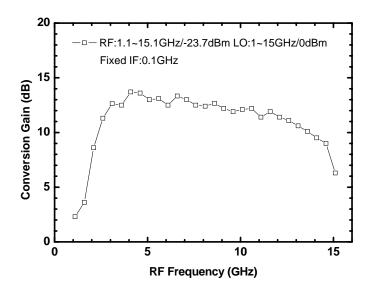

圖 4.6 轉換增益 VS. RF Frequency

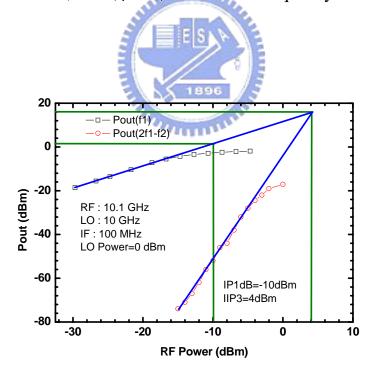

圖 4.7 IM3

圖 4.9 返回損耗

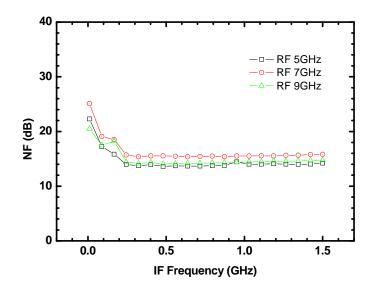

圖 4.10 雜訊指數

# 表 4.1 Rat race mixer Summary

1896

| Process            | TSMC 0.35um SiGe BiCMOS |  |  |

|--------------------|-------------------------|--|--|

| DC Current         | 31.94mA@5V              |  |  |

| Conversion Gain    | 11.6dB@LO:0dBm          |  |  |

| IP1dB              | -10dBm                  |  |  |

| IIP3               | 4dBm                    |  |  |

| LO-to-IF Isolation | -40dB                   |  |  |

| LO-to-RF Isolation | -40dB                   |  |  |

| RF-to-IF Isolation | -45dB                   |  |  |

| LO Return Loss     | -10dB                   |  |  |

| RF Return Loss     | -14dB                   |  |  |

| IF Return Loss     | -16dB                   |  |  |

| Chip Size          | 1.4 mm x 1.4 mm         |  |  |

### Die photo

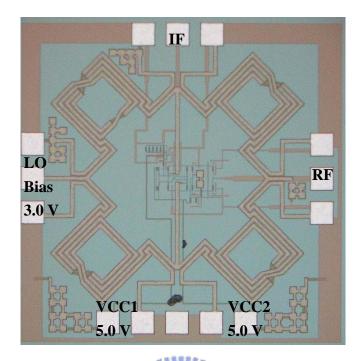

圖 4.11 Rat race mixer die photo

# 4.2.5 結果與討論

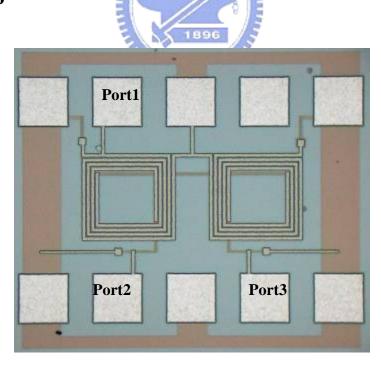

由圖 4.11 可以看出主動電路是擺在 Rat race 的中間,然後將訊號線拉到外面的 PAD。量測結果由圖 4.3 所示在 LO=0dBm 大約有 11.6dB 的轉換增益,圖 4.5 量測為 IF 頻寬,顯示出此電路 IF 頻寬大約只有一兩百 MB,並沒有充分表現出 Cherry Hooper 的效果。從 RF 頻寬來看如圖 4.6,亦如預期的非常寬頻,以 3dB 頻寬來看,RF bandwidth 大約可從 3GHz 到 14GHz 這麼寬頻,表示 rat race 特性在 混頻器表現出來。圖 4.7 為 IM3 的量測,P1dB 為-10dBm,IIP3 為 4dBm。從圖 4.9 來看各端埠的返回損耗皆在-10dB 以下,而圖 4.10 的雜訊指數量測結果很好,皆在 15dB 左右。

### 4.3 微小化 Transformer Rat race 混頻器設計與實現

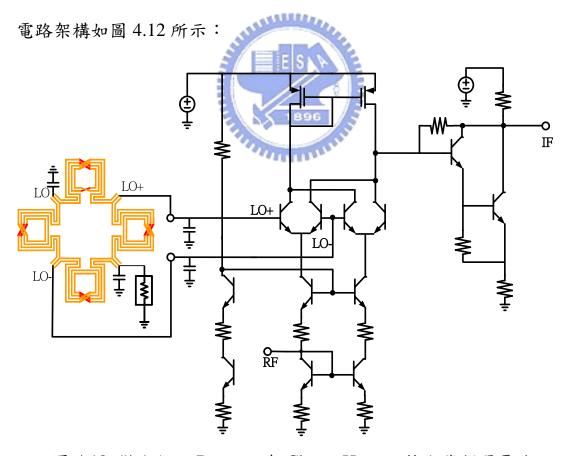

本電路利用 TSMC 0.35 um SiGe BiCMOS 製程技術,實現一個中心頻率在 5GHz 左右的吉伯特降頻微混頻器。將上一小節的 Rat race更進一步微小化,利用四邊加電容的方式[5][6]讓操作頻率縮小,更容易整合到積體電路中。為了減少量測上的不便,在混頻器的 LO、RF 與 IF 端均為單端輸入(出)。在 LO 端採用微小化的 Rat race 來產生 differential 訊號,在 RF 端利用微混頻器的方式單端轉雙端輸入,而 IF 端則應用 Cherry Hooper 架構式的 Buffer。

圖 4.12 微小化之 Rat race 與 Cherry Hooper 技術降頻器電路

### 4.3.1 本地震盪源輸入極

LO 端我們採用 Rat race 產生 differential 訊號,並在四邊加電容,使得操作頻率往低頻走,一般而言,愈低頻的電路尺寸愈大,所以我們將原本操作在 25GHz 左右的 Rat race, Size 為 1000 um x 1000 um,利用 lump 化的方式以電容影響其操作頻率,使其應用在 5GHz 左右的電路,但尺寸仍然維持 1000 um x 1000 um,即達到微小化的目的。由微小化方式如上一章之圖 3.16 所示

### 4.3.2 射頻輸入極

本電路一樣是採用 Gilbert cell mixer 為主要架構核心,由四個電晶體形成一個差動電流開關,至於在射頻輸入極(RF)微混頻器為主體,如圖 3.3 在輸入端的轉導放大器(TCA),構成一個 Single to Differential 之電路。

### 4.3.3 輸出緩衝極

在輸出IF端,我們仍然採用 Cherry Hooper 的放大機制單端輸出,為一個轉阻放大器(TIA),不僅僅有提高增益的效果,而且頻寬也變更寬。如之前的電路分析所示,因為兩個極點皆受到 1+g<sub>m</sub>R 的影響,使得極點向外延伸,以達到寬頻的機制。主動混頻器部分架構上與之前幾乎完全一樣,只有頻率部分不同而已。

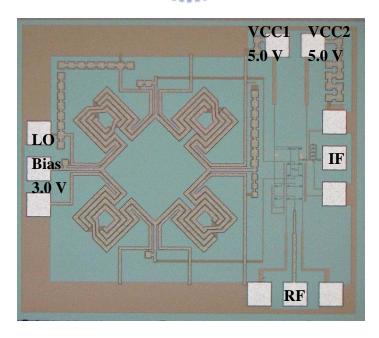

# 4.3.4 晶片量測結果

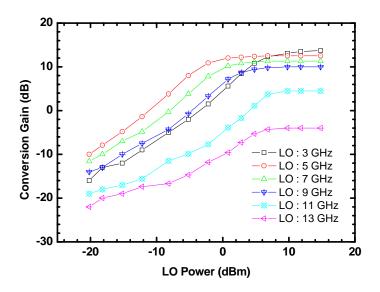

圖 4.13 轉換增益 VS. LO Power

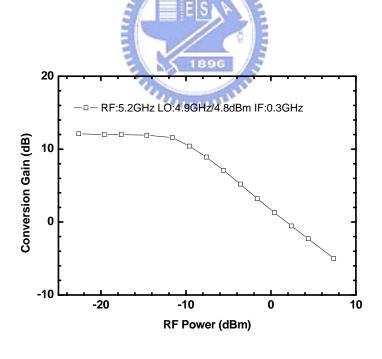

圖 4.14 轉換增益 VS. RF Power (P1dB)

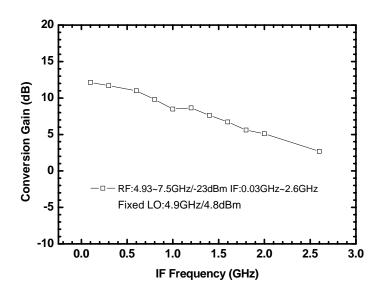

圖 4.15 轉換增益 VS. IF Frequency

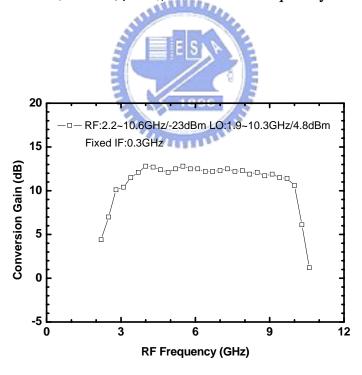

圖 4.16 轉換增益 VS. RF Frequency

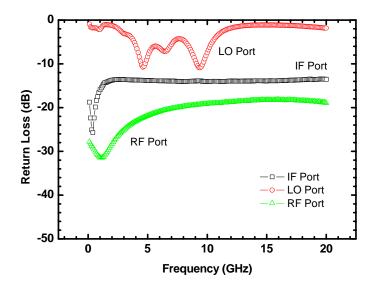

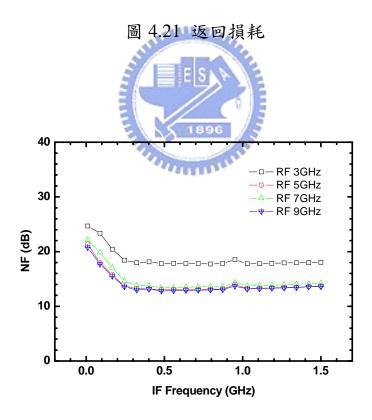

圖 4.18 IM3 (LO: 4.9GHz)

圖 4.20 隔離度

圖 4.22 雜訊指數

| 表 4.2 Miniaturized Rat race mixer Summary | 表 | 4.2 | Miniatu | rized | Rat | race | mixer | <b>Summar</b> | y |

|-------------------------------------------|---|-----|---------|-------|-----|------|-------|---------------|---|

|-------------------------------------------|---|-----|---------|-------|-----|------|-------|---------------|---|

| Process            | TSMC 0.35um SiGe BiCMOS |  |  |

|--------------------|-------------------------|--|--|

| DC Current         | 5.17mA & 18.18mA@5V     |  |  |

| Conversion Gain    | 12.5dB@LO:4.8dBm        |  |  |

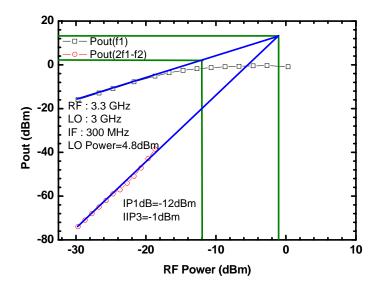

| IP1dB              | -12dBm@LO:3GHz          |  |  |

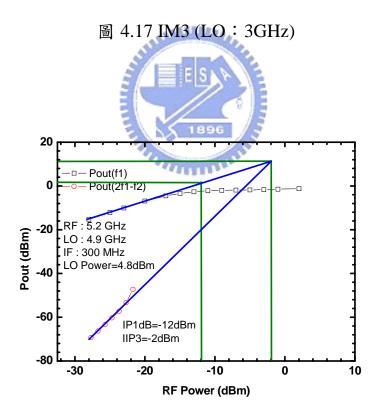

| IP1dB              | -12dBm@LO:4.9GHz        |  |  |

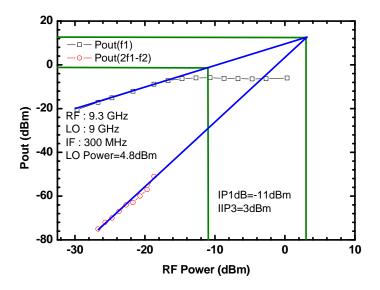

| IP1dB              | -11dBm@LO: 9GHz         |  |  |

| IIP3               | -1dBm@LO:3GHz           |  |  |

| IIP3               | -2dBm@LO:4.9GHz         |  |  |

| IIP3               | -3dBm@LO:9GHz           |  |  |

| LO-to-IF Isolation | -50dB                   |  |  |

| LO-to-RF Isolation | -50dB                   |  |  |

| RF-to-IF Isolation | -30dB                   |  |  |

| LO Return Loss     | -10dB                   |  |  |

| RF Return Loss     | <-20dB                  |  |  |

| IF Return Loss     | <-20dB                  |  |  |

| Chip Size          | 1.2 mm x 1.4 mm         |  |  |

# Die photo

圖 4.23 Miniaturized Rat race mixer die photo

#### 4.3.5 結果與討論

從量測結果來看,圖 4.13 顯示了在不同 LO 頻率下的轉換增益, 圖 4.15 為 IF 頻寬,因為 Cherry Hooper 的效果,使得頻寬超過 1GHz 以上,如圖 4.16 所示,也因為 Marchand balun,其 RF 頻寬可從 3GHz~10GHz 這麼寬頻,剛好符合 Ultra band 的規格,所以我們分別 量測 3GHz、5GHz 與 9GHz 的 IM3,如圖 4.17、圖 4.18 與圖 4.19。 而 P1dB 大約為-12dBm 左右,而 IIP3 約為-2dBm 左右。我們再來看 隔離埠的效果,從圖 4.20 所示,量測結果 LO-to-IF 和 LO-to-RF 隔 離度約為-50dB,而 RF-to-IF 隔離度約為-30dB。所以我們可以知道 此電路埠與埠之間的隔離度還不錯。而各埠之間的返回損耗亦都在 -10dB 以下。另外雜訊指數也是混頻器滿重要的一個指標,從圖 4.22 量測結果來看,除了RF為3GHz時,雜訊指數為-18dB以外在RF 為 5GHz、7GHz 與 9GHz 皆在-13dB 左右,符合一般設計混頻器的規 格。所以綜合上面量測結果分析,將變壓器型式的分合波器再加上電 容微小化後,進而與混頻器整合到積體電路中,結合微波與類比的概 念,仍然有著不錯的特性。

# 4.4 利用 Marchand balun 和交指型相位轉換分合波器 之降頻器設計與實現

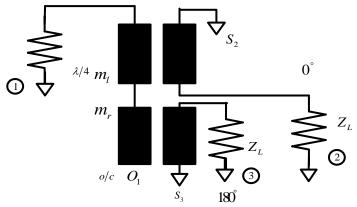

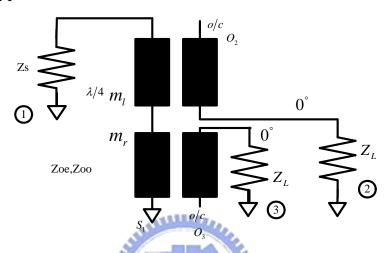

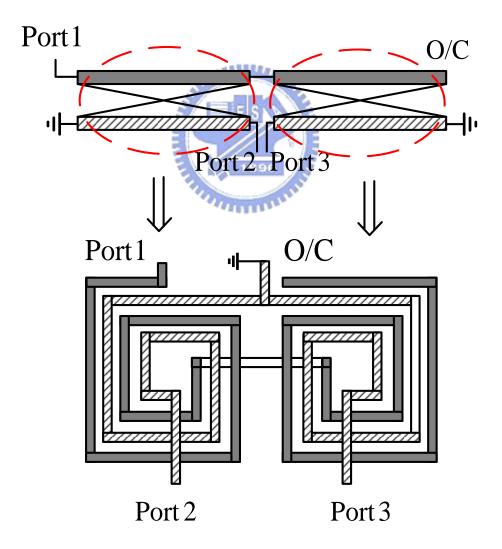

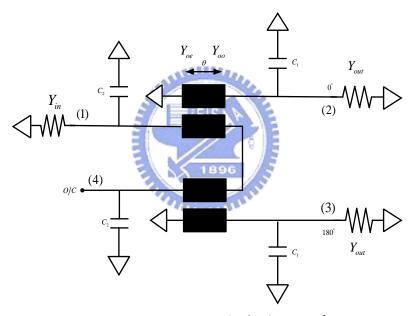

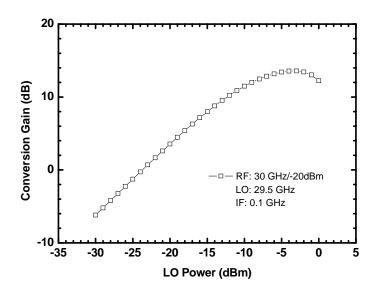

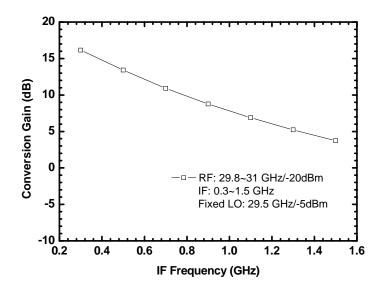

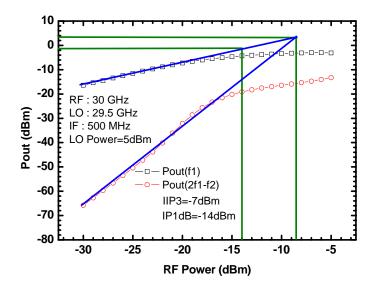

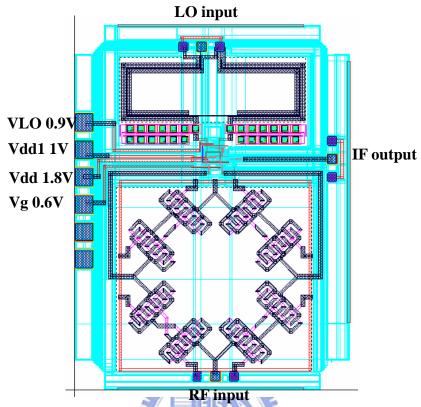

本電路利用 TSMC 013 um CMOS 製程技術,實現一個中心頻率在 30GHz 左右的吉伯特降頻微混頻器。為了減少量測上的不便,在混頻器的 LO、RF 與 IF 端均為單端輸入(出)。在 LO 端採用 Marchand balun 來產生 differential 訊號,在 RF 端利用 Interdigital Rat race 來產生 differential 訊號,而 IF 端則應用電流鏡方式單端輸出。電路架構如圖 4.24 所示:

圖 4.24 Interdigital Rat race 與 Marchand balun 降頻器電路

### 4.4.1 本地震盪源輸入極

LO 端我們採用傳統式的 Marchand balu 來產生 differential 訊號 [7],並且將目標訂在 30GHz 這個頻段,被動電路將會更小。

#### 4.4.2 射頻輸入極

本電路一樣是採用 Gilbert cell mixer 為主要架構核心,由四個電晶體形成一個差動電流開關,在射頻輸入極(RF)利用在第二章節所提到的 Inter-digital Rat race 提供 differential 訊號[8],可縮小被動分合波器的尺寸面積。在傳統的 Gilbert Mixer 架構中,多是 RF 訊號通過Balun 成為 differential 訊號由 Gate 端注入採用 CS 架構,這樣的做法會導致雜訊指數較高、匹配不易和 CS 放大器速度慢等缺點,在操作頻率日漸增高的情況下,不利於高頻使用。另外若要達到 50 歐姆阻抗匹配,得並聯電阻或放入電感,並聯電阻會再度提高雜訊指數,置入電感則大幅增加面積。所以我們在射頻輸入極採用 CG 放大器的架構,並搭配 rat-race 本身的特性,有效達到阻抗匹配與單端轉differential 的效果。

### 4.4.3 輸出緩衝極

在輸出IF端,我們採用PMOS當負載,並利用電流鏡的方式做單端輸出,因為負載阻抗很大,所以混頻器轉換增益也會相對提高很多。

# 4.4.4 模擬結果

圖 4.26 Marchand balun Magnitude (S21 & S31)

30G

Frequency

50G

40G

60G

20G

-50

0

10G

圖 4.27 Marchand balun Phase difference (S21 & S31)

圖 4.28 Inter-digital Rat race 返回損耗 (S11)

圖 4.29 Inter-digital Rat race Magnitude (S21 & S41)

圖 4.30 Inter-digital Rat race Phase difference (S21 & S41)

# 整體模擬結果

圖 4.32 轉換增益 VS. RF Power (P1dB)

圖 4.33 轉換增益 VS. IF Frequency

圖 4.34 轉換增益 VS. RF Frequency

圖 4.35 IM3

表 4.3 Inter-digital Rat race and Marchand balun mixer

| Process            | TSMC 0.13um CMOS |

|--------------------|------------------|

| DC Current         | 12.6mA@2.2V      |

| Conversion Gain    | 13.41dB@LO:-5dBm |

| IP1dB              | -7dBm            |

| IIP3               | -14dBm           |

| LO-to-IF Isolation | N/A              |

| LO-to-RF Isolation | N/A              |

| RF-to-IF Isolation | N/A              |

| Chip Size          | 2.0 mm x 1.5 mm  |

#### Die photo

圖 4.36 Inter-digital Rat race and Marchand balun mixer die photo

# 4.4.5 結果與討論

由圖 4.25、圖 4.26 和圖 4.27 來看被動電路 Marchand balun 模擬的結果,發現操作頻寬非常的寬,且大小相等,相位差 180 度,適合當作混頻器的本地振盪極輸入。而圖 4.28、圖 4.29 和圖 4.30 顯示出被動電路 Inter-digital Rat race 因為相位反轉的結果使得頻寬很寬,並且大小幾乎相等,相位差 180 度。將兩個分合波器整合到混頻中模擬結果發現 LO 在-5dBm 時有 13.41dB 的轉換增益,而 P1dB 為-14dBm,IIP3 則為-7dBm,另外在 RF bandwidth 上面非常寬頻,操作頻率可由20GHz~40GHz 都仍然有著不錯的特性。此晶片待測中。

# 第五章

# 毫米波覆晶封裝之驅動放大器

## 5.1 前言

毫米波頻段系統提供了較寬的頻帶,滿足了現代通訊高速率與大容量的需求,音而成為了近十年來歐、美、日等先進國家無線寬頻通訊產品之重要技術,例如區域多點分佈服務系統(LMDS: Local Multipoint Distribution Service)。目前使用高頻段毫米波頻段的系統甚多,如符合 IEEE 802.16 的寬頻無線接取系統(BWA: Broad band Wireless Access)、23~28 GHz 之高速率無線電數據機(Radio Modem),35~44 GHz 之超小型口徑通訊站(USAT)、60 GHz 之高速率無線區域網路、35~77 GHz 之汽車防撞雷達及衛星通信系統等。

而此章節主要是在介紹在毫米波頻段,操作頻率在 V band (60GHz)的放大器,因為考慮到量測問題,之後希望在 NDL 量測,因在如此高的頻段無法量測其功率等特性,所以設計驅動放大器,以 S 参數為其量測重點。並且進行覆晶封裝(flip chip)的測試,比較 flip chip 前後特性的區別,故先設計頻率在 30GHz 的電路做測試,確定 flip chip 是可行的,再進行操作頻率為 60GHz 的驅動放大器設計。並採取微帶線與共平面波導兩種方式做設計。

因為傳統 bonding wire 對整體電路的影響很大,尤其是在很高頻的時候,所以進而利用低成本的氧化鋁陶瓷基板進行 flip chip,達到即使在高頻下的電路,仍然不影響其特性。

# 5.2 基本放大器設計原理

一般在設計放大器時有幾個依據,其中最重要的兩個大方向即是 穩定度和阻抗匹配的問題,穩定度是希望此放大器不要產生振盪,而 阻抗匹配則是希望能將最大的輸入功率傳送到負載端。底下則針對這 兩個部分進行討論。

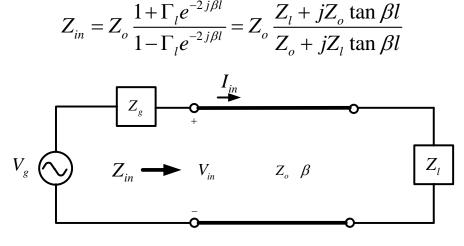

#### 5.2.1 波源和負載之間的阻抗匹配

一般而言,設計放大器時阻抗匹配最很重要的一個部分,依照傳輸線理論,倘若一個傳輸線電路沒考慮到阻抗匹配問題,在傳輸線上會有多重反射,嚴重影響到電路的設計。至於要匹配到多少的阻抗值,目前一般常用的儀器或者電路規格其特性阻抗都是 $50\Omega$ ,其原因是因為在特性阻抗為 $77\Omega$ 時,衰減為最小;而在其特性阻抗為 $30\Omega$ 時,會有最大的傳輸功率,所以 $50\Omega$ 就是取兩者的折衷。[1]

如圖 5.1 所示,有載傳輸線的輸入阻抗為

圖 5.1 有載傳輸線示意圖

而送入到負載的功率為

知道送入負載的功率後,目的是希望能讓負載收到最大的輸出功率, 取功率的極大值,則對功率P對 $Z_{in}$ 的實部與虛部偏微分均為零:

$$\frac{\partial P}{\partial R_{in}} = 0 \longrightarrow \frac{1}{(R_{in} + R_g)^2 + (X_{in} + X_g)^2} + \frac{-2R_{in}(R_{in} + R_g)}{\left[(R_{in} + R_g)^2 + (X_{in} + X_g)^2\right]^2} = 0$$

$$\frac{\partial P}{\partial X_{in}} = 0 \longrightarrow \frac{-2X_{in}(X_{in} + X_g)}{\left[(R_{in} + R_g)^2 + (X_{in} + X_g)^2\right]^2} = 0$$

由上面兩個式子可以解出當 $R_{in} = R_g$ 和 $X_{in} = -X_g$ 時,即 $Z_{in} = Z_g^*$ 會有最大功率的輸出,也就是所謂的共軛匹配。

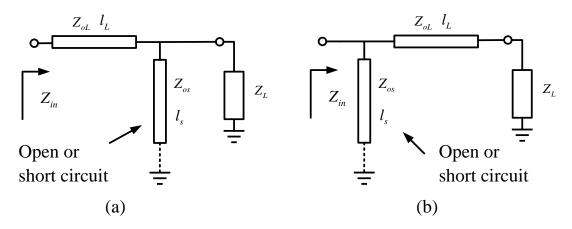

底下將介紹以傳輸線的匹配方式,以利於在設計放大器時達到最大的功率傳輸。一般來說,傳統式的匹配方式不外乎是以電容、電感的方式來達到阻抗匹配,常見的即是L型或T型的匹配方式,但在毫米波頻段時,這些被動電容、電感就不能再使用了,取而代之就是以傳輸線做匹配。而常見的傳輸線匹配方式如下列幾種型式[2]:

## (1)單殘段阻抗匹配(Single-Stub matching networks)

圖 5.2 L 型匹配方式

#### (2)雙殘段阻抗匹配(Double-Stub matching networks)

圖 5.3 多級匹配方式

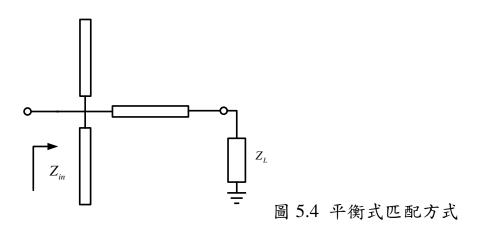

# (3)平衡式殘段阻抗匹配(Balanced Stub matching networks)

#### 5.2.2 穩定度

設計放大器時,穩定度是滿重要的一個問題,如果輸入或輸出端的阻抗實部為負,也就是說, $|\Gamma_{in}| > 1$ 或 $|\Gamma_{out}| > 1$ ,電路就很有可能振盪,所以放大器的穩定性和輸入、輸出端的匹配網路有關。底下將介紹兩種穩定性[3]:

#### (1)無條件穩定

當 $\left|\Gamma_{in}\right|$ <1且 $\left|\Gamma_{out}\right|$ <1時,則此電路為無條件穩定。 也就是必須滿足下列兩個條件:

$$\left|\Gamma_{in}\right| = \left|S_{11} + \frac{S_{12}S_{21}\Gamma_L}{1 - S_{22}\Gamma_L}\right| < 1 \quad \left|\Gamma_{out}\right| = \left|S_{22} + \frac{S_{12}S_{21}\Gamma_S}{1 - S_{11}\Gamma_S}\right| < 1$$

## (2)有條件穩定

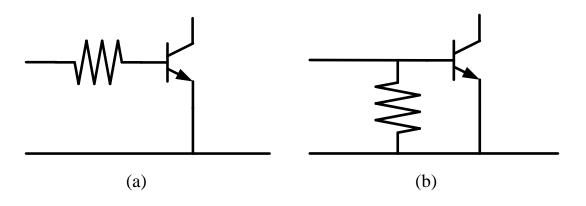

倘若  $\left|\Gamma_{in}\right|$  < 1 和  $\left|\Gamma_{out}\right|$  < 1 只有在特定範的負載阻抗,則稱為有條件穩定,端看在設計匹配網路時,必須將它設計在穩定區內。而如何將有條件穩定的電路轉變為一個穩定的電路將於底下介紹。最常見的就是加電阻讓  $\Gamma$  值落在穩定區內,而加電阻有下列四種方式:

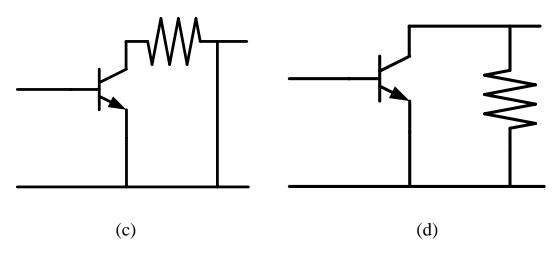

圖 5.5 四種加電阻穩定方式

圖(a)為串聯一個小電阻、圖(b)為並聯一個大電阻,這兩種方式比較使用在一般的驅動放大器或者功率放大器,因為若電阻放在輸出端會降低輸出的功率。而圖(c)為串聯一個小電阻、圖(d)為並聯一個大電阻,這兩種方式則是比較適合在設計低雜訊放大器(LNA)時,因為若將電阻放在輸入端則會增加整體電路的雜訊。

穩定度的分析與數學在此就不詳加贅述,而在確定是否該電路為 無條件穩定可以簡單的看底下式子是否成立

Water Company

當

$$K = \frac{1 - \left| S_{11} \right|^2 - \left| S_{22} \right|^2 + \left| \Delta \right|^2}{2 \left| S_{12} S_{21} \right|} > 1$$

大口  $\left| \Delta \right| < 1$

$$(\Delta = S_{11}S_{22} - S_{12}S_{21})$$

或者可参考底下式子

$$\mu = \frac{1 - \left| S_{11} \right|^2}{\left| S_{22} - S_{11}^* \Delta \right| + \left| S_{21} S_{12} \right|} > 1$$

即是說當 $\mu > 1$ ,則電路為無條件穩定,其 $\mu$ 值愈大,穩定性愈高。

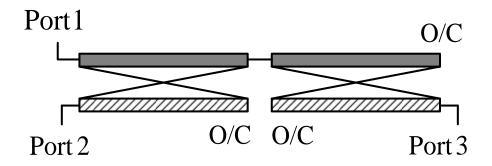

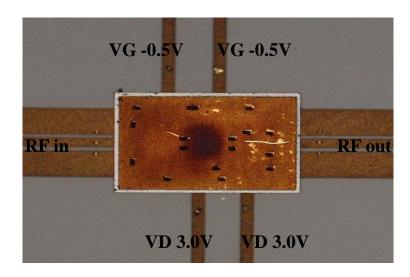

# 5.3 覆晶封裝之 30GHz 微帶線型式驅動放大器 5.3.1 架構簡介

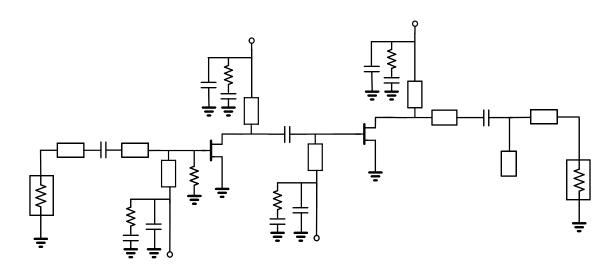

本電路是以 WIN 0.15um PHEMT 製作之兩級驅動放大器,此兩級的放大器架構輸入端與級間的匹配電路採高通型態,目的在於彌補電晶體高頻響應,而為了抑制高次諧波成份輸出端的匹配電路採低通型態,第一級跟第二級的電路匹配以增益匹配為考量。

為了確保電路不會產生振盪,在第一級的電晶體之閘級端均並接了一個電阻,降低電晶體些微的增益,但增加了整個電路的穩定性,達到之前所述之無條件穩定。且因為在如此高頻的頻段表現出增益的特性,所以電晶體尺寸採用最小的,即兩級電晶體尺寸皆為2x50um,洩極電壓為3V,閘極電壓為-0.5V。並在偏壓地方並聯電容及電阻以濾除不必要的雜訊。整體架構如圖5.6所示

圖 5.6 微帶線式 30 GHz 兩級驅動放大器架構

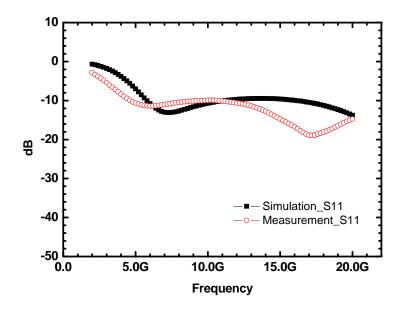

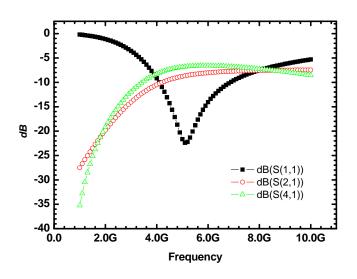

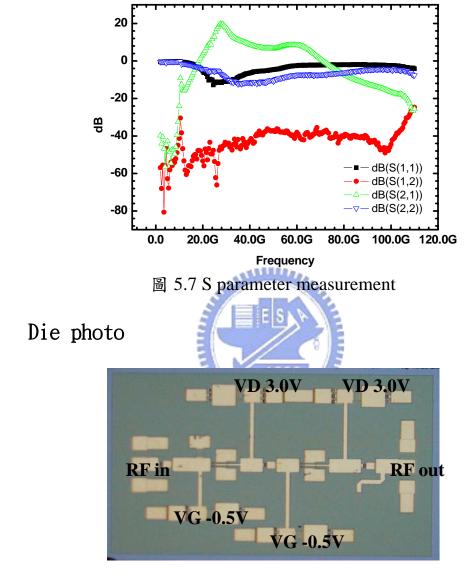

## 5.3.2 晶片量測結果

晶片下線回來後,在NDL利用網路分析儀進行S參數的量測。

圖 5.8 A 30 GHz driving amplifier die photo

量測時利用 NDL 的 on wafer 高頻量測環境。晶片大小為 1.5 um x 1.0 um,除了輸入 和輸出 matching network 外,中間部分為 interstage matching network。

# 5.3.3 覆晶封裝後(flip chip)量測結果比較

圖 5.10 Flip chip 前後輸入返回損耗 (S11)比較

圖 5.11 Flip chip 前後 linear gain (S21)比較

圖 5.12 Flip chip 前後輸出返回損耗 (S22)比較

# Die photo

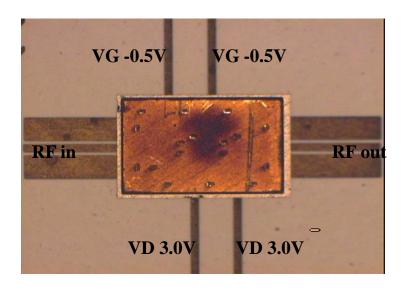

圖 5.13 Flip chip 後 30 GHz MS amplifier die photo

# 表 5.1 Flip chip 前後之 30GHz Amplifier Summary

| Center frequency               | 30G Hz          |

|--------------------------------|-----------------|

| Input Return Loss              | -10.938 dB      |

| Input Return Loss (flip chip)  | -12.081 dB      |

| Output Return Loss             | -8.922 dB       |

| Output Return Loss (flip chip) | -24.245 dB      |

| Linear gain                    | 17.502 dB       |

| Linear gain (flip chip)        | 15.436 dB       |

| Isolation                      | -44.429 dB      |

| Isolation (flip chip)          | -39.2 dB        |

| Die size                       | 1.5 mm x 1.0 mm |

#### 5.3.4 結果與討論

由圖 5.7 所示,在 30GHz 時有 17dB 的增益,且輸入、輸出返回 損耗皆約-10dB 左右,達到原先所設計的規格。而隔離度也在-40dB 以下,整體特性皆有表現出來。

為了驗證 Flip chip 的正確性,將已經量測過後的晶片進行覆晶封裝,再進行量測。圖 5.10、圖 5.11 與圖 5.12 顯示出進行 flip chip 量測後,與原本電路的量測結果差異不大,驗實 flip chip 的可行性。在放大器電路中,我們著中增益的表現,其中由表 5.1 顯示,Flip chip 前在 30GHz 的線性增益為 17.502 dB,而 Flip chip 後為 15.436 dB,其結果差了 2dB,但仍屬於可接受的範圍內;在輸入返回損耗上兩者皆滿一致的,而在輸出返回損耗上,由圖 5.12 可看出過了 25GHz 以後開始與原始量測結果有所不同,反而匹配的效果更好,這是因為在Flip chip 後有可能在加熱處理過程中或長 bump 後所產生與原本電路的匹配,導致 S22 有所改變。

圖 5.13 為將原本晶片覆晶封裝後的結果,將晶片翻轉並黏於陶 瓷基板上,而由 GSG 輸入與輸出的傳輸線皆為 50 毆姆系統,長度約為 1000 um。由以上的量測結果可看出 Flip chip 在 30GHz 左右,其表現出來的特性都還不錯,底下將進行 60GHz 的電路測試與 Flip chip 後的結果比較。

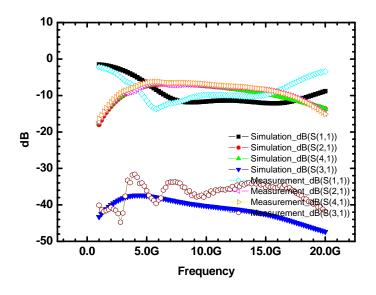

# 5.4 覆晶封裝之 60GHz 微帶線型式驅動放大器 5.4.1 架構簡介

本電路是以 WIN 0.15um PHEMT 製作之兩級驅動放大器,其設計方式大致與上個電路 30GHz 的驅動放大器類似,但因為是操作在 60GHz 如此高頻的頻段下,設計起來很不容易,必須考慮到傳輸線之間耦合的效應。所以在設計過程中必須以 EM 模擬軟體進行模擬,那 我們採用 IE3D 模擬軟體進行模擬,設計兩級 60GHz 驅動放大器。

在兩個電晶體的閘極端並聯適當的電阻,達到整體電路的穩定性。在輸入 matching network 利用 L型 open stub 的匹配方式做匹配,在輸出 matching network 則利用 L型 short stub 做匹配。在 Bias 地方利用細長的傳輸線進行偏壓,使得其特性類似一個 RF choke,RF 部分看到一個高阻抗,且在輸入、輸出與中間級加上 DC block 來阻隔直流部分。整體架構如圖 5.14 所示

圖 5.14 微帶線式 60 GHz 兩級驅動放大器架構

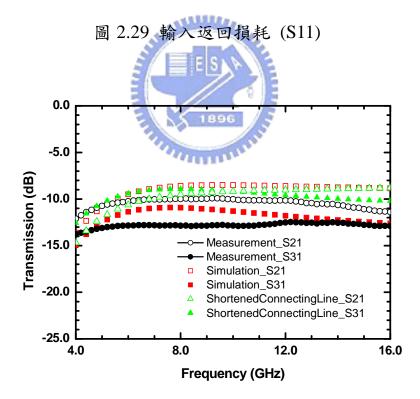

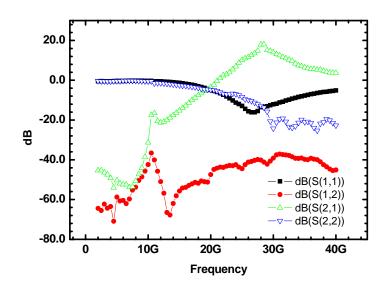

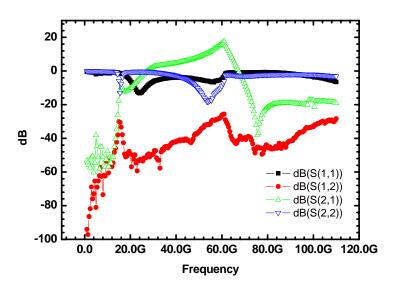

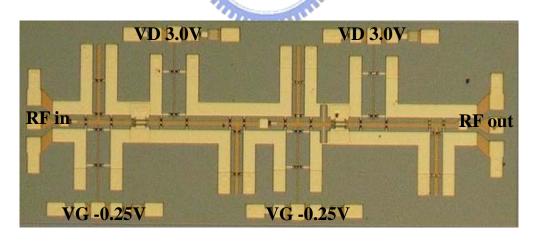

# 5.4.2 晶片量測結果

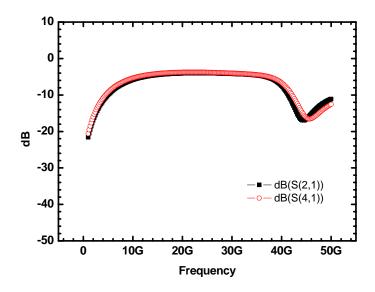

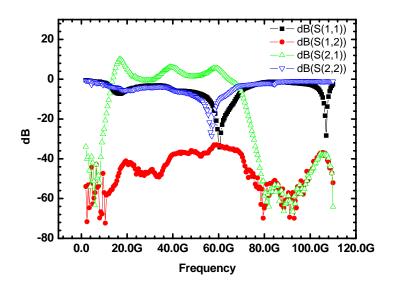

圖 5.15 S parameter measurement

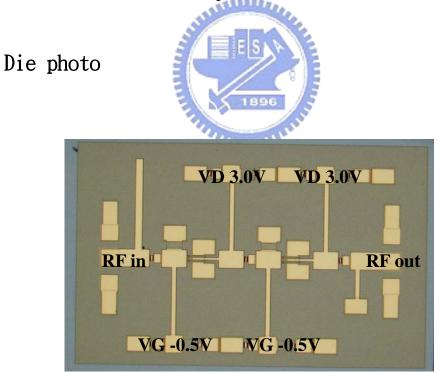

圖 5.16 A 60 GHz driving amplifier die photo

量測時利用 NDL 的 on wafer 高頻量測環境。晶片大小為 1.5 um x 1.0 um。輸入與輸出匹配方式分別利用 open 與 short stub。

# 5.4.3 覆晶封裝後(flip chip)量測結果比較

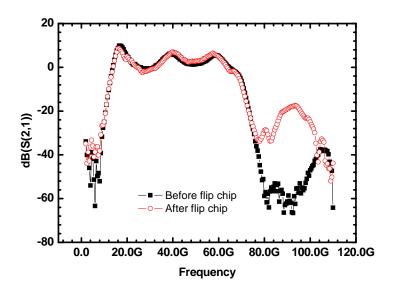

圖 5.17 Flip chip 後量測結果

圖 5.18 Flip chip 前後輸入返回損耗 (S11)比較

圖 5.19 Flip chip 前後 linear gain (S21)比較

圖 5.20 Flip chip 前後輸出返回損耗 (S22)比較

# Die photo

圖 5.21 Flip chip 後 60 GHz MS amplifier die photo

# 表 5.2 Flip chip 前後之 60GHz Amplifier Summary

| Center frequency               | 60 GHz          |

|--------------------------------|-----------------|

| Input Return Loss              | -4.6 dB         |

| Input Return Loss (flip chip)  | -1.328 dB       |

| Output Return Loss             | -5.4 dB         |

| Output Return Loss (flip chip) | -0.548 dB       |

| Linear gain                    | 15.123 dB       |

| Linear gain (flip chip)        | 12.067 dB       |

| Isolation                      | -26.714 dB      |

| Isolation (flip chip)          | -20.348 dB      |

| Die size                       | 1.5 mm x 1.0 mm |

#### 5.4.4 結果與討論

由圖 5.15 顯示 S 參數的量測可看出,此次設計電路操作頻率在 60GHz,且線性增益約有 15dB 左右,輸入和輸出 返回損耗量測結果 約為-5dB 左右,雖達不到原先預計-10dB 以下的規格,但仍屬於可接 受的範圍內,且在增益上有不錯的特性表現。

經過覆晶封裝後可由圖 5.18 所示,除了 30GHz 到 50GHz 這個頻 段的 S11 差異較大以外,其它地方皆與原本電路所量測的結果相似。 再由圖 5.19 可看出 Flip chip 前後增益曲線幾乎都很貼近,但是過了 60GHz 以後開始有點偏離原本的曲線,或許因為是利用微帶線所設計 之 60GHz 的驅動放大器,下一章節會採用共平面波導的方式下去做 設計,再比較 Flip chip 前後的區別,看是否特性會比用微帶線的方式 設計來的更好。另外圖 5.20 顯示出兩者曲線皆滿靠近的。由此次量 測結果,更驗證了 Flip chip 在 60GHz 仍然有不錯的可行性。

圖 5.21 為晶片經由覆晶封裝後的 Die photo。而表 5.2 列出 Flip chip 前後在 60GHz 的特性表現。發現 Flip chip 後的返回損耗變差了,不過對整體而言,仍然與原本電路滿相似的。

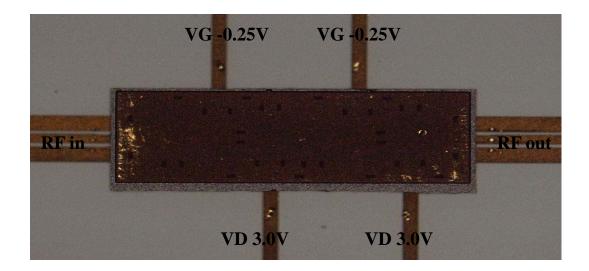

# 5.5 覆晶封裝之 60GHz 共平面波導驅動放大器 5.5.1 架構簡介

本電路同樣是以 WIN 0.15um PHEMT 製作之兩級驅動放大器,在 60GHz 這麼高頻的環境下,再加上以共平面波導(CPW)的方式來設計,在實現在更加不容易,而且共平面波導在模擬軟體裡並沒有內建 Library,所以完全都必須採取 EM 模擬軟體進行設計與考慮傳輸線之間的耦合效應。首先必須先訂定 50 毆姆的共平面波導傳輸線(GSG),包括 G 與 S 之間的 gap 和 S 的 width,還有 ground 要多大才會幾乎驅近於完美的 Ground。另外在匹配方式與傳輸線匹配有點差異,CPW 在繞線上不容易轉彎,所以更不容易匹配,且浪費的面積更大,EM 模擬的時間比傳輸線方式模擬多好幾倍。最重要的是以CPW 方式設計必須加上很多 Air-bridge 將兩邊的 ground 連接起來以避免信號在傳輸的過程中損耗掉。至於電路架構與 MS 60GHz 的放大器一致,只是以 CPW 來實現之。如圖 5.22 所示

圖 5.22 共平面波導式 60 GHz 兩級驅動放大器架構

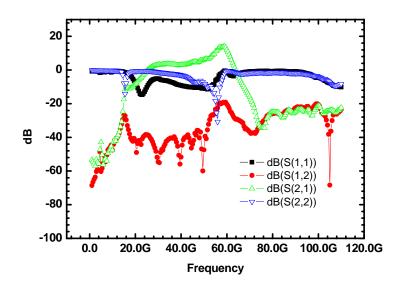

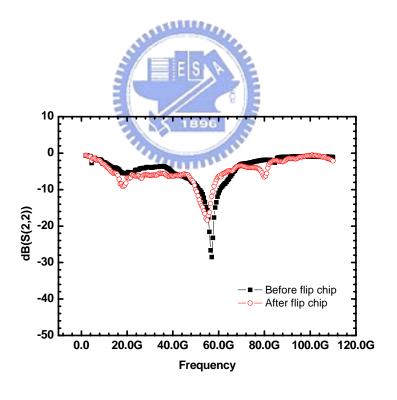

# 5.5.2 晶片量測結果

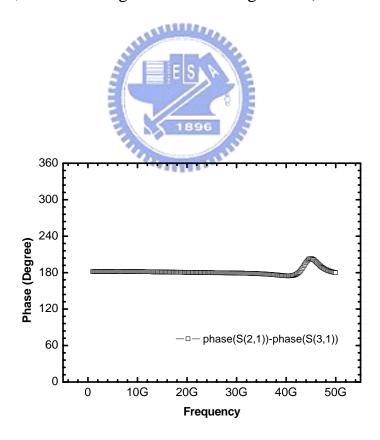

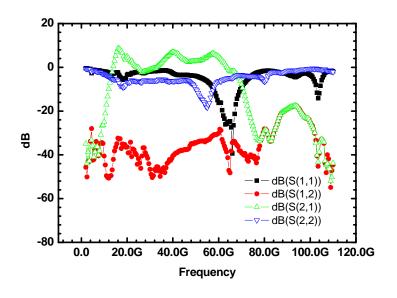

圖 5.23 S parameter measurement

Die photo

圖 5.24 A 60 GHz driving amplifier die photo

量測時利用 NDL 的 on wafer 高頻量測環境。晶片大小為 2.5 um x 1.0 um。在輸入與輸出匹配網路皆利用 open stub 做匹配。

# 5.5.3 覆晶封裝後(flip chip)量測結果比較

圖 526 Flip chip 前後輸入返回損耗 (S11)比較

圖 5.27 Flip chip 前後 linear gain (S21)比較

圖 5.28 Flip chip 前後輸出返回損耗 (S22)比較

# Die photo

圖 5.29 Flip chip 後 60 GHz CPW amplifier die photo

# 表 5.3 Flip chip 前後之 CPW 60GHz Amplifier Summary