## 國立交通大學

電信工程學系

碩士論文

應用於多媒體串流處理之可重組式 運算單元硬體加速矽智產設計

Design and Implementation of an ALU Cluster Intellectual Property as a Reconfigurable Hardware Accelerator for Media Streaming Architecture

研究生:張 紹 宣

指導教授:關河鳴博士

中華民國九十五年七月

# 應用於多媒體串流處理之可重組式 運算單元硬體加速矽智產設計

Design and Implementation of an ALU Cluster Intellectual Property as a Reconfigurable Hardware Accelerator for Media Streaming Architecture

研究生:張紹宣 Student: Shao-Hsuan Chang

指導教授:闕 河 鳴 博士 Advisor:Herming Chiueh

#### **A** Thesis

Submitted to Department of Communication Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master of Science

in

Communication Engineering

July 2006

Hsinchu, Taiwan.

中華民國九十五年七月

# 應用於多媒體串流處理之可重組式 運算單元硬體加速矽智產設計

研究生:張紹宣 指導教授:闕河鳴 博士

國立交通大學 電信工程學系碩士班

### 摘要

ES

現在的生活裡,有著越來越多的行動式系統像是行動電話、MP3 播放器、PDA、以及攜帶式電子遊樂器,其功能與複雜度都較過去上升。因此,對於行動式系統來說大量的多媒體運算能力是必須的,而若是使用傳統的硬體架構來執行這些運算,會因為架構上沒有很好的對應到多媒體檔案的特性,沒辦法很有效率的對多媒體檔案作存取,會使得運算效能低落,最糟糕的是無法達到及時的需求。本論文,為參考史丹佛大學所提出的串流處理器架構,設計了對應多媒體特性的運算單元以提供所需運算能力,除此之外,在考量到了未來使用上的便利性,以及能快速與真實的多媒體應用接軌,將此運算單元加上設計的介面電路後使之成為能與 AMBA 相容的矽智產,如此便能在 ARM 的平台上,利用其他現成的矽智產或是週邊,真實的將此設計變成多媒體運算所需要的硬體加速器。本論文以軟式矽智產完成,並且經過 ARM 系列的基板驗證過所設計的介面電路,確定了所設計的介面電路是符合 AMBA 規定的電路。

## Design and Implementation of an ALU Cluster Intellectual Property as a Reconfigurable Hardware Accelerator for Media Streaming Architecture

Student: Shao-Hsuan Chang Advisor: Dr. Herming Chiueh

Department of Communication Engineering

National Chiao Tung University

Hsinchu, Taiwan

#### **Abstract**

There are more and more portable systems such as mobiles, MP3 player, PDA, and other entertainment systems in today's life. The functionality and complexity of them thus increase much higher than old-time ones. Therefore, having a great deal ability of multimedia operation is important for portable systems. However, it is tough to have enough amounts of multimedia operations from conventional hardware architecture. This results from the poor match between conventional architecture and features of media applications. It hence leads to inefficient memory access that induces performance degression. The worst case is unable to meet the real time requirement.

According, this thesis designs an operational unit, ALU cluster, that is referenced from Stanford's stream processor architecture and thus matches to media applications to provide necessary processing requirements for media applications. Besides, considering the issues of convenient usage in the future and rapid integration of real multimedia applications, we wrap ALU cluster as an AMBA-compatible IP by adding designed interface. Then, it is possible to exploit other existing IP and peripherals in the AMBA platform and truly treats our design as hardware accelerator for real multimedia applications. This thesis is finished with a synthesizable soft IP. The designed interface is verified by ARM-series baseboard. This ensures that the interface conforms to AMBA specification.

#### **ACKNOWLEDGMENTS**

This thesis would not have been possible without the support of many exceptional people. First and foremost, thanks go to my research advisor, Professor Herming Chiueh. He has always been an inspiration to me and everyone else on this project through his vision and leadership. He also provided irreplaceable guidance for me when I needed for a fascinating problem, good advice, constructive criticism, support, and flexibility.

I would also like to thank all team members of the SoC LAB group, especially my classmates over the years: We-Li Su and Joseph Tsai. They not only put up with me all of those years, but also made my days as an enjoyable graduate student.

Finally, I can not say enough about the support provided by my family. My parents have been my biggest supporters and for that I am forever grateful. My girlfriend has always providing timely encouragement and advice. To all of my friends and family members who have helped me in one way or another over the years, I would like to say thanks.

#### **CONTENTS**

| 摘要   | <del>5</del>                                                     | Ι   |

|------|------------------------------------------------------------------|-----|

| Abs  | tract                                                            | II  |

| Ack  | nowledgement                                                     | III |

| List | of Table                                                         | VI  |

| List | of Figure                                                        | VII |

| Cha  | pter 1 Introduction                                              | 1   |

| 1.1  | Issues of Media Applications                                     | 1   |

| 1.2  | Proposed design: An ALU Cluster Intellectual Property (IP)       | 3   |

| 1.3  | Organization                                                     | 5   |

| Cha  | pter 2 Background                                                | 6   |

| 2.1  | Reconfigurable Architectures for Media Applications              | 6   |

| 2    | .1.1 Stream Processor Architecture                               | 7   |

| 2    | .1.2 Stream Processing Model                                     | 8   |

| 2    | .1.3 Implementations of Stanford's Stream Processor Architecture | 9   |

| 2.2  | Design Methodology in the SoC Era                                | 11  |

| 2.3  | Overview of AMBA                                                 | 13  |

| 2    | .3.1 Overview of AMBA AHB                                        | 15  |

| 2    | .3.2 Bus Connection                                              | 16  |

| 2    | .3.3 Signals of AHB Interface                                    | 17  |

| 2    | .3.4 Address Decoding                                            | 18  |

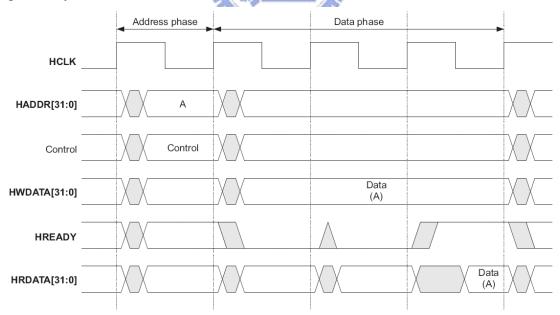

| 2    | .3.5 Basic Transfer                                              | 19  |

| 2    | .3.6 Transfer Type                                               | 20  |

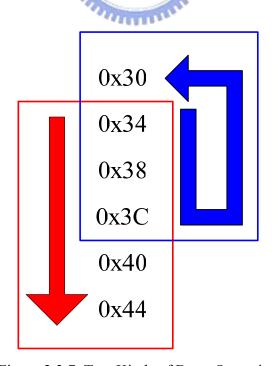

| 2    | .3.7 Burst Operation                                             | 21  |

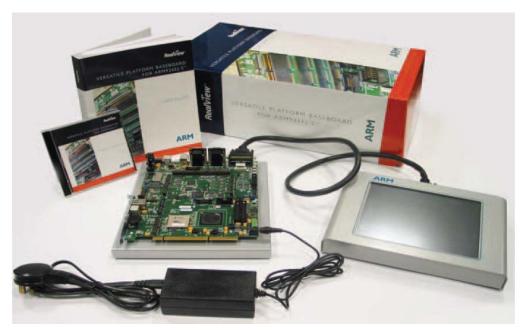

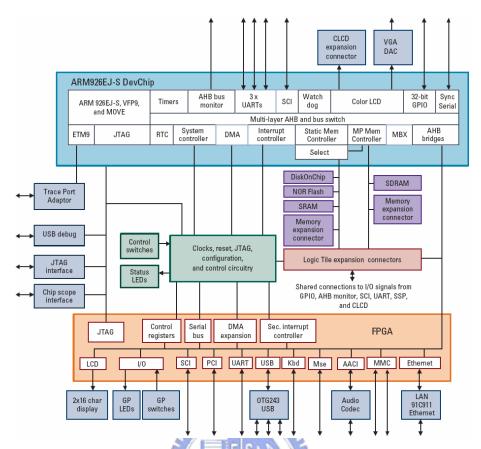

| 2.4  | Overview of Emulation Environment                                | 23  |

| 2.5  | Summary                                                          | 25  |

| Chapter 3 Design and Implementation of an ALU Cluster Intellectual | 26 |

|--------------------------------------------------------------------|----|

| Property                                                           |    |

| 3.1 An ALU Cluster                                                 | 27 |

| 3.1.1 Architecture of an ALU cluster                               | 27 |

| 3.1.2 Implementation Results                                       | 28 |

| 3.1.3 Chip Testing                                                 | 31 |

| 3.1.3.1 Testing Environment                                        | 32 |

| 3.1.3.2 Testing flow and result                                    | 33 |

| 3.2 Design and Emulation for the AHB Slave Wrapper of Intellectual | 35 |

| Property                                                           |    |

| 3.2.1 Architecture of AHB Slave Wrapper                            | 35 |

| 3.2.1.1 Finite State Machine of AHB Slave Wrapper                  | 36 |

| 3.2.2 Modifications for Baseboard and Data Preparing               | 38 |

| 3.2.3 Emulation Result                                             | 40 |

| 3.3 An ALU Cluster Intellectual Property                           | 42 |

| 3.3.1 Architecture of an ALU Cluster Intellectual Property         | 42 |

| 3.3.2 Functional Verification                                      | 43 |

| 3.3.2.1 Testbench: 16-tap FIR filter System                        | 44 |

| 3.3.2.2 Simulation Results                                         | 45 |

| 3.3.3 Improvements from ALU Cluster to ALU Cluster IP              | 49 |

| 3.3.4 Extension of ALU cluster IP at magnetic RAM (MRAM)           | 51 |

| 3.3.4.1 Overview of MRAM                                           | 51 |

| 3.3.4.2 Modifications for MRAN                                     | 51 |

| 3.3.4.3 Implementation Result                                      | 52 |

| 3.4 Implementation Comparisons                                     | 54 |

| 3.5 Summary                                                        | 56 |

| Chapter 4 Conclusion and Future Work                               | 57 |

| Bibliography                                                       | 59 |

| Appendix A: Assembly Code for Chip Testing                         | 62 |

| A.1: Assembly Code for FIR                                         | 63 |

| A.2: Access Method for Memory Testing                              | 66 |

| Appendix B: Memory Map                                             | 69 |

### LIST OF TABLES

| Table 2.1 | SPECIFICATION OF STREAM PROCESSOR ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2 | BURST SIGNAL ENCODING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22  |

| Table 2.3 | ACTICE BYTE LANES FOR A 32-BIT LITTLE ENDIAN DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23  |

| Table 2.4 | ACTICE BYTE LANES FOR A 32-BIT BIG ENDIAN DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Table 3.1 | SUMMARY OF AN ALU CLUSTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29  |

| Table 3.2 | TESTING RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 34  |

| Table 3.3 | MODIFICATIONS FROM ALU CLUSTER TO ALU CLUSTER IP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 49  |

| Table 3.4 | SUMMARY OF IMPLEMENTATION RESULTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53  |

| Table 3.5 | TABLE OF IMPLEMENTATED COMPARSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 55  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| Table A.1 | THE OPERATIONS CORRESPONG TO THE ALU UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62  |

| Table A.2 | THE OPERATIONS CORRESPONG TO THE MUL UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62  |

| Table A.3 | THE OPERATIONS CORRESPONG TO THE DIV UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62  |

| Table A.4 | ASSEMBLE CODE FOR FIR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 63, |

|           | 1896                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 64, |

|           | The state of the s | 65  |

| Table A.5 | ACCESS TABLE FOR ODD BANK MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 66, |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67  |

| Table A.6 | ACCESS TABLE FOR EVEN BANK MEMORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 67, |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68  |

### LIST OF FIGURES

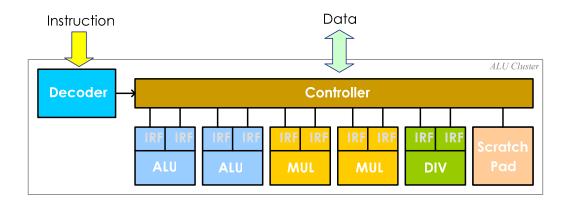

| FIGURE 1.2.1 PROPOSED ALU CLUSTER IP                        | 4  |

|-------------------------------------------------------------|----|

| FIGURE 2.1.1 STREAM PROCESSOR ARCHITECTURE                  | 8  |

| FIGURE 2.1.2 STREAM PROCESSING MODEL OF FIR FILTER SYSTEM   | 9  |

| FIGURE 2.1.3 CHIP IMPLEMENTATION OF STREAM PROCESSOR        | 10 |

| ARCHITECTURE                                                |    |

| FIGURE 2.2.1 AN ASIC DESIGN                                 | 11 |

| FIGURE 2.2.2 AN EXAMPLE OF PLATFORM DESIGN                  | 13 |

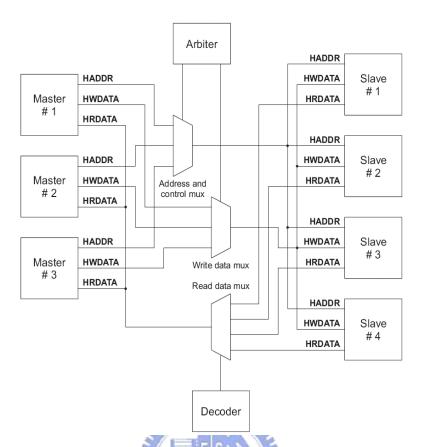

| FIGURE 2.3.1 A TYPICAL AMBA SYSTEM                          | 15 |

| FIGURE 2.3.2 DIAGRAM OF BUS CONNECTION                      | 16 |

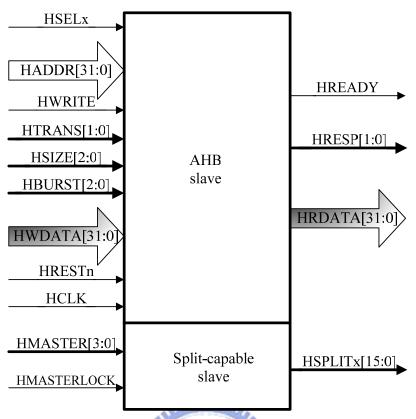

| FIGURE 2.3.3 DIAGRAM OF AHB SLAVE                           | 17 |

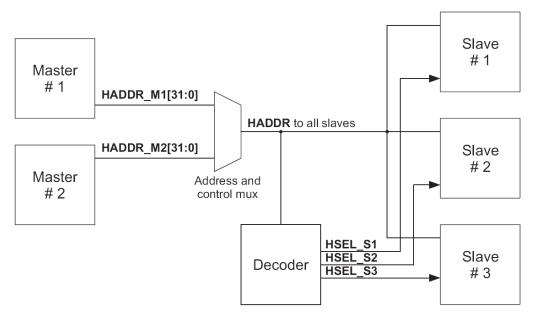

| FIGURE 2.3.4 SIGNALS TO SELECT WHICH SLAVE                  | 18 |

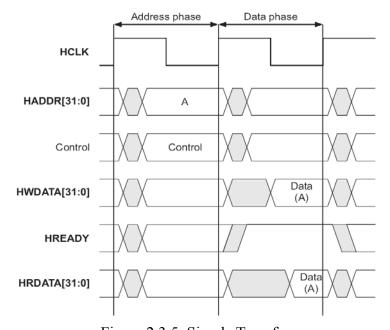

| FIGURE 2.3.5 SIMPLE TRANSFER                                | 19 |

| FIGURE 2.3.6 TRANSFER WITH TWO WAIT                         | 20 |

| FIGURE 2.3.7 TWO KINDS OF BURST OPERATION                   | 22 |

| FIGURE 2.4.1 VERSATILE PLATFORM BASEBOARD FOR ARM926EJ-S    | 24 |

| FIGURE 2.4.2 ARCHITECTURE OF VERSATILE PLATFORM BASEBOARD   | 25 |

| FIGURE 3.1.1 ARCHITECTURE OF AN ALU CLUSTER                 | 27 |

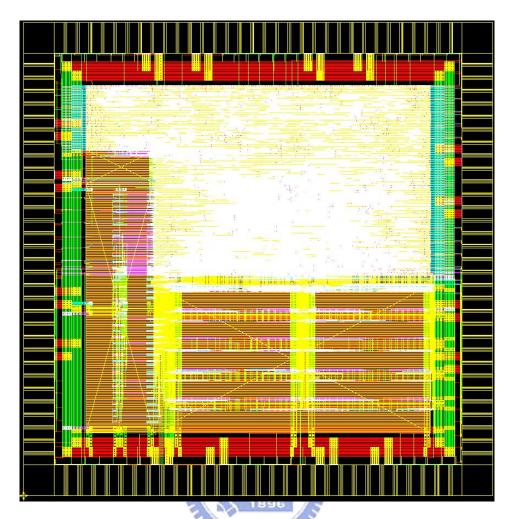

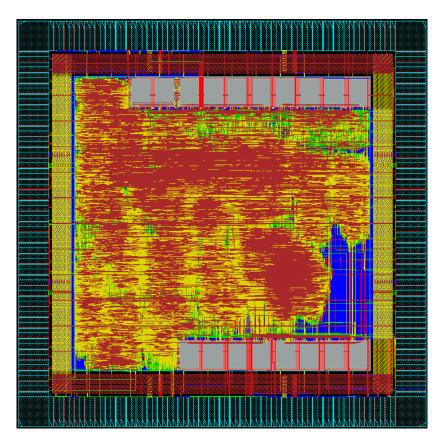

| FIGURE 3.1.2 LAYOUT OF AN ALU CLUSTER                       | 29 |

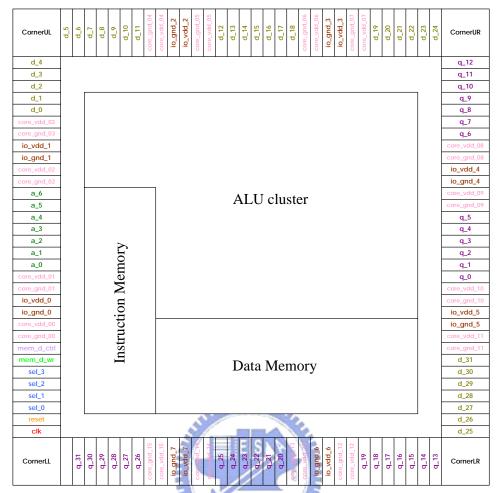

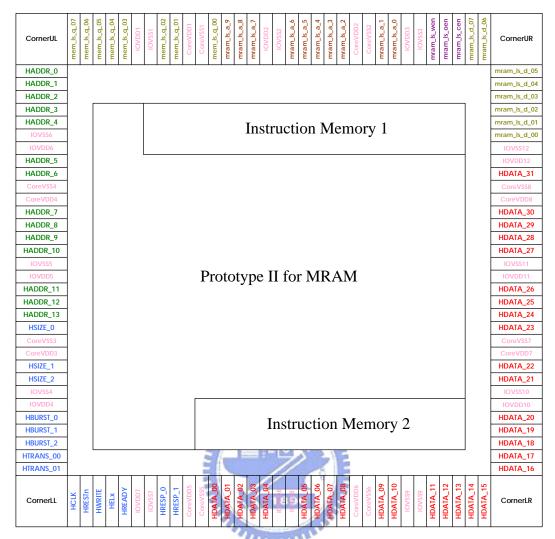

| FIGURE 3.1.3 FLOORPLAN AND PAD ASSIGNMENT OF AN ALU CLUSTER |    |

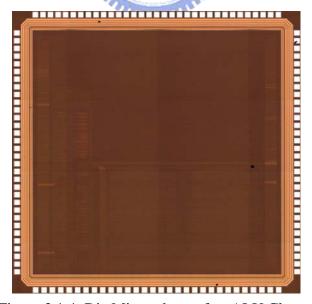

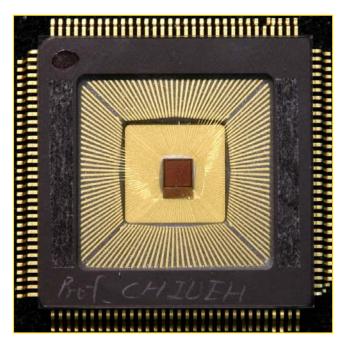

| FIGURE 3.1.4 DIE MICRO PHOTO OF AN ALU CLUSTER              | 30 |

| FIGURE 3.1.5 PACKAGE OF AN ALU CLUSTER                      | 31 |

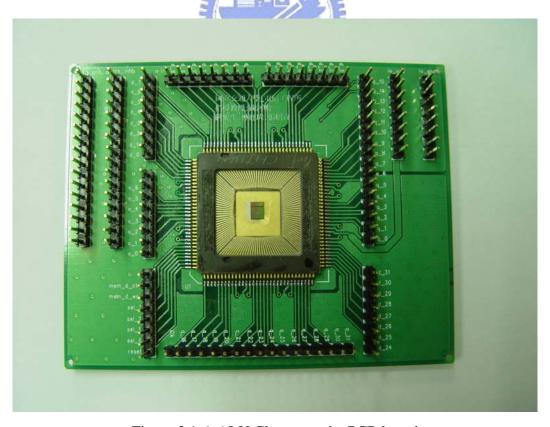

| FIGURE 3.1.6 AN ALU CLUSTER ON THE PCB BOARD                | 32 |

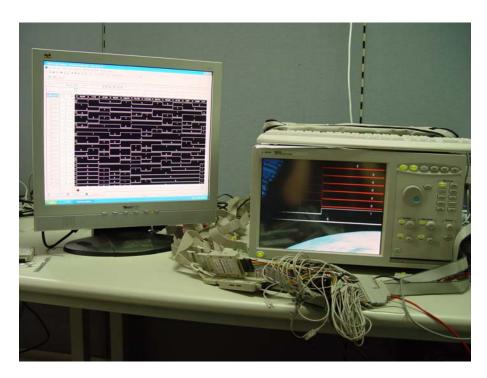

| FIGURE 3.1.7 LOGIC ANALYZER SYSTEM WITH LCD MONITOR DISPLAY |    |

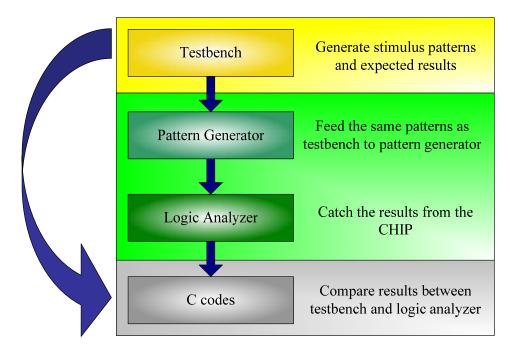

| FIGURE 3.1.8 TESTING FLOW OF CHIP LEVEL TESTING             | 34 |

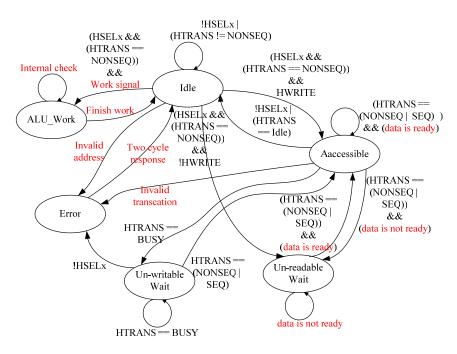

| FIGURE 3.2.1 ARCHITECTURE OF AHB SLAVE WRAPPER              | 35 |

| FIGURE 3.2.2 FINITE STATE MACHINE                           | 36 |

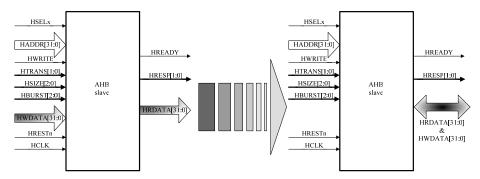

| FIGURE 3.2.3 PORTS MODIFICATIONS                            | 39 |

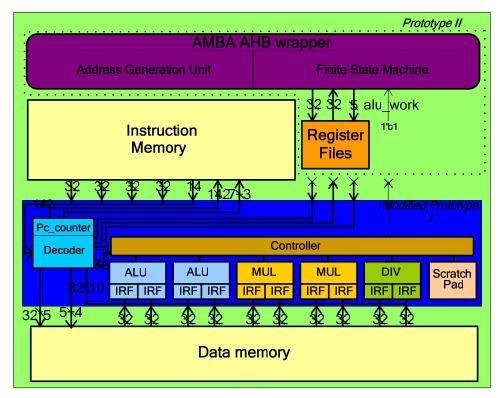

| FIGURE 3.2.4 MODIFICATIONS WITH ADDED REGISTER FILES        | 40 |

| FIGURE 3.2.5 SOFTWARE CODES FOR ADS                         | 42 |

| FIGURE 3.2.6 ADDRESS DEFINITION                             | 42 |

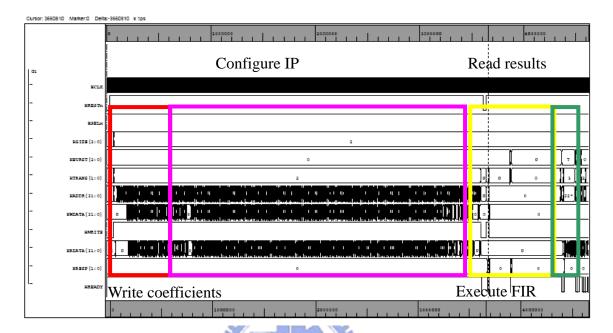

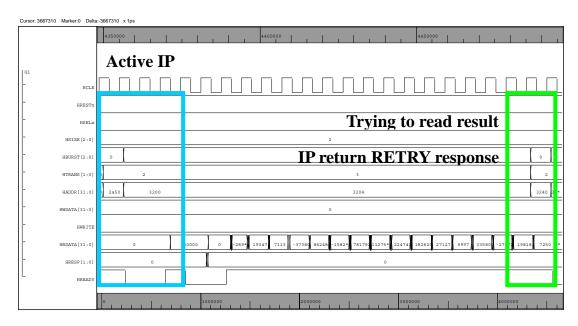

| FIGURE 3.2.7  | EMULATION RESULTS                                   | 43 |

|---------------|-----------------------------------------------------|----|

| FIGURE 3.3.1  | ARCHITECTURE OF AN ALU CLUSTER IP                   | 43 |

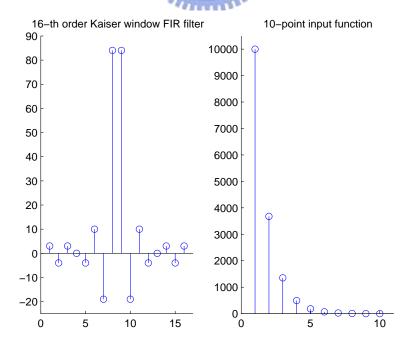

| FIGURE 3.3.2  | COEFFICIENTS OF THE FIR FILTER SYSTEM AND ITS INPUT | 44 |

|               | FUNCTION                                            |    |

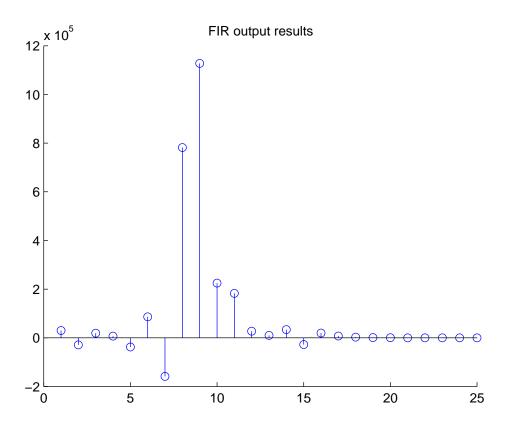

| FIGURE 3.3.3  | EXPECTED OUTPUT RESULTS OF THE FIR FILTER SYSTEM    | 45 |

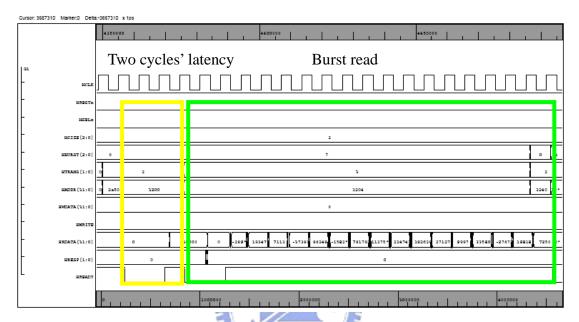

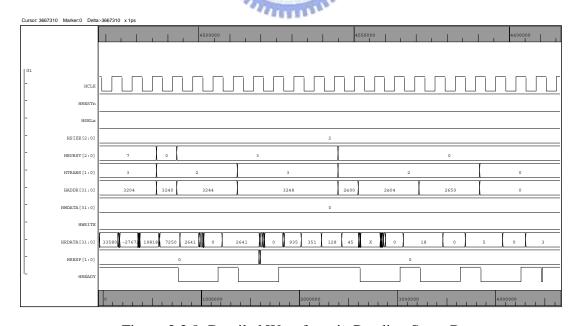

| FIGURE 3.3.4  | FULL WAVEFORM VIEW OF SIMULATION                    | 46 |

| FIGURE 3.3.5  | DETAILED WAVEFORM IN EXECUTION STAGE A              | 47 |

| FIGURE 3.3.6  | DETAILED WAVEFORM IN EXECUTION STAGE B              | 47 |

| FIGURE 3.3.7  | DETAILED WAVEFORM IN READING STAGE A                | 48 |

| FIGURE 3.3.8  | DETAILED WAVEFORM IN READING STAGE B                | 48 |

| FIGURE 3.3.9  | MODIFICATIONS FOR MRAM WITH ADDED LOAD_STORE UNIT   | 52 |

| FIGURE 3.3.10 | LAYOUT OF AN ALU CLUSTER IP EXTENDED AT MRAM        | 53 |

| FIGURE 3.3.11 | FLOORPLAN OF AN ALU CLUSTER IP EXTENDED AT MRAM     | 54 |

# CHAPTER 1 Introduction

With the technology improving, there are many media applications related to our life such as mobiles, MP3 player, PDA, and other portable entertainment system. It is hard to avoid the usage of these products because it is convenient to use them for watching movies, listening to music, and even playing video games at anywhere and anytime. The functionality of them keeps growing day by day. Thus, the processing requirements of media applications are more and more important right now. However, the conventional architecture with only single processor is hard to handle all jobs by itself. Therefore, another solution according to the features of media applications must be brought up to overcome the growing processing requirements.

#### 1.1 Issues of Media Applications

It is known that media applications have three main characteristics: large available parallelism, little data reuse, and a high computation to memory access ratio [1] [2]. The first one, large available parallelism, is due to each streaming is independent to others. Thus, each streaming is possible to be operated solely at the same time. Little data reuse results from the streaming element reading from the memory only accesses memory once and do not revisit again, causing poor performance to the cache in the conventional architecture. Large amount of data operations result in high computation to memory access ratio is needed is the third characteristic. All these characteristics are poorly matched to conventional architectures and the performance will be extremely awful while media applications running on conventional ones. It must have another dedicate design to solve these issues by multiple operational units and efficient bandwidth hierarchy.

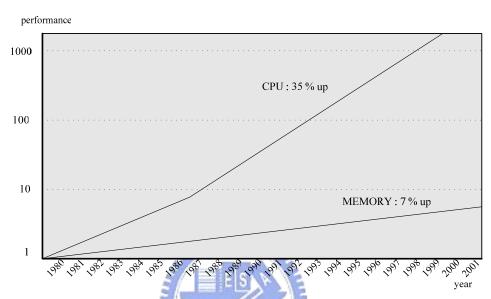

From the media characteristics, we know memory access is the most serious problem for processing of media applications. In the mean time, the processor and memory performance gap that reveals the performance growing of memory is much slower than processor, as shown in Figure 1.1.1 [3]. This phenomenon will cause more latency for memory access. That means communication between processor and memory is more precious.

Figure 1.1.1: Processor-Memory Gap

Fortunately, in the modern VLSI technology, as the process goes down to the deep submicron, it is possible to put lots of arithmetic logic unit (ALU) on a single chip in low cost [4] [5] [6]. It means that many operations are able to be executing at the same time by lots of functional units with little area cost. It is a great help for parallel processing. Summing up features of media applications and evolution of technology, there are many researches that are trying to improving the disability of conventional architecture by their own architectures such as Application Specific Integrated Circuit (ASIC), Platform-Based Architecture, and Reconfigurable Architecture. ASIC is specific to one application. It thus can have most balance to power, area, and performance. However, it lacks of flexibility to reuse design while the specification changes. Platform-Based Architecture consists of a processor core, memory, peripherals and other intellectual property (IP) with the same interface as hardware accelerator. By changing different IP, the same platform can be reused for distinct usages. The IP is mostly from ASIC by adding interface to solve different purposes. Although the flexibility of Platform-Based Architecture is better than ASIC, it still needs to change different IP for varied purposes. It is a characteristic, supporting application is limited, from ASIC. Therefore, Reconfigurable Architecture

is another choice. It will use many general purpose operational units. As the demand is modified, the operational units are modified by reconfiguration, too. It therefore uses the same hardware to achieve different purposes. Details about architectures listed above and design methodology will be addressed in Chapter 2.

#### 1.2 Proposed design: An ALU cluster IP

According to the issues of media applications and three associated architectures, we choose IP as a our target to process media applications, because we can get best trade-off from some physical issues, reuse other ready components to simplify developing efforts, and make our IP reusable for further possible development. In order to provide a more powerful ability for our IP, we reference from Stanford's stream processor that is a reconfigurable architecture and thus develop our IP as a reconfigurable hardware accelerator for media applications [7].

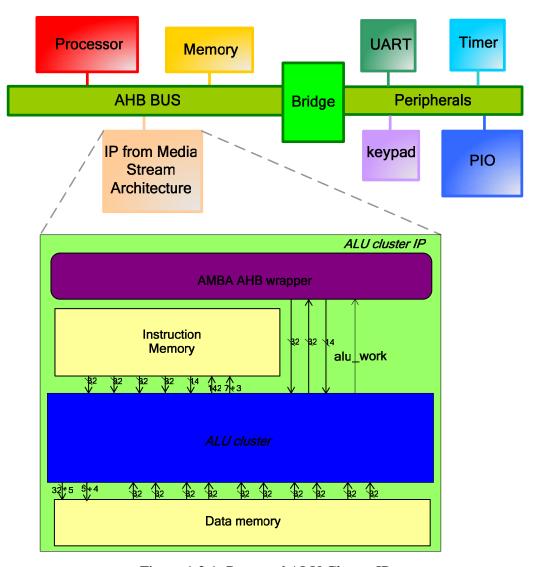

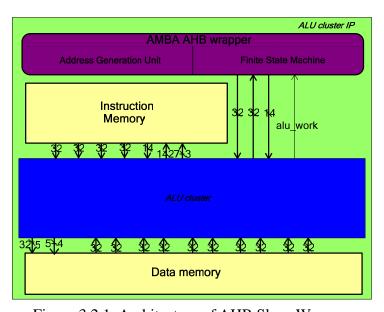

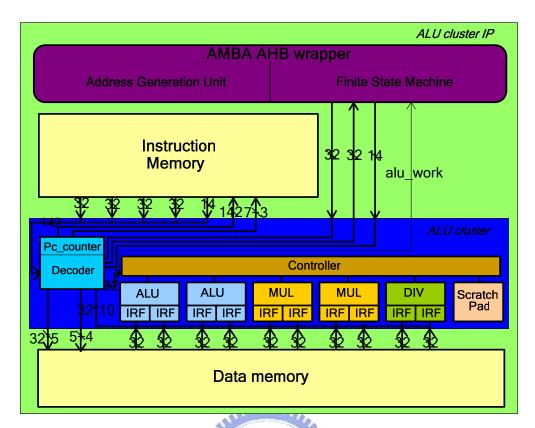

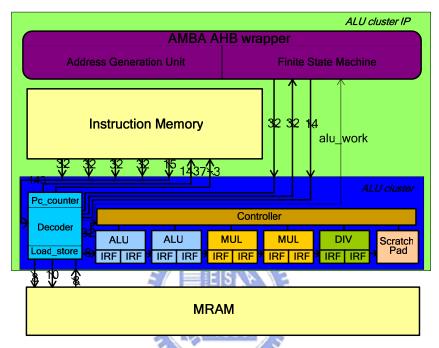

The stream processor architecture is designed for media applications. Therefore, it matches the features of media ones and can handle them very well. However, it is a complete and huge system. Thus, it requires many human resources and much time to implement it. As a result, we select the processing part, ALU cluster, to be wrapped as an IP. Then, it can reduce efforts for developing a architecture to deal with media applications and be reused in the further. Details about stream processor architecture will be demonstrated in Chapter 2. The proposed design is shown in Figure 1.2.1. It is an ALU cluster IP that is compatible to AMBA-based platform. This platform may contain some available blocks such as processor, memory, other peripherals, and our intentional IP that is wrapped from an innovated ALU cluster from the stream processor architecture, as shown in the bottom part of the figure.

Therefore, our proposed IP can be divided as hardware and software parts. The hardware part includes AMBA-AHB wrapper, ALU cluster, and memory. As for software, it must have architecture simulator to decide the number of internal operational units, depth of internal memory, and so on. The ALU cluster and architecture simulator are finished by our seniors last year [8] [9]. Taking these two previous designs as basement, some improvements are added to increase its performance that will be shown in Chapter 3.

Figure 1.2.1: Proposed ALU Cluster IP

The advantages of the usage of the AMBA-based platform will be addressed in the Chapter 2. One major reason for choosing AMBA bus as a platform is because we take most care of connecting our design with real media applications. This can be benefited from the complete environment of AMBA bus. Except for the free specification of AMBA bus, there are already many baseboards and software that help to accelerate the design procedure. With these basebaords, there are mamy ready IPs, including processor core, memory, and peripherals, can be used directly. Besides, they are controlled by adequate software. Thererfore, these hardware and software are helpful to accelerate development. Details about the used platform and baseboard are in Chpater 2.

#### 1.3 Organization

The motivation for the thesis is introduced in this Chapter. The remaining of organization about this thesis is as follow. In the Chapter 2, the first part will introduce architectures memtioned above for media applications, and the second part will discuss the design methodology. This section induces us to establish AMBA-base platform. Then, the overview of AMBA on-chip bus and AHB slave protocol will be presented. The last section is the introduction of emulation environment

The Chapter 3 is the main chapter about the design and implementation of the ALU cluster IP. The first section demonstrates the implementation results of ALU cluster, prototype I, and its testing outcomes. The second part is the hardware emulation of AHB wrapper by ARM baseboard. The following is the architecture, simulation results, and modifications of the ALU cluster IP. The last one is about IP that is extended to implement a real chip with magnetic RAM (MRAM) as data memory [10]. Then, the conclusion and future work will be addressed in the last chapter.

# CHAPTER 2 Background

In this chapter, the related review of background about two architectures are used to deal with media applications, design methodology, AMBA specification of AHB protocol for the design, and used platform baseboard in this thesis is described. The first section will address reconfigurable architectures for media applications; they are DIVA and stream processor architecture [7] [11]. We will focus on stream processor architecture that is what we choose to further development. The second section is about the trend of design methodology, it reviews from ASIC to platform-based architecture. This section induces us to establish an AMBA-based platform that will advantage to further development. The third section is overview of the AMBA on-chip bus and the AHB slave protocol will be introduced most. As for the other details about AMBA bus, they could be found in the AMBA specification. The last section is about emulation environment that is our used platform baseboard in this thesis.

#### 2.1 Reconfigurable Architectures for Media Applications

As we know from the introduction, media applications need an architecture that is different from conventional one to increase the processing requirements. Two kinds of architectures will be shown up. First, DIVA architecture will be introduced shortly. Then, the stream processor architecture is addressed.

Brief speaking, DIVA is an architecture that integrates processor logic and memory in a processing-in-memory (PIM) chip. The advantages of its architecture is that internal PIM processors are directly connected to the memory banks, the memory bandwidth is dramatically increased (up to 2 orders of magnitude, tens or even hundreds of gigabits aggregate bandwidth on a chip). Latency to on-chip logic is also

reduced, down to as little as one-fourth that of a conventional memory system, because of the usages of internal memory access without the associated delays by communicating to off chip. It thus overcomes the large amount of memory demands and provides the ability to handle media applications. However, this architecture must have completely mechanism to communicate between each PIM. This will cause that extra efforts are needed to investigate the communications. Besides, the communicated protocol is not a general one that could not be portable to other hardware. Thus, it is not worthy to put much more efforts on it. We therefore choose stream processor as our reference architecture for further development.

#### 2.1.1 Stream Processor Architecture

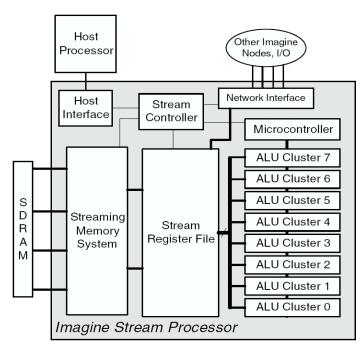

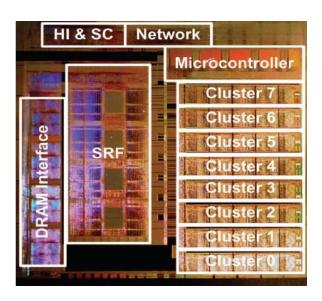

By trading off from features of media applications and growing technology, Stanford proposes the programmable stream processor architecture with three accents that are locality, concurrency and bandwidth hierarchy to better the processing performance of media applications. The stream processor architecture is shown in Figure 2.1.1 [12] [13]. It consists of ALU clusters, stream register file, streaming memory system, stream controller, micro controller, and host interface. The core of working part of that architecture is the eight ALU clusters. These eight ALU clusters achieve one of the features, the concurrency processing. They are controlled by microcontroller in single instruction multiple data (SIMD) manner. Therefore, all ALU clusters getting the same instructions from microcontroller and operate on different data streaming. Besides, these are very long instruction word (VLIW) instructions, performing compound stream operations on each streaming elements.

There are many embedded local register files in the ALU clusters. The embedded local register files make the processing in local and accomplish the feature of locality. The streaming memory system is the interface to connect off chip SDRAM and is able to solve rare data bandwidth and provide ability to schedule dynamically. The stream register file is the novel organization of high performance memory pool and is used to store streaming of any length. Together with local register file, the stream register file can efficiently re-circulate streaming with different ALU clusters and perform the last characteristic of bandwidth hierarchy by storing the data from the streaming memory system to itself. By programming varied instructions, it is possible to execute different media applications. Stanford use stream processing model to map the media application into the stream architecture. The stream programming model allows simple control, makes explicit communication, and exposes the inherent parallelism of media applications. It will be discussed in next section.

Figure 2.1.1: Stream Processor Architecture

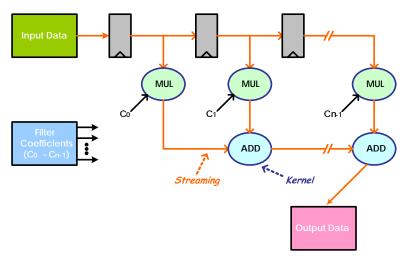

#### 2.1.2 Stream Processing Model

The processing flow of media applications is certainly like a sequence of computation kernels that operate on long data streaming. The kernel is a small program that repeats its operation for the continuous input streaming and produces the output streaming for the following subsequent kernels. The streaming is a variable length collection of records and these records are logical grouping of media data. An example of stream processing model is shown in Figure 2.1.2. It is one kind of media applications, the finite impulse response (FIR) filter system [14]. An FIR filter is a one dimensional convolution. It only has two kinds of kernel, MUL and ADD which are also the common operations in the media operations, over a long data streaming. Thus, the FIR filter system is a good demonstration for stream processing model. The equation 2.1 describes its operation:

$$y[n] = \sum_{k=0}^{M-1} b_k * x[n-k]$$

(2.1)

The y[n] represents the output data streaming of the FIR filter system. It is the weighted average of the of input data streaming, x[n], from x[n] to x[n-M+1], with the weights given by the coefficients  $b_k$ . The coefficient of n represents its instant time for both x[n] and y[n]. The coefficient of k stands for the number of taps in the filter, and  $b_k$  is nth tap coefficient.

Figure 2.1.2: Stream Processing Model of FIR Filter System

The kernel in the stream processing model reveals the possibility to process media applications: parallel and pipeline execution. Multiple kernels can activate at the same time on independent streaming data. The front side kernel handles its input streaming and produces the output streaming and the streaming data is then passed to be processed by the next kernel. Therefore, the kernels are not only parallel but also pipeline to cope with the media data. Since all data are organized as streaming, only single memory access from off chip is required and the succeeding transfers are from register to register. It is helpful to optimize for bandwidth requirement. As a result, the memory bandwidth demands of the media applications can be solved by exploiting this stream processing model.

Mapping the media applications to proper kernels and streams expose the characteristics that are enumerated in previous section, large available parallelism, little data reuse, and high computation to memory access ratio, so that the hardware can easily exploit them and achieve the needed performance requirements.

#### 2.1.3 Implementations of Stanford's Stream Processor Architecture

We now take a look at Stanford's work. The chip is shown in Figure 2.1.3. The eight ALU clusters are in the right side, and the microcontroller is on top of them. The stream register file is at the center. The left side is the interface to off-ship DRAM. The other modules are in the top side. The chip is placed similar to the block diagram as shown Figure 2.1.1.

The specification is shown in table 2.1. It is fabricated in the 1.5V  $0.15~\mu m$  process with five layers of aluminum metal by Texas Instruments (TI). The peak

performance is at 180M Hz. The power dissipation running at 180M Hz is around 8 to 10W, and the best power-efficient is at the operating point of 1.2v at 96M Hz. The total gate count is 21 million, and the chip area is 2.6 cm<sup>2</sup>.

As shown in figure and table, it is obviously that the whole architecture of the stream processor architecture is complete and huge. The inventor, Stanford, spends eight graduate students to complete all the architecture including design and verification. As shown in the Figure 2.1.3, there are many different modules of different functionality. The module level test must be exercised completely to ensure the pre-defined functionality is correct. Then, it is necessary to verify the integration of these modules. However, the fully system simulation takes much time and needs high level cycle accurate simulation model to shorten it. This model will also require some human resources. Aside from these issues, how to map the stream processor architecture to operating system (OS) and perform a real application on the stream processor architecture are the other two subjects. As long as running real media applications on the design, it thus is convincible.

Table 2.1: Specification of Stream Processor Architecture

| 1                         |                    |

|---------------------------|--------------------|

| Process                   | TI 0.15 um (1.5V)  |

| Performance               | 180 MHz            |

| Power (At 180 MHz, 2.0 V) | <b>5</b> 8∼10 W    |

| Power (At 96 MHz , 1.2 V) | 1.6~1.9W           |

| Gate count                | 21-million         |

| Area                      | $2.6 \text{ cm}^2$ |

Figure 2.1.3: Chip Implementation of Stream Processor Architecture

#### 2.2 Design Methodology in the SoC Era

In today's technology, although the development methodology is different for system designers and processor designers as well as between DSP developers and chipset developers, there are some common problems in designing chips [15].

- ➤ Time-to-market pressures

- > Difficulty in verification of increasing chip complexity

- > Difficulty in timing closure while entering deep submicron sizes

- > Difficulty in integrating different levels and areas expertise

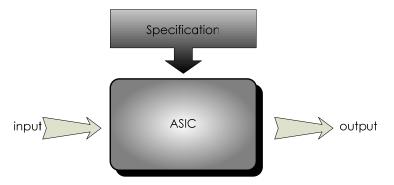

Taking ASIC as example, it is the conventional design methodology. However, in the SoC era, more and more transistors are placed into the chip causing the complexity of chip increases dramatically higher than used to. This results in problems listed above get worsen and loss competitiveness if the ASIC design is not able to come out betimes. The basic principle of ASIC is shown in Figure 2.2.1. The chip implementation could be finished as quickly as soon as the well-defined specification. The physical area, operating frequency, and power consumption are able to be optimized as being defined in the specification. The advantage of ASIC is that it could design a specific architecture that fully matches the pre-defined specification and thus incurs the best trade off between performance, power, and area. This is why the ASIC is still popular now day. However, it has a serious drawback of lacking of flexibility for reusing the design. As long as the specification changes, the chip must also change.

Figure 2.2.1: An ASIC design

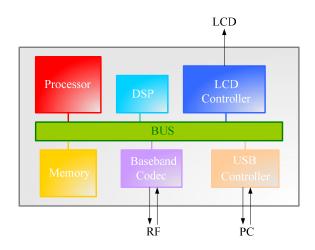

Platform-based architecture aims the target of design reuse. It consists of a core and many pre-defined robust intellectual property (IP, sometimes called cores, block, or macro) as hardware accelerator that have already been designed and verified solidly with the same interface. There are some existing platforms are developed, such

as AMBA on-chip bus from ARM, device control bus (DCR) from IBM [16], and automated bandwidth allocation bus system from Silicon Backplane of Sonics [17]. The topologies of them are similar to each other. They communicate through the share bus with the same interface of protocol, although the needed standard interface will extend the design cycle and have extra overhead of timing and area.

With the same communicating protocol, it could be helpful to integrate many different modules tightly. By adding or deleting some IP could set up a different system as fast as possible. Therefore, if there is already plenty of reusable IP with the same interface, it can reduce much time to re-develop a new system depending on different requirements. One more attractive thing is that these platforms have been set up with a developing baseboard. There are many common IP such as processor, memory, and peripherals on the baseboard that benefits to fast prototyping. Forbye, they have OS in existence and can reduce the effort of connecting the real applications to intent design.

Furthermore, it makes the physical design problems, interconnect issue, clock skew, power consumption, etc, be engaged in the early stage of design process. The pre-defined IP not only can solve the physical problems early but also is easy to verify in advance. It changes the global problems to local ones to be dealt with. Therefore, because of lots of advantages of this design methodology, it gradually becomes a trend in the SoC era. Not only it is able to ease off the common problems but also has possibility to low down overall cost by reusing ready IP.

There is one more thing needed to be noticed in order to finish a platform design, only preparing robust IP for reuse is not enough. The designers have to provide other things that are complete documents and enough deliverables, such as functional, timing, synthesis, physical models and so on. Otherwise, the effort to integrate a pre-existing block into new designs will still be prohibitive high.

Here is simple example to illustrate platform-based design, as shown in Figure 2.2.2. It is a simplified block diagram of cell phone system that consists of a processor, on-chip memory, DSP core, baseband codec, LCD controller, and USB controller and each block has the same protocol. The blocks communicate with others by bus through the same interface. It is obviously that there are many blocks in this platform are able to be reused in other system. For example, the USB controller can be reused directly in another design such as a MP3 player if they have the same interface.

Figure 2.2.2: An Example of Platform Design

#### 2.3 Overview of AMBA

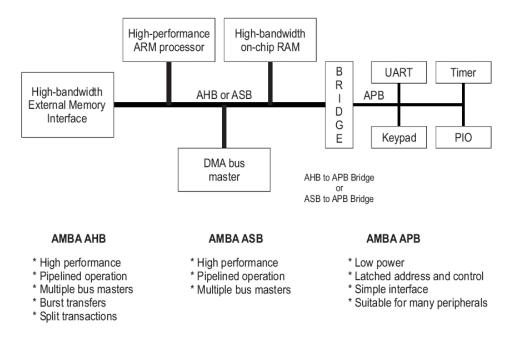

The AMBA specification defines an on-chip communications standard for designing high-performance embedded microcontrollers [18] [19]. There are four objectives of the AMBA on-chip bus system; right-first-time, technology-independent, modular system design, and minimization the silicon infrastructure.

The AMBA system could be used to facilitate the right-first-time development of embedded microcontroller products with one or more CPUs or signal processors. Being technology-independent and ensuring that highly reusable peripheral and system macrocells can be migrated across a diverse range of IC processes and be appropriate for full-custom, standard cell and gate array technologies. Improving processor independence and providing a development road-map for advanced cached CPU cores and the results from the modular system design. Then, it minimizes the silicon infrastructure requirement and supports efficient on-chip and off-chip communication for both operation and manufacturing test. There are three distinct buses are defined with the AMBA system.

#### ➤ The Advanced High-performance Bus (AHB)