國立交通大學

光電工程學系 顯示科技研究所

碩士論文

五環素有機薄膜電晶體可靠度之研究

**Study on the Reliability of Pentacene-Based

Organic Thin Film Transistor**

研究 生：陳弘根

指 導 教 授：劉柏村 博士

中 華 民 國 九 十 五 年 七 月

國立交通大學

光電工程學系 顯示科技研究所

碩士論文

五環素有機薄膜電晶體可靠度之研究

Study on the Reliability of Pentacene-Based

Organic Thin Film Transistor

研究 生：陳弘根

指 導 教 授：劉柏村 博士

中 華 民 國 九 十 五 年 七 月

# 五環素有機薄膜電晶體可靠度之研究

## Study on the Reliability of Pentacene-Based Organic Thin Film Transistor

研究 生：陳弘根

Student: Hung-Keng Chen

指 導 教 授：劉 柏 村 博 士

Advisor : Dr. Po-Tsun Liu

國立交通大學

光電工程學系顯示科技研究所

碩士論文

Submitted to Department of Photonics & Display Institute

College of Electrical Engineering and Computer Science

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Master

in

Display

July 2006

Hsinchu, Taiwan, Republic of China

中華民國九十五年七月

# 五環素有機薄膜電晶體可靠度之研究

研究生:陳弘根

指導教授: 劉柏村 博士

國立交通大學 光電工程學系 顯示科技研究所碩士班

## 摘要

在有機薄膜電晶體的技術演進中，其載子遷移率表現出來的電性已經迎頭趕上複晶矽薄膜電晶體的電性了。而其中五環素為電洞導通的有機半導體，載子遷移率最高已高過  $1\text{cm}^2/\text{V s}$ ，可說已到了單晶有機的傳輸極限了。不過儘管電性已有大幅改善，但是在接面電阻，導通機制和電性上的不穩定這三個方面還未作有系統的探討。

因而在本論文裡，首先我們會利用四點探測法來了解接面電阻。而四點探測是在上源極和汲極結構時，同時製作上去的，而非額外多了兩根測電位的探針製作步驟。因此我們用原本兩個電極(源極和汲極)注入並接收電流，另外通道中的兩個電極來感測電壓。這手法跟最近報導的四點探針電晶體很像。而相較於傳統的電阻對通道長作圖法求接觸電阻，四點探測主要優點是可在單一元件上單獨量到薄膜電阻和各接觸電阻，並使得元件元件間在既存在的電阻差異下更容易對此元件作評估。因此我們可利用它來作進一步作現象分析。

接著我們作變溫量測，此可在遷移率與溫度有關的半導薄膜上作量測。在與溫度相關的遷移率中，蘊育著半導體和傳導機制有關或和缺限分布有關的資訊。有一些模型已提出來解釋這些半導晶體中熱活化的載子遷移率現象，然而“Multiple trapping and release model(MTR)”是最為被大家所廣泛接受的。因此我們再利用橫

向電導，可同時來觀測Meyer-Neldel relationship的電性傳輸行為。而我們也適當的利用Multiple trapping and release model(MTR)來解釋變溫量測中過程的熱活化現象。

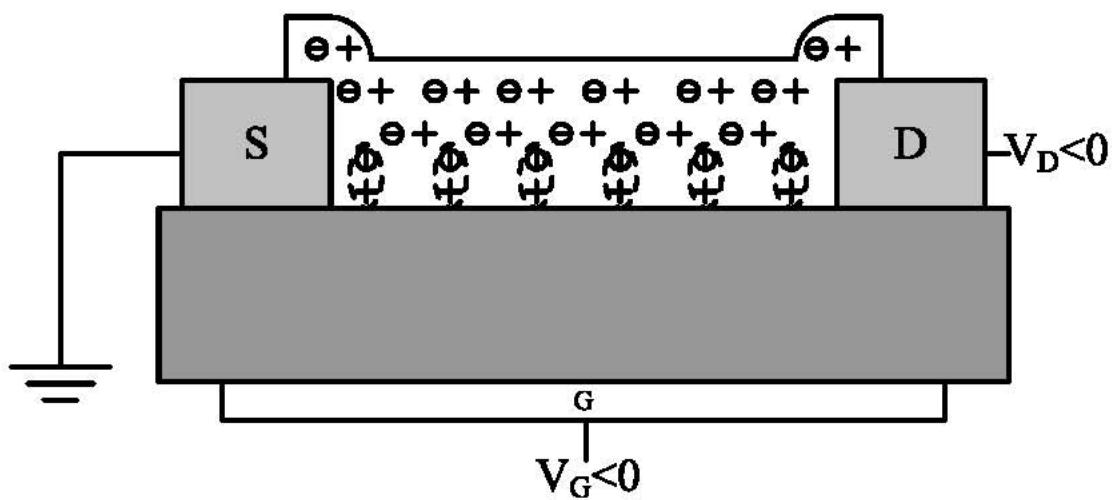

最後，我們在連續量測中了解到有機薄膜電晶體電性上的不穩定性，進而在定汲極電流的運作下，來探討這五環素有機薄膜電晶體的特性。在此我們也發現極化現象在定電流運作過程中扮演很重要的角色。因此提供簡單的能帶圖來陳述有機薄膜電晶體的特殊行為，而這些是載子受到束縛而在臨界電壓和遷移率上的不穩定現象也都一一會被探討。

# Study on the Reliability of Pentacene-Based Organic Thin Film Transistor

Student: Hung-Keng Chen

Advisor: Dr. Po-Tsun Liu

Department of Photonics & Display Institute

National Chiao Tung University

## Abstract

Recent progress in organic thin film transistor (OTFT) technology has led to charge carrier mobility comparable to amorphous silicon. Pentacene, a hole conductor, has shown the highest OTFT mobility( $>1 \text{ cm}^2/\text{V}\cdot\text{s}$ ) to date, and has nearly reached the intrinsic transport limit of organic single crystals. Despite the progress in realizing OTFTs with good properties, three important aspects of OTFTs have not been systematically studied: contact resistance, conduction mechanism, and electrical instability.

In this thesis, at first, we use an improved four-probe method for ascertaining contact resistance. The four-probe method is based on the standard OTFT source and drain geometry, but with two additional mid-channel voltage sensing probes. Thus, we use two electrodes to inject and receive current, and two to sense voltage in the OTFT channel. The technique we employ is similar to other recently reported four-probe transistor devices. The major advantage of the four-probe method over conventional R

vs L plots is that it allows the film and each contact resistance to be measured independently in a single device, which facilitates assessment of device-to-device variation in these resistances. Hence, we use it to further analyze the phenomenon.

Variable temperature TFT measurements are adapted later. It can be used to determine the temperature dependence of the mobility in a semiconductor thin film. The temperature dependence of the mobility can yield information about the conduction mechanism and trap states in the semiconductor. Several models have been proposed to explain thermally activated mobility in crystalline organic semiconductor films, but the multiple trapping and release (MTR) model is the most widely accepted. Thus, a Meyer–Neldel relationship was simultaneously observed for electrical transport, using a transconductance. We properly use the multiple trapping and release model to explain the thermally activated phenomenon from the variable temperature measurement.

Finally, we understand the instability of electrical characteristics in a continued series measurements and investigated the characteristics of bottom-contact pentacene-based OTFTs under drain current stress conditions. Here, we find that polarization phenomenon plays an important role during stress, and thus we provide the rough energy band figure to depict these special properties of OTFTs. The effect of these charge trapping instability on the measured threshold voltage and mobility of the transport studies would be discussed.

## 誌 謝

我的老師：

感謝劉柏村老師，在我的碩士二年生涯中給予我指導，並灌輸給我嚴謹的治學態度和積極的辦事習慣。也要感謝張鼎張老師，在我的研究遇到困難時，能即時提供我再走下去的方向，並在我報告時，給予我關照，叮嚀和指正。

我的論文口試委員：

感謝老師們撥空來為我的口試論文作評審，所給我的提問與建議讓我受益良多，能讓我對論文上探討的思路更加全面而完整。

我們的實驗團隊：

感謝我們的實驗團隊，讓我在遇到實驗技術上的問題時都能迎刃而解。猶其要感謝我的學長，峻豪學長在我作實驗灰心時給予我很多幫忙和鼓勵，緯仁學長都能提供我最具體的建議和指示，世青和立偉學長很不好意思多次打擾不過依然地熱心幫忙，大山和震鑠學長也都不時地會提醒沒經驗的我以免迷失，敏全和致宏學長在我論文第二和第五章的問題上提供了不少看法和意見，謝謝泓緯、皓彥、志宗、士哲學長跟他們請教時能給予指正，也謝謝興華、彥宇、國權學長帶過我作實驗。還有中山的書瑋、原瑞學長和志憲也給我提供不少方向上的意見。同時也要感謝我的同學佳州提供我實驗上不少幫忙，和彥伯也跟我同樣是作有機的，在實驗上也都時常相照應。逸哲、建文、一德也在修課實驗時大家相互切磋。

我的朋友：

感謝我的好朋友們，有緣再次在交大相聚，彼此更懂得珍惜。永昇，力仁，東賢，映萍，穎婷，家揚，黑狗，皓達，神箭，維哲，建成，俊嘉，溥寬，聖忠，仁豪，志豪，俊賢，忠謬，峻榮，LK，資高，俊傑，楊仔，佳寧，婉玲，俊宇，和政，政展，佐昇，大家互相鼓勵，互吐苦水，甚至還出盡一些鬼點子，碩士生涯有了你們，增添不少趣味。

我的父母和家人：

感謝你們總是開明懷柔，尊重我的決定；因為你們的支持與鼓勵，我才能夠突破我人生中的每一項關卡，我才能夠在求學的路程上順利的完成我的學業。最後我要將我的碩士論文獻給你們，希望能不負你們的栽培並且期望能看到我這些日子的成長。

# Contents

*page*

---

|                             |     |

|-----------------------------|-----|

| Abstract (in Chinese).....  | iii |

| Abstract (in English) ..... | v   |

| Acknowledgements .....      | vii |

| Contents.....               | ix  |

| List of Figures .....       | xi  |

| List of Tables.....         | xx  |

## Chapter 1 Introduction

|                                                    |   |

|----------------------------------------------------|---|

| 1.1 Overview of Organic Thin Film Transistor ..... | 1 |

| 1.2 Properties of Pentacene.....                   | 3 |

| 1.3 Operation of Organic Thin Film Transistor..... | 5 |

| 1.4 Motivation .....                               | 6 |

| 1.5 Thesis Organization.....                       | 8 |

## Chapter 2 Devices Fabrication and Four Probe Measurement

|                                                                |    |

|----------------------------------------------------------------|----|

| 2.1 Introduction .....                                         | 15 |

| 2.2 Devices Fabrication and Measurement                        |    |

| 2.2.1 Process Flow of Pentacene-Based OTFT Fabrication.....    | 17 |

| 2.2.2 Electrical Characteristics of Pentacene-Based OTFTs..... | 18 |

| 2.3 Results and Discussions                                    |    |

| 2.3.1 The Growth of Pentacene .....                            | 22 |

| 2.3.2 Four Probe Measurement.....                              | 25 |

| 2.3.3 Sensitivity to Deposition Substrate Temperature.....     | 28 |

| 2.3.4 The Effect of Scaling .....                              | 29 |

| 2.4 Summary .....                                              | 33 |

## Chapter 3 Variable Temperature Measurements

|                                       |    |

|---------------------------------------|----|

| 3.1 Introduction .....                | 65 |

| 3.2 Variable Temperature Measurements |    |

|                                                                                |           |

|--------------------------------------------------------------------------------|-----------|

| <b>3.2.1 The Multiple Trapping and Release Model and The Meyer–Neldel Rule</b> | <b>69</b> |

| <b>3.2.2 Experiment Detail</b>                                                 | <b>71</b> |

| <b>3.3 Results and Discussions</b>                                             |           |

| <b>3.3.1 The Existence of Meyer–Neldel Rule</b>                                | <b>72</b> |

| <b>3.3.2 Sensitivity to Variable Temperature during Measurement</b>            | <b>74</b> |

| <b>3.4 Summary</b>                                                             | <b>75</b> |

## **Chapter 4 Electric Instability of Pentacene-Based OTFTs**

|                                                                          |           |

|--------------------------------------------------------------------------|-----------|

| <b>4.1 Introduction</b>                                                  | <b>88</b> |

| <b>4.2 Instability of OTFTs during current stress</b>                    |           |

| <b>4.2.1 Experiment Detail</b>                                           | <b>89</b> |

| <b>4.2.2 Results and Discussions</b>                                     | <b>90</b> |

| <b>4.3 The Recovery after Current Stress and Polarization Phenomenon</b> |           |

| <b>4.3.1 Experiment Detail</b>                                           | <b>93</b> |

| <b>4.3.2 Results and Discussions</b>                                     | <b>93</b> |

| <b>4.4 Transient Stress Phenomenon in Measurements</b>                   |           |

| <b>4.4.1 Experiment Detail</b>                                           | <b>96</b> |

| <b>4.4.2 Results and Discussions</b>                                     | <b>97</b> |

| <b>4.5 Summary</b>                                                       | <b>97</b> |

## **Chapter 5 Conclusions and Further Recommendations**

|                                    |            |

|------------------------------------|------------|

| <b>5.1 Conclusions</b>             | <b>128</b> |

| <b>5.2 Further Recommendations</b> | <b>130</b> |

| <b>Reference</b>                   | <b>132</b> |

| <b>Vita</b>                        | <b>141</b> |

# *List of Figures*

---

## **Chapter 1**

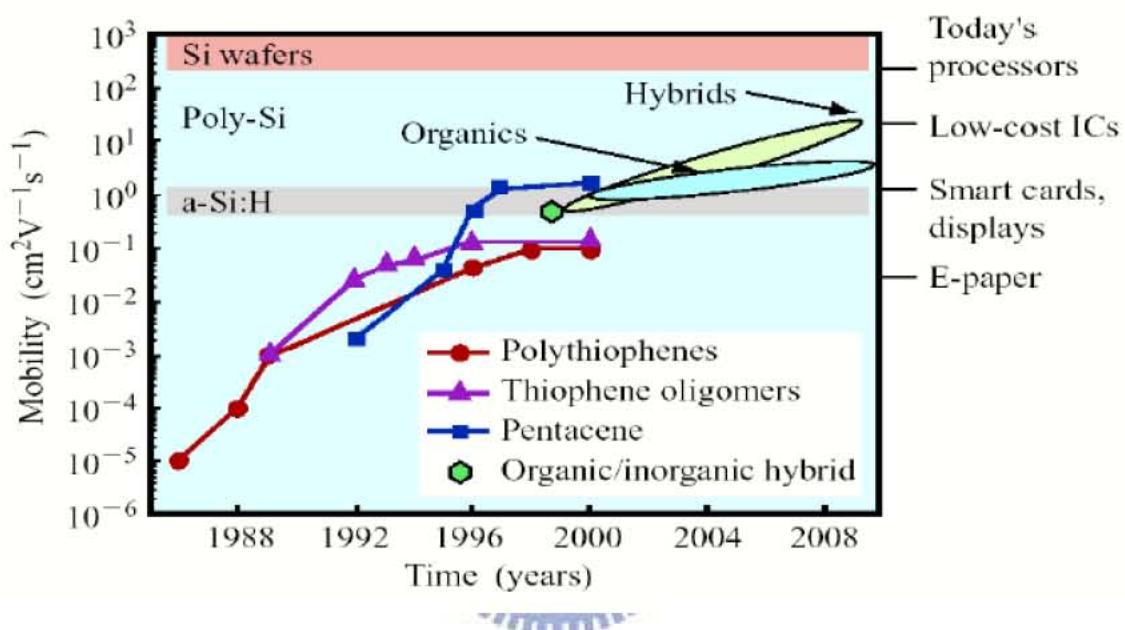

Figure 1-1: Mobility of organic semiconductors have improved by five orders of magnitude over the past 15 years. Large research efforts using materials such as these led to some of this increase.

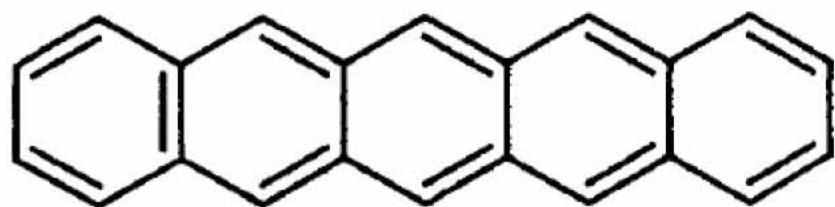

Figure 1-2: Pentacene molecular structure

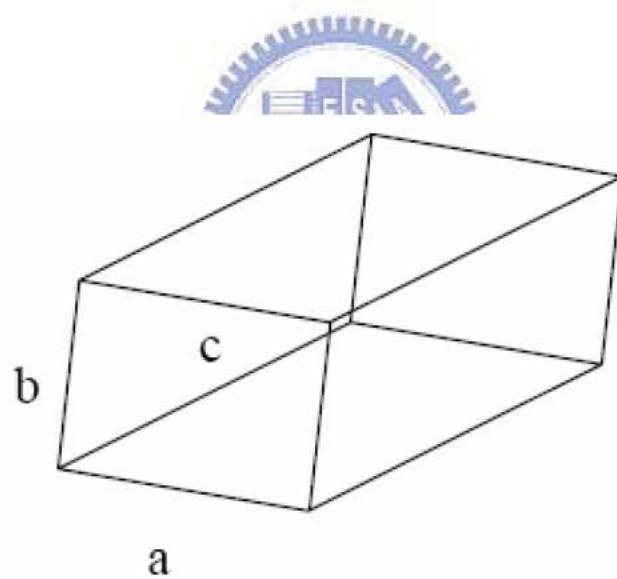

Figure 1-3: Triclinic lattice

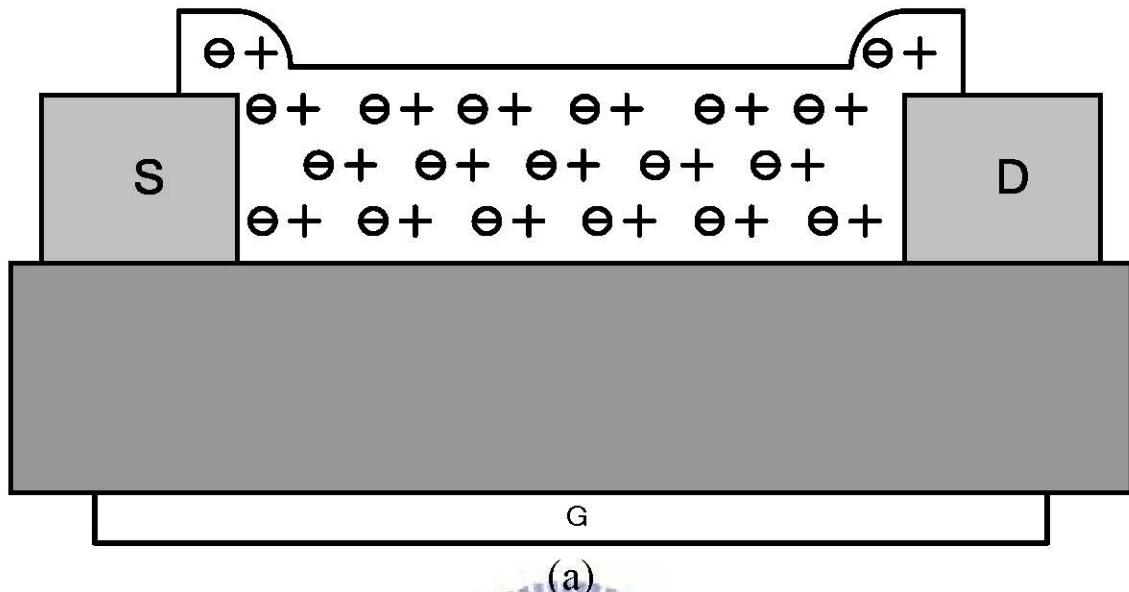

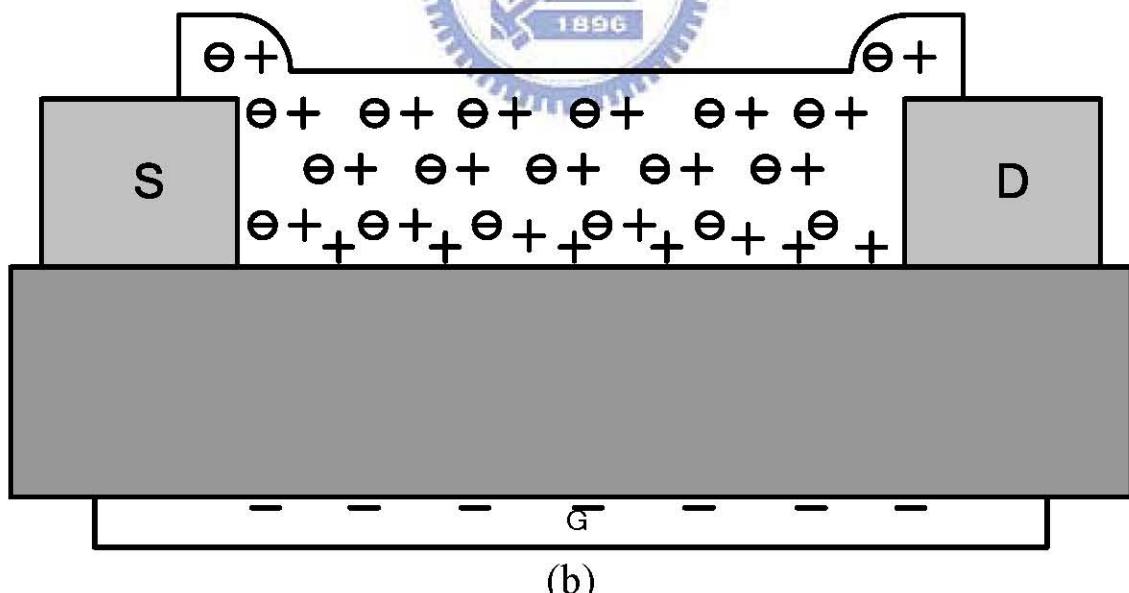

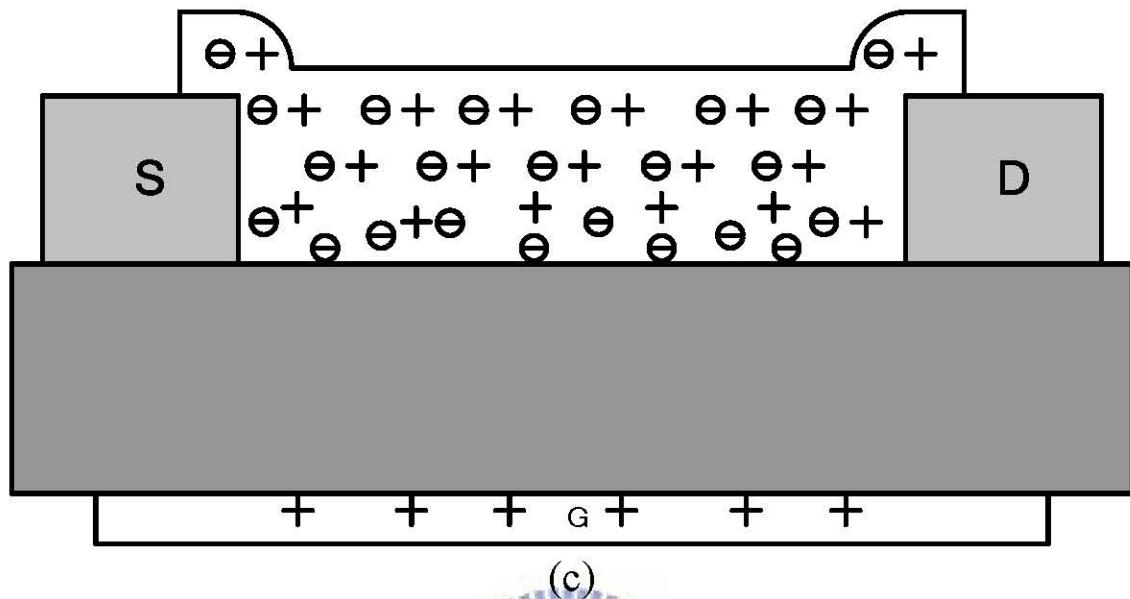

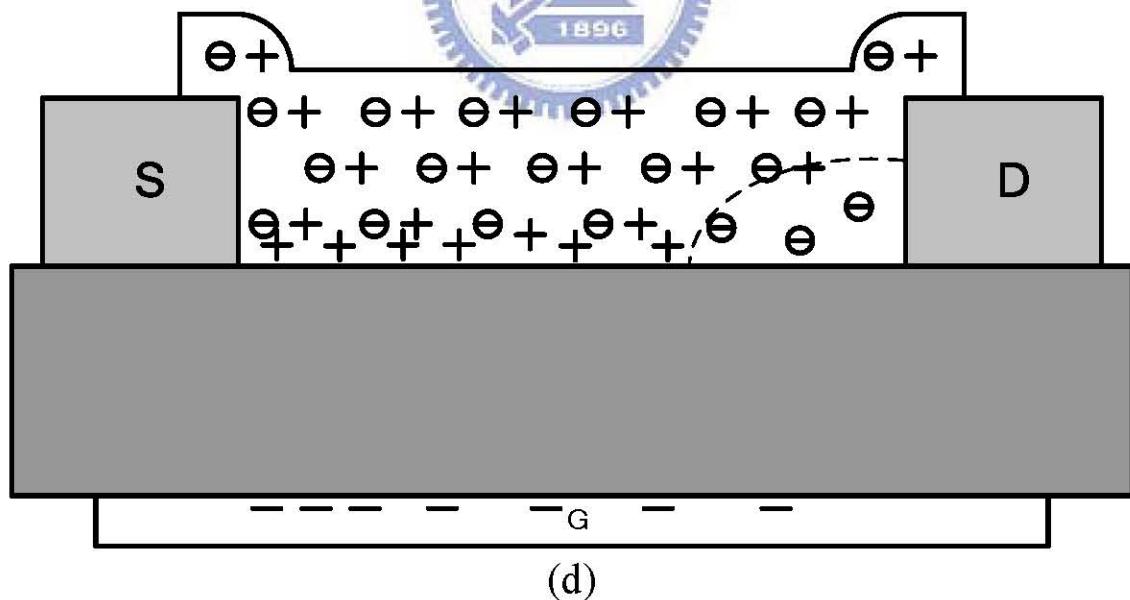

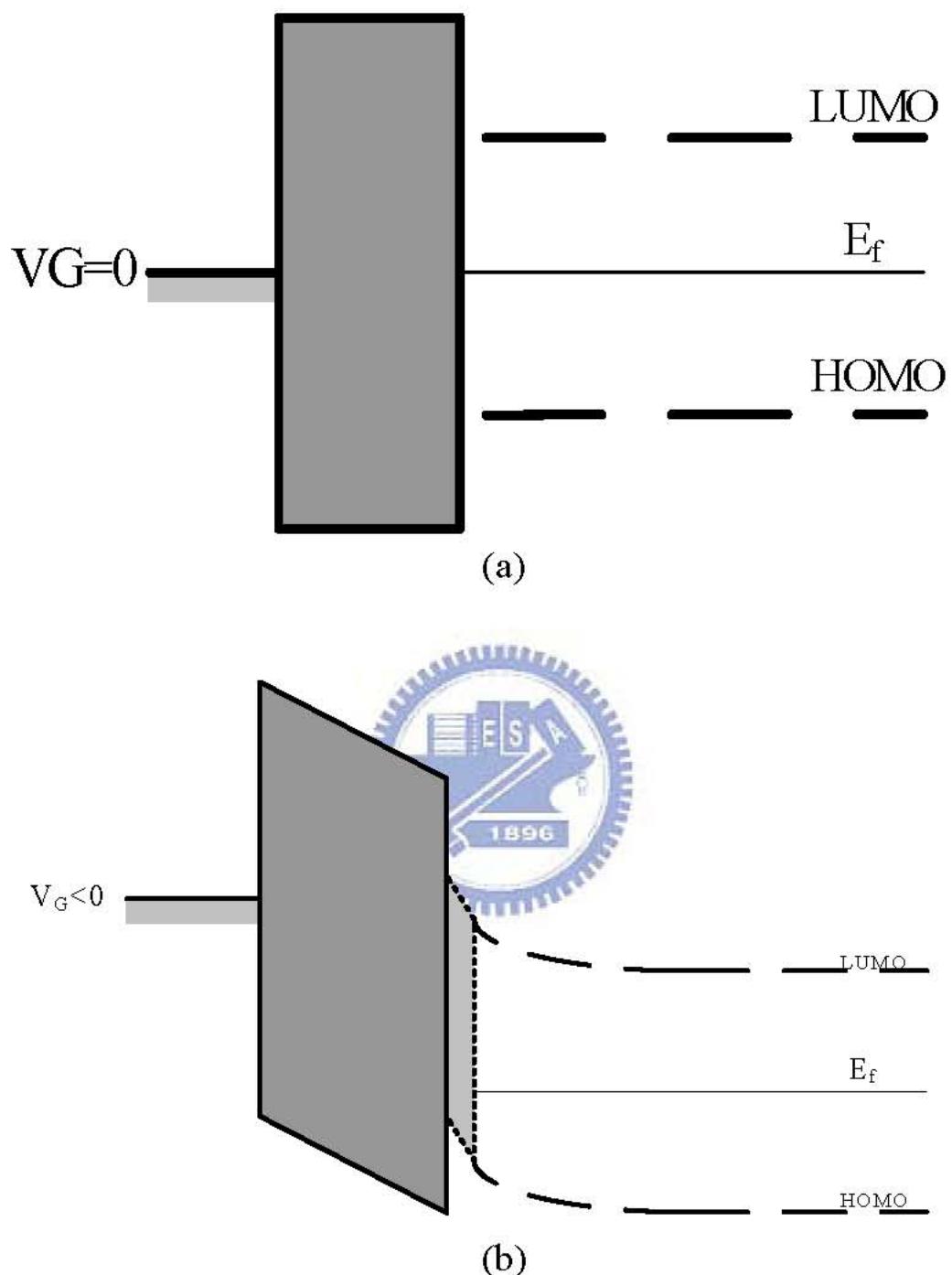

Figure 1-4: Schematic of operation of organic thin film transistor, showing a lightly p-doped semiconductor: + indicates a positive charge in semiconductor ; - indicates a negatively charge counterion (a) no-bais (b) accumulation mode (c)depletion mode (d) channel pinch-off

## **Chapter 2**

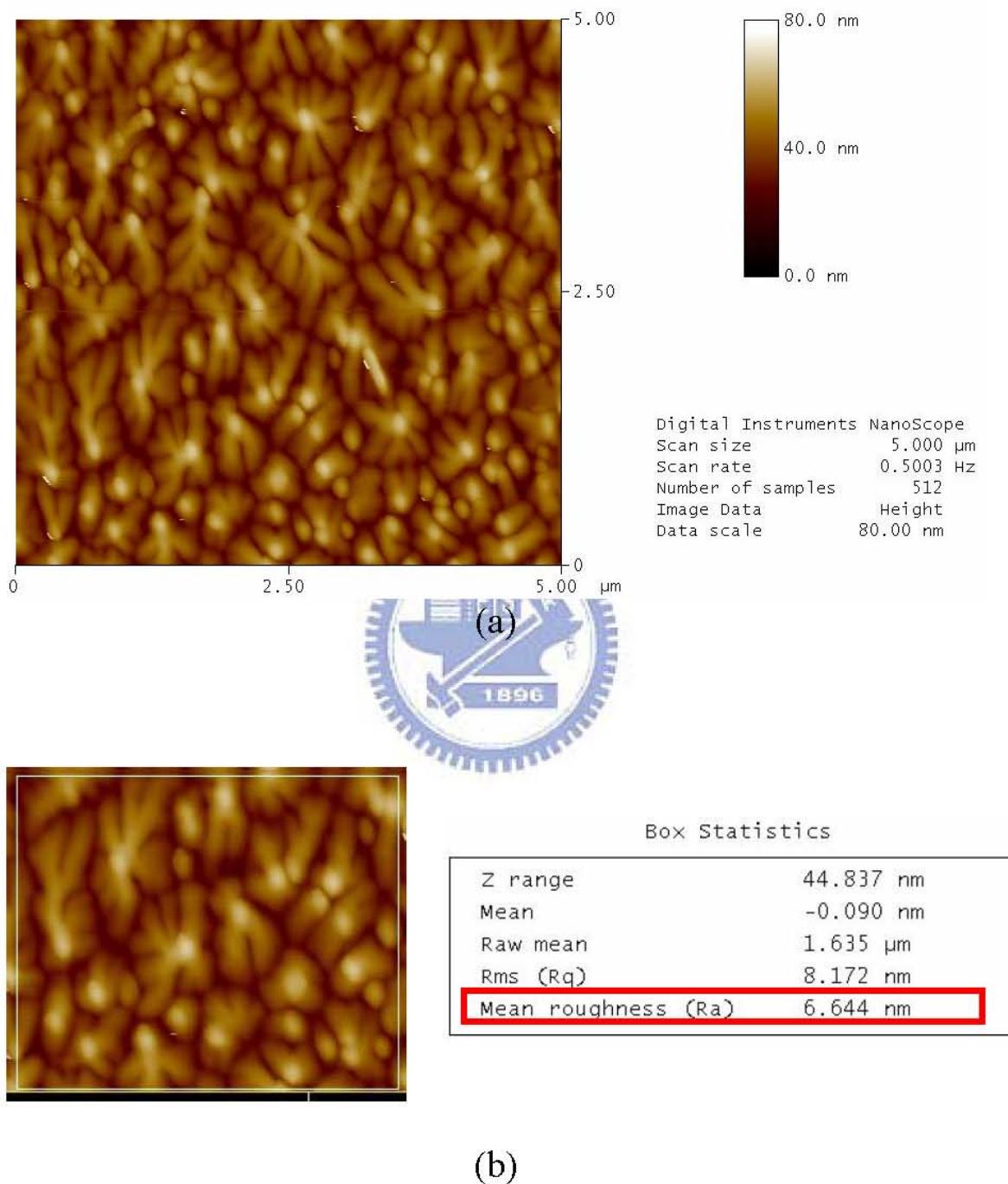

Figure 2-1: (a)A 5um×5um AFM topography of pentacene film at the substrate temperature of 25°C during the deposition, and (b) the mean roughness of the thin film is about 6.644nm.

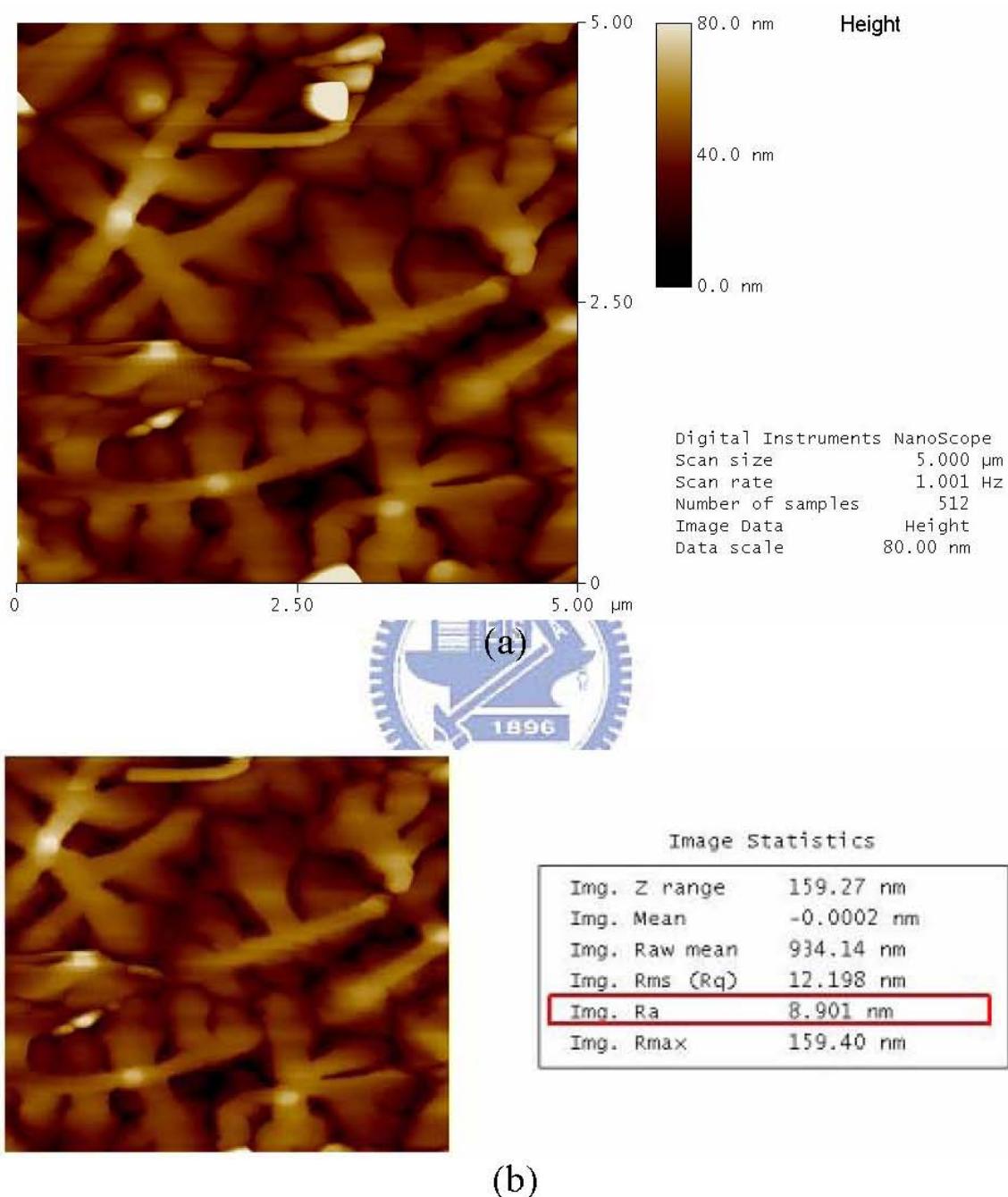

Figure 2-2: (a)A 5um×5um AFM topography of pentacene film at the substrate temperature of 70°C during the deposition, and (b) the mean roughness of the thin film is about 8.901nm.

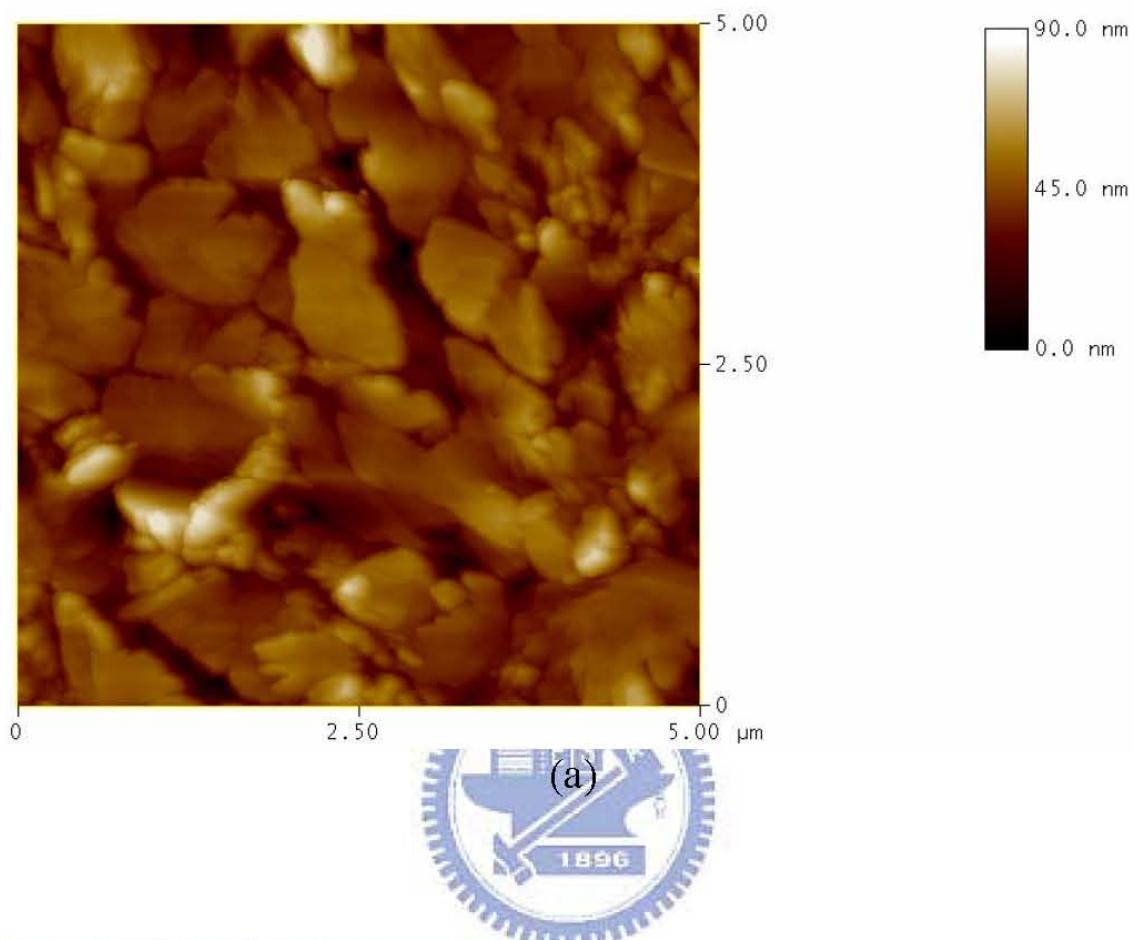

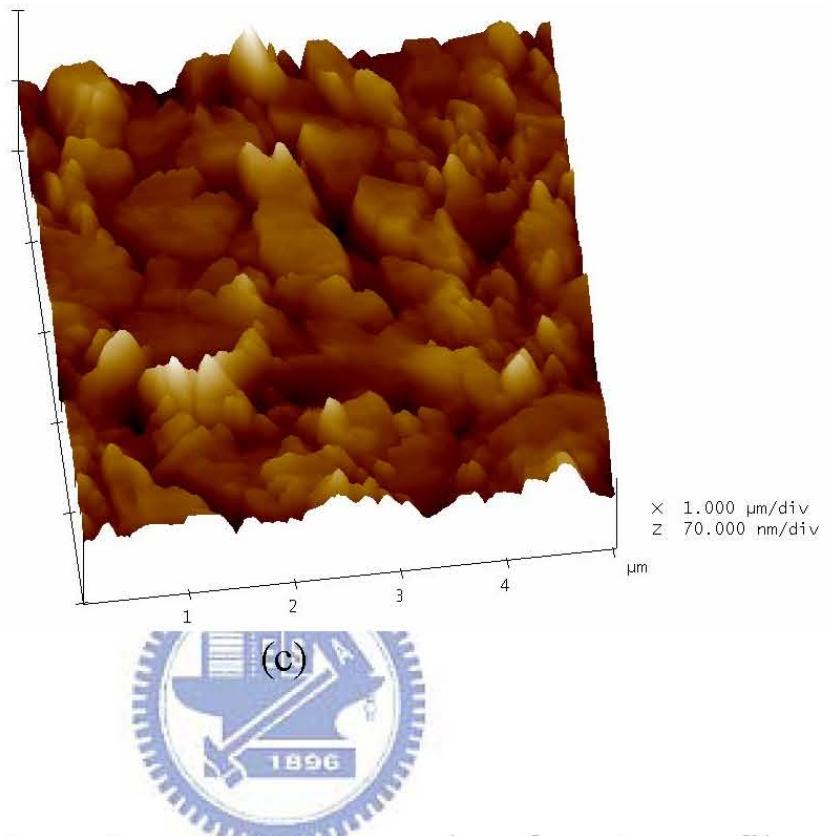

Figure 2-3: (a)A 5um×5um AFM topography of pentacene film at the substrate temperature of 120°C during the deposition, and (b) The mean roughness of the thin film is about 6.655nm. (c)The lateral view of three dimension AFM topography.

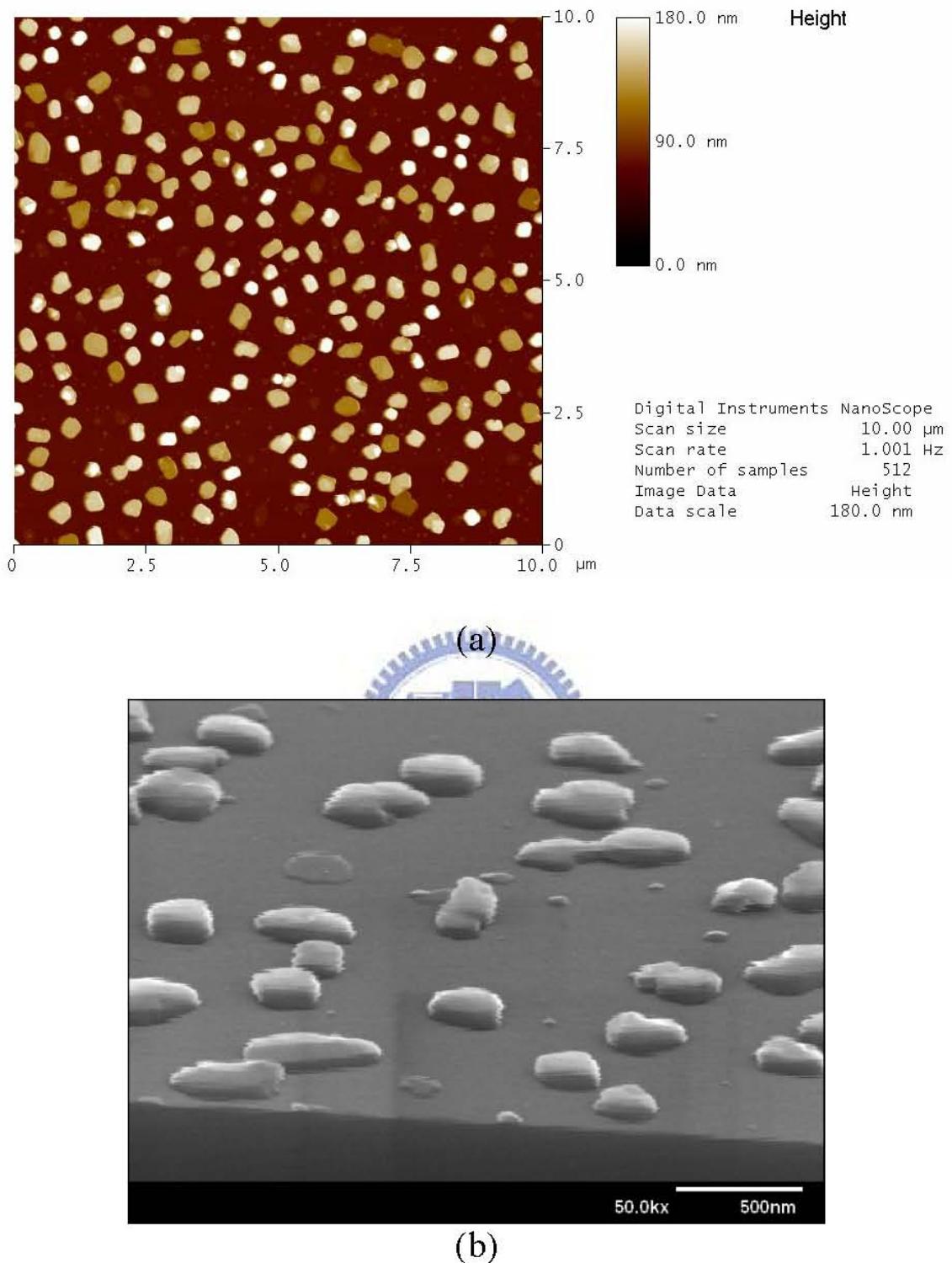

Figure 2-4: (a)The 10um×10um AFM topography of pentacene film, and (b)the lateral view SEM image of pentacene film in the initial period of crystallization. The morphology is like crystalline species.

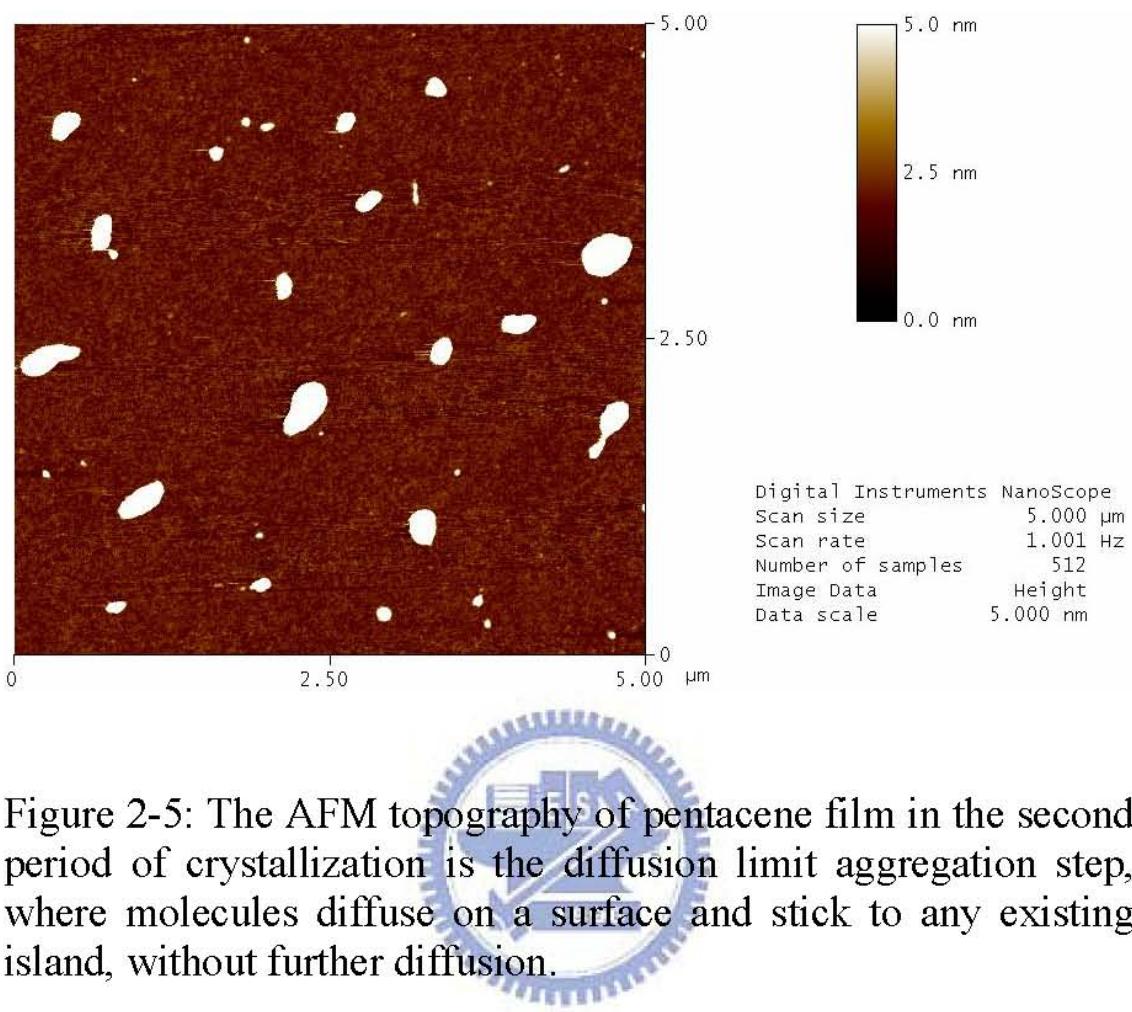

Figure 2-5: The AFM topography of pentacene film in the sond period of

crystallization is the diffusion limit aggregation step, where molecules diffuse on a surface and stick to any existing island, without further diffusion.

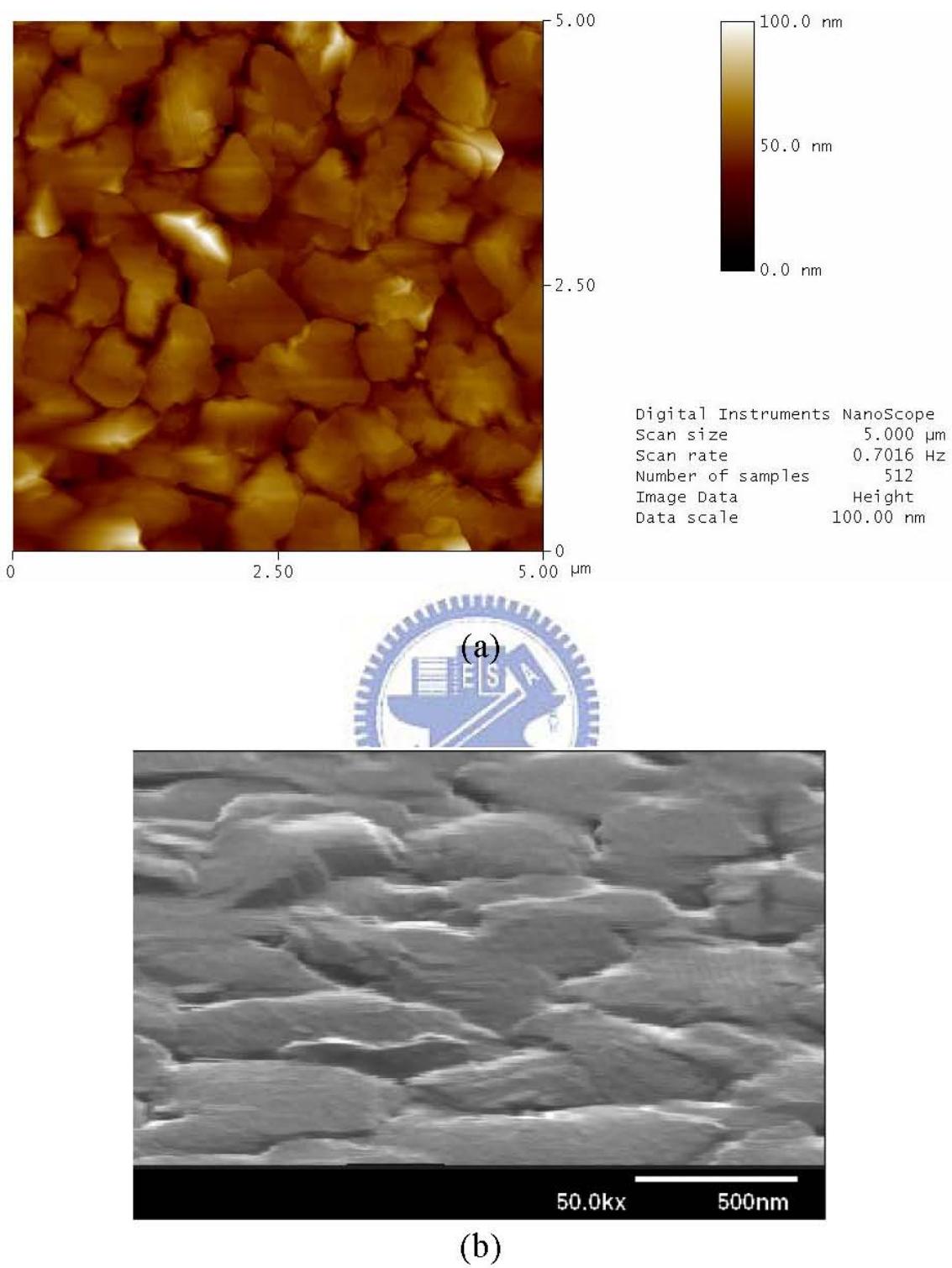

Figure 2-6: (a)The AFM topography of pentacene film, and (b)the lateral view SEM image of pentacene film in the third period of crystallization is the coarsening step, the pentacene islands coarsen until the grains touch each other.

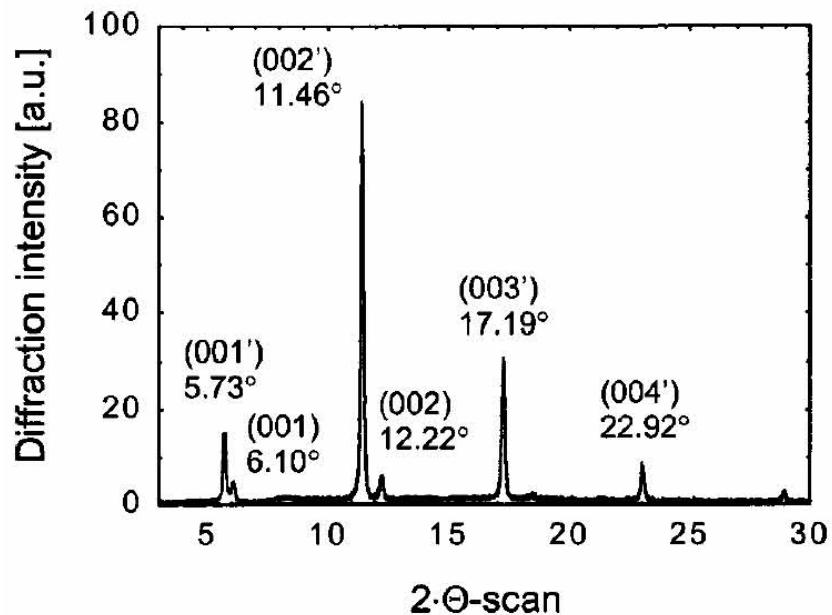

Figure 2-7: X-ray diffraction pattern of thermally deposited pentacene film on thermal oxide film. (D. Knipp et al., J. Appl. Phys. 2003)

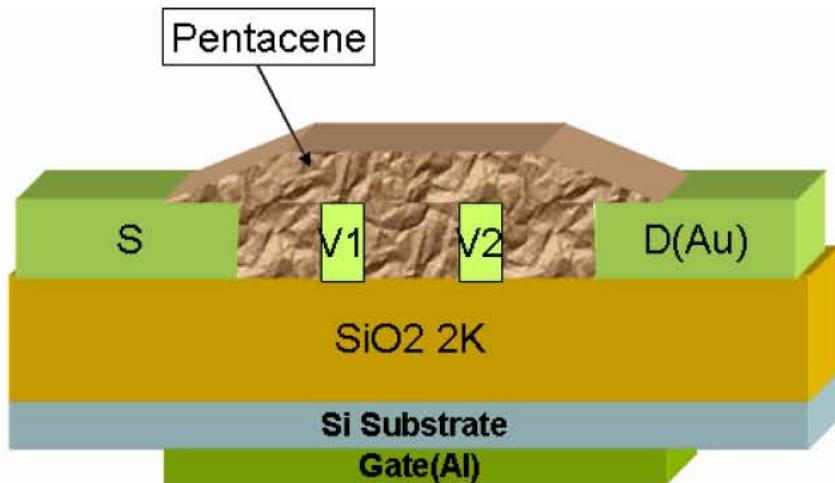

Figure 2-8: The schematic diagram of the bottom-contact OTFT with four probe structure. The voltage sensing probes are evaporated simultaneously with the source and drain electrodes in the staggered structure.

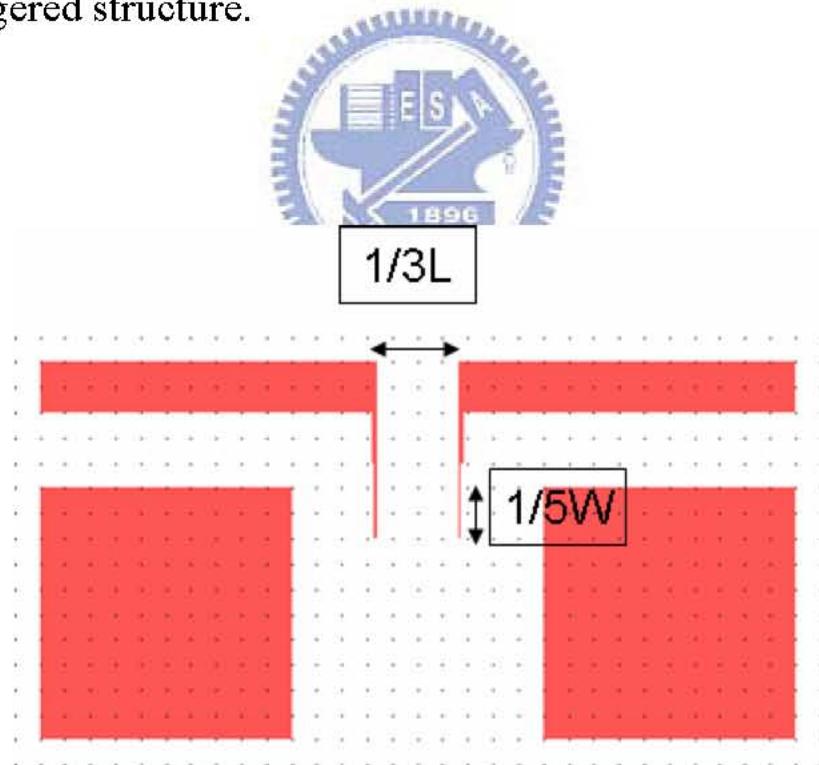

Figure 2-9: Top-view schematic of the four-probe OTFT geometry. Pentacene films are patterned to minimize overlap between the sense probe leads outside the channel area.

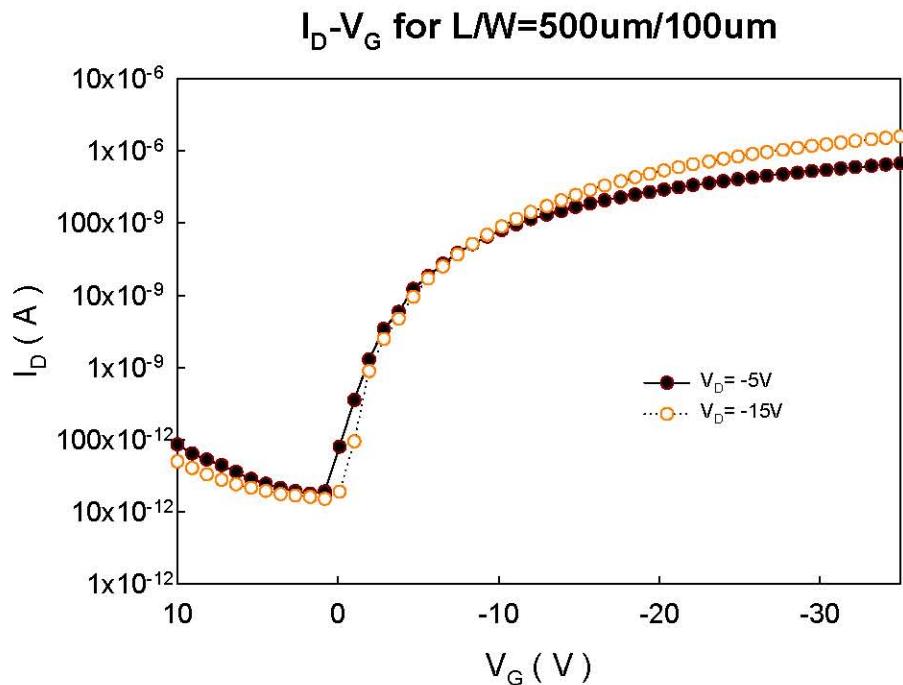

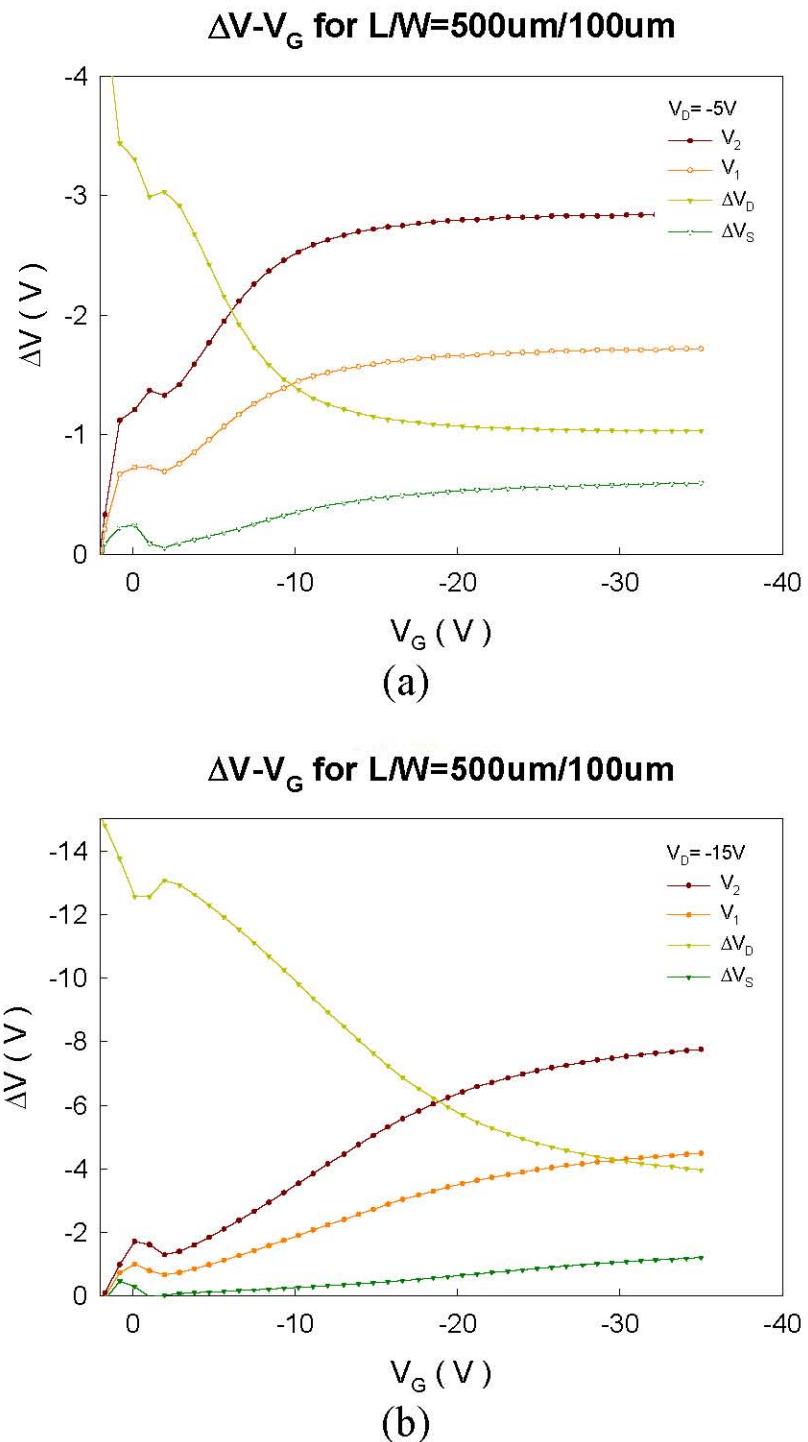

Figure 2-10: The transfer characteristics  $I_D$ - $V_G$  of OTFT at the drain voltages of -5V and -15V with length /width =500um/1000um

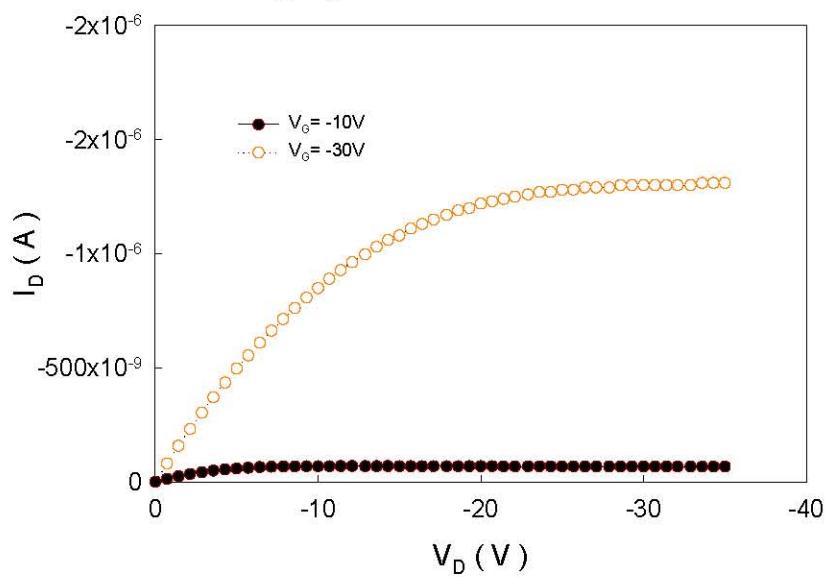

Figure 2-11: The output characteristics for pentacene-based OTFT with four probe structure at the gate voltage of -10V and -30V.

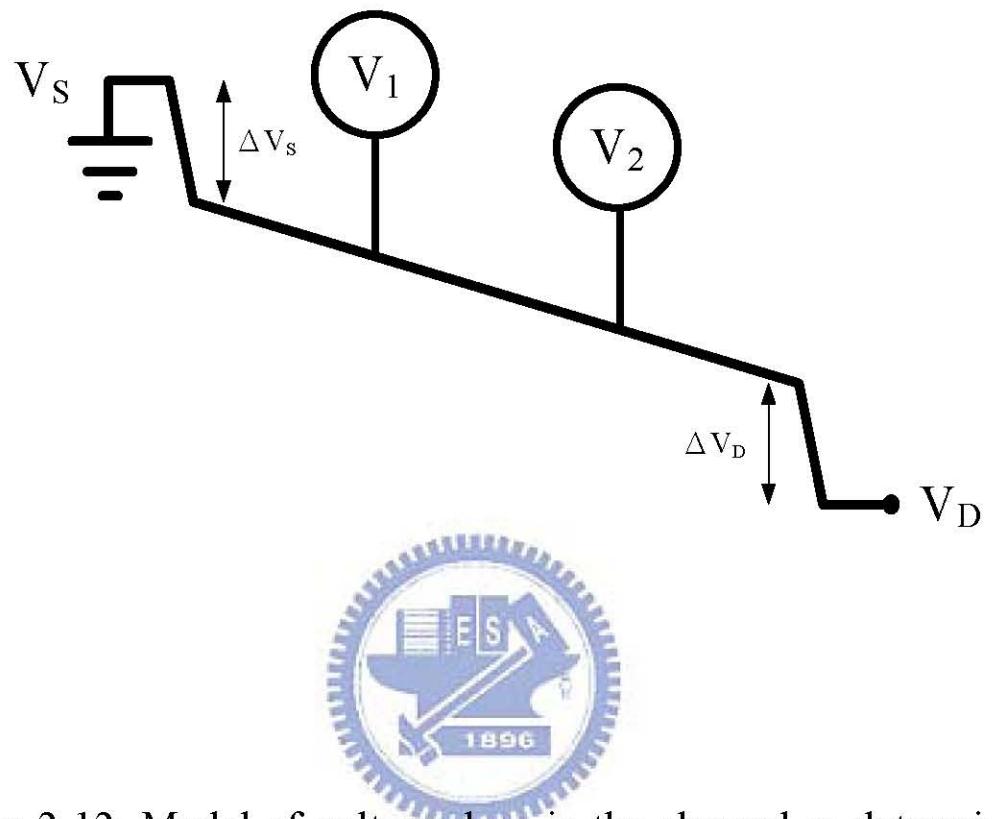

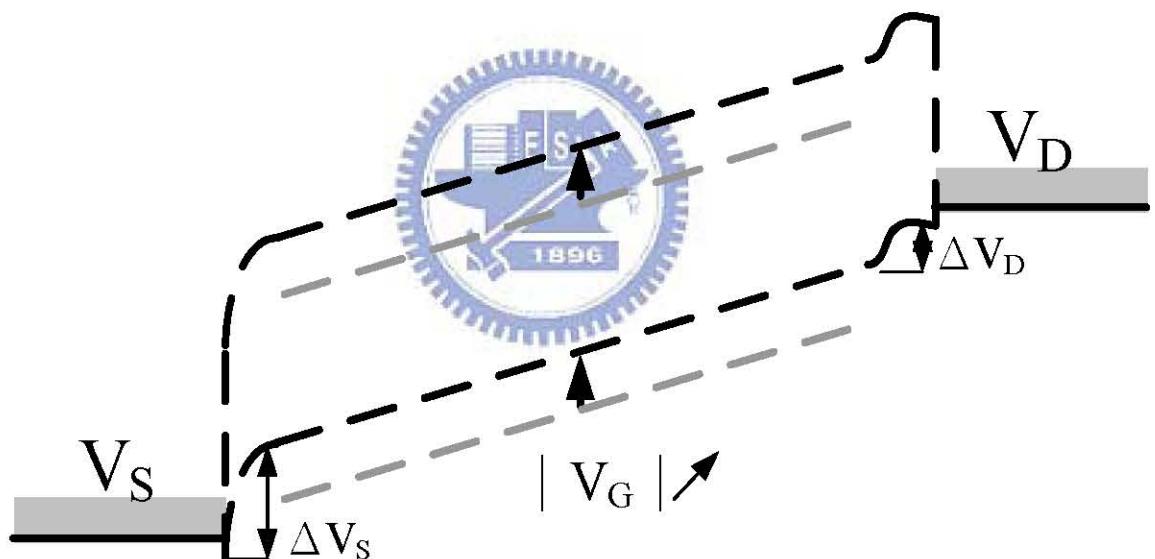

Figure 2-12: Model of voltage drop in the channel as determined by voltage probes  $V_1$  and  $V_2$ .  $\Delta V_S$  and  $\Delta V_D$  are voltage drops at the source and drain, extrapolated from the channel gradient.

Figure 2-13: Plot of sense probe ( $V_1$ ,  $V_2$ ) and source/drain voltage drops ( $\Delta V_S$ ,  $\Delta V_D$ ) as a function of gate voltage. The data correspond to the device in Figure 2-10 operating at room temperature with (a) $V_D$ = -5 V, (b) $V_D$ = -15 V.

Figure 2-14: The diagram of energy band along the channel. (a)At the smaller gate voltage, band bending leads to the more depletion region at drain side and the less voltage drop at source side. (b)At the large gate voltage, band

bending leads to the less depletion region at drain side and the more voltage drop at source side.

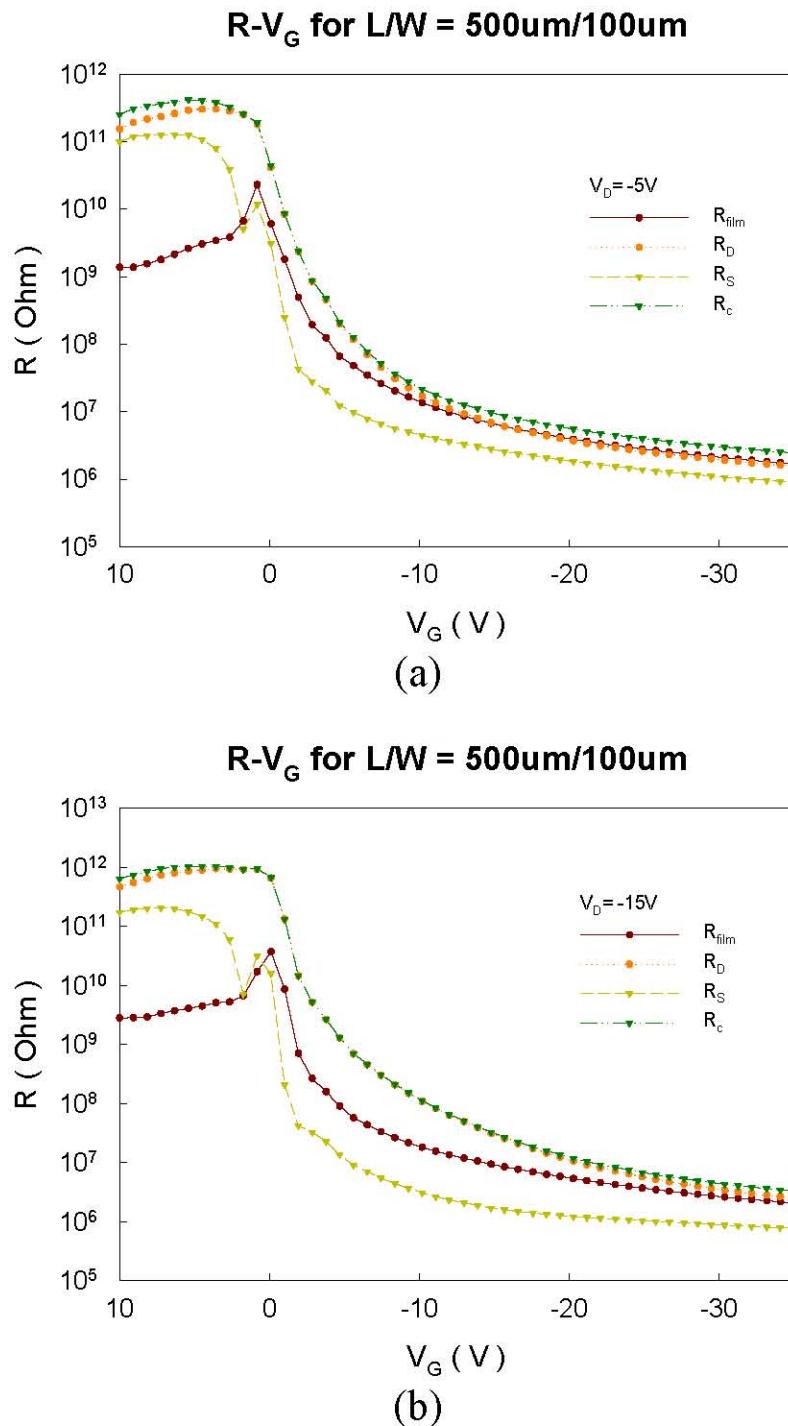

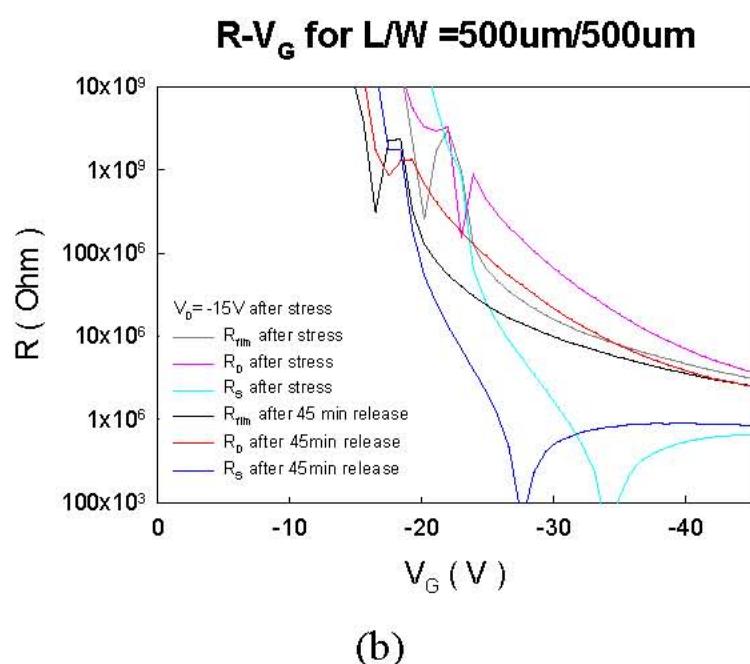

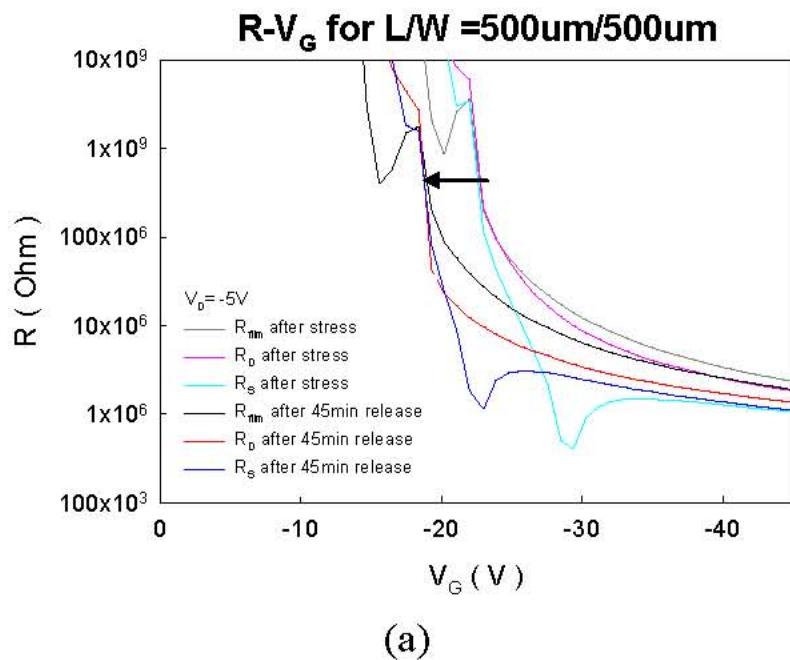

Figure 2-15:Plot of film resistance, source resistance, drain resistance and total contact resistance as a function of gate voltage for an operating OTFT. The data correspond to the device in Figure 2-10 operating at room temperature with (a) $V_D = -5$  V and (b) $V_D = -15$  V.

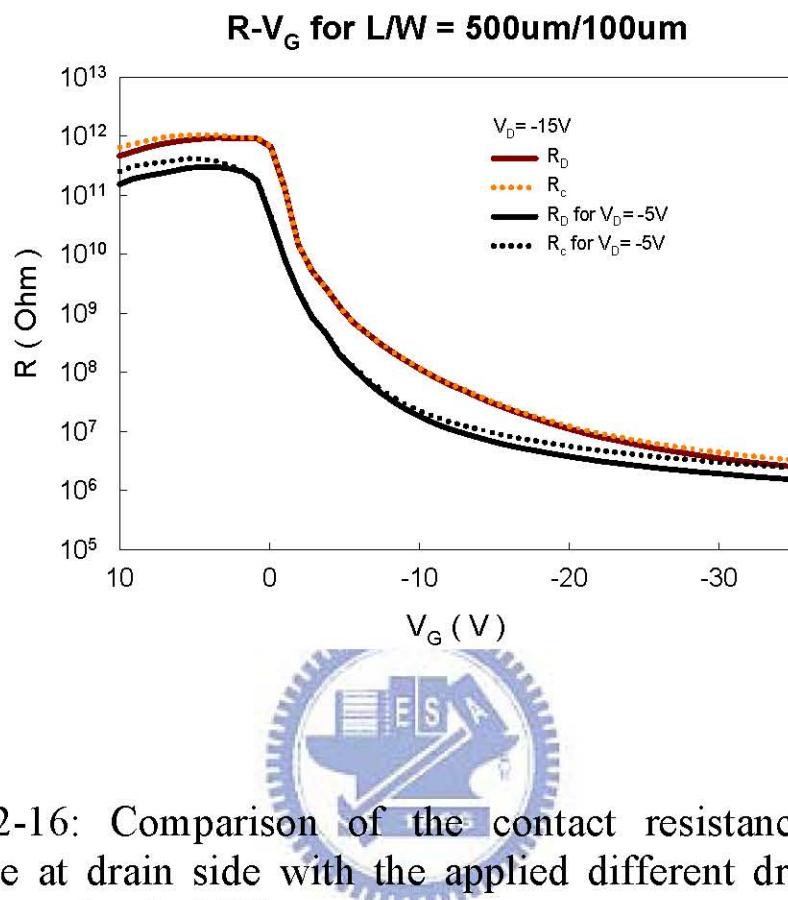

Figure 2-16:Comparison of the contact resistance and the resistance at drain side with the applied different drain voltage drops ( $V_D = -5$  and  $-15$  V).

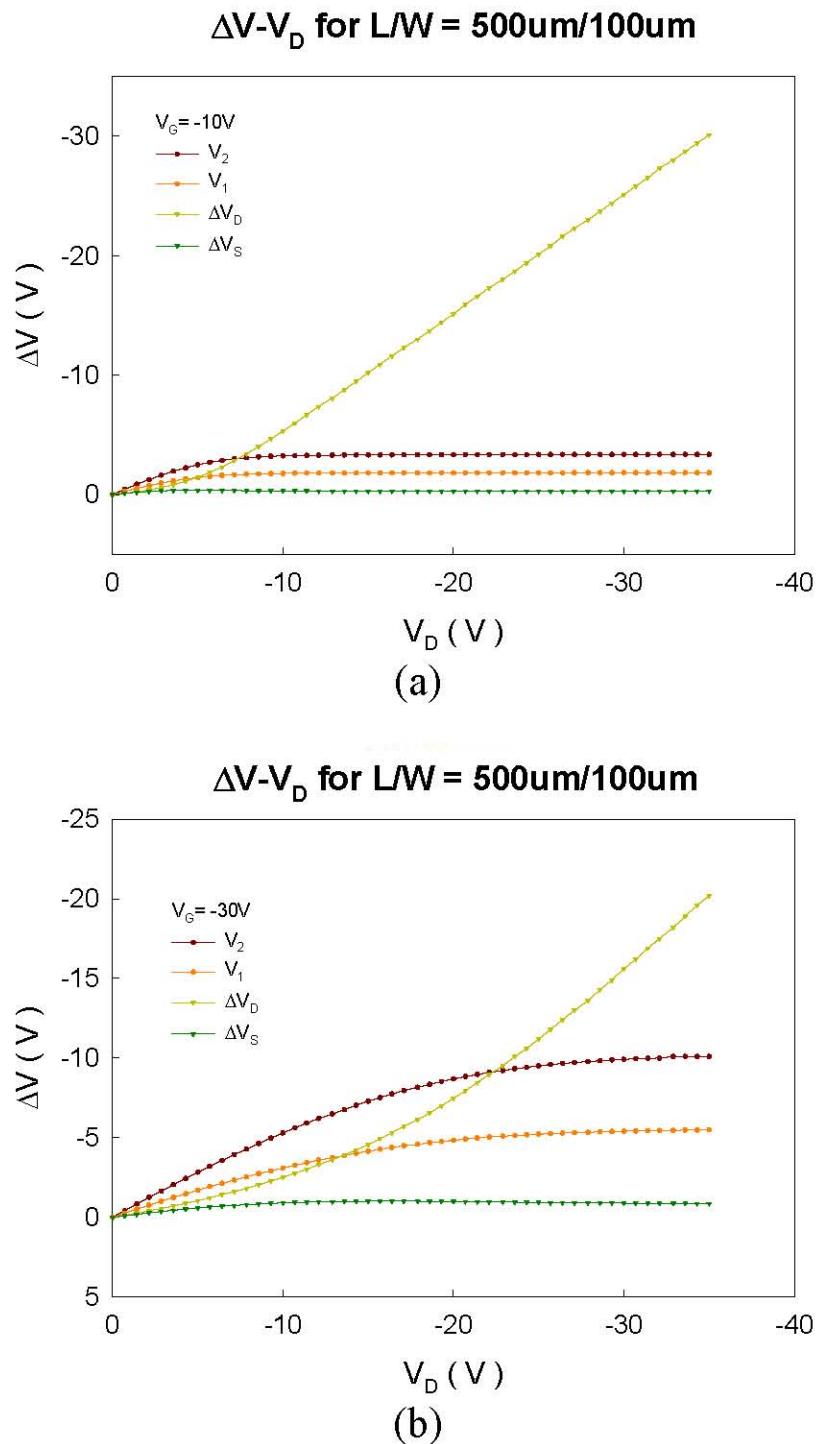

Figure 2-17:Plot of sense probe ( $V_1, V_2$ ) and source/drain voltage drops ( $\Delta V_S, \Delta V_D$ ) as a function of drain voltage. The data correspond to the device in Figure 2-11 operating at room temperature with (a) $V_G = -10$  V and (b) $V_D = -30$  V.

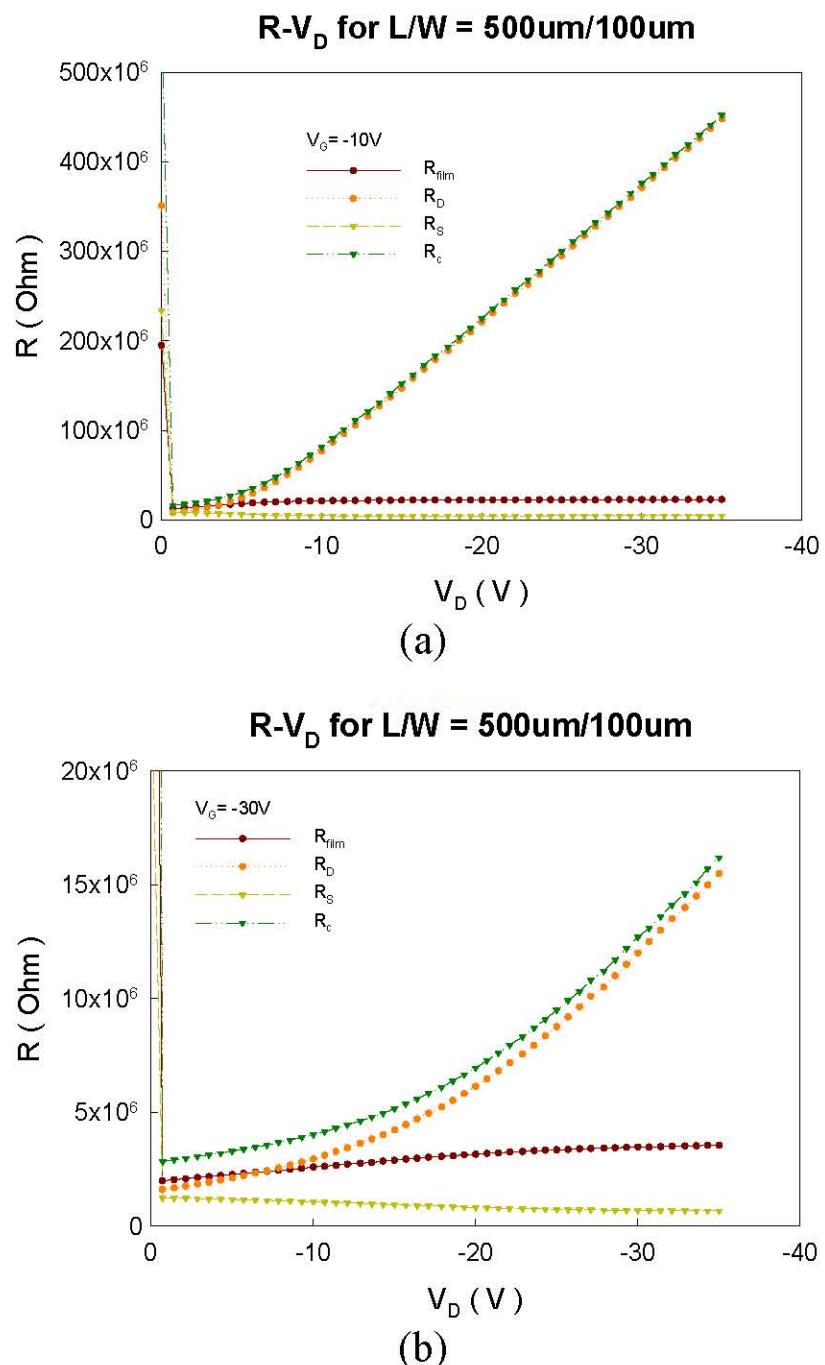

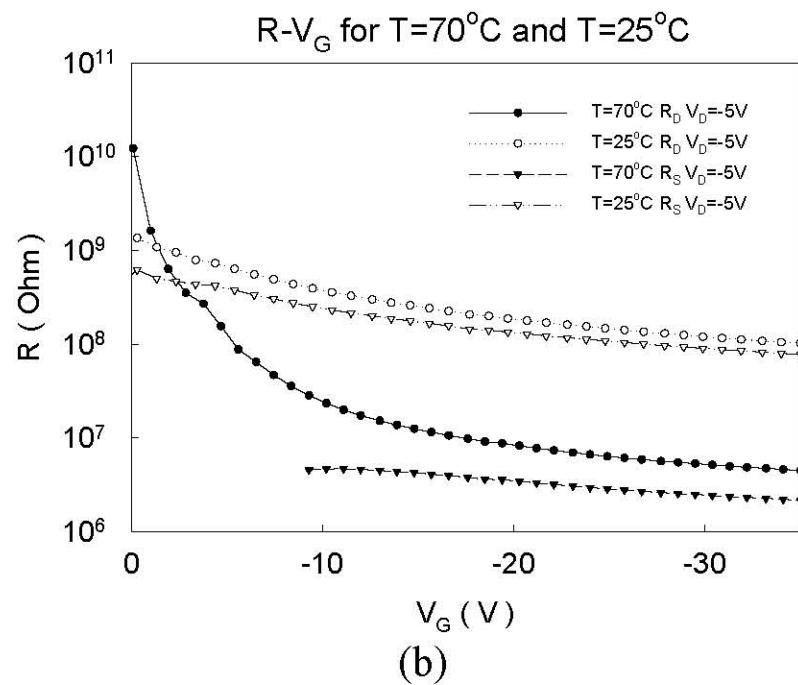

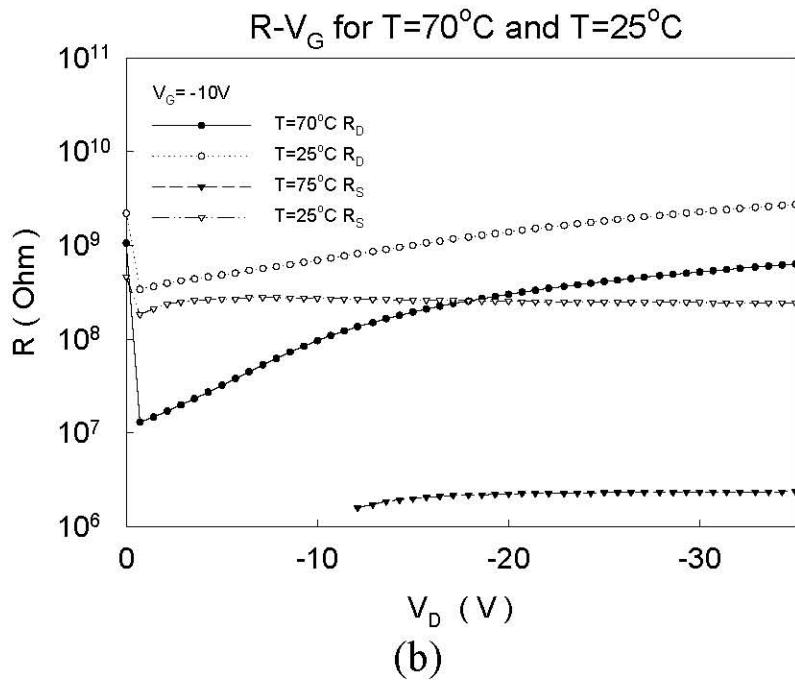

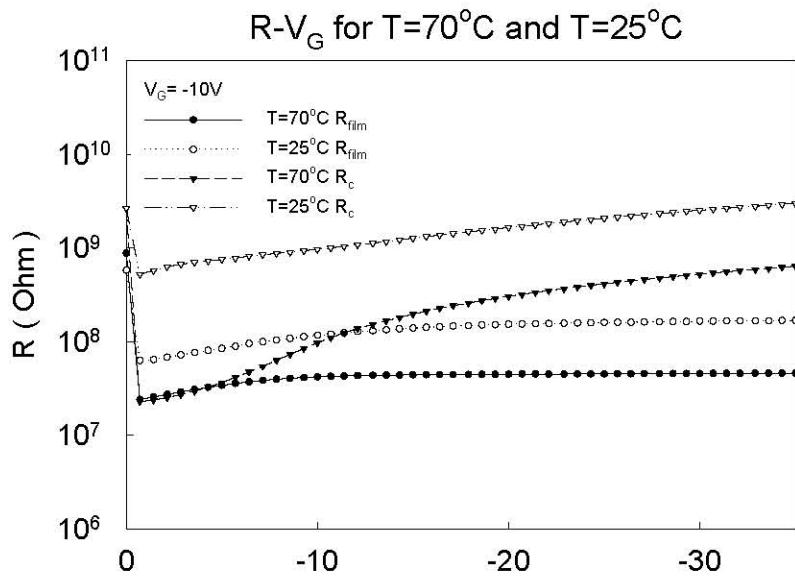

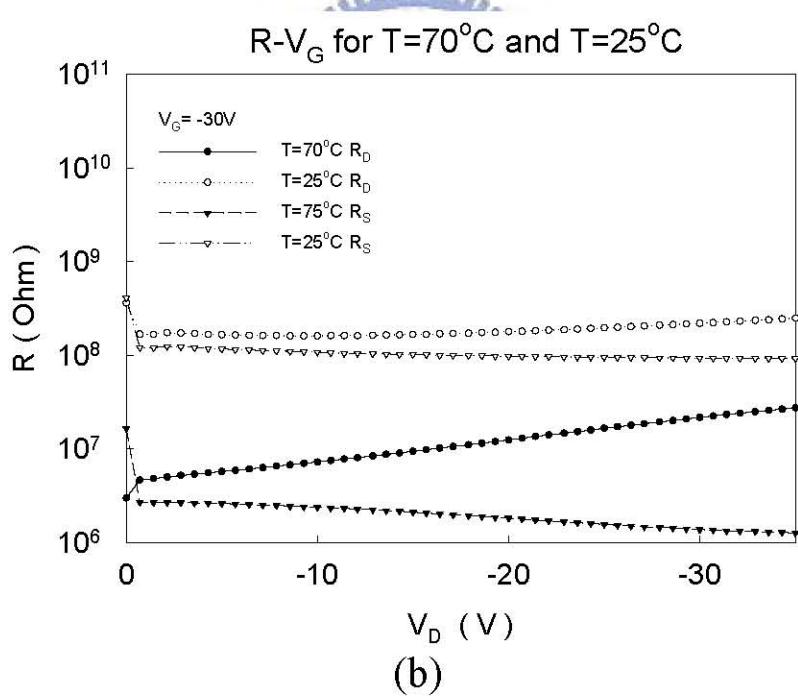

Figure 2-18:Plot of film resistance, source resistance, drain resistance and total contact resistance as a function of drain voltage for an operating OTFTs. The data correspond to the device in Figure 2-11 operating at room temperature with (a) $V_G = -10$  V and (b) $V_G = -30$  V.

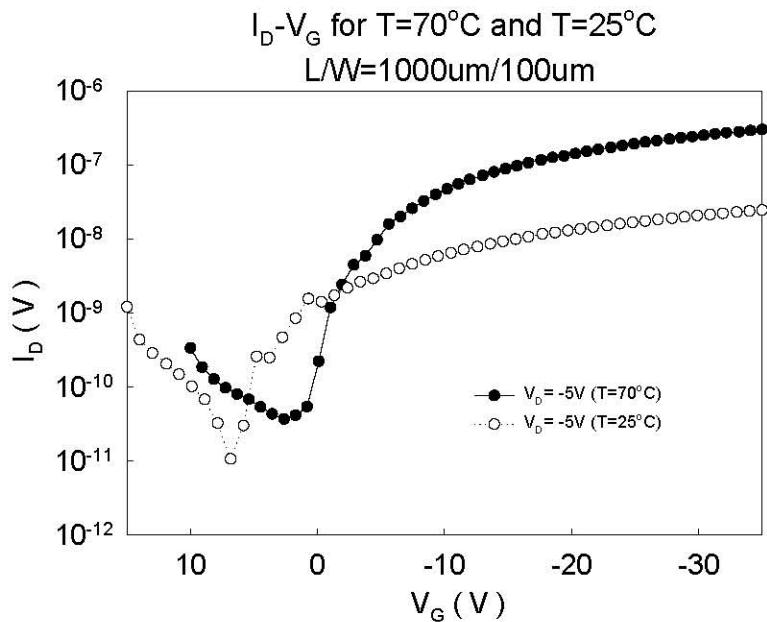

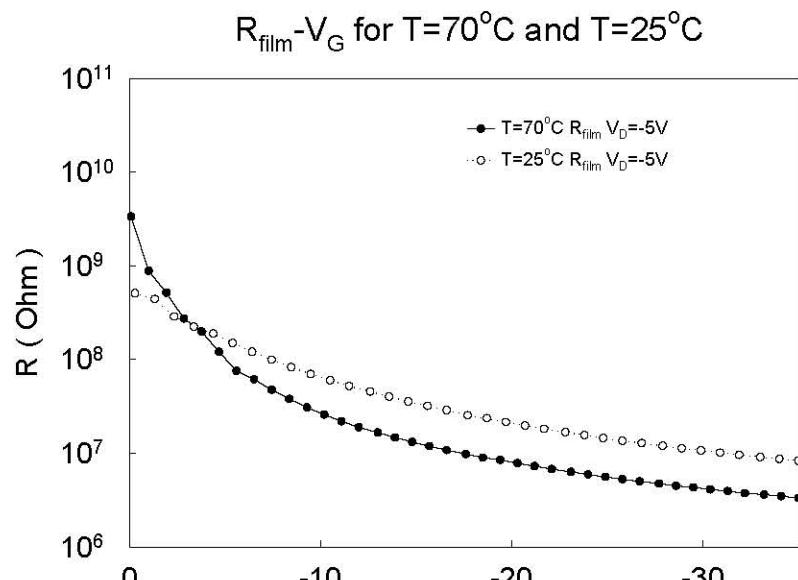

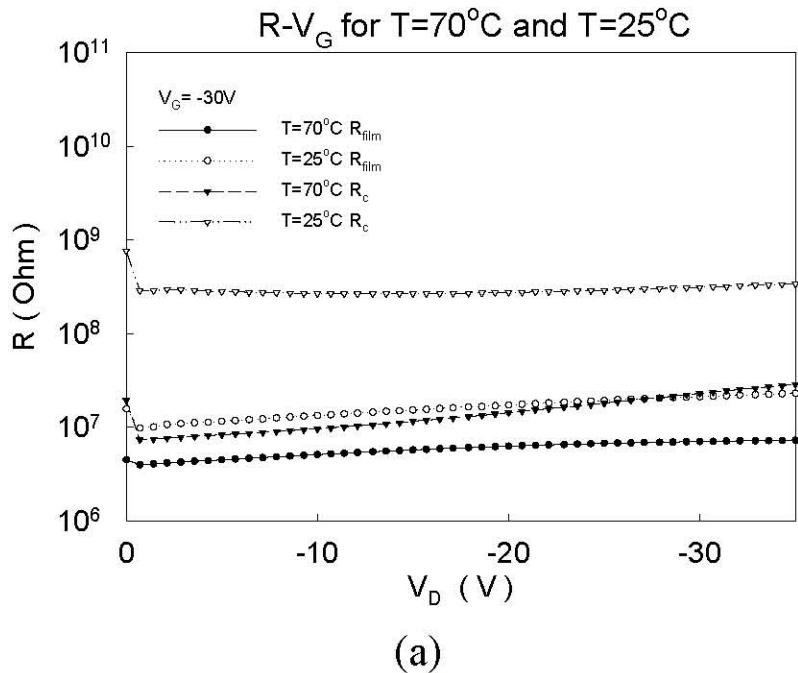

Figure 2-19:Comparison of the transfer characteristics  $I_D - V_G$  with the different deposition temperature of  $25^\circ\text{C}$  and  $70^\circ\text{C}$  at the drain voltages of  $-5$  V.

Figure 2-20:Comparison of the output characteristics  $I_D - V_D$  with the different deposition temperature of  $25^\circ\text{C}$  and  $70^\circ\text{C}$  at the gate voltages of  $-10$  V and  $-30$  V,separately.

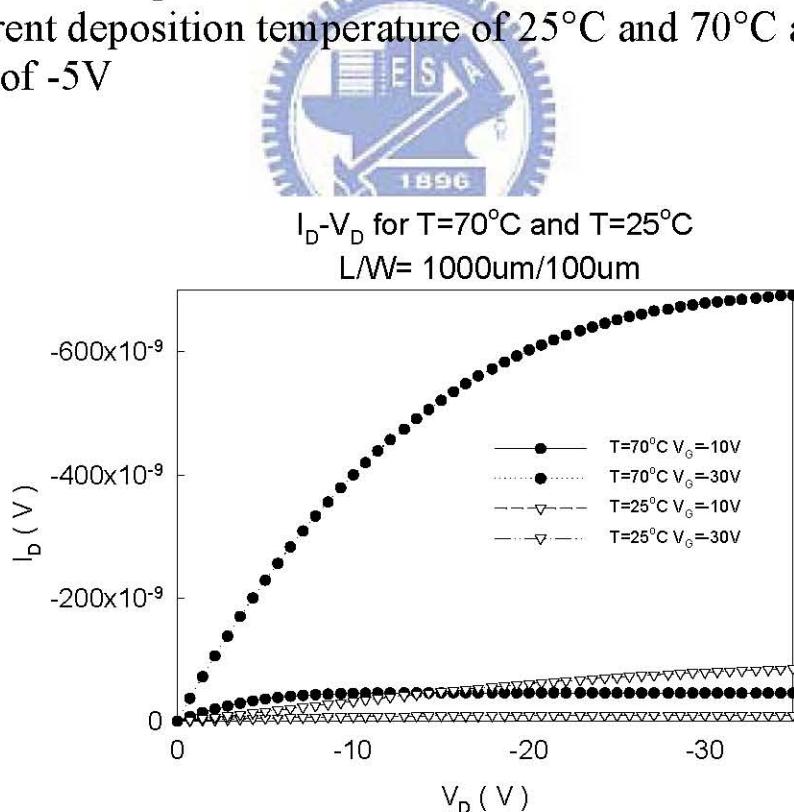

Figure 2-21:Comparison of (a)film resistance, (b)source resistance and drain resistance as a function of gate voltage with different deposition temperature of  $25^\circ\text{C}$  and  $70^\circ\text{C}$  for an operating OTFT. The data correspond to the device in Figure 2-20(a) operating at room temperature.

Figure 2-22:Comparison of (a)film resistance, (b)source resistance and drain resistance as a function of drain voltage at  $V_D = -10$  V with different deposition temperature of  $25^\circ\text{C}$  and  $70^\circ\text{C}$  for an operating OTFT. The data correspond to the device in Figure 2-20(b) operating at room temperature

Figure 2-23:Comparison of (a)film resistance, (b)source resistance and drain resistance as a function of drain voltage at  $V_D = -30V$  with different deposition temperature of  $25^{\circ}C$  and  $70^{\circ}C$  for an operating OTFT. The data correspond to the device in Figure 2-20(b) operating at room temperature

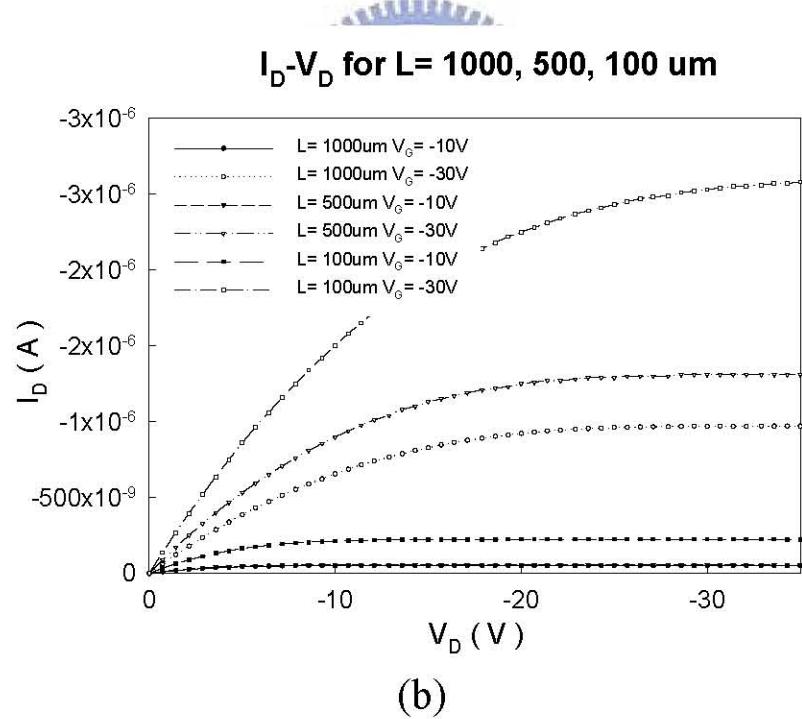

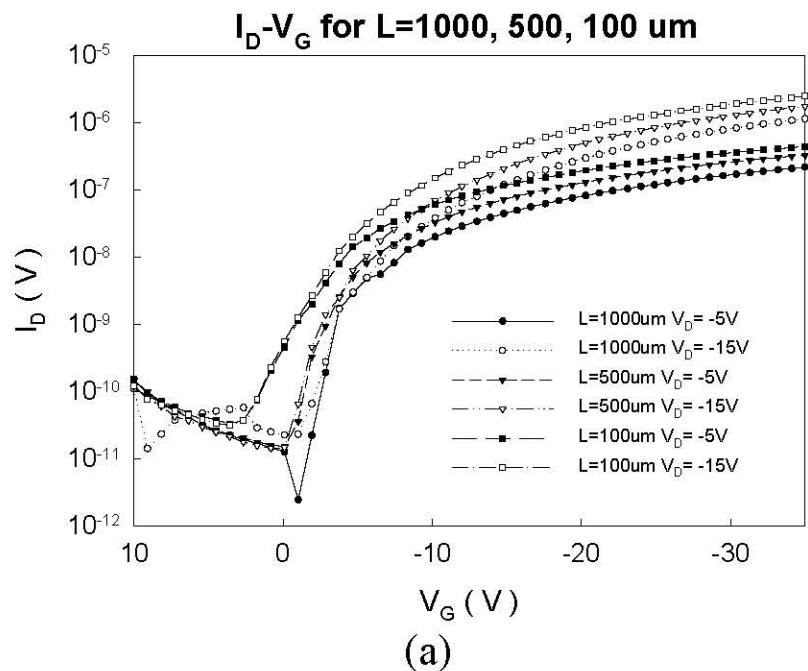

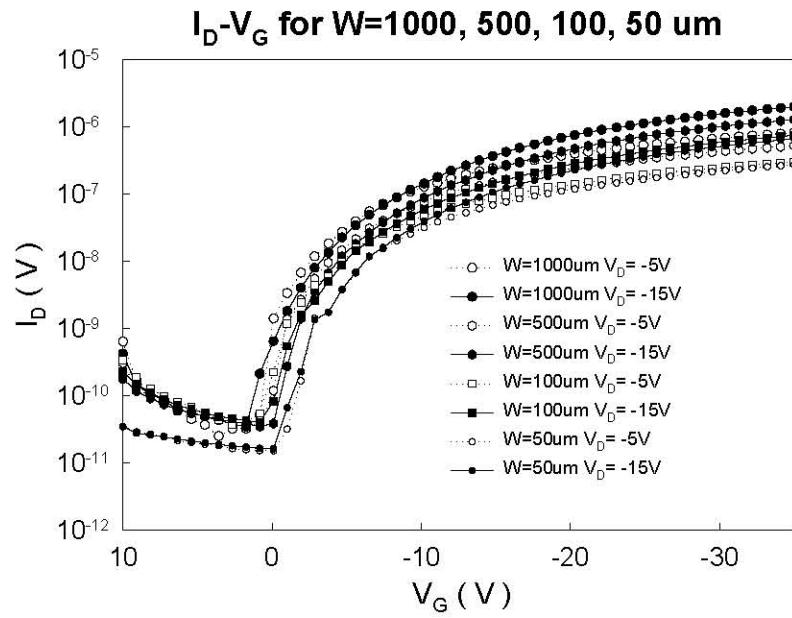

Figure 2-24:(a)The transfer characteristics of the device at drain voltages  $V_D = -5V$  and  $V_D = -15V$ , and (b)the output characteristics at gate voltage  $V_G = -10$  and  $V_G = -30V$ , compared with the length of 1000um ,500um and 100um.

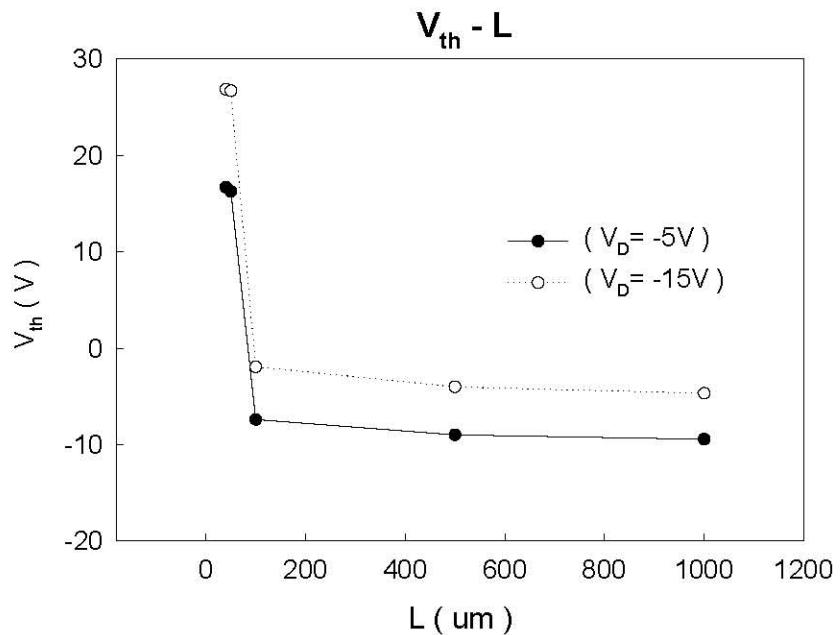

Figure 2-25:The threshold voltage versus length under drain bias ( $V_D = -5V$  and  $-15V$ ), in linear and saturation region respectively.

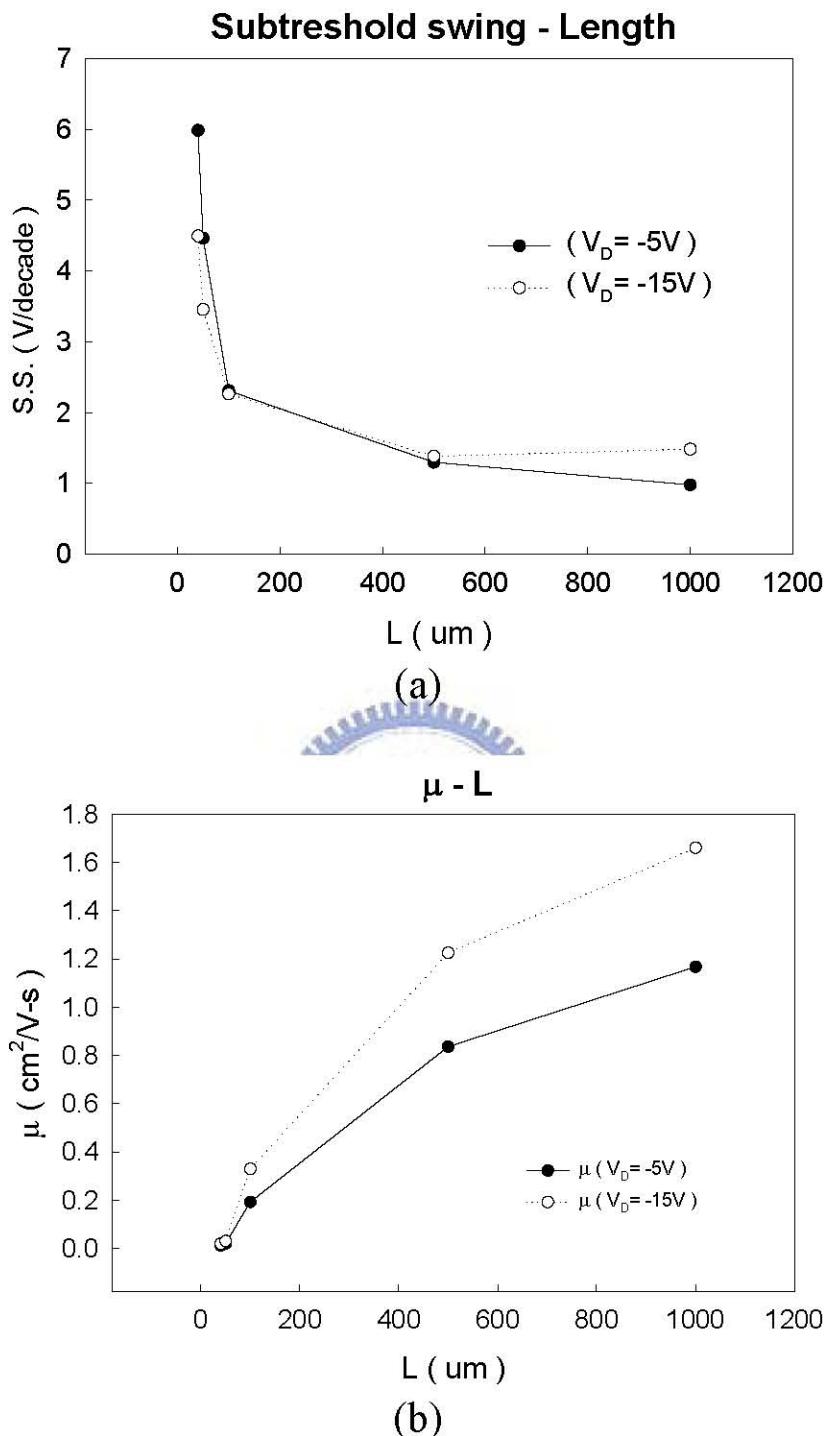

Figure 2-26:(a)The subthreshold swing versus length under the drain voltage of  $-5V$  and  $-15V$ , and (b)the linear and saturation mobility versus length under drain bias ( $V_D = -5V$  and  $-15V$ ).

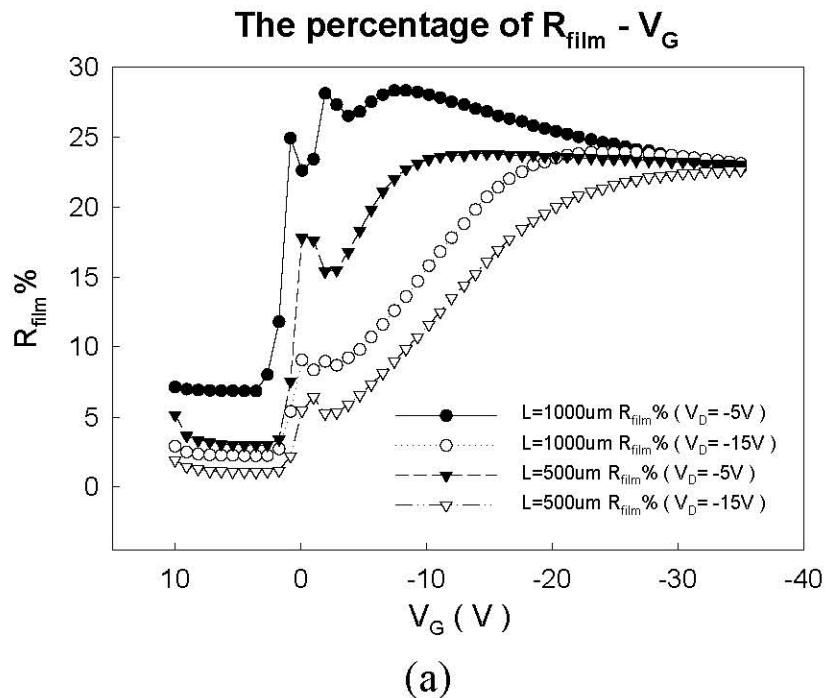

Figure 2-27:(a)The percentage of the film resistances as a function of gate voltage under drain bias ( $V_D = -5V$  and  $-15V$ ). (b)The percentage of the film resistances as a function of drain voltage under gate bias ( $V_G = -10V$  and  $-30V$ ). Two different kinds of devices with Length (1000 um and 500 um) would be compared with.

Figure 2-28:(a)The transfer characteristics of the device at drain voltages  $V_D = -5V$  and  $V_D = -15V$ , and (b)the output characteristics at gate voltage  $V_G = -10$  and  $V_G = -30V$ , compared with the width of 1000um, 500um, 100um and 50um.

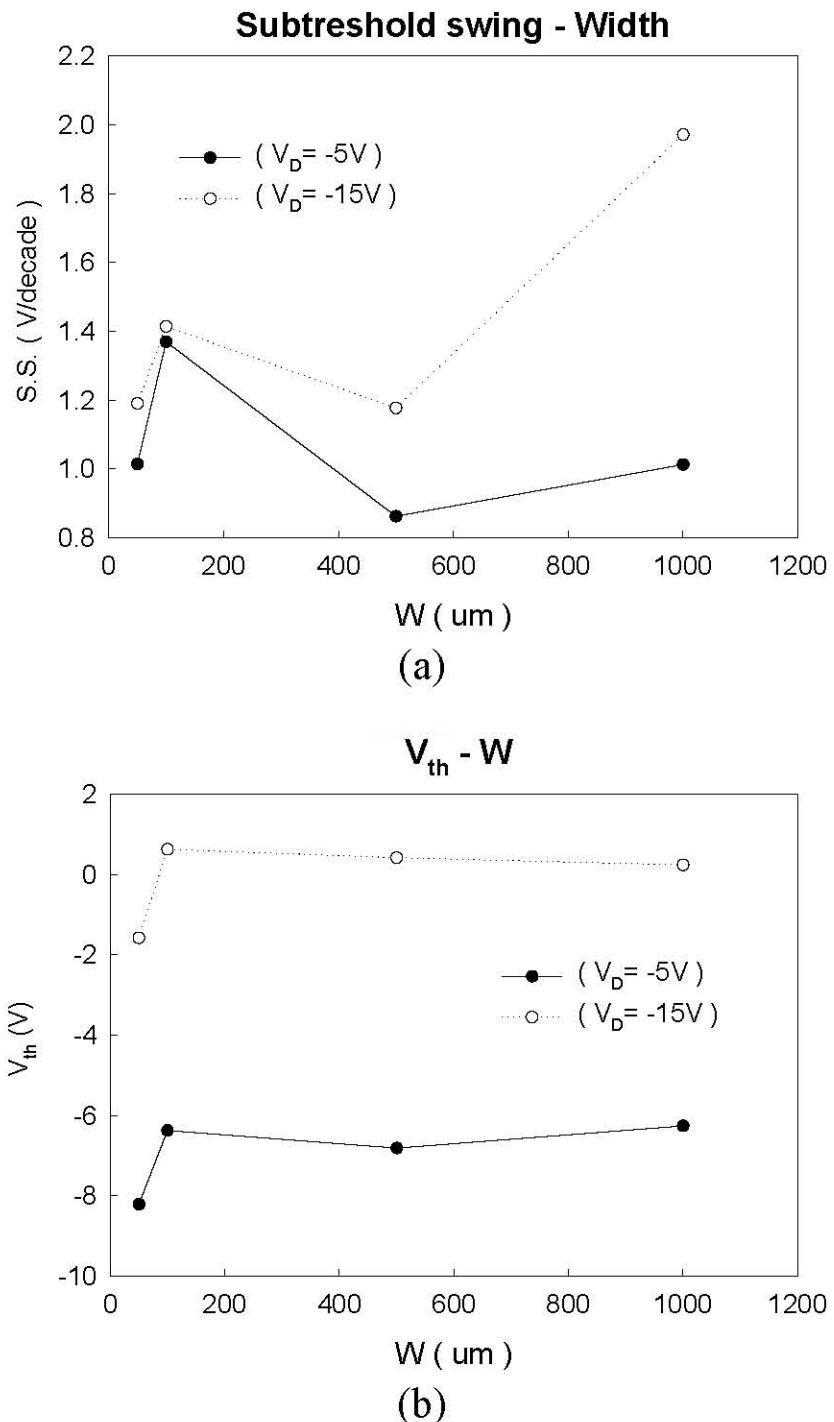

Figure 2-29:(a)The subthreshold swing versus width under the drain voltage of  $-5V$  and  $-15V$ , and (b)the threshold voltage versus width under drain bias ( $V_D = -5V$  and  $-15V$ ), in linear and saturation region respectively.

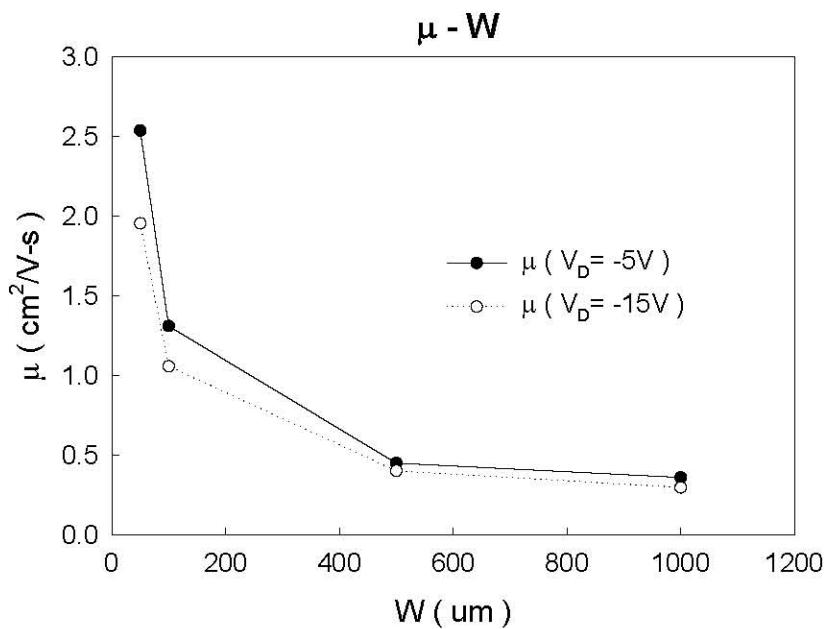

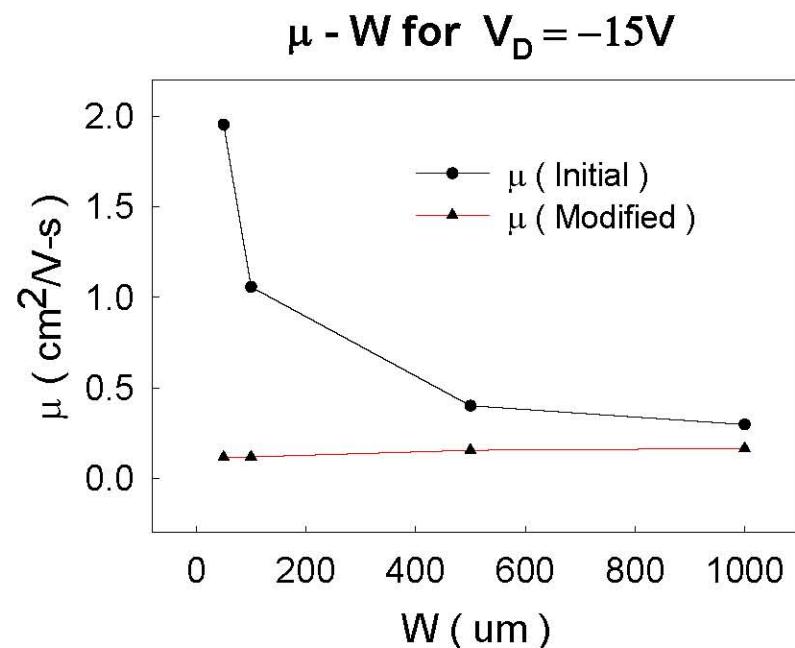

Figure 2-30:The mobility of OTFTs for linear and saturation region as the function of width.

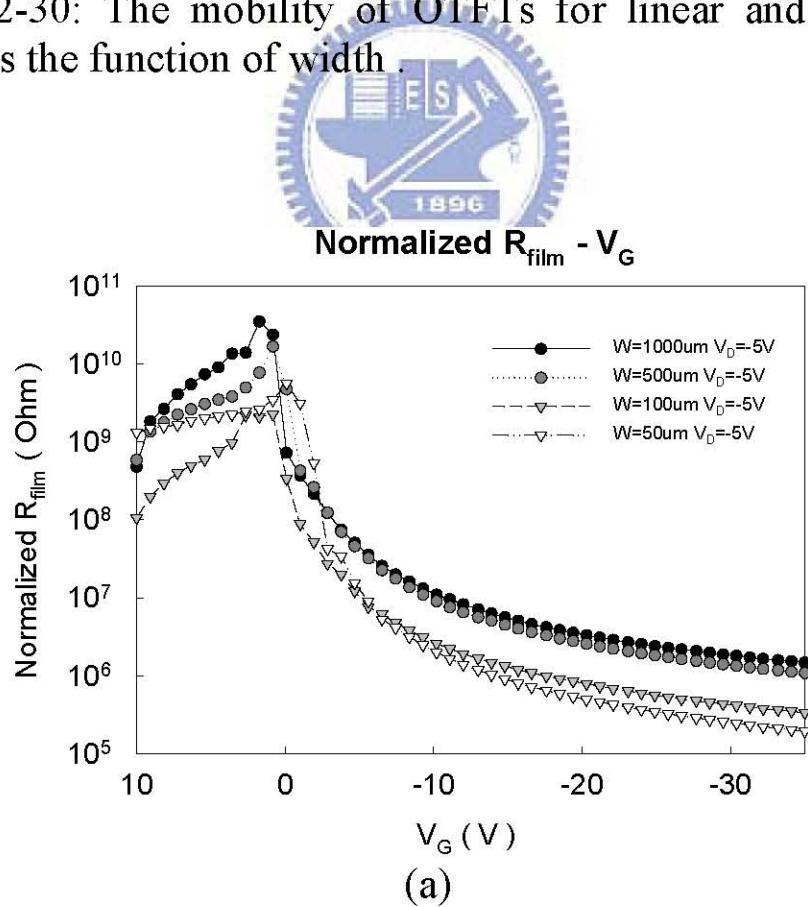

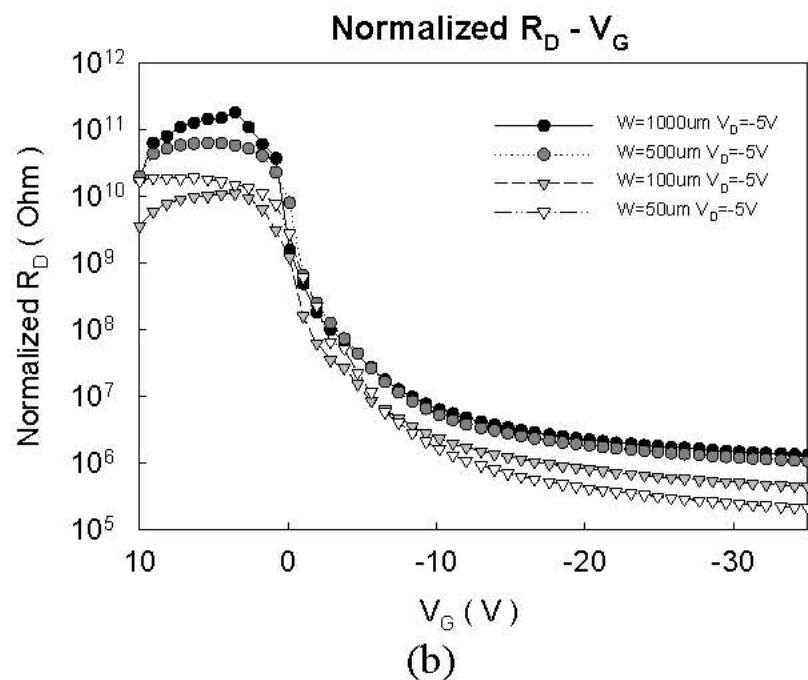

Figure 2-31:(a)The normalized film resistances and (b)the normalized resistances at drain side as a function of gate voltage under drain bias  $V_D = -5V$  and  $-15V$ , taken with the different width of 1000um, 500um, 100um and 50um.

Figure 2-32: The border effect for device, which result from active region fabricated by shadow mask.

Figure 2-33: Comparison with initial mobility and modified mobility, modified by additional width.

## Chapter 3

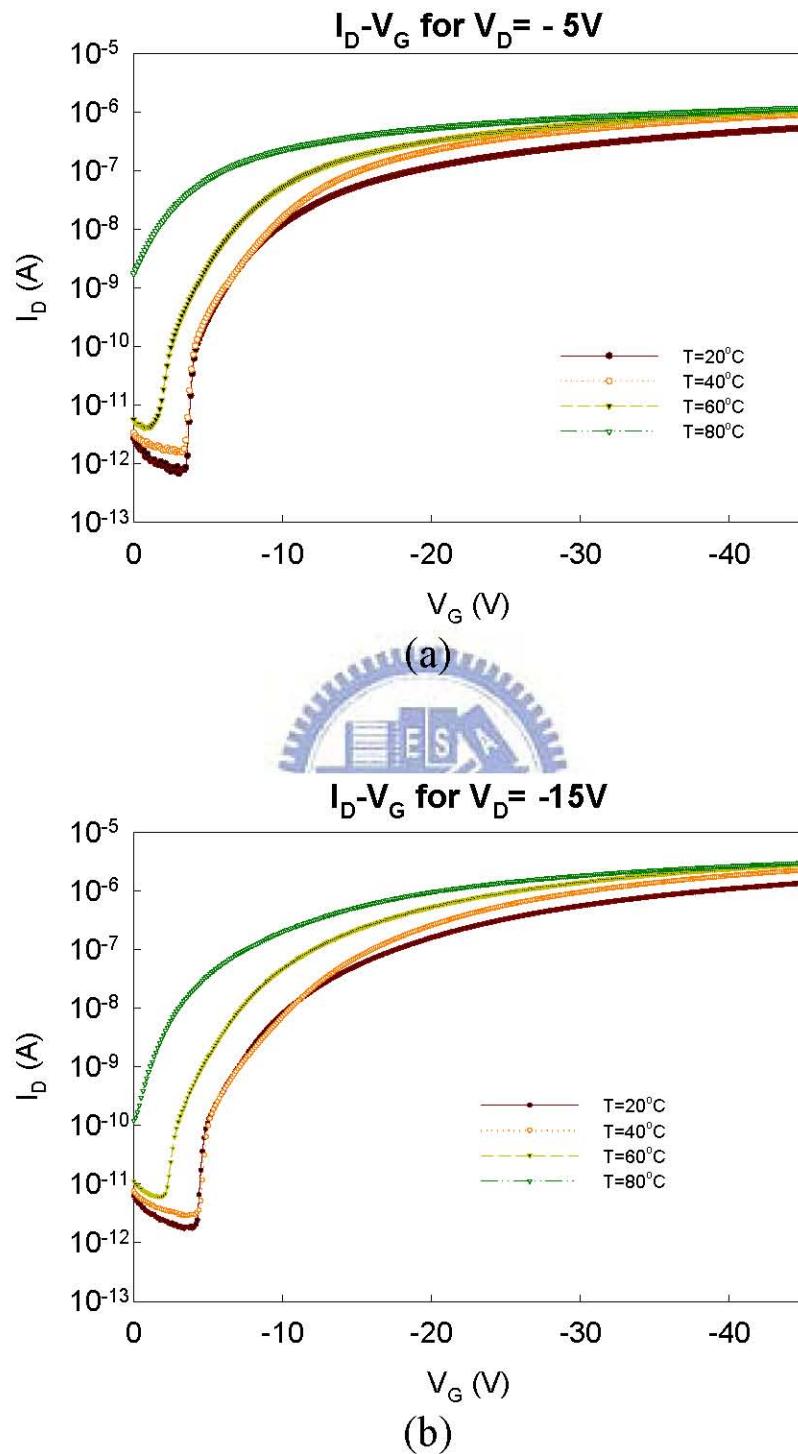

Figure 3-1: The transfer characteristics  $I_D$ - $V_G$  of OTFT with (a) $V_D = -5V$  and (b) $V_D = -15V$ , measured at the temperatures of  $20^\circ C$ ,  $40^\circ C$ ,  $60^\circ C$  and  $80^\circ C$ .

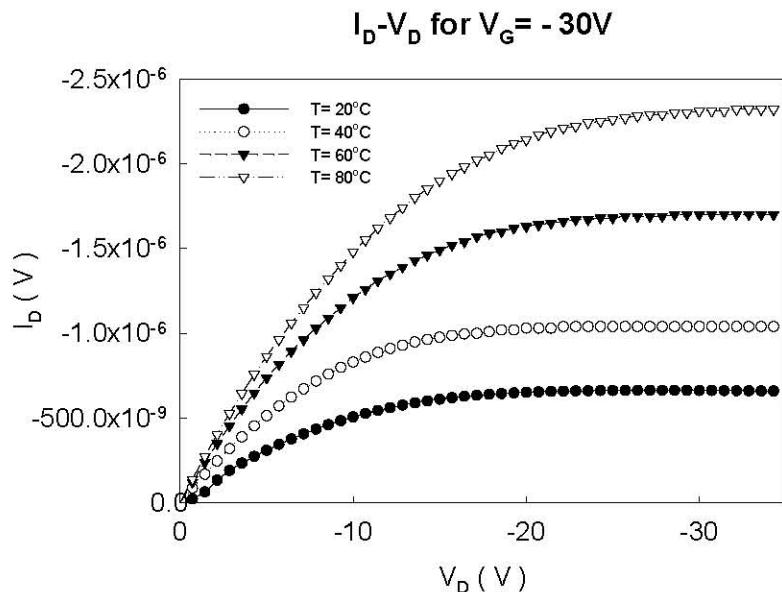

Figure 3-2: The output characteristics for pentacene-based OTFT with four probe structure at the gate voltage drop of  $-30V$ , taken at the substrate temperature of  $20^\circ C$ ,  $40^\circ C$ ,  $60^\circ C$  and  $80^\circ C$ .

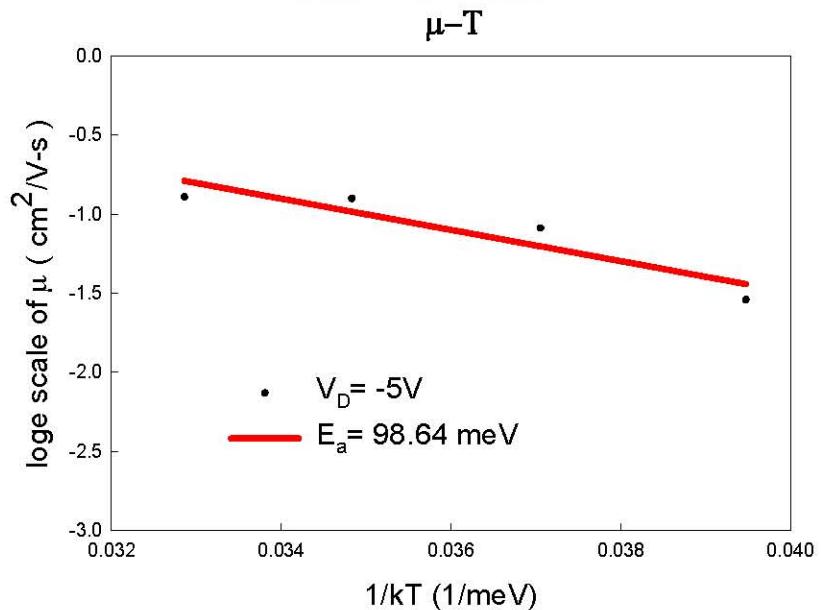

Figure 3-3: Arrhenius plot of linear regime mobility illustrating the activated nature of mobility in pentacene-based OTFT over a temperature range (293-375K).

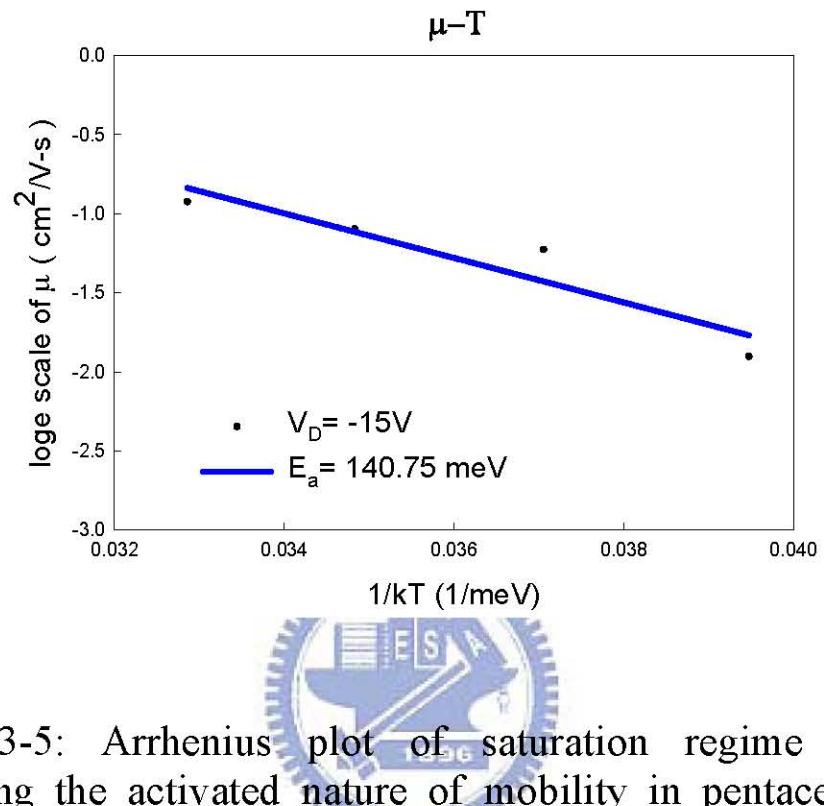

Figure 3-4: Arrhenius plot of saturation regime mobility illustrating the activated nature of mobility in pentacene-based OTFT over a temperature range (293-375K).

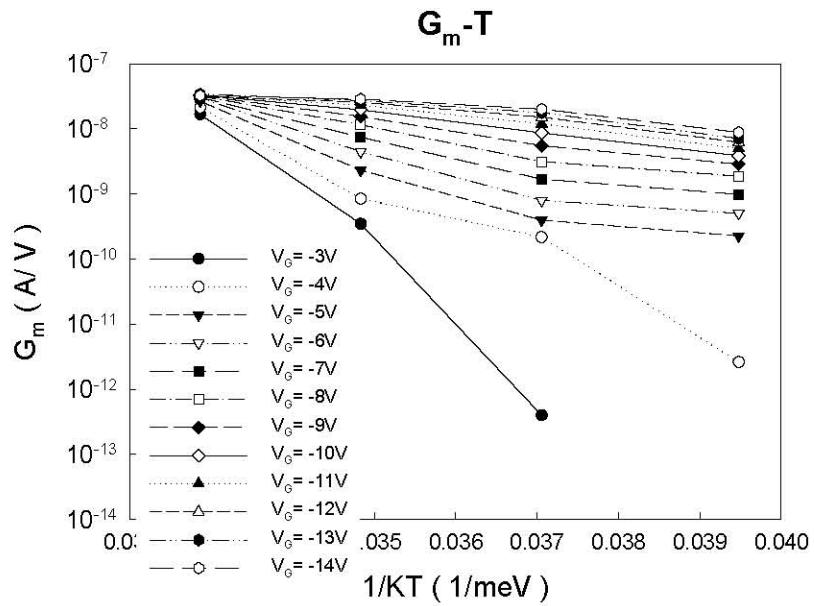

Figure 3-5: Activation plots of transconductance for different gate voltages for the device corresponding to Figure 3-1. The activation fits appear to intersect at  $355K$  approximately, which is the isokinetic temperature.

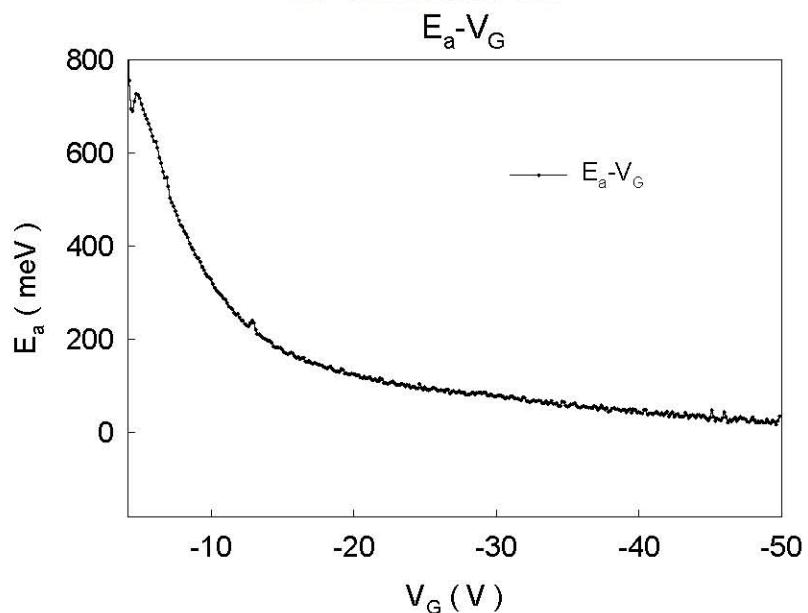

Figure 3-6: Plot of activation energy derived from the transconductance as a function of gate voltage.

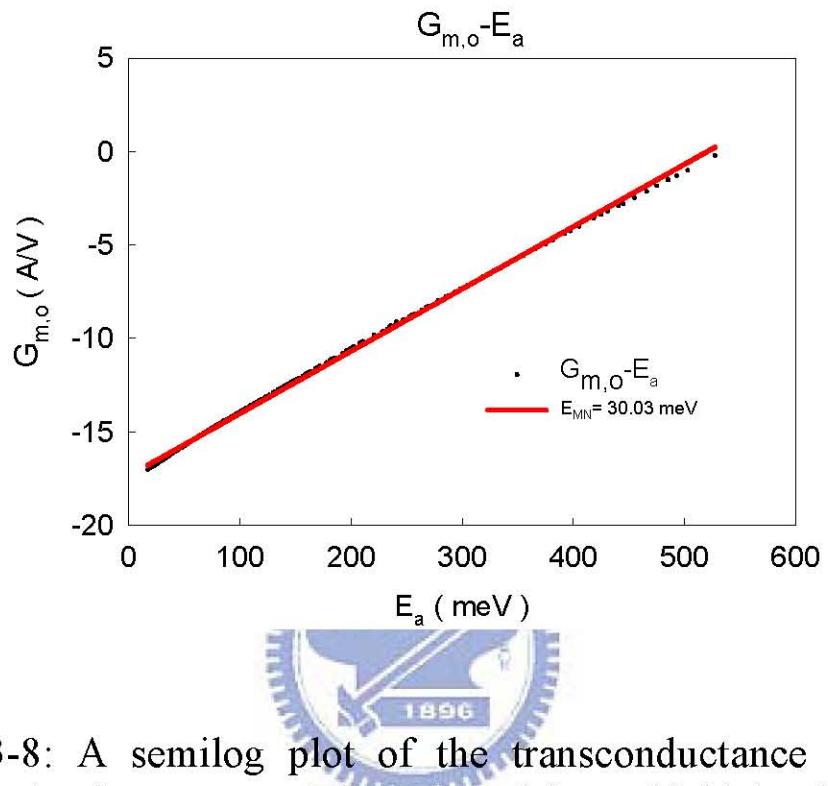

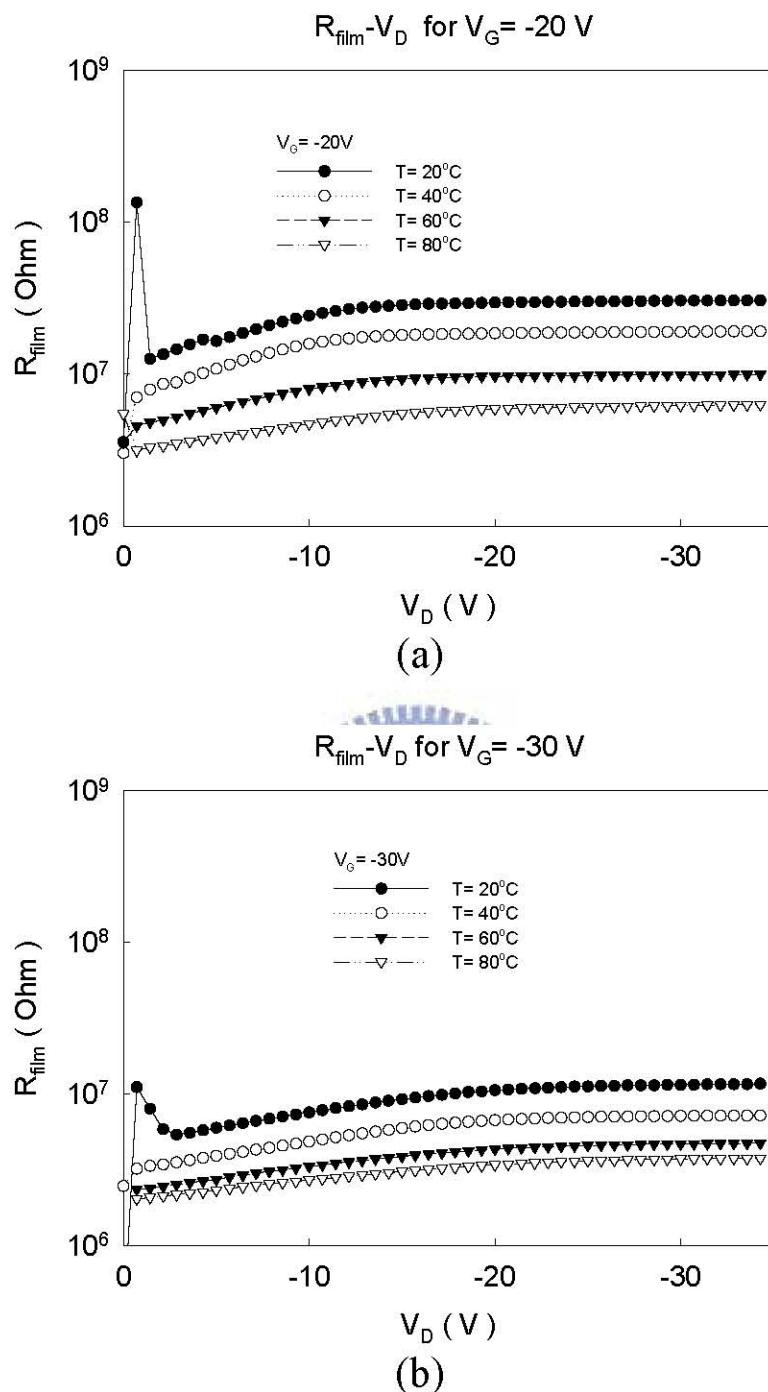

Figure 3-7: A semilog plot of the transconductance prefactor versus activation energy. There is a Meyer–Neldel relationship between the activation energy and the prefactor with a Meyer–Neldel energy of  $30.03$  meV, which corresponds well with the isokinetic temperature of  $348.5K$ .

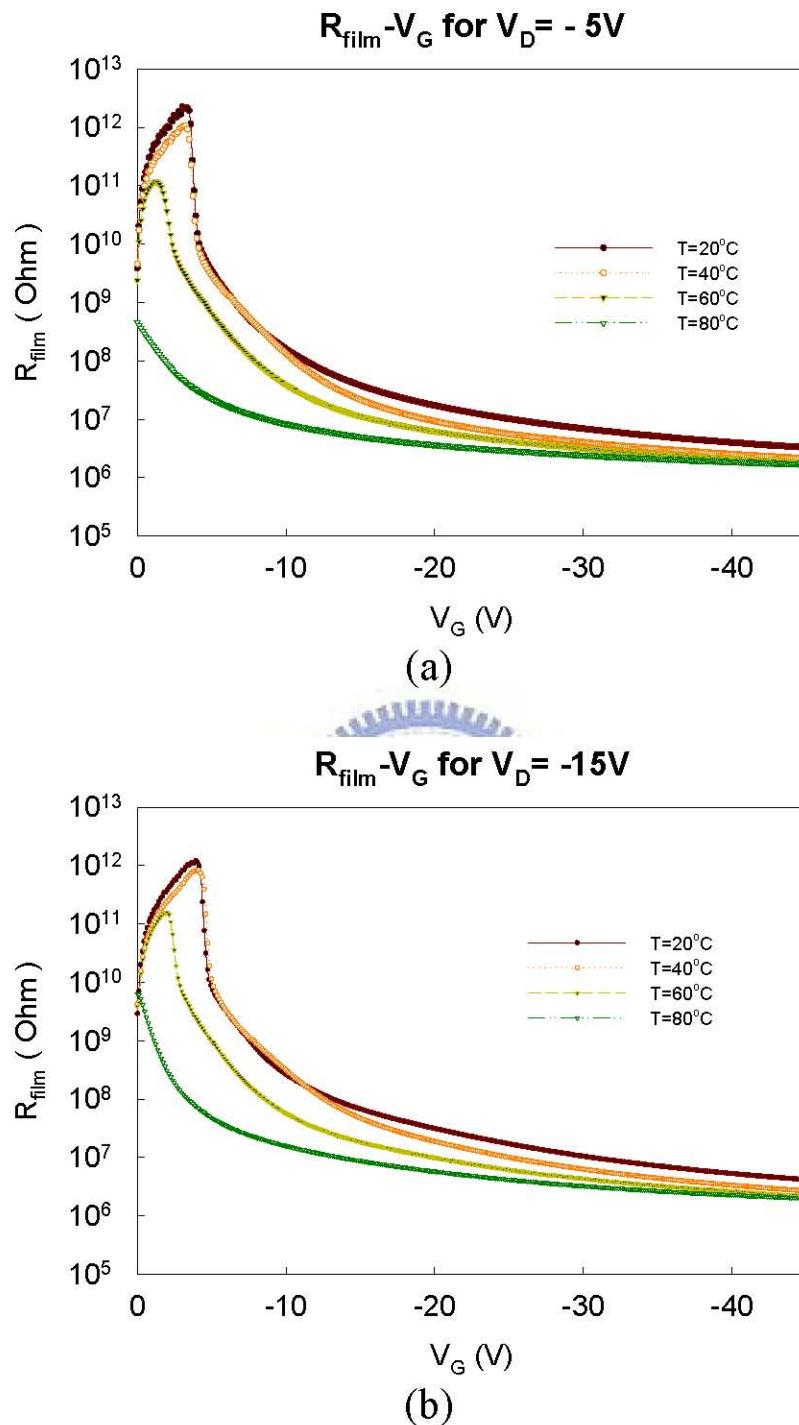

Figure 3-8: Plots of film resistance as a function of gate voltage at the drain voltage of (a) $V_D = -5V$  and (b) $V_D = -15V$  for an operating OTFT at different temperatures of  $20^\circ C$ ,  $40^\circ C$ ,  $60^\circ C$  and  $80^\circ C$ .

Figure 3-9: The resistance in channel as a function of drain voltage under gate bias of (a) $V_D = -20V$  and (b) $V_G = -30V$ , taken at the temperatures of  $20^\circ C$ ,  $40^\circ C$ ,  $60^\circ C$  and  $80^\circ C$ .

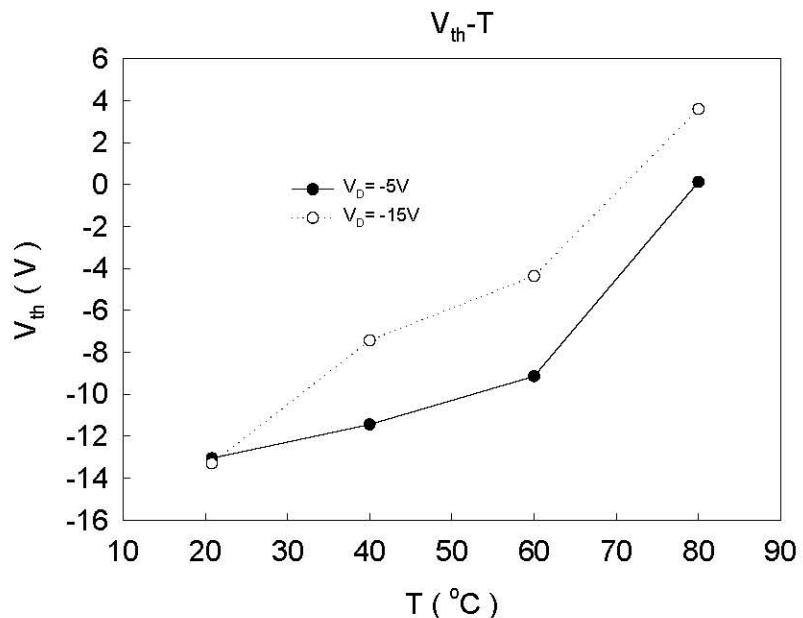

Figure 3-10: The threshold voltage versus temperature under drain bias ( $V_D = -5V$  and  $-15V$ ), in linear and saturation region respectively.

Figure 3-11: The subthreshold swing versus temperature under the drain voltage of  $-5V$  and  $-15V$ .

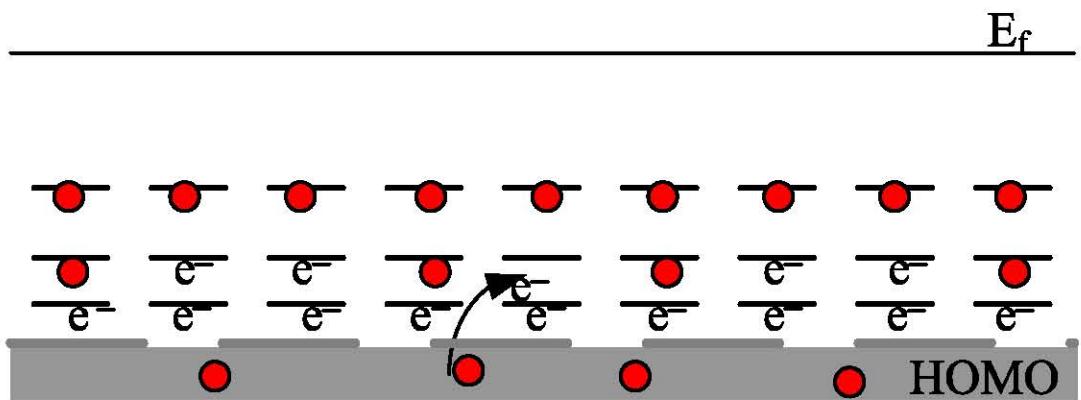

Figure 3-12: Schematic illustration of conduction by multiple trapping and release at lower temperature.

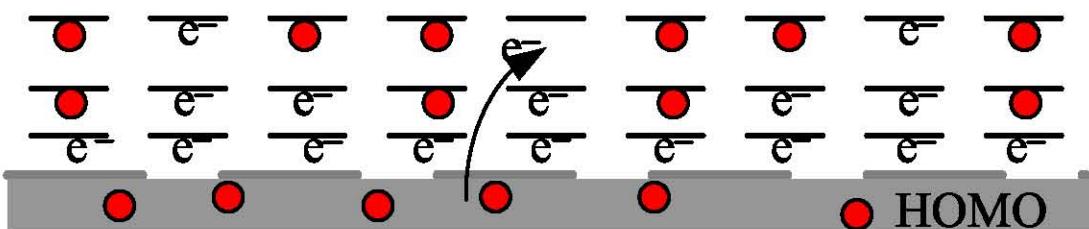

Figure 3-13: Schematic illustration of conduction by multiple trapping and release at higher temperature.

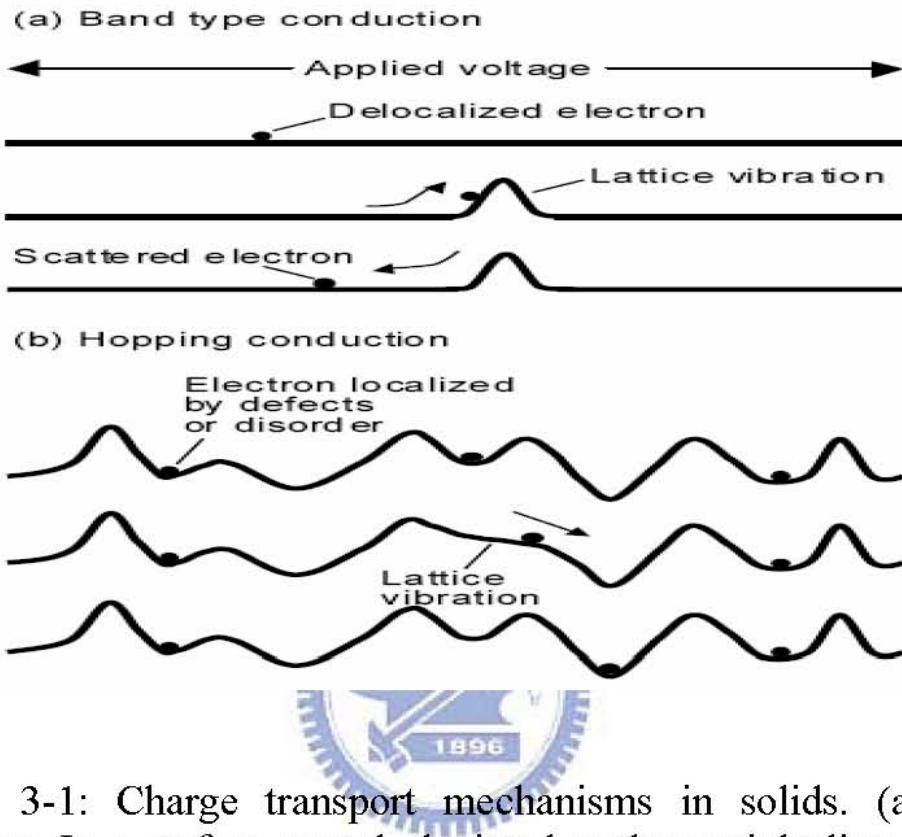

Figure 3-14: Charge transport mechanisms in solids. (a) Band transport. In a perfect crystal, depicted as the straight line, a free carrier is delocalized. There are always lattice vibrations that disrupt the crystal symmetry. Carriers are scattered at these phonons, which limit the charge carrier mobility. The mobility for band transport increases with decreasing temperature. (b) Hopping transport. If the carrier is localized due to defects, disorder or self localization, e.g. in the case of polarons, the lattice vibrations are essential for a carrier to move from one site to another. For hopping transport the mobility increases with increasing temperature. (M. Matters et al. Synth. Met. 1999 [43])

## Chapter 4

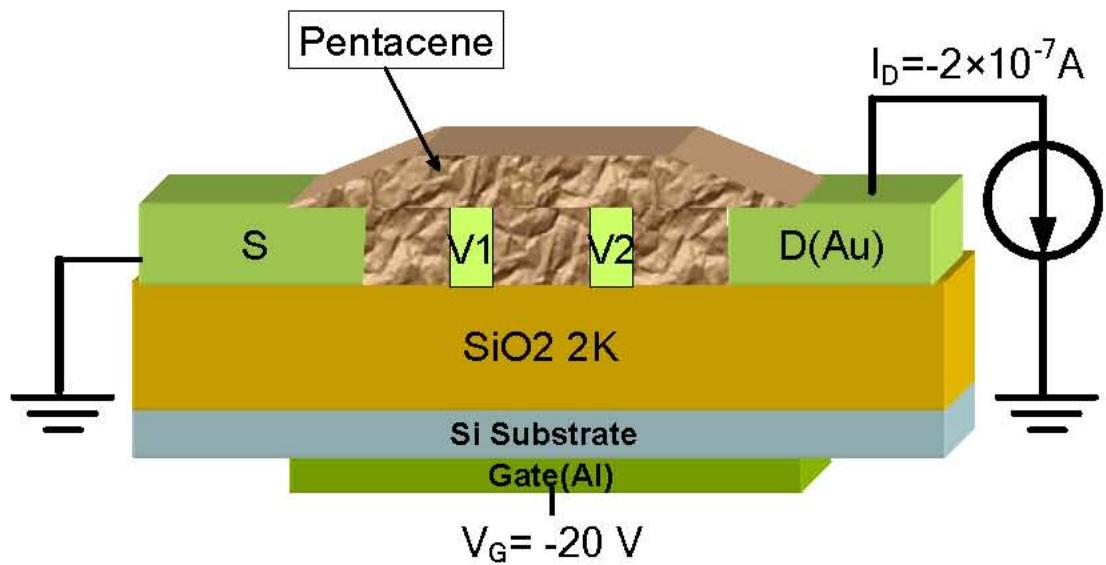

Figure 4-1: The schematic diagram of the bottom-contact OTFT with four probe structure. The applied current source is  $2 \times 10^{-7} A$  with DC gate bias ( $V_G = -20V$ ) to induce a channel of accumulated carriers.

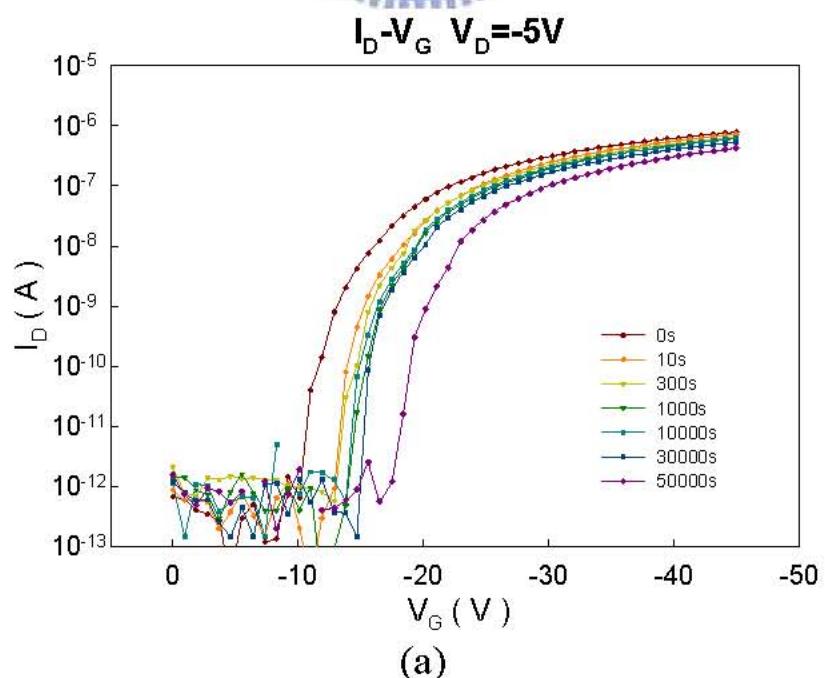

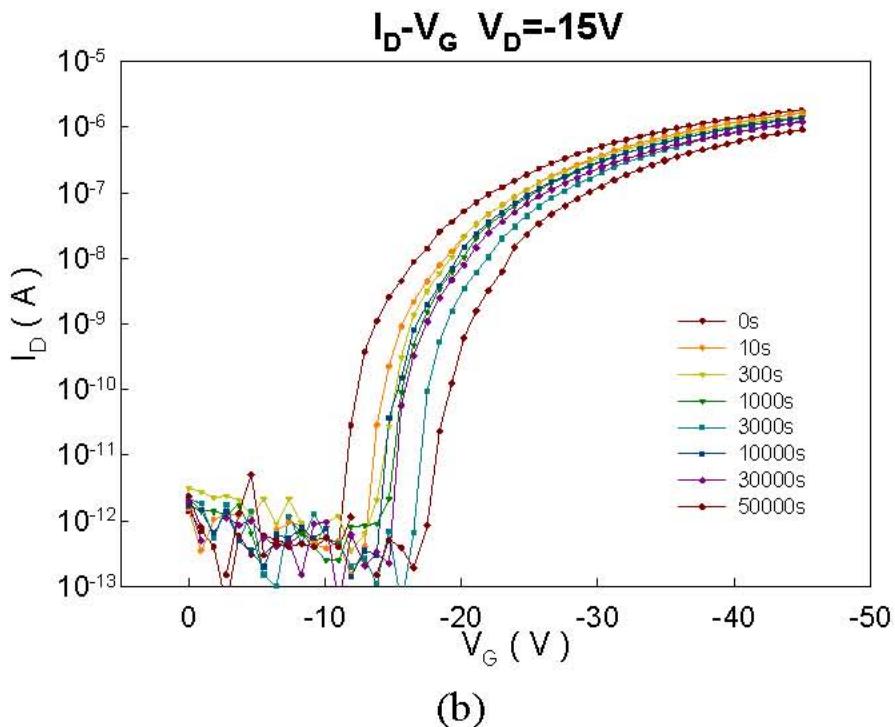

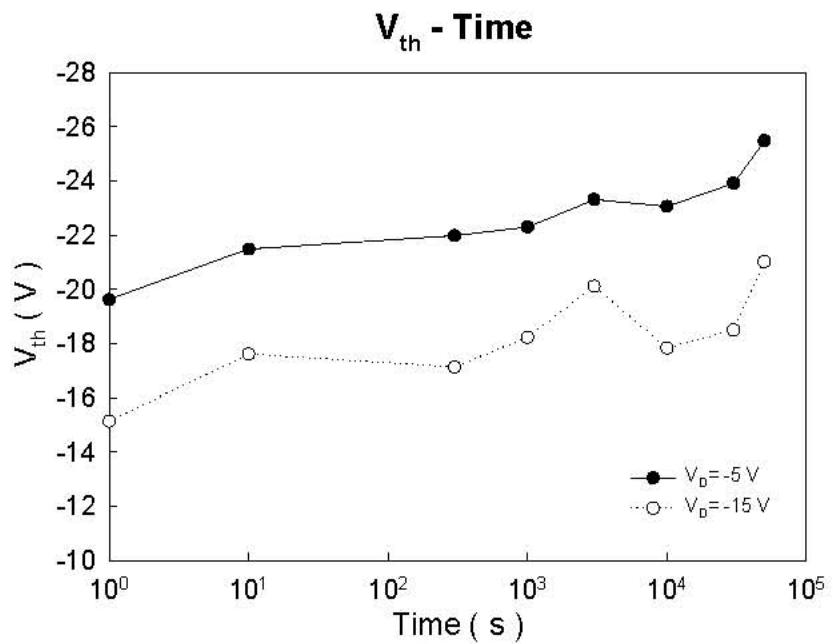

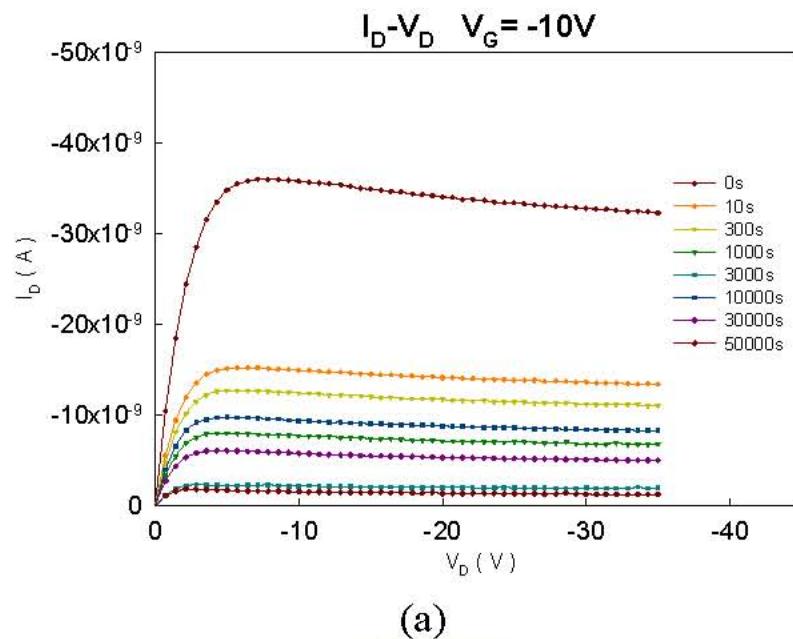

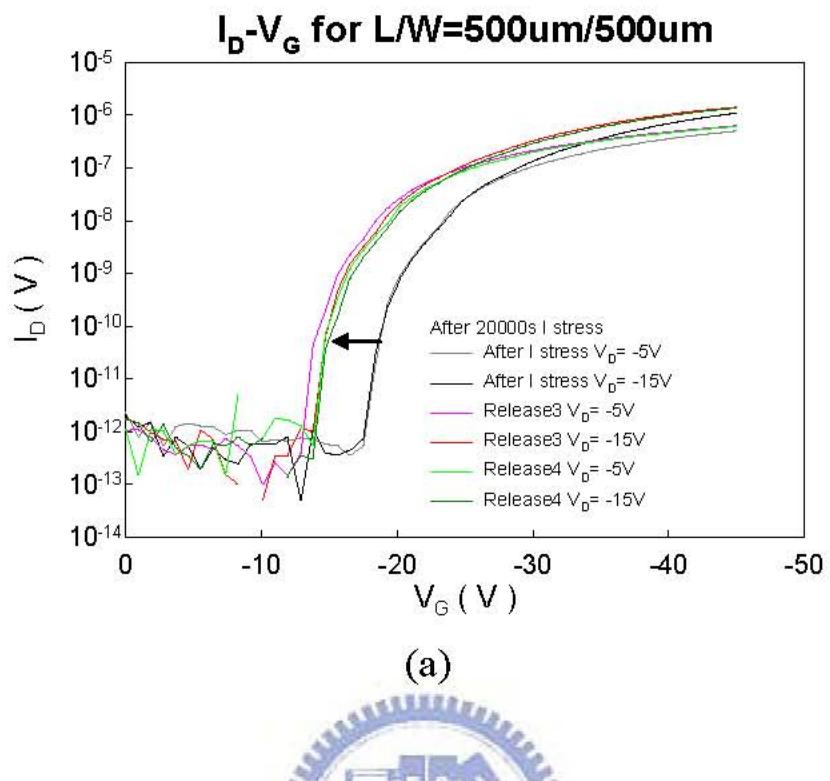

Figure 4-2: The transfer characteristics  $I_D$ - $V_G$  of OTFT with (a) $V_D = -5V$  and (b) $V_D = -15V$  after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

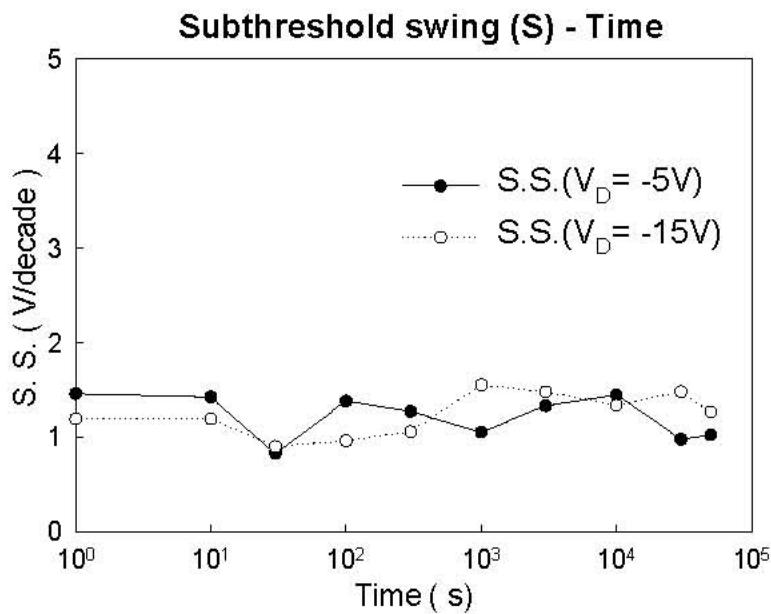

Figure 4-3: The subthreshold swing versus time under drain bias ( $V_D = -5V$  and  $-15V$ ),

taken after 0s, 10s, 1000s, 10000s, 30000s and 50000s current stress.

Figure 4-4: The threshold voltage versus time under drain bias ( $V_D = -5V$  and  $-15V$ ) taken after 0s, 10s, 1000s, 10000s, 30000s and 50000s current stress.

Figure 4-5: The linear and saturation mobility versus time under drain bias ( $V_D = -5V$  and  $-15V$ ) taken after 0s, 10s, 1000s, 10000s, 30000s and 50000s current stress.

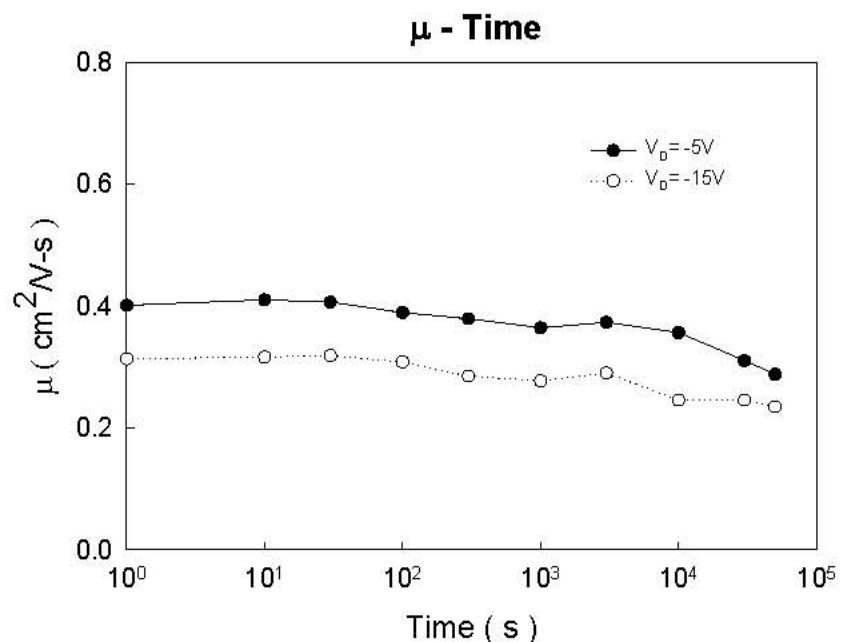

Figure 4-6: The structure of benzene in pentacene. Comparing the degradation of  $\pi$  bond (a)before current stress, and (b)after current stress.

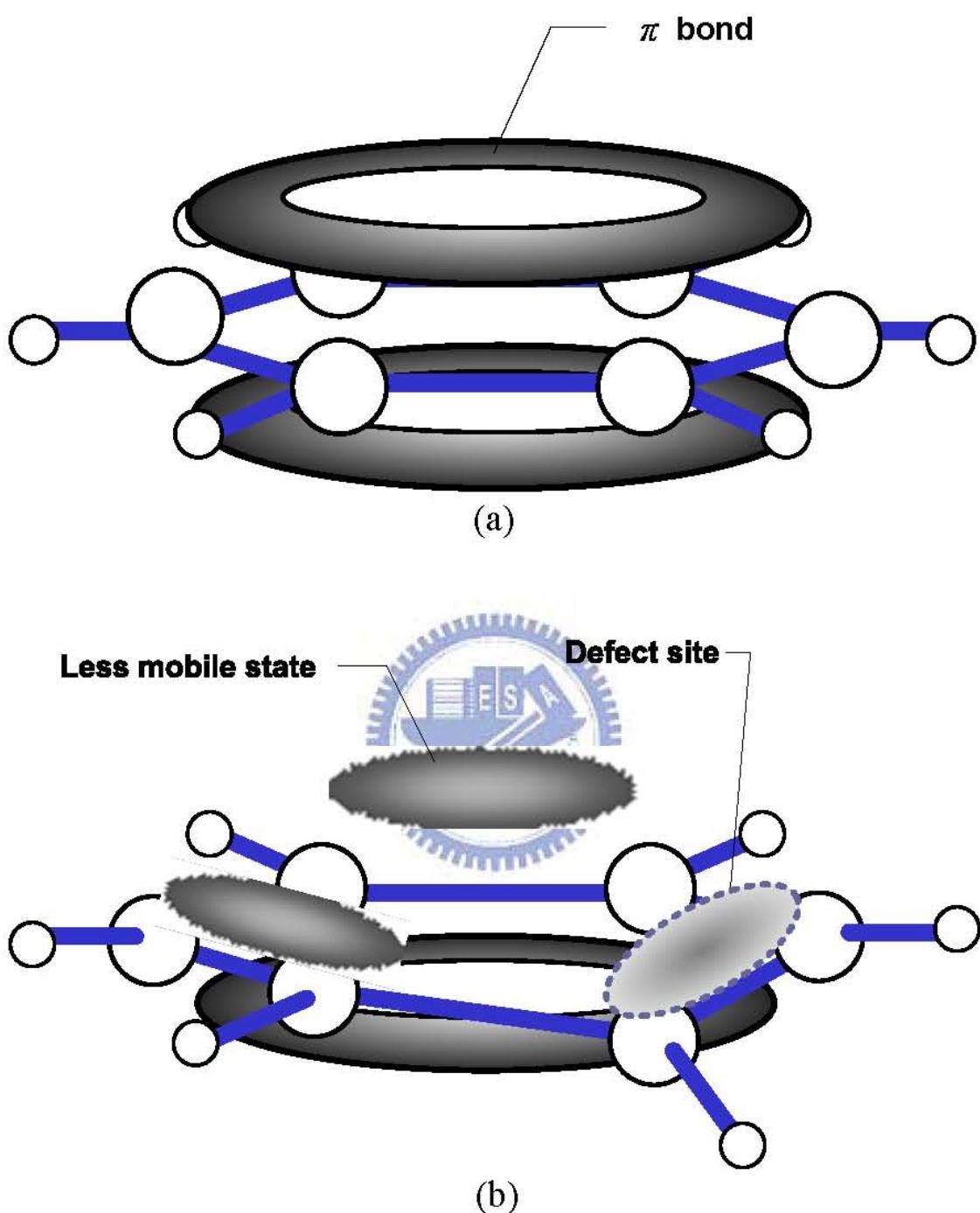

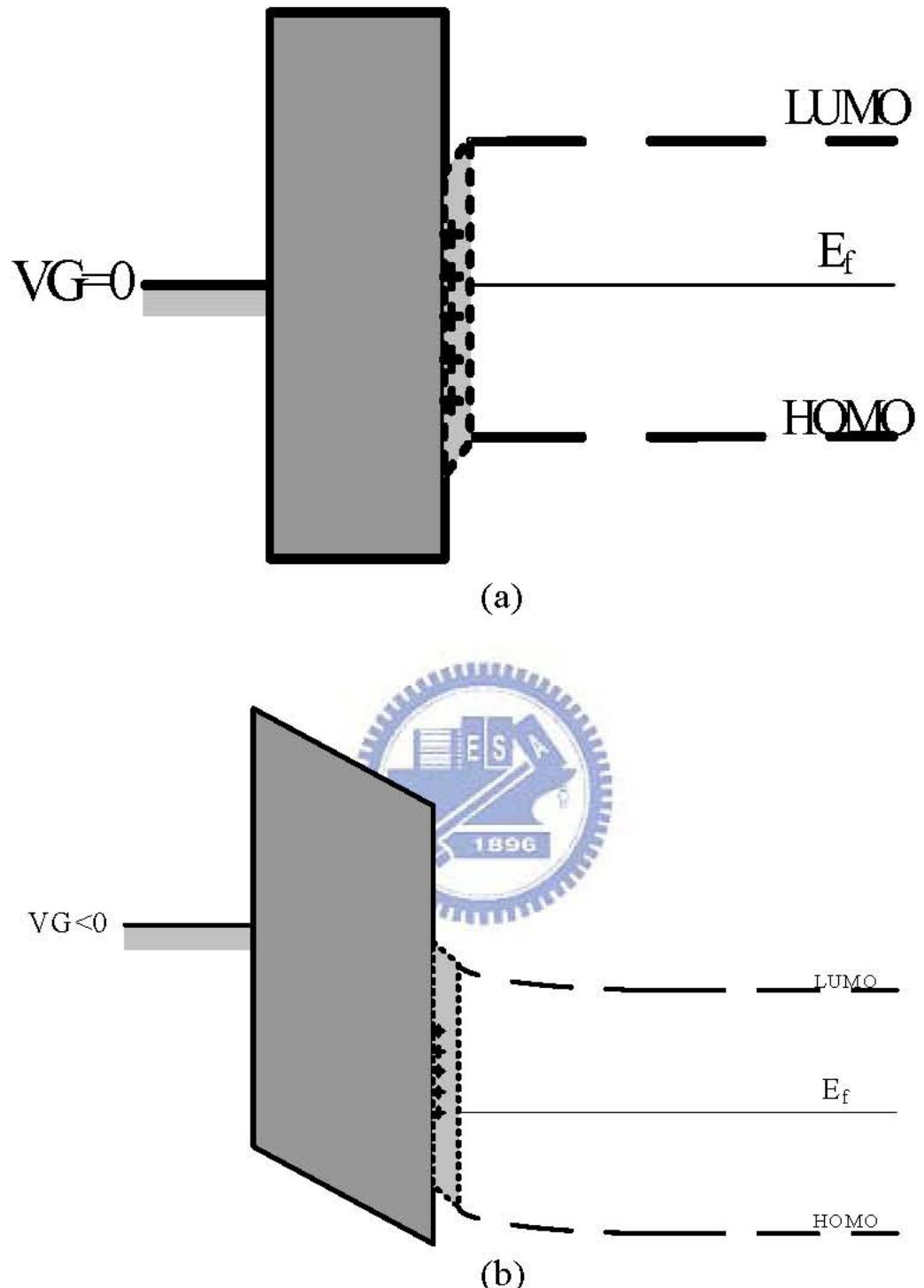

Figure 4-7: The energy band diagrams show the formation of the positive trapping charges between LUMO and HOMO. (a)The energy band diagram of a metal and a semiconductor with an oxide layer between them, and (b)the energy level of pentacene.

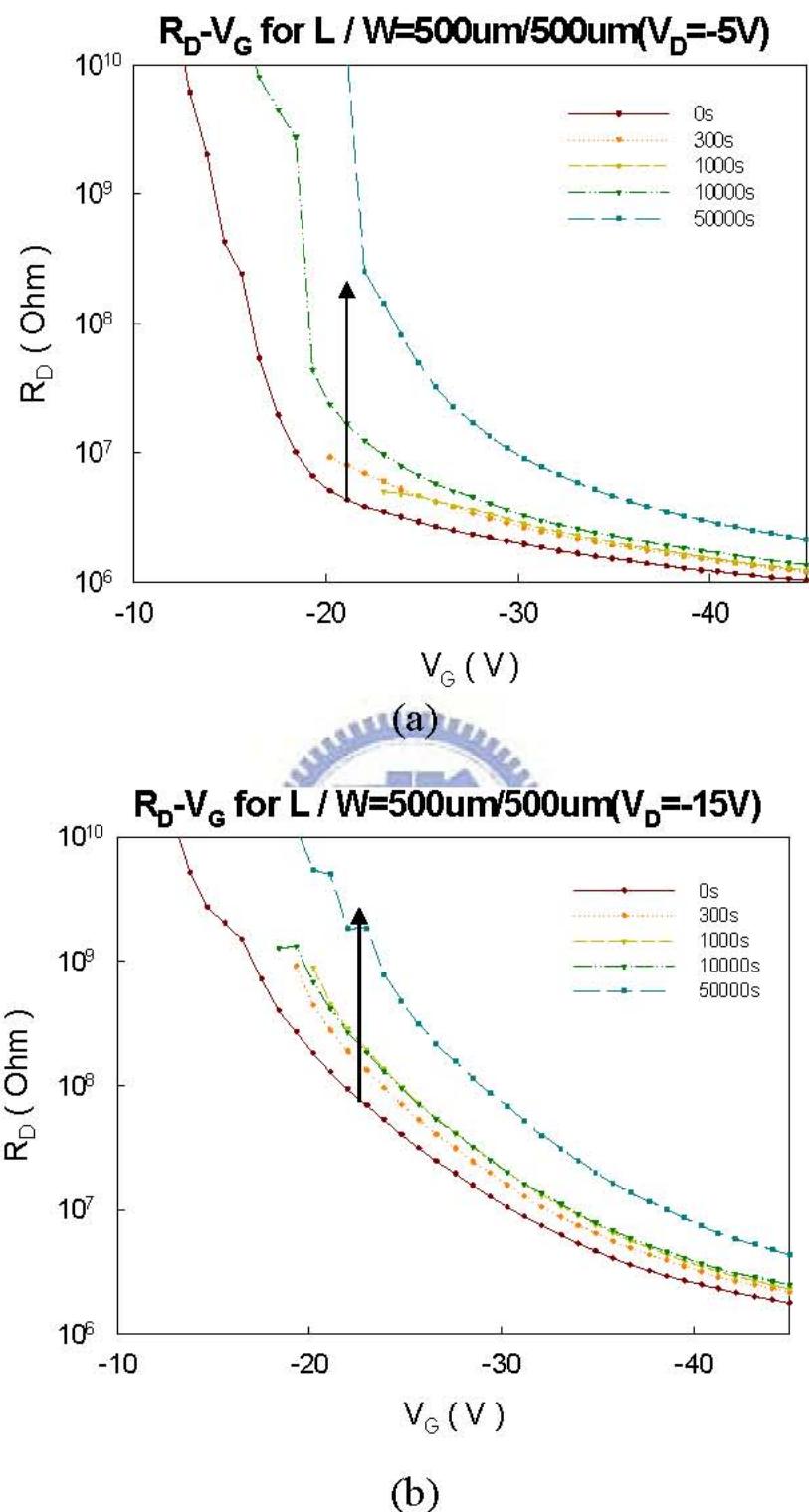

Figure 4-8: The resistance at drain side as a function of gate voltage under drain bias (a) $V_D = -5V$  and (b) $V_G = -15V$  taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

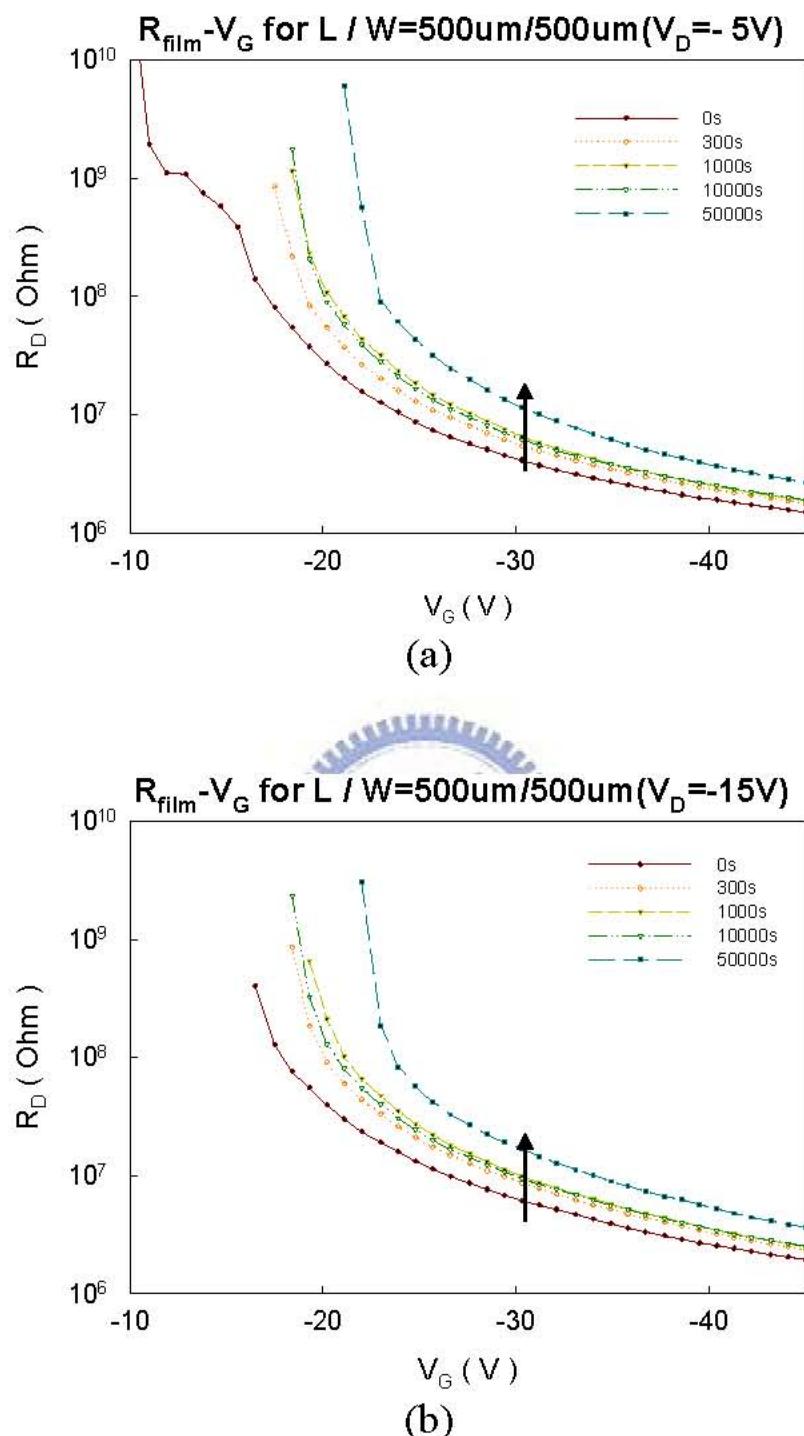

Figure 4-9: The resistance in channel as a function of gate voltage under drain bias (a) $V_D = -5V$  and (b) $V_G = -15V$  taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

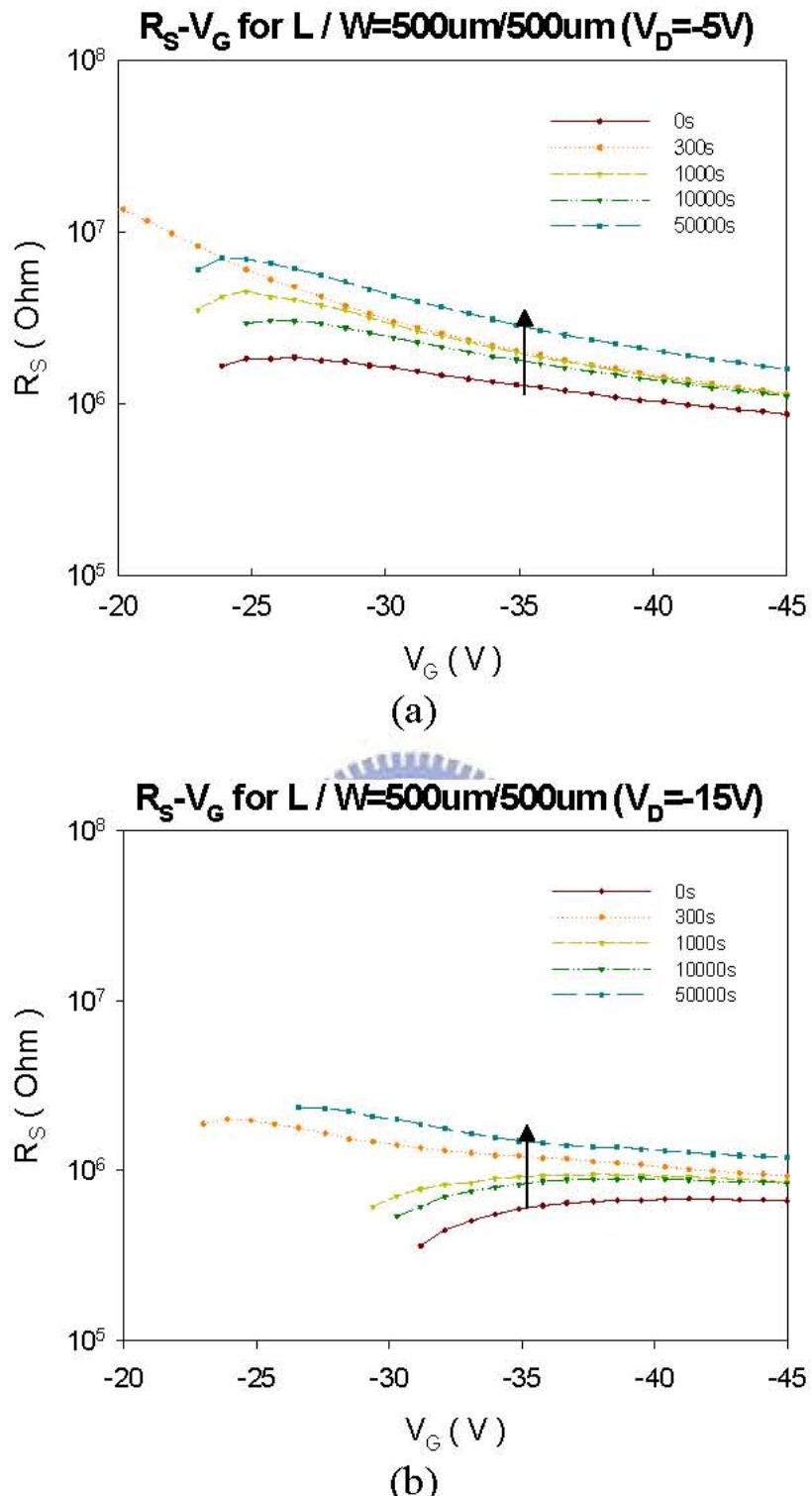

Figure 4-10: The resistance at source side as a function of gate voltage under drain bias (a) $V_D = -5V$  and (b) $V_G = -15V$  taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

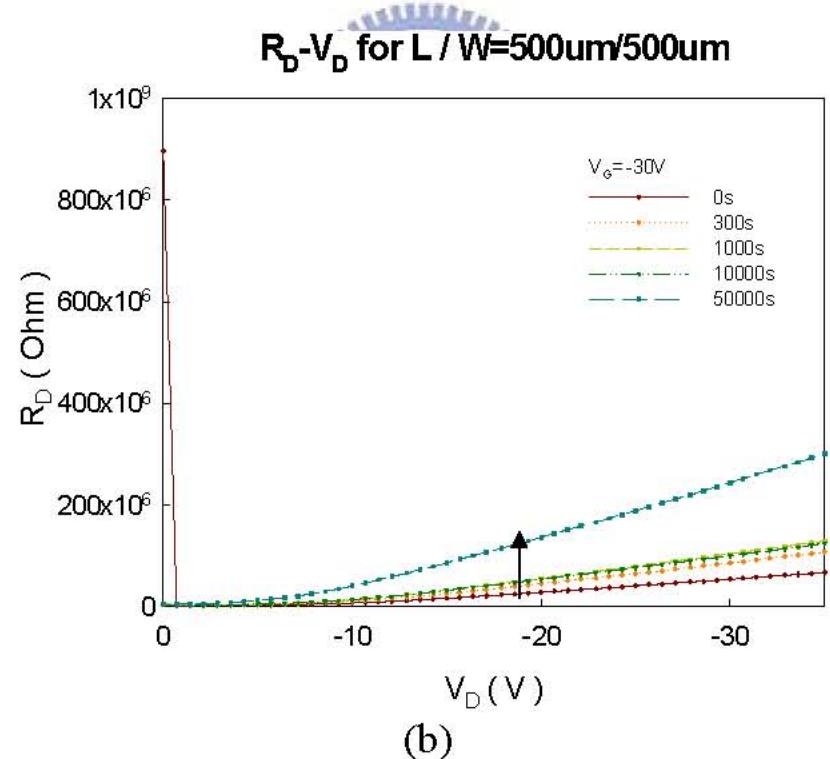

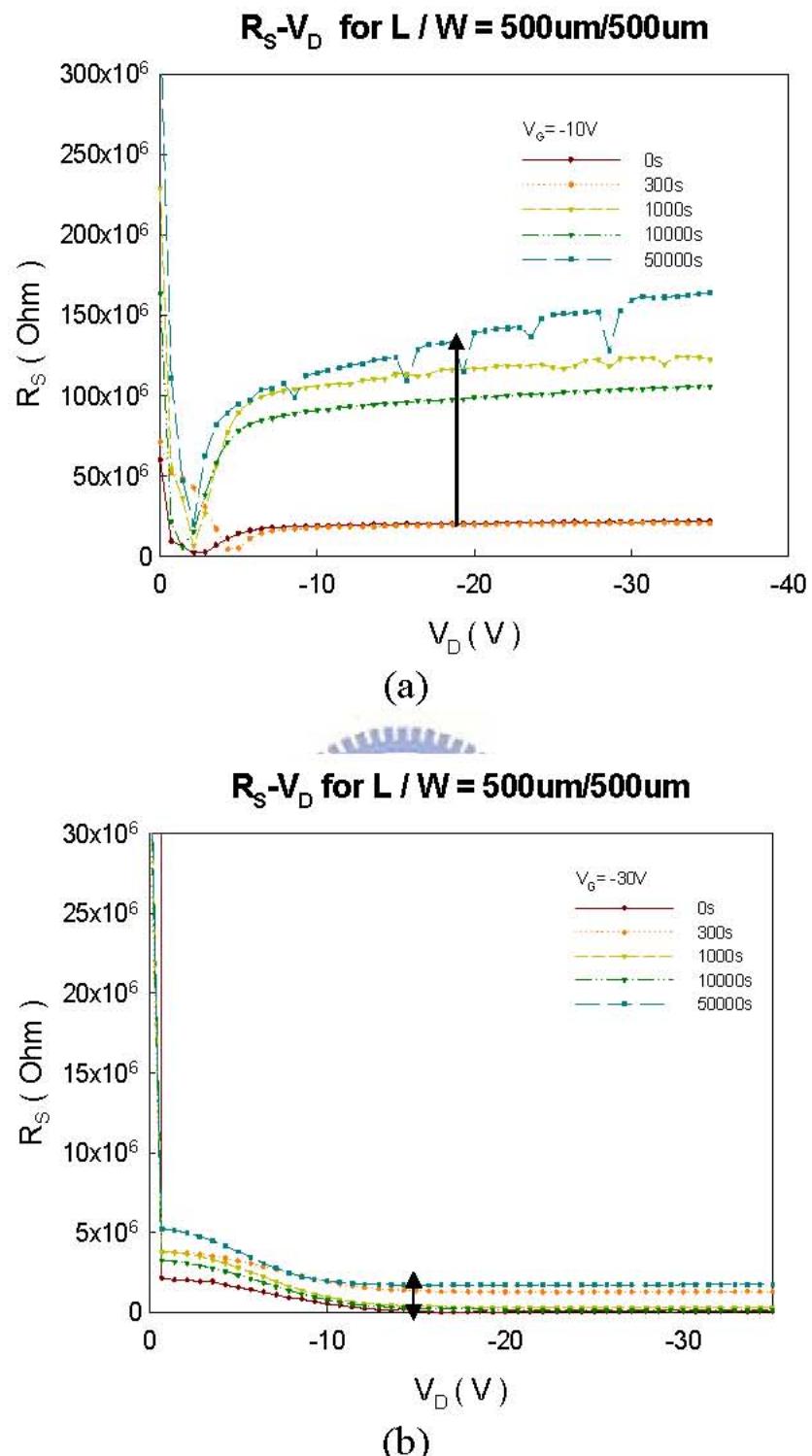

Figure 4-11: The resistance at drain side as a function of drain voltage under gate bias (a) $V_G = -10V$  and (b) $V_G = -30V$  taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

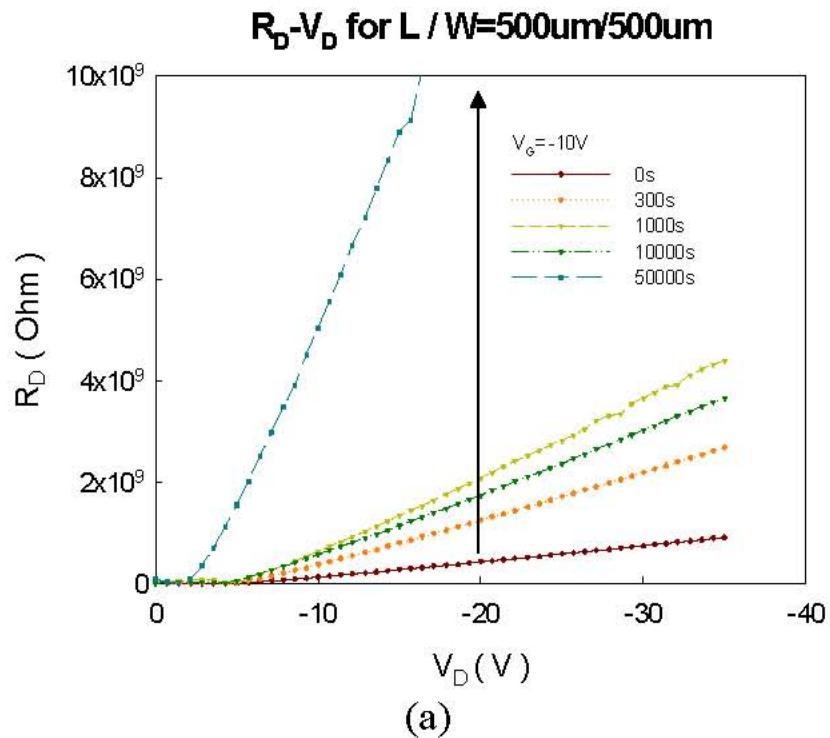

Figure 4-12: The resistance at drain side as a function of drain voltage under gate bias (a) $V_G = -10V$  and (b) $V_G = -30V$  taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

Figure 4-13: The resistance at source side as a function of drain voltage under gate bias

(a)  $V_G = -10V$  and (b)  $V_G = -30V$  taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

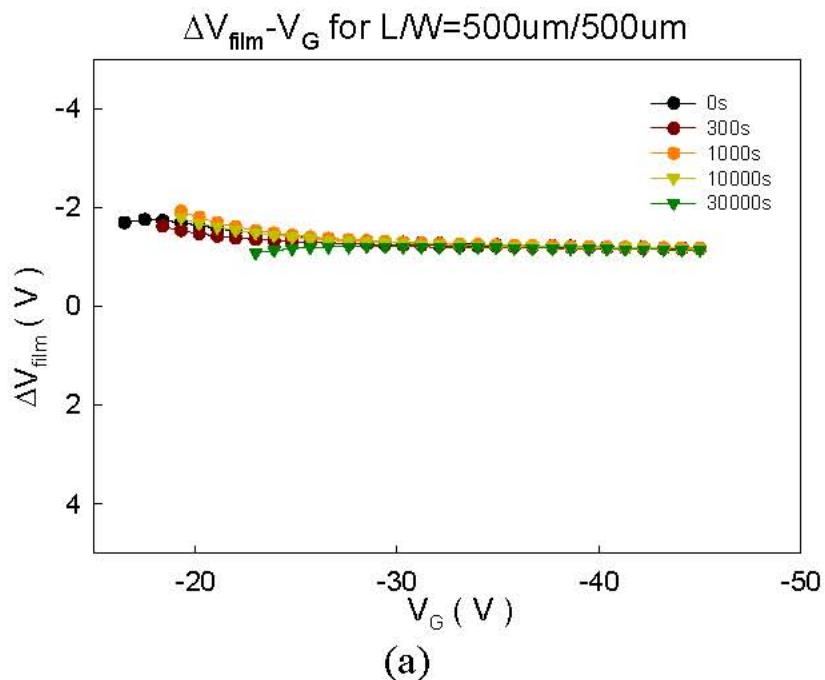

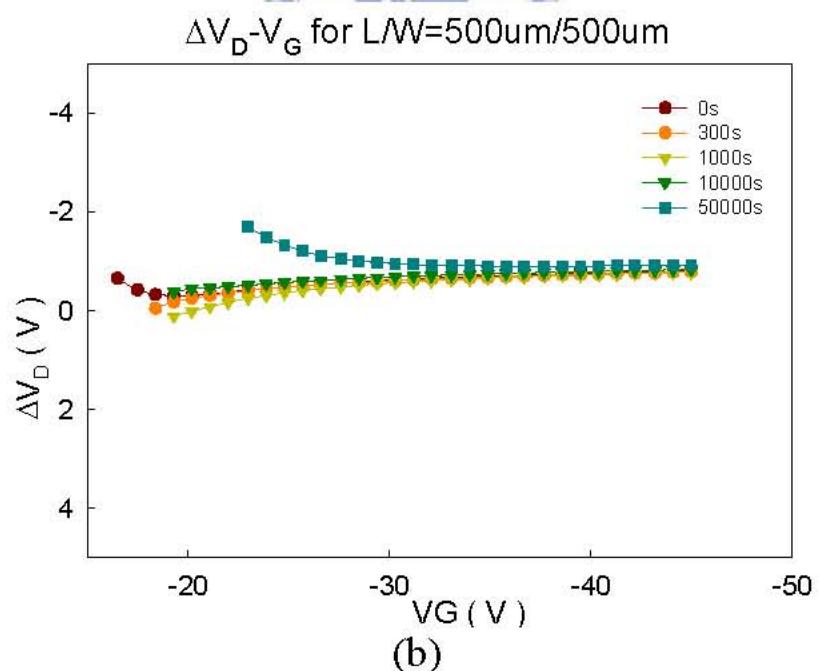

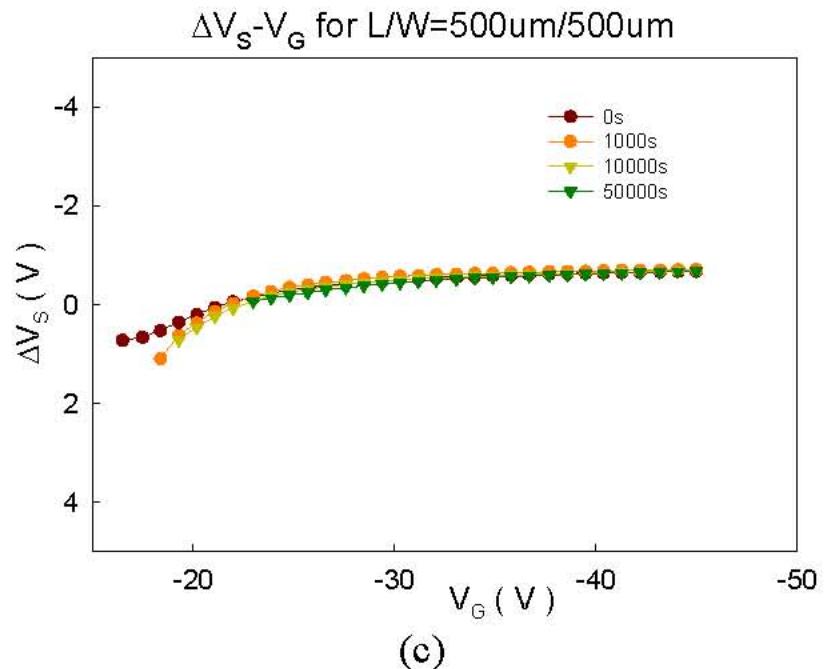

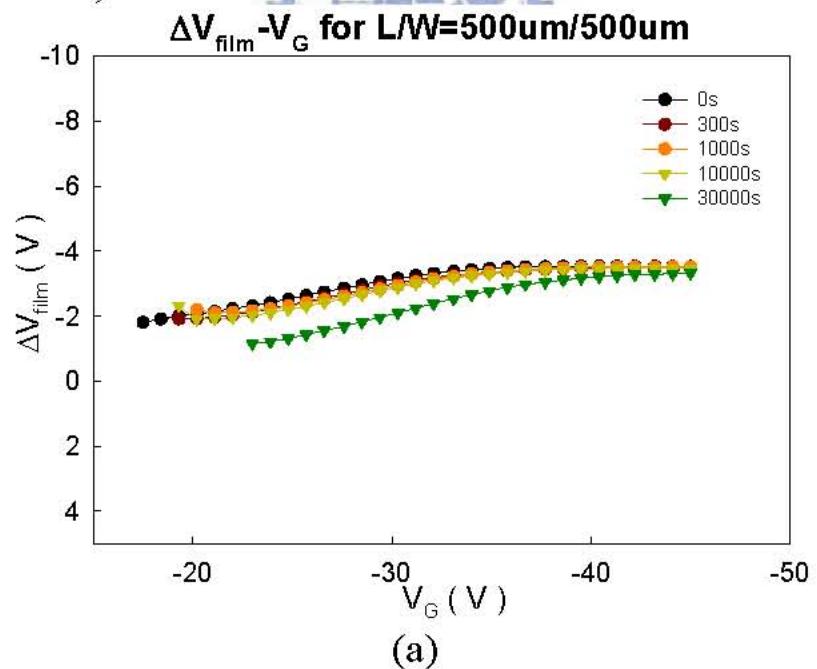

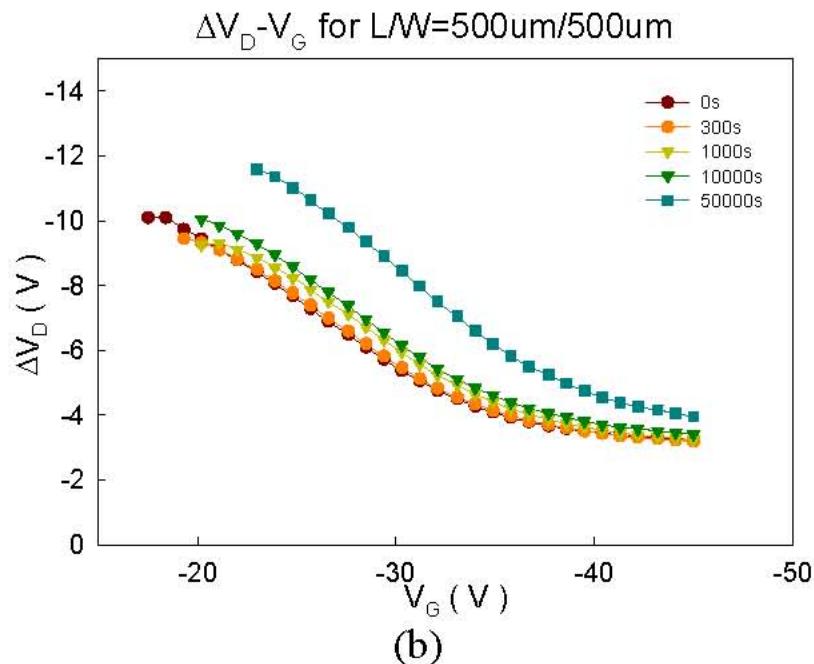

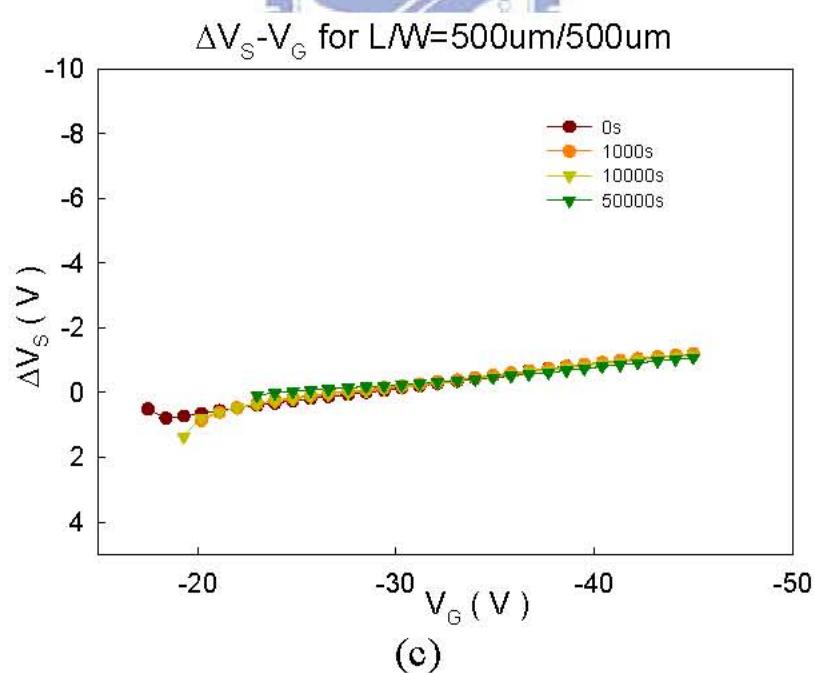

Figure 4-14: The voltage drop of (a) channel between probe1 and probe2, (b) drain side, and (c) source side in linear region as a function of gate voltage taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

Figure 4-15: The voltage drop of (a) channel between probe1 and probe2, (b) drain side, and (c) source side in saturation region as a function of gate voltage taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

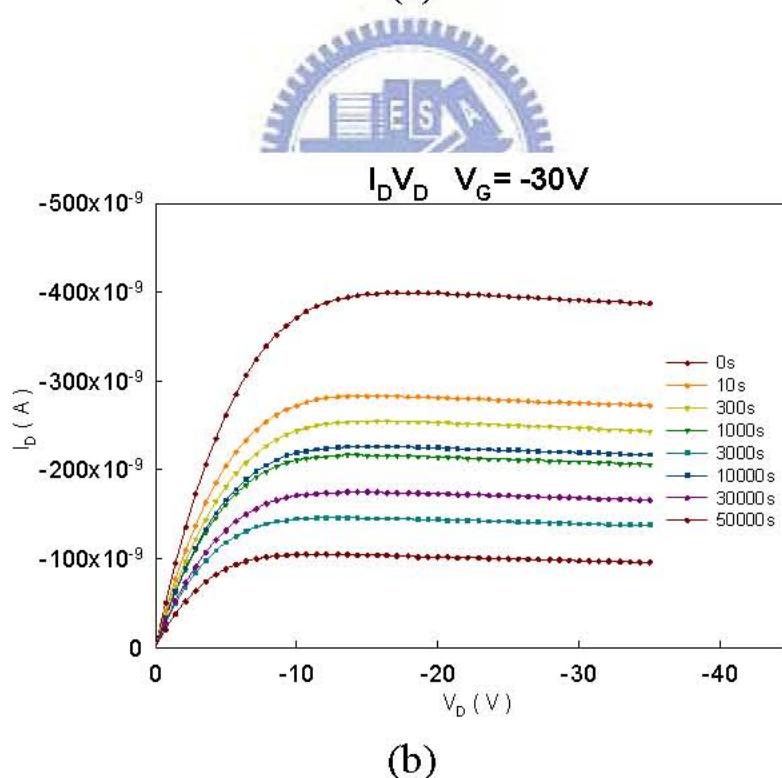

Figure 4-16: The output characteristics for pentacene-based OTFT with four probe structure (a) at  $V_G = -10V$  and (b) at  $V_G = -30V$ .

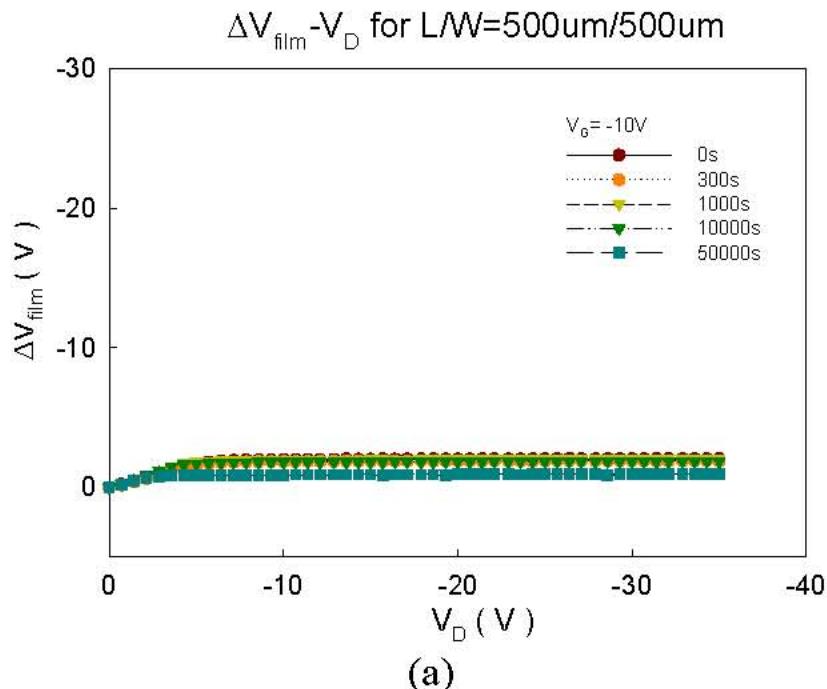

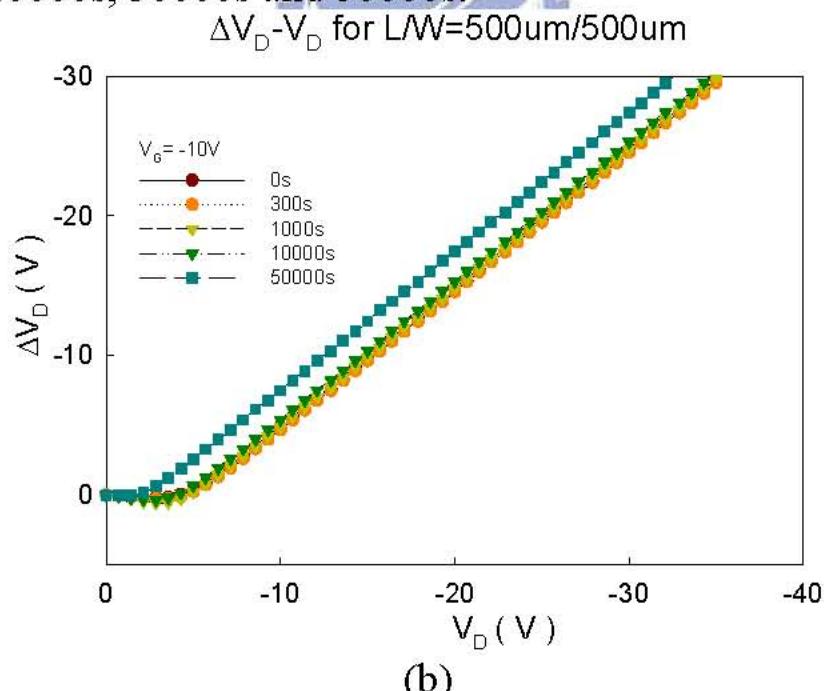

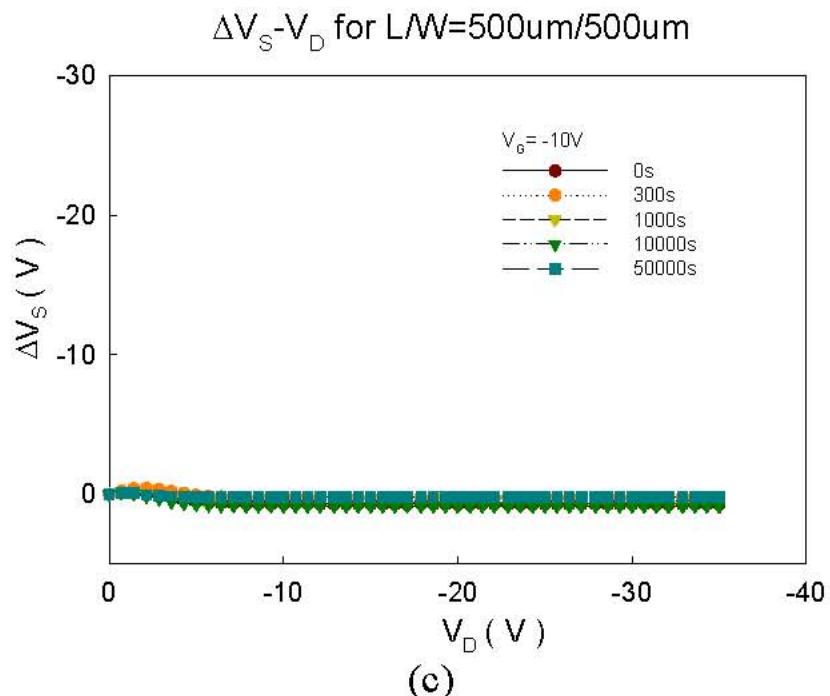

Figure 4-17: The voltage drop of (a) channel between probe1 and probe2, (b) drain side, and (c) source side at gate bias ( $V_G = -10V$ ) as a function of drain voltage taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

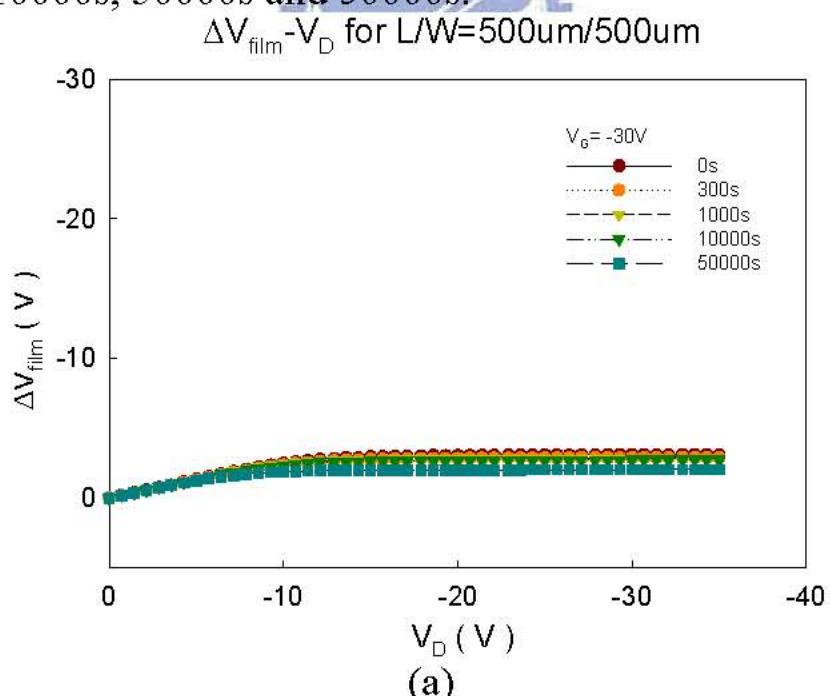

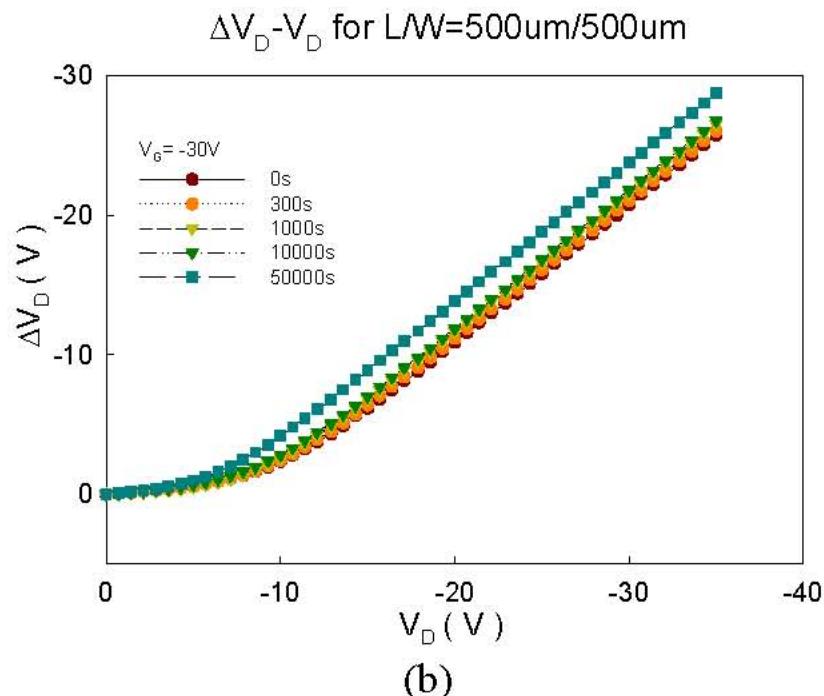

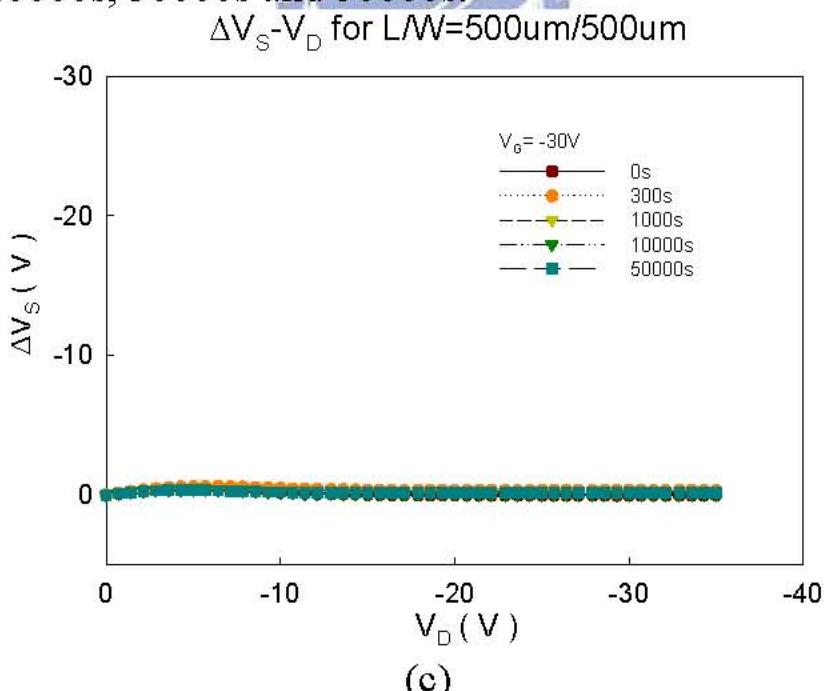

Figure 4-18: The voltage drop of (a) channel between probe1 and probe2, (b) drain side, and (c) source side at gate bias ( $V_G = -30V$ ) as a function of drain voltage taken after current stress of 0s, 10s, 1000s, 10000s, 30000s and 50000s.

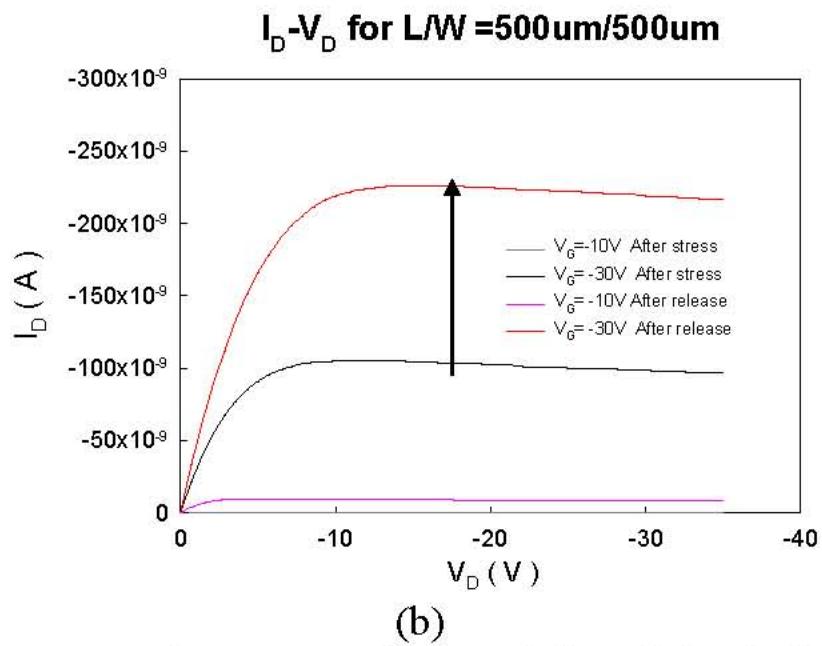

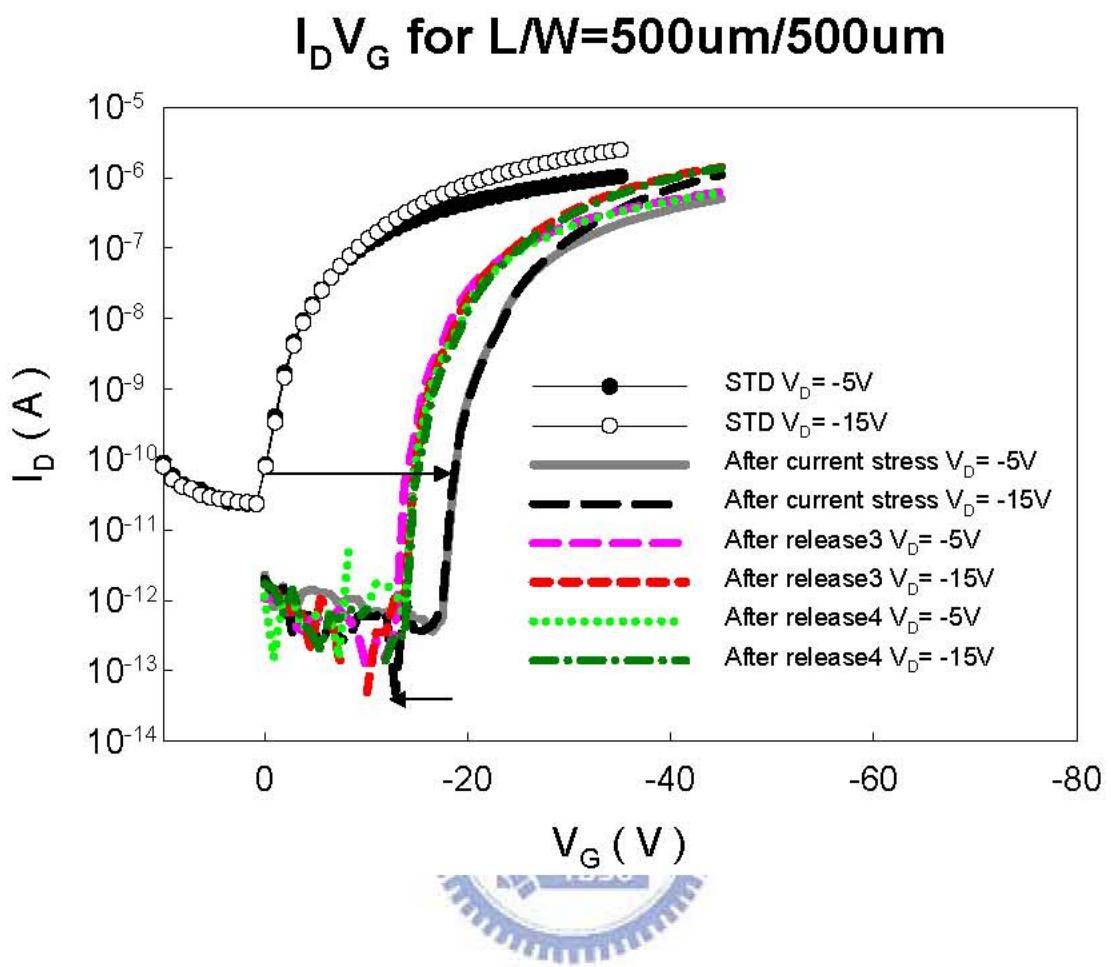

Figure 4-19: (a) The transfer characteristics of the device at drain voltages  $V_D = -5V$  and  $V_D = -15V$ , and (b) the output characteristics at gate voltage  $V_G = -10$  and  $V_G = -30V$ , compared with after stress and after release.

Figure 4-20: Schematic of organic field transistor, showing the formation of dipole during the current stress.

Figure 4-21: (a) The energy band diagram of flat band with the positive charges induced by dipoles, and (b) the energy band diagram through a MIS structure with a positive gate bias. Smooth band bending due to the energy level of interface, pinned down by the positive charges.

Figure 4-22: (a) The energy band diagram of flat band, and (b) energy band diagram through the MIS structure with a positive gate bias after its recovery. The

band bending is more winding.

Figure 4-23: The resistances as a function of gate voltage under drain bias of (a)  $V_D = -5V$  and (b)  $V_D = -15V$  for drain side, source side, and channel between probe1 and probe2. They after stress and after release would be compared.

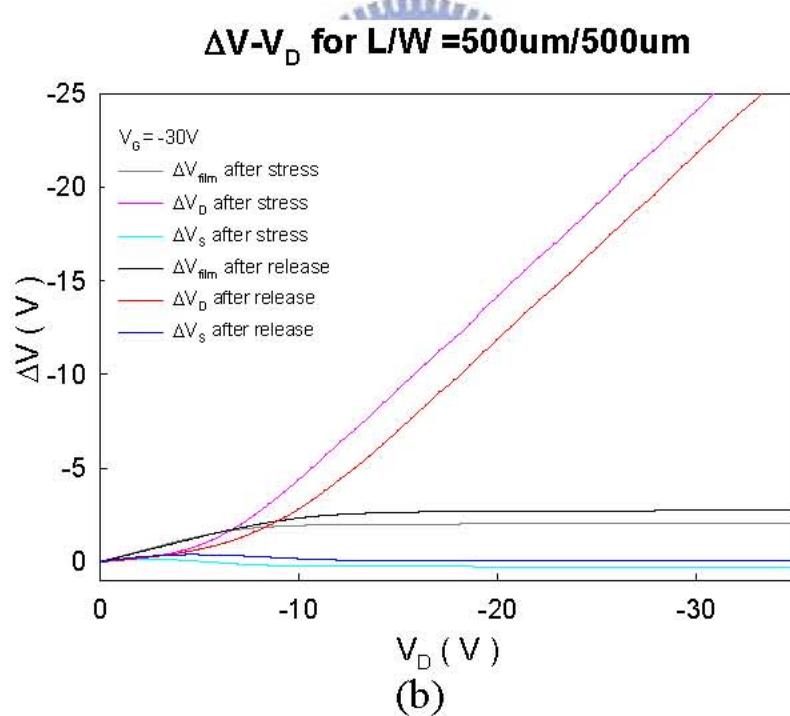

Figure 4-24: (a) The resistances as a function of drain voltage under gate bias ( $V_G = -30V$ ) for drain side, source side, and channel between probe1 and probe2. (b) The voltage drop of channel between probe1 and probe2, drain side, and source side as a function of drain voltage. They after stress and release would be compared.

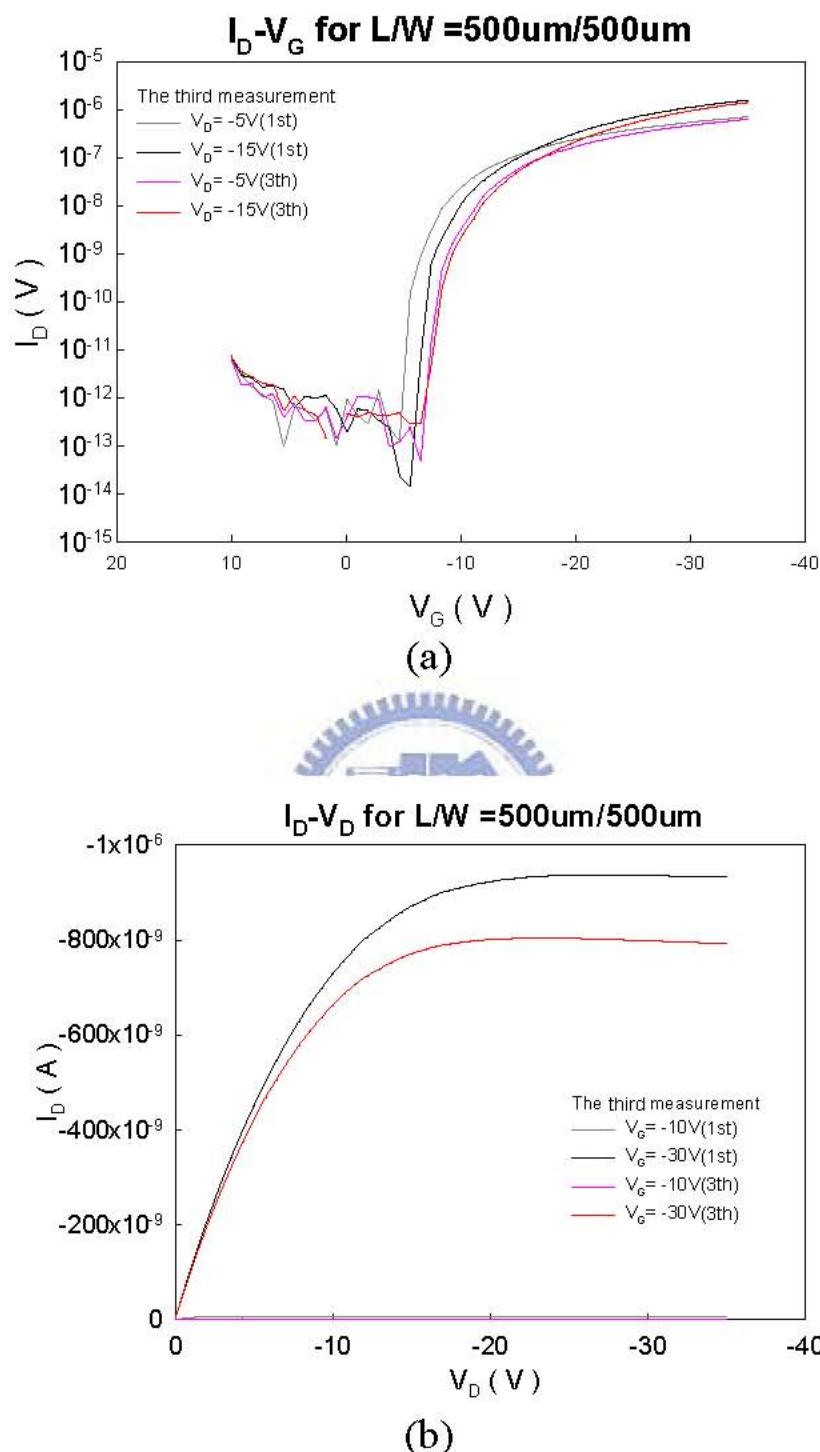

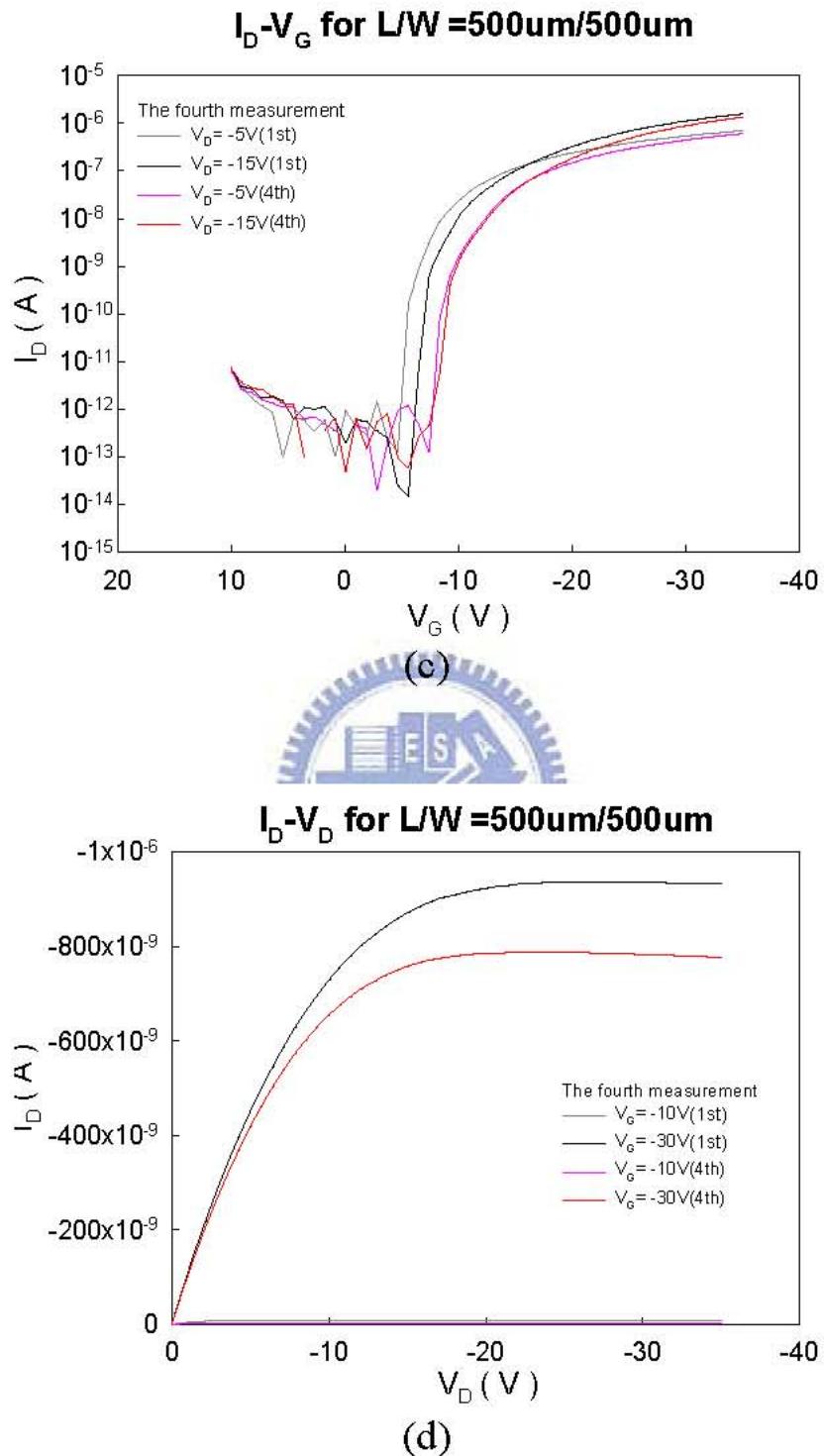

Figure 4-25: Comparison with (a) the transfer curve, and (b) the output characteristic for the first and third measurement. At the same time, comparison with (c) the transfer curve, and (d) the output characteristic for the first and fourth measurement.

Figure 4-26: The summary for threshold voltage shift after stress and release.

# *List of Tables*

---

## **Chapter 1**

Table 1-1: Thin film transistor performances for different oligomer active layer

## **Chapter 3**

Table 3-1: The relative list of Meyer–Neldel Energy

## **Chapter 4**

Table 4-1: Threshold voltage shift during current stress

Table 4-2: Instability of mobility during current stress

Table 4-3: Instability of subthreshold swing during current stress

Table 4-4: Transient stress phenomenon

# Chapter 1

## Introduction

### 1.1 Overview of Organic Thin Film Transistor

Electronics based on organic and polymer materials have attracted much attention in recent years. The interest can be attributed to emerging demands in novel electronic devices like radio frequency tags (wireless transponders), smart cards, and display media (active and passive) on low cost and/or flexible substrates. Progress in this field has been sustained by improvements of the material properties [1–3] (see Figure 1-1) and in the development of processing techniques such as printing [4–7], stamping, or other high volume parallel processing technologies. The processing techniques facilitate patterning of organic and inorganic materials without using standard photolithography. Therefore, most of the research has been driven by an interest in low cost electronics.

Currently, hydrogenated amorphous silicon, the most widely used broad area electronic material requires temperatures of 250–350°C for high-quality material deposition and thus requires the use of glass or other high-temperature substrates. Up to now amorphous and polycrystalline silicon have dominated low cost electronics due to low processing temperatures and the application of low cost substrates like glass or flexible foil, which facilitates scaling of the process to larger substrates.

Pentacene, or other organic semiconductors, may allow device fabrication on flexible plastic substrates. For applications such as active matrix liquid crystal displays (AMLCD's), which currently use glass substrates, this would allow displays with decreased weight and improved ruggedness. The use of a flexible substrate could also

dramatically lower fabrication cost by allowing continuous web processing. In addition, although the bonds are often quite strong, individual molecules are held together by relatively weak van der Waals forces. Hence the electronic properties of the material are primarily determined by the molecular properties, potentially making organic devices more tolerant to at least some types of impurities than devices fabricated from covalently bonded inorganic materials.

At present, Pentacene ( $C_{22}H_{14}$ ) has demonstrated the highest hole and electron mobility of organic small molecules. The material exhibits a strong tendency to form highly ordered films which depend on the growth conditions and the substrate. Bulk single crystals are not favorable for low cost electronics, because the fabrication is time consuming and the crystals are small. Thin films are more favorable, because they can be fabricated on various low cost substrates. The hole mobility of thin film pentacene is close to the intrinsic transport limit of bulk single crystals, and thin film transistors (TFTs) with mobility of  $>1 \text{ cm}^2/\text{Vs}$  have been fabricated by several groups [2,8–11]. The mobility is therefore comparable with that achieved by amorphous silicon TFTs and hence pentacene TFTs might be considered for large area active matrix arrays. Promising methods for the fabrication of pentacene for low cost electronics on large areas are organic vapor phase deposition [12] and thermal evaporation [8]. In this thesis we focus on thermally evaporated pentacene.

The thermally evaporated material is polycrystalline and has large grains. The diameters are usually in the range of a few microns [8,11,13]. Despite the enormous progress in the realization of TFTs with good properties, the transport mechanism especially of polycrystalline films is not completely understood. In order to investigation, most of organic TFTs so far have been fabricated on thermal oxide coated

crystalline wafers. Thermal oxide on silicon wafers is a favorable substrate for the growth of pentacene, and proper to operate with more stable characteristic.

Pentacene transistor drain-source contacts can be made in one of two configurations—top contact and bottom contact. It has been demonstrated that the bottom contact configuration gives inferior performance to the top contact configuration for a range of deposition conditions and material thickness [14-15]. As a consequence of this behavior, the top contact configuration is almost exclusively studied and reported in the literature. Shadow masking is generally used in the laboratory to define the top contacts made to pentacene, a procedure which does not lend itself well to manufacturing. To create a manufacturable process photolithographically defined drain and source contacts are needed. The performance levels needed for commercial technologies have only been demonstrated in top contact devices, however, and since no photolithography may be performed after pentacene has been deposited, bottom contact devices are the only option for a fully lithographic pentacene process.

## 1.2 Properties of Pentacene

Structure of pentacene is shown in Figure 1-2. Crystals of pentacene are triclinic lattice (see Figure 1-3). The lattice parameters of pentacene were shown in Table1-1. And the other important parameters were described as follows [14-15]:

Pentacene Formula :  $C_{22}H_{14}$ ;

Molecular weight : 278.3;

Melting point: 573 K;

Volume of the unit cell :  $705.0 \text{ \AA}^3$ ;

Density:  $1.303 \text{ g.cm}^{-3}$  (calculated with  $Z = 2$ ) ,

$1.30 \text{ g.cm}^{-3}$  ( measured ).

Optical Bandgap: 2.8 eV.

Absorption coefficient for X-rays:  $\lambda = 1.542 \text{ nm}$ .

Resistivity:  $\sim 10^{14}$ - $10^{15} \text{ ohm}\cdot\text{cm}$ ;

We have fabricated organic thin film transistors (OTFTs) using pentacene, a fused-ring polycyclic aromatic hydrocarbon, as the active material. It is typically used as p-type semiconductor. These devices have field-effect mobility comparable to hydrogenated amorphous silicon (a-Si:H) TFTs ( $> 0.5 \text{ cm}^2/\text{V}\cdot\text{s}$ ). While the bulk electrical conductivity of acenes such as pentacene ( $\sim 10$ - $15 \text{ S/cm}$ ) is well known, the field-effect properties of pentacene and many other conjugated materials remain relatively unexplored.

On organic small molecules, pentacene ( $C_{22}H_{14}$ ) has demonstrated the highest hole and electron mobility. Pentacene has a strong tendency to form molecular crystals and when deposited by evaporation will typically form well-ordered films even for low substrate temperatures. With pentacene, for example, ordered films are obtained when deposited by evaporation at temperatures as low as  $0^\circ\text{C}$ . This tendency to form ordered films at low temperature may be extremely important.

The material exhibits a strong tendency to form highly ordered films, which, depending on the deposition and substrate conditions, can be poly or single crystalline. In the case of single crystal material, hole mobility of  $3.2 \text{ cm}^2/\text{V}\cdot\text{s}$  and electron mobility of  $2.0 \text{ cm}^2/\text{V}\cdot\text{s}$  have been realized at room temperature using metal - insulator - semiconductor (MIS) transistor structures. However, the size of the single crystal substrates is relatively small in comparison to large area and/or low cost substrates. A more promising process to realize large area electronics is the thermal evaporation of

the organic material. The thermal evaporated material is poly crystalline with large grain sizes, usually in the range of a few microns. The mobility of polycrystalline transistors at room temperature is about  $0.1\text{-}1\text{ cm}^2/\text{V}\cdot\text{s}$ , achieving the same range as amorphous silicon.

### 1.3 Operation of Organic Thin Film Transistor

The operation of the pentacene-base OTFT is described below [18]. Organic thin film transistors are opposed to the usual inversion mode operation of silicon MOSFETs and primarily operated as a P-type accumulation-mode enhancement type transistor.

When zero bias was applied to three terminals of OTFT, the carrier distribution is uniform without the electrical field effect, which's schematic diagram is shown in Figure 1-4(a). If applied a small drain bias ( $V_D$ ), in this condition, the source-drain current, ( $I_D$ ), will be not easy to conduct and small enough to neglect .

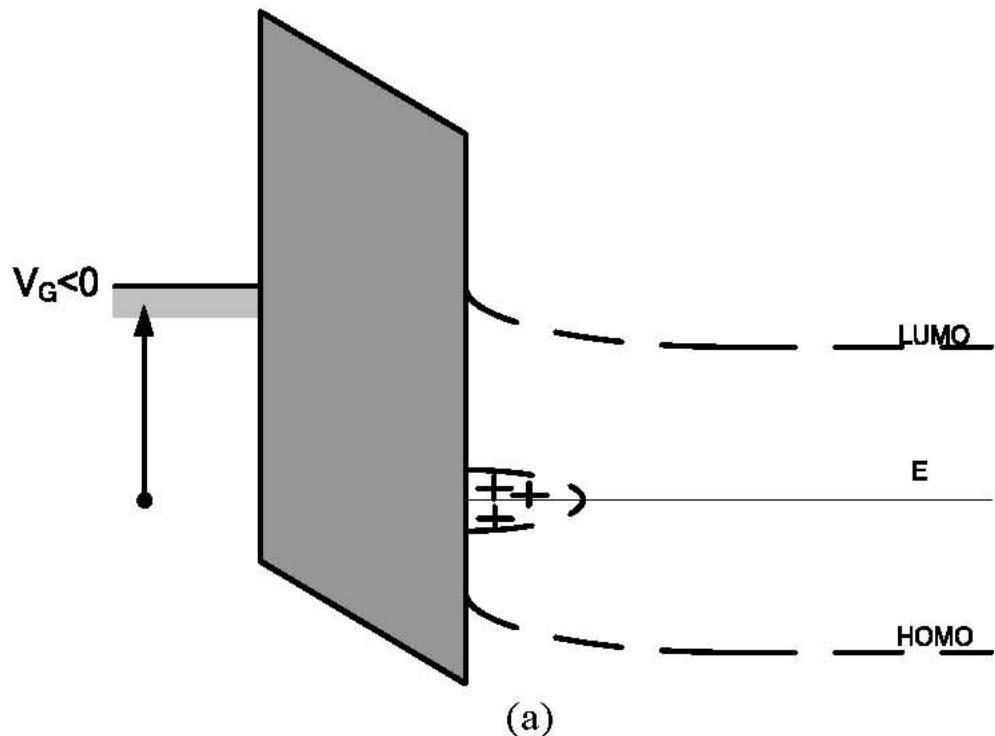

When a negative bias ( $V_G$ ), is applied to the gate electrode, the voltage is dropped over the insulator and over the semiconductor near insulator/semiconductor interface and accumulate more positive charge in the accumulation region to form a conduction channel. The schematic diagram is shown in Figure 1-4(b). The additional positive charge is supplied by the ohmic source and drain contact and will reduce the resistance of channel. When a small bias is applied on the drain terminal, the source-drain current will form.

In Figure 1-4(c), the schematic diagram shows the depletion mode for device. When a positive bias is applied, the band bending occurs in the semiconductor at the insulator interface. Charge will reject from the interface and depletion region will form.

The channel resistance is large so the source-drain current will be smaller than the Mode in Figure 1-4(a). Because of the large band gap, inversion layer cannot be observed in the organic TFTs.

When a negative bias, more than gate bias, is applied to drain electrode in Figure 1-4(a), the positive charge near the drain will be swiped in to drain electrode and form a depletion region. The schematic diagram is shown in Figure 1-4(d). This condition is similar to saturation mode of silicon MOSFETs. In this mode the source-drain current will not increase with increase drain bias voltage.

## 1.4 Motivation

Recent focus and attention on organic thin film transistors ( TFTs ) resulted in dramatic performance improvements [1-3]. Earlier literature pointed out that the properties of organic TFTs were highly dependent on the film quality of organic semiconductors, which were determined by pre-layer 's morphology, surface energy, process temperature, thickness and so on. In the early stage, researches interests on the formation of large poly-grains or single crystal of pentacene film due to that the larger poly grain of pentacene usually have higher mobility. However, the large poly grain is not the only factor to reach high mobility. The detail mechanisms are still under investigated.

Equations describing TFT operation assume ohmic ( negligible resistance ) contacts, which often may not be the case for OTFTs. Recent reports reveal that contact resistance in OTFTs can be of the same order of magnitude or more than the film channel resistance. The traditional method for determining contact resistance involves

making multiple OTFTs with various channel lengths, measuring device resistance versus channel length, and then extrapolating back to zero channel length to determine the contact resistance. For the instability of OTFT, we use an improved four-probe method for simple investigation of contact resistance, comparing it to the variation of length and width. The four-probe method is based on the standard OTFT source and drain geometry, but with two additional mid channel voltage sensing probes.

Despite the enormous progress in the realization of TFTs with good properties, the transport mechanism especially of polycrystalline films is not completely understood. Variable temperature electrical measurements are a well-established means for determining the conduction mechanism in semiconductors. In amorphous and polycrystalline silicon, for example, temperature dependent measurements have been used to determine whether charge transport occurs in extended states, by variable range hopping (VRH) or by multiple trapping and release (MTR). Each of these models predicts a specific temperature dependence of the charge carrier mobility that can be used to identify the underlying conduction mechanism. Therefore, it would be adopted to further investigation on transport mechanism.

Besides, electric stability of OTFTs during long time operation is another important needed subject of research. Typically, the instabilities are observed as a shift of the threshold voltage ( $\Delta V_{th}$ ) accompanied by a possible change in the charge carrier mobility, which is due to charge trapping at the gate insulator– dielectric interface or at defect sites in the active layer itself. Both change are found in pentacene-based TFTs. Also the origin of the changing threshold voltage is not known, which complicates both the analysis of the transport properties and degrades potential use of organic TFTs in applications. Therefore, we applied the current stress and attempted to analysis

instability phenomenon and explain trapping charge mechanism during stress.

## 1.5 Thesis Organization

This thesis addresses the investigation of the reliability on the pentacene-based OTFT. The organization is as followings.

In chapter 1, we introduce the background of organic thin film transistor.

In chapter 2. First, we took the simple material measurements to understand the crystallization and growth mechanisms of pentacene through deposition . Pentacene was thermal evaporated at different substrate temperatures. The film quality was characterized by atomic force microscope ( AFM ), scan electron microscope ( SEM ) and referenced X-ray diffraction ( XRD ). They help us to further understand the crystallization process for pentacene under our fabrication and check the phenomenon depicted on paper at the same time . Next, for the instability of OTFT, we use an improved four-probe method for facilitating investigation of contact resistance, and compare to the electrical characteristics of devices with different length and width. The four-probe method is based on the standard OTFT source and drain geometry, but with two additional mid-channel voltage sensing probes. Thus, we use two electrodes to inject and receive current, and two to sense voltage in the OTFT channel. The major advantage of the four-probe method over conventional R vs L plots is that it allows the contact resistance at source side, drain side and in channel to be measured independently in a single device, which facilitates assessment of device-to-device variation in these resistances.

In chapter 3, variable temperature electrical measurements are a well-established

means for determining the conduction mechanism in semiconductors. Variable temperature TFT measurements can be used to determine the temperature dependence of the mobility in a semiconductor thin film. The temperature dependence of the mobility can yields information about the conduction mechanism and trap states in the semiconductor. Several models have been proposed to explain thermally activated mobility in crystalline organic semiconductor films, but the multiple trapping and release (MTR) model is the most widely accepted. We properly use the multiple trapping and release model to explain the thermally activated phenomenon .

In chapter 4, we found the instability of electrical characteristics in a continued series measurements and further investigated the characteristics of bottom-contact pentacene-based OTFTs under the condition of drain current stress. Here, we find that polarization phenomenon play an important role during stress, and thus we provide the rough energy band figure to depict these special properties of OTFTs. The effect of these charge trapping instability on the measured threshold voltage and mobility on the transport studies are discussed.

In chapter 5, we concludes all results and provide further recommendations.

Figure 1-1: Mobility of organic semiconductors have improved by five orders of magnitude over the past 15 years. Large research efforts using materials such as these led to some of this increase.

Figure 1-2: Pentacene molecular structure

$$a \neq b \neq c, \\ \alpha \neq \beta \neq \gamma \neq 90^\circ$$

Figure 1-3: Triclinic lattice

$$V_G = V_S = V_D = 0$$

$$V_G < 0 \quad V_S = V_D = 0$$

Figure 1-4: Schematic of operation of organic thin film transistor, showing a lightly p-doped semiconductor: + indicates a positive charge in semiconductor ; - indicates a negatively charge counterion (a)no-bias (b) accumulation mode (c)depletion mode (d)channel pinch-off (continue)

$$V_G > 0, V_S = V_D = 0$$

$$V_D < V_G < 0, V_S = 0$$

Figure 1-4: Schematic of operation of organic thin film transistor, showing a lightly p-doped semiconductor: + indicates a positive charge in semiconductor; - indicate a negatively charge counterion (a)no-bais (b) accumulation mode (c)depletion mode (d)channel pinch-off

| Oligomer materials                       | Channel | Thin film deposition | Mobility (cm <sup>2</sup> /V-s)     | Comments                       |

|------------------------------------------|---------|----------------------|-------------------------------------|--------------------------------|

| $\alpha$ -6T ( $\alpha$ -hexathienylene) | p-type  | Vacuum evaporation   | 0.01~0.03                           | Highly purified oligomers      |

| $\alpha$ -6T                             | p-type  | Single crystal       | 0.075                               |                                |

| DH- $\alpha$ -6T (dihexyl- $\alpha$ -6T) | p-type  | Vacuum evaporation   | 0.03~0.05                           | Thermal annealing at 100~250°C |

| <b>Pentacene</b>                         | p-type  | Vacuum evaporation   | 0.06~2.1                            | Substrate at T>25 °C           |

| <b>Pentacene</b>                         | p-type  | Solution cast        | 10 <sup>-5</sup> ~10 <sup>-3</sup>  |                                |

| <b>Pentacene</b>                         | p-type  | Single crystal       | 3.2                                 |                                |

| C <sub>60</sub> (fullerene)              | n-type  | Vacuum evaporation   | 0.08                                |                                |

| TCNQ (tetracyanoquinodimethane)          | n-type  | Vacuum evaporation   | 10 <sup>-10</sup> ~10 <sup>-4</sup> |                                |

| NTCDA                                    | n-type  | Vacuum evaporation   | 1~3x10 <sup>-3</sup>                | Substrate at T=55°C            |

| PTCDA                                    | n-type  | Vacuum evaporation   | 10 <sup>-5</sup> ~10 <sup>-4</sup>  |                                |

| F <sub>16</sub> CuPc                     | n-type  | Vacuum evaporation   | 0.03                                |                                |

Table 1-1: Thin film transistor performances for different oligomer active layers

## Chapter 2

### Devices Fabrication and Four Probe Measurement

#### 2.1 Introduction

Recent focus and attention on organic thin film transistors ( TFTs ) resulted in dramatic performance improvements [19-21]. Earlier literature pointed out that the properties of organic TFTs were highly dependent on the film quality of organic semiconductors, which were determined by pre-layer's morphology, surface energy, process temperature, thickness, and so on [22]. In the early stage, researches interests on the formation of large poly-grains or single crystal of pentacene film due to that the larger poly grain of pentacene usually have higher mobility. However, the large poly grain are not the only factor to reach high mobility [22]. The detail mechanisms are still under investigated.

In one part of this chapter, we took the simple material measurements to understand the crystallization and growth mechanisms of pentacene through deposition. Pentacene was thermal evaporated at different substrate temperatures. The film quality was characterized by atomic force microscope ( AFM ), scan electron microscope ( SEM ) and reference X-ray diffraction ( XRD ). They help us to further understand the crystallization process for pentacene under our fabrication and check the phenomenon depicted on paper at the same time.

On the other hand, we report on OTFTs based on pentacene and specifically focus

on characterizing the contact resistance, and the voltage drop between channel. Equations describing TFT operation assume ohmic ( negligible resistance ) contacts, which often may not be the case for OTFTs [23]. Recent reports reveal that contact resistance in OTFTs can be of the same order of magnitude or more than the film channel resistance [24-26]. Katz et al. noted that contact resistance played a key role in the operation of n-channel OTFTs [27]. The traditional method for determining contact resistance involves making multiple OTFTs with various channel lengths, measuring device resistance versus channel length, and then extrapolating back to zero channel length to determine the contact resistance.

In the another part of this chapter, we use an improved four-probe method for facilitating investigation of contact resistance, and compare to the electrical characteristics of devices with different width and length. The four-probe method is based on the standard OTFT source and drain geometry, but with two additional mid-channel voltage sensing probes. Thus, we use two electrodes to inject and receive current, and two to sense voltage in the OTFT channel. The technique we employ is similar to other recently reported four-probe transistor devices [28-30]. The major advantage of the four-probe method over conventional R vs L plots is that it allows the contact resistance at source side, drain side and in channel to be measured independently in a single device, which facilitates assessment of device-to-device variation in these resistances.

## 2.2 Devices Fabrication and Measurement

### 2.2.1 Process Flow of Pentacene-Based OTFT Fabrication

#### *Film Growth and Characterization*

Thin films of pentacene were prepared by thermal evaporation from an boron crucible onto the transistor test substrate consisting of dummy silicon wafer of low resistivity ( $1-100 \Omega\text{-cm}$ ), and a 200 nm thick thermal oxide layer grown in furnace. The base pressure in the evaporation system was about  $10^{-7}$  torr. Film thickness was measured by a calibrated quartz crystal monitor. The substrate holder held at constant temperature during deposition. The different substrate temperatures ( $T_S$ ) were investigated into  $25^\circ\text{C}$ ,  $70^\circ\text{C}$ ,  $120^\circ\text{C}$ , and  $150^\circ\text{C}$ .

After deposition, the sample was determined by atomic force microscopy (AFM) and Scan electron microscope (SEM). Film grain structure and morphology were examined using atomic force microscopy. A Digital Instruments Multimode AFM was used in tapping mode, and all images were taken in ambient conditions. Figure 2-2 shows an atomic force topography of a 650-Å-thick pentacene film grown at  $T_S=70^\circ\text{C}$ . Sometimes, the thickness of the film was determined by scan electron microscope (SEM) in order to calibrate quartz crystal monitor.

#### *Device Fabrication*

A bottom gate, inverted staggered transistor structure was used to characterize the pentacene thin films. The cross section of four probe structure is shown schematically in Figure 2-8. The gate and insulator layers consisted of 2000 Å thermally deposited silicon oxide on a dummy silicon wafer of low resistivity ( $1-100 \Omega\text{-cm}$ ) in furnace. The measured capacitance of the thermal oxide layer was about  $17 \text{ nF/cm}^2$ , which compares

well with the theoretical limit of  $17.26 \text{ nF/cm}^2$ . Source and drain electrodes were defined by thermal evaporation of metal through a shadow mask onto thermal oxide.

The contact metal of a patterned gold layer formed ohmic contacts as the four probe structure, including of the source, drain electrodes, sense probe1 and sense probe2, were investigated. The typical thickness of the contact metal was  $600 \text{ \AA}$  for gold. It noted that the transistor channel width (W) range from  $1000\text{um}$  to  $50 \text{ um}$  with the length (L) between  $1000\text{um}$  and  $40\text{um}$ .

The organic TFTs are prepared by evaporated pentacene on a transistor structure of bottom contact in thermal coater. The base pressure in the evaporation chamber was  $10^{-6}$  torr, and stayed below  $10^{-7}$  torr during deposition. Thin films of pentacene were thermally evaporated up to a thickness of  $650 \text{ \AA}$  measured by calibrated quartz crystal monitor. To minimize parasitic leak, the active area of pentacene film was defined by shadow masking. We measured the electrical characteristics of OTFT as soon as after fabrication.

## 2.2.2 Electrical Characteristics of Pentacene-Based OTFTs

### *Measurement*

The electrical characterization was measured in probe station with semiconductor parameter analyzer of E5270B at room temperature in atmosphere around dark environment. All measurements were carried out in an electrically shielded box. Drain current was measured by using semiconductor parameter analyzer of E5270B. Figures 2-10 and 2-11 show the transfer curves and the output characteristic, respectively, for a pentacene base TFT with the thermal oxide insulator and Au contacts.

In the output characteristics, the drain-source current,  $I_{DS}$ , was measured as a

function of the drain-source voltage,  $V_{DS}$ , to observe FET-like characteristics. In the transfer curve, drain current also was measured as a function of the gate voltage,  $V_D = -5V$ , which was constructed to determine the gate bias modulation of the FET conductive channel and at the drain voltage of  $-15V$ , which are usually present for OTFT.

Some parameters were extracted from the experimental I-V curves: the transistor threshold voltage ( $V_{th}$ ), the current modulation (the ratio of the current in the accumulation mode over the current in the depletion mode, also referred to as ON-OFF current ratio), and the field effect mobility ( $\mu$ ). The  $V_1$  and  $V_2$  between channel was sensed by probe 1 and probe 2 at the same time. Furthermore, we can use the data of voltage drops and resistances between channel by four probe structure to analyze phenomenon. The detail extraction method will be discussed in the following sections.

#### *ON-OFF Ratio*

Inorganic semiconductors, such as Si or Ge, can be operated in three modes: depletion mode, accumulation mode, and inversion mode. For organic semiconductors such as pentacene-based OTFTs, they can not be operated in the inversion mode. Therefore, pentacene-based OTFTs were turned ON in the accumulation mode ( $V_G < 0$ , see Figure 1-4(b)) and were turned OFF in the depletion mode ( $V_G > 0$ , see Figure 1-4(c)).

Therefore, the ratio of the current in the accumulation mode over the current in the depletion mode also refers to as ON-OFF current ratio. We think it as the ratio of the maximum drain current under accumulation region to the minima current under depletion region.

### ***The Extraction Methods of Mobility and Threshold Voltage***

Linear and saturation regime mobility is calculated based on standard TFT equations [31]. Pentacene-based OTFT is PMOS like FET. Therefore, the field effect mobility in the linear regime can be obtained by the calculation described below.

At low drain voltage ( $V_D$ ), source-drain current ( $I_{DS}$ ) increases linearly with  $V_D$  (linear regime) and is approximately determined from the following equation (2-1):

$$I_D = \frac{W}{L} \mu C_{ox} (V_G - V_{th}) V_D \dots \text{for linear region} \quad (2-1)$$

where  $L$  is the channel length,  $W$  is the channel width,  $C_{ox}$  is the capacitance per unit area of the insulating layer,  $V_{th}$  is the threshold voltage, and  $\mu$  is the field effect mobility, which can be calculated in the linear regime from the transconductance,

$$G_m = \left. \frac{\partial I_D}{\partial V_G} \right|_{V_D=const} = \frac{WC_{ox}}{L} \mu V_D \dots \text{for linear region} \quad (2-2)$$

by plotting  $I_{DS}$  versus  $V_G$  at a constant low value of  $V_D$ , with  $-V_D \ll -(V_G - V_{th})$ , and equating the value of the slope of this plot to  $G_m$ . We can compute the linear regime mobility from equation (2-2). Threshold voltage ( $V_{th}$ ) was determined from a linear plot of drain current ( $I_D$ ) versus gate voltage ( $V_G$ ) extrapolated to the  $x$ -axis intercept.

On the other hand, the field effect mobility in the saturation regime can be obtained by the calculation described below. At high drain voltage, source-drain current increases with the square of  $(V_G - V_{th})$  (saturation regime) and is approximately determined from the following equation (2-3):

$$I_D = \frac{1}{2} \frac{W}{L} \mu C_{ox} (V_G - V_{th})^2 \dots \text{for saturation region} \quad (2-3)$$

where  $L$  is the channel length,  $W$  is the channel width,  $C_{ox}$  is the capacitance per unit area of the insulating layer,  $V_{th}$  is the threshold voltage, and  $\mu$  is the field effect mobility,

which can be calculated in the saturation regime from the transconductance,

$$G_m = \frac{\partial \sqrt{I_D}}{\partial V_G} \Big|_{V_D=const} = \sqrt{\frac{1}{2} \frac{WC_{ox}}{L} \mu} \dots \text{for saturation region} \quad (2-4)$$

by plotting  $I_{DS}$  versus  $V_G$  at a constant high value of  $V_D$ , with  $-V_D \gg -(V_G - V_{th})$ , and equating the value of the slope of this plot to  $G_m$ . We can compute the saturation regime mobility from equation (2-4). Threshold voltage ( $V_{th}$ ) was determined from a linear plot of square root of drain current ( $\sqrt{I_D}$ ) versus gate voltage ( $V_G$ ) extrapolated to the  $x$ -axis intercept.

For most devices, transfer curves were taken in 0.92 V gate steps from 10 V up to -35 V. The devices made in our lab had mobility as high as 1.574 and 1.142  $\text{cm}^2/\text{V}\cdot\text{s}$  in linear region and saturation region respectively at temperature of 70°C, as shown in Figure 2-10 and 2-11. The threshold voltages ranging from -10V to 10 V depending on the device (see the Figure 2-10:  $V_{th} = -8.1\text{V}$  in linear region and  $V_{th} = -2.6\text{V}$  in saturation region), and on-to-off current ratio (on/off) about  $10^6$ . We were able to fabricate devices of this quality several times, but observed some variability from run to run. The drain current of the transfer curve measured as a function of gate voltage at drain voltage of -5V and -15V. Later, the output characteristics is taken at gate voltage  $V_G = -10$  and  $V_G = -30\text{V}$ . The  $V_1$  and  $V_2$  between channel was sensed by probe 1 and probe 2 at the same time. In four-probe measurements, floating potentials of two mid-channel sensing probes were measured using Agilent E5287 (high resolution SMU module) with the zero current source. Furthermore, we use the data of voltage drops and resistances between channel by four probe structure to analyze phenomenon.

Finally, the sample would be stored carefully in dry cabinet to avoid moisture and pollution after measurements.

## 2.3 Results and Discussions

### 2.3.1 The Growth of Pentacene

Film grain structure and morphology were examined using atomic force microscopy after deposition of pentacene on thermally oxide silicon substrate. A Digital Instruments Multimode AFM was used in tapping mode, and all images were taken in ambient conditions.

The most of difficulties to analyze the properties of pentacene based TFTs is the uncertain reproducibility. Therefore, the study on the properties of pentacene TFTs sometimes focused on the qualitative analysis rather than quantitative analysis. Figure 2-1, 2-2, and 2-3 denotes the surface morphology of pentacene at different substrate temperatures of 25°C, 70°C, and 120°C, respectively. Figure 2-1 and 2-2 shows an atomic force topography of a 650-Å-thick pentacene film grown at the different substrate temperature of 25 and 70 °C. The morphology of grain is similar but the grain size are smaller at lower substrate temperature of 25°C. In Figure 2-2 and 2-3, pentacene films grown at the substrate temperature of 70°C and 120°C have similar grain sizes about 2.5um, observed by optical microscopy and AFM. Additionally, there are some different about the morphology of grain boundary. Obviously, the sizes of ploy grains gradually increase from 0.5um to nearly 2.5 um when substrate temperature increases in process.

The phenomenon was also observed by C.D. Dimitrakopoulos et al [32]. At very low substrate temperature, the rod-like pentacene molecules do not have sufficient momentum to move during deposition, thus the molecules would immediately stick

when they reach the surface of substrate, therefore forming an amorphous type in film structure. When the substrate temperature increases, the pentacene molecules have enough momentum to arrange a will-ordered crystalline structure, therefore a ploy crystalline morphology would be observed. In our experiments, the room temperature sample formed a poly crystalline morphology with smaller poly grains, as shown in Figure 2-1. When substrate temperature approach at 70°C or ,even more, 120°C, the grain size was growing about 2.5um (see Figure 2-2 and 2-3).

It is interesting to find the variation of morphology in grain boundary. At temperature of 25 and 70°C, the grain size is textured with micron-sized, terraced dendritic grains. However, at the temperature of 120 and 150°C, the film get together with many pieces like crystal piece.

We can further investigate by the nucleation process of pentacene at subtract temperature of 150°C, as shown in Figure 2-4, 2-5 and 2-6. IBM reported that the pentacene growth mechanism would be divided into three steps [33]. First, the resolution limit step, pentacene molecules form the crystalline seeds in the beginning. The resolution strongly depends on the interaction between pentacene molecules and surface molecules of substrate. Second, the diffusion limit aggregation step, where molecules diffuse on a surface and stick to any existing island, without further diffusion. Third, the coarsening step, the pentacene islands coarsen until the grains touch each other. We monitor the nucleation process of pentacene (see Figure 2-4, 2-5, and 2-6) and find that the grown of pentacene is crystalline pieces but dendritic in shape during deposition. Hence, we find papers which depict about this phenomenon.

The surface morphology of the thin films was studied by x-ray diffraction (XRD). Figure 2-7 shows a typical X-ray diffraction of pentacene thin film taken on paper [34]

and XRD pattern illustrates the crystalline order in the films. There is the crystalline phase of so-called “thin film phase” with  $d(001')$  value of 15.4 Å, which give the first order diffraction peak at  $5.7^\circ$ . But in the oxide case, another crystalline phase of so-called “single crystal phase” with  $d(001)$  values of 14.4 Å at the peak range from  $5.9$ - $6.2^\circ$  appears. Pentacene grown on the oxide mixes two crystalline phase.

In Figure 2-7, the sharp primary peak at  $2\theta = 6.10^\circ$  assigned to (001) corresponds to a distance spacing of 14.4 Å. There is a second smaller peak at  $2\theta = 12.22^\circ$ , which corresponds to the second order reflection (002) of the primary peak. In thicker films, more high order (00k) peaks are observed. In films grown with low substrate temperature, XRD reveals another set of peaks (00k') based on a different primary peak with the longer distance spacing. In films grown at the substrate temperature of 25°C and 70°C, the major part was (00k') peaks in the mixture phase, and almost only (00k) peak sets were observed at 150°C. Thereby, we can tell the difference in shape of grain boundary. At temperature of 25 and 70°C, the grain size was texture with micron-sized, terraced dendritic grains. However, at the temperature of 120 and 150°C, the film got together with many pieces of crystal pieces.

The single crystal structure of pentacene reveals  $\pi$  stacking in a triclinic structure with a  $c$ -axis length of 16.01 Å, which corresponds well to the (00k) distance spacing of 14.4 Å. We find that it would be thin films grown at 150°C. Therefore, the (00k) film ordering corresponds to single crystal-like packing, with the  $c$ -axis parallel to the surface normal. We attribute the (00k') peaks observed at low substrate temperature to a “thin film phase” of pentacene. The thin film phase may be a metastable growth-limited phase or a thermodynamically stable polymorph. These thin film polymorphs have also been observed in the previous research of pentacene [35]. The

TFTs based on mixed phase films exhibited inferior transistor performance.

In a short summary, pentacene crystallization as a continuous film was influenced by substrate temperature, morphology and different phase. Although many approaches were proposed to enhance pentacene grain growth, however larger poly grains do not mean better electrical properties. A good interface between pentacene and gate dielectric layer is another key factor. In material, however, a single phase of pentacene crystal is preferred for carrier transport due to the lack of interference between two kinds of orientation of pentacene molecules.

### 2.3.2 Four Probe Measurement

Contact resistance was investigated in TFTs by two different methods: (1) Four-probe conductance measurements on operating TFTs, and (2) resistance versus channel length ( $R$  vs  $L$ ) plots. Both techniques have been used to study contact resistance in  $\alpha$ -Si TFTs [32], however, they are not widely used in organic TFT research. In our four-probe conductance measurements, voltage sensing probes were evaporated simultaneously with the source and drain electrodes in the staggered structure ( see Figure 2-8 ). Figure 2-9 shows a schematic of the four-probe geometry used to determine film and contact resistance in operating pentacene-based TFTs. The probes are typically 10  $\mu\text{m}$  in width, and penetrate into the channel one fifth of the width. The sensing probes make up less than 10% of channel length and locate at one third and two third of channel length. The small geometric footprint and staggered geometry of the sensing probes minimize impact to the operating TFT.

The sense probes float at a voltage ( $V_1, V_2$ ) corresponding to the channel voltage at that position; thus, the voltage drop at the source and drain electrodes (due to carrier

injection) can be determined by extrapolating the channel voltage gradient back to the source and drain. Figure 2-12 shows a schematic of the voltage profile determined from a four-probe TFT measurement. The voltage drops between the probe1 and probe2 ( $\Delta V_{\text{film}}$ ), are calculated by the following equations:

$$\Delta V_{\text{film}} = V_2 - V_1$$

The voltage drops at the source and drain electrode ( $\Delta V_s$  ,  $\Delta V_D$  ), are calculated by the following equations:

$$\Delta V_s = [V_1 - (V_2 - V_1) / (L_2 - L_1) \times L_1] - V_s \quad (2-5)$$

$$\Delta V_D = V_D - [V_2 - (V_2 - V_1) / (L_2 - L_1) \times (L - L_2)] - V_s \quad (2-6)$$

where  $V_s$ ,  $V_D$ ,  $V_1$ ,  $V_2$  are the voltages at the source, drain and sense probes, respectively, and  $L_1$  ,  $L_2$  , and  $L$  are distances measured from the source electrode to the first probe, the second probe, and drain electrode respectively. These voltage drops represent the voltage required to inject carriers into the film.

In Figure 2-13, plot of sense probe ( $V_1$  , $V_2$ ) and source/drain voltage drops ( $\Delta V_s$  ,  $\Delta V_D$ ) as a function of gate voltage. The data correspond to transfer curve in Figure 2-10 operating with  $V_D = -5$  V and  $V_D = -15$  V. We can find the voltage drop across the channel would increase with the rising gate voltage due to induce channel conduction. In the beginning, the increasing gate voltage from small value lets the longitudinal field enough to form the depletion region at fix drain voltage as shown in Figure 2-14(a) and gate voltage induces the weakly band bending at source side. When the gate voltage become high, the band bending lets the voltage drop at source side increasing, but eased depletion region at drain side leading to the voltage drop decreasing as shown in Figure 2-14(b). It is additionally noted that the reasons for voltage drop at contact maybe the

schottky barrier, organic dipole barrier, depletion region and the access resistance at contact .

Using the drain current and sense probe data, the contact resistance can be calculated using

$$R_c = (\Delta V_D + \Delta V_S) / I_D = R_D + R_S \quad (2-7)$$

Separating source ( $R_S$ ) and drain ( $R_D$ ) contact resistances can be similarly determined, and this is an advantage of the four probe technique compared to  $R$  vs  $L$  plots, which lump both source and drain contact resistance together. The film resistance ( $R_{film}$ ) is calculated according to

$$R_{film} = \Delta V_{film} / I_D \quad (2-8)$$

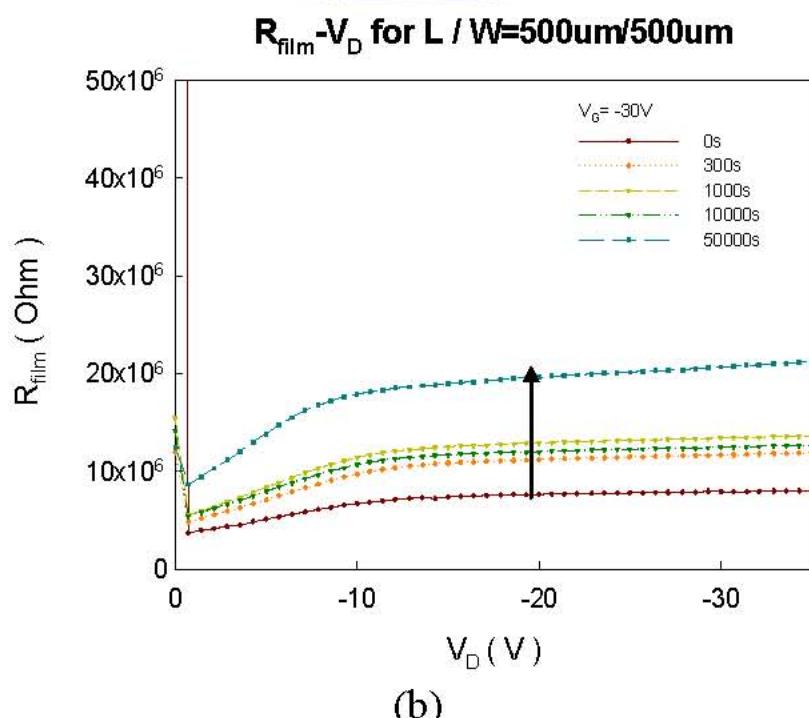

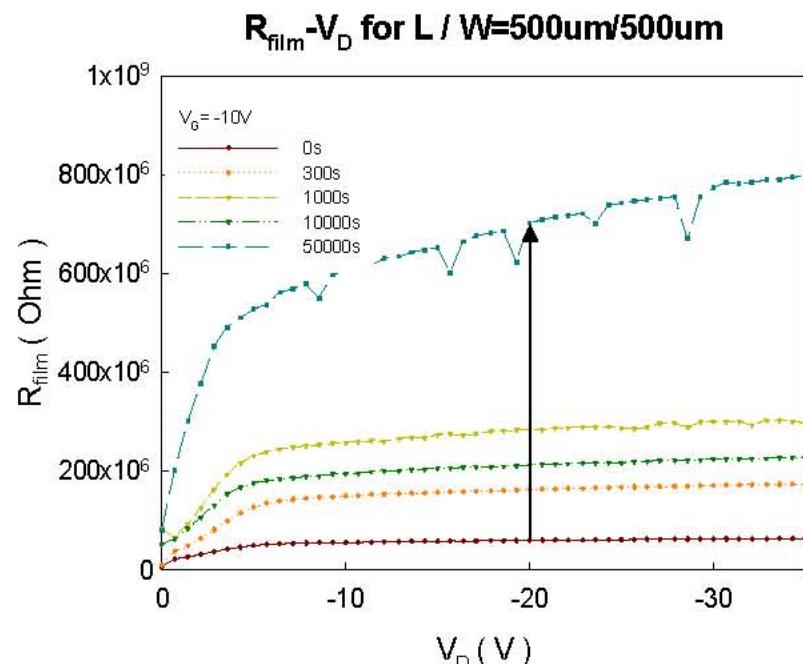

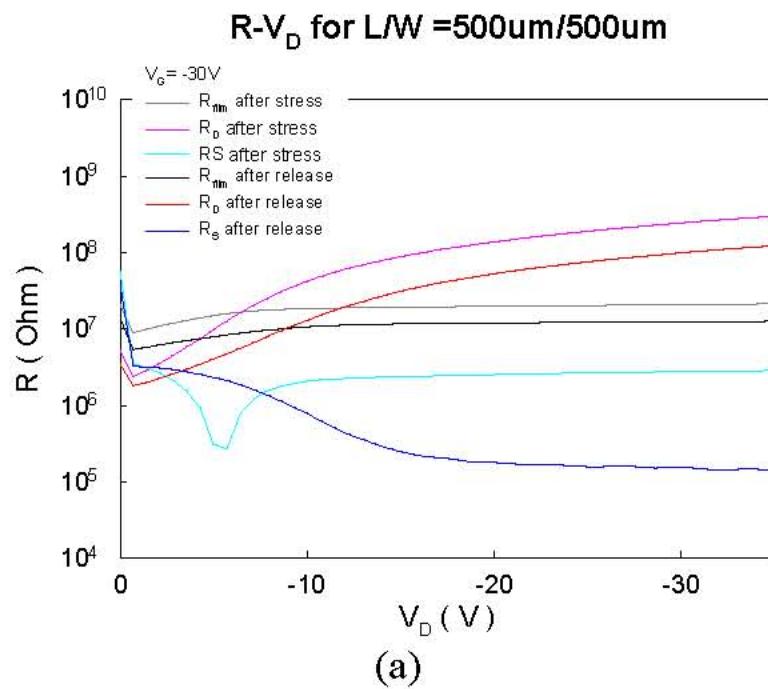

where  $\Delta V_{film}$  is the voltage drops between the probe1 and probe2. Figure 2-15 shows the plots of film resistance, source resistance, drain resistance and total contact resistance as a function of gate voltage for an operating OTFT. The data correspond to the device in Figure 2-10 operating at room temperature with  $V_D = -5$  V and  $V_D = -15$  V.

$R_S$  decreases weakly with increasing gate voltage, while  $R_D$  and  $R_{film}$  decrease significantly and soon line out. The decreasing resistance is originated from the more carrier concentration. The difference between Figure 2-15 (a) and (b) is the different drain voltage of -5V and -15V. When the applied drain voltage is -5V, smaller than -15V, it leads to the depletion region at drain side reduced. Therefore, the drain resistance at  $V_D = -5$  V is obviously smaller than at  $V_D = -15$  V as shown in Figure 2-16.

Sense probe data are only valid for characterizing contact resistance in the linear regime of TFT operation. In the saturation regime, the pinch off effect (non uniform channel electric field) complicates the voltage profile but we can still use them due to long channel which minimized the effect of the non uniform channel electric field. Next,

we double check these voltages and resistances as function of drain voltage. In figure 2-17, the plot of sense probe ( $V_1, V_2$ ) and source/drain voltage drops( $\Delta V_S, \Delta V_D$ ) as a function of drain voltage. The data correspond to the device in Figure 2-11 operating at room temperature with  $V_G = -10$  V and  $V_D = -30$  V. In the beginning, the voltage drops of all increase with the applied drain voltage rising. When the channel pinch off at drain side, the voltage drops at source side and the voltage sensed from probe1 and probe2 would enter into the saturation condition. In contrary, the voltage drop at drain side would go up abruptly. Therefore, the resistance at drain side should increase abruptly as the channel pinches off, as shown in Figure 2-18. the plots of film resistance, source resistance, drain resistance and total contact resistance as a function of drain voltage for an operating OTFT. The data correspond to the device in Figure 2-11 operating at room temperature with  $V_G = -10$  V,  $V_D = -30$  V. In the same way, the film resistance and the resistance at source side would increase with rising drain voltage till the channel pinches off.

Similar to the four-probe result, the contact resistance measured conventionally by  $R$  vs  $L$  plots is observed to decrease with increasing gate voltage (carrier concentration). TFTs using  $R$  vs  $L$  plots has shown that contact resistance decreases with increasing carrier concentration [36-38]. There is also well-documented evidence of decreased  $R_C$  with decreased  $R_{film}$  (increased carrier concentration, or increased mobility) in amorphous silicon TFTs [39]. Thus, it is important to note that when comparing contact resistance determined from four-probe and  $R$  vs  $L$  plots, the devices must have similar mobility and threshold voltage.

### 2.3.3 Sensitivity to Deposition Substrate Temperature

We can further investigate on the OTFT for different substrate temperature during

deposition by four probe structure. The transfer characteristics  $I_D-V_G$  at the drain voltages of -5V are compared with the different substrate temperature of 25°C and 70°C. We also have simultaneously the comparison of the output characteristics  $I_D-V_D$  with different deposition temperature of 25°C and 70°C at the gate voltages of -10V and -30V, separately. In traditional analysis, the electrical characteristics of OTFT at the temperature of 70°C would be better, including of higher on-current, better mobility, and smaller subthreshold swing as shown in Figure 2-19 and 2-20.

In Figure 2-21, we can have the comparison of film resistance, source resistance and drain resistance as a function of gate voltage with different deposition temperature of 25 °C and 70 °C for an operating OTFT. The data correspond to the device in Figure 2-19 operating at room temperature. The smaller film resistance was affected by high quality and large grains at the higher substrate temperature rightly. At the same time, it is interesting to find that the resistance at drain and source side reduced more obviously. It imply that the higher substrate temperature not only improve the thin film growth, but also help the connection of the contact between metal and semiconductor. Bottom contact devices consistently gave much higher contact resistance, which may be associated with poor semiconductor film morphology around the metal electrodes [40]. However, it can be improved by the increasing the substrate temperature during deposition.

We can double check these resistances as function of drain voltage as shown in Figure 2-22 and 2-23. Similar to the result of the resistance as function of gate voltage, the film resistance and the contact resistance is observed to decrease with increasing substrate temperature.

### 2.3.4 The Effect of Scaling

At first, we compared with the electrical characteristics for the different lengths of device. Figure 2-24 shows the transfer characteristics of the device at drain voltages  $V_D = -5V$  and  $V_D = -15V$ , and the output characteristics at gate voltage  $V_G = -10$  and  $V_G = -30V$ , compared with the length of 1000um, 500um and 100um.

As we known, the drain current with the longer length for device would be lower. However, we have the investigation on the threshold voltage versus length under drain bias ( $V_D = -5V$  and  $-15V$ ), in linear and saturation region respectively, and the effect of threshold voltage shift toward positive is observed in Figure 2-25. In the other word, the OTFT is easy to turn on or normally on like the short channel effect even if the smallest length still keeps with 40um. It is also surprised to observe Figure 2-26 (a). The subthreshold swing versus length under the drain voltage of  $-5V$  and  $-15V$  is strongly dependent on length even if the instability of OTFT still exists. Hence, the phenomenon of normally-on current is the significant reason for bad subthreshold swing due to the poor gate voltage controlling. In Figure 2-26 (b), the linear and saturation mobility versus length under drain bias ( $V_D = -5V$  and  $-15V$ ) also depicts that the trend of curve downward with the decreasing length.

It implies that the electrical characteristics are strongly dependent on the effect of length. Figure 2-26(b) and 2-25 shows the variation of extracted mobility and threshold voltage versus channel length for organic devices. As expected, for OTFTs the extracted mobility decreases at shorter channel lengths [23]. Because of a large drain-source voltage drop at source/drain series resistance in comparison to the channel resistance for a shorter channel-length OTFT (the channel resistance is smaller), this results in a lower extracted mobility. For a longer channel-length OTFT, e.g.  $L=1000\mu m$ ,

the channel resistance is much larger than source/drain series resistances, and the extracted mobility approaches its intrinsic mobility value (1.17 cm<sup>2</sup>/Vs).

In addition, the percentage of total device resistance indicated as  $R_{film}\%$  is a convenient gauge to understand the effect how contact resistance affects in device performance. We defined that,

$$R_{film}\% = \frac{R_{film}}{R_{tot}} = \frac{R_{film}}{3R_{film} + R_D + R_S} \quad (2-9)$$

Therefore, two kinds of devices with length (1000 um and 500 um) would be compared with the percentage of the film resistances. In Figure 2-27(a), the percentage of the film resistances as a function of gate voltage under drain bias ( $V_D = -5V$  and  $-15V$ ), the percentage of the film resistance with  $L=1000\mu m$  is more than with  $500\mu m$ . It depicts that there is the larger portion of the contact resistance in the shorter channel of  $500\mu m$ , rather than  $1000\mu m$ . For the same reason, the percentage of the film resistances as a function of drain voltage under gate bias ( $V_D = -10V$  and  $-30V$ ) in Figure 2-27(b) show the similar result.

Then, we compare with the electrical characteristics for the device with different widths. Figure 2-28 shows the transfer characteristics of the device at drain voltages  $V_D = -5V$  and  $V_D = -15V$ , and the output characteristics at gate voltage  $V_G = -10$  and  $V_G = -30V$ , compared with the device width of  $1000\mu m$ ,  $500\mu m$ ,  $100\mu m$  and  $50\mu m$ . Similar to the general result of TFT, the current with the narrower width for device would be lower. Next, we observe the subthreshold swing versus width and the threshold voltage versus width under drain bias ( $V_D = -5V$  and  $-15V$ ) as shown in Figure 2-29. It is unfortunate to find that there is no relation with the different width, maybe due to instability of device.

In Figure 2-30, the linear and saturation mobility versus width under drain bias

( $V_D = -5V$  and  $-15V$ ) also have the trend of curve upward with the decreasing width.

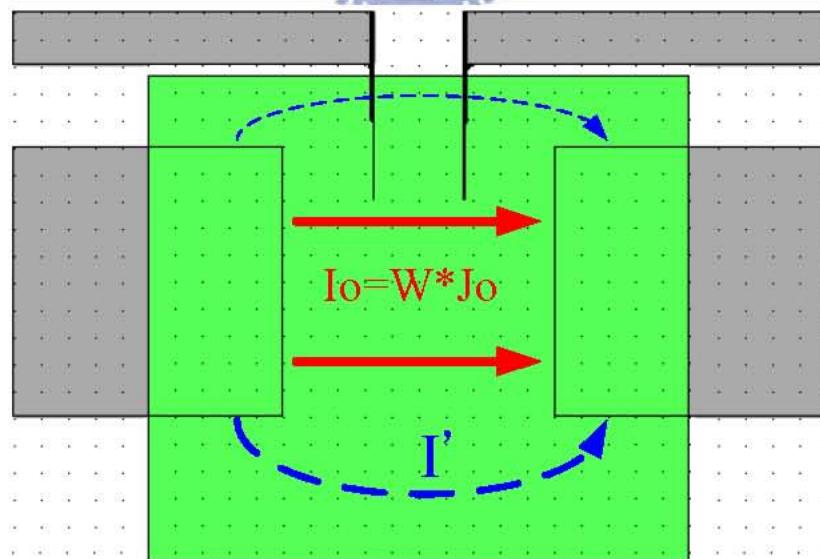

We take the further investigation on this phenomenon by normalize resistance and the percentage of the film resistance. We define the normalized resistance as the resistance divided by 1000 of width. In Figure 2-31, the normalized film resistance and the normalized resistance at drain side as a function of gate voltage under drain bias  $V_D = -5V$  and  $-15V$  were taken with the different widths of 1000um, 500um, 100um and 50um. We can find that the normalized resistance between the probe1 and the probe2 and at drain side reduced with the decreasing width. It also depicts that the resistances are sensitive to the width. There must be some additional effect to affect the film resistance which reduced as the width decreased. Therefore, we review our process and check our device as shown in Figure 2-32. The border effect for device, which result from active region fabricated by shadow mask should be considered. It attributed to the additional drain current. If we assume that the ideal drain current ( $I_o$ ) and the additional drain current ( $I'$ ) from the edge of active region, the total drain current as shown below:

$$I_{tot} = W \times J_o + I' \quad (2-10)$$

Then we estimate the mobility in linear regime by Equation ( 2-2 ), it yields

$$\mu_w = \frac{L}{C_{ox}} \left( \frac{\partial J_o}{\partial V_G} + \frac{1}{W} \frac{\partial I'}{\partial V_G} \right) \dots \text{for linear region} \quad (2-11)$$

The relationship between mobility and channel width corresponds well to the phenomenon as shown in Figure 2-30. We can also estimate the normalized film resistance as follows:

$$NR_{film} = \frac{R_{film}}{W} = \frac{\Delta V_{film}}{I_{tot} \times W} = \frac{\Delta V_{film}}{J_o + I'/W} \quad (2-12)$$