## 第一章 序論

## 1.1 液晶顯示器發展史

奥地利植物學家 F.Reinitzer 早在 1888 年就發現了液晶這一呈液體狀的物質,它是一種幾乎完全透明的物質,同時呈現固體與液體的某些特徵。液晶從形狀和外觀看上去都是一種液體,但它的水晶式分子結構又表現出固體的形態。美國無線電公司(RCA)在 1963 年時發現液晶分子會受到電場的影響而產生偏轉,當受到外界電場影響時,其分子會產生精確的有序排列;如對分子的排列加以適當的控制,液晶分子將會允許光線穿透;光線穿透液晶的路徑可由構成它的分子排列來決定,這又是固體的一種特徵。直到 1968 年,美國 RCA 公司的工程師們製造了世界第一台使用液晶顯示的螢幕,至此,「液晶」和「顯示器」才連結在一起,而有了「液晶顯示器」,Liquid Crystal Display(LCD)一詞[1]。

## 1.2 液晶顯示器原理

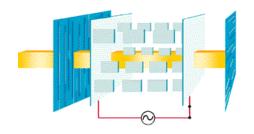

液晶顯示器(LCD)也就是使用液晶元件來調變光的螢幕。液晶可以改變它的分子結構,因此可以讓不同程度的光量通過它本身。液晶顯示器中含有兩片偏極片、彩色濾光片陣列及配向膜,它們可決定光通量的最大值與顏色的產生。液晶層位於兩片玻璃片之間,當施以一個電壓給配向層,則產生一個電場,使配向層界面的液晶朝某一個方向排列。每一個像素都由紅、綠、藍三個子像素(Sub-pixel)所組成,就如同映像管一樣。當液晶層不施任何電壓降時,液晶是在它的初始狀態,會把入射光的方向扭轉 90 度,因此讓背光源的入射光能夠通過整個結構(圖 1-1)。當液晶層施以某一電壓差,液晶會改變它的初始狀態,使液晶的排列方向不扭轉,而不改變光的極化方向,因此經過液晶的光會被第二層偏極片吸收而整個結構呈現不透光的狀態(圖 1-2)[2]。

圖 1-1 不施加電壓

圖 1-2 施加電壓

## 1.3 液晶顯示器驅動方式

LCD 主要可分成三種,分別為扭轉向列型(TN)、超扭轉向列型(STN)及薄膜電晶體型(TFT)。依驅動電路方式的不同又可分為被動式矩陣驅動及主動式矩陣驅動。TN 與 STN 屬於被動式矩陣,此型的液晶顯示器由於電容串因(Capacitor Coupling)嚴重,而導致會有殘影及對比差及反應速度慢等缺點,再加上又是採用多工方式驅動,驅動方式較為複雜。因此此類型的顯示器要達到高解析度、高畫質與全彩的目標便十分困難。但由於製造成本低廉因此部分低階的顯示器如手機上的面板便常用此技術[3]。目前國內趨勢 TFT 型則是屬主動式矩陣[4]。此種技術由於利用薄膜電晶體作為控制液晶旋轉的開關元件,使得每個畫素相互間的影響變小,改善了上述被動式矩陣驅動液晶顯示器的缺點。且驅動方式較為簡單,因此顯示器的畫質與解析度能夠進一步提升。然而利用薄膜電晶體方式驅動的液晶顯示器,其成像品質的好壞與電晶體的特性有很大的關係,如漏電流、驅動電流、寄生電容、臨界電壓與開關速率等。因此如何製造出品質好,特性佳的薄膜電晶體相當重要。

## 1.4 薄膜電晶體

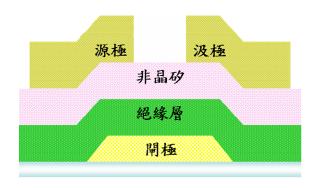

電晶體是由一個閘極、一個源極和一個汲極所構成的三接點電子元件 (圖 1-3)。其原理是利用絕緣層讓閘極和通道的部分隔開,當閘極沒有外加 一個電壓時,就沒有電流從源極流向汲極。此時唯一通過的電流即稱為漏 電流。而當閘極加一夠大的正電壓時,在通道部分會感應出電子來,此時 如果再在汲極部分加一電壓,將使大量電子經由源極流向汲極,使得薄膜 電晶體從原本的「關閉」變成「開啟」的狀態。所以薄膜電晶體可以被視 為一個開關[3]。

圖 1-3 電晶體基本結構(Bottom Gate)

#### 1.4.1 非晶矽薄膜電晶體

非晶矽薄膜電晶體(a-Si TFT)為 TFT-LCD 中較為成熟的技術,故目前大多數的 LCD 市場仍以非晶矽為主流。主要是因為非晶矽 TFT 有以下優點:為一低溫製程(<350℃),非常適合製造於玻璃基板上的 TFT;為連續製程。一般多利用電漿輔助化學氣相沉積(PECVD, Plasma Enhanced Chemical Vapor Deposition)的方式連續沉積閘極介電層、主動層和汲/源極層,再回蝕(Etchback)定義所需的形貌。因此底閘極(Bottom Gate)結構的薄膜電晶體較符合要求。整個製程步驟較為簡單;並且有較低的漏電流。但是非晶矽 TFT也有著某些無法改進的缺點,如電子遷移率(mobility)很低(<1cm²/V・S),開啟電流(on current)較小。在這些先天缺陷下,非晶矽的 TFT-LCD 有著反應速率慢,解析度低,開口率較低等缺點。由於畫素的增加,需要比非晶矽 TFT 電性更好的視晶矽薄膜電晶體,以改進上述的缺點。

## 1.4.2 複晶矽薄膜電晶體

複晶矽薄膜電晶體(p-Si TFT)與非晶矽薄膜電晶體的不同在於主動層以複晶矽取代非晶矽,使得電晶體之驅動能力大大的提升。一般複晶矽薄膜製作的方法分為直接沉積複晶矽(As-deposited Polysilicon)及沉積非晶矽再退火(Annealing)兩種。直接沉積複晶矽製程溫度在 625 C以上,高於一般玻璃基板的軟化溫度(600 C),且直接沉積的複晶矽,其晶粒(Grain)較小,缺

陷(Defect)較多,製作出來的薄膜電晶體特性較差,所以通常無人使用此方式製作。另外一種製作複晶矽的方法為先利用低壓化學氣相沉積(LPCVD, Low Pressure Chemical Vapor Deposition)、PECVD 或濺鍍(Sputtering)的方式沉積非晶矽薄膜,再利用熱處理的方式使其再結晶為複晶矽薄膜。

再結晶的方式可分為高溫及低溫兩類,以玻璃基板的軟化溫度(600°C)為分界。高溫再結晶通常以爐管(Furnace)或是快速熱退火(RTA, Rapid Thermal Annealing)的方式進行,由於使用高溫製程,所以必須使用較昂貴且小尺寸的石英基板,並限制了其應用範圍。因此低溫再結晶的方式是目前最受矚目並為工業界採用的技術。利用低溫再結晶所製造的低溫複晶矽(LTPS, Low-Temperature-Poly-Silicon)薄膜電晶體具有較高載子移動率[5]。而電子與電洞的移動率是決定一個 TFT 元件等效傳導率與尺寸大小的重要參數,而高載子移動率使得 LTPS TFTT-LCD 具有下列的競爭優勢:

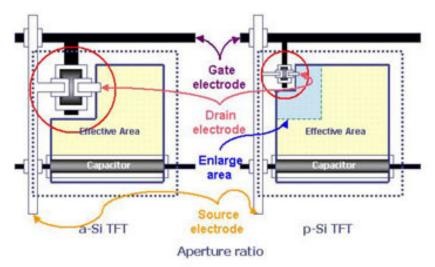

- a. 可縮小畫素(Pixel)中 TFT 的尺寸,增加透光區域的面積,而達到高開口率(圖 1-4)[6]。因此在相同的發光亮度下,LTPS TFT-LCD可採用低瓦數的背光源,達到低耗電量的要求。另外藉由完全自我對準(Fully Self-Alignment)來形成源/汲極區域,則可降低寄生與重疊電容所需的儲存電容面積也能因此縮小,讓開口率進一步提高,而能提供更高精細、高解析度的液晶面板。

- b. 可將周邊驅動電路與液晶面板同時製作於玻璃基板上,有利 於減少電路板驅動 IC 與面板電極之間的連線,而降低材料成 本;同時更可以在後段模組組裝過程中,避免組裝造成的產品 損害,進而提升良率降低製造成本。

- c. 可降低顯示器模組的重量與厚度。驅動電路的整合不但能消除驅動 IC 本身的重量與厚度,也省去的與其相關的 TAB 及PCB 封裝所增加的厚度與重量,可達到縮小面板厚度約10%~20%,達成產品薄型化的要求。

- d. 可增加液晶顯示器面板的可靠度。TAB 連接線的故障與鬆脫 是面板損壞的主因,因此省去 TAB 的封裝將使得液晶顯示器 面板的可靠度得以提升。

- e. 可降低驅動電壓,進而降低液晶面板的功率消耗。LTPS-TFT 具有高載子移動率與低臨界電壓(Threshold Voltage)的特性, 因此在固定驅動電流下,驅動 LTPS-TFT 的電壓可大幅降低, 再加上寄生電容的減少,則驅動液晶面板的功率消耗能大幅

降低。表 1-1[7]列出了 a-Si TFT 與 LTPS TFT 的各方面特性比較。

圖 1-4 非晶矽與多晶矽面板之開口率比較[6]

表 1-1 a-Si TFT 與 LTPS TFT 特性比較[7]

|                         | a-Si TFT            | LTPS TFT     |  |  |

|-------------------------|---------------------|--------------|--|--|

| Mobility <sub>eff</sub> | 0.3~1cm²/V-sec      | >50cm²/V-sec |  |  |

| TFT元件面積                 |                     | 約1/2         |  |  |

| 耐衡撞強度                   | 180G                | 300G         |  |  |

| 耐扭強度                    | 約1,000次             | >10,000次     |  |  |

| 週邊接點數                   | 4,000個接點            | <200個接點      |  |  |

| PCB数量                   | 2片                  | 1片           |  |  |

| TAB-IC數量                | Scan:3個<br>Data:10個 | 無            |  |  |

| 電容零件數                   | 270個                | 195個         |  |  |

## 1.5 低溫複晶矽結晶方法

低溫複晶矽的量產技術在過去十年間急速熱絡的展開,包括固相結晶法(SPC, Solid Phase Crystallization)、準分子雷射退火(ELA, Excimer Laser Annealing)及金屬誘發/金屬誘發側向結晶(MIC/MILC, Metal Induced Lateral Crystallization)等,以下將分別介紹。

## 1.5.1 固相結晶法(SPC, Solid Phase Crystallization)

固相結晶法是成本最低,也是技術門檻最低的結晶法。一般的作法是將已沉積之非晶矽薄膜置入爐管中進行 600°C 24~72 小時的退火。為了得到較大的晶粒,可以改變非晶矽的沈積參數及退火條件。但是利用固相結晶法所得到的複晶矽晶粒品質和另兩種結晶法相比仍然是較差的,且晶粒中的缺陷多。另外,退火溫度過高並不適用於一般的玻璃基板(一般的玻璃基板軟化溫度約為 600°C 左右),可能會造成玻璃的變形,會影響到後續的微影製程。固相結晶包括二個步驟,分別為成核 (Nucleation)和成長 (Growth)。成核又可分為均質成核 (Homogeneous)和異質 (Heterogeneous)成核。以固相結晶法來說,由於非晶矽裡含有缺陷,缺陷自由能較高,較容易吸附溶質原子造成原子聚集,形成異質成核,進而成長;也有部分的成核是以均質成核進行,然後再進行成長。但是一般的固相結晶法退火時間太長,且最後所得到的晶粒缺陷多,因此最後所做出的薄膜電晶體特性並不佳。

## 1.5.2 準分子雷射退火結晶法(ELA, Excimer Laser Annealing)

ELA 製備複晶矽薄膜的溫度通常低於 450℃,以準分子雷射作為熱源。雷射光經過投射系統後,會產生能量均勻分布的雷射光束,投射於具有非晶矽薄膜的玻璃基板上。當非晶矽薄膜吸收準分子雷射的能量後,非晶矽熔融而形成複晶矽結構。這種方法獲得的複晶矽薄膜的特性滿足顯示面板用 TFT 開關元件及周邊驅動用 TFT 元件性能的要求[8]。準分子雷射主要是在紫外光範圍的高輸出脈衝雷射 (high-output pulsed lasers) 振盪,光束相當大,脈衝的時間非常短,約 10ns。因為加熱的時間是很短暫的,而且結晶的均晶粒缺陷較少,品質較佳。缺點是雷射設備成本過高,而且結晶的均

与性不佳,晶粒尺寸還不夠大,故對大面積的玻璃基板來說在製程上仍然有很多需改進的地方。另外,雷射將非晶矽層溶融結晶後,在兩晶粒的交界處會隆起產生晶界。此現象會導致表面粗糙,將會影響元件的製作。當然還有其他的缺點,像是玻璃基板通常需要雷射掃描 20 次左右才能形成良好的結晶。為了提高生產效率,現在有採用多路雷射同時掃描的方式。也可以採用矩形光束的方法,使雷射能量均勻集中形成一個矩形光束,對基板進行有選擇性的掃描。常用的準分子雷射器如表 1-2 所示。因為 XeCl 準分子雷射器具有較好的氣體穩定性和在波長 30 8nm 處非晶矽薄膜具有高吸收係數(~106 cm<sup>-1</sup>)的優點。所以很多廠商採用 XeCl 準分子雷射器進行生產。

表 1-2 準分子雷射氣體及其波長

| Laser gas | F <sub>2</sub> | ArF | KrCl | KrF | XeCl | XeF |

|-----------|----------------|-----|------|-----|------|-----|

| λ (nm)    | 157            | 193 | 222  | 248 | 308  | 351 |

# 1.5.3 金屬誘發 / 金屬誘發側向結晶(MIC / MILC, Metal Induced / Metal Induced Lateral Crystallization )

Wagner 和 Ellis 在 1963 年發現少量的特定金屬可以幫助矽結晶[9]。依照不同誘發結晶的方式可以分成兩類:第一種是與矽產生共晶反應(例如:Al[10]、Au[11]等),由於共晶點的溫度通常比一般單相結晶的溫度低,所以可以在低溫下產生結晶。以 Al 為例,M. S. Haque[10]在研究中指出 Al 與Si 的共晶溫度在 577℃,但在 200℃左右便開始與 a-Si 層反應產生結晶。金屬向內擴散時不僅使 a-Si 結晶,同時因為金屬摻雜的關係導致 Si 層轉變成 p型。

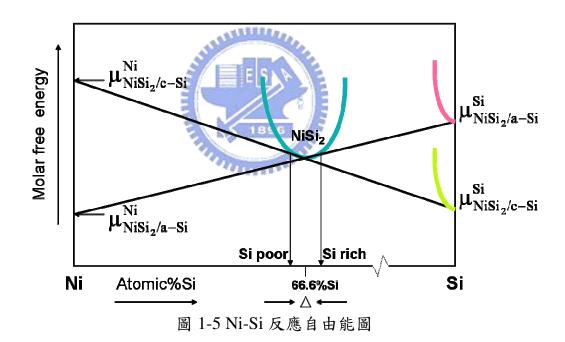

另一種低溫結晶的方式是利用金屬與矽反應成介穩定(Metastable)的矽化物(例如: Ni[12][13]、Pd[13],[14]等),在矽化物移動的過程中,金屬原子的自由電子與介面處的 Si-Si 共價鍵發生反應,降低 a-Si 結晶所需的能障 (Energy Barrier),使得結晶溫度降低。一般較常用的金屬為 Ni,而其機制也最清楚,因此以 Ni 來說明此類金屬誘發結晶的過程。 Ni 會先與 Si 反應成多種矽化物[15],在靠近 a-Si 區域的地方會產生富 Si 的 NiSi2。由圖 1-5 的

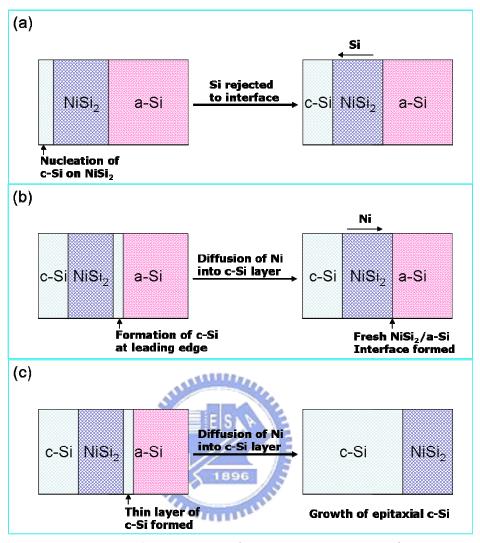

Ni-Si 反應自由能圖[16]中可知,在 NiSi2 中的 Ni 原子在 NiSi2 與 a-Si 介面的自由能比在 NiSi2 與 c-Si 介面處低,這個自由能差會使 Ni 原子往 a-Si 層移動;反之,在 NiSi2 中的 Si 原子在 NiSi2 與 c-Si 介面的自由能比在 NiSi2 與 a-Si 介面處低,所以有個驅動力驅使 Si 原子往 c-Si 的方向擴散。這結果會使得 NiSi2 持續的往 a-Si 延伸,而所經之處產生 Si 結晶。由 Hayzelden 在 1993 年提出的分裂機制,首先會在 NiSi2 上形成 c-Si 結晶核,然後 Si 會往 c-Si/NiSi2 的介面移動,而誘發結晶,如圖 1.6(a)所示,接著,又在 NiSi2 的領導端(leading edge)處形成結晶(c-Si) 核,而為了降低 Ni 在 NiSi2/c-Si 介面處的化勢(Chemical Potential),因此 Ni 會往 NiSi2/a-Si 介面處擴散,而造成 NiSi2 的遷移,同時也形成一個新的 NiSi2/c-Si 介面,如圖 1.6(b),而此過程一直重複,因而得到針狀的誘發結晶,圖 1.6(c)。

圖 1-6 c-Si 在 NiSi<sub>2</sub>/a-Si 介面形成的結晶成長機制

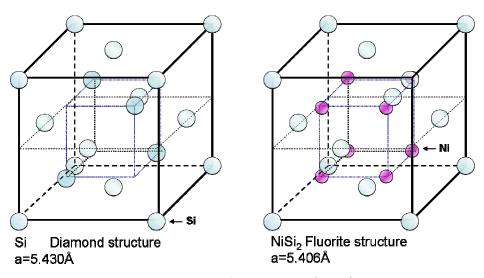

圖 1-7 Si 與 NiSi<sub>2</sub> 晶體結構

圖 1-7 為 NiSi<sub>2</sub>與 Si 的晶體結構。NiSi<sub>2</sub>屬於螢石(Fluorite)結構、晶格常數為 5.406Å;而 Si 為鑽石(Diamond)結構、晶格常數為 5.430Å,兩者因晶格常數不同所產生的晶格不匹配(Lattice Mismatch)僅有 0.44%。在眾多金屬矽化物中 NiSi<sub>2</sub>擁有與矽最相似的結構及最接近的晶格常數,因此相當適合做為誘發結晶的核。故我們在實驗中將以 Ni 為誘發結晶的金屬。

Ni 在結晶或非晶矽中都屬於快速擴散源,主要是藉著間隙式擴散 (Interstitial Diffusion)所造成的。在此機制中,擴散係數(D)會遵守 Arreherius 方程式:

$$D_{i} = D_{i,0} \exp\left(-\frac{H_{i}^{M}}{KT}\right) \tag{1}$$

$$D_{Ni}(a-Si) = D_{Ni}(a-Si)/\left[1 + \alpha C^{t} \exp\left(H_{Ni}^{B}/KT\right)\right]$$

(2)

其中  $\alpha=Z_{Ni}(\theta^0/\theta^*)\exp(S^B_{Ni}/KT)$ , $C^t$  為被阻礙的原子比例、 $H^B(S^B)$ 為焓  $Z_{Ni}$  阻礙的空隙數以及  $\theta$  代表空隙被佔據的比例。

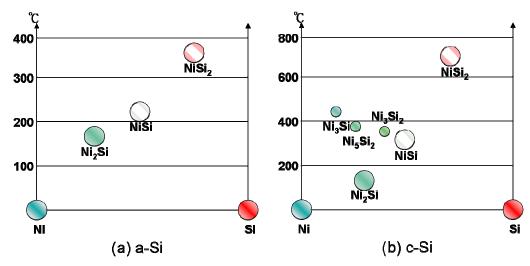

在 Ni-Si 的反應中,主要是藉由 Ni 原子的擴散。在富矽相的情況下,約  $200^{\circ}$ C 時開始產生  $\delta$ -Ni $_2$ Si 。之後隨著退火溫度的提高,在  $350^{\circ}$ C 時 Ni $_2$ Si 逐漸被 NiSi 相所取代。在  $750^{\circ}$ C 左右慢慢形成 NiSi $_2$  。NiSi $_2$  的形成主要是由成核機制所控制的,需要在高溫下才能形成。但在退火的過程中 Ni 並不會直接與矽反應形成 NiSi $_2$ ,而會先反應形成 NiSi 的介穩定相[15][17],再由 NiSi 與 Si 反應而得到 NiSi $_2$ 。在 NiSi 與 Si 的反應機制裡,NiSi 與 a-Si 反應形成 NiSi $_2$ 是屬於擴散控制,在  $350^{\circ}$ C 左右就可以形成 NiSi $_2$ ;而 NiSi 與 c-Si 反應形成 NiSi $_2$ 則是屬於成核控制,所以需要在高溫下才能得到。所以就金屬誘發而言,Ni 與 a-Si 薄膜反應形成 NiSi $_2$ 來誘發結晶並不需要很高的溫度[18]。圖 1-8(a)(b)列出了鎳金屬薄膜在非晶矽與複晶矽中對應不同溫度下所形成的矽化物相[19]。

圖 1-8 鎳金屬薄膜對應不同溫度下之矽化物相[19]

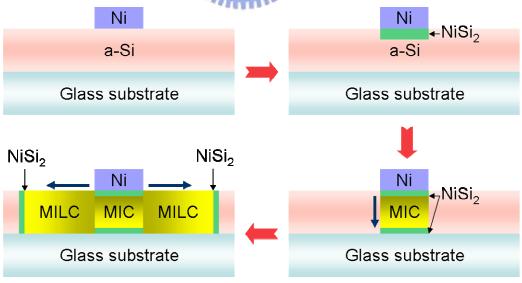

接下來描述 MILC 的成長機制,從圖 1-9 來看,首先我們會在非晶矽上面利用黃光微影技術擇區鍍覆上一層鎳金屬薄膜。接著在適當溫度下退火(350℃~550℃),首先會形成一層 NiSi<sub>2</sub>。由於熱力學上的驅動力,NiSi<sub>2</sub>向下移動,如前述的結晶成長機制,形成金屬誘發結晶 (MIC)。在 NiSi<sub>2</sub>移動至非晶矽底部受到基板阻擋後,接著 NiSi<sub>2</sub>向兩側移動,形成金屬誘發側向結晶 (MILC)。此即為 MILC 的成長機制。

圖 1-9 MILC 成長機制

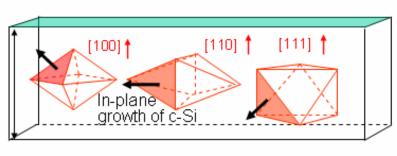

接下來討論 MILC 成長方向之優選性,我們知道 NiSi<sub>2</sub> (111) 平面跟 Si (111) 平面的晶格常數只有 0.44% 的不匹配。當 c-Si 在 NiSi<sub>2</sub>{111}平面上產生磊晶時,並不會有介面差排的出現。所以在 MILC 的過程中,{111}為其 c-Si 的優選方向[20]。而我們可以從圖 1-10 中看出,在軸向為<110>的情況下,c-Si 八面體結構的四個{111}方向將會平行薄膜的上下表面。但是如果軸向為<100>或<111>的情況下,{111}方向並不會平行薄膜表面。所以 c-Si 的成長將會被薄膜上下表面所限制。所以 c-Si 的成長的優選軸向為<110>而優選成長方向為<111>。由於 MILC 有上述的優選性,所以以此方法成長的複晶矽會有其方向性,這也成為 MILC 方法最大的優點。

圖 1-10 MILC 的優選成長方向

## 1.6 電性影響因素

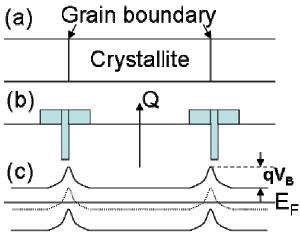

## 1.6.1 晶界能障

在基本的載子捕陷的模式中假設晶界本身是非常窄的(與晶粒相比)他們唯一的效應是去改變有效的摻雜物原子及在晶粒中的自由載子數目。晶界本身即當作摻雜物偏析及載子捕陷的位置,因此晶界的存在會影響載子移動進而影響元件的特性。如圖 1-11 所示,當電荷被晶界所捕陷時,為了去補償被晶界所捕陷的電荷,所以在晶界周圍形成一個空乏區域,根據Poisson's equation,在空乏區的電荷造成能帶彎曲,而且會形成能障而阻礙剩下的主要載子在晶粒間移動[21]。能障高度( $V_B$ )能用摻雜濃度 N 及空乏區寬度  $x_d$  以 Poission's equation 表示:

$$\frac{d^2V}{dx^2} = \frac{qN}{\varepsilon} \tag{3}$$

q:一個電子的電荷大小

$\varepsilon$ :矽的介電常數

只考慮一維的空間,解方程式得到 V<sub>1</sub>

$$V_{B} = \frac{qN}{2\varepsilon} x_{d}^{2} \tag{4}$$

由  $V_B$  的解可以了解能障大小和置換型雜質濃度、捕陷密度及能量有很大的關係。

圖 1-11 (a) 晶粒與晶界示意圖 (b)為了去補償被晶界所捕陷的電荷在晶粒周圍的晶界處形成空乏區域 (c)電荷空乏區造成能帶彎曲,而且形成能障[25]

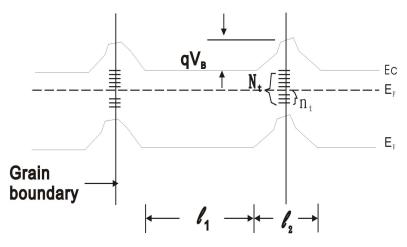

## 1.6.2 晶界處的載子捕陷(carrier traps at grain boundary)

由於電子的傳導行為由載子的數目多寡所決定,要決定自由載子在多晶矽中的數目,必須先考慮置換型的雜質濃度,雜質原子會偏析在晶界中造成損失,而且在電性上不發生作用;但即使將此損失考慮進去,多晶矽的電導度仍然比具有相同摻雜濃度的單晶矽低,因為單晶矽中自由載子直接由在晶粒中的置換型摻雜原子所貢獻至價帶及導電帶,而多晶矽因為有晶界的關係,大部分的自由載子會被捕陷(trap)在低能量的晶界位置,因而無法貢獻到傳導帶[22],[23],示意圖如圖 1-12 所示。

圖 1-12 很多在晶粒中的置換型摻雜原子所貢獻的自由載子很快速的就被固定在晶界處的捕陷位置 Nt(每單位面積的能量不超過能隙 (bandgap))[24]

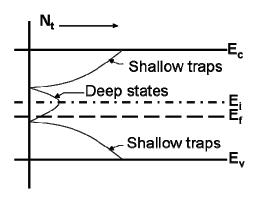

在晶界處的懸鍵(dandling bonds)及晶粒中的缺陷兩者都會引出一個在多晶矽中的允許的態位(allowed state),如圖 1-13 所示。其中和懸鍵有關的深態位(deep state) 擁有大約禁止能隙(forbidden energy gap)一半的能量[21],此深態位對載子傳輸的最大影響就是允許載子產生(generation)與再結合(recombination)。除了在中間能隙(mid-gap)附近的態位是由斷鍵(broken bonds)造成之外,應變鍵(strained bonds)也會產生的一個高密度的在能帶邊的淺拖曳態位(shallow tail state)。這些態位都會捕捉載子而造成載子傳導率下降。

圖 1-13 捕陷(traps)主要集中在晶界處,然而在晶粒中的缺陷也有建立起一些態位。淺拖曳態位(shallow tail state)與應變鍵(strained bonds)有關,而在中間能隙的深態位(deep state)是由斷鍵(broken bonds)造成的 [24]

## 1.6.3 雜質原子

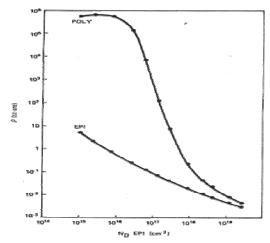

阻值的控制是非常重要的,多晶矽的阻值都比相同雜質原子濃度的單晶矽或磊晶矽大,如圖1-14所示。由圖1-14中可看出在低雜質濃度(10<sup>15</sup>/cm³)時,多晶矽的阻值隨著雜質濃度增加改變不大,阻值維持在105Ω-cm中間,而單晶矽在相同雜質濃度時,阻值小於多晶矽的阻值 6 個等級。在中等雜質濃度時複晶矽阻值驟降,而且快接近單晶矽的阻值。但是雖然中等濃度的雜質原子能有效的降低複晶矽的阻值,但由於變動性太大,不易控制,會造成元件特性不均勻,所以一般製作 TFT 元件還是會控制在低雜質濃度下來製作。但雜質濃度也不可太低,會需要較長的活化時間及阻值過高的影響。

圖 1-14 複晶矽與磊晶矽阻值與雜質濃度關係圖[26]

## 1.7 電性改良方法

在之前有提到晶界中的捕陷位置的存在會大大的減損複晶矽元件的電性,所以減少晶界中有效的捕陷密度,將可提升複晶矽元件的電性。因此為了提升電性,將試著減少晶界中的有效的捕陷位置或著減少晶界的數量。以下描述提升電性的方式:

## 1.7.1 晶界鈍化 (Grain-boundary passivation )

由於缺陷被鈍化,所以禁止能隙的態位不會被活化。因此不會再捕陷載子。晶界中的懸鍵的形成是由於不同指向的晶粒的接和點的晶格排列不連續所引起的,因而這些懸鍵形成了很多的捕陷位置。在 Si/SiO<sub>2</sub> 界面的懸鍵一般常用 H 原子將懸鍵中斷,所以利用 H 原子可以將晶界中的懸鍵鈍化以減少晶界中的有效捕陷數目。當捕陷載子的數目減少晶界的能障也跟著減少[27]。 一般可利用電漿(plasma)來進行晶界鈍化改善元件的執行效果,常用來進行晶界鈍化的電漿有  $H_2 \cdot N_2 O$  及  $H_2/N_2$  混和型電漿[28]-[29] 。根據文獻[29]報導, $H_2/N_2$  混和型電漿會比  $H_2$  電漿有更好的鈍化效果。這是由於  $H_2/N_2$  混和型電漿除了有氮離子 (N+) 的鈍化作用外,同時提高原子間的撞擊機會,因而提高鈍化的離子數目,可以加強鈍化的效果。另外  $NH_3$  電漿也有不錯的鈍化效果,跟  $H_2$  電漿相比可以讓熱載子 (hot carrier) 有更好的穩定性,同時可以讓匣極氧化層有更低的漏電流及更高的崩潰電壓 [30],[31]。

## 1.7.2 後退火(post-annealing)

前面有提到晶界本身是個能障,晶界的存在將會阻礙載子移動,因而減少電子移動率,而減損 TFT 元件的效能,因此如何減少晶界的數量對改善 TFT 元件特性來說也是一個很重要的課題。另外,晶粒內缺陷的消除對提升元件特性也有很大的幫助。因此很多研究相繼的提出如何減少晶界及消除晶粒缺陷,其中最有效的方式就是利用後退火的方式[32]-[33],即在非晶矽膜結晶完後,再利用高溫退火的方式或準分子雷射退火的方式進行結晶,通常可以得到尺寸較大,缺陷較少的晶粒,因而改善多晶矽膜的品質。

## 1.8 實驗動機

金屬誘發側向結晶(Metal Induced Lateral Crystallization)的方法可在低於 600℃的製程溫度下於玻璃基板製造高品質的薄膜電晶體。與準分子雷射退火(Excimer Laser Annealing)相比,有更好的均勻性,且能節省更多的生產成本,達到大尺寸面板的目標。

然而,利用金屬誘發側向結晶的複晶矽薄膜中,鎳會被針狀(Needlelike)結晶間的晶界及缺陷(Defect)所陷捕(Trap),並於矽能隙中產生深層能階(Deep Level)。這些深層能階會致使元件操作在關閉狀態(Off State)時在汲極端受到汲極電壓影響,使得熱離子場放射(Thermionic Field Emission)與穿隧(Tunneling)這兩種效應所產生的漏電流提高。對於高解析度的面板而言,漏電流的要求需要在  $pA/\mu$ m 以下,以避免畫面殘影等缺點。且漏電流降低後,便能減少儲存電容的面積而更近一步提高開口率,往更高畫質邁進。

因此,在金屬誘發結晶的研究上著重於如何降低複晶矽薄膜中的鎳含量。目前有兩種方向:

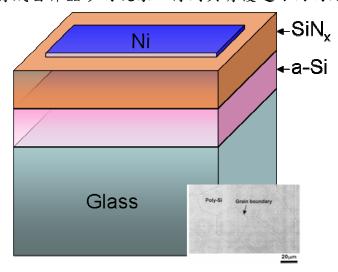

第一種方向是降低誘發結晶前鍍覆的鎳濃度,如在 2003 年由 Choi 等人 [35]提出加大 NILC 晶粒的方法。即將非晶矽薄膜鍍覆在二氧化矽基材上接著將氮化矽  $(SiN_x)$ 薄膜沈積在非晶矽薄膜上如圖 1-15 所示,再用濺鍍的方式鍍覆 0.5nm Ni 膜在  $SiN_x$ 上。最後將此試片在快速退火爐(RTA)中進行退火,結果發現得到的平均晶粒尺寸為  $20\sim90~\mu$  m 的晶粒(圖 1-15)。 文獻中提到利用  $SiN_x$  薄膜當作過濾器(filter)能有效的過濾鎳原子的數目,而控制 Ni 在非晶矽中的濃度,進而減少鎳誘發結晶的成核點,因而得到較大尺寸的鎳誘發結晶的晶粒。另外在一些文獻中曾經提出利用 MBE,在較厚的 silicide 層(~1000Å)成長磊晶 Si/silicide/Si 結構,而其中以  $CoSi_2$  及  $NiSi_2$  在 (111) 的矽晶圓上長磊晶的結果最好[36],[37]。而且在 Si(111)的晶圓上,低溫下 $(500^{\circ}C)$ 即可得到磊晶的  $NiSi_2[38]$ ,很適合用於低溫複晶矽的製程,因此想用一種新的方式成長出具有磊晶效果的複晶矽薄膜。

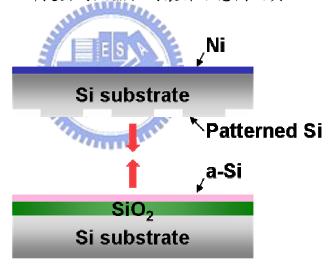

由前面的介紹引發了新的想法,提出了一種新的結晶技術,即利用矽晶圓當過濾基板進行鎳誘發結晶。簡單說明一下實驗的設計,首先在 Si wafer 背面鍍覆鎳金屬,並且在 Si wafer 正面利用微影(photolithography)與蝕刻方式來製作圖形(pattern),再與非晶矽膜接觸後,進行退火誘發結晶(如圖1-16)。由於鎳不需直接鍍覆在非晶矽薄膜上,可避免鎳金屬直接轉移到非晶矽上。又因鎳金屬鍍覆在另一晶圓背面所以可藉由晶圓當做一過濾之媒

介,進而減少鎳金屬的殘留。另外,利用矽晶圓的單晶特性可以讓所誘發的 複晶矽會有磊晶(Epitaxy)的特性,進而改善結晶品質,並改善一般 NILC 結 晶在晶粒間會有殘留非晶矽的現象,得到具有優選方向的結晶。

圖 1-15 Choi 等人所提出的大晶粒的製作示意圖及其 SEM 結果

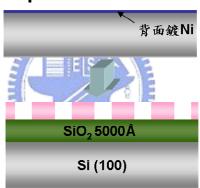

圖 1-16 NILC with patterned Si wafer filter

第二種方向則是在誘發結晶後減少複晶矽薄膜中的殘餘鎳含量。即所謂的捉聚、捕捉或去疵(Gettering)。捉聚一般是應用在晶圓上,因為在晶體成長之後的晶圓製程階段,無可避免的會引入第三類過渡金屬原子(例如鉬、鐵、銅、鎳),這些金屬原子的高擴散性會更進一步的對元件造成有害結果。因此從前的文獻都對捉聚晶圓內的金屬雜質做研究[39]、[40]。

目前捉聚複晶矽中殘餘鎮並實際應用在薄膜電晶體量產的例子為夏普

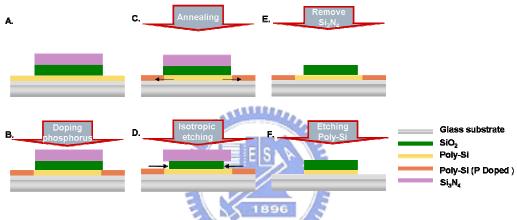

(Sharp)的 CGS 技術[41]。其減少了鎳含量並降低漏電流。但是製程上需要額外的離子植入、黃光微影及蝕刻步驟,如圖 1-17。整體製造成本與時間上的增加為其缺點。在本研究中,利用晶圓接合[34]的技術將鍍覆非晶矽的晶圓做為補抓基板與金屬誘發側向結晶的複晶矽接合,由於兩者鎳含量之差異以及熱力學上的因素,成功的把殘餘鎳捕捉至基板,顯著的降低了複晶矽中鎳含量。

圖 1-17 Sharp CGS 技術之捉聚製程步驟

## 第二章 NILC 晶圓過濾基板之研究

## 1.9 简介

由於鎳誘發結晶技術是一種可以得到高品質的複晶矽薄膜的技術,因此鎳誘發結晶技術目前被熱烈的研究中。鎳誘發技術的研究一直以來朝著如何加快結晶速率、改善結晶品質及增大晶粒尺寸與減少鎳污染的目標進行,因此有各種的新方法被提出,接下來簡述一下各種改善的方法。

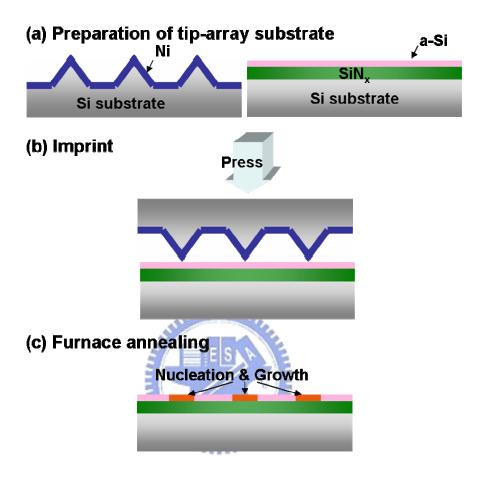

在 2000 年由 Bae 等人[42]提出利用壓印方法來進行鎳誘發結晶,其主要過程如圖 2-1 所示:首先在玻璃基板上鍍覆氮化矽 (SiN<sub>x</sub>)薄膜,接著沈積一層 1000Å 非晶矽,另外準備一片壓印板,在壓印板上鍍覆上 500Å 的 Ni,再將 Ni 圖形化接著進行壓印退火的動作,結果發現在 550℃ 的退火溫度下,其結晶速率可以達到 8  $\mu$  m/hr,這比一般的 NILC 結晶速率快上 2 倍以上。文獻中提到當壓印退火後會有大量的鎳轉移至結晶薄膜上,這將會造成嚴重的鎳污染。另一篇的文獻報導[43],壓印技術能有效的減少 NILC 的成核時間,這是由於壓印造成膜中存在著拉應力的關係。以及第一章所提及在2003 年由 Choi 等人[35]提出加大 NILC 晶粒的方法,將非晶矽薄膜鍍覆在二氧化矽基材上接著將氮化矽 (SiN<sub>x</sub>)薄膜沈積在非晶矽薄膜上,再用濺鍍的方式鍍覆 0.5nm Ni 膜在 SiNx 上,最後將此試片在快速退火爐(RTA)中進行退火,得到的平均晶粒尺寸為 20~90  $\mu$  m 的晶粒。文獻中提到利用 SiN<sub>x</sub> 薄膜當作過濾器(filter)能有效的過濾鎳原子的數目,而控制 Ni 在非晶矽中的濃度,進而減少鎳誘發結晶的成核點,因而得到較大尺寸的鎳誘發結晶的農粒。

由以上文獻的研究,我們發展出將鎳鍍覆在矽晶圓的背面,並在矽晶圓正面利用黃光微影蝕刻出一圖形,將此晶圓當做壓印以及過濾基板。如此,則可兼顧壓印技術成長較快且能定位成核點以及過濾基板技術降低鎳濃度兩者的優點。另外我們使用(110)的晶圓,因為先前文獻指出 NILC 成長機制中,c-Si 的優選軸向為<110>。故希望以(110)的矽晶圓當做壓印基版能在 NILC 成長時產生磊晶的效果,得到優選方向更佳的結晶。

圖 2-1 壓印技術流程圖

## 2.2 實驗步驟

首先將分別說明沉積非晶矽基板與過濾基板之流程,再來介紹如何利用晶圓接合技術(Wafer Bonding)製備 NILC 複晶矽薄膜,並對不同參數之過濾基板所製備薄膜做各種材料分析。

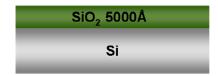

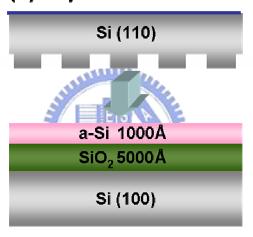

## 2.2.1 非晶矽基板製備

先介紹此實驗試片的製備。首先在(100)的四吋矽晶圓上利用濕式氧化成長  $5000\text{\AA}$  的  $SiO_2$  層(圖 2-2 a),此步驟是為了要模擬 TFT 的玻璃基板。在成長氧化層之前,用傳統的 RCA clean 清洗矽晶圓,其流程如下:

表 2-1 RCA clean

| 去離子水沖洗五分鐘                               |

|-----------------------------------------|

| 硫酸:雙氧水 = 3:1 (75~85℃) 10~15 分鐘          |

| 去離子水沖洗五分鐘                               |

| 氰氟酸:去離子水 = 1:100 (dip 15 秒)             |

| 去離子水沖洗五分鐘                               |

| 氨水:雙氧水:去離子水 = 1/4:1:5 (75~85℃) 10~15 分鐘 |

| 去離子水沖洗五分鐘                               |

| 鹽酸:雙氧水:去離子水 = 6:1:1 (75~85℃) 10~15 分鐘   |

| 去離子水沖洗五分鐘                               |

| 氰氟酸:去離子水 = 1:100 (dip 15 秒)             |

| 氮氣吹乾                                    |

而在成長完氧化層之後,利用低壓化學沉積系 (LPVCD),成長  $1000\,\text{Å}$  的非晶矽(圖  $2\text{-}2\,\text{b}$ ),其 LPCVD 的參數如表  $2\text{-}2\,\text{o}$

表 2-2 LPCVD 沉積非晶矽的參數

| - |                  |       |         |        |

|---|------------------|-------|---------|--------|

|   | 通入氣體             | 操作温度  | 壓力      | 流量     |

|   |                  | (℃)   | (mtorr) | (sccm) |

|   | SiH <sub>4</sub> | 550°C | 100     | 40     |

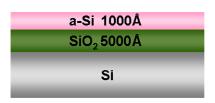

## 2.2.2 過濾基板製備

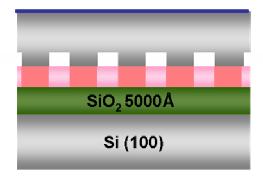

在(110)的四吋矽晶圓正面(拋光面)成長 5000Å 的  $SiO_2$ ,當作蝕刻阻障層(圖 2-3 a),再利用黃光微影定義出圖形。用 BOE 蝕刻  $SiO_2$ 層,然後用DI water 清洗五分鐘。在 Hot Plate 上將 KOH 溶液加熱至  $75^{\circ}$ C,再將晶圓浸置 KOH 溶液中將矽蝕刻 30 分鐘。用 DI water 沖洗,再用 BOE 將剩餘  $SiO_2$ 層移除,得到圖形化的矽晶圓(圖 2-3 b)。最後用氮氣槍將試片吹乾。將此蝕刻出圖形的試片利用 E-gun 在試片正或反面鍍覆 3 或 20Å 的鎳(圖 2-3 c),如表 2-3 所示。

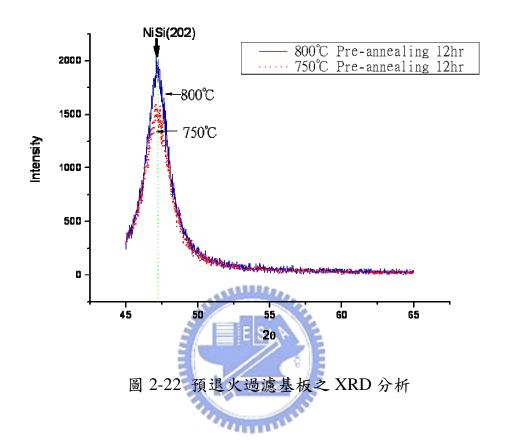

NILC 的鎳濃度取決於鍍覆鎳的厚度,但由於 E-gun 所能精準鍍覆的鎳厚度到了 3Å 已經不準確,且要再鍍覆更薄的厚度相當的困難,因此本研究提出了預退火(Pre-annealing)的方法。先前相關的研究文獻[19][44][45][46]指出,鎳薄膜與單晶矽加熱至 450°C 時形成 NiSi。而 NiSi 的熱穩定度範圍約在 450~750°C,當加入至約 800°C 時才會形成 NiSi<sub>2</sub>。

既然鎳鍍覆的厚度已經不能再減少,因此利用預退火的方式,將鍍覆鎳的試片置入高溫退火爐管中,在  $N_2$  氣氛下, $750^{\circ}$ C 退火 12 小時。藉此預退火的處理,讓鎳薄膜與矽晶圓反應形成 NiSi,消耗鎳的含量,讓後續進行 NILC 時鎳的濃度能夠降低。並且製作另一組試片,在一同樣(110)的矽晶圓背面鍍覆  $3\mathring{A}$  的鎳,預退火至  $800^{\circ}$ C,再進行 NILC 的步驟,驗證在預退火  $750^{\circ}$ C 與  $800^{\circ}$ C下的差別。

(a)

(b)

圖 2-2 非晶矽基板製備

圖 2-3 過濾基板製備

## 2.2.3 過濾基板與非晶矽基板接和步驟

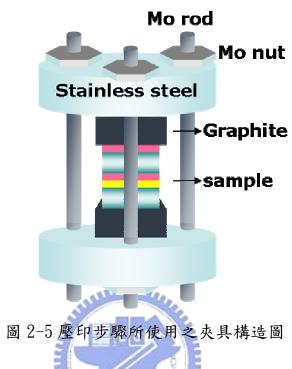

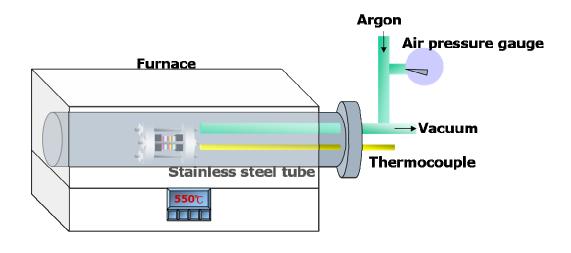

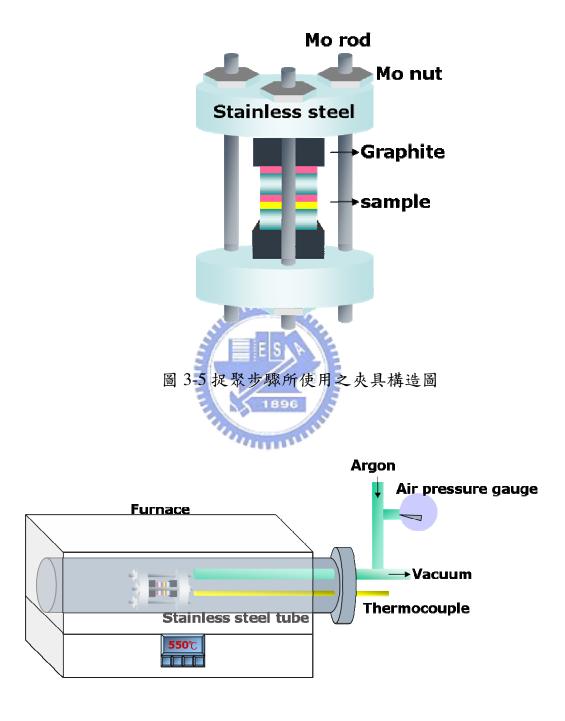

將欲接合的非晶矽基板與過濾基板兩試片使用稀釋的氫氟酸清洗,再用 DI water 沖洗,最後進行加壓退火的動作(圖 2-4 a、b)。加壓的工具如圖 2-5 所示是利用不銹鋼片和鉬螺帽、鉬螺棒所組合之夾具,在加熱時利用他們的熱膨脹係數不同(不銹鋼的熱膨脹係數大於鉬螺帽、鉬螺棒),所以在加熱後會對試片進行加壓的動作。在兩片試片上墊有石墨墊片是為了避免試片與不銹鋼直接接觸而受污染。最後將試片放入不鏽鋼製真空爐管(圖 2-5)中,並在 Ar 氣氛下退火,退火溫度為 550℃。

# (a) imprint

# (b) annealing

圖 2-4 (a) 將兩片晶圓做壓印的動作 (b) 放至爐管中進行退火

圖 2-6 真空爐管示意圖

## 2.3 結果與討論

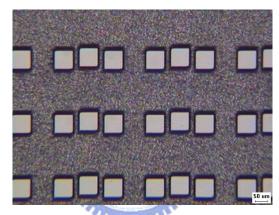

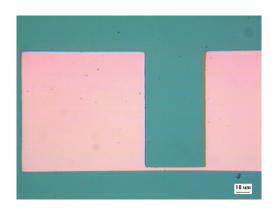

如圖 2-4 之實驗流程,在過濾基板蝕刻出如圖 2-7 圖形,然後進行過濾基板誘發結晶的實驗。第一步將與先前研究[47]中未使用預退火步驟來進行過濾基板誘發結晶的結果做比較,來驗證預退火步驟對於降低鎳濃度的效果。然後再比較在過濾基板正面及背面分別鍍覆 20 或 3Å 鎳的四組試片(表 2-3)並進行誘發結晶後的結果。利用光學顯微鏡(OM)來觀察其結晶大小及結晶狀況;二次電子顯微鏡(SEM)觀察結晶的微結構,而試片在 SEM 觀察前需先進行 Secco etching 處理。因為 Secco etching 溶液能蝕刻非晶矽以及 NiSi<sub>2</sub>,可以幫助觀察結晶形貌與鎳在晶界聚集的情形。

圖 2-7 蝕刻圖形後過濾基板之 OM 圖

表 2-3 四種試片參數設定

|       | 鍍覆正面 | 鍍覆背面 |

|-------|------|------|

| 鎳 20Å | F20  | B20  |

| 鎳 3Å  | F03  | В03  |

## 2.3.1 預退火步驟對鎳含量之影響

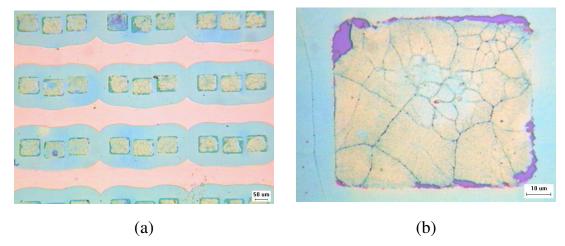

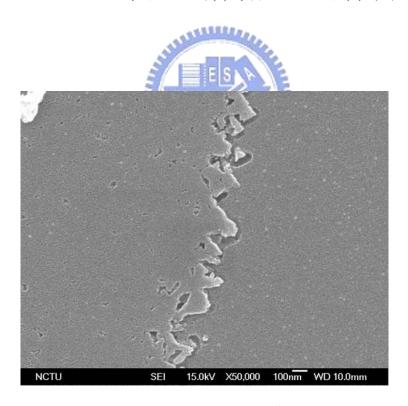

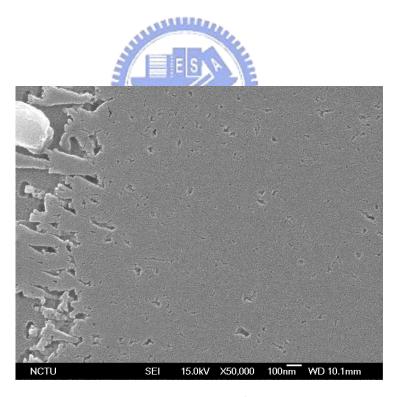

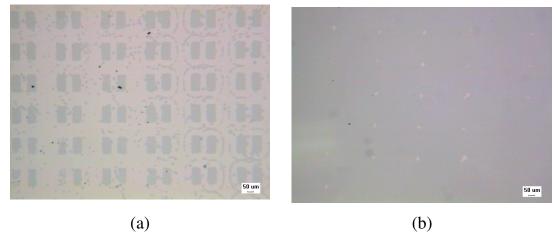

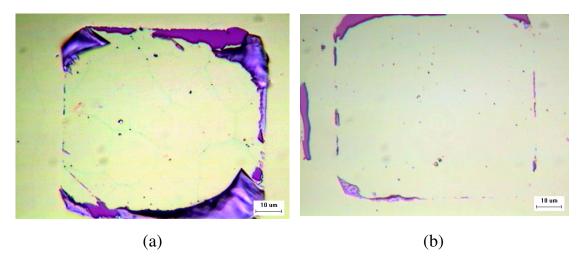

圖 2-8 是 B20 的試片在 550 ℃下直接接合退火 12 小時的 OM 照片,試片有經過 Secco etching 處理,由圖 2-8 (a) 可發現有部份薄膜剝落的情形,這可能是因為退火過程中在過濾基板與非晶矽基板介面,Ni 與 Si 反應形成強的鍵結,因此在分開試片時造成膜的剝離。而在之前的研究中[47]指出,從 OM 照片中可以發現鎳在晶界聚集的現象,如圖 2-9(b)中的黑點。此黑點在 SEM 觀察(圖 2-10)下發現是由過多的 NiSi₂聚集在晶粒的邊界處,而後被 Secco etching solution 所蝕刻遺留下的孔洞所造成。這證明了鎳的含量的確 過多。所以為了減少鎳濃度我們利用預退火的方法以便在誘發結晶前,先一步降低鎳含量,讓後續接和的退火過程中,擴散至非晶矽層之鎳減少而降低鎳污染。由圖 2-8 與 2-9 比較,可以明顯發現有經過預退火步驟之試片,其誘發結晶之晶粒明顯較無預退火步驟之晶粒大上數倍,意即結晶成核時的成核點數量較少,所以可以成長至較大晶粒半徑。且發現有預退火的試片在晶界上只有少數 NiSi₂所造成之孔洞,與無預退火的試片相比,鎳的含量確實的降低,證明了預退火步驟的確能減少鎳在非晶矽薄膜中造成的汗染。

圖 2-8 B20 的試片退火 12 小時的 OM 圖(有預退火) (a)誘發結晶區域 (b) 局部放大圖

圖 2-9 B20 的試片退火 12 小時的 OM 圖(無預退火) (a)誘發結晶區域 (b) 局部放大圖[47]

圖 2-10 B20 的試片退火 12 小時 (無預退火)的 SEM 影像[47]

## 2.3.2 預退火溫度選擇

由於先前文獻對於鎮薄膜與矽晶圓形成 NiSi₂之溫度範圍略有差異,約在 700~800℃之間。為了大致確定我們預退火溫度設定為 750℃是適合溫度,另外製備一組背面鍍鎳 3Å,預退火溫度為 800℃的試片,與一蝕刻出主動層圖形的非晶矽基板接合(圖 2-11)並在 550℃下退火 3 小時。其結果如圖 2-12 所示。可以發現非晶矽層並未出現如先前實驗結果般的 NILC 誘發結晶晶粒。因此可以推斷在 800℃的預退火溫度下,原本鍍覆在矽晶圓背面的鎳薄膜已經與矽完全反應形成 NiSi₂。故在後續 550℃下退火時已經沒有鎳擴散過過濾基板而到達非晶矽層形成誘發結晶。因此要減少鎳含量而進行預退火時,其退火溫度不可高於 800℃以免鎳薄膜與矽晶圓完全反應而無法誘發非晶矽層結晶。

## imprint

圖 2-11 預退火溫度 800℃之過濾基板接合

圖 2-12 無誘發結晶之非晶矽層 OM 影像

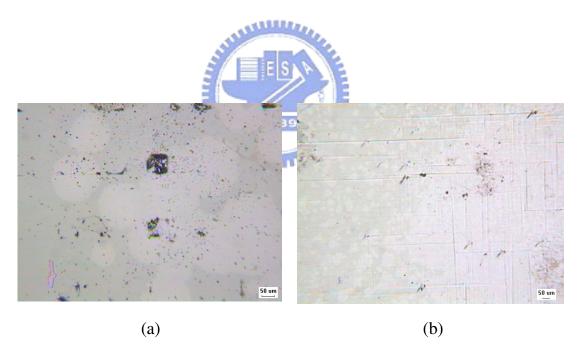

#### 2.3.3 鎳鍍覆厚度以及鍍覆面之差異

前一段實驗以背面鍍鎳 20Å 的試片來證明使用預退火步驟的確能減少 鎮含量,而在本段將討論鍍覆 20 或 3Å 厚度以及鎳鍍覆在過濾基板正面或 背面來進行誘發結晶後的差異性。以下四組試片皆在 550 ℃下直接接合退 火3小時。

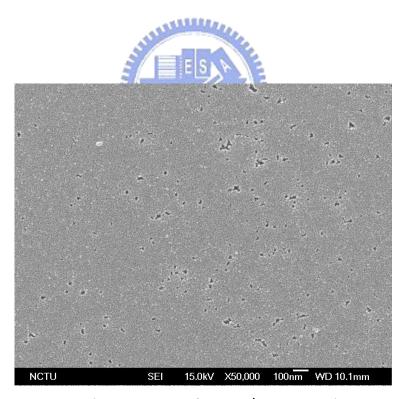

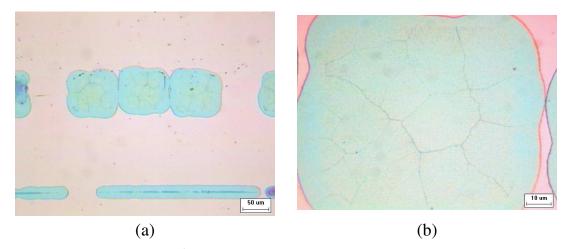

圖 2-13 為試片 F20 的 OM 影像。從圖 2-13(b)中可以發現,誘發結晶之晶粒數目多而且尺寸很小,直徑皆在 5μm 以下。鎳要成核形成 NiSi<sub>2</sub> 來誘發結晶的條件是鎳需要達到 10<sup>13~14</sup>atoms/cm² 的濃度。所以形成之成核點越多,代表擴散至非晶矽層中的鎳濃度越高。而過多之成核點會導致晶粒在成長時會與其他晶粒互相抑制,在晶粒與晶粒間形成晶界而無法成長為大尺寸的晶粒。圖 2-14 為試片 F20 的 SEM 下的微結構。

圖 2-15 為試片 B20 的 OM 影像。與圖 2-13 比較,試片 B20 的晶粒數目較少且尺寸較大,代表擴散至非晶矽層中的鎳濃度較低。因為鎳鍍覆在矽晶圓背面,在預退火過程先形成 NiSi, 然後在接和退火誘發結晶時由於鎳要從 NiSi 相擴散過基板至非晶矽層,所以速率較慢;而鎳鍍覆在矽晶圓正面與非晶矽直接接觸,無須擴散過基板,因此鎳濃度會比鍍覆在背面的高。圖 2-16 為試片 B20 的 SEM 下的微結構。

圖 2-17 為試片 F03 的 OM 影像。與試片 F20 相比雖然鎳同樣鍍覆在正面,但由於試片 F03 鍍覆的鎳厚度只有 3Å,小於試片 F20 的 20Å,所以非晶矽聚集成核的鎳濃度較低,因此可以發現晶粒尺寸較大,直徑約在10μm。不過鎳鍍覆在正面所誘發結晶的鎳仍然會過多而聚集在晶界處,如圖 2-18 的 SEM 圖中的孔洞即為 NiSi₂聚集後而被蝕刻所致。

圖 2-19 為試片 B03 的 OM 影像。可以明顯看到其晶粒尺寸為四組試片中最大,平均直徑在 25μm 以上。證明將鎳鍍覆在晶圓背面並減少鍍覆厚度確實可以減少鎳的濃度,使得成核點減少而能成長至大晶粒尺寸。則後續元件製作時通道部份可以完全在單一晶粒中而避開晶界缺陷的影響,對於提升電性有很大的助益。

圖 2-13 F20 退火 3 小時的 OM 圖(a)誘發結晶區域 (b)局部放大圖

圖 2-14 F20 退火 3 小時的 SEM 圖

圖 2-15 B20 退火 3 小時的 OM 圖(a)誘發結晶區域 (b)局部放大圖

圖 2-16 B20 退火 3 小時的 SEM 圖

圖 2-17 F03 退火 3 小時的 OM 圖(a)誘發結晶區域 (b)局部放大圖

圖 2-18 F03 退火 3 小時的 SEM 圖

圖 2-19 B03 退火 3 小時的 OM 圖(a)誘發結晶區域 (b)局部放大圖

圖 2-20 B03 退火 3 小時的 SEM 圖

#### 2.3.4 預退火過濾基板誘發結晶機制探討

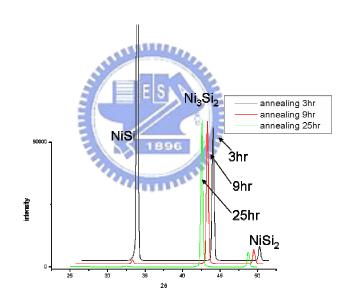

在 2003 年由 Choi 提出利用 SiNx 當 filter 進行誘發結晶的機制[35],其 中提到在 850°C 時 Ni 在 SiN<sub>x</sub> 中的擴散係數約  $4.4 \times 10^{-12}$  cm<sup>2</sup>/s, 與在 450°C 時 Ni 在非晶矽中的擴散係數差不多。所以 SiNx 可以當作一個很好的擴散阻障 層,而因此可以控制 Ni 在 a-Si 上的成核數目,以得到較大的結晶晶粒。而 我們研究中是利用矽晶圓當 filter, Ni 在 550℃ 時, 在矽晶圓中的擴散係數 是 2.66×10<sup>-6</sup>, 遠大於 SiN<sub>x</sub>, 因此 Ni 的擴散是非常快的。矽晶圓本身也會和 Ni 反應形成其他的金屬矽化物的相[46],之前的研究已經有針對矽晶圓過 濾基板在接合退火分開後,用 X-ray 來分析過濾基板表面的金屬矽化物相, 結果如圖 2-21[47]所示。Ni 在退火過程中的確會跟 c-Si 反應,因此也會過 瀘掉一些 Ni,但是過濾的量仍然不足,因此加上預退火的步驟,將過濾基 板在接合前預先退火至 750℃,使鎳與矽晶圓形成穩定的 NiSi 相,讓由過 濾基板擴散至非晶矽的鎳濃度更低。我們也發現若是預退火溫度提高至800 ℃時,就無法形成誘發結晶。於是將預退火750℃以及800℃的過濾基板利 用 X-ray 分析其表面金屬矽化物相, 結果如圖 2-22 所示。從圖中可看出隨 著溫度由 750℃升高至 800℃, 其 NiSi (202)的 峯值由 1500 提升到 2000,代 表更多的鎳形成 NiSi 相以至於沒有足夠的鎳擴散至非晶矽層,所以無法成 核而誘發結晶。

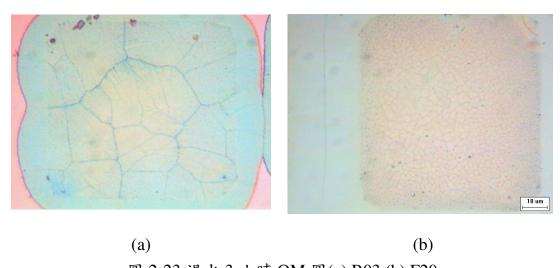

而從 B03(3Å 鎳鍍覆在過濾基板背面)與 F20 (20Å 鎳鍍覆在過濾基板正面) 做比較,圖 2-23,B03 擁有明顯較大的晶粒。由 Ni 在單晶矽中的擴散係數 如下式:

$$D_{c-Si} = 2 \times 10^{-3} \times e^{-0.47ev/kT} \text{ cm}^2/\text{s}$$

(3)

$k : 8.625 \times 10^{-5}$  ev/k

在  $550^{\circ}$ C下, $D_{c-Si}$ = ~2.66×10<sup>-6</sup> cm<sup>2</sup>/s ,而單晶矽厚度約  $525\,\mu$  m,而擴散距離 L=(Dt)<sup>1/2</sup> ,將 L和 D 代入後得到時間約 17 分鐘,所以 Ni 在  $550^{\circ}$ C下,只需 17 分鐘即可擴散到非晶矽表面,這表示 Ni 在單晶矽中的擴散速率是非常快的,因此 F20 與 B03 同樣退火 3 小時下,試片 D 需 17 分鐘的時間來擴散過基板到達非晶矽層,而 F20 則不需要。但這個原因還不至於造成晶粒尺寸上如此大的差異,推測應該是預退火過程中,B03 大部分

的鎮在矽晶圓背面形成穩定的 NiSi 相,故接合退火過程中能擴散至非晶矽的鎮大量減少。而 F20 則是在矽晶圓正面形成 NiSi 化合物,在接合時 NiSi 直接與非晶矽層接觸,此時的鎳因為與非晶矽形成 NiSi<sub>2</sub>相可降低熱力學中的自由能之故,便大量的擴散至非晶矽層中,而只能成長至小晶粒尺寸。

圖 2-21 Ni 與矽晶圓在 550℃ 時反應形成的相

圖 2-23 退火 3 小時 OM 圖(a) B03 (b) F20

#### 2.4 結論

提出利用預退火的步驟使得鍍覆在(110)過濾基板的鎳與矽晶圓形成 NiSi 相,以降低鎳濃度的研究已經可以得到 25µm 的大尺寸晶粒,從 OM 以及 SEM 影像可以證實其聚集在晶界的 NiSi2數量較無預退火處理的試片來的少。經由控制在適當預退火溫度並將鎳鍍覆在過濾基板背面即可抑制成核數目而得到大尺寸晶粒。

另外,由於預退火會讓鎳與矽形成穩定的 NiSi 相而消耗鎳含量,若將預退火溫度升高至 800℃則會消耗過多的鎳而導致鎳濃度不夠聚集成核來誘發結晶。因此將預退火溫度設定在 750℃下,並將鎳鍍覆背面可以成功將鎳濃度控制在可形成 NILC 的下限,降低鎳的汙染。

# 第三章 利用晶圓接合技術之捉聚基板研究

# 3.1 简介

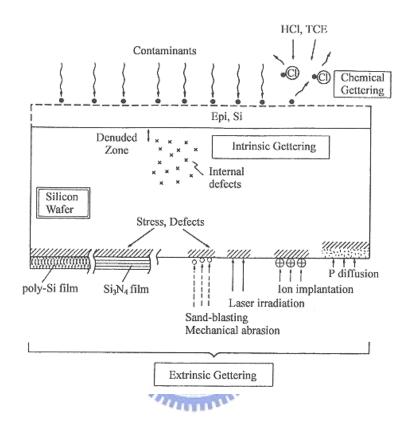

在晶圓製程階段,由於成長環境的雜質污染及熱應力造成之缺陷均留於晶圓當中,且無可避免的會引入第三類過渡金屬原子(鉬、鐵、銅、鎳等),這些金屬原子在矽中均屬快速擴散源,其高擴散性會更進一步的減損元件特性,同時後續之加工所造成之缺陷亦存於其中,在 IC 製造過程中,這些缺陷均會影響元件之良率及電性品質。這些金屬雜質會在 MOS 結構的 Gate Oxide 中成為矽化物析出,導致電性崩潰,且在半導體中產生的能隙深層能階(deep levels in the band gap)會強烈的影響少數載子(minority carrier)的壽命。金屬雜質的濃度上限主要是由元件尺寸所決定,目前一般是 1×10<sup>10</sup>atoms/cm³ 或更低。於主動元件區域要達到此污染等級,需使用到捉聚(gettering)步驟,讓晶圓部分區域的金屬原子能移除到其他預先決定的區域,降低這些金屬原子造成的傷害[48]。

一般捉聚技術包含內部捉聚法(internal gettering)、化學捉聚法(Chemical gettering),以及外部捉聚法(external gettering) [49],如圖 3-1 所示 [52]。外部捉聚法包括在晶圓背面施以一層複晶矽或鋁矽合金,磷擴散捉聚 (phosphorus-diffusion gettering),以及由氦或氫原子植入所造成的奈米級空隙進行捉聚[50]。這些方法所連帶的不同物理機制導致下述的分類:鬆弛 (relaxation)、分離 (segregation)、或注入誘發的捉聚 (injection induced gettering)[51]。

雖然捉聚應用在處理矽晶圓上已經有相當深入的研究,但對於薄膜電晶體方面則是尚未有太多的資料。目前只有夏普的 CGS 技術,利用離子植入將磷離子植入主動層中通道區域的兩端,在退火過程因為植入磷離子區域有缺陷的出現,造成此區域的金屬雜質溶解度提高而將通道區域的金屬雜質吸附到離子植入區,達到捉聚的效果。但是 CGS 技術需要增加一道黃光、離子植入、退火以及三道蝕刻製程,在整體的生產成本與時間都提高為其最大缺點。

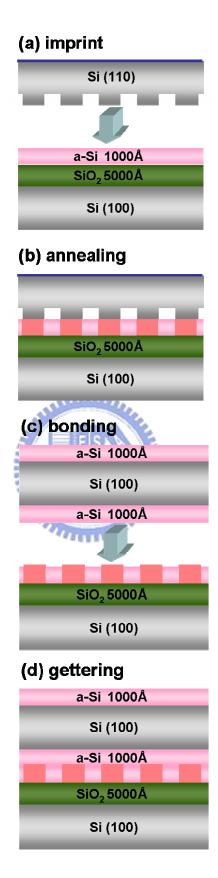

本研究利用晶圓接合技術將鍍覆非晶矽的晶圓做為捉聚基板與金屬 誘發側向結晶的複晶矽接合,由於兩者鎳含量之差異以及熱力學上的因 素,成功的把殘餘鎳捕捉至基板,顯著的降低了複晶矽中鎳含量。

圖 3-1 (1)內部捉聚法(Intrinsic Gettering) (2)外部捉聚法(Extrinsic Gettering) (3)化學捉聚法(Chemical Gettering) [52]

# 3.2 實驗步驟

首先將分別說明沉積非晶矽基板與捕捉基板之流程,再來介紹如何利用晶圓接合技術(Wafer Bonding)捉聚 NILC 複晶矽薄膜中殘留的鎳雜質,對照捉聚前後複晶矽薄膜的表面形貌與鎳含量,並對沉積不同材料之捕捉基板所捉聚後的薄膜做各種材料分析。

# 3.2.1 複晶矽薄膜製備

先介紹此實驗試片的製備。首先在(100)的四吋矽晶圓上利用濕式氧化成長5000Å的 $SiO_2$ 層,此步驟是為了要模擬TFT的玻璃基板,在成長氧化層之前,用傳統的RCA clean 清洗矽晶圓,其流程如下:

表 3-1 RCA clean

| 去離子水沖洗五分鐘                               |

|-----------------------------------------|

| 硫酸:雙氧水 = 3:1 (75~85℃) 10~15 分鐘          |

| 去離子水沖洗五分鐘                               |

| 氰氟酸:去離子水 = 1:100 (dip 15 秒)             |

| 去離子水沖洗五分鐘                               |

| 氨水:雙氧水:去離子水 = 1/4:1:5 (75~85℃) 10~15 分鐘 |

| 去離子水沖洗五分鐘                               |

| 鹽酸:雙氧水:去離子水 =6:1:1 (75~85℃) 10~15 分鐘    |

| 去離子水沖洗五分鐘                               |

| 氰氟酸:去離子水 = 1:100 (dip 15 秒)             |

| 氮氣吹乾                                    |

而在成長完氧化層之後,利用低壓化學沉積系(LPVCD),成長 1000 Å 的非晶矽,其 LPCVD 的參數如表 3-2。

表 3-2 LPCVD 沉積非晶矽的參數

| 通入氣體             | 操作溫度          | 壓力      | 流量     |

|------------------|---------------|---------|--------|

|                  | $(^{\circ}C)$ | (mtorr) | (sccm) |

| SiH <sub>4</sub> | <b>550</b> ℃  | 100     | 40     |

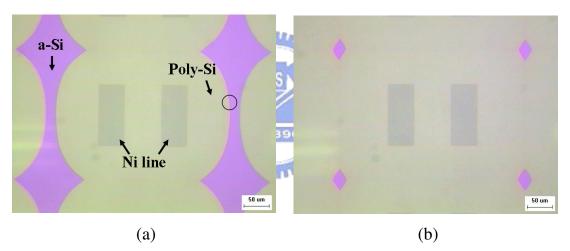

接著利用黃光微影在非晶矽層上定義一條狀圖形,並用 E-gun 在試片

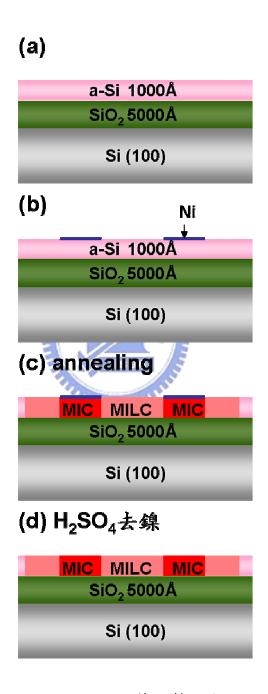

鍍覆  $20\text{\AA}$  的鎮,最後用 Lift-off 將多餘光阻及鎮移除,留下鎮金屬線(Metal line)圖形。然後將試片在高溫退火爐管中,在  $N_2$  氣氛下,550℃退火 24 小時。在誘發結晶後,將試片上殘餘未消耗的鎳用硫酸清洗半小時,流程如圖 3-2 所示。

圖 3-2 複晶矽薄膜製備流程

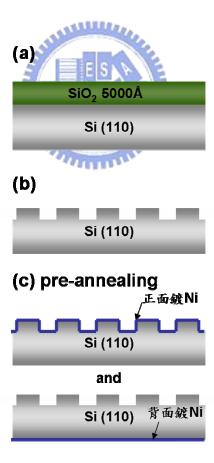

# 3.2.2 捉聚基板製備

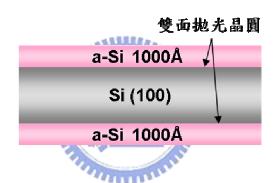

在(100)的四吋矽晶圓正反面(雙面拋光)利用低壓化學沉積系(LPVCD)成長1000Å的非晶矽(圖3-3),其LPCVD的參數如表3-2。使用雙面拋光的晶圓是為了後續用OM以及SEM觀察捕捉基板背面的形貌。因為若使用背面未拋光的晶圓,其表面粗糙度(Sureface Roughness)過大,在OM與SEM下無法分辨出金屬誘發結晶的形貌。

圖 3-3 捉聚基板示意圖

#### 3.2.3 接合捉聚步驟

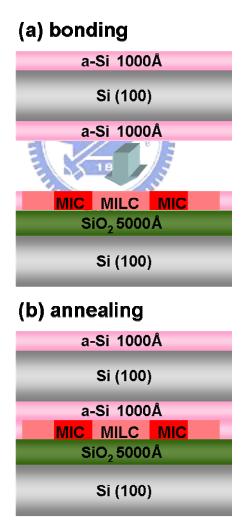

將欲接合的金屬誘發結晶複晶矽薄膜與捉聚基板兩試片使用稀釋的氫氟酸清洗,再用 DI water 沖洗,最後進行加壓退火的動作(圖 3-4 a、b)。加壓的工具如圖 3-5 所示是利用不銹鋼片和鉬螺帽、鉬螺棒所組合之夾具,在加熱時利用他們的熱膨脹係數不同(不銹鋼的熱膨脹係數大於鉬螺帽、鉬螺棒),所以在加熱後會對試片進行加壓的動作。在兩片試片上墊有石墨墊片是為了避免試片與不銹鋼直接接觸而受污染。 最後將試片放入不鏽鋼製真空爐管(圖 3-6)中,並在 Ar 氣氛下,550℃退火 12 小時將複晶矽薄膜中的鎳捕捉至基板中。

圖 3-4(a) 將兩片晶圓做接合的動作 (b) 爐管中進行退火捉聚

圖 3-6 真空爐管示意圖

## 3.2.4 元件製備

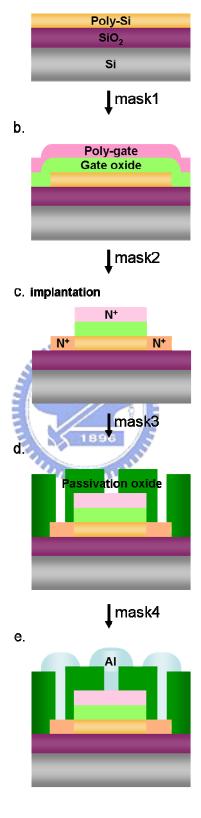

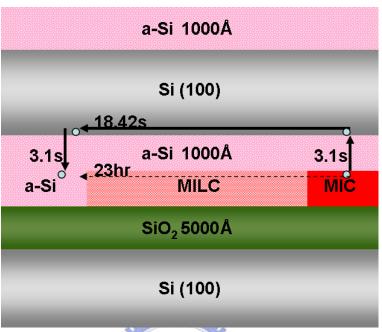

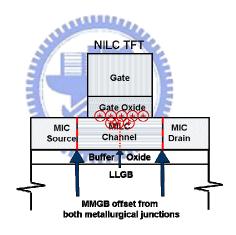

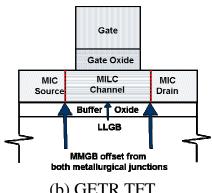

以 NILC POLY 與 GETR POLY 兩組試片做為不同主動層之比較,結構如圖 3-7 所示,製作流程如下:

- 1. 利用黃光微影系統定義出主動層(mask1)

- 2. 使用 Poly-RIE 蝕刻出主動層

- 3. RCA Clean

- 4. 利用 PECVD 沉積一層厚度為 1000Å 的 SiH<sub>4</sub>/N<sub>2</sub>O oxide 作為 gate oxide

- 5. 利用 LPCVD 沉積一層厚度為 2000Å 的 Poly-Si 膜作為 gate

- 6. 利用黃光微影系統定義出 gate(mask2)

- 7. 利用 Poly-RIE 將 Poly-gate 定義出來

- 8. 利用 BOE 將 gate oxide 蝕刻出來

- 9. 離子佈植: PH<sub>3</sub> 能量: 35kev; 濃度: 5×10<sup>15</sup> ions/cm<sup>2</sup>

- 10. activation: 在 600°C 進行 24 小時的活化

- 11. 利用 PECVD 沉積 passivation oxide 5000Å

- 12. 利用黃光微影系統定義出接觸窗(contact hole) (mask3)

- 13. 利用 BOE 將接觸窗蝕刻出來

- 14. 利用 thermal coater 蒸鍍厚度為 5000Å 的 Al 電極

- 15. 利用黃光微影系統定義出 source、 drain 及 gate 的接觸電極(mask4)

- 16. 利用 Al 的蝕刻液進行 source、 drain 及 gate 的 Al 電極蝕刻

- 17. Al sintering :  $400^{\circ}$ C , 30min

- 18. 電性量測

a.

圖 3-7 TFT 元件製程流程圖

#### 3.3 結果與討論

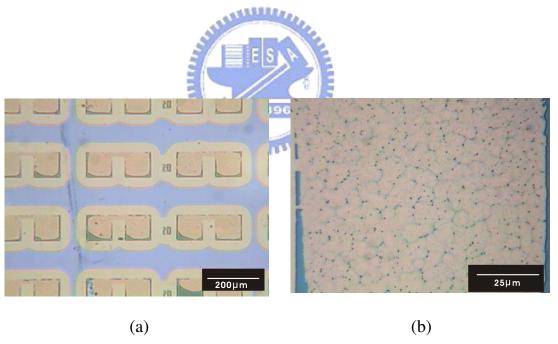

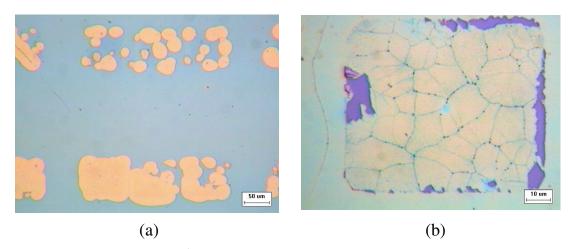

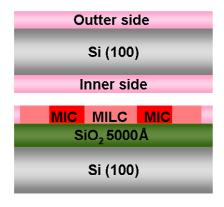

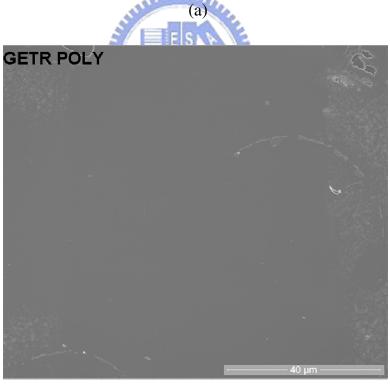

在經過圖 3-2 之實驗流程後,然後將試片分為兩組:第一組 NILC POLY 是未經捉聚步驟的複晶矽薄膜試片,但除了退火 24 小時外,在去除鎳後,另外後在 550℃後退火(Post annealing)12 小時,得到如圖 3-8a 之金屬誘發結晶。後退火的原因是為了讓總退火時間與第二組試片相同,皆為 24+12=36 小時。第二組 GETR POLY 是將退火 24 小時的複晶矽薄膜試片,經由圖 3-4 的步驟退火 12 小時後,將捕捉基板分離所得,如圖 3-8b。而我們將捕捉基板與複晶矽接觸面稱為 Inner side,另一面為 Outer side,圖 3-9。

分析上將利用 OM、SEM、SIMS 與 AFM 觀察量測捉聚前後試片表面 形貌、粗糙度、鎳含量的差異。並比較沉積不同材料之補捉基板、不同捉 聚時間對於捉聚效果的影響。

圖 3-8 (a) NILC POLY (b) GETR POLY

圖 3-9 捉聚基板之 Inner side 與 Outer side

# 3.3.1 捉聚步驟對於鎳含量之影響

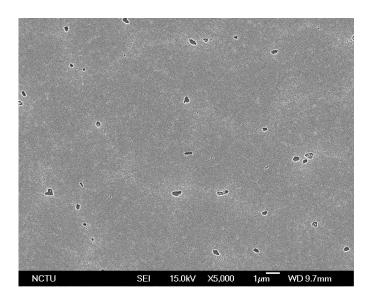

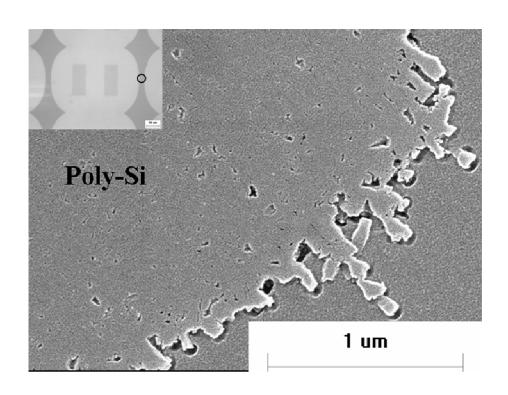

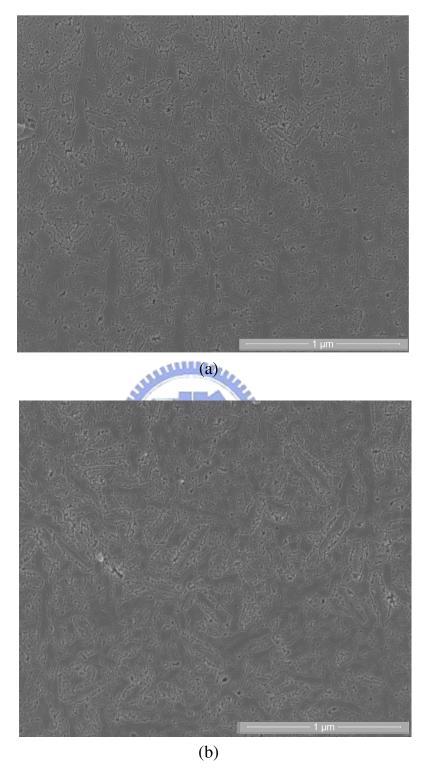

圖 3-10 左上角為鎳金屬線誘發結晶之 NILC POLY 的光學顯微鏡(OM) 影像。在鎳金屬線周圍的白色區域為誘發結晶之複晶矽,而黑色區域為非晶矽。然後經由 Secco etching solution 蝕刻掉非晶矽及矽化物區域,利用掃描式電子顯微鏡(SEM)觀察圖 NILC POLY 前端(圈選處),結果如圖 3-10 所示,NILC 是由針狀的矽晶粒所組成。

圖 3-10 NILC POLY 前端的 SEM 影像(Secco etching 處理後)

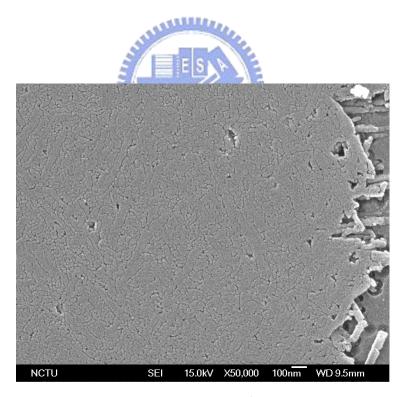

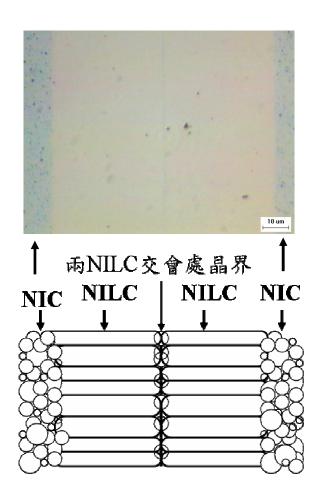

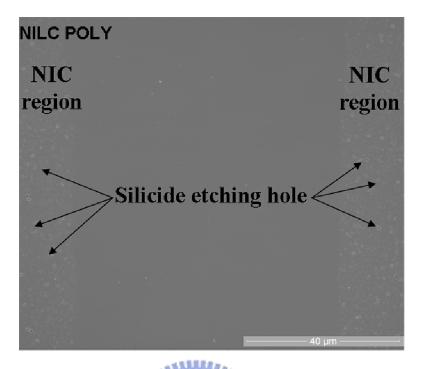

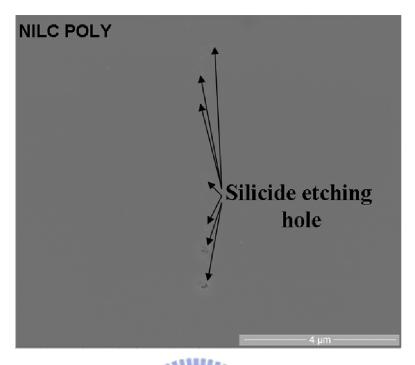

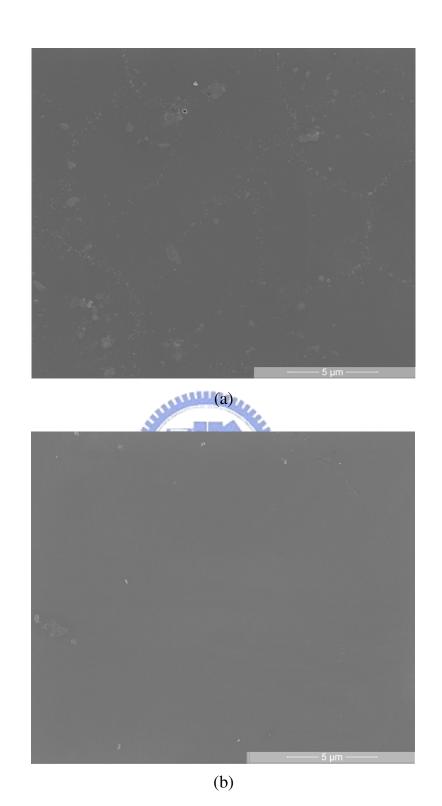

將試片經由矽化物蝕刻溶液(HNO3:NH4F:H2O = 4:1:50)處理後,將會在NIC 區域以及兩 NILC POLY 前端交會處所形成的晶界發現大量的孔洞,其示意圖如圖 3-11 所示。這些孔洞是由殘留在複晶矽內之鎳矽化物(NiSi2)被矽化物蝕刻溶液蝕刻移除後所造成。由於此溶液只會蝕刻矽化物而不會蝕刻非晶矽,故孔洞數目的多寡與複晶矽內鎳之殘餘量有強烈的關係。經由比較 NILC POLY 與 GETR POLY 兩組試片的 SEM 影像可以發現,在 GETR POLY 所觀察到的 NIC 區域矽化物孔洞數目,圖 3-12(b),明顯較 NILC POLY 試片來的少,圖 3-12(a);兩 NILC POLY 前端交會處晶界也沒有發現孔洞,圖 3-13(b)。而 NILC POLY 則有明顯孔洞所形成的晶界,圖 3-13(a)。由此可以證實經過鎳捉聚(Ni-gettering)步驟的 GETR POLY 鎳殘餘量確實降低,而減少的鎳可能都擴散至鎳捕捉基板中。

圖 3-11 NIC&NILC 示意圖

(b) 圖 3-12 (a)NILC (b) GETR POLY 之 NIC 區域矽化物孔洞

(b) 圖 3-13 (a)NILC (b) GETR POLY 之晶界矽化物孔洞

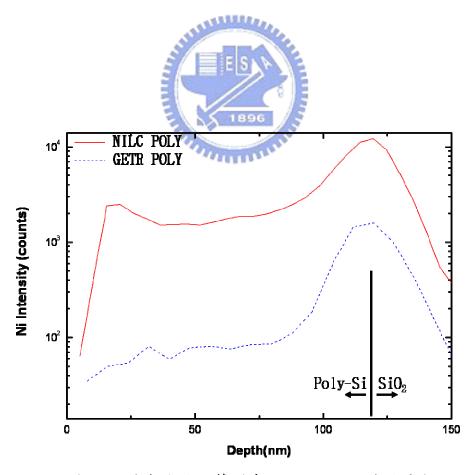

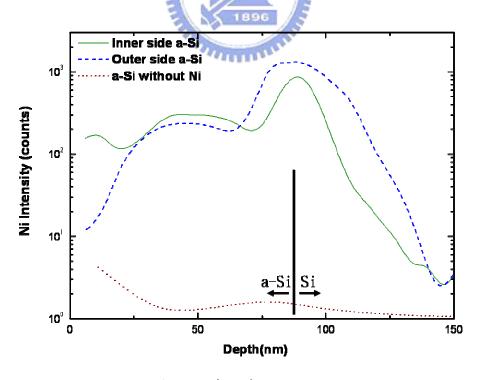

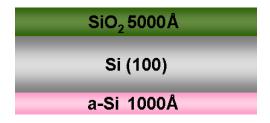

更進一步利用二次離子質譜儀(SIMS)量測複晶矽薄膜內的鎳殘餘量。我們選擇使用 TOF-SIMS(Time-of-Flight-SIMS),因為複晶矽中的鎳濃度相當低,儀器的偵測極限(detection limit)需要在 ppm 以下。一般 AES 與 ESCA的偵測極限約在 0.1~5%,無法偵測到精確的鎳含量。而 SIMS 之偵測極限在 ppm~ppb(10<sup>12</sup>~10<sup>16</sup>atoms/cm³),故在分析 MILC 時皆使用 SIMS 作為縱深分析儀器。如圖 3-14 所示,在 GETR POLY 所量測到的鎳濃度只有 NILC POLY 中的十分之一以下。這再次證明了鎳的確已經擴散至捉聚基板中,使得原本複晶矽薄膜中的鎳殘餘量降低。可以發現在 Poly-Si 與 SiO<sub>2</sub> 界面處鎳的濃度特別高,這是因為界面處的缺陷很容易陷捕 NiSi<sub>2</sub>之故。

圖 3-14 鎳在複晶矽薄膜中之 SIMS 縱深成份分析

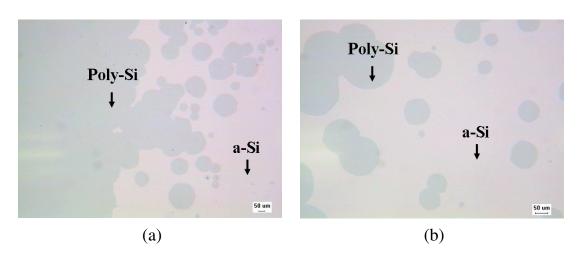

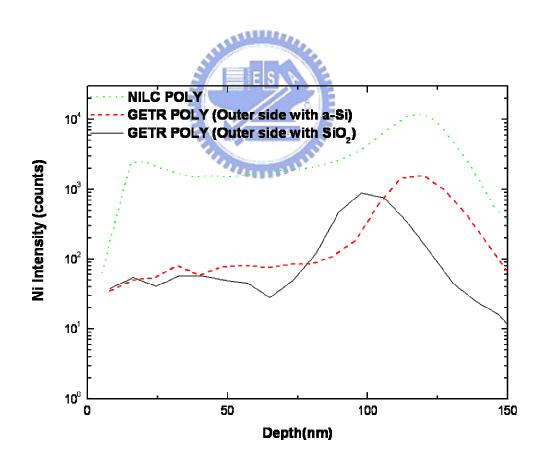

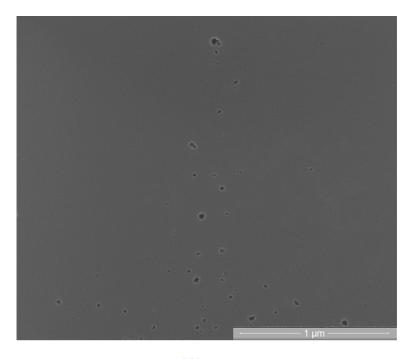

為了確認鎳已擴散至捕捉基板,我們觀察捉聚基板之 Inner side 與 Outer side。從 OM 影像可以發現捕捉基板兩面之非晶矽層已大部分變成複晶矽,如圖 3-15 所示,其中呈碟狀(Disk-like)的區域為金屬誘發結晶的複晶矽。其機制類似於利用矽晶圓當做過濾器(Filter)來誘發結晶,鎳需要擴散過晶圓再聚集成核,由成核點輻射狀向外成長,故會形成為碟狀。再從 SEM 影像發現其複晶矽為針狀結晶,圖 3-16,證明是由鎳誘發之複晶矽結構。故可證明經由 Ni-gettering 步驟後,鎳從複晶矽層擴散至 Inner side 再經過 Si wafer 到達 Outer side。從二次離子質譜儀(SIMS)分別量測 Inner side 與 Outer side 已轉變成複晶矽之非晶矽層中鎳含量(圖 3-17),可以發現與未經誘發結晶之非晶矽相比,其鎳含量已提高,且在非晶矽與矽晶圓的界面,鎳含量也有較高的情況,推測也是因為界面缺陷陷捕 NiSi2之故。另外作為對照的非晶矽中,有微弱的鎳訊號出現,是因為儀器本身的雜訊所影響。由以上分析可確切證實捉聚基板能成功將複晶矽薄膜中的殘餘鎳捕捉出來,降低金屬雜質污染。

圖 3-15 捉聚基板之 OM 影像 (a) Inner side (b) Outer side

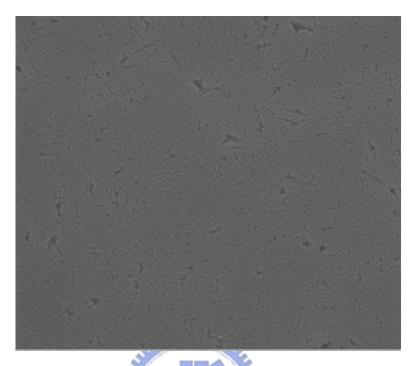

圖 3-16 Outer side 複晶矽區之 SEM 影像(Secco etching 後)

圖 3-17 鎳在捉聚基板中之 SIMS 縱深成份分析

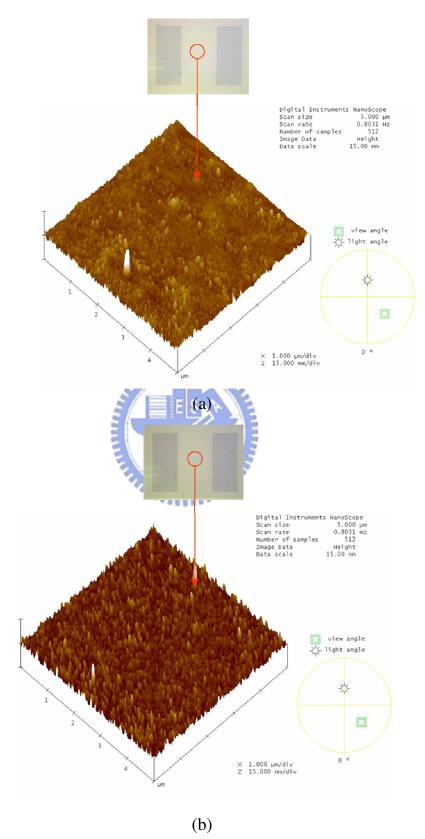

在複晶矽與閘極氧化層間的界面性質也是影響電晶體特性的重要因 素,其中表面粗糙度對漏電流的影響成正相關。一般以矽甲烷為主的氧化 層粗糙度約為 2nm,而 TEOS 氧化層則為 0.2~0.4nm,因此閘極氧化層多以 TEOS 為主。而複晶矽的表面粗糙度則會與結晶方式不同而有相當大的差 異。以 ELA 法製備的複晶矽表面粗糙度會與結晶能量及晶粒大小有很大的 關係。因為在雷射退火時,融熔矽的密度為 2.53g/cm3 大於固態矽的 2.3g/cm3, 當雷射照射, 從晶核向外成長為晶粒, 固化後的矽因為密度小體 積大,多餘的體積會推擠到未固化的融熔矽區域,而複晶矽晶界是最後固 化的地方,因此兩晶粒擠壓而在晶界形成突起,此時在三顆晶粒交會處的 有一更高聳的尖端。這些都是造成 ELA 複晶矽表面粗糙度高達 6~10 幾 nm 的原因。晶界的突起會使得局部的電場增強而讓崩潰電壓降低、漏電流突 增,也減損了元件的可靠度。而 MILC 複晶矽的表面粗糙度則遠低於 ELA, 約在 1nm 左右。在這裡我們比較 NILC POLY 與 GETR POLY 的表面粗糙 度,研究接合捉聚步驟後將捉聚基板與複晶矽分離,複晶矽的表面粗糙度 是否有所改變,圖 3-18 是經由稀釋的氫氟酸清洗後,利用 AFM 得到的複 晶矽表面形貌,掃描區域為兩 NILC 交會之晶界,因為此區域為元件通道, 對於元件特性影響最大。其表面粗糙度如表 3-3 所示,捉聚步驟前 Rms 為 0.874nm, 在捉聚後小幅上升 0.335 到 1.209nm, 這應該是由於接合時所形 成的矽與矽鍵結在捉聚基板分離時所造成的缺陷所致。但是與 ELA 相比其 表面粗糙度仍然是很低。

表 3-3 捉聚步驟前後表面粗糙度

|                    | NILC POLY | GETR POLY |

|--------------------|-----------|-----------|

| Rms(nm)            | 0.874     | 1.209     |

| Mean roughness(nm) | 0.622     | 0.910     |

圖 3-18 複晶矽表面之 AFM 影像(a)NILC POLY(b)GETR POLY

## 3.3.2 捉聚退火時間之影響

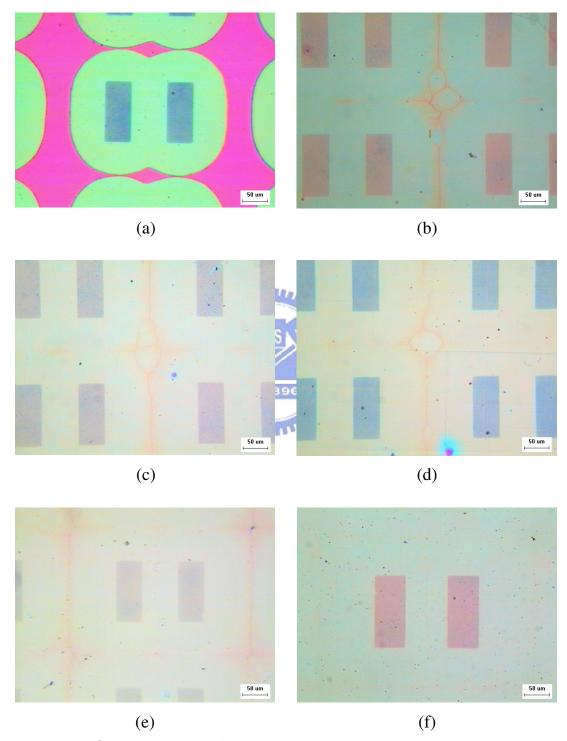

前述之捉聚步驟皆是在 550℃下退火 12 小時所得的結果,這章節將討 論在不同捉聚時間下,複晶矽層與捕捉基板的差異。圖 3-19 為 550℃下退 火 1~18 小時的複晶矽 OM 影像。在圖 3-19(a)退火一小時下,可以發現試片 尚未完全結晶,由鎳金屬線圖形成長出橢圓狀的複晶矽晶粒,兩橢圓狀複 晶矽晶粒相擠壓形成一直線晶界。在圖 3-19(b)退火三小時以上之試片可以 看到,以兩金屬線為一單位,在四個單位所成長之複晶矽晶粒相交會處有 一些小晶粒出現,但是其成核點並沒有鎳鍍覆而誘發結晶,故可推測這是 在與捉聚基板接合時,鎳從複晶矽薄膜擴散至捉聚基板中,在 Inner side 與 Outer side 誘發結晶,因為鎳在矽晶圓中擴散相當快,並且傾向往非晶矽區 擴散,而原本複晶矽晶粒成長時,尚有部分非晶矽區還未結晶,故捉聚基 板中的鎳又擴散回複晶矽薄膜中的非晶矽區域,而鎳在550℃下單晶矽中的 擴散係數為 2.66×10-6cm²/s 遠高於在複晶矽與非晶矽中的擴散係數 3.2×10<sup>-11</sup> cm<sup>2</sup>/s。如圖 3-20 所示, 鎮從 MIC 區域擴散過 1000Å 的 Inner side 非 晶矽只需 3.1 秒就可到達單晶矽晶圓,而在單晶矽中只要 18.42 秒就可以擴 散超過 70μm, 而鎳若要在複晶矽薄膜中從 MIC 區域經過 70μm 的複晶矽 區域是以 MILC 的過程擴散過去,其速率約為 3μm/hr。所以至少要 23 小時 後才能到達,而此時從捉聚基板擴散的鎮早已到達此非晶矽區開始誘發結 晶,所以才會在晶粒交會處發現部分小晶粒出現。

另外在圖 3-21 的 Inner side OM 影像可以看到,在退火 1hr 的試片上產生如同複晶矽晶粒的圖形,因為在接合的過程產生類似壓印的效果,所以在鎳含量最高的 MIC 區域以及 MILC 前端的鎳與捉聚基板的 Inner side 非晶矽誘發結晶,而在退火 3hr 的試片明顯看到幾乎完全結晶,速率較普通 NILC 快上很多,這就是因為前面提及的鎳經由捉聚基板的晶圓部分快速擴散後,在其他非晶矽區誘發結晶之故。

圖 3-19 550℃退火 1~18 小時之複晶矽 OM 影像 (a) 1hr (b) 3hr (c) 6hr (d) 9hr (e) 12hr (f) 18hr

圖 3-20 擴散路徑示意圖

圖 3-21 550℃ 退火後之 Inner side OM 影像 (a) 1hr (b) 3hr

#### 3.3.3 沉積不同捉聚基板薄膜之比較

由前面的 SIMS 研究可以發現,鎳擴散至捉聚基板後,除了在非晶矽層誘發結晶外,還會被非晶矽層與矽晶圓界面缺陷所陷捕。在此界面的鎳濃度明顯較高,顯示其捉聚的效果很好,而我們也發現在複晶矽薄膜與 SiO<sub>2</sub> 界面同樣也有鎳陷捕的效應,因此嘗試將捉聚基板由雙面沉積非晶矽改變為 Outer side 沉積 SiO<sub>2</sub> 而 Inner side 保持非晶矽來進行捉聚步驟,如圖 3-22 所示,研究此結構捉聚的效果。置備步驟是將晶圓在高溫氧化爐管中成長5000Å的氧化層,再將正面之氧化層用 BOE 蝕刻移除後,利用 PECVD 成長 1000Å 的非晶矽層,然後在爐管中 400℃下退火 2 小時進行去氫,因為PECVD 所鍍覆之非晶矽含氫量約在 8%~15%,若無進行去氫的動作則在後續高溫製程下氫氣會使得非晶矽薄膜產生氫爆。

同樣在550℃退火12小時後,利用二次離子質譜儀(SIMS)量測複晶矽薄膜內的鎳殘餘量,其結果如圖3-23所示。利用沉積SiO₂之捉聚基板進行捉聚處理後的複晶矽鎳含量與處理前相比降低了一個數量級以上,甚至較雙面沉積非晶矽的捉聚基板還低,但是其還是可以視做誤差範圍內。優異的捉聚效果可以歸功於矽晶圓的體積較複晶矽薄膜大上5000倍以上,因為矽晶圓厚度約525μm,而複晶矽厚度1000Å,在相同面積下體積比為5250:1。且在非晶矽層與矽晶圓界面、SiO₂層與矽晶圓界面皆可陷捕大量鎳,所以雖然與雙面沉積非晶矽層相比,SiO₂層無法捉聚鎳,但總合捉聚效果並無差異。

圖 3-22 沉積 SiO<sub>2</sub> 之捉聚基板結構圖

圖 3-23 鎳在複晶矽薄膜中之 SIMS 縱深成份分析

## 3.3.4 結合過濾基板與捉聚步驟

第二章中以過濾基板事先減少鎳誘發結晶時擴散至複晶矽薄膜中的鎳含量,而本章節則是以後續的捉聚步驟來減少已經存在於複晶矽薄膜中的鎳含量,因此我們自然會好奇結合兩者之後的效果。同樣的先以背面鍍鎳3Å的過濾基板與非晶矽接合後,在550℃下退火12小時,然後分離過濾基板,再以稀釋的氫氟酸清洗試片,然後再與捉聚基板接合,繼續在550℃下退火12小時,如圖3-24所示。

圖 3-25 為利用矽化物蝕刻溶液後所得之 OM 影像,圖 3-25(a)為單純用 過濾基板退火 12 小時,圖 3-25(b)為後續捉聚 12 小時之 OM 影像。可以發 現圖 3-25(a)有較明顯之晶界,圖 3-25(b)則較為模糊,我們利用 SEM 進一 步觀察可以清楚的看到未經捉聚之試片有矽化物被蝕刻後之孔洞,圖 3-27(a),而捉聚後的試片則幾乎沒有發現孔洞存在,圖 3-26(7)。在放大倍 率下的 SEM,圖 3-28,可以肯定兩者的捉聚前後的效果。

接著觀察捉聚基板之 Inner side 與 Outer side 層,在 OM 同樣可以發現碟狀(Disk-like)的鎳誘發結晶的情形,證實鎳已擴散至捕捉基板,如圖 3-26。從圖 3-26(b)發現在 Outer side 的晶粒尺寸較一般 MILC 捉聚後的 Outer side 層晶粒小,這是因為利用過濾基板誘發結晶的複晶矽薄膜鎳濃度低,所以捉聚後的鎳含量因此較少,造成擴散至 Outer side 層的鎳較少,誘發結晶的晶粒較稀疏,這點由 SEM 可以發現,在圖 3-29 中,可以發現針狀結晶間參雜許多橢圓狀的 SPC 晶粒,顯示在鎳不足的情況下,誘發結晶成長受到 SPC的抑制。

但是從 OM 影像也可以發現經由過濾基板結晶後再捉聚的複晶矽薄膜明顯有剝落的現象,因為經過兩次接合又剝離處理後,表面粗糙度太高,已經不適合做為後續元件的主動層,這點需要從接合時的壓力著手,增加試片接合面積並提高接合均勻性是繼續努力的目標。

圖 3-24 結合過濾基板與捉聚步驟流程圖

圖 3-25 複晶矽 OM 影像(a) 過濾基板退火 12 小時 (b) 後續捉聚 12 小時

圖 3-26 捉聚基板 OM 影像 (a) Inner side (b) Outer side

圖 3-27 複晶矽 SEM 影像(a) 過濾基板退火 12 小時 (b) 後續捉聚 12 小時

圖 3-28 複晶矽 SEM 大倍率影像(a) 過濾基板退火 12 小時 (b) 後續捉聚 12 小時

圖 3-29 捉聚基板 SEM 影像 (a) Inner side (b) Outer side

#### 3.3.5 捉聚機制探討

過渡金屬的捉聚機制隨著捉聚方法而有不同,但大致可分為以下五種: (1)金屬矽化物析出 (2) 偏析出第二相 (3) 缺陷之原子陷捕 (4) 與電性參雜物互相反應 (5) 磷擴散捉聚。在本研究中利用雙面沉積非晶矽之雙面拋光的(100) p-type 晶圓作為捉聚鎳的吸附基材,其結構上將之分為 Inner side 非晶矽、矽晶圓與 Outer side 非晶矽三部份討論。在接合退火的過程中,原本殘留在複晶矽薄膜中 MIC 區域、針狀結晶晶界以及 MILC 前端交會晶界處的 NiSi₂與捉聚基板的 Inner side 非晶矽接觸形成一冶金接面,依照前述的 MILC 原理,熱力學上鎳會由結晶矽往非晶矽擴散以降低自由能,故在退火一小時的 Inner side 非晶矽會發現與複晶矽薄膜相同的壓印圖形。在退火捉聚時,鎳約 3.1 秒即擴散過 Inner side 非晶矽而到達矽晶圓,而在 550℃下鎳與單晶矽的平衡相為 NiSi,但是須要考慮到鎳在矽中的溶解度問題。一般過渡金屬在矽中擴散是靠間隙型(Interstitial)的擴散,因為過渡金屬原子小故可以輕易在矽的 tetrahedral interstitial site 中擴散。考慮到鎳在矽化物與矽中的化學能差異,而有下列式子可以表示其溶解度:

$$\left[\mathbf{M}_{i}\right]^{sol} = \left[\mathbf{M}_{Si}\right] \exp\left(\frac{\Delta S_{sil}^{0}}{k} - \frac{\Delta H_{Ssil}}{kT}\right) \tag{4}$$

其中 $[M_i]^{sol}$ 是間隙溶解度, $[M_{Si}]$ 為矽原子密度, $\triangle S^0_{sil}$ 是一個金屬原子從矽化物轉變到間隙固溶物的亂度差, $\triangle H_{sil}$ 則是其相對應的熱焓差。以上公式是對本質的單晶矽,而在有參雜的矽中帶電的金屬原子溶解度則須修正成下列式子:

$$\left[\mathbf{M}_{i}^{\sigma}\right]^{sol} = \left[\mathbf{M}_{Si}\right] \exp\left(\frac{\Delta S_{sil}^{0}}{k} - \frac{\Delta H_{Ssil}}{kT} - \frac{\sigma(E_{F} - E_{F}^{i})}{kT}\right)$$

(5)

其中 $\sigma$ 價電數, $E_F$ 為費米能量, $E_F$ 為本質矽中費米能量。

可以求得在  $550^{\circ}$ C 鎮在矽中的溶解度約為  $10^{14}$ atoms/cm³, $500^{\circ}$ C 下為  $10^{13}$ atoms/cm³。而從之前的研究[53][54]可以推測得知在  $500^{\circ}$ C 進行鎳誘發結晶後,在 MIC 區域的鎳濃度最高約在  $10^{20}$ atoms/cm³以上,佔矽中的原子百分率為 4at%,次高區域為 MILC 的前端,因為此處也有  $NiSi_2$  層在誘發結晶,其濃度約為  $4\times10^{19}$ atoms/cm³,原子百分率為 0.4at%,而在 MILC 區域 鎳濃度最低,為  $8\times10^{18}\sim2\times10^{19}$ atoms/cm³,原子百分率為 0.08at%。可以發現在 MILC 中的鎳濃度遠高於鎳原子在矽的間隙溶解度,所以能夠說明鎳

都是以 NiSio 的相存在複晶矽中,而在接合捉聚時 MIC 區域、MILC 前端及 針狀結晶晶界處的 NiSiz 與捉聚基板的 Inner side 非晶矽進行另一次的誘發 結晶過程,可歸類於第一種的金屬矽化物析出機制,此時複晶矽薄膜中的 NiSio 也因此變成結晶矽,所以在 GETR POLY 的 SEM 圖中沒有發現 NiSio 孔洞。而在捉聚處理後,複晶矽薄膜與捉聚基板的非晶矽量測到的鎳濃度 並不相同,若單純只考慮 1000Å 複晶矽薄膜與 1000Å Inner side 與 1000Å Outer side 非晶矽達到平衡濃度,則捉聚後鎳濃度應為原來的三分之一。但 由 SIMS 可得到捉聚後複晶矽薄膜鎳濃度降低至原本的 4%,因此捉聚基板 的矽晶圓也捉聚了一部份的鎳,而在 550℃下鎳在矽中的溶解度為  $10^{14}$ atoms/cm³,與 MILC 區域鎳濃度  $8 \times 10^{18}$ atoms/cm³ 有很大的差距,故多 餘的鎳應該會有部份析出成 NiSi 相存在矽晶圓中。另外在與電性參雜物互 相反應之機制中,已經有人發現鐵與硼反應而產生 B-Fe pairing,而我們使 用的矽晶圓為 P-type, 參雜硼離子之晶圓, 故也有可能鎳與硼產生相關的 B-Ni pairing 得到捉聚效果。而最多的鎳吸附位置(Sink)應為捉聚基板之 MILC 晶界處以及 Inner side 與 Outer side 跟矽晶圓界面處,因為此處的缺 陷最多,而缺陷會提高金屬雜質的溶解度。當有缺陷出現,會在能帶中產 生一受體能階 EA(Acceptor state),造成費米能階(Fermi level)提高,而雜質 溶解度則隨著費米能階提高而增加。帶負電之雜質濃度與未帶電之雜質濃 度比可由以下公式求得:

$$\frac{\left[\mathbf{M}^{(-)}\right]}{\left[\mathbf{M}^{0}\right]} = \exp\left(\frac{E_{F} - E_{A}}{kT}\right) \tag{6}$$

晶格缺陷除了造成費米能階平移提高溶解度外,在這些點缺陷、差排、疊差與晶界等處都是提供矽化物成核析出與原子陷捕的吸附位置,故在以SiO<sub>2</sub> Outer side 代替非晶矽 Outer side 之捉聚基板因為也有相當多之界面缺陷,故捉聚的效果與非晶矽 Outer side 相同,若是能增加更多缺陷位置,例如沉積多層薄膜以增加界面缺陷等方法,可以再提高捉聚的能力,可以作為未來研究的重心。

## 3.3.6 電性分析與探討

我們以 GETR POLY 與 NILC POLY 兩組試片來製作元件。此兩組試片皆是在 550℃下經由金屬誘發側向結晶 24 小時,然後用硫酸移除剩餘未反應的鎳。NILC POLY 則繼續在 550℃下退火 12 小時;GETR POLY 則在 550℃下接合捉聚 12 小時,所以兩組試片的總退火時間皆為 36 小時。

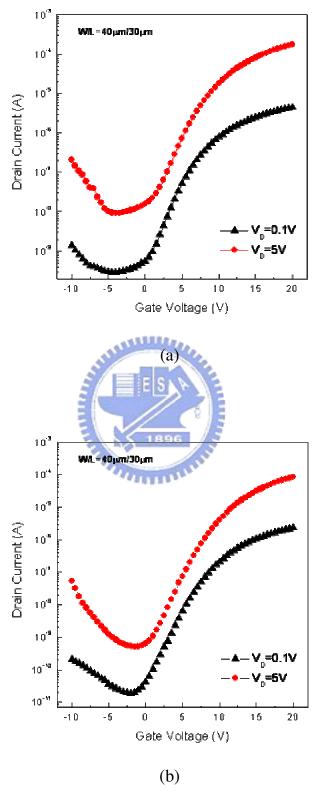

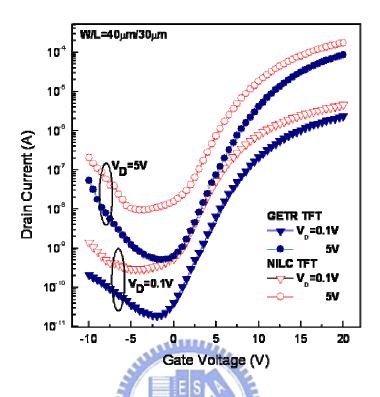

圖 3-30 為兩組元件其個別汲極電流對閘極電壓轉移特性曲線( $I_d$ - $V_g$  transfer characteristics),元件尺寸為 W=40 $\mu$ m、L=30 $\mu$ m。圖 3-31 將兩元件特性曲線做比較。

表 3-4 為兩組試片所製備之元件電性上的比較,選擇的元件條件為 W=40 $\mu$ m、L=30 $\mu$ m。電子遷移率(Mobility)、次臨界斜率(Subthreshold Slope) 及臨界電壓(Threshold Voltage)是在操作電壓( $V_d$ =5V)的狀態下做量測,而開/關電流比(On Off ratio)和最小電流/通道寬度(Minimun leakage current/channel width)是在  $V_d$ =0.1V的狀態下量測。其中電子遷移率由公式(7)導出:

$$\mu_{fe} = \frac{L}{W} \times \frac{g_m}{C_{oxide} V_D} \tag{7}$$

$\mu_{fe}$  為電子遷移率,L 為通道長度,W 為通道寬度, $g_m$  為轉移電導 (Transconductance), $C_{oxide}$  為閘極氧化層電容, $V_D$  為操作電壓。

次臨界斜率則是以 Id-Vg 特性曲線之斜率的倒數決定

臨界電壓的計算方法是使用定電流法,在  $V_D$ =0.1V 的狀況下,額訂一  $I_D$  值,其  $I_D$  值計算由公式(8)決定,而將此  $I_D$  值對應到其相對的  $V_G$ ,此對應的  $V_G$ 即所謂的  $V_{th}$ 。

$$I_d = \frac{W}{L} \times 10nA \tag{8}$$

開/關電流比的部分, $I_{on}$ 是取決於  $V_{d}$ =5V 的最大電流值,而  $I_{off}$ 部分是看最小電流值。

最小電流/通道寬度則是 Vd=5V 下最小電流值除以通道寬度所得。

圖 3-30  $I_{d}\text{-}V_{g}\,\text{transfer}$  characteristics (a) NILY TFT (b) GETR TFT

圖 3-31 Comparison of the transfer characteristics of GETR and NILC TFTs

表 3-4 GETR and NILC TFTs 元件電性上比較

| 元件参数<br>W=40μm L=30μm                              | GETR TFT | NILC TFT |

|----------------------------------------------------|----------|----------|

| 電子遷移率(cm²/Vs)<br>(V <sub>d</sub> =0.1V)            | 64       | 73.5     |

| <b>次</b> 臨界斜率(V/dec)<br>(V <sub>d</sub> =0.1V)     | 0.98     | 1.01     |

| 臨界電壓(V)<br>(V <sub>d</sub> =0.1V)                  | 5.5      | 3.5      |

| 開/關 電流比(x10 <sup>5</sup> )<br>(V <sub>d</sub> =5V) | 1.7      | 0.19     |

| 最小電流/通道寬度(pA/μm)<br>(V <sub>d</sub> =5V)           | 16.9     | 311      |

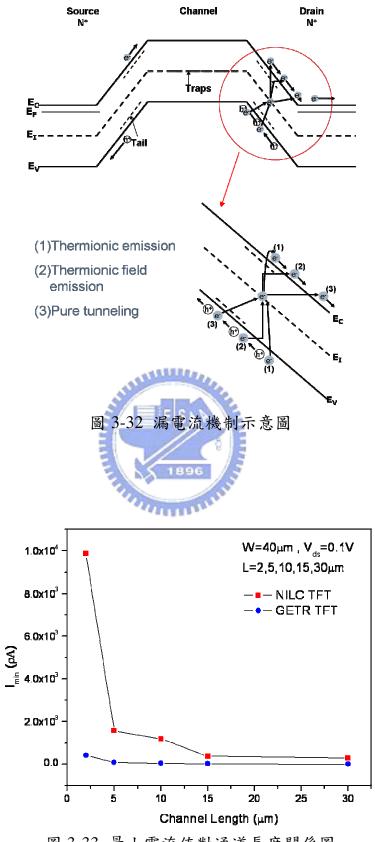

由圖 3-31 可以明顯發現經過捉聚步驟的 GETR TFT 其漏電流明顯比 NILC TFT 降低近一個數量級,符合預期的結果。對漏電流如此極佳的抑制 效果應歸功於經過捉聚步驟後,複晶矽薄膜中的殘餘鎳含量降低。複晶矽 本身就含有許多晶粒內(Inter-Grain)與晶粒間(Intra-Grain)缺陷,大部分的深 層缺陷能階(Deep level)位於能隙中間,隨著未鍵結鍵(Dangling bond)增加而 增加。而鎳在複晶矽中會造成更多的深層能階,且複晶矽的活化能介於 0.5~0.6eV之間,非常靠近中間能隙(Mid-gap),因而容易產生 Thermionic field emission 與 Pure tunneling 現象使得漏電流增加。一般而言漏電流的機制如 圖 3-32 所示,分為三種:(1) Thermionic emission (2) Thermionic field emission (3) Pure tunneling。在汲極電壓較低的操作情形下,主要漏電流的來源是靠 汲極空乏區中的 Thermionic emission(或稱 Thermal generation)機制所產生, 此漏電流值會隨著主動層厚度降低而減少。當汲極電壓升高時,漏電機制 轉而由 Thermionic field emission(或稱 Trap-assisted generation)所貢獻。而當 汲極電壓繼續提高後,能隙間距減少,此時漏電由 Pure tunneling(或稱 Trap-assisted field emission)所主導。在關閉狀態下隨著閘極電壓越小,漏電 流隨著上升,這是因為閘極所施加的負偏壓越大,致使通道與汲極端的界 面空乏區能隙減小,穿遂效應更加明顯, Pure tunneling 漏電流因而提高。

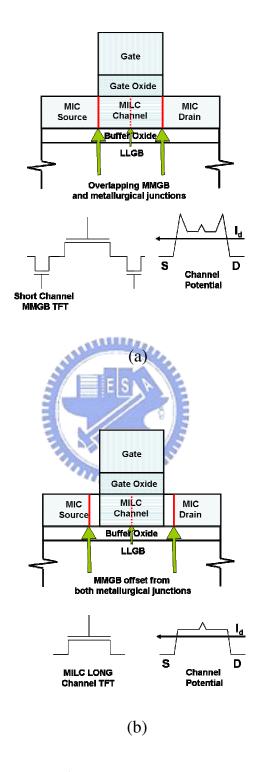

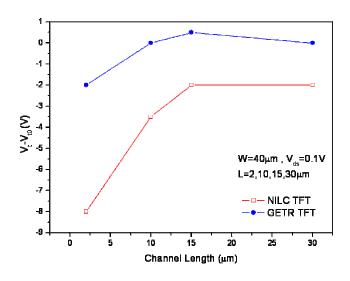

我們也發現在比較最小電流時, GETR TFT 較 NILC TFT 低數十倍以 上。若考慮整體阻值對漏電流的影響可分為兩部份:通道電阻以及接面電 阻[55]。而通道電阻明顯的會與通道長度 L 成正相關,所以漏電流會隨著通 道長度縮減而增加。由圖 3-33 最小電流值對不同通道長度可以發現,電流 的確隨著通道縮減而升高。而當通道長度縮減至一定大小時,此時接面電 阻將主導漏電的大小,可以看到在通道長度縮減至 2μm 以下時漏電流大幅 增加。從微結構的觀點來看,如圖 3-34 所示,我們在通道兩邊利用鍍覆鎳 金屬線來誘發側向結晶,在 MIC 與 MILC Boundary 存在一 MMGB,而通 道中央存在一 MILC 與 MILC Grain Boundary, 簡稱 LLGB。此 LLGB 存在 大量的缺陷以及 NiSi<sub>2</sub>,這些晶界的存在會造成一能障,所以我們在製作元 件時會作一 Off-set 結構,將 MMGB 避開汲極端接面,以避免此晶界會形 成一能障極高的超短通道 TFT,進而會增加其臨界電壓[56]。圖 3-34 中 NILC TFT 在通道長度縮減至 2µm 後漏電流增加的幅度遠大於 GETR TFT, 可推測是由於短通道時LLGB所包含的高密度缺陷與NiSi2導致。GETR TFT 由於捉聚後通道中殘餘鎳以及被晶界所陷捕的 NiSi2 含量大幅降低,所以在 短通道的漏電情形可以被抑制住。

圖 3-33 最小電流值對通道長度關係圖

圖 3-34 元件模型與能障示意圖 (a) MMGB is Self-aligned to both source and drain junctions (b) NILC TFT with double-side offfsets

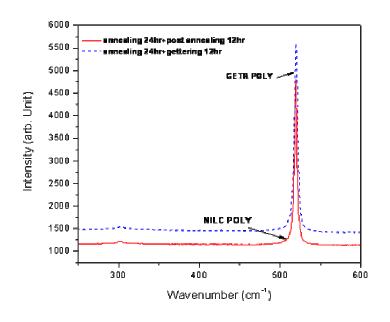

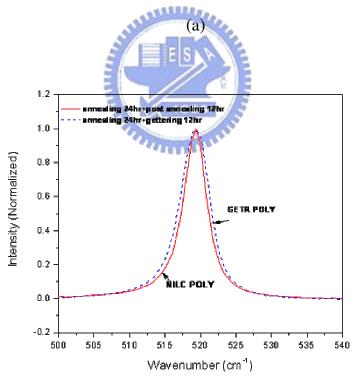

再來比較捉聚步驟前後電子遷移率的差異,可以發現 NILC TFT 的電子 遷移率為 73.5 cm²/Vs 高於 GETR TFT 的 64 cm²/Vs。經過捉聚後的 GETR TFT 通道中鎳污染降低,漏電流也確實下降,金屬雜質造成的缺陷理應消 失,但是電子遷移率卻下降,因此推測是複晶矽本身品質的差異,於是利 用 Raman 分析複晶矽薄膜的結晶性,如圖 3-35(a)所示,由於在強度(Intensity) 不同的情況下無法準確辨別個別試片的結晶性好壞,於是我們將數據正規 化(Normalized),得到圖 3-35(b)。我們比較 NILC POLY 與 GETR POLY,從 圖中可以發現 NILC POLY 的圖形最為狹窄,其半高寬較小,結晶性較佳。 GETR POLY 圖形較寬,其半高寬大,結晶性較差。NILC POLY 與 GETR POLY都是經過24小時退火後,將鎳移除再後續退火12小時,而NILC POLY 結晶性較 GETR POLY 好的原因,我們認為是因為 NILC POLY 在後續退火 時晶界中殘餘 NiSi2 已經將 MILC 晶界間的非晶矽區域完全結晶,而 GETR POLY 則是與捉聚基板接合來後續退火 12 小時,此時晶界中殘餘 NiSio 被捉 聚而移除無法將 MILC 晶界間的非晶矽區域誘發結晶,此時的非晶矽只能 靠 SPC 或是 MIC 的產生,但是 SPC 的結晶性較 MILC 差,所以導致 GETR POLY 的結晶性劣於 NILC POLY。這也說明了為何 GETR TFT 的最大電流 略小於 NILC TFT, 而臨界電壓較大。但是從次臨界斜率(次臨界擺幅)來看, 雨者並無太大差異,另一個可能因素可能是由於 NILC TFT 通道中存在 LLGB, 導致整體的電性漂移。可以從圖 3-31 看出在 GETR TFT 最小電流 值在閘極電壓約-2.5V處,而 NILC TFT 最小電流則在-5V處, NILC TFT 呈 現一負漂移。NILC TFT 在次臨界區-5V~0V 間有明顯較平緩的曲線,顯示 其弱反轉時受到大量缺陷影響,電子需要填補深層能階,所以造成次臨界 斜率的增加。由圖 3-36 兩種元件不同通道長度對臨界電壓漂移圖可以清楚 發現隨著通道長度縮減, NILC TFT 臨界電壓負漂移的程度越來越大, 臨界 電壓折曲(Roll-off)情形越嚴重。由圖 3-37 示意圖來看,NILC TFT 通道中央 的 LLGB 會造成一固定氧化物電荷,會陷捕正電荷造成整體電性負漂移, 而通道中央的氧化物電荷密度最高,所以當通道長度縮減,負漂移情形會 越嚴重。相對的 GETR TFT 因為捉聚後可減少固定氧化物電荷,因此抑制 了負漂移的影響。所以兩種元件比較電性時會有所偏差,因兩元件次臨界 斜率相近,則將 GETR TFT 與 NILC TFT 平移至相同臨界電壓比較,電流 值也相似,量測到的轉移電導也可能因此相似而導致電子遷移率也會更加 接近。那麼捉聚過後的元件電性則擁有漏電流下降的優點,開關電流比也 更加優異。

(b) 圖 3-35 Raman 結晶性分析 (a) 絕對強度 (b) 正規化強度

圖 3-36 不同通道長度對臨界電壓漂移圖

(a) NILC TFT

(b) GETR TFT

圖 3-37 通道中央之固定氧化物電荷示意圖

## 3.4 結論

我們利用晶圓鍍覆非晶矽的方式作為捉聚基板,將捉聚基板與複晶矽薄膜接合退火,成功的把複晶矽中殘餘鎳捕捉至捉聚基板中。從 SEM 影像中清楚觀察到捉聚後聚集在晶界的 NiSi2 蝕刻孔洞明顯減少,而由 SIMS 所偵測到的鎳濃度也大量降低了一個數量級以上,並從捉聚基板之 Inner side 與 Outer side 非晶矽層觀察到因捕捉鎳而產生誘發結晶的情形。我們另外也嘗試了使用石英基板鍍覆非晶矽當作捉聚基板,同樣也成功的有捉聚的效果,並可將捉聚後之 Inner side 與 Outer side 非晶矽層利用蝕刻或研磨移除,而達到石英基板重複使用的效果。結合過濾基板與捉聚步驟後的複晶矽薄膜也成功的觀察到 NiSi2 蝕刻孔洞減少的現象,證明捉聚的效果,但由於表面粗糙度過大,不適合利用於製作元件上。

我們將捉聚前後的複晶矽薄膜製做 NILC TFT 與 GETR TFT 兩組元件,從電性上經過捉聚後的 GETR TFT 因為鎳雜質的減少,漏電流進而降低的一個數量級以上,開關電流比也因此提高。雖然從量測的數據上捉聚後的元件其臨界電壓與電子遷移率較差,一方面是由於 GETR POLY 結晶性不如 NILC POLY 優異,另一方面是因為捉聚後鎳含量的減少,使的整體電性有了正漂移的情形,且由於鎳污染減少,在短通道效應導致的漏電流上升及臨界電壓折曲(Roll-off)以及整體電性負漂移方面都有顯著的抑制效果。

## 第四章 未來工作

從本研究已經證明經過捉聚步驟減少鎳污染的確可以降低漏電流,若能成功結合過濾基板與捉聚步驟,改善其表面粗糙度,可望在電性上能有更優異的提升。而在結晶性方面,可在捉聚步驟前先將複晶矽薄膜退火至完全結晶,可以消彌捉聚前後的電子遷移率差異。而捉聚步驟還可以應用在結合其他結晶方式,如 MILC+Gettering+ELA,可望能開發出表現更突出的薄膜電晶體。

對於臨界電壓以及次臨界斜率較大方面可以利用電漿護佈(Passivation) 改善,而改良捉聚方式如沉積其他材料於複晶矽薄膜來取代晶圓接合,相 信可將捉聚的技術應用於量產上,將 MILC 的方法製作大尺寸之 LTPS 面板。

## 第五章 参考文獻

- [1] http://cn.fpdisplay.com:7751/technology/Tech\_Shtml/3\_200616133\_57138. htm

- [2] <a href="http://www.thg.com.tw/">http://www.thg.com.tw/</a>

- [3] 紀國鐘,鄭晃忠,液晶顯示器技術手冊

- [4] 薛友仁, TFT-LCD 製程 I

- [5] 林敬偉,低溫多晶矽薄膜電晶體液晶顯示器技術,電子月刊第十 卷第八期

- [6] <a href="http://cn.fpdisplay.com/technology/">http://cn.fpdisplay.com/technology/</a>

- [7] 工研院電子所網站

- [8] LTPS TFT-LCD 技術綜述, 光電科技 No.01, 2005/4

- [9] R.S. Wanger, W.C. Ellis, J. Appl. Phys., vol. 4, pp. 89, 1964

- [10] M. S. Haque, H. A. Naseem, and W. D. Brown, J. Appl. Phys., vol. 79, pp. 7529-7536, 1996

- [11] L. Hultman, A. Robertsson, H. T. G. Hentzell, I. Engström, and P. A. Psaras, J. Appl. Phys., vol 62, pp. 3647-3655, 1987

- [12] SY Yoon, KH Kim, CO Kim, JY Oh and J. Jang, J. Appl. Phys., vol. 82, pp. 5865-5867, 1997

- [13] F. A. Quli and J. Singh, Materials Science and Engineering, vol. B67, pp. 139-144, 1999

- [14] S.-W. Lee, Y.-C. Jeon and S.-K. Joo, Appl. Phys. Lett., vol. 66, pp. 1671-1673, 1995

- [15] Huang-Chung Cheng, Epitaxial Growth of Transition Metal Silicide, 國立 清華大學博士班論文

- [16] C.Hayzelden,J.L. Batstone, "Silicide formation and silicide-mediated crystallization of nickel-implanted amorphous silicon thin films", <u>J. Appl. Phys.</u>, **73**, pp.8280~8289, June 1993

- [17] Yun Tian, Yu-Long Jiang, Yu Chen, Fang Lu and Bing-Zong Li, Electrically active defects in Ni–Si silicide tudied by deep-level transient pectroscopy", Semicond. Sci. Technol. **17** (2002) 83–86

- [18] 陳文照,鎮金屬薄膜與矽晶之界面反應研究,國立清華大學博士班論

文

- [19] Yue Kuo, "THIN FILM TRANSISTORS-Materials and Processes Volume2-Polycrystalline Silicon Thin Film Transistors", pp. 236

- [20] C.Hayzelden, J.L. Batstone, "Silicide formation and silicide-mediated crystallization of nickel-implanted amorphous silicon thin films", J. Appl. Phys., 73, pp.8280~8289, June 1993

- [21] M. Cao, T. King, and K. Saraswat, "Determination of the densities of gap states in hydrogenated polycrystalline si and Si0.8Ge0.2 films," Appl. Phys. Lett., 61, pp.672~674, 1992

- [22] M. M.Mandurah, K. C. Saraswat, C. R. Helms and T. I. Kamins, "Dopant segregation in polycrystalline silicon", J. Appl. Phys., 51 pp. 5575~5763, 1980

- [23] A. L. Fripp, "Dependence of resistivity on the doping level of polycrystalline silicon", J. Appl. Phys., 46 pp. 1240~1244, 1975

- [24] T. I. kamins, "Hall mobility in chemically deposited polycrystalline silicon," J. Appl. Phys., 42 pp. 4357~4365, 1971

- [25] G. Baccarani, B. Ricc'o and G. Spadini, "Transport properties of polycrystalline silicon films," J. Appl. Phys., 49, pp. 5565~5570, 1978

- [26] M. M.Mandurah, K. C. Saraswat, C. R. Helms and T. I. Kamins, "Dopant segregation in polycrystalline silicon", J. Appl. Phys., 51 pp. 5575~5763, 1980

- [27] Wu, I-Wei, Huang, Tiao-Yuan, Jackson, Warren B., Lewis, Alan G., and Chiang, Anne, "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation", IEEE Electron Device Lett., 12, pp. 181-183, 1991

- [28] F. S. Wang, C. Y. Huang, H. C. Cheng, "Novel N2O plasma passivation on polycrystalline silicon thin-film transistors," Materials Research Society Symposium - Proceedings, 424, Flat Panel Display Materials, pp 177-181, 1996

- [29] C. M. Yu, H. C. Lin, T. Y. Huang, and T. F. Lei, "H2 and NH3 Plasma Passivation on Poly-Si TFTs with Bottom-Sub-Gate Induced Electrical Junction," J. Electrochem. Soc., 150, pp. G843-G848, 2003

- [30] H. C. Cheng, , F. S. Wang , and C. Y. Huang, "Effects of NH3 plasma

- passivation on N-channel polycrystalline silicon thin-film transistors," IEEE Trans. Electron Devices, 44, pp 64-68, 1997

- [31] Y. Lee, Li Handong, and S.J. Fonash, "High-performance poly-Si TFTs on plastic substrates using a nano-structured separation layer approach", IEEE Electron Device Lett., v 24, pp. 19-21, 2003

- [32] M. MIYASAKA, T. SHIMODA, K. MAKIHIRA, T. ASANO, Be la PECZ and J. STOEMENOS, "Structural Properties of Nickel Metal-Induced Laterally Crystallized Silicon Films and Their Improvement Using Excimer Laser Annealing" Jpn. J. Appl. Phys., 42, pp.2592~2599, 2003

- [33] S.Bae and S. J.Fonash, "Defined crystallization of amorphous-silicon films using contact printing", Appl. Phys. Lett., 76, pp.595-597, January 2000

- [34] P. C. Liu, C. Y. Hou and Y. S. Wu, Thin Solid Films 478,280(2005).

- [35] J. H. Choi, D. Y. Kim, B. K. Choo, W. S. Sohn and J. Jang, "Metal Induced Lateral Crystallization of Amorphous Silicon Through a Silicon Nitride Cap Layer", Electrochemical and Solid-State Letters, 6 (1) G16-G18, 2003

- [36] J. C. Bean and J. M. Poate, "Silicon/metal silicide heterostructures grown by molecular beam epitaxy", Appl. Phys. Lett., 37, pp.643~646, 1980

- [37] Shyuichi Saitoh, Hiroshi Ishiwara, and Seijiro Furukawa, "Double heteroepitaxy in the Si (111)/CoSi2/Si structure", Appl. Phys. Lett., 37, pp.203~2051980

- [38] R. T. Tung, "Schottky-Barrier Formation at Single-Crystal Metal -Semiconductor Interfaces", Phys Rev. Lett., 52, pp.461 1984

- [39] A. Ourmazd and W. Schröter, "Phosphorus gettering and intrinsic gettering of nickel in silicon", Applied Physics Letters -- October 1, 1984 -- Volume 45, Issue 7, pp. 781-783

- [40] R. Hoelzl, K.-J. Range, L. Fabry, J. Hage, V. Raineri, "Gettering efficiencies of polysilicon, stacking fault and He implanted backsides for Cu and Ni", Materials Science and Engineering B73 (2000) 95–98

- [41] Toshio Mizuki, Junko Shibata Matsuda, Yoshinobu Nakamura, Junkoh Takagi, and Toyonobu Yoshida, "Large Domains of Continuous Grain Silicon on Glass Substrate for High-Performance TFTs ", IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 51, 204(2004)

- [42] S. Bae and S. J. Fonash, "Defined crystallization of amorphous-silicon

- films using contact printing", Appl. Phys. Lett., 76, pp.595-597, January 2000

- [43] K. Makihira and T. Asano," Enhanced nucleation in solid-phase crystallization of amorphous Si by imprint technology", Appl. Phys. Lett., 76, 3774(2000)

- [44] Yun Tian, Yu-Long Jiang, Yu Chen, Fang Lu and Bing-Zong Li, " Electrically active defects in Ni–Si silicide studied by deep-level transient spectroscopy", Semicond. Sci. Technol. 17 (2002) 83–86

- [45] P.S. Lee, D. Mangelinck, K.L. Pey, J. Ding, J.Y. Dai, C.S. Ho, A. See," On the Ni–Si phase transformation with/ without native oxide", Microelectronic Engineering 51–52 (2000) 583–594

- [46] 鄭晃忠,過渡金屬矽化物之磊晶成長,國立清華大學/材料科學工程研究所博士論文

- [47] 胡國仁,金屬誘發側向結晶應用於低溫多晶矽薄膜電晶體-結晶成長之熱力學、動力學及電晶體元件效能,國立交通大學/材料科學與工程系所博士論文

- [48] S. M. Myers, M. Seibt and W. Schro" ter, "Mechanisms of transition-metal gettering in silicon", J. Appl. Phys. 88, 3795, 2000.

- [49] N. Gay, S.Martinuzzi, Solid St. Phenom. 57 V58, 115, 1997

- [50] J.S. Williams, et al., Appl. Phys. Lett. 75, 2424, 1999

- [51] W. Schroter, et al., Materials Science and Technology 4, 540, 1992

- [52] http://www.arconet.com.tw/ssttpro/tech/tech\_1.asp?idxid=119

- [53] C. F. Cheng, M. C. Poon, C. W. Kok, and Mansun Chan, "Modeling of Metal-Induced-Lateral-Crystallization Mechanism for Optimization of High Performance Thin-Film-Transistor Fabrication", IEEE 2002.

- [54] Woo Sung Sohn, Jong Hyun Choi, Kyung Ho Kim, Jae Hwan Oh, Seung Soo Kim, and Jin Jang, "Crystalline orientation of polycrystalline silicon with disklike grains produced by silicide-mediated crystallization of amorphous silicon", JOURNAL OF APPLIED PHYSICS VOLUME 94, NUMBER 7 1 OCTOBER 2003

- [55] Gururaj A. Bhat, Zhonghe Jin, Hoi S. Kwok, and Man Wong, "Effects of Longitudinal Grain Boundaries on the Performance of MILC-TFT's", IEEE ELECTRON DEVICE LETTERS, VOL. 20, NO. 2, FEBRUARY 1999

[56] Man Wong, Zhonghe Jin, Gururaj A. Bhat, Philip C. Wong, and Hoi Sing Kwok, Senior" Characterization of the MIC/MILC Interface and Its Effects on the Performance of MILC Thin-Film Transistors", IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 47, NO. 5, MAY 2000