### 國立交通大學

#### 資訊科學與工程研究所

#### 碩士論文

使用分支目標暫存器協助的可存放分支及副程 式的迴圈緩衝器以減少指令擷取能源消耗

Power Reduction in Instruction Fetch Using Forward-Branch and Subroutine Bufferable Innermost Loop Buffer with

Assistance of BTB

研究生:田濱華

指導教授:鍾崇斌 博士

中華民國九十五年七月

## 使用分支目標暫存器協助的可存放分支及副程式的迴圈緩衝器以減 少指令擷取能源消耗

Power Reduction in Instruction Fetch Using Forward-Branch and Subroutine Bufferable Innermost Loop Buffer with Assistance of BTB

研究生:田濱華 Student:Bin-Hua Tein

指導教授:鍾崇斌 Advisor: Chung-Ping Chung

#### 國立交通大學

#### A Thesis

Submitted to Institute of Computer Science and Engineering

College of Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Computer Science

July 2006

Hsinchu, Taiwan, Republic of China

中華民國九十五年七月

## 使用分支目標暫存器協助的可存放分支及副程式的 迴圈緩衝器以減少指令擷取能源消耗

學生:田濱華 指導教授:鍾崇斌 教授

國立交通大學資訊工程系

#### 摘要

减少嵌入式處理器的能源消耗以增加使用時間變得日益重要。在嵌入式處 理器中,指令擷取的能源消耗佔整個動態能源消耗很大一部分。近來提出一減 少指令擷取能源消耗之設計,在指令快取及處理器間加入一更小的記憶體,利 用指令的時間區域性,使得大部分的指令能從此小的記憶體中擷取。迴圈有很 好的空間區域性,因此許多的迴圈緩衝器設計便被提出。然而,在設計複雜度 的限制下,大多數的迴圈暫存器只存放迴圈內無向前分支指令及沒有副程式的 最內層迴圈,或是存放迴圈內的指令直到向前分支指令及副程式的最內層迴 圈。但許多的迴圈內包含向前分支及副程式,因此現有的設計仍有減少指令擷 取能源的改善空間。我們提出一個簡單且有效率的方法,來存放迴圈內含向前 分支及副程式的最內層迴圈:因爲分支目的緩衝器在現今的嵌入式處理器設計 中將普遍存在,如果我們加入一額外欄位在每項分支目的緩衝器內容後,用來 指示這個在迴圈緩衝器存放的分支後的下一到指令是分支後接續的下一道或是 分支目的,如此可避免掉設計複雜度而存放內含向前分支的最內層迴圈。含副 程式的最內層迴圈且這個副程式內不包含迴圈也可用相似的方法處理 。使用 MiBench 模擬的結果得到,我們的設計可比先前無法存放向前分支及副程式的 迴圈緩衝器更減少13.66%的指令擷取能源消耗。

# Power Reduction in Instruction Fetch Using Forward-Branch and Subroutine Bufferable Innermost Loop Buffer with Assistance of BTB

Student : Bin-Hua Tein Advisor : Chung-Ping Chung

Dept. of Computer Science

National Chiao Tung University

#### **ABSTRACT**

Reducing power of embedded processors is becoming increasingly important for mobile applications. Much of the dynamic power of a typical embedded processor is consumed by instruction fetching. Recently, addition one tiny memory between CPU core and instruction cache had been proposed. Using the temporal locality of instructions, most of instructions can be fetched from this tiny memory to replace from instruction cache. Loops have temporal locality, so that many of loop buffer design had been proposed. Nevertheless, on design complexity dictates most loop buffer designs to store only innermost loops without forward branch or instructions within innermost loops before a forward branch. While program modeling shows that typical programs can best be represented with a simple loop model, many of them contain forward branches and subroutines in their innermost loops. Hence, existing designs lead to limitation in reduction of instruction fetch power. We propose a simple and effective way to cope with this complexity: since using BTB is a norm in most designs, if we add an extra bit in BTB, indicating if the loop buffer stores the fall-through or target trace after a within-the-innermost-loop forward branch, then much of the complexity can be avoided. The subroutine including no loop is also handled by using similar way. Results with MiBench indicate that up to 18% of further reduction in instruction fetch power compared with the design without forward branch and subroutine handling.

#### 誌謝

首先感謝我的指導老師 鍾崇斌教授,在他的諄諄教誨、辛勤指導與勉勵下,而得以順利完成此論文。同時也感謝是我的口試委員的單智君、林正宗、楊竹星教授,由於他們的建議,使得這篇論文能更加完整。

感謝吳奕緯學長全程的協助,給我很多的幫助。也感謝 jojo 大學長、程式 超強的林大頭、人超好又瘦的幾米學妹、強汪、陳 17、很帥的葉大帥跟黃士嘉、 屁屁鄭、黃富群、莊富源的幫助,給我很多意見及鼓勵。

最後感謝我的家人和女朋友,謝謝你們在背後全心全意的支持我,關懷我, 鼓勵我。讓我在這求學的路上走的更順利,使我能堅持追求自己的理想。

所有支持我、勉勵我的師長與親友、奉上我最誠摯的感謝與祝福、謝謝你們。

田濱華 2006.8

#### **Contents**

| 摘要                                                                         | i      |

|----------------------------------------------------------------------------|--------|

| ABSTRACT                                                                   | ii     |

| 誌謝                                                                         | iii    |

| Contents                                                                   | iv     |

| List of Figures                                                            | vi     |

| List of Table                                                              | . viii |

| Chapter 1 Introduction                                                     | 1      |

| 1.1 Instruction Fetch Power Reduction Techniques                           | 1      |

| 1.2 The Problems of Loop Buffer to Store Branch(es)                        | 4      |

| 1.3 Motivations and Objectives                                             | 5      |

| 1.4 Organization of This Thesis                                            | 7      |

| Chapter 2 Background and Related Work                                      | 8      |

| 2.1 Categorization of Execution Time of Program                            | 8      |

| 2.2 Related Research and Technology                                        | 9      |

| 2.2.1 Dynamic Loop Cache                                                   |        |

| 2.2.2 Hardware-Based Two-Way Loop Buffer                                   | 11     |

| 2.2.3 Pre-load Loop Cache. E.S                                             | 12     |

| 2.2.4 Cluster Loop Cache                                                   | 13     |

| Chapter 3 Design of the Forward-Branch and Subroutine Bufferable Innermost |        |

| Loop Buffer                                                                | 14     |

| 3.1 Features of Our Approach                                               | 14     |

| 3.2 Architecture and Design Issues of Our Approach                         | 15     |

| 3.2.1 Innermost Loop Detection                                             | 16     |

| 3.2.2 Filling or Refilling an Innermost Loop Into Loop Buffer              | 17     |

| 3.2.3 Determining that CPU Core Should Fetch Intrusions From Loop          |        |

| Buffer or IL1                                                              | 19     |

| 3.2.4 Handling Incorrect Instruction Filling and Fetching due to Branch    |        |

| Misprediction                                                              | 20     |

| 3.2.5 No-loop-inside Subroutine Handling                                   | 21     |

| 3.3 Operation.                                                             | 22     |

| Chapter 4 Simulation and Evaluation                                        | 27     |

| 4.1. Power Model                                                           | 27     |

| 4.2 Simulation Environment                                                 | 28     |

| 4.2.1 Simulator                                                            | 28     |

| 4.2.2 Benchmark Programs                                                   | 29     |

| 4.3. Simulation Results of Loop Buffer Policies                            | 32     |

| 4.3.1 Loop Buffer Policies in Each loop Buffer state              | 32      |

|-------------------------------------------------------------------|---------|

| 4.3.2 Simulation Results of Loop Buffer Policies                  | 35      |

| 4.3.2.1 Simulation Results of the Loop Buffer Policies in IDLE S  | State35 |

| 4.3.2.2 Simulation Results of the Loop Buffer Policies in FILL S  | tate 38 |

| 4.3.2.3 Simulation Results of the Loop Buffer Policies in ACTIV   | Έ       |

| State                                                             | 42      |

| 4.3.2.4 Simulation Results of the Best Loop Buffer Policies       |         |

| 4.4 The Penalty of Miss-prediction in Loop Buffer Policies        | 49      |

| 4.5 The Reasons of Affecting the Loop Buffer Efficiency           | 51      |

| 4.5.1 The Nature of Benchmark                                     | 51      |

| 4.5.1.1 The Benchmark Has Less Execution Time in Innermost I      | Loops52 |

| 4.5.1.2 The Execution Paths are changed frequently                | 54      |

| 4.5.1.3 The Benchmark Has a Few of Loop Iteration                 | 56      |

| 4.5.1.4 The Size of Innermost Loops is too large or too small tha | n       |

| Loop Buffer                                                       | 58      |

| 4.5.2 The Architecture of Processor                               | 63      |

| 4.5.3 The Optimal of Compiler                                     | 64      |

| 4.6. Simulation Results and Evaluation                            | 65      |

| 4.6.1 Strategies of Loop Buffer management as Comparison          | 65      |

| 4.6.2 Simulation Results of Different Loop buffer Designs         | 66      |

| Chapter 5 Conclusions and Future Work 1896                        | 73      |

| Reference                                                         | 75      |

| Appendix                                                          | 78      |

| A-1 Profiling of Innermost Loop                                   | 78      |

#### **List of Figures**

| Figure 1.1: (a) Organization of CPU core, IL1, and filter cache;(b) Organization of   | ,   |

|---------------------------------------------------------------------------------------|-----|

| CPU core, IL1, and loop buffer.                                                       | 4   |

| Figure 1.2: A code segment without branch                                             | 4   |

| Figure 1.3: A code segment with a branch                                              | 5   |

| Figure 2.1: Profile the execution time of MiBench                                     | 9   |

| Figure 2.2: the management of Dynamic Loop Cache                                      | 10  |

| Figure 2.3: the management of Hardware-Based Two-Way Loop Buffer                      | 12  |

| Figure 2.4: the management of Pre-load Loop Cache                                     | 13  |

| Figure 3.1: Architecture of our approach                                              | 15  |

| Figure 3.2: An innermost loop consists of subroutine                                  | 22  |

| Figure 3.3: Memory accessing in different states                                      | 23  |

| Figure 3.4: State diagram of loop buffer controller                                   | 26  |

| Figure 4.1: Access ratio of IL1 of different loop buffer policies sets (IDLE state)   | 36  |

| Figure 4.2: Access ratio of loop buffer of different loop buffer policies sets (IDLE  |     |

| state)                                                                                | 37  |

| Figure 4.3: Reduction in instruction fetch power of different loop buffer policies se | ets |

| (IDLE state)                                                                          | 38  |

| Figure 4.4: Access ratio of IL1 of different loop buffer policies sets (FILL state)   | 40  |

| Figure 4.5: Access ratio of loop buffer of different loop buffer policies sets (FILL  |     |

| state)                                                                                | 40  |

| Figure 4.6: Reduction in instruction fetch power of different loop buffer policies se | ets |

| (FILL state)                                                                          | 41  |

| Figure 4.7: Access ratio of IL1 of different loop buffer policies sets (ACTIVE state  | ;)  |

|                                                                                       | 43  |

| Figure 4.8: Access ratio of loop buffer of different loop buffer policies sets       |     |

|--------------------------------------------------------------------------------------|-----|

| (ACTIVE state)                                                                       | 44  |

| Figure 4.9: Reduction in instruction fetch power of different loop buffer policies s | ets |

| (ACTIVE state)                                                                       | 45  |

| Figure 4.10: Access ratio of IL1 of different loop buffer policies sets              | 47  |

| Figure 4.11: Access ratio of loop buffer of different loop buffer policies sets      | 48  |

| Figure 4.12: Reduction in instruction fetch power of different loop buffer policies  |     |

| sets                                                                                 | 49  |

| Figure 4.13: The penalty of miss-prediction of innermost loop detection              | 51  |

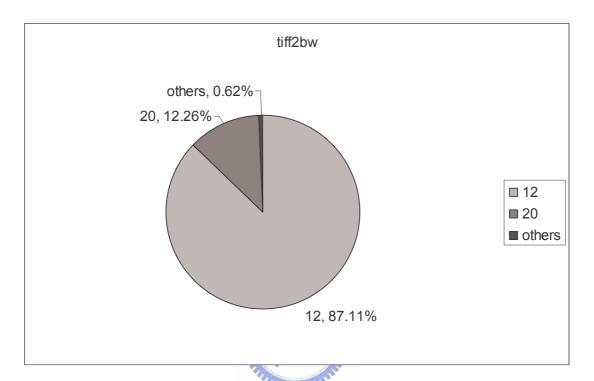

| Figure 4.14: The ratio of different sizes (instructions) of innermost loop— tiff2bw  | 59  |

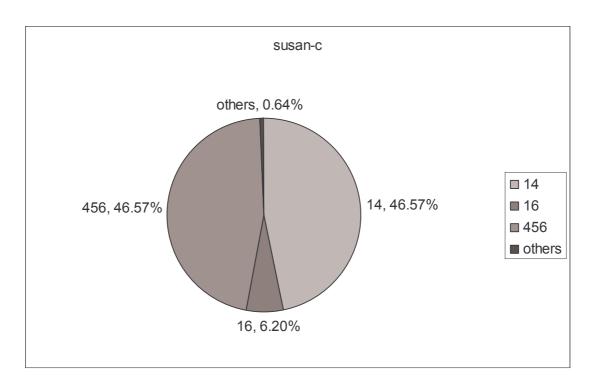

| Figure 4.15: The ratio of different sizes (instructions) of innermost loop—susan-c   | 60  |

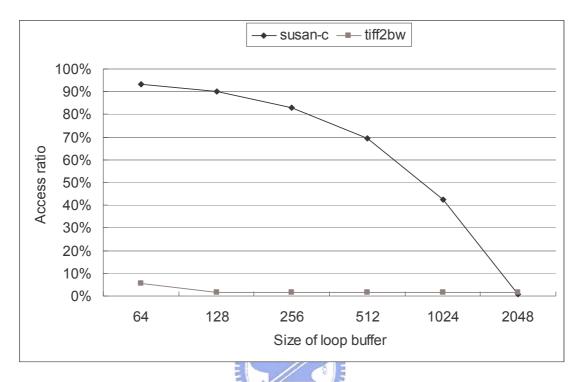

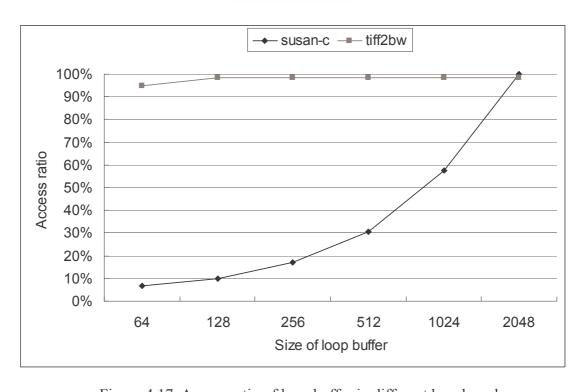

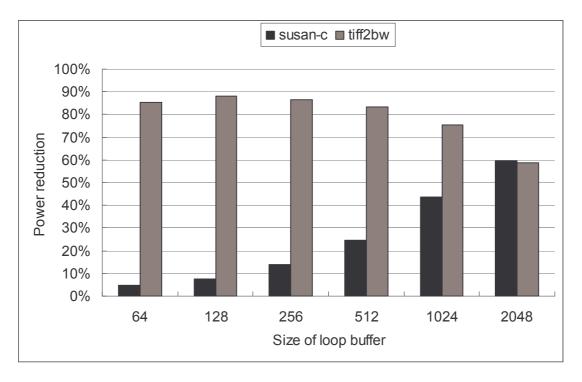

| Figure 4.16: Access ratio of IL1 in different benchmarks                             | 61  |

| Figure 4.17: Access ratio of loop buffer in different benchmarks                     | 61  |

| Figure 4.18: Reduction in instruction fetch power in different benchmarks            | 62  |

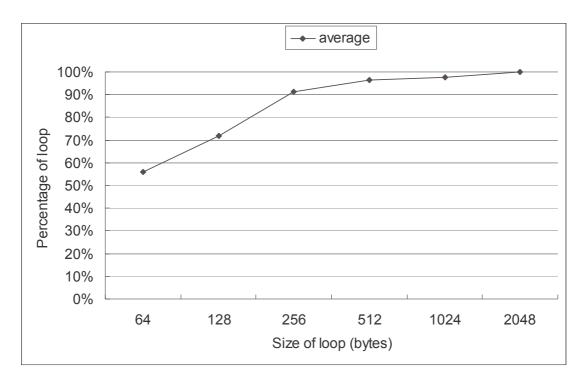

| Figure 4.19: The percentage of innermost loops with different sizes of innermost     |     |

| loops                                                                                | 63  |

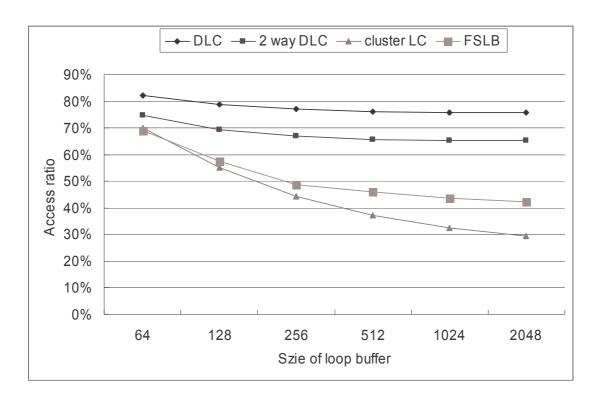

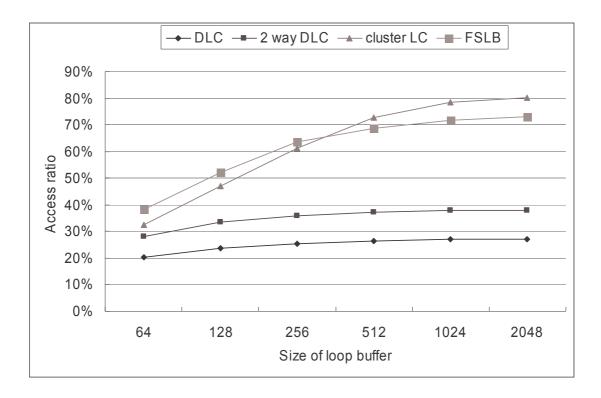

| Figure 4.20: Access ratio of IL1 of different designs                                | 67  |

| Figure 4.21: Access ratio of loop buffer of different designs                        | 68  |

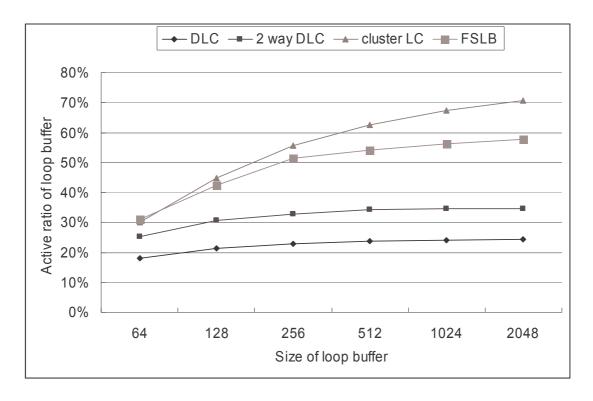

| Figure 4.22: Loop buffer ACTIVE ratio                                                | 70  |

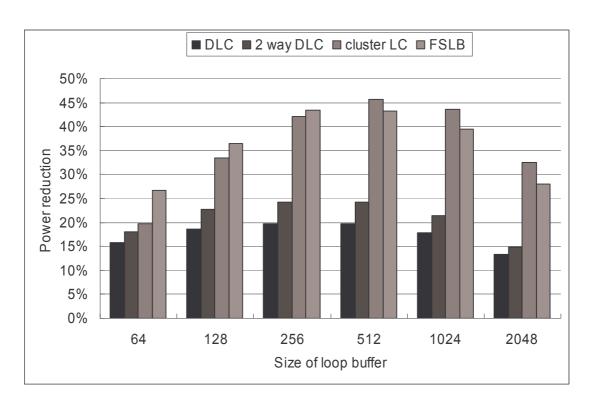

| Figure 4.23: Reduction in instruction fetch power of different designs               | 72  |

#### **List of Table**

| Table 4.1: Ratio of P <sub>LB</sub>                                                        | 28 |

|--------------------------------------------------------------------------------------------|----|

| Table 4.2: Parameters setting in SimpleScalar/ARM                                          | 29 |

| Table 4.3: MiBench workloads                                                               | 30 |

| Table 4.4: Policies of loop buffer in each state of loop buffer                            | 34 |

| Table 4.6: Ratio of P <sub>ctrl</sub> of different loop buffer policy sets (IDLE state)    | 35 |

| Table 4.6: Power of loop buffer controller of different loop buffer policy sets (ID)       | LE |

| state)                                                                                     | 37 |

| Table 4.7: Loop buffer policies sets (FILL state)                                          | 38 |

| Table 4.8: Ratio of P <sub>ctrl</sub> of different loop buffer policy sets (FILL state)    | 41 |

| Table 4.9: loop buffer policies sets (ACTIVE state)                                        | 42 |

| Table 4.10: Ratio of P <sub>ctrl</sub> of different loop buffer policy sets (ACTIVE state) |    |

| Table 4.11: Loop buffer policies sets                                                      | 48 |

| Table 4.12: Ratio of P <sub>ctrl</sub> of different loop buffer policy sets                | 48 |

| Table 4.13: Loop buffer policies sets                                                      | 50 |

| Table 4.14: The relation between innermost loop ratio to ACTIVE ratio                      | 53 |

| Table 4.15: The relation between execution path ratio to the increase ratio                | 54 |

| Table 4.16: the relation between execution path ratio to the increase ratio                | 57 |

| Table 4.17: The best policies set of FSLB                                                  | 66 |

| Table 4.18: Ratio of P <sub>LB</sub> and P <sub>ctrl</sub>                                 | 70 |

# Chapter 1 Introduction

Power consumption has become an increasingly greater concern in digital system designs, especially for battery powered devices. Much of the dynamic power of a typical embedded processor is consumed by instruction fetching, for example, 30-50%. Since instruction fetching happens on almost every cycle, involves switching of large number of high capacitance wires, and may involve access to a power hungry set-associative cache.

Loop buffering is an effective technique to reduce energy consumption in the instruction memory hierarchy. In any typical embedded application, significant amount of execution time is spent in small program segments. Hence, by storing them in a small loop buffer or an LO buffer instead of the big instruction cache, energy can be reduced.

In this thesis, we propose a loop buffering mechanism which can store innermost loop with forward branch(es) or subroutine call(s) inside this innermost loop in loop buffer, so that the instruction fetch power can be reduced.

In this chapter, we will first instruction fetch power reduction techniques in section 1.1. In section 1.2, we describe the problems of loop buffer to store forward branch(es) and subroutine(s). The motivations and objectives are proposed in section 1.3. The organization of this thesis is described in section 1.4.

#### 1.1 Instruction Fetch Power Reduction Techniques

Current embedded systems for multimedia applications like mobile and hand-held devices are typically battery operated. Therefore, low energy is one of the

key design goals of such systems. Power analysis of such processors indicate that a significant amount of power is consumed in the instruction caches during instruction fetch [1], [2] . For example in the TMS320C6000, a VLIW processor from Texas Instruments, up to 30% of the total processor energy is consumed in the instruction caches alone [1]. Since instruction fetching happens on almost every cycle, involves switching of large number of high capacitance wires, and may involve access to a power hungry set-associative cache.

Thus, several approaches have been proposed to reduce instruction fetch power. Some have focused on encoding the address and data bus signals to reduce bus switching [3-5]. Others have focused on compressing [6-7] or buffering instructions [8], also to reduce bus switching. Some researches have looked at reducing the power of the cache itself by deactivating several ways of a set-associative cache when deactivation does not heavily impact performance [9-10], or accessing items using multiple phases [11], thus trading off performance for reduced power.

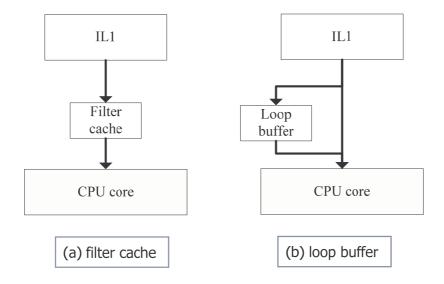

Another class of approaches adds an unusually small instruction cache called instruction level zero cache as the first level of memory (level 0) in the instruction memory hierarchy, perhaps 16 to 128 word (typically 64 to 512 byte), between CPU core and instruction level one cache. The extremely low power per access for an instruction level zero cache is achieved because of very short wires inside the cache. Another reason for very low power per access to an instruction level zero cache comes from the fact that an instruction level zero cache can be integrated very close to or even inside a microprocessor, resulting in shorter and hence lower power bus lines. Two approaches of instruction level zero cache in recent years, one is called filter cache which is a cache-like architecture; the other is called loop buffer which is a simple instructions buffer without tag.

[12] proposes an instruction level zero cache design called a filter cache. A

filter cache is a tiny direct-mapped cache introduced as the first level of memory (level 0) in the instruction memory hierarchy as shown in figure 1.1 (a).

[12] shows that a 256 byte filter cache has a hit rate between 60–85% on MediaBench benchmarks. Using a 32 KB direct-mapped cache for the L1 cache, the filter cache could reduce instruction access power by over 50%, but at the expense of about 20% performance overhead. The energy\*delay product related to memory accesses was reduced by about 50%. To reduce the performance overhead, [13] proposed using a profile-aware compiler to map frequent loops to a special address region recognized by the processor as loadable into the filter cache, resulting in less performance overhead along with improved energy savings.

In many researches [14-17], loop buffer has been proposed to reduce instruction fetch power. A loop buffer is a memory located between CPU core and L1 instruction cache, called IL1 hereafter, as shown in figure 1.1 (b). CPU core fetches instructions from either IL1 or loop buffer. Due to its limited, a loop buffer can provide instructions to CPU core at a very low power level. And the best pieces of code to be placed in a loop buffer will be innermost loops, since their executions tend to repeat many times. As an evidence, MiBench spends 71.22% of execution time on innermost loops.

Figure 1.1: (a) Organization of CPU core, IL1, and filter cache;

(b) Organization of CPU core, IL1, and loop buffer

#### 1.2 The Problems of Loop Buffer to Store Branch(es)

The loop buffer is a simple instruction buffer without tag, so that the management of loop buffer is different from cache. In general, loop buffer need an address generator to determinate whether the fetched instruction is in loop buffer and calculate where the fetched instruction address is in loop buffer.

Since the instructions fetch are usual in sequent order, we can place these sequent instructions into loop buffer in the same order, so that address generator of loop buffer can be implement by a counter to avoid area and delay overhead. An example for a sequent fetch code segment (i.e. a code segment without branch) is in figure 1.2.

On the other hand, the addresses of instruction fetch are not sequent between a branch and the next instruction after this branch, so that the address generator of loop buffer using a counter can not determinate whether this instruction after a branch has been stored in loop buffer at run time. An example for a code segment

with a branch is in figure 1.3.

Since the address generator of loop buffer can not handle the code segment with a branch, the utilization of loop buffer is limited.

| Instruction | Address of next instructions | Address in loop buffer |

|-------------|------------------------------|------------------------|

| Non-branch  | PC+4                         | next (+1)              |

Figure 1.2: A code segment without branch

| Instruction | Address of next instructions | Address in loop buffer |

|-------------|------------------------------|------------------------|

| Non-branch  | PC+4                         | next (+1)              |

| Branch      | PC+46                        | next (+1)              |

| Unknown     | PC+4 / target                | Unknown                |

| Unknown     | Unknown                      | Unknown                |

Figure 1.3: A code segment with a branch

#### 1.3 Motivations and Objectives

To maximize the power advantage, a loop buffer should store innermost loops with forward branch(es) and subroutine(s). For example, MiBench spends 38.32% of execution time on innermost loops with forward branch(es) and subroutine(s) without backward branch. It is over half of total execution time on innermost loop.

However, to avoid design complexity, most loop buffer designs are capable of storing only innermost loops without forward branch [14, 15] or instructions within

innermost loops before a forward branch [15]. Since many applications consist of forward branch(es) in their innermost loops, utilization of loop buffer and reduction in instruction fetch power in [14, 15] is limited.

To increase utilization of loop buffer, [16, 17] propose a loop buffer consisting of an additional address generator to store any kinds of code segment. Before fetching instruction from loop buffer, address generator must generate an address and use this address to determine whether this instruction has been stored in loop buffer and if it is, where it is located.

Consequently, this address generator leads to a significant increase in power and fetch latency. In addition, most designs [14, 16, and 17] require compiler help to insert special instruction(s) in program to start filling instructions into loop buffer [14, 17] or to determine which code segments should be stored in loop buffer [16]. Recompilation and code compatibility issues hence arise.

To increase utilization of loop buffer without introducing much overhead, we use BTB to assist loop buffer in storing the innermost loops with following characteristics:

- (1) they can contain forward branch(es) and

- (2) they can call any number of subroutines as long as these subroutines have no loop inside.

In our design, an extra bit is added in branch target buffer (BTB) to record forward branch outcome. This bit indicates whether the loop buffer stores the fall-through or target trace after a forward branch. The subroutine including no loop is also handled by using similar way. Notice also that different form previous designs [14, 16, and 17], our approach does not need special branch instruction or compiler to assist loop buffer controller in innermost loop detection.

Results with MiBench indicate that our design can further reduce 18.00% and

14.61% instruction fetch power compared with only capable of innermost loop without forward branch and [15], respectively.

#### 1.4 Organization of This Thesis

The remaining parts of this thesis are organized as follows. In Chapter 2, we examine some related the previous work. In Chapter 3, we present our proposed loop buffer design. In Chapter 4, we show the simulation results and discussion. Finally, in Chapter 5, we give the conclusions of this work.

#### **Chapter 2**

#### **Background and Related Work**

In Section 2.1 we divide the execution time of program into four categories that have different nature of execution flows. In Section 2.2, we survey the related researched in improving the loop buffer.

#### 2.1 Categorization of Execution Time of Program

We divide the execution time of program into five categories which have different nature of execution flow:

Type A is innermost loop without forward branch and without subroutine. The addresses of instruction in Type A are sequent from the first instruction of innermost loop to the last instruction of innermost loop and the execution flow in this type is exclusive.

Type B is innermost loop with forward branch(es) but without subroutine. The addresses of instruction in Type B may not be sequent because of forward branch taken so that the execution flow in this type could not be exclusive, and the addresses of instruction in execution flow are within from the first instruction of innermost loop to the last instruction of innermost loop.

Type C is innermost loop with subroutine(s) consisting of no loop and it may contain forward branch(es) or not. If we inline the subroutine(s) in Type C, Type C will convert to Type A or Type B. Since an innermost loop with subroutine(s) consisting of loop(s) can not be called an innermost loop, we classify it into Type D. others. Unlike Type B, the addresses of instruction in subroutine(s) will beyond from the first instruction of innermost loop to the last instruction of innermost loop.

*Type D* is the outer loop of a nested loop.

*Type E* is others witch we consider that the execution flow is not in any loop.

As an evidence, MiBench spends 71% of execution time on innermost loops which include *Type A*, *Type B* and *Type C*, and 79.85% of execution time on loops. MiBench is a benchmark suite for embedded processor. The profiling results of each category are shown in brackets at the right of figure 2.1. More detail profiling results of each benchmark are shown in Appendix A-1.

Figure 2.1: Profile the execution time of MiBench

#### 2.2 Related Research and Technology

In this section, we study the research and technology related to our thesis including dynamic loop cache, hardware-based two-way loop buffer, pre-load loop cache, and cluster loop cache.

#### 2.2.1 Dynamic Loop Cache

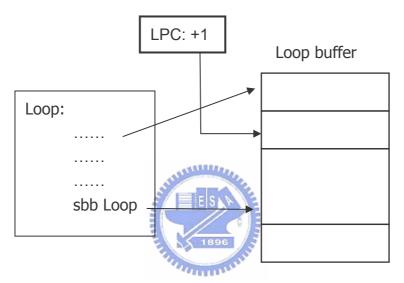

[14] is capable of storing only innermost loops without forward branch. To indicate where a backward branch exists, [14] uses a special branch instruction

"sbb". If a "sbb" is detected and taken, loop buffer controller starts to fill instructions into loop buffer. Only if a "sbb" is detected and taken twice successively, CPU core starts to fetch instructions from loop buffer until this "sbb" is detected but not taken, meaning the loop is being exited. To reduce design complexity, [14] uses a counter to generate loop buffer addresses, called loop buffer program counter (LPC). The management of Dynamic Loop Cache is shown in figure 2.2.

Figure 2.2: the management of Dynamic Loop Cache

If the entire loop does not fit in the loop cache, then the cache will be filled completely with the first part of the loop, so that CPU core fetch instructions will switch between loop buffer and IL1. [14] also explored a "warm-fill" version of the dynamic loop buffer that continually filled the loop buffer on every instruction fetch so that at any given time, the last N instructions were available in the loop buffer, where N is the loop buffer size. However, [14] showed that this design yielded little benefit—the power savings of being able to switch to loop buffer fetching immediately after detecting a "sbb" do not outweigh the power overhead for keeping the loop buffer filled.

Because filling of [14] is nonintrusive (i.e., no microprocessor stall occurs), a control of flow change (cof) which will cause the next instruction address is not the current address plus one, but the loop buffer may not get filled with the entire loop. Thus, in [14], a cof (other than the triggering sbb) encountered within a small loop would immediately terminate the loop cache filling or fetching. In other words, only loops without any cof were supported so that utilization of loop buffer and the reduction in instruction power are limited.

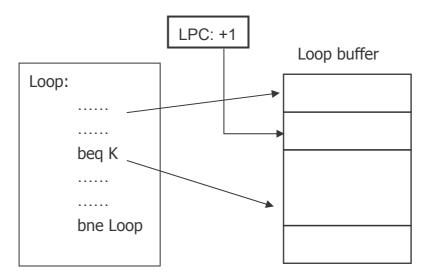

#### 2.2.2 Hardware-Based Two-Way Loop Buffer

Instead of using a special branch instruction "sbb" in [14], [15] deploys a special register to record the address of backward branch. Once a backward branch is detected and taken twice successively, loop buffer controller starts to fill instructions into loop buffer. After successively filling, CPU core begins to fetch instructions from loop buffer. We also use this method to detect an innermost loop in this paper. Unlike [14], [15] can also store instructions within an innermost loop from first instruction of loop until a forward branch or a subroutine call. This is because instruction addresses from first instruction of loop until a forward branch or subroutine call are sequentially (i.e., there is no cof from first instruction of loop until a forward branch or subroutine call). To reduce design complexity, [15] also uses a counter to generate LPC so that [15] encounters the same limitation with [14]. The management of Hardware-Based Two-Way Loop Buffer is shown in figure 2.3.

Figure 2.3: the management of Hardware-Based Two-Way Loop Buffer

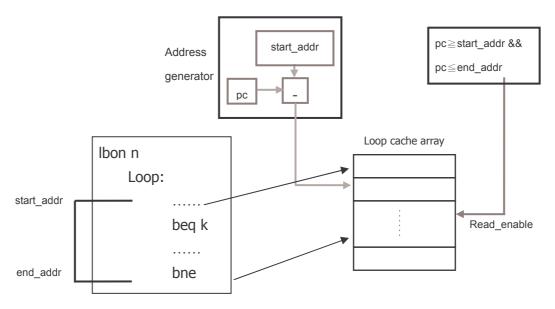

#### 2.2.3 Pre-load Loop Cache

[16] is capable of storing many kinds of code segment in which instruction addresses must be sequential. In [16], which code segment can be stored in loop buffer are analyzed statically. After the CPU booting, several code segments and their start address (start\_addr) and end address (end\_addr) are filled into loop buffer and special registers, called loop address registers (LARs), respectively. CPU core then continuously compares each instruction address with LARs to determine whether start and terminate to fetch instructions from loop buffer. This leads to inflexible usage of loop buffer. Since code segments stored in loop buffer may consist of forward branch, [16] uses an address generator to cope with non-sequential instruction fetch. Before fetching one instruction from loop buffer, loop buffer controller must wait for LPC calculated by address generator and use LPC to determine whether this instruction has been stored in loop buffer and where this instruction is. Consequently, this address generator leads to a great increase on instruction fetch latency and hardware cost. The management of Pre-load Loop Cache is shown in figure 2.4.

Figure 2.4: the management of Pre-load Loop Cache

#### 2.2.4 Cluster Loop Cache

To dynamically fill code segments into loop buffer, [17] uses a special instruction "lbon n", where n is number of instruction should be filled into loop buffer, to indicate where start to fill instructions into loop buffer. [17] also uses the same method to calculate LPC so that [17] encounters the same difficulties with [16]. The management of Cluster Loop Cache is similar to Pre-load Loop Cache which is already shown in figure 2.4.

Except for [15], all designs [14, 16, and 17] use compiler to assist in loop detection. This causes that program(s) must be recompiled in order to execute on a CPU containing one of these designs.

#### **Chapter 3**

# Design of the Forward-Branch and Subroutine Bufferable Innermost Loop Buffer

In this chapter, we present the approach of our buffering mechanism which can store innermost loop with forward branch(es) and subroutine(s). In Section 3.1, we describe the features of our approach. In Section 3.2, we present the architecture and design issues of our approach in detail. In Section 3.3, we propose a possible design for our approach.

#### 3.1 Features of Our Approach

In order to avoid the increase in the hardware design complexity, and can store innermost loop with forward branch and no-loop-inside subroutine, we add an extra bit in BTB to indicates whether the loop buffer stores the fall-through or target trace after a forward branch. No-loop-inside subroutine is also handled by the similar way. Here, we list several features of our approach as follows:

- 1. Loop buffer is a tagless memory unit.

- 2. Only one innermost storable.

- 3. Each entry in loop buffer only stores one instruction.

- 4. Instruction sequence in loop buffer is same with instruction trace, i.e. loop buffer only stores one execution path of innermost loop. This is because we does not employ extra address generator in our design, instructions must be fetched from loop buffer in sequence order.

Dynamically filling and refilling instructions according to runtime branch behaviors.

#### 3.2 Architecture and Design Issues of Our Approach

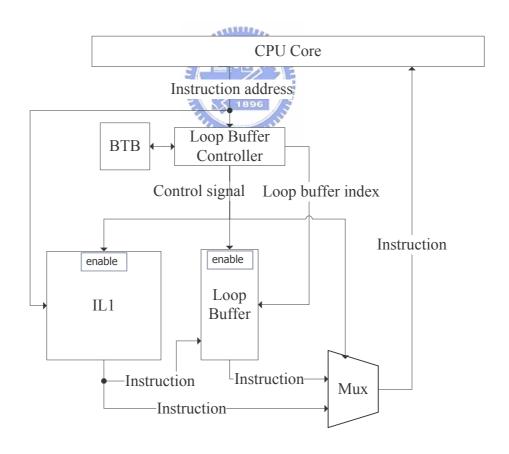

In our approach, only one innermost loop can be stored in loop buffer. Since we does not employ extra address generator in our design, instructions must be fetched from loop buffer in sequence order such that only one execution path in innermost loop can be stored. To achieve these objects, we propose a design approach of loop buffer, as illustrated in figure 3.1. The main components consist of loop buffer, loop buffer controller and FD-bit (filled direction bit) in BTB.

Figure 3.1: Architecture of our approach

Loop buffer controller is responsible for:

- (1) innermost loop detection;

- (2) filling or refilling an innermost loop into loop buffer;

- (3) determining that CPU core should fetch intrusions from loop buffer or IL1;

- (4) handling incorrect instruction filling and fetching due to branch miss-prediction; and

- (5) subroutine handling.

These five design issues will be introduced in detail later. FD-bit records the branch perdition result during filling or refilling instructions into loop buffer. It assist loop buffer controller in determining whether the loop buffer stores the fall-through or target trace after a forward branch.

#### 3.2.1 Innermost Loop Detection

The objectives of innermost loop detection are as follow:

- (1) Detecting an innermost loop as early as possible to increase loop buffer utilization; and

- (2) Reducing the miss-detection rate such that energy overhead caused by miss-detection is low

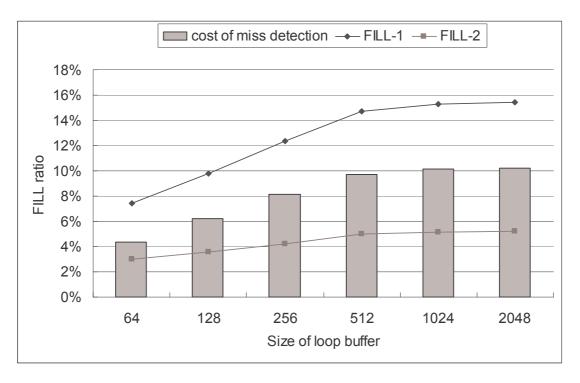

However, both objectives conflict each other. We therefore propose two innermost loop detection policies which are aimed at different objectives in this thesis. First, called FILL-1, if a backward branch is taken once, we identify that an innermost loop is detected. Second, called FILL-2, an innermost loop is detected only if a same backward branch is taken twice successively.

Since FILL-1 is more aggressive than FILL-2, it can increase loop buffer utilization. But FILL-1 has higher miss-detection rate such that it may cause higher power consumption. The power simulation of both policies will be shown in later

chapter.

We also can use a special instruction as "sbb" proposed in [1] to indicate that the execution flow is in an innermost loop at run time, but it need compiler to support.

During detecting an innermost loop, loop buffer controller also determines whether this innermost loop exists in loop buffer or not. If yes, the following instruction sequence has been stored in loop buffer, CPU core can immediately fetch instruction from loop buffer. If no, the current detected innermost loop is not same with one in loop buffer, and the following instruction sequence should be filled into loop buffer right now.

To determine whether this innermost loop exists in loop buffer or not, we add an extra register, called L\_addr, to record the start or end address of an innermost loop been stored in loop buffer. If the program counter value is the same with L\_addr, it indicates that the following instructions sequence has been stored in loop buffer. Otherwise, loop buffer controller should start to fill following instruction sequence into loop buffer.

Advantage of using start address is detecting existed innermost loop in one loop iteration in advance. Using end address has the advantage of fetching instructions from first one in innermost loop. However, using start address would cause that CPU core must start to fetch instructions from second one due to the delay of comparing L\_addr with start address of an innermost loop. An innermost loop is detected until CPU core fetches the last instruction of one, if using end address.

#### 3.2.2 Filling or Refilling an Innermost Loop Into Loop Buffer

Since only one execution path can be stored into loop buffer in our approach, we must determine which execution path should be stored into loop buffer.

Intuitively, the most frequently executed path should be stored. However, detecting the most frequently executed path would take a period of time such that loop buffer utilization is reduced. Therefore, the objective of filling or refilling an innermost loop into loop buffer has two:

- (1) filling or refilling instructions as early as possible; and

- (2) trying to fill or refill the most frequently executed path.

These are very similar with innermost loop detection.

To meet different objectives, we propose several filling or refilling policies. Loop buffer controller starts to fill instructions if first, partial or all forward branch(es) in innermost loop are predicted as strongly or weakly taken(non-taken), after detecting a innermost loop.

Refilling is executed when the execution path in innermost loop had changed. Similar to filling strategy, refilling is started only if first, partial or all forward branch(es) in innermost loop change its or their prediction result from strongly or weakly taken/non-taken to non-taken/taken.

During filling or refilling, the branch prediction result of each forward branch stored in loop buffer and the start or end address of innermost loop are recorded into FD-bit and L\_addr respectively. After filling or refilling, loop buffer controller must count how many instructions are stored in loop buffer and record this result in an extra register, called L\_leng.

During fetching instructions from loop buffer, loop buffer controller uses a counter to count how many instructions have been fetched. Once the counter counts down to zero, CPU core will fetch instructions from IL1 instead of loop buffer and loop buffer controller must start to detect innermost loop again.

In this paper, we employ the most aggressive policy for both filling and refilling, i.e. loop buffer controller starts to fill or refill instructions without

considering each forward branch's state (strongly or weakly taken/non-taken). In other word, loop buffer controller only follows instruction fetching sequence to fill or refill instructions. This is because that only 0.67% of branch prediction results in an innermost loop changes from weakly taken/non-taken to weakly non-taken/taken, i.e. the execution path in an innermost loop changes infrequently. Using the most aggressive policy can lead to higher loop buffer utilization such that more instruction fetch power is reduced.

### 3.2.3 Determining that CPU Core Should Fetch Intrusions From Loop Buffer or IL1

There are four situations that CPU core should fetch instructions from IL1 as follows:

- 1. No innermost loop is detected.

- 2. Loop buffer controller has detected an innermost loop, but not successfully fills or refills instructions into loop buffer.

- 3. Loop buffer is full due to a BIG loop which its size is larger than loop buffer's capacity.

- 4. The execution path has changed, but instructions located on new execution path do not be stored in loop buffer. We call this situation as loop buffer miss.

First and second situation can be determined according to the current status of loop buffer controller. The current status means current action of loop buffer controller, such as innermost loop detection, filling or refilling instructions ... etc. Comparing L\_leng with the size of loop buffer, third situation can be solved. Fourth situation can be determined according to the comparing result of FD-bit with branch prediction result. This is because FD-bit can indicate that the loop buffer stores the

### 3.2.4 Handling Incorrect Instruction Filling and Fetching due to Branch Misprediction

The reason why we need to handle branch misprediction during fetching or filling instructions is that branch misprediction means the execution path has changed and instructions followed a mispredicted branch do not exist in loop buffer.

The simplest method which copes with forward branch misprediction during filling instructions into loop buffer is flushing all instructions which have been filled into loop buffer. However, since instruction sequence before a mispredicted forward branch is same, this method is an inadvisable one. We therefore propose second method that loop buffer controller just counts back M entries from current position and then refills instructions located at another control path. M is number of pipeline stages between instruction fetch (IF) and execution stage (EXE). Since an innermost loop has been successfully filled into loop buffer before a mispredicted backward branch, loop buffer controller just lets CPU core fetch instructions from IL1 without flushing instructions in loop buffer.

In another situation, i.e. during fetching instructions from loop buffer, a forward or backward branch misprediction indicates that the execution path has changed. Loop buffer controller therefore should let CPU core fetch instructions from IL1.

An exception happened when a new BTB entry created caused by misprediction and replaced the prediction result and FD-bit of branch in BTB entry during Loop detecting, which this branch is stored in loop buffer. Loss of the FD-bit record will make the loop buffer controller fail to determine CPU core should fetch instruction from loop buffer or IL1. If this situation occurred, we should flush loop

buffer.

Recognizing the FD-bit of branch which is stored in loop buffer at present of innermost loop or in the pass of innermost loop can not implement straightforward, because the FD-bit of branch which is stored in loop buffer in the pass of innermost loop would not be clean. To avoid the design complexity of detecting and handling this exception, we propose a simple approach. When a new BTB entry created caused by misprediction during loop detecting, L\_addr will be clean so that loop buffer controller can not detect this innermost loop which already filled in loop buffer. Our simulation of MiBench is shown that this approach has decreased the utilization of loop buffer only 0.03% compared by the case of exception has never happened.

#### 3.2.5 No-loop-inside Subroutine Handling

Subroutine call and subroutine return can be automatically handled by BTB and return stack, respectively. To store no-loop-inside subroutine in loop buffer, we only need to handle two situations:

- (1) CPU core has no return stack; and

- (2) return stack is full.

In fact, case 1 and 2 is same due to a full return stack means CPU core can not store any return address into return stack, i.e. return stack is useless at this moment. Therefore, we only need to handle one of situations.

The basic idea of handling subroutine return is to fill but disregard these invalid instructions followed with subroutine return. Since a subroutine return is an always-taken branch, CPU core without return stack always fetches G invalid instructions. According to when the subroutine return is detected by CPU core, G has two different values:

(1) G is number of pipeline stages between IF and EXE; and

loop buffer, the instruction fetch sequence is held.

(2) G is number of pipeline stages between IF and instruction decoder (ID). However, these invalid instructions would be automatically flushed by CPU core and do not affect the correctness of program. If we store G invalid instructions into

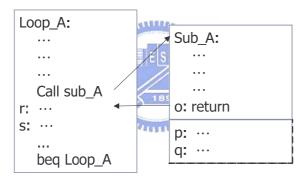

We use the figure 3.2 to explain this idea. Here, a five pipeline stages CPU core without return stack is assumed in this example. When Sub\_A returns to Loop\_A, the instruction fetch sequence is o (subroutine return), p, q, r, and s in which p and q are invalid instructions. If we also follow the same instruction fetch sequence, i.e. o, p, q, r and s, to fill instructions into loop buffer, the fetch sequence is held.

Figure 3.2: An innermost loop consists of subroutine

#### 3.3 Operation

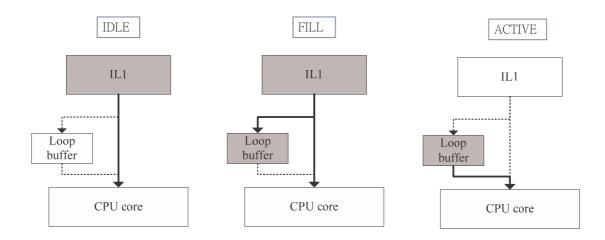

In this section, we propose a possible design for our approach and describe it as follows. The operation status of our design which is similar with [1] consists of three states: IDLE, FILL and ACTIVE. In the figure 3.3, the gray rectangle and the solid black line are currently accessing block and bus respectively during different states.

Figure 3.3: Memory accessing in different states

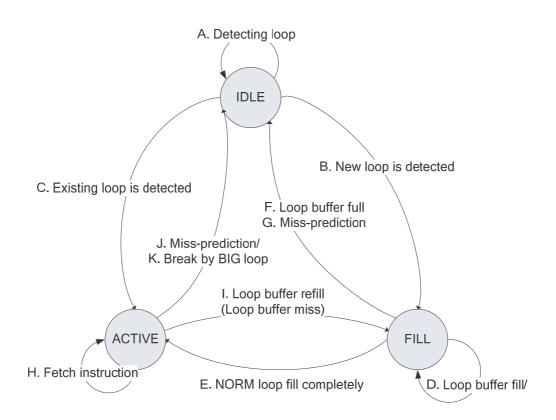

The state diagram of the loop buffer controller's finite state machine (FSM) is shown in the figure 3.4. When CPU core initializes or resets, loop buffer controller enters IDLE state first. During IDLE state, loop buffer controller continuously detects an innermost loop, as action A. Action C is taken if and only if an innermost loop has been detected and this innermost loop has been stored in loop buffer. Otherwise, loop buffer controller would enter FILL state, as action B. When BTB entry created caused by misprediction, L\_addr will be clean.

There are two possible policies for detecting the innermost loop by a backward branch taken once or twice, respectively, denoted "FILL-1" and "FILL-2"; and two possible policies for detecting the innermost loop which has been stored in loop buffer are recording the start or end address of this innermost loop, denoted "START" and "END". The policies "FILL-1" and "START" are more aggressive than "FILL-2" and "END", respectively. The best choice of those policies in our simulation is "FILL-1" and "END". We will show the simulation result at next chapter.

During FILL state, instructions are sequentially filled into loop buffer from first entry, as action D. In the meanwhile, the branch predicted result of each forward branch stored in loop buffer and the start or end address of innermost loop are also recorded into FD-bit and L\_addr respectively. After successfully filling all instructions, loop buffer controller counts how many instructions are stored in loop buffer and record this result in L\_leng and enters ACTIVE state, as action E. Loop buffer is full caused by a BIG loop would let loop buffer controller return to IDLE state, as action F. Action G would gives up this fill iteration and returns IDLE state when a forward branch miss-prediction occurs.

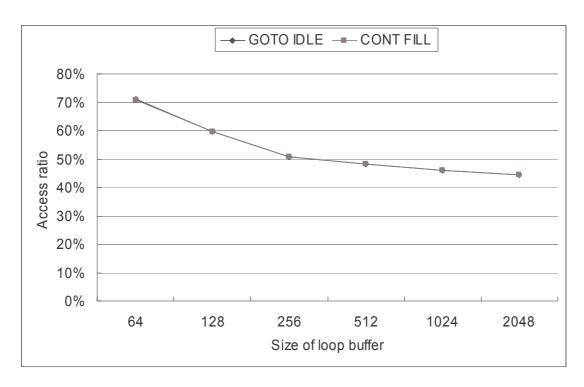

There two possible policies for handling miss-prediction of a forward branch. First policy is giving up this fill iteration and returns IDLE state, denoted "GOTO IDLE". Second policy is counting back M entries of loop buffer and continuing filled instructions, denoted "CONT FILL". "CONT FILL" is more aggressive than "GOTO FILL". The best choice of those policies is "GOTO IDLE" (i.e. Action G). We will show the simulation result at next chapter.

During ACTIVE state, CPU core fetches instructions from loop buffer instead of IL1, as action H. When loop buffer miss, CPU core fetches instructions from IL1 and return to FILL state as action I. When CPU core has already fetched last instruction of loop buffer (action K) or loop buffer controller encounters a branch miss-prediction (action J), loop buffer controller would enter IDLE state. First situation occurs when loop buffer encounters a BIG loop. Since loop buffer dose not store a whole BIG loop, loop buffer controller must enter IDLE state to let CPU core fetch other instructions of BIG loop from IL1 after the last instruction in loop buffer has fetched. The second situation, a branch miss-prediction occurs, indicates that the execution path has changed and loop buffer does not store instructions on this execution path. Hence, loop buffer controller must also enter IDLE state.

There are two possible policies for handling loop buffer miss. First policy is entering FILL state to store another execution path immediately, denoted "aFILL".

Second policy is entering FILL state when the branch prediction result is in strong state (i.e. strong taken or strong not taken), denoted "pFILL". "pFILL" can avoid the invalid loop buffer writing caused by prediction result changing frequently. "aFILL" is more aggressive than "pFILL". The best choice for handling loop buffer miss is "aFILL" (i.e. Action I).

There are three possible policies for handling miss-prediction of a forward branch. First policy is giving up this fill iteration and returns IDLE state, denoted "aIDLE". Second policy is counting back M entries of loop buffer and continuing filled instructions, denoted "aFILL". "aFILL" may cause more loop buffer miss, because not all miss-prediction will cause the branch prediction result changed prediction direction. Third policy is counting back M entries of loop buffer and continuing filled instructions when the branch prediction result is in weak state (i.e. weak taken or weak not taken), denoted "pFILL". "pFILL" can improve the disadvantage of "aFILL", because the branch prediction result changed prediction direction when the branch prediction result is in weak state and miss-prediction happened. The best choice of those policies is "pFILL" (i.e. Action J). We will show the simulation result at next chapter.

Figure 3.4: State diagram of loop buffer controller

# **Chapter 4**

# Simulation and Evaluation

In Chapter 3, we proposed the mechanism and architecture of our buffering mechanism which can store innermost loop with forward branch(es) and subroutine(s). In this chapter, we present the simulation result and evaluation of our design. In Section 4.1, we present the power model of instruction fetch power. In Section 4.2, we describe the simulation environment and the benchmark programs that we used in the simulation. In section 4.3, we present the simulation results for finding the best choice of loop buffer policies in each state of loop buffer. In section 4.4, we present the penalty caused by miss-prediction of loop buffer policies. In section 4.5, we analyses the reasons of affecting the loop buffer efficiency. In section 4.6, we present the simulation result for comparing other loop buffer managements and our analyses on them.

#### 4.1. Power Model

The instruction fetch power ( $P_{IF}$ ) per fetch dissipated by the loop buffer and lower level instruction memories can be expressed by equation (1):

$$P_{IF} = P_{IC} * R_{IC} + P_{LB} * R_{LB} + P_{ctrl}$$

(1)

where  $P_{IC}$  and  $P_{LB}$  are fetch power of lower level instruction memories and loop buffer respectively,  $R_{IC}$  and  $R_{LB}$  are access ratio of lower level instruction memory and loop buffer, respectively. In this paper,  $R_{IC}$  ( $R_{LB}$ ) is defined as the ratio of number of instruction fetch from of lower level instruction memory (loop buffer) to total number of instruction fetch, as expressed by equation (2):

$$R_{IC}(R_{LB}) = \frac{\text{number of instruction fetch from lower level memory (loop buffer)}}{\text{total number of instruction fetch}} *_{100\%} (2)$$

Since  $P_{IC}$  is not affected by operation strategy and size of loop buffer, we assume  $P_{IC}$  as a constant in this paper. Comparatively,  $P_{LB}$ ,  $R_{IC}$  and  $R_{LB}$  highly depend on the size of loop buffer.  $P_{ctrl}$  is the power consumed by loop buffer controller. Since loop buffer controller is always active, we assume that each instruction fetch would consume  $P_{ctrl}$ .

The loop buffer controller of each design is synthesized using Synopsys design tools in 0.18  $\mu m$  TSMC CMOS technology. The power consumptions of loop buffer and IL1 are calculated by Wattch power modeling tool. The ratios of  $P_{LB}$  and  $P_{IC}$  are shown in table 4.1. The power consumption of FD-bit is 0.13% of power consumption of  $P_{IC}$

Table 4.1: Ratio of PLE

| Size of loop buffer       | 64B   | 128B  | 256B   | 512B   | 1KB    | 2KB    |

|---------------------------|-------|-------|--------|--------|--------|--------|

| $(P_{LB}/P_{IC}) * 100\%$ | 8.26% | 8.92% | 10.35% | 13.56% | 21.40% | 38.34% |

#### 4.2 Simulation Environment

In Section 4.2.1, we describe the simulation tools that we used. In Section 4.2.2, we describe the benchmark programs that we used in the simulation.

#### 4.2.1 Simulator

We use SimpleScalar/ARM simulator [18] to evaluate each design. SimpleScalar is an execution-driven simulator and used to simulate modern processor architectures.

The power evaluation of loop buffer, BTB and IL1 is based mainly on the

Wattch [20] power modeling tool. The loop buffer controller of each method is synthesized using Synopsys design tools.

In this thesis, we experimented with the different sizes of loop buffer, included 64, 128, 256, 512, 1024 and 2048 bytes (B). Other parameters used in SimpleScalar are shown in the table 4.2.

Table 4.2: Parameters setting in SimpleScalar/ARM

| Parameter        | Value                              |  |

|------------------|------------------------------------|--|

| Loop buffer      | 64B, 128B, 256B, 512B, 1KB and 2KB |  |

| IL1              | 8KB, direct-mapped, 32B line       |  |

| Branch predictor | Bimodal                            |  |

| ВТВ              | 512-set, 4-way                     |  |

| Return stack     | No return stack                    |  |

## 4.2.2 Benchmark Programs

The benchmark programs that we use are from MiBench suite [19]. These benchmarks are divided into six suites with each suite targeting a specific area of the embedded market. The six categories are Automotive and Industrial Control, Consumer Office Automation, Devices. Networking, Security, and Telecommunications. All the programs are available as standard C source code so that it focuses on portable applications written in high-level languages as processor architecture and software developers are moving in this direction. Where appropriate, there provide a small and large data set. The small date set represents a light-weight, useful embedded application of benchmark, while the large data set provides a more stressful, real-world application. We use the large data set in this thesis. All the programs of Mibench are publicly available and widely used on general purpose

processors. Table 4.3 gives the description of the benchmark programs that we used.

Table 4.3: MiBench workloads

| Description                                                     |

|-----------------------------------------------------------------|

| trial Control                                                   |

| Testing the bit manipulation abilities of a processor by        |

| counting the number of bits in an array of integers.            |

| Sorting a large array of strings into ascending order using the |

| well known quick sort algorithm.                                |

| Susan is an image recognition package. It was developed for     |

| recognizing corners and edges in Magnetic Resonance             |

| Images of the brain and it can smooth an image and has          |

| adjustments for threshold, brightness, and spatial control.     |

|                                                                 |

| JPEG is a standard, lossy compression image format and it is    |

| commonly used to view images embedded in documents.             |

| Tiff2bw converts a color TIFF image to black and white          |

| image.                                                          |

| Tiff2rgba converts a color image in the TIFF format into a      |

| RGB color formatted TIFF image.                                 |

| Tiffdither dithers a black and white TIFF bitmap to reduces     |

| the resolution and size of the image at the expense of clarity. |

| Tiffmedian converts an image to a reduced color palette by      |

| taking several medians of the current color palette.            |

| A GPL'ed MP3 encoder that supports constant, average and        |

|                                                                 |

|                   | variable bit-rate encoding.                                    |

|-------------------|----------------------------------------------------------------|

| mad               | A high-quality MPEG audio decoder.                             |

|                   | Typeset is a general typesetting tool, that has a front-end    |

| typeset           | processor for HTML.                                            |

| Office Automation |                                                                |

| chastsorint       | Ghostscript is a postscript language interpreter without its   |

| ghostscript       | graphical interface.                                           |

| gtringgoorgh      | This benchmark searches for given words in phrases using a     |

| stringsearch      | case insensitive comparison algorithm.                         |

| ignall            | Ispell is a fast spelling checker that is similar to the Unix  |

| ispell            | spell, but faster.                                             |

| rsynth            | Rsynth is a text to speech synthesis program that integrates   |

| rsyntii           | several pieces of public domain code into a single program.    |

| Networking        |                                                                |

| dijkstra          | Calculating the shortest path between every pair of nodes      |

| ujkstra           | using repeated applications of Dijkstra's algorithm.           |

| patricia          | Patricia tries are used to represent routing tables in network |

| рантета           | applications.                                                  |

| Security          |                                                                |

| blowfish encrypt  | A symmetric block cipher with a variable length key.           |

| blowfish decrypt  | A symmetric block cipiler with a variable length key.          |

|                   | SHA is the secure hash algorithm that produces a 160-bit       |

| sha               | message digest for a given input. It is often used in the      |

| Siia              | secure exchange of cryptographic keys and for generating       |

|                   | digital signatures.                                            |

|                    | Rijndael was selected as the National Institute of Standards |  |  |

|--------------------|--------------------------------------------------------------|--|--|

| rijndael encrypt   | and Technologies Advanced Encryption Standard (AES). It      |  |  |

|                    | is a block cipher with the option of 128-, 192-, and 256-bit |  |  |

| rijndael decrypt   | keys and blocks.                                             |  |  |

| Telecommunications |                                                              |  |  |

| FFT                | A Fast Fourier Transform and its inverse transform on an     |  |  |

| IFFT               | array of data.                                               |  |  |

| GSM encode         | The Global Standard for Mobile (GSM) communications is       |  |  |

|                    | the standard for voice encoding/decoding in Europe and       |  |  |

| GSM decode         | many countries.                                              |  |  |

| ADPCM encode       | The encoder and decoder of Adaptive Differential Pulse       |  |  |

| ADPCM decode       | Code Modulation                                              |  |  |

| CRC32              | A 32-bit Cyclic Redundancy Check (CRC) on a file             |  |  |

# 4.3. Simulation Results of Loop Buffer Policies

In the following sections, we will show our simulations and the analysis for finding the best choice of the loop buffer policies in each state. In section 4.3.1, we describe loop buffer policies in each state briefly. In section 4.3.2, we present the access ratio of loop buffer and lower level memory and instruction fetch power reduction for these loop buffer policies.

# 4.3.1 Loop Buffer Policies in Each loop Buffer state

There are three states of loop buffer, IDLE state, FILL state, ACTIVE state.

In IDLE state, we handle the loop buffer detection. To detect the innermost loop, we propose two policies "FILL-1" and "FILL-2". "FILL-1" and "FILL-2" are

detecting innermost loop when a backward branch taken once or twice successive, respectively. "FILL-1" is more aggressive than "FILL-2". The hardware cost of "FILL-1" is less than "FILL-2", because "FILL-2" needs more one register to record the backward branch then "FILL-1".

To detect the innermost loop which has been stored in loop buffer, we propose two policies "START" and "END". "START" and "END" are detecting the innermost loop which has been stored in loop buffer by recording the start or end address of this innermost loop, respectively. "START" is more aggressive than "END". The hardware cost of "END" is less then "START", because "END" can use BTB to assist record the end address of this innermost loop.

In FILL state, we handle the execution path changed caused by branch miss-prediction. To handle miss-prediction, we propose two policies "GOTO IDLE" and "CONT FILL" are entering IDLE state or filling the changed execution path into loop buffer, respectively. "CONT FILL" is more aggressive than "GOTO IDLE". The hardware cost of "GOTO IDLE" is less than "CONT FILL" because "CONT FILL" needs extra logic (for example, another counter) to count back the index in loop buffer to the next entry of this miss-prediction branch.

In ACTIVE state, we handle the execution path changed caused by loop buffer miss (i.e. branch prediction direction is not equal to FD-bit) or branch miss-prediction. To handle loop buffer miss, we propose two policies "aFILL" and "pFILL" are filling the changed execution path immediately or when the branch prediction result is in strong state, respectively. "aFILL" is more aggressive than "pFILL". The hardware cost of "aFILL" is less then "pFILL", because "pFILL" needs extra logic to determinate whether the prediction result is in strong state or not.

To handle the branch miss-prediction, we propose three policies "aIDLE", "aFILL", "pFILL". "aIDLE" is entering IDLE state without any changing. "aFILL" and "pFILL" are filling the changed execution path immediately or when the branch prediction result is in weak state, respectively. "aFILL" is more aggressive than "pFILL" and "aIDLE", but "aFILL" may cause more loop buffer miss because not all branch miss-prediction would cause prediction direction changed. The hardware cost of "aIDLE" is less than "aFILL" and "pFLLL", because "aFILL" or "pFILL" needs extra logic (for example, another counter) to count back the location in loop buffer to the next entry of this miss-prediction branch.

We summarize the policies of loop buffer in each state of loop buffer to table 4.4. There are 48 cases of loop buffer policies set totally.

Table 4.4: Policies of loop buffer in each state of loop buffer

| State of Loop buffer | Handling event                         | Policy    |

|----------------------|----------------------------------------|-----------|

|                      | Detecting the innerment lean           | FILL-1    |

| IDI E                | Detecting the innermost loop           | FILL-2    |

| IDLE state           | Detection the innermost loop stored in | START     |

|                      | loop buffer                            | END       |

| FILL state           | Branch miss-prediction                 | GOTO IDLE |

| FILL State           | Branch miss-prediction                 | CONT FILL |

|                      | Loop buffer miss                       | aFILL     |

|                      | Loop ounce miss                        | pFILL     |

| ACTIVE state         |                                        | aIDLE     |

|                      | Branch miss-prediction                 | aFILL     |

|                      |                                        | pFILL     |

#### 4.3.2 Simulation Results of Loop Buffer Policies

To find the best choice of loop buffer policies set, we divide the simulation into two parts. First, we simulate each loop buffer policies in the same state of loop buffer and analysis them to find the local optimal. Second, we simulate loop buffer policies set to find the best choice of loop buffer policies set.

#### 4.3.2.1 Simulation Results of the Loop Buffer Policies in IDLE State

In IDLE state, we compare four loop buffer policies set list in table 4.5.

Table 4.5: Loop buffer policies sets (IDLE state)

| IDLE state     |                | FILL state      | ACTIVE state |                 |  |

|----------------|----------------|-----------------|--------------|-----------------|--|

|                | Detection the  |                 |              |                 |  |

| Detecting the  | innermost loop | Branch          | Loop buffer  | Branch          |  |

| innermost loop | stored in loop | miss-prediction | miss         | miss-prediction |  |

|                | buffer         |                 |              |                 |  |

| EH I 1         | END            |                 |              |                 |  |

| FILL-1         | START          | COTO IDI E      | erii i       | alDLE           |  |

| FILL-2         | END            | GOTO IDLE       | aFILL        | aIDLE           |  |

| FILL-2         | START          |                 |              |                 |  |

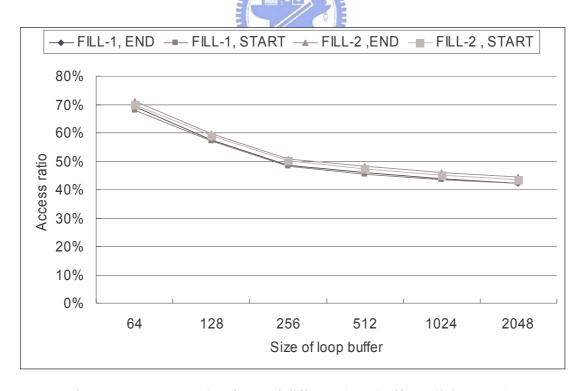

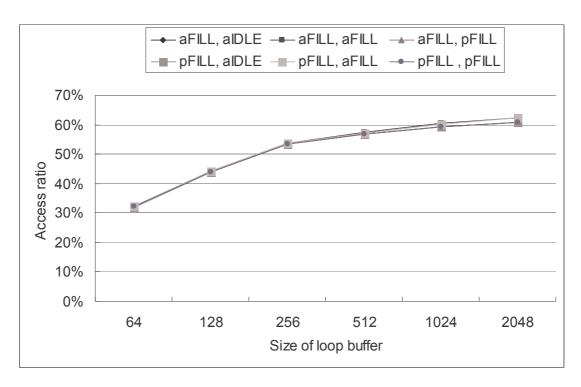

Figure 4.1 shown  $R_{IC}$  for different loop buffer policy sets in different loop buffer size. We examined the size of loop buffer from 64 to 2048 bytes, i.e. 16 to 512 instructions. Simulation results show that "FILL-1" and "SATRT" averagely further decrease  $R_{IC}$  by 2.20% and 0.41%, respective ("FILL-2" and "END").

Ideally, the R<sub>IC</sub> of ("FILL-1", "START") will decrease 8.33% than ("FILL-2", "END"), because that average number of innermost loop iterations are 12.41. The effects of the aggressive policies (i.e. "FILL-1" or "START") are limited, because of the nature of MiBench. If one benchmark has much execution time on innermost loop, these innermost loops also have a lot of loop iterations; on the other hand, if one benchmark has less execution time on innermost loop, these innermost loops have few loop iterations.

Figure 4.2 shown  $R_{LB}$  for different loop buffer policies sets in different loop buffer size. Simulation results show that "FILL-1" and "SATRT" averagely further increase  $R_{LB}$  by 10.32% and 0.39%, respective ("FILL-2" and "END").  $R_{LB}$  of "FILL-1" is more than "FILL-2" because of the invalid loop buffer filled caused of miss-detection of innermost loop.

Figure 4.1: Access ratio of IL1 of different loop buffer policies sets (IDLE state)

Figure 4.2: Access ratio of loop buffer of different loop buffer policies sets

Table 4.6 is the power consumption of loop buffer controller of different loop buffer policy sets.

(IDLE state)

Table 4.6: Ratio of P<sub>ctrl</sub> of different loop buffer policy sets (IDLE state)

|              | 64B   | 128B  | 256B  | 512B  | 1KB   | 2KB   |

|--------------|-------|-------|-------|-------|-------|-------|

| FILL1, end   | 1.91% | 1.95% | 2.00% | 2.08% | 2.25% | 2.34% |

| FILL1, start | 2.75% | 2.83% | 2.90% | 2.97% | 3.14% | 3.23% |

| FILL2, end   | 2.57% | 2.62% | 2.65% | 2.74% | 2.90% | 2.98% |

| FILL2, start | 3.41% | 3.49% | 3.55% | 3.63% | 3.79% | 3.87% |

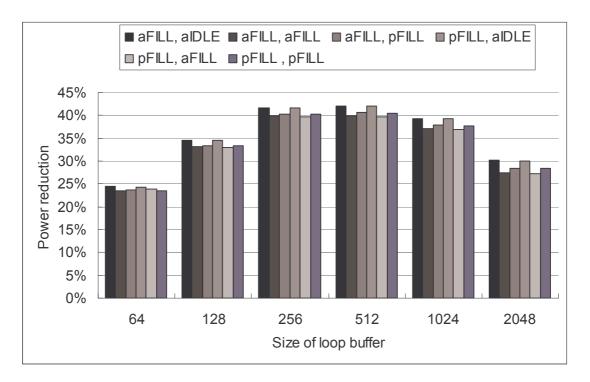

The reduction in instruction fetch power of different loop buffer policy sets is shown in the figure 4.3. For each loop buffer policies sets, 256B or 512B has the maximum power reduction. According to figure 4.1 and 4.2, increasing loop buffer size can improve  $R_{\rm IC}$  and  $R_{\rm LB}$  but also increases  $P_{\rm LB}$ . Hence, larger loop buffer may

be not beneficial for  $P_{IF}$ . The best loop buffer policies set of these four set is (FILL-1, END) because of the minimum power consumption of loop buffer controller.

Figure 4.3: Reduction in instruction fetch power of different loop buffer policies sets (IDLE state)

#### 4.3.2.2 Simulation Results of the Loop Buffer Policies in FILL State

In FILL state, we compare two loop buffer policies set list in table 4.7.

Table 4.7: Loop buffer policies sets (FILL state)

| IDLE state                   |                                             | FILL state             | ACTIVE state     |                        |

|------------------------------|---------------------------------------------|------------------------|------------------|------------------------|

| Detecting the innermost loop | Detection the innermost loop stored in loop | Branch miss-prediction | Loop buffer miss | Branch miss-prediction |

|        | buffer |           |        |       |

|--------|--------|-----------|--------|-------|

| EH 1 2 | END    | GOTO IDLE | oeii i | oIDLE |

| FILL-2 | END    | CONT FILL | aFILL  | aIDLE |

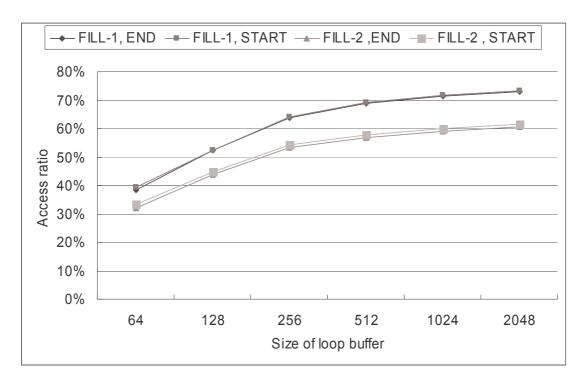

Figure 4.4 shown  $R_{IC}$  for different loop buffer policy sets in different loop buffer size. Simulation results show that "CONT FILL" averagely further decrease  $R_{IC}$  by 0.05% ("GOTO IDLE").

The effect of the aggressive policy—"CONT FILL" are limited, because of the execution time in FILL state is limited, just about 4.37% averagely, and the execution path changed ratio in FILL state which has been defined as expressed by equation (3) is 18.79%.

execution path ratio =  $\frac{\text{the number of loop iteration which has execution path changed}}{\text{total number of loop iteration}} *100\%(3)$

Figure 4.5 shown  $R_{LB}$  for different loop buffer policies sets in different loop buffer size. Simulation results show that "CONT FILL" averagely further increase  $R_{LB}$  by 1.66% ("GOTO IDLE").

Figure 4.4: Access ratio of IL1 of different loop buffer policies sets (FILL state)

Figure 4.5: Access ratio of loop buffer of different loop buffer policies sets (FILL state)

Table 4.8 is the power consumption of loop buffer controller of different loop

buffer policy sets. To implement "CONT FILL", we need add one counter to indicate the index of the next entry of the miss-prediction branch in loop buffer, and this counter will increase about 60% of power consumption of loop buffer controller.

Table 4.8: Ratio of P<sub>ctrl</sub> of different loop buffer policy sets (FILL state)

|           | 64B   | 128B  | 256B  | 512B  | 1KB   | 2KB   |

|-----------|-------|-------|-------|-------|-------|-------|

| GOTO IDLE | 2.57% | 2.62% | 2.65% | 2.74% | 2.90% | 2.98% |

| CONT FILL | 3.76% | 3.92% | 4.10% | 4.28% | 4.40% | 4.56% |

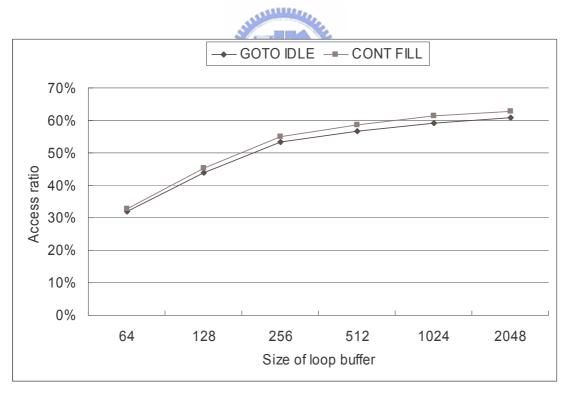

The reduction in instruction fetch power of different loop buffer policy sets is shown in the figure 4.6. The best loop buffer policies set of these two set is "GOTO IDLE", because that in "CONT FILL", the fetch power reduction of IL1 is less than the increasing of power consumption of loop buffer controller.

Figure 4.6: Reduction in instruction fetch power of different loop buffer policies sets (FILL state)

### 4.3.2.3 Simulation Results of the Loop Buffer Policies in ACTIVE State

In ACTIVE state, we compare six loop buffer policies set list in table 4.9.

Table 4.9: loop buffer policies sets (ACTIVE state)

| IDLE state     |                | FILL state      | ACTIVE state |                 |

|----------------|----------------|-----------------|--------------|-----------------|

|                | Detection the  |                 |              |                 |

| Detecting the  | innermost loop | Branch          | Loop buffer  | Branch          |

| innermost loop | stored in loop | miss-prediction | miss         | miss-prediction |

|                | buffer         |                 |              |                 |

|                |                |                 |              | aIDLE           |

|                |                | JULIU BERE      | aFILL        | aFILL           |

| EILL 2         | END            | ESTA            |              | pFILL           |

| FILL-2         | END            | GOTO IDLE       |              | aIDLE           |

|                |                | William.        | pFILL        | aFILL           |

|                |                |                 |              | pFILL           |

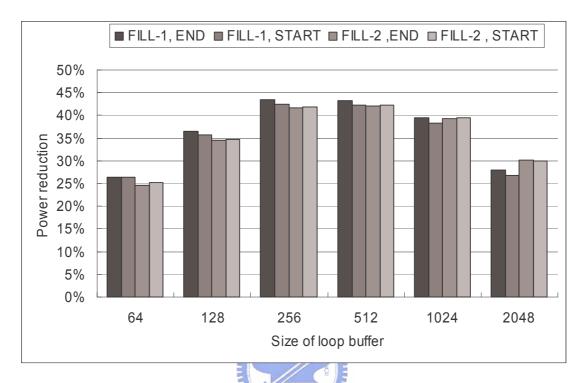

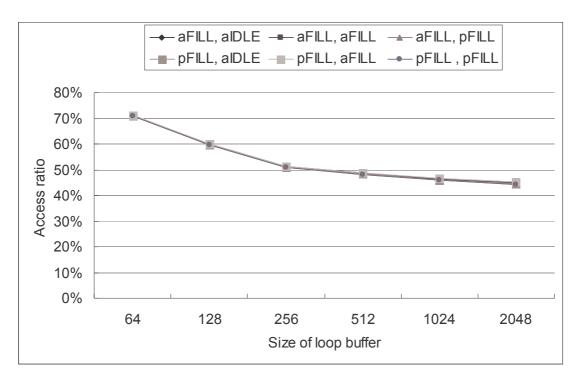

Figure 4.7 shown  $R_{IC}$  for different loop buffer policy sets in different loop buffer size. Simulation results show that the loop buffer miss handling policy—"aFILL" averagely further decrease  $R_{IC}$  by 0.12% ("pFILL"), and the branch miss-prediction handling policy—"pFILL" averagely further decrease  $R_{IC}$  by 0.13% / 0.45% ("aIDLE" / "aFILL").

The effects of the aggressive policies are limited; because of the execution path changed ratio in ACTIVE state is 1.90%. And it implies that the execution path changed seldom in ACTIVE state.

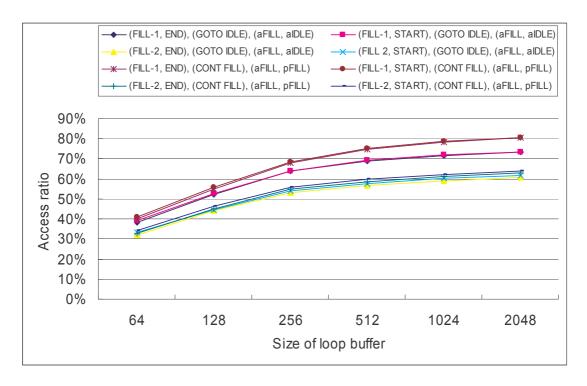

Figure 4.8 shown  $R_{LB}$  for different loop buffer policies sets in different loop buffer size. Simulation results show that the loop buffer miss handling policy—"aFILL" averagely further increase  $R_{LB}$  by 0.04% ("pFILL"), and the branch miss-prediction handling policy—"aIDLE" averagely further decrease  $R_{IC}$  by 0.79% / 0.14% ("aFILL" / "pFILL").

The results of  $R_{IC}$  and  $R_{LB}$  in branch miss-prediction handling policies show that "aFILL" will cause more invalid loop buffer filled but not decrease  $R_{IC}$ , and the best policy is "pFILL" which has least  $R_{IC}$  and limited increases  $R_{LB}$ .

The best policy of loop buffer miss handling is "aFILL" shown in the results, too.

Figure 4.7: Access ratio of IL1 of different loop buffer policies sets (ACTIVE state)

Figure 4.8: Access ratio of loop buffer of different loop buffer policies sets

(ACTIVE state)

Table 4.10 is the power consumption of loop buffer controller of different loop buffer policy sets. Like the policy—"CONT FILL" in FILL state, we need add one counter to indicate the index of the next entry of the miss-prediction branch in loop buffer.

Table 4.10: Ratio of P<sub>ctrl</sub> of different loop buffer policy sets (ACTIVE state)

|               | 64B   | 128B  | 256B  | 512B  | 1KB   | 2KB   |

|---------------|-------|-------|-------|-------|-------|-------|

| aFILL, aIDLE  | 2.57% | 2.62% | 2.65% | 2.74% | 2.90% | 2.98% |

| aFILL, aFILL  | 3.71% | 3.87% | 4.05% | 4.23% | 4.35% | 4.51% |

| aFILL, pFILL  | 3.78% | 3.94% | 4.12% | 4.30% | 4.42% | 4.58% |

| pFILL, aIDLE  | 2.67% | 2.72% | 2.75% | 2.84% | 3.00% | 3.08% |

| pFILL, aFILL  | 3.81% | 3.97% | 4.15% | 4.33% | 4.45% | 4.61% |

| pFILL , pFILL | 3.88% | 4.04% | 4.22% | 4.40% | 4.52% | 4.68% |

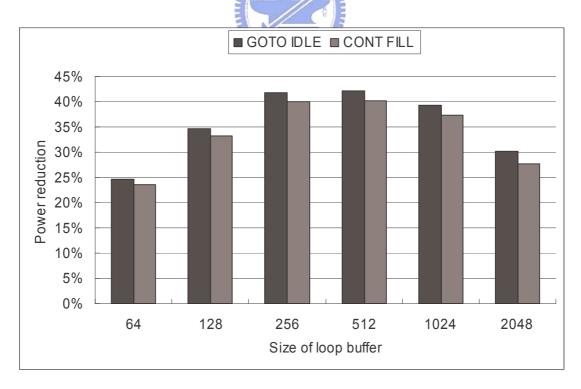

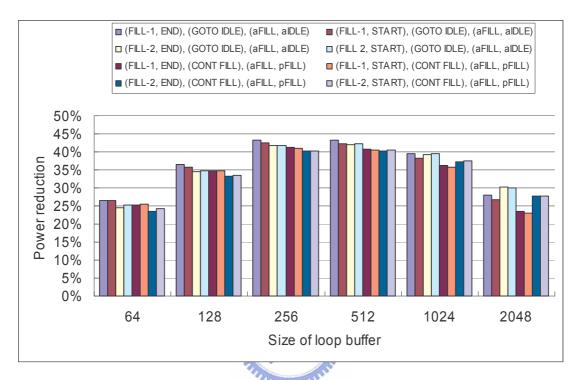

The reduction in instruction fetch power of different loop buffer policy sets is

shown in the figure 4.9. The best loop buffer policies set of these two sets is (aFILL, aIDLE), because that in the branch miss-prediction handling policy—"aFILL" and "pFILL", the fetch power reduction of IL1 is less than the increasing of power consumption of loop buffer controller, like the policy—"CONT FILL" in FILL state.

Figure 4.9: Reduction in instruction fetch power of different loop buffer policies sets (ACTIVE state)

#### 4.3.2.4 Simulation Results of the Best Loop Buffer Policies

Now we have the best policy in each state of loop buffer. In IDLE state, the best policy is "(FILL-1, END)"; in FILL state, the best policy is "GOTO IDLE"; in ACTIVE state, the best policy is "(aFILL, aIDLE)". The results show that the best policy in each state of loop buffer is the policy which has least power consumption of loop buffer controller, because that the power reduction of IL1 is less then the increase of power consumption of loop buffer controller in an aggressive policy like

#### "CONT FILL" in each state of loop buffer.