# 國立交通大學

電機學院與資訊學院 電子與光電學程

碩士論文

薄膜電晶體之暫態電流測量技術

Thin Film Transistor measurement

By transient current

研究 生：蔡尚公

指 導 教 授：崔秉鉞 教 授

中華民國九十五年七月

# 薄膜電晶體之暫態電流測量技術

Thin film transistor measurement by transient current

研 究 生：蔡尚公

Student : Shang-Kung Tsai

指 導 教 授：崔秉鉞

Advisor : Bing-Yue Tsui

國 立 交 通 大 學

電機學院與資訊學院專班 電子與光電學程

Submitted to Degree Program of Electrical Engineering and Computer Science

College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Electronics and Electro-Optical Engineering

July 2006

Hsinchu, Taiwan, Republic of China

中華民國九十五年七月

# 薄膜電晶體之暫態電流測量技術

研究生：蔡尚公

指導教授：崔秉鉞

國立交通大學

電機學院與資訊學院專班 電子與光電學程

## 摘要

非晶矽薄膜電晶體(Amorphous silicon thin film transistor)被廣泛應用在主動式液晶顯示器上，雖然它的電子移動力(mobility)比多晶矽(Poly silicon)還要來的低，但是應用在顯示影像上卻是足夠的，然而它本身在關閉狀態下的漏電流卻是比多晶矽元件(Device)來的低，而這也是非晶矽元件運用在大尺寸液晶顯示器的一個重要因素。

由於非晶矽的光導電度(Photoconductivity)偏高，因此在製造薄膜電晶體液晶顯示器(Thin Film Transistor Liquid Crystal Display, TFT-LCD)時需用光盾膜(Light Shielding)遮蓋，所以在薄膜電晶體液晶顯示器所長出的元件都是採用底層閘極(Bottom gate)有別於一般半導體製程的上層閘極(Up gate)方式，因此在元件製程中為了長出非晶矽的通道，則必須在蝕刻源/汲極金屬後再過蝕刻 n+(over etching n+)，而這個過程會導致源/汲極金屬殘留及通道層的損傷造成禁錮缺陷(Trap defect)。

本論文主要探討放電幕那(Discharge mura)造成的原因，首先我們從幾個方面去探討放電幕那的成因，最後利用量測暫態電流(Transient current)及改良型戴韋遜理論(Modified Levinson theory)的方法去求出在元件的禁錮缺陷密度(Trap defect density)，發現暫態電流量測法可以準確量出放電幕那元件的禁錮缺陷密度及放電時間，而改良型戴韋遜理論雖可以量測出元件的禁錮缺陷密度但無法求出元件之間的差異且無法反應元件的放電時間。

由於具有放電幕那的元件無法從量測電流(I)-電壓(V)曲線上看出與正常元件之間的差異，因此我們透過吉時利 428 電流放大器(Keithley 428 current amplifier)去量測具有放電幕那元件與正常元件的暫態電流(Transient current)放電曲線去做比較，並透過公式的換算因而可以求出個別元件的禁錮缺陷密度，另外我們再次透過其他的元件在不同的氨氣電漿處理(NH<sub>3</sub> plasma treatment)條件下去驗證暫態電流量測法對於量測元件的禁錮缺陷密度是否有效，經過驗證之後我們發現暫態電流量測法可以有效量測出元件的禁錮缺陷密度，且元件會隨著氨氣電漿處理時間增加而使禁錮缺陷密度減少，這在第四章節將有詳細的說明。

本論文對放電幕那問題提出了全新的分析方法，透過量測待測元件的暫態電流進而畫出暫態電流放電曲線，經過公式的換算而將禁錮缺陷密度量化求出實際值，在實際運用上製程人員能藉由求出禁錮缺陷密度的數值來調整製程參數(Recipe)，進而有效將放電幕那問題解決。

# Thin film transistor measurement by transient current

Student : Shang Kung Tsai

Advisor : Bing-Yue Tsui

College of Electrical and Computer Engineering

Institute of Electronics and Electro-Optical Engineering

## ABSTRACT

Amorphous silicon thin film transistor has been widely used in active LCD(liquid crystal display). Although its electronic mobility is lower than poly silicon, it is good enough for display applications. Moreover, the leakage current at “off” state on amorphous silicone devices is much lower than poly silicone and that's why amorphous silicone has been extensively adopted for large size LCD.

Because of the high photoconductivity on amorphous silicone devices, a light shielding is required for the amorphous silicone-based TFT-LCD. As such, bottom gate structure is used for TFT-LCD, and which is different from the up-gate structure on semiconductor. In the process of the device channel development, to over etch n+ after etching drain/source metal is required, and this process will lead to drain/source metal residue as well as channel damage which would eventually cause trap defect.

In this paper, we will discuss the root cause and mechanism of the discharge mura. First, we use different method to distinguish root cause. Finally, we find Transient current measurement is a good approach to get trap defect density and discharge time precisely

as we used Transient current measurement and Modified Levinson theory to obtain the channel trap defect density. Although Modified Levinson measurement can get the trap defect density, it can't verify differences among devices and get the discharge time.

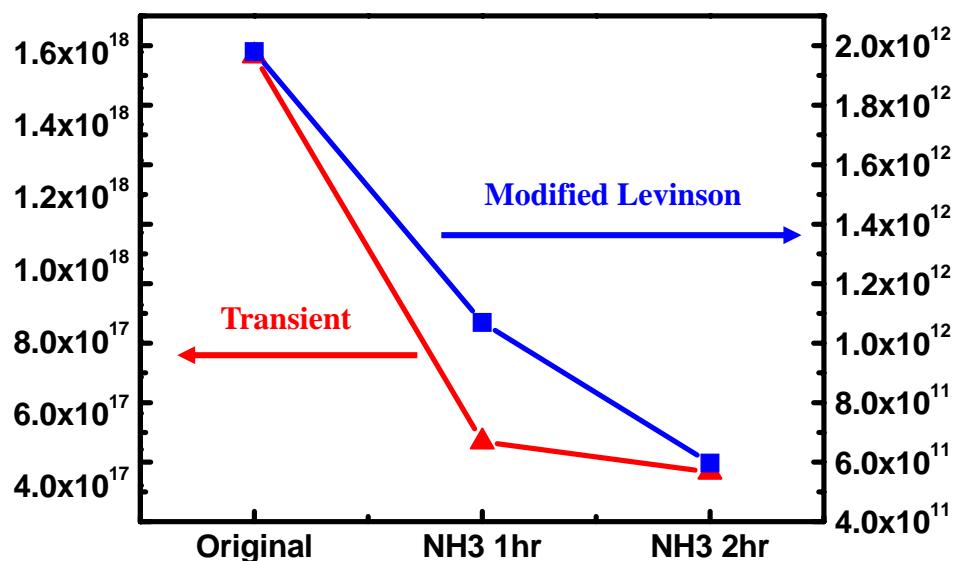

As measuring the I-V curve is not able to observe the difference between normal devices and discharge mura devices, we use Transient current measurement method to obtain the difference by Keithley 428 current amplifier and with formula calculation, we are able to get the trap defect density of each device. Finally, we produce new devices to verify Transient current method in different NH<sub>3</sub> plasma treatment condition. After measurement, we observe that Transient current method can effectively get the trap defect density and it will drop down gradually by increasing NH<sub>3</sub> plasma treatment time.

In this paper, we provide the new approach to measure device transient current and get the transient current discharge curve. Upon this approach, the trap defect density can be obtained after formula calculation. In actual practice, engineers can modify the process recipe as the trap defect density is acquired to solve discharge mura.

## 誌謝

時光荏苒，碩士在職班研究生涯就要以此論文之告成因而即將畫上句號。在這段日子裡，首當感謝指導教授 崔秉鉞老師於實驗、研究與論文上給予充分且詳實的指導與教誨鼓勵，老師嚴謹認真的研究態度、條理分明的思考模式及廣博的知識，令學生受益匪淺。特別是學生本身因為在職緣故所以需兼顧課業與工作，因此替老師帶來些許困擾深深感到歉意。

衷心的感謝實驗室的林家彬、黃誌鋒、蕭逸璿、方國龍、張修維、謝志民、呂智勳、張志廉、蘇柏智在實驗上的指導與支援，以及這幾年來生活上的照顧與陪伴，特別是黃誌鋒在我學業有困惑時總是能夠適時地指導我，讓我對於問題能夠很快解決，在此我要特別謝謝他。

最後，要特別感謝我的家人，謝謝你們對我的辛苦栽培及默默付出，使我得以全心投入學業，完成碩士學位，謝謝。

## 目 錄

|                |      |

|----------------|------|

| 論文摘要(中文) ..... | i    |

| 論文摘要(英文) ..... | iii  |

| 誌謝 .....       | v    |

| 目錄 .....       | vi   |

| 表目錄 .....      | viii |

| 圖目錄 .....      | ix   |

### 第一章 緒論

|                  |   |

|------------------|---|

| 1.1 論文研究背景 ..... | 1 |

| 1.2 論文研究動機 ..... | 3 |

| 1.3 論文架構 .....   | 4 |

### 第二章 放電幕那描述及原因分析

|                        |    |

|------------------------|----|

| 2.1 薄膜式電晶體製作 .....     | 7  |

| 2.2 放電幕那現象描述 .....     | 8  |

| 2.3 放電幕那可能原因分析 .....   | 9  |

| 2.4 工程上迴避放電幕那的方法 ..... | 13 |

| 2.5 放電幕那機制探索 .....     | 14 |

| 2.5.1 改良型戴韋遜的原理 .....  | 14 |

| 2.5.2 改良型戴韋遜量測方法 ..... | 16 |

### 第三章 暫態電流方法及系統架設

|                    |    |

|--------------------|----|

| 3.1 暫態電流的原理 .....  | 18 |

| 3.2 暫態電流量測系統 ..... | 20 |

|                  |    |

|------------------|----|

| 3.3 雜訊抑制.....    | 21 |

| 3.4 禁錮缺陷的量測..... | 22 |

## 第四章 暫態電流量測方法的延伸應用

|                                    |    |

|------------------------------------|----|

| 4.1 元件製作.....                      | 24 |

| 4.2 氮氣電漿處理對N通道非晶矽的影響.....          | 25 |

| 4.3 經過氮氣電漿處理後用改良型戴韋遜量測禁錮缺陷值比較..... | 25 |

| 4.4 經過氮氣電漿處理後用暫態電流量測禁錮缺陷值比較.....   | 26 |

| 4.5 改良型戴韋遜與暫態電流量測方法比較.....         | 27 |

## 第五章 總結與未來工作

|                                |    |

|--------------------------------|----|

| 5.1 改良型戴韋遜及暫態電流量測禁錮缺陷密度比較..... | 29 |

| 5.1.1 改良型戴韋遜量測結果.....          | 29 |

| 5.1.2 暫態電流量測結果.....            | 30 |

| 5.2 暫態電流量測的應用.....             | 30 |

| 5.3 未來工作.....                  | 30 |

| 參考文獻.....                      | 32 |

## 表 目 錄

### 第二章

表 2-1 薄膜式電晶體各層厚度。

表 2-2 通道膜厚量測統計表。

表 2-3 PI 膜厚量測值。

### 第三章

表 3-1(a)由暫態電流與暫態時間所求出白色幕那的禁錮缺陷密度。

表 3-1(b)由暫態電流與暫態時間所求出黑色幕那的禁錮缺陷密度。

### 第四章

表 4-1(a)由改良型戴韋遜量測法所求出原始樣本的禁錮缺陷密度。

表 4-1(b)由改良型戴韋遜量測法所求出氨氣電漿處理 1hr 的禁錮缺陷密度。

表 4-1(c)由改良型戴韋遜量測法所求出氨氣電漿處理 2hr 的禁錮缺陷密度。

表 4-2(a)由暫態電流與暫態時間所求出原始樣本的禁錮缺陷密度。

表 4-2(b)由暫態電流與暫態時間所求出氨氣電漿處理 1hr 的禁錮缺陷密度。

表 4-2(c)由暫態電流與暫態時間所求出氨氣電漿處理 2hr 的禁錮缺陷密度。

# 圖 目 錄

## 第一章

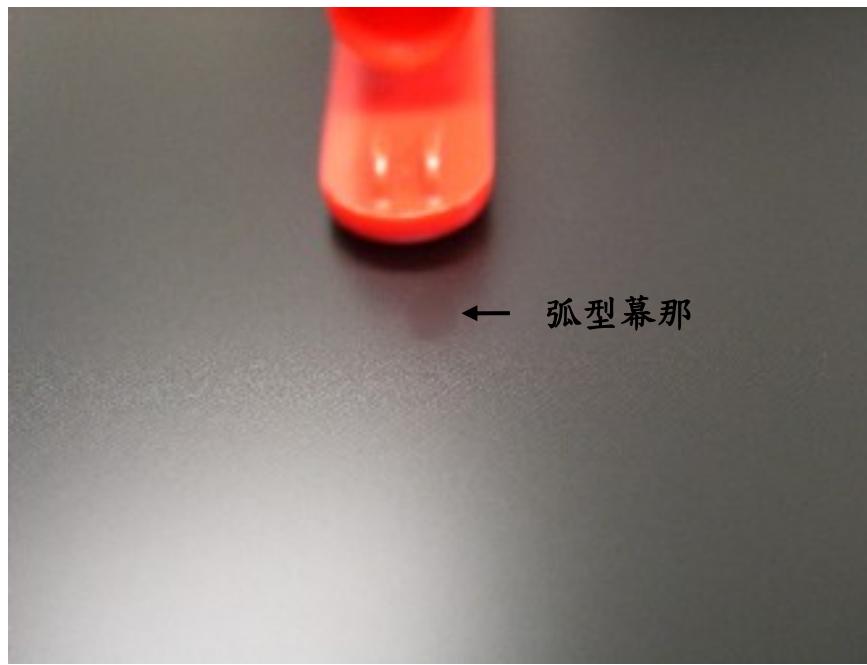

圖 1-1 弧形幕那為箭頭指引處，上頭筆蓋為協助聚焦用

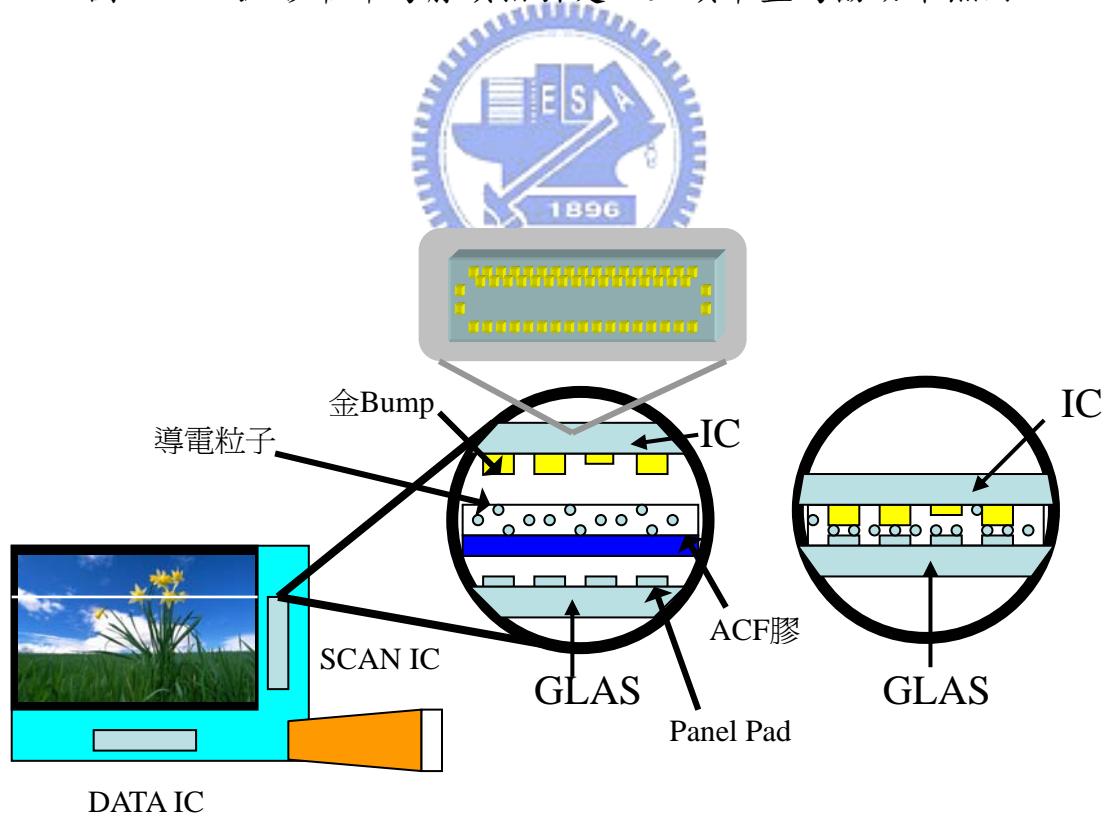

圖 1-2 COG 壓合製程示意圖

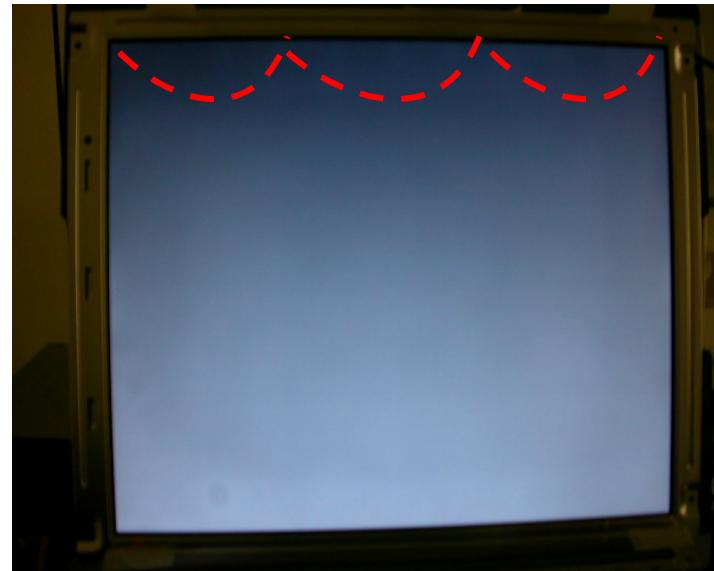

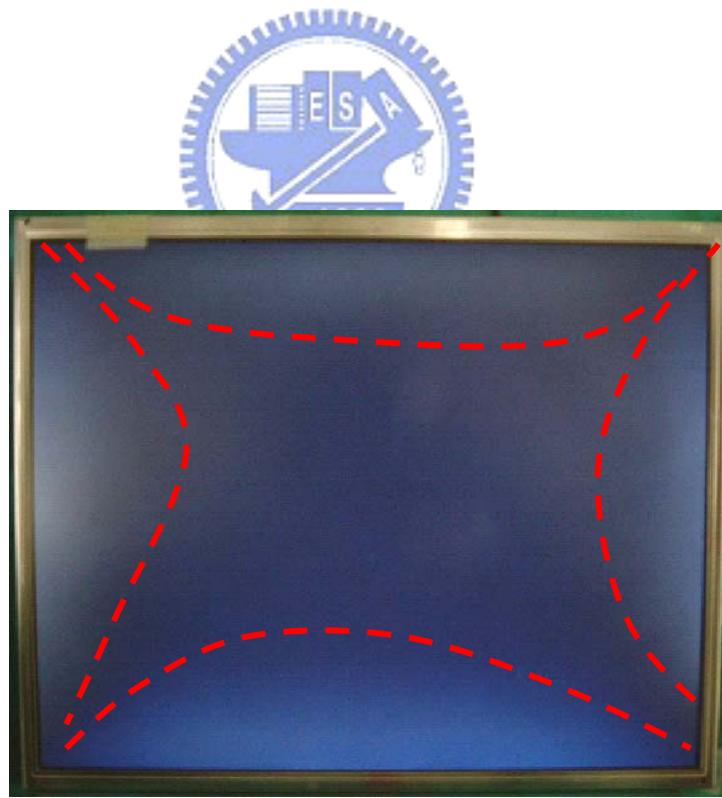

圖 1-3 COG 幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-4 邊緣幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

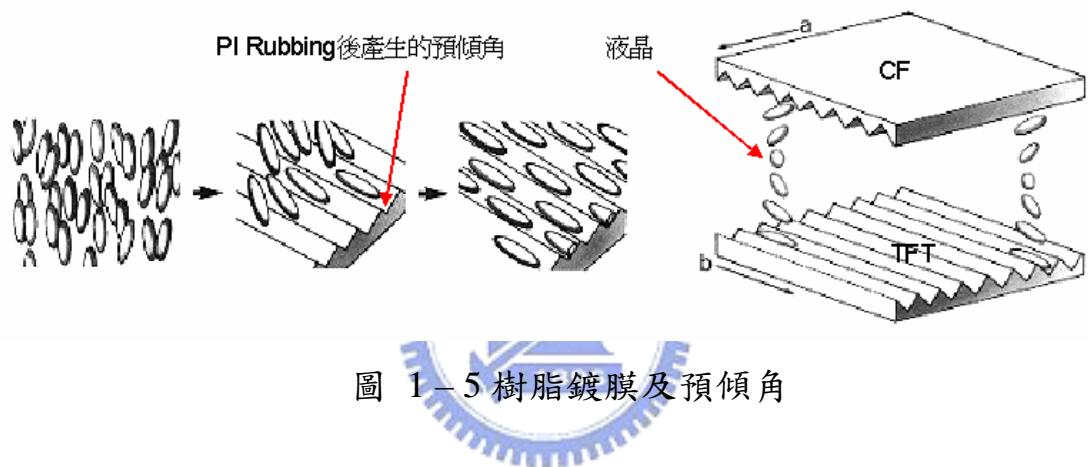

圖 1-5 樹脂鍍膜及預傾角

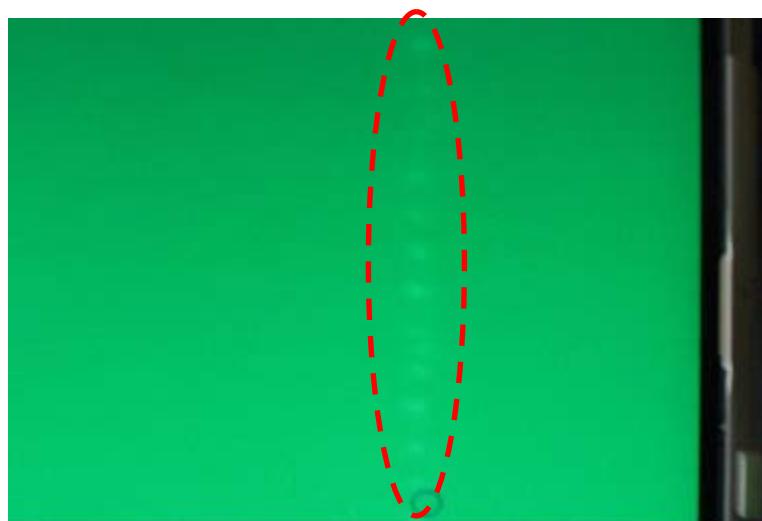

圖 1-6 樹脂幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-7 樹脂幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-8(a) 時間= 0 sec 剛關機瞬間

圖 1-8(b) 時間= 30 msec 放電幕那的現象

圖 1-8(c) 時間= 120 msec 放電幕那的現象

圖 1-8(d) 時間= 180 msec 放電幕那的現象

圖 1-8(e) 時間= 300 msec 放電幕那的現象

圖 1-8(f) 時間= 450 msec 放電幕那的現象

圖 1-8(g) 時間= 630 msec 放電幕那的現象

圖 1-8(h) 時間= 720 msec 放電幕那的現象

## 第二章

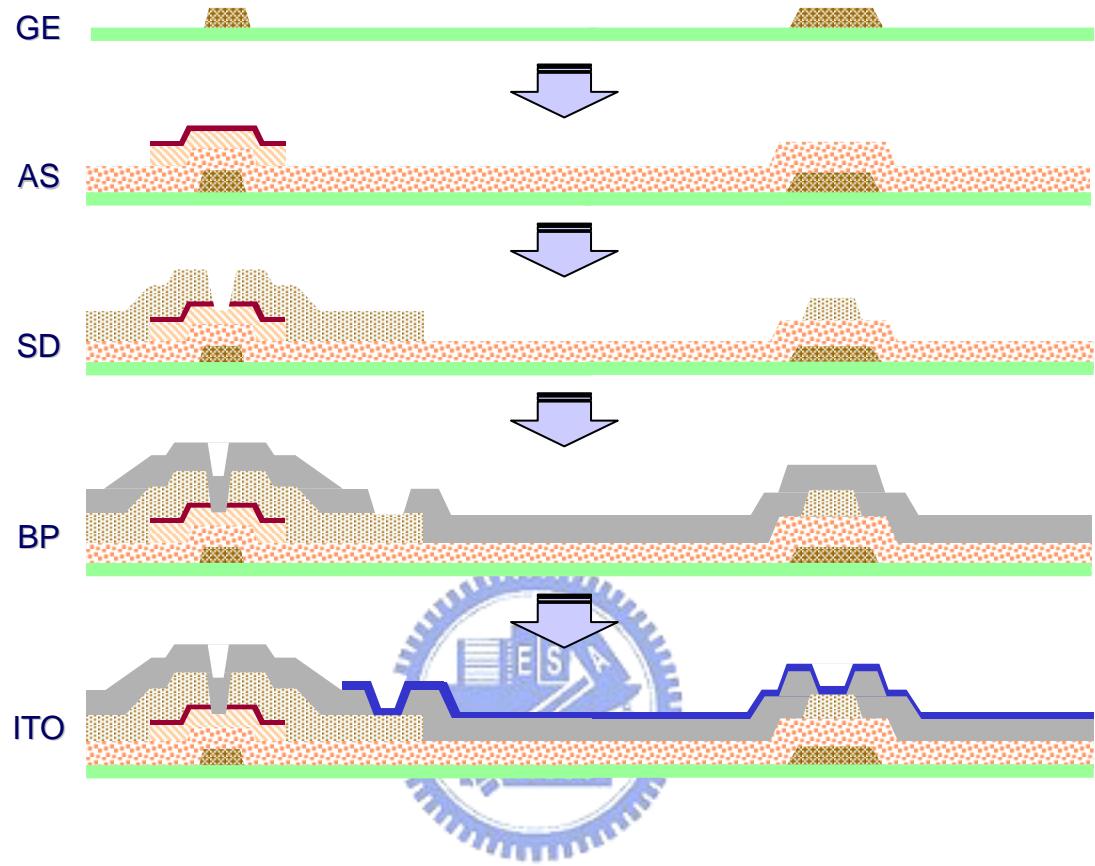

圖 2-1 薄膜式電晶體製程步驟

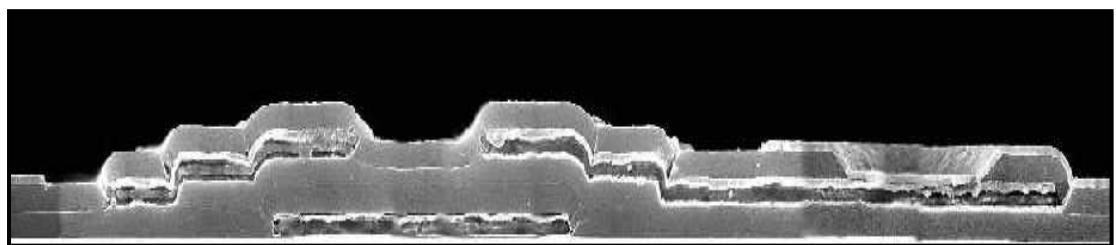

圖 2-2 薄膜式電晶體之掃瞄式電子顯微鏡剖面影像

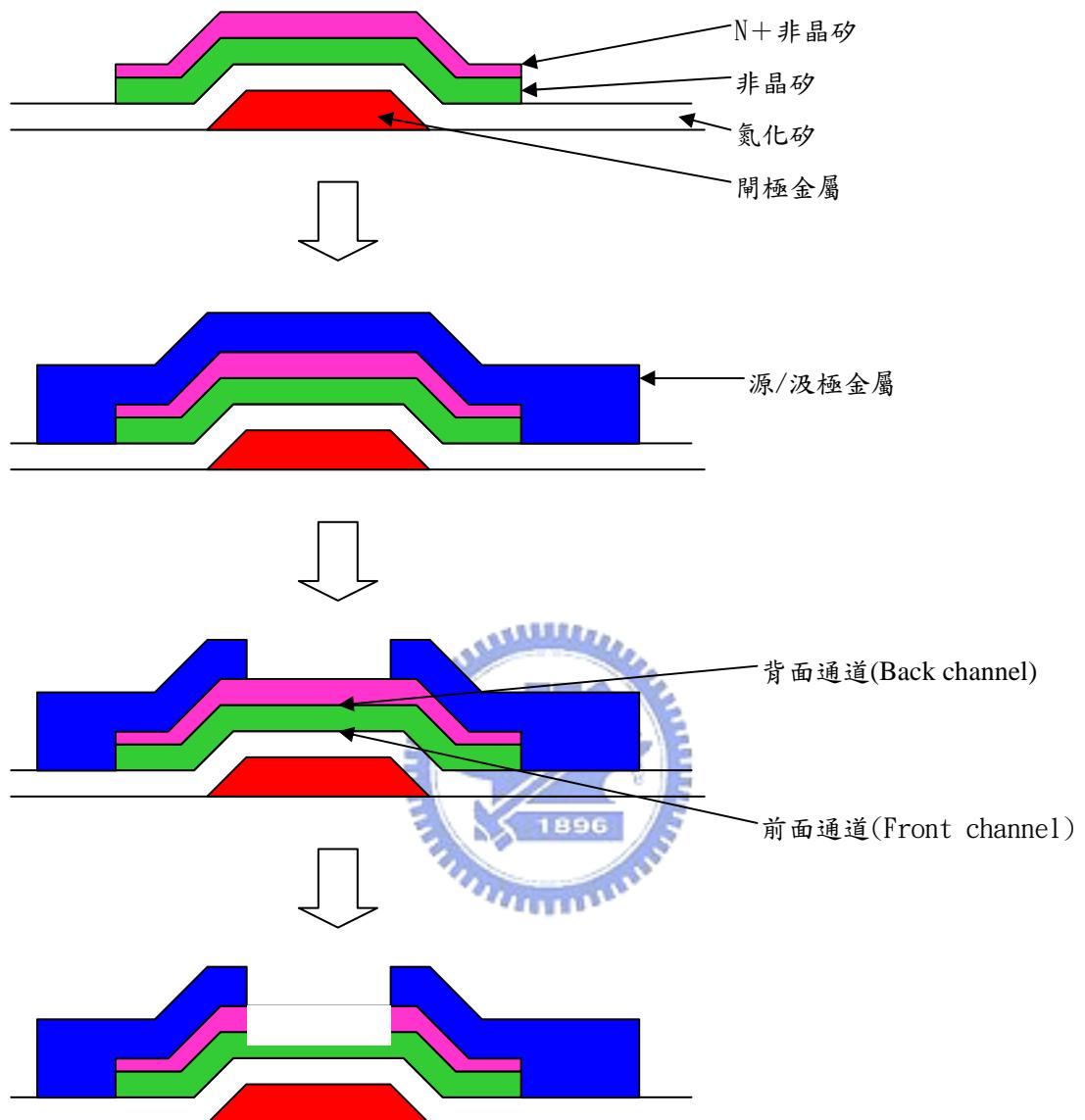

圖 2-3 背面式通道蝕刻方法示意圖

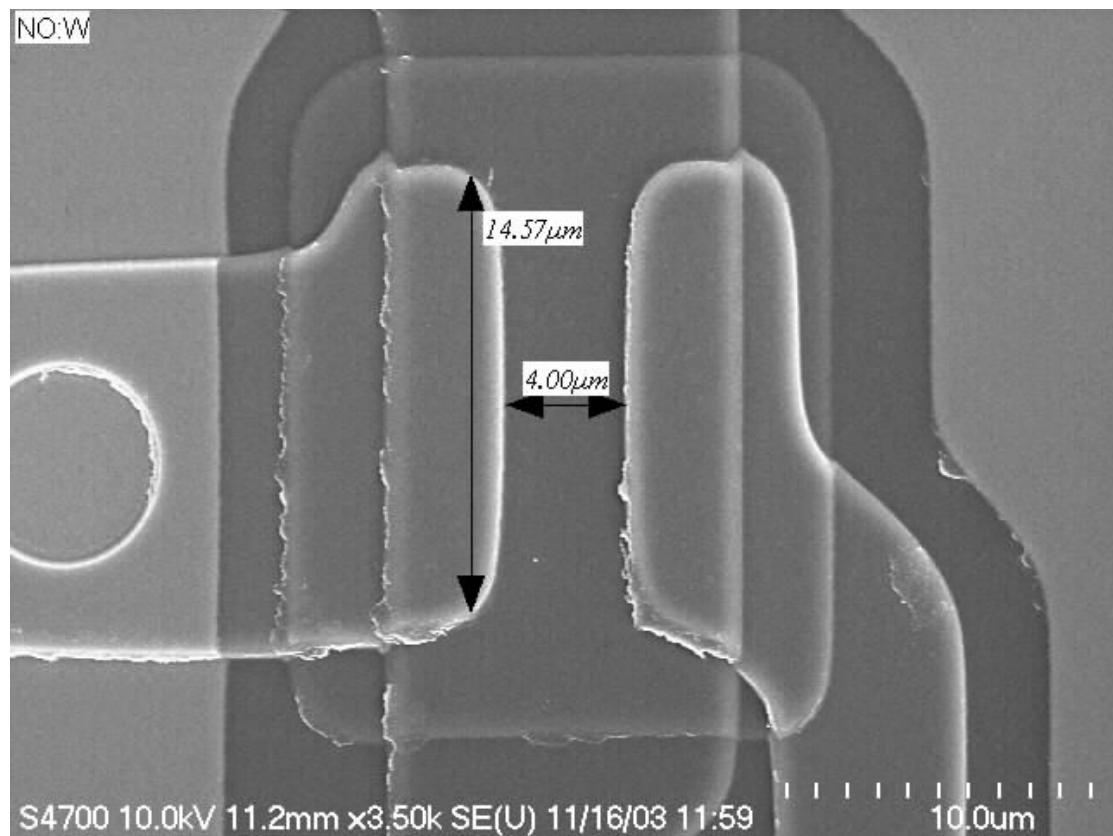

圖 2-4 薄膜式電晶體的  $W/L = 14.5\mu\text{m} / 4\mu\text{m}$

圖 2-5 典型的 TN 模式電壓 - 穿透率特性圖

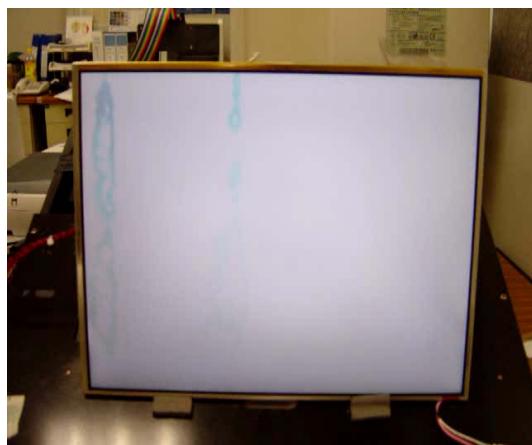

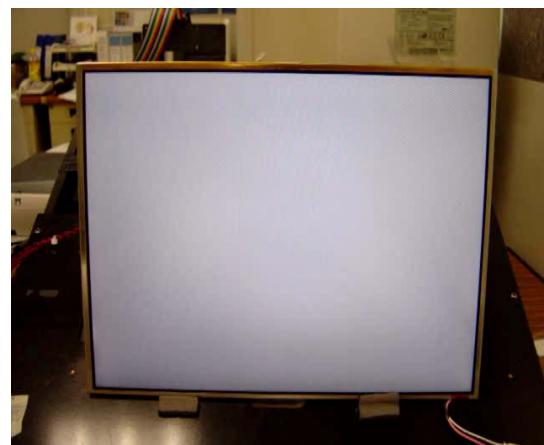

圖 2-6 放電幕那

圖 2-7 白色正常幕那量測的膜厚

圖 2-8 黑色異常幕那量測的膜厚

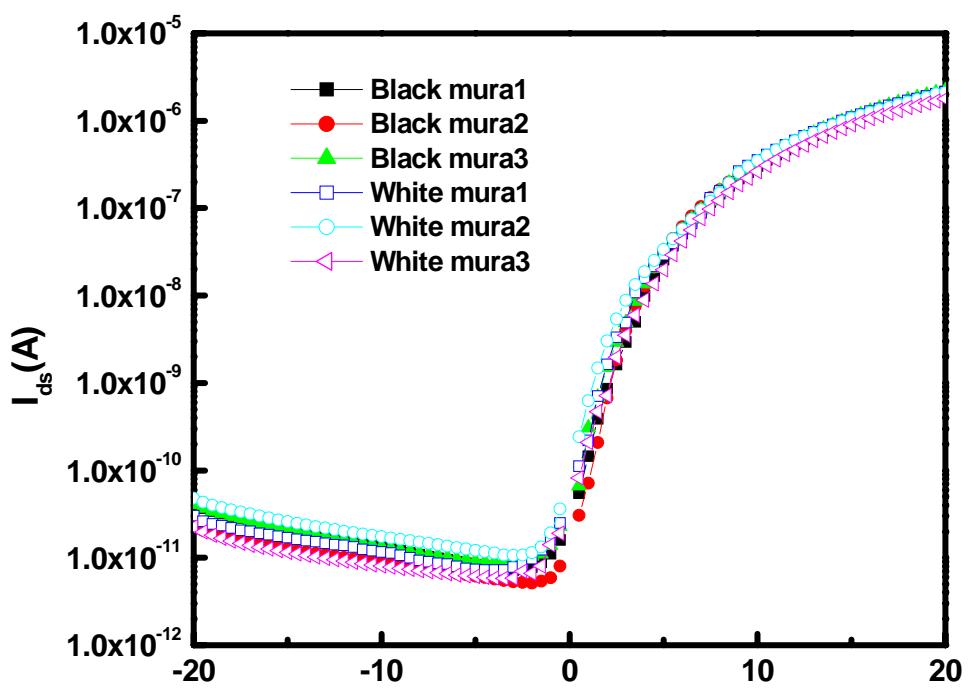

圖 2-9 元件的電流 - 電壓曲線

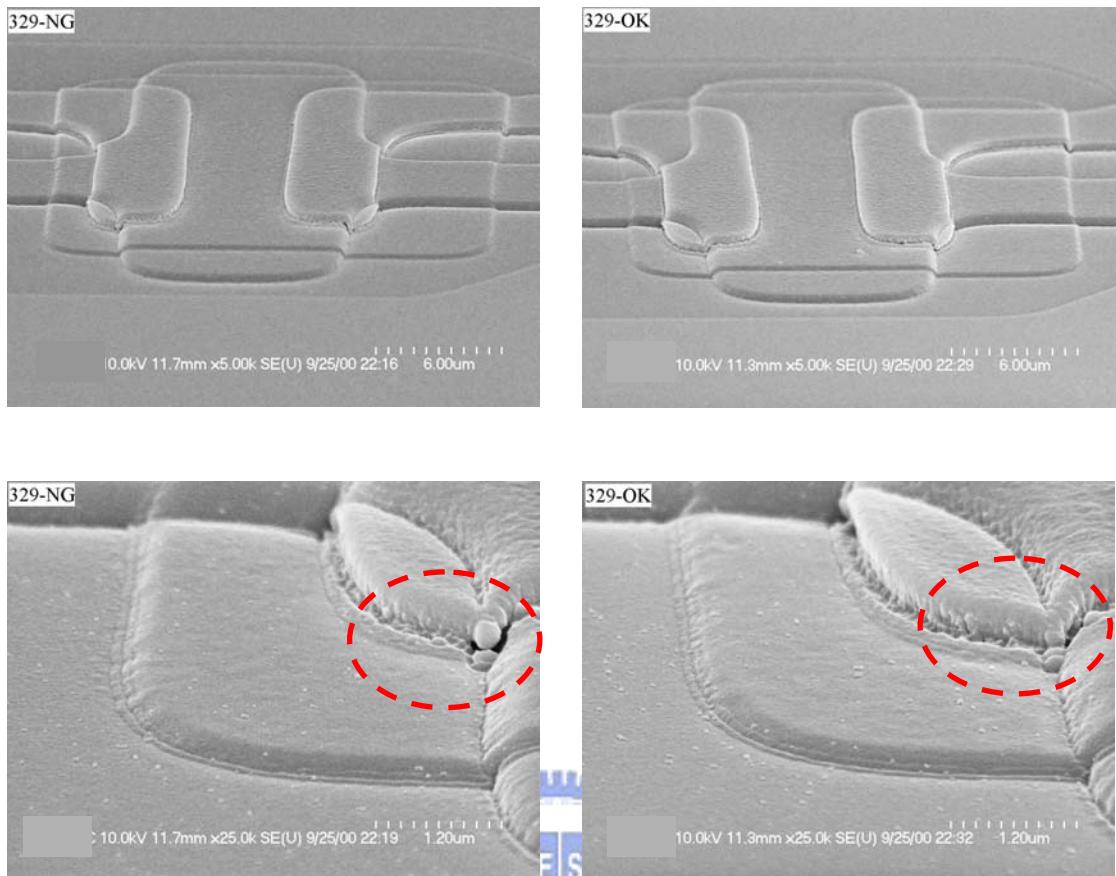

圖 2-10 正常與異常元件在蝕刻後殘留顆粒示意圖

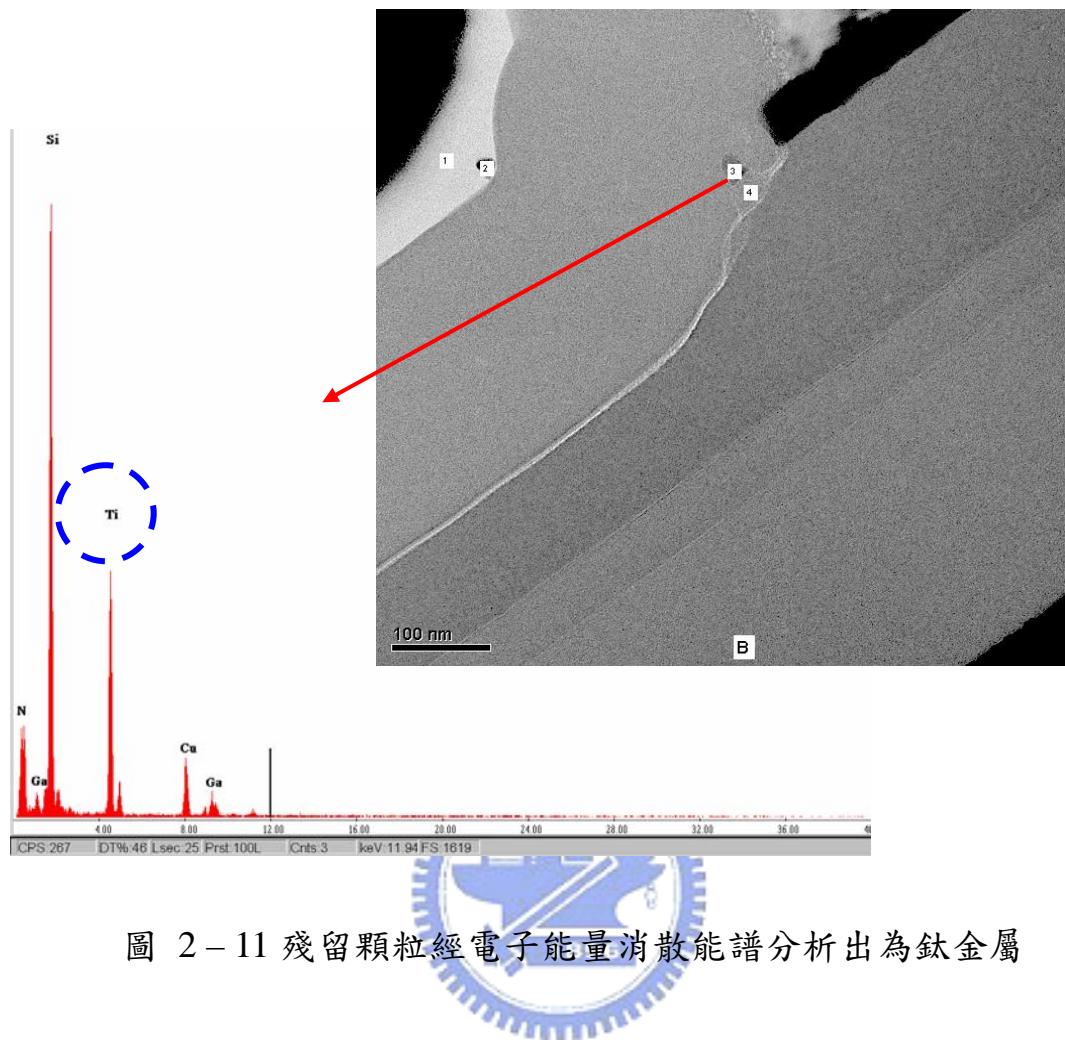

圖 2-11 殘留顆粒經電子能量消散能譜分析出為鈦金屬

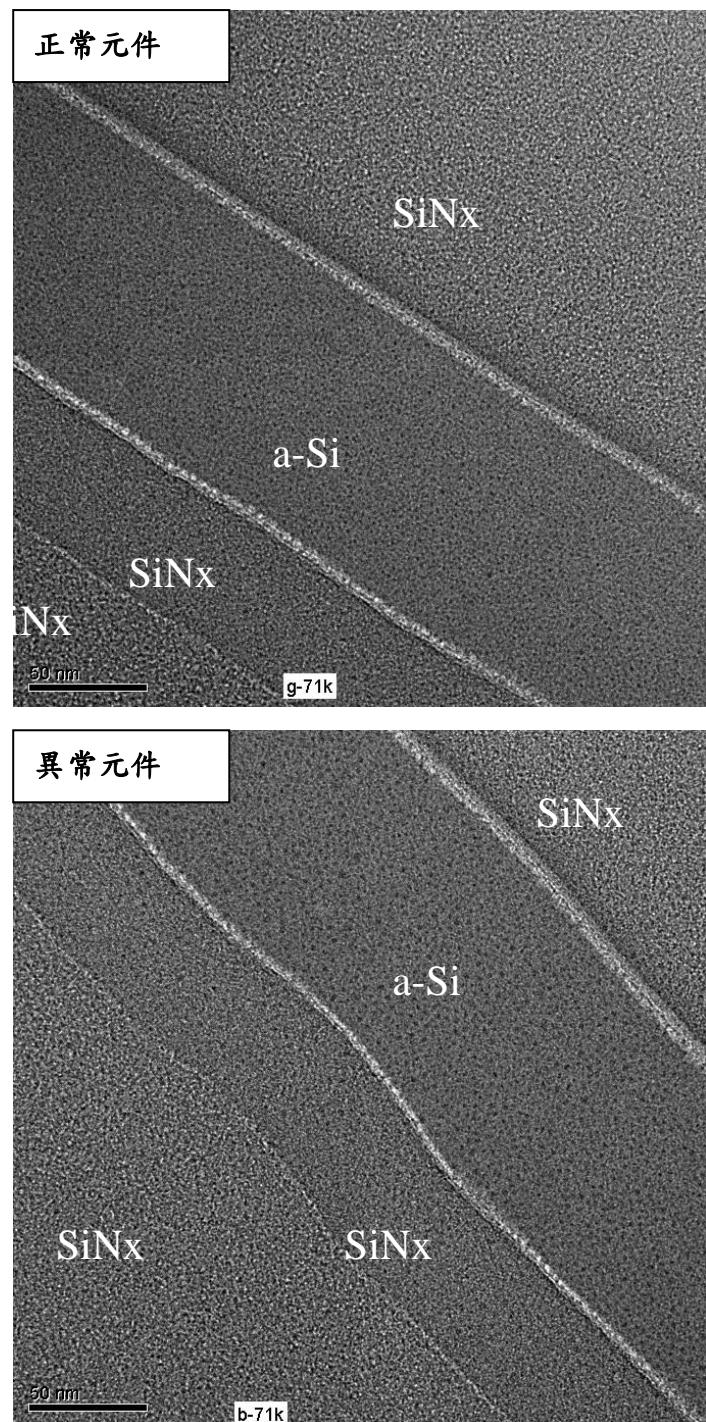

圖 2-12 正常元件與異常元件在穿透式電子顯微鏡下觀察的現象

圖 2-13 電路設計修正前後  $V_{gh}$  放電的變化

圖 2-14 改良型戴韋遜斜率的求出方法

圖 2-15 改良型戴韋遜斜率的求出方法

### 第三章

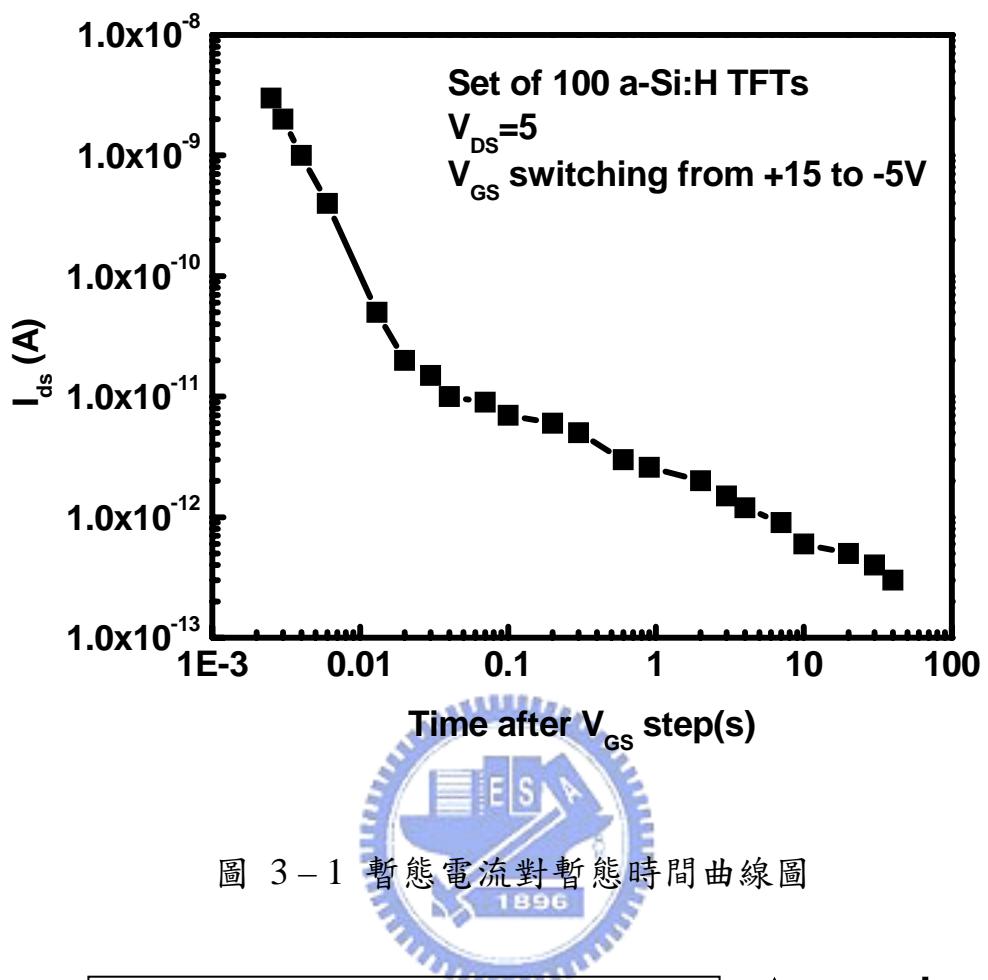

圖 3-1 暫態電流對暫態時間曲線圖

圖 3-2  $X(E_f)$ 為通道有效厚度

圖 3-3 雜訊  $= 8.5 \times 10^{-10} A$

圖 3-4 來自市電 60Hz 的雜訊來源

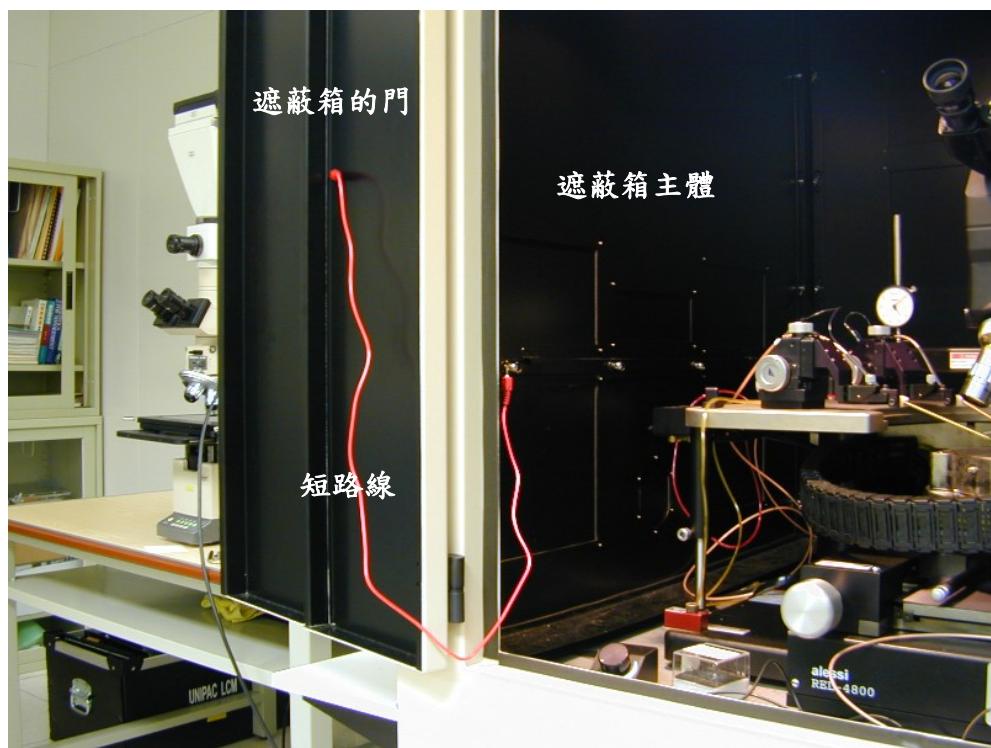

圖 3-5 短路線將遮蔽箱的門與遮蔽箱主體短路

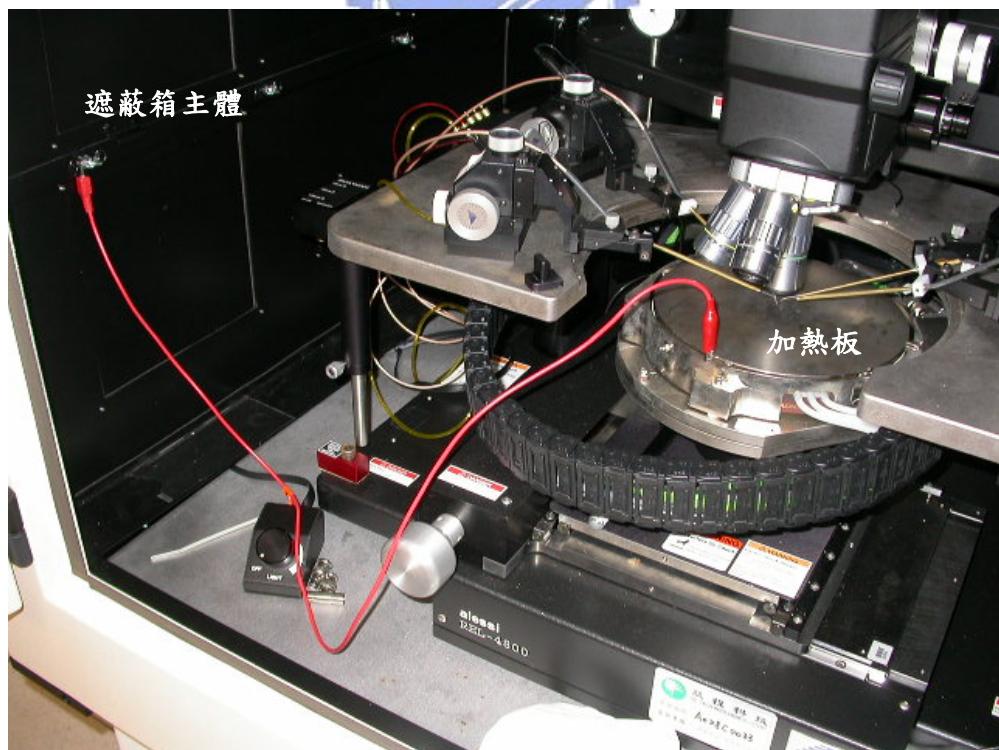

圖 3-6 短路線將遮蔽箱主體與加熱板短路

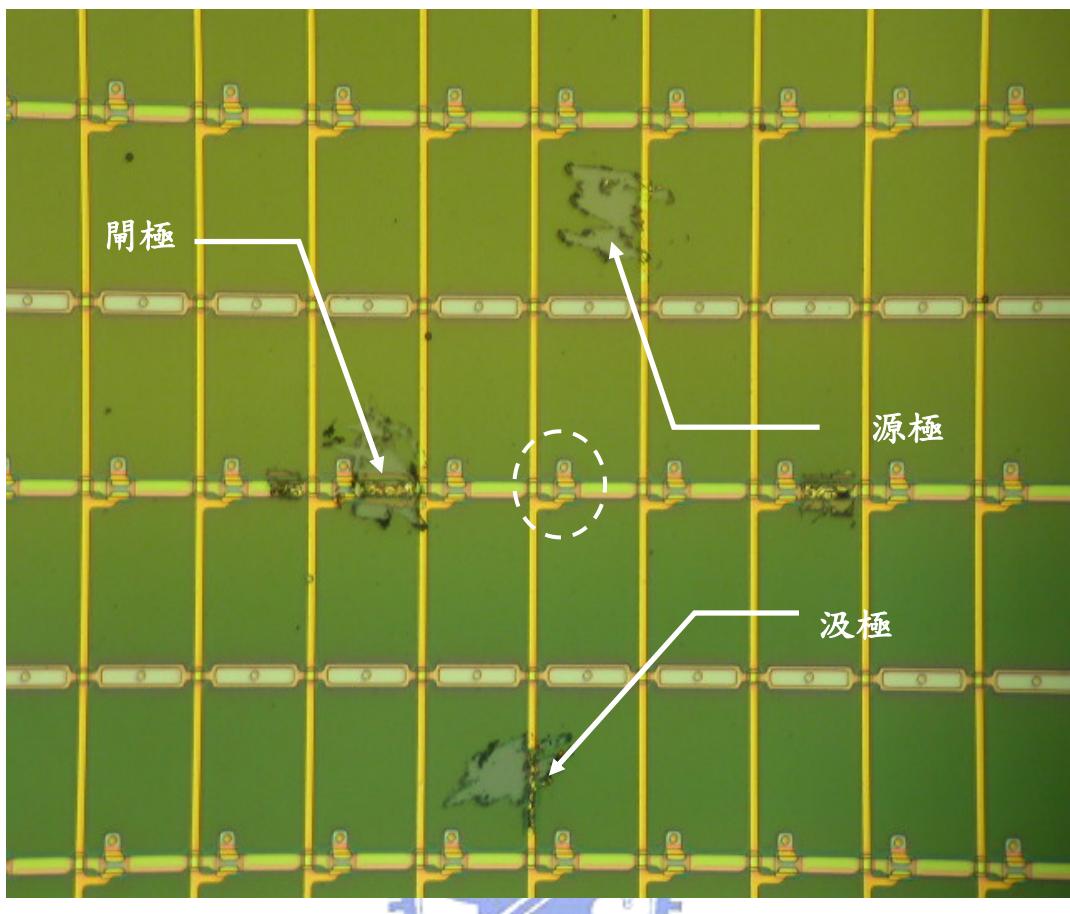

圖 3-7 元件要被探針探測的位置示意圖

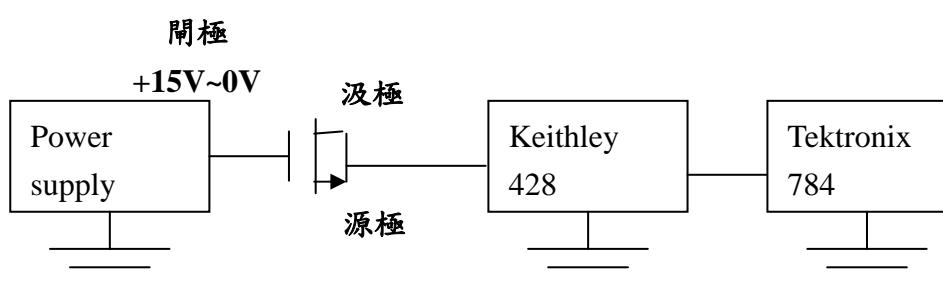

圖 3-8 暫態電流量測儀器的接法

圖 3-9 暫態電流及暫態時間量測值

圖 3-10 暫態電流及暫態時間的曲線圖

## 第四章

圖 4-1 元件製作流程

圖 4-2 原始元件及經過氮氣電漿處理後元件的電流 – 電壓曲線

圖 4-3 原始樣本一元件的斜率

圖 4-4 原始元件及經過氮氣電漿處理後元件的暫態電流與暫態時間

曲線圖

圖 4-5 經氮氣電漿處理後用改良型戴韋遜及暫態電流所求出禁錮缺

陷密度的趨勢圖

# 第一章 緒論

## 1.1 液晶顯示器的幕那現象

經過了近 30 年的大力發展，液晶顯示器 (Liquid Crystal Display，簡稱 LCD) 已經成為平板顯示器器的主流[1]，並逐漸取代桌上型陰極射線管 (CRT) 監視器。其主要原因有三：低操作電壓、低耗電量及與半導體相容的製程技術，因此在現今顯示器產業中，液晶顯示器經常被應用在許多人機介面方面，例如電腦螢幕、數位相機、手機以及家庭電視等。

1968 年首先由美國 RCA 公司發表液晶在液晶顯示器上的運用，後來經由日本將液晶顯示器發揚光大，台灣為了在這波液晶顯示器的熱潮中不缺席，在 1990 年代陸續有五家液晶顯示器廠成立，並在 1998 年從日本轉移生產液晶顯示器面板的技術，由於生產技術主要靠日本轉移，因此有很多生產重要參數就只有靠自己去摸索。

液晶顯示器經過多年來的努力，生產尺寸逐漸往大尺寸的方向發展如目前多家廠商積極投入的七代及八代線，並且在生產良率上也獲得重大的突破，往 90% 以上的高良率發展。然而液晶顯示器生產過程中常會製造出不同的缺陷，包括最常見到的亮點暗點、亮線暗線、偏光板刮傷及幕那 (Mura) 等

1999 年由於剛量產初期就面臨很多生產線的製程問題，其中以幕那的問題最為嚴重，幕那一詞主要來自日本，原是人名，但也被用來描述顯示器畫面不均勻的現象。當顯示器在顯示同一顏色畫面時，

如果畫面會有顏色不均勻的現象時，就稱這種現象為幕那。由於幕那的現象有很多種，且成因也不盡相同，以下我們將列舉幾種常見的幕那並簡單描述其現象與造成的原因：

### (1) 弧形幕那(Arc mura)

在顯示器的生產過程中，由於前段的玻璃基板尺寸常大於 1000mm x 1000mm 以上，故在玻璃基板搬運的過程中，需藉由機器手臂搬運，避免玻璃破裂。由於機器手臂是藉由真空吸盤來固定玻璃基板，當真空吸盤的壓力過大，或是與玻璃基板接觸面的吸盤材質太硬時，就會造成弧形幕那如圖 1-1 所示。

### (2) IC 壓合幕那(COG mura)

COG(Chip On Glass)是表示 IC 直接壓合在玻璃基板上，主要是透過熱壓頭加在 IC 上加熱，並且施加壓力，另外在 IC 與玻璃基板的中間有一層導電粒子及膠質，當熱壓頭加在 IC 上加熱並且施加壓力後，IC 上的聯接點金凸塊(Gold bump)會透過導電粒子與玻璃基板上的金屬墊(Pad)短路，如圖 1-2 所示。另外膠質主要使 IC 與玻璃基板緊密黏貼，當熱壓頭上的溫度過高，導致傳導到玻璃基板的溫度過高，會使得玻璃基板些微軟化，而這些軟化區域的玻璃間距(Cell gap)與正常區域不同因而造成 IC 壓合幕那，如圖 1-3 所示。

### (3) 邊緣幕那(Edge mura)

偏光板(Polarizer)主要黏貼於面板(Panel)玻璃上下兩面，其主要功能是讓光具有方向性，而偏光板主要由 TAC / PVA / TAC(三醋酸鹽/綜合乙烯基/三醋酸鹽)三層所組成，其中 TAC 是一般所謂的塑膠層用於保護 PVA 層，而當光通過 PVA 層時，由於 PVA

具有吸收軸與穿透軸，因此只有經過穿透軸的光可以通過，當外界的溫度過高時會導致偏光板的 TAC 層收縮，連帶著 PVA 也跟著些微收縮因而造成邊緣幕那，如圖 1-4 所示。

#### (4) 樹脂幕那(PI mura)

PI (樹脂 Polyimide) 膜常被鍍於與液晶接觸的 CF(彩色濾光片 Color Filter)玻璃與 TFT 玻璃的內緣，如圖 1-5 所示，樹脂膜在經過棉質布摩擦(Rubbing)過後，表面會形成一個預傾角(Pre-tilt angle)，而這個預傾角會提供液晶比較快的反應速度，但當樹脂膜鍍在玻璃的厚度不均勻時，經過摩擦後，樹脂膜比較厚的地方與樹脂膜比較薄的地方所得到的預傾角就不同，因而造成樹脂幕那，如圖 1-6 及 1-7 所示。

以上所提的是幾種常見幕那，其造成的原因主要是來自於後段製程異常而導致的，而本論文研究主題主要是針對第 5 種放電幕那的成因及量測方法做討論，在往後的章節將會做深入的說明。

## 1.2 論文研究動機

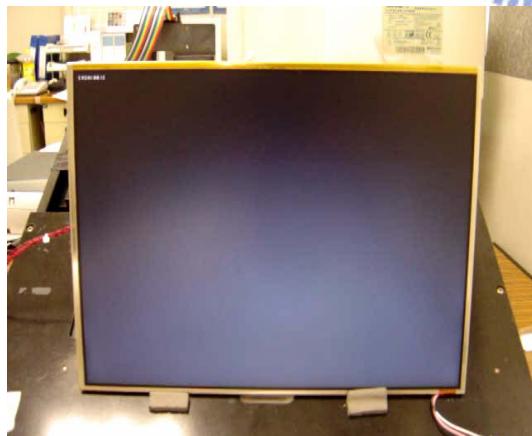

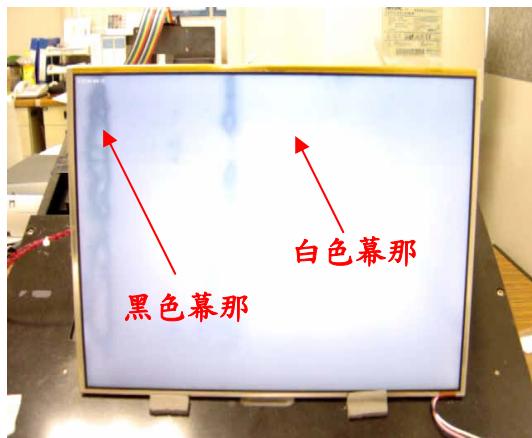

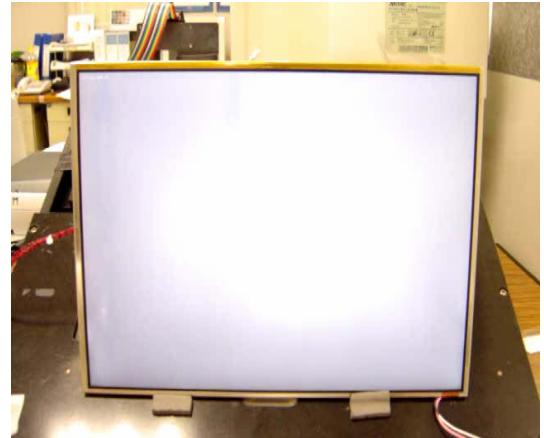

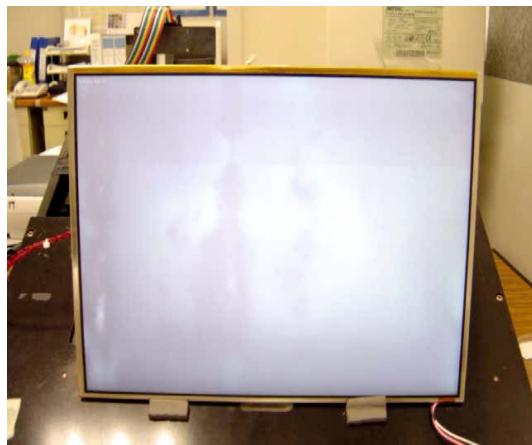

在本文中主要討論的是放電幕那(Discharge mura)意即顯示器在關機後因為元件(Device)放電速度快慢不同導致畫面呈現亮暗不均勻的現象稱之為放電幕那。圖 1-8(a)-(h)分別是放電幕那發生時間與現象圖，從圖中我們可以觀察到異常區域(黑色幕那 Black mura)放電時間長達 630msec 左右，而正常區域(白色幕那 White mura)放電時間則介於 300msec 到 450msec 之間，也由於這種因為放電速度不均所導致的現象我們稱之為放電幕那。

為了解決放電幕那問題，剛開始針對正常與異常元件去量測電流 – 電壓曲線( I – V curve)，但在量測得到的電流 – 電壓曲線上並未能找出任何差異。另外也針對各製程去追蹤問題點，雖然最後有找出對應的製程步驟，但未能針對此原因做學理上的解釋。本論文就是在這種背景下所產生，我們希望針對放電幕那能提供一個學理的解釋，並提供一個可供量化的量測方法做為未來工程師調整製程參數解決問題的依據，譬如改變以下製程參數：

- (1) 改變非晶矽(a-Si:H)的回火(anneal)溫度及時間

- (2) 改變非晶矽的沉積速度[2]

- (3) 改變背面式通道蝕刻(Back channel etching)的深度及速度

- (4) 改變與非晶矽接觸的不同材料[3]

放電幕那是一種面板關機後所觀察到的幕那現象，其造成異常的原因主要是與前段元件製程有關，我們根據液晶顯示器矩陣(LCD Array)前段的製程步驟一一分析，包括非晶矽的厚度量測、元件電流 – 電壓曲線的量測及元件在掃瞄式電子顯微鏡(SEM)下觀察是否有異常等，然而這樣的分析並無學理上的解釋及驗證方法，為了能夠更深入了解放電幕那，在後續的章節我們將透過暫態電流(Transient current)的量測方法來有效量化放電幕那的禁錮缺陷密度(Trap defect density)並給予學理上的解釋。

### 1.3 論文架構

本論文分為三個部分：

1. 放電幕那描述及原因分析(第二章)

第二章首先會說明元件製程條件，然後介紹什麼叫做放電幕那，並根據製程步驟，逐一探討造成放電幕那的原因。根據我們對製程分析調查的結果發現放電幕那主要來自蝕刻下電極異常所致。製程技術上，可以透過控制下電極的使用時間及表面鍍膜(Coating)物質來避免放電幕那問題的發生。

## 2. 暫態電流方法及系統架設(第三章)

放電幕那主要是會造成異常區域之元件放電緩慢，這是因為異常元件的非晶矽層有較多的缺陷，導致異常元件在關閉後，由於非晶矽層禁錮缺陷較多，因此相對應的放電速度就慢，因而造成放電幕那的現象。

為了了解正常與異常區域非晶矽層的禁錮缺陷數量，我們藉由改良型戴韋遜(Modified Levinson)及暫態電流(Transient current)量測等兩種不同的方法去求出禁錮缺陷的數量，由於兩種方法求出禁錮缺陷的數量不同，顯然這兩種方法對所求出的禁錮缺陷有不同的意義，後續將會有所討論。另外在本章節也會提到如何架設系統去量測暫態電流及求出禁錮缺陷數量的方法。

## 3. 暫態電流量測方法的延伸應用(第四章)

既然暫態電流的量測方法可以求出元件非晶矽層的禁錮缺陷，我們製作三組新的元件樣本，藉由不同氮氣電漿處理(NH<sub>3</sub> plasma treatment)時間來改變元件內禁錮缺陷密度的數量，再藉由暫態電流量測方法，求出各元件的禁錮缺陷密度，驗證經氮氣電漿處理時間越長的元件，其缺陷密度也最少。

透過以上內容的編排方式，我們分析液晶顯示器的特性及幕那現象的種類和發生原因，最後再藉由暫態電流的量測，找出放電幕那與禁錮缺陷密度之間的關係。最後是結論與未來工作的建議。

圖 1-1 弧形幕那為箭頭指引處，上頭筆蓋為協助聚焦用

圖 1-2 COG 壓合製程示意圖

圖 1-3 COG 幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-4 邊緣幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-5 樹脂鍍膜及預傾角

圖 1-6 樹脂幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-7 樹脂幕那，如圖中虛線包含的區域造成亮暗不均幕那現象

圖 1-8(a) 時間 = 0 sec 剛關機

瞬間

圖 1-8(b) 時間 = 30 msec 放電幕

那的現象

圖 1-8(c)時間= 120 msec 放電

幕那的現象

圖 1-8(d)時間= 180 msec 放電

幕那的現象

圖 1-8(e)時間= 300 msec 放電

幕那的現象

圖 1-8(f)時間= 450 msec 放電

幕那的現象

圖 1-8(g)時間= 630 msec 放電

幕那的現象

圖 1-8(h)時間= 720 msec 放電

幕那的現象

## 第二章 放電幕那描述及原因分析

放電幕那(Discharge mura)主要是顯示器在關機後所呈現出畫面灰階不均的現象，本章節主要針對薄膜式電晶體(Thin Film Transistor 簡稱 TFT)製程做說明，另外就是對於放電幕那所做的製程原因分析，包括元件的量測及機台設備相關性的確認。

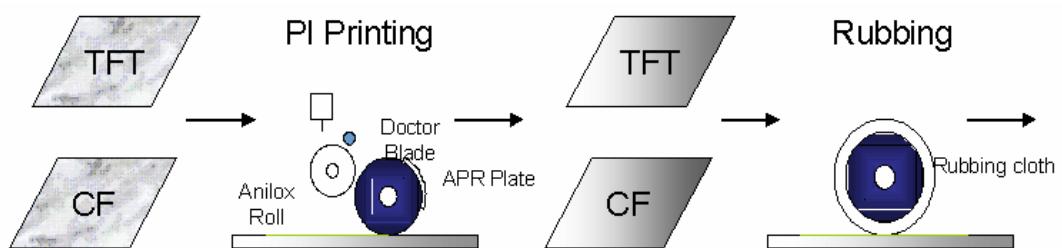

### 2.1 薄膜式電晶體製作

薄膜式電晶體(Thin Film Transistor 簡稱 TFT) 主要經過五道光罩製程，如圖 2-1 及 2-2 所示。其說明如下：

第一道光罩：是定義閘極金屬(Gate metal)，閘極金屬是以濺鍍(Sputter)方式形成鈦/鋁/鈦(Ti/Al/Ti)金屬堆疊 (stack)，其中各層金屬層的厚度分別為底層鈦(bottom Ti)：50nm / 鋁：180nm / 上層鈦(Up Ti)：100nm，其中底層鈦主要是為了防止鋁金屬與玻璃基板之間的應力(stress) 所導致的突起(Hillock)現象，另外上層鈦主要是用於防止在400°C 以上，矽會擴散到鋁中而鋁也會回填到矽所留下的空缺而形成穿刺(Spike)，造成電路短路。

第二道光罩：是定義元件區域。閘極介電質結構為氮化矽( $\text{SiN}_x$ ) / 非晶矽(a-Si) /  $n^+$ 非晶矽，由電漿輔助化學氣像沉積(PECVD)系統所沉積而成，其各層的厚度分別為氮化矽：345nm / 非晶矽：200nm /  $n^+$ 非晶矽：20nm。值得一提的是非晶矽通道長度主要是透過背面式通道蝕

刻(Back channel etching)製程形成，如圖 2-3，主要是先對源極/汲極金屬層做蝕刻，之後再對 $n^+$ 非晶矽過蝕刻，由於對 $n^+$ 非晶矽過蝕刻因此部份通道也會被蝕刻，所以通道的厚度一般會比較厚約 200nm。

第三道光罩：是源極/汲極金屬，其沈積方式與閘極金屬一樣都是濺鍍，另外其組成也是鈦/鋁/鈦，其各層的厚度也與閘極金屬相同。

第四道光罩：是氮化矽(用途為當 Passivation)，其是藉由物理增強型化學氣像沉積系統所沉積而成，厚度則是 300nm。

第五道光罩：為氧化銻錫(Indium Tin Oxygen 簡稱 ITO)，主要功能為當做電極 (Electrode)，利用電場使液晶 (Liquid crystal) 旋轉因而改變光通過面板的強度。詳細各層厚度如表 2-1 所示。而整個元件的寬(Width 簡稱 W)和長(Length 簡稱 L) 經過量測為  $W / L = 14.5 \mu\text{m} / 4\mu\text{m}$  如附圖 2-4 所示。

## 2.2 放電幕那現象描述

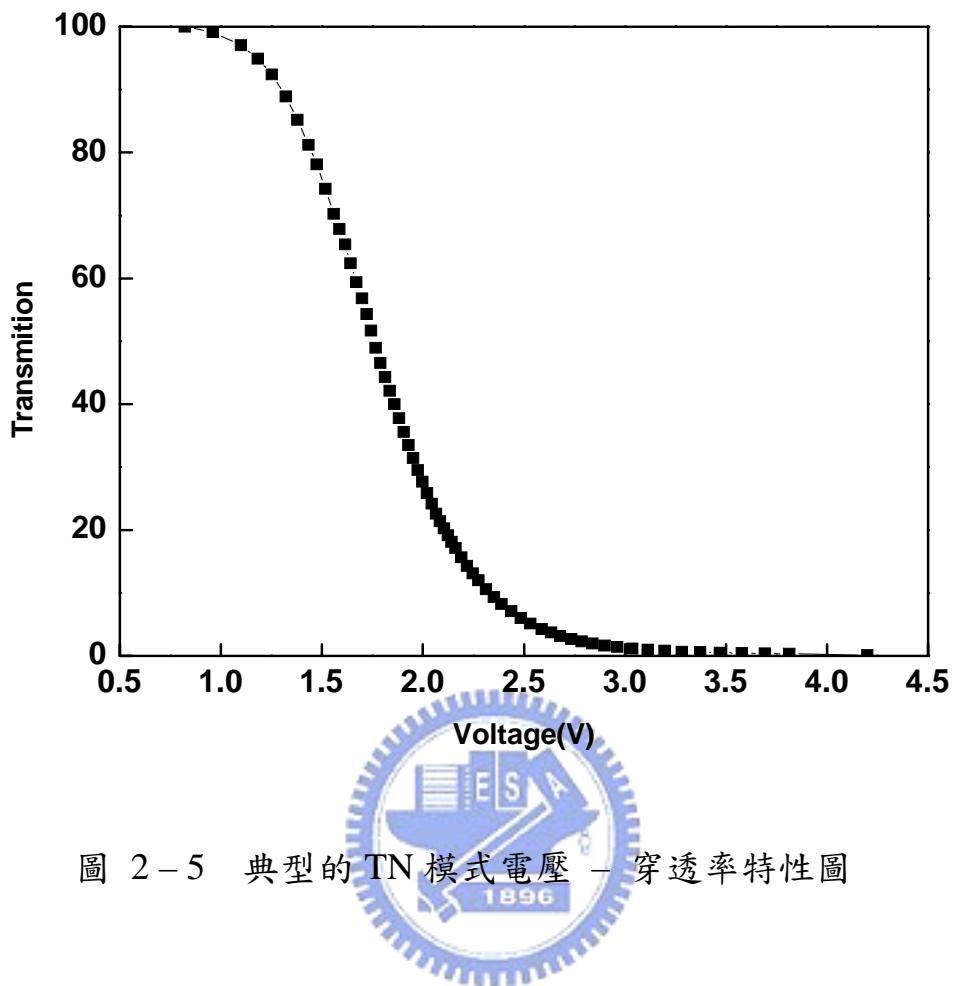

液晶顯示器的驅動原理主要是藉由閘極驅動器(Gate driver)與資料驅動器(Data driver) 來控制NMOS元件對氧化銻錫導電層(Pixel ITO) 充電，再透過與另外一片彩色濾光片基板(Color Filter substrate)上的 $V_{\text{com}}$  (共通電極) 做電壓差，促使液晶旋轉改變光通過的量，達到控制顯示器灰階明亮度。電壓差與光穿透的電壓 - 穿透率曲線圖( $V - T$  curve)如圖 2-5 所示，在正常的情況下當資料驅動器給面板

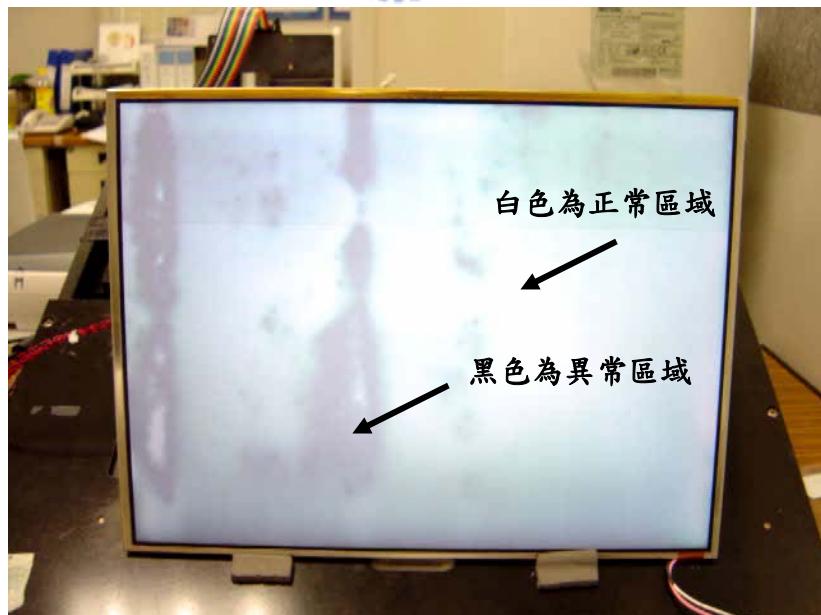

一個全黑畫面的訊號，正常面板整個螢幕必須要顯示全黑畫面，但如果某些區域顯示的灰階與正常的黑畫面灰階不同，這種灰階不均勻的現象稱為幕那，另外當面板只有在關機後所看到的幕那現象我們就稱之為放電幕那，如圖 2-6 所示。

一般會造成放電幕那這種現象主要是因為不同元件在電源關機後放電速度不一，為了釐清造成放電幕那的原因，在接下來的章節將會有各種可能造成的原因分析討論。

### 2.3 放電幕那可能原因分析

我們首先根據前面的描述針對 TFT 元件分析如下：

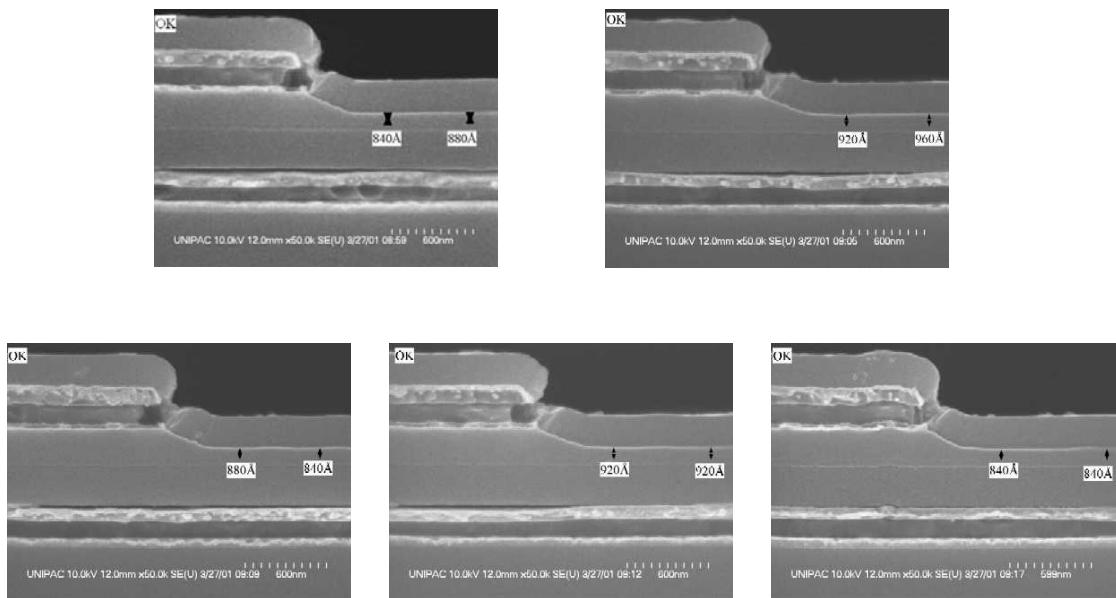

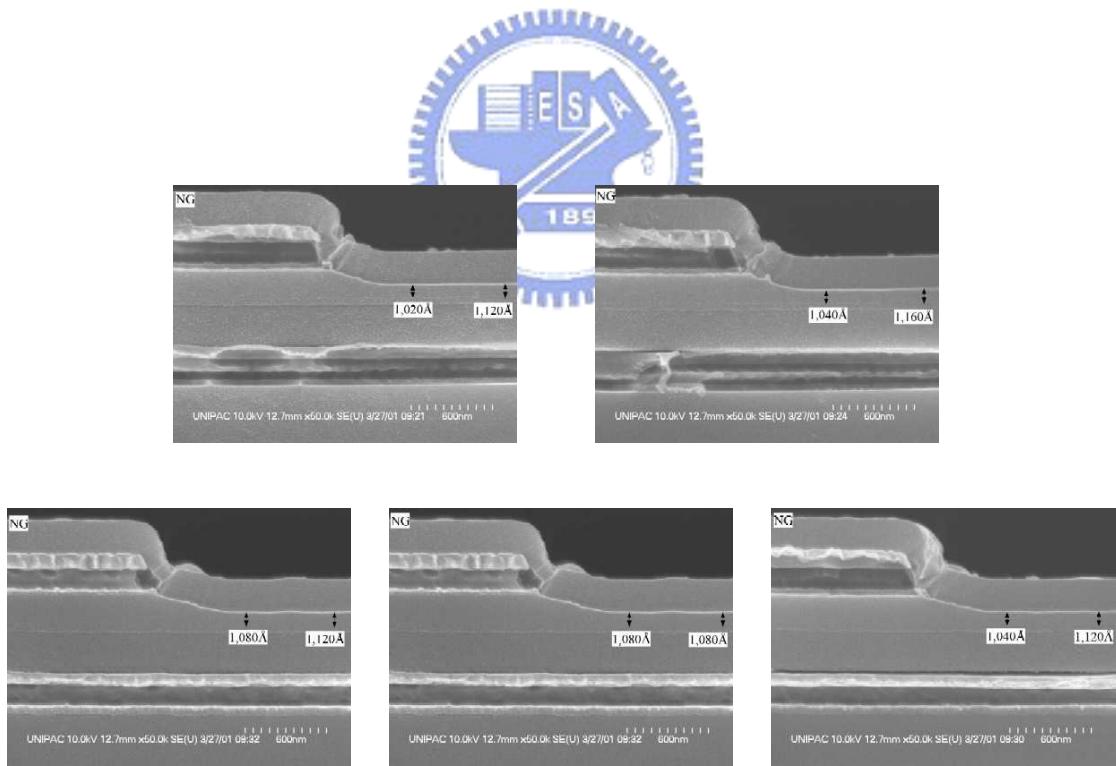

#### 一、 非晶矽層厚度量測：

為了瞭解非晶矽層厚度與放電幕那之間的關係，因此特別量測正常區域(幕那白色區域)的膜厚及異常區域(幕那黑色區域)的膜厚，經過量測之後，發現正常區域的膜厚平均為 89.6nm，而異常區域的膜厚平均為 112nm，如表 2-2 所示，異常區域的膜厚平均比正常區域膜厚多 22.4nm。由此量測可以知道正常區域與異常區域的膜厚存在差異性，與放電幕那不均勻的現象相同，關於正常區域與異常區域的量測膜厚分別如圖 2-7 及 2-8 所示。但是厚度影響放電速度的機制則不清楚。

## 二、電流 - 電壓曲線確認：

分別量測放電幕那與正常區域元件的電流 - 電壓曲線，經使用 Keithley 4200 精密電表所量到正常與異常區域元件電流 - 電壓曲線如圖 2 - 9 所示，可以看出正常與異常區域的電流 - 電壓曲線並沒有任何明顯差異，且  $I_{on}$  約為  $2 \times 10^{-6} \text{ A}$  左右而  $I_{off}$  約為  $1 \times 10^{-11} \text{ A}$ ，因此放電幕那並無法以電流 - 電壓曲線來判別。

## 三、元件結構觀察：

分別取異常與正常區域的元件，以掃瞄式電子顯微鏡(SEM)觀察其差異，發現正常與異常區域的元件在源極/汲極 金屬四周邊緣都有蝕刻後殘留的顆粒，如圖 2 - 10 所示，由於正常與異常區域皆有這種現象，因此排除與放電幕那有關。另外以穿透式電子顯微鏡(TEM)觀察元件側視圖，由圖 2 - 11 可以發現源極端有殘留金屬顆粒，且經由電子能量消散能譜(EDX)的分析得知為鈦(Ti)金屬。為了釐清此殘留金屬顆粒是否是造成放電幕那的主因，我們進行以下估算：假設 Ti 的電阻係數為  $\rho = 50 \mu\Omega \cdot \text{cm}$ ，長度(Length) =  $20 \mu\text{m}$ ，偏壓  $V = 10\text{V}$ ，漏電流  $I = 10\text{pA}$  則，表示漏電路徑阻抗  $R$  為：

$$R = \frac{V}{I} = \frac{10\text{ Volt}}{1 \times 10^{-11} \text{ Amp}} = 1 \times 10^{12} \Omega = \rho \frac{L}{Area} = 50 \times 10^{-6} \times \frac{20 \times 10^{-4}}{Area}$$

故截面積  $A = 1 \times 10^{-19} \text{ cm}^{-2}$ ，因此直徑  $2r = 3.6 \times 10^{-10} \text{ cm}$  長度  $L = 3.2 \times 10^{-10} \text{ cm}$ 。另外假設電流  $I = 1 \times 10^{-8} \text{ A}$  則面積  $A = 1 \times 10^{-16} \text{ cm}^2$  因此長度  $L = 1 \times 10^{-8} \text{ cm}$ ，因為求出的金屬顆粒長度太小比原子還小不可能存在。另外假設這樣的漏電路徑是存在的，則其電流密度  $J = 100 \text{ MA/cm}^2$ ，必然會燒斷(Stringer burned out)，因此再次證明在源極與汲極之間並不存在連續串接的殘留金屬顆粒使源極與汲極產生漏電流路徑，所以從圖 2-11 中所看到的殘留金屬顆粒應該只是個單一殘留金屬顆粒與放電幕那無關。

另外再次透過穿透式電子顯微鏡去觀察正常與異常元件，從圖 2-12 可以看出正常與異常元件的通道層並不存在任何缺陷，且在層與層之間的介面也無任何異狀，因此會造成放電幕那的差異應該與通道層沉積狀態無關。

#### 四、樹脂(PI)膜厚相關性確認：

由於樹脂(Polyimide 簡稱 PI) 膜主要功用是讓液晶能夠規則排列使液晶具有控制性，樹脂膜厚的差異亦有可能導致放電幕那現象發生，因此分別取具有放電幕那與正常區域，以掃瞄式電子顯微鏡觀察樹脂膜厚的差異，經過測量得到正常與異常區域的膜厚如表 2-3，

雖然樹脂膜厚極不均勻，但正常與異常區域之樹脂膜厚並沒有絕對的關係，因此推論放電幕那與樹脂膜厚無關。

## 五、源/汲極上下電極相關性確認：

追蹤至此，發現放電幕那現象似乎與源極/汲極蝕刻機台有關。進一步追查發現更換蝕刻機台的上電極前後，產品發生放電幕那的比率相同，因此放電幕那與上電極無關聯性。但比較更換各種型號的下電極前後，發現發生放電幕那的比率與下電極型號有強相關，其中 A 型號改善效果優於 B 型號及 C 型號，因此可以說放電幕那主要是發生在當下電極有異常時所導致的。

乾式蝕刻機台內具有上下電極，其中下電極板主要成份為鋁(Al)機材，而鋁基材會透過洗床機具來使表面平整均勻，然而鋁基材在洗床的過程中難免在表面還是會產生些許紋路，另外鋁基材的表面也需要經過陽極處理使其表面反應生成一層的陽極膜，一般陽極膜的厚度約為  $60\mu\text{m}$ ，而陽極膜主要是用來保護電極板，由於洗床過程中產生的不平整，使電極板產生紋路區域因為電場強度與其他平整區域不同，導致陽極膜在乾式蝕刻過程中被帶正電的離子撞擊後產生不均勻的現象，這種不均勻的現象會反應在通道的品質上，經過長時間的日積月累之後這種不均勻的現象更為嚴重因而產生放電幕那，由於放電

幕那本身就是一種不均勻的現象，根據工廠的分析去實際比對玻璃面板出現放電幕那的區域正好就是電極鋁基板在洗床過程中產生紋路的區域，因此可以證明放電幕那與下電極板有關。

## 2.4 工程上迴避放電幕那的方法

雖然從製程追蹤的方式發現與放電幕那相關連的機台，但是物理機制並不清楚，在未能從根本解決之前，可以先從工程設計的角度設法改善，以下略做說明。

### (1) 定期更換下電極板：

由於在通道蝕刻過程中，因為電極板洗床有產生紋路區域與沒有產生紋路區域的電場不同，但在新電極剛開始使用過程中並不會立即產生電場明顯的差異，因此我們可以觀察當下電極使用多久時，會使蝕刻後的通道厚度產生明顯的差異因而造成放電幕那，而我們只要正確設定更換下電極板的週期，就可避免放電幕那發生。

### (2) 修改電路設計在面板關機後加速放電：

一般在面板關機後，所有內部電源及訊號都會關閉，這會導致 $V_{gh}$  ( $V_{gs}$ ) 電壓馬上降為 0V，因而使  $I_{ds}$  的電流變小，面板放電時間變長，如果我們讓面板關機後，使  $V_{gh}$  電壓還能維持一段

時間如圖 2 – 13 所示，這時使所有元件都打開維持高的  $I_{ds}$  電流，則就可以加速面板放電速度，減少放電幕那現象產生。

## 2.5 放電幕那機制探索

前面 2.3 節已經提到放電幕那幾種傳統成因的排除，其中最主要與蝕刻機台下電極板的異常有關，因此工程上最佳的迴避方法就是定期更換下電極板，然而放電幕那隱藏在背後的真實原因才是本論文想到探討的主題。從圖 2 – 9 可以看出正常與異常有放電幕那的元件其在相同的  $V_{gs}$  電壓時相對應的  $I_{off}$  電流也相同，因此放電幕那與 DC 電流 – 電壓曲線的  $I_{off}$  電流無關，另外從 AC 的角度來看，當將  $V_{gs}$  電壓從 15V 切換到 0V 時去量測正常與異常有放電幕那的元件，我們可以觀察到兩者之間放電的暫態電流明顯不同，會有這樣的差異主要與通道的品質有關，當通道的禁錮缺陷越多時其暫態電流放電時間相對也會比較長。

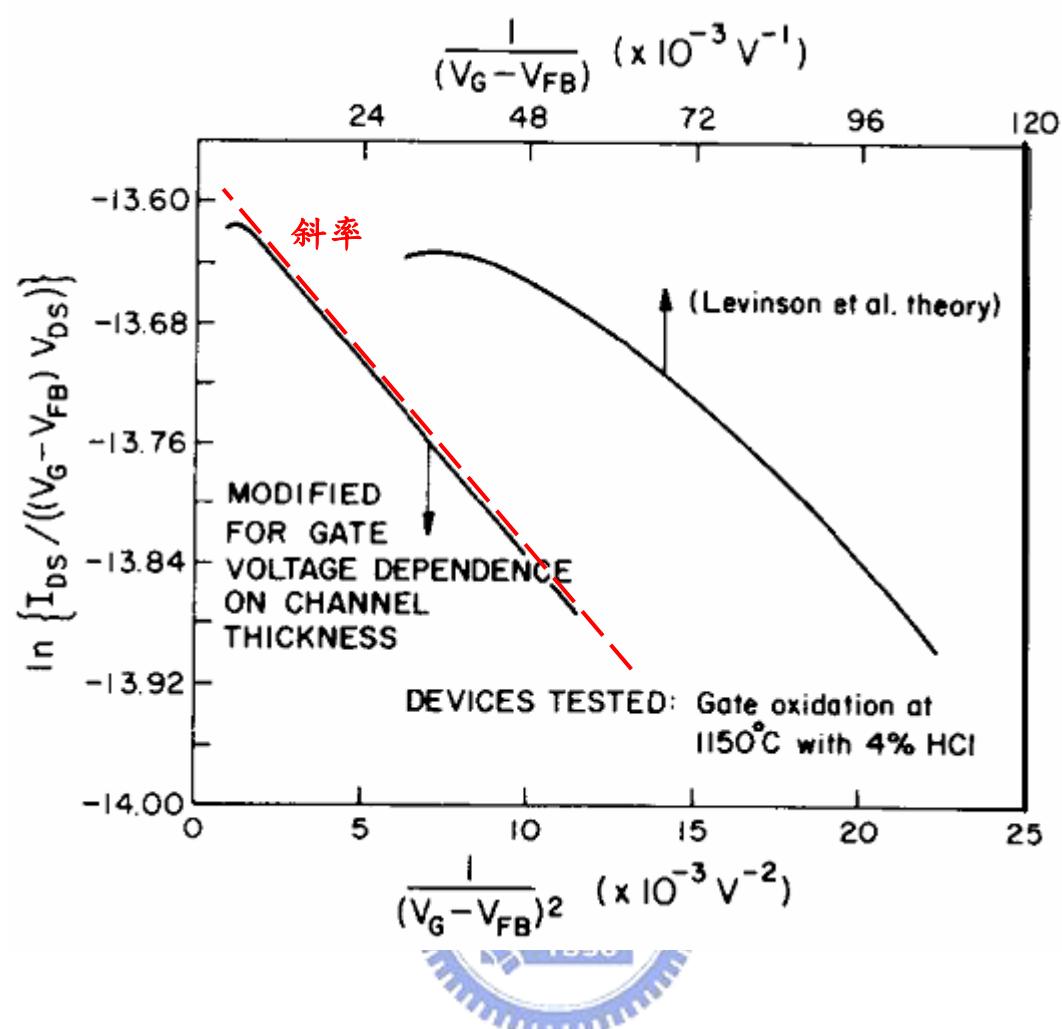

### 2.5.1 改良型戴韋遜(Modified Levinson)的原理

為了有效將放電幕那量化成缺陷密度的數值，本節利用改良型戴韋遜方法計算缺陷密度的數值。

改良型戴韋遜方法量測原理為量測穩態電流。量測固定偏壓下通

道的電流(I) – 電壓(V)曲線，此電流 – 電壓曲線因缺陷中心會禁錮電子使得空間電位有別於沒有禁錮電子通道的狀況，因此得以利用此種因區域性禁錮電子的特性進而影響穩態電流的變化，所以我們可以利用此變化得以去推測缺陷的數量。

此方法於 1989 年由 R. E. PROANO & R. S. MISAGE & D. G. AST [4]提出，在次臨界區域，電流-電壓特性公式為：

$$I_{DS} = (W / L_{eff}) * C_{ox} * (V_G - V_{FB}) * V_{DS} * \mu_{BO} * \exp\left\{-\frac{qE_B}{kT}\right\} \quad \text{-----(1)}$$

$$E_B = q^2 Q_T^2 t / 8 \varepsilon_{si} C_{ox} (V_G - V_{FB}) \quad \text{-----(2)}$$

$$t = \left\{ 8KTt_{ox} \sqrt{(\varepsilon_{si}/\varepsilon_{sio_2})} \right\} / \{q(V_G - V_{FB})\} \quad \text{-----(3)}$$

其中  $q$  為電荷， $k$  為波茲曼常數， $\varepsilon_{si}$  為矽的介電常數， $C_{ox}$  為閘極氧化層電容， $t$  為通道的膜厚， $V_{FB}$  為平板電壓， $E_B$  為晶粒邊界能障(grain boundary potential barrier)， $Q_T$  為禁錮缺陷密度。分別將公式(2)及(3)帶入(1)內，經過化簡之後就可以得到下式：

$$Q_T = \frac{C_{ox}}{q} \sqrt{|slope|} \quad \text{-----(4)}$$

由上公式可知要求出禁錮缺陷密度  $Q_T$  需先求出斜率(Slope)，為了求出斜率需先量出元件的電流-電壓曲線，在文獻[4]中有提到當電流-電壓曲線的最小漏電流  $I_{DS}$  所對應到的  $V_G$  電壓即是  $V_{FB}$ ，因此將  $V_{FB}$  的值帶入式子經過換算成  $\ln\{I_{DS}/((V_G - V_{FB})V_{DS})\}$  對  $1/(V_G - V_{FB})^2 (\times 10^{-3} V^{-2})$

的曲線後就可以求出斜率。

### 2.5.2 改良型戴韋遜量測方法

首先將待測元件置於探針量測台的平臺上，以Keithley 4200 測量電流( $I_{ds}$ ) – 電壓( $V_{gs}$ ) 曲線，其中 $V_{ds}$ 的電壓固定在 5V 而 $V_{gs}$ 電壓的範圍從-20V到 20V，每 0.5V 量測一次，即可得到如圖 2 – 9 的電流-電壓曲線。再來就是將前面所求出電流( $I_{ds}$ ) – 電壓( $V_{gs}$ ) 曲線的資料轉換成如圖 2 – 14 的曲線圖並找出斜率，最後再將斜率值帶入公式(4)內即可以求出禁錮缺陷密度 $Q_T$ 。以這次分析的元件來看，量出的電流( $I_{ds}$ ) – 電壓( $V_{gs}$ ) 曲線如圖 2 – 9，電流最小值發生在 $V_G = V_{FB} = -2.5V$ ，再經過換算可以得到圖 2 – 15 的曲線，並求出斜率 = -303。根據元件通道厚度  $d = 3450 \times 10^{-8} \text{ cm}$ ，將斜率值帶入公式(4)可得到  $Q_T = 1.08 \times 10^{12} \text{ cm}^{-2}$ 。

總共量測 6 組元件，包括 3 組正常的元件(又簡稱 White mura)及 3 組有放電幕那現象的元件(又簡稱 Black mura)，我們可以發現這 6 組元件所量測出來的電流( $I_{ds}$ ) – 電壓( $V_{gs}$ ) 曲線幾乎相同，如圖 2 – 9 所示，因此所量測出的禁錮缺陷密度值也相同，所以改良型戴韋遜的方法無法有效地反應出幕那元件放電速度的快慢與禁錮缺陷密度之間的關係。我們推測是因為改良型戴韋遜方法是測量穩態特性，而放電幕那是一暫態特性。為了找出兩者之間的關係，在下一章我們將利用

暫態電流的量測方法，求出元件禁錮缺陷的暫態反應。

表 2-1 薄膜式電晶體各層厚度

| Layer | Material |          | Thickness (A) | Tool    |

|-------|----------|----------|---------------|---------|

| GE    | Ti/Al/Ti |          | 500/1800/1000 | Sputter |

| AS    | 3L       | SiNx     | 3450          | PECVD   |

|       |          | a-Si     | 2000          |         |

|       |          | n+ a- Si | 200           |         |

| SD    | Ti/Al/Ti |          | 500/1800/1000 | Sputter |

| BP    | SiNx     |          | 3000          | PECVD   |

| ITO   | a-ITO    |          | 750           | Sputter |

表 2-2 通道膜厚量測統計表

|            | 1    | 2    | 3    | 4    | 5    | Average |

|------------|------|------|------|------|------|---------|

| White area | 880  | 960  | 880  | 920  | 840  | 896     |

| Black area | 1120 | 1160 | 1120 | 1080 | 1120 | 1120    |

表 2-3 PI 膜厚量測值

|   | PI 厚度 (um) |      |

|---|------------|------|

|   | 異常區域       | 正常區域 |

| 1 | 1018       | 580  |

| 2 | 1029       | 659  |

| 3 | 646        | 838  |

| 4 | 640        | 670  |

| 5 | 1000       | 789  |

| 6 | 1157       | 719  |

| 7 | 719        | 579  |

| 8 | 620        | 539  |

圖 2-1 薄膜式電晶體製程步驟

圖 2-2 薄膜式電晶體之掃瞄式電子顯微鏡剖面影像

圖 2-3 背面式通道蝕刻方法示意圖

圖 2-4 薄膜式電晶體的  $W/L = 14.5\mu m / 4\mu m$

圖 2-5 典型的 TN 模式電壓 - 穿透率特性圖

圖 2-6 放電幕那

圖 2-7 白色正常幕那量測的膜厚

圖 2-8 黑色異常幕那量測的膜厚

圖 2-9 元件的電流 - 電壓曲線

圖 2-10 正常與異常元件在蝕刻後殘留顆粒示意圖

圖 2-11 殘留顆粒經電子能量消散能譜分析出為鈦金屬

圖 2-12 正常元件與異常元件在穿透式電子顯微鏡下觀察的現象

圖 2-13 電路設計修正前後  $V_{gh}$  放電的變化

圖 2-14 改良型戴韋遜斜率的求出方法

圖 2-15 改良型戴韋遜斜率的求出方法

# 第三章 暫態電流方法及系統架設

本章主要是探討如何將放電幕那(Discharge mura)量化成暫態反應缺陷密度(defect density)，以下將會說明暫態電流(Transient current)的量測方法，另外會就量測儀器系統與儀器參數設定作一個探討，最後就是實際利用暫態電流方法去量測具有放電幕那的元件，並求出暫態禁錮缺陷密度(Trap defect density)的數值。

## 3.1 暫態電流的原理

暫態電流的形成是由於元件在工作狀態時，缺陷中心(Trap center)禁錮電子，使得缺陷中心存有區域性的空間電荷，當加在元件上的電源瞬間關閉時，則整體空間電位開始變化，而原本禁錮電子的缺陷中心受此整體電位的變化，本身區域性電位亦隨著改變，致使原先被禁錮的電子開始釋出，成為電源關閉時所量到的暫態電流，此電流隨著時間的增長而遞減。由於電流會慢慢隨著時間而遞減，因此我們可以推導出一個特定的電流 - 時間關係式，而由此關係式可推測受缺陷中心所禁錮的電子數多寡。

非晶矽(a-Si:H) 元件本身具有許多缺陷，這些缺陷主要來自於氮化矽( $\text{SiN}_x$ )與非晶矽的介面缺陷(interface defect)、非晶矽層本身的缺陷及背面式通道蝕刻後所產生的缺陷。2000 年 Lemmi & Robert A. 提出了正確量測非晶矽元件缺陷的方法[5, 6]，一般而言元件在電源關閉的狀態下我們在源極(source)端可以量到  $I_{ds}$  的暫態電流，這個暫態電流會隨著時間慢慢遞減到穩定狀態(Steady state)，而整個暫態電流量測時間從  $10^{-3}$  到 100 秒，且暫態電流遞減的過程趨近於  $1/t$ ，如圖

3 – 1 所示。我們可從暫態電流遞減曲線中換算得到非晶矽中的禁錮缺陷密度。由於這整個暫態電流主要由通道電荷釋放(Channel charge emission)及汲極接觸面射出電荷(Drain contact injection)所組成，但汲極接觸面射出電荷並不是缺陷的一種，而是當電場強度在汲極接觸面兩端變大時，原本通道應該進入空乏區(Depletion)及電洞累積(Holes accumulation)的狀態，但當汲極接觸面兩端電場強度越變越大時，汲極接觸面兩端就會造成通道穿遂(Punch through)形成汲極接觸面射出電荷。Lemmi & Robert A.的論文提到，當  $V_{ds}$  電壓只要低於 +0.8V，則汲極接觸面射出電荷就可以忽略不計，因此在  $V_{ds}$  電壓低於 +0.8V 的情況下量到的暫態電流就等於通道電荷釋放電流，所以我們可以從暫態電流中換算得到非晶矽的禁錮缺陷密度。

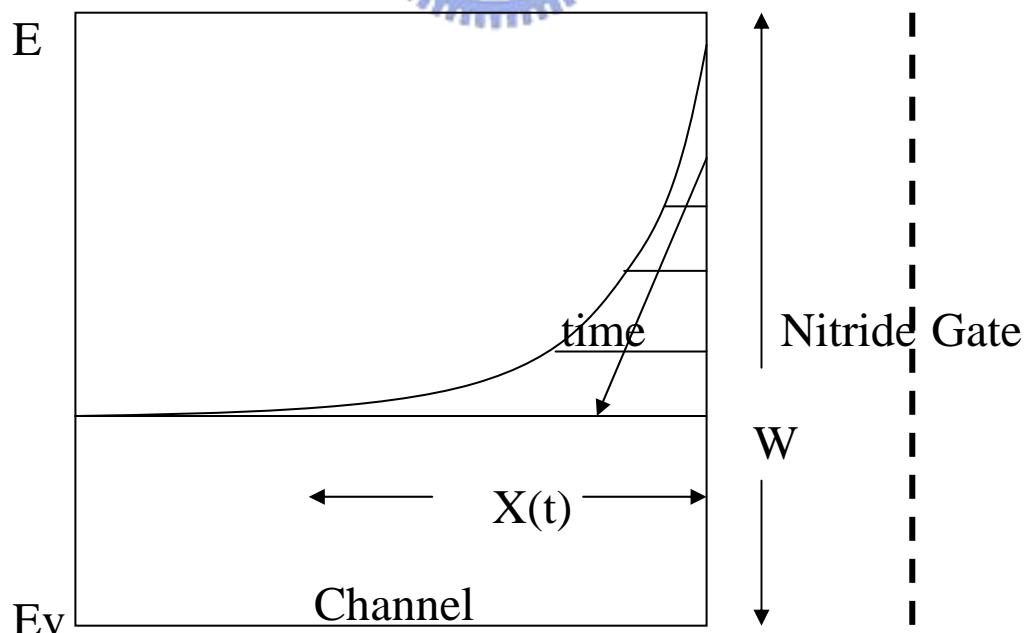

首先我們假設通道為一個均勻的材料且延著通道與閘極絕緣層介面有均勻的能帶彎曲，亦即等電位。最大的熱激發(thermal emission)發生於費米能階上下  $\frac{1}{2}KT$  區間，令此區間內的缺陷能態密度為  $N(E_f)$ ，且等效通道厚度為  $x(E_f)$ ，即為通道能帶彎曲的長度如圖 3 – 2， $E_c$  為傳導帶的基態能階及  $f(E,t)$  為與時間相關的費米函數(Fermi function)，所以熱載子傳導比率為[7]：

$$\frac{dQ}{dt} = q \times W \times L \times N(E_f) \times x(E_f) \times \int_{E_f - \frac{kT}{2}}^{E_f + \frac{kT}{2}} f(E, t) \times \omega_0 \times e^{-\frac{E_c - E}{kT}} \times dE \quad \text{--- (1)}$$

其中  $q$  為電荷常數， $k$  為波茲曼常數， $T$  為絕對溫度， $L$  與  $W$  分別為元件通道的長與寬。

假設位於能隙中費米能階的時間鬆弛關係如下：

$$\left\{ \begin{array}{ll} E_f(t) = E_{f0} & \text{for } t < t_0 = \omega_0^{-1} \times e^{\frac{E_{f0}}{kT}} \\ \\ E_f(t) = E_C - KT \times \ln(\omega_0 t) & \text{for } t > t_0 = \omega_0^{-1} \times e^{\frac{E_{f0}}{kT}} \end{array} \right. \quad \text{--- (2)}$$

其中  $E_{f0}$  是費米能階在累積狀態下的初始位置， $\omega_0$  則是射出率，其一般值為  $1 \times 10^{13} \text{ sec}^{-1}$ ，價帶(valence band)的邊界則做為參考能階。假設  $E_C - E > kT$  且時間  $t$  遠大於  $\omega_0^{-1}$  及  $t_0$ ，則  $f(E, t)$  可被近似為：

$$f(E, t) \approx \frac{e^{\frac{E_C - E}{kT}}}{\omega_0 t} \quad \text{--- (3)}$$

將第(3)式帶入(1)式內則我們可以得到暫態電流為：

$$I(t) = q \times K \times T \times L \times W \times N(E_f) \times x(E_f) \times \frac{1}{t} \quad \text{--- (4)}$$

所以禁錮電子缺陷密度  $N(E_f)$  為：

$$N(E_f) = \frac{I(t)}{q \times K \times T \times L \times W \times x(E_f)} \times t \quad \text{--- (5)}$$

由(4)式知暫態電流  $I(t)$  與時間  $1/t$  成正比，當我們從量到的暫態電流  $I(t)$  對時間  $t$  的曲線中，如果固定時間則可以求得一個相對的暫態電流值，將非晶矽元件的有效厚度帶入  $x(E_f)$ ，則我們就可以求出禁錮缺陷密度  $N(E_f)$  的值。

### 3.2 暫態電流量測系統

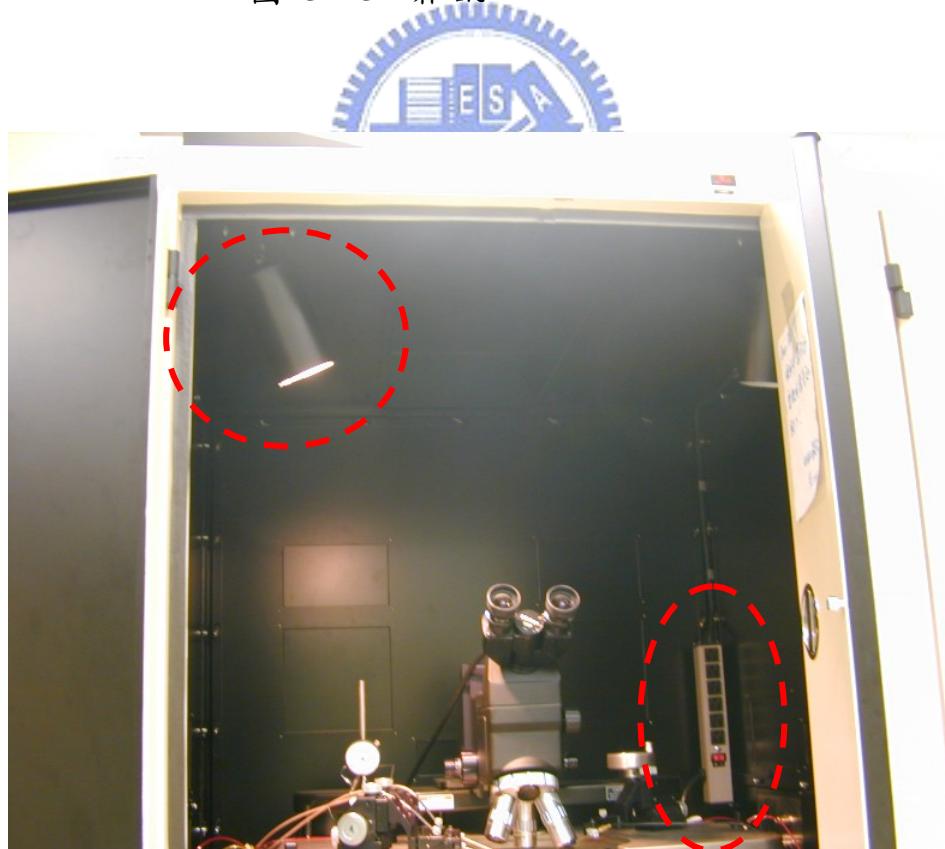

本論文擬量測的暫態電流是元件在關機瞬間後的電流，量測時間約在 1ms 到 100s 之間。對於時間大於 1s 以上時，可以使用 Keithley 4200 電子電表(electrometer)，它具有解析度 0.1 fA 的能力。對於極短時間內的暫態電流則需要以 Keithley 428 電流放大器搭配 Tektronix TDS 784D 數位示波器一起使用。電流放大器具有  $10^{11}$  V/A 的放大倍率，但同時需搭配適當的上升時間濾波功能(Rise time filter)以降低雜訊(Noise)干擾。如果上升時間濾波功能選擇的時間太長，量到的暫態電流時間就會等於濾波的時間，但如果濾波選擇的時間太短，則雜訊過高。

由於 Keithley 428 每次只可以調整在 10 倍的放大範圍內如  $10^8$  到  $10^9$  內，因此每量一次放大倍率就需調整一次，經過 Keithley 428 所量出來的訊號會被反相，這都是在實際使用時須注意的事項。

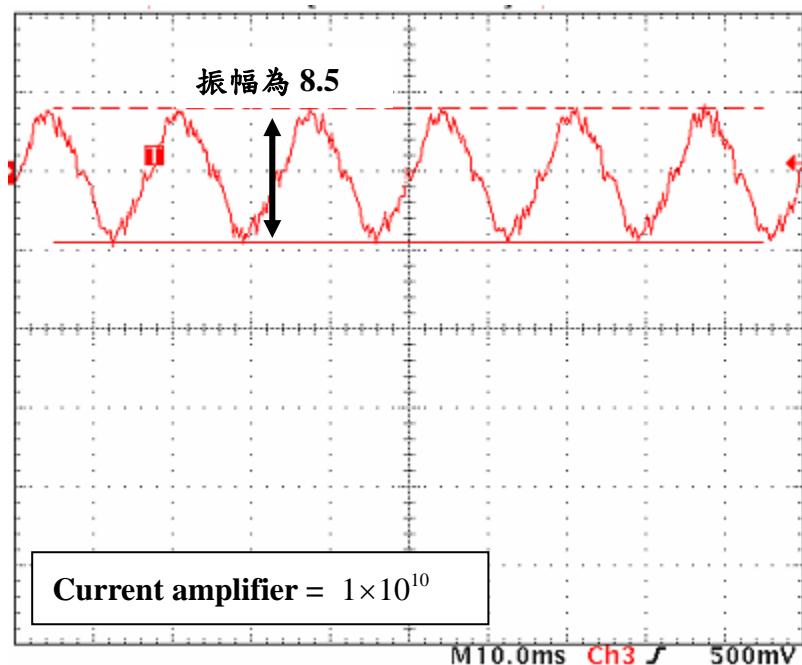

### 3.3 雜訊抑制

雜訊抑制是測量低暫態電流的重點。一般探針量測台(Probe station)外的遮蔽箱(Shield box)本身雖具備良好隔絕外界雜訊的能力，但是當待測的暫態電流低於 10nA，外界雜訊仍然很容易就會被電流放大器放大進而影響量測數據的準確度。如圖 3-3 所示，當只有遮蔽箱而無其它抑制雜訊對策時，會有約 0.85nA 的背景雜訊。以下提供幾點量測暫態電流時，抑制雜訊的技巧：

- (1) 將所有提供遮蔽箱內使用的交流電源拔除，如圖 3-4 所示，避免市電透過電源線耦合傳入遮蔽箱內。

- (2) 遮蔽箱的門本身與遮蔽箱主體均需接地，如圖 3-5 所示。

- (3) 乘載待測物的基座(substrate)特別是加熱板(Thermal chuck)，

本身易藉由電源線將外界雜訊傳給基座，而待測物又直接與基座接觸，所以雜訊干擾也最為嚴重，解決之道就是將基座與遮蔽箱主體短路，如圖 3-6 所示，使基座接地，將雜訊排除。

### 3.4 禁錮缺陷的量測

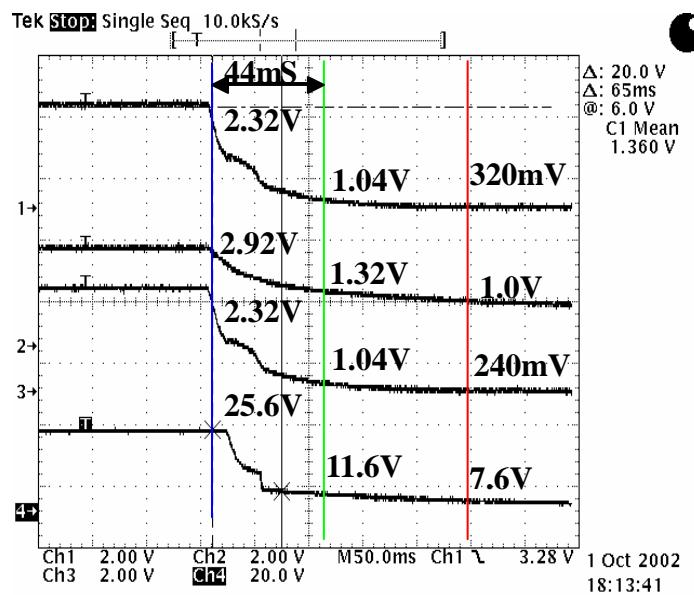

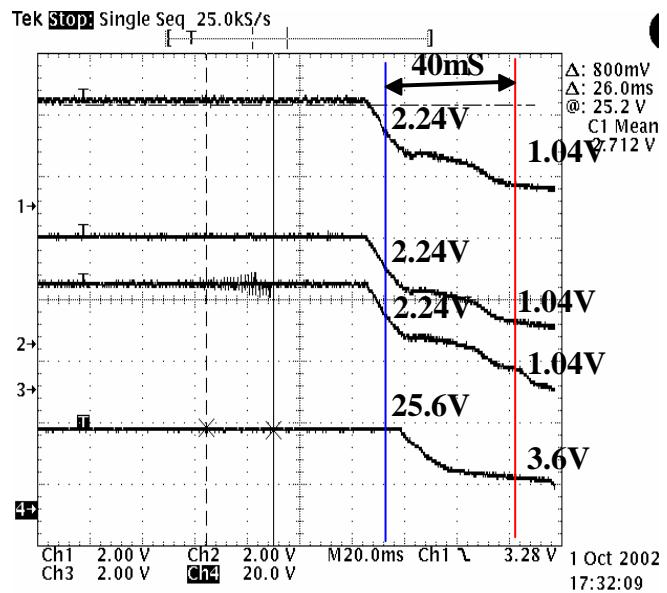

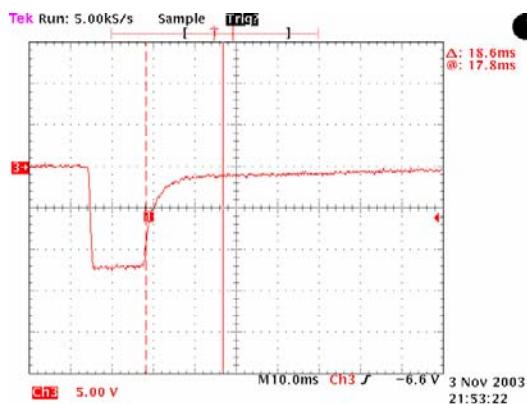

暫態電流的針測方式如圖 3-7 所示，將汲極與源極透過一個轉接頭將兩端短路再接到Keithley 428 電流放大器上，如圖 3-8。將汲極與源極短路主要是避免量到的暫態電流內含有汲極接觸面射出電荷的電流，另外在量測暫態電流時， $V_{gs}$  會從 15V 切換到 0V，以模擬面板關機後的現象。我們用暫態電流量測法測量第二章的 6 個元件的暫態電流。當  $V_{gs}$  從 15V 切換到 0V 後，典型的訊號如圖 3-9 所示，經過整理之後可以畫出如圖 3-10 的暫態電流對放電時間曲線圖。從圖 3-10 可得到正常白色幕那最後穩定時的暫態電流對應到的放電時間約為 300msec 左右，與第一章實際放電幕那放電時間吻合，而異常黑色幕那最後穩定時的暫態電流對應到的放電時間約為 650msec 左右，也與第一章實際放電幕那放電時間吻合。

由於暫態電流隨時間遞減，為了在相同的條件下去比較 6 個元件的禁錮缺陷密度  $N(E_f)$ ，我們定義暫態時間為當暫態電流最後趨近於穩定值時，其相對應的時間。從圖 3-10 得到的暫態電流與暫態時間關係列於表 3-1，當正常白色幕那 1 在  $I_{ds} = 2.5 \times 10^{-10} \text{ A}$  時，相對應的放電時間為 300.84ms，將元件的  $L/W = 4.5\mu\text{m} / 14\mu\text{m}$  與有效膜厚  $x(E_f)$  為 125nm，因此帶入公式(1)可以求出禁錮缺陷密度  $N(E_f)$  為：

$$N(E_f) = \frac{I(t)}{q \times K \times T \times L \times W \times x(E_f)} \times t$$

$$\text{所以 } N(E_f) = 2.3 \times 10^{21} \text{ cm}^{-3} \text{ eV}^{-1}$$

依此類推，各元件的禁錮缺陷密度列於表 3 – 1(a)及(b)，可以得知異常區域的黑色幕那的禁錮缺陷密度的確比正常區域的白色幕那還高，而這也是導致放電幕那現象的根本原因。

表 3-1(a) 由暫態電流與暫態時間所求出的白色幕那禁錮缺陷密度

|                                              | White mura-1          | White mura-2          | White mura-3          |

|----------------------------------------------|-----------------------|-----------------------|-----------------------|

| 暫態電流(A)                                      | $2.5 \times 10^{-10}$ | $1.0 \times 10^{-11}$ | $1.7 \times 10^{-10}$ |

| 暫態時間(sec)                                    | 0.30084               | 0.2748                | 0.32026               |

| 禁錮缺陷密度<br>( $\text{cm}^{-3}\text{eV}^{-1}$ ) | $2.3 \times 10^{21}$  | $8.42 \times 10^{19}$ | $1.67 \times 10^{21}$ |

表 3-1(b) 由暫態電流與暫態時間所求出的黑色幕那禁錮缺陷密度

|                                              | Black mura-1          | Black mura-2          | Black mura-3          |

|----------------------------------------------|-----------------------|-----------------------|-----------------------|

| 暫態電流(A)                                      | $1.9 \times 10^{-10}$ | $2.9 \times 10^{-10}$ | $2.0 \times 10^{-10}$ |

| 暫態時間(sec)                                    | 0.60006               | 0.78476               | 0.66485               |

| 禁錮缺陷密度<br>( $\text{cm}^{-3}\text{eV}^{-1}$ ) | $3.49 \times 10^{21}$ | $6.97 \times 10^{21}$ | $4.07 \times 10^{21}$ |

圖 3-1 暫態電流對暫態時間曲線圖

圖 3-2  $x(E_f)$ 為通道有效厚度

圖 3-3 雜訊 =  $8.5 \times 10^{-10}$  A

圖 3-4 來自市電 60Hz 的雜訊來源

圖 3-5 短路線將遮蔽箱的門與遮蔽箱主體短路

圖 3-6 短路線將遮蔽箱主體與加熱板短路

圖 3-7 元件要被探針探測的位置示意圖

圖 3-8 暫態電流量測儀器的接法

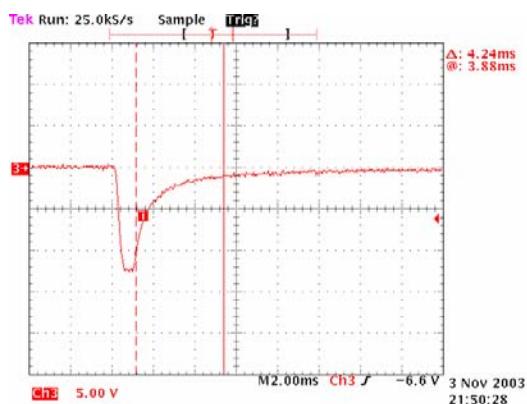

暫態時間=4.24msec 放大倍率=  $10^8$

暫態時間=18.6msec 放大倍率=  $10^9$

暫態時間=278msec 放大倍率=  $10^{10}$

圖 3-9 暫態電流及暫態時間量測值

圖 3-10 暫態電流及暫態時間的曲線圖

# 第四章 暫態電流量測方法的延伸應用

本章節主要是應用暫態電流測量技術分析不同製程條件的非晶矽薄膜電晶體(TFT)元件。由於非晶矽元件通道本身存在很多禁錮缺陷，因此我們將元件藉由 300°C 的氮氣電漿處理(NH<sub>3</sub> plasma treatment)來改善通道的禁錮缺陷數，文中將會介紹元件製程及氮氣電漿處理條件，藉由第三章所提到的暫態電流量測方法量測元件及經氮氣電漿處理後的元件，並由量測的數據求出元件的禁錮缺陷密度，最後分析經過氮氣電漿處理後的元件改善情況。

## 4.1 元件製作

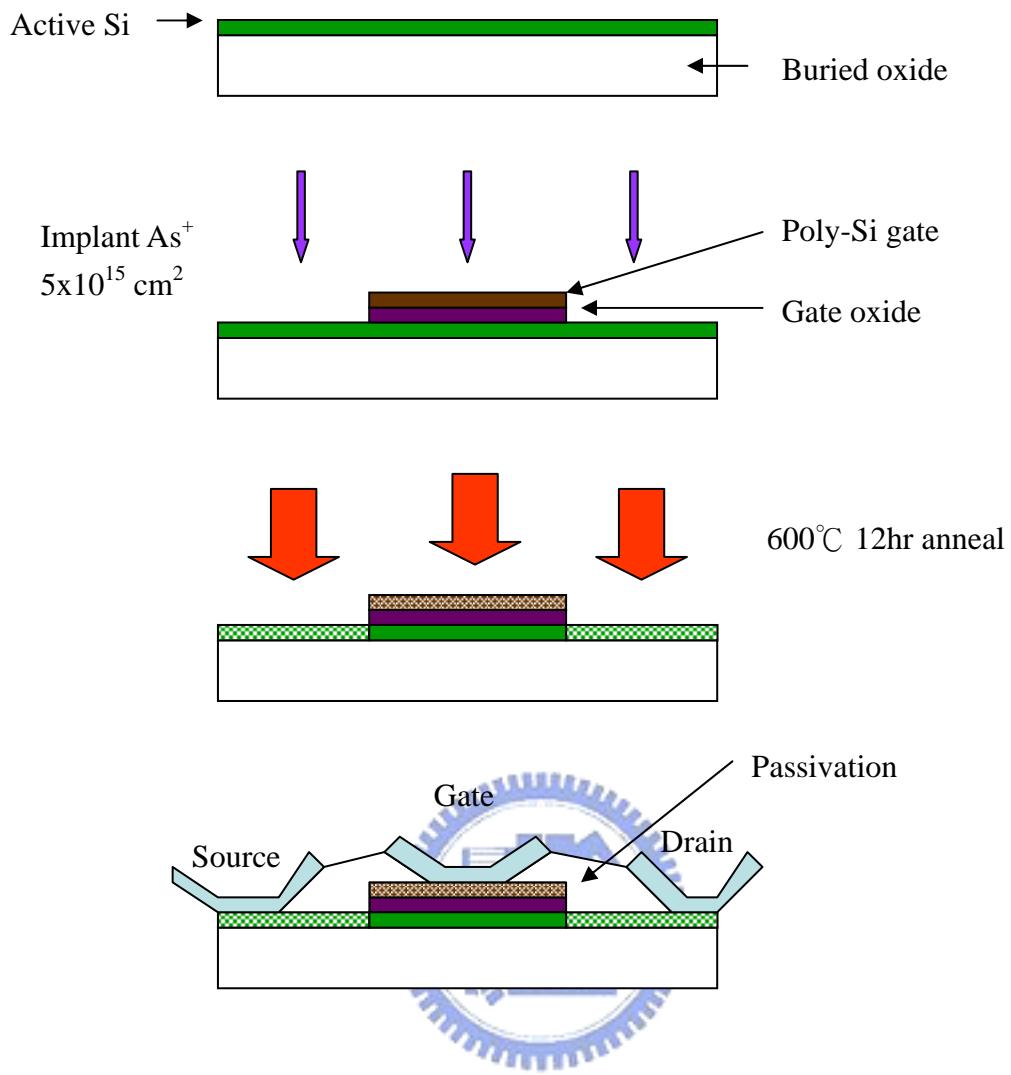

首先在(100)晶向矽晶片上利用濕式氧化(wet oxidation)的方式在矽晶片表面上長出 1 微米的二氧化矽絕緣層，用此以絕緣矽基板與元件，接著在 550°C 沈積 100nm 厚的非晶矽(amorphous silicon 簡稱 a-Si)，並藉由光阻塗佈機、G-line 曝光機及顯影設備，以傳統的微影技術定義出元件的主動區域(active region)，利用電漿蝕刻方式蝕刻非晶矽，分離各主動區域。接著利用低壓化學氣象沈積(LPCVD)爐管沈積 50nm 的氧化矽，作為閘極絕緣層，低壓化學氣象沈積機爐管沈積溫度為 550°C，通入氣體為 TEOS 及氧。沈積 100nm 的多晶矽(poly silicon)當作閘極(gate)電極使用。利用微影技術定義閘極圖案(gate pattern)，經多晶矽蝕刻形成閘極，接著進行源極(source)/汲極(drain)的砷(As)離子佈值，劑量為  $5 \times 10^{15} \text{ cm}^{-2}$ 、能量 65KeV，形成源/汲電極，同時亦摻雜多晶矽閘極以降低閘極電阻。接著經溫度 600°C 12 小時長時退火，以活化摻入雜質(dopant)。利用電漿增強化學氣象沈積(PECVD)設備沈積 300nm 的氧化矽，作為元件保護層(passivation layer)，最後

利用微影技術定義出金屬接觸窗(contact hole)及導線(interconnect)並藉由 G-line 微影產生所需的接觸窗，最後從接觸窗引出我們要的鋁金屬墊(Al pad)作為量測使用，詳細的元件說明如圖 4-1 所示。

## 4.2 氮氣電漿處理對 N 通道非晶矽的影響

利用氮氣電漿處理對於改善元件的通道缺陷具有很好效果的特性。由於氮氣電漿處理的時間越長，對於改善缺陷的效果也就越好，所以我們給予元件氮氣電漿處理，電漿處理環境條件為溫度 300°C、功率 200 watt、製程壓力 10 mtorr、時間包括 60 分鐘及 120 分鐘，使改善缺陷的效果不同，另外再透過暫態電流的量測就可以量化出缺陷數，並比較缺陷數的數量及驗證理論的實用性。

氮氣電漿處理能夠改善禁錮缺陷的機制是因為氫會繫住晶粒邊界(grain boundary)中的懸空鍵(dangling bond)，一旦懸空鍵被氫繫住它就變成穩定不再去捕獲其它電子。除此之外，氫也會可能累積在氧化矽/非晶矽介面間，並且形成很強的矽-氫鍵結，阻斷非晶矽晶粒邊界上的懸空鍵隨意捕獲其它電子，因而也可以減少缺陷數，並且增加了氧化層崩潰電壓(oxide breakdown)。

氮氣及氫電漿處理都具改善禁錮缺陷的能力，但為何選擇氮氣而不選擇氫電漿處理？因為從文獻[8]中得知在相同的條件下氮氣電漿處理對於改善禁錮缺陷具有較佳的能力，因此為了更加凸顯出處理前後的禁錮缺陷的變化，因此選擇氮氣電漿處理當作本次實驗改善的方法。

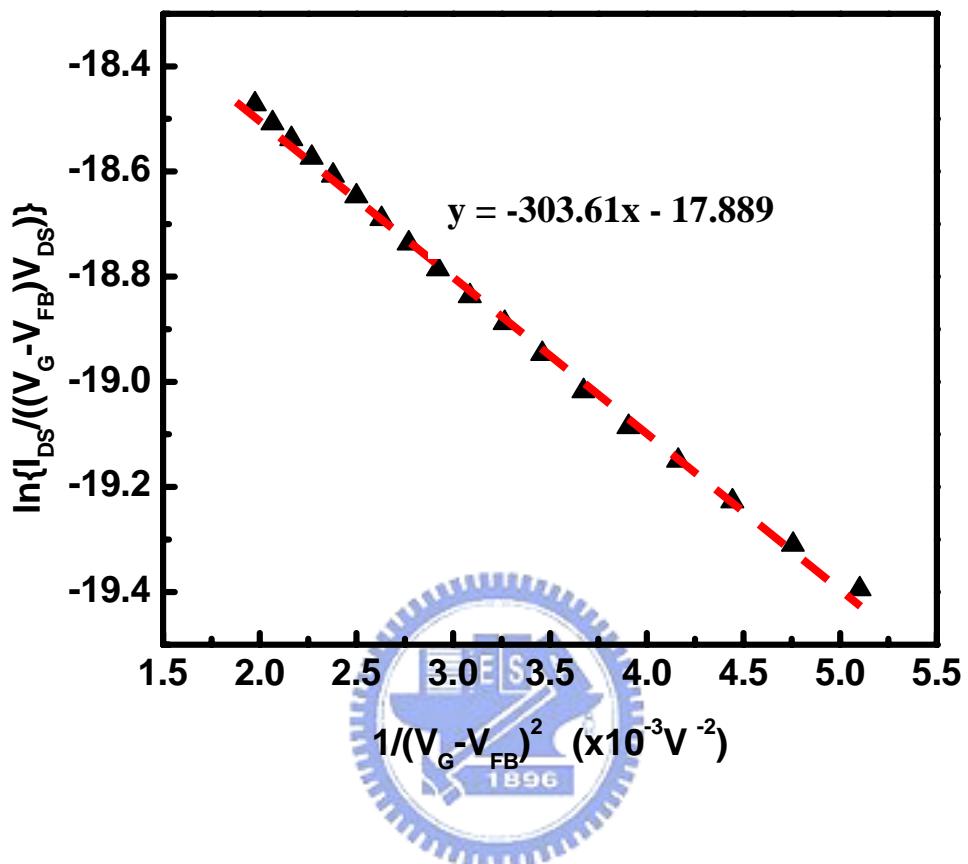

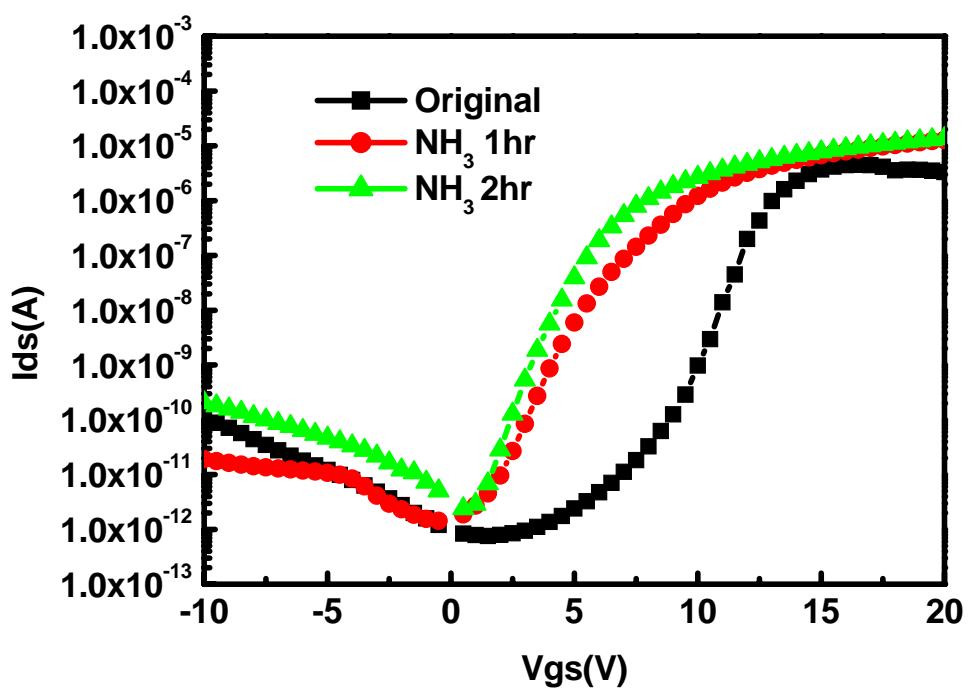

## 4.3 經過氮氣電漿處理後用改良型戴韋遜量測禁錮缺陷值比較

首先我們量測原始元件、經過 60 分鐘氮氣電漿處理及經過 120 分鐘氮氣電漿處理元件的電流 – 電壓曲線如圖 4-2 所示。未經電漿處理前  $V_{th}$  約為 12 V 且在區間  $V_g=3-6V$  升幅(swing)值約為 4.3 V/decade，經電將處理後 60 分鐘後， $V_{th}$  變為約 8.1V 且在區間  $V_g=3-6V$  升幅值約為 1.1V/decade，經電將處理 120 分鐘後  $V_{th}$  變為 7.3 V 且在區間  $V_g=3-6V$  升幅值約為 0.91V/decade，明顯的元件的升幅變好， $V_{th}$  變小，此結果反應氮氣電漿處理會改善元件特性。

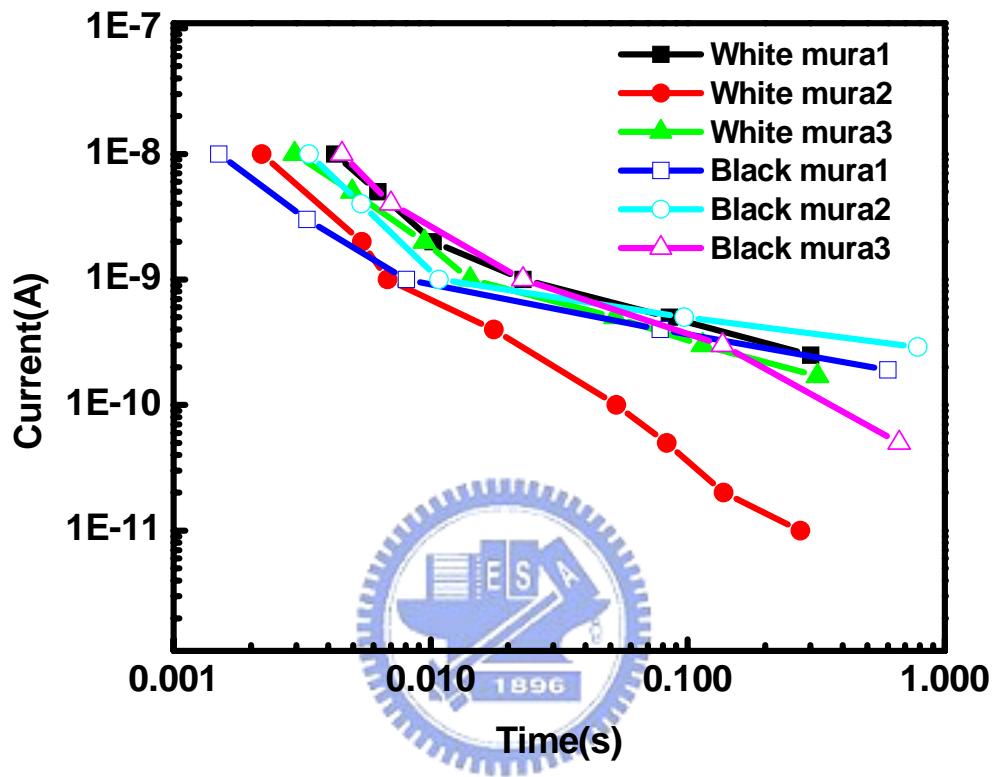

利用改良型戴韋遜方法量測禁錮缺陷密度，求出各元件的禁錮缺陷密度 如表 4-1 未經氮氣電漿處理原始第 1 個樣本(元件長為  $10\mu m$  寬為  $50\mu m$ )，此元件其次臨界斜率如圖 4-3，將此斜率帶入公式 (2-4)，即可求出  $Q_T = 1.98 \times 10^{12} cm^{-2}$ 。

此次量測總共量測 9 組元件，包括 3 組原始元件、3 組經過 60 分鐘氮氣電漿處理及 3 組經過 120 分鐘氮氣電漿處理等元件，求得的禁錮缺陷密度列於表 4-1(a)-(c)。我們可以發現經過氮氣電漿處理後，各元件之間的禁錮缺陷密度皆不相同，其中經過氮氣電漿處理過後的禁錮缺陷密度比未處理的數值小，而經過 120 分鐘氮氣電漿處理後的又比 60 分鐘氮氣電漿處理的數值小，與文獻[8]所提吻合。

由於改良型戴韋遜量測法只能求出元件的禁錮缺陷密度，但卻無法量測出元件內禁錮缺陷的暫態反應，因此我們再藉由暫態電流量測法量測元件的禁錮缺陷密度與放電的暫態時間。

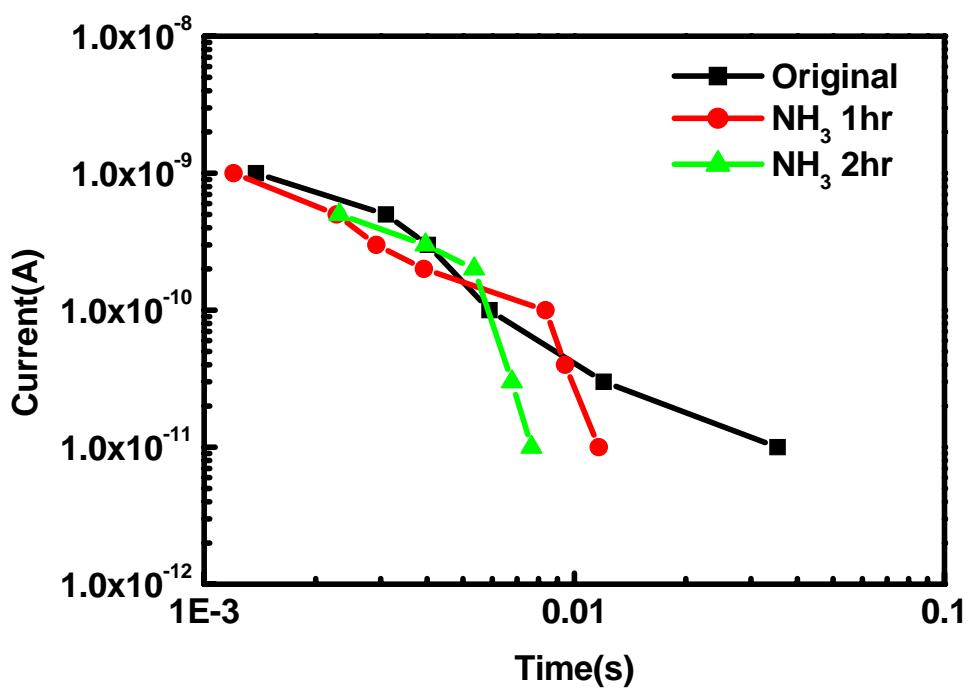

#### 4.4 經過氮氣電漿處理後用暫態電流量測禁錮缺陷值比較

以暫態電流量測方法量測原始元件、經過 60 分鐘氮氣電漿處理

及經過 120 分鐘氮氣電漿處理元件的暫態電流，圖 4-4 是暫態電流對暫態時間的關係圖。

與第 3 章相同的暫態時間定義，當暫態電流最後趨近於穩定值時，其相對應的時間即為暫態時間。從圖 4-3 得到暫態電流與暫態時間關係如表 4-2(a)-(c)，當未經氮氣電漿處理原始第 1 個樣本在  $Id_s = 1 \times 10^{-11} \text{ A}$  時則相對應的放電時間為 32.92ms，且元件的  $L/W = 10\mu\text{m} / 50\mu\text{m}$  與有效膜厚  $x(E_f)$  為 100nm，因此帶入公式(3-5)可以求出禁錮缺陷密度  $N(E_f) = 1.59 \times 10^{18} \text{ cm}^{-3} \text{ eV}^{-1}$ ，所有元件的禁錮缺陷密度列於表 4-2(a)-(c)，因此從量測到的禁錮缺陷密度可以得知當元件經由氮氣電漿處理之後其禁錮缺陷密度隨著時間增加而變小，而我們也可以藉由暫態電流的量測方法去求出元件禁錮缺陷密度之間的差異。

#### 4.5 改良型戴韋遜與暫態電流量測方法比較

由表 4-1(a)-(c) 及表 4-2(a)-(c) 可以歸納出改良型戴韋遜及暫態電流量測方法經過氮氣電漿處理後，所求得禁錮缺陷密度的趨勢圖，如圖 4-5，可以發現改良型戴韋遜透過直流量到的禁錮缺陷密度，電漿處理一小時是原始值的一半，又兩小時也是一小時的一半。而暫態電流量到的一小時即降低到原始值的三分之一，再增加一小時則只有小幅改善。

會有這樣的差異主要是改良型戴韋遜求出的缺陷包括淺層禁錮缺陷(shallow trap defect)及深層禁錮缺陷(deep trap defect)，明顯地，當元件經一小時及兩小時氮氣電漿處理後，電流 - 電壓特性持續被改善，升幅(swing)及  $V_{th}$  變小，這說明了缺陷總量被改善下降，所以

改良型戴韋遜量到的禁錮缺陷密度會有明顯下降的情況，且隨著氮氣電漿處理時間增加而下降。

而利用暫態電流量測到的缺陷，其禁錮電子跳脫率需大於  $10^{-3}$  秒，在量測時間大於  $10^{-3}$  秒時，大半的淺層禁錮缺陷已釋出，此時暫態量測到的缺陷屬於深層禁錮缺陷，由前一章量測的結果得知，深層禁錮缺陷並無法完全代表元件的缺陷總數，亦即大部份的缺陷是屬於淺層禁錮缺陷(電子跳脫率需小於  $10^{-3}$  秒)，由量測的禁錮缺陷密度結果發現，一小時即降低到原始值的三分之一，再增加一小時則只有小幅改善，這說明經一小時氮氣電漿處理後大部份的深層禁錮缺陷(電子跳脫率需大於  $10^{-3}$  秒)已修補，使得後續的氮氣電漿處理效果不明顯。

表 4 – 1(a)由改良型戴韋遜量測法所求出原始樣本的禁錮缺陷密度

|                         | 原始樣本 1                | 原始樣本 2                | 原始樣本 3                |

|-------------------------|-----------------------|-----------------------|-----------------------|

| $V_{FB}(V)$             | 2.0                   | 1.5                   | 1.5                   |

| 斜率                      | -848.62               | -1000.3               | -1000.3               |

| 禁錮缺陷密度 $\text{cm}^{-2}$ | $1.82 \times 10^{12}$ | $1.98 \times 10^{12}$ | $1.98 \times 10^{12}$ |

表 4 – 1(b)由改良型戴韋遜量測法所求出氮氣電漿處理 1hr 的禁錮缺陷密度

|                         | NH3 1hr 樣本 1          | NH3 1hr 樣本 2          | NH3 1hr 樣本 3          |

|-------------------------|-----------------------|-----------------------|-----------------------|

| $V_{FB}(V)$             | -0.5                  | -0.5                  | -1.5                  |

| 斜率                      | -293.6                | -293.6                | -182.34               |

| 禁錮缺陷密度 $\text{cm}^{-2}$ | $1.07 \times 10^{12}$ | $1.07 \times 10^{12}$ | $8.45 \times 10^{11}$ |

表 4 – 1(c)由改良型戴韋遜量測法所求出氮氣電漿處理 2hr 的禁錮缺陷密度

|                         | NH3 2hr 樣本 1          | NH3 2hr 樣本 2          | NH3 2hr 樣本 3          |

|-------------------------|-----------------------|-----------------------|-----------------------|

| $V_{FB}(V)$             | 0.5                   | 0.5                   | 0.0                   |

| 斜率                      | -91                   | -106                  | -101.2                |

| 禁錮缺陷密度 $\text{cm}^{-2}$ | $5.97 \times 10^{11}$ | $6.44 \times 10^{11}$ | $6.29 \times 10^{11}$ |

表 4-2(a)由暫態電流與暫態時間所求出原始樣本的禁錮缺陷密度

|                                       | 原始樣本 1                | 原始樣本 2                | 原始樣本 3                |

|---------------------------------------|-----------------------|-----------------------|-----------------------|

| 暫態電流(A)                               | $1.0 \times 10^{-11}$ | $1.0 \times 10^{-11}$ | $1.0 \times 10^{-11}$ |

| 暫態時間(sec)                             | 0.03292               | 0.03482               | 0.0354                |

| 禁錮缺陷密度 $\text{cm}^{-3}\text{eV}^{-1}$ | $1.59 \times 10^{18}$ | $1.68 \times 10^{18}$ | $1.71 \times 10^{18}$ |

表 4-2(b)由暫態電流與暫態時間所求出氮氣電漿處理 1hr 的禁錮缺陷密度

|                                       | NH3 1hr 樣本 1          | NH3 1hr 樣本 2          | NH3 1hr 樣本 3          |

|---------------------------------------|-----------------------|-----------------------|-----------------------|

| 暫態電流(A)                               | $1.0 \times 10^{-11}$ | $1.0 \times 10^{-11}$ | $1.0 \times 10^{-11}$ |

| 暫態時間(sec)                             | 0.0108                | 0.0094                | 0.01164               |

| 禁錮缺陷密度 $\text{cm}^{-3}\text{eV}^{-1}$ | $5.21 \times 10^{17}$ | $4.54 \times 10^{17}$ | $5.62 \times 10^{17}$ |

表 4-2(c)由暫態電流與暫態時間所求出氮氣電漿處理 2hr 的禁錮缺陷密度

|                                       | NH3 2hr 樣本 1          | NH3 2hr 樣本 2          | NH3 2hr 樣本 3          |

|---------------------------------------|-----------------------|-----------------------|-----------------------|

| 暫態電流(A)                               | $1.0 \times 10^{-11}$ | $1.0 \times 10^{-11}$ | $1.0 \times 10^{-11}$ |

| 暫態時間(sec)                             | 0.00906               | 0.0078                | 0.00766               |

| 禁錮缺陷密度 $\text{cm}^{-3}\text{eV}^{-1}$ | $4.37 \times 10^{17}$ | $3.76 \times 10^{17}$ | $3.70 \times 10^{17}$ |

圖 4-1 元件製作流程

圖 4-2 原始元件及經過氨氣電漿處理後元件的電流 - 電壓曲線

圖 4-3 原始元件的斜率

圖 4-4 原始元件及經過氨氣電漿處理後元件的暫態電流與暫態時間

曲線圖

圖 4-5 經氨氣電漿處理後用改良型戴韋遜及暫態電流所求出禁錮缺陷密度的趨勢圖

# 第五章 總結與未來工作

在液晶顯示器生產過程中由於製程參數、溫度及機台的關係導致在面板上產生各式各樣的幕那現象，在工業上我們透過各種製程及材料的改善來降低幕那產生的機率，而本論文則透過元件物性及電性的量測分析去找出幕那產生的機制，在這之間發現放電幕那的產生主要來自元件缺陷中心的禁錮電子，當加在元件上的電源瞬間關閉時，原先被禁錮的電子開始釋出。由於不同元件間的放電幕那時間不同，為了找出放電幕那時間與禁錮電子缺陷密度之間的關係，我們透過暫態電流及改良型戴韋遜等兩種量測方法去求出禁錮電子缺陷密度並比較兩種量測方法的差異，重要結論整理如下。

## 5.1 改良型戴韋遜及暫態電流量測禁錮缺陷密度比較

### 5.1.1 改良型戴韋遜量測結果

改良型戴韋遜為量測穩態電流，指量測固定偏壓下通道的電流(I) – 電壓(V)曲線，由於缺陷中心會禁錮電子，改變通道電位，進而影響電流 – 電壓曲線，因而我們可以利用此變化得以去推測缺陷的數量。由於一般 I-V 曲線測試速率不快，約數十至數百毫秒測得一個數據，在任一偏壓下，缺陷中心都有足夠的時間禁錮或釋放電子。所以測到的缺陷密度是穩定狀態下的總量，只和數量有關，和反應速率無關，無法反應暫態狀態。當不同區域的元件穩態缺陷密度幾乎相同時，無法解釋為何會出現放電幕那現象。

### 5.1.2 暫態電流量測結果

暫態電流的形成是由於元件在工作狀態時，缺陷中心禁錮電子，當加在元件上的電源瞬間關閉時，整體空間電位開始變化，而原本禁錮電子的缺陷中心受此整體電位的變化，本身區域性電位亦隨著改變，致使原先被禁錮的電子開始釋出，並成為電源關閉時所量到的暫態電流。缺陷中心的性質不同，會造成電子釋出需要的時間不同，有些電子在數微秒內即被釋出，有些則需要數百微秒。暫態電流的測量可以反應出缺陷密度以及缺陷反應速率。如果不同元件的缺陷反應速率接近，放電幕那的現象就不容易被觀察到。反之，即使缺陷數量不是很多，但是不同元件的缺陷反應速率不同，就會出現放電幕那。

### 5.2 暫態電流量測的應用

暫態電流既然可以測到缺陷密度以及反應速率，應該可以應用在其它場合。氮氣電漿處理可以減少禁錮缺陷，因此在第四章嘗試用暫態電流方法分析氮氣電漿處理前後的缺陷反應。透過暫態電流與改良型戴韋遜量測方法對未經氮氣電漿處理、氮氣電漿處理 60 分鐘及 120 分鐘三個元件的禁錮缺陷密度做量測，證實經過氮氣電漿處理時間越久的元件對於改善禁錮缺陷密度也就越好。暫態電流和穩態電流反應的改善趨勢稍有不同。穩態電流表示總量陸續減半，但是暫態電流顯示初期改善較快，延長時間改善有限。似乎表示氮氣電漿處理主要是減少反應速率較慢(deep traps)的缺陷，對於反應速率快(shallow traps)的缺陷改善有限，具體原因值得繼續探討。

### 5.4 未來工作

在第二章中觀測到厚膜元件的幕那現象都較薄膜元件明顯，原因有可能因厚膜有較多的深層禁錮缺陷，使得幕那現象較為嚴重，然而深層禁錮缺陷量多與幕那放電時間長，兩者一為數量的多寡，另一為時間長短，兩者並無直接必然的關係，要進一步確認幕那放電時間長短與膜厚厚薄(禁錮缺陷多寡)相關，需進一步量化比較確認，這有待更多不同膜厚在相同製程元件量測做確認。

量測暫態電流時，目前僅能做到最短時間量測為 $10^{-3}$ 秒，無法量測到反應時間更快的淺層缺陷而所造成的暫態電流，此乃因實驗儀器限制無法量測缺陷更快速的反應時間，此有待反應速度更快的儀器提供更有力直接證明。

暫態電流量測法具有量測元件本身的禁錮缺陷多寡及禁錮缺陷放電時間的長短，從圖 4-4 我們觀察到元件內的禁錮缺陷放電時間可以被切割成兩部份，一部份就是禁錮缺陷放電的初期即是元件的快速禁錮屬於元件內淺層禁錮缺陷會快速遭到釋放，這段時間內所有元件的放電時間相同，而另一部份就是禁錮缺陷放電的後期即是元件的慢速禁錮屬於元件內深層禁錮缺陷會慢慢被釋放，利用元件放電不同時間差的這個特性，再搭配調整不同 $V_{gs}$ 電壓使元件導通的通道深淺不一，進而可以區別出元件表層缺陷(Interface defect)還是元件主體缺陷(Bulk defect)。可以假設當 $V_{gs}$ 電壓小於臨界電壓( $V_{th}$ )時求得的禁錮缺陷為表層缺陷，當 $V_{gs}$ 電壓大於臨界電壓時求得的禁錮缺陷為表層缺陷與主體缺陷的相加，這可以從後續的實驗再去做驗證找出最恰當的定義。

## 參考文獻

- [1] N. Ibaraki, “a-Si TFT technologies for AM-LCDs,” in MRS Symp. Proc., vol. 336, 1994, pp. 749-756.

- [2] S. Sherman, p. –Y. LU, R.A. Gottscho and S. Wagner, “TFT performance – material quality correlation for a-Si:H deposited at high rates,” in MRS Symp. Proc. Vol. 337, pp. 749-753, 1995.

- [3] M.C. Jun, Y.S. KIM, E.Y. OH, “Stability of a-Si:H TFTs employing APCVD SiO<sub>2</sub> with N<sub>2</sub> plasma treatment as a gate dielectric,” in MRS Symp. Proc. Vol. 336, pp. 799-803, 1994.

- [4] R. E. Proano, R. S. Misage, “Development and electrical properties of undoped polycrystalline silicon thin-film transistors,” on Electron Devices, Vol. 36, No. 9, pp. 1915-1922, 1989.

- [5] F. Lemmi and Robert A. Street, “The leakage currents of amorphous silicon thin-film transistors: injection currents, back channel currents and stress effects,” IEEE Trans. on Electron Devices, Vol. 47, No. 12, pp. 2404-2409, 2000.

- [6] F. Lemmi and Robert A. Street, “The leakage currents of amorphous silicon thin-film transistors: channel charge emission,” on Electron Devices, Vol. 47, No. 12, pp. 2399-2403, 2000.

- [7] F. Lemmi and Robert A. Street, “Analysis of drain currents during switching off a-Si:H based thin film transistors,” in MRS Symp. Proc. Vol. 507, pp. 79-84, 1998.

- [8] S. Luan and G. W. Neudeck, “Effect of NH<sub>3</sub> plasma treatment of gate nitride on the performance of amorphous silicon thin film

transistor" , J. Appl. Phys., vol. 68, pp. 3445-3450, 1990.

# 個人簡歷

姓名：蔡尚公

生日：民國 63 年 8 月 19 日

籍貫：台灣省高雄市

地址：高雄市楠梓區聖雲街 110 巷 32 號

學歷：市立高雄高工畢 (1989 / 09 ~ 1992 / 06 )

國立雲林科技大學電機工程學系畢 (1992 / 09 ~ 1996 / 06 )

國立交通大學在職專班電子與光電研究所碩士班畢

( 2000 / 09 ~ 2006 / 06 )

碩士論文題目：

薄膜電晶體之暫態電流測量技術

Thin film transistor measurement by transient current