國立交通大學

電機學院微電子奈米科技產業研發碩士班

碩士論文

複晶矽薄膜電晶體製程效應與偏壓溫度不穩定性

**Study on Process Effects and Bias Temperature

Instability of Poly-Si Thin-Film Transistors**

研究 生：王 統 億

指 導 教 授：雷 添 福 博 士

中華民國 九十六 年 一 月

# 複晶矽薄膜電晶體製程效應與偏壓溫度不穩定性 之研究

## Study on Process Effects and Bias Temperature Instability of Poly-Si Thin-Film Transistors

研究 生：王統億

Student: Tong-Yi Wang

指導教授：雷添福 博士

Advisor: Dr. Tan-Fu Lei

國立交通大學

電機學院微電子奈米科技產業研發碩士班

碩士論文

Submitted to College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Industrial Technology R & D Master Program on

Microelectronics and Nano Sciences

January 2007

Hsinchu Taiwan Republic of China

中華民國 九十六年一月

# 複晶矽薄膜電晶體製程效應與偏壓溫度不穩定

## 性之研究

學生：王統億

指導教授：雷添福 博士

國立交通大學

電機學院 微電子奈米科技產業研發碩士班

### 摘要

在本論文中，首先，我們在閘極氧化層沉積後利用高溫通氧的條件來提升閘極氧化層的可靠度。另外我們在成長薄膜電晶體通道之前，運用低溫低壓的條件預沉積一氧化氮含量較高的薄膜矽襯墊層，因為較高的氮含量會抑制固相再結晶(Solid-Phase Crystallization) 時的成核。藉由這個方式，可以在通道中形成更大的晶粒尺寸(Grain size)，藉而得到更高的載子場效遷移率。我們發現，特別是在小尺寸的元件中，預沉積矽襯墊層有效的提高複晶矽薄膜電晶體 (poly-Si TFTs) 的場效遷移率、驅動電流，並有效降低閘極引發汲極漏電流 (GIDL current) 以及次臨限擺幅 (Subthreshold Swing)。再者藉由使用預沉積矽襯墊層，也改善了元件的可靠度以及均勻性。

接著，我們分別對 p-通道複晶矽薄膜電晶體進行負偏壓溫度不穩定性 (Bias Temperature Instability) 之研究，以及對 n-通道複晶矽薄膜電晶體進行正偏壓溫度不穩定性對於元件可靠度的影響之研究。我們分別探討不同的溫度以及所施加的偏壓，對於上述兩種偏壓溫度不穩定性在元件退化所造成的影响。實驗結果顯示，正、負偏壓溫度不穩定性在低溫複晶矽薄膜電晶體中會有著不同的退化機制，但對於元件可靠度都有很大程度的影響。

最後，我們探討動態負偏壓溫度不穩定性對於 p-通道複晶矽薄膜電晶體可靠度的影響。藉由不同的偏壓方式，我們可以發現元件在進行負偏壓溫度不穩定性之測試時所產生的缺陷狀態，會在正閘極偏壓下被修補。在 CMOS 反向器使用中，這樣的修補會使得元件使用期限大幅提升，藉由使用動態負偏壓溫度不穩定性測試，可以得到更貼近現實使用下的元件使用期限。

# **Study on Process Effects and Bias Temperature Instability of Poly-Si Thin-Film Transistors**

Student: Tong-Yi Wang

Advisor: Dr. Tan-Fu Lei

Department of Electronics Engineering &

Institute of Electronics

National Chiao Tung University

In this thesis, first, we used a post-anneal procedure with oxygen ambient after the deposition of gate oxide. Poly-Si TFTs with such a post-anneal procedure have enhanced electrical characteristics and much improved reliability. In addition, we deposited a buffer amorphous Si (a-Si) layer under both low temperature and pressure before the deposition of the channel. Si layers grown under this condition would have higher oxygen concentration, and this would suppress the nucleation mechanism under solid-phase crystallization (SPC). With the buffer Si layer, the bi-layer Si, with a-Si layer beneath the poly-Si channel after the SPC process, would have larger grain size and lead to enhanced performance. Measurements revealed that the devices' electrical characteristics are improved not only in field effect mobility and gate-induced-drain leakage (GIDL) current, but also in driving current and

subthreshold swing. Moreover, the ability of immunity against hot-carrier injection and device uniformity are improved.

Then, we studied the degradation mechanisms of negative bias temperature instability (NBTI) and positive bias temperature instability (PBTI) in p- and n-channel low-temperature polycrystalline silicon thin-film transistors (LTPS TFTs), respectively. As the stress gate voltage increases, the absolute values of threshold voltages shift ( $|\Delta V_{th}|$ ) increase under NBTI and PBTI stress. When the stress temperature is raised, the  $|\Delta V_{th}|$  increases under NBTI stress but almost unchanged under PBTI stress, indicating that the degradation mechanisms of NBTI and PBTI are different. Furthermore, the field-effect mobility is rarely changed under NBTI stress; however, it increases under PBTI stress. From the experimental results, we demonstrated that the NBTI degradation can be explained by the diffusion-controlled electrochemical reactions, while the PBTI degradation is caused by charge trapping in the gate dielectric.

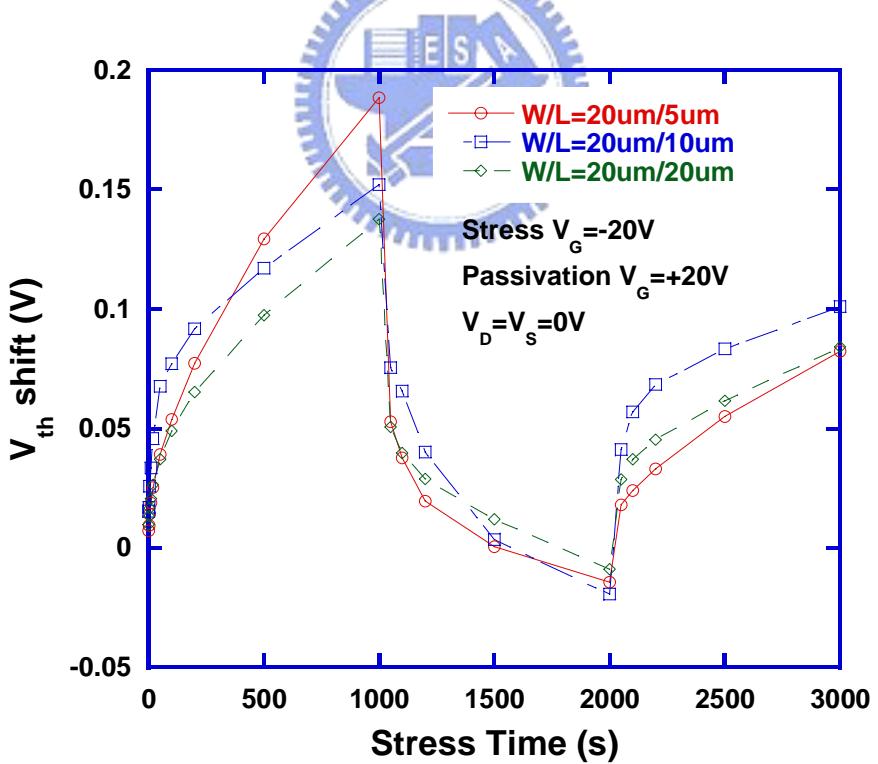

Finally, we investigated the impact of dynamic NBTI in p-channel LTPS TFTs. In conventional NBTI studies, static gate bias is used to determine the lifetime of p-channel LTPS TFTs. However, DNBTS in p-MOSFETs showed that the lifetime was much longer than that derived from static NBTI stress because of the passivation effect. We found that LTPS p-TFTs have passivation effect under positive gate bias during a stress-passivation-stress process. As a result, we would underdetermine the true lifetime of LTPS p-TFTs when we use static NBTS to derive it. Therefore, it is necessary to use DNBTS to simulate the bias condition of their really applications.

## 誌謝

首先要向我的指導教授雷添福博士致上無限的謝意。兩年的研究生涯中，不僅從老師身上學習到做研究的精神與方法，有老師的關心與鼓勵本論文才得以順利完成。另外也要感謝聯華電子公司提供的機會，並提供生活上的協助，還有聯電王宗鴻先生的幫忙，讓我能夠完成這本論文。

這兩年的碩士生涯中，能在研究上有些小小的成果，需要感謝的人很多。特別要感謝志仰學長與家文學長，不論是在學業上、實驗上甚至生活上都給了我莫大的幫助，此外也要感謝林孝義學長提供元件，讓我可以進行可靠度量測，還有李介文學長、陳建豪學長、謝明山學長、游信強學長、楊紹明學長、王獻德學長、林育賢學長、郭伯儀學長、馬鳴文學長、桑任逸學長，感謝你們這些日子來的關心與指導。另外也感謝俊嘉、源竣、伯浩、宗元、梓翔、錦石、伊容不管是在課業或生活上的幫忙。也感謝廷圍、久騰、明爵、仕傑、文呈、哲綸、文瑋、子恆、張婷，與你們相處的時光總是充滿歡樂。

另外也要感謝我的大學同學，尤其是電工羅漢團的好朋友們，這兩年多虧有你們跟我一起吃苦與享樂，讓我可以快樂的渡過苦悶的研究生活。

最後感謝我最親愛的家人，尤其感謝我的父親王茂隆先生和母親呂秀月女士，多年來對我無悔的付出與關懷，提供我最好的避風港。二十多年來無以回報，只能以這本論文稍稍慰藉你們的含辛茹苦。也很感謝我爺爺、奶奶以及統弘、鈺婷多年來的照顧與疼愛。當然也要感謝乖巧體貼的喬蓉與可愛的小億讓我可以忘記煩惱，還有感謝登洲與小涵照顧我的姊姊與哥哥。感謝我最親愛的家人們，因為有你們，讓我有繼續努力下去的動力。

# Contents

|                                          |             |

|------------------------------------------|-------------|

| <b>Abstract (Chinese) .....</b>          | <b>I</b>    |

| <b>Abstract (English) .....</b>          | <b>III</b>  |

| <b>Acknowledge .....</b>                 | <b>V</b>    |

| <b>Contents .....</b>                    | <b>VI</b>   |

| <b>Table &amp; Figure Captions .....</b> | <b>VIII</b> |

|                                     |          |

|-------------------------------------|----------|

| <b>Chapter 1 Introduction .....</b> | <b>1</b> |

|-------------------------------------|----------|

|                                                     |   |

|-----------------------------------------------------|---|

| 1.1 Overview of Poly-Si Thin-Film Transistors ..... | 1 |

| 1.2 Overview of Bias Temperature Instability .....  | 3 |

| 1.3 Motivation .....                                | 5 |

| 1.4 Organization of the Thesis .....                | 6 |

| References .....                                    | 8 |

|                                                                                                        |           |

|--------------------------------------------------------------------------------------------------------|-----------|

| <b>Chapter 2 Characteristics of Low Temperature Poly-Si TFTs Using a Bi-layer Poly-Si Channel.....</b> | <b>16</b> |

|--------------------------------------------------------------------------------------------------------|-----------|

|                                                            |    |

|------------------------------------------------------------|----|

| 2.1 Introduction .....                                     | 16 |

| 2.2 Device Fabrication .....                               | 17 |

| 2.3 Methods of Device Parameter Extraction .....           | 18 |

| 2.3.1 Determination of Threshold Voltage .....             | 18 |

| 2.3.2 Determination of Subthreshold-Swing.....             | 19 |

| 2.3.3 Determination of Field Effect Mobility.....          | 20 |

| 2.3.4 Determination of ON/OFF Current Ratio .....          | 20 |

| 2.3.5 Extraction of Grain Boundary Trap State Density..... | 21 |

| 2.4 Results and discussion.....                            | 23 |

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| 2.4.1 Characteristics of Poly-Si TFTs with post anneal after gate oxide deposition..... | 23 |

| 2.4.2 Characteristics of Poly-Si TFTs with Bi-layer Poly-Si Channel.....                | 24 |

| 2.4.3 Reliability of Poly-Si TFTs with Bi-layer Poly-Si Channel.....                    | 25 |

| 2.5 Summary .....                                                                       | 25 |

| References .....                                                                        | 27 |

### **Chapter 3 Degradation Mechanisms of NBTI and PBTI in Low-Temperature**

|                                            |           |

|--------------------------------------------|-----------|

| <b>Poly-Si Thin-Film Transistors .....</b> | <b>44</b> |

| 3.1 Introduction .....                     | 44        |

| 3.2 Experimental .....                     | 45        |

| 3.3 Results and Discussion.....            | 46        |

| 3.4 Summary .....                          | 48        |

| References .....                           | 49        |

### **Chapter 4 Dynamic Negative Bias Temperature Instability of Low-Temperature Poly-Silicon Thin-Film Transistors.....67**

|                                 |    |

|---------------------------------|----|

| 4.1 Introduction.....           | 67 |

| 4.2 Experimental .....          | 68 |

| 4.3 Results and Discussion..... | 69 |

| 4.4 Summary .....               | 70 |

| References .....                | 72 |

### **Chapter 5 Conclusions .....**85

## **TABLE CAPTIONS**

### **Chapter 2**

Table 2-1 Comparison of device characteristics of poly-Si TFTs with and without an anneal procedure after the gate oxide deposition (L/W=1um/10um).

Table 2-2 Comparison of device characteristics of the Control and Bi-layer samples.

### **Chapter 3**

Table 3-1 Comparison of the effects of NBTI and PBTI on the TFT performance.

# FIGURE CAPTIONS

## Chapter 2

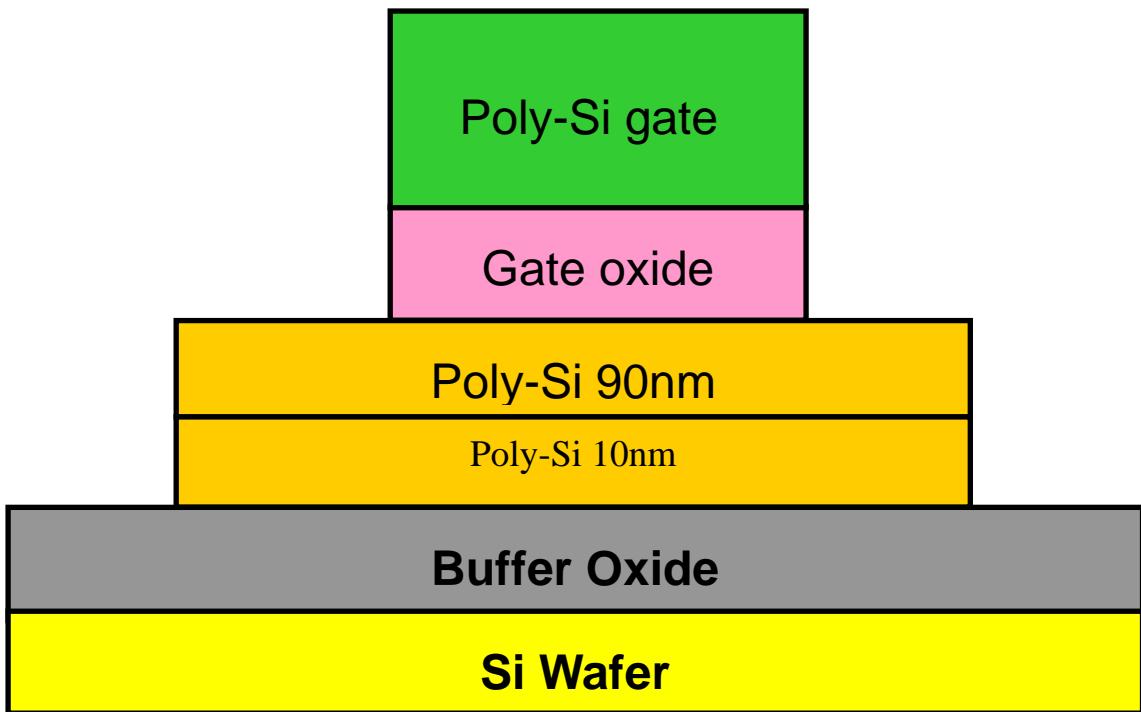

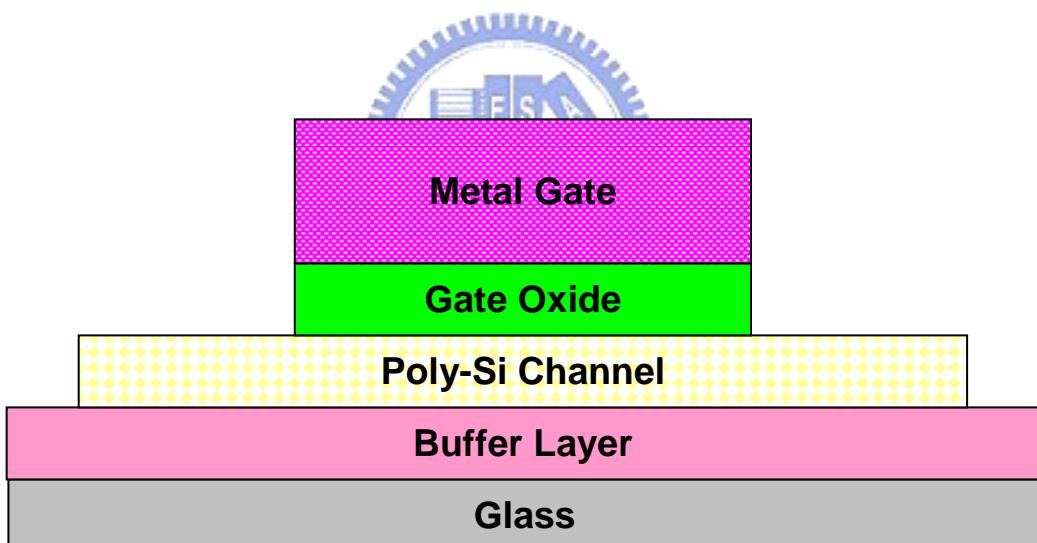

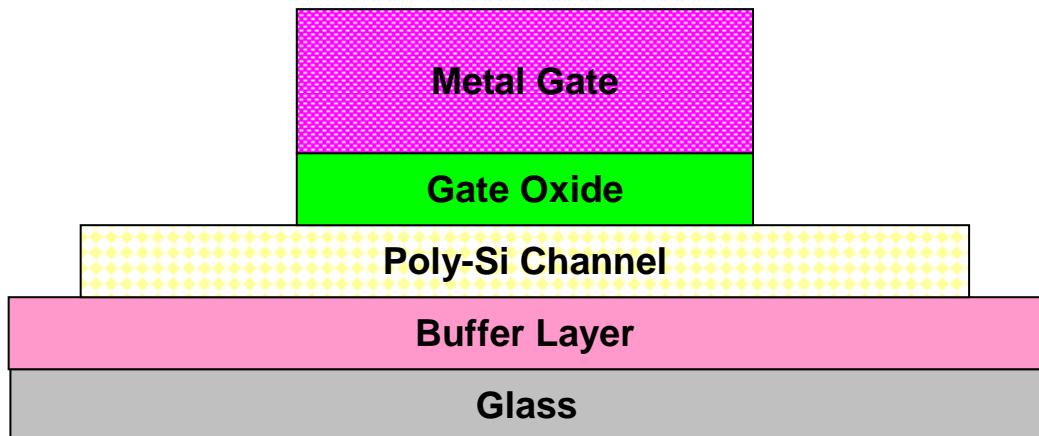

Fig. 2-1 Schematic diagram of fabrication process for bi-layer poly-Si TFTs.

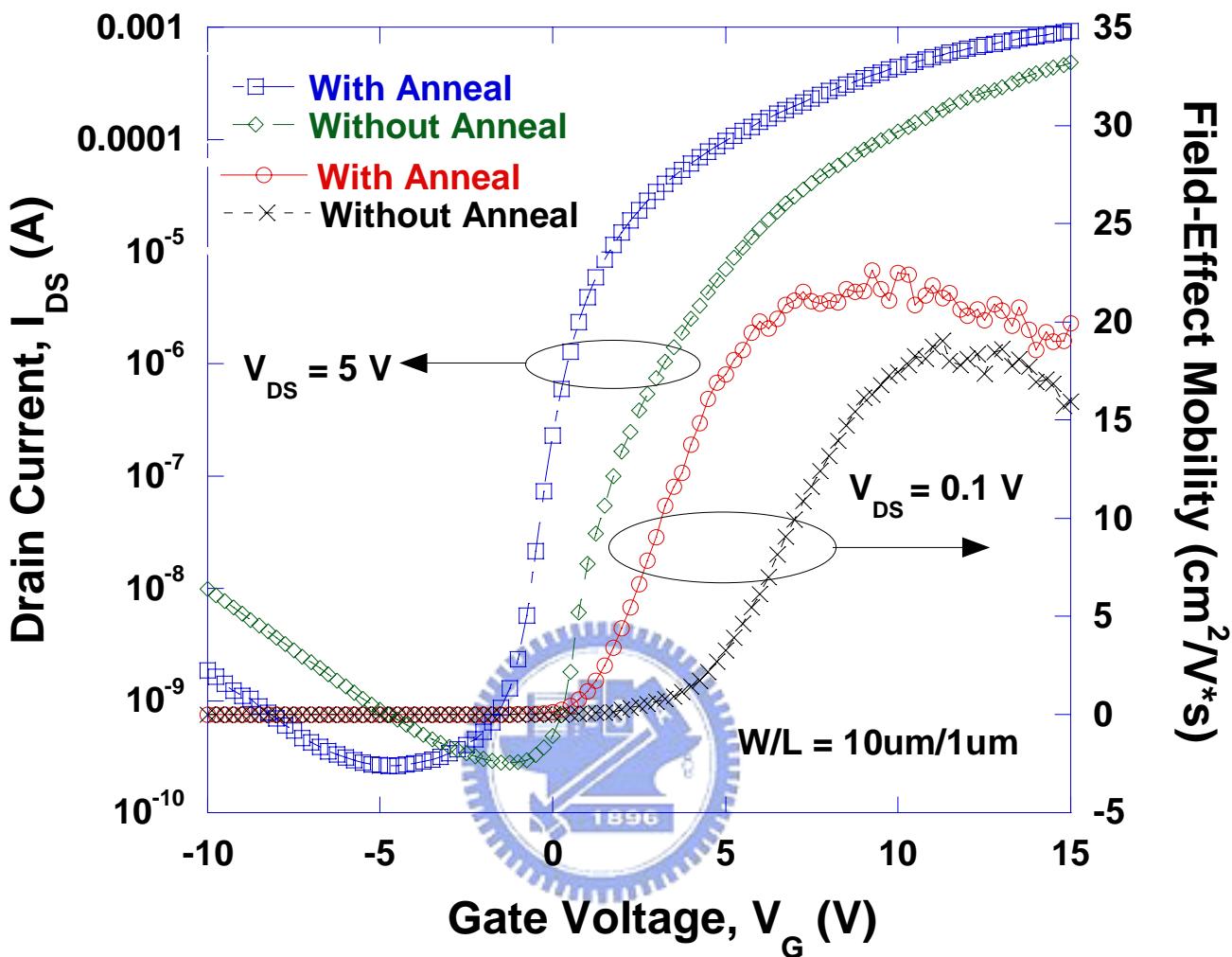

Fig. 2-2 Transfer characteristics of poly-Si TFTs with and without an anneal procedure after the deposition of gate oxide.

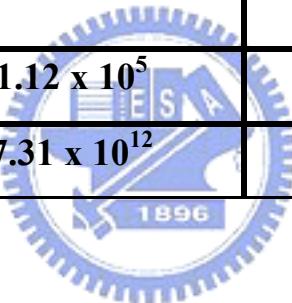

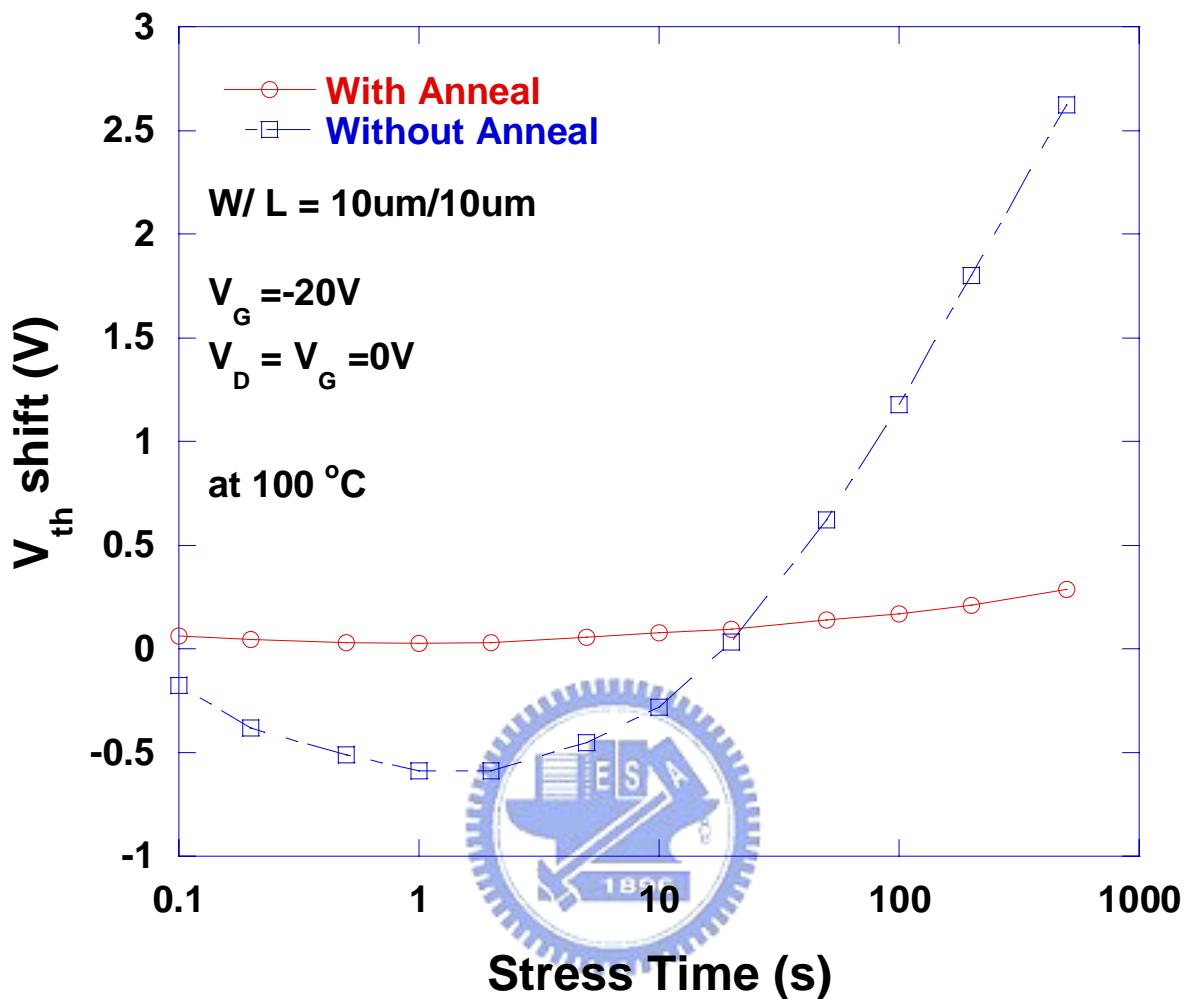

Fig. 2-3 (a) Threshold voltage shift ( $V_{th}$ ) versus stress time of n-TFTs with and without gate oxide anneal under static gate bias  $V_G=-20V$  while S/D were grounded at  $100^\circ C$ .

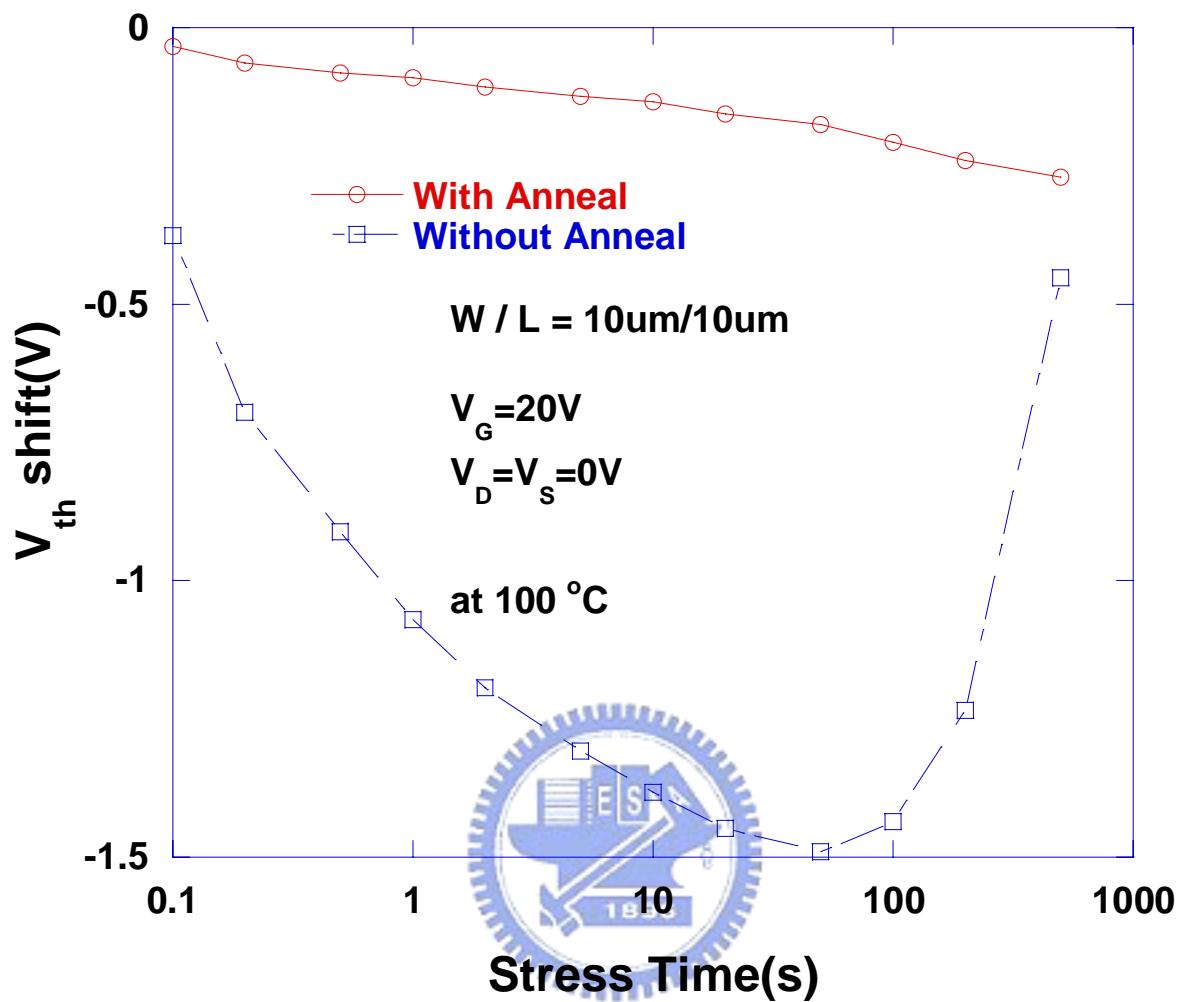

(b) Threshold voltage shift ( $V_{th}$ ) versus stress time of n-TFTs with and without gate oxide anneal under static gate bias  $V_G=20V$  while S/D were grounded at  $100^\circ C$ .

Fig. 2-4 (a) Transfer characteristics of the Control and LP poly-Si TFTs with  $V_{DS}=5V$ .

(b) Field-effect mobility of the Control and the LP poly-Si TFTs with  $V_{DS}=0.1V$ .

Fig. 2-5 Trap state density extraction of the Control and the LP poly-Si TFTs.

Fig. 2-6 Output characteristic of the Control and the LP poly-Si TFTs.

Fig. 2-7 (a) Threshold voltage and (b) subthreshold swing degradation versus stress time under hot-carrier stress at room temperature.

Fig. 2-8 (a) Threshold voltage and (b) subthreshold swing degradation versus stress time under hot-carrier stress at  $100^\circ C$ .

## Chapter 3

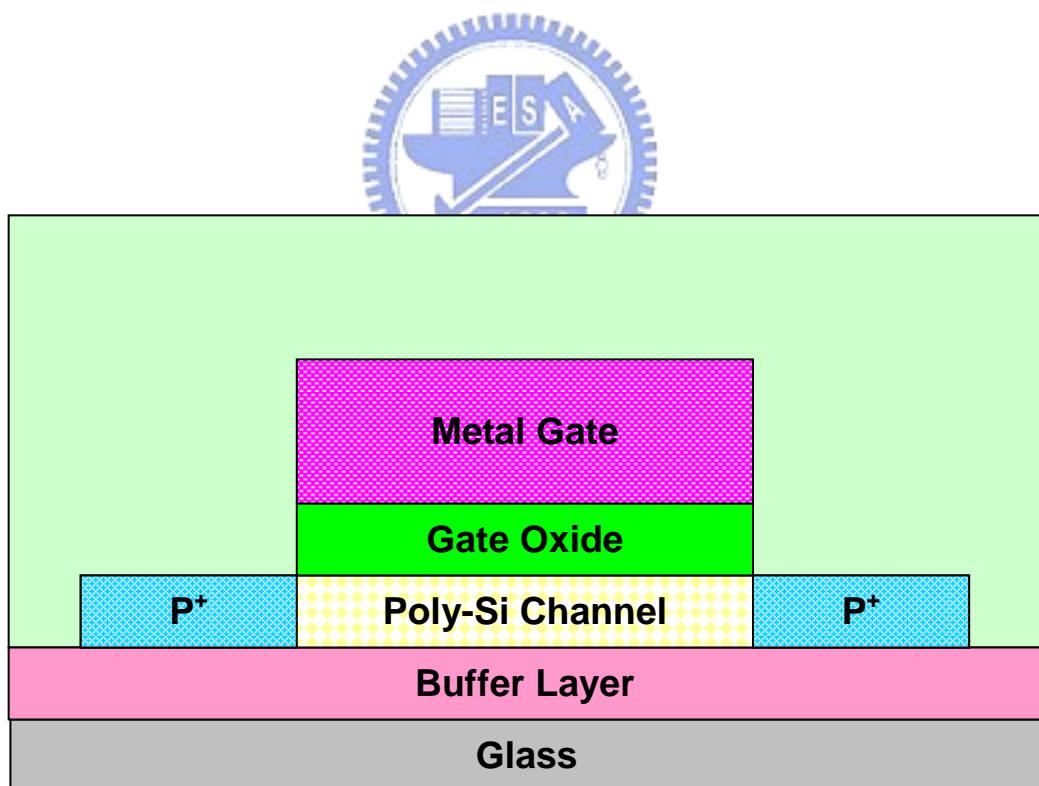

Fig. 3-1 Process flow of the poly-Si TFT.

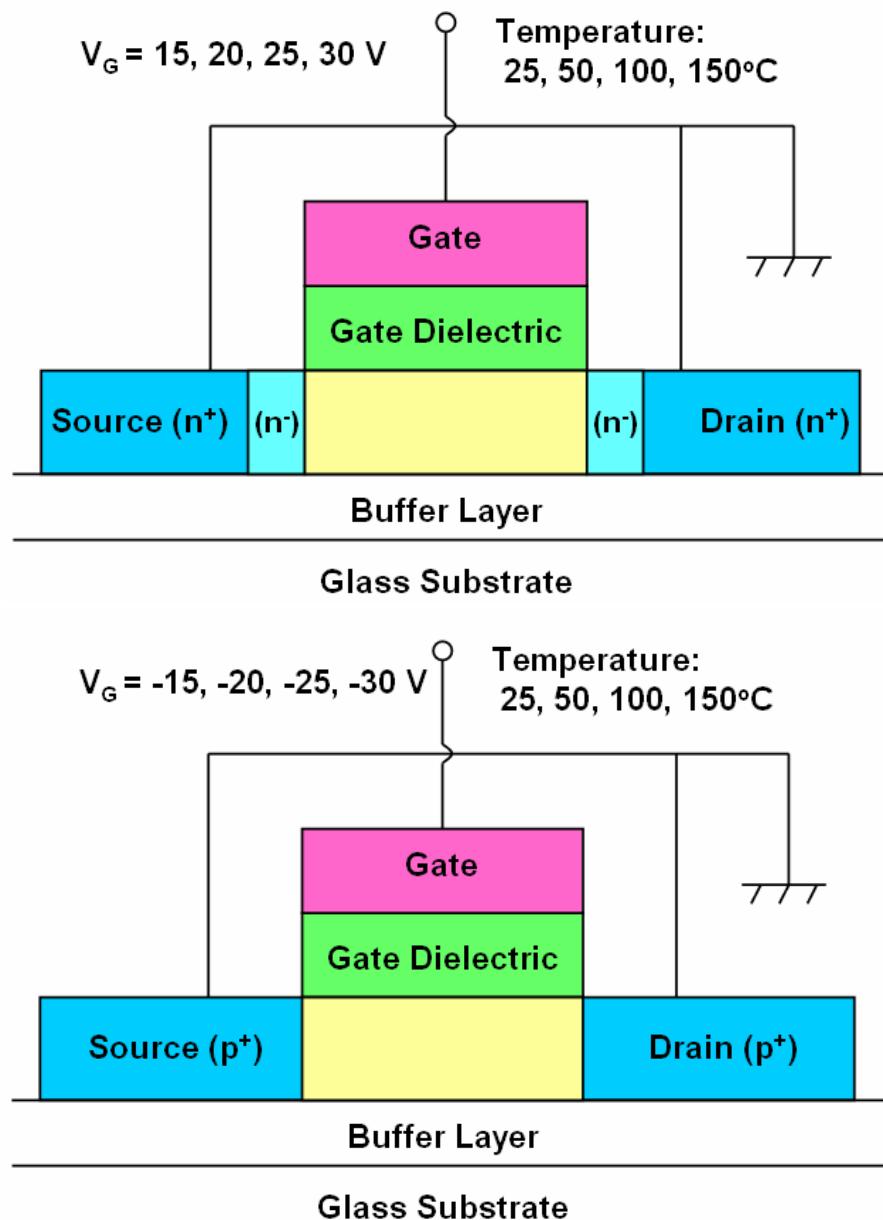

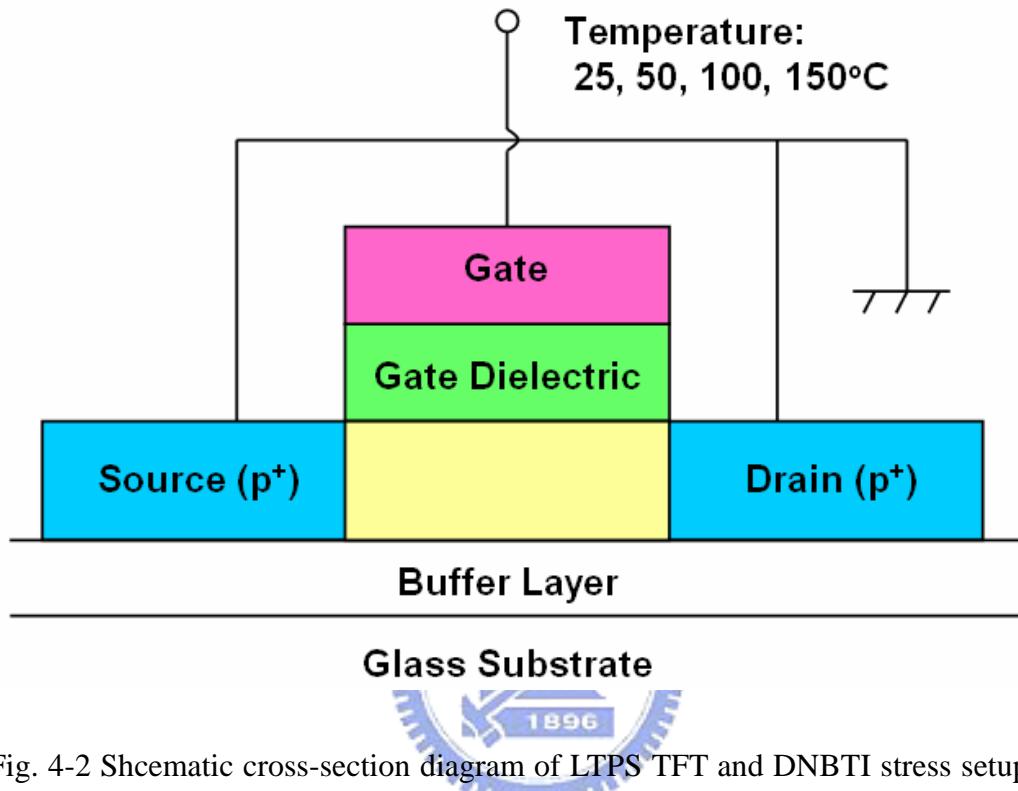

Fig. 3-2 Schematic cross-section diagram of LTPS TFT and NBTI stress setup. The stress temperature was performed from 25°C to 150°C, and the stress gate voltage was applied in the range of -15V to -30V with source and drain grounded.

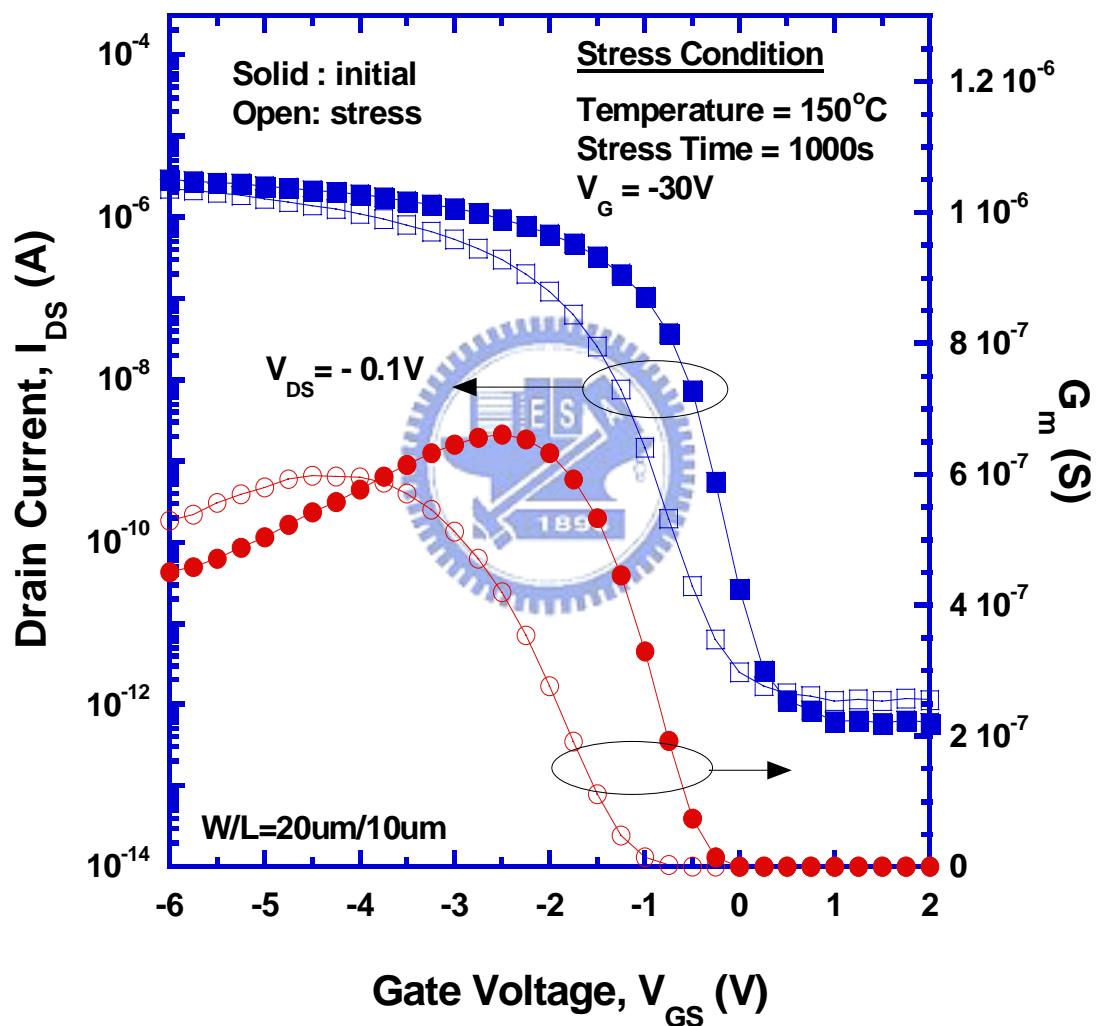

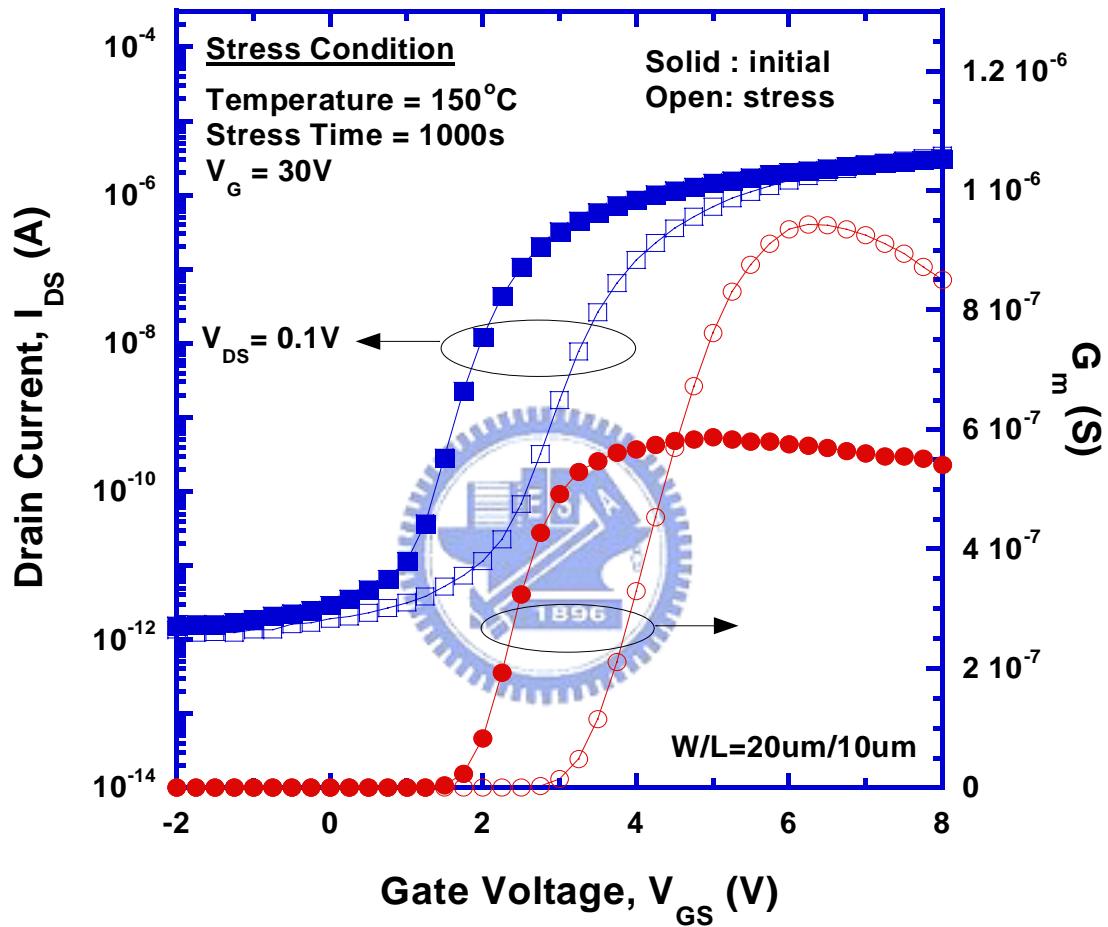

Fig. 3-3 (a) Transfer characteristics of LTPS TFT before and after 1000sec NBTI stress at 100°C with the stress voltage of -30V.

(b) Output characteristics of LTPS TFT before and after 1000sec NBTI stress at 100°C with the stress voltage of -30V.

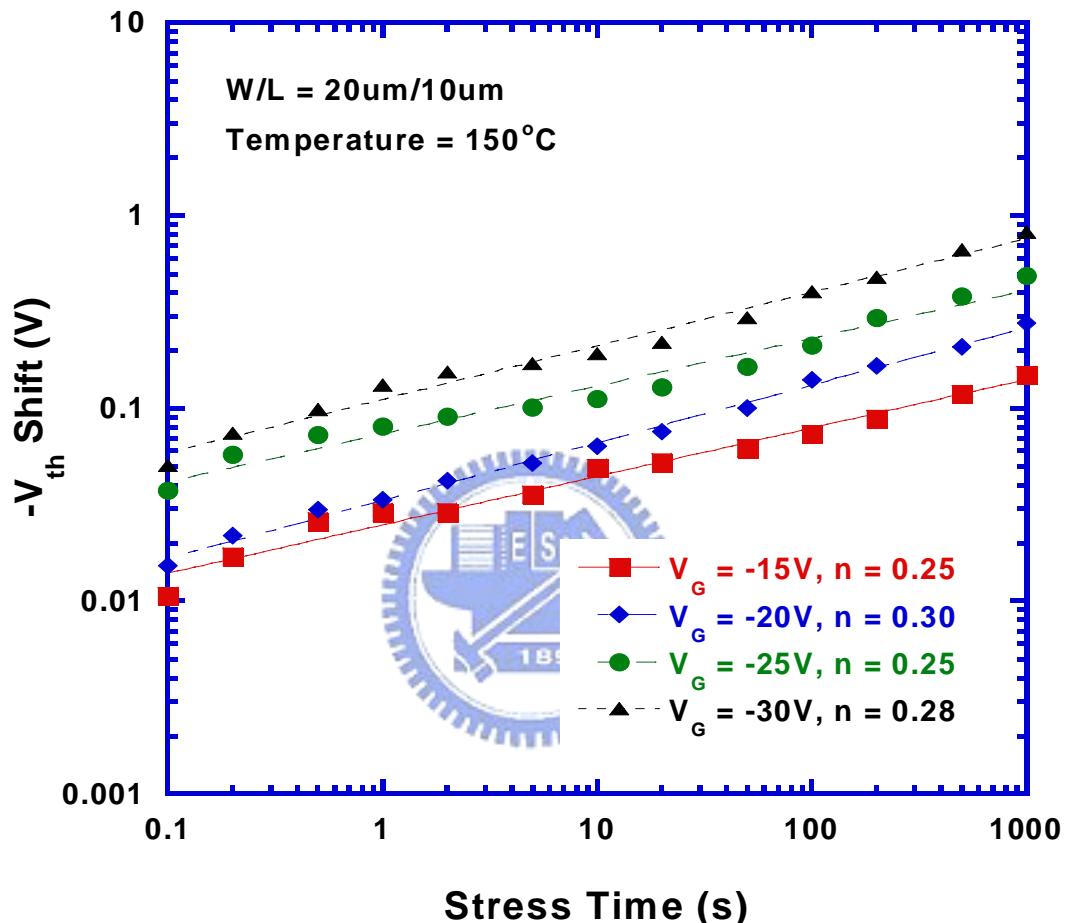

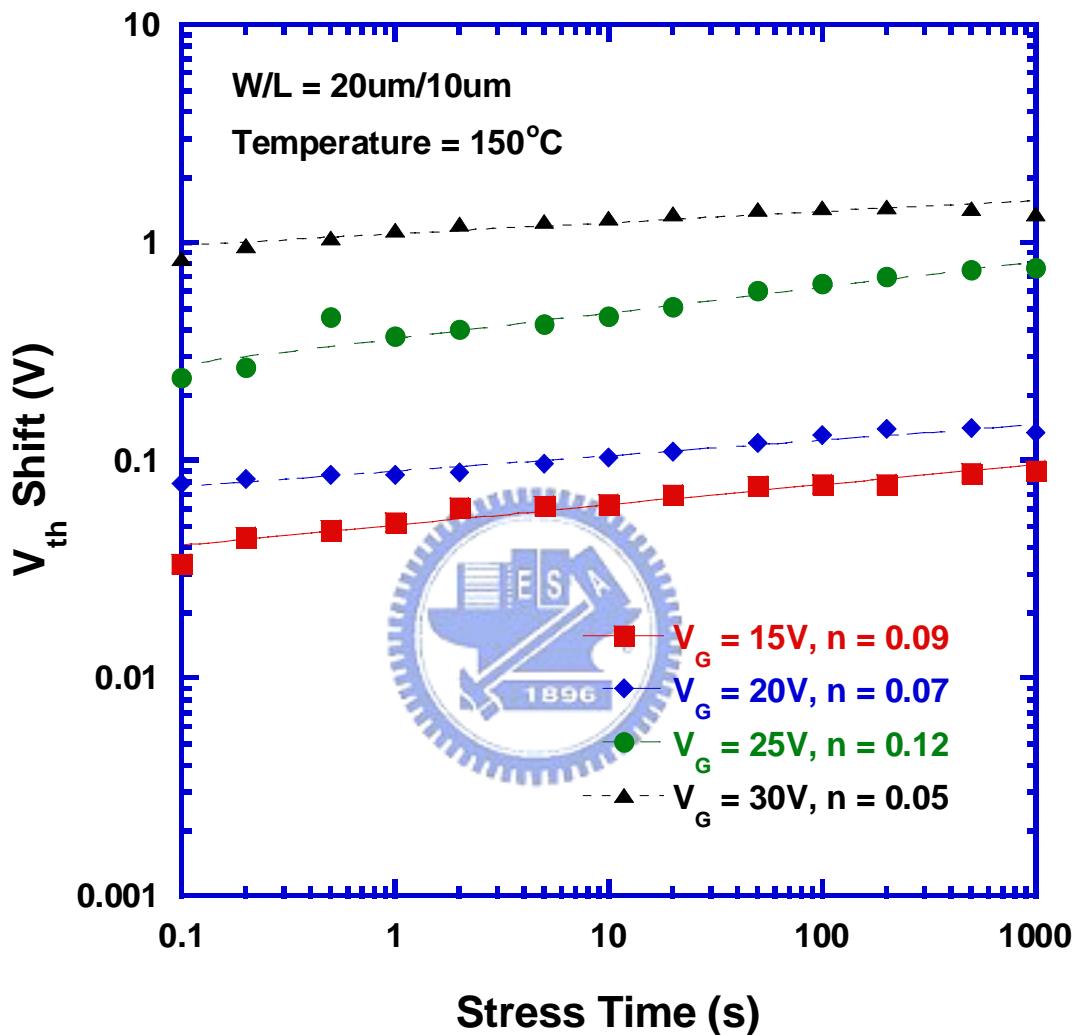

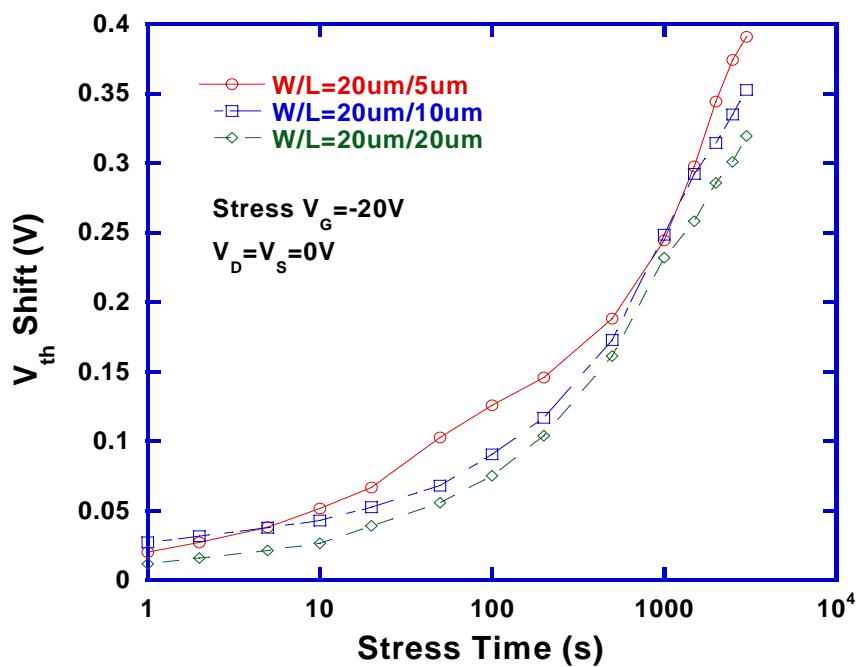

Fig. 3-4 (a) Dependences of threshold voltage shift on the stress time of LTPS TFTs under various stress conditions.

(b) Dependences of threshold voltage shift on the stress voltage of LTPS TFTs under various stress conditions.

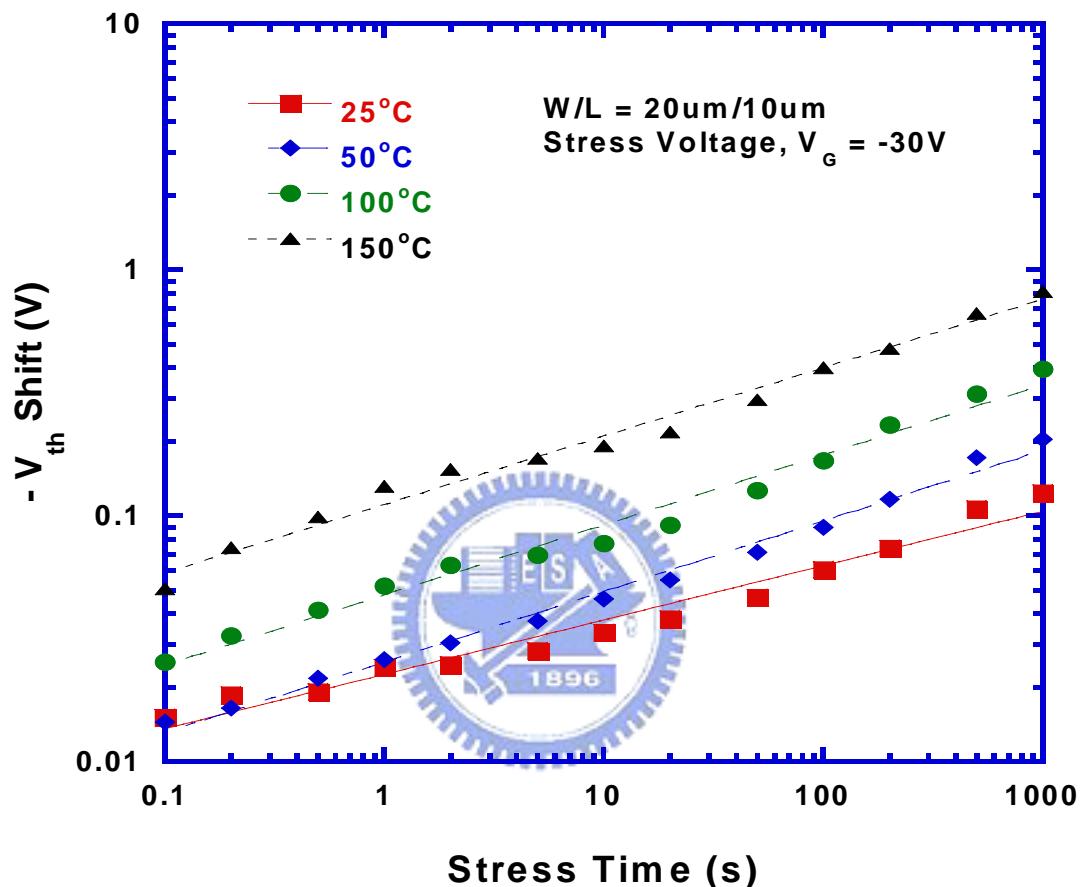

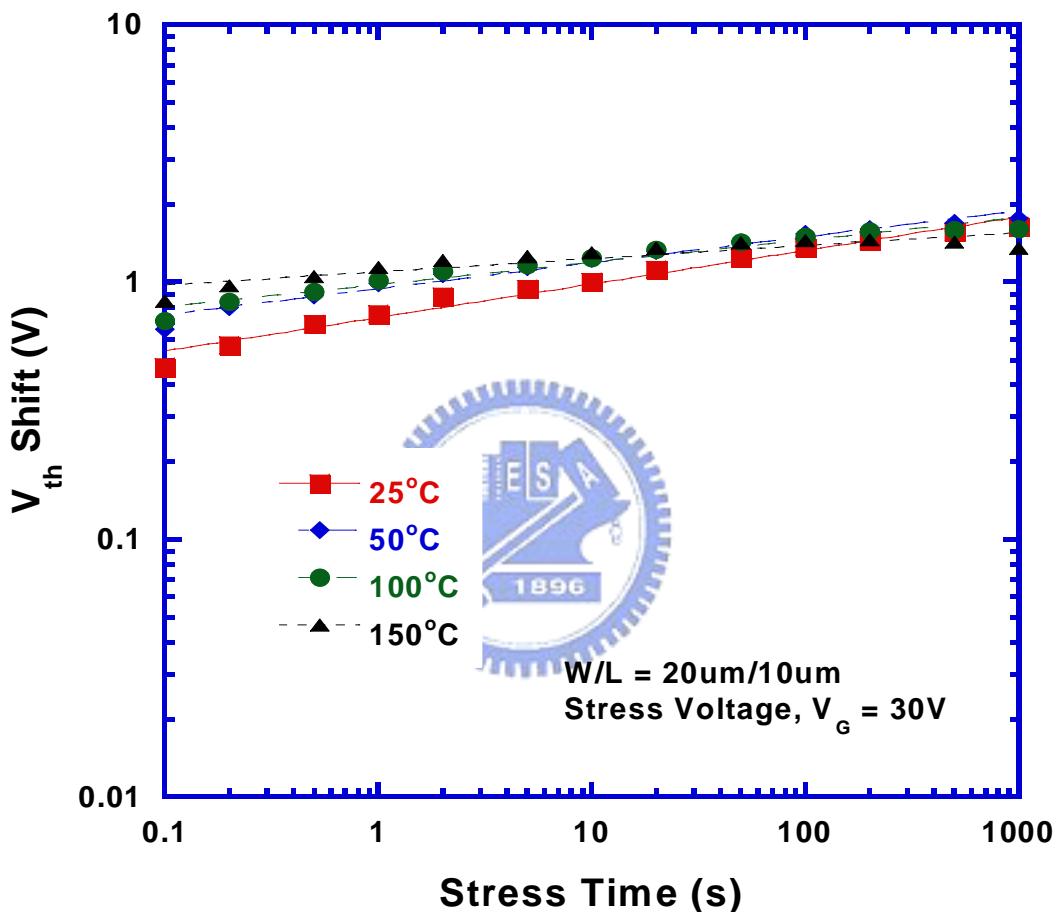

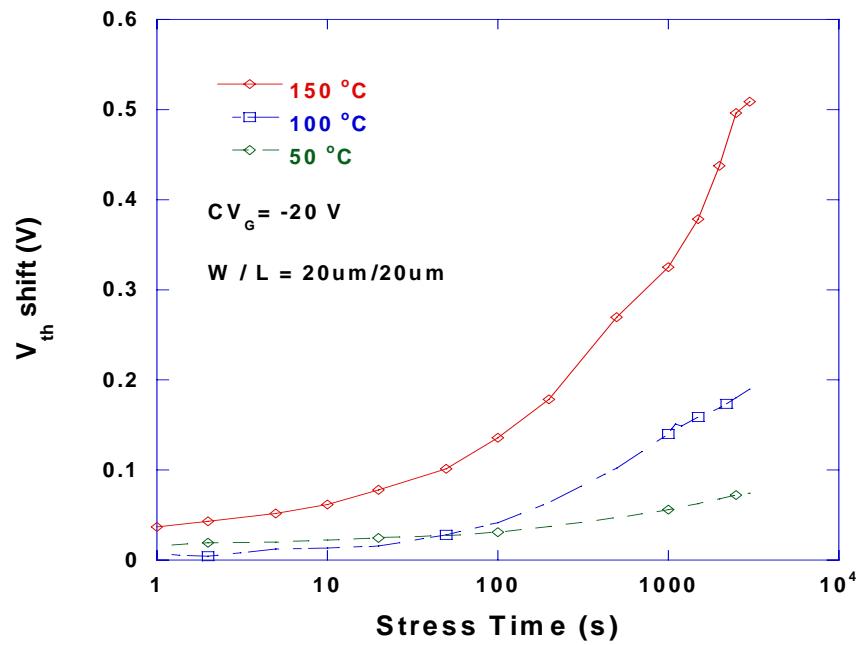

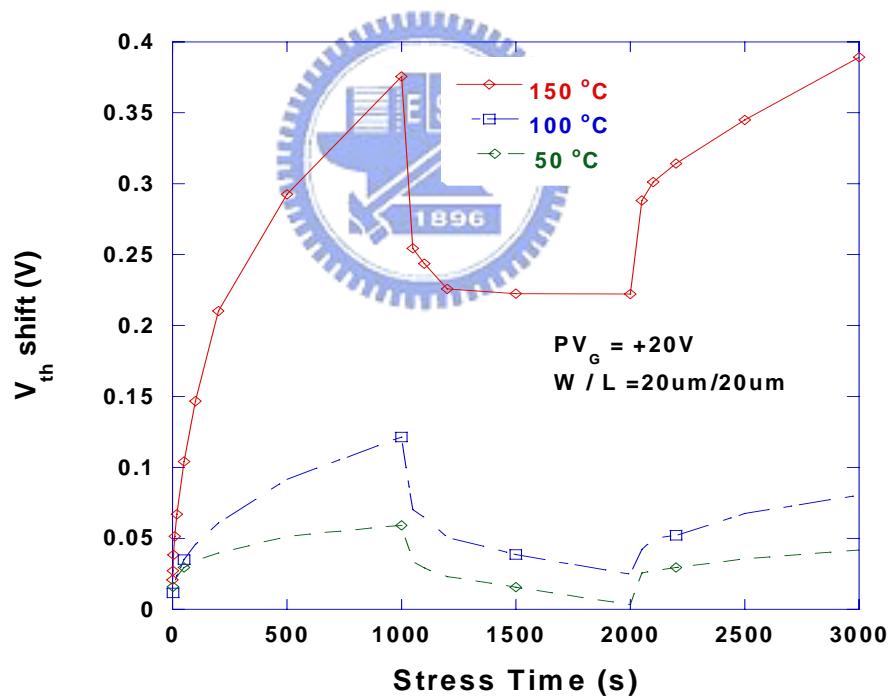

Fig. 3-5 (a) Time dependence of the  $\Delta V_{th}$  of p-channel and under various stress temperatures.

(b) Time dependence of the  $\Delta V_{th}$  of n-channel TFTs under various stress temperatures.

Fig. 3-6 (a) Correlation between the degradation of subthreshold swing, and threshold voltage shift of p-channel LTPS TFTs after NBTI stress.

(b) Correlation between the degradation of maximum transconductance, and threshold voltage shift of n-channel LTPS TFTs after NBTI stress.

Fig. 3-7 (a) Driving current variation as a function of the stress voltage for p-channel LTPS TFTs.

(b) Driving current variation as a function of the stress voltage for n-channel LTPS TFTs.

## Chapter 4

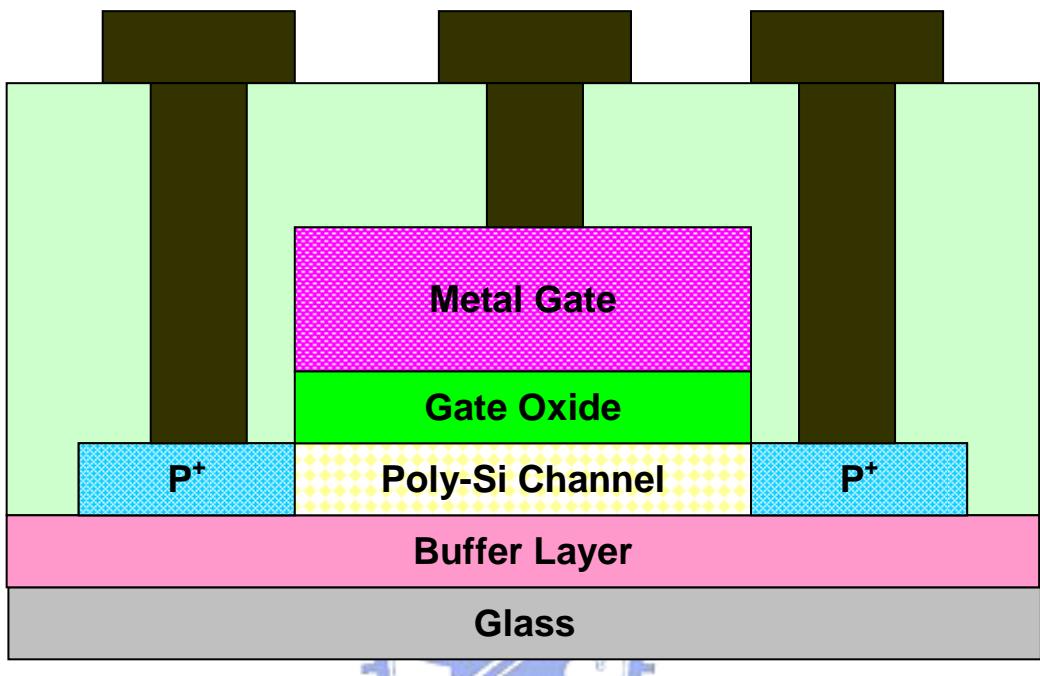

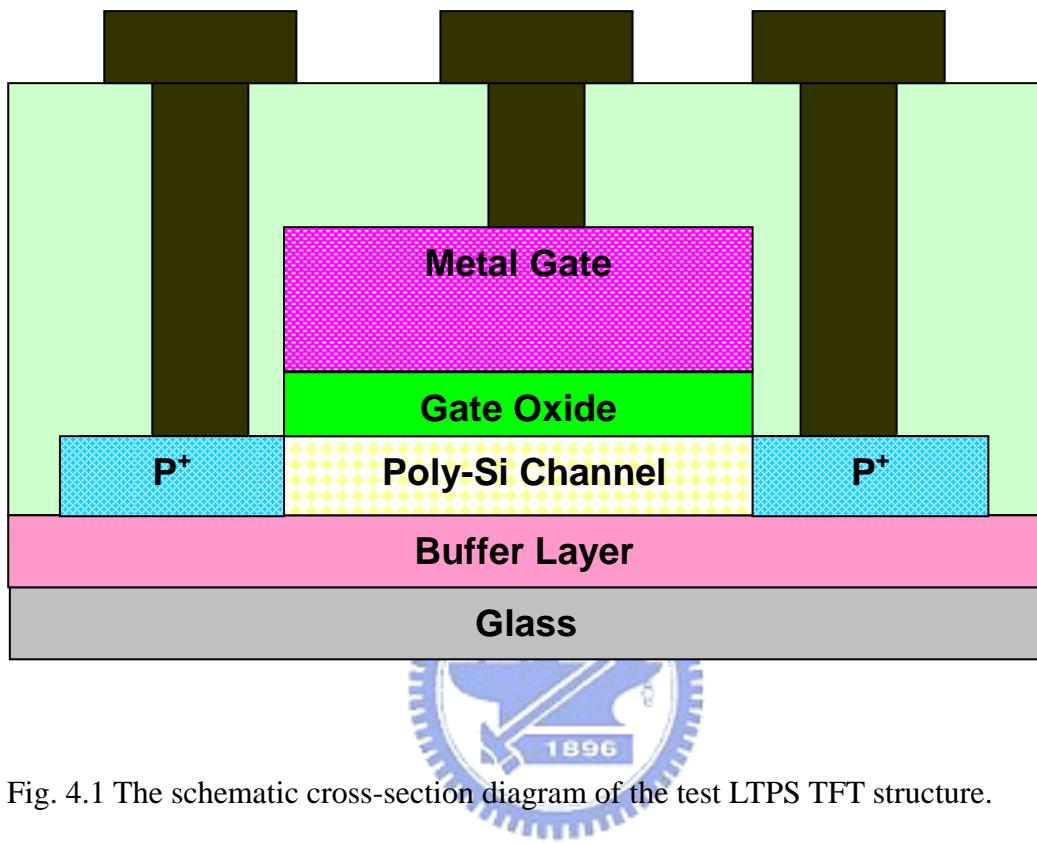

Fig. 4-1 The schematic cross-section diagram of the test LTPS TFT structure.

Fig. 4-2 Shchematic cross-section diagram of LTPS TFT and DNBTI stress setup. The stress temperature was performed from 25°C to 150°C, and the stress bias was applied to the gate electrode while source and drain electrodes were grounded.

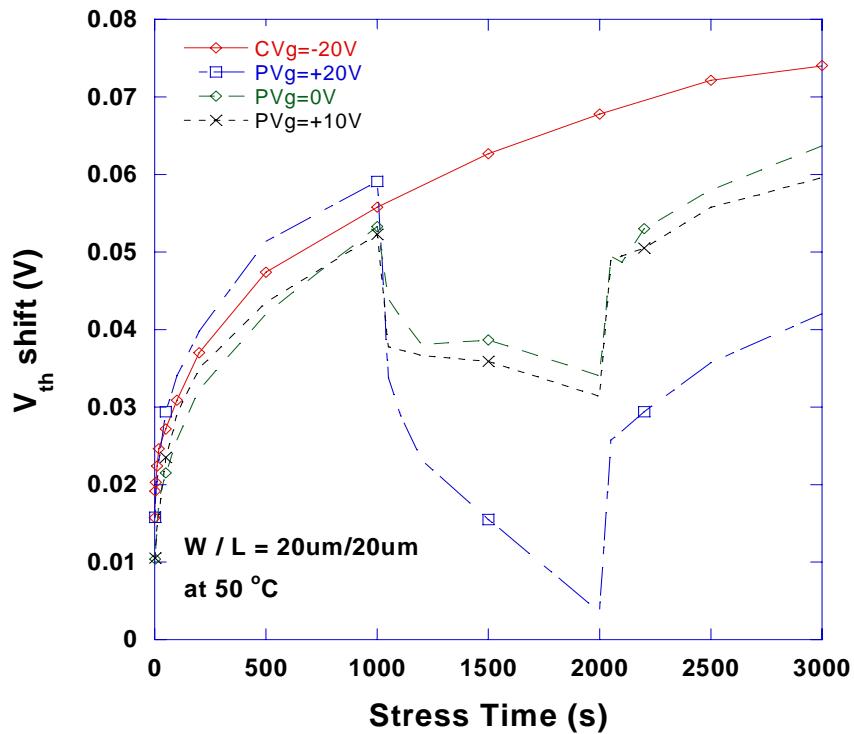

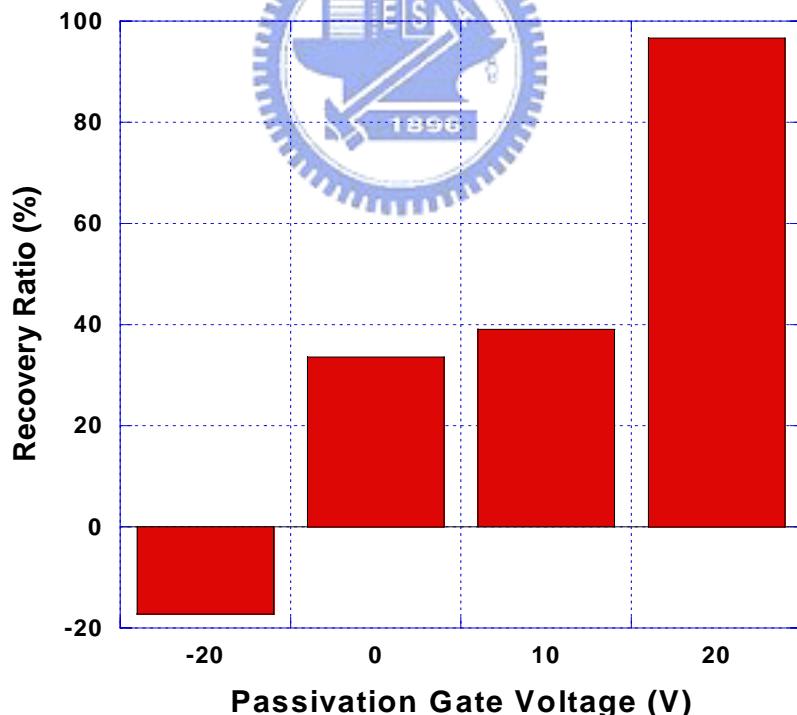

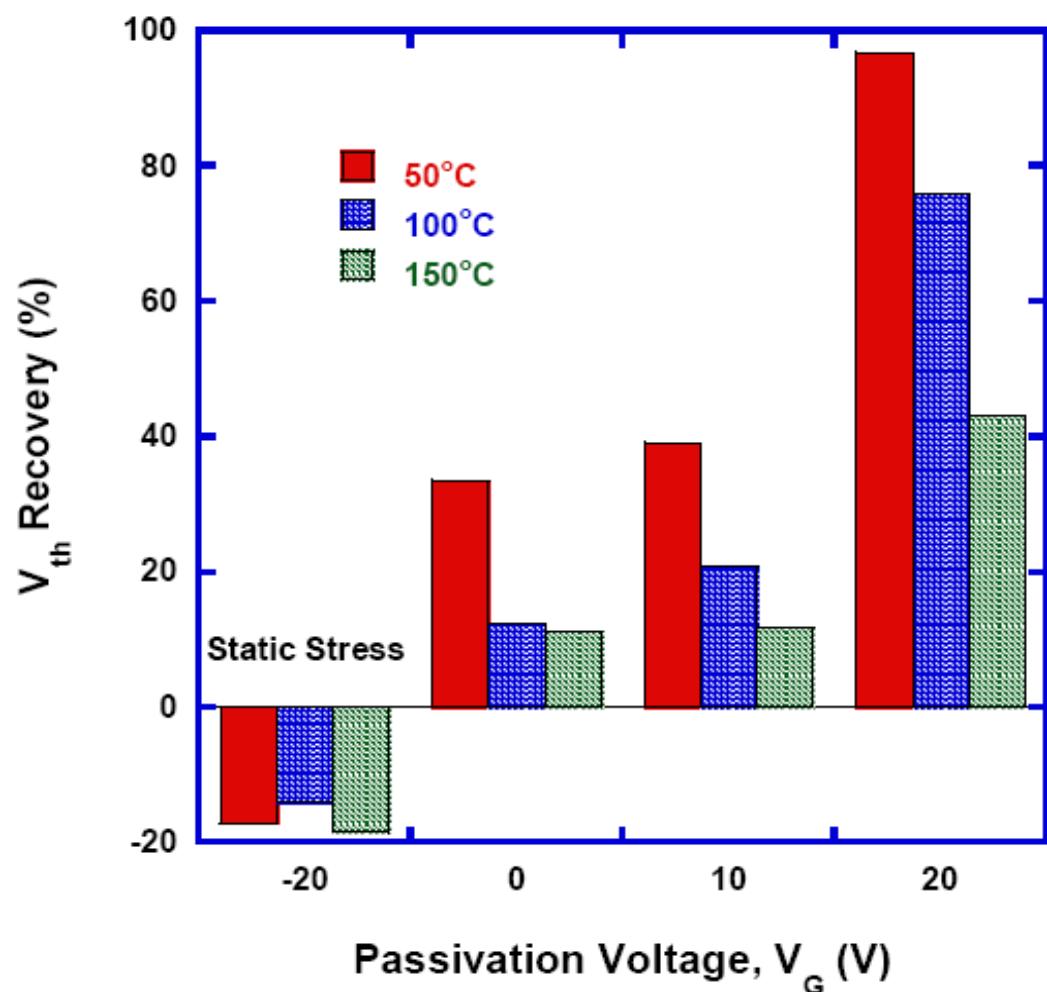

Fig. 4-3 Threshold voltage degradation and recovery under different passivation biases at 50°C.

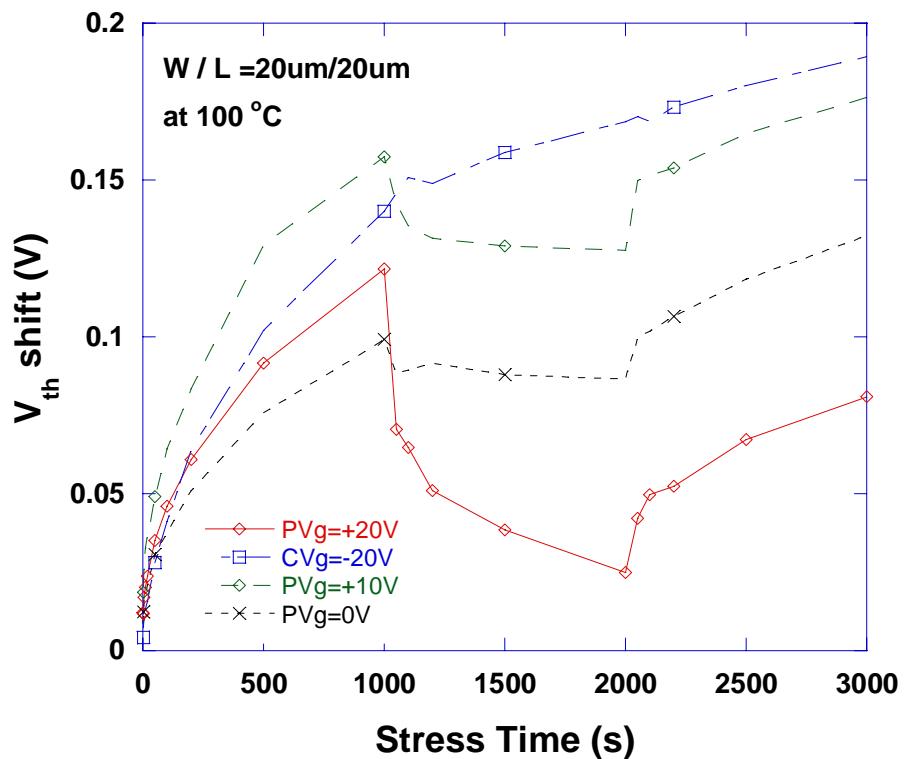

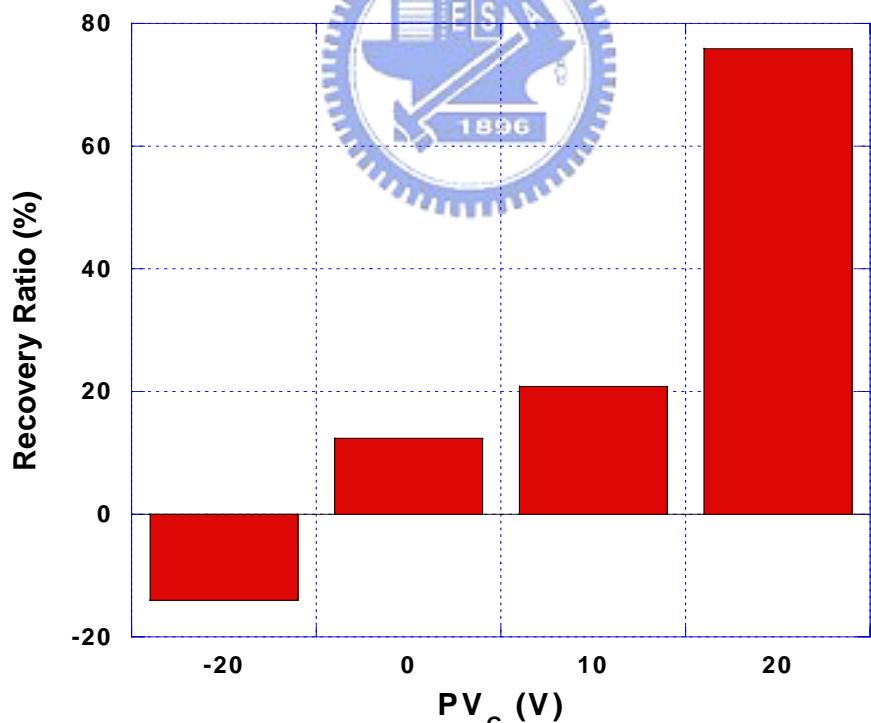

Fig. 4-4 Threshold voltage degradation and recovery under different passivation biases at 100°C.

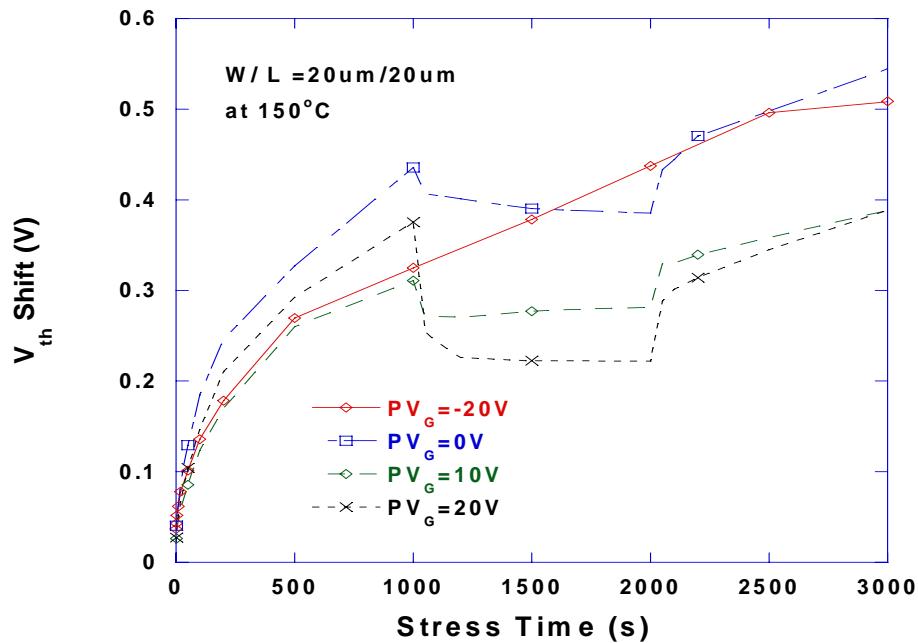

Fig. 4-5 Threshold voltage degradation and recovery under different passivation biases at 150°C.

Fig. 4-6 NBTI degradation and recovery during long-period stress and passivation.

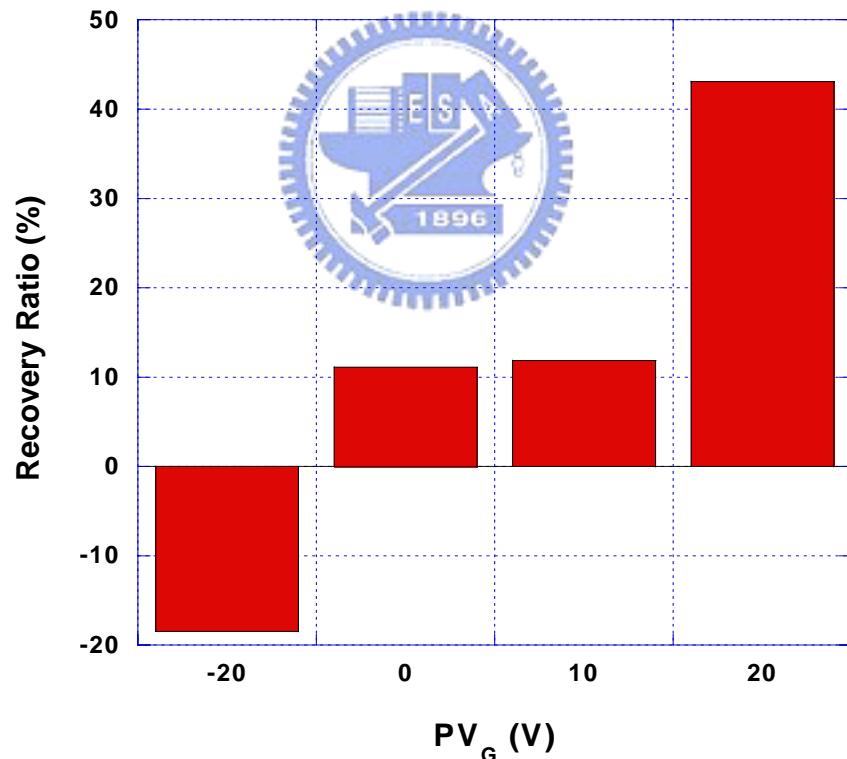

Fig. 4-7 Comparison of threshold voltage recovery dependence on temperature and passivation voltage.

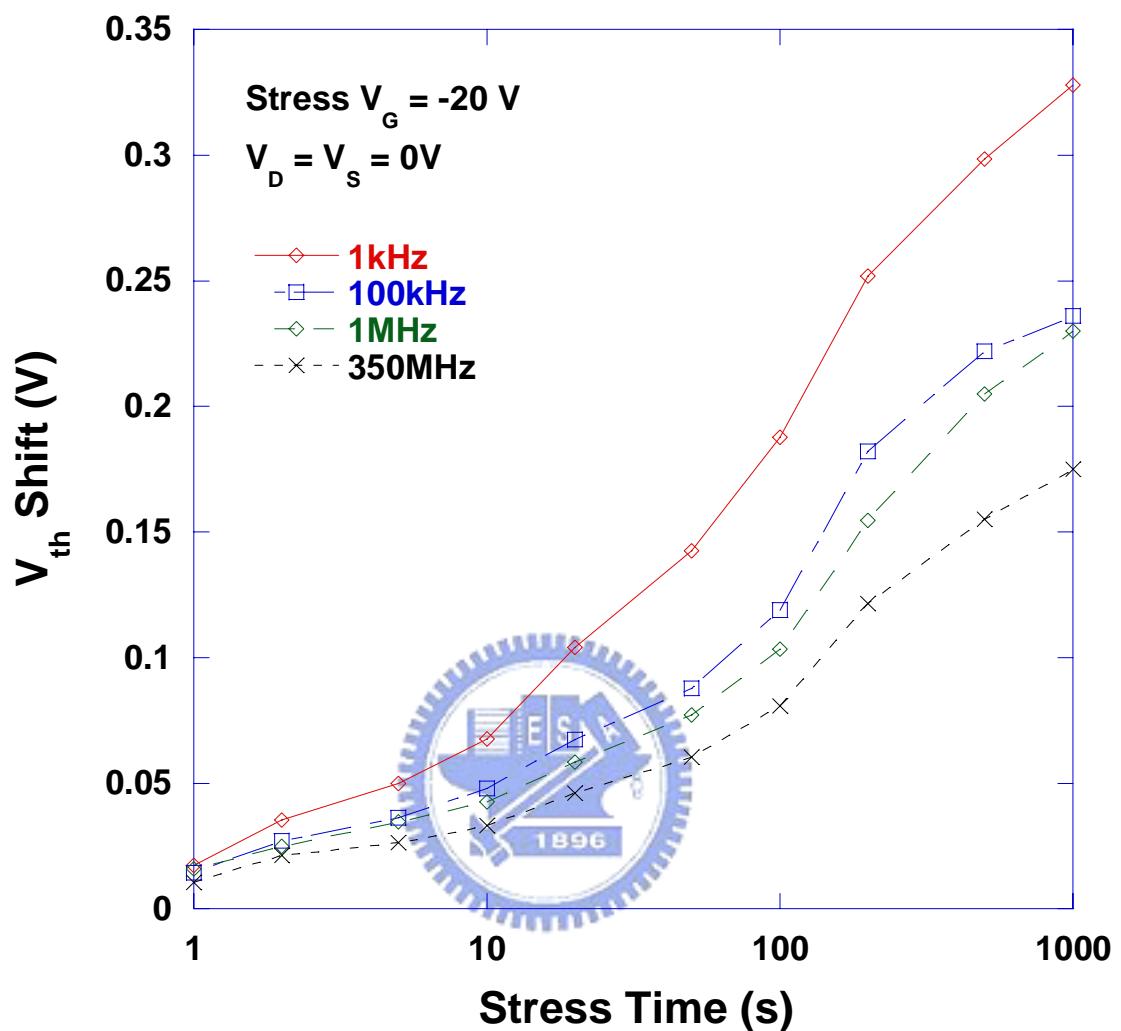

Fig. 4-8 Threshold voltage shift during DNBTI with different stress frequencies.

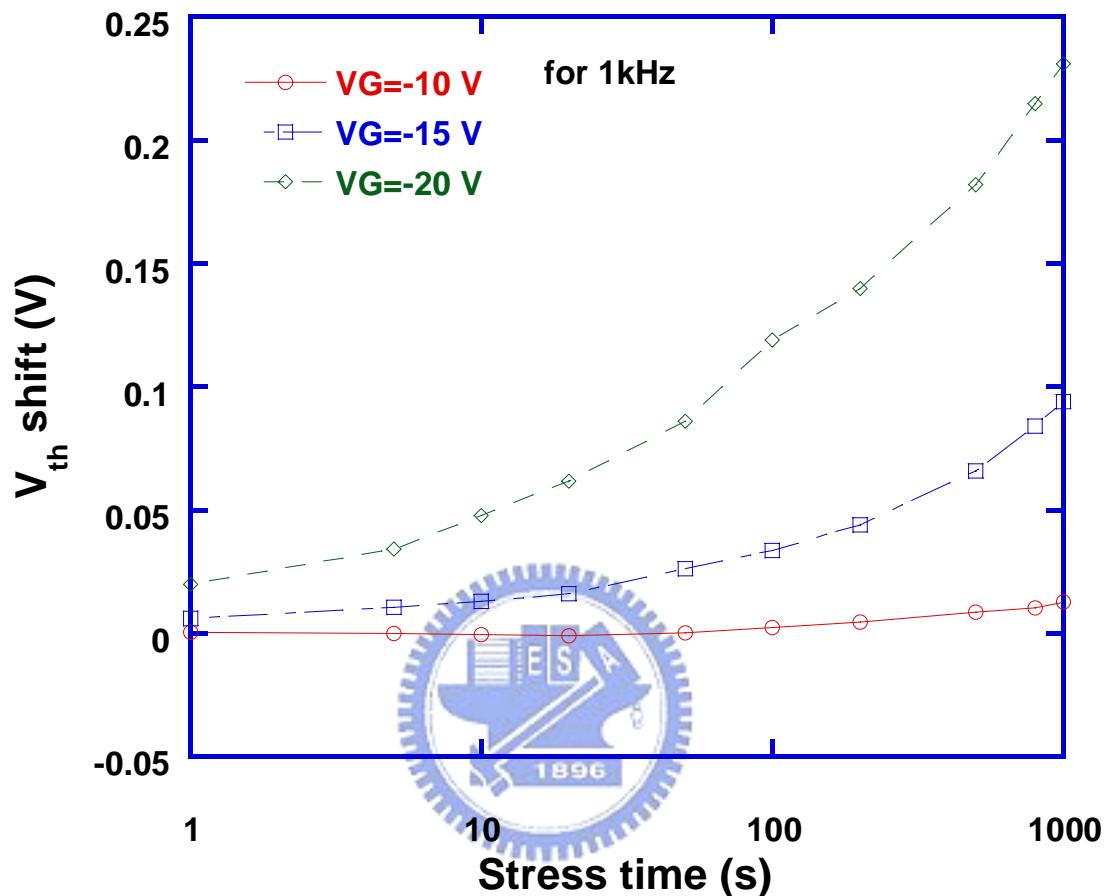

Fig. 4-9 Threshold voltage shift during DNBTS with different stress biases.

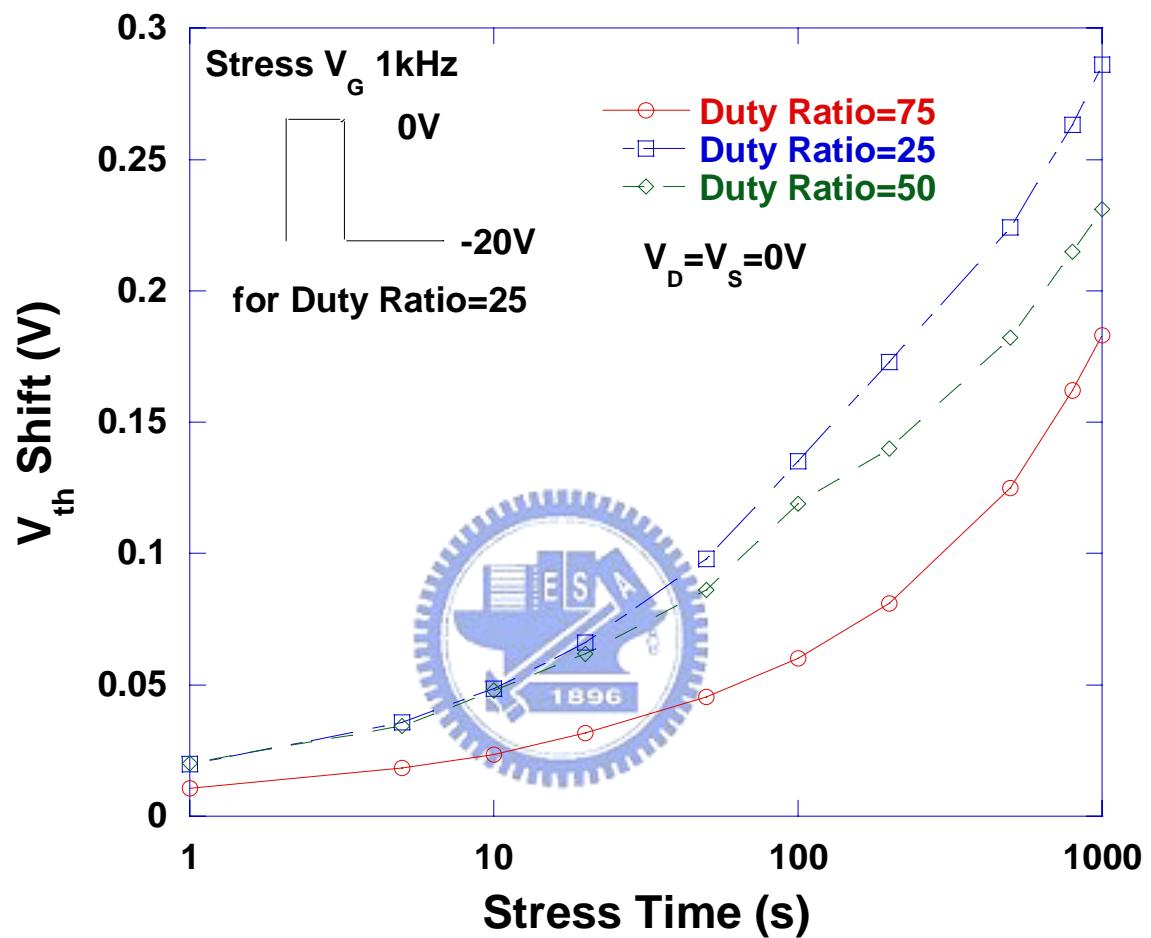

Fig. 4-10 Threshold voltage shift during DNBTS with different duty ratio.

Fig. 4-11 Dependence of device dimension to threshold voltage and recovery during NBTS.

# Chapter 1

## Introduction

### 1.1 Overview of Poly-Si Thin-Film Transistors

In recent years, thin-film transistors (TFTs) have been widely investigated in industrial applications, such as active-matrix liquid-crystal displays (AMLCDs) [1-3], high density static random access memories (SRAMs) [4], electrical erasable programming read only memories (EEPROM) [5][6], linear image sensors [7], photodetector amplifiers [8], and also candidates for 3-D ICs' applications [9], etc. Within those applications, the application of active-matrix liquid-crystal displays (AMLCDs) is the major driving force to promote the developments of poly-Si TFT technology.

It is known that hydrogenated amorphous silicon (a-Si:H) TFTs were used for the pixel switching device at the first generation of AMLCDs. The advantages of a-Si:H TFTs are their compatibility with low processing temperature on large-area glass substrates and high off-stated impedance which result in a low leakage current. However, the low electron mobility ( $\leq 1 \text{ cm}^2/\text{V} \cdot \text{s}$ ) make it hard to realize the integration of the switching pixels with the peripheral driver circuits in one signal substrate to further reduce the production cost of AMLCDs. It was until 1966, the first polycrystalline silicon thin film transistors (poly-Si TFTs) were fabricated by C. H. Fa *et al.* [10]. In comparison with a-Si TFTs, poly-Si TFTs have superior carrier mobility, higher CMOS capability, and better reliability. The high driving current of poly-Si TFTs makes the integration of switching pixels and driver circuits possible [11].

Moreover, the aperture ratio (A.R.) and the panel brightness can also be greatly promoted for the sake of the scaling device size, needed using poly-Si [12]. Therefore, the performance of display can be significantly improved. As a result, poly-Si TFTs have a great potential to realize both high-performance and large-area AMLCDs, and further to accomplish System-on-Panel (SOP).

The study of poly-Si TFTs fabrication with the maximum process temperature below 620°C was not commenced until 1980s. These TFTs fabricated with such low maximum process temperature are so-called Low-Temperature Poly-Si (LTPS) TFTs. With such low process temperature, poly-Si TFTs could be fabricated on inexpensive, low-melting point, and large-area glass substrates. So far, many crystallization techniques have been proposed to achieve LTPS TFTs, such as solid-phase crystallization (SPC) [13-16], metal-induced crystallization (MIC) [17-19], metal-induced lateral crystallization (MILC) [20-22], and laser annealing crystallization [23-27], and etc. Among these techniques, excimer laser annealing (ELA) crystallization is believed to become the mainstream technology for mass production because high-quality poly-Si films can be obtained.

Compared to the single crystal silicon, the performance of poly-Si TFTs are strongly related to grain boundaries and intra-grain defects. For example, defects in the grain boundary would trap carriers and generate a potential barrier which degrades the on-stated current of poly-Si TFTs. Moreover, the grain boundaries also provide the path of leakage current. In order to obtain desirable electrical characteristics of poly-Si TFTs, it is necessary to improve the device performance by enlarging the grain size of poly-Si films [28] and reducing the trap states in grain boundaries to raise the field effect mobility. Additionally, there were other methods such as plasma treatments to passivate the defects in the channel or narrowing the channel width to reduce the trap state density [29-32].

Moreover, novel structures are also used to fabricate high-performance poly-Si TFTs. These techniques are focus on the reduction of the electric field near the drain junction, thus suppress the OFF-state leakage current of the device. Many structures such as multi-channel ones [33], offset drain/source ones [34], lightly doped drain (LDD) ones [35], field induced drain ones [36], and etc. have been proposed and investigated intensively.

## 1.2 Overview of Bias Temperature Instability

With the continuous scaling of the dimensions of transistors, negative bias temperature instability (NBTI) stress in p-MOS transistors has become one of the most critical reliability issues which determine the lifetime of CMOS devices [37]-[40]. In the contrary, positive temperature instability (PBTI) stress ultimately determine the lifetime of n-MOS transistors, especially of high- $k$  n-MOS transistors [41]-[47]. Hot carrier stressing and Fowler-Nordheim tunneling can cause degradation both near the  $\text{SiO}_2$  /Si interface [48] [49] and in the bulk of gate oxide [50]-[52], while BTS only induces degradation within a few nm of the interface [53] [54]. In conventional NBTI studies, the degradation refers to the generation of positive oxide charge and interface traps under negative gate bias at elevated temperature, especially in p-channel MOSFETs. While NBTI includes both interface state generation and positive oxide charge formation [55]-[58], PBTI only exists the formation of donor-like interface states [59].

NBTI was first reported by Miura and Matukura [37], named as Instability Number VI by Deal [60], and further researched by Goetzberger et al., which was one of the first groups at Bell Labs trying to show the detailed characterization of NBTI [61]. Despite numerous efforts in researching the NBTI degradation mechanism, it

has not been fully understood till now. Hot carrier injection (HCI) would no longer play the dominator in device when the gate oxide thickness of device is shrunk to nm scale due to the reducing applied operation voltage. However, NBTI is more and more severe for ultra-thin oxides because of the increasing interface trap density induced by it. Recently, NBTI has been identified as one of the major reliability concerns for deep sub-micron pMOSFETs [62]. During negative-bias-temperature stressing (NBTS), typical stress temperature lies in the 100-250°C range, a large number of interface states and positive fixed charges are generating. Either negative gate voltage or elevated temperatures can produce NBTI, but a stronger and faster effect is produced by their combined action. Additionally, the higher the origin interface trap density ( $D_{it}$ ) is, the higher the final stress-induced  $D_{it}$ . The  $D_{it}$  increased with gate voltage and time with a time dependence of  $t^{0.25}$ ,  $D_{it}$  (T=250°C) >  $D_{it}$  (T=150°C), and devices with p-type substrates give higher  $D_{it}$  than devices with n-type substrate do. The shift in threshold voltage and degradation in transconductance have been suggested to be due to the interfacial electro-chemical reactions related to the holes from the channel inversion layer. During the NBTS, both fixed oxide charges and interface trap density ( $D_{it}$ ) increase. However, the generation of fixed oxide charges is independent of oxide thickness, while the interface trap generation is inversely proportional to oxide thickness.[63] This suggests that NBTI is worse for thinner oxide.

In the other hand, it is found that the importance of PBTI in nMOSFETs could be as critical as that of NBTI in pMOSFETs. Various models have been proposed to explain PBTI with  $V_t$  shift or on-current degradation. There are roughly two kinds of models which explain the mechanisms responsible for the degradation in PBTI stress. One of these models indicates that the degradation due to PBTI stress is owing to the charge de-trapping from the high-k gate insulator, which possesses numerous defects.

This kind of models has ignored the influence of the generation of trap states under the PBTI stress. Another kind of models shows that there is still another mechanism which causes degradation except the charge de-trapping mechanism, i.e., the trap creation mechanism. As a result, it is necessary to take the trap creation during a positive-bias-temperature stressing (PBTS) into consideration.

Both NBTI and PBTI do play important parts in the device reliability issues. Because of the shrinking dimensions of devices and the integrating scale of circuits, devices would work under high temperature. As a result, it is necessary to investigate BTI not only under conventional DC stress bias but also under AC stress condition.

### 1.3 Motivation

In this thesis, we focus not only on the enhancement of mobility, but also on the reliability of poly-Si TFTs. It is necessary for TFTs to have both high performance and good reliability to meet the criteria of commercial applications such as AMLCDs, 3-D IC's application, SRAMs, and EEPROMs. Compared to the single crystal silicon, the performance of poly-Si TFTs are strongly related to grain boundaries and intra-grain defects. Defects in the grain boundary would trap carriers and degrades the on-stated current of poly-Si TFTs. Moreover, the grain boundaries also provide the path of leakage current. In order to obtain desirable electrical characteristics of poly-Si TFTs, it is necessary to improve the device performance by enlarging the grain size of poly-Si films and reducing the trap states in grain boundaries to raise the field effect mobility.

There are several ways to improve the electrical characterization of TFTs, such as SPC and ELA, mentioned above. One coincidence of them is to enlarge the grain size in the poly-Si channel of TFTs. By means of growing larger grains, we can derive

not only higher carrier mobility but also suppressed path of leakage current due to the decrease of GBs in channel. In order to achieve high performance poly-Si TFTs, we fabricated poly-Si TFTs with a novel method using a buffer a-Si layer to enhance their performance.

Besides, NBTI in p-MOSFETs, while PBTI in n-MOSFETs have been found to be important reliability issues and have been widely investigated yet. It has been reported the degradation of NBTI in MOSFETs is mainly due to the generation of interface states and fixed oxide charges, and NBTI can be thermally and electrically activated[19]-[22]. Owing to the poor thermal conductivity of the glass substrates and high voltage operations in poly-Si TFTs, BTI must be the important issue in the reliability of poly-Si TFTs. However, BTI is still not thoroughly studied in poly-Si TFTs and the mechanism is not fully understood. In addition, the degradation mechanism of BTI stress in poly-Si TFTs, due to the grain boundaries in the channel region, might be different from MOSFETs. So, we studied the instabilities and mechanisms of LTPS TFTs upon BTI stress.

Finally, we investigated both the degradation and the passivation mechanisms under dynamic NBTI (DNBTI) stress. With DC NBTI stress, we would ignore the passivation mechanism for actually applications in IC circuits. As a result, we would underestimate the device lifetime. So we studied the degradation mechanisms of LTPS TFTs upon DNBTI stress.

## 1.4 Organization of the Thesis

In the following sections, we will show our research efforts.

In Chapter 2, the fabrication process and electrical characteristics of poly-Si TFTs using a buffer a-Si layer beneath the channel and devices with anneal procedure after gate oxide deposition will be proposed. Experimental results reveal that the

performance and reliability of our devices have remarkable improvement in comparison with conventional TFTs. Additionally, we made a detail discussion to explain the results of our experiment.

In Chapter 3, we discuss the reliability issues of p-channel TFTs and n-channel TFTs under NBTI and PBTI, respectively. Experimental results reveal that the mechanisms of NBTI and PBTI are quite different from each other. NBTI and PBTI also caused different degradation on p-TFTs and n-TFTs, respectively. We will make a detail discussion between the NBTI and PBTI.

In Chapter 4, the passivation phenomenon under dynamic negative-bias temperature stress (DNBTS) will be investigated by applying different stress gate biases, different stress frequencies, and different passivation voltages under different temperatures. Then, we will analyze the degradation and passivation mechanisms under DNBTI from our experimental results.

In the end of this thesis, we will make conclusions in Chapter 5.

## References:

[1] Y. Oana, "Current and future technology of low-temperature poly-Si TFT-LCDs," *Journal of the SID*, vol. 9, pp. 169-172, 2001.

[2] S. Morozumi, K. Oguchi, S. Yazawa, Y. Kodaira, H. Ohshima, and T. Mano, "B/W and color LC video display addressed by poly-Si TFTs," *SID Dig.*, pp.156, 1983.

[3] R. E. Proano, R. S. Misage, D. Jones, and D. G. Ast, "Guest-host active matrix liquid-crystal display using high-voltage polysilicon thin film transistors," *IEEE Trans. Electron Devices*, vol. 38, pp. 1781, 1991.

[4] S. Batra, "Development of drain-offset (DO) TFT technology for high density SRAM's," Extended Abstracts, vol.94-2, in *Electrochemical Soc. Fall Mtg., Miami Beach, FL*, Oct. pp. 677,1994.

[5] N. D. Young, G. Harkin, R. M. Bunn, D. J. McCulloch, and I. D. French, "The fabrication and characterization of EEPROM arrays on glass using a low temperature poly-Si TFT process," *IEEE Trans. Electron Devices*, vol. 43, pp. 1930-1936, 1996.

[6] M. Cao, *et al.*, "A simple EEPROM cell using twin polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 15, pp. 304, 1994.

[7] T. Kaneko, Y . Hosokawa, M. Tadauchi, Y . Kita and H. Andoh, "400 dpi integrated contact type linear image sensors with poly-Si TFT's analog readout circuits and dynamic shift registers," *IEEE Trans. Electron Devices*, vol. 38, no. 5 pp. 1086-1096, 1991.

[8] N. Yamauchi, Y . Inada and M. Okamura, "An intergated photodetector-amplifier using a-Si p-i-n photodiodes and poly-Si thin-film transistors," *IEEE Photonic Tech. Lett.*, vol. 5, pp. 319, 1993.

[9] K. Banerjee, S. J. Souri, P. Kapur, and K. C. Saraswat, "3-D ICs: a novel chip design for improving deep-submicrometer interconnect performance and

system-on-chip integration," *Proceedings of the IEEE*, vol.89, pp. 602-633, 2001.

[10] C. H. Fa, and T. T. Jew, "The polysilicon insulated-gate field-effect transistor," *IEEE Trans. Electron Devices*, vol. 13, no. 2, pp. 290, 1966.

[11] W. G. Hawkins, "Polycrystalline -silicon device technology for large-area electronics," *IEEE Trans. Electron Devices*, vol. 33, pp. 477-481, 1986.

[12] I. -W. Wu, "Cell design considerations for high-aperture-ratio direct-view and projection polysilicon TFT-LCDs," in *SID Tech. Dig.*, pp. 19, 1995.

[13] A. Nakamura, F. Emoto, E. Fujii and A. Tamamoto, "A high-reliability, low-operation-voltage monolithic active-matrix LCD by using advanced solid-phase growth technique," in *IEDM Tech. Dig.*, pp.847, 1990.

[14] R. B. Iverson and R. Reif, "Recrys tallization of amorphized polycrystalline silicon films on  $\text{SiO}_2$ : temperature dependence of the crystallization parameters," *J. Appl. Phys.*, vol. 62, no. 5, pp. 1675-1681, 1987.

[15] F. Emoto, K. Senda, E. Fujii, A. Nakamura, A. Yamamoto, Y . Yamamoto, Y . Uemoto, and Gota Kano, " Solid phase growth technique for hogh cut-off frequency polysilicon TFT integrated circuits on a quartz substrate," *IEEE Trans. Electron Devices*, vol. 37, pp. 1462, 1990.

[16] M. K. Hatalis and D. W. Greve, "Large grain polycrystalline silicon by low-temperature annealing of low-pressure chemical vapor deposited amorphous silicon films," *J. Appl. Phys.*, vol. 63, no. 7, pp. 2260-2266, 1988.

[17] S. Y . Yoon, K. Hyung, C. O. Kim, J. Y . Oh and J. Jang, "Low temperature metal induce crystallization of amorphous silicon using a Ni solution," *J. Appl. Phys.*, vol. 82, pp. 5865-5867, 1997.

[18] G. Radnoci, A. Robertsson, H. T. G.. Hentzell, S. F. Gong and M. A. Hasan, "Al induced crystallization of a-Si," *J. Appl. Phys.*, vol. 69, pp. 6394-6399, 1991.

[19] Z. Jin, G. A. Bhat, M. Yeung, H. S. Kwok and M. Wong, "Nickel induced

crystallization of amorphous silicon thin films," *J. Appl. Phys.*, vol. 84, pp.194-200, 1998.

[20] S. W. Lee and S. K. Joo, "Low temperature poly-Si thin-film transistor fabrication by metal-induced lateral crystallization," *IEEE Electron Device Lett.*, vol. 17, pp. 160-162, 1996.

[21] H. Kim, J. G. Couillard and D. G. Ast, "Kinetic of silicide- induced crystallization of polycrystalline thin-film transistors fabricated from amorphous chemical-vapor deposition silicon," *Appl. Phys. Lett.*, vol. 72, pp. 803-805, 1998.

[22] Z. Jin, H. S. Kwok and M. Wong, "Performance of thin-film transistors with ultrathin Ni-NiLC polycrystalline silicon channel layers," *IEEE Electron Device Lett.*, vol. 20, pp. 167-169, 1999.

[23] G. K. Guist, and T. W. Sigmon, "High-performance laser-processed polysilicon thin-film transistors," *IEEE Electron Device Lett.*, vol. 20, no. 2, pp. 77-79, 1999.

[24] N. Kudo, N. Kusumoto, T. Inushima, and S. Yamazaki, "Characterization of polycrystalline-Si thin-film transistors fabricated by excimer laser annealing method," *IEEE Trans. Electron Devices*, vol. 41, no. 10, pp. 1876-1879, 1994.

[25] T. Sameshima, S. Usui and M. Sekiya, "XeCl excimer laser annealing used in the fabrication of poly-Si TFT's," *IEEE Electron Device Lett.*, vol. 7, no. 5, pp. 276-278, 1986.

[26] D. H. Choi, E. Sadauyki, O. Sugiura and M. Matsumura, "Excimer-laser crystallized poly-Si TFT's with mobility more than 600 cm<sup>2</sup>/V.s," *IEEE Trans. Electron Devices*, vol. 40, no. 11, pp. 2129, 1993.

[27] K. Shimizu, O. Sugiura and M. Matsumura, "High-mobility poly-Si thin-film transistors fabricated by a novel excimer laser crystallization method," *IEEE*

*Trans. Electron Devices*, vol. 40, no. 1, pp. 112-117, 1993.

[28] H. Kuriyama *et al.*, “Enlargement of poly-Si film grain size by excimer laser annealing and its application to high-performance poly-Si thin film transistor,” *Jpn. J. Appl. Phys.*, vol. **30**, pp. 3700-3703, 1991.

[29] A. Yin, and S. J. Fonash, “High-performance p-channel poly-Si TFT’s using electron cyclotron resonance hydrogen plasma passivation,” *IEEE Electron Device lett.*, vol. 15, no. 12, pp. 502-503, 1994.

[30] C. K. Yang, T. F. Lei, C. L. Lee, “The combined effects of low pressure NH<sub>3</sub> annealing and H<sub>2</sub> plasma hydrogenation on polysilicon thin-film-transistors,” *IEEE Electron Device lett.*, vol. 15, pp. 389-390, 1994.

[31] J. W. Lee, N. I. Lee, J. I. Kan, C. H. Han, “Characteristics of polysilicon thin-film transistor with thin-gate dielectric grown by electron cyclotron resonance nitrous oxide plasma,” *IEEE Electron Device lett.*, vol. 18, pp.172-174, 1997.

[32] K. C. Moon, J. H. Lee, M. K. Han, “Improvement of polycrystalline silicon thin film transistor using oxygen plasma pretreatment before laser crystallization,” *IEEE Trans. Electron Devices*, vol. 49, pp. 1319-1322, 2002.

[33] T. Unagami and O. Kogure, “Large on/off current ratio and low leakage current poly-Si TFTs with multichannel structure,” *IEEE Trans. Electron Devices*, vol. 35, no. 11, pp. 1986-1989, 1988.

[34] B. H. Min, C. M. Park and M. K. Han, “A novel offset gated polysilicon thin film transistor without an additional offset mask,” *IEEE Electron Device lett.*, vol. 16, no. 5, pp. 161-163, 1995.

[35] P. S. Shih, C. Y. Chang, T. C. Chang, T. Y. Huang, D. Z. Peng and C. F. Yeh, “A novel lightly doped drain polysilicon thin-film transistor with oxide sidewall spacer formed by one-step selective liquid phase deposition,” *IEEE Electron*

*Device lett.*, vol. 20, no. 8, pp. 421-423, 1999.

[36] H. C. Lin, C.-M Yu, C.-Y. Lin, K.-L. Y eh, T. Y. Huang and T. F. Lei, “A novel thin-film transistor with self-aligned field induced drain,” *IEEE Electron Device lett.*, vol. 22, no. 1, pp. 26-28, 2001.

[37] N. Kimizuka, T. Yamamoto, T. Mogami, K. Yamaguchi, K. Imai, and T. Horiuchi, “Impact of bias temperature instability for direct-tunneling ultrathin gate oxide on MOSFET scaling,” in *Dig. Tech. Papers—Symp. VLSI Technology*, 1999, pp. 73–74.

[38] S. Ogawa, M. Shimaya, and N. Shiono, “Interface-trap generation at ultrathin SiO<sub>2</sub>–Si interfaces during negative-bias temperature aging,” *J. Appl. Phys.*, vol. 77, pp. 1137–1148, 1995.

[39] T. Yamamoto, K. Uwasawa, and T. Mogami, “Bias temperature instability in scaled p polysilicon gate p-MOSFETs,” *IEEE Trans. Electron Devices*, vol. 46, pp. 921–926, 1999.

[40] S. Ogawa and N. Shiono, “Generalized diffusion-reaction model for the low-field charge-buildup instability at the Si–SiO<sub>2</sub> interface,” *Phys. Rev. B, Condens. Matter*, vol. 51, pp. 4218–4230, 1995.

[41] S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, “Charge trapping related threshold voltage instabilities in high permittivity gate dielectric stacks,” *J. Appl. Phys.*, vol. 93, pp. 9298–9303, 2003.

[42] C. Shen, M. F. Li, X. P. Wang, H. Y. Yu, Y. P. Feng, A. T.-L. Lim, Y. C. Yeo, D. S. H. Chan, and D. L. Kwong, “Negative U traps in HfO<sub>2</sub> gate dielectrics and frequency dependence of dynamic BTI in MOSFETs,” in *IEDM Tech. Dig.*, Dec. 2004, pp. 733–736.

[43] R. Choi, S. J. Rhee, J. C. Lee, B. H. Lee, and G. Bersuker, “Charge trapping and detrapping characteristics in hafnium silicate gate stack under static and

dynamic stress,” *IEEE Electron Device Lett.*, vol. 26, no. 3, pp. 197–199, Mar. 2005.

[44] A. Shanware, M. R. Visokay, J. J. Chambers, A. L. P. Rorondaro, H. Bu, M. J. Bevan, R. Khamankar, S. Aur, P. E. Nicollian, J. McPherson, and L. Colombo, “Evaluation of the positive biased temperature stress stability in HfSiON gate dielectrics,” in *Proc. IRPS*, 2003, pp. 208–213.

[45] K. Onishi, R. Choi, C. S. Kang, H. J. Cho, Y. H. Kim, R. E. Nieh, J. Han, S. A. Krishnan, M. S. Akbar, and J. C. Lee, “Bias-temperature instabilities of polysilicon gate HfO MOSFETs,” *IEEE Trans. Electron Device*, vol. 50, no. 6, pp. 1517–1524, Jun. 2003.

[46] S. J. Rhee, Y. H. Kim, C. Y. Kang, C. S. Kang, H.-J. Cho, R. Choi, C. H. Choi, M. S. Akbar, and J. C. Lee, “Dynamic positive bias temperature instability characteristics of ultrathin HfO NMOSFET,” in *Proc. IRPS*, 2004, pp. 269–272.

[47] S. J. Rhee, Y. H. Kim, C. Y. Kang, C. S. Kang, H.-J. Cho, R. Choi, C. H. Choi, M. S. Akbar, and J. C. Lee, “Dynamic positive bias temperature instability characteristics of ultrathin HfO NMOSFET,” in *Proc. IRPS*, 2004, pp. 269–272.

[48] C. Hu, S. C. Tam, F. C. Hsu, P. K. Ko, T. Y. Chan, and K. W. Terrill, “Hot-electron-induced MOSFET degradation model, monitor, and improvement,” *IEEE J. Solid-State Circuits*, vol. SC-20, p. 295, 1985.

[49] D. J. DiMaria and J. W. Stasiak, “Trap creation in silicon dioxide produced by hot electrons,” *J. Appl. Phys.*, vol. 65, p. 2342, 1989.

[50] P. Heremans, R. Bellens, G. Groeseneken, and H. E. Maes, “Consistent model for the hot-carrier degradation in n-channel and p-channel MOSFET’s,” *IEEE Trans. Electron Devices*, vol. 35, p. 2194, 1988.

[51] F. Matsuoka, H. Iwai, H. Hayashida, K. Hama, Y. Toyoshima, and K. Maeguchi, “Analysis of hot-carrier-induced degradation mode on pMOSFET’s,” *IEEE*

*Trans. Electron Devices*, vol. 37, p. 1487, 1990.

[52] J. F. Zhang, S. Taylor, and W. Eccleston, “Electron trap generation in thermally grown SiO<sub>2</sub> under Fowler–Nordheim stress,” *J. Appl. Phys.*, vol. 71, p. 725, 1992.

[53] B. E. Deal, M. Sklar, A. S. Grove, and E. H. Snow, “Characteristics of the surface-state charge (Q<sub>ss</sub>) of thermally oxidized silicon,” *J. Electrochem. Soc.*, vol. 114, p. 266, 1967.

[54] D. J. Breed, “Non-ionic room temperature instabilities in MOS devices,” *Solid-State Electron.*, vol. 17, p. 1229, 1974.

[55] B. E. Deal, M. Sklar, A. S. Grove, and E. H. Snow, “Characteristics of the surface-state charge (Q<sub>ss</sub>) of thermally oxidized silicon,” *J. Electrochem. Soc.*, vol. 114, p. 266, 1967.

[56] A. Goetzberger, A. D. Lopez, and R. J. Strain, “On the formation of surface states during stress aging of thermal Si-SiO<sub>2</sub> interfaces,” *J. Electrochem. Soc.*, vol. 120, p. 90, 1973.

[57] D. J. Breed, “Non-ionic room temperature instabilities in MOS devices,” *Solid-State Electron.*, vol. 17, p. 1229, 1974.

[58] C. E. Blat, E. H. Nicollian, and E. H. Poindexter, “Mechanism of negative-bias-temperature instability,” *J. Appl. Phys.*, vol. 69, p. 1712, 1991.

[59] Zhang, J.F., Eccleston, W., “Positive bias temperature instability in MOSFETs,” *IEEE Trans. Electron Devices*, vol. 45, Issue 1, Jan. 1998 Page(s):116 - 124

[60] B. E. Deal, J. Electrochem. Soc. 121, 198C (1974)

[61] A. Goetzberger, A. D. Lopez, and R. J. Strain, J. Electrochem. Soc. 120, 90 (1973)

[62] N. Kimizuka, T. Yamamoto, T. Mogami, K. Yamaguchi, K. Imai, and T. Horiuchi, “The impact of bias temperature instability for direct-tunneling

ultra-thin gate oxide on MOSFET scaling”, in *Symp. VLSI Tech. Dig.*, pp.73-74, 1999.

[63] S. Ogawa, M. Shimaya, and N. Shiono, “Interface trap generation at ultrathin  $\text{SiO}_2$ (4-6nm) interfaces during negative-bias temperature aging”, *J. Appl. Phys.*, vol.77, pp.1137-1148, 1995.

# Chapter 2

## Characteristics of Low Temperature Poly-Si TFTs Using a Bi-layer Poly-Si channel

### 2.1 Introduction

In recent years, polycrystalline silicon thin-film transistors (poly-Si TFTs) have been used to realize the integration of driving circuits and pixel switching elements on a single glass substrate in active matrix liquid crystal displays (AMLCDs) [1]-[3], and also attracted much attention for the potential to accomplish the System-on-Panel (SOP) [4]. Both high-performance and high-reliability poly-Si TFTs are required to accomplish this goal. However, it is known that trap states in poly-Si channel lead to lower carrier mobility and higher off-state leakage current. As a result, it is need for the number of trap states to be as low as possible. For example, Solid-Phase-Crystallization (SPC) [5]-[9] and Excimer Laser Annealing (ELA) [10]-[13] has been utilized in enlarging the grain size of the poly-Si to reduce trap states, leading to an excellent device performance.

It was found that with the increasing concentration of oxygen in the amorphous Si (a-Si) layer, the re-crystallization mechanism in it would be suppressed [14]. With the use of an optimized condition to form an oxygen-rich a-Si film before the deposition of the a-Si layer, we could derive larger grain size and less grain boundaries in poly-Si channel after SPC.

In this chapter, we used the method mentioned above to form the poly-Si channel to enlarge the grains, combing with the use of anneal with oxygen ambient

after the deposition of gate oxide to mend the defects in it. It was found that our devices have better electrical characteristics and stress immunization from Hot-Carrier Stress (HCS) than conventional poly-Si TFTs. We enhanced the transform characteristics in higher driving current and field effect mobility, and less leakage current, leading to a higher ON/OFF ratio, and also better reliability. We will make a detail discussion in the following sections.

## 2.2 Device Fabrication

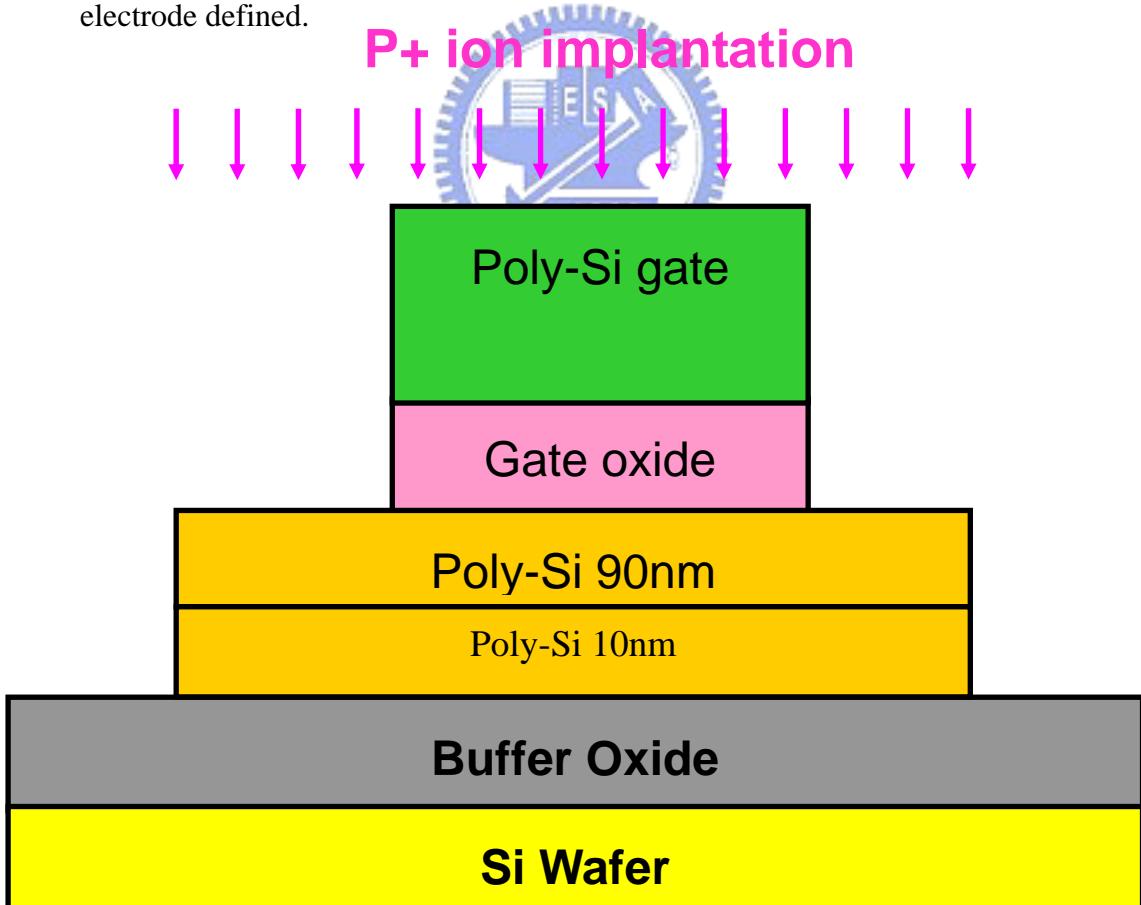

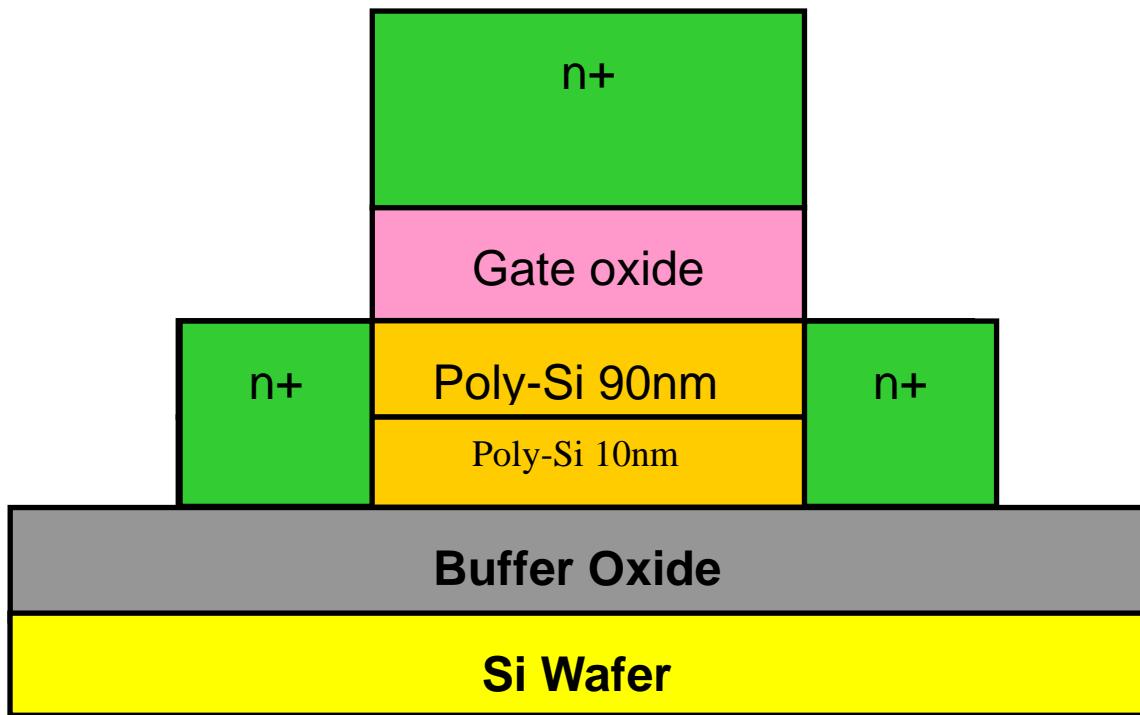

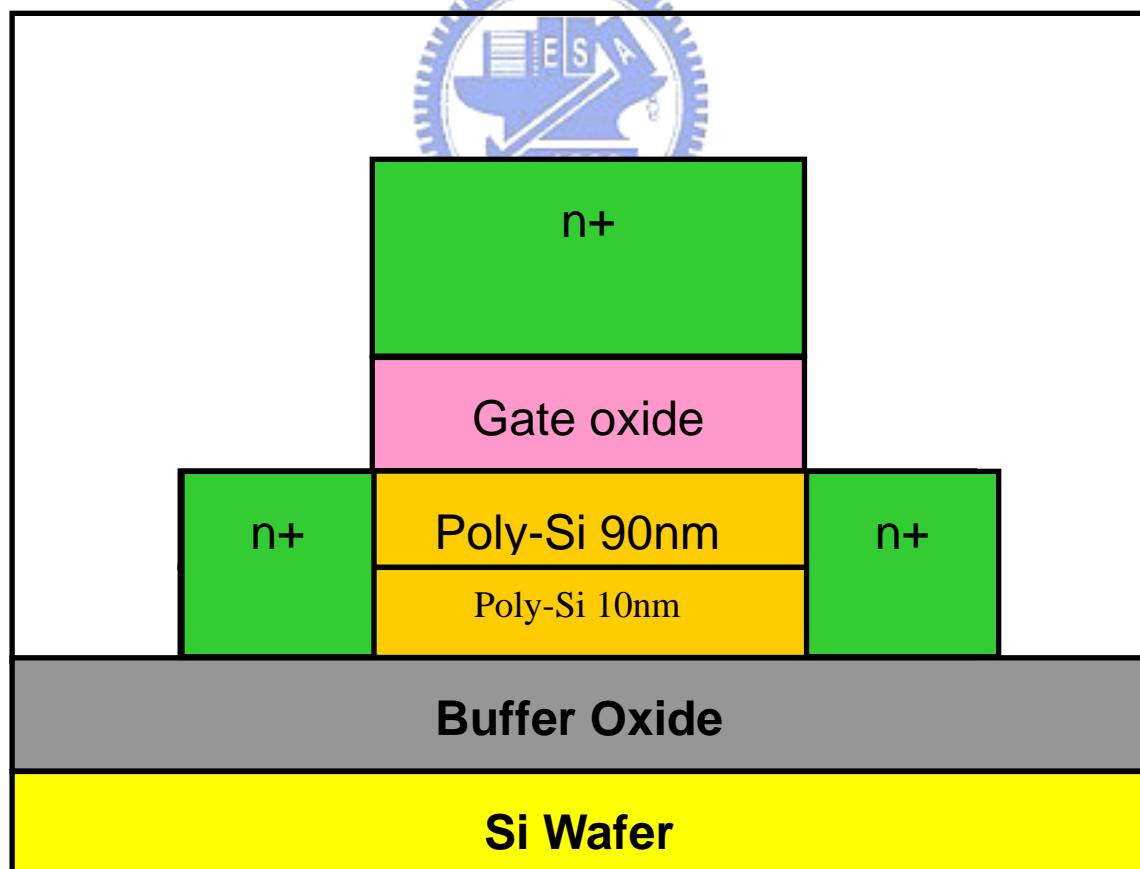

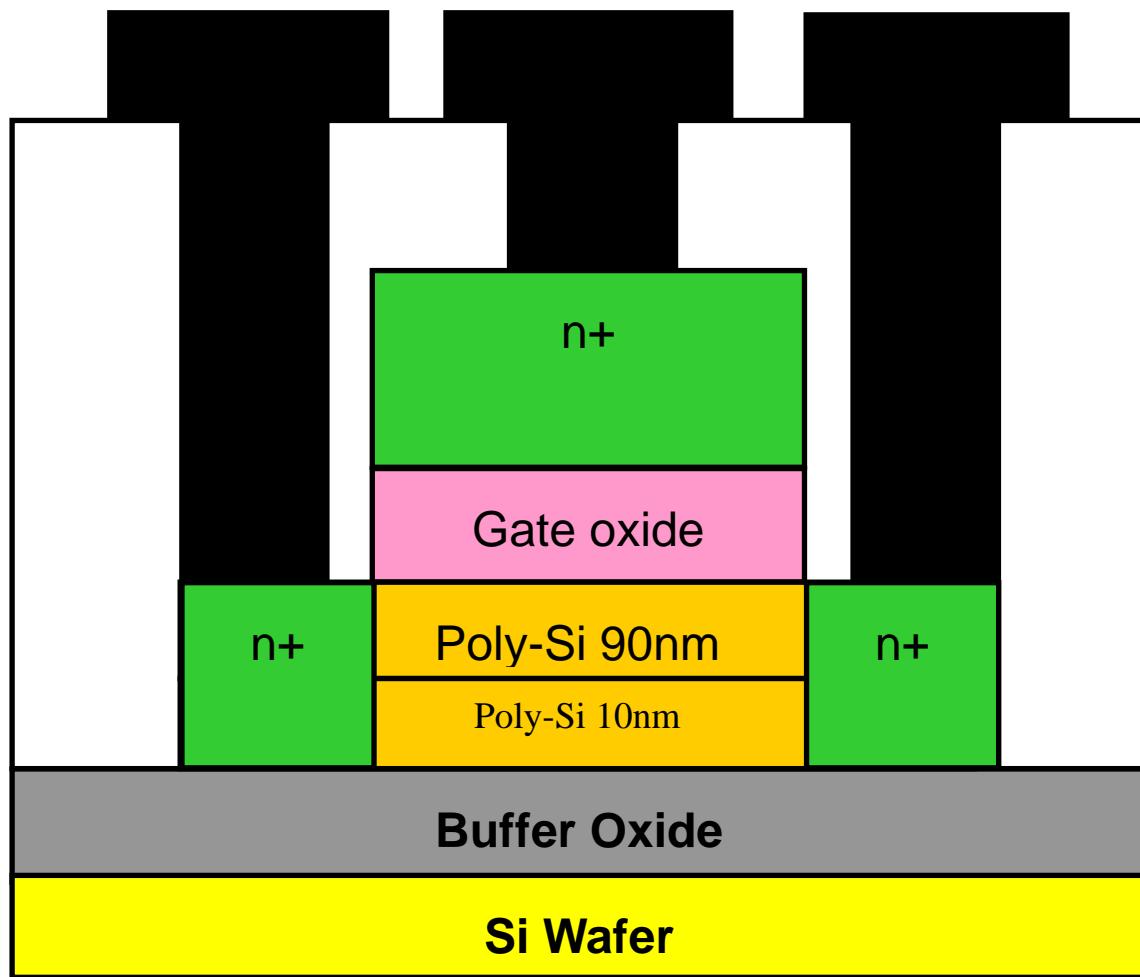

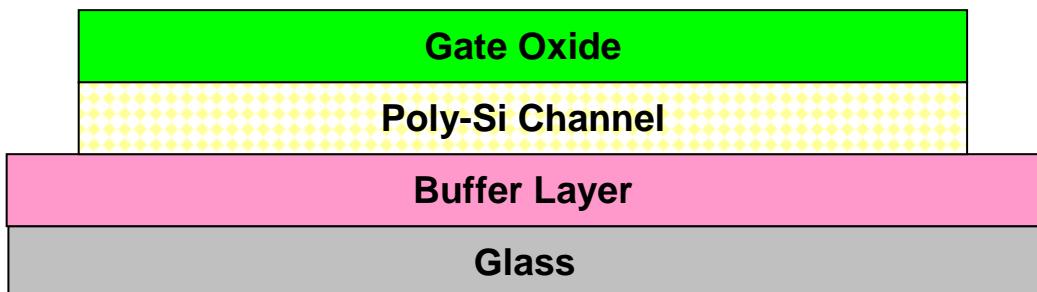

Fig 2-1 schematically depicts the process flow and the cross-sectional view of the proposed n-channel poly-Si TFTs. First, a 550nm-thick thermal oxide layer was grown on the 6-in Si wafer with a furnace system. All the experimental devices in this study were fabricated on thermally oxidized Si wafers. Then, 100-nm amorphous Si layer was deposited on the thermally oxidized wafers as the control one and two, denoted as C1 and C2 later, with a low-pressure chemical vapor deposition (LPCVD) system at 550 °C and 100 mTorr in pressure, while the other one, denoted as Bi-layer later, deposited a 10-nm amorphous Si layer as the buffer layer under 500 °C and 15 mTorr before a 90-nm amorphous Si deposited under the environment as the controls without venting the system. Then, we checked the thicknesses of them respectively with n&k system to make sure they had almost the same thickness. Then, we used solid-phase-crystallization (SPC) method to recrystallize the amorphous Si films into poly-Si ones at 600 °C for 24 hours in N<sub>2</sub> ambient. The poly-Si films were patterned into active regions by transformer couple plasma (TCP) etching system using mixture gases of Cl<sub>2</sub> and HBr.

After RCA cleaning procedure, we deposited 50-nm TEOS oxide on them by TEOS and O<sub>2</sub> gases at 695 °C with LPCVD system to form the gate insulators. After

the deposition, we annealed C2 and Bi-layer by furnace with O<sub>2</sub> ambient at 700 °C for 1hr, while no treatment was done with C1. Then 200-nm amorphous Si was deposited with LPCVD system followed by SPC at 600 °C for 24 hours to serve as the poly-Si gate electrodes. Then, the poly-Si films were patterned by TCP etching system to form the gate electrodes and the gate oxides on source/drain were removed with dilute HF solution. The regions of sources, drains, and gates were doped by a self-aligned phosphorous ion implantation at the dosage and energy of 5E15 ions/cm<sup>2</sup> and 20 KeV, respectively. The dopants were activated at 600 °C for 12 hours by furnace system, and 400-nm passivation oxide layers were deposited with plasma-enhanced CVD (PECVD) system at 300 °C. After the definition of contact holes with BOE solution, 500-nm Al layers were deposited by sputter and patterned as metal pads. Finally, we passivated them by NH<sub>3</sub> plasma treatment for 1 hour at 300 °C.

## 2.3 Methods of Device Parameter Extraction

In this thesis, all of the electrical characteristics of proposed poly-Si TFTs were measured by HP 4156B-Precision Semiconductor Parameter Analyzer.

Many methods have been proposed to extract the characteristic parameters of poly-Si TFTs. In this section, those methods are described.

### 2.3.1 Determination of Threshold Voltage

Threshold voltage (V<sub>th</sub>) is an important parameter required for the channel length-width and series resistance measurements. However, V<sub>th</sub> is not defined uniquely. Various definitions have been proposed and reasons can be found in I<sub>D</sub>-V<sub>GS</sub> curves. One of the most common techniques is the linear extrapolation method with the drain current measured as a function of gate voltage at a low drain voltage of

50~100mV to ensure operation in the linear region [15]. The drain current is not zero when  $V_{GS}$  below threshold voltage and approaches zero asymptotically. Hence the  $I_{DS}$  versus  $V_{GS}$  curve can be extrapolated to  $I_D=0$ , and the  $V_{th}$  is determined from the extrapolated intercept of gate voltage ( $V_{GSi}$ ) by

$$V_{th} = V_{GSi} - \frac{V_{DS}}{2} \quad \text{----- (Eq. 1.1)}$$

Equation (1.1) is strictly only valid for negligible series resistance. Fortunately series resistance is usually negligible at the low drain current when threshold voltage measurements are made. The  $I_{DS}$ - $V_{GS}$  curve deviates from a straight line at gate voltage below  $V_{th}$  due to subthreshold current and above  $V_{th}$  due to series resistance and mobility degradation effects. It is common practice to find the point of maximum slope of the  $I_{DS}$ - $V_{GS}$  curve and fit a straight line to extrapolate to  $I_D=0$  by means of finding the point of maximum of transconductance ( $G_m$ ).

In this thesis, we use a simpler method to determinate the  $V_{th}$  called constant drain current method. The voltage at a specified threshold drain current is taken as the  $V_{th}$ . This method is adopted in the most studied papers of poly-Si TFTs. It can be given a threshold voltage close to that obtained by the complex linear extrapolation method. Typically, the threshold current is specified at  $(W/L) \times 10\text{nA}$  for  $V_{DS}=0.1\text{V}$  and  $(W/L) \times 100\text{nA}$  for  $V_{DS}=5\text{V}$ , where  $W$  and  $L$  are channel width and channel length, respectively.

### 2.3.2 Determination of Subthreshold Swing

Subthreshold swing (S.S.) is a typical parameter to describe the control ability of gate toward channel, which reflects the turn on/off speed of a device. It is defined as the amount of gate voltage required to increase/decrease drain current by one order of magnitude.

The S.S. should be independent of drain voltage and gate voltage. However, in reality, the S.S. increases with drain voltage due to channel shortening effect such as charge sharing, avalanche multiplication and punchthrough effect. The subthreshold swing is also related to gate voltage due to undesirable and inevitable factors such as the serial resistance and interface states.

In this thesis, the S.S. is defined as one-third of the gate voltage required to decrease the threshold current by three orders of magnitude. The threshold current is specified to be the drain current when the gate voltage is equal to threshold voltage.

### 2.3.3 Determination of Field Effect Mobility

Usually, field effect mobility ( $\mu_{eff}$ ) is determined from the maximum value of transconductance (Gm) at low drain bias. The transfer characteristics of poly-Si TFTs are similar to those of conventional MOSFETs, so that the first order of I-V relation in the bulk Si MOSFETs can be applied to poly-Si TFTs. The drain current in linear region ( $V_{DS} < V_{GS} - V_{th}$ ) can be approximated as the following equation:

$$I_{DS} = \mu_{eff} C_{ox} \left( \frac{W}{L} \right) \left[ (V_{GS} - V_{th}) V_{DS} - \frac{1}{2} V_{DS}^2 \right] \quad \text{----- (Eq. 1.2)}$$

where W and L are channel width and channel length, respectively.  $C_{ox}$  is the gate oxide capacitance per unit area and  $V_{th}$  is the threshold voltage. Thus, the transconductance is given by

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}} = \mu_{eff} C_{ox} \left( \frac{W}{L} \right) V_{DS} \quad \text{----- (Eq. 1.3)}$$

Therefore, the field-effect mobility is

$$\mu_{eff} = \frac{L}{C_{ox} W V_{DS}} g_{m(\max)} \Big|_{V_{DS} \rightarrow 0} \quad \text{----- (Eq. 1.4)}$$

### 2.3.4 Determination of ON/OFF Current Ratio

On/off current ratio is one of the most important parameters of poly-Si TFTs since a high-performance device exhibits not only a large on-current but also a small off-current (leakage current). The leakage current mechanism in poly-Si TFTs is not like that in MOSFET. In MOSFET, the channel is composed of single crystalline Si and the leakage current is due to the tunneling of minority carrier from drain region to accumulation layer located in channel region. However, in poly-Si TFTs, the channel is composed of poly-Si. A large amount of trap state densities in grain structure attribute a lot of defect states in energy band gap to enhance the tunneling effect. Therefore, the leakage current is much larger in poly-Si TFTs than in MOSFET. When the voltage drops between gate voltage and drain voltage increases, the band gap width decreases and the tunneling effect becomes much more severe. Normally we can find this effect in typical poly-Si TFTs'  $I_{DS}$ - $V_{GS}$  characteristics where the magnitude of leakage current will reach a minimum and then increase as the gate voltage decreases/increases for n/p-channel TFTs.

There are a lot of ways to specify the on and off-current. In this chapter, take n-channel poly-Si TFTs for examples, the on-current is defined as the drain current when gate voltage at the maximum value and drain voltage is 5V. The off-current is specified as the minimum current when drain voltage equals to 5V.

$$\frac{I_{ON}}{I_{OFF}} = \frac{\text{Maximum Current of } I_{DS} - V_{GS} \text{ Plot at } V_{DS} = 5V}{\text{Minimum Current of } I_{DS} - V_{GS} \text{ Plot at } V_{DS} = 5V} \quad \text{----- (Eq. 1.5)}$$

### 2.3.5 Extraction of Grain Boundary Trap State Density

The Trap State Density ( $N_t$ ), which can be determined by the theory established by Levinson *et al.* [16], which is based on Seto's theory [17].

For poly-Si TFTs, the drain current  $I_{DS}$  can be given as following:

$$I_{DS} = \mu_{FE} C_{ox} \left( \frac{W}{L} \right) V_{DS} V_{GS} \exp \left( \frac{-q^3 N_t^2 L_c}{8\epsilon_{Si} k T C_{ox} V_{GS}} \right) \quad \text{----- (Eq. 1.6)}$$

Where,

$\mu_{eff}$  field-effect mobility of carriers

q electron charge

k Boltzmann's constant

$\epsilon_{Si}$  dielectric constant of silicon

T temperature

$N_t$  trap-state density per unit area

$L_c$  channel thickness

This expression, first developed by Levinson *et al.*, is a standard MOSFET's equation with an activated mobility, which depends on the grain-boundary barrier height. Levinson *et al.* assumed that the channel thickness was constant and equal to the thickness of the poly-Si film (t). This simplifying assumption is permissible only for very thin film ( $t < 10\text{nm}$ ). The trap-state density can be obtained by extracting a straight line on the plot of  $\ln(I_{DS}/V_{GS})$  versus  $1/V_{GS}$  at low drain voltage and high gate voltage.

Proano *et al.* [18] thought that a barrier approximation is to calculate the gate induced carrier channel thickness by solving Poisson's equation for an undoped material and to define the channel thickness ( $L_c$ ) as a thickness in which 80% of the total charges were induced by the gate. Doing so, one obtains

$$L_c = \frac{8kTt_{ox} \sqrt{\frac{\epsilon_{Si}}{\epsilon_{SiO_2}}}}{q(V_{GS} - V_{fb})} \quad \text{----- (Eq. 1.7)}$$

which varies inversely with  $(V_{GS} - V_{fb})$ . This predicts, by substituting Eq.2.7 into Eq.1.6, that  $\ln[I_{DS}/(V_{GS} - V_{fb})]$  versus  $1/(V_{GS} - V_{fb})^2$ . We use the gate voltage at which

minimum leakage current occurs as flat-band voltage ( $V_{fb}$ ). Effective trap-state density ( $N_t$ ) can be determined from the square root of the slope.

## 2.4 Results and Discussion

### 2.4.1 Characteristics of poly-Si TFTs with post anneal after gate oxide deposition

Figure 2-2 shows the transfer characteristics ( $I_{DS}$ - $V_{GS}$ ) of the conventional poly-Si TFT and the poly-Si TFT which was annealed after gate oxide deposition. The measurements was performed at drain voltage of  $V_{DS}=5V$ . The measured and extracted parameters from the devices are listed in Table 2-1. The on-current (at  $V_{GS}=15V$ ), and off-current (at  $V_{GS}=-10V$ ) were measured at  $V_{DS}=5V$ , while the threshold voltage and the subthreshold swing were derived from the transfer characteristics at  $V_{DS}=0.1V$ .

In Fig. 2-2, we can see that the poly-Si TFTs with an anneal procedure exhibit better on-state and off-state characteristics than those of the conventional sample. Notably, the annealed poly-Si TFT has higher ON-state current and lower OFF-state leakage current, leading to larger ON/OFF current ratio. Moreover, the annealed poly-Si TFT also has smaller threshold voltage, smaller subthreshold swing, and larger field effect mobility than the conventional poly-Si TFT. From Fig. 2-3, we found that the poly-Si TFT with annealed gate oxide has much better reliability than the conventional poly-Si TFT under high stressed gate voltages at high temperature. From these significant improvements mentioned above, we found that the quality of the gate oxide has been mended after anneal. In order to exclude the influence of the oxide quality in our study, we used the same anneal procedure in our fabrication process of control sample and our proposed sample, Bi-layer.

## 2.4.2 Characteristics of Poly-Si TFTs with Bi-layer Poly-Si Channels

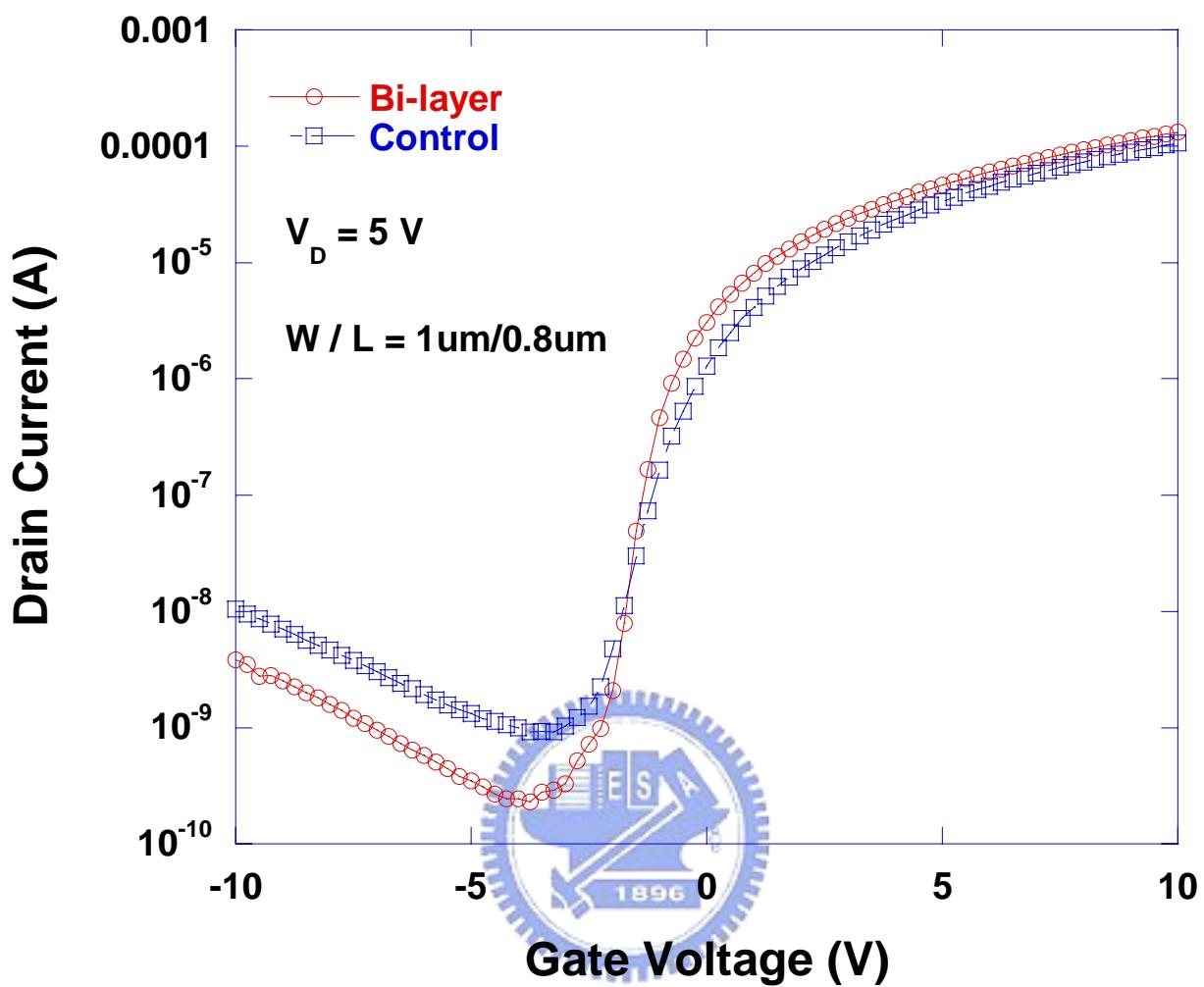

Fig. 2-4(a) shows the transfer characteristics ( $I_{DS}$ - $V_{GS}$ ) of the annealed conventional poly-Si TFT, Control, and the proposed bi-layer poly-Si TFTs, Bi-layer. The measurements was performed at drain voltage of  $V_{DS}=5V$ . The on-current (at  $V_{GS}=15V$ ), and off-current (at  $V_{GS}=-10V$ ) were measured at  $V_{DS}=5V$ , while the threshold voltage and the subthreshold swing were derived from the transfer characteristics at  $V_{DS}=0.1V$ .

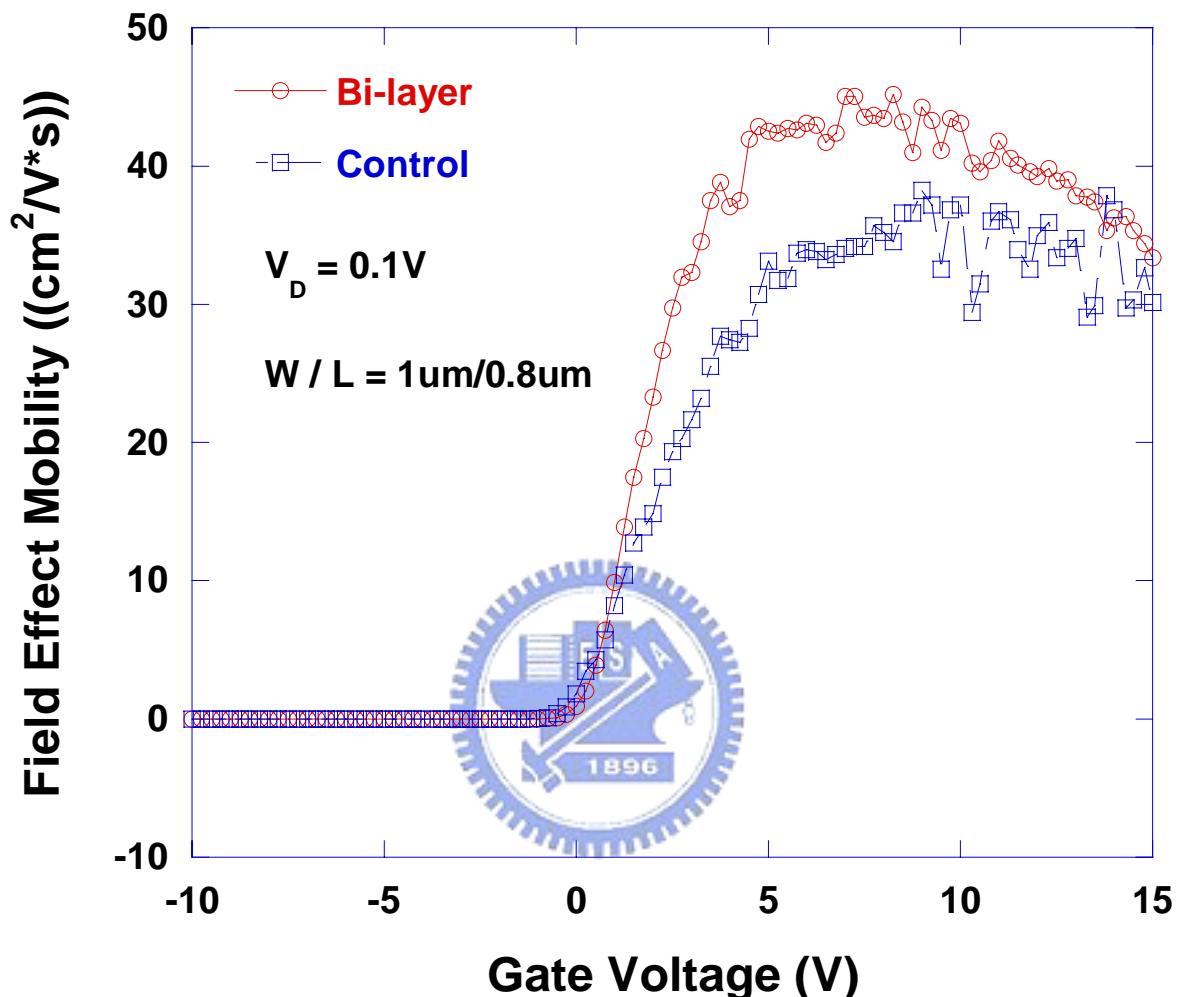

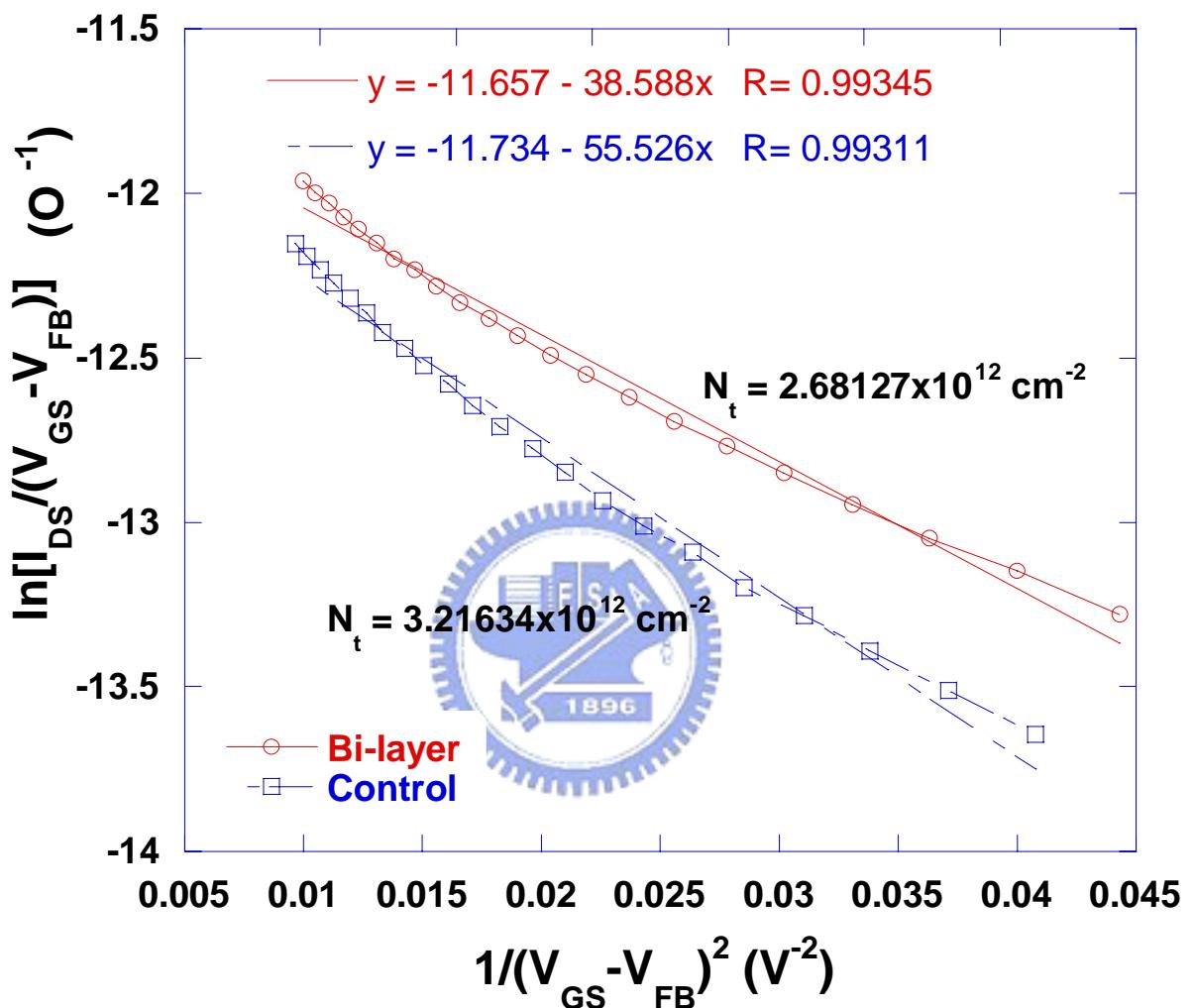

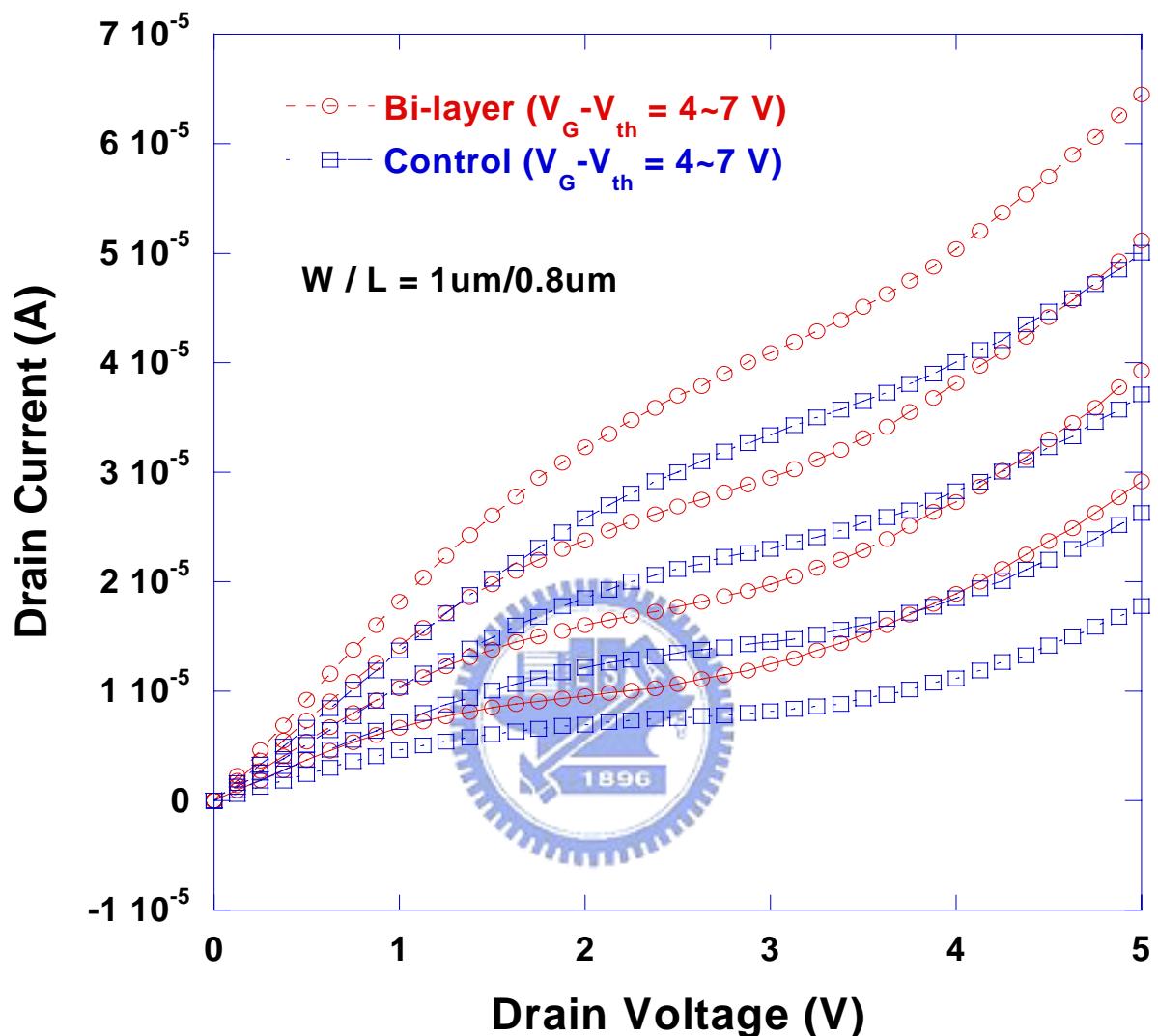

From Fig. 2-4(a), we can see that Bi-layer exhibit better ON-state characteristics than the control sample. In OFF-state, under a large negative gate bias, the leakage current of Bi-layer ( $3.84 \times 10^{-9} A$ ) is significant lower than that of the control sample ( $1.05 \times 10^{-8} A$ ). It was obvious that the gate induced grain leakage (GIDL) was suppressed in Bi-layer. Moreover, the threshold voltage and subthreshold swing of Bi-layer (0.26V & 0.71V/dec.) was found to be superior to the control sample (0.48V & 1.05V/dec.). In Fig. 2-4(b), we compared the field effect mobility between these two samples, the proposed poly-Si TFTs Bi-layer shows obvious enhancement in mobility compared with the conventional TFT from  $38 (\text{cm}^2/\text{Vs})$  to  $45 (\text{cm}^2/\text{Vs})$ . The mobility of Bi-layer has been enhanced by 18.4%. Fig. 2-5 shows the plot of  $\ln[I_{DS}/(V_{GS}-V_{fb})]$  versus  $1/(V_{GS}-V_{fb})^2$  at low drain voltage and high gate voltage for Control and Bi-layer. The effective trap state density calculated from the slopes for Control and Bi-layer were  $3.22 \times 10^{12}$  and  $2.68 \times 10^{12} \text{ cm}^{-2}$ , respectively. Bi-layer has less trap state density than that of Control, and we deduced that Bi-layer has less grain boundary trap states than Control. Fig. 2-6 shows the output characteristics of the control and the proposed poly-Si TFTs. We can see that the driving current of the proposed poly-Si TFTs has been significantly enhanced. The measured and extracted parameters from the devices are listed in Table 2-2.

### 2.4.3 Reliability of Poly-Si TFTs with Bi-layer Poly-Si Channels

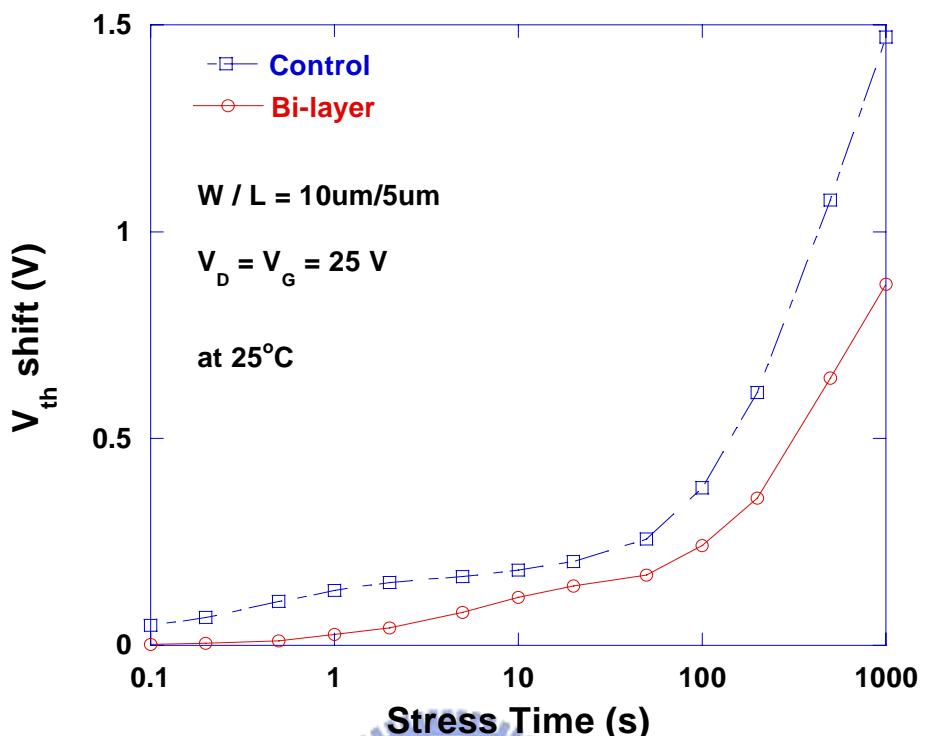

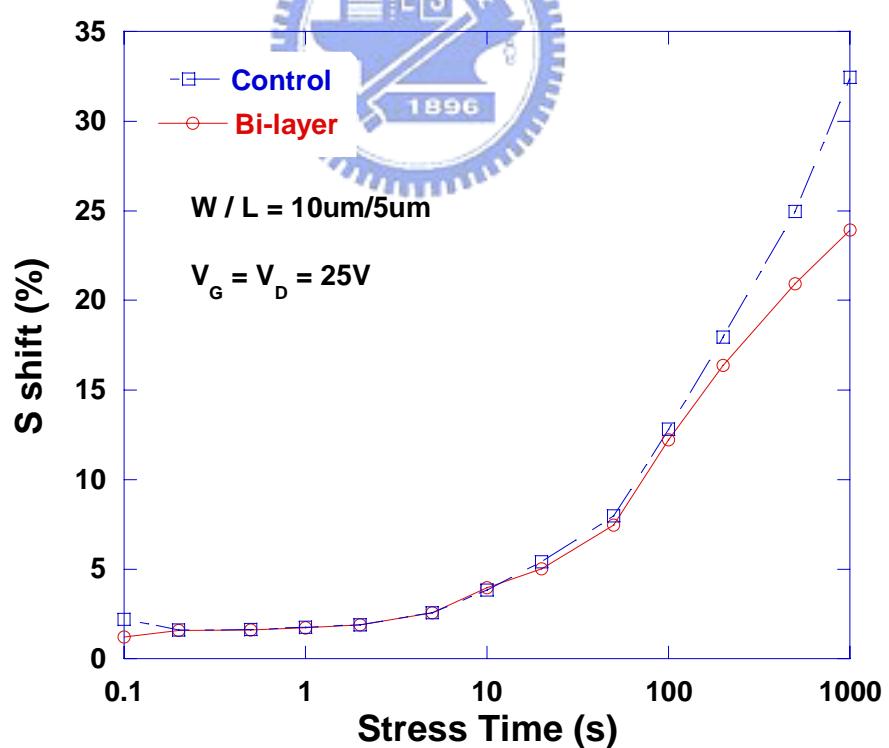

Furthermore, we discussed the reliability of the proposed TFTs and conventional TFTs. In Fig. 2-7, we applied DC stress to the devices with channel length and width equal to  $5 \mu\text{m}$  and  $10 \mu\text{m}$ , respectively. The hot-carrier stress (HCS) test was performed at  $V_G = V_D = 25\text{V}$  while  $V_S = 0\text{V}$  under  $25^\circ\text{C}$  for 1000 seconds to investigate the device reliability. Fig. 2-7 (a) shows the shift of their threshold voltages while Fig. 2-8 (b) shows the variation of their subthreshold swings under the HCS test. The shift of threshold voltage was defined as  $V_{\text{th,stressed}} - V_{\text{th,initial}}$  and the variation of subthreshold swing was defined as  $100\% * (S_{\text{stressed}} - S_{\text{initial}}) / S_{\text{initial}}$ , where  $V_{\text{th,stressed}}$  and  $V_{\text{th,initial}}$  represent the threshold voltage after and before stress, respectively while  $S_{\text{stressed}}$  and  $S_{\text{initial}}$  represent the subthreshold swing shift after and before stress, respectively.

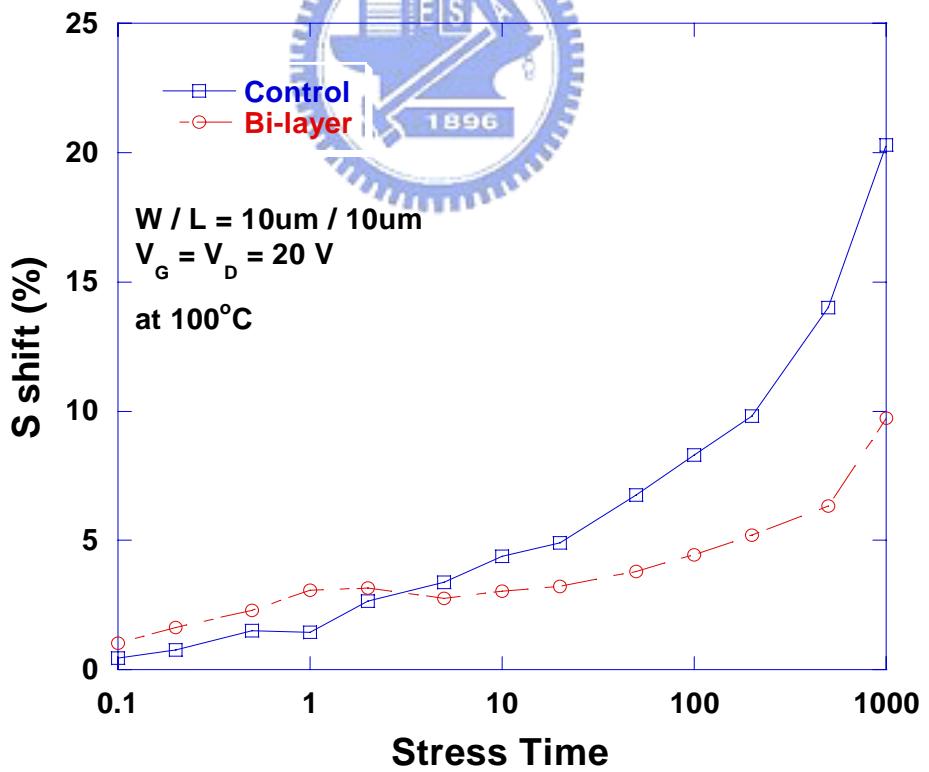

Moreover, we applied DC stress to the devices with channel length and width equal to  $10 \mu\text{m}$  and  $10 \mu\text{m}$ , respectively. The Hot-Carrier Stress test was performed at  $V_G = V_D = 20\text{V}$  while  $V_S = 0\text{V}$  under  $100^\circ\text{C}$  for 1000 seconds to investigate the device reliability under high temperature use. The variation of their threshold voltages and subthreshold swings of them are shown in Fig. 2-8, the same definition as in Fig. 2-7 was used.

From Fig. 2-7 and Fig. 2-8, we found that the proposed TFT shows suppression in device degradation owing to HCS not only at room temperature but also at high temperature, indicating that it has much better reliability than conventional TFTs.

## 2.5 Summary

We used an anneal procedure after gate oxide deposition to improve the transfer characteristics and reliability of poly-Si TFTs. With the deposition of a buffer a-Si layer under low-temperature and low-pressure condition, we fabricated high-performance poly-Si TFTs with enhanced reliability. The characteristics of the

proposed TFTs have great improvement, such as higher On-state current, higher field effect mobility, lower subthreshold swing, suppressed GIDL current, and better reliability. With an optimized deposition condition of the buffer a-Si layer, the proposed TFTs would be candidates in high performance TFTs application.

## References:

[1] Y. Oana, "Current and future technology of low-temperature poly-Si TFT-LCDs," *Journal of the SID*, vol. 9, pp. 169-172, 2001.

[2] S. Morozumi, K. Oguchi, S. Yazawa, Y. Kodaira, H. Ohshima, and T. Mano, "B/W and color LC video display addressed by poly-Si TFTs," *SID Dig.*, pp.156, 1983.

[3] R. E. Proano, R. S. Misage, D. Jones, and D. G. Ast, "Guest-host active matrix liquid-crystal display using high-voltage polysilicon thin film transistors," *IEEE Trans. Electron Devices*, vol. 38, pp. 1781, 1991.

[4] K. Werner, "The flowering of flat displays," *IEEE Spectrum*, vol. 34, pp. 40–49, May 1997.

[5] A. Nakamura, F. Emoto, E. Fujii and A. Tamamoto, "A high-reliability, low-operation-voltage monolithic active-matrix LCD by using advanced solid-phase growth technique," in *IEDM Tech. Dig.*, pp.847, 1990.

[6] R. B. Iverson and R. Reif, "Recrys tallization of amorphized polycrystalline silicon films on SiO<sub>2</sub>: temperature dependence of the crystallization parameters," *J. Appl. Phys.*, vol. 62, no. 5, pp. 1675-1681, 1987.

[7] R. B. Iverson and R. Reif, "Stochastic model for grain size versus dose in implanted and annealed polycrystalline silicon films on SiO<sub>2</sub>," *J. Appl. Phys.*, vol. 57, p. 5169, 1985.

[8] T. Noguchi, H. Hayashi, and T. Ohshima, "Advanced superthin polysilicon film obtained by Si<sup>+</sup> implantation and subsequent annealing," *J. Electrochem. Soc.*, vol. 134, p. 1771, 1987.

[9] M. K. Hatalis and D. W. Greve, "Large grain polycrystalline silicon by low-temperature annealing of low-pressure chemical vapor deposited amorphous silicon films," *J. Appl. Phys.*, vol. 63, p. 2260, 1988.

[10] N. Kudo, N. Kusumoto, T. Inushima, and S. Yamazaki, “Characterization of polycrystalline-Si thin-film transistors fabricated by excimer laser annealing method,” *IEEE Trans. Electron Devices*, vol. 41, no. 10, pp. 1876-1879, 1994.

[11] T. Sameshima, S. Usui and M. Sekiya, “XeCl excimer laser annealing used in the fabrication of poly-Si TFT’s,” *IEEE Electron Device Lett.*, vol. 7, no. 5, pp. 276-278, 1986.

[12] D. H. Choi, E. Sadauyki, O. Sugiura and M. Matsumura, “Excimer-laser crystallized poly-Si TFT’s with mobility more than 600 cm<sup>2</sup>/V.s,” *IEEE Trans. Electron Devices*, vol. 40, no. 11, pp. 2129, 1993.

[13] Noguchi, T., Tang, A.J., Tsai, J.A., Reif, R., “Comparison of effects between large-area-beam ELA and SPC on TFT characteristics,” *Electron Devices, IEEE Transactions*, Vol 43, Issue 9, pp.1454 – 1458, 1996

[14] M. K. Ryu, J. Y. Kwon, and K. B. Kim, “SOLID PHASE CRYSTALLIZATION (SPC) BEHAVIOR OF AMORPHOUS Si BILAYER FILMS WITH DIFFERENT CONCENTRATION<sub>96</sub> OF OXYGEN: *Surface vs. Interface-nucleation*,” *Mat. Res. Soc. Symp. Proc.* Vol. 621, 2000.

[15] Dieter K. Schroder, “Semiconductor Material and Device Characterization,” *Wiley-INTERSCIENCE*, 1998

[16] J. Levinson, G. Este, M. Rider, P. J. Scanlon, F. R. Shepherd, and W. D. Westwood, “Conductivity behavior in polycrystalline semiconductor thin film transistors,” *J. Appl. Phys.*, vol. 53, no. 2, pp. 193, 1982

[17] J. Y. W. Seto, “The electrical properties of polycrystalline silicon films,” *J. Appl. Phys.*, vol. 46, no. 12, pp. 5247, 1975

[18] R. E. Proano, R. S. Misage, D. Jones, and D. G. Ast, “Development and electrical properties of undoped polycrystalline silicon thin film transistors,” *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1915, 1989.

**Buffer Oxide**

**Si Wafer**

(a) Thermal oxidation grown by furnace.

a-Si (~90nm)

a-Si (~10nm)

**Buffer Oxide**

**Si Wafer**

(b) Bi-layer amorphous Si (a-Si) deposited by LPCVD.

Poly-Si 90nm

Poly-Si 10nm

**Buffer Oxide**

**Si Wafer**

(c) Recrystallization of a-Si film into poly-Si channel by SPC, followed by active region definition.

(d) Deposition of TEOS gate oxide by LPCVD and poly-Si gate by LPCVD, gate electrode defined.

(e) Self-aligned phosphorous ion implantation.

(f) Dopants activated by furnace.

(g) Deposition of passivation oxide by PECVD.

(h) Contact holes opened and metal pads formation.

Fig. 2-1 Schematic diagram of fabrication process for bi-layer poly-Si TFTs.

Table 2-1 Comparison of device characteristics of the poly-Si TFTs with and without an anneal procedure after the gate oxide deposition (W/L=10um/1um).

|                                            | Without Anneal                          | With Anneal                             |

|--------------------------------------------|-----------------------------------------|-----------------------------------------|

| $V_{th}$ (V)                               | <b>4.02</b>                             | <b>1.76</b>                             |

| $S$ . (V/dec.)                             | <b>1.07</b>                             | <b>0.90</b>                             |

| $\mu_{FE}$ (cm <sup>2</sup> /V*s)          | <b>19.8</b>                             | <b>22.5</b>                             |

| $I_{on}$ @ $V_G$ =10 V,<br>$V_D$ = 5 V (A) | <b><math>7.72 \times 10^{-4}</math></b> | <b><math>8.71 \times 10^{-4}</math></b> |

| $I_{off}$ @ $V_G$ =-10V,<br>$V_D$ = 5V (A) | <b><math>6.92 \times 10^{-9}</math></b> | <b><math>2.58 \times 10^{-9}</math></b> |

| $I_{on}/I_{off}$                           | <b><math>1.12 \times 10^5</math></b>    | <b><math>3.38 \times 10^5</math></b>    |

| $N_t$ (cm <sup>-2</sup> )                  | <b><math>7.31 \times 10^{12}</math></b> | <b><math>3.47 \times 10^{12}</math></b> |

Fig. 2-3(a) Threshold voltage ( $V_{th}$ ) shift versus stress time of n-TFTs with and without gate oxide anneal under static gate bias  $V_G = -20\text{V}$  while S/D were grounded at  $100^\circ\text{C}$ .

Fig. 2-3(b) Threshold voltage ( $V_{th}$ ) shift versus stress time of n-TFTs with and without gate oxide anneal under static gate bias  $V_G=20\text{V}$  while S/D were grounded at  $100^\circ\text{C}$ .

Fig. 2-4(a) Transfer characteristics of the Control and the Bi-layer poly-Si TFTs with  $V_{DS}=5\text{V}$ .

Fig. 2-4(b) Field effect mobility of the Control and the Bi-layer poly-Si TFTs with  $V_{DS}=0.1\text{ V}$ .

Fig. 2-5 Trap state density extraction of the Control and the Bi-layer poly-Si TFTs.

Fig. 2-6 Output characteristic of the Control and the Bi-layer poly-Si TFTs.

Table 2-2 Comparison of device characteristics of the Control and the Bi-layer poly-Si TFTs.

|                                                    | Control               | Bi-layer              |

|----------------------------------------------------|-----------------------|-----------------------|

| $V_{th}$ (V)                                       | 0.48                  | 0.26                  |

| $S$ (V/dec.)                                       | 1.05                  | 0.71                  |

| $\mu_{FE}$ ( $\text{cm}^2/\text{V}\cdot\text{s}$ ) | 38                    | 45                    |

| $I_{on}$ @ $V_G=10$ V,<br>$V_D=5$ V (A)            | $1.07 \times 10^{-4}$ | $1.33 \times 10^{-4}$ |

| $I_{off}$ @ $V_G=-10$ V,<br>$V_D = 5$ V (A)        | $1.05 \times 10^{-8}$ | $3.84 \times 10^{-9}$ |

| $I_{on}/I_{off}$                                   | $1.02 \times 10^4$    | $3.46 \times 10^4$    |

| $N_t$ ( $\text{cm}^{-2}$ )                         | $3.22 \times 10^{12}$ | $2.68 \times 10^{12}$ |

(a) Threshold voltage degradation versus the stress time

(b) Subthreshold swing degradation versus stress time

Fig. 2-7 (a) Threshold voltage and (b) subthreshold swing degradation versus the stress time under hot-carrier stress at room temperature

(a) Threshold voltage degradation versus stress time

(b) Subthreshold swing degradation versus stress time

Fig. 2-8 (a) Threshold voltage and (b) subthreshold swing degradation versus the stress time under hot-carrier stress at  $100^\circ\text{C}$ .

# Chapter 3

## Degradation Mechanisms of NBTI and PBTI in Low-Temperature Poly-Si Thin-Film Transistors

### 3.1 Introduction

Recently, low temperature polycrystalline silicon thin-film transistors (LTPS TFTs) have attracted much attention due to the high potential of realizing system on panel (SOP) [1], the possibility of realizing the integration of peripheral circuit, and applications in active matrix liquid crystal displays (AMLCDs)[2][3]. Inevitably, the stability of poly-Si TFTs is of significant importance from the fabrication technology point of view and as a long-term reliability concern [2]. In p-channel MOSFETs, negative bias temperature instability (NBTI) has been found to be an important reliability concern [3][4][5], while positive bias temperature instability (PBTI) been found to be an important problem to n-channel MOSFETs. Both the influences of NBTI to p-channel MOSFETs and PBTI to n-channel MOSFETs have been widely investigated. It was found that the degradation mechanisms for NBTI and PBTI were quite different. The degradation due to NBTI is mainly responsible for the generation of interface states and fixed oxide charge, as a result, NBTI could be thermally and electrically activated by elevated stress temperature and voltage [6]. Unlike NBTI, n-channel MOSFETs with high- $k$  gate insulators have attracted much attention. PBTI only exist in the formation of donor-like interface states and charge de-trapping from the gate insulators [7].

In LTPS TFTs, due to the poor thermal conductivity of the glass substrates and high operation voltages, we supposed NBTI and PBTI would be important in the

reliability of LTPS TFTs. Additionally, the LTPS TFT driving circuit is designed using the CMOSFET structure, we speculate that the effects of NBTI and PBTI will degrade the reliability of p-channel and n-channel TFTs, respectively. Some researches have pointed out BTI stress caused the performance degradation in poly-Si TFTs as well as in MOSFETs [8]. Moreover, the degradation mechanism of BTI stress in poly-Si TFTs, due to the grain boundaries in the channel region, may be different from MOSFETs. Some studies have indicated that BTI stress on poly-Si TFTs may generate trap states in the grain boundaries [9]. However, the effects of NBTI and PBTI on the reliability of LTPS TFTs have not been explored.

In this chapter, the reliability of the LTPS TFTs was studied by applying NBTI and PBTI stress on TFTs. The NBTI stress was applied to the p-channel LTPS TFTs, while the PBTI stress was applied to the n-channel LTPS TFTs. By varying the stress voltages and temperatures, the basic devices parameters were extracted and analyzed to explain the degradation mechanisms.

## 3.2 Experimental

The p- and n-channel LTPS TFTs were fabricated on glass substrates. A 40nm-thick amorphous-Si layer was first deposited by PECVD on a buffer layer and crystallized into poly-Si film by excimer laser annealing. For the p-channel TFTs, the gate dielectric was deposited with an equivalent 100nm-thick  $\text{SiO}_2$  layer after defining the active region. Mo was then deposited and patterned as the gate electrode. Self-align source/drain was formed by plasma doping. Fig. 3-1 shows the schematic diagram of fabrication process. For the n-channel devices, the source and drain were first formed after defining the active region. The gate dielectric and metal film were deposited and patterned as the gate electrode. Following that, self-aligned

lightly-doped source and drain were formed. Then, the inter-layer dielectric was deposited on all the devices and densified. The dopants were activated during the densification of the inter-layer dielectric. Finally, inter-connection metal was deposited and patterned. The channel length (L) and channel width (W) of the device used in this study were 10 and 20  $\mu\text{m}$ , respectively.

During NBTI stress, the glass substrate was heated to the stress temperature ranging from 25 to 150°C, and the stress voltage in the range of -15 to -30 V was applied to the gate with the source/drain grounded. The schematic cross-section diagrams of the LTPS TFTs and stress setup is shown in Fig. 3-2. The stress was periodically stopped to measure the basic characteristics of the device to characterize the NBTI effect. All the measurements were taken at the stress temperature. Fowler-Nordheim current was not pronounced at these bias conditions; therefore, the extra trap state generation and device instability caused by the small current can be neglected.

### 3.3 Results and Discussion

Fig. 3-3(a) and 3-3(b) show the influence of NBTI and PBTI stress on the transfer characteristics of the p- and n-channel TFTs, respectively. In both case, the absolute values of threshold voltages ( $|V_{th}|$ ) increase after NBTI or PBTI stress. The subthreshold swing (S) degrades after NBTI stress for p-channel TFT, while it remains almost unchanged after PBTI stress for n-channel TFT. This indicates that NBTI stress generate more interface trap states in the device. Besides, the field-effect mobility ( $\mu_{FE}$ ) is found to decrease under NBTI stress; however, it is worth noting that the  $\mu_{FE}$  increases after PBTI stress.

Fig. 3-4(a) and 3-4(b) show the time dependence of the threshold voltage shift ( $\Delta V_{th}$ ) of the p- and n-channel TFTs, respectively. The stress was performed at 150°C

with various stress gate voltages. In our study, the gate voltage at a specified threshold drain current ( $I_{DS}$ ),  $\pm (W/L) \times 10$  nA for  $V_{DS} = \pm 0.1$  V, is taken as the threshold voltage. In both cases, the  $|\Delta V_{th}|$  increases as the absolute value of the stress gate voltage increases, indicating that both NBTI and PBTI can be electrically activated. Besides, the  $|\Delta V_{th}|$  shows a power law dependence on the stress time ( $|\Delta V_{th}| \sim t^n$ ). The exponent factor  $n$  is around 0.25 to 0.30 for p-channel TFTs under NBTI stress, which is similar to the results previously reported for poly-Si TFTs [10][11] and bulk MOSFETs [10]. It has been reported that the exponent factor between 1/3 to 1/4 can be explained by the diffusion-controlled electrochemical reactions [7][12]. However, for the n-channel TFT under PBTI stress, the  $n$  value is below 0.12, indicating the PBTI-degradation mechanism is different to that of NBTI.

Fig. 3-5(a) and 3-5(b) show the time dependence of the  $|\Delta V_{th}|$  of p- and n-channel TFTs, respectively, under various stress temperatures with stress gate voltage of -30 V. As the stress temperature increases, the  $|\Delta V_{th}|$  increases under NBTI stress; however, it shows almost temperature independent under PBTI stress. It has been reported that the NBTI-degradation in MOSFETs is mainly attributed to the generation of interface trap states and fixed oxide charges, and it can be thermally and electrically activated [3][5][6]. However, the PBTI-degradation mechanism is generally explained by the charge trapping in the gate dielectric. Therefore, the NBTI- and PBTI-degradation show different dependent on the stress temperature.

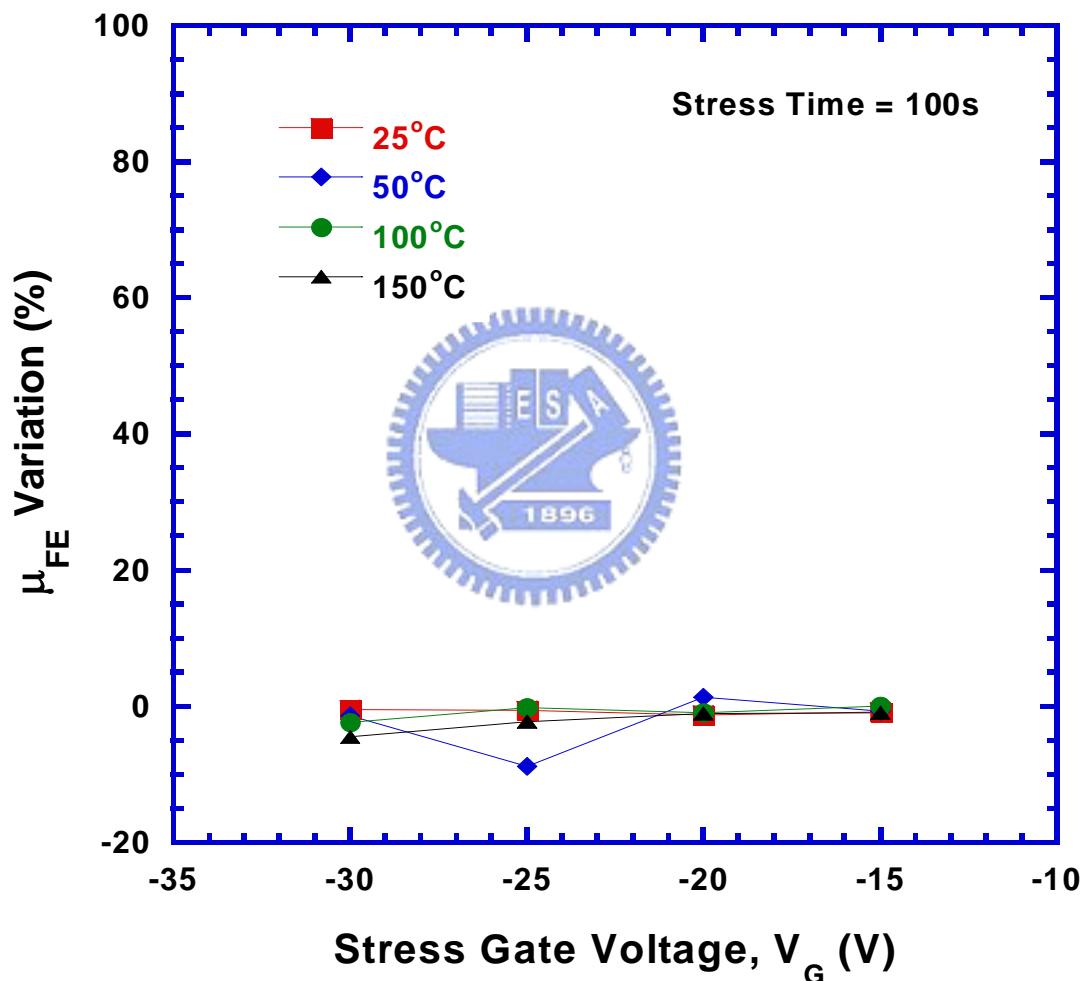

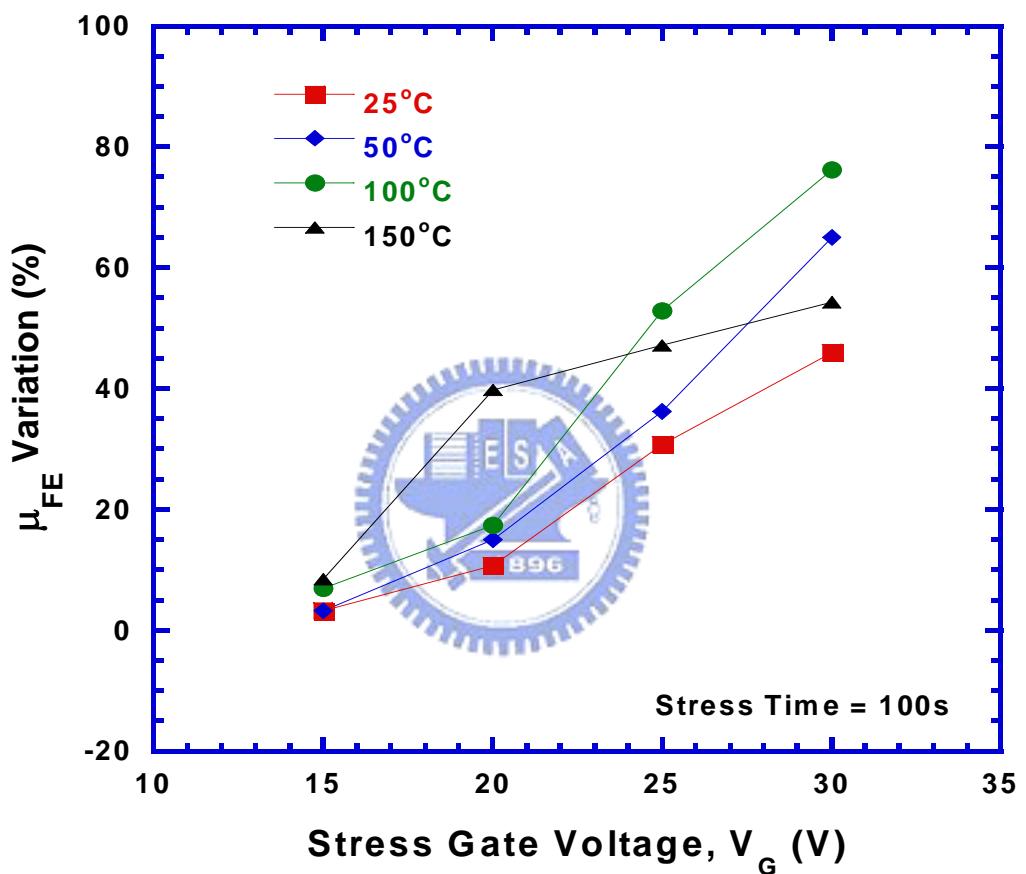

Fig. 3-6(a) and 3-6(b) show the  $\mu_{FE}$  variation as a function of the stress voltage for p- and n-channel TFTs, respectively. It has been reported that the subthreshold swing is more closely related to the trap states located near the midgap (deep states), while the mobility is more associated with the trap states located near the band edge (tail states) [11]. For the p-channel TFTs, the NBTI stress rarely changes the  $\mu_{FE}$ , indicating that the generation of the tail states can be neglected under NBTI stress. For

the n-channel TFTs, the  $\mu_{FE}$  increases with the stress voltage or temperature, implying that the tail states can be passivated during PBTI stress.

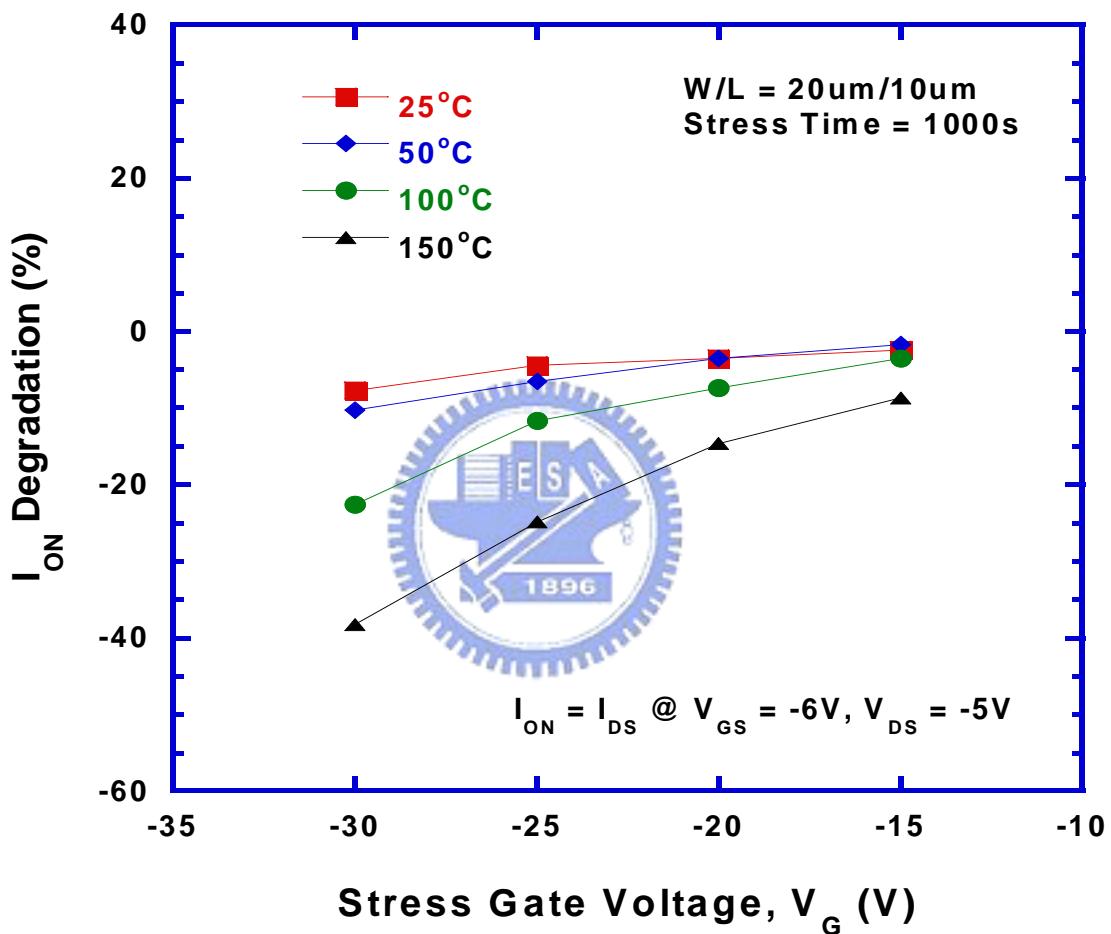

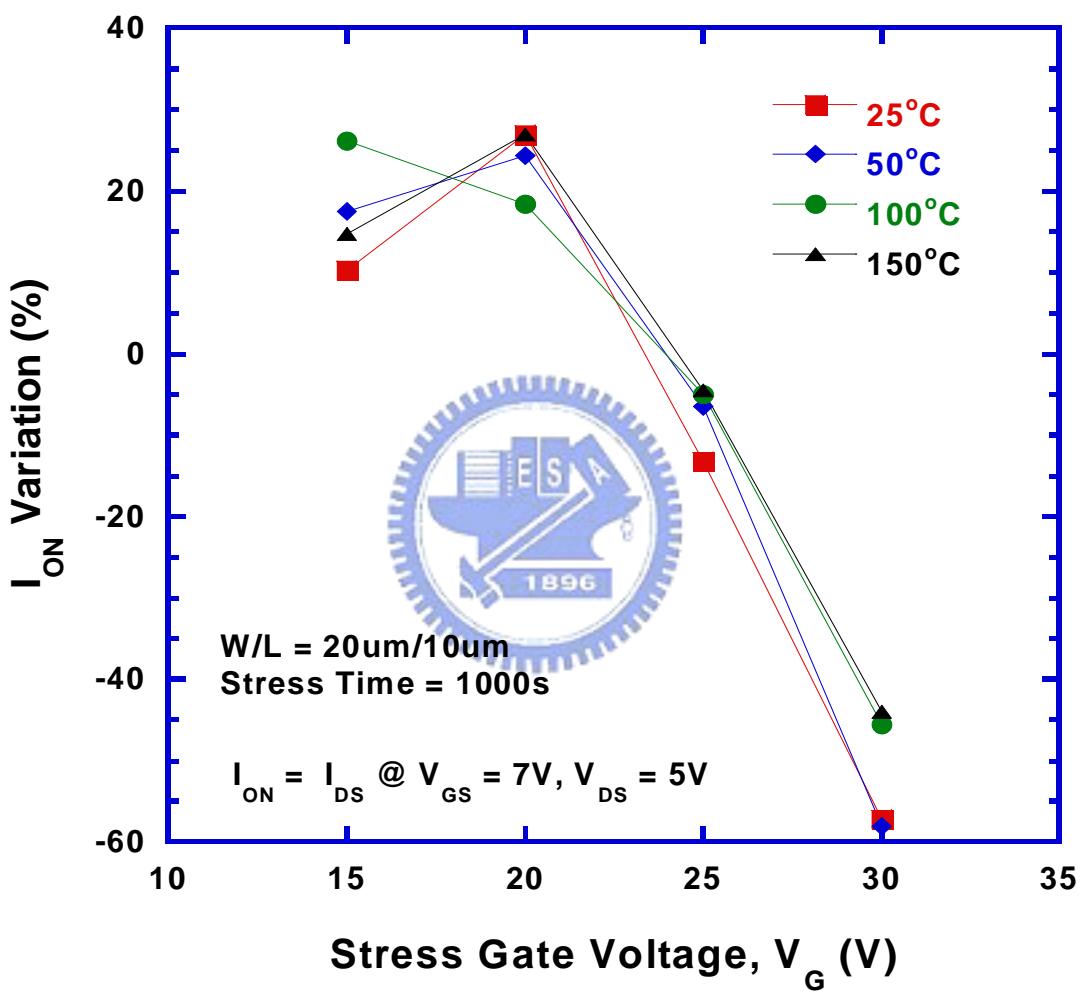

Fig. 3-7(a) and 3-7(b) show the drive current degradation as a function of the stress voltage for p- and n-channel TFTs, respectively. For the p-channel TFTs, the drive current degrades as the stress voltage or temperature increases. This is because that NBTI can be electrically or thermally activated, leading to the  $V_{th}$  shift and drive current degradation. For the n-channel TFTs, the drive current variation exhibits two regimes: in the low stress voltage regime, the drive current increases with the stress voltage; in the high stress voltage regime, the drive current decreases as the stress voltage increases. In the low stress voltage regime, the drive current increase is due to the  $\mu_{FE}$  enhancement. In the high stress voltage regime, the  $\Delta V_{th}$  becomes so large that the effect of mobility enhancement is screened; therefore, the drive current decreases with the stress voltage. The comparison of the effects of NBTI and PBTI on the TFT performance is shown in Table 3-1.

### 3.4 Summary

In this study, the mechanisms of NBTI and PBTI in LTPS TFTs were analyzed. The  $|\Delta V_{th}|$  increases with the stress gate voltage. However, as the stress temperature increase, the  $|\Delta V_{th}|$  increases under NBTI stress but almost unchanged under PBTI stress. Furthermore, the  $\mu_{FE}$  is rarely changed under NBTI stress but increases under PBTI stress. From our analysis, the NBTI-degradation mechanism in p-channel LTPS TFTs is attributed to the diffusion-controlled electrochemical reactions, while the PBTI-degradation in n-channel LTPS TFTs is arisen from the charge trapping in the gate dielectric.

## REFERENCES:

[1] T. Serikawa, S. Shirai, A. Okamoto and S. Suyama, "Low-temperature fabrication of high-mobility poly-Si TFT's for large-area LCD's," *IEEE Trans. Electron Devices*, vol. 36, pp. 1929-1933, 1989.

[2] I W. Wu, W. B. Jackson, T. Y. Huang, A. G. Lewis and A. Chiang, "Mechanism of device degradation in n- and p-channel polysilicon TFT's by electrical stressing," *IEEE Electron Device Lett.*, vol. 11, pp. 167-170, 1990.

[3] C. E. Blat, E. H. Nicollian and E. H. Poindexter, "Mechanism of negative-bias-temperature instability," *J. Appl. Phys.*, vol. 63, pp. 1712-1720, 1991.

[4] J. F. Zhang and W. Eccleston, "Positive bias temperature instability in MOSFET's," *IEEE Trans. Electron Devices*, vol. 45, pp. 116-124, 1998.

[5] N. Kimizuka, K. Yamaguchi, K. Imai, T. Iizuka, C. T. Liu, R. C. Keller and T. Horiuchi, "NBTI enhancement by nitrogen incorporation into ultrathin gate oxide for 0.1- $\mu$ m gate CMOS generation," in *Symp. VLSI Tech. Dig.*, pp. 92-93., 2000.

[6] Kousuke Okuyama, Katsuhiko Kubota, Takashi Hashimoto, Shuji Ikeda and Atsuyosi Koike, "Water-Related Threshold Voltage Instability of Polysilicon TFTs," in *IEDM Tech. Dig.*, pp. 527-530, 1993.

[7] S. Maeda, S. Maegawa, T. Ipposhi, H. Nishimura, T. Ichiki, J. Mitsuhashi, M. Ashida, T. Muragishi and T. Nishimura, "NEGATIVE BIAS TEMPERATURE INSTABILITY IN POLY-Si TFTs ,," in *Symp. VLSI Tech. Dig.*, pp. 29-30, 1993.

[8] D. K. Schroder and J. A. Babcock, "Negative bias temperature instability: road to cross in deep submicron silicon semiconductor manufacturing," *J. Appl. Phys.*, vol. 94, pp. 1-18, 2003.

[9] S. Ogawa and N. Shiono, “Generalized diffusion-reaction model for the low-field charge-buildup instability at the Si-SiO<sub>2</sub> interface,” *Phys. Rev. B*, vol. 51, pp. 4218-4230, 1995.

[10] K. Okuyama, K. Kubota, T. Hashimoto, S. Ikeda and A. Koike, “Water-related threshold voltage instability of polysilicon TFTs,” in *IEDM Tech. Dig.*, 1993, pp. 527-530.

[11] S. Maeda, S. Maegawa, T. Ipposhi, H. Nishimura, T. Ichiki, J. Mitsuhashi, M. Ashida, T. Muragishi and T. Nishimura, “Negative bias temperature instability in poly-Si TFTs ,” in *Symp. VLSI Tech. Dig.*, 1993, pp. 29-30.

[12] N. Kimizuka, T. Yamamoto, T. Mogami, K. Yamaguchi, K. Imai and T. Horiuchi, “The impact of bias temperature instability for direct-tunneling ultra-thin gate oxide on MOSFET scaling,” in *Symp. VLSI Tech. Dig.*, 1999, pp. 73-74.

[13] T. J. King, M. G. Hack and I W. Wu, “Effective density-of-states distributions for accurate modeling of polycrystalline-silicon thin-film transistors,” *J. Appl. Phys.*, vol. 75, pp. 908-913, 1994.

[14] K. O. Jeppson and C. M. Svensson, “Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices,” *J. Appl. Phys.*, vol. 48, pp. 2004-2014, 1977.

(a) Buffer layer deposition on glass substrate.

(b) Amorphous Si (a-Si) deposited by PECVD.

(c) Crystallization of a-Si film into poly-Si film by excimer laser annealing, and active region defined.

(d) Deposition of gate oxide by PECVD

(e) Deposition Mo as the gate electrode.

# Plasma Doping

(f) Self-align Source/Drain was formed.

(g) Interface layer deposition and dopant activation.

(h) Contact holes were opened and inter-connection metal was deposited and patterned.