## **Appendix**

# A. Design Rule Check

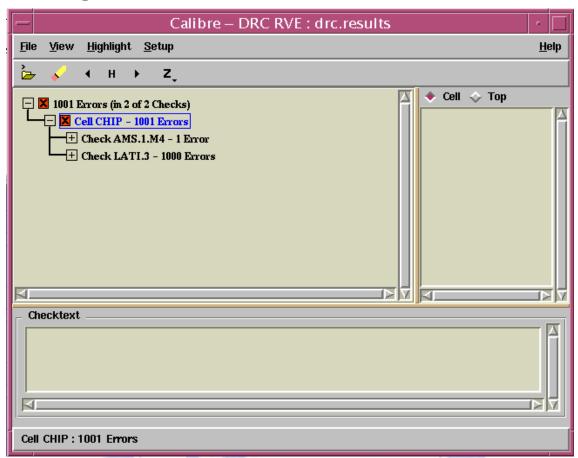

Fig. A-1 Calibre DRC results

extracted from this thesis' (Shao-Hang Hung. 's ) coordination

Fig. A-2 Calibre DRC Summary

extracted from this thesis' (Shao-Hang Hung. 's ) coordination

#### AMS.1.M4 DRC error 說明:

由於本晶片為影像感測器,需要使用大面積的Metal 4來當作遮光罩,經7月27日信件詢問CIC工程師鄧宗維先生後(Fig, A-3),確認為可忽略之DRC error。

#### LATI.3 DRC error 說明:

CIC網頁公佈之假錯,為電阻上之LATI.2之DRC錯誤,不需要考慮此錯誤。經十月26日去函詢問CIC工程師鄧宗維先生(Fig. A-4),得知該錯誤在電阻部份可以忽略。又在Summary檔案中,得知本項錯誤均集中在電阻上,故本錯誤確認為可忽略之DRC error。

# Re: 鄧先生您好,我是交通大學電控所林進燈教授碩士班研究生洪紹航 T.W.Teng <twteng@cic.org.tw> 📑 新增 收件者: siegfi <siegfi@yahoo.com.tw> 請你在報告內說明原因,並提及有訊問過CIC工程師, 我看到會讓你WAIVE這個DRC ERROR,OK!! ---- Original Message -----From: "sieqfi" <sieqfi@yahoo.com.tw> To: "T.W.Teng" <twteng@cic.org.tw> Sent: Thursday, July 27, 2006 2:30 PM Subject: 鄧先生您好,我是交通大學電控所林進燈教授碩士班研究生洪紹航 > 鄧先生您好,我是交通大學林進燈教授實驗室碩士班研究生洪紹航 > 有個LAYOUT上的問題想請教~~ > 我目前在LAYOUT DRC上遇到如附圖上的問題 > M4>35um should have slot~~ > 但是我是做image > sensor~~需要m4的金屬板來當作遮光罩~~~所以勢必須要大面積的金屬板 > 不知道這個問題要怎麼解決呢~~~~ > 煩請支援~~謝謝~~~ > 交通大學電控所 > 洪紹航敬上

Fig. A-3 The email answer for AMS.1.M4 DRC error, July 27 extracted from this thesis' (Shao-Hang Hung. 's') coordination

### Re: 障?先生緒寫D,我是交通大學電控所林進燈教授碩士班研究生洪紹航 T.W.Teng <twteng@cic.org.tw> 📑 新增

收件者: siegfi <siegfi@yahoo.com.tw>

如果這個錯誤(所有LATI系列)是發生在MOS上就不可以忽略,電阻可以。

---- Original Message -----

From: "siegfi" <siegfi@yahoo.com.tw> To: "T.W.Teng" <twteng@cic.org.tw> Sent: Thursday, October 26, 2006 3:16 PM

Subject: 障?先生緒寫D,我是交通大學電控所林進燈教授碩士班研究生洪紹航

鄧先生您好,我是交通大學電控所林進燈教授碩士班研究生洪紹航

想請教您TSMC.35製程之DRC問題

目前我面臨的DRC問題為

LATI.3 error的問題(如附圖)

但是CIC所公佈的網頁上

允許的假錯只存在LATI.2

想請教一下這個問題要如何解決,謝謝

煩請支援~~謝謝~~~

交通大學電控所

洪紹航敬上

Fig. A-4 The email answer for LATI.3 DRC error, October 26 extracted from this thesis' (Shao-Hang Hung. 's') coordination

82

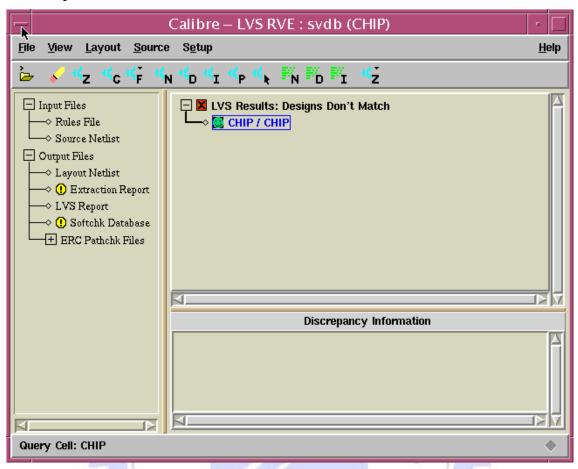

## **B.** Layout Versus Schematic check

Fig. B-1 Calibre LVS results

extracted from this thesis' (Shao-Hang Hung. 's ) coordination

Fig. B-2 Calibre LVS Layout match smile figure

extracted from this thesis' (Shao-Hang Hung. 's ) coordination

## C. Pins Instructions & SPEC Table

### Table C-1 Chip Pins Instructions and Signal illustration

extracted from this thesis' (Shao-Hang Hung. 's ) coordination

| Pin No.      | 訊號名稱     | I/O       | 訊 號 說 明                      |  |

|--------------|----------|-----------|------------------------------|--|

|              |          | direction |                              |  |

| 16           | vout1    | O         | 類比輸出信號 1                     |  |

| 21           | vout2    | О         | 類比輸出信號 2                     |  |

| 8            | Reset    | I         | 輸入 0 V 為重置,輸入 3.3 V 開始 訊號掃描  |  |

| 9            | CLK      | I         | 數位電路操作時脈,輸入 10MHz<br>信號      |  |

| 15           | SCAN_EN  | I         | Scan train Enable 模式         |  |

| 14           | SCAN_IN  | LLL       | Scan train 輸入端               |  |

| 13           | SCAN_OUT | I         | Scan train 輸出端               |  |

| 3,5,19,23    | VDDA     | Power     | 3.3V,並外接鐵粉芯與 VDD、GI<br>隔絕    |  |

| 2,4,10,18,22 | VSSA     | Power     | 0V                           |  |

| 1,7,11       | VDD      | Power     | 3.3V,並外接鐵粉芯與 VDDA、<br>GD 隔絕  |  |

| 6,12,24      | VSS      | Power     | 0V                           |  |

| 20           | GD       | Power     | 3.3V,並外接鐵粉芯與 VDDA、<br>VDD 隔絕 |  |

| 17           | GS       | Power     | 0V                           |  |

### **Table C-2 Chip Spec Table**

extracted from this thesis' (Shao-Hang Hung. 's ) coordination

| 規格                           | <b>基</b>                                   |  |  |

|------------------------------|--------------------------------------------|--|--|

| Technology                   | TSMC 0.35um 2P4M                           |  |  |

|                              | Standard CMOS Technology                   |  |  |

| Power supply                 | 3.3 (Volts)                                |  |  |

| Number of total pixels       | $17(H) \times 16(V)$                       |  |  |

| Number of effective pixels   | 16(H) × 16(V)                              |  |  |

| Fill factor                  | 67 %                                       |  |  |

| Die Size                     | $2.826 \times 2.826 \text{ (mm}^2\text{)}$ |  |  |

| Dynamic Range                | 73 ~ 84 (dB)                               |  |  |

| Frame rate                   | 30 fps @ 640×480                           |  |  |

| Power Consumption @ Dark     | 167.7mW (含類比及數位)                           |  |  |

| Pixel Size                   | 62.65 × 43.425 (um²)                       |  |  |

| Operation Frequency          | 10 (MHz)                                   |  |  |

| Package                      | SB 24                                      |  |  |

| Operation Temperature        | 0 ~ 125 (°C)                               |  |  |

| Test ADC Resolution          | 8 (bit)                                    |  |  |

| Test ADC Operation Frequency | 30 (MHz)                                   |  |  |

| Test ADC Input Range         | DC:1 (Volts);Vpp:1 (Volts)                 |  |  |

# **D. CIC Tapeout Review Form**

# **Tapeout Review Form** (for Full-custom IC)

Tapeout review form 的用意在提醒設計者在設計、模擬、佈局、佈局驗證及 tapeout 時具備設計理念及了解應注意事項,希望能藉此提昇晶片設計的成功率及 達到完整的學習效果。因此,請指導教授及設計者確實檢查該晶片設計過程是否已注意本表格之要求,並在填寫確定後簽名,若審查時發現設計內容與Tapeout Review Form 之填寫不符,很可能遭取消該晶片下線製作資格。可參考本表後所附範例確實填寫。

| 1            | 電路           | 概述                                                                     |  |

|--------------|--------------|------------------------------------------------------------------------|--|

|              | 1-1.         | 電路名稱 (circuit name):                                                   |  |

|              |              | Wide Dynamic Range & Temperature Compensated Gain CMOS Image Sensor in |  |

|              |              | utomotive applications                                                 |  |

|              | 1-2.         | 製程名稱 (process): TSMC 0.35 µm 2P4M CMOS process                         |  |

|              | 1-3.         |                                                                        |  |

|              | 1-4.         | 8 1 37                                                                 |  |

|              | 1-5.         | 功率消耗 (power consumption): 78 mW (類比部分)+ 89.714mW(數位部                   |  |

|              |              | <u>分)=167.7mW</u>                                                      |  |

|              | 1-6.         | 此電路架構於貴實驗室是否第一次設計?是(接 2-1) <u>√</u> 否(接 1-6-1)                         |  |

|              | 1-0          | 5-1. 此電路之前不 work 或 performance 不好的原因為何?                                |  |

|              | 1-0          | 6-2. 對之前的錯誤作何種修改?                                                      |  |

|              |              |                                                                        |  |

| 2            | 電路           | 模擬考量                                                                   |  |

|              | 2-1.         | 已用 SS,SF,TT,FS,FF 中哪些不同狀態之 spice model 模擬? SS, TT, FF,SF,FS            |  |

|              | 2-2.         | 已模擬過電壓變動+/-10%中哪些情況對電路工作之影響? Yes,Sensor 本體                             |  |

| +DDA+Bandgap |              |                                                                        |  |

|              | 2-3.         | 如何考量溫度變異 (temperature variety) 之影響? 使用溫度補償電路自動控制                       |  |

|              | 2-4 .        | 如何考量電阻、電容製程變異之影響? <u>使用對稱佈局法以減少變異影響</u>                                |  |

|              | <b>2-5</b> . | 模擬時是否加入 IO PAD、Bonding wire 的效應及考量測試儀器之負載等影響?                          |  |

|              |              | 已含測試儀器負載                                                               |  |

|              |              | 是否作 LPE 及 post layout simulation? Yes 使用的軟體為 Hspice                    |  |

|              |              |                                                                        |  |

| 3            | Pow          | er Line 佈局考量                                                           |  |

|              | 3-1.         | Power Line 畫多寬? <u>主要 Power Line 最大寬度為 32um</u>                        |  |

|              | 3-2.         | 是否考量 power line current density?Yes                                    |  |

|              | 3-3.         | 是否考量 Metal Line 之寄生電阻、電容? Metal lines are short, only 寄生 capacitance   |  |

|              |              |                                                                        |  |

| 4            | DRO          | C,LVS                                                                  |  |

|              | 4-1.         | 是否有作 whole chip 的 DRC 及 LVS?Yes                                        |  |

|              | 4-2.         | 除了PAD上DRC的錯誤之外,內部電路及與PAD連接的線路是否有錯?但錯誤                                  |  |

|              |              | 原因為何?                                                                  |  |

|              | 4-3.         | 在作 LVS 的過程中,PIN 腳及元件是否 match?                                          |  |

|              |              | 何?                                                                     |  |

|              | 4-4.         | 檢查 PAD 與 PAD 間是否有移位、短路或斷路的現象?                                          |  |

| 5            | 類比           | 混合訊號電路佈局考量(類比-混合訊號電路設計者填寫)                                             |  |

|              | 5-1          | 佈局對稱性及一致性考量                                                            |  |

|   |     | 5-1-1 OP(Comparator) Input Stage 是否對稱? Yes                                                   |

|---|-----|----------------------------------------------------------------------------------------------|

|   |     | 5-1-2 OP(Comparator) Input Stage 是否對稱? <u>Yes</u>                                            |

|   |     | 5-1-3 佈局中對稱元件是否使用 dummy cell 技巧? Yes                                                         |

|   |     | 5-1-4 對稱電容是否採用同心圓佈局? <u>Yes</u>                                                              |

|   |     | 5-1-5 對稱單位電容四周是否切成 45 度斜角? No                                                                |

|   |     | 5-1-6 對稱電容的單位面積是否一致? Yes                                                                     |

|   |     |                                                                                              |

|   |     | 單位電容面積多大? <u>18.6</u> um x <u>18.6</u> um                                                    |

|   |     | 單位電容值多大? <u>0.2</u> pF                                                                       |

|   |     | 5-1-7 電阻採用哪一材質製作? <u>N+ diffusion</u>                                                        |

|   |     | 單位電阻值多大?                                                                                     |

|   | 5-2 | 電路雜訊佈局考量                                                                                     |

|   |     | 5-2-1 是否將 Analog 及 Digital 的 power line 分開? Yes, analog 及 digital 為不同                        |

|   |     | Power                                                                                        |

|   |     | 5-2-2 Analog area 是否用 guard ring 隔絕? <u>Yes</u>                                              |

|   |     | 5-2-3 Digital area 是否用 guard ring 隔絕? Yes,類比電路內之數位部分有使用                                      |

|   |     | guard ring                                                                                   |

|   |     | 5-2-4 對於 sensitive line 是否使用 shield 的技巧? <u>Not need</u>                                     |

|   |     | 5-2-5 Analog guard ring 及 shield 是否接至乾淨之電位?                                                  |

|   |     | Yes, 有區分guard ring 電位及類比電位                                                                   |

|   |     | 5-2-6 是否將 sensitive line 儘量縮短及避免跨越 noise(clock)line? <u>Yes</u>                              |

|   |     | 5-2-7 電容的上下極板是否接對? <u>Yes</u>                                                                |

|   | 5-3 | - W = C   -                                                                                  |

|   |     | AMS.1.M4 DRC error 說明:由於本晶片為影像感測器,需要使用大面積的 Metal 4 來                                         |

|   |     | 當作遮光罩,經七月27日信件詢問CIC工程師鄧宗維先生後(如圖八-2),確認為可                                                     |

|   |     | <u>忽略之 DRC error。</u><br>LATI.3 之 DRC 錯誤說明:CIC 網頁公佈之假錯,為電阻上之 LATI.3 之 DRC 錯誤,                |

|   |     | 不需要考慮此錯誤。經十月26 日去函詢問CIC 工程師鄧宗維先生 (如圖八-3),得知                                                  |

|   |     | 該錯誤在電阻部份可以忽略。又在Summary 檔案中,得知本項錯誤均集中在電阻上,                                                    |

|   |     | 故本錯誤卻認為可忽略之DRC error。                                                                        |

|   | 5-4 | LVS 驗證過程中, 電感電容或其他特殊元件的比對是否做過處理, 請說明_ Yes_                                                   |

|   |     | 加入 DUMMY CELL 減少製程上的飄移與 shadow 現象                                                            |

|   | 5-5 | 量測方式為 on wafer, on PCB or in package? 並說明量測時應該注意事項與量                                         |

|   |     | 測地點                                                                                          |

|   |     | 在 PCB 板上進行量測,分為兩個步驟,初步為電性量測,次為顯相量測,測試平台                                                      |

|   |     | 分為常溫 $(25^\circ\text{C})$ ,高溫 $(85^\circ\text{C})$ ,低溫 $(0^\circ\text{C})$ ,以測試電路是否能如常溫下正常工作 |

|   |     |                                                                                              |

| 8 | PAD | Replacement 考量(使用 TSMC I/O PAD 設計者填寫)                                                        |

|   | 8-1 | 已於申請表勾選申請使用 TSMC I/O PADYes                                                                  |

|   | 8-2 | 個人設計的 Cell 名稱(cell-name)未與 TSMC 所提供之任一 Pad Cell 名稱相同                                         |

|   |     | <u>Yes</u>                                                                                   |

|   | 8-3 | 採用 Create Instance 方式加入 I/O Pad,未用 Copy 或 Flatten 破壞 Instance 的結                             |

|   |     | 構 <u>Yes</u>                                                                                 |

|   | 8-4 | 由 IC Core 部份拉線到 Pad 只拉到最邊緣部分,未過於覆蓋 Pad                                                       |

|   |     |                                                                                              |

| 9 | 其他  | 考量                                                                                           |

|   | 9-1 | 是否考量測試時的輸出量測點? <u>Yes</u>                                                                    |

|   | 9-2 | 是否考量電路之可修改性(如用 laser cut 設備) No, 電路規則性設計,輸出為連續                                               |

|   |     | <u> </u>                                                                                     |

|   |     |                                                                                              |

|   |     | 設計者簽名:                                                                                       |

|   |     |                                                                                              |

### **Tapeout Review Form**(for Cell-Based IC) version 1.3

2006/6/22

Page 87 /3

Tapeout review form 的用意在提醒設計者在設計、模擬、佈局、佈局驗證及 tapeout 時具備設計理念及了解應注意事項,希望能藉此提昇晶片設計的成功率及達到完整的學習效果。因此,請指導教授及設計者確實檢查該晶片設計過程是否已注意本表格之要求,並在填寫確定後簽名,若審查時發現設計內容與 Tapeout Review Form 之填寫不符,很可能遭取消該晶片下線製作資格。可參考本表後所附範例確實填寫。

1.

晶片概述:

|    | 1-1.     | 專題名稱: Wide Dynamic Range & Temperature Compensated Gain CMOS               |

|----|----------|----------------------------------------------------------------------------|

|    |          | Image Sensor in automotive applications                                    |

|    | 1-2.     | Top Cell 名稱:                                                               |

|    | 1-3.     | 使用 library 名稱:                                                             |

|    |          | CIC_CBDK13; CIC_CBDK18; \(\bullet CIC_CBDK35                               |

|    |          | CBDK 版本:                                                                   |

|    |          | 是否使用 Core Cell: <u>V</u> 若有使用 Core Cell 有無更改 Cellname: <u>No</u> (建議保留勿更改) |

|    |          | 是否使用 IO: _ 若有使用 IO, 採用形式是: Linear Staggered                                |

|    | 1-4.     | 是否使用 CIC 提供之 Memory?No 若使用 Memory, 是否已上傳 spec 檔:                           |

|    |          | 使用 Memory 之種類為何?                                                           |

|    | 1-5.     | 工作頻率:10MHz                                                                 |

|    | 1-6.     | 功率消耗: 78 mW (類比部分) +89.714mW(數位部分=167.7mW                                  |

|    | 1-7.     | 晶片面積:2826um^2                                                              |

|    |          |                                                                            |

| 2. | 設計台      | <b>全成:</b>                                                                 |

|    | 2-1.     | 使用之合成軟體?Synopsys design compiler                                           |

|    | 2-2.     | 是否加入 boundary condition:                                                   |

|    |          | input drive strength input delay input delay output loading input delay    |

|    | 2-3.     | 是否加入 timing constraint:                                                    |

|    |          | specify clock (sequential design)                                          |

|    |          | max delay \ min delay (combinational design)                               |

|    | 2-4.     | 是否加入 area constraint?No                                                    |

|    | 2-5.     | 合成後之 report 是否有 timing violation?No                                        |

|    |          | 有 setup time violation、 有 hold time violation                              |

|    | 2-6.     | 合成後之 verilog 是否含有 assign 描述? <u>No</u>                                     |

|    | 2-7.     | 合成後之 verilog 是否含有 *cell* 之 instance name? <u>No</u>                        |

|    | 2-8.     | 合成後之 verilog 是否含有反鈄線 \ 之 instance name 或 net name?                         |

| 3. | 可測言      | 式性設計(前瞻性晶片必填):                                                             |

| ٥. | 3-0.     | 使用之設計軟體? <u>DFT compiler</u>                                               |

|    | 3-2.     |                                                                            |

|    | 3-3.     | 使用 Embedded memory 數量: SRAM No , ROM No                                    |

|    | 5 5.     | Memory 大小:                                                                 |

|    |          | 测試方法: BIST, or 其他測試方法                                                      |

|    |          | 若使用 BIST,其 Test Algorithm 為何?                                              |

|    |          | 同時有多個 memory,是否共用 BIST controller, BIST controller 數量                      |

|    | 3-4.     | Scan Chain Information                                                     |

|    | <i>.</i> | Flip-Flop 共有多少個?                                                           |

|    |          | Scan chain 的數量共有多少條?1                                                      |

|    |          | Scan chain length (Max.) ? <u>43377.510</u>                                |

|    | 3-5.     | Uncollapsed fault coverage 是否超過 90% ?                                      |

|    |          | ATPG pattern 的數目為多少?                                                       |

|    |          | 註:若使用 Synopsys TetraMAX 來產生 ATPG pattern,請使用 set faults                    |

|    |          | -fault_coverage 指令指定 TetraMAX 產生 fault coverage information                |

若使用 SynTest TurboScan 之 asicgen 來產生 ATPG pattern,請以 atpg pessimistic fault coverage 的值為準

| 4. | 佈局前模擬                                                                         |

|----|-------------------------------------------------------------------------------|

|    | 4-1. gate level simulation 是否有 timing violation ? <u>No</u>                   |

|    | 有 setup time violation、 有 hold time violation                                 |

|    |                                                                               |

| 5. | 實體佈局                                                                          |

|    | 5-1. 使用之 P&R 軟體? Apolo、* SOC Encounter                                        |

|    | 5-2. power ring 寬度?8_ 是否已考量 current density(1mA/1um)?Yes                      |

|    | 5-3. 是否考慮 output loading? <u>Yes</u>                                          |

|    | 5-4. 是否加上 Clock Tree ? <u>Yes</u>                                             |

|    | 5-5. 是否加上 Corner pad? Yes                                                     |

|    | 5-6. IO Buffer 間是否加上 IO Filler: <u>Yes</u> IO Filler 寬度: <u>230</u> um (建議至少需 |

|    | 12um 寬)                                                                       |

|    | 5-7. 是否加上 Core Filler? <u>Yes</u>                                             |

|    | 5-8. 是否上加 Bonding Pad ? <u>Yes</u>                                            |

|    | 以下(A-1)為使用 Apollo 者才須回答                                                       |

|    | A-1. 是否執行 Fill Notch and Gap 步驟?                                              |

|    | 以下(S-1 至 S-2)為使用 SOC Encounter 者才須回答                                          |

|    | S-1. power ring 上是否有 overlap vias?No                                          |

|    | S-2. 是否確定 IO Row 和 Corner Row 互相貼齊? <u>Yes</u>                                |

| 6. | 佈局後模擬                                                                         |

| •  | 6-1. 是否做過 post-layout gate-level simulation?Yes                               |

|    | STA(static timing analysis) 軟體?                                               |

|    | 6-2. 是否做過 post-layout transistor-level simulation?                            |

|    | 6-3. 已針對以下環境狀態模擬: SS、 TT、 FF                                                  |

|    | 6-4. 晶片取得時將以何種方式進行測試? 在PCB 板上進行量測,分為兩個步驟,初步                                   |

|    | 為電性量測,次為顯相量測,測試平台分為常溫 $(25^\circ C)$ ,高溫 $(85^\circ C)$ ,低溫 $(0^\circ C)$ ,   |

|    | 以測試電路是否能如常溫下正常工作_                                                             |

|    | 6-5. 模擬時是否考量輸出負載影響? <u>Yes</u> 若有輸出負載是: <u>20</u> pF (建議至                     |

|    | 少需 20pF)                                                                      |

|    |                                                                               |

| 7. | DRC/LVS 驗證                                                                    |

|    | 7-1. 是否有 DRC 錯誤? <u>Yes</u> 錯誤原因:                                             |

|    | AMS.1.M4 DRC error 說明:由於本晶片為影像感測器,需要使用大面積的 Metal 4 來                          |

|    | 當作遮光罩,經七月27 日信件詢問CIC 工程師鄧宗維先生後(如圖八-2),確認為可                                    |

|    | 忽略之 DRC error。                                                                |

|    | LATI.3 之DRC 錯誤說明:CIC 網頁公佈之假錯,為電阻上之LATI.3 之DRC 錯誤,                             |

|    | 不需要考慮此錯誤。經十月26日去函詢問CIC工程師鄧宗維先生(如圖八-3),得知                                      |

|    | 該錯誤在電阻部份可以忽略。又在Summary 檔案中,得知本項錯誤均集中在電阻上,                                     |

|    | 故本錯誤卻認為可忽略之 DRC error。                                                        |

|    | 驗證 DRC 軟體?                                                                    |

|    | 是否有不作 DRC 的區域?                                                                |

|    | 7-2. 是否有 LVS 錯誤?                                                              |

|    | 驗證 LVS 軟體? <u>Calibre</u>                                                     |

| 0  | 是否有非 CIC 提供的 BlackBox ?                                                       |

| 8. | MT Form 填寫                                                                    |

|    | 8-1. 是否填上 <u>V</u> 系所單位、 <u>V</u> 設計者姓名、 <u>V</u> 聯絡電話(與手機)、 <u>V</u> 日期      |

|    | 8-2. 是否填上晶片上傳目錄?                                                              |

|    | 8-3. 是否填上檔案名稱?                                                                |

|    | 8-4. 是否寫上 top cell name?                                                      |

| 批計 | - 者簽名: 洪紹航、薛智文、黄德瑋 指導教授簽名: 林進燈                                                |

| 以口 | 14 从11·                                                                       |

### E. CIC Tapeout Question & Reply

## D35-95E 審查結果報告暨審查回覆

#### 編號 02a

計畫名稱: 高動態範圍及溫度補償增益之車用CMOS 影像感測器 包裝材料: 24S/B:8Pcs,DieSort:10EA, 製作經費預估\$134,554 評比 C

#### 建議/修改及回覆

1. 為何溫度範圍由25度C開始,25度以下沒有cover到design?

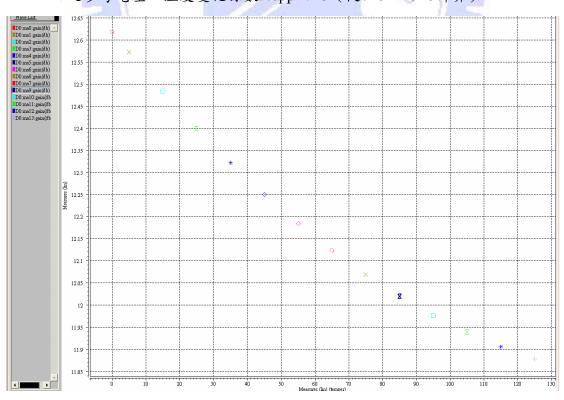

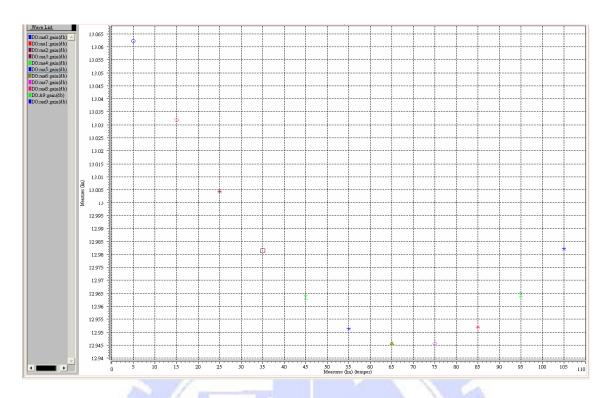

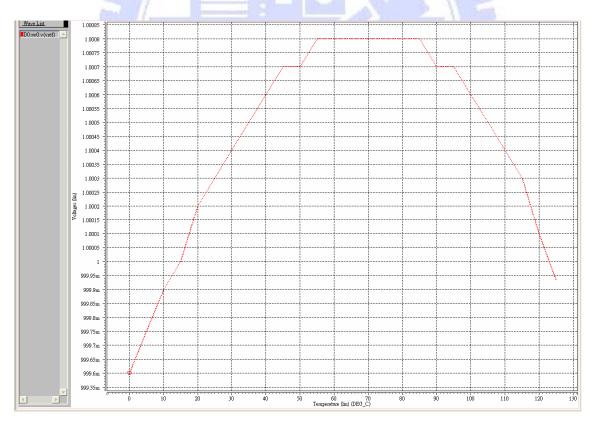

回覆:當初設計時,由於考量到Hspice的參數模型準確有效範圍僅限於25度至85度,模擬25度以下之數據誤差甚大,所以並沒有將其數據放進去模擬圖形之中。經評審委員之建議後,已將該模擬數據放入新的報告之中,如以下附圖,Fig. E-1:未添加溫度補償電路時,增益隨溫度之變化Gain隨溫度下降了0.69dB(0°C~125°C),平均變化661.437ppm/°C;Fig. E-2添加溫度補償電路時,增益隨溫度之變化圖 Gain隨溫度最大變化值為0.117dB(0°C~125°C),平均變化135.612ppm/°CPage 16;Fig. E-3,Bandgap可提供1V之參考電壓,溫度變化係數9.6ppm/°C(從0°C~125°C計算)。

Fig. E-1未添加溫度補償電路時,增益隨溫度之變化圖 extracted from this thesis' (Shao-Hang Hung.'s ) coordination

Fig. E-2添加溫度補償電路時,增益隨溫度之變化圖 extracted from this thesis' (Shao-Hang Hung.'s ) coordination

Fig. E-3可提供1V之參考電壓,溫度變化係數9.6ppm/°C (從0°C~125°C計算) extracted from this thesis' (Shao-Hang Hung.'s ) coordination

- 2. 報告者沒有很清楚的將chip的內容解說。

- 回覆:本設計着重的特色,是在於注重各組電路對於溫度上的補償效果以及其對應方針,包含整體晶片架構、Sensor部分、放大器部份,偏壓電路部份等等,就報告上難免在短時間內難以將晶片全部的設計架構完整表達清楚。在此特別針對此部分於後者說明報告時以評審委員的建議做改進與檢討,同時未來將會調整晶片的設計方針,將重點集中在同一目標以方便設計者暨報告者能充分發揮及說明晶片的特色以及創新點。在此特別針對此部分做一簡單的晶片的設計內容描述如下:

- (1)影像Sensor部分,使用類比記憶體的模式,擴充放電電量已達到高動態 範圍之效果;又使用雙重減法之方式減除溫度造成的雜訊,以得到純 粹的光訊號。至於類比記憶體受到溫度造成的膨脹影響,能有效的延 展動態範圍之結果,此為本晶片最主要的特色之一。

- (2)溫度補償DDA部分,採用正溫度係數之電阻值,隨溫度而補足原本差動對會漏失的電流值,繼而達到補償增益的效果。該電路亦為本晶片的創新之一。

- (3) Bandgap部分,沿用K. N. Leung所提出來的架構,將其電路中的Bipolar 用MOS取代後,製作出一1V參考電壓值的Bandgap,其效果為 9.6ppm/°C。

- (4) Timing Generator部分,採用Cell base方式進行電路合成。

- 3. 強調溫度補償和車用其應用溫度必須在25度以下。

- 回覆:同問題1之回答,已將25度C以下溫度補償之數據該模擬數據放入新的報告中,Fig. E-1:未添加溫度補償電路時,增益隨溫度之變化Gain隨溫度下降了0.69dB(0°C~125°C),平均變化661.437ppm/°C;Fig. E-2添加溫度補償電路時,增益隨溫度之變化圖 Gain隨溫度最大變化值為0.117dB(0°C~125°C),平均變化135.612ppm/°CPage 16;Fig. E-3,Bandgap可提供1V之參考電壓,溫度變化係數9.6ppm/°C(從0°C~125°C計算)。

4. 動態範圍需補上操作範圍之range (worst/best case)。

回覆:已補上動態範圍之最佳狀況以及最差狀況,其關鍵性影響應會在於實際上製作的電容值不均(包含感光元件以及類比記憶體)以及感光元件最低靈敏度之影響。而其不均勻的原因可來自製程上的miss-match抑或是操作時的溫度因素;而感光元件最低靈敏度抑是受離子佈植的均勻度而影響,其動態範圍之最佳狀況以及最差狀況整理如下表,同Page 24之預計規格列表。

Table E-1 預計規格列表 extracted from this thesis' (Shao-Hang Hung. 's ) coordination

| 規格                           | · 結 果                                       |  |  |

|------------------------------|---------------------------------------------|--|--|

| Technology                   | TSMC 0.35um 2P4M                            |  |  |

| LH m                         | Standard CMOS Technology                    |  |  |

| Power supply                 | 3.3 (Volts)                                 |  |  |

| Number of total pixels       | $17(H) \times 16(V)$                        |  |  |

| Number of effective pixels   | $16(H) \times 16(V)$                        |  |  |

| Fill factor                  | 67 %                                        |  |  |

| Die Size                     | $2.826 \times 2.826 \text{ (mm}^2\text{)}$  |  |  |

| Dynamic Range                | 73 ~ 84 (dB)                                |  |  |

| Frame rate                   | 30 fps @ 640×480                            |  |  |

| Power Consumption @ Dark     | 167.7mW(含類比及數位)                             |  |  |

| Pixel Size                   | $62.65 \times 43.425 \text{ (um}^2\text{)}$ |  |  |

| Operation Frequency          | 10 (MHz)                                    |  |  |

| Package                      | SB 24                                       |  |  |

| Operation Temperature        | 0 ~ 125 (°C)                                |  |  |

| Test ADC Resolution          | 8 (bit)                                     |  |  |

| Test ADC Operation Frequency | 30 (MHz)                                    |  |  |

| Test ADC Input Range         | DC: 1 (Volts); Vpp: 1 (Volts)               |  |  |

### 5. 功率消耗是否有競爭力,需詳細討論。

回覆:因本設計所着重的特色定位在高動態範圍以及抗溫度雜訊的方向,並未討論到功率消耗的競爭力問題。經過資料查證與一些文獻上的整理(下圖為Micron MT9V022車用影像感測器Datasheet),本晶片在功率消耗的設定方面與一般業界或學界所設計相距無遠,其原因在於確保晶片能正常工作,不至於因為設計電流太低,而導致無法操作;在未來的規劃方面,已經把低功率或超低功率設計方法列為改版考慮的優先決定。

#### Specifications

| • Pixel Size:                                                     | 6µm x 6µm                                                                                                                                                                                                                          | • ADC:                                            | 10-, 8-bit, selectable                               |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------------------|

| <ul><li>Array Format<br/>(active):</li></ul>                      | 752H x 480V                                                                                                                                                                                                                        | • Data Rate:                                      | 26.6 megapixels per second<br>(master clock, 26 MHz) |

| <ul><li>Imaging Area:</li></ul>                                   | 4.55mm x 2.97mm                                                                                                                                                                                                                    | <ul><li>Responsivity:</li></ul>                   | 4.8 V/lux-sec (550nm)                                |

| <ul> <li>Color Filter Array:</li> </ul>                           | Monochrome or RGB Bayer color filters                                                                                                                                                                                              | Minimum     Detectable Light:                     | sub-0.1 lux (mono),<br>5 lux (color)                 |

| Optical Format:                                                   | 1/3-inch                                                                                                                                                                                                                           | • Lag:                                            | 0.5%, 0%-100% of full well                           |

| • Frame Rate:                                                     | 60 fps @ 752H x 480V,<br>higher frame rates at                                                                                                                                                                                     | Dark Current:                                     | <10% of saturation signal at +85°C                   |

|                                                                   | lower resolutions                                                                                                                                                                                                                  | Spectral Range:                                   | 450nm-1,050nm                                        |

| <ul><li>Dynamic Range:</li></ul>                                  | 75dB-110dB                                                                                                                                                                                                                         | Quantum                                           |                                                      |

| <ul><li>Shutter:</li></ul>                                        | TrueSNAP™ simultaneous<br>integrate and readout<br>global shutter                                                                                                                                                                  | Efficiency:                                       | >40% (@ 850nm)                                       |

|                                                                   |                                                                                                                                                                                                                                    | <ul> <li>Conversion Gain:</li> </ul>              | 30 uV/e-                                             |

| Data Format:                                                      | Parallel/LVDS (serial),<br>selectable<br>10 to 8 bits                                                                                                                                                                              | • Pixel Read Noise:                               | <25e-                                                |

|                                                                   |                                                                                                                                                                                                                                    | <ul><li>Supply Voltage:</li></ul>                 | 3.0V–3.6V (3.3V nominal)                             |

| • Window Size:                                                    | Programmable to any size<br>(e.g., QVGA, CIF, QCIF, etc.)                                                                                                                                                                          | <ul><li>Power<br/>Consumption:</li></ul>          | <320mW (@ 60 fps),<br><120μW standby                 |

| • Scan Mode:                                                      | Progressive or interlaced                                                                                                                                                                                                          | <ul><li>Operating<br/>Temp. Range:</li></ul>      | -40°C to +85°C                                       |

| <ul> <li>Automatic and<br/>Programmable<br/>Functions:</li> </ul> | Regionally weighted exposure,<br>black level offset correction,<br>horizontal blanking, vertical<br>blanking, lighting control,<br>left-right and top-bottom<br>image reversal, windowing,<br>regional gain, image decima-<br>tion | <ul> <li>Storage Temp.</li> <li>Range:</li> </ul> | -55°C to +125°C                                      |

|                                                                   |                                                                                                                                                                                                                                    | <ul><li>Package:</li></ul>                        | 52-ball iBGA or die,<br>automotive-qualified         |

Fig. E-4 Micron MT9V022 車用影像感測器 Datasheet

extracted from Micron MT0V022 Automotive CMOS Image Sensor Datasheet [19]

6. 規格需要一個range badnd gap,既然不用低的supply voltage,可以選擇更簡單的架構。

回覆:本設計有考量到需要一個不隨溫度變化之穩定參考電壓,因此需要使用到band gap電路,但目前的結構如委員所說,使用不到低的supply voltage,所以可以選擇更簡單的架構設計參考電壓源。已經在進行中的下一版本,我們將專注於研發重心之電路,簡化其他部分的支援電路的設計,以減少實驗中或實際量測上訊號的變因。

#### 佈局是否需修改?

No