# 國立交通大學

電子工程學系 電子研究所

博士論文

新穎高介電常數材料與奈米微晶粒

非揮發性記憶體之研究

Study on Novel Nonvolatile Memory with High-k

Dielectric Materials and Nanocrystals

研究生:林育賢

指導教授:雷添福

簡昭欣

中華民國 九十五 年 五 月

## 新穎高介電常數材料與奈米微晶粒

#### 非揮發性記憶體之研究

# Study on Novel Nonvolatile Memory with High-k Dielectric Materials and Nanocrystals

研究生:林育賢 Stud

指導教授:雷添福 博士

簡昭欣 博士

Student: Yu-Hsien Lin

Advisor: Dr. Tan-Fu Lei

Dr. Chao-Hsin Chien

#### 國立交通大學

雷子工程學系 雷子研究所

#### 1896

A Dissertation

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

In Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy

In

Electronics Engineering May 2006

Hsinchu, Taiwan, Republic of China

中華民國 九十五 年 五 月

# 新穎高介電常數材料與奈米微晶粒 非揮發性記憶體之研究

學生:林育賢 指導教授:雷添福博士

簡昭欣博士

#### 國立交通大學

電子工程學系 電子研究所博士班

摘要

此論文製作許多不同的非揮發性快閃記憶體,將使用數種材料、不同的製程方法及結構來製備捕陷電荷層,來取代現今傳統氮化矽 (Si<sub>3</sub>N<sub>4</sub>) 材料。再用不同的寫入/抹除的操作方式,在低電壓下來操作快閃記憶體。以達成電荷捕捉效率 佳、有快速的寫入/抹除速度、大的記憶窗口、儲存資料持久性、以及寫入、清除操作造成的性能退化少的非揮發性快閃記憶體。

首先,我們利用氧化鉿 (HfO<sub>2</sub>) 奈米微晶粒作為捕陷電荷層來製作新額的 SONOS型非揮發性快閃記憶體。此氧化鉿奈米微晶粒快閃記憶體在一萬次的寫入/抹除下,還是擁有好的儲存資料持久性、以及寫入、清除操作造成的性能退化少。其電荷儲存方式可以很區域性,使其一個單元儲存2個位元,並具有高密度之優點,可用於相關記憶體及半導體產業中。

再者,利用氧化鉛 (HfO<sub>2</sub>)薄膜作為捕陷電荷層隨著後處理溫度的不同來製作 SONOS 型非揮發性快閃記憶體。我們發現到隨著退火的溫度愈高,記憶窗口愈大而儲存資料持久性愈差且寫入、清除操作造成的性能退化變多了。此為高溫

下結晶額外產生的淺能量的捕陷電荷所造成。之後我們也討論了溫度變化,以及其記憶體在一般操作時和其旁元件的電性影響。

接著,我們使用三種高介電常數材料成功的製作出了 SONOS 型非揮發性快 閃記憶體於低溫多晶矽薄膜電晶體上,材料包含氧化鉿,氧化鉿矽化物以及氧化 鋯矽化物。我們在其低溫製程中,達成電荷捕捉效率佳、有快速的寫入/抹除速 度、大的記憶窗口、儲存資料持久性、以及寫入、清除操作造成的性能退化少 的非揮發性快閃記憶體。而且,我們也成功的設計一個單元儲存 2 個位元的記憶 體操作。

在論文的最後,我們製作出五十奈米的氧化鉛 (HfO<sub>2</sub>) 奈米微晶粒記憶體在 SOI 的晶片上。此可以完全和現今 CMOS 的製程互相配合,來製作電荷非常有 區域性的記憶體。如此一來,我們可以把現今的非揮發性快閃記憶體來縮小到七 十個奈米以下,在次世代的小線寬記憶體的應用上將會完善。

# Study on novel nonvolatile memory with high-k dielectric materials and nanocrystal

Student: Yu-Hsien Lin Advisor: Dr. Tan-Fu Lei

Dr. Chao-Hsin Chien

Department of Electronics Engineering &

Institute of Electronics

National Chiao Tung University

#### **ABSTRACT**

In this thesis, we design various nonvolatile memory with a high-k charge-trapping layer and nanocrystals. This high-k layer replaces the silicon nitride layer in the SONOS structure. Different program/erase methods are also proposed for low power applications. This nonvolatile memory structure will have superior characteristics in terms of considerably large memory window, high speed program/erase, long retention time, and excellent endurance.

First, we present a novel nonvolatile SONOS-type flash memory that was fabricated using hafnium oxide ( $HfO_2$ ) nanocrystals as the trapping storage layer. These  $HfO_2$  nanocrystal memories exhibit excellent data retention, endurance, and

Ш

good reliability, even for the cells subjected to 10k P/E cycles. These features suggest that such cells are very useful for high-density two-bit nonvolatile flash memory applications.

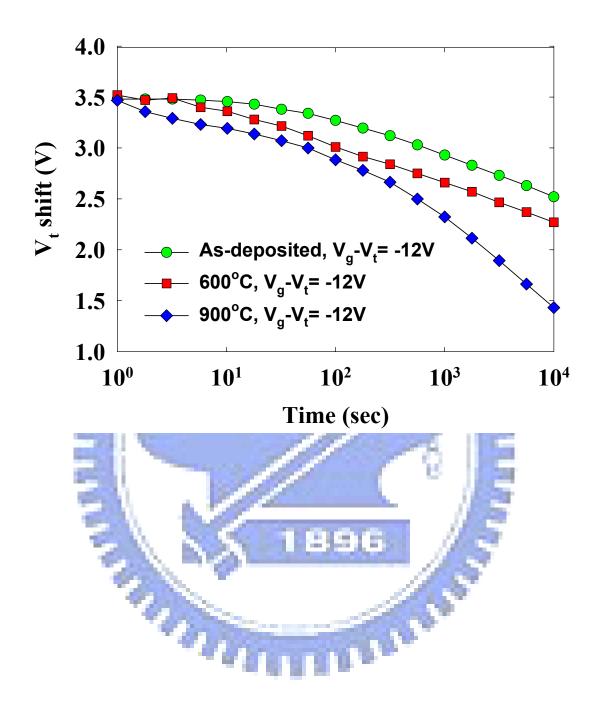

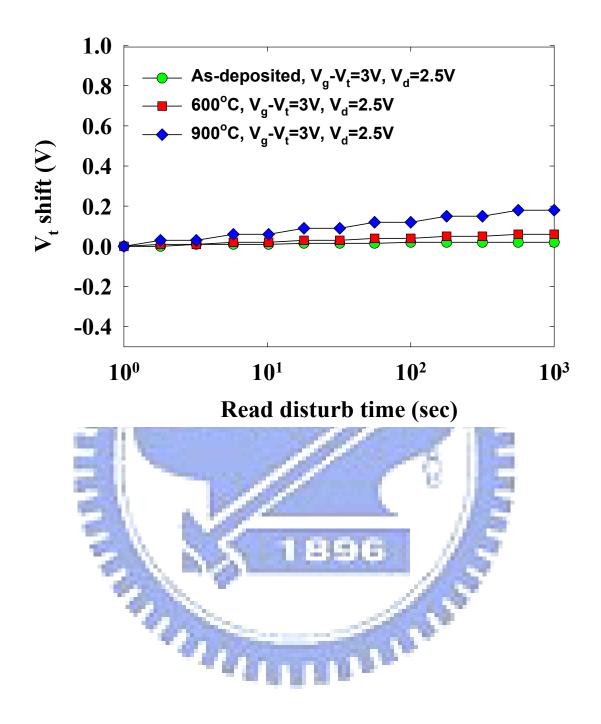

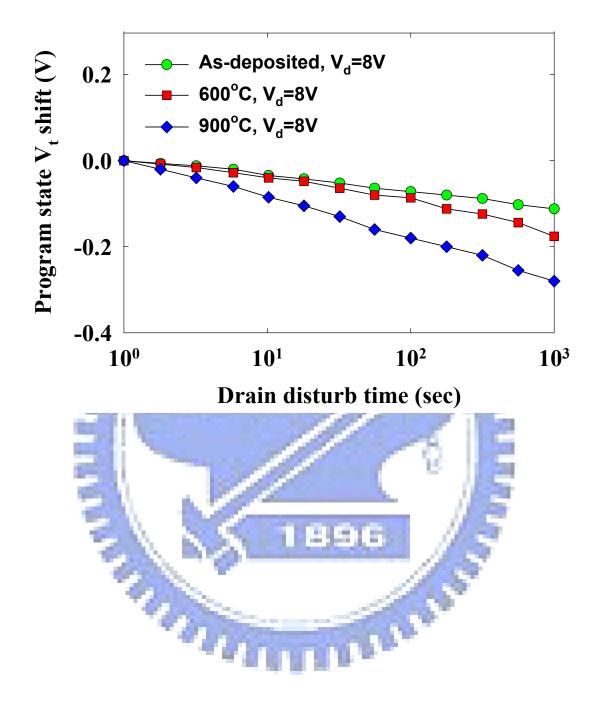

Then, we demonstrate the effect of the post-deposition annealing for the HfO<sub>2</sub> trapping layer on the performance of the SONOS-type flash memories. It was found that the memory window becomes larger while the retention and endurance characteristics get worse as the annealing temperature increases. This was ascribed to the larger amount and the shallower energy levels of the crystallization-induced traps as compared to the traps presented in the as-fabricated HfO<sub>2</sub> film. Finally, in the aspect of disturbances, we show only insignificant read, drain and gate disturbances presented in the three samples in the normal operation.

Next, we have successfully fabricated SONOS-type poly-Si-TFT memories employing three kinds of high-k dielectrics, including HfO<sub>2</sub>, Hf-silicate and Zr-silicate, as the trapping layer with low-thermal budget processing. It was demonstrated that the fabricated memories exhibit good performance in terms of relatively large memory window, high program/erase speed (1ms/10ms), long

retention time ( $>10^6$ s for 20% charge loss) and negligible read/write disturbances. In particular, 2-bit operation has been successfully demonstrated.

Finally, we demonstrate 50nm nonvolatile HfO<sub>2</sub> nanocrystal memory on SOI wafer. With this technique, which is fully compatible to current CMOS technologies, to form the very local HfO<sub>2</sub> nanocrystals for the application of the nonvolatile flash memories. For aggressively scaling the conventional nonvolatile floating gate memories below sub-70nm node, we can successfully achieve the nano-devices for the application in the next-generation nonvolatile memories

#### 誌謝

首先我要向我的指導教授雷添福博士致上最高的敬意。感謝他在學業研究與 生活上給我的指導與鼓勵。在這五年的學習生涯中,讓我學習到研究的態度及方 法,也讓我能充實自我的學問。此外,我也要感謝簡昭欣博士無論是在課堂上、 研究上或平日會議時給我的非常多地指導與幫助,令我獲益良多。

感謝眾學長們帶我進入半導體領域,包括李名鎮、張子云、俞正明、李介文、王哲麒、以及李宗霖學長對我的照顧及協助。特別要感謝我所帶過的兩位學弟棟煥、宗元與錦石,此論文是我們一齊努力出來的成果。此外,已畢業的李美錡及謝德慶同學,謝謝你們陪我度過漫長的實驗時間。也感謝實驗室裡一起研究的夥伴,謝明山、小強、建豪、楊紹明、伯儀、志仰、家文,以及久盟、松齡、國誠、韋翔、任逸、余俊、伯浩、宗元、梓翔、源俊、俊嘉、統億,有你們的陪伴與討論,實驗過程不再枯燥乏味而是充滿著歡樂。因為有你們的幫忙與笑聲,讓我能以快樂的心情面對實驗上與生活上的挑戰。

由衷地感激在實驗中曾給我幫助的朋友們,特別是計測實驗室的彭作煌先生,與奈米中心的徐秀鑾、林素珠、黃月美、楊月嬌、何惟梅、劉曉玲小姐以及奈米元件實驗室其他工程師們,若沒有你們的大力幫忙,我無法順利地完成此論文,在此獻上我最深的敬意。

最後,謝謝我的家人與我可愛的女友,感謝你們在我心情低落時給我打氣, 在我需要溫暖時給我照顧,謝謝你們陪我一路走過這漫長的求學生涯。僅此論文 獻給所有關心我的朋友。

## **Contents**

| Abstract (Chinese)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Abstract (English)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | III   |

| Acknowledge                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | VI    |

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VII   |

| Figure Captions & Table Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | X     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1     |

| 1.1 Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1     |

| 4,395                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6     |

| 1.3 Thesis Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| Chapter 2 Characteristics of HfO <sub>2</sub> Nanocrystal Nonvolatile Flash Memo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | rv 15 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

| The state of the s | 15    |

| 2.2 Experimental                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16    |

| 2.3 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17    |

| 2.3.1 Material Analysis of HfO <sub>2</sub> nanocrystals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17    |

| 2.3.2 Characteristics of Fresh Devices and 2-bit operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19    |

| 2.3.3 Migration of storage charges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20    |

| 2.3.4 Disturbance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22    |

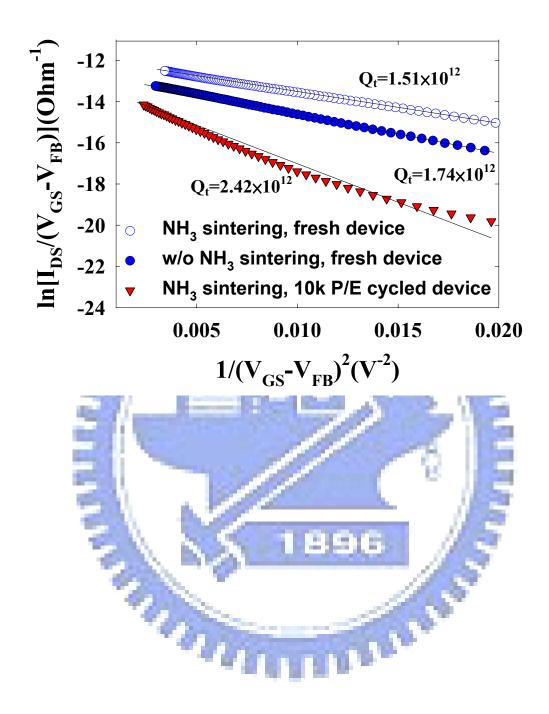

| 2.3.5 Charge pumping characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 24    |

| 2.3.6 Characteristics after P/E cycling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25    |

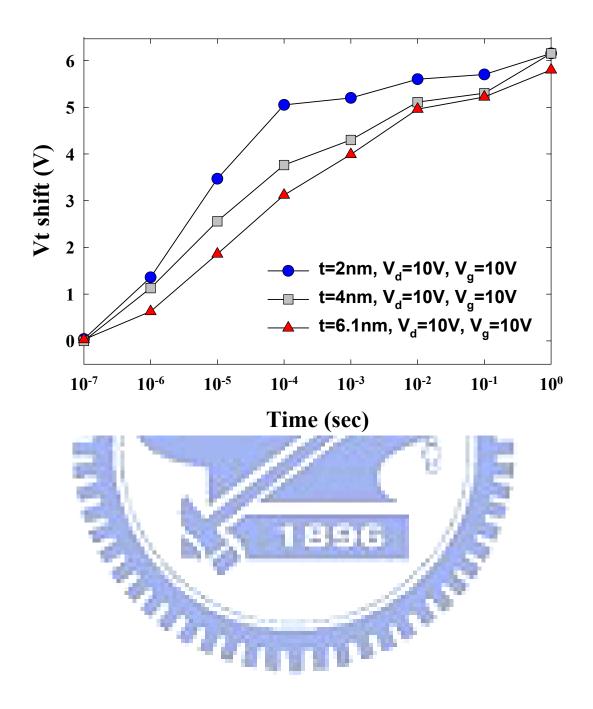

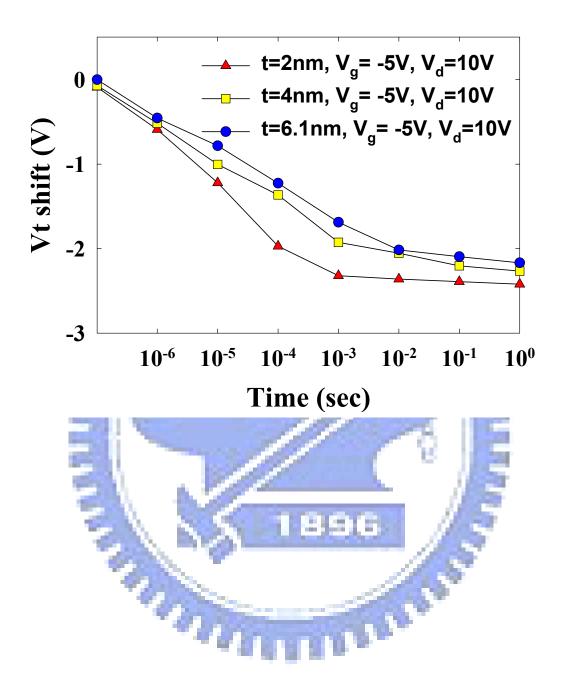

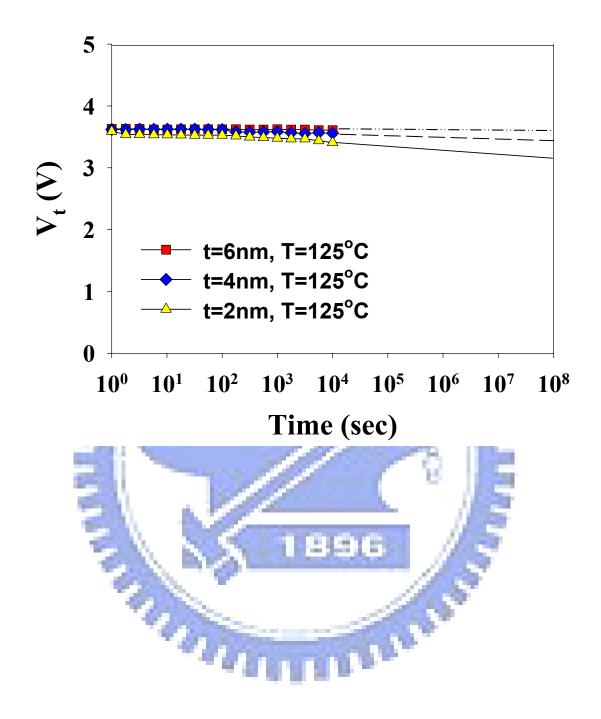

| 2.3.7 Characteristics of different tunnel oxide thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 2.3.8 Vt distribution and realization of multi-bit operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28    |

| 2.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |

| ·· J · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

| Chapter 3 Annealing Temperature Effect on the Performance of | of Nonvolatile |

|--------------------------------------------------------------|----------------|

| HfO <sub>2</sub> SONOS-type Flash Memory                     | 61             |

| 3.1 Introduction.                                            | 61             |

| 3.2 Experimental                                             | 62             |

| 3.3 Results and Discussion.                                  | 62             |

| 3.3.1 Devices Operation.                                     | 62             |

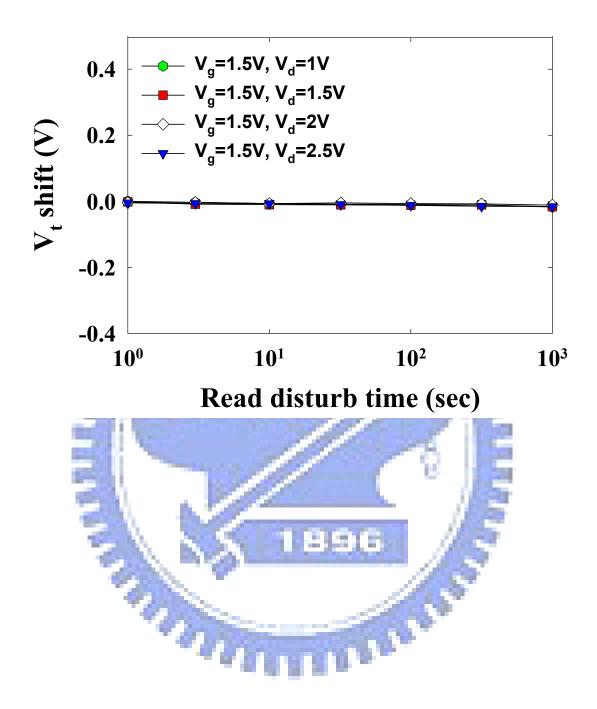

| 3.3.2 Disturbances                                           | 64             |

| 3.3.3 Charge pumping characteristics                         | 66             |

| Co. Section 1                                                | 66             |

|                                                              | b              |

| Chapter 4 Low Temperature Polycrystalline Silicon Thin-Film  | Flash Memory   |

| with High-k Materials                                        | 79             |

| 4.1 Introduction.                                            | 79             |

| 4.2Experimental                                              | 80             |

| 4.3 Results and Discussion                                   | 80             |

| 4.3.1 Material Analysis                                      | 80             |

| 4.3.2 Characteristics of three kinds of high-k TFT memories. | 81             |

| 4.3.3 Comparison of different tunnel oxide thickness         | 82             |

| 4.3.4 Disturbance characteristics                            |                |

| 4.3.5 Channel dangling bonds                                 |                |

| 4.4 Summary                                                  |                |

| Sannaa,                                                      |                |

| Chapter 5 Nano Scaled Tri-Gate HfO2 Nanocrystal Flash Mem    | ory on SOI110  |

| 5.1 Introducion.                                             | 110            |

| 5.2 Experimental                                             | 111            |

| 5.3 Results and Discussion                                   | 111            |

| 5.3.1 Material Analysis of HfO <sub>2</sub> Nanocrystal memory      | 111  |

|---------------------------------------------------------------------|------|

| 5.3.2 Characteristics of Fresh Devices and 2-bit operation          | 112  |

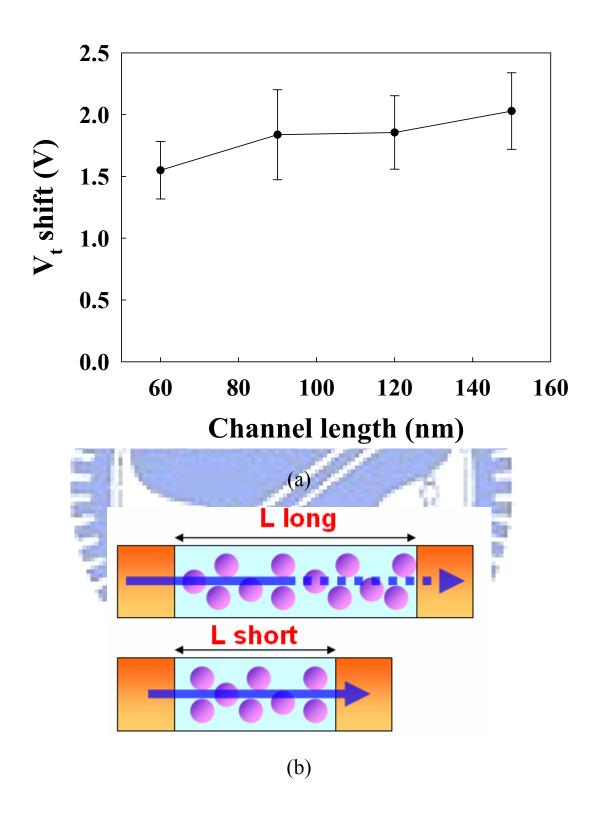

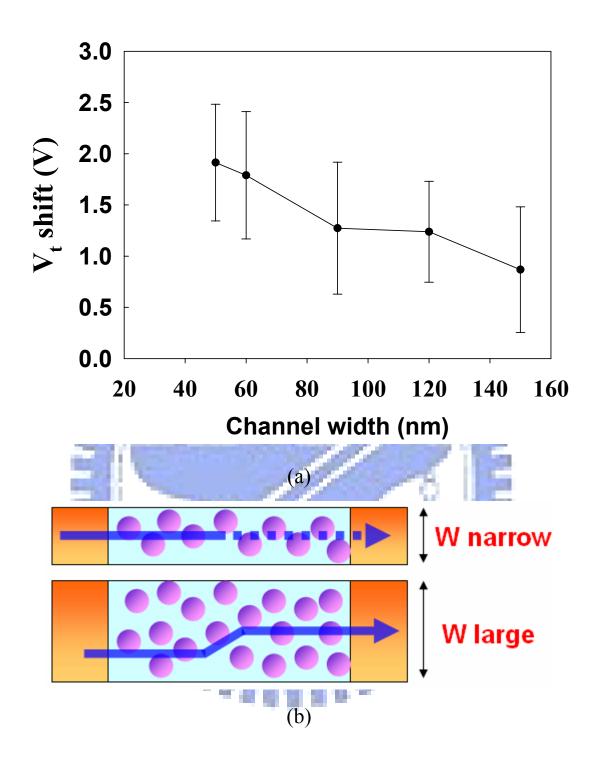

| 5.3.3 Different Length and width characteristics                    | 113  |

| 5.3.4 Disturbances.                                                 | 114  |

| 5.3.5 Few Electron Effect.                                          | 114  |

| 5.4 Summary                                                         | 116  |

| Chapter 6 2-Bit Lanthanum Oxide Trapping Layer Nonvolatile Flash Me |      |

|                                                                     | 130  |

| 6.1 Introduction                                                    | 130  |

| 6.2 Experimental                                                    | 131  |

| 6.3 Results and Discussion                                          | 131  |

| 6.3.1 Devices Operation                                             | 131  |

| 6.3.2 Disturbances                                                  | 133  |

| 6.4 Summary                                                         | 134  |

|                                                                     |      |

| Chapter 7 Conclusions and Further Recommendations                   | 147  |

| Spall of All management 1864                                        | 1.45 |

| 7.1 Conclusions                                                     | 147  |

| 7.2 Further Recommendations                                         | 148  |

| THE REAL PROPERTY.                                                  |      |

| Reference                                                           | 150  |

#### Vita

#### **Publication list**

## **Figure Captions**

#### Chapter 1

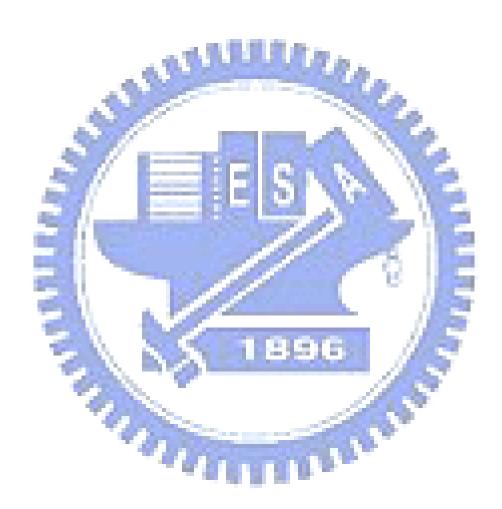

- Fig. 1.1 (a)Schematic of a basic ETOX flash memory device. (b) Electron flow (red arrows) during programming by CHE injection. Electron flow (green arrows) or hole flow (orange arrows) during erasing by FN tunneling or BTBTHH injection to the source.

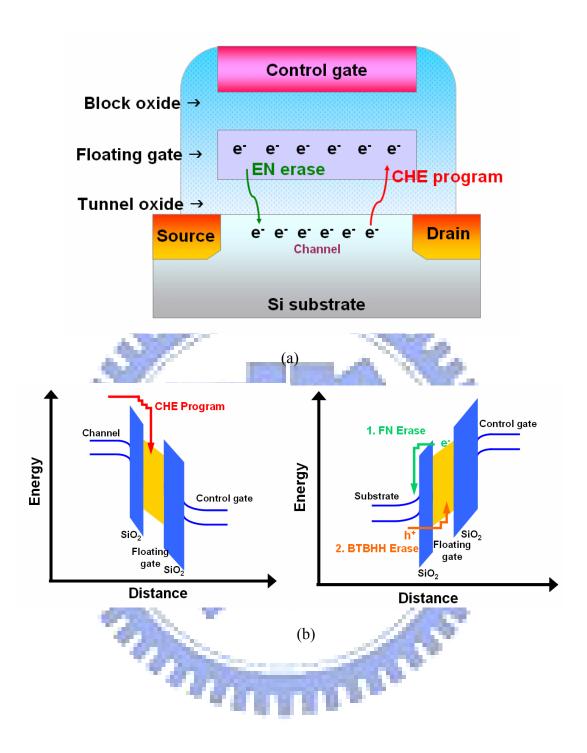

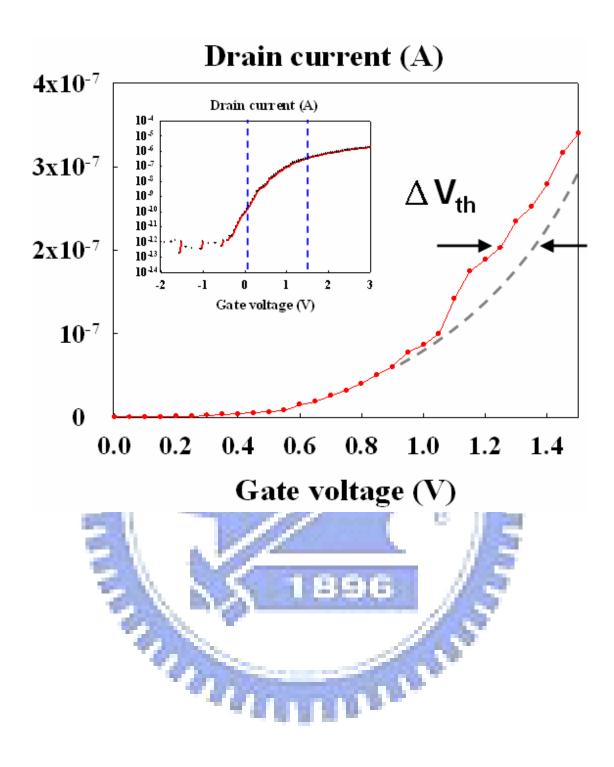

- Fig. 1.2 Current-voltage characteristic of a memory device in the erased and programmed state, showing the VT shift and the memory window.

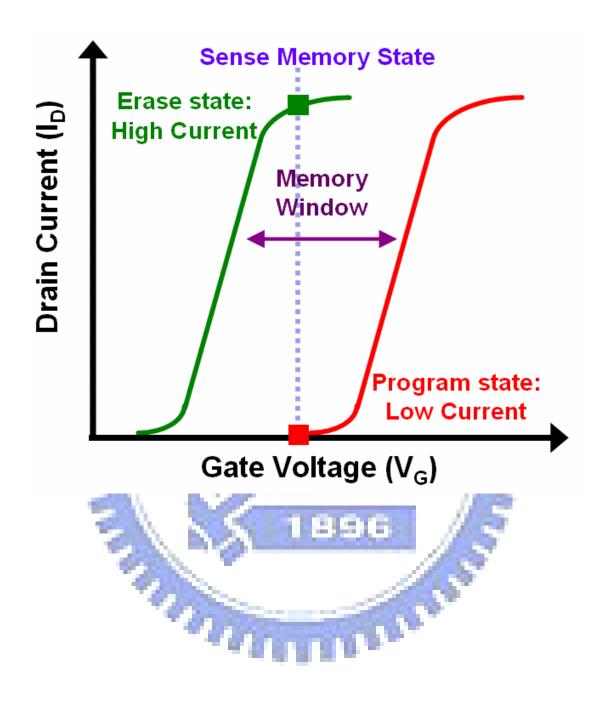

- Fig. 1.3 (a) Charges in the dielectric stored in isolated storage nodes. (b) A schematic of a continuous FG structure with all the charges drained by an isolated defect in the dielectric.

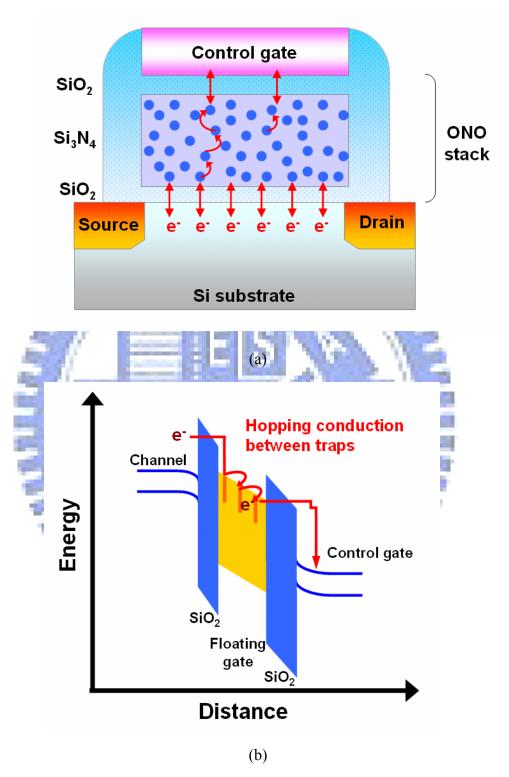

- Fig. 1.4 (a) Basic SONOS memory device structure. Red arrows show paths of electron transport during memory operation. The electrons hop between trap.(b) Energy diagram illustrating the physical process of a typical SONOS program operation sites (blue dots) within the Si3N4 layer.

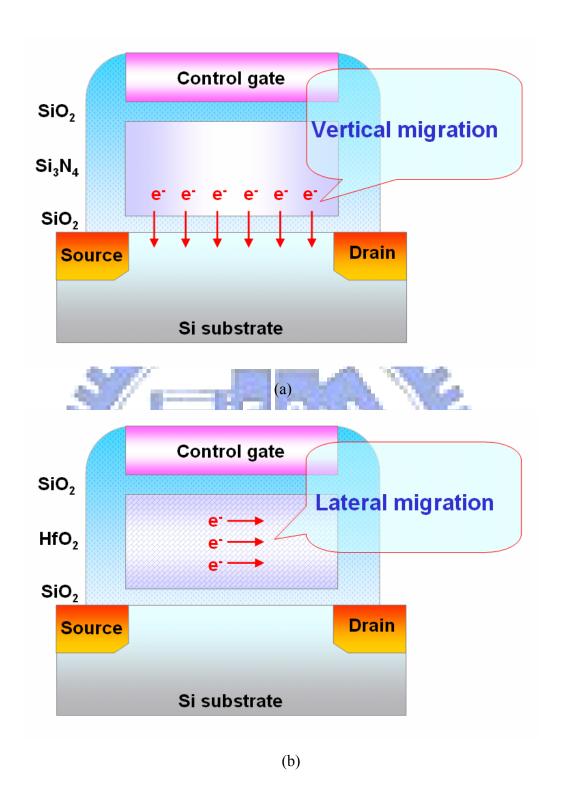

- Fig. 1.5 (a) Vertical migration of the stored charge in the Si<sub>3</sub>N<sub>4</sub> trapping layer in SONOS memory device structure. (b) Lateral migration of the stored charge in the HfO<sub>2</sub> trapping layer in SONOS memory device structure.

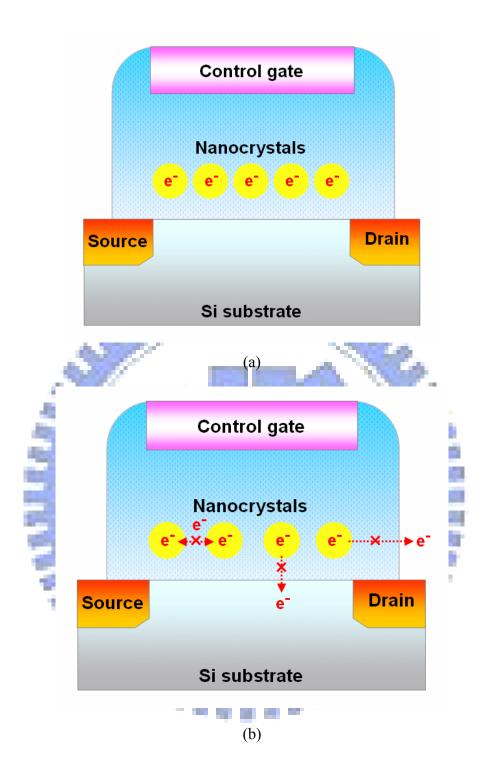

- Fig. 1.6 (a) An illustration of a nanocrystal Memory. (b) The nanocrystal can store the charge locally due to the well isolation of nanocrystals from each other and effectively prevents formation of good conductive paths between the adjacent nodes

#### Chapter 2

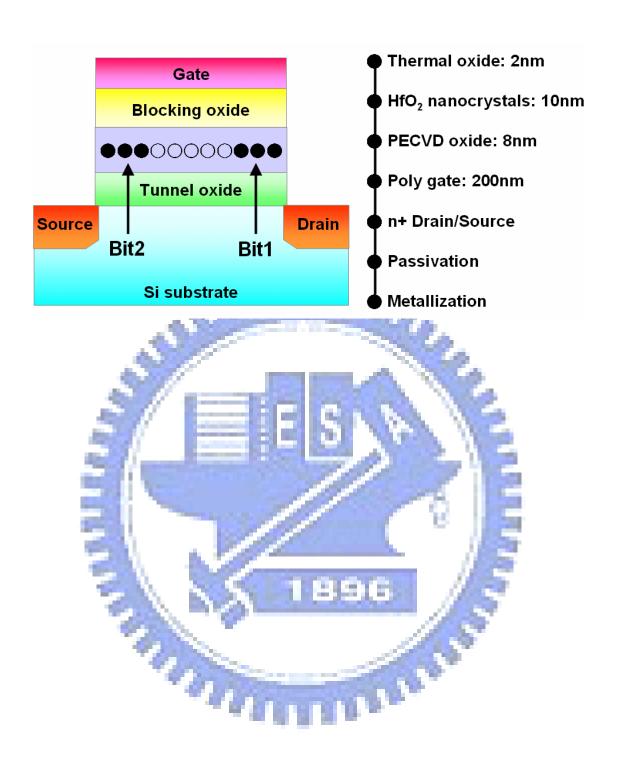

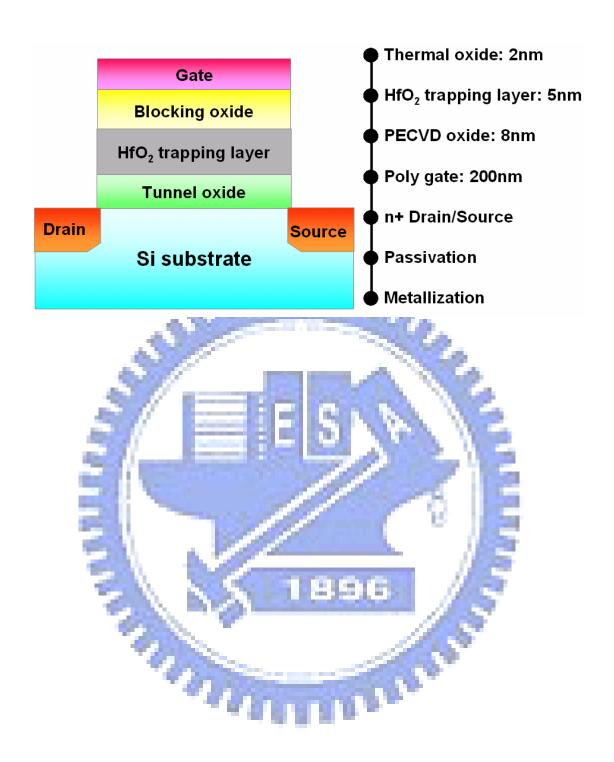

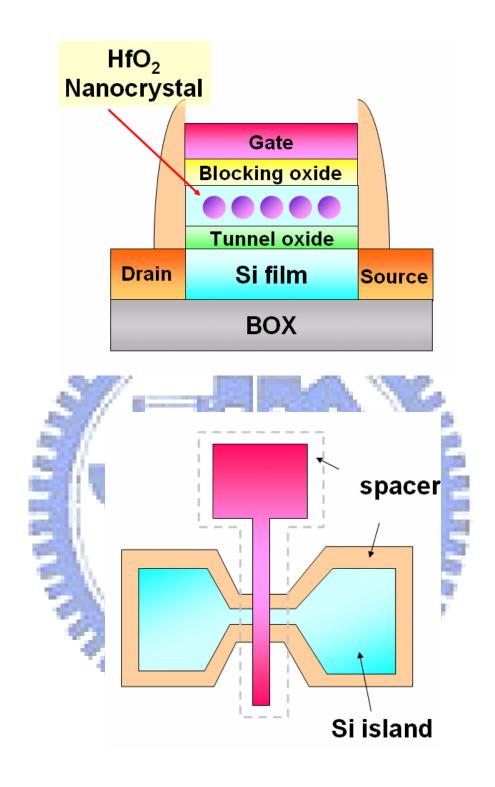

Fig. 2.1 Schematic representation of the HfO<sub>2</sub> nanocrystal Flash memory cell structure

- and localized charge storage.

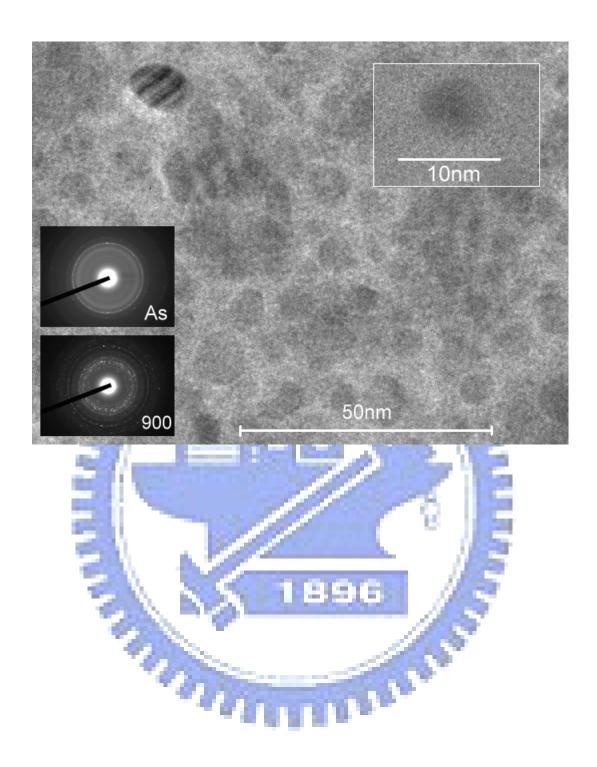

- Fig. 2.2 Planar-view HRTEM image of the  $HfO_2$  nanocrystals. The cell size is 5-8 nm and the dot density is  $0.9\text{-}1.9 \times 10^{12}$  cm<sup>-2</sup>. The inset shows the diffraction patterns of the as-deposited and  $900^{\circ}\text{C-RTA-treated}$  samples.

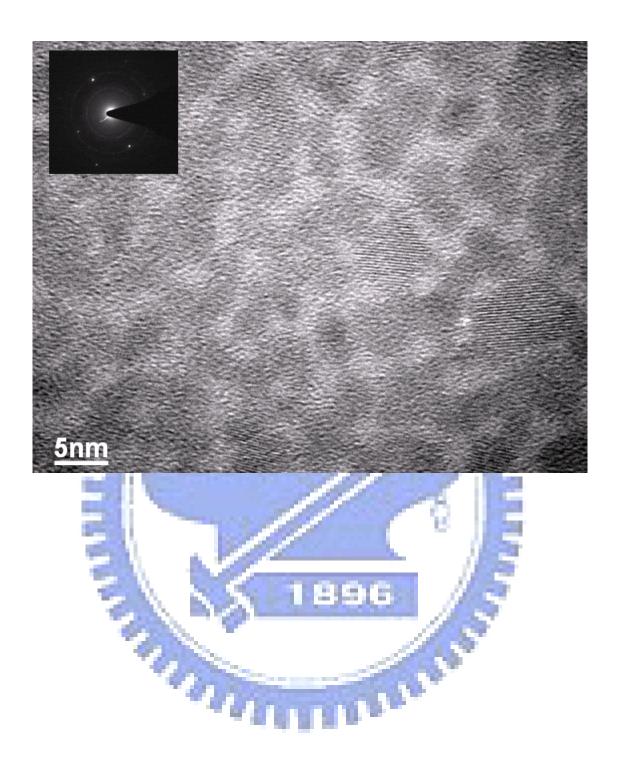

- Fig. 2.3 (a) Planar-view HRTEM image of the  $HfO_2$  nanocrystals for the 2nm thickness sample. The cell size is 3-7 nm and the dot density is  $1.2-2.0 \times 10^{12}$  cm<sup>-2</sup>. The inset shows the diffraction pattern of the RTA-treated samples.

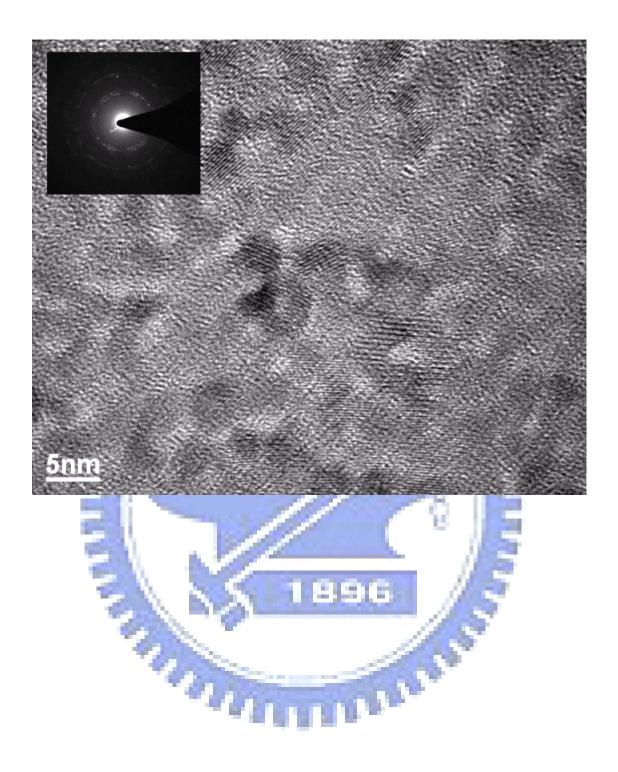

- Fig. 2.3 (b) Planar-view HRTEM image of the  $HfO_2$  nanocrystals for the 2nm thickness sample. The cell size is 4-7 nm and the dot density is  $2.1-3.2 \times 10^{12}$  cm<sup>-2</sup>. The inset shows the diffraction pattern of the RTA-treated sample.

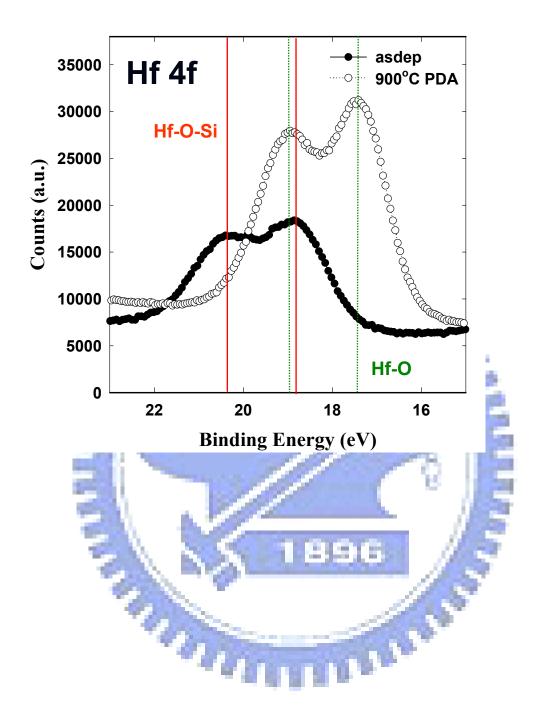

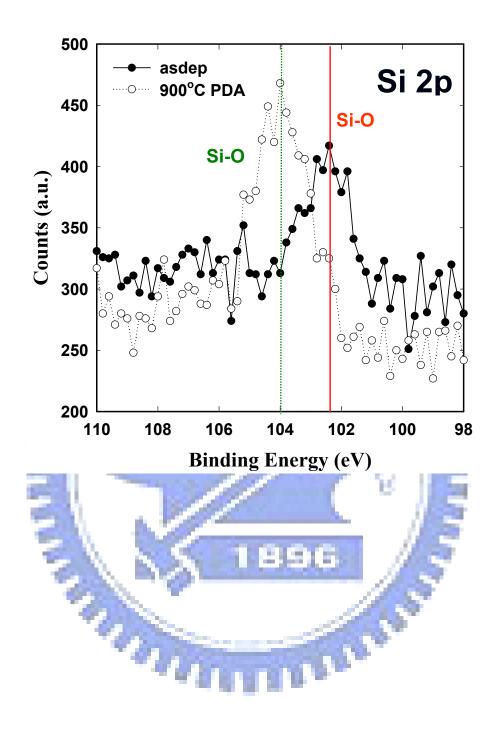

- Fig. 2.4 XPS spectra of the as-deposited and 900°C-RTA-treated samples. (a) Hf 4f; (b) Si 2p. These spectra indicate that the Hf-silicate was fully converted to HfO<sub>2</sub> and SiO<sub>2</sub> through phase separation after PDA at 900 °C under O<sub>2</sub>.

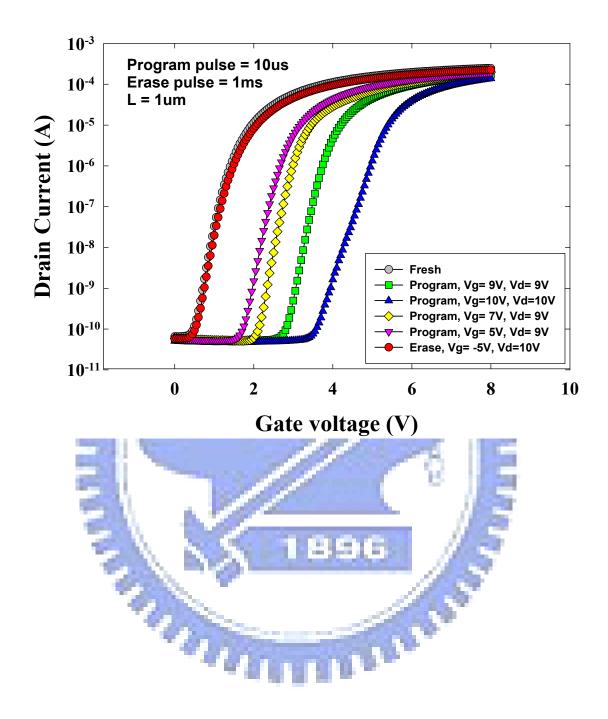

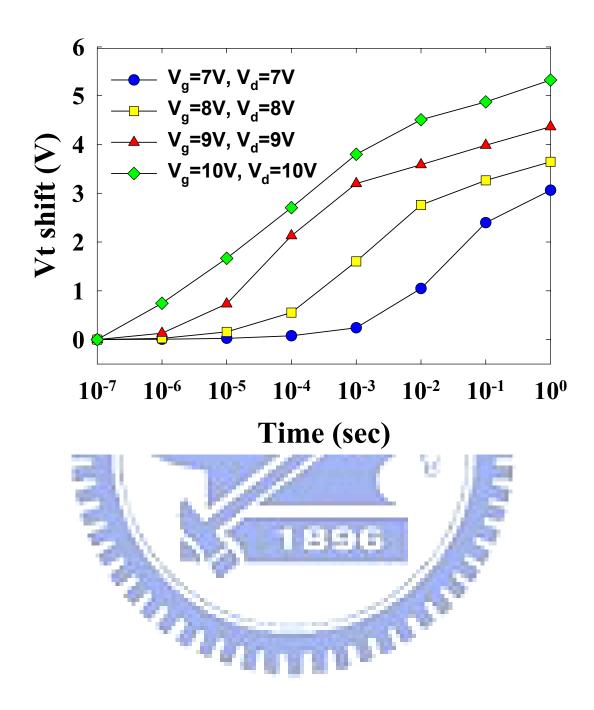

- Fig. 2.5  $I_{ds}$ - $V_{gs}$  curves of programmed memories with different programming conditions. The programming time is  $10\mu s$ . A memory window of larger than 3V can be achieved with  $V_g$ = $V_d$ =10V programming operation.

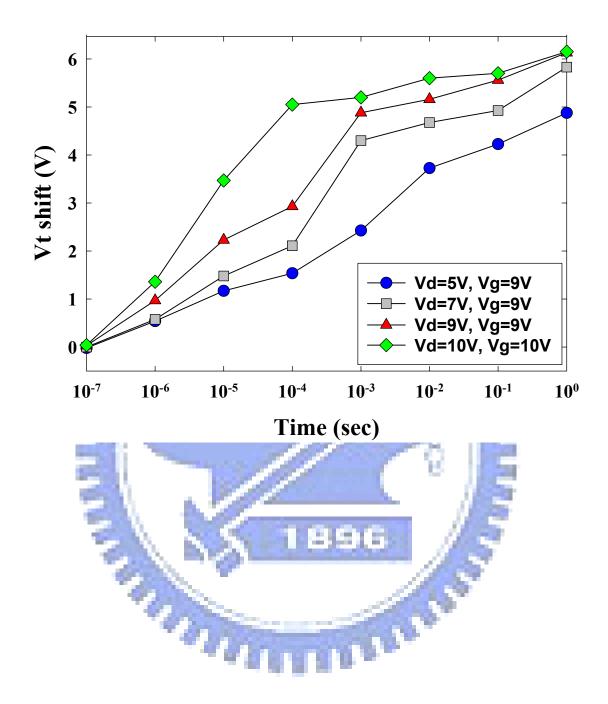

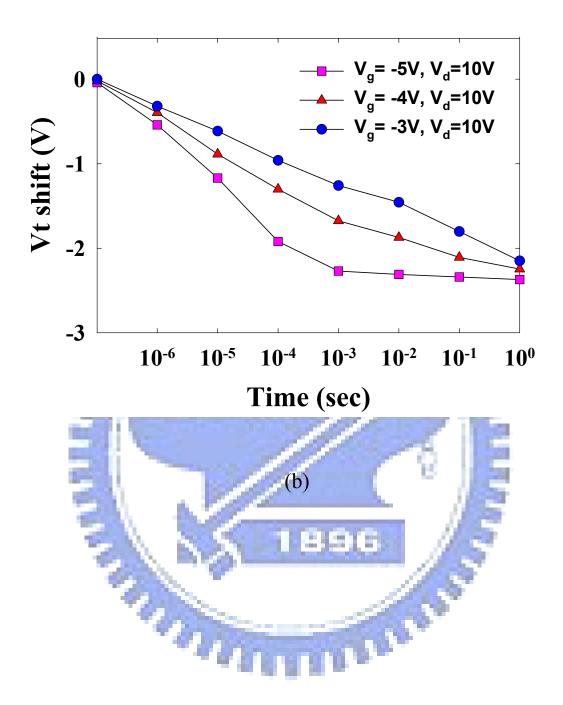

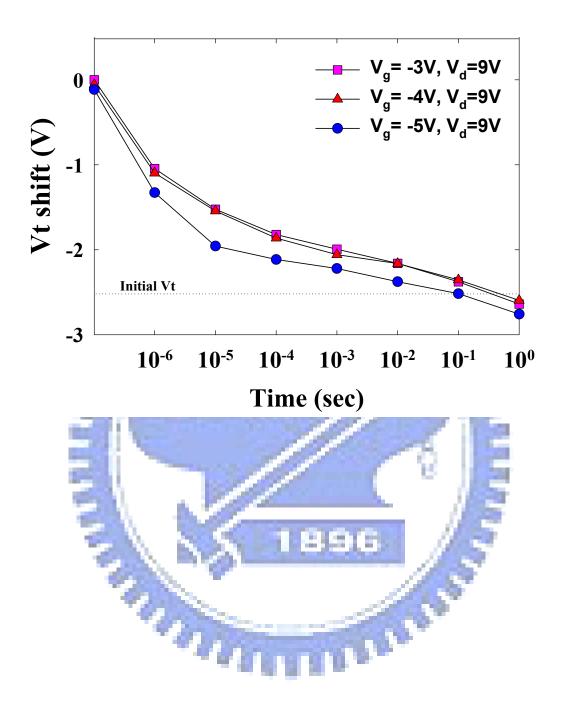

- Fig. 2.6 (a) Program characteristics of  $HfO_2$  nanocrystal memory devices with different programming conditions. A memory window of about 5V can be achieved with  $V_g=V_d=10V$ , and time=100 $\mu$ s programming operation. (b). Erase characteristics of  $HfO_2$  nanocrystal memory devices with different erasing voltages.

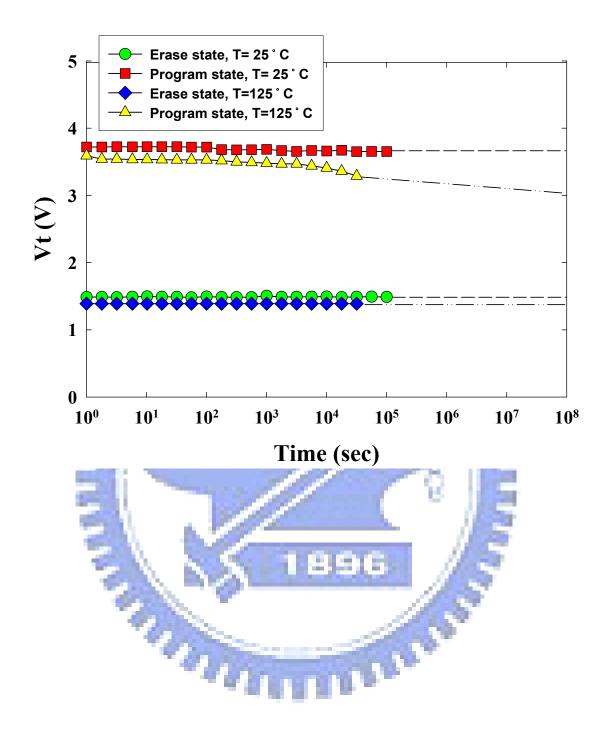

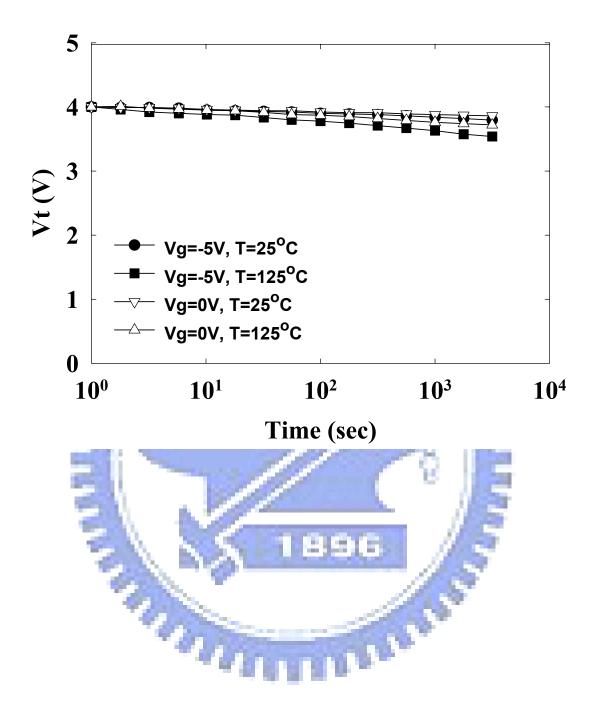

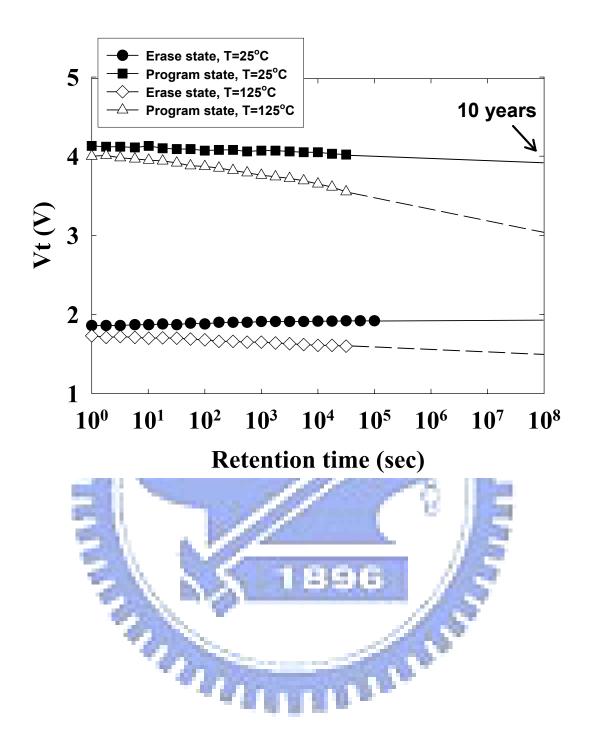

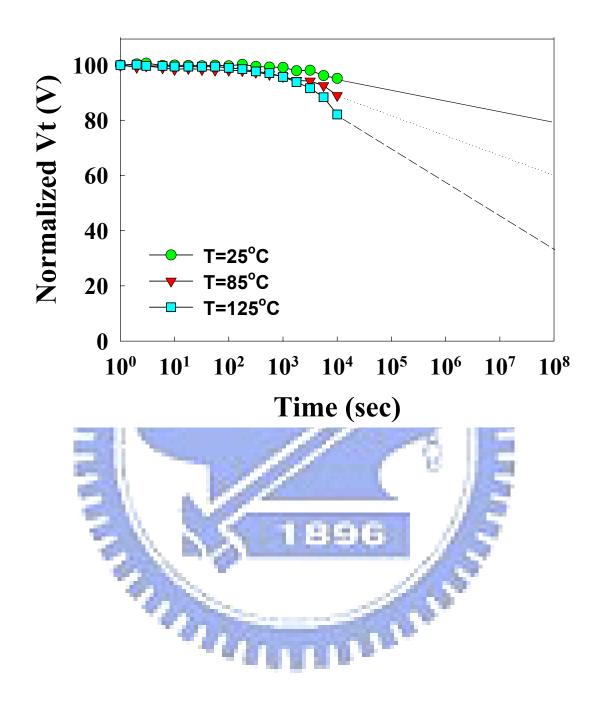

- Fig. 2.7 Retention characteristics of HfO<sub>2</sub> nanocrystal memory devices at T=25°C and 125°C. Very low charge loss is seen even after 10<sup>5</sup> seconds.

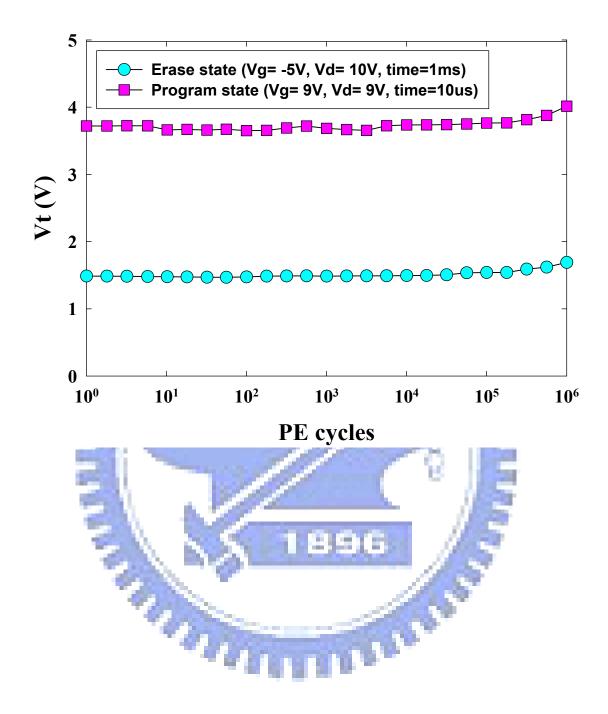

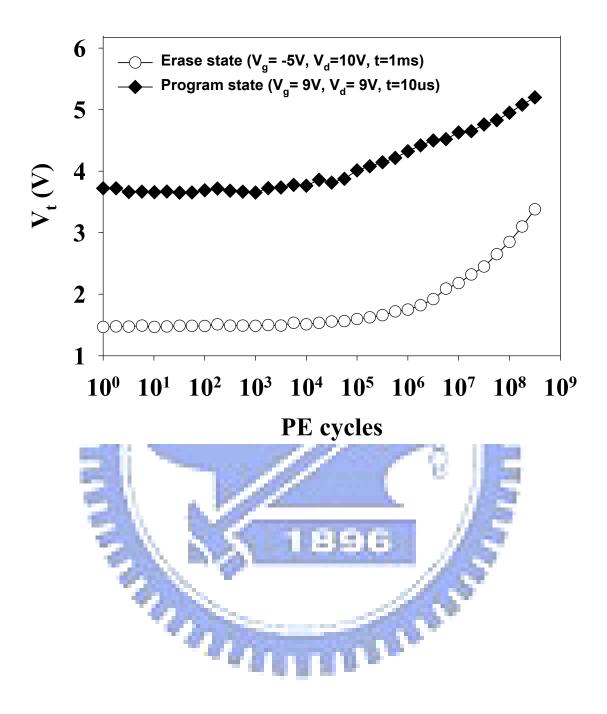

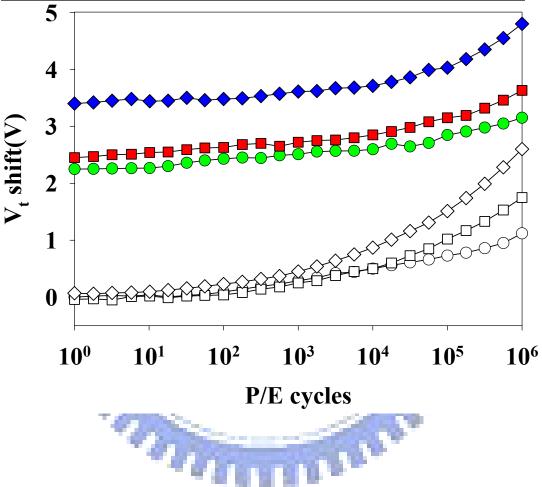

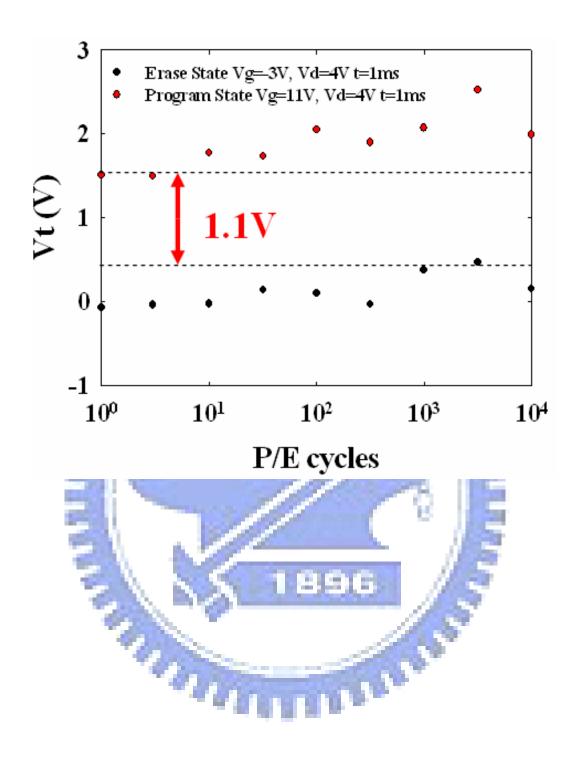

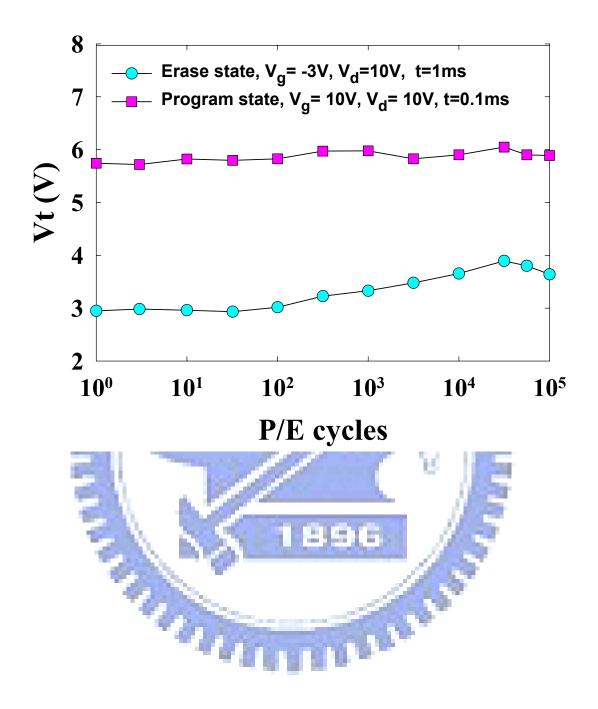

- Fig. 2.8 Endurance characteristics of HfO<sub>2</sub> nanocrystal memory devices. Negligible

- degradation is found even after 10<sup>6</sup> P/E cycles.

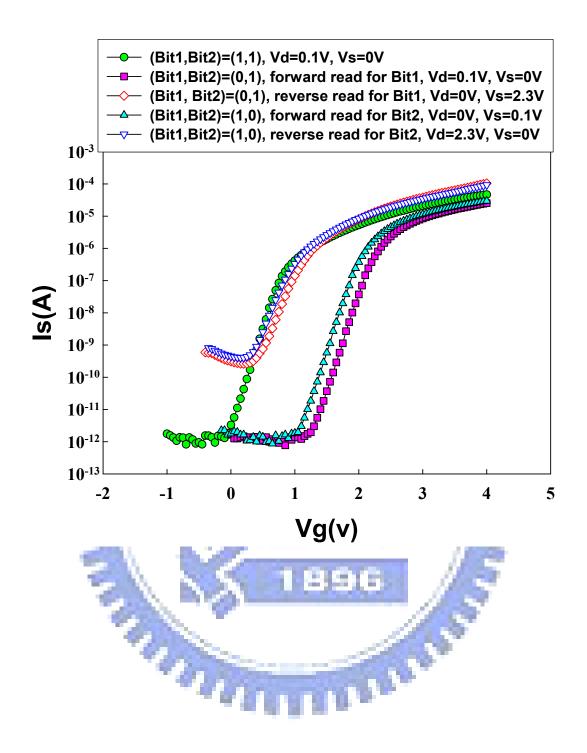

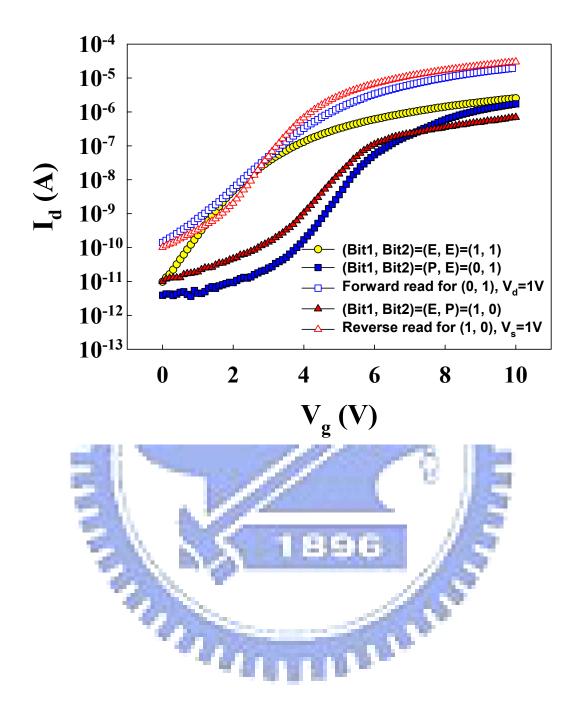

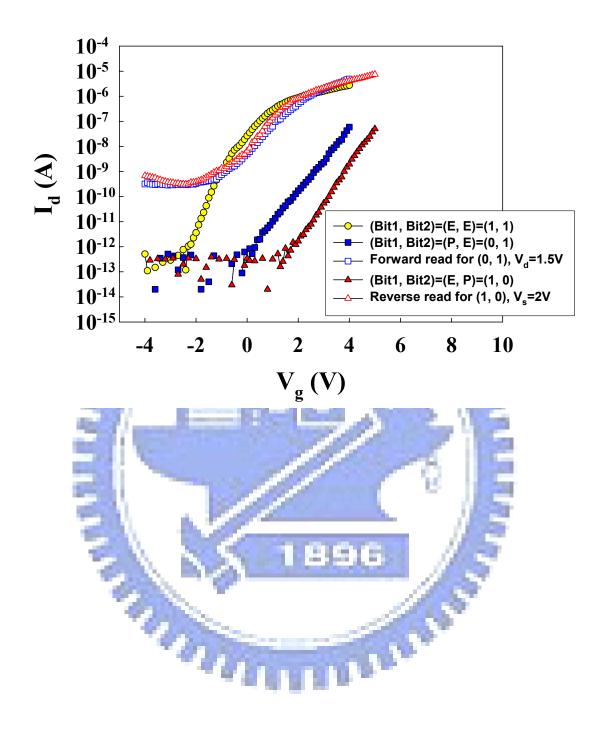

- Fig. 2.9  $I_{ds}$ – $V_{gs}$  Curves of the two-bit memory in a cell; forward read and reverse read for programmed bit1 and programmed bit2.

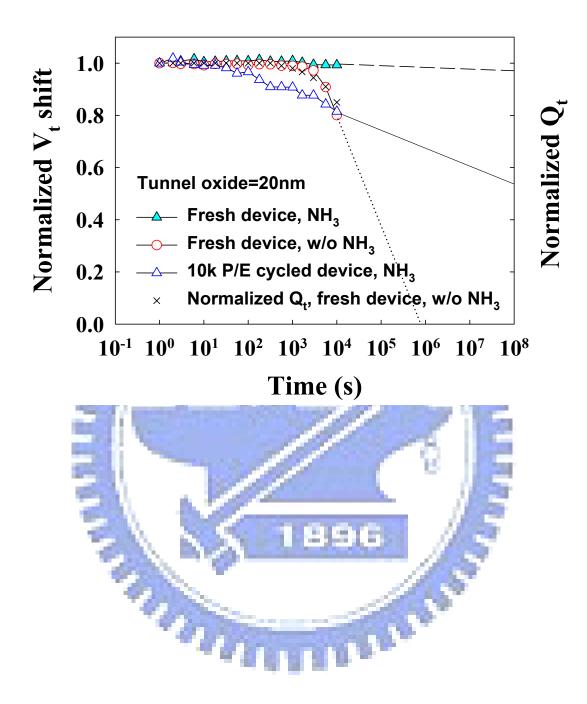

- Fig. 2.10 Vertical charge migration characteristics of the HfO<sub>2</sub> nanocrystal Flash memory cells after 10k P/E cycling.

- Fig. 2.11 Lateral charge migration characteristics of the HfO<sub>2</sub> nanocrystal Flash memory cells after 10k P/E cycling.

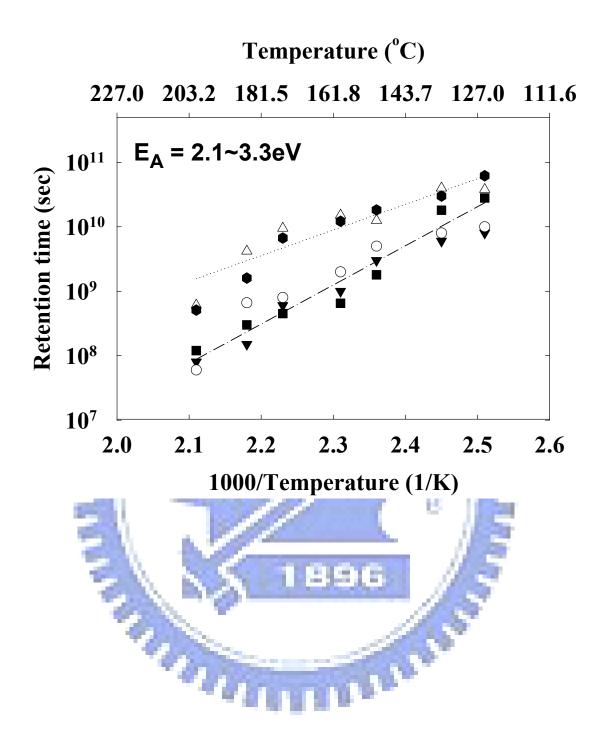

- Fig. 2.12 Activation energy characteristics of the HfO<sub>2</sub> nanocrystal Flash memory cells taken from five samples.

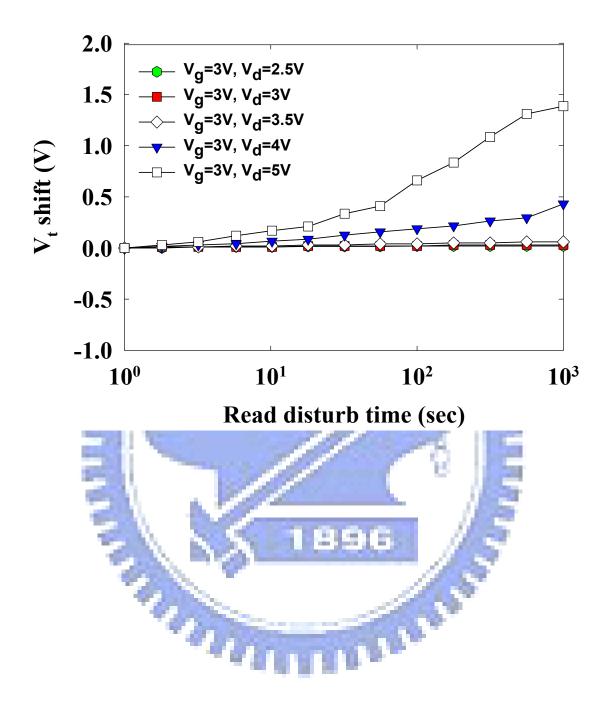

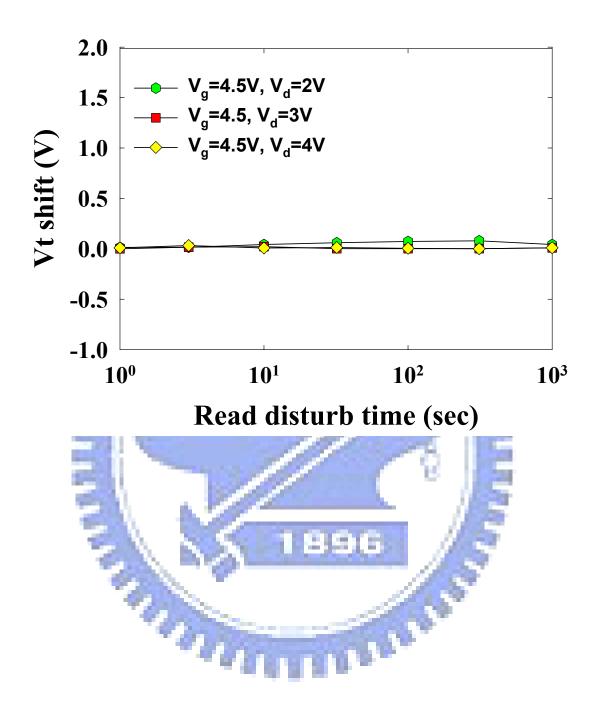

- Fig. 2.13 Read disturbance characteristics of the  $HfO_2$  nanocrystal memory devices. No significant  $V_t$  shift occurred for  $V_d < 4$ , even after 1000 s at 25 °C.

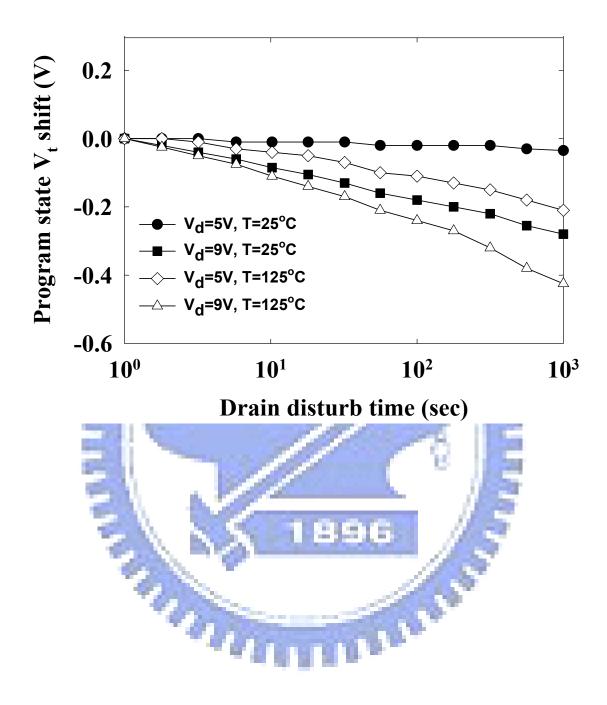

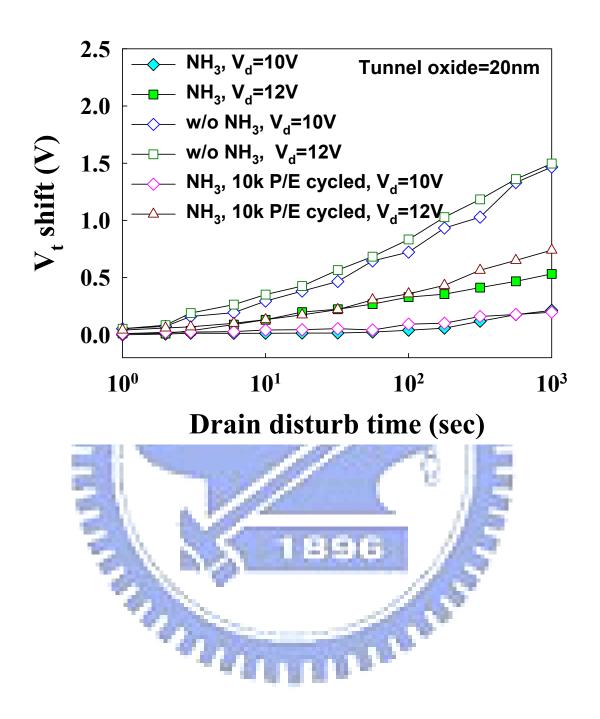

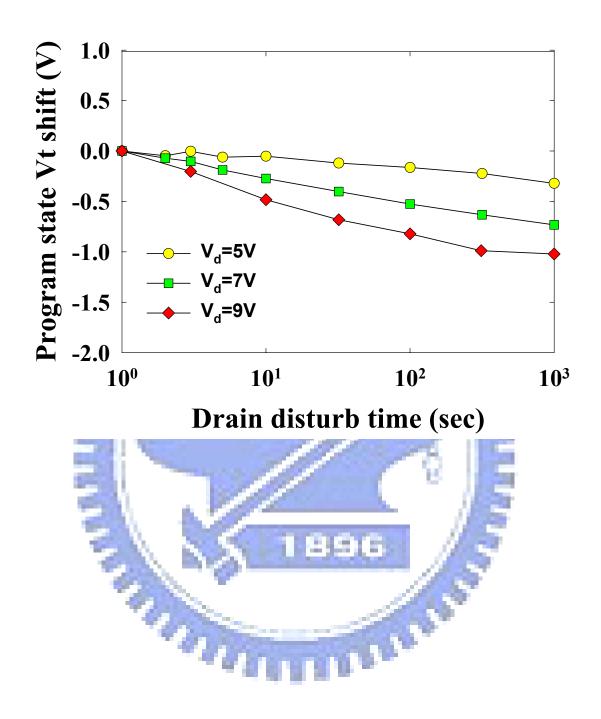

- Fig. 2.14 Drain disturbance characteristics of the HfO<sub>2</sub> nanocrystal memory cells.

After 1000 s at 25 °C, only a 0.3V drain disturb margin was observed.

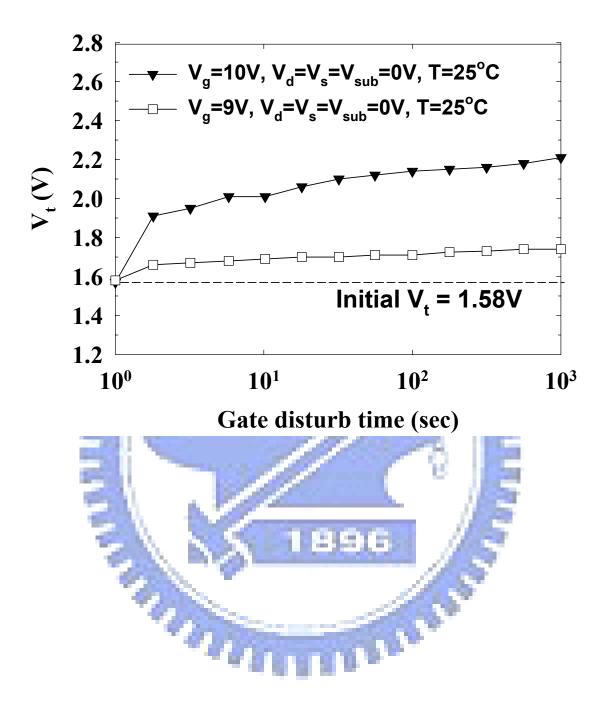

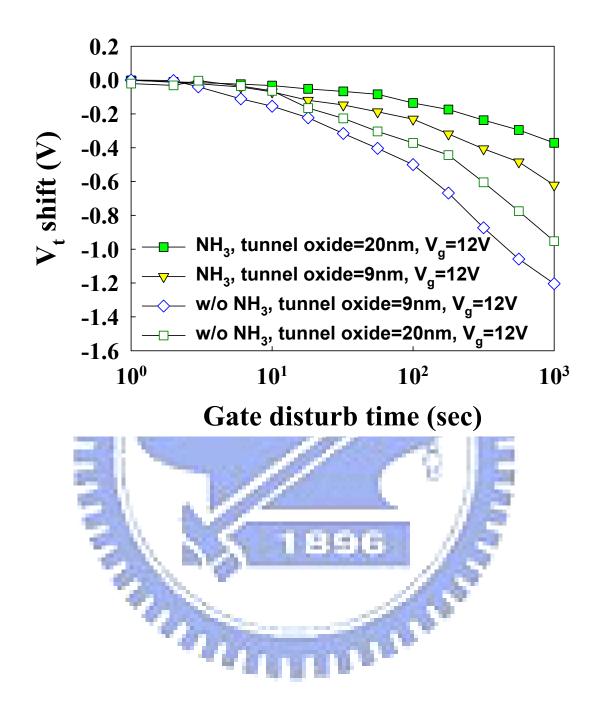

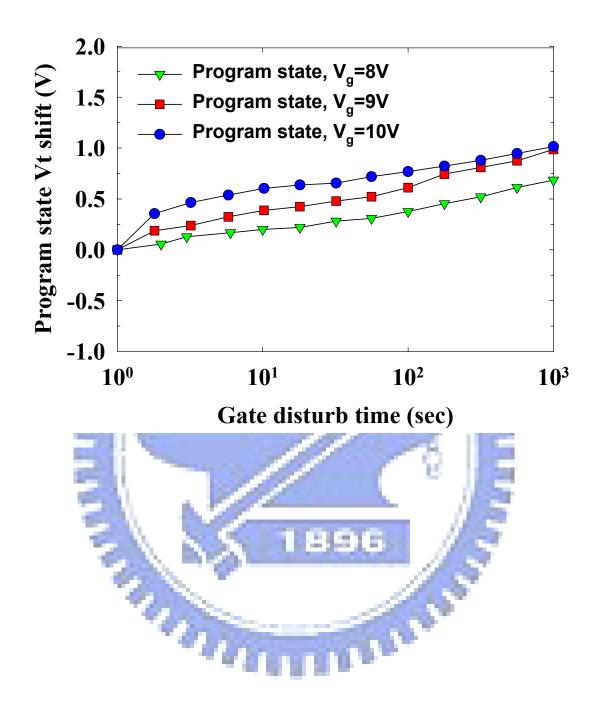

- Fig. 2.15 Gate disturbance characteristics of the  $HfO_2$  nanocrystal memory devices. A threshold voltage shift of only 0.22 V occurred after stressing at  $V_g = 9$  V and  $V_s = V_d = V_{sub} = 0$  V for 1000 s.

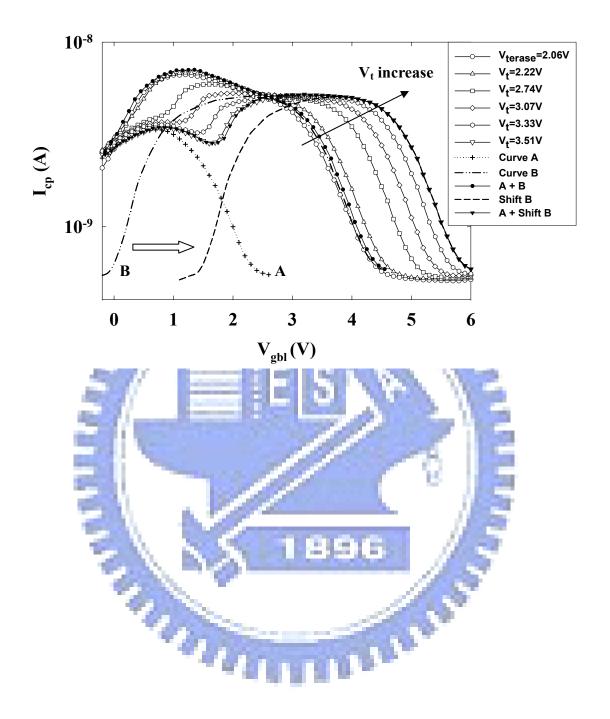

- Fig. 2.16 Plots of  $I_{cp}$  vs  $V_{gbl}$  for the  $HfO_2$  nanocrystal memory cell after F–N programming to different  $V_t$  levels.

- Fig. 2.17 Endurance characteristics of the HfO<sub>2</sub> nanocrystal memory after 10k P/E cycling.

- Fig. 2.18 Retention characteristics of the HfO<sub>2</sub> nanocrystal memory after 10k P/E cycling at 25 and 125 °C. No significant charge loss occurred at 25 °C; and only a very low charge loss occurred at 125 °C.

- Fig. 2.19 Program characteristics of HfO<sub>2</sub> nanocrystal memory devices with different tunnel oxide thickness for different programming conditions

- Fig. 2.20 Erase characteristics of HfO<sub>2</sub> nanocrystal memory devices with different

- tunnel oxide thickness for different programming conditions

- Fig. 2.21 Retention characteristics of HfO<sub>2</sub> nanocrystal memory devices at 125°C with different tunnel oxide thickness.

- Fig. 2.22 The activation energy of the traps in the HfO<sub>2</sub> nanocrystals for the fresh device with different tunnel thickness

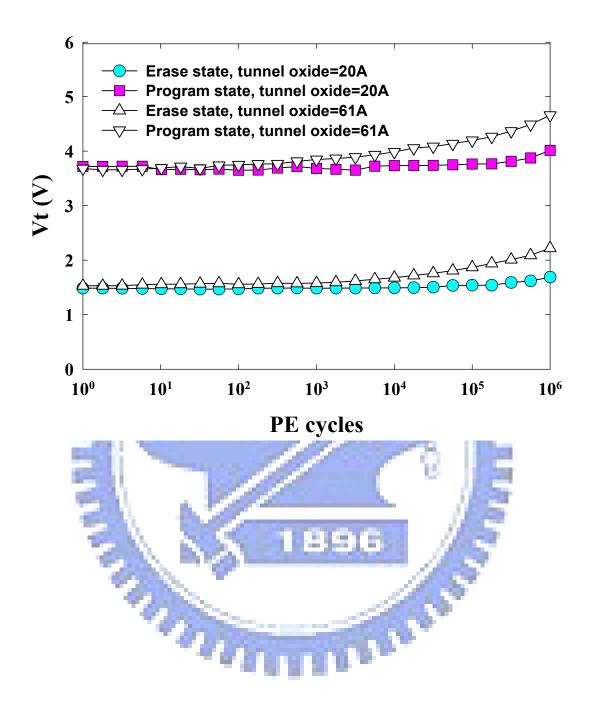

- Fig. 2.23 Endurance characteristics of HfO<sub>2</sub> nanocrystal memory devices with different tunnel oxide thickness.

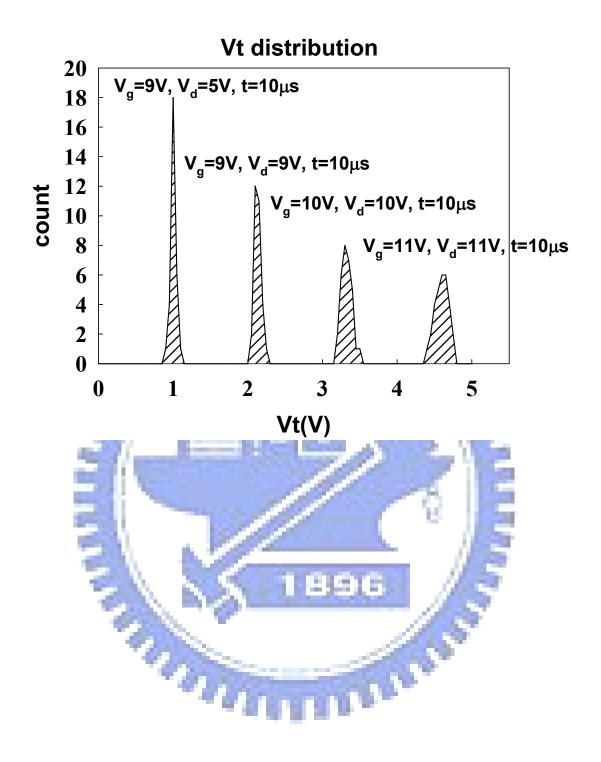

- Fig. 2.24 Four-level threshold voltage (V<sub>th</sub>) distribution of multilevel programming.

#### Chapter 3

- Fig. 3.1 Schematic cross section and process flow of the HfO<sub>2</sub> SONOS-type flash memory device.

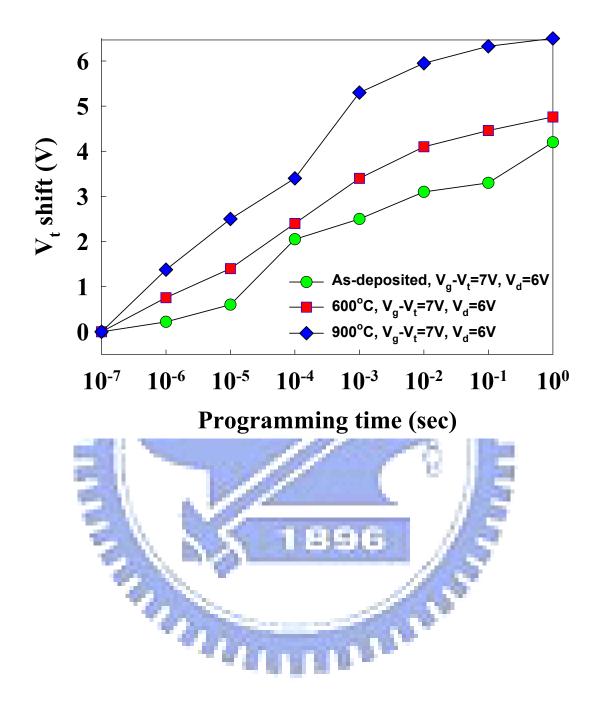

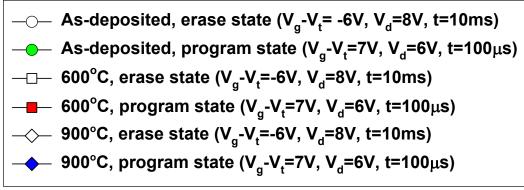

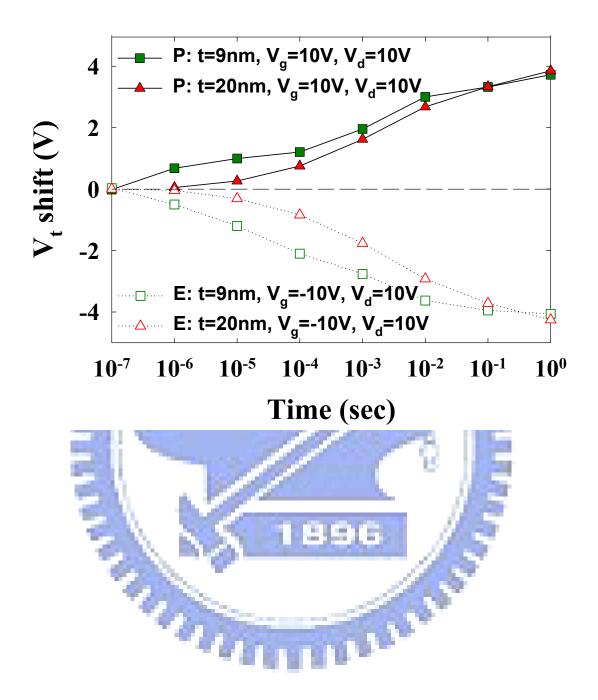

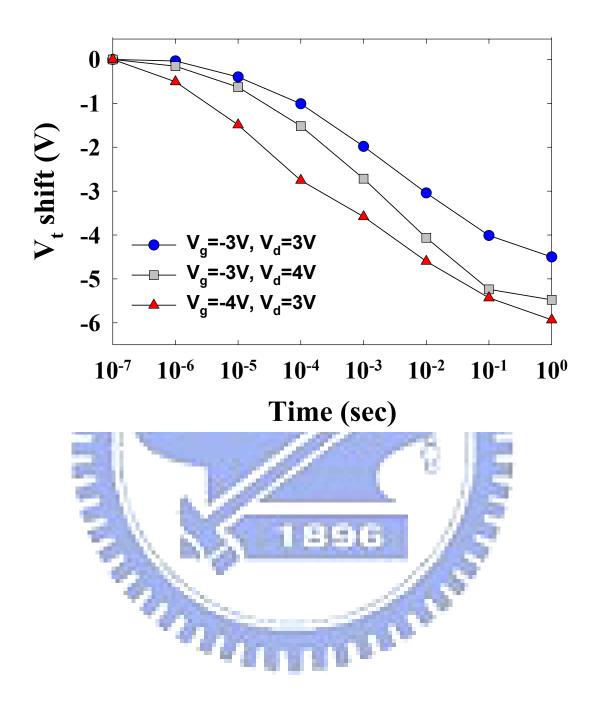

- Fig. 3.2 Programming characteristics of the HfO<sub>2</sub> SONOS-type flash memories. It was clearly observed that the programming speed and the memory window increase when the annealing temperature increases.

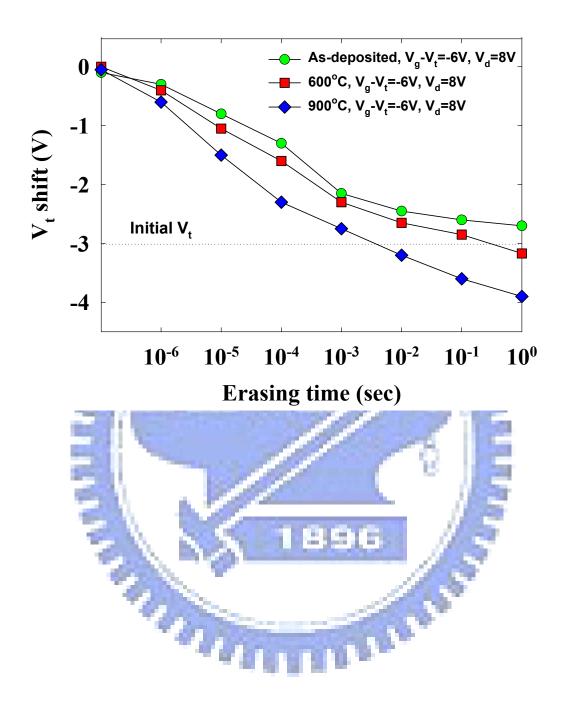

- Fig. 3.3 Erasing characteristics of the HfO<sub>2</sub> SONOS-type flash memories. With the annealing temperature increases, the erasing speed increase and shows little overerasure.

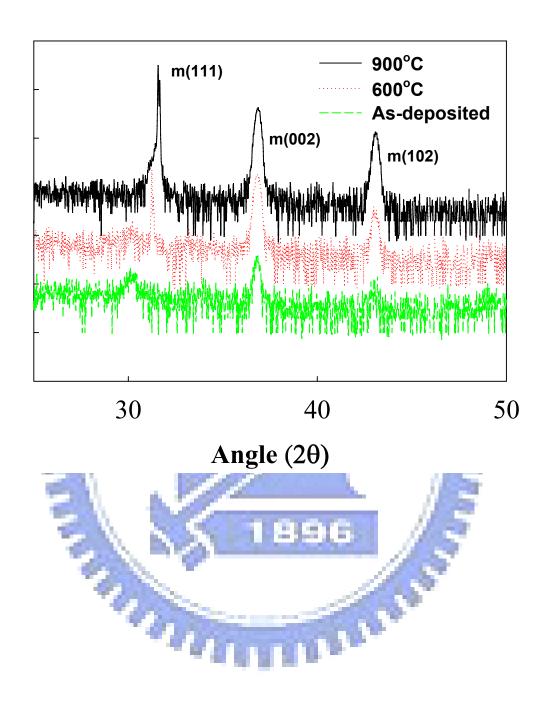

- Fig. 3.4 X-ray Diffraction (XRD) analysis of the HfO<sub>2</sub> trapping layer with different temperature.

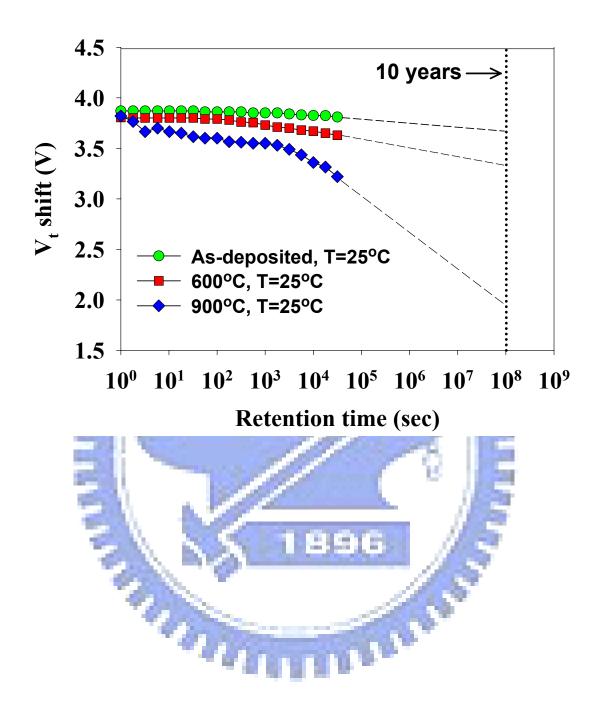

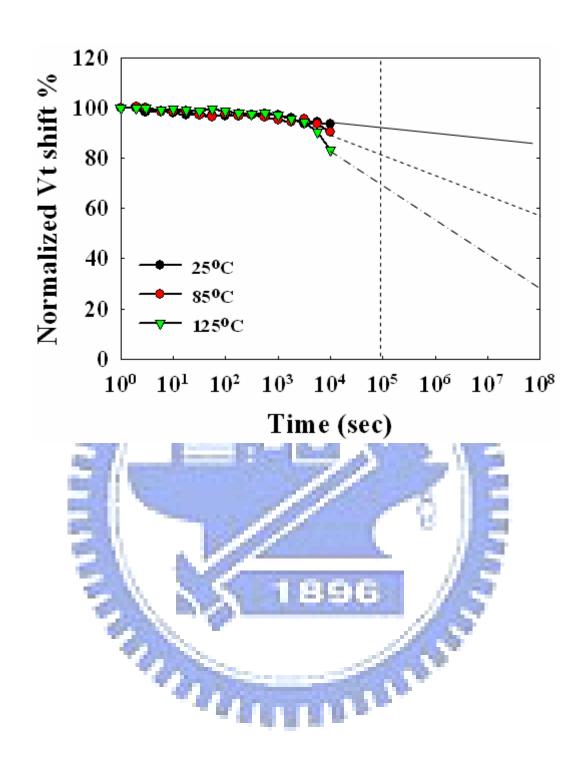

- Fig. 3.5 Retention characteristics of the HfO<sub>2</sub> SONOS-type flash memories at room temperature T=25°C. The 900°C-annealed device shows the worst retention performance.

- Fig. 3.6 Endurance characteristics of the HfO<sub>2</sub> SONOS-type flash memories. The 900° C-annealed device shows larger memory window but worse endurance performance in the same condition.

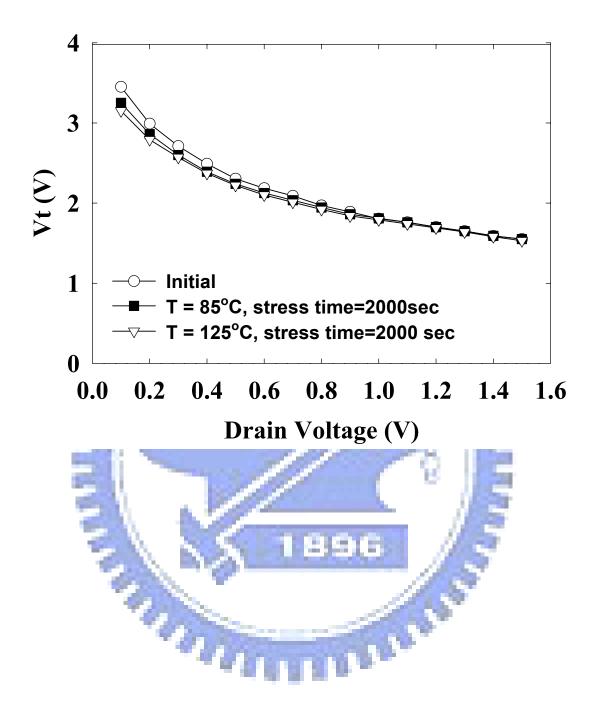

- Fig. 3.7 Vertical migration characteristics of HfO<sub>2</sub> SONOS-type flash memories.

Consistent with the former result, the vertical charge migration is exacerbated by increasing annealing temperature.

- Fig. 3.8 Read disturbance characteristics of HfO<sub>2</sub> SONOS-type flash memories. No significant V<sub>t</sub> shift for all samples even after 1000 seconds at 25°C.

- Fig. 3.9 Drain disturbance characteristics of HfO<sub>2</sub> SONOS-type flash memories. After 1000 seconds at 25°C, only 0.4V drain disturb margin is observed for the 900°C annealed devices.

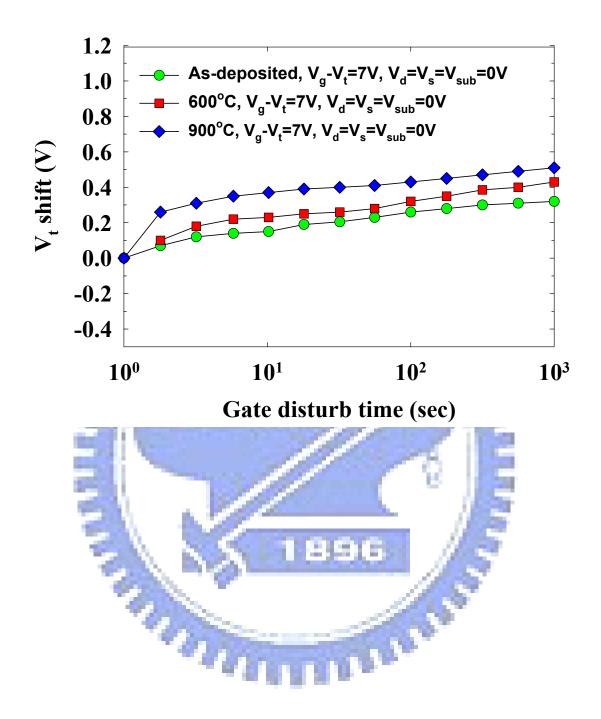

- Fig. 3.10 Gate disturbance characteristics of  $HfO_2$  SONOS-type flash memories. Only 0.5V threshold voltage shift has been observed for the 900°C annealed devices after  $V_g$ - $V_t$ =7V and  $V_s$ = $V_d$ = $V_{sub}$ =0V, 1000 seconds stressing.

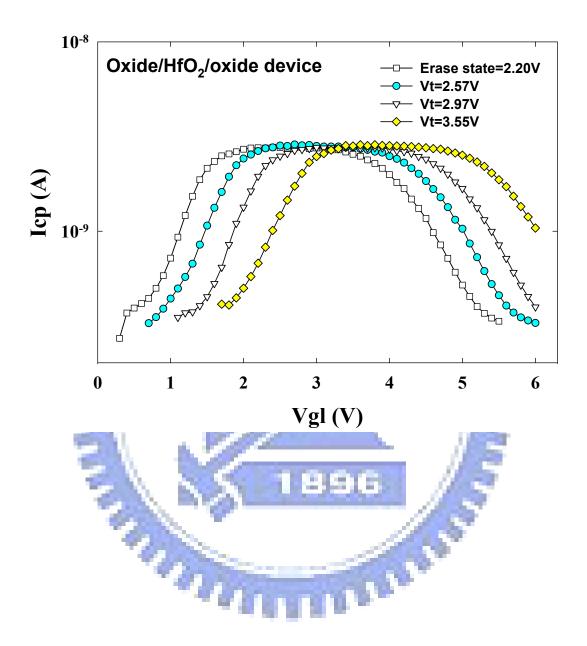

- Fig. 3.11 Plots of  $I_{cp}$  vs  $V_{gbl}$  for the  $HfO_2$  memory cell after F–N programming to different  $V_t$  levels.

#### Chapter 4

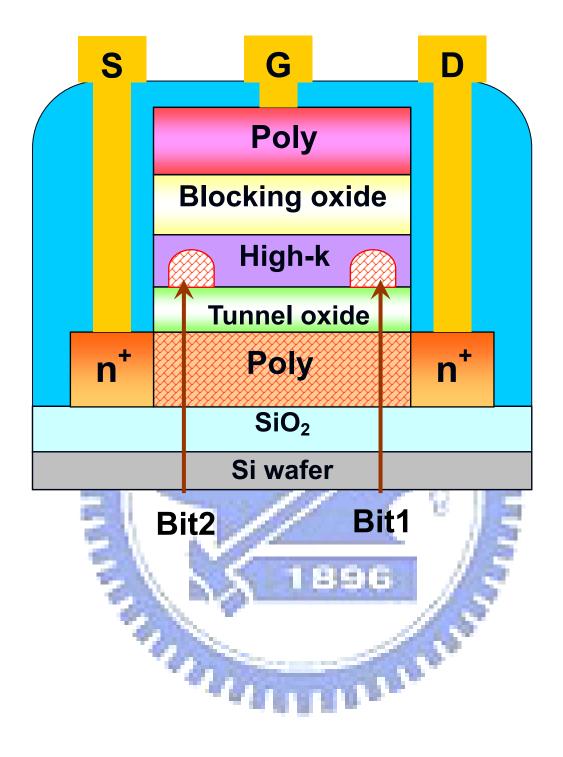

- Fig. 4.1 Schematic cross section and process flow of the high-κ dielectric poly-Si-TFT nonvolatile memories.

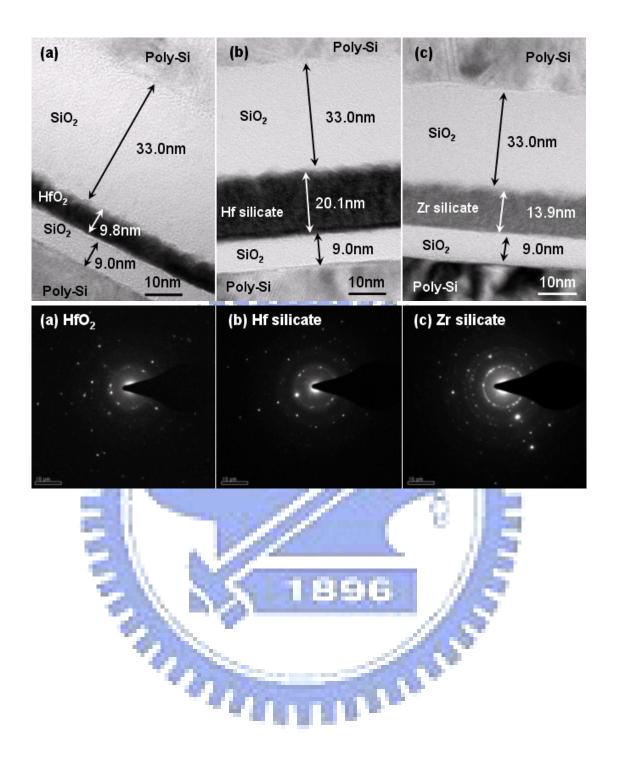

- Fig. 4.2 Cross-sectional HRTEM images of the gate stacks for the poly-Si-TFT memories with HfO<sub>2</sub>, Hf silicate and Zr silicate trapping layers. The inset show the diffraction patterns of them.

- Fig. 4.3 Demonstration of 2 bits/cell operation. E: erased; P: programmed; Bit1: drain side; Bit2: source side.

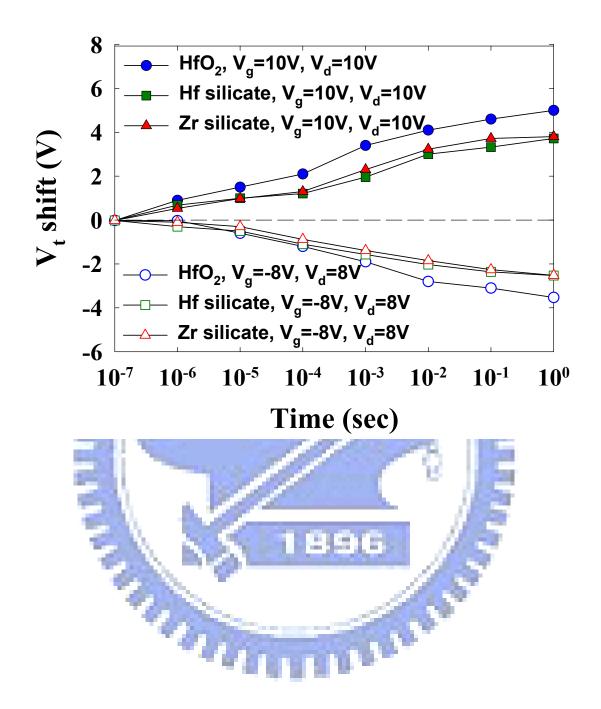

- Fig. 4.4 Programming and erasing speed characteristics of poly-Si TFT memories with  $HfO_2$ , Hf silicate and Zr silicate trapping layers for different programming conditions. The programming time can be as short as 1ms if the window margin is set to 3V with  $V_g=V_d=12V$ . The erasing time is about 10

ms.

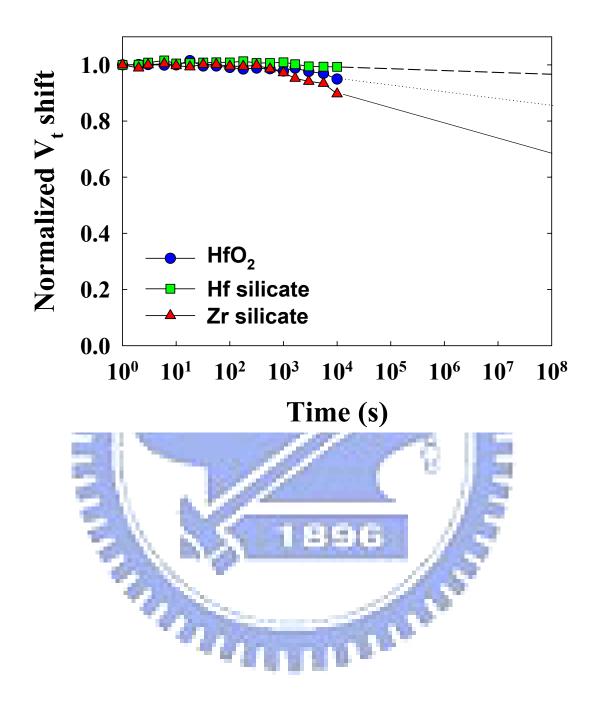

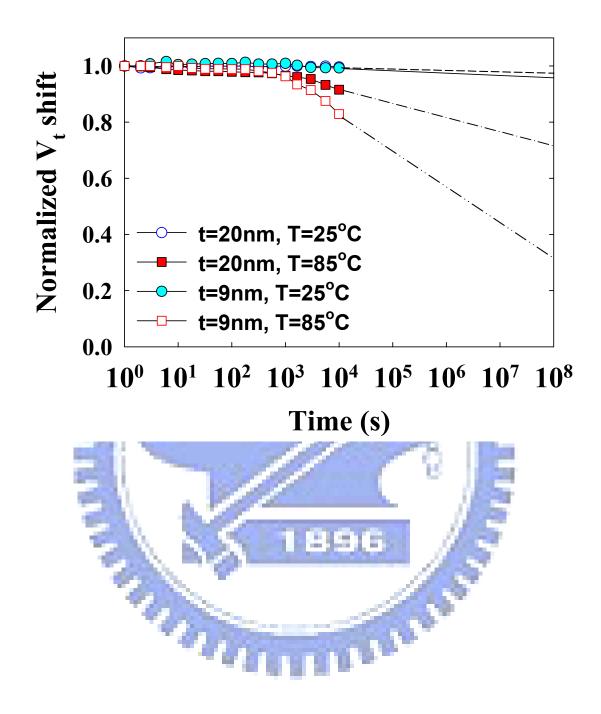

- Fig. 4.5 Retention characteristics of the fabricated poly-Si-TFT memories at T=25°C.

The retention time can be up to 10<sup>6</sup> s for 20% charge loss at room temperature.

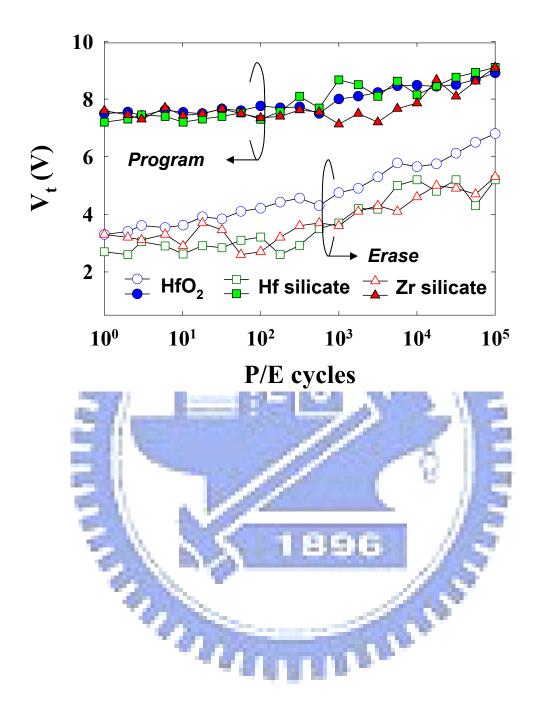

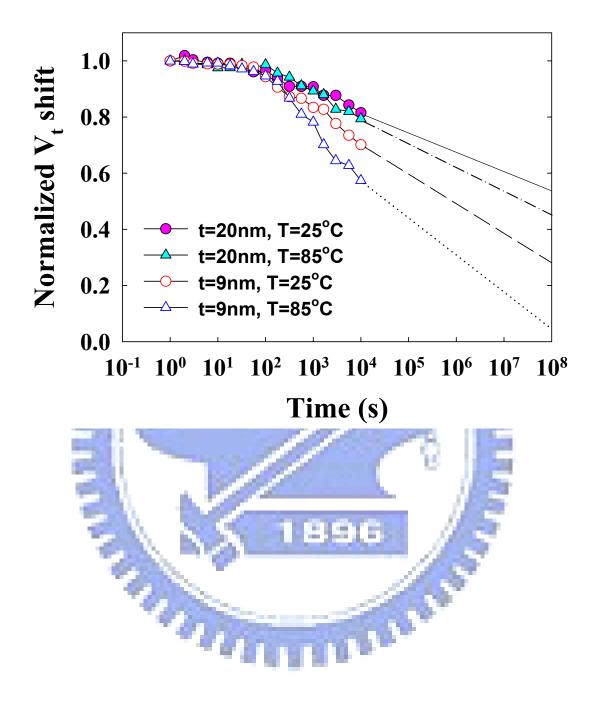

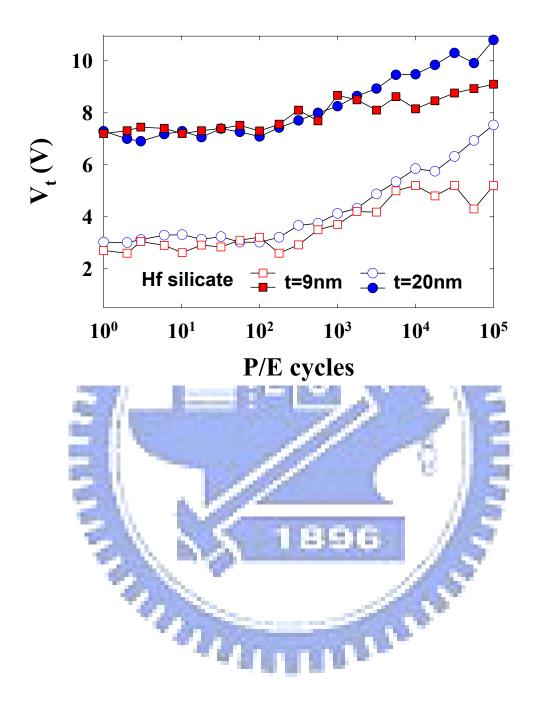

- Fig. 4.6 Endurance characteristics of the poly-Si-TFT memories. Despite the occurrence of significant memory window narrowing, a memory window of about 2V is sustained even after 10<sup>5</sup> P/E cycles.

- Fig. 4.7 Programming and erasing speed characteristics of poly-Si TFT memories with HfO<sub>2</sub>, Hf silicate and Zr silicate trapping layers for different programming conditions. The programming time can be as short as 1ms if the window margin is set to 3V with  $V_g=V_d=12V$ . The erasing time is about 10 ms.

- Fig. 4.8 Retention characteristics of the fabricated poly-Si-TFT memories with two different tunnel oxide thickness samples at T=25°C.

- Fig. 4.9 Retention characteristics of the fabricated poly-Si-TFT memories with two different tunnel oxide thickness samples at T=85°C.

- Fig. 4.10 Endurance characteristics of the poly-Si-TFT memories with two different tunnel oxide thickness samples.

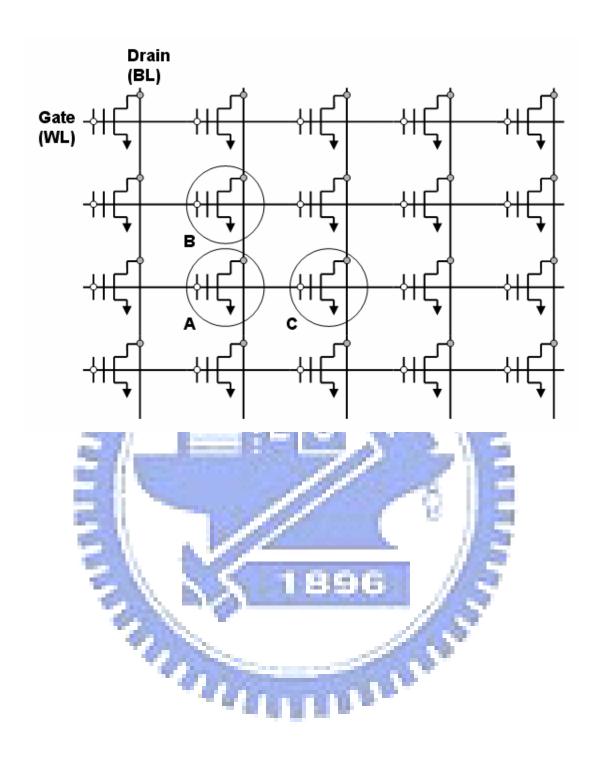

- Fig. 4.11 The schematic illustration of disturb condition. Cell A is the programming cell. Cell B and Cell C are the drain disturbance and gate disturbance, respectively.

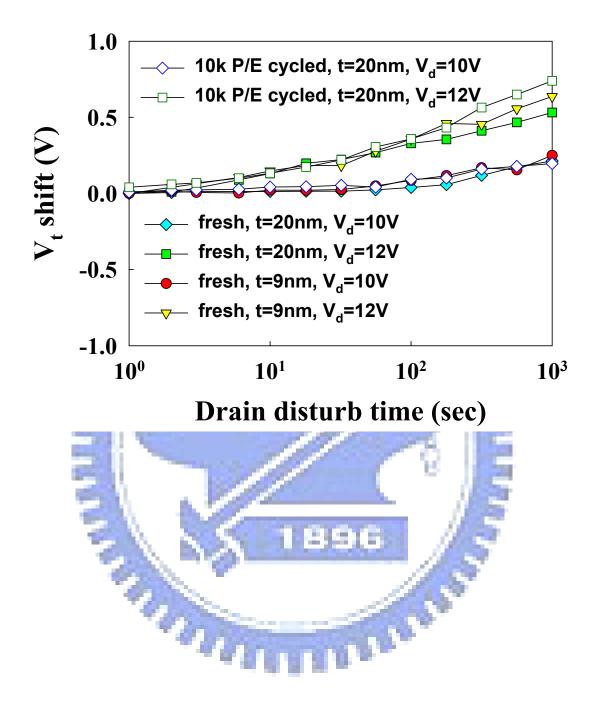

- Fig. 4.12 Drain disturbance characteristics of the Hf silicate TFT memory devicess with two different tunnel oxide thickness samples. After 1000 s at 25 °C, small 0.7V drain disturb margin was observed.

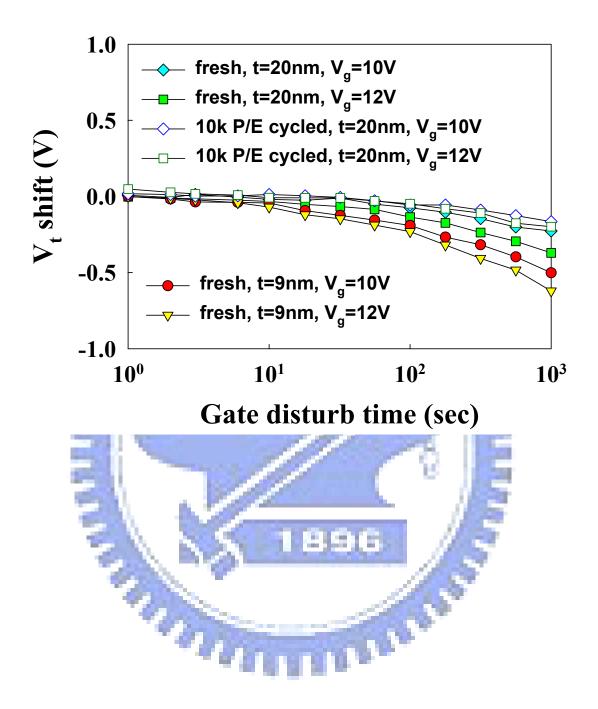

- Fig. 4.13 Gate disturbance characteristics of the Hf silicate TFT memory devices with two different tunnel oxide thickness samples.

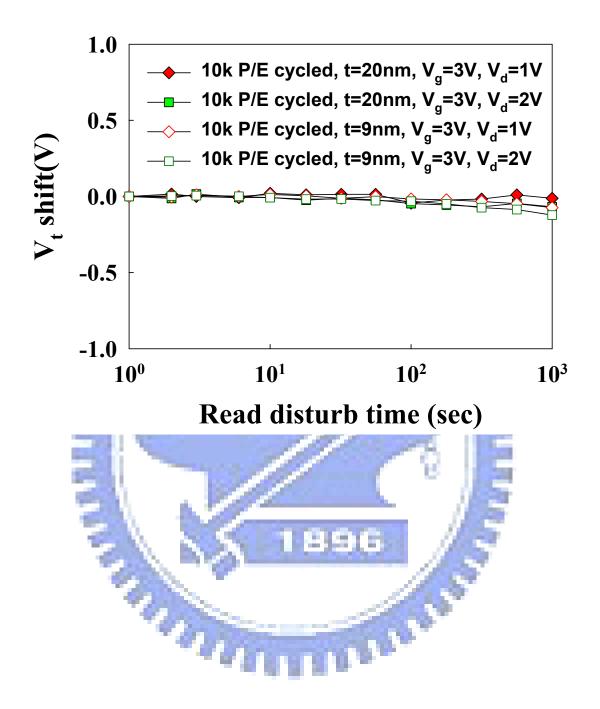

Fig. 4.14 Read disturbance characteristics of the Hf silicate TFT memory devices with two different tunnel oxide thickness samples. No significant  $V_t$  shift occurred for  $V_d < 1$ , even after 1000 s at 25 °C.

#### **Chapter 5**

- Fig. 5.1 HfO<sub>2</sub> nanocrystal Flash memory cell structure.

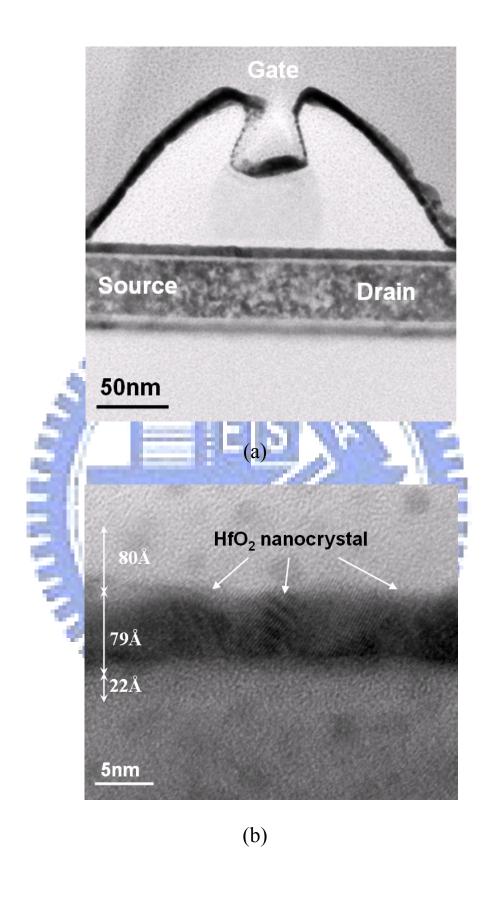

- Fig. 5.2 (a) Planar-view HRTEM image of the 50nm HfO<sub>2</sub> nanocrystals devices. (b) Planar-view HRTEM image of the HfO<sub>2</sub> nanocrystals trapping layer.

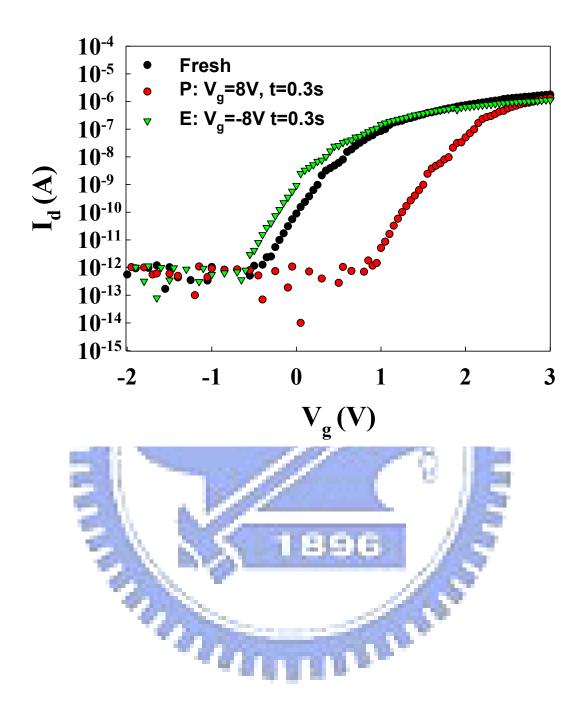

- Fig. 5.3  $I_{ds}$ - $V_{gs}$  curves of programmed memories with different programming conditions. The programming time is  $10\mu s$ . A memory window of larger than 3V can be achieved with  $V_g$ = $V_d$ =10V programming operation.

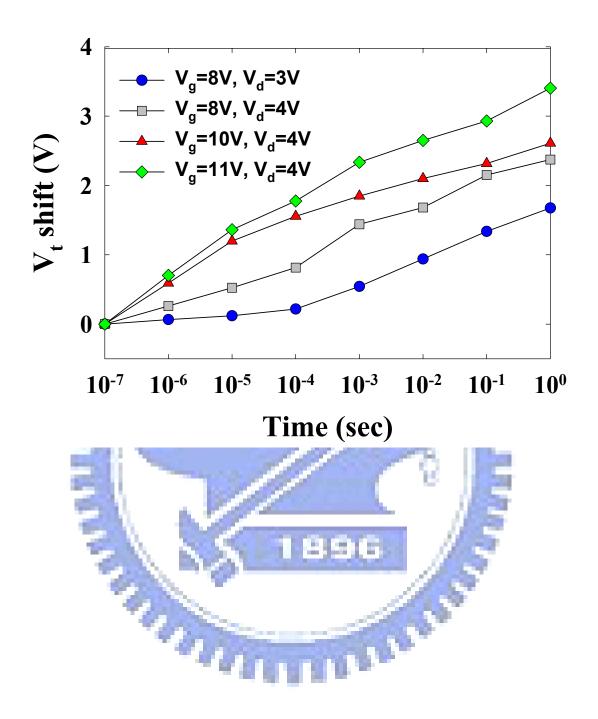

- Fig. 5.4 (a) Program characteristics of HfO<sub>2</sub> nanocrystal memory devices with different programming conditions. (b). Erase characteristics of HfO<sub>2</sub> nanocrystal memory devices with different erasing voltages.

- Fig. 5.5 Retention characteristics of HfO<sub>2</sub> nanocrystal memory devices at T=25°C.

- Fig. 5.6 Endurance characteristics of HfO<sub>2</sub> nanocrystal memory devices. Negligible degradation is found even after 10<sup>5</sup> P/E cycles.

- Fig. 5.7 I<sub>ds</sub>–V<sub>gs</sub> Curves of the two-bit memory in a cell; forward read and reverse read for programmed bit1 and programmed bit2.

- Fig. 5.8 (a) Room-temperature hysteresis characteristics of the fabricated devices with various channel lengths. (b) The carrier mobiles with various channel lengths.

- Fig. 5.9 (a) Room-temperature hysteresis characteristics of the fabricated devices with various channel widths. (b) The carrier mobiles with various channel widths.

- Fig. 5.10 Read disturbance characteristics of the  $HfO_2$  nanocrystal memory devices. No significant  $V_t$  shift occurred for  $V_d < 4$ , even after 1000 s at 25 °C.

- Fig. 5.11 Drain current versus gate voltage characteristic.

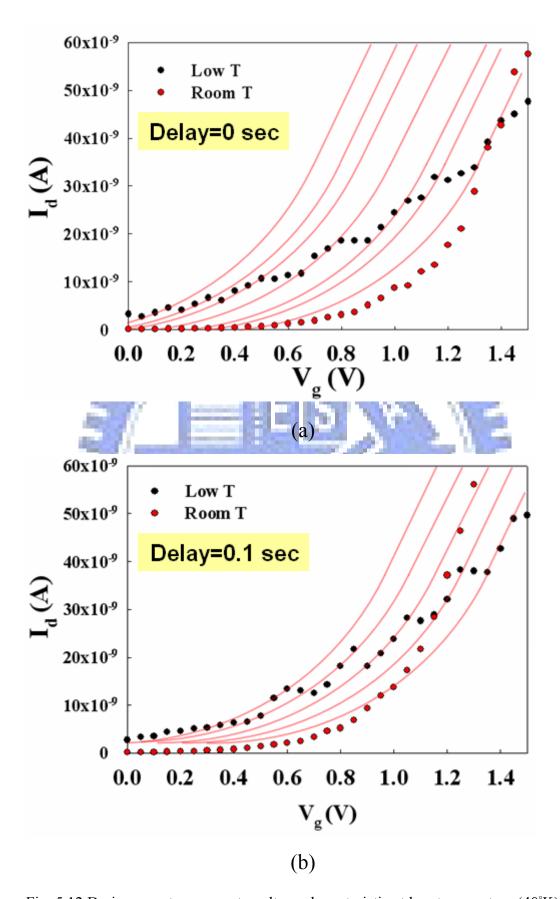

- Fig. 5.12 Drain current versus gate voltage characteristic at low temperature (40°K) for different swept times. (a) delay=0 sec. (b) delay=0.1sec.

#### Chapter 6

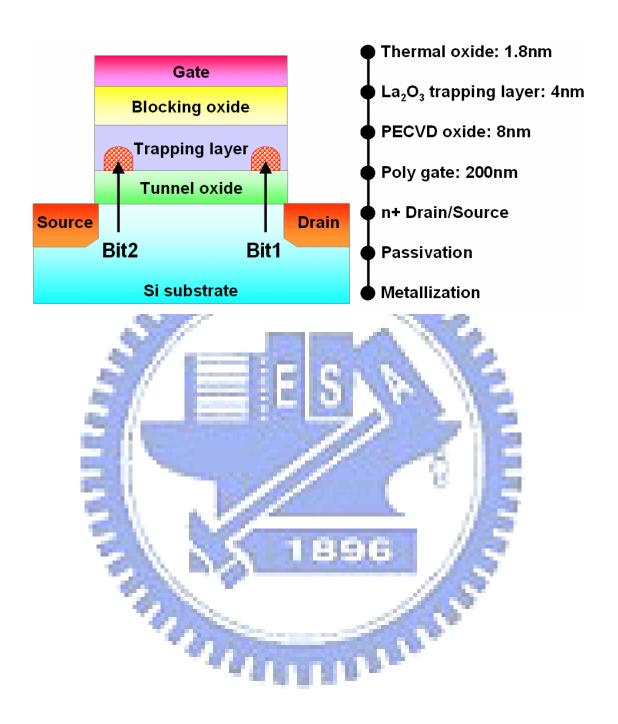

- Fig. 6.1 Schematic representation of the La<sub>2</sub>O<sub>3</sub> SONOS-type Flash memory cell structure and localized charge storage.

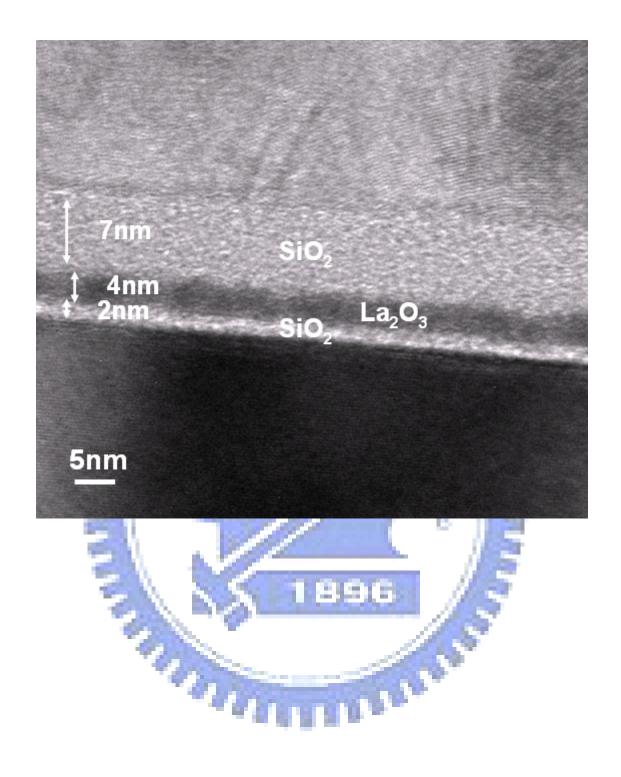

- Fig. 6.2 Planar-view HRTEM image of the La<sub>2</sub>O<sub>3</sub> SONOS-type memory.

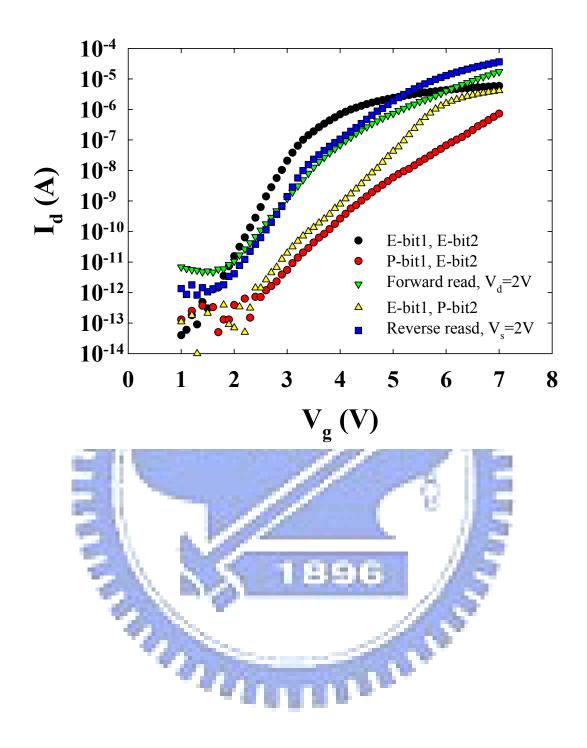

- Fig. 6.3 I<sub>ds</sub>–V<sub>gs</sub> Curves of the two-bit memory in a cell; forward read and reverse read for programmed bit1 and programmed bit2.

- Fig. 6.4 Program speed of the La<sub>2</sub>O<sub>3</sub> SONOS-type memory

- Fig. 6.5 Erase speed of the La<sub>2</sub>O<sub>3</sub> SONOS-type memory.

- Fig. 6.6 Retention of. the La<sub>2</sub>O<sub>3</sub> SONOS-type memory for three temperature (T=25°C, 85°C, and 125°C). 22% charge loss occurred at 25 °C; and 40% charge loss occurred at 125 °C up to 10<sup>8</sup> sec..

- Fig. 6.7 Endurance characteristics of the La<sub>2</sub>O<sub>3</sub> SONOS-type memory after 10k P/E cycling.

- Fig. 6.8 Drain disturbance characteristics of the La<sub>2</sub>O<sub>3</sub> SONOS-type memory. After 1000 s at 25 °C, only a 1V drain disturb margin was observed.

- Fig. 6.9 Gate disturbance characteristics of the  $La_2O_3$  SONOS-type memory. A threshold voltage shift of only 1 V occurred after stressing at  $V_g = 10$  V and  $V_s = V_d = V_{sub} = 0$  V for 1000 s.

- Fig. 6.10 Read disturbance characteristics of the  $La_2O_3$  SONOS-type memory devices. No significant  $V_t$  shift occurred for  $V_d < 4$ , even after 1000 s at 25 °C.

## **Table Lists**

#### **Chapter 2**

- Table 2.1 Average elemental compositions in the HfSiO<sub>x</sub> silicate layers, as examined through EDS analysis of the as-deposited and 900°C-RTA-treated samples.

- Table 2.2 Comparison table of the different thickness samples of  $HfSiO_x$  silicate layers after 900°C-RTA-treated.

- Table 2.3 Operation principles and bias conditions utilized during the operation of the HfO<sub>2</sub> nanocrystal Flash memory cell.

- Table 2.4 Memory characteristics of the device fabricated in this study and the comparison with reported data for various SONOS-type memory cells.

#### Chapter 3

Table 3.1 Summary of the bias conditions for two-bit operation in the memory cell.

## Chapter 4

Table 4.1 Operation principles and bias conditions utilized during the operation of the poly-Si TFT flash memory cell.

#### Chapter 6

Table 6.1 Operation principles and bias conditions utilized during the operation of the La<sub>2</sub>O<sub>3</sub> SONOS-type memory cell.

# **Chapter 1**

#### Introduction

#### 1.1 Background

Recently, complementary metal-oxide-semiconductor (CMOS) memory technologies which driven by the more and more increasing demand for mobile capabilities, computer, and some electronic consumer products, have developed rapidly for the need in the people's livelihood.

Memories can be divided into two main categories by whether the storage data can be affected by the power supply. One is volatile memory, and the other is non-volatile memory. Volatile memory will lose stored information once the power supply is switched off. On the other hand, nonvolatile memory does not lose its data when the system or device is turned off, and offer low power and high storage density solutions to generic needs of data storage.