## 國立交通大學

電子工程學系電子研究所

碩士論文

先進奈米元件結構 於光感測與太陽能電池之研究

1896

## The Research of Advanced Nanodevice Structures for Photo-Sensing and Solar Cell Application

研究生:廖廷偉

指導教授:吳重雨 教授

李耀坤 教授

中華民國 九十六 年 十 月

#### 先進奈米元件結構於光感測與太陽能電池之研究

## The Research of Advanced Nanodevice Structures for Photo-Sensing and Solar Cell Application

研究生: 廖廷偉 Student: Ting-Wei Liao

指導教授:吳重雨 教授 Advisor: Chung-Yu Wu

李耀坤 教授 Yaw-Kuen Li

國立交通大學電子工程學系 電子研究所碩士班碩士論文

A Thesis

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

**Electronic Engineering**

October 2007

Hsin-Chu, Taiwan, Republic of China

中華民國九十六年十月

#### 先進奈米元件結構於光感測與太陽能電池之研究

研究生:廖廷偉 指導教授:吳重兩 老師

李耀坤 老師

#### 國立交通大學電子工程系電子研究所碩士班

#### 摘 要

在本論文中,使用硒化鎘量子點和金奈米粒子,透過離子作用力建構多層光感測奈米元件結構於矽基板上。在掃描式電子顯微鏡的觀察下,證明其結構成功生長於矽基板上。在製程上,利用lift-off技術成功在電極上定義出奈米粒子和量子點所要的圖樣。最後在結合硒化鎘量子點和金奈米粒子的奈米結構中,照射 375 nm電射光以及 0.16 mW/cm²日光燈後,在各種偏壓下有固定的光電流增加。在此研究中,在 0.16 mW/cm²日光燈照射下,可得到奈米元件的效率為 0.67%,最大光電流為 1.02nA,光電流體積密度 1.334\*10<sup>-23</sup>A/nm³,單位體積產生功率為 2.45\*10<sup>-25</sup>W/nm³。

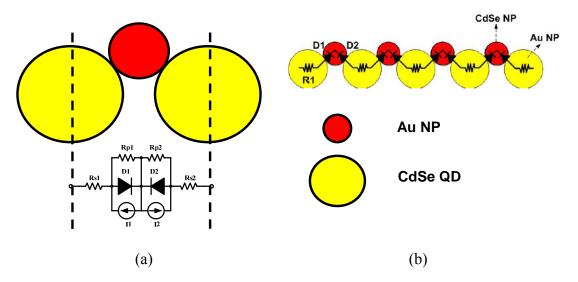

在此同時,並做了三維方向的奈米元件探討(元件寬度、元件長度、元件層數),實驗的結果發現元件長度的減少以及層數的增加有助於效率的提升,但是元件層數並非呈現線性的增加,而是在結構層數為八層之後開始會有飽和的現象。此外,以上的現象可以利用"奈米蕭特基二極體和電阻陣列"模型成功地解釋之,我們可以利用 HSPICE 去模擬此三維模型發現有同樣的現象。

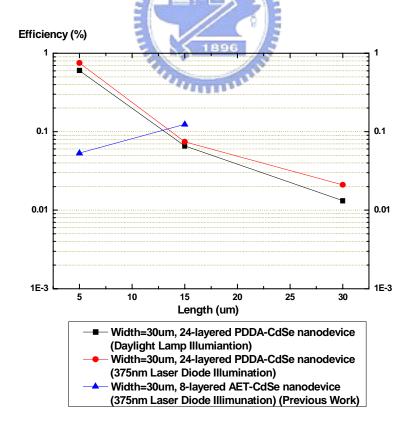

最後,我們發現 24 層的金奈米粒子/硒化鎘量子點奈米結構之"太陽能電池效率"至少為先前金奈米粒子/硒化鎘奈米結構相關研究的 5 倍,且在我們理想的模型推導下,可以推得高效率太陽能電池。

i

The Research of Advanced Nanodevice Structures for Photo-Sensing and Solar Cell Application

Student: Ting-Wei Liao Advisor: Chung-Yu Wu

Yaw-Kuen Li

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung University

#### **ABSTRACT**

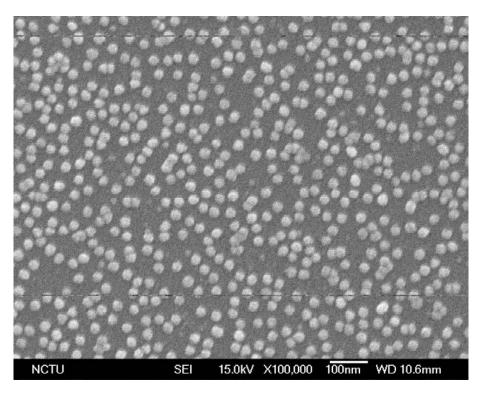

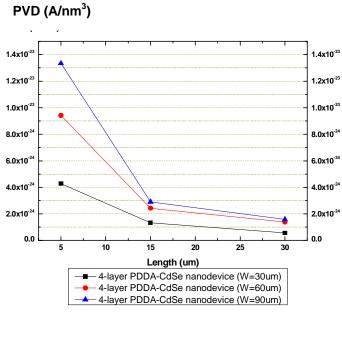

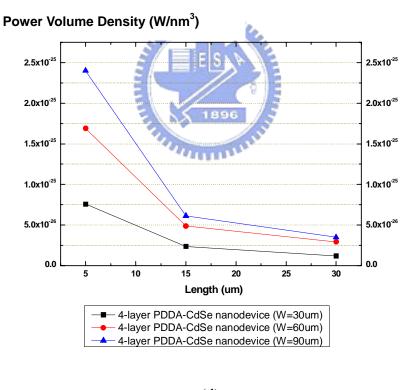

In this work, we used CdSe QDs and Au NPs to construct the multi-layer photo-sensing nanodevice structures on a silicon substrate through ionic interaction. By the SEM views, the CdSe QDs and Au NPs successfully deposited on the silicon substrate. In the nanodevice process, the lift-off technology was successfully utilized to define the pattern of the Au NPs and CdSe QDs. Finally, the Au / CdSe nanodevices were illuminated by the 375 nm laser diode and the 0.16 mW/cm² daylight lamp. As a result, the multi-layer nanostructure composed of CdSe QDs and Au NPs, there was constant photocurrent increment to the current measured in the dark for each voltage bias after illumination with 375 nm laser and the 0.16 mW/cm² daylight lamp. In this work, under 0.16 mW/cm² daylight lamp illumination, the solar cell efficiency is 0.67% . The maximum photocurrent is 1.02nA. The highest PVD (photocurrent volume density) is 1.334\*10<sup>-23</sup>A/nm³. The power volume density is 2.45\*10<sup>-25</sup>W/nm³.

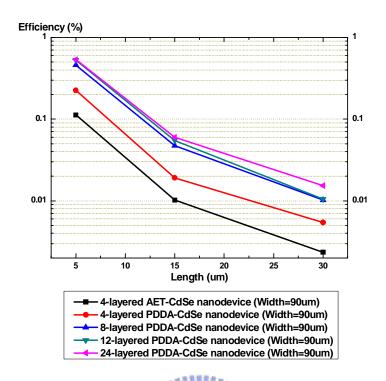

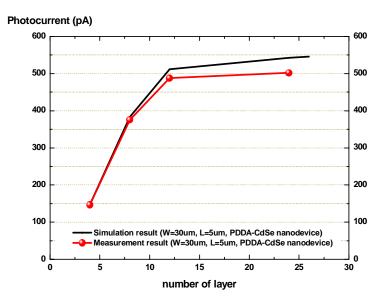

Meanwhile, the 3-dimension (width, length and the number of the layer) nanodevice efficiency investigation was executed. The shorter and thicker devices would benefit the performance of the solar cell efficiency. However, increasing the number of the layer would cause the saturation

ii

phenomenon when the number of the layer is more than eight. Besides, the above characteristics can be explained by the "nano-Schottky-diodes and resistor array" model. We can obtain the same phenomenon as using HSPICE to simulate the three dimensional model.

In conclusion, we found that the "solar cell efficiency" of the 24-layered Au NPs / CdSe QDs nanostructure is at least 5 times better than the previous work of the Au NPs / CdSe QDs nanodevices. The solar cell can achieve high efficiency based on our model calculation.

#### **ACKNOWLEDGEMENTS**

首先,感謝我的兩位指導教授,吳重雨老師與李耀坤老師,在這兩年來對我的耐心指導與諄諄教誨,讓我能夠順利完成碩士學業。記得剛進來交大唸電子研究所時,對於奈米科技的相關研究極俱陌生,深怕自己無法勝任接替廖廷偉學長的再續研究,研究過程中遇到種種挫折與失敗,多虧兩位指導教授的鼓勵與教誨,讓我可以循序漸進,完成此論文。在積體電路設計上,再次感謝吳重雨老師以他淵博的專業知識,給予我指導與啟發,讓我充分學習到分析電路的技巧;在生化領域上,萬分感謝李耀坤老師細心教導,充實我在生化方面的專業知識,使我受益良多。其次要感謝論文口試的評審委員,許鉦宗教授、謝志成教授對我的論文提出了許多寶貴的建議,使這篇論文的內容更加完整。真的很感謝您們!

接下來要感謝應化所陳登銘老師實驗室的黃靜萍學姐,在我碩士兩年的研究過程中給予最大的幫忙與經驗分享,讓我在研究的路途中走的更加順利;也感謝率耀坤老師實驗室的可欣學長,在我研究遇到挫折時給予鼓勵。感謝電子所羅正忠老師實驗室的建宏、正凱、宏仁,在製程上編幫助我解決不少問題。感謝電子所崔秉鉞老師實驗室的玉仁,對於製程技術上的建議。感謝奈米所許鉦宗老師實驗室的柏鈞學長,指導我設計光單。我只能說認識你們真好;百忙之中抽空幫我照 SEM 的奈米所博士班陳蓉萱學姊;半導體中心 SEM 陳聯珠小姐,你們總是給予我不求回報的幫助,真的很感謝你們!當然還要感謝 307 實驗室的學長姊:林俐如學姊、陳勝豪學長、王文傑學長、蘇烜毅學長、虞繼堯學長、陳煒明學長、蔡夙勇學長、張志遠學長們給予我的指教幫忙和研究上的經驗傳承。同時也要感謝維德、晏維、國忠、順維、柏宏、松諭、巧伶、宗裕、世豪、鯉魚、小王,陪伴我度過這段溫馨的研究生活,增添了許多歡笑與回憶;還有幫忙我許多的學弟:政邦,以及其他學弟妹國權、威宇、建銘、筱 好,謝謝你們,也祝你們研究順利,早日畢業!

最後,要感謝我的父母以及所有的親戚朋友們,感謝您們在我研究生活的兩年中給予莫 大的加油鼓勵,讓我可以順利完成碩士學業。還有要感謝雅姿,在我面對龐大壓力時給我的 鼓勵。最後把我的論文研究成果獻給在天上的外公、外婆,希望我所認識的朋友都可以過的 平平安安。

> 廖廷偉 誌於 風城交大 2007 秋

### **CONTENT**

| ABSTRA                  | CT (CHINESE)                                                         | i       |

|-------------------------|----------------------------------------------------------------------|---------|

| ABSTRA                  | CT (ENGLISH)                                                         | ii      |

| ACKNOV                  | VLEDGEMENTS                                                          | iv      |

| CONTEN                  | TS                                                                   | v       |

| TABLE C                 | CAPTIONS                                                             | viii    |

| FIGURE                  | CAPTIONS                                                             | ix      |

| Chapter 1.1 1.2 1.3 1.4 | Thesis Organization.                                                 | 5       |

| Chapter                 | r 2 Fabrication Technologies of CdSe<br>Nanoparticles and Nanodevice | / Au    |

| 2.1                     | The Synthesis of Citrate-Capped Au Nanoparticles                     | 19      |

| 2.2                     | The Synthesis of AET-Capped and PDDA-Capped CdSe Q                   | )uantum |

|       | Dots20                                                           |

|-------|------------------------------------------------------------------|

| 2.3   | The Physical Characteristics of Au Nanoparticles and CdSe        |

|       | Quantum Dots22                                                   |

| 2.4   | The Self-assembly Process of Au Nanoparticles / CdSe Quantum     |

|       | Dots Nanodevice with Lift-off Technology25                       |

| 2.5   | Reaction Environment Investigation30                             |

|       |                                                                  |

| Chapt | er 3 Experimental Results and Discussions                        |

| 3.1   | The Environment Setup for Measurement49                          |

| 3.2   | SEM and Optical Absorption / Emission Spectra51                  |

| 3.3   | Au / CdSe Nanodevice53                                           |

| 3.4   | Au / CdSe Nanodevice Solar Cell Efficiency Estimation and Device |

|       | Model Construction56                                             |

|       |                                                                  |

| Chapt | er 4 Application of Linear Regulator on CdSe / Au                |

|       | Nanoparticle Solar Cell                                          |

| 4.1   | System Design Considerations86                                   |

|       | 4.1.1 System Architecture86                                      |

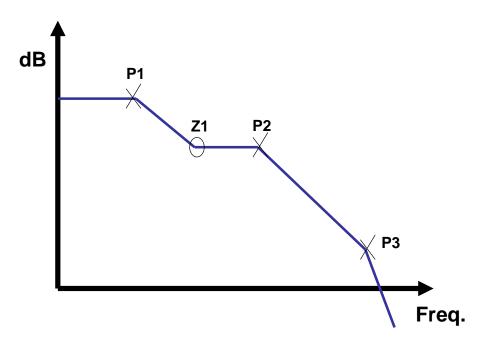

|       | 4.1.2 AC Analysis86                                              |

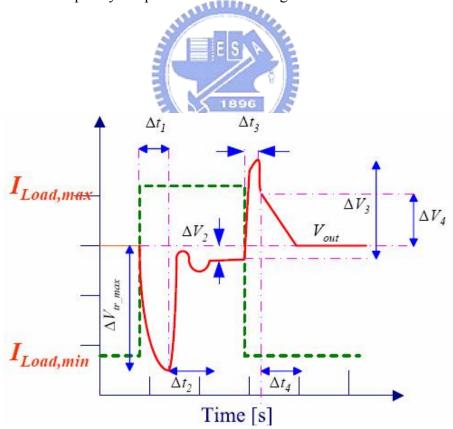

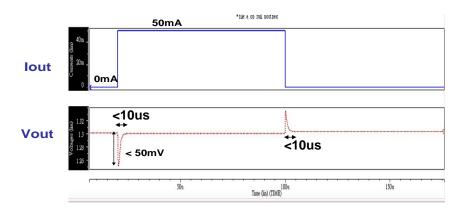

|        | 4.1.3 Transient Analysis        | 91  |

|--------|---------------------------------|-----|

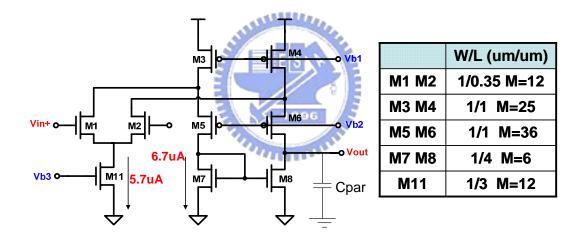

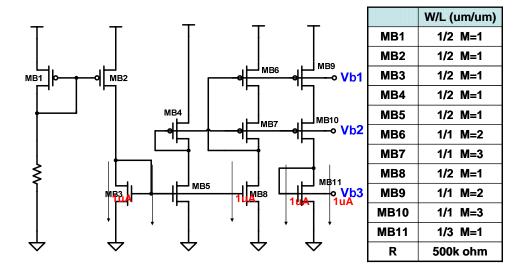

| 4.2    | Circuit Blocks                  | 94  |

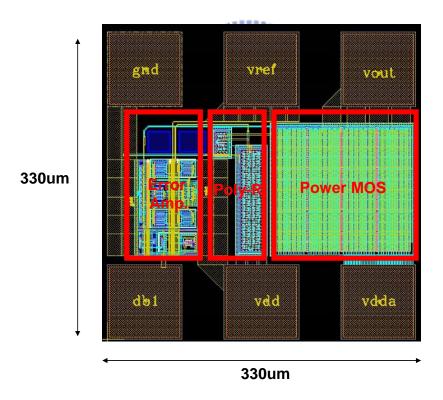

| 4.3    | Simulation Result and Layout    | 96  |

| 4.4    | Measurement Results             | 97  |

|        |                                 |     |

| Chapte | r 5 Conclusions and Future Work |     |

| 5.1    | Conclusions                     | 108 |

| 5.2    | Future Work                     | 110 |

| REFER  | RENCE                           | 113 |

| REFER  | ILITCE                          | 113 |

| VITA   |                                 | 115 |

#### **TABLE CAPTIONS**

#### **CHAPTER 3**

**Table 3.1** The measurement results of the 4-layered PDDA-CdSe nanodevice (PVD: photocurrent volume density, Power VD: power volume density) (P.65)

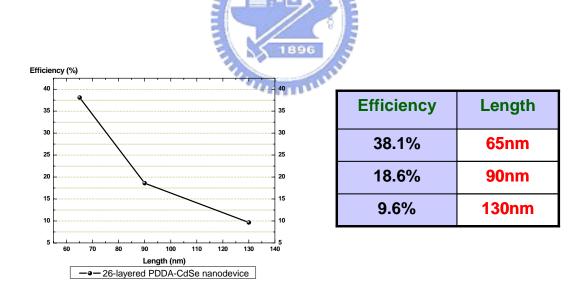

**Table 3.2** According to the simulation results, the better device dimension to reach the high efficiency solar cell can be decided. 26-layered nanodevices with 30um in width are adopted to predict the high efficiency. On the basis of the ideal inference, the 9.2% PDDA-CdSe nanodevice can be fabricated if the length of the device is 65nm. (P.82)

#### **CHAPTER 4**

**Table 4.1** The specification of the error amplifier (P.102)

**Table 4.2** The specification of the feedback loop (P.103)

**Table 4.3** The specification comparison of the simulation and measurement result (P.107)

1896

#### FIGURE CAPTIONS

#### **CHAPTER 1**

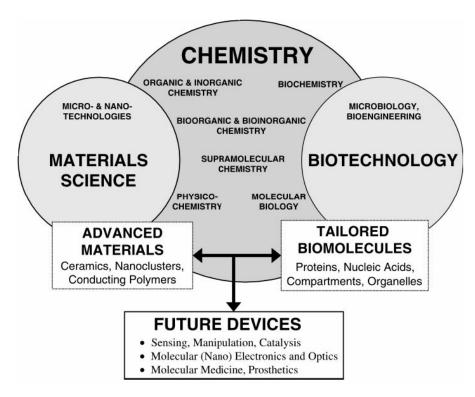

- **Figure 1.1** Chemistry is the central science for further applications such as materials science and biotechnology. The combination of advanced materials and tailored biomolecules will produce the future nanodevices [1]. (P.13)

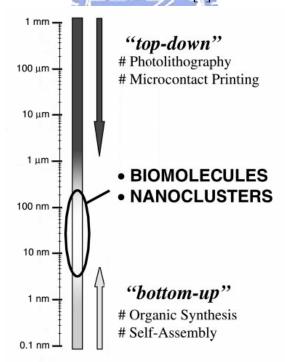

- **Figure 1.2** A gap currently exists in the engineering of small-scale devices. The top-down processes will have their limit below 100 nm, and the bottom-up processes will also have a limit at 2~5 nm. The gap will be filled by nanoclusters and biomolecules [1]. (P.13)

- **Figure 1.3** The TEM images of  $SiO_2@Au$  NP clusters synthesized at (A) pH=8.4, (B) pH=8.6, (C) pH=10.2, (D) pH=11.1. The scale bar for all micrographs is 200 nm [2]. (P.14)

- **Figure 1.4** The TEM images of SiO<sub>2</sub>@CdSe NP clusters synthesized at (A) pH=6.8, (B) pH=7.2, (C) pH=10.2, (D) pH=11.1. The scale bar for all micrographs is 100 nm [2]. (P.14)

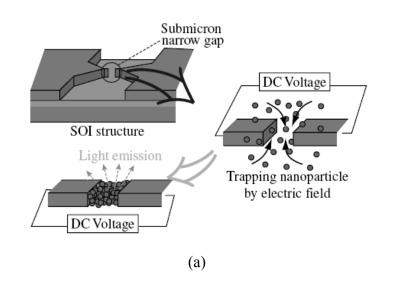

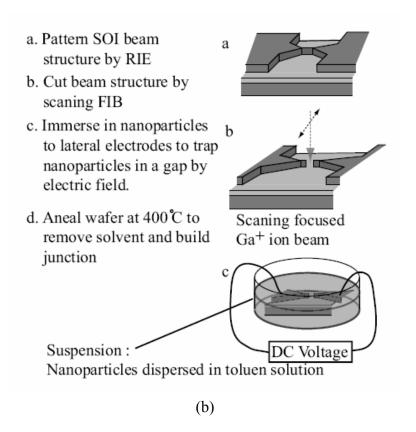

- **Figure 1.5** (a) The schematic diagram of trapping NPs in a submicron narrow gap (5  $\mu$ m \* 5  $\mu$ m \* 1  $\mu$ m) and a submicron sized light source. (b) The fabrication process of a submicron sized light source based on SOI and CdSe QDs [16]. (P.15)

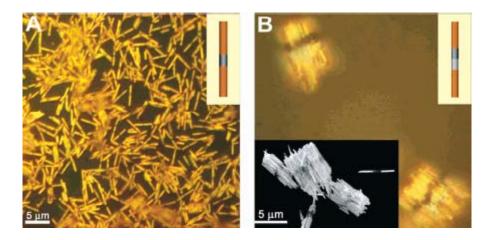

- **Figure 1.6** (A) Optical microscope image of Au-Ppy-Au rods. (B) Optical microscope image of Au-Ppy-Cd-Au rods. The lower left inset shows the corresponding FESEM image [17]. (P.16)

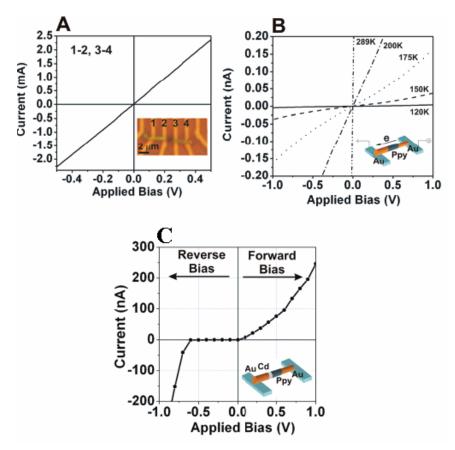

- **Figure 1.7** The measurement results of **I-V** characteristics. (A) For the gold blocks (1-2, 3-4) within a single nanorod at room temperature. **Inset** shows the optical microscope image (1000 magnification) of a single Au-Ppy-Au rod on microelectrodes. (B) Temperature-dependent I-V curves for measurements across electrodes 2 and 3. (C) For a single Au-Ppy-Cd-Au rod at room temperature [17]. (P.16)

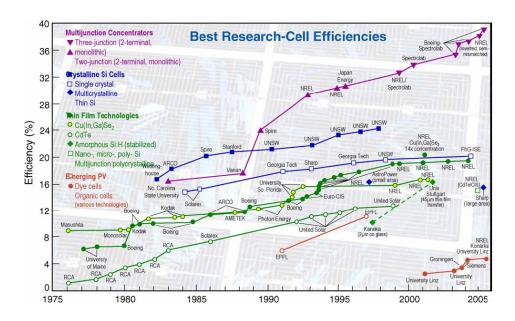

- **Figure 1.8** The efficiency evolution of best research cells by several of technology types. This table identifies those cells that have been measured under standard conditions and confirmed at one of the word's accepted centers for standard solar-cell measurements [18]. (P.17)

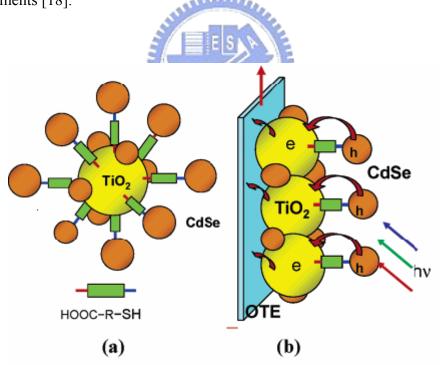

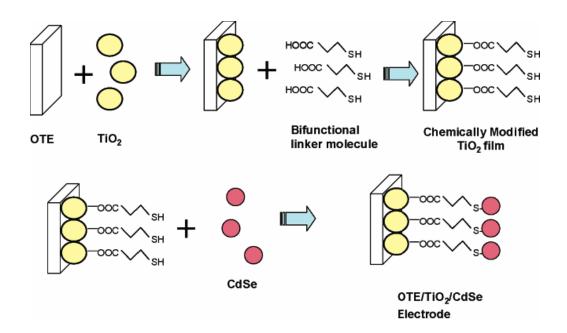

- **Figure 1.9** (a) Linking CdSe QDs to TiO<sub>2</sub> particles with bifunctional surface modifier (HS-R-COOH); (b) Light harvesting assembly composed of TiO<sub>2</sub> film functionalized with CdSe QDs on Optically Transparent Electrode (OTE) [19]. (Not to scale) (P.17)

- **Figure 1.10** The sequence of steps for linking CdSe QDs to TiO<sub>2</sub> surface with a bifunctional surface modifier [19]. (P.18)

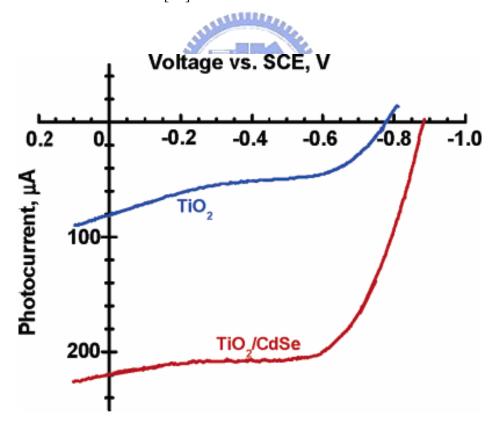

- **Figure 1.11** I-V characteristics of (a) OTE /  $\text{TiO}_2$  and (b) OTE /  $\text{TiO}_2$  / MPA /CdSe films. The filtered lights allowed excitation of  $\text{TiO}_2$  and CdSe films at wavelengths greater than 300 and 400 nm, respectively [19]. (P.18)

#### **CHAPTER 2**

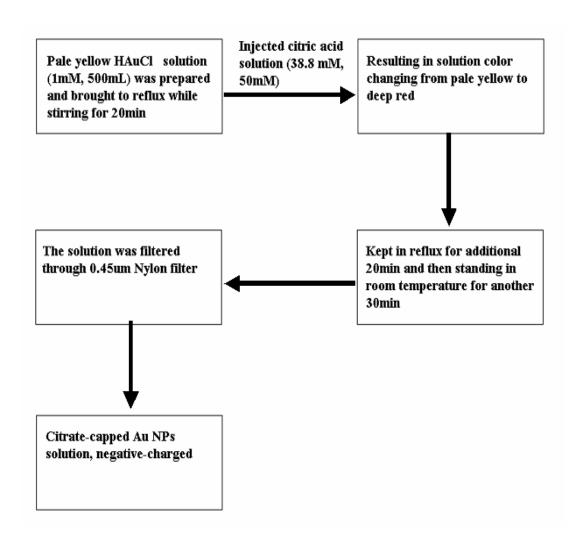

- Figure 2.1. The flow diagram for preparing the Citrate-capped Au NPs solution. (P.32)

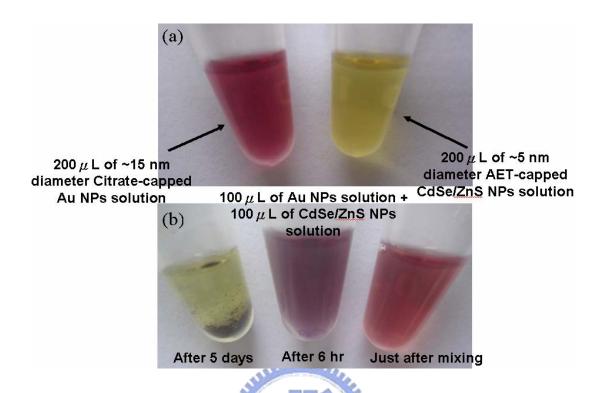

- **Figure 2.2.** (a) The close photographs of 100 μL of approximately 15 nm diameter Au NPs solution + 100 μL DI water (left) and 100 μL of approximately 5 nm diameter AET-CdSe/ZnS NPs solution + 100 μL DI water (right). The Au NPs solution was in deep red while the AET-modified CdSe/ZnS NPs solution was in yellow. (b) The close photographs of the mixture of 100 μL Au NPs solution and 100 μL AET-modified CdSe/ZnS NPs solution just after mixing (right), the mixture after standing 6 hrs (middle) in room temperature, and the mixture after standing 5 days in room temperature (left). As we can see, the color of mixture just after mixing was like that of Au NPs solution. However, after 6 hrs, it became dark purplish red. After 5 days, there was obvious precipitate at the bottom and the supernatant became pale yellow. (P.33)

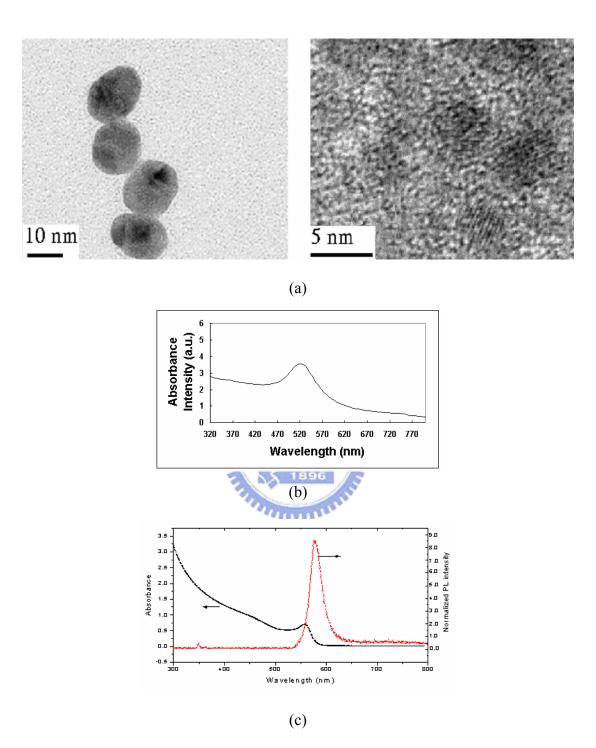

- **Figure 2.3.** (a) The TEM image of Citrate-capped approximately 15 nm diameter Au NPs and the TEM image of AET-capped approximately 5 nm diameter CdSe/ZnS NPs. (b) The UV-visible spectrum of Au NPs solution. (c) The UV-visible and PL intensity spectrum of MSA-CdSe/ZnS or AET-CdSe/ZnS NPs solution. (P.34)

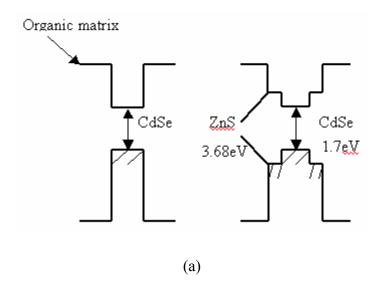

- **Figure 2.4** (a) The band gap and surface structure diagram of CdSe/ZnS NP. (b) The PL intensity spectrum of different kind of surface capping method of CdSe NP. (P.35)

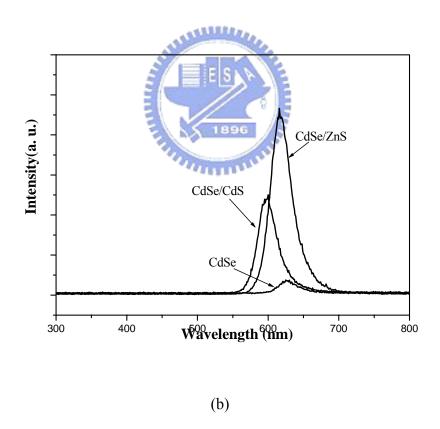

- Figure 2.5 The flow diagram for preparing the AET-capped CdSe/ZnS QDs solution. (P.36)

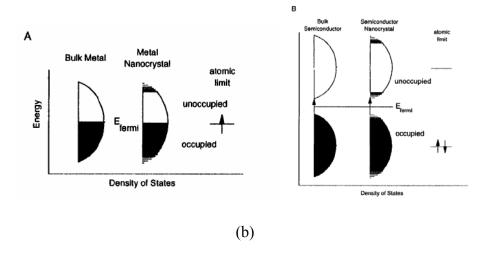

- **Figure 2.6** Density of states in metal (A) and semiconductor (B) nanocrystals. In each case, the density of states is discrete at the band edges. The Fermi level is in the center of a band in a metal, and so kT will exceed the level spacing even at low temperature and small size. In semiconductor, the Fermi level lies between two bands, so that there is large level spacing even at large size. The HOMO-LUMO gap increases as the semiconductor nanocrystals of smaller size (bellow 10 nm) [11]. (P.37)

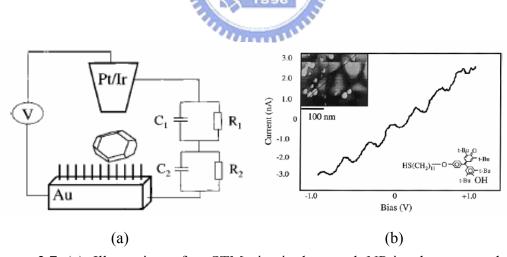

- **Figure 2.7** (a) Illustration of a STM tip-single metal NP-insulator coated gold substrate double tunnel junction and corresponding equivalent circuit. (b) Current versus voltage for a single galvinol-coated Au NP acquired in aqueous solution at pH 5. Insect shows an STM image of the sample. Tip was coated with Apiezon wax and gold substrate was coated with hexanethiol [8]. (P.37)

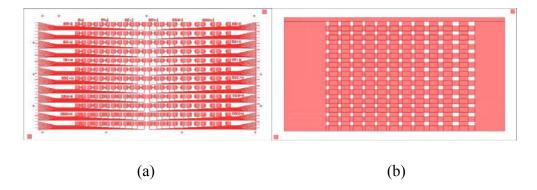

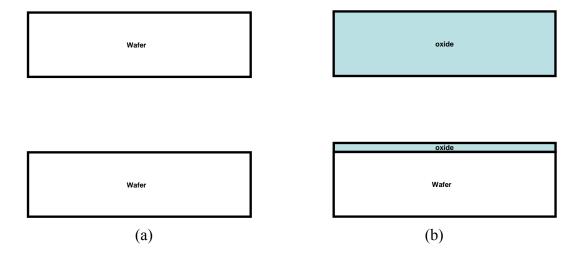

- Figure 2.8 (a) The first mask of the nanodevice, and it define the aluminum pattern.

- (b) The second mask of the nanodevice, and it define the lift-off region. (P.38)

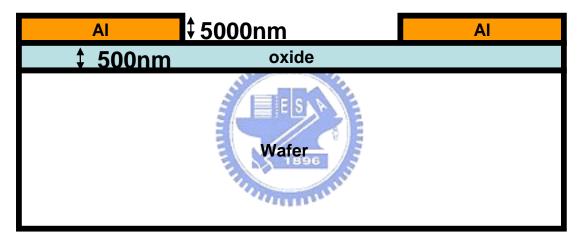

- **Figure 2.9** The cross-section view of the electrodes (P.38)

- **Figure 2.10** The process flow of the nanodevice (top-view and cross-section view) (a) The wafer was cleaned before the electrode process. (b) The oxide layer formed by thermal oxidization process. (c) The aluminum layer was constructed by thermal coating process. (d) The aluminum surface coated with photoresist. (e) The sample is exposed to define the electrode pattern. (f) Etch the extra aluminum and remain the desire region protected by the photoresist. (g) Remove the photoresist, and the electrodes formed. (P.39)

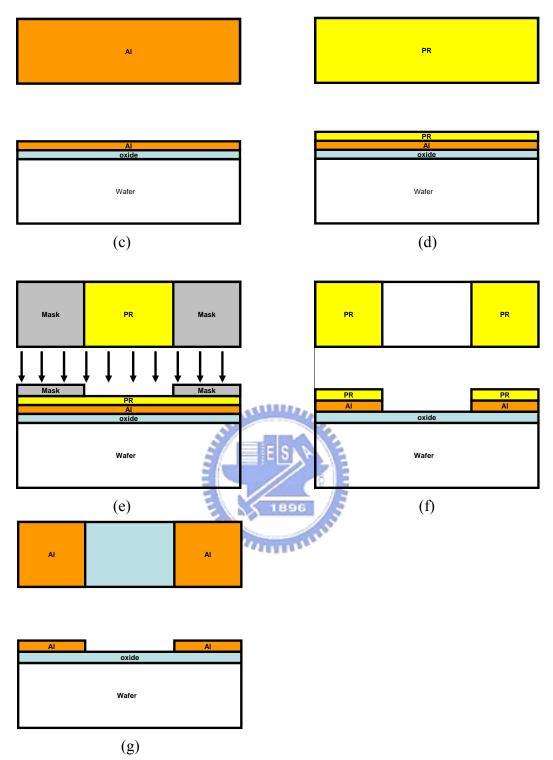

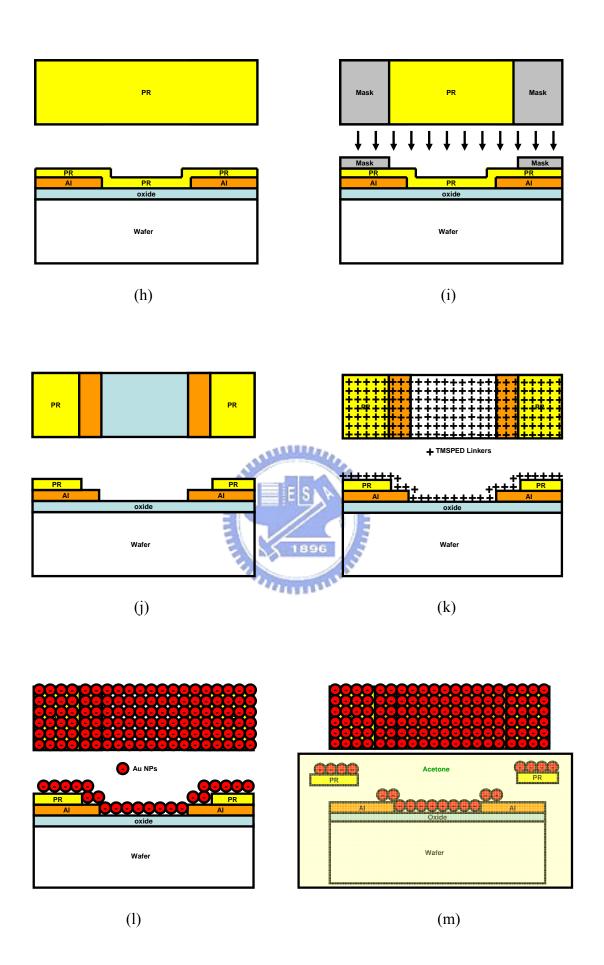

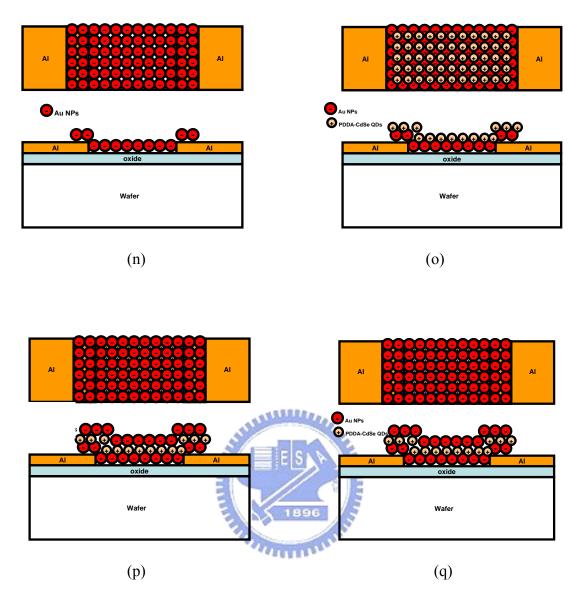

**Figure 2.11** The process flow of Nanodevices (top-view and cross-section view) (h) The wafer was coated with the photoresist. (i) The electrode sample was exposed to define the lift-off region. (j) The electrode sample was put into the developer. (k) TMSPED linkers were coated on the electrode surface. (l) The negative-charged Au NPs were coated on the surface. (m) The lift-off process was executed by immersing the sample in the acetone. (n) The unexpected NPs were removed. The desire pattern remained. (o)(p)(q) The layer-by-layer technology was repeated until the desire nanostructure was attained. (P.45)

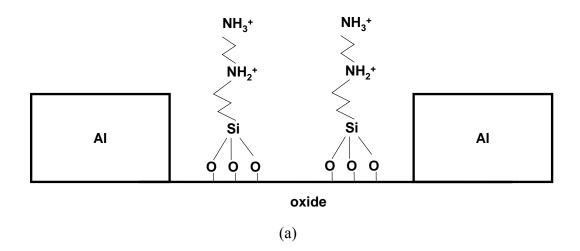

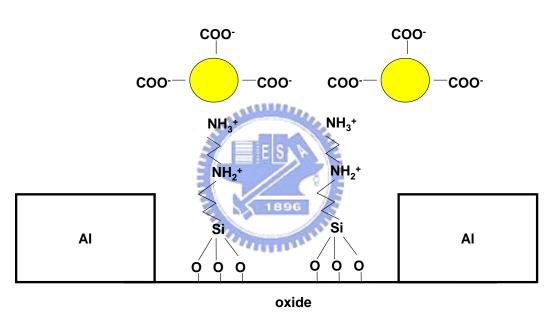

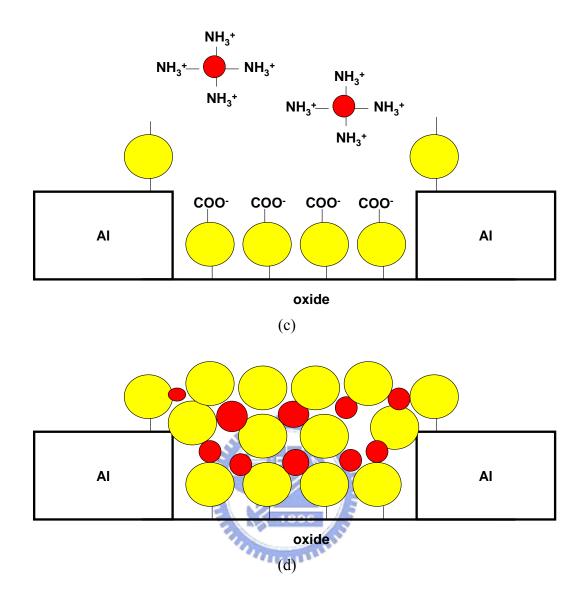

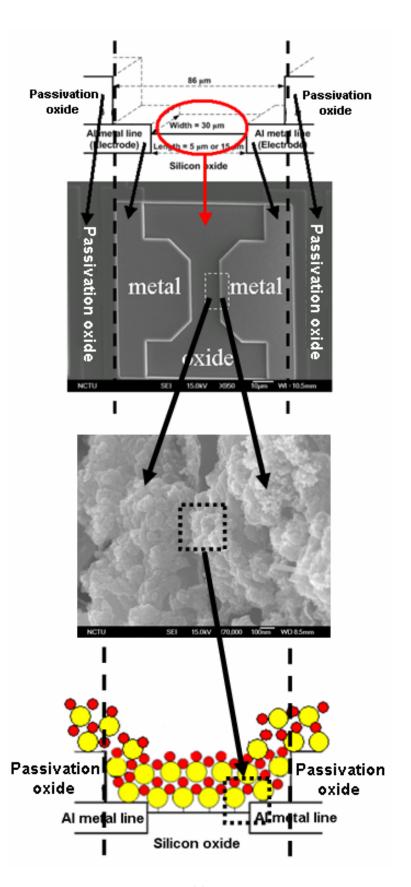

**Figure 2.12** The fabrication process of the photo-sensing nanodevice by coulombic force system after lift-off process. (a) The modification of TMSPED on the silicon oxide surface and the protonation of amino  $(-NH_3^+)$  groups, (b) The assembly of ~ 15 nm diameter Au NPs on silicon oxide substrate by ionic interaction, (d) The assembly of ~ 5 nm diameter AET-CdSe/ZnS NPs on the silicon oxide substrate by ionic interaction, and (e) The formation of the photo-sensing nanodevice structures after repeated assembly process. (Not to scale) (P.45)

**Figure 2.13** (a) The cross section figure of the electrodes structure corresponds to SEM image of the nanodevice-modified silicon chip. (b) The current flow trend of the nanodevice structure, and the electrodes dominated the source of the generated current. In the worse case, the whole chip area is considered, not the area of the electrodes. (The twill line means the thin film structure composed of NPs and QDs.). (P.45)

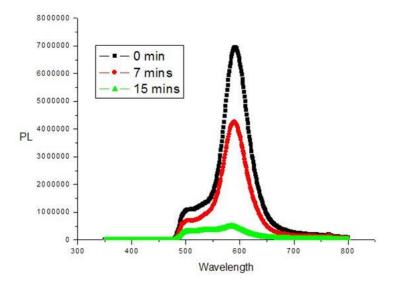

Figure 2.14 The 4-layer nanostructure immersed in acetone during different period (P.45)

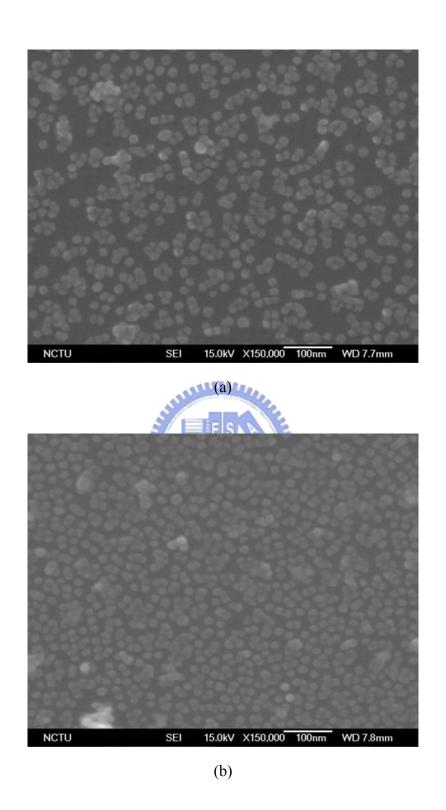

**Figure 2.15** The reaction time effect on the 2-layer nanostructure (SEM view), (a) nanostructure with 3-hour-reaction-time per layer, (b) nanostructure with 24-hour-reaction-time per layer (P.46)

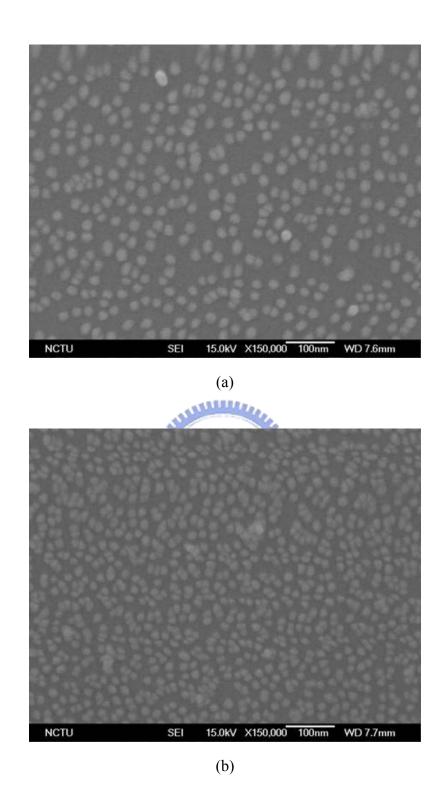

**Figure 2.16** The temperature effect on 2-layer nanostructure (SEM view), (a) the nanostructure constructed at room temperature, (b) the nanostructure constructed at 4°C environment. (P.47)

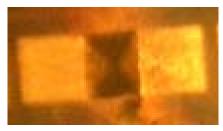

**Figure 2.17** The nanodevice with lift-off process, the black part is the place that Au NPs and CdSe deposit on the electrode surface. (P.48)

#### **CHAPTER 3**

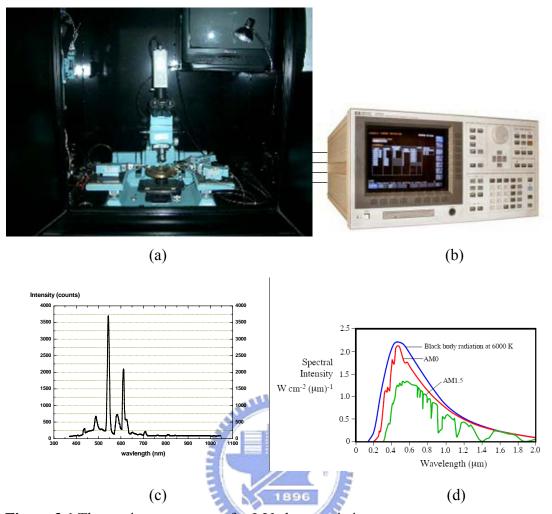

- **Figure 3.1** The environment setup for I-V characteristics measurement, (a)probe station (b) HP4156 (c) the spectrum of the daylight lamp (d) Solar Spectrum (P.60)

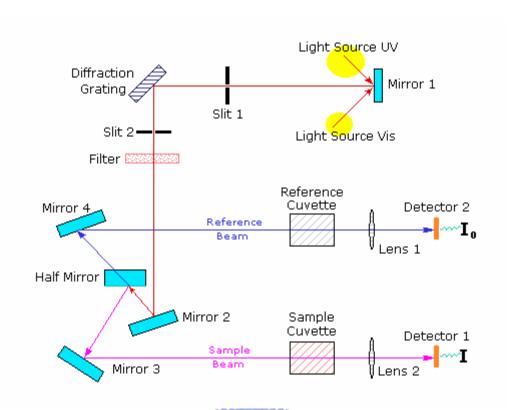

- Figure 3.2 The environment setup for UV-visible absorbance spectrum measurement. (P.61)

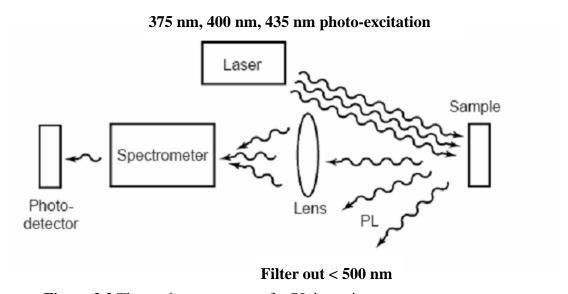

- Figure 3.3 The environment setup for PL intensity spectrum measurement. (P.61)

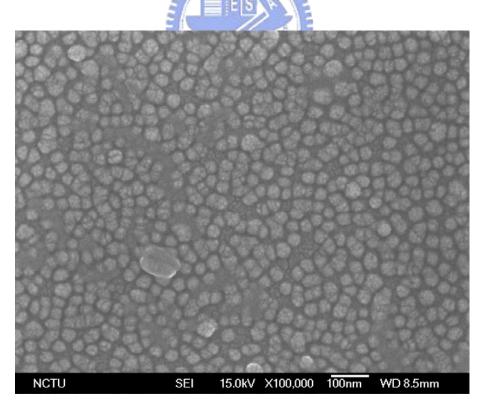

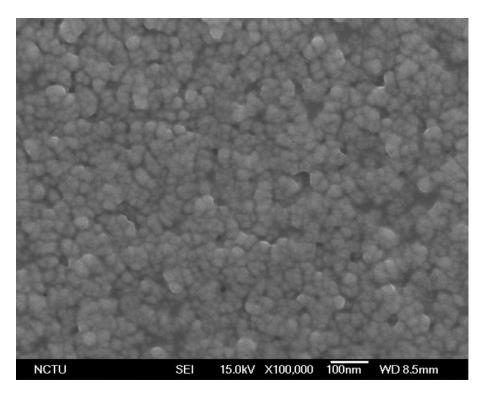

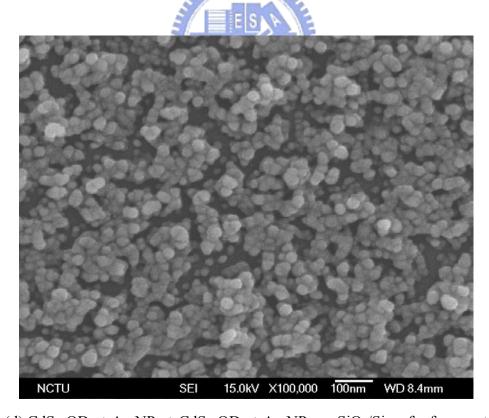

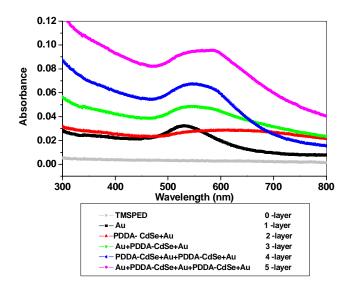

- **Figure 3.4** The SEM images (100k magnification) of Au / CdSe nanostructure of different level construction are shown above (a)~(e). (P.63)

- **Figure 3.5** The UV-visible absorption spectrum of multi-layered nanostructure on quartz glass. The Light Gray Line: 10% TMSPED/methanol ->quartz glass. The Black Line: 1-layered nanostructure. The Red Line: 2-layered nanostructure. The Green Line: 3-layered nanostructure. The Blue Line: 4-layered nanostructure. The Magenta Line: 5-layered nanostructure. (P.64)

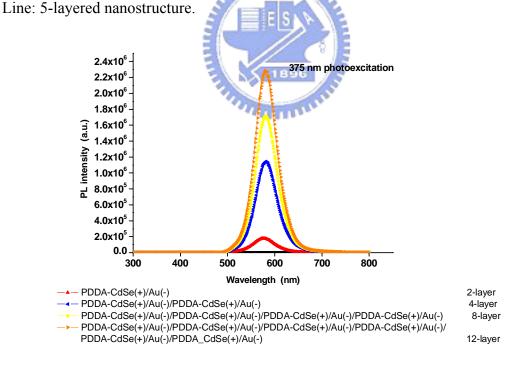

- **Figure 3.6** The PL emission spectrum of multi-layered nanostructures on quartz glass. The PL intensity of Au / AET-CdSe/ZnS multi-layer nanostructure under 375nm photo-excitation is shown above. The Black Line: 1-layered nanostructure; The Red Line: 2-layered nanostructure; The Green Line: 3-layered nanostructure; The Blue Line: 4-layered nanostructure; The Magenta Line: 5-layered nanostructure; The Yellow Line: 8-layered nanostructure; The Orange Line: 12-layered nanostructure. (P.64)

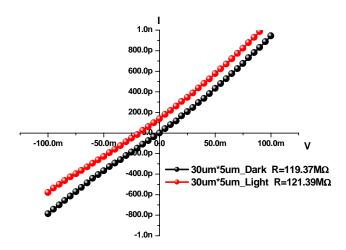

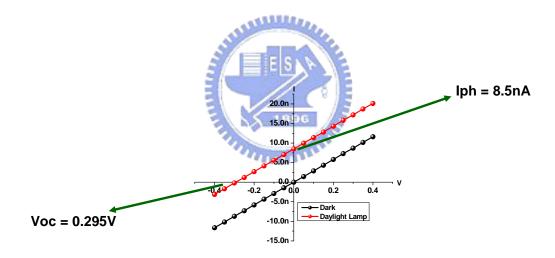

- **Figure 3.7** The I-V curve of the 30um / 5um (width / length) 4-layered PDDA-CdSe nanodevice (P.65)

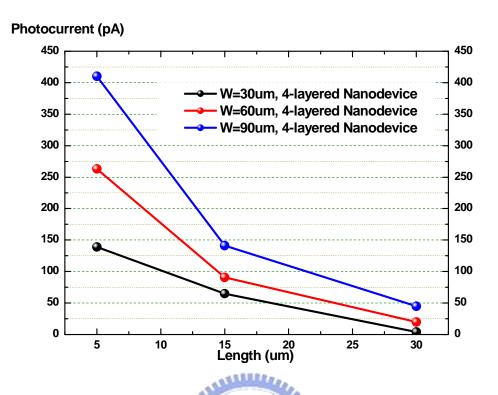

- Figure 3.8 The photocurrent comparison of the 4-layered AET-CdSe nanodevice (P.66)

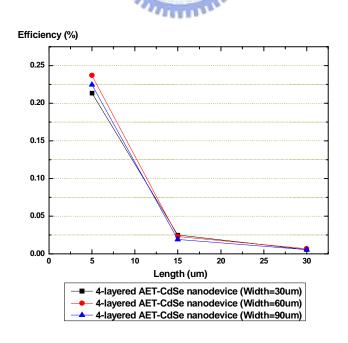

- Figure 3.9 The Efficiency comparison of the 4-layered AET-CdSe nanodevice (P.66)

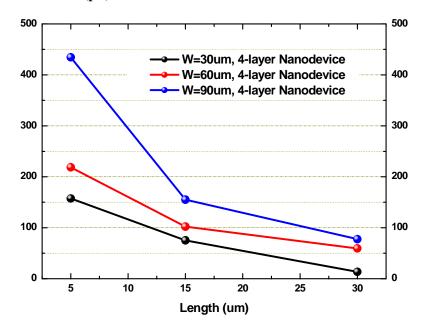

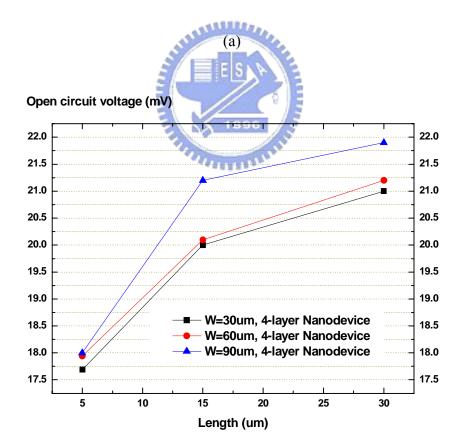

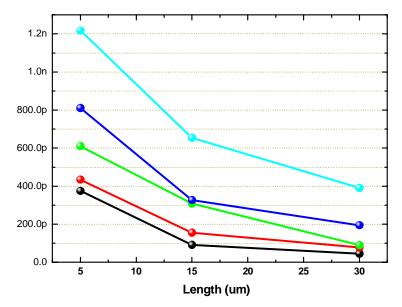

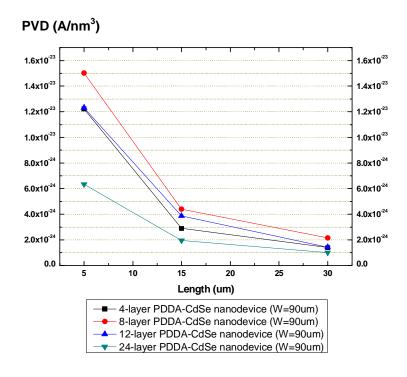

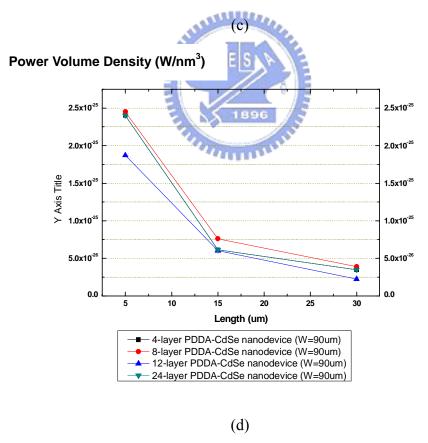

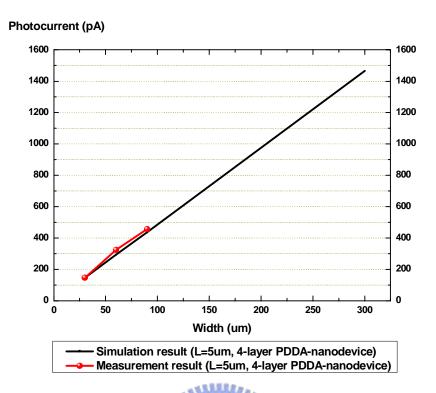

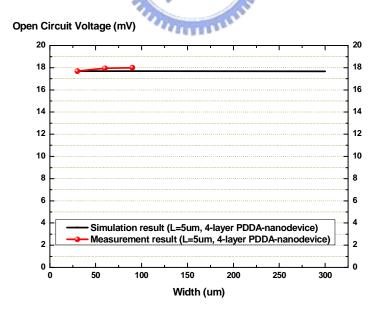

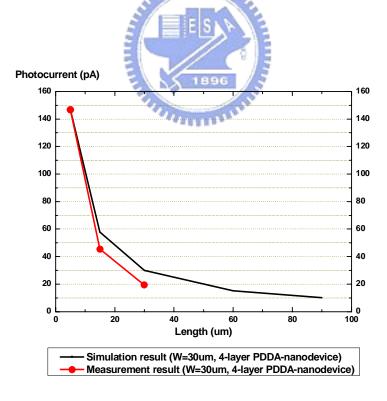

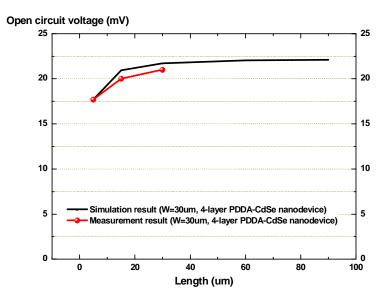

- **Figure 3.10** (a) The photocurrent comparison of the 4-layered PDDA-CdSe nanodevice (b) The open circuit voltage comparison of the 4-layered PDDA -CdSe nanodevice (c) The PVD comparison of the 4-layered PDDA -CdSe nanodevice (d) The power volume density comparison of the 4-layered PDDA -CdSe nanodevice (P.68)

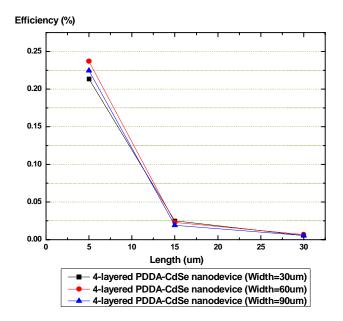

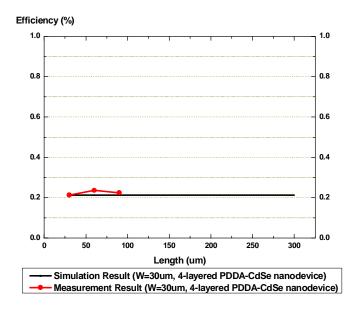

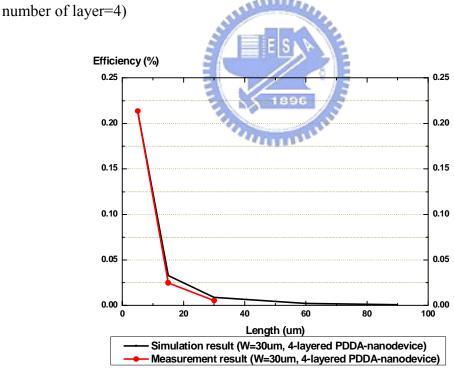

- **Figure 3.11** The efficiency comparison of the 4-layered PDDA-CdSe nanodevice (P.69)

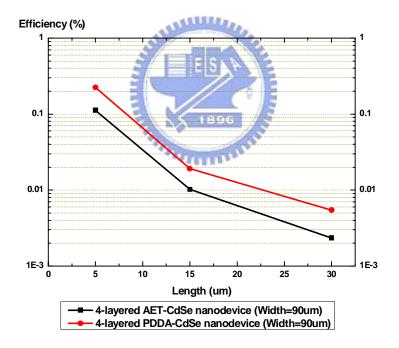

- **Figure 3.12** The efficiency comparison of the 4-layered nanodevices with different types of CdSe QDs. (P.69)

- **Figure 3.13** (a) The photocurrent comparison of the nanodevices (width = 90um) (b) The open circuit voltage comparison of the nanodevices (width = 90um) (c) The photocurrent volume density comparison of the nanodevices (width = 90um) (d) The power volume density comparison of the nanodevices (width = 90um) (P.71)

- Figure 3.14 The efficiency comparison of the nanodevices (width = 90um) (P.72)

- Figure 3.15 The efficiency comparison of the nanodevices with previous work (P.72)

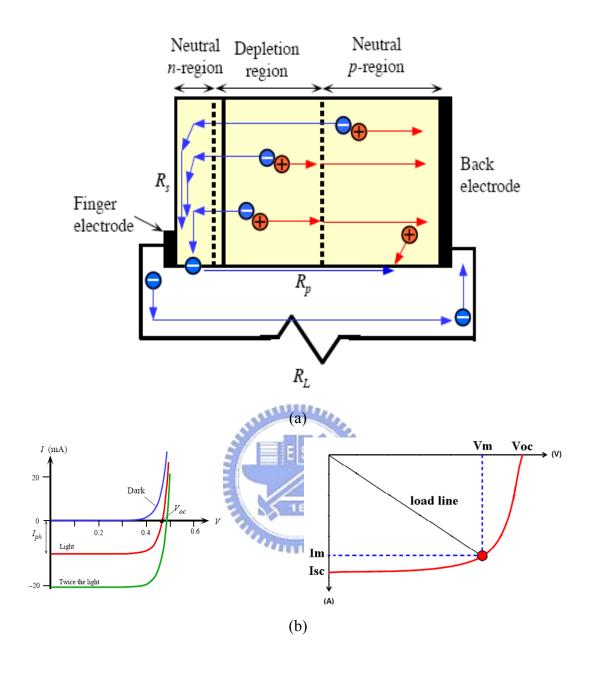

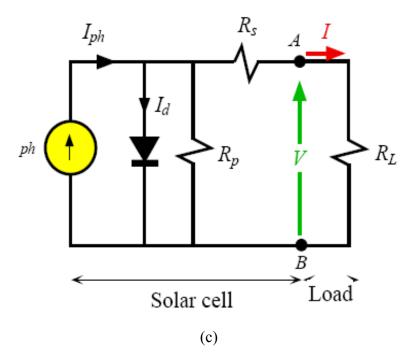

- **Figure 3.16** (a) The p-n junction solar cell structure, (b) the I-V cureve of the p-n junction solar cell, (c) the equivalent circuit of the p-n junction solar cell. (P.74)

- **Figure 3.17** The I-V curve of the Au / CdSe nanodevice (P.75)

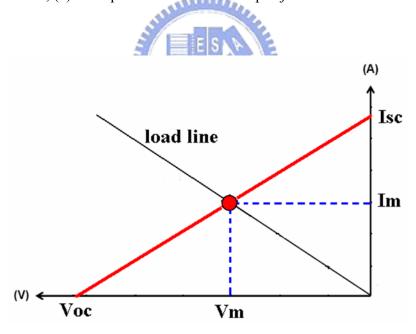

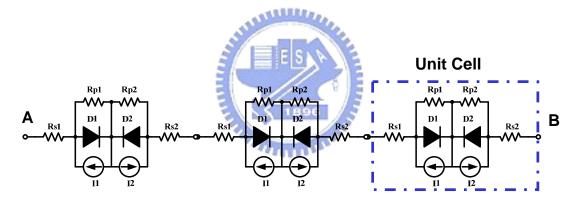

- Figure 3.18 The 1-D nanodevice model. For HSPICE simulation, Metal-Insulator-Semiconductor

- diode model was employed. (P.75)

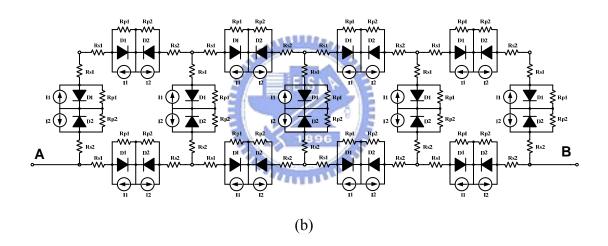

- **Figure 3.19** The 2-D nanodevice model (HSPICE). (a) The structure view of the 2-D nanodevice, (b) the 2-D nanodevice model equivalent circuit (4-layer nanodevice). For HSPICE simulation, Metal-Insulator-Semiconductor diode model was employed. (P.76)

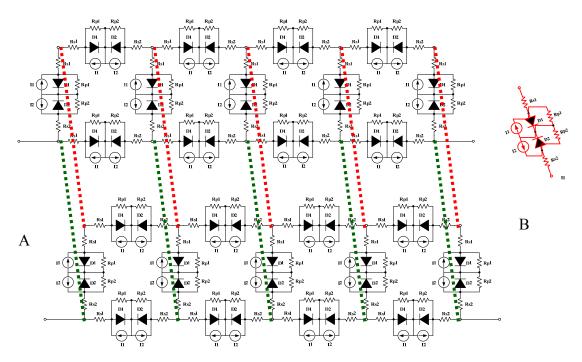

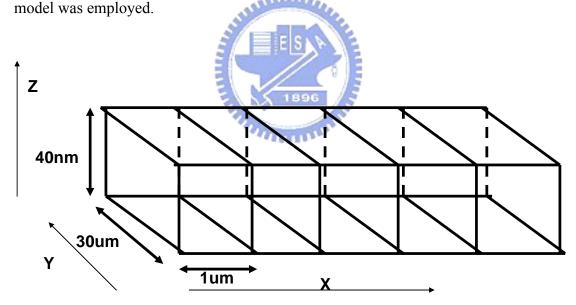

- **Figure 3.20** The 3-D nanodevice model (HSPICE). The dash line parts are substituted for the unit cells. For HSPICE simulation, Metal-Insulator-Semiconductor diode model was employed. (P.76)

- **Figure 3.21** The 3-D nanodevice model (HSPICE). The line parts are substituted for the unit cells. For HSPICE simulation, Metal-Insulator-Semiconductor diode model was employed. X-dimension unit cell: Rs=0.153M  $\Omega$ , Rp=48.178M  $\Omega$ , I=2.1nA Y-dimension unit cell: Rs=0.918M  $\Omega$ , Rp=289M  $\Omega$ , I=2.1nA, Z-dimension unit cell: Rs=6120  $\Omega$ , Rp=1.95M, I=2.1nA (P.77)

- **Figure 3.22** (Width Effect) The 3-D nanodevice model (HSPICE) simulation result. The photocurrent increases linearly as the width increases. (fixed length=5um, fixed number of layer=4) (P.78)

- **Figure 3.23** (Width Effect) The 3-D nanodevice model (HSPICE) simulation result. The open circuit voltage is a constant value. (fixed length=5um, fixed number of layer=4) (P.78)

- **Figure 3.24** (Width Effect) The 3-D nanodevice model (HSPICE) simulation result. The efficiency is a constant value when the nanodevice width varies. (fixed length=5um, fixed number of layer=4) (P.79)

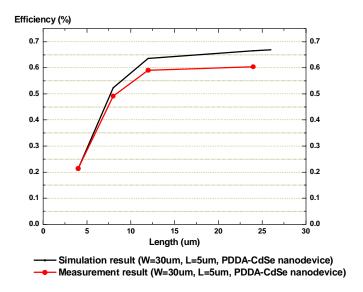

- **Figure 3.25** (Length Effect) The 3-D nanodevice model (HSPICE) simulation result. The photocurrent decreases as the length increases. (fixed width=30um, fixed number of layer=4) (P.79)

- **Figure 3.26** (Length Effect) The 3-D nanodevice model (HSPICE) simulation result. The open circuit voltage saturates as the length increases. (fixed width=30um, fixed number of layer=4) (P.80)

- **Figure 3.27** (Length Effect) The 3-D nanodevice model (HSPICE) simulation result. The efficiency decreases as the length increases. (fixed width=30um, fixed number of layer = 4) (P.80)

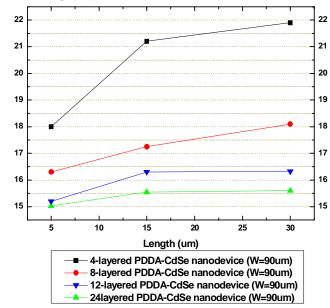

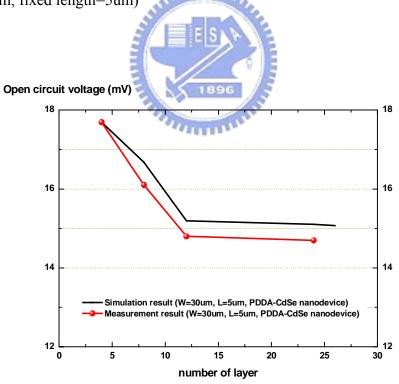

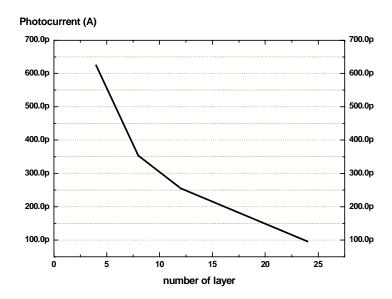

- **Figure 3.28** (Layer Effect) The 3-D nanodevice model (HSPICE) simulation result. The photocurrent saturates when the number of the layer larger than eight. (fixed width=30um, fixed length=5um) (P.81)

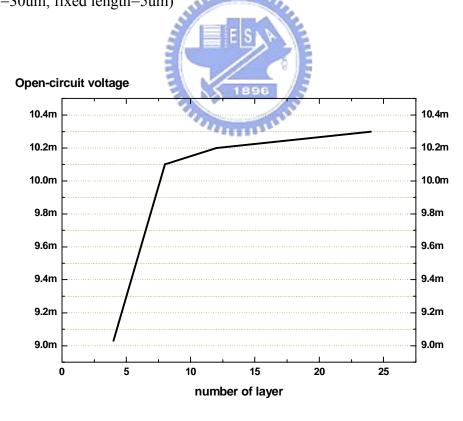

- **Figure 3.29** (Layer Effect) The 3-D nanodevice model (HSPICE) simulation result. The open circuit voltage decreases linearly, and then settles to a constant value. (fixed width=30um, fixed length=5um) (P.81)

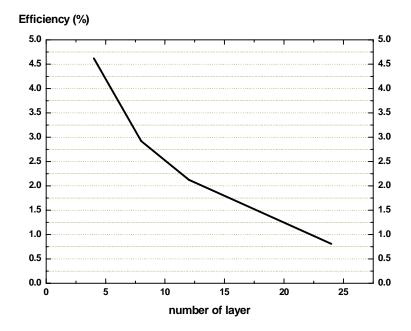

- **Figure 3.30** (Layer Effect) The 3-D nanodevice model (HSPICE) simulation result. The efficiency saturates when the number of the layer is larger than 12. According to the simulation result, the efficiency does not increase obviously if the number of the layer exceeds 26. (fixed width=30um, fixed length=5um) (P.82)

- **Figure 3.30** According to the simulation results, the better device dimension to reach the high efficiency solar cell can be decided. 26-layered nanodevices with 30um in width are adopted to predict the high efficiency. On the basis of the ideal inference, the 9.2% PDDA-CdSe nanodevice can be fabricated if the length of the device is 65nm. (P.83)

- Figure 3.31 (Vertical Structure) The 3-D nanodevice model (HSPICE) simulation result. The

photocurrent decreases when the number of the layer increases. (fixed width=30um, fixed length=5um) (P.83)

**Figure 3.32** (Vertical Structure) The 3-D nanodevice model (HSPICE) simulation result. (fixed width=30um, fixed length=5um) (P.83)

**Figure 3.33** (Vertical Structure) The 3-D nanodevice model (HSPICE) simulation result. The efficiency increases as the number of the layer decreases. (fixed width=30um, fixed length=5um) (P.84)

#### **CHAPTER 4**

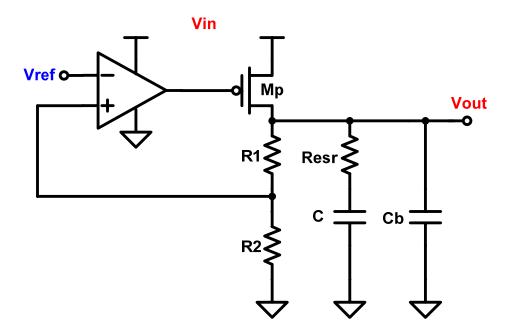

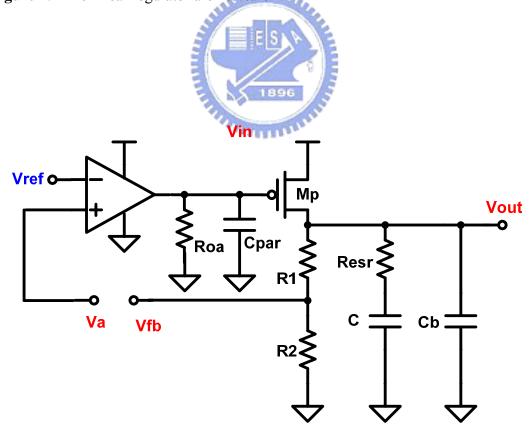

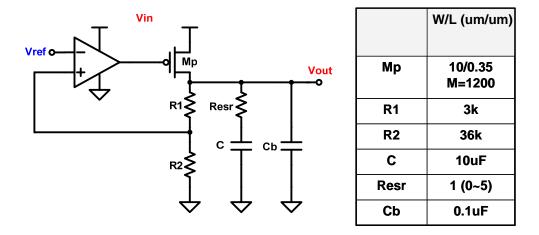

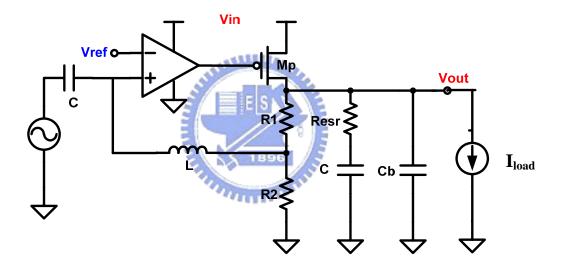

- Figure 4.1 The linear regulator architecture (P.98)

- **Figure 4.2** The System Model of the linear regulator (P.98)

- Figure 4.3 The frequency Response of the linear regulator (P.99)

- Figure 4.4 Typical linear regulator response (P.99)

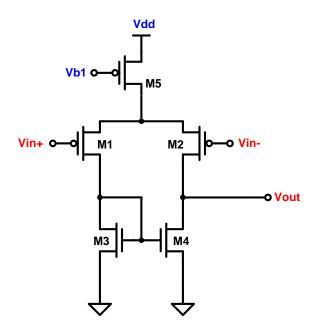

- Figure 4.5 The folded cascode amplifier (P.100)

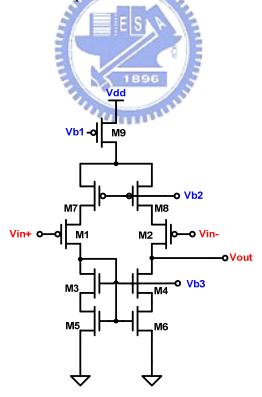

- **Figure 4.6** The telescopic amplifier (P.100)

- **Figure 4.7** The single stage amplifier (P.101)

- **Figure 4.8** The two-stage amplifier (P.101)

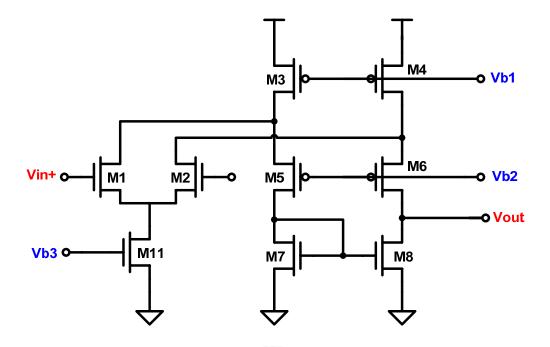

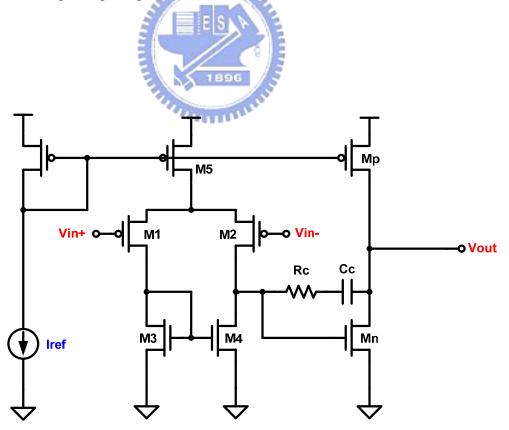

- Figure 4.9 The error amplifier (P.102)

- Figure 4.10 The bias circuit (P.102)

- **Figure 4.11**The linear regulator (P.103)

- Figure 4.12 The simulation method of the loop gain (P.103)

- Figure 4.13 The transient response of the linear regulator (P.104)

- **Figure 4.14** The chip layout view (P.104)

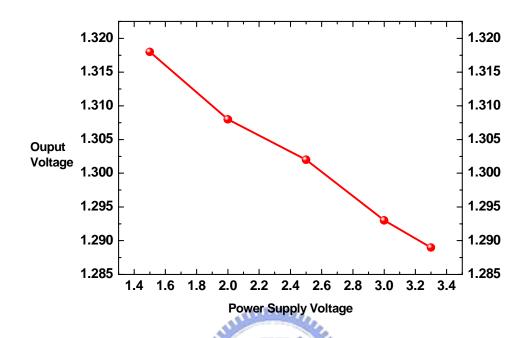

- **Figure 4.15** The measurement result of the output voltage with different power supply voltages (@ loading current = 50mA) (P.105)

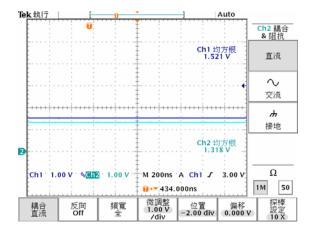

- **Figure 4.16** The measurement result of the output voltage with the lowest power supply voltages of this work 1.5V (@ loading current = 50mA) (P.105)

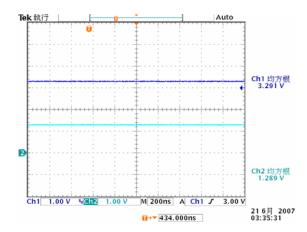

- **Figure 4.17** The measurement result of the output voltage with the highest power supply voltage of this work 3.3V (@ loading current = 50mA) (P.106)

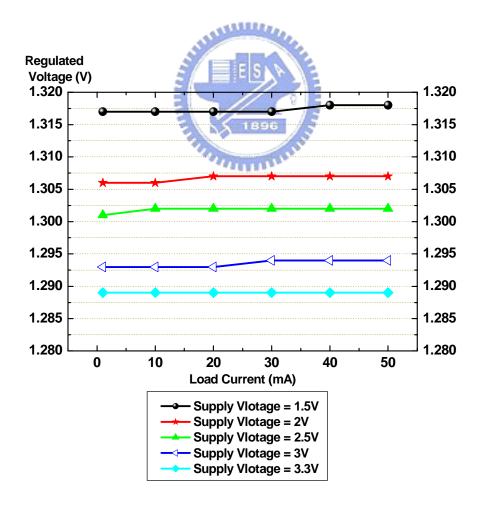

- **Figure 4.18** The measurement result of the output voltages with different power supply voltages and loading current (P.107)

# TABLE FOR FULL TEXT OF CHEMICAL REAGENTS

| Simplified<br>Form | Full Text (or Synonyms)                        | Formula                                                         | Molecular<br>Weight |

|--------------------|------------------------------------------------|-----------------------------------------------------------------|---------------------|

| TMSPED             | N-[3-(trimethoxysilyl)propyl]-ethylene diamine | C <sub>8</sub> H <sub>22</sub> N <sub>2</sub> O <sub>3</sub> Si | 222.36              |

| APTES              | 3-aminopropyltriethoxysilane                   | C <sub>9</sub> H <sub>23</sub> NO <sub>3</sub> Si               | 221.37              |

| PDDA               | Poly(diallyldimethylammonium chloride)         | $(C_8H_{16}ClN)_n$                                              |                     |

| Tyramine           | 4-(2-Aminoethyl)phenol                         | C <sub>8</sub> H <sub>11</sub> NO                               | 137.18              |

| AET                | 2-aminoethane thiol                            | C <sub>2</sub> H <sub>7</sub> NS.HCl                            | 113.61              |

#### **CHAPTER 1**

#### Introduction

#### 1.1 Background

Over the past three decades into today's powerful disciplines and knowledge that allow the engineering of advanced technical device has been developed based on fundamental chemistry, biotechnology and material science. They are focus on current approaches emerging at the intersection of materials research, nanosciences, and molecular biotechnology. The novel and highly interdisciplinary field of chemistry is closely associated with both the chemical and physical properties of organic and inorganic nanoparticles (NPs), as well as to the various aspects of molecular cloning, recombinant DNA and protein technology, and immunology. Today's materials research is used to develop instruments and techniques for basic and applied studies of fundamental biological processes [1]. The pioneering work of Pedersen, Cram, and Lehn on supramolecular aggregates held together by weak non-covalent interactions in a highly interdisciplinary effort has developed over the past 30 days into a well-established discipline. Supramolecular chemistry concerns the investigation of nature's principles to produce fascinating complex and functional molecular assemblies, as well as the utilization of these principles to generate novel device and materials, potentially useful for sensing, catalysis, transport, and other applications in medicinal or engineering science. In this area, the enormous advance attained so far is illustrated impressively by comparing materials used in last centuries electrical devices such as millimeter-sized copper wires to today's submicrometer-sized optical and electronical parts, comprised of modern conducting and electro-luminescent organic polymers [1]. The significant property of nanotechnology is its "interdisciplinary nature". The chemistry is the central science for the development of applied disciplines such as material science and biotechnology as shown in Figure 1.1. Material science, which is based on classic chemical research fields and engineering technologies, has led to enormous advances in tailoring advanced modern materials, such as ceramics, nanoclusters, and conducting polymers. For biotechnology combined with tailored biomolecules, like proteins, nucleic acids, compartments, and organelles. We can merge these disciplines to take advantage of the improved evolutionary biological components to generate new smart materials and develop future nanodevices composed of various advanced modern materials [1].

As we can see in Figure 1.2, both biotechnology and materials science meet at the same length scale. A gap currently exists in the engineering of small-scale devices. Whereas conventional top-down processes hardly allow the production of structures smaller than about 100 nm, the limits of regular bottom-up processes are in the range of about 2-5 nm. Their own dimensions show a result, two different types of compounds appear to be suited for addressing that gap: (1) biomolecular components, such as proteins and nucleic acids, and (2) colloidal NPs comprised of metal and semiconductor materials. The main concepts in the development of human civilization are the conventional top-down processes. As human technology develops, people tend to fabricate more and more delicate tools or functional devices. However, this strategy will eventually reach a limit that people cannot easily go beyond based on available technologies. For example, the structural dimensions of computer microprocessors are currently in the range of about 65 nm, which is already the highest level of conventional top-down technology. "There is plenty of room at the bottom", as Nobel physicist Richard Feynman pointed out more than 40 years ago, which best describes the central idea of nanotechnology [1]. Today's nanotechnology research puts a great

emphasis on the development of bottom-up, which concern the self-assembly of molecular and colloidal building blocks to create larger, functional device. Inorganic NPs are particularly attractive building blocks for the generation of larger superstructure. Such NPs can be prepared readily in large quantities from various materials by relatively simple methods. It can be controlled the sizes of the NPs from one to several hundred nanometers. Most often, the particles are comprised of metals, metal oxides, and semiconductor materials, such as Ag<sub>2</sub>S, CdS, CdSe, and TiO<sub>2</sub>. The NPs have highly interesting optical and electrical properties, which are very different from those of the corresponding bulk materials and which often depend strongly on the size of particles in a highly predictable way. Moreover, some types of NPs can be considered as "artificial atoms" since they are obtainable as highly perfect nanocrystals, which can be used as building blocks for the assembly of larger two-and three-dimensional structures [1].

Inorganic NPs are attractive building blocks for the construction of nanostructured materials and devices with adjustable physical and chemical properties. With a variety of inorganic NPs now at hand, the identification of chemical methods for the selective linkage of these nano-building blocks to produce nanostructured aggregates, or clusters, of controllable structure becomes increasingly important. The amine modified SiO<sub>2</sub> and carboxylic acid modified Au and CdSe NPs has been self-assembly in aqueous solution to give well-defined core-shell type cluster, whose composition can be controlled with the pH. Ligand modified 50 nm SiO<sub>2</sub>, 7 nm Au, and 6 nm CdSe NPs were employed for the electrostatic assembly [2]. Transmission electron micrographs of SiO<sub>2</sub>@Au and SiO<sub>2</sub>@CdSe composites formed at the indicated solution pH values are shown in Figure 1.3 and 1.4, respectively.

Recently, semiconductor NPs are being vigorously investigated as new materials for traditional electronic and optical applications, as chemical and biological sensors,

and as building blocks for conceptually novel molecule-based devices. Most of these practical implementations of nanotechnology will require the immobilization of NPs on various substrates in the form of thin films. One of the new techniques that can be used for NP processing in thin films is the layer-by-layer assembly on polyelectrolyte has been proposed. It affords a high degree of structural control and quality of the coatings. [3]. However, the forces that make the assembly to happen are similar to those that involve in the interaction between molecules, such as hydrogen bonds, coulombic force, and Van der Waals force [1] [2] [3].

In general, with work involving self-assembly processes, nucleotides with various lengths were employed to take advantage of their self-recognition and self-assembly abilities [4]. The synthesis of ~ 15 nm Au NPs by Citrate Reduction method and ~ 5 nm CdSe NPs by Tyramine-modification method was reported in literatures, which provide negative-charged and positive-charged on the surface of the NPs, respectively [4][5]. For further study, the resulting solution consisting of Tyramine-modified CdSe NPs was vacuumed to dryness and re-dissolved in D.I. water [6]. In order to modify the silicon oxide substrate provide amino groups (-NH3<sup>+</sup>) for assembling of Colloidal Au NPs, the silicon oxide substrate was immersed in a 10% N-[3-(trimethoxysily)propyl] ethylene diamine (TMSPED) / methanol solution for several time and further washed by methanol to remove excess TMSPED [7]. Recent research in several of nanodevices / nanostructures with unique optical and electrical properties has increased significantly. Among these nanodevices / nanostructures, semiconductor NPs exhibited spectacular size-dependent properties when the particles size is less than 10 nm, and producing the quantum-effect [8]-[10]. As the particles size becomes smaller, the band gap becomes larger, resulting in the blue shift of UV-visible absorption spectrums [11]. For metal NPs, the Fermi level lies at the center of one continuous band. As a result in literatures, across the entire

size range, the optical and electrical behaviors of metal NPs are described using classical equations for corresponding bulk metal material rather than quantum mechanical concepts [12]. Most recently, a 350 nm diameter Au-CdSe-Au nanowires were fabricated using a template growth method, and can function as sensitive photo sensors, which can potentially be massively multiplexed in devices of small size [13]. However, the fabrication process and the electrofluidic alignment method of nanowires as described in the study were not feasible with conventional silicon chip. Consequently, since the potential application of this device on silicon chip is severely limited, a new nanomaterials and/or a new process for the fabrication of nanodevice on silicon chips arise. The process of assembling negative-charged Au NPs and positive-charged CdSe NPs onto the silicon chip has been developed and proposed in [14].

#### 1.2 Reviews on Nanodevice

Several of the assembly processes, inorganic nanoparticles (NPs) and nanoclusters are the most attractive ones. Recently, the researches on the synthesis, characterization and applications of inorganic NPs have been increasing significantly. The inorganic NPs have some advantages: (1) Many well-developed synthesis methods of the NPs have been proposed, which are often simple and cheap for large quantity preparation. (2) The NPs have their unique optical, electronic, and catalytic properties, which are quite different from those of their corresponding bulk materials. For example, when the size of NP becomes smaller than its Bhor exciton radius (~6 nm for CdSe NP), the photo-excited electrons are delocalized. (3) The size of NPs, conventionally ranging from one to hundreds of nanometers, is particularly suitable

for them to serve as building blocks for the assembly of larger nanostructures and contact closely with the micro systems, like the silicon chips.

In this section, we review some significant experiments about nanodevices composed of nanomaterials or NPs. One of the methods to construct nanodevices is the self-assembly techniques, which provide a means to realize structures such as quantum dots (QDs), NPs and other electronic / optoelectronic device configurations. Because these techniques do not rely on lithography to realize the specific nanostructures and assemblies, they can represent efficient, high throughput fabrication approaches. For self-assembled semiconductor structures, the electronic device functionality has been limited by the difficulty in achieving suitable interfaces for passivating and contacting the resulting islands or dots [15]. A patterning method of trapping and deposition of NPs in a submicron narrow gap have been developed in recently year. It demonstrated a light-emitting device, which consists of NPs trapped in the gap of lateral electrodes. The CdSe/ZnS NPs in the solvent were electrostatically trapped as a dielectric material in the gap by lateral electric field. The NPs were deposited in the gap as the solvent was evaporating. Electroluminescence from the NPs in the gap was observed when current was applied through the lateral electrodes [16]. Fig 1.5(a) shows a schematic diagram of the method. It was able to fabricate an ultra small light source smaller than the wavelength of visible light. This small light source can be applied to optical devices, such as scanning probes, integrated photonic crystals, and so on. The fabrication process of the submicron sized light source was shown in Figure 1.5(b). At first, an electrode structure on p-type SOI was made with DRIE (The Alcatel A601E), and then a submicron gap was fabricated by cutting the electrode structure with Focused Ion Beam (FIB) that can enable us to fabricate a submicron narrow gap easily. Next, the wafer was immersed in NPs solution of toluene solvent, and applied the voltage to the gap between the lateral electrodes to trap NPs. At last, wafer was annealed at 400°C to remove excess organic molecules such as toluene and TOPO. After annealing, junctions between p-type Si and CdSe/ZnS NPs were built [16].

The synthesis of quasi-one-dimensional (1D) nanostructures has been developed, many of which have interesting electronic, optical, and chemical sensor properties that derive from size, composition, and shape. One-component systems are now quite common, but there are few examples of methods for synthesizing multi-component materials composed of organic and inorganic materials. The hybrid multi-component (i.e. organic-inorganic) nanorods that have either diode or resistor properties has been proposed in [17]. In a typical experiment, the synthesis of segmented metal-polymer nanorods by electrochemical deposition of gold into alumina templates, followed by electrochemical polymerization of pyrrole (Ppy). During the electrodeposition process, it can control the length of each block by monitoring the charge. Other metals (e.g. Ag and Cd) with low work functions and inorganic semiconductors (e.g. CdSe), also can be deposited on top of the polymer block and polyaniline can be used in place of polypyrrole. This allows one to prepare multi-component rod structures with tailorable electronic properties that derive from the choice of the individual compositional blocks. For the Au portions of the nanostructure (contacts 1-2 and 3-4) exhibit linear I-V characteristics and bulk metallic behavior at room temperature as shown in Fig. 1.7(A), and demonstrate Ohmic behavior. For the Au-Ppy-Au system, one can see dark Ppy domains sandwiched between two bright segments of gold as shown in Fig. 1.6(A). Significantly, Fig. 1.7(B) shows the I-V measurements across the Ppy block of the Au-Ppy-Au nanorod (2-3 and 1-4 contacts) also exhibit a highly reproducible, linear response at room temperature but nonlinear behavior at low temperature (<175 K), characteristic of a semiconductor. The I-V curves and the corresponding electrical

conductivities provide two important observations. First, the conductivity of the polymer block at room temperature is 6 orders of magnitude lower than the metallic blocks, and all data are consistent with Ohmic contact between the Ppy-Au junctions. Second, the I-V response for the Au-Ppy-Au nanorod becomes slightly nonlinear as the temperature decreases [Fig. 1.7(B)]. Since the Ppy for the nanostructures discussed herein were generated by oxidative polymerization, they are p-type semiconductor. Continuously, four-segment nanorods (Au-Ppy-Cd-Au) also can be prepared via an analogous procedure [Fig. 1.6(B)]. I-V measurements on devices constructed from single Au-Ppy-Cd-Au rods exhibit "diode" behavior at room temperature as shown in Fig. 1.7(C), and the typical response is asymmetric and non-Ohmic. In the forward bias, there is a positive voltage on the Au block adjacent to the Ppy and negative potential on the Au block interfaced with the Cd block. Therefore, holes move from the Ppy block to the Cd block during the forward bias. In reverse bias, current does not flow until the bias overcomes the breakdown potential (-0.61 V). The turn-on voltage for these diode nanorods is approximately 0.15V. The I-V characteristics of the Au-Ppy-Cd-Au nanorods at room temperature suggest that an Schottky-like junction is formed at Ppy/Cd due to the difference in work functions of the two materials and an Ohmic junction at the Ppy/Au interface due to the similarity in work functions for the two materials. It is a powerful method for deliberately producing structures with desirable electrical properties with a straightforward synthetic procedure that offers a high degree of reproducibility [17]. These structures could be useful for a wide range of electronic and sensor devices.

Now, we will introduce the state of current and coming solar photovoltaic technologies and their further development. The emphasis is on R&D advances and cell and module performances, with indications of the limitations and strengths of crystalline (Si and GaAs) and thin film (a-Si:H, Si, Cu(In,Ga)(Se,S)<sub>2</sub>, CdTe). The

contributions and technological pathways for *now and near-term* technologies (silicon, III–V, and thin films) and status and forecasts for next-next generation photovoltaic (organics, nanotechnologies, multi-multiple junctions) are evaluated. Recent advances in concentrators, new directions for thin films, and materials/device technology issues are discussed in terms of technology evolution and progress. Insights to technical and other investments needed to tip photovoltaic to its next level of contribution as a significant clean-energy partner in the world energy portfolio [18]. The research progress over the past 25–30 years has been substantial and steady, as shown in Fig. 1.8. Photovoltaic is poised at what may be its most critical tipping point; the one that will cause this technology to "spread like wildfire" as it finally becomes a major part of our world's energy portfolio.

Recently, in order to provide innovative strategies for designing next generation energy conversion devices, people efforts to design ordered assemblies of semiconductor and metal NPs as well as carbon nanostructures. Renewable energy such as solar radiation is ideal to meet the projected demand but requires new initiatives to harvest incident photons with higher efficiency, for example, by employing nanostructured semiconductors and molecular assemblies. Dye sensitization of mesoscopic TiO<sub>2</sub> has been widely used in this context. Power conversion efficiencies up to 11% have been achieved for such photochemical solar cells. Semiconductors such as CdS, PbS, Bi<sub>2</sub>S<sub>3</sub>, CdSe, and InP, which absorb light in the visible, can serve as sensitizers as they are able to transfer electrons to large band gap semiconductors such as TiO<sub>2</sub> or SnO<sub>2</sub>. CdSe quantum dots (QDs) have been assembled onto mesoscopic TiO<sub>2</sub> films by using bifunctional surface modifiers (SH-R-COOH) [19]. During visible light excitation, CdSe QDs inject electrons into TiO<sub>2</sub> nanocrystallites. The injected charge carriers in a CdSe-modified TiO<sub>2</sub> film can be collected at a conducting electrode to generate a photocurrent. The TiO<sub>2</sub>-CdSe

composite, when employed as a photoanode in a photoelectrochemical cell, exhibits a power conversion efficiency of 12%. Significant loss of electrons occurs due to scattering as well as charge recombination at TiO<sub>2</sub>/CdSe interfaces and internal TiO<sub>2</sub> grain boundaries. Fig. 1.9 shows the assembled TiO<sub>2</sub> and CdSe NPs using bifunctional surface modifiers of the type HS-R-COOH. Fig. 1.10 shows the sequence of steps followed.

One approach to facilitating electron transport in nanostructured semiconductor films involves applying a positive bias to the working electrode. The photocurrent generated at different applied potentials for OTE/TiO<sub>2</sub> and OTE/TiO<sub>2</sub>/CdSe electrodes is shown in Fig. 1.11. Excitation of TiO<sub>2</sub> and TiO<sub>2</sub>/CdSe films was carried out using light with wavelengths greater than 300 and 400 nm, respectively. Both films show anodic photocurrents when subjected to band gap excitation. The observed photocurrents increase as the potential is swept toward positive values. The potential at which we observe zero current is a measure of the flat band potential and reflects the maximum attainable open-circuit voltage ( $V_{oc}$ ). We observe zero current at potentials of -0.78 and -0.88 V vs. SCE for TiO<sub>2</sub> and TiO<sub>2</sub>/CdSe films, respectively. The 100 mV shift represents the improved energetic of the TiO<sub>2</sub>/CdSe films and shows the advantage of using composite nanostructures for boosting  $V_{oc}$  [19].

#### 1.3 Motivation

As we have discussed previously, interactive forces between molecules, such as hydrogen bonds, Van der Waal force, and coulombic force, are also effective for NPs and play an important role in the assembly process. The researches on the synthesis of organic and inorganic NPs have been increased significantly. Among the semiconductor NPs, CdSe QDs or QDs is the most suitable for harvesting light energy

in the visible region of the solar spectrum. So many researchers always choose the CdSe QDs or QDs to realize the nanodevices, optical devices, and solar-like devices. Recently, the photo-sensing nanodevice composed of negative-charged Au and positive-charged Tyramine-CdSe QDs has been developed and proposed. This functional nanodevice composed of inorganic NPs directly on the surface of silicon chip is the simplest and most effective process and without damage of the circuits in silicon chip. However, the method of Tyramine modification on CdSe QDs will seriously damage the optical and electrical properties of CdSe NPs. Therefore, it is important to develop more efficient methods. In our works, we propose another modify method of CdSe QDs and follow the 'dipping-and-washing' process to improve the performance of Au / CdSe nanodevice, continuously, we also construct another nanodevice composed of CdSe-modified QDs based on "self-assembly technology".

Meanwhile, to correctly define the pattern of the QDs and NPs, lift-off process was utilized for this purpose. Finally, three dimension nanodevice model is simulated by HSPICE. It successfully explains the phenomenon of the characteristics of the nanodevice. The power conversion efficiency can achieve 40% based in our ideal interference on the basis of the 3-D nanodevice model.

#### 1.4 THESIS ORGANIZATION

The background has been introduced in section 1.1, including the basic concepts, the trend of nanotechnology development in the world, the synthesis methods of Au and CdSe QDs, and several of assembly methods of NPs on silicon substrate. Then, we have some reviews on the most representative experiments about nanodevices

based on nanomaterials, QDs, and NPs in section 1.2. At last, the motivations of this work and thesis organization will be proposed in section 1.3 and section 1.4.

In chapter 2, the fabrication technology will be discussed, including the process flow and the nanodevice structure design concepts. In section 2.1 and 2.2, the synthesis of Au NPs and CdSe QDs will be introduced. Then, the physical characteristics of the nanodevices will be demonstrated. In section 2.4, some experiments of the environment factors were tested to optimize the reaction conditions. In section 2.5, the electrode process with the lift-off technology will be proposed to solve the unexpected NPs and QDs. In section 2.6, the self-assembly technology of the nanodevice process is announced.

In chapter 3, experimental results will be showed and discussed. First, the measurement environment is introduced in the section 3.1. Secondly, the nanostructure physical characteristics would be demonstrated, for example, SEM view and absorption / emission Spectra. Thirdly, different layer Au / CdSe (AET-CdSe and PDDA-CdSe) Nanodevice would be measured. Then, the results would be showed and discussed in section 3.3. Next, Nanodevice solar cell efficiency would be estimated in section 3.5. Finally, using HSPICE software to construct the nanodevice model was executed in section 3.6. The simulation result fits the nanodevice measurement results, and it also could explain the electrical characteristics of the different dimension nanodevice.

In chapter 4, a linear regulator is designed to target the low voltage conditions and integrated with the CdSe / Au nanoparticle solar cell. The relevant analysis is introduced to design the system, and the TSMC 2P4M CMOS 0.35um technology is used to implement the linear regulator. Finally, the measurement result of the linear regulator chip is showed and discussed.

In chapter 5, the conclusions and future works are given in section 5.1 and 5.2.

**Figure 1.1** Chemistry is the central science for further applications such as materials science and biotechnology. The combination of advanced materials and tailored biomolecules will produce the future nanodevices [1].

**Figure 1.2** A gap currently exists in the engineering of small-scale devices. The top-down processes will have their limit below 100 nm, and the bottom-up processes will also have a limit at  $2\sim5$  nm. The gap will be filled by nanoclusters and biomolecules [1].

**Figure 1.3** The TEM images of  $SiO_2@Au$  NP clusters synthesized at (A) pH=8.4, (B) pH=8.6, (C) pH=10.2, (D) pH=11.1. The scale bar for all micrographs is 200 nm [2].

**Figure 1.4** The TEM images of SiO<sub>2</sub>@CdSe NP clusters synthesized at (A) pH=6.8, (B) pH=7.2, (C) pH=10.2, (D) pH=11.1. The scale bar for all micrographs is 100 nm [2].

**Figure 1.5** (a) The schematic diagram of trapping NPs in a submicron narrow gap (5  $\mu$ m \* 5  $\mu$ m \* 1  $\mu$ m) and a submicron sized light source. (b) The fabrication process of a submicron sized light source based on SOI and CdSe QDs [16].

**Figure 1.6** (A) Optical microscope image of Au-Ppy-Au rods. (B) Optical microscope image of Au-Ppy-Cd-Au rods. The lower left inset shows the corresponding FESEM image [17].

**Figure 1.7** The measurement results of I-V characteristics. (A) For the gold blocks (1-2, 3-4) within a single nanorod at room temperature. Inset shows the optical microscope image (1000 magnification) of a single Au-Ppy-Au rod on microelectrodes. (B) Temperature-dependent I-V curves for measurements across electrodes 2 and 3. (C) For a single Au-Ppy-Cd-Au rod at room temperature [17].

**Figure 1.8** The efficiency evolution of best research cells by several of technology types. This table identifies those cells that have been measured under standard conditions and confirmed at one of the word's accepted centers for standard solar-cell measurements [18].

**Figure 1.9** (a) Linking CdSe QDs to TiO<sub>2</sub> particles with bifunctional surface modifier (HS-R-COOH); (b) Light harvesting assembly composed of TiO<sub>2</sub> film functionalized with CdSe QDs on Optically Transparent Electrode (OTE) [19]. (Not to scale)

**Figure 1.10** The sequence of steps for linking CdSe QDs to TiO<sub>2</sub> surface with a bifunctional surface modifier [19].

**Figure 1.11** I-V characteristics of (a) OTE /  $TiO_2$  and (b) OTE /  $TiO_2$  / MPA /CdSe films. The filtered lights allowed excitation of  $TiO_2$  and CdSe films at wavelengths greater than 300 and 400 nm, respectively [19].

#### **CHAPTER 2**

# FABRICATION TECHNOLOGIES OF CdSe / Au NANOPARTICLES AND NANODEVICE

In this chapter, the fabrication technology will be discussed, including the process flow and the nanodevice structure design concepts. In section 2.1 and 2.2, the synthesis of Au NPs and CdSe QDs will be introduced. Then, the physical characteristics of the nanodevices will be demonstrated. In section 2.4, some experiments of the environment factors were tested to optimize the reaction conditions. In section 2.5, the electrode process with the lift-off technology will be proposed to solve the unexpected NPs and QDs. In section 2.6, the self-assembly technology of the nanodevice process is announced.

#### 2.1 The Synthesis of Citrate-Capped Au Nanoparticles

Au NPs with ~ 15 nm diameter were prepared by citrate reduction of HAuCl<sub>4</sub> as described in literature [4]. The pale yellow HAuCl<sub>4</sub> solution (1 mM, 500 mL) was prepared and brought to reflux while stirring for 20 minutes. A solution of citric acid (38.8 mM, 50 mM) was then quickly injected into the flask. The color of the solution changed from pale yellow to deep red indicating the formation of Au NPs. After color changing, the solution was kept in reflux for additional 20 minutes and then standing in room temperature for another 30 minutes. Finally, the solution was

filtered through  $0.45~\mu m$  Nylon filter. The flow diagram of the Au NPs solution preparation is shown in Figure 2.1. The close photograph of the Au NPs solution is shown in Figure 2.2(a), (left). The TEM image of the approximately 15 nm diameter Au NPs is shown in Figure 2.3(a) and the UV-visible absorbance spectrum of Au NPs solution is shown in Figure 2.3(b).

### 2.2 The Synthesis of AET-Capped and PDDA-Capped CdSe Quantum Dots

The emission efficiency, spectrum and time evolution of QDs are strongly affected by the surface. A better surface structure of QDs can provide higher stability, higher quantum yield and longer lifetime. Mostly the CdSe QDs lose a large portion of emission efficiency because of electron leakage resulting from the surface defect. Therefore, ZnS layer, a large band gap semiconductor, is used to passivate the surface and improve the quantum yield of CdSe NPs. The band gap diagram and the surface structures of CdSe/ZnS QDs are shown in Figure 2.4(a). It shows the PL intensity spectrum, which confirms the superior quantum yield property of CdSe/ZnS structure over the other two structures, CdSe and CdSe/CdS. The approximately 5 nm diameter fluorescent water-soluble ((PDDA)-coated) and (2-aminoethane thiol (AET)-coated) CdSe/ZnS QDs were obtained from Prof. Teng-Ming Chen's lab, National Chiao Tung University, Taiwan. The surface of the AET-coated CdSe/ZnS NPs had positive-charged amino groups (-NH3<sup>+</sup>). In this section, we will to introduce the synthesis procedure of CdSe/ZnS QDs.

#### Synthesis of water-soluble AET-capped CdSe/ZnS QDs

In order to prepare positive charge on the NPs surface, the water stabilized amine terminating QDs (NP-NH<sub>2</sub>) was fictionalized. Adding methanol washed off the HDA stabilizing layer and rendered a cloudy suspension which was centrifuged and the pellet containing QDs were washed with methanol 4 times to re-dissolve into chloroform. 1.0M 2-aminoethane thiol (AET) was added to the above solution and allowed to react for 2hrs. When ZnS capped CdSe QDs were reacted with AET, the mercapto group in AET bind to the Zn atoms and render the QDs hydrophilic, in addition to facilitating further functionalization possibilities. After the reaction, excess AET was washed off with methanol/chloroform mixed solution and store into the D.I. water.

The close photographs of the AET-CdSe/ZnS QDs solution is shown in Figure 2.2(a), (right). Figure 2.2(b) shows the close photographs of the mixture of 100 µL Au NPs solution and 100 µL AET-modified CdSe/ZnS QDs solution just after mixing (right), the mixture after standing 6 hrs (middle) in room temperature, and the mixture after standing 5 days in room temperature (left). As we can see, the color of mixture just after mixing was like that of Au NPs solution. However, after 6 hrs, it became dark purplish red. After 5 days, there was obvious precipitate at the bottom and the supernatant became pale yellow. The TEM image of the approximately 5 nm diameter CdSe/ZnS QDs is shown in Figure 2.3(a) and the UV-visible/PL spectra of CdSe/ZnS QDs solution is shown in Figure 2.3(c). The detailed modification processes of AET-capped CdSe/ZnS QDs are shown in Figure 3.5.

The PDDA-CdSe QDs are provided by Prof. Teng-Ming Chen's Lab.

#### 2.3 The Physical Characteristics of Au Nanoparticles and CdSe Quantum Dots

Recently, many several of nanostructures or nanoparticles (NPs) have been proposed and improved significantly. They have their unique electrical and optical properties, herein, in order to achieve the Nanodevice that has good performance; we must know their electrical and optical properties as well as the size and the synthesis procedure of the NPs. In nanometer-scaled metal particles, for examples Au or Ag, are certain to be important fundamental building blocks of future nano-scale electronic and optical devices. However, there are numerous challenges that need to be addressed before NPs technologies can be implemented successfully. Metal particles comprise a fundamentally interesting class of matter in part because of an apparent dichotomy that exists between their sizes and many of their physical and chemical properties. For example, Au particles may be synthesized in diameters that span from the macroscopic down to the molecular scale (0.8 µm). Across almost this entire size regime, however, their electrical and optical behaviors are described with relatively simple classical equations, rather than the quantum mechanical concepts required understanding molecular entities. The classical free electron theory combined with optical constants for bulk gold is employed to successfully model the intense visible extinction of Au NPs. Moreover, the electrical and optical properties of metal particles can be tuned considerably simply by adjusting the size, shape, or extent of aggregation of the particles. For example, a typical solution of 13 nm diameter Au NPs is red in color and exhibits a surface plasmon band centered at 518-520 nm. After aggregation, the extended polymeric Au NPs/polynucleotide aggregate shows a red to purplish blue color change in solution, due to a red shift in surface plasmon resonance of Au NPs [4]. The optical property of Au NPs is dominated by collective oscillation of conduction electrons resulting from the interaction with electromagnetic radiation. The electric field of incoming radiation induces the formation of a dipole in the NP. A restoring force in the NP tries to compensate for this, resulting in a unique resonance wavelength. The oscillation wavelength depends on particle size, particle shape and surrounding medium. [27]

In semiconductor nanocrystals, however, exhibit a wide range of size-dependent properties when the size regime is below 10 nm [9] [11]. Variations in fundamental characteristics ranging from phase transitions to electrical conductivity can be induce by controlling the size of the crystals [11]. There are two major effects to explain these size variation properties in nanocrystals. First, the number of surface atoms is a large fraction of the total atoms of a single nanocrystal. The high surface-to-volume ration will make a contribution to variations in thermodynamic properties of nanocrystals, such as melting point, and solid-solid phase transition. Second, nanocrystals with the same interior bonding geometry as the corresponding bulk material but with only a few hundred to thousand atoms exhibit dramatic size-dependent optical and electrical properties. These variations are because the density of states of electronic energy levels transforms as a function of the size of interior nanocrystal, known as quantization effects [11]. Nanocrystals lie in between the atomic and molecular limit of discrete density of electronic states and the extended crystalline limit of continuous bands.

The diagrams of density of states in metal and semiconductor nanocrystals are shown in Figure 3.6. Now in any material, there will be a size below which there is substantial variation of fundamental electrical and optical properties with size, which will be seen when the energy level spacing exceeds the temperature. For a given temperature, this occurs at a very large size in semiconductors, as compared to metal, insulators, and Van der Waals or molecular crystals. This can be understood by

considering that the bands of a solid are centered about atomic levels, with the width of the band related to the strength of nearest-neighbor interactions. As the size of solid increases, the center of a band develops first and the edges develop last. Thus, in metal, the Fermi level lies in the center of a band, so that the relevant energy level spacing is still very small, and at temperature above a few Kelvin, the electrical and optical properties of a metal solid react more closely like those of no energy level spacing, even as small as tens or hundreds of atoms. In semiconductor, however, the Fermi level lies between two bands, so that the edges of bands dominate the low-energy optical and electrical behavior. Optical excitations across the gap depend strongly on the size, even for crystallites as large as 10,000 atoms. Besides, the HOMO-LUMO gap increases as the semiconductor nanocrystals become smaller (bellow 10 nm) [11].

In this work, we used positive-charged 2-aminoethane thiol (AET)-capped CdSe/ZnS (core/shell) NPs of approximately 5 nm in diameter as photoreceptors to detect lamination with above band gap photoexcitation [11]. We proposed two nanodevices composed of semiconductor QDs and/or metal NPs for self-assembly: (1) Au / AET-CdSe/ZnS. (2) Au / PDDA-CdSe/ZnS. However, some properties about CdSe QDs we must know that the **exciton Bohr radius**  $r_b$  is the spatial extent of the electron hole pair in material and is defined as  $r_b = 4\pi\hbar^2\epsilon$  / (m \* e²), where  $\hbar$  is the Plank's constant,  $\epsilon$  is the permittivity in bulk material, and m\* is the effective mass. For CdSe semiconductor, the electron's effective mass is 0.13 m<sub>e</sub> and hole effective mass is 0.45 m<sub>e</sub>. So the exciton Bohr radius of CdSe is calculated to be 4.9 nm [8] [9]. If the dimension of CdSe QDs is smaller than 4.9 nm, the **quantum confinement** of electron hole pairs effects significantly. As size is reduced, the electronic excitation shift higher energy, and there is concentration of oscillator strength into a few transitions [9]. The dynamics of the charge carriers in CdSe QDs have been studied in

several reports. These studies revealed that photoexcitation leads to a bleach of the lowest exciton transition within the first few hundred femtoseconds [20]. The bleach recovery has a lifetime between several picoseconds to microseconds, which is similar to the lifetime of the photoluminescence. In literature, it is well known that electron acceptors adsorbed on the surface of CdSe QDs quench the exciton emission by fast electron transition [20]. Monitored the electrons shuttling across the interface of CdSe QDs by femtosecond laser spectroscopy and showed that in CdSe QDs with no electron acceptors adsorbed on the particle surface, the excited electrons get trapped at the surface within 30 ps. Subsequently, electron-hole recombination takes place on a much longer time period of  $> 10^{-7}$  s [20]. This is quite a useful knowledge for understanding the dynamics of electrons in CdSe QDs.

The electrical transport properties of nanocrystals also depend strongly on size. On extended crystal, the energy required to add successive charges does not vary. In a nanocrystal, the presence of one charge prevents the addition of another charge. Thus, in metal or semiconductor, the current-voltage curves of individual nanocrystal resemble a staircase, known as **Coulomb blockade effect** [11]. Steps in the staircase are spaced proportional to 1/radious of nanocrystal. A typical Coulomb blockade staircase is shown in Figure 3.7.

### 2.4 The Self-assembly Process of Au Nanoparticles / CdSe Quantum Dots Nanodevice with Lift-off Technology

In order to measure and utilize the power generated from the Nanodevices, the electrodes are required. Hence, the electrodes are prepared before the NPs and QDs process. The electrode cross-section view is shown as the Figure 2.8. The aluminum is used as the conductor to collect the current. On the other hand, the oxide layer is

utilized as the dielectric to prevent the substrate current flow to the aluminum. This phenomenon will cause the incorrect result to the measurement outcome.

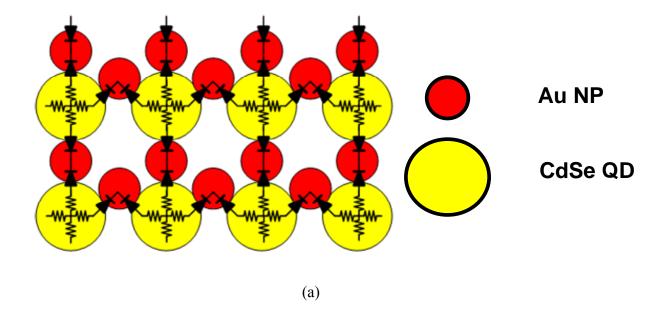

In previous chapter, we have discussed the forces that direct the assembly of NPs is similar to those involving in the interaction between molecules, such as hydrogen bonds, coulombic force, and Van der Waal force. In this work, we utilize the coulombic force system control the assembly of NPs on the silicon substrate. In coulombic force system, we take advantage of the positive or negative charges on the surfaces of NPs to induce repulsion or attraction forces between different NPs or between NPs and the substrate. The repulsion force will prevent NPs from random aggregation before assembled on the substrate. On the other hand, the attraction force will assemble NPs on the substrate. By well controlling the two forces, we are able to construct the structure of photo-sensing nanodevice on the silicon oxide substrate effectively. The overall fabrication process of the photo-sensing nanodevice composed of CdSe QDs and Au NPs on the silicon chip by ionic interaction system is shown in Figure 2.14.

As the structure shown in Figure 2.9, one mask is needed to define the aluminum region (Figure 2.8(a)). The process flow of the electrodes process is demonstrated in Figure 2.10(a)-(g). First, the wafer was cleaned to remove the particles and organics on its surface as the Figure 2.10(a) shown. Secondly, thermal oxidization was carried out to form the oxide film as the dielectric layer as the Figure 2.10(b) demonstrated. The thickness of the oxide layer is 500nm. According to the standard process, the thickness is thick enough to prevent the substrate current from flowing onto the aluminum. Then, the next stage was to coat the aluminum on the oxide by the thermal coater. The thickness of the aluminum is 5 um. The cross-section view and the top-view of the process is shown in Figure 2.10(c). After thermal coating, the photoresist was coated on the surface of the aluminum to define the electrode region

at the next step (Figure 2.10(d)). The samples were exposed by utilizing the mask (Figure 2.8(a)) designed to define the electrode patterns (Figure 2.10(e)). Then, use the acid to etch the aluminum. Meanwhile, the photoresist protected the auminum designed to remain (Figure 2.10(f)). Therefore, the desire pattern was constructed. Finally, remove the photoresist by using the acetone, and the electrode process finished (Figure 2.10(g)).

In previous work, some problems were generated when the self-assembly technology was executed. As the Figure 2.11(a) shown, according to the SEM picture, some unexpected NPs and QDS appears. Therefore, the anticipated patterns of the electrode were disturbed by connecting with other electrode through the thin film composed of NPs and QDs. It is clear that unexpected NPs and QDs have influence on the measurement result. This phenomenon may be caused by the presence of the –OH groups on the surface of the electrodes, which can be modified by TMSPED molecules, making them suitable sites for NP assembly. The presence of NPs on the Al electrodes enhances continuity at the interface between the NP's packed silicon oxide surface and the Al electrodes. Identically, it also enhances continuity at the interface between the NP's packed passivation oxide surface and the Al electrodes. That is the reason why it is necessary to solve this problem.

Turning now to the current flowing path analysis, in figure 3.8(b), the cross-section view of the whole chip shows there are two paths for the current to flow. One is the major path that contains the metal line between the electrodes and the pads. The other is the minor path composed of the NPs and QDs. This path has low conductance because of the CdSe QDs, but it still provides a way for the photocurrent to flow. The unexpected QDs and NPs create the path for the photocurrent. As a result, the measurement of the electrodes (30umX5um, 30umX15um) is affected. To solve the problem issued above, one method to remove the unexpected NPs and QDs is

proposed. Lift-off technology is used in this work to realize the purpose.

First of all, the issue if the lift-off technology damages the nanostructure is concerned. The acetone is used in lift-off process to dissolve the photoresist and bring out the substance attached to the photoresist. Therefore, the acetone should not destroy the nanostructure. The experiment was executed to observe if the acetone destructs the physical characteristics of the nanostructure.

In general, the lift-off process needs the samples immersed in the acetone for a period. Therefore, this condition is simulated. Several 4-layer nanostructure samples were immersed for three kinds of different periods, 0 minute, 15 minutes and 30 minutes. Finally, the samples were observed under PL (Photoilluminace) measurement. Figure 2.12 shows the result of this experiment. The PL emission spectrum of 4-layer nanostructures on quartz glass is shown. The PL of the nanostructure decays as the immersed time increases. There is enough evidence to show that the acetone would damage the nanostructure optical properties.

According to the experimental result, the lift-off process must be executed without CdSe QDs. Therefore, the lift-off is implemented after the first Au-NP-layer is constructed.

Now, the lift-off process will be introduced below. The process flow is shown in the Figure 2.13. In the beginning, the electrode samples were prepared. Then, the samples were coated with photoresist on their surface as the Figure 2.13(a) shown. Next, the samples were exposed by using the definition of the mask 2 (Figure 2.8(b)). In this process, the region we want it to lift off was blocked by the mask (Figure 2.13(b)). In turn, the samples were put into the developer after they were exposed. The photoresist on the region that was exposed was removed (Figure 2.13(c)). In order to modify the electrode surface with positive charges, the electrode surface was modified by N- [3-(trimethoxysilyl) propyl] ethylene diamine (TMSPED) to make the

electrode surface provide amino groups (-NH3<sup>+</sup>) as the Figure 2.13(d) shown. The sample was immersed in 10% TMSPED/methanol solution for 5 minute [7]. Note that because TMSPED is very moisture sensitive, the methanol used here must be completely dried and all cleaned glasswares must also be dried in oven at 65°C for 30 min prior to use. After immersion, the sample was cleaned by plenty of methanol to remove excess TMSPED staying on the surface, followed by dipping in 30 mM HCl for 3 seconds to protonate the amino groups. Finally, the silicon oxide substrate was cleaned by using plenty of D.I. water for several times and dried in vacuum. Subsequently, Citrate-capped Au NPs (~15 nm) were self-assembled to the TMSPED linkers. In order to construct photo-sensing nanodevice structures, the TMSPED-modified electrode sample was immersed in the Au NPs solution for 24 hours to make negative-charged (-COO<sup>-</sup>) Au NPs assembled on the positive-charged (-NH3<sup>+</sup>) substrate by ionic interaction. Au NPs were coated not only on the electrode part but also on the photoresist region. Therefore, Au NPs were coated on the entire wafer (Figure 2.13(e)).

Next, the most important step of the experiment was to lift off the unexpected part where the Au NPs were on the photoresist. Then, the samples were immersed in the acetone for 5 minutes as Figure 2.13(f) shown. The Au NPs on the photoresist were remove with the photoresist. Therefore, the structure of the nanodevice is shown in Figure 2.46(g). After this step, the sample was immersed in the Au NPs solution for 24 hours again to confirm if the Au NPs were coated with high density.

After 24-hour-immersion, the sample was cleaned by D.I. water for several times to remove free Au NPs and then dried in vacuum. Subsequently, the sample was immersed in AET-capped CdSe/ZnS QDs solution for 24 hours to make positive-charged (-NH<sub>3</sub><sup>+</sup>) AET-CdSe/ZnS QDs assembled to negative-charged (-COO). Au NPs, followed by D.I. water cleaning and vacuum dry as described above.

Theoretically, this process can be repeated for several times to form layers of closely packed CdSe QDs and Au NPs nanostructures. As a result, it can be used as the photovoltaic nanodevice. The measurement result and discussion will be investigated in the following chapter.

#### 2.5 Reaction Environment Investigation

We may now proceed to investigate the environment factor which would have effect on the nanostructure, for example, reaction temperature and reaction time. These effects should be optimized. Accordingly, several experiments to affirm the suitable reaction condition for the nanodevice to fabricate were executed.

As a matter of fact, to construct the nanostructure is like to build the building. The base of the nanostructure should have high density. In this work, the base of the nanostructure is Au NPs which form the thin film. Therefore, if the density of the Au NPs is high, the second layer would also get high. The reason is that CdSe QDs assemble with Au NPs.

Hence, two experiments were executed. One is to observe the reaction time effect on the nanostructure construction. The other is to investigate the reaction temperature effect. Owing to the SEM picture of the nanodevice, we can judge which condition gets high density.

The first experiment is to observe if the different reaction time influence the nanostructure. Therefore, two piece of p-type silicon wafer was prepared. One was to be coated with Au NPs and CdSe QDs as a 2-layer basic nanostructure for 3 hours per layer. The other was to be coated in the same way, but 24 hours per layer reaction period. The result is shown as Figure 2.15. Figure 2.15(a) is the nanostructure that was fabricated with 3 hours reaction time per layer. Figure 2.15(b) is the

nanostructure that was constructed with 24 hours reaction time per layer. As a result, the 24-hour-reaction-time one got high particle density. It benefits the nanodevice construction.

The other experiment is to investigate the temperature effect on the nanostructure construction. Hence, two piece of p-type silicon wafer was prepared. One was to be coated with Au NPs and CdSe QDs as a 2-layer basic nanostructure in the room temperature environment. The other was to be coated in the same way, but in the 4°C reaction environment. Figure 2.16 shows the experiment outcome. As the Figure 2.16(a) shown, the nanostructure which was constructed on condition of the room temperature got lower density.

On the basis of the previous two experiments, lower temperature and longer reaction period would benefit the nanostructure. Thus, these two factors would be adopted in the nanodevice fabrication technology.

1896

Figure 2.1. The flow diagram for preparing the Citrate-capped Au NPs solution.

**Figure 2.2.** (a) The close photographs of 100 μL of approximately 15 nm diameter Au NPs solution + 100 μL DI water (left) and 100 μL of approximately 5 nm diameter AET-CdSe/ZnS NPs solution + 100 μL DI water (right). The Au NPs solution was in deep red while the AET-modified CdSe/ZnS NPs solution was in yellow. (b) The close photographs of the mixture of 100 μL Au NPs solution and 100 μL AET-modified CdSe/ZnS NPs solution just after mixing (right), the mixture after standing 6 hrs (middle) in room temperature, and the mixture after standing 5 days in room temperature (left). As we can see, the color of mixture just after mixing was like that of Au NPs solution. However, after 6 hrs, it became dark purplish red. After 5 days, there was obvious precipitate at the bottom and the supernatant became pale yellow.

**Figure 2.3.** (a) The TEM image of Citrate-capped approximately 15 nm diameter Au NPs and the TEM image of AET-capped approximately 5 nm diameter CdSe/ZnS NPs. (b) The UV-visible spectrum of Au NPs solution. (c) The UV-visible and PL intensity spectrum of MSA-CdSe/ZnS or AET-CdSe/ZnS NPs solution.

**Figure 2.4** (a) The band gap and surface structure diagram of CdSe/ZnS NP. (b) The PL intensity spectrum of different kind of surface capping method of CdSe NP.

Figure 2.5 The flow diagram for preparing the AET-capped CdSe/ZnS QDs solution.

**Figure 2.6** Density of states in metal (A) and semiconductor (B) nanocrystals. In each case, the density of states is discrete at the band edges. The Fermi level is in the center of a band in a metal, and so kT will exceed the level spacing even at low temperature and small size. In semiconductor, the Fermi level lies between two bands, so that there is large level spacing even at large size. The HOMO-LUMO gap increases as the semiconductor nanocrystals of smaller size (bellow 10 nm) [11].